Selex Sistemi Integrati DMEH2 AVIATION SERVICES DME TRANSMITTER User Manual TECHNICAL DESCRIPTION Manual

Selex Sistemi Integrati Inc. AVIATION SERVICES DME TRANSMITTER TECHNICAL DESCRIPTION Manual

Contents

- 1. USERS MANUAL 1

- 2. USERS MANUAL 2

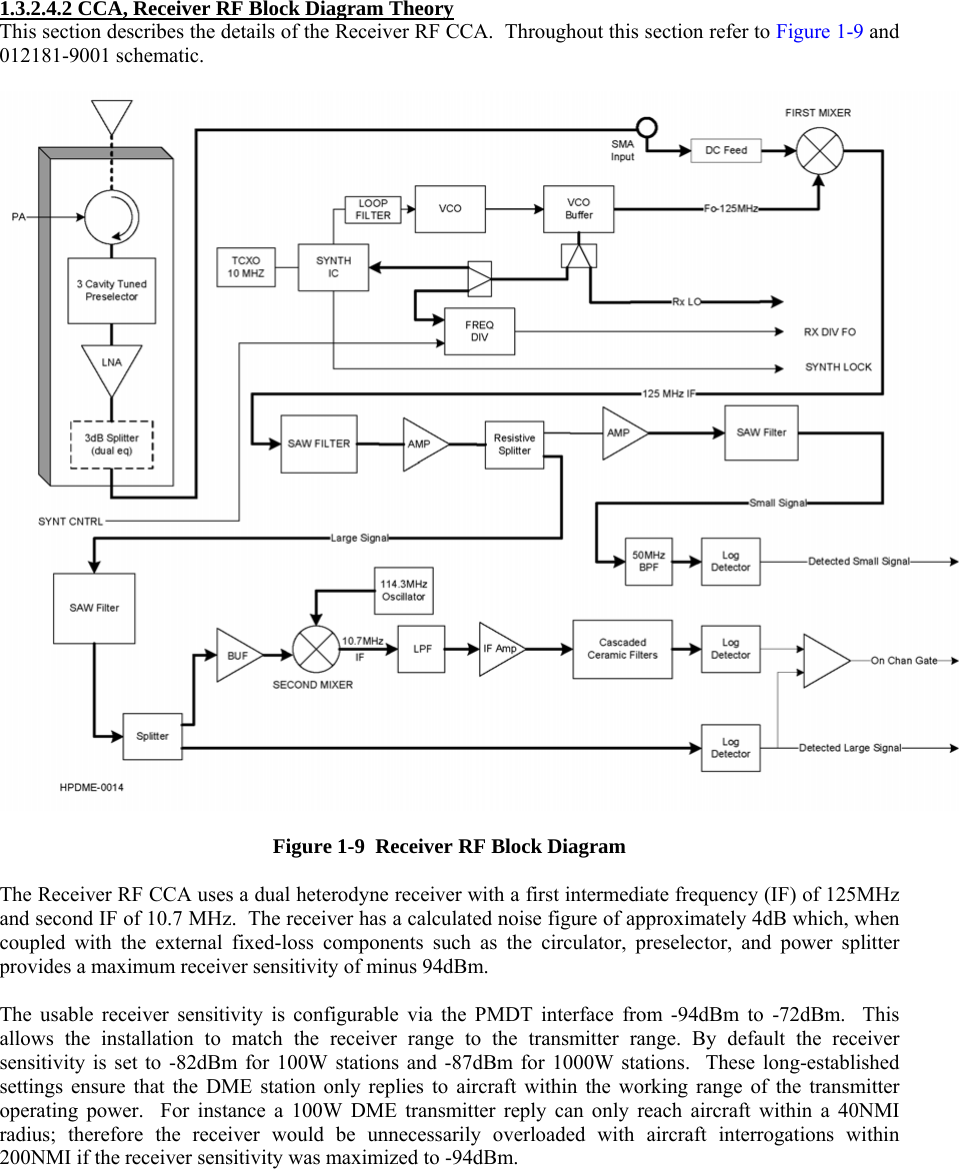

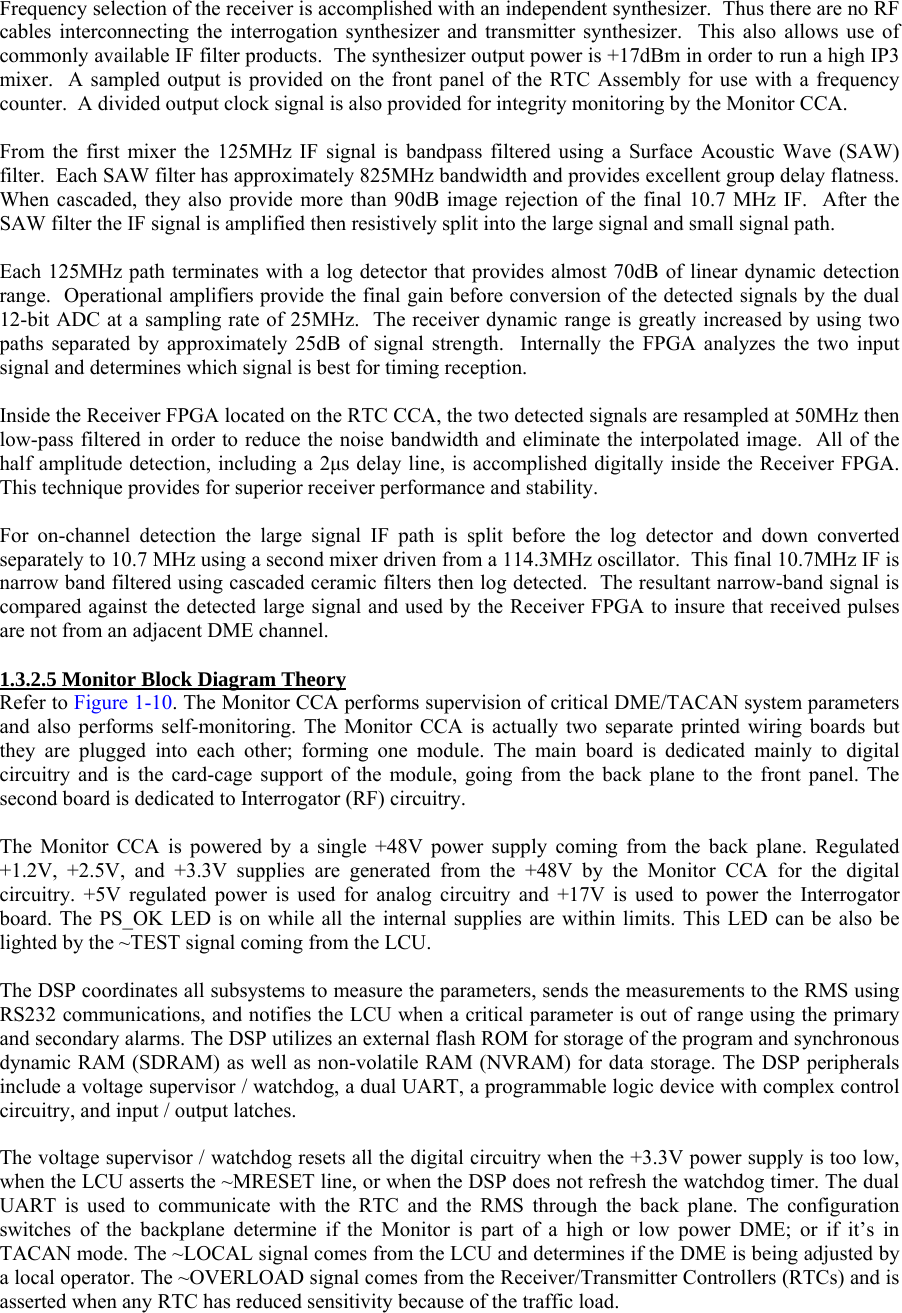

USERS MANUAL 2