# Datasheet Bluetron<sup>™</sup> Module BTR602

# **Key Features**

- A small and cost effective Bluetooth<sup>®</sup> System

- Bluetooth<sup>®</sup> specification v2.1 +EDR compliant

- •Class 2, up to 10-meter range

- Transmit RF power, up to +4dBm

- Receive sensitivity, up to -85dBm@BER = 0.1%

- Complete 2.4GHz Bluetooth® System including:

- Hardware: Radio, Baseband ,Crystal, MCU, Regulators & ROM

- Standard Firmware: HCI stack 23C

- Integrated 1.8V & 1.5V regulators (linear mode)

- •Compact size: 28.2 mm x 15.0 mm x 2.8 mm

- ■SDIO (Bluetooth type A) & UART @4Mbps interfaces

- Auristream Codec (16, 24, 32, 40kbps), transmit power is minimized

- •Built-in PCM or I2S interfaces

- •Surface mount module for embedded applications

- Chip Antenna on board or External antenna design

- IEEE 802.11 coexistence

- •Green (RoHS & Halogen free)

- ■Operating & Storage temperature within -40° C to +85° C

# Description

**Bluetron™ BTR602 module** from AvantWave is a complete Bluetooth<sup>®</sup> solution for fast implementation, cutting your time-tomarket. It is a short-range, compact and cost effective radio/baseband module that can be implemented in any kind of electronic devices, such as Bluetooth hands-free car kit, PDA and Mobile phone handset etc.

In standard configuration the module includes a baseband processor with on board 4M Bytes ROM memory, a radio front-end, supporting circuitry, able to connect with some higher-levels external software protocols and applications such as HSP, HFP, A2DP, AVRCP are coexisted with the external Host MCU (via I2S interface DAC codec).

The **Bluetron<sup>™</sup> BTR602 module** is a power class 2 Bluetooth<sup>®</sup> device, and is in compliance with version 2.1 +EDR of the Bluetooth<sup>®</sup> specification. It is supplied with Bluetooth<sup>®</sup> HCI stack firmware which runs on the internal microprocessor. **Bluetron<sup>™</sup> BTR602 module** is built on CSR BC06 QFN ROM core with ROM memory for firmware and application software storage.

# **Applications**

Automotive Car Kit Applications

PDAs

Mobile Phones

Cellular Handsets

# Software

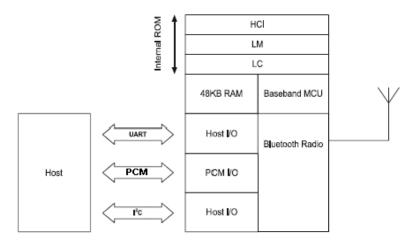

The lower layers of the Bluetooth stack (HCI) runs on-package. An external microcontroller is required. Bluetron™ BTR602 is integrated with a digital ADPCM low power CODEC, and interface to power management circuit.

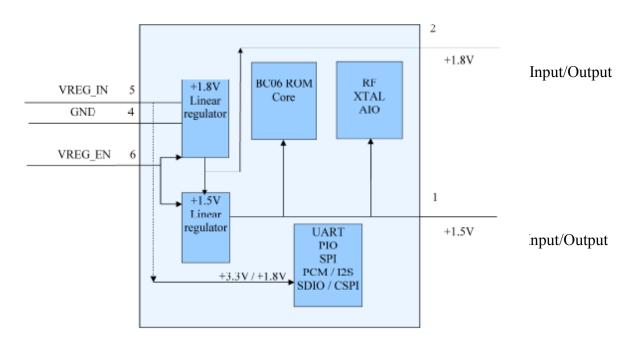

Fig. 1 System block diagram

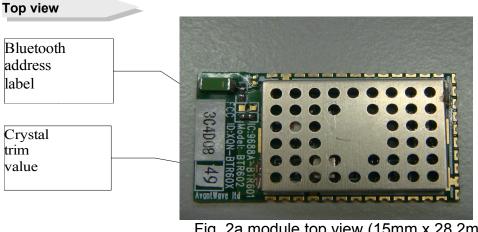

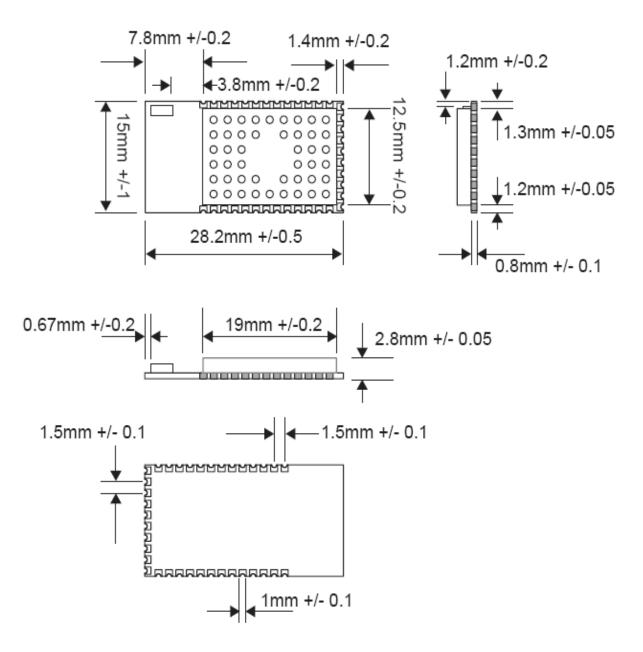

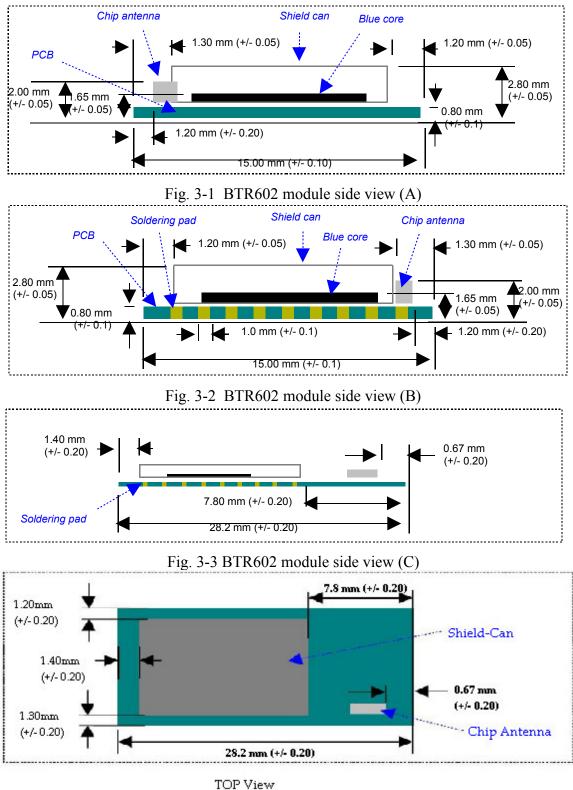

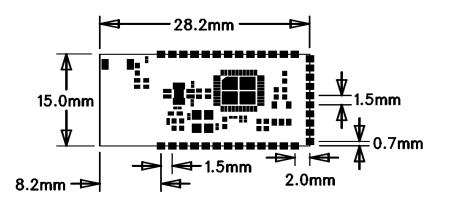

## **Mechanical Specification**

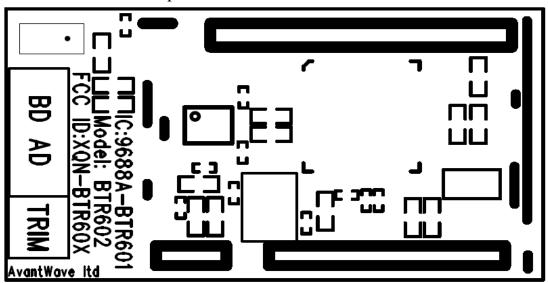

Fig. 2a module top view (15mm x 28.2mm)

Fig. 2b module bottom view

Page 2 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

Tel: (852) 2648 9887 Fax: (852) 2646 3713 inquiry@avantwave.com

**Bottom view**

#### Sectional view

Fig. 3-4 BTR602 module Top view (D)

\*\* All terminations surface finishing are coated by the Electroless Nickel immersion gold (ENIG) material, the advantages of the ENIG are good conductive, high solder-ability and excellent wettability,,etc.

Page 4 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

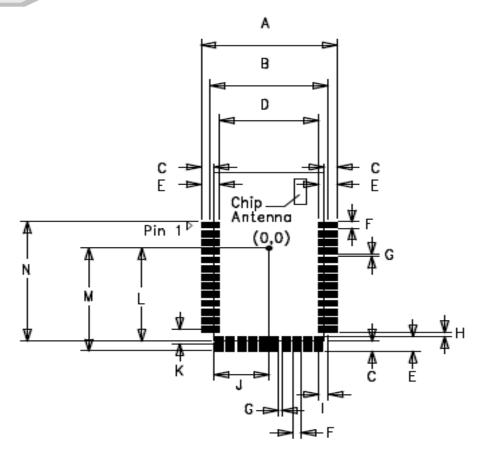

Suggested Land Pattern

Fig.4a BTR602 module recommended PCB Land Pattern

| Symbol      | Dimension(mm) | Description                       |  |  |  |  |

|-------------|---------------|-----------------------------------|--|--|--|--|

| Α           | 18.50         | Outer width                       |  |  |  |  |

| В           | 16.00         | Center width                      |  |  |  |  |

| С           | 1.75          | Pad length outer from module edge |  |  |  |  |

|             | 13.50         | Inner width                       |  |  |  |  |

| D<br>E<br>F | 2.50          | Pad length                        |  |  |  |  |

| F           | 1.10          | Pad width                         |  |  |  |  |

| G           | 0.40          | Inner gap                         |  |  |  |  |

| Н           | 0.70          | Inner gap                         |  |  |  |  |

|             | 1.30          | Center pad to center pad          |  |  |  |  |

| J           | 7.50          | Module center to module edge      |  |  |  |  |

| ĸ           | 2.50          | Center pad to center pad          |  |  |  |  |

| L           | 16.00         | Module center to module edge      |  |  |  |  |

| м           | 17.70         | Module center to pad edge         |  |  |  |  |

| N           | 20.55         | Module edge to pin1 edge          |  |  |  |  |

|             |               |                                   |  |  |  |  |

## Table 1 Land Pattern Dimensions

Remark: all dimensions may have some tolerance within +/- 10%

Terminal Coating: The BTR602 module pads finishing material is flash gold over nickel (ENIG). The thickness is around 0.05 to 0.25 micron. It is the metallic surface finish plated onto the copper base by means of a chemical decomposition process

Page 5 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

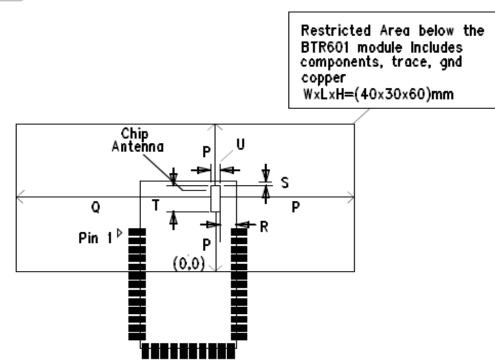

Fig.4b BTR601 module Antenna & its restricted area

| 15.00 | Antenna restricted area                        |

|-------|------------------------------------------------|

|       | Automu usstaisted ansa                         |

| 25.00 | Antenna restricted area                        |

|       | Antenna edge to right side pcb edge            |

|       | Antenna edge to top side pcb edge              |

| 4.2   | Antenna pad to pad length<br>Antenna pad width |

|       | 1.0<br>0.67<br>4.2                             |

## Table 2 restricted area dimensions

Restricted Area assumption: It is a reference guideline to suggest the application PCB designer about how to maximize the RF performance, generally, the restricted area should be as large as possible to attain the better performance. And the restricted area is different shape or size due to different application's PCB design. The basic concept is related to avoid obstacles around the Antenna. So, there is suggested a restricted area surround the on board Antenna with the certain dimension (>BT wavelength ~12.5cm long). For the height of restricted area, it also depends on different applications feasibility. The height supposed to be +z/-z axis (+65mm/-65mm) in order to totally achieve as long as BT wavelength(65mm+65mm). It is a reference only but not definitely can be achieved for all applications.

For the shield can cover area(P), it is simulate the EVB ground plane design of the Chip Antenna datasheet. The ground plane is replaced by the shield can(short to ground). The purpose is minimized the interference from/to the module.

Page 6 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

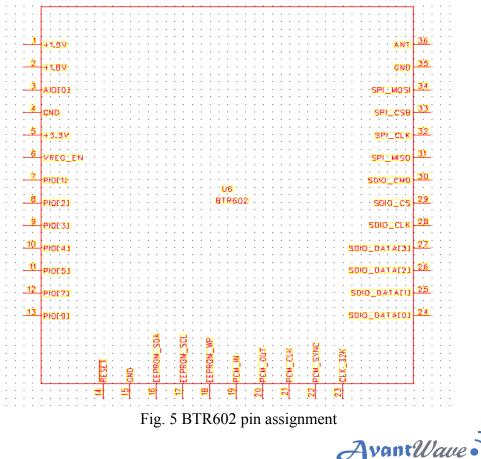

# **Pin Description**

| Terminal | Name         | Description                                            |

|----------|--------------|--------------------------------------------------------|

| 1        | +1.5V        | +1.5V voltage supply input /output(default)            |

| 2        | +1.8V        | +1.8V voltage supply input/ output(default)            |

| 3        | AIO[0]       | Analog Programmable input/output line                  |

| 4        | GND          | Ground pin                                             |

| 5        | VREG_IN      | voltage supply input                                   |

| 6        | VREG_EN      | Enable the high-ion LDO regulator, active high input   |

| 7        | PIO[1]       | Programmable input/output line                         |

| 8        | PIO[2]       | Programmable input/output line                         |

| 9        | PIO[3]       | Programmable input/output line                         |

| 10       | PIO[4]       | Programmable input/output line                         |

| 11       | PIO[5]       | Programmable input/output line                         |

| 12       | PIO[7]       | Programmable input/output line                         |

| 13       | PIO[9]       | Programmable input/output line                         |

| 14       | /Reset       | Reset pin, active low input                            |

| 15       | GND          | Ground pin                                             |

| 16       | EEPROM_SDA   | EEPROM serial address/data (input / output)            |

| 17       | EEPROM_SCL   | EEPROM serial clock input                              |

| 18       | EEPROM_WP    | EEPROM write protect input                             |

| 19       | PCM_IN       | PCM synchronous data input                             |

| 20       | PCM_OUT      | PCM synchronous data output                            |

| 21       | PCM_CLK      | PCM synchronous data clock input(slave)/output(master) |

| 22       | PCM_SYNC     | PCM synchronous data sync input(slave)/output(master)  |

| 23       | CLK_32K      | 32kHz external reference clock input                   |

| 24       | SDIO_DATA[0] | Synchronous data input/output                          |

|          | CSPI_MISO    | CSR SPI Master in Slave out output                     |

|          | UART_TX      | UART data output, active high                          |

| 25       | SDIO_DATA[1] | Synchronous data input/output                          |

|          | CSPI_INT     | CSR SPI interrupt output                               |

|          | UART_RTS     | UART request to send, active low output                |

| 26       | SDIO_DATA[2] | Synchronous data input/output                          |

|          |              |                                                        |

| Terminal | Name         | Description                                                      |

|----------|--------------|------------------------------------------------------------------|

|          | UART_RX      | UART data input, active high                                     |

| 27       | SDIO_DATA[3] | Synchronous data input/output                                    |

|          | CSPI_CS#     | Chip select for CSR SPI, active low input                        |

|          | UART_CTS     | UART clear to send, active low input                             |

| 28       | SDIO_CLK     | SDIO Clock input                                                 |

|          | CSPI_CLK     | CSR SPI Clock input                                              |

| 29       | SDIO_CS      | SDIO chip select to allow SDIO Accesses input                    |

| 30       | SDIO_CMD     | SDIO data input                                                  |

|          | CSPI_MOSI    | CSPI Master out Slave in input                                   |

| 31       | SPI_MISO     | SPI Master in Slave out output                                   |

| 32       | SPI_CLK      | SPI clock input                                                  |

| 33       | SPI_CSB      | Chip select for SPI, active low input                            |

| 34       | SPI_MOSI     | SPI Master out Slave in input                                    |

| 35       | GND          | Ground pin                                                       |

| 36       | ANT          | 50 ohm impedance RF port input/output<br>Table 3 Pin Description |

\*\* CSR SPI interface is an extension of SPI interface, 8 bit command, 24 bit address, 16 bit burst length \*\* SDIO is a host interface that allows a SDIO host to gain access to the internal of the core.

Page 8 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

Tel: (852) 2648 9887 Fax: (852) 2646 3713 inquiry@avantwave.com

www.avantwave.com

# Pin initial status (after reset)

| Signalname                | Pin #    | I/0   | Status under<br>reseting<br>(I/O) | Status under<br>reseting<br>(H/L/Hi-Z) | Externaloperation                      | InternalPU/PD           |

|---------------------------|----------|-------|-----------------------------------|----------------------------------------|----------------------------------------|-------------------------|

| +1.5V (de fau lt          | 1        | DWD   | DWD                               | DWD                                    | ם שם                                   | DWD                     |

| output)<br>+1.8V (output) | 1        | PW R  | PWR                               | PWR                                    | PW R                                   | PWR                     |

|                           | 2        | PW R  | PWR                               | PWR                                    | PW R                                   | PWR                     |

| A 10 [0]                  | 3        | I/0   | I                                 | Hi-Z                                   | NC                                     | -                       |

| GND                       | 4        | GND   | G N D                             | GND                                    | GND<br>up to +3.3V input connect via a | GND                     |

| VREG_N (+3.3V)            | 5        | PW R  | PWR                               | PWR                                    | decoupling capacitor to the GND        | _                       |

| VREG EN                   | 6        | T     | T                                 | Н                                      | NC                                     | _                       |

| P 10 [1]                  | 7        | I/0   | I                                 | Hi-Z                                   | NC                                     | programmable PU or PD   |

| P 10 [2]                  | 8        | I/0   | I                                 | Нi-Z                                   | NC                                     | programmable PU or PD   |

| P 10 [3]                  | 9        | I/0   | Ι                                 | Hi−Z (Open-drain                       | NC                                     | programmable PU or PD   |

| P 10 [4]                  | 10       | I/0   | Ι                                 | Ηi-Z                                   | Pulldown 100k ohm                      | programmable PU or PD   |

| P 10 [5]                  | 11       | I/O   | Ι                                 | Ні-Z                                   | NC                                     | program m able PU or PD |

| P 10 [7]                  | 12       | I/O   | I                                 | Hi−Z                                   | NC                                     | program m able PU or PD |

| P 10 [9]                  | 13       | I/O   | I                                 | Hi−Z                                   | NC                                     | program m able PU or PD |

| /Reset                    | 14       | I     | I                                 | Hi−Z                                   | Pullup 4k7 ohm                         | weak PU                 |

| GND                       | 15       | GND   | GND                               | GND                                    | GND                                    | GND                     |

|                           |          |       |                                   |                                        | pullup 10k ohm (100kHz) or 1k          |                         |

| EEPROM_SDA                | 16       | I/0   | I/0                               | Ηi-Z                                   | ohm (400kHz)                           | N O N E                 |

| EEPROM <u>S</u> CL        | 17       | I/0   | I/0                               | Ηi-Z                                   | pu∥up 10k ohm                          | -                       |

| EEPROM_WP                 | 18       | I/0   | I/0                               | Ηi-Z                                   | GND                                    | -                       |

| PCM IN                    | 19       | Т     | Т                                 | ΗĖΖ                                    | N C                                    | weak PD                 |

| PCM_OUT                   | 15       | _     |                                   |                                        | 110                                    |                         |

|                           | 20       | 0     | 0                                 | Hi−Z                                   | N C                                    | weak PD                 |

| PCM_CLK                   | 21       | I/0   | I                                 | Н÷-Z                                   | NC                                     | weak PD                 |

| PCM_SYNC                  | 21<br>22 | I/0   | I                                 | Ні-Z                                   | N C NC                                 | weak PD                 |

| CLK_32K                   | 23       | Τ     | I<br>T                            | Hi-Z                                   | N C N C                                | weak PD                 |

| SD IO_DATA[0]             | 23       | I/0   | T                                 | +1.7V                                  | N C                                    | weak PU                 |

| CSPIM ISO                 | 24       | 1/0   | T                                 | +1.7V                                  | N C                                    | w eak PU                |

| UART_TX                   | 24       | 1/0   | TRI-STATE                         | +1.7V                                  | Pullup 4K7 ohm                         | weak PU                 |

| SD ID_DATA[1]             | 25       | 1/0   | I                                 | +1.7V                                  | NC                                     | w eak PU                |

| CSPINT<br>CSPINT          | 25       | 1/0   | T                                 | +1.7V                                  | N C                                    | w eak PU                |

| UART_RTS                  | 25       | 1/0   | TRI-STATE                         | +1.7V                                  | -                                      | weak PU                 |

| SD IO_DATA[2]             | 26       | 1/0   | T                                 | +1.7V                                  | N C                                    | w eak PU                |

| UART RX                   | 26       | 1/0   | TRI-STATE                         | +1.7V                                  | Pullup 4K7 ohm                         | weak PU                 |

| SD IO_DATA[3]             | 20       | 1/0   | I                                 | Н                                      | NC                                     | weak PU                 |

| CSPICS#                   | 27       | I/0   | I                                 | Н                                      | NC                                     | weak PU                 |

| UART_CTS                  | 27       | 1/0   | TRI-STATE                         | Н                                      | =                                      | weak PU                 |

| SD ID _C LK               | 28       | 1/0   | I                                 | +1.7V                                  | Pulldown 100k ohm                      | weak PU                 |

| CSP <u>I</u> CLK          | 28       | 1/0   | I                                 | +1.7V                                  | -                                      | weak PU                 |

| SDID_CS                   | 29       | 1/0   | I                                 | +1.7V                                  | -                                      | weak PU                 |

| SDD_CMD                   | 30       | I/O   | I                                 | +1.7V                                  | Pulldown 100k ohm                      | weak PU                 |

| CSP <u>IM</u> OSI         | 30       | 1/0   | I                                 | +1.7V                                  | NC                                     | weak PU                 |

| SPIM ISO                  | 31       | 0     | 0                                 | L                                      | test pad (debug)                       | weak PD                 |

| SPICLK                    | 32       | IJ∕ O | I                                 | Н                                      | test pad (debug)                       | w eak PD                |

| SPI <u>C</u> SB           | 33       | 1/0   | I                                 | Н                                      | test pad (debug)                       | weak PD                 |

| SPIMOSI                   | 34       | Ι     | I                                 | L                                      | test pad (debug)                       | weak PD                 |

| GND                       | 35       | GND   | GND                               | GND                                    | GND                                    | GND                     |

| ANT                       | 36       | I/0   | I/0                               | Hi−Z                                   | -                                      | NONE                    |

Table. 4 Pin assignment initial status

AvantWave . www.avantwave.com

Bluetron<sup>™</sup> 600 Series

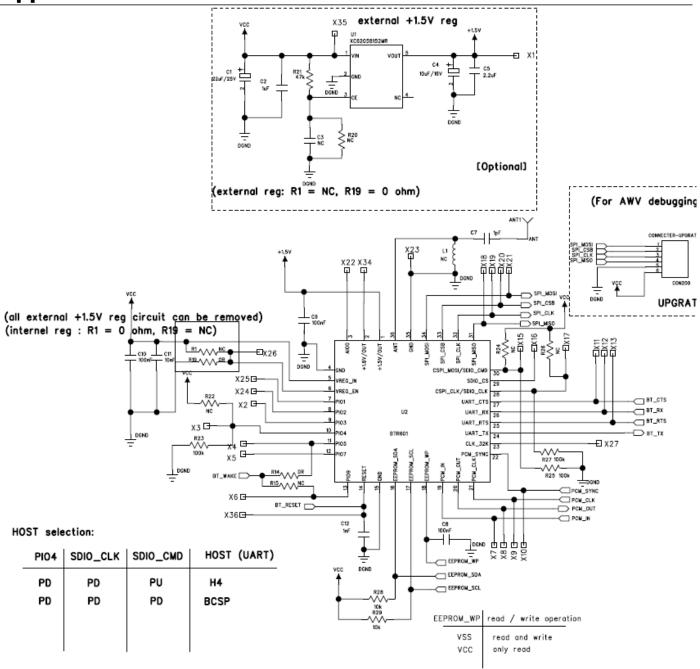

# **Applications Reference Circuit**

Fig.5 BTR602 module reference circuit

AIO & PIO depend on the application will be pull up or down, otherwise it will be open connection.

AvantWave . www.avantwave.com

# **General Specifications**

|                                                           | Minimum       | Typical               | Maximum      |

|-----------------------------------------------------------|---------------|-----------------------|--------------|

| Supply Voltage: VREG_IN                                   | -0.4V         | 3.3V                  | 4.9V         |

| High Voltage Regulator Output (I <sub>load</sub> = 70 mA) | 1.7V          | 1.8V                  | 1.9V         |

| Low Voltage Regulator Output (I <sub>load</sub> = 70 mA)  | 1.4V          | 1.5V                  | 1.6V         |

| Operating Temperature range                               | -40°C         | 25°C                  | 85°C         |

| Storage Temperature range                                 | -40°C(*)      | 25 °C                 | 85°C(*)      |

| Frequency Range                                           | 2.402 GHz     | 2.441 GHz             | 2.480 GHz    |

| Crystal Frequency                                         | 26MHz - 15ppm | 26MHz                 | 26MHz +15ppm |

| AFH                                                       | -             | 79 channels           | -            |

| Channel Bandwidth (Basic rate / Enhanced data rate)       | -             | 1Mbps / 2 or<br>3Mbps | -            |

| Internal ROM / RAM                                        | -             | 4MB / 48KB            | -            |

Table. 4 General Specifications

Remark: (\*) assume all components are soldered on the module PCB, although all components can be stored in between -40 to 85°C, but not recommend to store this module in the extreme temperature before it has soldered on the application PCB. The device is turn off but the environment also in between -40 to 85°C, assume it is able to sustain the extreme temperature. All components on the module can sustain the storage temperature between -40 to 85°C. Typically, we have tested the storage temperature(-40°C or +85°C) as maximum duration is 12 hours per each time.

We have passed the high/low temperature test for operated at -40 to 85°C, and most of the components have -40 to 85°C storage temperature

# **RF Specifications (Basic Data Rate)**

Voltage Supplies = 3.3V VREG\_IN => 1<sup>st</sup> internal step down to 1.8V => 2<sup>nd</sup> internal step down to 1.5V BC06 core supply voltage (all AIO/PIOs, PCM and SDIO/CSPI channels are NC)

| core suppry von | aye (all Alorrios |

|-----------------|-------------------|

| Temperature     | = 25°C            |

| Frequency       | = 2 441GHz        |

| Frequency = 2.441GHz                               |     |     |      |                            |      |

|----------------------------------------------------|-----|-----|------|----------------------------|------|

| Receiver                                           | Min | Тур | Мах  | Bluetooth<br>Specification | Unit |

| Sensitivity (DH1/3/5) at 0.1% BER                  | -80 | -84 | -86  | ≪-70                       | dBm  |

| Maximum received signal at 0.1% BER                | -20 | 3   | 6    | ≥-20                       | dBm  |

| C/I Co-channel                                     | 6   | 9   | 11   | ≤11                        | dB   |

| C/I Adjacent channel (f = f <sub>0</sub> +/- 1MHz) | -7  | -4  | -1   | <0                         | dB   |

| C/I Adjacent channel (f = f <sub>0</sub> +/- 2MHz) | -50 | -45 | -40  | ≪-40                       | dB   |

| C/I Adjacent channel (f = f <sub>0</sub> - 3MHz)   | -60 | -50 | -40  | ≪-40                       | dB   |

| C/I Adjacent channel (f = f <sub>0</sub> - 5MHz)   | -60 | -50 | -40  | ≪-40                       | dB   |

| C/I Image rejection (carrier –3MHz)                | -30 | -20 | -10  | ≪-9                        | dB   |

| Transmitter                                        | Min | Тур | Мах  | Bluetooth<br>Specification | Unit |

| Average Output Power                               | -6  | 0   | 4    | -6 to +4                   | dBm  |

| 20dB bandwidth  f <sub>H</sub> - f <sub>L</sub>    | 900 | 950 | 1000 | ≤ 1000                     | kHz  |

| 2 <sup>nd</sup> ACP (+/-2MHz)                      | -40 | -30 | -20  | ≤ <b>-20</b>               | dBc  |

| 3 <sup>rd</sup> ACP (+/-3MHz)                      | -60 | -50 | -40  | <b>≤ -40</b>               | dBc  |

|                                                    |     |     |      |                            |      |

Table 5 Basic Data Rate

Avantlane www.avantwave.com

Unit

dBm

dBm

dB

dB

dB

dB

dB

dB

Unit dBm dB

dbm

%

%

%

# **RF** Specifications (Enhanced Data Rate)

Voltage Supplies = 3.3V VREG\_IN => 1<sup>st</sup> internal step down to 1.8V => 2<sup>nd</sup> internal step down to 1.5V BC06 core supply voltage (all AIO/PIOs, PCM and SDIO/CSPI channels are NC) Temperature = 25°C

Frequency

= 2.441GHz

| Receiver                                           | Modulation                                                     | Min               | Тур                 | Мах               | Bluetooth<br>Specification |

|----------------------------------------------------|----------------------------------------------------------------|-------------------|---------------------|-------------------|----------------------------|

| Sensitivity (DH1/3/5) at 0.01% BER                 | π/4 DQPSK<br>8DPSK                                             | -75<br>-73        | -83<br>-78          | -84<br>-80        | ≤-70                       |

| Maximum received signal at 0.1% BER                | π/4 DQPSK<br>8DPSK                                             | -15               | 0                   | 5                 | ≥ -20                      |

| C/I Co-channel at 0.1% BER                         | π/4 DQPSK<br>8DPSK                                             | 5<br>17           | 10<br>19            | 12<br>20          | ≤13<br>≤21                 |

| C/I Adjacent channel (f = f <sub>0</sub> +/- 1MHz) | π/4 DQPSK<br>8DPSK                                             | -18<br>-15        | -10<br>-5           | 0<br>5            | ≪0<br>≪5                   |

| C/I Adjacent channel (f = $f_0$ +/- 2MHz)          | π/4 DQPSK<br>8DPSK                                             | ≥-30              | ≥-27                | ≥-25              | ≥-30<br>≪-25               |

| C/I Adjacent channel (f = f <sub>0</sub> + 3MHz)   | π/4 DQPSK<br>8DPSK                                             | -40               | -35                 | -33               | ≤-40<br>≤-33               |

| C/I Adjacent channel (f = f <sub>0</sub> - 5MHz)   | π/4 DQPSK<br>8DPSK                                             | -40               | -35                 | -33               | ≤-40<br>≤-33               |

| C/I Image rejection (carrier –3MHz)                | π/4 DQPSK<br>8DPSK                                             | -30<br>-15        | -20<br>-15          | -10<br>0          | ≤-7<br>≤0                  |

| Transmitter                                        |                                                                | Min               | Тур                 | Max               | Bluetooth<br>Specification |

| Average Output Power                               |                                                                | -6                | 0                   | 4                 | -6 to +4                   |

| Relative Transmit Power                            |                                                                | -4                | 0                   | 1                 | -4 to +1                   |

| In-band spurious emissions                         | $f = f_0 +/- 1MHz$<br>$f = f_0 +/- 2MHz$<br>$f = f_0 +/- 3MHz$ | -40<br>-45<br>-55 | -35<br>≥-34<br>≥-50 | -26<br>-20<br>-40 | ≤-26<br>≤-20<br>≤-40       |

π/4 DQPSK Modulation Accuracy **8DPSK Modulation Accuracy** EDR Differential Phase Encoding

Table 6 Enhanced Data Rate

Peak DEVM

Peak DEVM

19

17

99.9

8

10

99

34

25

100

≤35

≤25

≥99

AvantWave. www.avantwave.com

Bluetron<sup>™</sup> 600 Series

# **Power Control & Regulation**

Fig. 6 BTR602 Power Management Block Diagram

VREG\_EN (step down LDO regulator enable): Up to +4.9V dc voltage input

VREG\_IN (positive supply for UART, PIOs, PCM/I2S, SPI & SDIO/CSPI) : typically +3.3V dc voltage input (can change to +1.8V dc depends on different applications)

VREG\_OUT

•option 1 (+3.3V input, +1.8V output & +1.5V output):

=> input +3.3V to VREG\_IN & VREG\_EN, use the internal +1.8V & +1.5V regulator, +1.8V & 1.5V become the outputs

• option 2 (+1.8V input & +1.5V input):

=> input +1.8V to VREG\_IN, use the external +1.5V input

•option 3 (+3.3V input & +1.5V input):

=> input +3.3V to VREG\_IN, use the external +1.5 input

•option 4 (+1.8V input & +1.5V output):

=> input +1.8V to VREG\_IN & VREG\_EN, use the internal+1.8V & +1.5V regulator, +1.5V become the output, but +1.8V output may not as equal to +1.8V (-0.2V tolerance due to voltage drop.)

**Remark**: - If VREG\_IN to +1.8V, all the UART, PIOs, PCM/I2S, SPI & SDIO/CSPI are set to +1.8V.

- If +1.5V is output, the maximum output current is lower than 70mA.

- Option 1 is default setting, option 4 is not recommend to use.

AvantWave www.avantwave.com

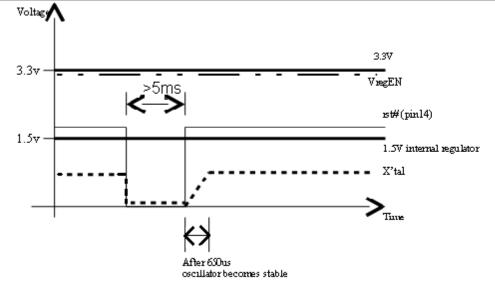

# **RESET** timing diagram(+3.3V, +1.5V, VREG\_EN & reset)

Fig. 7a Active low RESET pulse timing diagram

Sequence:

•External Reset signal (pin14) is generated

•Active low Reset pulse > 5ms

•+3.3V(pin5),VREG\_EN(pin6),+1.5V(pin1)[internal or external regulator modes] remain no change •After (Reset pulse rising edge + 650us), module crystal frequency is stable

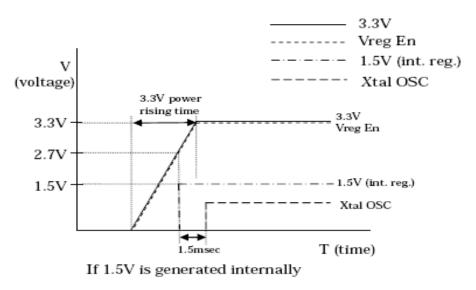

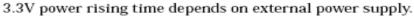

Fig. 7b Power on reset timing diagram (1.5V internal regulator mode)

Sequence:

•Input +3.3V and then power on the module, +3.3V(pin5) & VREG\_EN(pin6) are started up •After [+3.3V(pin5) rising from 0 to 2.7V], +1.5V(pin1) is pull high •After [+1.5V(pin1) pull high + 1.5m sec], the module crystal frequency is stable

Page 14 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

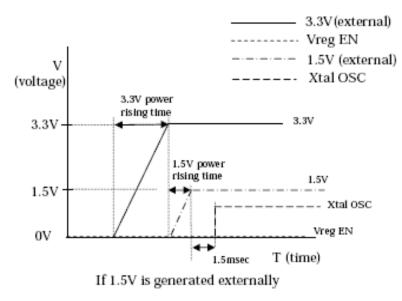

Fig. 7c Power on reset timing diagram (1.5V external regulator mode)

Sequence:

•+3.3V(pin5) is started up

•After [+3.3V(pin5) rising from 0 to 3.3V], +1.5V(pin1) is rising to the high level •After [+1.5V(pin1) pull high + 1.5m sec], the module crystal frequency is stable

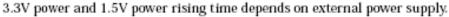

## **EEPROM Connection**

Fig. 8 EEPROM connection

Pin16 EEPROM\_SDA: It is a bidirectional pin for transfer addresses and data in/out of the device, Due to the open-drain output, the I2C SDA port need a pull up resistor to Vcc (10k ohm for 100kHz, 2k ohm for 400kHz). I2C SDA bus is only able to change during I2C SCL low. Changes during I2C SCL high are reserved for indication Start and Stop bit status.

Page 15 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

Pin17 EEPROM\_SCL: I2C SCL input is assigned to synchronize the data transfer to and from the device.

Pin18 EEPROM\_WP: Write protect(WP) input pin is selected by the external device to define the EEPROM is able to write or not.

If tied it to Vss, memory operation(write/read) is enabled normally. If tied it to Vcc, write operation is disabled and read operation is enabled.

EEPROM slave address = 1010XYZ for BT address, crystal trim value and crystal frequency PSKEY storage, X is don't care bit, YZ = "00" is block select bits.

## **Host Interface Selections**

For the protocol that is selected by the UART host interface, it is determined by the status of the SDIO\_CLK and SDIO\_CMD lines when sampling the PIO[4] status. Table 7 & 8 shown the host and protocol setting:

Select UART, SDIO or CSPI Host Interface by the hardware configurable method:

| (PIN10) PIO | Input | Connection      | Host        |

|-------------|-------|-----------------|-------------|

| 4           | High  | 100k ohm to Vcc | SDIO / CSPI |

| 4           | Low   | 100k ohm to GND | UART        |

|             |       |                 |             |

Table 7. PIO 4 selections

PIO[4] is pulled low: UART host interface is chose (default configure) PIO[4] is pulled high: SDIO/CSPI host interface is chose.

Select UART Protocols by the hardware configurable method:

| (PIN28) SDIO_CLK | Connection      | (PIN30) SDIO_CMD | Connection      | UART protocol |

|------------------|-----------------|------------------|-----------------|---------------|

| Low              | 100k ohm to GND | Low              | 100k ohm to GND | BCSP          |

| Low              | 100k ohm to GND | High             | 100k ohm to Vcc | H4            |

| High             | 100k ohm to Vcc | Low              | 100k ohm to GND | H4DS          |

| High             | 100k ohm to Vcc | High             | 100k ohm to Vcc | Н5            |

Table 8. UART protocol selections

## Example

BCSP mode: SDIO\_CLK and SDIO\_CMD both add a 100k ohm resistor pull down to GND. H5 mode: SDIO\_CLK and SDIO\_CMD both add a 100k ohm resistor pull up to Vcc.

UART connection:

| Host       | Module   |

|------------|----------|

| UART       | UART RX  |

| TX<br>UART | UART TX  |

| RX         | UART RTS |

|            | UART CTS |

Fig. 9 UART connection method

BCSP : CSR proprietary, reliable alternative to the standard bluetooth UART Host Transport.

H4DS : CSR proprietary, alternative to the standard bluetooth UART Host Transport, it supports deep sleep mode for low-power applications.

H4 => a transport protocol for bluetooth HCl packets over UART, the name came from bluetooth spec. appendix H4. H5 => a three-wire protocol, presumably based on CSR's BCSP protocol.

UART operation : Set the hardware configurable pins (PIO4, SDIO\_CLK & SDIO\_CMD), if hardware configurable selection is BCSP transport(PIO4 is low, SDIO\_CLK is low & SDIO\_CMD is low), the baudrate is auto detected. The UART connection method is referent to fig. 8.

•UART\_RX and UART\_TX transmit data between the BTR602 module and external host. UART\_RX should pull up to Vcc via a 10k ohm resistor. UART\_TX is already internal pull up. UART\_CTS & UART\_RTS is hardware flow control (default is NC).

e.g default BCSP(0x0806) is configured to 8bit length, no hardware flow control, even parity bit. The parameter details can refer to the Appendix 1. The other default transport settings (H4, H4DS & H5 parameter) please refer to the Appendix1. All settings(PSKEY) can be changed by the external MCU via UART channel. Both the transports with auto detected baudrate and same connection method.

| UART Se     | ttings:  |                       |

|-------------|----------|-----------------------|

| Parameter   |          | Possible values       |

| Baud rate   | minimum  | 1200 baud (≤2% error) |

|             |          | 9600 baud (≤1% error) |

|             | maximum  | 4M baud (≤1% error)   |

| Flow contr  | ol       | RTS / CTS or none     |

| Parity      |          | Odd, Even or none     |

| Number of   | stop bit | 1 or 2                |

| Bits length |          | 8                     |

Table. 9 UART configurable value

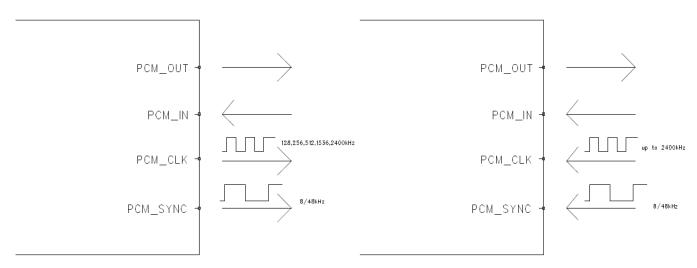

### PCM interface connections:

The module PCM interface is included the digital transmission and reception of PCM encoded audio data via the bluetooth channel. The BTR602 module is hardware ready for the PCM transceiver function, so, the processor computation power can be increased due to its overhead decreased. The module supports a bidirectional digital audio interface that streams directly into the baseband layer inside the on-chip firmware. It won't pass through the HCI protocol layer.

This PCM channel is able to send and receive the audio data from a SCO channel, it is three SCO channels can be supported by the PCM interface at any one time only.

For the PCM master, it can generate an output clock of 128, 256, 512, 1536 or 2400kHz. For the PCM slave, it can co-operate with an input clock up to 2400kHz. The module PCM supports 13bit or 16 bit linear, 8-bit

Avantlane www.avantwave.com

Page 17 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

$\mu$ -law or A-law companding sample formats at 8k samples/s and send and receive on any three of first four slots following PCM\_SYNC.

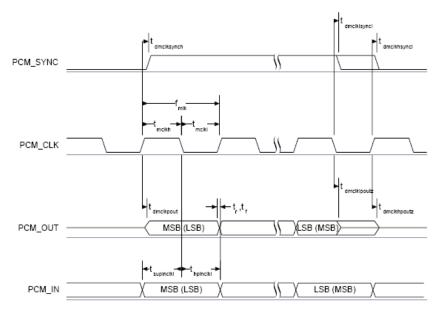

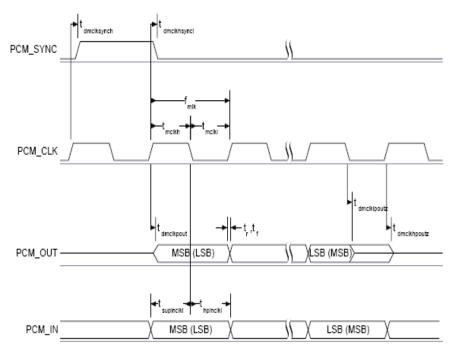

Fig. 10a) PCM interface master

Fig. 10b) PCM interface slave

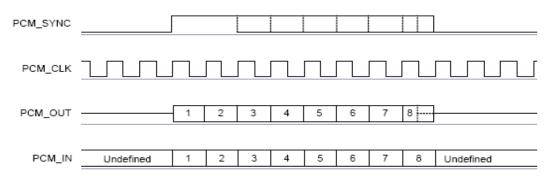

Long Frame Sync:

A clocking format which is controlled the transfer of PCM data words/samples. The rising edge of PCM\_SYNC indicates the start of the PCM data. For the PCM master, PCM\_SYNC & PCM\_CLK are output, PCM\_SYNC is 8 bits long. Besides, as PCM slave, PCM\_SYNC from two continue falling edges of PCM\_CLK to half the PCM\_SYNC rate (62.5us long).

Fig. 10c) Long Frame Sync (8 bit PCM\_OUT data)

Short Frame Sync:

The falling edge of PCM\_SYNC indicates the start of the PCM\_OUT data. PCM\_SYNC is only one clock cycle duty.

Fig. 10d) Short Frame Sync (8 bit PCM\_OUT data)

AvantWave www.avantwave.com

For the BTR602 module, it samples PCM\_IN on the falling edge of PCM\_CLK and generates PCM\_OUT on the rising edge. And, PCM\_OUT can be configured to be either high impedance on the falling edge of PCM\_CLK in the LSB position or on the rising edge.

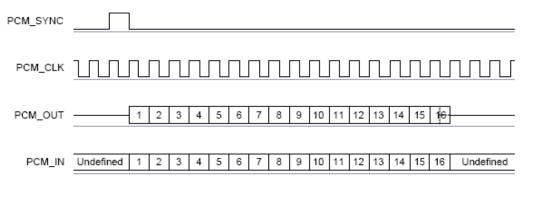

Slots and Sample Formats:

BTR602 module able to transmit and receive on any first four slots following each sync pulse. Slot periods can be either 8 or 16 clock pulses. The 8 clock cycles can only apply for the 8 bit sample formats. The 16 clock cycles can apply for 8 bit, 13 bit and 16 bit sample formats.

BTR602 module supports 13 bit linear, 16 bit linear and 8 bit  $\mu$ -law or A-law sample formats. The sample rate is 8k samples/s. In case 16 bit slots are used, there are 3 or 8 unused bits in each slot will be filled with sign extension , padded with zero or a programmable 3 bit audio attenuation which is compatible with some Motorola CODEC.

| Symbol                | Parameter          |                                                                                             | Min    | Тур | Max   | Unit |

|-----------------------|--------------------|---------------------------------------------------------------------------------------------|--------|-----|-------|------|

| Symbol                | i arameter         |                                                                                             | IVIIII | тур | IVIAX | Unit |

| fmclk                 | PCM_CLK frequency  | 4MHz DDS generation. Selection of frequency is programmable.<br>See Table. 24               | 128    | 256 | 512   | kHz  |

|                       |                    | 48MHz DDS generation. Selection of frequency is programmable<br>. See Table. 23 and page 20 | 2.9    | 3   | 3.1   | kHz  |

| -                     | PCM_SYNC frequency | y for SCO connection                                                                        | 4      | 8   | 8     | kHz  |

| tmclkh <sup>(a)</sup> | PCM_CLK high       | 4MHz DDS generation                                                                         | 980    | 990 | 1000  | ns   |

| tmclkl <sup>(a)</sup> | PCM_CLK low        | 4MHz DDS generation                                                                         | 730    | 740 | 750   | ns   |

Page 19 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

Tel: (852) 2648 9887 Fax: (852) 2646 3713 inquiry@avantwave.com

vw.avantwave.com

AvantWave

| i i         | L                                                      |                                               | 1  |    |    | i  |    |

|-------------|--------------------------------------------------------|-----------------------------------------------|----|----|----|----|----|

|             |                                                        |                                               |    |    |    |    |    |

| -           | PCM_CLK jitter                                         | 48MHz DDS generation                          |    | 10 | 15 | 21 | ns |

| tmclksynch  | Delay time from PCM                                    |                                               | 10 | 15 | 20 | ns |    |

| tmclkpout   | Delay time from PCM                                    | 10                                            | 15 | 20 | ns |    |    |

| tmclklsyncl | Delay time from PCM_                                   | 10                                            | 15 | 20 | ns |    |    |

| tmclkhsyncl | Delay time from PCM                                    |                                               | 10 | 15 | 20 | ns |    |

| tmclklpoutz | Delay time from PCM                                    |                                               | 10 | 15 | 20 | ns |    |

| tmclkhpoutz | Delay time from PCM_CLK high to PCM_OUT high impedance |                                               |    |    |    | 20 | ns |

| tsupinclkl  | Set-up time for PCM_I                                  | 30                                            | 35 | 40 | ns |    |    |

| thpinclkl   | Set-up time for PCM_0                                  | Set-up time for PCM_CLK low to PCM_IN invalid |    |    |    |    |    |

|             |                                                        |                                               |    |    |    |    |    |

## Table. 10a) PCM Master Timing

## ig. 10f) PCM Master Timing Long Frame Sync

AvantWave. www.avantwave.com

Bluetron<sup>™</sup> 600 Series

Fig. 10g) PCM Master Timing Short Frame Sync

| Symbol       | Parameter                                                                                       | Min | Тур | Max  | Unit |

|--------------|-------------------------------------------------------------------------------------------------|-----|-----|------|------|

| fmclk        | PCM_CLK frequency (slave mode: input)                                                           | 64  | 512 | 2048 | kHz  |

| tclkh        | PCM_CLK high time                                                                               | 200 | 300 | 400  | ns   |

| tclkl        | PCM_CLK low time                                                                                | 200 | 300 | 400  | ns   |

| thclksynch   | hold time from PCM_CLK low to PCM_SYNC high                                                     | 30  | 50  | 70   | ns   |

| tsusclksynch | Set-up time for PCM_SYNC high to PCM_CLK low                                                    | 30  | 50  | 70   | ns   |

| tdpout       | Delay time from PCM_SYNC or PCM_CLK that is later, to valid PCM_OUT data (Long Frame Sync only) | 15  | 20  | 20   | ns   |

| tdsclkhpout  | Delay time from CLK high to PCM_OUT valid data                                                  | 15  | 20  | 20   | ns   |

| tdpoutz      | Delay time from PCM_SYNC or PCM_CLK that is later, to valid PCM_OUT data line high impedance    | 15  | 20  | 20   | ns   |

| tsupinclkl   | Set-up time for PCM_IN valid to PCM_CLK low                                                     | 30  | 40  | 50   | ns   |

| thpinclkl    | Set-up time for PCM_CLK low to PCM_IN invalid                                                   | 30  | 40  | 50   | ns   |

Table. 10b) PCM Slave Timing

AvantWave. www.avantwave.com

Fig. 10h) PCM Slave Timing Long Frame Sync

Fig. 10i) PCM Slave Timing Short Frame Sync

PCM CLK and PCM-SYNC generation:

•Generating these by DDS from the Core internal 4MHz clock. It is limited the PCM\_CLK to 128, 256 or 512kHz and PCM\_SYNC to 8kHz

•Generating these by DDS from an internal 48MHz clock. Set bit via 48M\_PCM\_CLK\_GEN\_EN in PSKEY\_PCM\_CONFIG32. For the long frame sync, the length of PCM\_SYNC maybe either 8 or 16 bit cycles of PCM\_CLK, determined by LONG\_LENGTH\_SYNC\_EN in PSKEY\_PCM\_CONFIG32.

PCM\_CLK frequency(internal 48MHz clock) formula: f = (CNT\_RATE / CNT\_LIMIT) x 24MHz

PCM\_SYNC frequency relevant to PCM\_CLK (PCM\_SYNC\_MULT = 0) f = PCM\_CLK / (SYNC\_LIMIT x 8)

AvantWave www.avantwave.com

Page 22 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

## PCM\_SYNC frequency relevant to PCM\_CLK (PCM\_SYNC\_MULT = 1) f = PCM\_CLK / SYNC\_LIMIT

CNT\_RATE, CNT\_LIMIT and SYNC\_LIMIT all are set by PSKEY\_PCM\_LOW\_JITTER\_CONFIG. For example, to generate PCM\_CLK at 512kHz with PCM\_SYNC at 8kHz, set PSKEY\_PCM\_LOW \_JITTER\_CONFIG to 0x08080177.

PCM configuration refer to the Appendix 4.

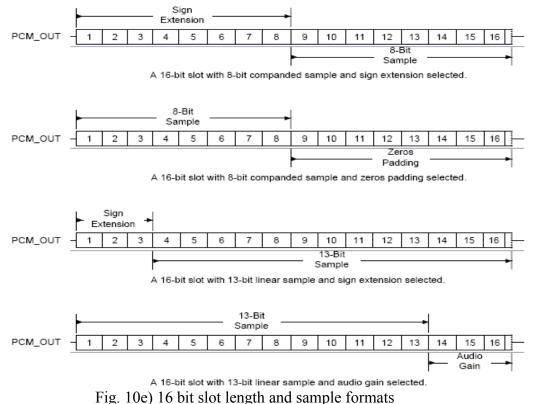

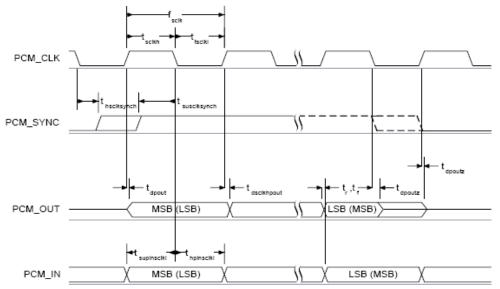

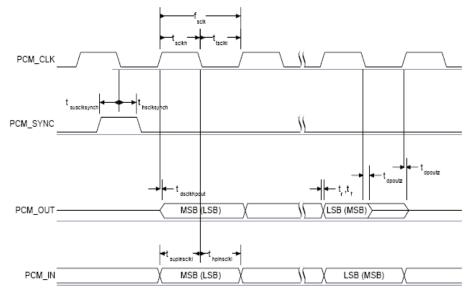

## <u>I<sup>2</sup>S interface connections:</u>

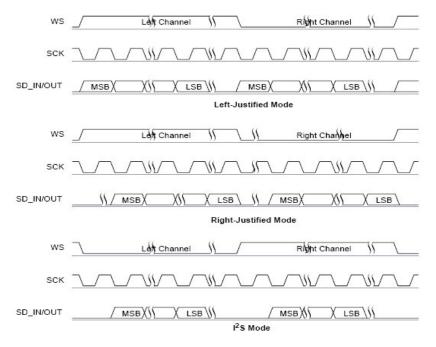

The BTR602 module digital audio interface provided the  $I^2S$ , left-justified or right justified. It is the same pins which shares with the PCM channel. So, the active digital audio interface is either PCM or  $I^2S$  at the same time.

| PCM interface | I <sup>2</sup> S interface |

|---------------|----------------------------|

| PCM_OUT       | SD_OUT                     |

| PCM_IN        | SD_IN                      |

| PCM_SYNC      | WS                         |

| PCM_CLK       | SCK                        |

Table. 10a) PCM & I2S interfaces pin assignment

Page 23 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

# <u>I2S interface (WS, SCK, SD OUT):</u>

Table. 11 shown the values for the PSKEY\_DIGITAL\_AUDIO\_CONFIG how to configure the digital audio interface. i e. to configure an I<sup>2</sup>S interface with 16 bit SD data set PSKEY\_DIGITAL\_CONFIG to 0x0406.

| Bit    | Mask   | Name                      | Description                                                                                                                                                                                                       |

|--------|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[0]   | 0x0001 | CONFIG_JUSTIFY_FORMAT     | 0 for left justified, 1 for right justified.                                                                                                                                                                      |

| D[1]   | 0x0002 | CONFIG_LEFT_JUSTIFY_DELAY | For left justified formats: 0 is MSB of SD data<br>occurs in the first SCLK period following WS<br>transition. 1 is MSB of SD data occurs in the<br>second SCLK period.                                           |

| D[2]   | 0x0004 | CONFIG_CHANNEL_POLARITY   | For 0, SD data is left channel when WS is high. For 1 SD data is right channel.                                                                                                                                   |

| D[3]   | 0x0008 | CONFIG_AUDIO_ATTEN_EN     | For 0, 17 bit SD data is rounded down to 16<br>bits. For 1, the audio attenuation defined in<br>CONFIG_AUDIO_ATTEN is applied over 24<br>bits with saturated rounding. Requires<br>CONFIG_16_BIT_CROP_EN to be 0. |

| D[7:4] | 0x00F0 | CONFIG_AUDIO_ATTEN        | Attenuation in 6 dB steps.                                                                                                                                                                                        |

| D[9:8] | 0x0300 | CONFIG_JUSTIFY_RESOLUTION | Resolution of data on SD_IN, 00=16 bit,<br>01=20 bit, 10=24 bit, 11=Reserved. This is<br>required for right justified format and with left<br>justified LSB first.                                                |

| D[10]  | 0x0400 | CONFIG_16_BIT_CROP_EN     | For 0, 17 bit SD_IN data is rounded down to 16 bits. For 1 only the most significant 16 bits of data are received.                                                                                                |

Table. 10b) I2S interface configurable PSKEY

## BC06 Master mode I2c(PSKEY\_DIGITAL\_AUDIO\_CONFIG): 0x0006

## => D[1] & D[2] is 1, others are 0

Fig. 11a) BTR602 module digital audio interface modes

Page 24 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

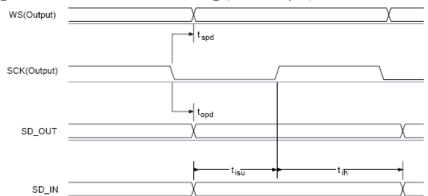

| Symbol | Parameer                 | Min | Тур | Max | Unit |

|--------|--------------------------|-----|-----|-----|------|

| -      | Clock frequency (SCK)    | 1.5 | 3   | 6.2 | MHz  |

| -      | L/R clock (WS)           | 24  | 48  | 96  | kHz  |

| topd   | SCK to SD_OUT delay      | 20  | 200 | 400 | ns   |

| tspd   | SCK to WS delay          | 20  | 100 | 200 | ns   |

| tisu   | SD_IN to SCK set up time | 20  | 200 | 400 | ns   |

| tih    | SD_IN to SCK hold time   | 10  | 200 | 450 | ns   |

# Table 10c) Digital audio interface master timing (Data Output)

#### Fig. 11b) Digital Audio Interface Master Timing

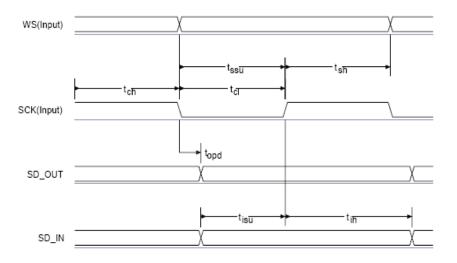

| a 1 1  |                          |     |     |     |      |

|--------|--------------------------|-----|-----|-----|------|

| Symbol | Parameter                | Min | Тур | Max | Unit |

| -      | SCK frequency            | 1   | 3   | 6.2 | MHz  |

| -      | WS frequnecy             | 16  | 48  | 96  | kHz  |

| tch    | SCK high time            | 80  | 340 | 600 | ns   |

| tcl    | SCK low time             | 80  | 350 | 650 | ns   |

| topd   | SCK to SD_OUT delay      | 20  | 50  | 150 | ns   |

| tssu   | WS to SCK set-up time    | 20  | 100 | 500 | ns   |

| tsh    | WS to SCK hold time      | 20  | 200 | 600 | ns   |

| tisu   | SD_IN to SCK set-up time | 20  | 100 | 400 | ns   |

| tih    | SD_IN to SCK hold time   | 20  | 100 | 400 | ns   |

|        | Table 10d) Digital Audia |     | -   |     |      |

Table. 10d) Digital Audio Interface Slave Timing

Page 25 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

Fig. 11c) Digital audio Interface Slave Timing

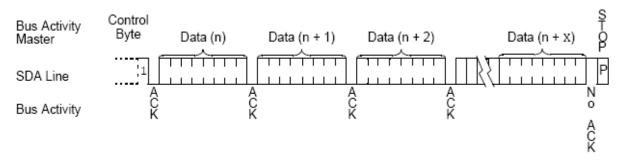

# BTR 601/BTR602 EEPROM I2C Read/Write Operation (To external MCU)

Aim:

Since there are some Bluetooth Configuration Parameter(**BT address, Crystal Trim, Crystal Frequency**) are required in production, EEPROM is applied for temporary storage the parameters. This document will interpret the parameter that stored in EEPROM (read/write)

Communication Interface: **I2C** Devices: External MCU to BTR601/BTR602

## I2C Read/Write Command format:

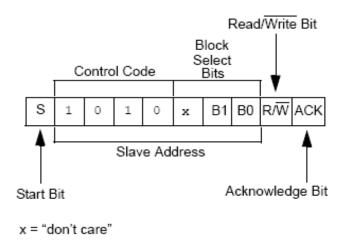

Fig. 12a) Control Byte Allocation

| Operation | Control<br>Code | Block Select  | R/W |

|-----------|-----------------|---------------|-----|

| Read      | 1010            | Block Address | 1   |

| Write     | 1010            | Block Address | 0   |

Fig. 12b) I2c Read/Write operations

•Control code is set as 1010 for read and write operations, block select bits B2, B1 & B0 are 000. •Read operation set to "1" and Write operation set to "0"

Page 26 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

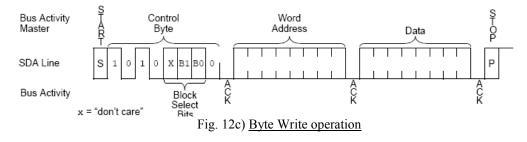

#### *Write Operation (slave address set to '0'):*

1. Byte Write

- From the Start condition from the master, the device code bits (1010), block select bits(000) and r/w bit (0 or 1), which is a logic low, is placed onto the bus by the master transmitter

- The addressed slave receiver is a byte with a word address will follow once it has generated an Acknowledge bit during the ninth clock cycle.

- The next byte transmitted by the master is the word address and will be written into the Address Pointer.

- After receiving another Acknowledge signal, the master device will transmit the data word to be written into the addressed memory location.

- One more Acknowledge again, the master generates a Stop operation, it indicates the internal write cycle and without Acknowledge signals.

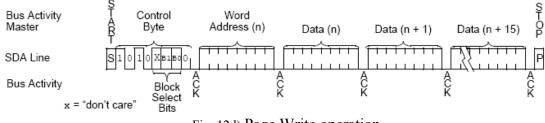

#### 2. Page Write

Fig. 12d) Page Write operation

- It is the same method to the Byte Write

- The master transmits up to 16 data bytes to the EEPROM, it is temporarily stored in the on chip page buffer and will be written into memory after it has sent a Stop condition.

- The four lower order address pointer bits are internally incremented by '1'

- The higher order 7 bits of the word address remain constant.

- If the master transmit more than 16 words, the address counter will roll over and will be overwritten the previous received data.

- After the Stop condition, the write cycle will begin.

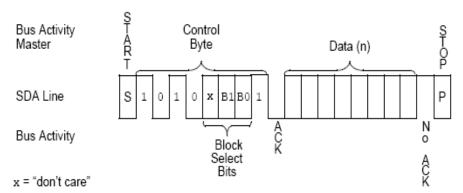

*Read Operation (slave address set to '1'):*

#### 1. Current Address Read

Fig. 12e) Current Address Read operation

• If the previous access was address n, the next current address read operation would access data from address n+1.

AvantWave www.avantwave.com

Page 27 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

Bluetron<sup>™</sup> 600 Series

- After received of the slave address with R/W bit is set to '1', there is an acknowledge send out and transmit 8-bit data word

- The master will not send Acknowledge again but generate a Stop condition to terminate the transmission.

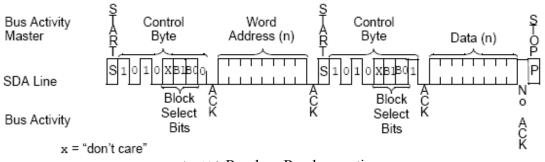

#### 2. **Random Read**

Fig. 12f) Random Read operation

- The word address is first to be set and become a part of write operation .

- After the word address is sent out, the master condition generates a Start condition follow the Acknowledge and terminate the write operation but not before an internal Address Pointer is set.

- The master generate the Control byte again and R/W is set to '1' instead of '0'

- Then, it issue an Acknowledge and send the 8-bit data word.

- It will not generate an Acknowledge but have a Stop condition.

#### 3. **Sequential Read**

## Fig. 12g) Sequential Read operation

- It is the same method to the Random Read except the master transmit the 1<sup>st</sup> data byte but use an Acknowledge to replace a Stop condition, it represents the continue read process.

- The EEPROM transmit the next sequentially addressed 8 bit word and increase the internal Address Pointer by 1 to allow the whole memory contents can be sequentially read as one operation.

## I2C Data Packet format:

All data (BT address, Crystal Trim, Crystal Frequency)will store as a packet in EEPROM with 8 byte code

BT address: It will store from address 0x00 to 0x07 in EEPROM.(8 byte code) 0x00,0x08 //NAP 0xe0, //UAP C\_LAP\_0,C\_LAP\_1,C\_LAP\_2, //LAP 0x00, //dummy C\_CHKSUM //checksum

ps: C\_CHKSUM =0xff - (0x00+0x08+0xe0+C\_UAP\_0+C\_UAP\_1+C\_UAP\_2 +0x00) & 0x00ff;

Datasheet BTR602 v2.4 Last Update 30/Apr/2014

Page 28

www.avantwave.com

| EEPROM<br>address | 0x00 | 0x01 | 0x02 | 0x03    | 0x04    | 0x05    | 0x06 | 0x07         |

|-------------------|------|------|------|---------|---------|---------|------|--------------|

| Data              | 0x00 | 0x08 | 0xe0 | C_LAP_0 | C_LAP_1 | C_LAP_2 | 0x00 | C_CHKSU<br>M |

Table. 11a) BT address data format

e.g. bluetooth address is 0008-e0-123456, In EEPROM as follows 00 08 e0 12 34 56 00 7b

Crystal Frequency

It will store from address 0x08 to 0x0f in EEPROM.(8 byte code)

C\_CRYFREQ\_HIGHER\_BYTE,C\_CRYFREQ\_LOWER\_BYTE, 0x00, 0x00,0x00,0x00,0x00, C\_CHKSUM //crystal frequency //dummy //checksum

ps:C\_CHKSUM=

0xff -(C\_CRYFREQ\_HIGHER\_BYTE+C\_CRYFREQ\_LOWER\_BYTE+0x00+0x00+0x00+0x00) & 0x00ff;

| EEPROM<br>address | 0x08                          | 0x09                         | 0x0a | 0x0b | 0x0c | 0x0d | 0x0e | 0x0f         |

|-------------------|-------------------------------|------------------------------|------|------|------|------|------|--------------|

| Data              | C_CRYFR<br>EQ_HIGHE<br>R_BYTE | C_CRYFR<br>EQ_LOWE<br>R_BYTE | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | C_CHKSU<br>M |

Table. 11b) Crystal Frequency data format

e.g. the crystal frequency is 16Mhz, In EEPROM as follows 3e 80 00 00 00 00 00 41

Crystal Trim

It will store from address 0x10 to 0x17 in EEPROM.(8 byte code) C\_CRYTRIM, //crystal trim 0x00,0x00, 0x00,0x00,0x00,0x00, //dummy C\_CHKSUM //chksum ps: C\_CHKSUM =0xff -(C\_CRYFTRIM+0x00+0x00+0x00+0x00+0x00) & 0x00ff;

| EEPROM<br>address | 0x10          | 0x11 | 0x12 | 0x13 | 0x14 | 0x15 | 0x16 | 0x17         |

|-------------------|---------------|------|------|------|------|------|------|--------------|

| Data              | C_CRYTR<br>IM | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | C_CHKSU<br>M |

Table. 11c) Crystal Trim data format

e.g. the crystal trim in decimal is 29 In EEPROM as follows 1d 00 00 00 00 00 00 e2

AvantWave www.avantwave.com

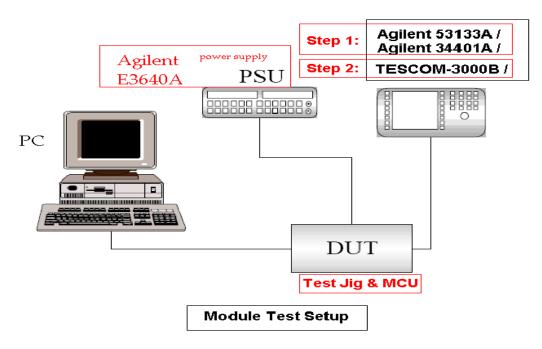

# Test equipment system diagram

#### Fig. 13 RF test setup configure

#### Step 1:

- (a) Stick the bar code label on the shield can, scan the bar code label for the unique BT address

- (b) Setup the PC & Test Fixture, connect the COM port & +8V power supply unit

- (c) Insert the BT module into the Fixture

- (d) Download the RF & basic PSKEY to the module via UART interface

- (e) Start the crystal trim, use the software program to trim the crystal value and log to a text file with the unique BT ID. Put the unique BD addr label on the BTR602 module.

- (f) Check the PIOs, AIO, +1.8V output, UART & SPI by the software testing program

- (g) Log and record the results into the text file

## Step 2:

- (h) Scan the bar code label for the unique BT address

- (i) Start the conductive RF test and log the result to a text file (refer to AWV Conductive RF Test)

- (j) Log and record the results into the text file

### Step 3:

- (k) Scan the bar code label for the unique BT address

- (1) Write the PSKEYs (unique BT address, crystal trim value & crystal frequency) into the EEPROM

- (m) Check the EEPROM by the external MCU to verify the written PSKEYs are corrected or not, put the crystal trim value label on the BTR602 module

### Step 4:

- $(\mathbf{n})$  Scan the bar code label for the unique BT address

- (o) visual check the BTR602 module and read the EEPROM value to confirm that it is matched between the BD addr label and EEPROM information per each module. Failed module will be collected and analyzed by the engineers.

(p) Log and record the MP products into the text file before deliver out

Avantlane www.avantwave.com

# **Power Consumption**

## Referent current consumption(different HCI settings):

Voltage Supplies = 3.3V VREG\_IN => 1<sup>st</sup> internal step down to 1.8V => 2<sup>nd</sup> internal step down to 1.5V BC06 core supply voltage (all AIO/PIOs, PCM and SDIO/CSPI channels are NC) Temperature = 25°C Frequency = 2.441GHz

| Mode                                                     | Average | Peak | Unit |

|----------------------------------------------------------|---------|------|------|

| SCO connection HV3 (30ms interval sniff mode)(slave)     | 16.1    | 25   | mA   |

| SCO connection HV3 (30ms interval sniff mode)(Master)    | 16.9    | 27   | mA   |

| SCO connection HV3 (no sniff mode)(slave)                | 23.1    | 30   | mA   |

| SCO connection HV1 (Slave)                               | 36.9    | 40   | mA   |

| SCO connection HV1 (Master)                              | 37.1    | 40   | mA   |

| ACL data transfer 115.2kbps UART (Master)                | 8.8     | 15   | mA   |

| ACL data transfer 115.2kbps UART (slave)                 | 17.2    | 20   | mA   |

| ACL data transfer 921kbps UART (Master or slave)         | 29.5    | 37   | mA   |

| ACL connection, sniff mode 40ms interval, 38.4kbps UART  | 1.6     | 5    | mA   |

| ACL connection, sniff mode 1.28s interval, 38.4kbps UART | 0.21    | 2    | mA   |

| Parked Slave, 1.28s beacon interval, 38.kpbs UART        | 0.26    | 1    | mA   |

| Standby Mode (Connected to host, no RF activity)         | 39      | 150  | μA   |

| Reset (RESET high or RESETB low)                         | . 38    | 120  | μA   |

Table. 13 HCI current consumption

## Measured current consumption(overall):

Voltage Supplies = 3.3V VREG\_IN => 1<sup>st</sup> internal step down to 1.8V => 2<sup>nd</sup> internal step down to 1.5V BC06 core supply voltage (all AIO/PIOs, PCM and SDIO/CSPI channels are NC) Temperature = 25°C Frequency = 2.402GHz to 2.480GHz (hopping)

•standby current consumption:  $\sim 0.8 \text{mA}$

•pairing current consumption:  $\sim 35 \text{mA}$

•A2DP audio streaming connected current consumption: ~ 45mA

•Headset/Handsfree connected current consumption: ~ 40mA

Remark: connect to PC via UART interface with the IVT software tool, HCI module can perform some different BT profiles function like A2DP, SPP, HID & HS/HF,,etc when connected to the IVT software tool.

# **Electrical Characteristics**

ESD Precautions:

The BTR602 module should be applied ESD handling precautions during PCBA manufacturing proceed.

## Absolute Maximum Ratings:

| Storage Temperature |                                         | Min     | Max       | Unit |

|---------------------|-----------------------------------------|---------|-----------|------|

| Core Supply         | +1.5V supply rail                       | -0.4    | 1.6       | V    |

| IO volage           | +3.3V supply rail                       | -0.4    | 3.6       | V    |

| Supply voltage      | +1.5V internal regulator input          | -0.4    | 2.6       | V    |

|                     | +1.8V internal regulator input, VREG_EN | -0.4    | 4.9       | V    |

| Other terminal      | voltages                                | Vss-0.4 | Vdd + 0.4 | V    |

## Recommended Operating Conditions:

| Operating Temperature Range   |                   |     | Max | Unit |

|-------------------------------|-------------------|-----|-----|------|

| Core Supply +1.5V supply rail |                   | 1.4 | 1.6 | V    |

| IO volage                     | +3.3V supply rail | 1.7 | 3.6 | V    |

## +3.3V Linear Regulator Conditions:

| Normal Operation                                                                                           | Min  | Тур | Max | Unit   |

|------------------------------------------------------------------------------------------------------------|------|-----|-----|--------|

| Input voltage                                                                                              | 2.7  | 3.3 | 4.9 | V      |

| Output voltage (I = 70mA, Vdd =+3.3V)                                                                      | 1.7  | 1.8 | 1.9 | V      |

| Temperature coefficient                                                                                    | -250 | 0   | 250 | ppm/ºC |

| Output noise (freq. Range 100Hz to 100kHz, reg. Output connected to 100nF and 10uF 2.2 ohm ESR capacitors) | 0    | 0.5 | 1   | mV rms |

| Load regulation ( I = 70mA)                                                                                | 40   | 45  | 50  | mV/A   |

| Settling time (1mA to 70mA pulse load, reg. Output connected to 100nF and 10uF 2.2 ohm ESR capacitors)     | 30   | 50  | 100 | μS     |

| Maximum output current                                                                                     | 60   | 70  | 75  | mA     |

| Minimum load current                                                                                       | 5    | 8   | 15  | μA     |

| Quiescent current (excluding load, I < 1mA)                                                                | 30   | 40  | 60  | μA     |

AvantWave .

www.avantwave.com

Page 32 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

|                                               | Bluetron <sup>™</sup> 600 Series |

|-----------------------------------------------|----------------------------------|

|                                               |                                  |

| Deep Sleep Mode Operation                     |                                  |

| Quiescent current (excluding load, I < 100µA) | 10 13 21 µA                      |

| Standby Mode                                  |                                  |

| Quiescent current                             | 1.5 2.5 3.3 μA                   |

## +1.8V Linear Regulator Conditions:

| Normal Operation                                                                                           | Min  | Тур | Max | Unit   |

|------------------------------------------------------------------------------------------------------------|------|-----|-----|--------|

| Input voltage                                                                                              | 1.7  | 1.8 | 2.6 | V      |

| Output voltage (I = 70mA, Vdd =+1.7V)                                                                      | 1.4  | 1.5 | 1.6 | V      |

| Temperature coefficient                                                                                    | -250 | 0   | 250 | ppm/ºC |

| Output noise (freq. Range 100Hz to 100kHz, reg. Output connected to 100nF and 10uF 2.2 ohm ESR capacitors) | 0    | 0.5 | 1   | mV rms |

| Load regulation ( I = 70mA)                                                                                | 40   | 45  | 50  | mV/A   |

| Settling time (1mA to 70mA pulse load, reg. Output connected to 100nF and 10uF 2.2 ohm ESR capacitors)     | 30   | 50  | 100 | μS     |

| Maximum output current                                                                                     | 60   | 70  | 75  | mA     |

| Minimum load current                                                                                       | 5    | 8   | 15  | μA     |

| Quiescent current (excluding load, I < 1mA)                                                                | 50   | 90  | 150 | μA     |

| Deep Sleep Mode Operation                                                                                  |      |     |     |        |

| Quiescent current (excluding load, I < 100µA)                                                              | 6    | 10  | 17  | μΑ     |

| Standby Mode                                                                                               |      |     |     |        |

| Quiescent current                                                                                          | 1.5  | 2.5 | 3.3 | μA     |

Digital part:

Page 33 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

| Digital Terminals                     | Min     | Тур     | Max      | Unit |

|---------------------------------------|---------|---------|----------|------|

| Input Voltage Levels                  |         |         | <u> </u> |      |

| Input logic level low                 | -0.4    | 0       | 0.25xVdd | V    |

| Input logic level high                | 0.7xVdd | 2.5     | Vdd+0.3  | V    |

| Output Voltage Levels                 |         |         |          |      |

| Output logic level low ( $I = 4mA$ )  | 0       | 0       | 0.12     | V    |

| Output logic level high( $I = -4mA$ ) | Vdd-0.4 | Vdd-0.1 | Vdd      | V    |

| Input and Tri-state Current with      | :       |         |          |      |

| Strong pull up                        | -100    | -40     | -10      | μA   |

| Strong pull down                      | 10      | 40      | 100      | μA   |

| Weak pull up                          | -5      | -1      | -0.2     | μA   |

| Weak pull down                        | 0.2     | 1       | 5        | μA   |

| I / O pad leakage current             | -1      | 0       | 1        | μA   |

| Input capacitance                     | 1       | 3       | 5        | pF   |

|                                       |         |         |          |      |

Crystal frequency input (reference clock input):

| Clock Source                                                         | Min | Тур  | Max  | Unit |

|----------------------------------------------------------------------|-----|------|------|------|

| Crystal Oscillator                                                   |     |      |      |      |

| Crystal Frequency (250kHz per one step)                              | 26  | 26   | 26   | MHz  |

| Frequency tolerance (at +25°C temperature)                           | -15 | -    | +15  | ppm  |

| Digital trim range (internal capacitance at min & max value)         | 5   | 6.2  | 8    | pF   |

| Trim step size (internal capacitance at min & max value)             | 0   | 0.1  | 0.1  | pF   |

| Transconductance                                                     | 2   | 4    | 4    | mS   |

| Negative resistance (xtal = $26$ MHz, Co = $0.76$ pF. Cl = $8.5$ pF) | 870 | 1500 | 2400 | ohm  |

Reset levels:

AvantWave www.avantwave.com

Page 34 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

| Power on Reser          | Min  | Тур  | Max  | Unit |

|-------------------------|------|------|------|------|

| +1.5V falling threshold | 1.13 | 1.25 | 1.3  | V    |

| +1.5V rising threshold  | 1.2  | 1.3  | 1.35 | V    |

| Hysteresis              | 0.05 | 0.1  | 0.15 | V    |

## RSSI ADC channel:

| RSSI ADC(*)                               |       | Min  | Тур  | Max | Unit |

|-------------------------------------------|-------|------|------|-----|------|

| Resolution                                |       | 10   | 10   | 10  | Bits |

| Input voltage range (LSB size = $+1.5$ V/ | 1024) | 0    | 1.5  | 1.6 | V    |

| Accuracy (Guaranteed monotonic)           | INL   | -1   | 0    | 1   | LSB  |

| DNL                                       |       | 0    | 1    | 1   | LSB  |

| Offset                                    |       | -4   | 0    | 4   | LSB  |

| Gain Error                                |       | -0.2 | 0    | 0.2 | %    |

| Sample rate                               |       | 680  | 690  | 700 | S/s  |

| Conversion time                           |       | 2.7  | 2.75 | 2.8 | μs   |

|                                           |       |      |      |     |      |

| Input Bandwidth                           |       | 90   | 100  | 110 | kHz  |

\* RSSI Analogue to Digital Converter: The ADC applies fast AGC. The ADC samples the RSSI voltage on a step by step base. The front end LNA gain will be changed refer to the measured RSSI value(receive), the 1<sup>st</sup> mixer input signal with a limited range. It improves the dynamic range of the receiver, enhancing RF performance in noisy limited environments.

## 32kHz External Reference Clock (deep sleep mode for power saving):

| 32kHz External Reference Clock       | Min         | Тур         | Max         | Units |

|--------------------------------------|-------------|-------------|-------------|-------|

| Frequency                            | 32748       | 32768       | 32788       | Hz    |

| Frequency deviation at 25°C          | 0           | ±10         | ±20         | ppm   |

| Frequency deviation at -30°C to 85°C | ±140        | ±145        | ±150        | ppm   |

| Input high level, square wave        | 0.625 x 1.5 | 0.625 x 1.5 | 0.65 x 1.5  | V     |

| Input low level, square wave         | 0.4 x 1.5   | 0.425 x 1.5 | 0.425 x 1.5 | V     |

| Duty cycle square wave               | 30          | 50          | 70          | %     |

| Rise and fail time                   | 30          | 40          | 50          | ns    |

\* 32kHz External Reference Clock: A 32kHz clock can be implemented to either CLK\_32K or AlO[0], refer to the PSKEY\_DEEP\_SLEEP\_EXTERNAL\_CLOCK\_SOURCE. Once the external clock is implemented to the analog AlO [0] pad in the 1.5V supply domain, the digital signal would be limited as +1.5V maximum driven voltage. If 32kHz clock is under 200ppm accuracy, the enhance power saving feature can be added.

\* 32kHz crystal is a optional selection (external circuitry), if seeking the power saving mode, 32kHz crystal is a must.

Otherwise, it can be NC.

AvantWave www.avantwave.com

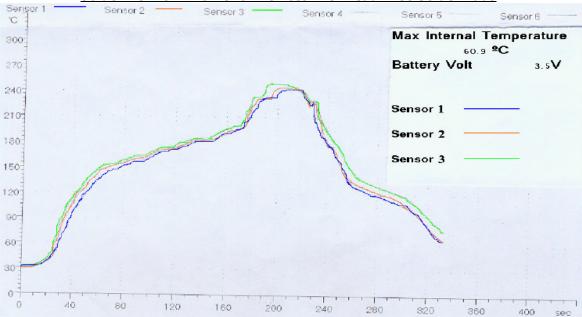

# Solder Profiles

In order to setup your application, it is required to have the soldering profile which is based on various parameters.

| Zone             | Sensor | Description                                                                                                                                                                                                                       |

|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preheat Zone     | 1-2    | This zone raises the temperature at a controlled rate. Generally 1~2.5°C/s.                                                                                                                                                       |

| Equilibrium Zone | 3      | This zone brings the board to a uniform temperature and also activates the flux. The duration in this zone will need to be adjusted to optimize the out gassing of the flux. Generally 120~180s duration.                         |

| Reflow Zone      | 4      | The peak temperature should be high enough to achieve good wetting but not so high as to cause component discoloration or damage. Excessive soldering time can lead to inter-metallic growth which can result in a brittle joint. |

| Cooling Zone     | 5-6    | The cooling rate should be fast, to keep the solder grains small which will give longer lasting joint. Generally 2~5°C/s.                                                                                                         |

|                  |        | Table 14 Soldering zones                                                                                                                                                                                                          |

Table 14. Soldering zones

### \*\* Normally, the components endure 2 times reflow & peak temperature around 255°C+/- 5°C. Solder Re-Flow Profile for Devices with Lead-Free Solder Pads

## Temperature Analysis at 200°C

| Sensor | Max °C | Max at (s) | Over (s) |

|--------|--------|------------|----------|

| S1     | 245.6  | 204.5      | 53       |

| S2     | 244.3  | 209        | 52       |

| S3     | 251.3  | 196        | 52       |

Fig. 14 Reflow soldering temperature

Hand soldering conditions:

- 1. Maximum hand soldering points  $\leq 8$  (not included to remove the shield can)

- 2. Maximum hand soldering times per each point( $3 \sim 5 \text{ seconds}$ )  $\leq 4$  with the solder iron temperature around  $360^{\circ}\text{C}$  +/-  $20^{\circ}\text{C}$

AvantWave www.avantwave.com

Page 36 Datasheet BTR602 v2.4 Last Update 30/Apr/2014

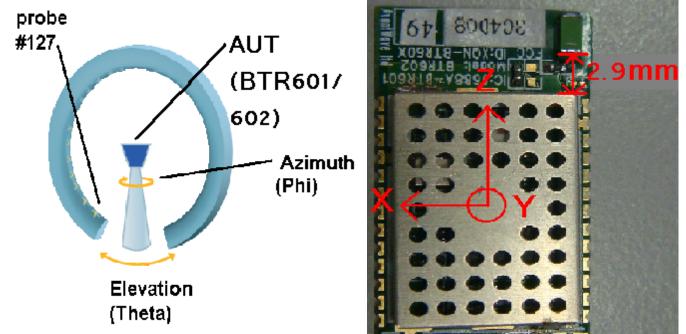

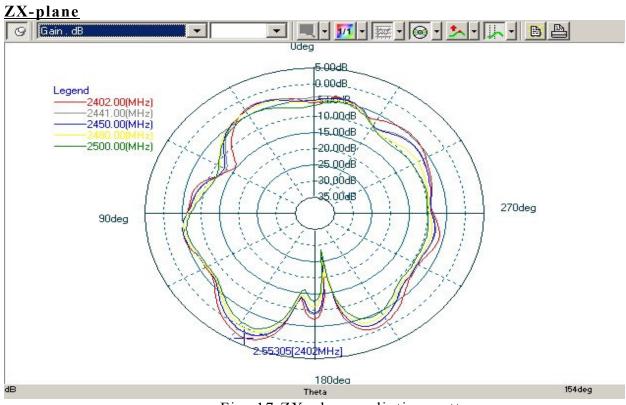

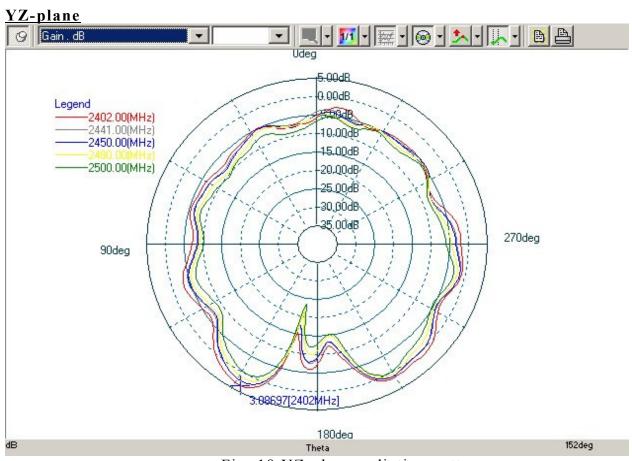

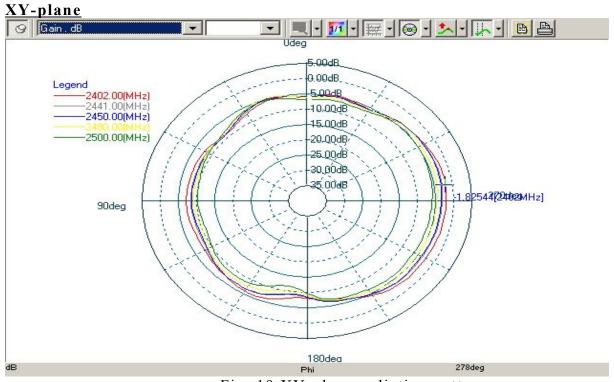

# **Module radiative characteristics**

The AUT is feed by a coaxial cable inserted with an attenuator and common mode current chocking components. During measurements, the AUT is rotated 180° with a step of 2.61°. As per each special measurement point, the dual polarization crossed probe filed intensity of Phi polarization (Azimuth) and Theta (Elevation) accordingly. After calibration, the system software computes the configure data and antenna parameters of the AUT. Probes are placed each 2.61° in Elevation. In azimuth, a complete rotation of the antenna is suitable to average results and get a better uncertainty. The AUT is under passive mode during the test.

Fig. 15 Laboratory setup environment & BTR602 AUT radiative measurement direction

| Frequency (MHz) | Average power gain (dBi) | Radiation Efficiency (%) |

|-----------------|--------------------------|--------------------------|

| 2402            | 3.2                      | 41                       |

| 2441            | 2.1                      | 34                       |

| 2450            | 2.1                      | 33                       |