# NI High-Speed Serial Instruments User Manual

PXIe-6591R PXIe-6592R PXIe-7902

April 2017 374574E-01

## Worldwide Technical Support and Product Information

#### Worldwide Offices

Visit ni.com/niglobal to access the branch office websites, which provide up-to-date contact information, support phone numbers, email addresses, and current events.

#### National Instruments Corporate Headquarters

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

For further support information, refer to the *NI Services* appendix. To comment on National Instruments documentation, refer to the National Instruments website at ni.com/info and enter the Info Code feedback.

© 2014-2017 National Instruments. All rights reserved.

#### Limited Warranty

This document is provided 'as is' and is subject to being changed, without notice, in future editions. For the latest version, refer to ni.com/manuals. NI reviews this document carefully for technical accuracy; however, NI MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMATION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS.

NI warrants that its hardware products will be free of defects in materials and workmanship that cause the product to fail to substantially conform to the applicable NI published specifications for one (1) year from the date of invoice.

For a period of ninety (90) days from the date of invoice, NI warrants that (i) its software products will perform substantially in accordance with the applicable documentation provided with the software and (ii) the software media will be free from defects in materials and workmanship.

If NI receives notice of a defect or non-conformance during the applicable warranty period, NI will, in its discretion: (i) repair or replace the affected product, or (ii) refund the fees paid for the affected product. Repaired or replaced Hardware will be warranted for the remainder of the original warranty period or ninety (90) days, whichever is longer. If NI elects to repair or replace the product, NI may use new or refurbished parts or products that are equivalent to new in performance and reliability and are at least functionally equivalent to the original part or product.

You must obtain an RMA number from NI before returning any product to NI. NI reserves the right to charge a fee for examining and testing Hardware not covered by the Limited Warranty.

This Limited Warranty does not apply if the defect of the product resulted from improper or inadequate maintenance, installation, repair, or calibration (performed by a party other than NI); unauthorized modification; improper environment; use of an improper hardware or software key; improper use or operation outside of the specification for the product; improper voltages; accident, abuse, or neglect; or a hazard such as lightning, flood, or other act of nature.

THE REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND THE CUSTOMER'S SOLE REMEDIES, AND SHALL APPLY EVEN IF SUCH REMEDIES FAIL OF THEIR ESSENTIAL PURPOSE.

EXCEPT AS EXPRESSLY SET FORTH HEREIN, PRODUCTS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND AND NI DISCLAIMS ALL WARRANTIES, EXPRESSED OR IMPLIED, WITH RESPECT TO THE PRODUCTS, INCLUDING ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE OR NON-INFRINGEMENT, AND ANY WARRANTIES THAT MAY ARISE FROM USAGE OF TRADE OR COURSE OF DEALING. NI DOES NOT WARRANT, GUARANTEE, OR MAKE ANY REPRESENTATIONS REGARDING THE USE OF OR THE RESULTS OF THE USE OF THE PRODUCTS IN TERMS OF CORRECTNESS, ACCURACY, RELIABILITY, OR OTHERWISE. NI DOES NOT WARRANT THAT THE OPERATION OF THE PRODUCTS WILL BE UNINTERRUPTED OR ERROR FREE.

In the event that you and NI have a separate signed written agreement with warranty terms covering the products, then the warranty terms in the separate agreement shall control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

National Instruments respects the intellectual property of others, and we ask our users to do the same. NI software is protected by copyright and other intellectual property laws. Where NI software may be used to reproduce software or other materials belonging to others, you may use NI software only to reproduce materials that you may reproduce in accordance with the terms of any applicable license or other legal restriction.

#### End-User License Agreements and Third-Party Legal Notices

You can find end-user license agreements (EULAs) and third-party legal notices in the following locations:

- Notices are located in the <National Instruments>\\_Legal Information and <National Instruments> directories.

- EULAs are located in the <National Instruments>\Shared\MDF\Legal\license directory.

- Review <National Instruments>\\_Legal Information.txt for information on including legal information in

installers built with NI products.

#### U.S. Government Restricted Rights

If you are an agency, department, or other entity of the United States Government ("Government"), the use, duplication, reproduction, release, modification, disclosure or transfer of the technical data included in this manual is governed by the Restricted Rights provisions under Federal Acquisition Regulation 52.227-14 for civilian agencies and Defense Federal Acquisition Regulation 252.227-7015 for military agencies.

#### Trademarks

Refer to the *NI Trademarks and Logo Guidelines* at ni.com/trademarks for more information on National Instruments trademarks.

ARM, Keil, and µVision are trademarks or registered of ARM Ltd or its subsidiaries.

LEGO, the LEGO logo, WEDO, and MINDSTORMS are trademarks of the LEGO Group.

TETRIX by Pitsco is a trademark of Pitsco, Inc.

FIELDBUS FOUNDATION<sup>™</sup> and FOUNDATION<sup>™</sup> are trademarks of the Fieldbus Foundation.

EtherCAT® is a registered trademark of and licensed by Beckhoff Automation GmbH.

CANopen® is a registered Community Trademark of CAN in Automation e.V.

DeviceNet<sup>™</sup> and EtherNet/IP<sup>™</sup> are trademarks of ODVA.

Go!, SensorDAQ, and Vernier are registered trademarks of Vernier Software & Technology. Vernier Software & Technology and vernier.com are trademarks or trade dress.

Xilinx is the registered trademark of Xilinx, Inc.

Taptite and Trilobular are registered trademarks of Research Engineering & Manufacturing Inc.

FireWire® is the registered trademark of Apple Inc.

Linux® is the registered trademark of Linus Torvalds in the U.S. and other countries.

Handle Graphics<sup>®</sup>, MATLAB<sup>®</sup>, Real-Time Workshop<sup>®</sup>, Simulink<sup>®</sup>, Stateflow<sup>®</sup>, and xPC TargetBox<sup>®</sup> are registered trademarks, and TargetBox<sup>™</sup> and Target Language Compiler<sup>™</sup> are trademarks of The MathWorks, Inc.

Tektronix®, Tek, and Tektronix, Enabling Technology are registered trademarks of Tektronix, Inc.

The Bluetooth® word mark is a registered trademark owned by the Bluetooth SIG, Inc.

The ExpressCard<sup>™</sup> word mark and logos are owned by PCMCIA and any use of such marks by National Instruments is under license.

The mark LabWindows is used under a license from Microsoft Corporation. Windows is a registered trademark of Microsoft Corporation in the United States and other countries.

Other product and company names mentioned herein are trademarks or trade names of their respective companies.

Members of the National Instruments Alliance Partner Program are business entities independent from National Instruments and have no agency, partnership, or joint-venture relationship with National Instruments.

#### Patents

For patents covering National Instruments products/technology, refer to the appropriate location: **Help»Patents** in your software, the patents.txt file on your media, or the *National Instruments Patent Notice* at ni.com/patents.

#### Export Compliance Information

Refer to the *Export Compliance Information* at ni.com/legal/export-compliance for the National Instruments global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

YOU ARE ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY AND RELIABILITY OF THE PRODUCTS WHENEVER THE PRODUCTS ARE INCORPORATED IN YOUR SYSTEM OR APPLICATION, INCLUDING THE APPROPRIATE DESIGN, PROCESS, AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

PRODUCTS ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING IN THE OPERATION OF NUCLEAR FACILITIES; AIRCRAFT NAVIGATION; AIR TRAFFIC CONTROL SYSTEMS; LIFE SAVING OR LIFE SUSTAINING SYSTEMS OR SUCH OTHER MEDICAL DEVICES; OR ANY OTHER APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, PRUDENT STEPS MUST BE TAKEN TO PROTECT AGAINST FAILURES, INCLUDING PROVIDING BACK-UP AND SHUT-DOWN MECHANISMS. NI EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES.

# Compliance

## Electromagnetic Compatibility Information

This hardware has been tested and found to comply with the applicable regulatory requirements and limits for electromagnetic compatibility (EMC) as indicated in the hardware's Declaration of Conformity  $(DoC)^1$ . These requirements and limits are designed to provide reasonable protection against harmful interference when the hardware is operated in the intended electromagnetic environment. In special cases, for example when either highly sensitive or noisy hardware is being used in close proximity, additional mitigation measures may have to be employed to minimize the potential for electromagnetic interference.

While this hardware is compliant with the applicable regulatory EMC requirements, there is no guarantee that interference will not occur in a particular installation. To minimize the potential for the hardware to cause interference to radio and television reception or to experience unacceptable performance degradation, install and use this hardware in strict accordance with the instructions in the hardware documentation and the  $DoC^1$ .

If this hardware does cause interference with licensed radio communications services or other nearby electronics, which can be determined by turning the hardware off and on, you are encouraged to try to correct the interference by one or more of the following measures:

- Reorient the antenna of the receiver (the device suffering interference).

- Relocate the transmitter (the device generating interference) with respect to the receiver.

- Plug the transmitter into a different outlet so that the transmitter and the receiver are on different branch circuits.

Some hardware may require the use of a metal, shielded enclosure (windowless version) to meet the EMC requirements for special EMC environments such as, for marine use or in heavy industrial areas. Refer to the hardware's user documentation and the  $DoC^1$  for product installation requirements.

When the hardware is connected to a test object or to test leads, the system may become more sensitive to disturbances or may cause interference in the local electromagnetic environment.

Operation of this hardware in a residential area is likely to cause harmful interference. Users are required to correct the interference at their own expense or cease operation of the hardware.

Changes or modifications not expressly approved by National Instruments could void the user's right to operate the hardware under the local regulatory rules.

<sup>&</sup>lt;sup>1</sup> The Declaration of Conformity (DoC) contains important EMC compliance information and instructions for the user or installer. To obtain the DoC for this product, visit ni.com/certification, search by model number or product line, and click the appropriate link in the Certification column.

#### About This Manual

| Related Documentation | xi  |

|-----------------------|-----|

| Xilinx Documentation  | xiv |

| Additional Resources  | xiv |

#### Chapter 1 Before You Begin

| Development Requirements     | 1-1 |

|------------------------------|-----|

| Xilinx Licensing Information |     |

| Installation Instructions    |     |

#### Chapter 2 PXIe-6591R Hardware Architecture

| PXIe-6591R Module Overview |  |

|----------------------------|--|

| Clocking Architecture      |  |

| PXIe-6591R Clocking        |  |

#### Chapter 3

#### Connecting and Interfacing with the PXIe-6591R

| Front Panel                              | 3-1 |

|------------------------------------------|-----|

| Recommended Mating Cables and Connectors | 3-2 |

| Transceiver Lane and Quad Mapping        | 3-2 |

| Signal Routing                           | 3-3 |

| Socketed CLIP Interface                  | 3-3 |

| PXIe-6591R Socketed CLIP                 | 3-4 |

#### Chapter 4

#### PXIe-6592R Hardware Architecture

| PXIe-6592R Module Overview |  |

|----------------------------|--|

| Clocking Architecture      |  |

| PXIe-6592R Clocking        |  |

#### Chapter 5

#### Connecting and Interfacing with the PXIe-6592R

| Front Panel                              |  |

|------------------------------------------|--|

| Recommended Mating Cables and Connectors |  |

| Transceiver Lane and Quad Mapping        |  |

| Signal Routing                           |  |

| Socketed CLIP Interface                  |  |

| PXIe-6592R Socketed CLIP                 |  |

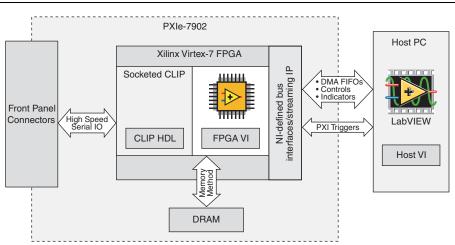

#### Chapter 6 PXIe-7902 Hardware Architecture

| PXIe-7902 Module Overview | 6-2 |

|---------------------------|-----|

| Clocking Architecture     | 6-3 |

| NI 7902 Clocking          |     |

#### Chapter 7 Connecting and Interfacing with the PXIe-7902

| Front Panel                              | 7-1 |

|------------------------------------------|-----|

| Recommended Mating Cables and Connectors | 7-2 |

| Transceiver Lane and Quad Mapping        | 7-2 |

| Signal Routing                           | 7-3 |

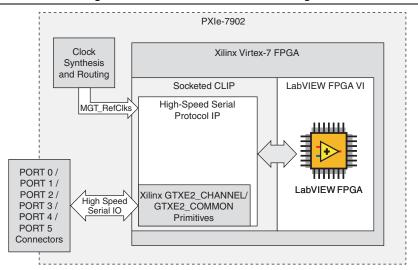

| Socketed CLIP Interface                  | 7-3 |

| PXIe-7902 Socketed CLIP                  | 7-4 |

|                                          |     |

### Chapter 8

#### Developing Applications for the High-Speed Serial Device

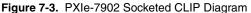

| Development Flow                                                     | 8-1  |

|----------------------------------------------------------------------|------|

| Socketed CLIP Development                                            | 8-1  |

| Accessing the Xilinx Vivado Tools                                    | 8-2  |

| Generating an IP Core from the Xilinx Vivado IP Catalog              | 8-3  |

| Modifying Third-Party IP Core Logic                                  | 8-3  |

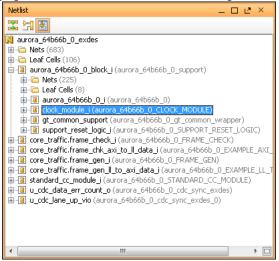

| Building a Netlist from the IP Core                                  | 8-4  |

| Writing a VHDL Wrapper Around the Protocol IP Core                   | 8-6  |

| Constraints and Hierarchy                                            |      |

| Documenting Your IP                                                  | 8-8  |

| Improving Performance in Larger Designs through Enable Chain Removal | 8-8  |

| Developing with LabVIEW FPGA                                         | 8-9  |

| Configuring the High-Speed Serial Device LabVIEW FPGA Targets        | 8-9  |

| Using Existing VHDL IP inside CLIP or IPIN                           | 8-13 |

| Adding High-Speed Serial Device Target I/O                           | 8-13 |

| Using the NI Common Instrument Design Libraries                      | 8-14 |

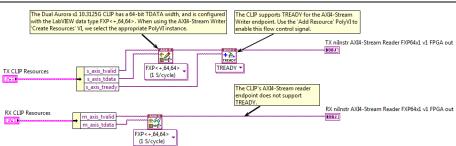

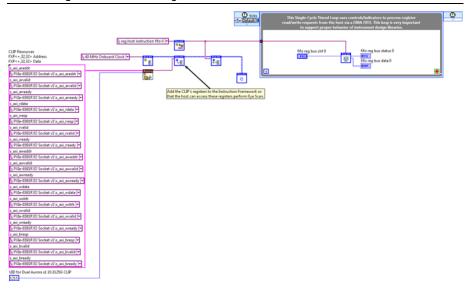

| Using niInstr Instruction Framework                                  |      |

| Using niInstr Streaming                                              | 8-15 |

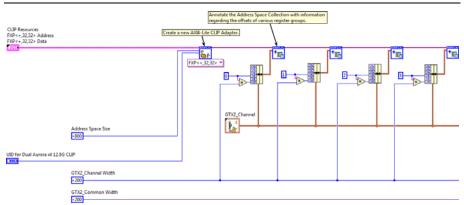

| Using niInstr CLIP Adapters                                          | 8-15 |

| Using niInstr Data Trigger                                           | 8-15 |

| Using niInstr Basic Elements                                         | 8-16 |

| Using niInstr Eye Scan                                               | 8-16 |

| Connecting AXI4-Lite and AXI4-Stream Interfaces to the Host          | 8-16 |

| Connecting Signals to Enable Eye Scan                                | 8-17 |

| Compiling LabVIEW FPGA VIs                                           | 8-19 |

|                                                                      |      |

| LabVIEW and System Integration                                           | 8-19   |

|--------------------------------------------------------------------------|--------|

| Download, Reset, and Run Side Effects in the LabVIEW FPGA Host Interface | . 8-19 |

| DMA Streaming                                                            | . 8-19 |

| Peer-to-Peer Streaming                                                   | 8-21   |

| Maximizing Peer-to-Peer Streaming Throughput                             | . 8-21 |

| PXI Triggers                                                             | . 8-21 |

| Configuring Trigger Pulses                                               | 8-21   |

| Reserving PXI Triggers                                                   | . 8-22 |

| Reserving Trigger Lines in MAX                                           | . 8-22 |

| Reserving Trigger Lines in the LabVIEW FPGA Host VI                      | . 8-22 |

| Reserving Trigger Lines                                                  | . 8-22 |

| Releasing Trigger Lines                                                  | 8-23   |

| Monitoring Power and Temperature                                         | . 8-23 |

| Soft Shutdown                                                            | . 8-24 |

| Power/Thermal Protection and Shutdown                                    | . 8-24 |

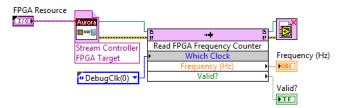

| Debugging Clocks Using Frequency Counters                                | . 8-24 |

| Debugging Link Connections Using Eye Scan                                | . 8-25 |

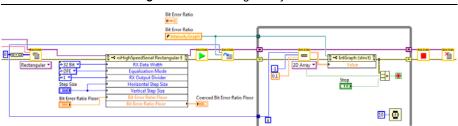

| Rectangular Eye Scan                                                     | . 8-25 |

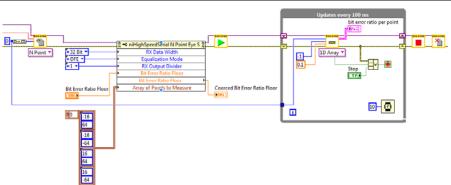

| N Point Eye Scan                                                         | . 8-26 |

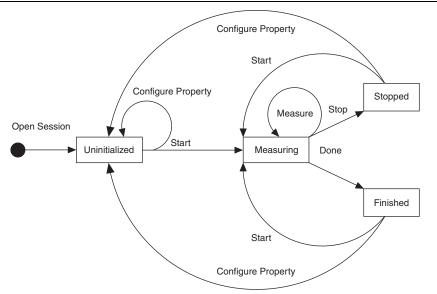

| Eye Scan State Model                                                     |        |

#### Appendix A Troubleshooting

#### Appendix B Xilinx Documentation References

#### Appendix C NI Services

#### Glossary

#### Figures

| Figure 2-1. | PXIe-6591R System Architecture Elements       |  |

|-------------|-----------------------------------------------|--|

| Figure 2-2. | PXIe-6591R Clocking Diagram                   |  |

| Figure 3-1. | PXIe-6591R Front Panel Connectors and Pinouts |  |

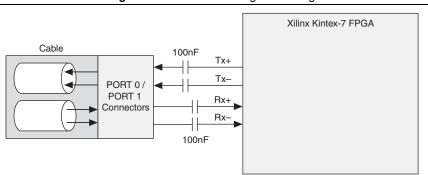

| Figure 3-2. | PXIe-6591R Signal Routing                     |  |

| Figure 3-3. | PXIe-6591R Socketed CLIP Diagram              |  |

| Figure 4-1. | PXIe-6592R System Architecture Elements       |  |

| Figure 4-2. | PXIe-6592R Clocking Diagram                   |  |

#### Contents

| Figure 5-1.  | PXIe-6592R Front Panel Connectors and Pinout           | 5-1 |

|--------------|--------------------------------------------------------|-----|

| Figure 5-2.  | PXIe-6592R Signal Routing                              |     |

| Figure 5-3.  | PXIe-6592R Socketed CLIP Diagram                       |     |

| Figure 6-1.  | PXIe-7902 System Architecture Elements                 | 6-2 |

| Figure 6-2.  | PXIe-7902 Clocking Diagram                             | 6-4 |

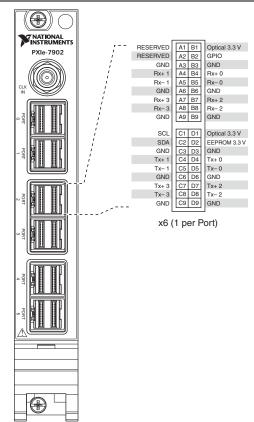

| Figure 7-1.  | PXIe-7902 Front Panel Connectors and Pinout            | 7-1 |

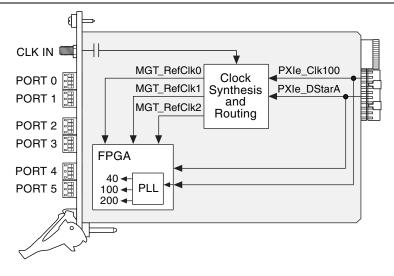

| Figure 7-2.  | PXIe-7902 Signal Routing                               | 7-3 |

| Figure 7-3.  | PXIe-7902 Socketed CLIP Diagram                        | 7-4 |

| Figure 8-1.  | High-Speed Serial Development Process                  |     |

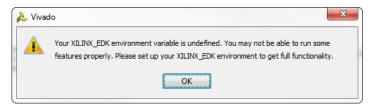

| Figure 8-2.  | EDK Environment Error Message                          |     |

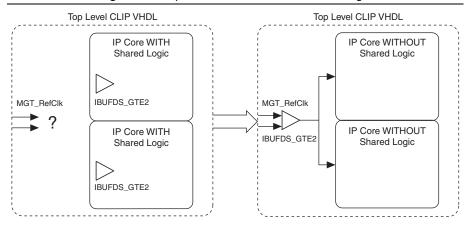

| Figure 8-3.  | Top-Level CLIP VHDL and Shared Logic                   |     |

| Figure 8-4.  | Instruction Framework Overview.                        |     |

| Figure 8-5.  | Create AXI4 Resources VI Block Diagram                 |     |

| Figure 8-6.  | Connecting CLIP Resources to the Instruction Framework |     |

| Figure 8-7.  | Create AXI4-Lite Resources.vi                          |     |

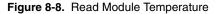

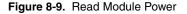

| Figure 8-8.  | Read Module Temperature                                |     |

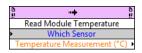

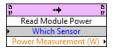

| Figure 8-9.  | Read Module Power                                      |     |

| Figure 8-10. | Rectangular Eye Scan                                   |     |

| Figure 8-11. | N Point Eye Scan                                       |     |

| Figure 8-12. | Eye Scan State Model                                   |     |

| Tables       |                                                        |     |

| Table 1.     | Documentation Locations and Descriptions               | xi  |

| Table 2.     | Xilinx Documentation                                   |     |

| Table 1-1.   | Fundamentals Resources                                 | 1-1 |

| Table 2-1.   | PXIe-6591R Key Features                                | 2-2 |

| Table 2-2.   | PXIe-6591R Reference Clocks                            | 2-3 |

| Table 3-1.   | PXIe-6591R Front Panel Connectors                      |     |

| Table 3-2.   | Transceiver Lane and Quad Mapping                      |     |

| Table 3-3.   | Clock Signal and Quad Mapping                          | 3-3 |

| Table 3-4.   | PXIe-6591R CLIP Signals                                |     |

| Table 4-1.   | PXIe-6592R Key Features                                | 4-2 |

| Table 4-2.   | NI 6591R Reference Clocks                              | 4-3 |

| Table 4-3.   | PXIe-6592R Reference Clocks                            | 4-3 |

| Table 4-4.   | NI 6591R Reference Clocks                              | 4-4 |

| Table 5-1. | PXIe-6592R Front Panel Connectors            |     |

|------------|----------------------------------------------|-----|

| Table 5-2. | Transceiver Lane and Quad Mapping            |     |

| Table 5-3. | Clock Signal and Quad Mapping                |     |

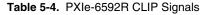

| Table 5-4. | PXIe-6592R CLIP Signals                      |     |

| Table 6-1. | PXIe-7902 Key Features                       |     |

| Table 6-2. | PXIe-7902 Reference Clocks                   |     |

| Table 7-1. | PXIe-7902 Front Panel Connectors             |     |

| Table 7-2. | Transceiver Lane and Quad Mapping            |     |

| Table 7-3. | Clock Signal and Quad Mapping                |     |

| Table 7-4. | PXIe-7902 Socketed CLIP Signals              |     |

| Table 8-1. | PXIe-6591R Clocking and Routing Dependencies |     |

| Table 8-2. | NI 6592R Clocking and Routing Dependencies   |     |

| Table B-1. | Xilinx 7-Series FPGA Documentation           | B-1 |

# About This Manual

The *NI High-Speed Serial Instruments User Manual* describes how to develop applications for use with the PXIe-6591R, PXIe-6592R, and PXIe-7902 high-speed serial FPGA targets.

The PXIe-6591R, PXIe-6592R, and PXIe-7902 are designed for use in the following applications:

- Real-time data transmission, reception, and validation

- Functional test for semiconductor production

- Device interfacing

- High performance embedded systems

This manual provides detailed information about the electrical and mechanical requirements of component-level IP (CLIP) and LabVIEW FPGA design.

Chapters 2 and 3 contain information about the PXIe-6591R hardware architecture and functionality, respectively. Chapters 4 and 5 contain information about the PXIe-6592R hardware architecture and functionality, respectively. Chapters 6 and 7 contain information about the PXIe-7902 hardware architecture and functionality, respectively. Chapter 8 contains information about how to develop applications for all high-speed serial devices.

## **Related Documentation**

The following documents contain information that you may find helpful as you read this manual.

| Document                            | Location                                             | Description                                               |

|-------------------------------------|------------------------------------------------------|-----------------------------------------------------------|

| NI PXIe-6591R Specifications        | Available from the Start menu and at ni.com/manuals. | Contains specifications for your PXIe-6591R module.       |

| NI PXIe-6592R Specifications        | Available from the Start menu and at ni.com/manuals. | Contains specifications for your PXIe-6592R module.       |

| PXIe-7902 Specifications            | Available from the Start menu and at ni.com/manuals. | Contains specifications for your PXIe-7902 module.        |

| PXIe-6591R Getting Started<br>Guide | Available from the Start menu and at ni.com/manuals. | Contains installation<br>instructions for your<br>system. |

| Document                                 | Location                                             | Description                                                                                                                              |

|------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| PXIe-6592R Getting Started<br>Guide      | Available from the Start menu and at ni.com/manuals. | Contains installation<br>instructions for your<br>system.                                                                                |

| PXIe-7902 Getting Started Guide          | Available from the Start menu and at ni.com/manuals. | Contains installation<br>instructions for your<br>system.                                                                                |

| NI High-Speed Serial Instruments<br>Help | Available from the Start menu and at ni.com/manuals. | Contains information about<br>how to add FPGA I/O to<br>your project, and how to<br>configure your high-speed<br>serial device with VIs. |

Table 1. Documentation Locations and Descriptions (Continued)

| Document                      |                                                                    | Location                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LabVIEW FPGA<br>documentation | NI LabVIEW<br>High-<br>Performance<br>FPGA<br>Developer's<br>Guide | Available at ni.com/<br>tutorial.                                                                                                                                                                                                                                                                                                                                                                                                                        | Summarizes the most<br>effective techniques for<br>optimizing throughput,<br>latency, and FPGA<br>resources when using the<br>LabVIEW FPGA Module<br>and the NI RIO hardware<br>platform.                                                                                                                                                                                                                                                                         |  |

|                               | FPGA<br>Module Help                                                | This document is a<br>book within the<br><i>LabVIEW Help</i> . Access<br>this document by<br>navigating to <b>Start»All</b><br><b>Programs»National</b><br><b>Instruments»</b><br><b>LabVIEW»</b><br><b>LabVIEW Help</b> , or by<br>searching for <i>FPGA</i><br><i>Module Help</i> at<br>ni.com/manuals.<br>Browse to the <b>FPGA</b><br><b>Module</b> book in the<br><b>Contents</b> tab for<br>information about<br>using the LabVIEW<br>FPGA Module. | With the LabVIEW FPGA<br>Module and LabVIEW,<br>you can create VIs that run<br>on National Instruments<br>FPGA targets.<br>The <i>Getting Started with</i><br><i>the LabVIEW FPGA</i> book<br>provides links to the top<br>resources that you can use<br>to get started with<br>LabVIEW FPGA.<br>The <i>Integrating</i><br><i>Third-Party IP (FPGA</i><br><i>Module)</i> book contains<br>information about adding<br>custom HDL code to your<br>LabVIEW project. |  |

|                               | LabVIEW<br>FPGA<br>Module<br>Release and<br>Upgrade<br>Notes       | Available at ni.com/<br>manuals.You can also<br>view this document by<br>selecting Start»All<br>Programs»National<br>Instruments»<br>LabVIEW»<br>LabVIEW Manuals.                                                                                                                                                                                                                                                                                        | Contains information<br>about installing the<br>LabVIEW FPGA Module,<br>describes new features, and<br>provides upgrade<br>information.                                                                                                                                                                                                                                                                                                                           |  |

Table 1. Documentation Locations and Descriptions (Continued)

#### Xilinx Documentation

Xilinx FPGA documentation provides information required for the successful development of your high-speed serial device. The following table provides a list of specific Xilinx documentation resources.

All Xilinx documentation can be found at www.xilinx.com.

| Document                                                                            | Document Part<br>Number | Description                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 Series FPGAs Overview                                                             | DS180                   | Outlines the features and product<br>selection of the Xilinx 7 series<br>FPGAs: Artix-7, Kintex-7, and<br>Virtex-7 devices.                                                                                     |

| Kintex-7 FPGAs Data Sheet: DC<br>and AC Switching<br>Characteristics                | DS182                   | Contains the DC and AC<br>switching characteristic<br>specifications for the Kintex-7<br>FPGAs.                                                                                                                 |

| Vivado Design Suite: Release<br>Notes, Installation, and<br>Licensing               | UG973                   | Provides an overview of the new<br>release of the Vivado Design<br>Suite, including information<br>on new and changed features,<br>installation requirements for<br>the software, and licensing<br>information. |

| High-Speed Serial I/O Made<br>Simple: A Designer's Guide, with<br>FPGA Applications |                         | Recommended for users new to high-speed serial.                                                                                                                                                                 |

| 7 Series FPGAs GTX/GTH<br>Transceivers User Guide                                   | UG476                   | Technical reference describing<br>the 7 series FPGAs GTX/GTH<br>transceivers.                                                                                                                                   |

| Vivado Design Suite User Guide:<br>Using Constraints                                | UG903                   | Describes using Xilinx Design<br>Constraints (XDC) in Vivado<br>tools.                                                                                                                                          |

| Table 2. Allin Documentation | Table | 2. | Xilinx | Documentation |

|------------------------------|-------|----|--------|---------------|

|------------------------------|-------|----|--------|---------------|

#### **Additional Resources**

The software-designed instruments webpage, located at ni.com/

software-designed-instruments, contains product information, white papers, and videos to help you develop applications.

# Before You Begin

This section contains information you need before developing applications using the high-speed serial devices.

## **Development Requirements**

Successful system design with the high-speed serial devices may require knowledge in the following areas, depending on your application.

- High-speed serial fundamentals

- VHDL code design

- NI LabVIEW and LabVIEW FPGA programming

If you are unfamiliar with any of these concepts, refer to the following table for a list of resources for learning the fundamentals required for development with high-speed serial devices.

| Concept                        | Resources                                                                                                                                                                                                                                                                                                           |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-speed serial fundamentals | High-Speed Serial I/O Made Simple: A<br>Designers' Guide, with FPGA Applications,<br>available at xilinx.com.                                                                                                                                                                                                       |

| VHDL code design               | Some VHDL training or experience is required<br>before working with the high-speed serial<br>devices. Do not attempt to develop<br>Component-Level IP (CLIP) without VHDL<br>knowledge. Refer to <i>An Introduction to</i><br><i>NI High-Speed Serial Instruments</i> for<br>information about programming options. |

| NI LabVIEW and LabVIEW FPGA    | NI LabVIEW and LabVIEW FPGA training are<br>available at ni.com/training. You can also<br>refer to the NI LabVIEW High-Performance<br>FPGA Developer's Guide, available at ni.com/<br>tutorial.                                                                                                                     |

Table 1-1.

Fundamentals Resources

## Xilinx Licensing Information

Refer to the *Xilinx Documentation* section in *About This Manual* for a list of Xilinx documentation that contains important Xilinx licensing information.

## Installation Instructions

Refer to the getting started guide for your device (refer to the *Related Documentation* section of this document) for instructions about how to install LabVIEW, LabVIEW FPGA, the NI LabVIEW Instrument Design Libraries for High Speed Serial Instruments software, and your high-speed serial device.

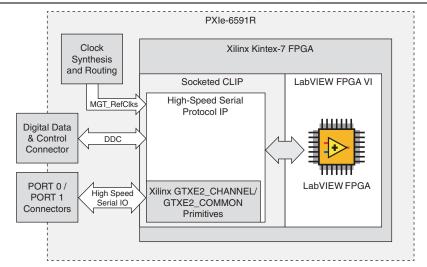

## PXIe-6591R Hardware Architecture

The following chapter contains information about the PXIe-6591R clocking architecture.

The PXIe-6591R is a high-speed serial interfacing module. The PXIe-6591R hardware architecture allows you to fully customize your serial digital protocol application. The high-speed serial interface uses Xilinx GTX transceiver technology; you can reuse existing protocol IP that works with Xilinx GTX transceivers, or you can develop your own protocol IP. If you develop your own protocol IP, the IP must be developed for a Xilinx Kintex-7 GTX transceiver.

Note The PXIe-6591R hardware does not require calibration.

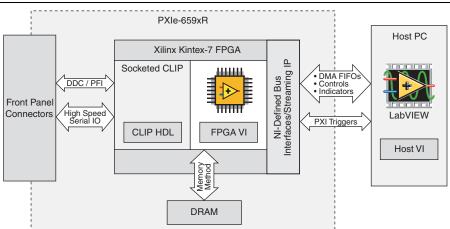

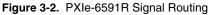

PXIe-6591R-based projects consist of the following key components:

- PXIe-6591R front panel connectors for data, clocking, and triggering external to the module

- Socketed CLIP for HDL IP and interface definition from the FPGA VI to the PXIe-6591R front panel

- Xilinx Kintex-7 FPGA

- Dynamic random access memory (DRAM)

- NI-defined bus interface from the FPGA to the host PC

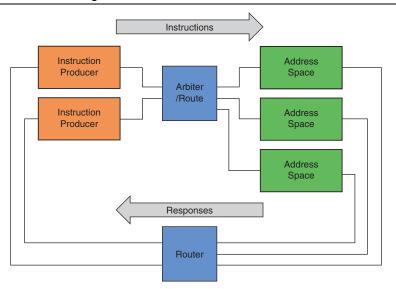

The following figure illustrates the key components of the PXIe-6591R architecture.

#### Figure 2-1. PXIe-6591R System Architecture Elements

## PXIe-6591R Module Overview

The PXIe-6591R module includes the following key features. Refer to the *PXIe-6591R Specifications* for more details.

| Line rate                       | 500 Mb/s to 8 Gb/s and 9.8 Gb/s to 12.5 Gb/s                                                                                                                                                                                                                          |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multi-gigabit transceiver lanes | 8 (4 per port)                                                                                                                                                                                                                                                        |

| Front Panel Connectors          | <ul> <li>Two Mini-SAS HD connectors (Port 0 and Port 1)<br/>for high-speed serial I/O</li> <li>One SMA (CLK IN/OUT) connector for external<br/>clock routing</li> <li>One VHDCI (Digital Data &amp; Control) for<br/>20 general-purpose input/output lines</li> </ul> |

| FPGA                            | Kintex-7 410T FFG900 package                                                                                                                                                                                                                                          |

| FPGA speed grade                | -3 (XC7K410T-3FFG900)                                                                                                                                                                                                                                                 |

| DRAM                            | <ul> <li>2 GB onboard DRAM</li> <li>166 MHz clock frequency</li> <li>Bit-width: 512-bit</li> </ul>                                                                                                                                                                    |

| Backplane connection            | Gen 2x8 PXI Express, PCIe 2.0 compliant                                                                                                                                                                                                                               |

Table 2-1. PXIe-6591R Key Features

### **Clocking Architecture**

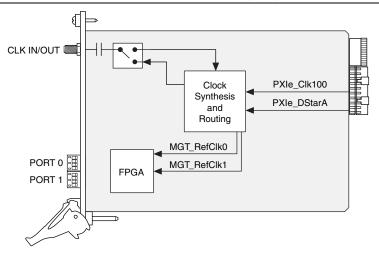

The PXIe-6591R module includes dedicated clocking hardware to provide a flexible clocking solution for generating the high-speed serial transceiver reference clocks (MGT\_RefClk). Use the **Clocking and IO** properties page in the LabVIEW project to configure the clock settings for your module. Refer to the *Configuring the High-Speed Serial Device LabVIEW FPGA Targets* section of Chapter 8, *Developing Applications for the High-Speed Serial Device*, for more detailed information about configuring clocking in your LabVIEW project.

### PXIe-6591R Clocking

The PXIe-6591R clocking architecture includes the following MGT Reference Clocks:

- MGT\_RefClk0

- MGT\_RefClk1

MGT\_RefClk0 and MGT\_RefClk1 are separate clocks, but are derived though simple integer division of a common, higher frequency PLL clock. Refer to the following table for information about the clocks' supported frequency ranges and available sources.

| Clock Name  | Frequency<br>Range | Available Sources                      |

|-------------|--------------------|----------------------------------------|

| MGT_RefClk0 | 60 MHz to          | Backplane: PXIe_Clk100 and PXIe_DStarA |

| MGT_RefClk1 | 700 MHz            | Front panel: CLK IN/OUT                |

#### Table 2-2. PXIe-6591R Reference Clocks

Refer to the *Configuring the High-Speed Serial Device LabVIEW FPGA Targets* section of Chapter 8, *Developing Applications for the High-Speed Serial Device*, for more information about how to configure Reference Clocks for your device.

The following figure illustrates the clocking circuitry on the PXIe-6591R.

Figure 2-2. PXIe-6591R Clocking Diagram

# 3

# Connecting and Interfacing with the PXIe-6591R

This chapter contains information about the PXIe-6591R module and its functionality, including front panel diagrams, connectors, and pinouts.

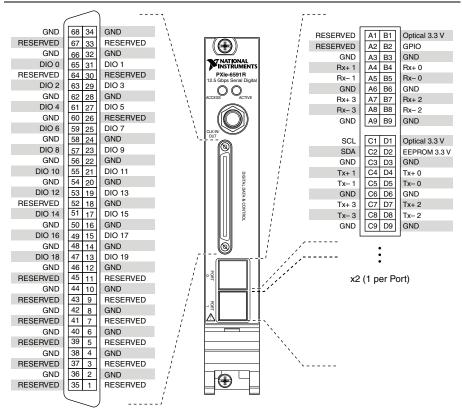

## Front Panel

The following figure shows the pinouts for the PXIe-6591R front panel connectors.

Refer to the following table for a list of the PXIe-6591R front panel connectors and their descriptions.

| Connector                    | Туре        | Description                                     |

|------------------------------|-------------|-------------------------------------------------|

| CLK IN/OUT                   | SMA         | Reference Clock input and exported clock output |

| Digital Data & Control (DDC) | VHDCI       | General purpose I/O                             |

| Port 0                       | Mini-SAS HD | High-speed serial interfacing ports             |

| Port 1                       | External    |                                                 |

Table 3-1. PXIe-6591R Front Panel Connectors

## **Recommended Mating Cables and Connectors**

Refer to the PXIe-6591R product listing page for a list of mating cables to use with your PXIe-6591R.

### Transceiver Lane and Quad Mapping

If your application requires multiple lanes, refer to Table 3-2 and Table 3-3 for information about transceiver and RefClk selection when using the Xilinx tools to generate protocol IP.

| Connector | Lane | Quad Location | Physical Resource |

|-----------|------|---------------|-------------------|

| PORT 0    | 0    | Quad 3 (Q3)   | GTX_X0Y13         |

|           | 1    |               | GTX_X0Y15         |

|           | 2    |               | GTX_X0Y14         |

|           | 3    |               | GTX_X0Y12         |

| PORT 1    | 0    | Quad 2 (Q2)   | GTX_X0Y10         |

|           | 1    |               | GTX_X0Y11         |

|           | 2    |               | GTX_X0Y9          |

|           | 3    |               | GTX_X0Y8          |

Table 3-2. Transceiver Lane and Quad Mapping

| Clock Signal | Quad Location | Physical Resource |

|--------------|---------------|-------------------|

| MGT_RefClk0  | Quad 3 (Q3)   | REFCLK1_Q3        |

| MGT_RefClk1  | Quad 2 (Q2)   | REFCLK0_Q2        |

Table 3-3. Clock Signal and Quad Mapping

For more information about lane and channel bonding caveats, refer to the 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) at xilinx.com.

**Note** The MGT\_RefClk quad location and physical resource identify the physical resource that clock signals use to enter the FPGA, but they still may act as a Reference Clock for adjacent quads. Refer to the *Reference Clock Selection and Distribution* section of *7 Series FPGAs GTX/GTH Transceivers User Guide* (UG476) for more information about cases when using single or multiple Reference Clocks for single or multiple transceivers.

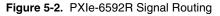

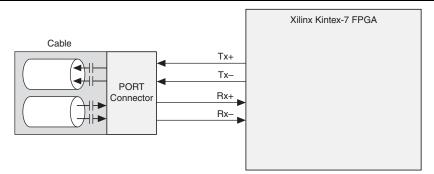

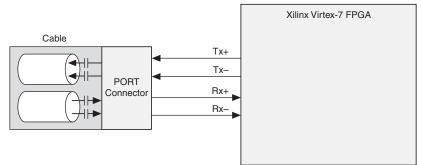

## Signal Routing

The PXIe-6591R high-speed serial differential signals are routed directly from the Kintex-7 FPGA pins to the PORT 0 and PORT 1 connector pins using a 100 nF AC-coupling capacitor, as shown in the following figure.

## Socketed CLIP Interface

Socketed CLIP allows you to insert HDL IP into an FPGA target, enabling VHDL code to communicate directly with an FPGA VI. Socketed CLIP also allows the CLIP to communicate directly with circuitry external to the FPGA.

The following sections provide information about how to configure your device for use with socketed CLIP.

#### PXIe-6591R Socketed CLIP

Refer to the following diagram for an overview of the PXIe-6591R socketed CLIP interface.

Refer to the following table for a list of the PXIe-6591R socketed CLIP signals.

| Table 3-4. | PXIe-6591R CLIP | Signals |  |

|------------|-----------------|---------|--|

|            |                 |         |  |

| Port          | Direction | Clock<br>Domain | Description                                             |

|---------------|-----------|-----------------|---------------------------------------------------------|

| MGT_RefClk0_p | In (pad)  | N/A             | Differential input clock that                           |

| MGT_RefClk0_n | In (pad)  | N/A             | you must connect to an<br>IBUFDS_GTE2 input buffer      |

| MGT_RefClk1_p | In (pad)  | N/A             | primitive when this input clock is used in your design. |

| MGT_RefClk1_n | In (pad)  | N/A             | is used in your design.                                 |

| Port                         | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                           |

|------------------------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MGT_RefClks_<br>ExtPllLocked | In        | Async           | Indicates the state of the PLL<br>within the clocking logic that<br>provides the Reference Clock to<br>the FPGA MGTs ( <b>MGT_</b><br><b>RefClkx</b> signals).                                                                        |

|                              |           |                 | Use this signal with MGT_<br>RefClks_Valid to gate and/or<br>reset the clocking signals into<br>any CLIP that depends on the<br>MGT_RefClkx signals.                                                                                  |

| MGT_RefClks_Valid            | In        | Async           | Indicates if the selected clock<br>input to the clocking logic is<br>valid and the PLL within the<br>clocking logic has locked.                                                                                                       |

|                              |           |                 | Use this signal to gate and/or reset the clocking signals into any CLIP that depends on the <b>MGT_RefClkx</b> signals.                                                                                                               |

|                              |           |                 | On the rising edge of MGT_<br>RefClks_Valid, you may need<br>to reset or relock state machines<br>and/or internal PLLs sensitive to<br>MGT_RefClkx signals.                                                                           |

| DebugClks(3:0)               | Out       | Clock           | Debug ports to aid in debugging<br>the clocking connections in the<br>CLIP. These ports connect to<br>frequency counters that can<br>monitor the frequency of any<br>clock that you connect to these<br>ports.                        |

|                              |           |                 | Refer to the <i>Debugging Clocks</i><br><i>Using Frequency Counters</i><br>section of Chapter 8, <i>Developing</i><br><i>Applications for the High-Speed</i><br><i>Serial Device</i> , for details about<br>how to use these signals. |

Table 3-4. PXIe-6591R CLIP Signals (Continued)

| Port                         | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ExportedUser<br>ReferenceClk | Out       | Clock           | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LED_ActiveRed                | Out       | Async           | The front panel Active<br>indicator's red LED turns on<br>when this signal is driven high.<br>The CLIP's access to this LED<br>may be temporarily overridden<br>to show error conditions,<br>temperature faults, and power<br>faults.<br>This signal is conditioned with<br>the pulse stretcher to guarantee a<br>minimum assertion time of<br>100 ms to comply with PXI<br>guidelines and to facilitate visual<br>perception. You can drive this<br>signal asynchronously if you<br>provide a 50 ns minimum<br>assertion time. You can also<br>drive this signal synchronously<br>for a minimum 1 cycle of<br>SocketClk40. |

Table 3-4.

PXIe-6591R CLIP Signals (Continued)

| Port            | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED_ActiveGreen | Out       | Async           | The front panel Active<br>indicator's green LED turns on<br>when this signal is driven high.                                                                                                                                                                                                                                                                                       |

|                 |           |                 | The CLIP's access to this LED<br>may be temporarily overridden<br>to show error conditions,<br>temperature faults, and power<br>faults.                                                                                                                                                                                                                                            |

|                 |           |                 | This signal is conditioned with<br>the pulse stretcher to guarantee a<br>minimum assertion time of<br>100 ms to comply with PXI<br>guidelines and to facilitate visual<br>perception. You can drive this<br>signal asynchronously if you<br>provide a 50 ns minimum<br>assertion time. You can also<br>drive this signal synchronously<br>for a minimum 1 cycle of<br>SocketClk40. |

| SocketClk40     | In        | Clock           | A 40 MHz clock that runs<br>continuously regardless of<br>connectivity. This signal is<br>connected to the <b>40 MHz</b><br><b>Onboard Clock</b> signal, which is<br>the default top-level clock for<br>the LabVIEW FPGA VI.                                                                                                                                                       |

Table 3-4. PXIe-6591R CLIP Signals (Continued)

| Port                              | Direction | Clock<br>Domain | Description                                                                                                                                                                           |

|-----------------------------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sFrontEndConfiguration<br>Done    | In        | SocketClk40     | Asserts high and stays high<br>when the power-on<br>self-configuration (POSC) state<br>machine is finished with<br>configuration.                                                     |

|                                   |           |                 | After the <b>aResetSl</b> signal<br>transitions from high to low,<br>indicating that the CLIP logic<br>should come out of reset, a<br>POSC reconfiguration occurs<br>unconditionally. |

|                                   |           |                 | The required clocking signals<br>are not valid until after this<br>signal asserts high.                                                                                               |

| sFrontEndConfiguration<br>Prepare | In        | SocketClk40     | Reserved for future use.<br>NI recommends assigning<br>this signal to <b>sFrontEnd</b><br><b>ConfigurationReady</b> .                                                                 |

| sFrontEndConfiguration<br>Ready   | Out       | SocketClk40     | Reserved for future use.<br>NI recommends assigning<br><b>sFrontEndConfiguration</b><br><b>Prepare</b> to this signal.                                                                |

#### Table 3-4. PXIe-6591R CLIP Signals (Continued)

| Port               | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                               |

|--------------------|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| aResetSl           | In        | Async           | This signal is not required.                                                                                                                                                                                                                                                                                                              |

|                    |           |                 | This signal is an asynchronous<br>reset signal from the LabVIEW<br>FPGA environment. If you<br>create an input signal to your<br>CLIP and assign it as <b>Reset</b> in<br>the CLIP wizard, that signal is<br>driven as an asynchronous reset<br>signal. Reset all CLIP state<br>machines and logic whenever<br>this signal is logic high. |

|                    |           |                 | This signal is driven high when<br>you call the LabVIEW FPGA<br><b>Reset</b> invoke method. Call <b>Run</b><br>on the FPGA VI to deassert this<br>signal.                                                                                                                                                                                 |

|                    |           |                 | Do not use CLIP inputs from the LabVIEW FPGA VI in the CLIP until <b>aResetSI</b> is deasserted.                                                                                                                                                                                                                                          |

| Port<01>_RX_p(3:0) | In (pad)  | N/A             | Dedicated MGT receive signals                                                                                                                                                                                                                                                                                                             |

| Port<01>_RX_n(3:0) | In (pad)  | N/A             | for Port <01>.                                                                                                                                                                                                                                                                                                                            |

| Port<01>_TX_p(3:0) | Out (pad) | N/A             | Dedicated MGT transmit signals                                                                                                                                                                                                                                                                                                            |

| Port<01>_TX_n(3:0) | Out (pad) | N/A             | for Port <01>.                                                                                                                                                                                                                                                                                                                            |

| Port<01>_SCL       | In/Out    | Async           | Bidirectional serial clock signal<br>for the two-wire communication<br>interface on the Port <01><br>connector.                                                                                                                                                                                                                           |

|                    |           |                 | Valid values: 0 and Z (open drain).                                                                                                                                                                                                                                                                                                       |

|                    |           |                 | This signal is also called MODDEF1.                                                                                                                                                                                                                                                                                                       |

|                    |           |                 | This signal has a 5 k $\Omega$ pull up to +3.3V.                                                                                                                                                                                                                                                                                          |

Table 3-4. PXIe-6591R CLIP Signals (Continued)

| Port                          | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                             |

|-------------------------------|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port<01>_SDA                  | In/Out    | Async           | Bidirectional serial data signal<br>for the two-wire communication<br>interface on the Port <01><br>connector.                                                                                                                                                          |

|                               |           |                 | Valid values: 0 and Z (open drain).                                                                                                                                                                                                                                     |

|                               |           |                 | This signal is also called MODDEF2.                                                                                                                                                                                                                                     |

|                               |           |                 | This signal has a 5 k $\Omega$ pull up to +3.3V.                                                                                                                                                                                                                        |

| Port<01>_GPIO_In              | In        | Async           | Active low presence detect<br>signal from pin B2 on the cable<br>connector. You must tie<br><b>GPIO_OutEnable_n</b> to "1" in<br>order to allow this functionality.<br>This input is driven low by the<br>high-speed connector while it is<br>inserted into the module. |

| Port<01>_GPIO_Out             | Out       | Async           | This signal is unused.                                                                                                                                                                                                                                                  |

| Port<01>_GPIO_<br>OutEnable_n | Out       | Async           | You must tie this signal to "1" to<br>disable output and allow the B2<br>pin to function as a presence<br>detect signal.                                                                                                                                                |

| sPort<01>_<br>EnablePower     | Out       | SocketClk40     | Enables or disables the power<br>supply to the cable on<br>Port <01>.                                                                                                                                                                                                   |

|                               |           |                 | This signal is active high.                                                                                                                                                                                                                                             |

| sPort<01>_Power<br>Good       | In        | SocketClk40     | Indicates that the power supply<br>to the cable for Port <01> is<br>enabled.                                                                                                                                                                                            |

|                               |           |                 | This signal may deassert if an over-power condition is detected.                                                                                                                                                                                                        |

Table 3-4.

PXIe-6591R CLIP Signals (Continued)

| Port                           | Direction | Clock<br>Domain | Description                                                                                                                                                                            |

|--------------------------------|-----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDC_GPIO_In(19:0)              | In        | Async           | These signals are GPIO inputs<br>within the DDC VHDCI<br>connector.                                                                                                                    |

|                                |           |                 | These signals, along with<br>DDC_GPIO_Out(19:0) and<br>DDC_GPIO_OutEnable_<br>n(19:0), allow control and<br>monitoring of the DIO(19:0)<br>connections on the DDC_<br>VHDCI connector. |

| DDC_GPIO_Out(19:0)             | Out       | Async           | These signals are GPIO outputs<br>within the DDC VHDCI<br>connector.                                                                                                                   |

|                                |           |                 | These signals, along with<br>DDC_GPIO_In(19:0) and<br>DDC_GPIO_OutEnable_<br>n(19:0), allow control and<br>monitoring of the DIO(19:0)<br>connections on the DDC_<br>VHDCI connector.  |

| DDC_GPIO_OutEnable_<br>n(19:0) | Out       | Async           | These signals enable GPIO_Out within the DDC VHDCI connector.                                                                                                                          |

|                                |           |                 | Drive these signals low to enable output.                                                                                                                                              |

|                                |           |                 | These signals, along with <b>DDC_GPIO_In(19:0)</b> and <b>DDC_GPIO_Out(19:0)</b> , allow control and monitoring of the DIO(19:0) connections on the DDC_VHDCI connector.               |

Table 3-4. PXIe-6591R CLIP Signals (Continued)

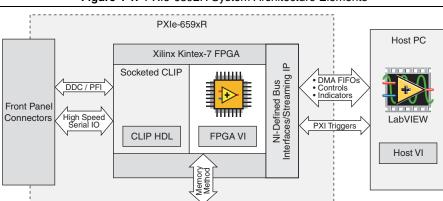

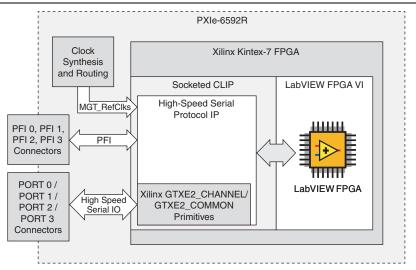

## PXIe-6592R Hardware Architecture

The following chapter contains information about the PXIe-6592R clocking architecture.

The PXIe-6592R is a high-speed serial interfacing module. The PXIe-6592R hardware architecture allows you to fully customize your serial digital protocol application. The high-speed serial interface uses Xilinx GTX transceiver technology; you can reuse existing protocol IP that works with Xilinx GTX transceivers, or you can develop your own protocol IP. If you develop your own protocol IP, the IP must be developed for a Xilinx Kintex-7 GTX transceiver.

Note The PXIe-6592R hardware does not require calibration.

PXIe-6592R-based projects consist of the following key components:

- PXIe-6592R front panel connectors for data, clocking, and triggering external to the module

- Socketed CLIP for HDL IP and interface definition from the FPGA VI to the PXIe-6592R front panel

- Xilinx Kintex-7 FPGA

- Dynamic random access memory (DRAM)

- NI-defined bus interface from the FPGA to the host PC

The following figure illustrates the key components of the PXIe-6592R architecture.

Figure 4-1. PXIe-6592R System Architecture Elements

## PXIe-6592R Module Overview

The PXIe-6592R modules include the following key features. Refer to the *PXIe-6592R Specifications* for more details.

DRAM

| Line rate                       | 500 Mb/s to 8 Gb/s and 9.8 Gb/s to 10.3125 Gb/s serial                                                                                                             |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Multi-gigabit transceiver lanes | 4 (1 per port)                                                                                                                                                     |  |

| Front Panel Connectors          | • Four SFP+ connectors (Port 0, Port 1, Port 2, and Port 3) for high-speed serial                                                                                  |  |

|                                 | <ul> <li>Four SMB connectors (PFI 0/CLK IN/OUT,<br/>PFI 1/CLK OUT, PFI 2/CLK OUT, and PFI 3/CLK<br/>OUT) for external triggering and clock input/output</li> </ul> |  |

| FPGA                            | Kintex-7 410T FFG900 package                                                                                                                                       |  |

| FPGA speed grade                | -2 (XC7K410T-2FFG900)                                                                                                                                              |  |

| DRAM                            | <ul> <li>2 GB onboard DRAM</li> <li>166 MHz clock frequency</li> <li>Bit-width: 512-bit</li> </ul>                                                                 |  |

| Backplane connection            | Gen 2x8 PXI Express, PCIe 2.0 compliant                                                                                                                            |  |

| Table 4-1. | PXIe-6592R Key | Features |

|------------|----------------|----------|

|------------|----------------|----------|

#### **Clocking Architecture**

The PXIe-6592R modules include dedicated clocking hardware to provide a flexible clocking solution for generating the high-speed serial transceiver reference clocks (MGT\_RefClk). Use the **Clocking and IO** properties page in the LabVIEW project to configure the clock settings for your module.

| Clock Name  | Frequency<br>Range | Available Sources                      |

|-------------|--------------------|----------------------------------------|

| MGT_RefClk0 | 60 MHz to          | Backplane: PXIe_Clk100 and PXIe_DStarA |

| MGT_RefClk1 | 700 MHz            | Front panel: CLK IN/OUT                |

| Table 4-2. PXIe-6592R Reference Clocks |

|----------------------------------------|

|----------------------------------------|

Refer to the *Configuring the High-Speed Serial Device LabVIEW FPGA Targets* section of Chapter 8, *Developing Applications for the High-Speed Serial Device*, for more detailed information about configuring clocking in your LabVIEW project.

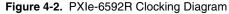

#### PXIe-6592R Clocking

The PXIe-6592R clocking architecture includes the following MGT Reference Clocks:

- MGT\_RefClk0

- MGT\_RefClk1

- MGT\_RefClk2

MGT\_RefClk0 and MGT\_RefClk1 are separate clocks, but are derived though simple integer division of a common, higher frequency PLL clock. MGT\_RefClk2 is an independent, free-running 156.25 MHz clock. Refer to the following table for information about the clocks' supported frequency ranges and available sources.

| Clock Name  | Frequency Range   | Available Sources                                                           |

|-------------|-------------------|-----------------------------------------------------------------------------|

| MGT_RefClk0 | 60 MHz to 670 MHz | Backplane: PXIe_Clk100 and                                                  |

| MGT_RefClk1 |                   | PXIe_DStarA<br>Front panel: PFI 0/CLK IN/OUT<br>Other: 10 MHz Onboard Clock |

| MGT_RefClk2 | 156.25 MHz        | _                                                                           |

Table 4-3. PXIe-6592R Reference Clocks

| Clock Name  | Frequency<br>Range | Available Sources                      |

|-------------|--------------------|----------------------------------------|

| MGT_RefClk0 | 60 MHz to          | Backplane: PXIe_Clk100 and PXIe_DStarA |

| MGT_RefClk1 | 700 MHz            | Front panel: CLK IN/OUT                |

| Table 4-4. PXIe-6592R Reference Clocks | Table 4-4. | PXIe-6592R Reference Clocks |

|----------------------------------------|------------|-----------------------------|

|----------------------------------------|------------|-----------------------------|

Refer to the *Configuring the High-Speed Serial Device LabVIEW FPGA Targets* section of Chapter 8, *Developing Applications for the High-Speed Serial Device*, for more information about how to configure Reference Clocks for your device.

You can also configure any of the four front panel PFI 0, PFI 1, PFI 2, or PFI 3 connectors to export a clock from the module.

**Note** If you configure the front panel PFI connectors to export a clock from the module, all of the PFI connectors must be the same frequency.

The following figure illustrates the clocking circuitry on the PXIe-6592R.

# 5

# Connecting and Interfacing with the PXIe-6592R

This chapter contains information about the PXIe-6592R module and its functionality, including front panel diagrams, connectors, and pinouts.

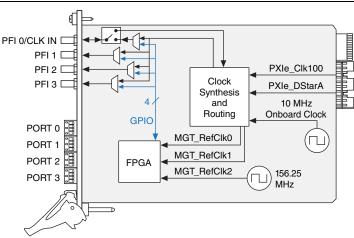

## Front Panel

The following figure shows the pinouts for the PXIe-6592R front panel connectors.

Figure 5-1. PXIe-6592R Front Panel Connectors and Pinout

Refer to the following table for a list of the PXIe-6592R front panel connectors and their descriptions.

| Connector        | Туре | Description                            |

|------------------|------|----------------------------------------|

| PFI 0/CLK IN/OUT | SMB  | Reference Clock input, exported        |

| PFI 1/CLK OUT    |      | clock output, and general-purpose I/O. |

| PFI 2/CLK OUT    |      |                                        |

| PFI 3/CLK OUT    |      |                                        |

| Port 0           | SFP+ | High-speed serial interfacing ports    |

| Port 1           |      |                                        |

| Port 2           |      |                                        |

| Port 3           |      |                                        |

Table 5-1. PXIe-6592R Front Panel Connectors

# **Recommended Mating Cables and Connectors**