# SC Express

NI PXIe-4302/4303 User Manual

32 Ch, 24-bit, 5 kS/s or 51.2 kS/s Simultaneous Filtered Data Acquisition Module

## Worldwide Technical Support and Product Information ni.com

#### Worldwide Offices

Visit ni.com/niglobal to access the branch office websites, which provide up-to-date contact information, support phone numbers, email addresses, and current events.

#### National Instruments Corporate Headquarters

11500 North Mopac Expressway Austin, Texas 78759-3504 USA

Tel: 866 ASK MYNI (275 6964)

For further support information, refer to the *NI Services* appendix. To comment on National Instruments documentation, refer to the National Instruments website at ni.com/info and enter the Info Code feedback.

© 2015 National Instruments. All rights reserved.

## Legal Information

#### Limited Warranty

This document is provided 'as is' and is subject to being changed, without notice, in future editions. For the latest version, refer to ni.com/manuals. NI reviews this document carefully for technical accuracy; however, NI MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMATION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS.

NI warrants that its hardware products will be free of defects in materials and workmanship that cause the product to fail to substantially conform to the applicable NI published specifications for one (1) year from the date of invoice.

For a period of ninety (90) days from the date of invoice, NI warrants that (i) its software products will perform substantially in accordance with the applicable documentation provided with the software and (ii) the software media will be free from defects in materials and workmanship.

If NI receives notice of a defect or non-conformance during the applicable warranty period, NI will, in its discretion: (i) repair or replace the affected product, or (ii) refund the fees paid for the affected product. Repaired or replaced Hardware will be warranted for the remainder of the original warranty period or ninety (90) days, whichever is longer. If NI elects to repair or replace the product, NI may use new or refurbished parts or products that are equivalent to new in performance and reliability and are at least functionally equivalent to the original part or product.

You must obtain an RMA number from NI before returning any product to NI. NI reserves the right to charge a fee for examining and testing Hardware not covered by the Limited Warranty.

This Limited Warranty does not apply if the defect of the product resulted from improper or inadequate maintenance, installation, repair, or calibration (performed by a party other than NI); unauthorized modification; improper environment; use of an improper hardware or software key; improper use or operation outside of the specification for the product; improper voltages; accident, abuse, or neglect; or a hazard such as lightning, flood, or other act of nature.

THE REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND THE CUSTOMER'S SOLE REMEDIES, AND SHALL APPLY EVEN IF SUCH REMEDIES FAIL OF THEIR ESSENTIAL PURPOSE.

EXCEPT AS EXPRESSLY SET FORTH HEREIN, PRODUCTS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND AND NI DISCLAIMS ALL WARRANTIES, EXPRESSED OR IMPLIED, WITH RESPECT TO THE PRODUCTS, INCLUDING ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE OR NON-INFRINGEMENT, AND ANY WARRANTIES THAT MAY ARISE FROM USAGE OF TRADE OR COURSE OF DEALING, NI DOES NOT WARRANT, GUARANTEE, OR MAKE ANY REPRESENTATIONS REGARDING THE USE OF OR THE RESULTS OF THE USE OF THE PRODUCTS IN TERMS OF CORRECTNESS, ACCURACY, RELIABILITY, OR OTHERWISE, NI DOES NOT WARRANT THAT THE OPERATION OF THE PRODUCTS WILL BE UNINTERRUPTED OR ERROR FREE.

In the event that you and NI have a separate signed written agreement with warranty terms covering the products, then the warranty terms in the separate agreement shall control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

National Instruments respects the intellectual property of others, and we ask our users to do the same. NI software is protected by copyright and other intellectual property laws. Where NI software may be used to reproduce software or other materials belonging to others, you may use NI software only to reproduce materials that you may reproduce in accordance with the terms of any applicable license or other legal restriction.

#### End-User License Agreements and Third-Party Legal Notices

You can find end-user license agreements (EULAs) and third-party legal notices in the following locations:

- Notices are located in the <National Instruments>\\_Legal Information and <National Instruments> directories.

- EULAs are located in the <National Instruments>\Shared\MDF\Legal\license directory.

- Review <National Instruments>\\_Legal Information.txt for information on including legal information in installers built with NI products.

#### U.S. Government Restricted Rights

If you are an agency, department, or other entity of the United States Government ("Government"), the use, duplication, reproduction, release, modification, disclosure or transfer of the technical data included in this manual is governed by the Restricted Rights provisions under Federal Acquisition Regulation 52.227-14 for civilian agencies and Defense Federal Acquisition Regulation Supplement Section 252.227-7014 and 252.227-7015 for military agencies.

#### Trademarks

Refer to the NI Trademarks and Logo Guidelines at ni.com/trademarks for more information on National Instruments trademarks.

ARM, Keil, and µVision are trademarks or registered of ARM Ltd or its subsidiaries.

LEGO, the LEGO logo, WEDO, and MINDSTORMS are trademarks of the LEGO Group.

TETRIX by Pitsco is a trademark of Pitsco, Inc.

FIELDBUS FOUNDATION™ and FOUNDATION™ are trademarks of the Fieldbus Foundation.

EtherCAT® is a registered trademark of and licensed by Beckhoff Automation GmbH.

CANopen® is a registered Community Trademark of CAN in Automation e.V.

DeviceNet<sup>™</sup> and EtherNet/IP<sup>™</sup> are trademarks of ODVA.

Go!, SensorDAQ, and Vernier are registered trademarks of Vernier Software & Technology. Vernier Software & Technology and vernier.com are trademarks or trade dress.

Xilinx is the registered trademark of Xilinx, Inc.

Taptite and Trilobular are registered trademarks of Research Engineering & Manufacturing Inc.

FireWire® is the registered trademark of Apple Inc.

Linux® is the registered trademark of Linus Torvalds in the U.S. and other countries.

Handle Graphics<sup>®</sup>, MATLAB<sup>®</sup>, Real-Time Workshop<sup>®</sup>, Simulink<sup>®</sup>, Stateflow<sup>®</sup>, and xPC TargetBox<sup>®</sup> are registered trademarks, and TargetBox<sup>™</sup> and Target Language Compiler<sup>™</sup> are trademarks of The MathWorks, Inc.

Tektronix®, Tek, and Tektronix, Enabling Technology are registered trademarks of Tektronix, Inc.

The Bluetooth® word mark is a registered trademark owned by the Bluetooth SIG, Inc.

The ExpressCard™ word mark and logos are owned by PCMCIA and any use of such marks by National Instruments is under license

The mark LabWindows is used under a license from Microsoft Corporation. Windows is a registered trademark of Microsoft Corporation in the United States and other countries.

Other product and company names mentioned herein are trademarks or trade names of their respective companies.

Members of the National Instruments Alliance Partner Program are business entities independent from National Instruments and have no agency, partnership, or joint-venture relationship with National Instruments.

#### Patents

For patents covering National Instruments products/technology, refer to the appropriate location: **Help»Patents** in your software, the patents.txt file on your media, or the *National Instruments Patent Notice* at ni.com/patents.

#### **Export Compliance Information**

Refer to the Export Compliance Information at ni.com/legal/export-compliance for the National Instruments global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

YOU ARE ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY AND RELIABILITY OF THE PRODUCTS WHENEVER THE PRODUCTS ARE INCORPORATED IN YOUR SYSTEM OR APPLICATION, INCLUDING THE APPROPRIATE DESIGN, PROCESS, AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

PRODUCTS ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING IN THE OPERATION OF NUCLEAR FACILITIES; AIRCRAFT NAVIGATION; AIR TRAFFIC CONTROL SYSTEMS; LIFE SAVING OR LIFE SUSTAINING SYSTEMS OR SUCH OTHER MEDICAL DEVICES; OR ANY OTHER APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, PRUDENT STEPS MUST BE TAKEN TO PROTECT AGAINST FAILURES, INCLUDING PROVIDING BACK-UP AND SHUT-DOWN MECHANISMS. NI EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES.

## Contents

| Chapter 1                                           |      |

|-----------------------------------------------------|------|

| Getting Started                                     |      |

| Installation                                        | 1-1  |

| Module Specifications                               |      |

| Module Accessories                                  |      |

|                                                     |      |

| Chapter 2                                           |      |

| Using the Module                                    |      |

| Connecting Signals                                  | 2-1  |

| Connecting Voltage Signals                          |      |

| Connecting Floating Signal Sources                  |      |

| Connecting Ground-Referenced Voltage Signal Sources |      |

| Connecting Thermocouple Signals                     |      |

| Cold-Junction Compensation                          |      |

| Connecting Current Signals                          |      |

| Module Pinout                                       |      |

| I/O Connector Signal Descriptions                   |      |

| NI PXIe-4302/4303 Block Diagram                     |      |

| Signal Acquisition Considerations                   |      |

| Nyquist Frequency and Nyquist Bandwidth             |      |

| ADC                                                 |      |

| Operation Modes                                     |      |

| Buffered Mode Acquisitions                          |      |

| Anti-Alias Filters                                  |      |

| Optional Buffered Mode IIR Filtering                |      |

| Hardware-Timed Single Point Acquisitions            |      |

| Hardware-Timed Single Point Acquisition Model       |      |

| Maximum HWTSP Rate Analysis                         | 2-13 |

| 2 kHz Control Loop Rate Calculation Example         | 2-14 |

| Timing and Triggering                               | 2-15 |

| Sample Clock Timebase                               | 2-15 |

| External Clock                                      | 2-16 |

| Digital Triggering                                  | 2-16 |

| Analog Triggering                                   | 2-16 |

| Triggering and Filter Delay                         | 2-17 |

| Synchronization                                     |      |

| Reference Clock Synchronization                     | 2-17 |

#### Contents

| Timing Engine  | es and DSP Streams                                             | 2-19 |

|----------------|----------------------------------------------------------------|------|

| Timing E       | Engines                                                        | 2-19 |

| DSP Stre       | ams                                                            | 2-19 |

| AI (           | Channels and DSP Streams                                       | 2-19 |

| Exa            | mples of Limitations                                           | 2-19 |

| Accessor       | y Auto-Detection                                               | 2-20 |

| Chapter 3      | }                                                              |      |

| •              | ss Considerations                                              |      |

| •              | lock and Trigger Signals                                       | 3-1  |

|                | .K100                                                          |      |

| _              | NC100                                                          |      |

| PXI_CLI        | K10                                                            | 3-1  |

| PXI Trig       | gers                                                           | 3-1  |

| PXI_STA        | AR Trigger                                                     | 3-2  |

| PXIe_DS        | STAR <ac></ac>                                                 | 3-2  |

| Appendix       | Α                                                              |      |

| NI Service     |                                                                |      |

|                | Resources                                                      | Λ_1  |

| Services and r | cesources                                                      | A-1  |

| Figures        |                                                                |      |

| Figure 2-1.    | Connecting Floating Signal Source without Bias Resistors       |      |

| Figure 2-2.    | Connecting Floating Signal Source with Single Bias Resistor    |      |

| Figure 2-3.    | Connecting Floating Signal Source with Balanced Bias Resistors |      |

| Figure 2-4.    | Connecting AC Coupled Floating Sources with Low Impedance      | 2-3  |

| Figure 2-5.    | Connecting AC Coupled Floating Sources                         |      |

|                | with Balanced Bias Resistors                                   |      |

| Figure 2-6.    | Connecting Ground-Referenced Signal Sources                    |      |

| Figure 2-7.    | Connecting a Loop-Powered Current Transducer                   |      |

| Figure 2-8.    | Connecting a Three-Wire Current Transducer                     |      |

| Figure 2-9.    | NI PXIe-4302/4303 Block Diagram                                |      |

| Figure 2-10.   | HWTSP Data Path Model                                          |      |

| Figure 2-11.   | Transfer Time and Application Time Relationship                |      |

| Figure 2-12.   | Typical Control System                                         |      |

| Figure 2-13.   | Input and Output of a Control System with Bandwidth ≥2 kHz     | 2-15 |

| Tables         |                                                                |      |

| Table 2-1.     | Front Connector Signal Pin Assignments                         | 2-8  |

| Table 2-2.     | I/O Connector Signal Descriptions                              |      |

| Table 3-1.     | PXIe_DSTAR Line Descriptions                                   | 3-2  |

## **Getting Started**

The NI PXIe-4302/4303 provides 32 simultaneously sampled filtered analog input channels. The NI PXIe-4302 can operate at sample rates up to 5 kS/s/ch and the NI PXIe-4303 can operate at sample rates up to 51.2 kS/s/ch. These modules can measure an analog voltage up to 10 V when using the TB-4302 and can measure 20 mA current signals when using the TB-4302C. Each channel has a 24-bit ADC and selectable digital filters to reject out-of-band noise.

#### Installation

Refer to the NI PXIe-4302/4303 and TB-4302/4302C User Guide and Terminal Block Specifications document for step-by-step software and hardware installation instructions.

**Note** For a complete list of terminal blocks supported by a specific release of NI-DAQmx, refer to the Readme, available on the version-specific download page or installation media.

## Module Specifications

Refer to the NI PXIe-4302/4303 Specifications document for module specifications.

## Module Accessories

Refer to ni.com/scexpress for information about and a complete listing of supported accessories

## Using the Module

This chapter describes how to connect voltage, thermocouple, and current input signals to the NI PXIe-4302/4303. It also provides the I/O connector signal pin assignments of the modules.

Driver support for the NI PXIe-4302/4303 was first available in NI-DAQmx 15.1. For the list of devices supported by a specific release, refer to the NI-DAOmx Readme, available on the version-specific download page or installation media.

## Connecting Signals

This section provides information regarding connecting voltage, thermocouple, and current signals.

**Caution** To ensure the specified EMC performance, operate this product only with shielded, twisted pair cables, and shielded accessories.

**Caution** To ensure the specified EMC performance, the length of all I/O cables must be no longer than 30 m (100 ft.).

## Connecting Voltage Signals

**Note** The TB-4302 terminal block is required when measuring voltage signals.

#### Connecting Floating Signal Sources

A floating signal source is not connected to the building ground system, but has an isolated ground-reference point through the ground of the device. Some examples of floating signal sources are outputs of transformers, thermocouples, battery-powered devices, optical isolators, and isolation amplifiers. An instrument or device that has an isolated output is a floating signal source

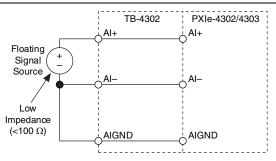

It is important to connect the negative lead of a floating source to AIGND (either directly or through a bias resistor). Otherwise, the source may float out of the maximum working voltage range and return erroneous data. The easiest way to reference the source to AIGND is to connect the positive side of the signal to AI+ and the negative side of the signal to both AIGND and AIwithout using resistors, as shown in Figure 2-1. This connection works well for DC-coupled sources with source impedances of less than 100  $\Omega$ .

Figure 2-1. Connecting Floating Signal Source without Bias Resistors

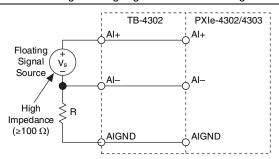

For source impedances  $\geq 100 \Omega$ , this connection leaves the differential signal path significantly off balance. Noise that couples onto the positive line does not couple onto the negative line because it is connected to ground. This noise appears as a differential mode signal instead of a common-mode signal, and therefore appears in your data. In this case, instead of directly connecting the negative line to AIGND, connect the negative line to AIGND through a resistor that is about 100 times the equivalent source impedance, as shown in Figure 2-2. The resistor puts the signal path nearly in balance, so that about the same amount of noise couples onto both connections, yielding better rejection of coupled noise. Since the bias resistor is between the negative line of the floating source and AIGND, this configuration does not load down the floating source output.

Figure 2-2. Connecting Floating Signal Source with Single Bias Resistor

R is about 100 times source impedance

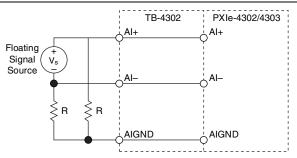

You can fully balance the signal path by connecting another resistor of the same value between the positive input and AIGND, as shown in Figure 2-3. This fully balanced configuration offers slightly better noise rejection, but has the disadvantage of loading the source down with the series combination of the two resistors. For example if the source impedance is  $2 \text{ k}\Omega$  and each of the two resistors is  $100 \text{ k}\Omega$ , the resistors load down the source with  $200 \text{ k}\Omega$  and produce a -1% gain error.

Figure 2-3. Connecting Floating Signal Source with Balanced Bias Resistors

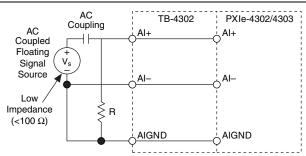

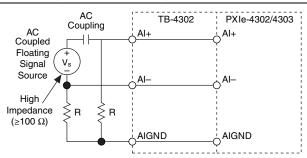

Both AI+ and AI- require a DC path to ground. If the source is AC coupled, a resistor is required between the positive input and AIGND, as shown in Figure 2-4. If the source has low-impedance, choose a bias resistor for the positive input that is large enough not to significantly load the source, but small enough not to produce significant input offset voltage as a result of input bias current. Connect the negative input directly to AIGND.

Figure 2-4. Connecting AC Coupled Floating Sources with Low Impedance

If the source has high output impedance and is AC coupled, balance the signal path as previously described with balanced bias resistors using the same value resistor on both the positive and negative inputs, as shown in Figure 2-5. Be aware that there is some gain error from loading down the source.

Figure 2-5. Connecting AC Coupled Floating Sources with Balanced Bias Resistors

#### Connecting Ground-Referenced Voltage Signal Sources

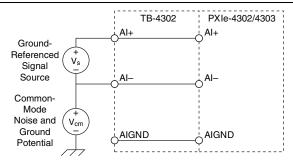

A ground-referenced signal source is a signal source connected to a common ground point with respect to the measurement device.

The difference in ground potential between two instruments connected to the same building power system is typically between 1 mV and 100 mV, but the difference can be much higher if power distribution circuits are improperly connected. If a grounded signal source is incorrectly measured, this difference can appear as measurement error. Follow the connection instructions for grounded signal sources to eliminate this ground potential difference from the measured signal.

Figure 2-6 shows how to connect a ground-referenced signal source to an NI PXIe-4302/4303 with a TB-4302.

Figure 2-6. Connecting Ground-Referenced Signal Sources

With this type of connection, the NI PXIe-4302/4303 rejects both the common-mode noise in the signal and the ground potential difference between the signal source and the device ground, shown as V<sub>cm</sub> in Figure 2-6.

## Connecting Thermocouple Signals

**Note** The TB-4302 terminal block is required when measuring a thermocouple signal.

For floating thermocouples, refer to the *Connecting Floating Signal Sources* section to bias the differential input of the NI PXIe-4302/4303.

For ground-reference thermocouples, refer to the Connecting Ground-Referenced Voltage Signal Sources section.

### Cold-Junction Compensation

Cold-junction compensation is the process of measuring the temperature of the screw terminal junction of the thermocouple and applying it to compensate the temperature measured by the thermocouple input channel. The TB-4302 has an onboard temperature sensor to measure the

terminal block temperature. The terminal block was carefully designed to minimize the temperature difference between the onboard temperature sensor and each screw terminal.

Refer to the NI PXIe-4302/4303 and TB-4302/4302C User Guide and Terminal Block Specifications for the CJC accuracy specifications.

### Connecting Current Signals

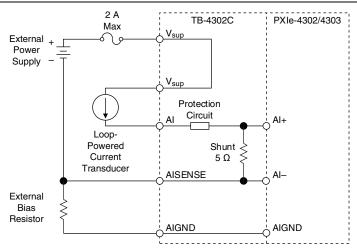

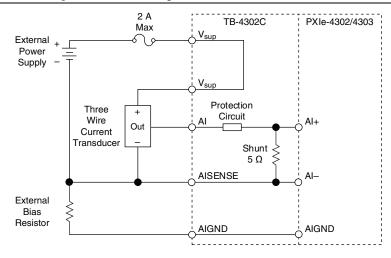

**Note** The TB-4302C terminal block is required when measuring a current signal.

Each channel has an AI terminal on the TB-4302C to which you can connect a current signal. A 5  $\Omega$  shunt resistor converts the current signal to a voltage measured by the NI PXIe-4302/4303.

The TB-4302C has 33 terminals for use with an external power supply. These terminals are labeled VSUP. All VSUP terminals are internally connected to each other by the terminal block. Using an external power supply with either 2 A current limiting or protected by a 2 A fuse. connect the positive supply lead to a VSUP terminal and the negative supply lead to an AISENSE terminal. The screw terminal pair with reference designator J19 on the terminal block is used specifically for this purpose. Additionally, there is a dedicated VSUP terminal to supply voltage to the transducer on each AI channel. You can only connect one external voltage supply to the TB-4302C.

The TB-4302C internally shorts all of the negative AI inputs of NI PXIe-4302/4303 to all of the AISENSE terminals on the TB-4302C terminal block. There are a total of 18 AISENSE terminals on the TB-4302C. One AISENSE terminal is for connecting the external power supply as described above. Another AISENSE terminal, J21, is paired with AIGND terminal to allow insertion of an external bias resistor between AISENSE and AIGND if a floating external power supply is implemented. All other AISENSE terminals are for transducer connections, one for every two channels. Refer to the NI PXIe-4302/4303 and TB-4302/4302C User Guide and Terminal Block Specifications for the maximum allowed voltage between AISENSE and AIGND

You can connect single-ended current signals to the TB-4302C, including loop-powered and three-wire current transducers. In both cases, connect the output of the current transducer to an AI terminal and the voltage supply of the current transducer to a VSUP terminal. For a three-wire transducer, also connect the negative lead of the current transducer to an AISENSE terminal. Refer to Figures 2-7 and 2-8 for illustrations of how to connect loop-powered and three-wire current transducers to the TB-4302C

Figure 2-7. Connecting a Loop-Powered Current Transducer

Figure 2-8. Connecting a Three-Wire Current Transducer

#### Module Pinout

Table 2-1 shows the pinout of the front connector of the NI PXIe-4302/4303. Refer to the I/O Connector Signal Descriptions section for definitions of each signal. Refer to the NI PXIe-4302/4303 and TB-4302/4302C User Guide and Terminal Block Specifications for signal locations on the terminal blocks.

Table 2-1. Front Connector Signal Pin Assignments

| Fre      | ont Cor<br>Diagr |           | tor    | Row<br>Number | Column A | Column B | Column C |

|----------|------------------|-----------|--------|---------------|----------|----------|----------|

|          |                  |           |        | 32            | AIGND    | AI0+     | AI1+     |

|          |                  |           |        | 31            | AI2+     | AI0-     | AI1-     |

|          |                  | lumr<br>B | n<br>C | 30            | AI2-     | AI3-     | AI3+     |

| 32       | 0                | 0         | 0      | 29            | AIGND    | AI4+     | AI5+     |

| 31       |                  | 0         | 0      | 28            | AI6+     | AI4-     | AI5-     |

| 30       | 0                | 0         | 0      | 27            | AI6-     | AI7-     | AI7+     |

| 29       |                  | 0         | 0      | 26            | AIGND    | AI8+     | AI9+     |

| 28<br>27 |                  | 0         | 0      | 25            | AI10+    | AI8-     | AI9-     |

| 26       |                  | 0         | 0      | 24            | AI10-    | AI11-    | AI11+    |

| 25       | 0                | 0         | 0      | 23            | AIGND    | AI12+    | AI13+    |

| 24       | 0                | 0         | 0      | 22            |          |          |          |

| 23       |                  | 0         | 0      |               | AI14+    | AI12-    | AI13-    |

| 22       |                  | 0         | 0      | 21            | AI14-    | AI15-    | AI15+    |

| 21       |                  | 0         | 0      | 20            | AIGND    | AI16+    | AI17+    |

| 20<br>19 |                  | 0         | 0      | 19            | AI18+    | AI16-    | AI17-    |

| 18       | 0                | 0         | 0      | 18            | AI18-    | AI19-    | AI19+    |

| 17       | 0                | 0         | 0      | 17            | AIGND    | AI20+    | AI21+    |

| 16       | 0                | 0         | 0      | 16            | AI22+    | AI20-    | AI21-    |

| 15       |                  | 0         | 0      | 15            | AI22-    | AI23-    | AI23+    |

| 14<br>13 |                  | 0         | 0      | 14            | AIGND    | AI24+    | AI25+    |

| 12       |                  | 0         | 0      | 13            | AI26+    | AI24-    | AI25-    |

| 11       | 0                | 0         | 0      | 12            | AI26-    | AI27-    | AI27+    |

| 10       |                  | 0         | 0      | 11            | AIGND    | AI28+    | AI29+    |

| 9<br>8   | 0                | 0         | 0      | 10            | AI30+    | AI28-    | AI29-    |

| 6<br>7   |                  | 0         | 0      | 9             | AI30-    | AI31-    | AI31+    |

| 6        |                  | 0         | 0      |               |          |          |          |

| 5        | 0                | 0         | 0      | 8             | AIGND    | NC       | NC       |

| 4        | 0                | 0         | 0      | 7             | NC       | NC       | NC       |

| 3        | 0                | 0         | 0      | 6             | NC       | NC       | NC       |

| 2        |                  | 0         | 0      | 5             | PFI0     | RSVD     | RSVD     |

| 1        | 0                | 0         | 0      | 4             | RSVD     | RSVD     | RSVD     |

|          |                  |           | 3      | RSVD          | RSVD     | RSVD     |          |

| PC       | VD is r          | -ecer     | ved    | 2             | RSVD     | DGND     | RSVD     |

|          | is no co         |           |        | 1             | RSVD     | RSVD     | RSVD     |

### I/O Connector Signal Descriptions

Table 2-2 describes the signals found on the I/O connector.

Table 2-2. I/O Connector Signal Descriptions

| Signal Names | Direction | Description                                                                                                              |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------|

| AIGND        | _         | Analog Input Ground                                                                                                      |

| AI<031>+     | Input     | Positive inputs of the differential analog input channels 0 to 31.                                                       |

| AI<031>-     | Input     | Negative inputs of the differential analog input channels 0 to 31.                                                       |

| RSVD         | _         | These pins are reserved for communication with the accessory.                                                            |

| DGND         | _         | Digital ground—this pin supplies the reference for module digital signals and is connected to the module digital ground. |

| PFI0         | Input     | 3.3 V digital signal for sending or receiving trigger and synchronization signals. This line is referenced to DGND.      |

## NI PXIe-4302/4303 Block Diagram

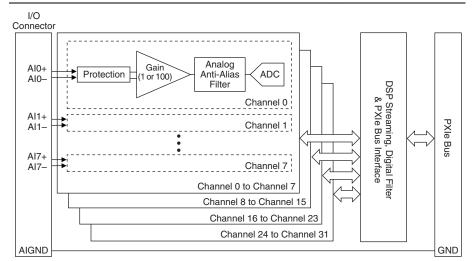

Figure 2-9 shows the block diagram of the NI PXIe-4302/4303. The analog signal conditioning for each channel consists of a software selectable gain block and an anti-alias filter. Each conditioned signal is then digitized by a 24-bit delta-sigma ADC to achieve simultaneous data acquisition. After the signal is digitized it passes through various DSP steps before being sent to software. Refer to the *Timing Engines and DSP Streams* section for more information about this digital block.

Figure 2-9. NI PXIe-4302/4303 Block Diagram

## Signal Acquisition Considerations

This section contains information about signal acquisition concepts, including operation modes, Delta-Sigma converters, Nyquist frequency and bandwidth, timing, triggering, and synchronization.

### Nyquist Frequency and Nyquist Bandwidth

Any sampling system, such as an ADC, is limited in the bandwidth of the signals it can measure. Specifically, a sampling rate of  $f_s$  can represent only signals with frequencies lower than  $f_s/2$ . This maximum frequency is known as the *Nyquist frequency*. The bandwidth from 0 Hz to the Nyquist frequency is the *Nyquist bandwidth*.

#### **ADC**

The NI PXIe-4302/4303 ADCs use a conversion method known as delta-sigma modulation. This approach involves oversampling the input signal and then decimating and filtering the resulting data to achieve the desired sample rate. The NI PXIe-4302 supports rates of 1 S/s to 5 kS/s. The NI PXIe-4303 supports rates of 1 S/s to 51.2 kS/s.

### **Operation Modes**

The NI PXIe-4302/4303 supports two modes of operation: Buffered Mode and Hardware-Timed Single Point Mode. In a Buffered Mode acquisition, oversampled data is decimated to your requested sample rate and digital anti-alias filters are applied to filter out frequency content above the Nyquist frequency. These digital anti-alias filters introduce group delay and for some applications this may be undesirable. For this reason, the NI PXIe-4302/4303 also supports

Hardware-Timed Single Point Mode. In Hardware-Timed Single Point Mode the oversampled data is filtered with a much looser filter to reduce the group delay.

### **Buffered Mode Acquisitions**

In buffered mode, the NI PXIe-4302/4303 uses a combination of analog and digital filtering to provide an accurate representation of in-band signals while rejecting out-of-band signals. These filters discriminate between signals based on the frequency range, or bandwidth, of the signal. The three important bands to consider are the passband, the stopband, and the alias-free bandwidth.

In buffered mode, the NI PXIe-4302/4303 accurately represents signals within the passband, as quantified primarily by passband flatness and phase nonlinearity. All signals that appear in the alias-free bandwidth are either unaliased signals or signals that have been filtered by at least the amount of the stopband rejection.

#### **Anti-Alias Filters**

A digitizer or ADC might sample signals containing frequency components above the Nyquist limit. The undesirable effect of the digitizer modulating out-of-band components into the Nyquist bandwidth is aliasing. The greatest danger of aliasing is that you cannot determine if aliasing occurred by looking at the ADC output. If an input signal contains several frequency components or harmonics, some of these components might be represented correctly while others contain aliased artifacts.

Lowpass filtering to eliminate components above the Nyquist frequency either before or during the digitization process can guarantee that the digitized data set is free of aliased components. In buffered mode, the NI PXIe-4302/4303 modules employ both digital and analog lowpass filters to achieve this protection.

In buffered mode, the NI PXIe-4302/4303 modules use an oversampled architecture and sharp digital filters<sup>1</sup> with cut-off frequencies that track the sampling rate. Therefore the filter automatically adjusts to follow the Nyquist frequency. Although the digital filter eliminates almost all out-of-band components, it is still susceptible to aliases from certain narrow frequency bands located at frequencies far above the sampling rate. These frequencies are referred to as the ADC alias holes.

To minimize the error from the ADC alias holes, the NI PXIe-4302/4303 modules feature a fixed-frequency analog filter. This analog filter removes high-frequency components in the analog signal path before they reach the ADC. This filtering addresses the possibility of high-frequency aliasing from the narrow bands that are not covered by the digital filter.

2-10 | ni.com

Looser filters with degraded alias-free bandwidth are used for sample rates < 25 Hz. This is done in order to reduce the large group delays associated with filtering at lower sample rates. Refer to the NI PXIe-4302/4303 Specifications document for performance at lower rates.</p>

#### **Passband**

The signals within the passband have frequency-dependent gain or attenuation. The small amount of variation in gain with respect to frequency is called the passband flatness. The digital anti-alias filters of the NI PXIe-4302/4303 adjust the frequency range of the passband to match the sample rate. Therefore, the amount of gain or attenuation at a given frequency depends on the sample rate.

#### Stopband

The digital anti-alias filter significantly attenuates all signals above the stopband frequency to prevent aliasing. Therefore, the stopband frequency scales precisely with the sample rate. The stopband rejection is the minimum amount of attenuation applied by the anti-alias filter to all signals with frequencies within the stopband.

#### Alias-Free Bandwidth

Any signal that appears in the alias-free bandwidth of the NI PXIe-4302/4303 is not an aliased artifact of signals at a higher frequency. The alias-free bandwidth is defined by the ability of the filter to reject frequencies above the stopband frequency, and it is equal to the sample rate minus the stopband frequency.

#### Filter Group Delay

The anti-alias digital filtering performed by the NI PXIe-4302/4303 produces a delay of many samples worth of time between when an event occurs on the input signal going into the NI PXIe-4302/4303 and when the data associated with that event is available at the output of the acquisition and filtering process. This delay is called the group delay.

In order to simplify the process of acquiring data from the NI PXIe-4302/4303 modules and correlating that data with data from other modules, the NI PXIe-4302/4303 compensates for this group delay in the following ways:

- The Sample Clock output from the NI PXIe-4302/4303 is generated at the point in time when the input signal is valid at the ADC input pins. When acquiring data, the NI PXIe-4302/4303 generates a Sample Clock, then waits for the data associated with that Sample Clock to be acquired, then returns that data. As a result, any other acquisitions timed with this Sample Clock line up with the data returned by the NI PXIe-4302/4303.

- Any triggers generated or received by the NI PXIe-4302/4303 are interpreted based on their relationship to the Sample Clock being generated. For example, a Start Trigger that starts an acquisition results in data from the next Sample Clock being returned as the first point in the acquisition. Refer to the *Triggering and Filter Delay* section for more details about how this affects analog trigger events.

On demand software sampling returns a single sample from an acquisition running at the maximum supported sample rate of the module. For any on-demand, software timed acquisition the NI PXIe-4302/4303 waits for the group delay to elapse before returning the sample. As a result, the data returned aligns closely in time with when the data was requested and is delayed by the sum of the analog input delay and digital filter delay.<sup>1</sup>

#### Optional Buffered Mode IIR Filtering

In addition to the sharp anti-alias filters used in buffered mode, the NI PXIe-4302/4303 also provides optional fourth order elliptical lowpass IIR filters that can be used in Buffered Mode. These lowpass filters have fixed cut-off frequencies that are not related to the sample rate and are intended to replicate placing an analog filter on the input. For example, if you want to filter out 60 Hz power line noise, you can select the digital 2 Hz lowpass filter and still use any desired sample rate.

The optional lowpass filter is in addition to the anti-alias filter. Therefore, the optional lowpass filter is only meaningful in the passband of the anti-alias filter. The anti-alias filter will still reject frequencies beyond the Nyquist frequency.

By default, the optional lowpass digital filter is not enabled. Each channel in a Buffered Mode task can independently be configured to use any of the available filters that the NI PXIe-4302/4303 supports. Refer to *Digital AI Filtering* in the *NI-DAQmx Help* for more information about how to configure the filter used. Refer to the *NI PXIe-4302/4303 Specifications* for more information about the cut-off frequencies supported and response characteristics of these filters.

#### Filter Settling Time

When a lowpass filter is first enabled, it takes time for the filter to settle to a correct value. Software automatically waits a fixed amount of time after enabling the filter and before starting a task to prevent showing invalid data. The amount of time software waits is dependent on the cut-off frequency of the filter selected. The lower the cut-off frequency, the longer software must wait for the filter to settle. Refer to the *NI PXIe-4302/4303 Specifications* for more information.

#### Filter Group Delay

Like all filters, the optional lowpass filter has group delay associated with it. Since the optional filters are IIR, the group delay is a function of both cut-off frequency and the frequency of the signal being attenuated. Since the group delay is not constant for all input frequencies, it cannot be automatically compensated for and will therefore appear as an additional delay on the input. Refer to the *NI PXIe-4302/4303 Specifications* for more information.

<sup>&</sup>lt;sup>1</sup> The maximum sample rate of the NI PXIe-4302/4303 is 51.2 kS/s. In addition to the fixed analog input delay, you must also account for the digital-filter group delay. For 51.2 kS/s, the digital filter group delay is  $1.79742 \text{ ms} + \frac{48.5 \text{ S}}{51.2 \text{ kS/s}} = 1.79837 \text{ ms}$ .

If a 10 V range is used, total delay is 1.79837 ms + 6.77  $\mu$ s = 1.80514 ms. Refer to the *NI PXIe-4302/4303 Specifications* for more information.

### Hardware-Timed Single Point Acquisitions

Hardware-Timed Single Point (HWTSP) is a hardware-timed acquisition mode in which a digital hardware signal (SampleClock) controls the rate of the acquisition. The SampleClock signal can be imported or internally generated on the NI PXIe-4302/4303 using the sample rate configured with a NI-DAQmx task.

During Buffered acquisitions, the device may wait to transfer data to the host machine to build larger bus transactions. This optimizes throughput. During HWTSP acquisitions, the device sends data to the host in response to every sample clock. This optimizes latency.

These features make HWTSP ideal for real-time control applications. HWTSP acquisitions, in conjunction with the wait for next sample clock function, provide more deterministic synchronization between the software layer and the hardware layer. Refer to the NI-DAQmx Hardware-Timed Single Point Lateness Checking document for more information. To access this document, go to ni.com/info and enter the Info Code daghwtsp.

#### Hardware-Timed Single Point Acquisition Model

The HWTSP data path is optimized for low-latency applications and is different than the data path used in buffered mode acquisitions.

When in HWTSP mode, the filtering and sampling systems can be modeled as being decoupled, which allows you to configure the filter and sampling rate independently.

Figure 2-10 shows the HWTSP data path model.

Figure 2-10. HWTSP Data Path Model

The ADC samples the input stream and returns it to the PXIe controller or computer based on the SampleClock signal.

### Maximum HWTSP Rate Analysis

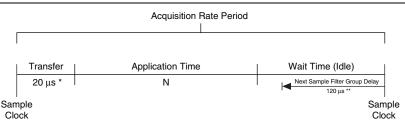

During HWTSP acquisitions the maximum achievable acquisition rate without missing a sample is affected by both the transfer and application time. Refer to Figure 2-11.

$$Rate_{MAX} = \frac{1}{TransferTime + ApplicationTime}$$

**Note** HWTSP acquisitions can detect if they cannot keep up with the acquisition rate. Refer to the Hardware-Timed Single Point Sample Mode topic in the NI-DAQmx *Help* for more information.

Figure 2-11. Transfer Time and Application Time Relationship

<sup>\*</sup>Transfer time may vary depending on system.

<sup>\*\*120</sup> μs is the approximate group delay of the 2 kHz filter for input frequencies < 1 kHz (passband of the filter).

**Note** For control applications, it is important to consider the group delay of the data being acquired and analyzed when calculating the control system bandwidth. Regardless of the sample rate, the bandwidth of the system is as follows:

$$bandwidth = \frac{1}{TransferTime + ApplicationTime + GroupDelay}$$

#### 2 kHz Control Loop Rate Calculation Example

Figure 2-12 represents a typical control system in which you have a process to control, a DAQ device to do the acquisitions and generate stimulus, and a PXIe controller or computer to do the data processing and determine the proper AO value and returning it to the process.

Figure 2-12. Typical Control System

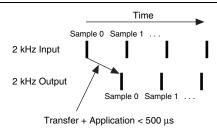

To successfully close a 2 kHz control loop, make sure that the time between the time the AI sample is acquired and the time the AO stimulus is generated is <500 µs. Refer to Figure 2-13.

Figure 2-13. Input and Output of a Control System with Bandwidth ≥2 kHz

To make sure that your application can run and control a process at 2 kHz, and that the first output is generated within the first sample period, make sure that the following conditions are satisfied:

500

$$\mu s \le Transfer\ Time + Application\ Time$$

(2-1)

where:

Transfer Time—the time it takes to transfer samples between the DAO device and the PXIe controller or computer.

Application Time—the time it takes for the PXIe controller or computer to analyze the acquired data and generate the AO stimulus.

Using Equation 2-1 and the Transfer Time from the sample system described in this section, you can determine that an application time of 480 µs is required to close a 2 kHz control loop.

Application Time

$$\leq 500~\mu s$$

- Transfer Time

Application Time  $\leq 500~\mu s$  -  $20~\mu s$

Application Time  $\leq 480~\mu s$

Any application taking more than 480 µs will fail to close the 2 kHz control loop.

When analyzing the bandwidth of the system, you must consider the group delay of all the components of the system. When using only the NI PXIe-4302/4303 internal 2 kHz filter, the bandwidth of the control loop is as follows:

$$ControlBandwidth = \frac{1}{TransferTime + ApplicationTime + FilterGroupDelay}$$

$$ControlBandwidth = \frac{1}{20\mu s + 480\mu s + 120\mu s}$$

**Note** You can increase the bandwidth of the system by either reducing the application time or by using another filter option with lower group delay.

## Timing and Triggering

This section contains information about the timing and triggering theory of operation.

#### Sample Clock Timebase

The ADCs require an oversample clock to drive the conversion. The oversample clock frequency is greater than the sample rate. On the NI PXIe-4302/4303 modules the oversample clock is produced from a 106.25 MHz reference clock. This 106.25 MHz reference clock can be phase locked with the PXIe backplane 100 MHz clock or be generated by an internal timebase

Using the Module

that runs freely. Multiple modules can be synchronized by selecting the PXIe backplane 100 MHz clock as the reference clock source for all the modules. Refer to the *Reference Clock Synchronization* section for more information.

#### External Clock

The NI PXIe-4302/4303 ADCs cannot be clocked from external sources such as encoders or tachometers. However, signal processing features in the Sound and Vibration Measurement Suite often provide an excellent alternative to external clocking in encoder and tachometer applications. Visit ni.com/soundandvibration for more information about the Sound and Vibration Measurement Suite.

#### Digital Triggering

You can configure the NI PXIe-4302/4303 modules to start an acquisition in response to a digital trigger signal from one of the PXI Express backplane trigger lines or the PFI from the front connector. The trigger circuit can respond either to a rising or a falling edge.

#### **Analog Triggering**

Analog triggering allows you to trigger your application based on an input signal and trigger level you define. You can configure the analog trigger circuitry to monitor any input channel acquiring data. Choosing an input channel as the trigger channel does not change the input channel acquisition specifications.

The analog trigger signal can be used as a reference trigger only. In a reference-triggered acquisition, you configure the module to acquire a certain number of pre-trigger samples and a certain number of post-trigger samples. Reference-triggered acquisitions can therefore only be configured as finite tasks. The analog trigger on the NI PXIe-4302/4303 cannot be used as a start trigger. This restriction is a result of the way the module compensates for the filter group delay.

When using an analog reference trigger, the module first waits for the specified number of pre-trigger samples to be acquired. Once enough pre-trigger samples are acquired, the reference trigger will occur the next time the analog trigger condition is met. You also can route the resulting reference trigger event to supported digital terminals. Refer to the device panels in MAX for additional information.

During repetitive triggering on a waveform, you might observe jitter because of the uncertainty of where a trigger level falls compared to the actual digitized data. Although this trigger jitter is never greater than one sample period, it might be significant when the sample rate is only twice the bandwidth of interest. This jitter usually has no effect on data processing, and you can decrease this jitter by sampling at a higher rate.

You can use several analog triggering modes with the NI PXIe-4302/4303 modules, for instance analog edge, analog edge with hysteresis, and window triggering.

#### Triggering and Filter Delay

The NI PXIe-4302/4303 interprets triggers based on where they occur in time. The hardware automatically compensates for its group delay such that data from this module will line up closely in time with the occurrence of the trigger event. However, the group delay affects how long it takes to receive data when starting an acquisition. Since linear phase FIR filters are used in the digital filtering, it is necessary to wait for the filter group delay to elapse after sending a sync pulse before the start trigger can be correctly handled in time. Step 6 in the Reference Clock Synchronization section allows NI-DAOmx to handle this delay automatically. After the digital start trigger, you cannot read data for the first sample in software until the digital filter group delay has elapsed. Therefore, it takes a total of twice the digital filter group delay to start an acquisition. You can insert additional time between when the sync pulse occurs and when the start trigger occurs. This will not affect the time it takes before samples are available after the start trigger, which is always the group delay time. Group delay time increases as sample rates decrease. Refer to the NI PXIe-4302/4303 Specifications document for details regarding the group delay at different sample rates.

### Synchronization

Some applications require tight synchronization between input and output operations on multiple modules. Synchronization is important to minimize skew between channels and to eliminate clock drift between modules in long-duration operations. You can synchronize the analog input operations on two or more NI PXIe-4302/4303 modules to extend the channel count for your measurements. In addition, the NI PXIe-4302/4303 can synchronize with certain DSA modules, such as the NI PXIe-449x modules, using Reference Clock Synchronization.

#### Reference Clock Synchronization

With reference clock synchronization, master and slave modules generate their ADC oversample clock from the shared 100 MHz reference clock from the PXIe backplane (PXIe CLK100). The backplane supplies an identical copy of this clock to each peripheral slot. In addition, multiple chassis can be synchronized by using a timing and synchronization board to lock the 100 MHz clock across chassis.

When you acquire data from multiple modules within the same NI-DAQmx task, NI-DAQmx will automatically handle all of the Reference Clock Synchronization details required to synchronize the modules within the task. This is known as a Multi-Device Task.

To perform Reference Clock Synchronization when using multiple NI-DAQmx tasks that are acquiring at the same rate, complete the following steps to synchronize the hardware.

- Specify PXIe CLK100 as the reference clock source for all modules to force all the modules to lock to the reference clock on the PXIe chassis.

- 2. Choose an arbitrary NI PXIe-4302/4303 master module to issue a sync pulse on one of the PXIe Trigger lines. The sync pulse resets the ADCs and oversample clocks, phase aligning all the clocks in the system to within nanoseconds.

- Configure the rest of the modules in your system to receive their sync pulse from the sync pulse master module. This will ensure all ADCs are running in lockstep.

#### Chapter 2 Using the Module

- Choose one module to be the start trigger master. This does not have to be the same module 4 you chose in step 3.

- 5. Configure the rest of the modules in your system to receive their start trigger from the start trigger master module. This ensures that all modules will begin returning data on the same sample.

- 6. Set the synchronization type of the Start Trigger slaves at DAQmx Trigger»Advanced» **Synchronization**»**Synchronization Type** to Slave and that of the Master to Master.

- 7. Ouery DAOmx Timing»More»Synchronization Pulse»Synchronization Time on all modules being synchronized, choose the maximum value and set that as the DAQmx Timing»More»Synchronization Pulse»Minimum Delay To Start on the module from which the synchronization pulse originates.

- 8. Commit all of the sync pulse slave module tasks using the DAOmxTaskControl VI/Function. This sets them up to expect the sync pulse from the master.

- 9. Commit the sync pulse master module task using the DAOmxTaskControl VI/Function. This will issue the sync pulse.

- 10. Start all of the start trigger slave module tasks. This sets them up to expect the start trigger from the master.

- 11. Start the start trigger master module task. You can now acquire data.

**Tip** Consider using a Multi-Device task when synchronizing multiple devices at the same rate.

**Tip** You can find example VIs in the NI Example Finder. Select **Help**»Find **Examples** to launch the NI Example Finder.

Consider the following caveat to using Reference Clock synchronization:

The NI PXIe-4302/4303 automatically compensates for its filter group delay. However, some other device families do not compensate for their filter delay. In this case, manually compensate for group delay in the waveforms when you synchronize between device families if this level of synchronization is required for your application.

## Timing Engines and DSP Streams

This section gives an overview of the internal implementation of the NI PXIe-4302/4303 and the limitations that exist on how the NI PXIe-4302/4303 can be configured. The use of NI-DAQmx software allows you to easily configure the NI PXIe-4302/4303 without you needing in depth knowledge about the internal workings of hardware. However, there are limitations in the way in which the NI PXIe-4302/4303 can be configured and to understand them requires some explanation about what is happening in hardware.

### **Timing Engines**

When you create a task in software, that software task interacts with one or more timing engines in the NI PXIe-4302/4303. There are a total of four timing engines in hardware that can be operated simultaneously. Each of these timing engines can have individualized configuration settings for timing, triggering, and the sample mode. Depending on the sample mode selected, the timing engine will use either a buffered mode or hardware-timed single point DSP stream.

#### **DSP Streams**

The DSP streams in the NI PXIe-4302/4303 perform the digital signal processing on the acquired data before sending the data to software. There are two types of DSP streams: buffered mode streams and hardware-timed single point streams. The NI PXIe-4302/4303 has four streams for each of these types and each stream can handle up to 8 channels. Therefore, it is possible to use all 32 channels in either buffered mode or hardware-timed single point mode.

#### Al Channels and DSP Streams

While all 32 analog input channels are simultaneously digitized by their ADC, the controls of the ADCs are grouped into four banks of eight. The configuration of the ADCs is different for buffered mode and hardware-timed single point mode, and as a result, there are limitations on how channels can be used when both buffered and hardware-timed single point tasks operate simultaneously. Analog input channels in the following banks must all be configured for either buffered mode or hardware-timed single point mode: ai0:7, ai8:15, ai16:23, and ai24:31.

To allow greater flexibility in how the NI PXIe-4302/4303 can be configured, a cross-point switch exists between the ADCs and the DSP streams. This cross-point switch allows a single DSP stream to use any eight of the 32 analog input channels, as long as the ADC for the analog input channel selected is configured for the same mode as the DSP stream. Once an analog input channel is used in a task, it is not available for use in other tasks.

#### **Examples of Limitations**

The following configuration scenarios will cause errors:

A task is setup and started using ai0 in buffered mode. A second task is created with ai1 in hardware-timed single point mode. The second task will produce an error since the first task has already placed ai0:7 in buffered mode and therefore ai1 cannot be used in hardware-timed single point mode.

#### Chapter 2 Using the Module

- A task is set up and started using ai0 in buffered mode. A second task is created with ai0 also in buffered mode. The second task will produce an error since the first task is already using ai0.

- Four buffered mode tasks are setup and started, each with a single and different ai channel and operating at different sample rates. A fifth task is created. The fifth task will produce an error, regardless of how it is configured, since the first four tasks are using the four timing engines, one per task.

- A buffered mode task is setup and started using ai0:24. A second buffered mode task is created using ai25. The second task will produce an error since the first task has 25 total channels and therefore must use all four buffered mode streams; each stream can handle only eight channels. There is not an unused buffered mode stream available. If the second task was set for hardware-timed single point mode, an error would still be produced by the second task since ai24 in the first task has forced ai24:ai31 to all be buffered mode channels

### Accessory Auto-Detection

SC Express modules automatically detect compatible accessories or terminal blocks. The RSVD pins on the I/O connector provide power to the accessories as well as digital communication lines. This allows software to detect when accessories are inserted or removed. In addition, software can automatically identify the specific terminal block as well as access any calibration or scaling information associated with the terminal block.

MAX allows you to see which accessories are currently connected to your module. In MAX, expand Devices and Interfaces and locate your module. If a terminal block is connected to your module, it will be displayed beneath the module. Unsupported terminal blocks appear in MAX with an X next to them.

NI-DAQmx property nodes can be used to programmatically access information about connected accessories in your application. Refer to the NI-DAQmx Help for documentation about programmatically accessing accessory status.

## SC Express Considerations

This chapter details the clock and trigger functionality available through the PXI Express chassis

## SC Express Clock and Trigger Signals

#### PXIe\_CLK100

PXIe CLK100 is a common, low-skew 100 MHz reference clock used for synchronization of multiple modules in a PXI Express measurement or control system. The PXIe backplane is responsible for generating PXIe CLK100 independently to each peripheral slot in a PXI Express chassis. For more information, refer to the PXI Express Specification at www.pxisa.org.

#### PXIe SYNC100

PXIe SYNC100 is a common, low-skew 10 MHz reference clock with a 10% duty cycle for synchronization of multiple modules in a PXI Express measurement or control system. The PXI Express backplane is responsible for generating PXIe SYNC100 independently to each peripheral slot in a PXI Express chassis. PXIe SYNC100 allows modules using PXIe CLK100 as their reference to recreate the timing of the PXI CLK10 signal while taking advantage of the lower skew of PXIe CLK100. For more information, refer to the PXI Express Specification at www.pxisa.org.

#### PXI CLK10

PXI CLK10 is a common, low-skew 10 MHz reference clock for synchronization of multiple modules in a PXI measurement or control system. The PXI backplane is responsible for generating PXI CLK10 independently to each peripheral slot in a PXI chassis. In PXIe chassis, the PXI CLK10 signal is in phase with PXIe CLK100.

Note PXI CLK10 cannot be used as a reference clock for SC Express modules.

## **PXI** Triggers

A PXI/PXIe chassis provides eight bused trigger lines to each module in a system. Triggers may be passed from one module to another, allowing precisely timed responses to asynchronous external events that are being monitored or controlled. Triggers can be used to synchronize the operation of several different PXI peripheral modules.

In a PXI chassis with more than eight slots, the PXI trigger lines may be divided into multiple independent buses. Refer to the documentation for your chassis for details.

### PXI STAR Trigger

In a PXI Express system, the Star Trigger bus implements a dedicated trigger line between the system timing slot and the other peripheral slots. The Star Trigger can be used to synchronize multiple modules or to share a common trigger signal among modules.

A system timing controller can be installed in the system timing slot to provide trigger signals to other peripheral modules. Systems that do not require this functionality can install any standard peripheral module in this system timing slot.

An SC Express module receives the Star Trigger signal (PXI STAR) from a System timing controller. PXI STAR can be used as a trigger signal for input operations.

An SC Express module is not a System timing controller. An SC Express module can be used in the system timing slot of a PXI system, but the system will not be able to use the Star Trigger feature.

#### PXIe DSTAR<A..C>

PXI Express devices can provide high-quality and high-frequency point-to-point connections between each slot and a system timing slot. These connections come in the form of three low-voltage differential star triggers that route between a PXI Express system timing controller and a peripheral device. Using multiple connections simplifies the creation of applications because of the increased routing capabilities.

Table 3-1 describes the three differential star (DSTAR) lines and how they are used.

| Trigger Line | Purpose                                                                                                          |

|--------------|------------------------------------------------------------------------------------------------------------------|

| PXIe_DSTARA  | Distributes high-speed, high-quality clock signals from the system timing slot to the peripherals (input).       |

| PXIe_DSTARB  | Distributes high-speed, high-quality trigger signals from the system timing slot to the peripherals (input).     |

| PXIe_DSTARC  | Sends high-speed, high-quality trigger or clock signals from the peripherals to the system timing slot (output). |

Table 3-1. PXIe\_DSTAR Line Descriptions

The DSTAR lines are only available for PXI Express devices when used with a PXI Express system timing module. For more information, refer to the PXI Express Specification at www.pxisa.org.

## **NI Services**

National Instruments provides global services and support as part of our commitment to your success. Take advantage of product services in addition to training and certification programs that meet your needs during each phase of the application life cycle; from planning and development through deployment and ongoing maintenance.

To get started, register your product at ni.com/myproducts.

As a registered NI product user, you are entitled to the following benefits:

- Access to applicable product services.

- Easier product management with an online account.

- Receive critical part notifications, software updates, and service expirations.

Log in to your National Instruments ni. com User Profile to get personalized access to your services.

#### Services and Resources

- Maintenance and Hardware Services—NI helps you identify your systems' accuracy and reliability requirements and provides warranty, sparing, and calibration services to help you maintain accuracy and minimize downtime over the life of your system. Visit ni.com/ services for more information.

- Warranty and Repair—All NI hardware features a one-year standard warranty that is extendable up to five years. NI offers repair services performed in a timely manner by highly trained factory technicians using only original parts at a National Instruments service center.

- Calibration—Through regular calibration, you can quantify and improve the measurement performance of an instrument. NI provides state-of-the-art calibration services. If your product supports calibration, you can obtain the calibration certificate for your product at ni.com/calibration.

- **System Integration**—If you have time constraints, limited in-house technical resources, or other project challenges, National Instruments Alliance Partner members can help. To learn more, call your local NI office or visit ni.com/alliance.

- **Training and Certification**—The NI training and certification program is the most effective way to increase application development proficiency and productivity. Visit ni.com/training for more information.

#### Appendix A NI Services

- The Skills Guide assists you in identifying the proficiency requirements of your current application and gives you options for obtaining those skills consistent with your time and budget constraints and personal learning preferences. Visit ni.com/skills-quide to see these custom paths.

- NI offers courses in several languages and formats including instructor-led classes at facilities worldwide, courses on-site at your facility, and online courses to serve your individual needs

- Technical Support—Support at ni.com/support includes the following resources:

- Self-Help Technical Resources—Visit ni.com/support for software drivers and updates, a searchable KnowledgeBase, product manuals, step-by-step troubleshooting wizards, thousands of example programs, tutorials, application notes, instrument drivers, and so on. Registered users also receive access to the NI Discussion Forums at ni.com/forums. NI Applications Engineers make sure every question submitted online receives an answer.

- Software Support Service Membership—The Standard Service Program (SSP) is a renewable one-year subscription included with almost every NI software product, including NI Developer Suite. This program entitles members to direct access to NI Applications Engineers through phone and email for one-to-one technical support, as well as exclusive access to online training modules at ni.com/self-paced-training. NI also offers flexible extended contract options that guarantee your SSP benefits are available without interruption for as long as you need them. Visit ni.com/ssp for more information.

- **Declaration of Conformity (DoC)**—A DoC is our claim of compliance with the Council of the European Communities using the manufacturer's declaration of conformity. This system affords the user protection for electromagnetic compatibility (EMC) and product safety. You can obtain the DoC for your product by visiting ni.com/certification.

For information about other technical support options in your area, visit ni.com/services, or contact your local office at ni.com/contact.

You also can visit the Worldwide Offices section of ni.com/niglobal to access the branch office websites, which provide up-to-date contact information, support phone numbers, email addresses, and current events.