# M3000

# MOTOR AND MOTION CONTROLLER INSTRUCTION SET

| M3000 Instruct | tion Set Manual | Change Log      |

|----------------|-----------------|-----------------|

| Date           | Revision        | Changes         |

| 08/07/2007     | R080707         | Initial Release |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                |                 |                 |

|                | <u> </u>        |                 |

The information in this book has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies.

System Semiconductor, reserves the right to make changes without further notice to any products herein to improve reliability, function or design. System Semiconductor does not assume any liability arising out of the application or use of any product or circuit described herein in accordance with System Semiconductor's standard warranty; neither does it convey any license under its patent rights of others. System Semiconductor System Semiconductor System Semiconductor

System Semiconductor's general policy does not recommend the use of its products in life support or aircraft applications wherein a failure or malfunction of the product may directly threaten life or injury. Per System Semiconductor's terms and conditions of sales, the user of System Semiconductor, products in life support or aircraft applications assumes all risks of such use and indemnifies System Semiconductor, against all damages.

## CONTENTS

| Section 1: Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <i>1</i>               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| The Program and Data Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                      |

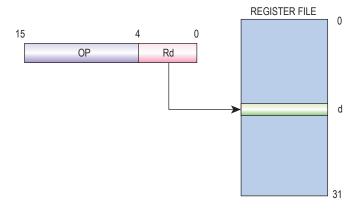

| Register Direct, Single Register Rd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |

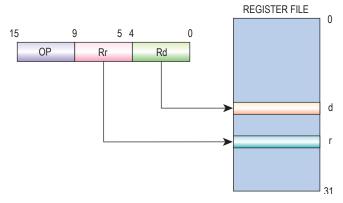

| Register Direct, Two Registers Rd and Rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        |

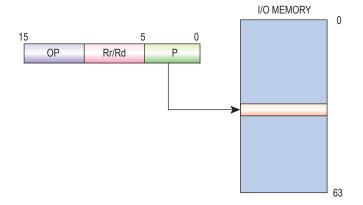

| I/O Direct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                      |

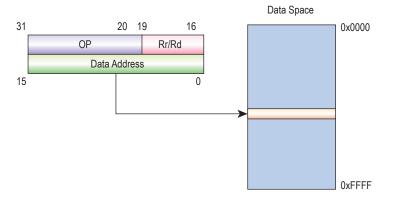

| Data Direct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2                      |

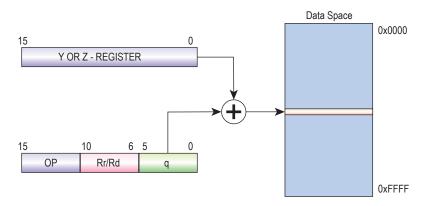

| Data Indirect with Displacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2                      |

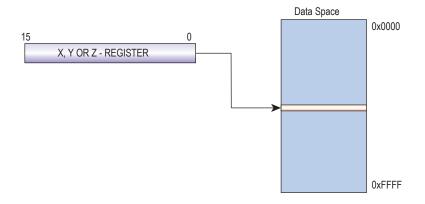

| Data Indirect Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                      |

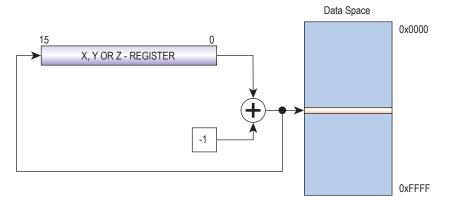

| Data Indirect with Pre-decrement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                      |

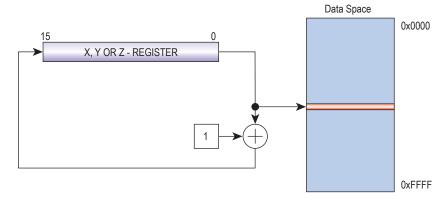

| Data Indirect with Post-increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |

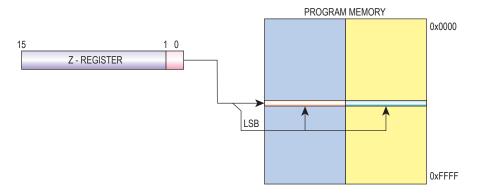

| Constant Addressing Using the LPM, ELPM, and SPM Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        |

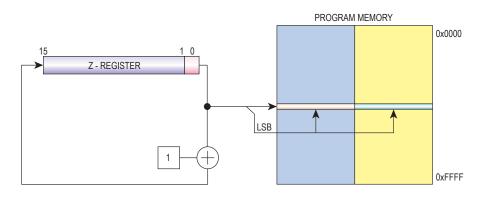

| Program Memory with Post-increment using the LPM Z+ and ELPM Z+ I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Instruction4           |

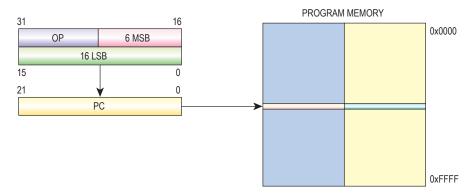

| Direct Program Addressing, JMP and CALL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

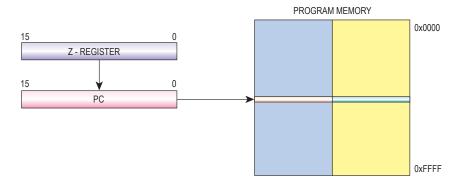

| Indirect Program Addressing, IJMP and ICALL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                        |

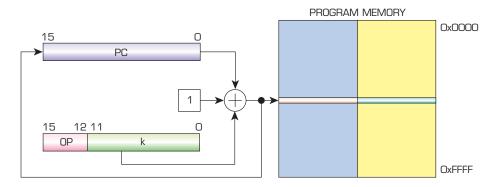

| Relative Program Addressing, RJMP and RCALL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5                      |

| Section 2: Instruction Set Nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                      |

| Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                      |

| Registers and Operands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |

| I/O Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        |

| Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |

| Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                      |

| Section 3: Complete Instruction Set Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <i>7</i>               |

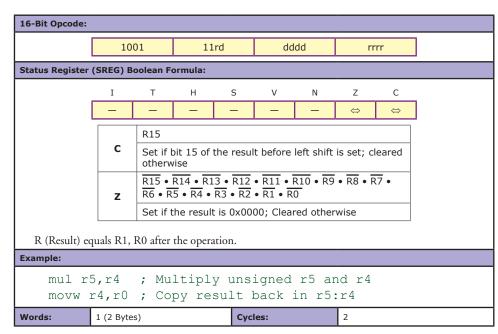

| Arithmetic and Logic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |

| MCU Control Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        |

| Branch Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |

| Data Transfer Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |

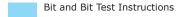

| Bit and Bit-Test Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |

| Conditional Branch Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                     |

| Conditional Branch Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |

| Section 4: Instruction Set Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11                     |

| Section 4: Instruction Set Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11                     |

| Section 4: Instruction Set Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11<br>11<br>12         |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry.  ADIW – Add Immediate to Word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11<br>12<br>13         |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry.  ADIW – Add Immediate to Word.  AND – Logical AND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11121314               |

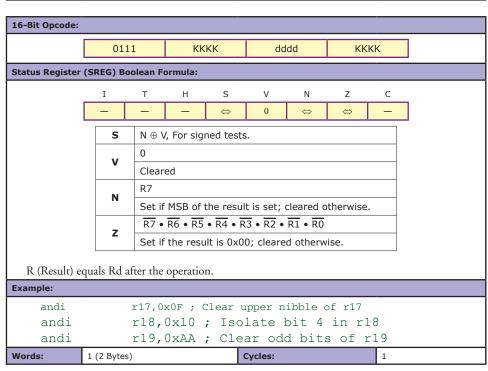

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry.  ADIW – Add Immediate to Word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1112131415             |

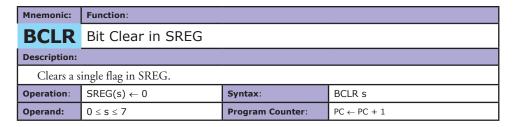

| Section 4: Instruction Set Details.  ADC – Add with Carry  ADC – Add without Carry  ADIW – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 111213141516           |

| Section 4: Instruction Set Details.  ADC – Add with Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11121314151617         |

| Section 4: Instruction Set Details.  ADC – Add with Carry  ADC – Add without Carry  ADIW – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11121314151617         |

| Section 4: Instruction Set Details.  ADC – Add with Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 111213141516171718     |

| Section 4: Instruction Set Details.  ADC – Add with Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1112131415161717181819 |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADIW – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BRCS – Branch if Carry Set  BREAK – Break                                                                                                                                                                                                                                                                                                                                                                                    |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADIW – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BRCS – Branch if Carry Set  BREAK – Break  BREQ – Branch if Equal                                                                                                                                                                                                                                                                                                                                                            |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADIW – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BRCS – Branch if Carry Set  BREAK – Break  BREQ – Branch if Equal  BRGE – Branch if Greater or Equal (Signed)                                                                                                                                                                                                                                                                                                                |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADIW – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BREAK – Break  BREQ – Branch if Equal  BRGE – Branch if Greater or Equal (Signed)  BRHC – Branch if Half Carry Flag is Cleared                                                                                                                                                                                                                                                                                               |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADIW – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BREAK – Break  BREQ – Branch if Equal  BRGE – Branch if Greater or Equal (Signed)  BRHC – Branch if Half Carry Flag is Cleared  BRHS – Branch if Half Carry Flag is Cleared                                                                                                                                                                                                                                                  |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADIW – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BRCS – Branch if Carry Set  BREAK – Break  BREQ – Branch if Equal  BRGE – Branch if Greater or Equal (Signed)  BRHC – Branch if Half Carry Flag is Cleared  BRHS – Branch if Half Carry Flag is Set  BRHS – Branch if Global Interrupt is Disabled                                                                                                                                                                           |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADI – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BREAK – Break  BREQ – Branch if Equal  BRGE – Branch if Greater or Equal (Signed)  BRHC – Branch if Half Carry Flag is Cleared  BRHS – Branch if Half Carry Flag is Set  BRID – Branch if Global Interrupt is Disabled  BRIE – Branch if Global Interrupt is Enabled                                                                                                                                                          |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADI – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BREAK – Break  BREQ – Branch if Equal  BREQ – Branch if Greater or Equal (Signed)  BRHC – Branch if Half Carry Flag is Cleared  BRHS – Branch if Half Carry Flag is Set  BRID – Branch if Global Interrupt is Disabled  BRIE – Branch if Global Interrupt is Enabled  BRIO – Branch if Lower (Unsigned)                                                                                                                       |                        |

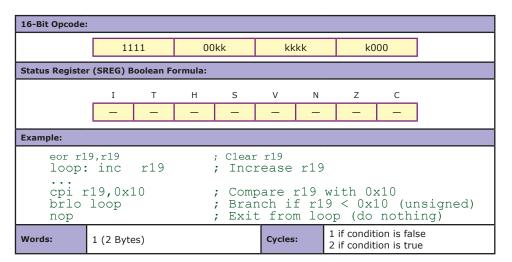

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADIW – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Bit in SREG is Set  BRCC – Branch if Carry Cleared  BRCS – Branch if Carry Set  BREAK – Break  BREQ – Branch if Greater or Equal (Signed)  BRHC – Branch if Half Carry Flag is Cleared  BRHS – Branch if Half Carry Flag is Set  BRID – Branch if Global Interrupt is Disabled  BRIE – Branch if Global Interrupt is Enabled  BRLO – Branch if Lower (Unsigned)  BRLT – Branch if Less Than (Signed)                                                                        |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADI – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BREAK – Break  BREQ – Branch if Equal  BREQ – Branch if Greater or Equal (Signed)  BRHC – Branch if Half Carry Flag is Cleared  BRHS – Branch if Global Interrupt is Disabled  BRID – Branch if Global Interrupt is Enabled  BRLO – Branch if Lower (Unsigned)  BRLO – Branch if Lower (Unsigned)  BRMI – Branch if Minus  BRMI – Branch if Not Equal |                        |

| ADC – Add with Carry.  ADC – Add without Carry  ADI – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BREAK – Break  BREQ – Branch if Equal  BREQ – Branch if Greater or Equal (Signed)  BRHC – Branch if Half Carry Flag is Cleared  BRHS – Branch if Global Interrupt is Disabled  BRID – Branch if Global Interrupt is Enabled  BRLO – Branch if Lower (Unsigned)  BRLO – Branch if Lower (Unsigned)  BRMI – Branch if Minus  BRMI – Branch if Minus  BRMI – Branch if Not Equal  BRNE – Branch if Not Equal  BRNE – Branch if Plus                                   |                        |

| Section 4: Instruction Set Details.  ADC – Add with Carry.  ADC – Add without Carry  ADI – Add Immediate to Word  AND – Logical AND  ANDI – Logical AND with Immediate  ASR – Arithmetic Shift Right  BCLR – Bit Clear in SREG  BLD – Bit Load from the T Flag in SREG to a Bit in Register  BRBC – Branch if Bit in SREG is Cleared  BRBS – Branch if Carry Cleared  BRCS – Branch if Carry Cleared  BREAK – Break  BREQ – Branch if Equal  BREQ – Branch if Greater or Equal (Signed)  BRHC – Branch if Half Carry Flag is Cleared  BRHS – Branch if Global Interrupt is Disabled  BRID – Branch if Global Interrupt is Enabled  BRLO – Branch if Lower (Unsigned)  BRLO – Branch if Lower (Unsigned)  BRMI – Branch if Minus  BRMI – Branch if Not Equal |                        |

| BRVC – Branch if Overflow Cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| BRVS – Branch if Overflow Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28                                                                               |

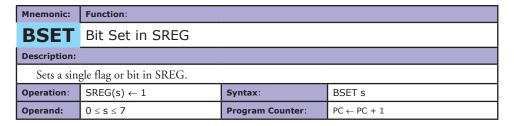

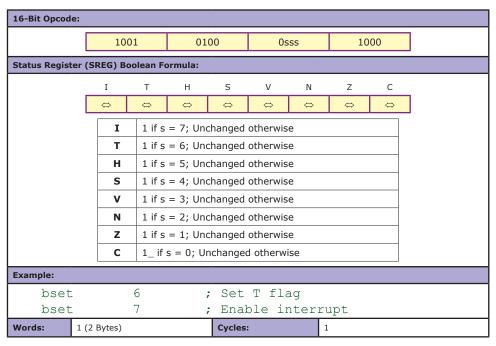

| BSET – Bit Set in SREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                                               |

| BST – Bit Store from Bit in Register to T Flag in SREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                                               |

| CALL – Long Call to a Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| CBI – Clear Bit in I/O Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

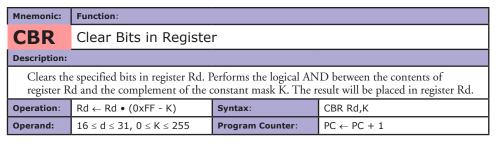

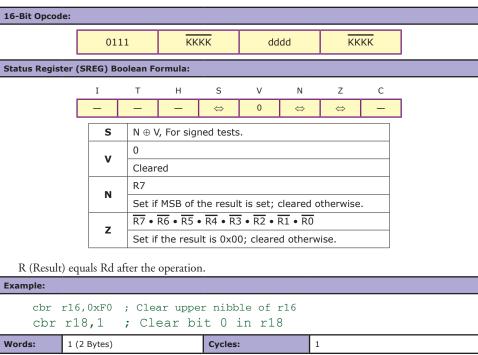

| CBR – Clear Bits in Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| CLC – Clear Carry Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| CLH – Clear Half Carry Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| CLI – Clear Global Interrupt Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

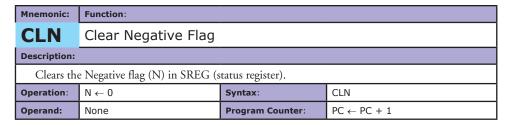

| CLN – Clear Negative Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33                                                                               |

| CLR – Clear Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

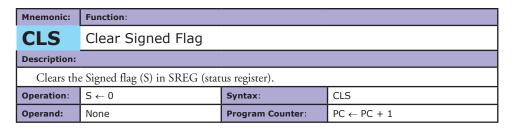

| CLS – Clear Signed Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| CLT – Clear T Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

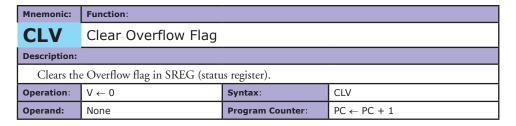

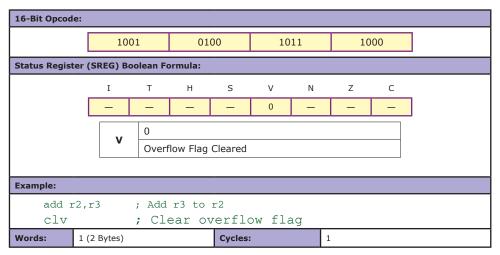

| CLV – Clear Overflow Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

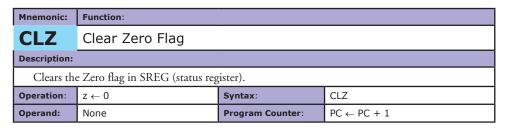

| CLZ – Clear Zero Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| COM – One's Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| CP – Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| CPC – Compare with Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| CPI – Compare with Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| CPSE – Compare Skip if Equal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| DEC – Decrement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| EICALL - Extended Indirect Call to Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| EIJMP - Extended Indirect Jump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42                                                                               |

| ELPM – Extended Load Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| EOR – Exclusive OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| FMUL - Fractional Multiply Unsigned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| FMULS - Fractional Multiply Signed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| FMULSU - Fractional Multiply Signed with Unsigned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48                                                                               |

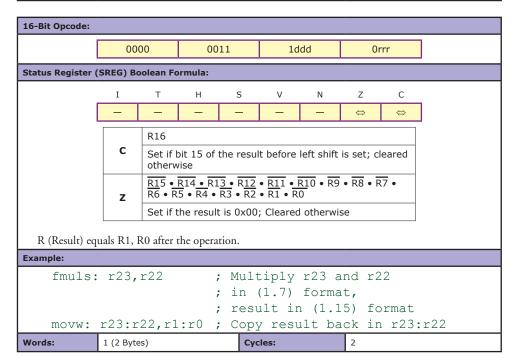

| ICALL – Indirect Call to Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                                                               |

| IJMP – Indirect Jump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| IN – Load an I/O Location to Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| IN(C = Increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.1                                                                              |