# M3000

## MOTOR AND MOTION CONTROLLER USER'S GUIDE

| M3000 Manual | Change Log |                 |

|--------------|------------|-----------------|

| Date         | Revision   | Changes         |

| 08/13/2007   | R081307    | Initial Release |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

|              |            |                 |

The information in this book has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies.

System Semiconductor, reserves the right to make changes without further notice to any products herein to improve reliability, function or design. System Semiconductor does not assume any liability arising out of the application or use of any product or circuit described herein in accordance with System Semiconductor's standard warranty; neither does it convey any license under its patent rights of others. System Semiconductor  $\text{SYSTEM}^{\text{SS}}$  and SSI are trademarks of System Semiconductor.

System Semiconductor's general policy does not recommend the use of its products in life support or aircraft applications wherein a failure or malfunction of the product may directly threaten life or injury. Per System Semiconductor's terms and conditions of sales, the user of System Semiconductor, products in life support or aircraft applications assumes all risks of such use and indemnifies System Semiconductor, against all damages.

## CONTENTS

| Section 1: M3000 Introduction                          | 1-1 |

|--------------------------------------------------------|-----|

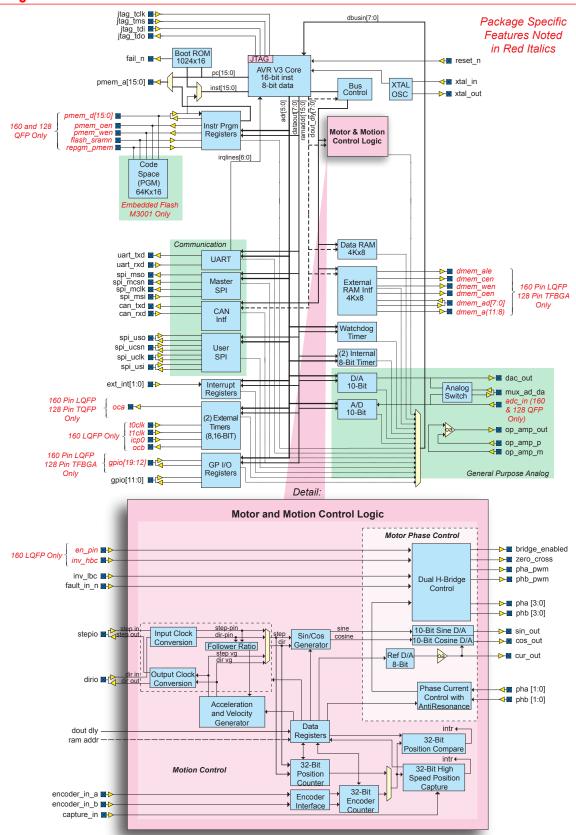

| M3000 Block Diagram                                    |     |

| Section 2: Physical Characteristics                    | 2-1 |

| Absolute Maximum Ratings                               |     |

| Analog Characteristics                                 |     |

| DC Characteristics                                     |     |

| Thermal Characteristics.                               |     |

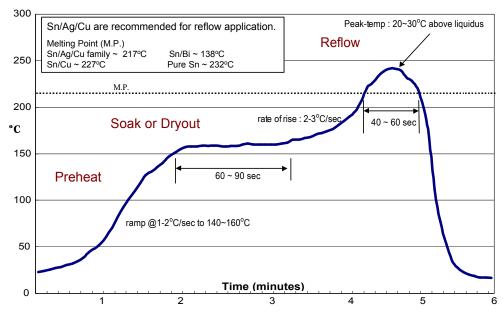

| Soldering Characteristics                              |     |

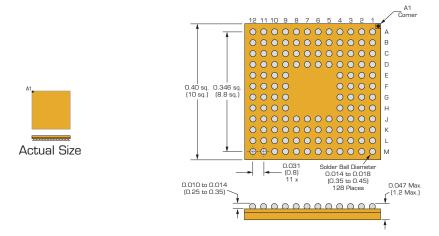

| Land Pattern - M3001 TFBGA Package                     |     |

| Reflow Profile - M3001 TFBGA Package                   |     |

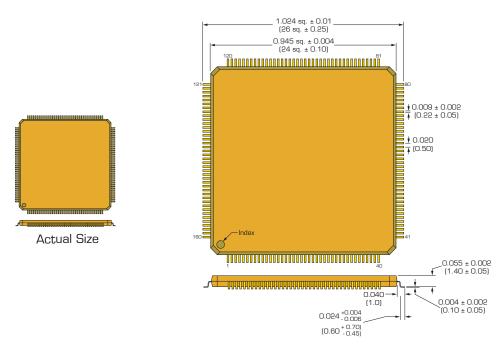

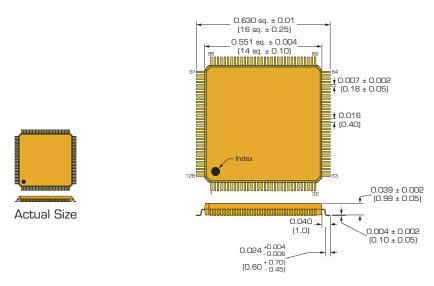

| Section 3: Mechanical Specifications                   | 3-1 |

| M3000F — LQFP-160                                      |     |

| M3000S — TQFP-128                                      |     |

| M3001 — TFBGA-128                                      |     |

|                                                        |     |

| Section 4: Pin Assignments                             |     |

| Feature Summary by Package Style                       |     |

| Processor Control                                      |     |

| Communications                                         |     |

| Memory (Code/Program Space) M3000 128 and 160 QFP Only |     |

| Memory (Code/Program Space) M3001 128 TFBGA            |     |

| External Timer                                         |     |

| Indexer Logic                                          |     |

| Analog                                                 |     |

| I/O Ports/Memory                                       |     |

| Motor Bridge Drive Stage<br>Power and Ground           |     |

| Tower and Ground                                       | 4-0 |

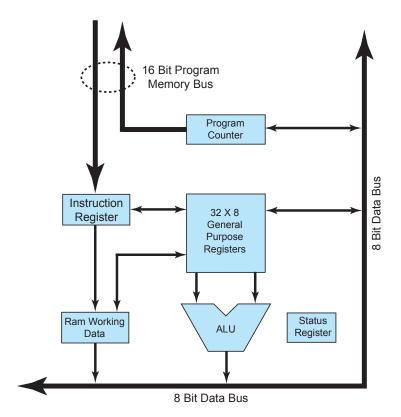

| Section 5: CPU Core                                    |     |

| Introduction                                           |     |

| Memory                                                 |     |

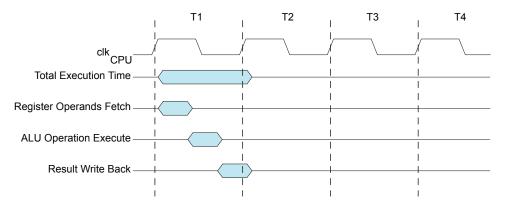

| ALU – Arithmetic Logic Unit                            |     |

| Status Register                                        |     |

| SREG – Status Register                                 |     |

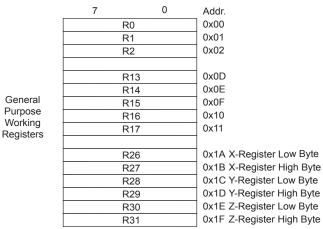

| General Purpose Register File                          |     |

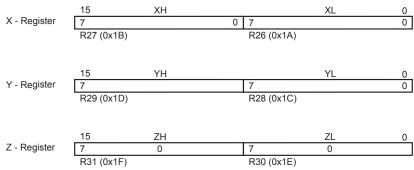

| The X-Register, Y-Register and Z-Register              |     |

| Stack Pointer                                          |     |

| Stack Pointer Register                                 |     |

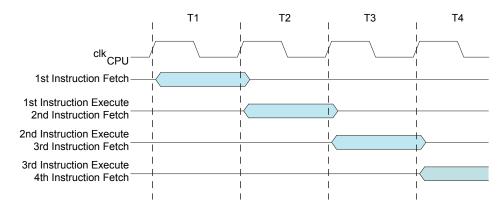

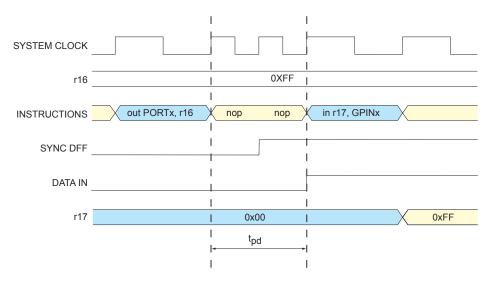

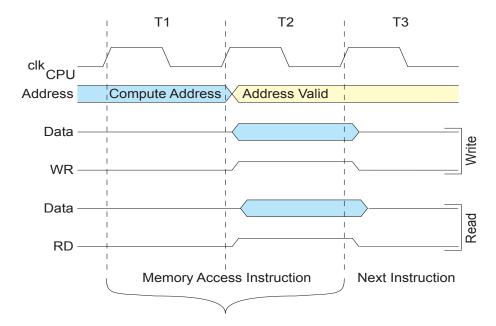

| Instruction Execution Timing                           |     |

| Memory Maps                                            |     |

| Instruction Memory                                     |     |

| Data Memory                                            |     |

| Data Memory Register Files                             |     |

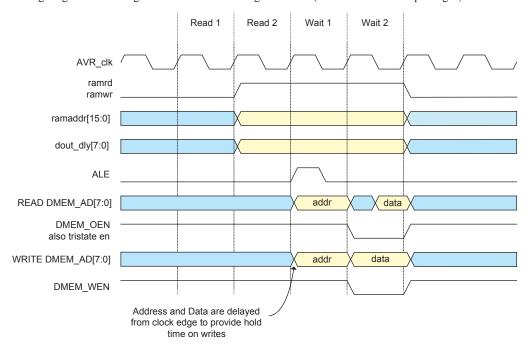

| Data Memory Access Times I/O Register Map              |     |

| I/O Register Map  Internal Timer Register Map          |     |

| Peripheral Connections                                 |     |

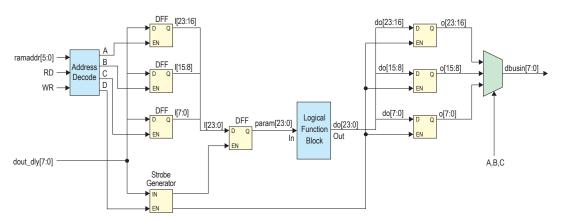

| External RAM Interface                                 |     |

| ction 6: General Purpose I/O                                 | 6-1         |

|--------------------------------------------------------------|-------------|

| Introduction                                                 | 6-1         |

| General Purpose I/O Registers                                |             |

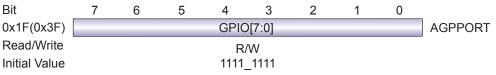

| AGPPORT (General Purpose I/O Data Register A)                |             |

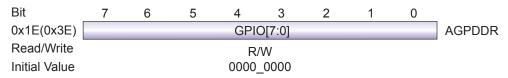

| AGPDDR (General Purpose I/O Data Direction Register A)       |             |

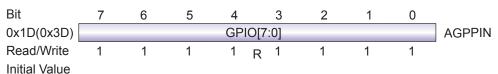

| AGPPIN (General Purpose I/O Input Pins A)                    |             |

| BGPPORT (General Purpose I/O Data Register B)                |             |

| BGPDDR (General Purpose I/O Data Direction Register B)       |             |

| BGPPIN (General Purpose I/O Input Pins B)                    |             |

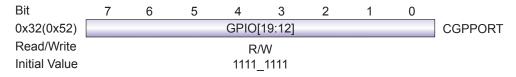

| CGPPORT (General Purpose I/O Data Register C)                |             |

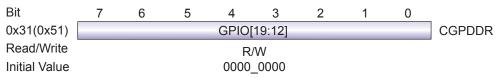

| CGPDDR (General Purpose I/O Data Direction Register C)       |             |

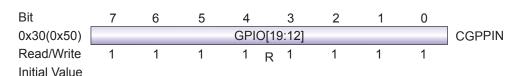

| CGPPIN (General Purpose I/O Input Pins C)                    |             |

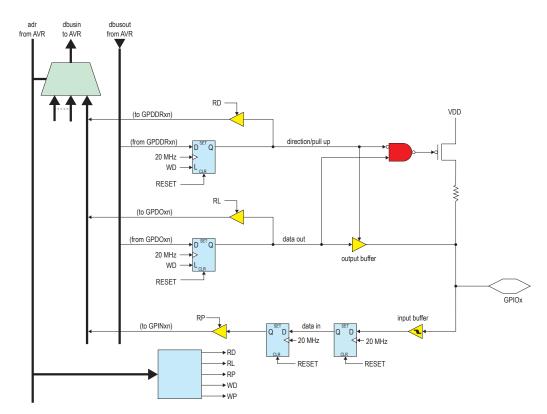

| I/O Ports                                                    |             |

| Ports as General Digital I/O                                 |             |

| General Digital I/O                                          |             |

| Port Pin Configurations                                      |             |

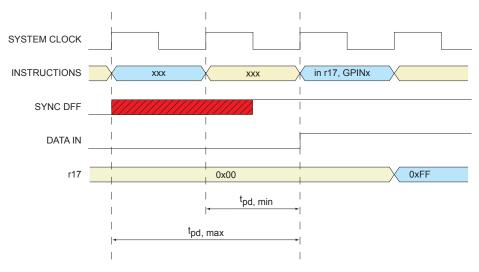

| Synchronization when Reading an Externally Applied Pin Value |             |

| I/O Port Code Examples                                       |             |

| C Code Example                                               |             |

| C Code Example                                               | 0-/         |

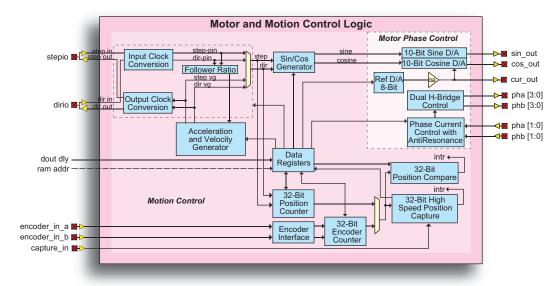

| ction 7: Motor And Motion Control Interface Introduction     | 7-1         |

| Function Blocks                                              |             |

| Description of the Motor and Motion Control Function Blocks  |             |

| Data Registers                                               |             |

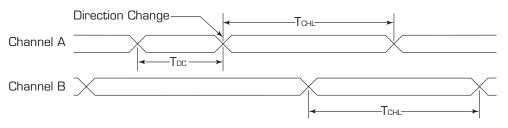

| Input/Output Clock Conversion                                |             |

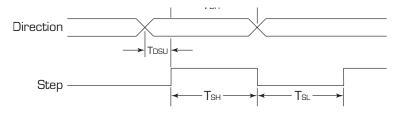

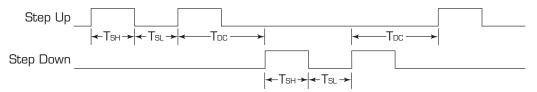

| Step and Direction Timing                                    |             |

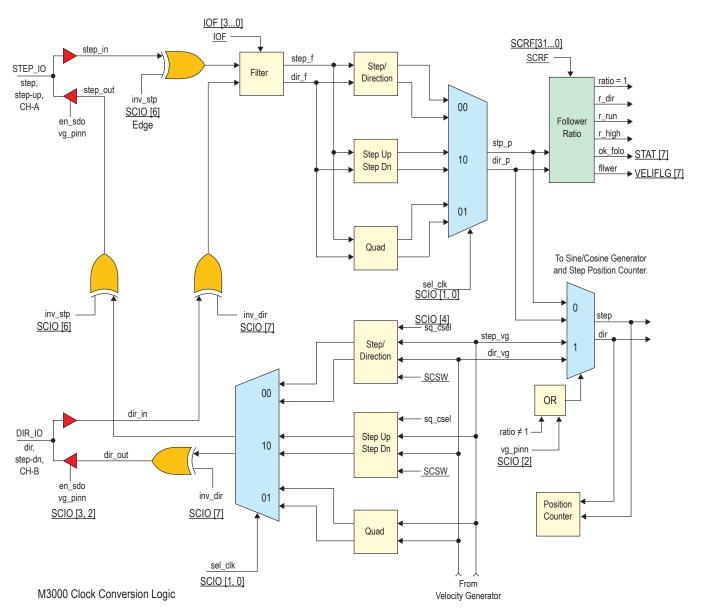

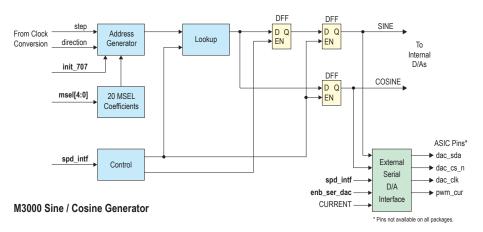

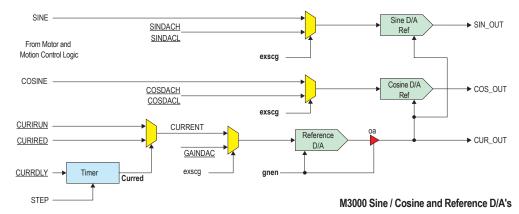

| Sine/Cosine Generator                                        |             |

| Internal 10-Bit Sine/Cosine D/As                             |             |

| Reference D/A                                                |             |

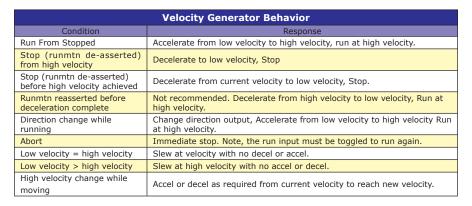

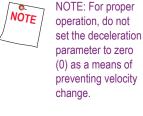

| Acceleration and Velocity Generator                          |             |

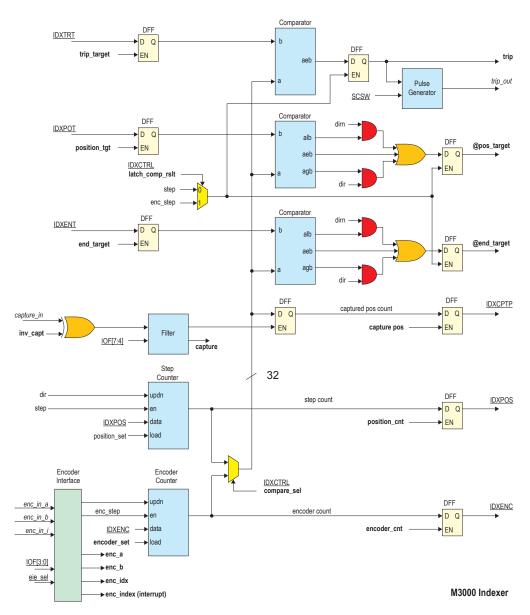

| Indexer                                                      |             |

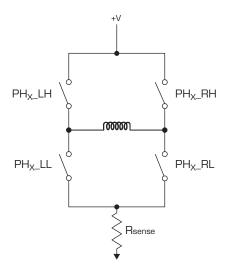

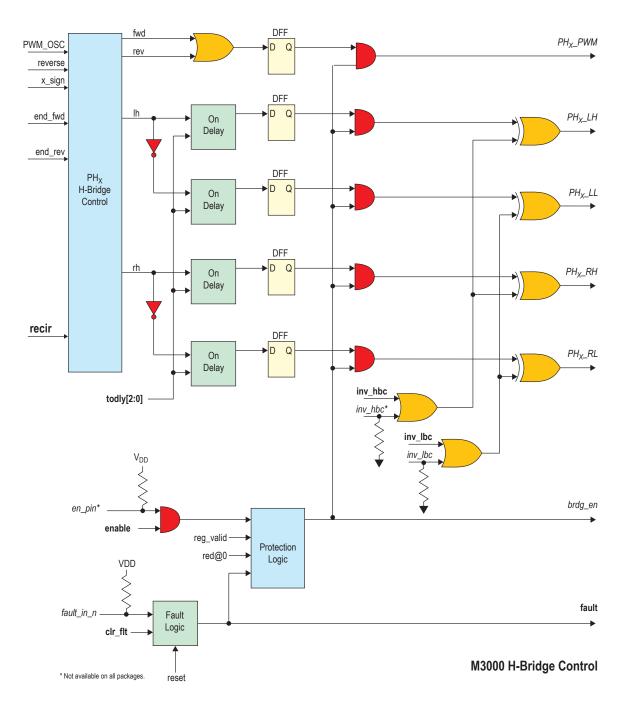

| Dual H-Bridge Control                                        |             |

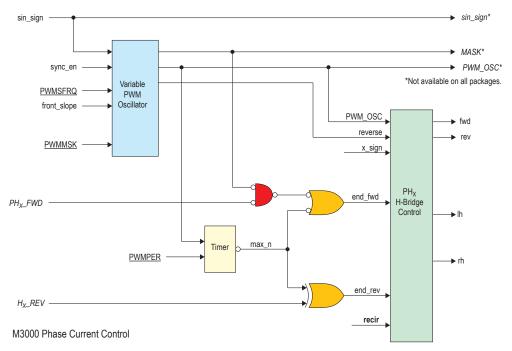

| Phase Current Control with Anti-Resonance                    |             |

| Motor and Motion Control Register Summary                    |             |

| Register Types                                               |             |

| PWM and Current Control Registers                            |             |

| Velocity Registers                                           |             |

| Index Registers                                              |             |

| Step Clock and Misc. Registers                               |             |

| PWM Registers                                                |             |

| PWMMSK (PWM Mask)                                            |             |

| PWMPER (PWM Percent)                                         |             |

|                                                              |             |

| PWMSFRQ (PWM Frequency)                                      |             |

| PWMCTL (PWM Control)                                         |             |

| CURRENT Registers                                            |             |

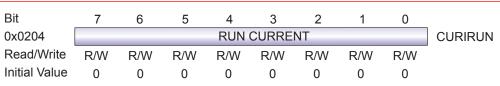

| CURIRUN                                                      |             |

| (Run Current)                                                |             |

| CURIRED (Current Reduction)                                  |             |

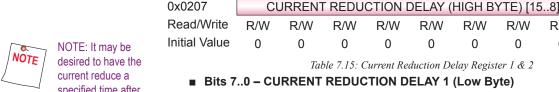

| CURRDLY (Current Reduction Delay 1 & 2)                      |             |

| VELOCITY Registers                                           | 7-20        |

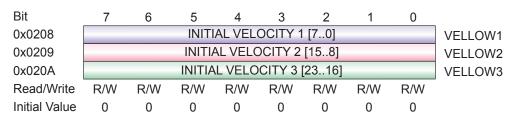

| VELLOW (Initial Low Velocity 1, 2 & 3)                       |             |

| VELHI (Terminal High Velocity 1, 2 & 3)                      |             |

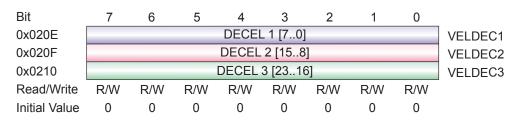

| VELDEC (Velocity Deceleration 1, 2 & 3)                      |             |

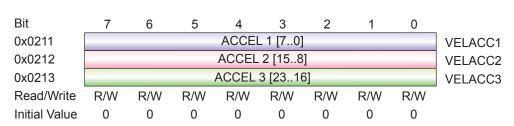

| VELACC (Velocity Acceleration 1, 2 & 3)                      |             |

| VELCVEL (Current Velocity 1, 2 & 3)                          |             |

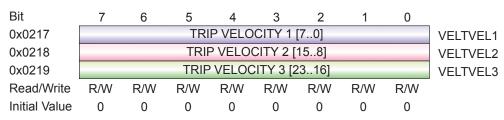

| VELTVEL (Trip Velocity 1, 2 & 3)                             | <i>7-22</i> |

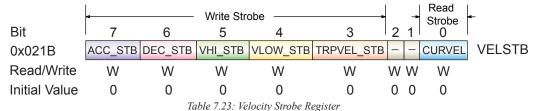

| VELVGCTL (Velocity Generator Control)                        | 7-23        |

| VELIFLG (Velocity Interrupt Flag)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <i>7-23</i>                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                     |

| VELIMSK (Velocity Interrupt Mask)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                     |

| INDEX Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                     |

| IDXTRT (Index Trip Target1, 2, 3 & 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-25                                                                                |

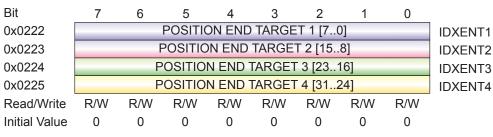

| IDXENT (Index End Target 1, 2, 3 & 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-25                                                                                |

| IDXMSDT (Index Motor Settling Delay Time 1& 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     |

| IDXPOT (Index Position Target 1, 2, 3 & 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                     |

| IDXPOS (Index Position Count 1, 2, 3 & 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                     |

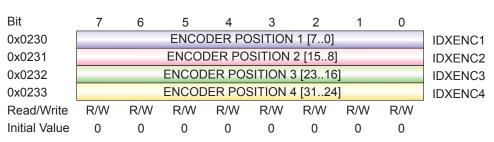

| IDXENC (Index Encoder Count 1, 2, 3 & 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                     |

| IDXCTRL (Index Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                     |

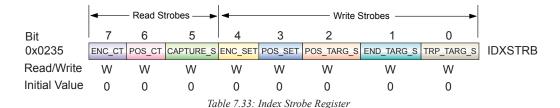

| IDXSTRB (Index Strobe)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                     |

| IDXCPTP (Index Capture Position 1, 2, 3 & 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                     |

| IDXIFLG (Index Interrupt Flag)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     |

| IDXIMSK (Index Interrupt Mask Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                     |

| STEP CLOCK Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                     |

| SCIO (Step Clock I/O)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                     |

| SCSW (Step Clock Step Width)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                     |

| SCRF (Step Clock Ratio Factor 1, 2, 3 & 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                     |

| Miscellaneous Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                     |

| IOF (Input/Output Filter)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                     |

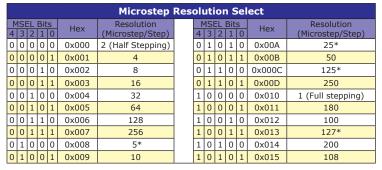

| MSELR (Microstep/Step Select Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                     |

| STAT (Status)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                     |

| SPWMCTL (Safety, PWM Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7-36                                                                                |

| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-37                                                                                |

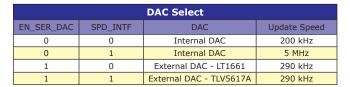

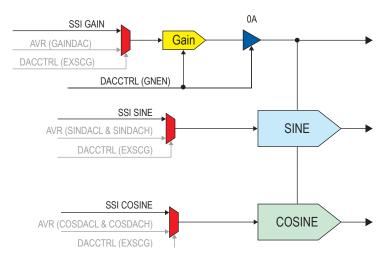

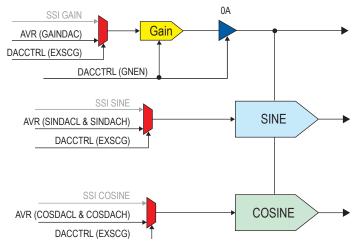

| DAC Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                     |

| DACCTRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                     |

| (D/A Converter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                     |

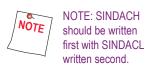

| SINDACL (Sine D/A Converter Low Bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                     |

| SINDACH (Sine DIA Converter High Bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                     |

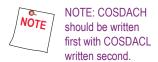

| COSDACL (Cosine D A Converter Low Bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                     |

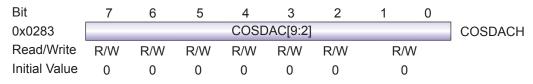

| COSDACH (Cosine D/A Converter High Bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                     |

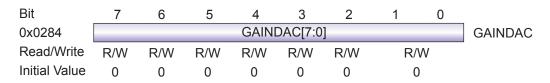

| GAINDAC (D/A Converter Gain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                     |

| GIII (DII Content Guin)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                     |

| Section 8: Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>Q</b> _1                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0-1                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                     |

| Interrupt Registers and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-1                                                                                 |

| Interrupt Registers and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-1<br><i>8-1</i>                                                                   |

| Interrupt Registers and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-1<br>8-1<br>8-1                                                                   |

| Interrupt Registers and Functions  Interrupt Capture Registers  External Interrupts  Interrupt Clearing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8-1<br>8-1<br>8-1                                                                   |

| Interrupt Registers and Functions  Interrupt Capture Registers  External Interrupts  Interrupt Clearing  Typical Code for Initializing Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-1<br>8-1<br>8-1<br>8-2                                                            |

| Interrupt Registers and Functions.  Interrupt Capture Registers  External Interrupts  Interrupt Clearing  Typical Code for Initializing Interrupts  Interrupt Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-1<br>8-1<br>8-1<br>8-2<br>8-2                                                     |

| Interrupt Registers and Functions.  Interrupt Capture Registers  External Interrupts  Interrupt Clearing  Typical Code for Initializing Interrupts  Interrupt Handling  Interrupt Response Time.                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-1<br>8-1<br>8-1<br>8-2<br>8-2                                                     |

| Interrupt Registers and Functions.  Interrupt Capture Registers  External Interrupts  Interrupt Clearing  Typical Code for Initializing Interrupts  Interrupt Handling  Interrupt Response Time  Interrupt Registers                                                                                                                                                                                                                                                                                                                                                                                                    | 8-1<br>8-1<br>8-1<br>8-2<br>8-2<br>8-2                                              |

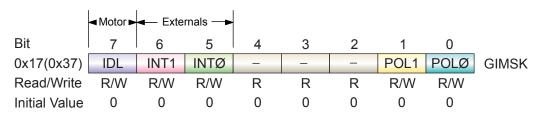

| Interrupt Registers and Functions.  Interrupt Capture Registers  External Interrupts  Interrupt Clearing  Typical Code for Initializing Interrupts  Interrupt Handling  Interrupt Response Time  Interrupt Registers  GIMSK (General Interrupt Mask)                                                                                                                                                                                                                                                                                                                                                                    | 8-1 8-1 8-1 8-2 8-2 8-3                                                             |

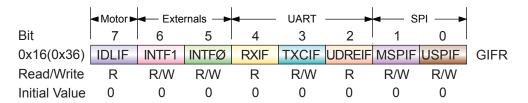

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Response Time.  Interrupt Registers.  GIMSK (General Interrupt Mask).  GIFR (General Interrupt Flag)                                                                                                                                                                                                                                                                                                                               | 8-1 8-1 8-1 8-2 8-2 8-3 8-3                                                         |

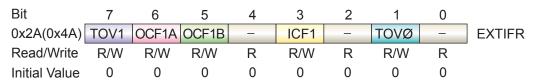

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Response Time  Interrupt Registers.  GIMSK (General Interrupt Mask).  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).                                                                                                                                                                                                                                                                             | 8-1<br>8-1<br>8-1<br>8-2<br>8-2<br>8-2<br>8-3<br>8-3<br>8-4                         |

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Response Time.  Interrupt Registers.  GIMSK (General Interrupt Mask)  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).  EXTIFR (External Timer/Counter Interrupt Flag).                                                                                                                                                                                                                            | 8-1 8-1 8-1 8-1 8-1 8-2 8-2 8-2 8-3 8-3 8-3 8-5 8-5 8-5 8-5                         |

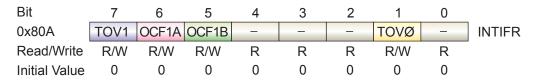

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts  Interrupt Handling  Interrupt Response Time.  Interrupt Registers.  GIMSK (General Interrupt Mask)  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).  EXTIFR (External Timer/Counter Interrupt Flag).  INTIMSK (Internal Timer/Counter Interrupt Mask).                                                                                                                                                                           | 8-1 8-1 8-1 8-1 8-2 8-2 8-2 8-3 8-3 8-4 8-5 8-5 8-6                                 |

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Response Time.  Interrupt Registers.  GIMSK (General Interrupt Mask)  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).  EXTIFR (External Timer/Counter Interrupt Flag).                                                                                                                                                                                                                            | 8-1 8-1 8-1 8-1 8-2 8-2 8-2 8-3 8-3 8-4 8-5 8-5 8-6                                 |

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Registers  GIMSK (General Interrupt Mask)  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).  EXTIFR (External Timer/Counter Interrupt Flag).  INTIMSK (Internal Timer/Counter Interrupt Mask).  INTIFR (Internal Timer Counter Interrupt Flag).                                                                                                                                                    | 8-1 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-5 8-6 8-6                                     |

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Response Time.  Interrupt Registers.  GIMSK (General Interrupt Mask)  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).  EXTIFR (External Timer/Counter Interrupt Flag).  INTIMSK (Internal Timer/Counter Interrupt Flag).  INTIMSK (Internal Timer Counter Interrupt Flag).  INTIFR (Internal Timer Counter Interrupt Flag).                                                                       | 8-1 8-1 8-1 8-1 8-2 8-2 8-2 8-3 8-3 8-4 8-5 8-6 8-6                                 |

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Registers.  GIMSK (General Interrupt Mask)  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).  EXTIFR (External Timer/Counter Interrupt Flag).  INTIMSK (Internal Timer/Counter Interrupt Flag).  INTIMSK (Internal Timer Counter Interrupt Flag).  INTIFR (Internal Timer Counter Interrupt Flag).  Section 9: Instruction Memory Programming.  Introduction.                                      | 8-1 8-1 8-1 8-1 8-2 8-2 8-2 8-3 8-3 8-4 8-5 8-6 8-6 8-6 9-1                         |

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Response Time  Interrupt Registers.  GIMSK (General Interrupt Mask).  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).  EXTIFR (External Timer/Counter Interrupt Flag).  INTIMSK (Internal Timer/Counter Interrupt Flag).  INTIFR (Internal Timer Counter Interrupt Flag).  Section 9: Instruction Memory Programming  Introduction  Description.                                                  | 8-1 8-1 8-1 8-1 8-1 8-2 8-2 8-2 8-3 8-3 8-4 8-5 8-6 8-6 8-6 9-1 9-1 9-1             |

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Response Time.  Interrupt Registers.  GIMSK (General Interrupt Mask)  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).  EXTIFR (External Timer/Counter Interrupt Flag).  INTIMSK (Internal Timer/Counter Interrupt Flag).  INTIFR (Internal Timer Counter Interrupt Flag).  Section 9: Instruction Memory Programming.  Introduction.  Description.  Definition of Software Code Types.            | 8-1 8-1 8-1 8-1 8-1 8-2 8-2 8-2 8-3 8-3 8-3 8-5 8-6 8-6 8-6 8-6 9-1 9-1 9-2         |

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Response Time.  Interrupt Registers.  GIMSK (General Interrupt Mask)  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).  EXTIFR (External Timer/Counter Interrupt Flag).  INTIMSK (Internal Timer/Counter Interrupt Flag).  INTIFR (Internal Timer Counter Interrupt Flag).  Section 9: Instruction Memory Programming  Introduction.  Description  Definition of Software Code Types.  Boot Loader | 8-1 8-1 8-1 8-1 8-1 8-1 8-2 8-2 8-2 8-3 8-3 8-3 8-4 8-5 8-6 8-6 8-6 9-1 9-1 9-2 9-2 |

| Interrupt Registers and Functions.  Interrupt Capture Registers.  External Interrupts.  Interrupt Clearing  Typical Code for Initializing Interrupts.  Interrupt Handling  Interrupt Response Time.  Interrupt Registers.  GIMSK (General Interrupt Mask)  GIFR (General Interrupt Flag).  EXTIMSK (External Timer/Counter Interrupt Mask).  EXTIFR (External Timer/Counter Interrupt Flag).  INTIMSK (Internal Timer/Counter Interrupt Flag).  INTIFR (Internal Timer Counter Interrupt Flag).  Section 9: Instruction Memory Programming.  Introduction.  Description.  Definition of Software Code Types.            | 8-1 8-1 8-1 8-2 8-2 8-2 8-3 8-3 8-3 8-4 8-5 8-6 8-6 9-1 9-1 9-2 9-2                 |

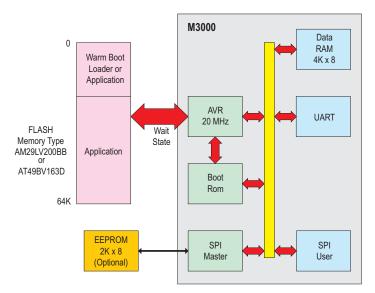

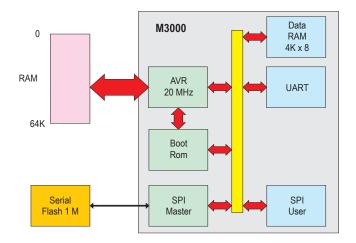

| System Memory Configurations                      |      |

|---------------------------------------------------|------|

| Normal                                            |      |

| High Speed (With Expanded Ram Capabilities)       | 9-2  |

| Data Memory Register Files                        |      |

| Data Memory Access Times                          |      |

| I/O Memory                                        |      |

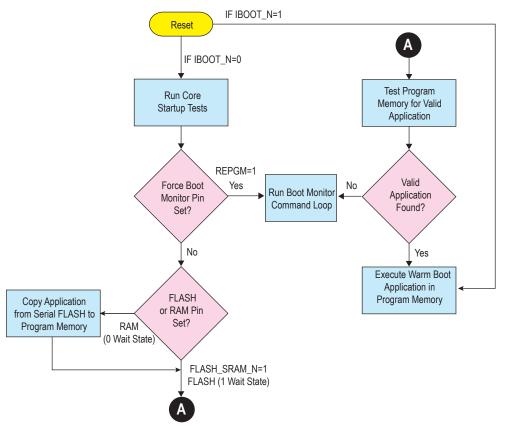

| Programming and Operating Scenarios               |      |

| Boot (New Production or Reprogram)                |      |

| Operation (Warm Boot)                             |      |

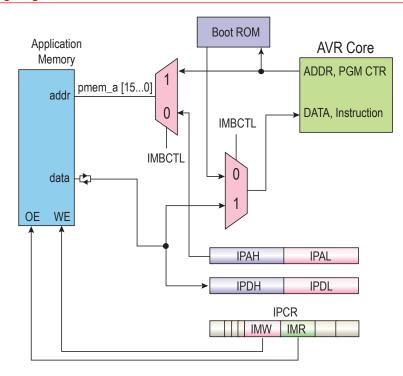

| Architecture                                      |      |

|                                                   |      |

| Power Up Sequence                                 |      |

| Internal Tests                                    |      |

| Forced Boot Monitor Execution                     |      |

| Application Code Locale Determination             |      |

| Validation of Application Code                    |      |

| Program Memory Functions                          |      |

| Program Memory Function Table                     | 9-6  |

| Program Memory Function                           | 9-7  |

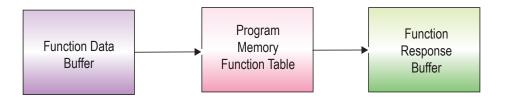

| Program Memory Function Data Buffer               |      |

| Program Memory Function Response Buffer           |      |

| Program Memory Command Example                    |      |

| Program Memory Access from SSI Code and User Code | 9-11 |

| Boot Monitor Command Mode                         |      |

| Commands                                          |      |

| Boot Monitor Command Protocol                     |      |

|                                                   |      |

| Boot Monitor Error Codes                          |      |

| Instruction Memory Programming Registers          |      |

| IPCR (Instruction Program Control)                |      |

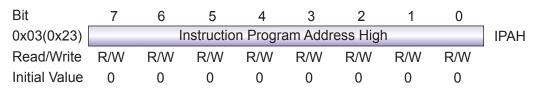

| IPAH (Instruction Program Address High)           |      |

| IPAL (Instruction Program Address Low)            | 9-15 |

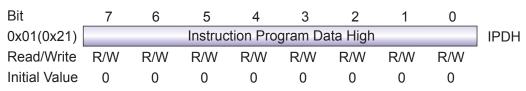

| IPDH (Instruction Program Data High)              | 9-15 |

| IPDL (Instruction Program Data Low)               | 9-15 |

| Program Memory Function Command Descriptions      | 9-16 |

| START_OF_CMD                                      |      |

| READ                                              |      |

| RD ARG                                            |      |

| WRITE                                             |      |

| WR ARG ADDR                                       |      |

|                                                   |      |

| WR_ARG_DATA                                       |      |

| WR_ARG_ARG                                        |      |

| PAUSE                                             |      |

| VERIFY                                            |      |

| VERIFY_WRITE                                      |      |

| END_OF_CMD                                        |      |

| Boot Monitor Command Descriptions                 | 9-19 |

| SET_PGM_MEM_FUNC                                  | 9-19 |

| EXE_PGM_MEM_FUNC                                  | 9-19 |

| PRG_SER_PGM                                       | 9-19 |

| START                                             |      |

| RESET                                             |      |

| RD_SER_PGM                                        |      |

| Boot Monitor Bypass                               |      |

| Don Monuor Dypuss                                 |      |

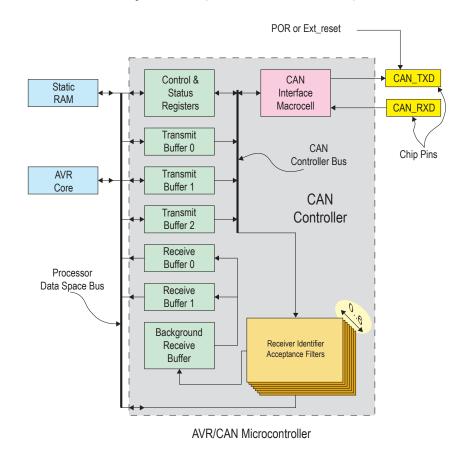

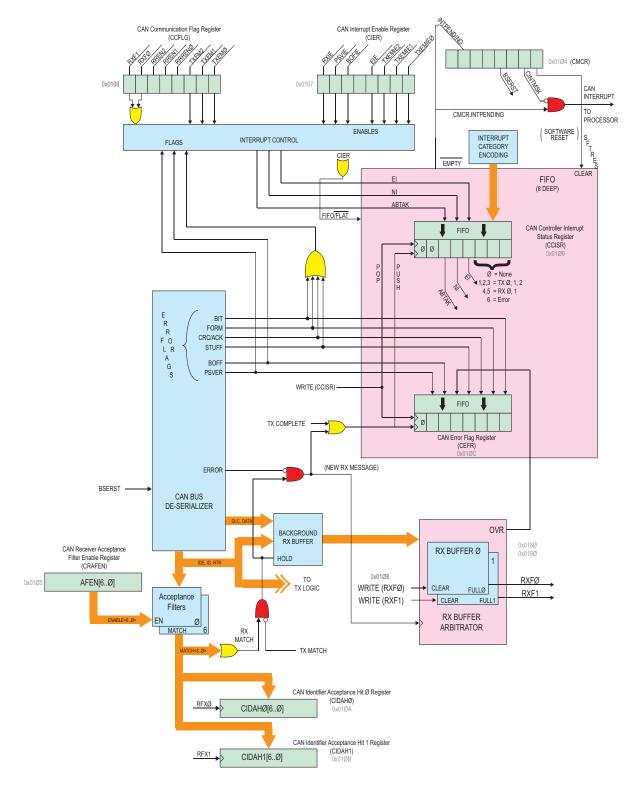

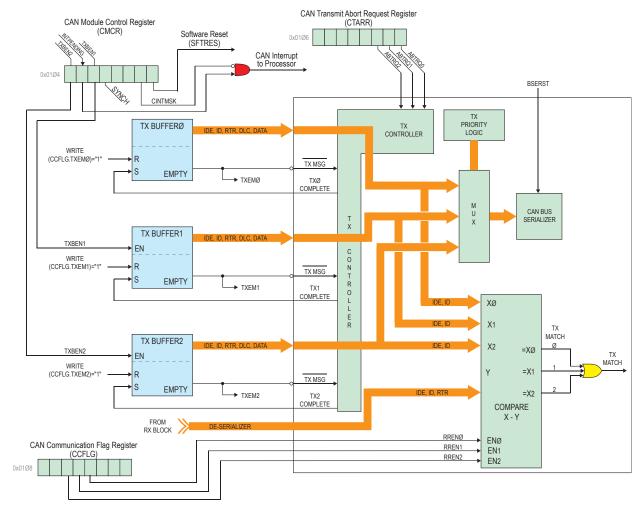

| ion 10: CAN Controller                            |      |

| Introduction                                      |      |

| Interfaces                                        | 10-2 |

| Receiving Messages                                | 10-2 |

| Transmitting Messages                             | 10-3 |

| CAN Controller Register Map                       |      |

|                                                   |      |

| Programmer's Model of Control and Interrupt Registers             | 10-7          |

|-------------------------------------------------------------------|---------------|

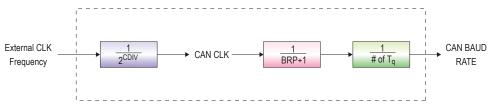

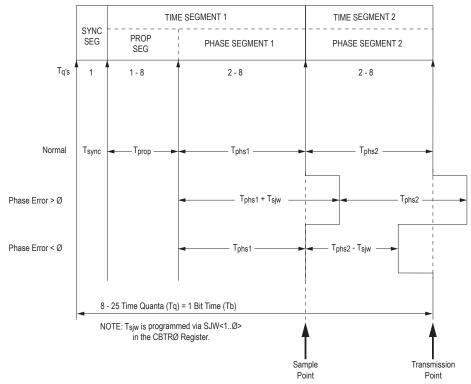

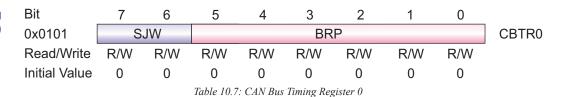

| CAN Baud Rate Control                                             | 10-8          |

| CAN Controller Registers                                          | 10-9          |

| CDIVCAN (CAN Clock Prescaler)                                     | 10-9          |

| CBTRO (CAN Bus Timing Register 0)                                 |               |

| CBTR1 (CAN Bus Timing Register 1)                                 |               |

| CBTR2 (CAN Bus Timing Register 2)                                 |               |

| CMCR (CAN Module Control Register)                                |               |

| CRAFEN (CAN Receiver Acceptance Filter Enable)                    |               |

| CTARR (CAN Transmit Abort Request Register)                       |               |

| CIANK (CAN Interrupt Enable Register)                             |               |

|                                                                   |               |

| CCFLG (CAN Communication Flag Register)                           |               |

| CCISR (CAN Controller Interrupt Status Register)                  |               |

| CIDAHO (CAN Identifier Acceptance Hit60 Register for Rx Buffer 0) |               |

| CIDAH1 (CAN Identifier Acceptance Hit60 Register for Rx Buffer 1) |               |

| CEFR (CAN Error Flag Register)                                    |               |

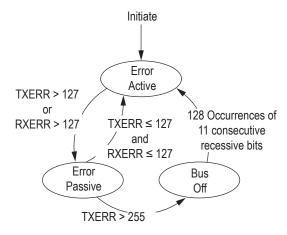

| Error Counters and Fault Confinement                              |               |

| CRXERR (CAN Receive Error Counter)                                |               |

| CTXERR (CAN Transmit Error Counter)                               |               |

| CVER (CAN Module Firmware Version)                                |               |

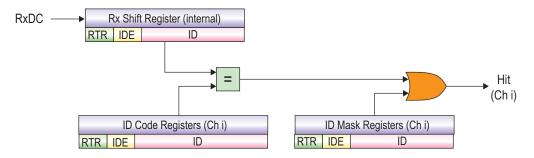

| CAN RX Acceptance Filtering                                       | 10-20         |

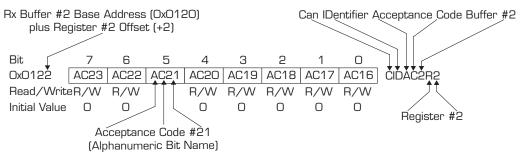

| CIDACnR<03> CIDMnR<03> (CAN Identifier Acceptance Code and        | Mask Register |

| 10-20                                                             |               |

| Message Handling Overview                                         | 10-22         |

| Programmers Model of Message Storage                              |               |

| Transmit Buffer Structure Description                             |               |

| Transmit Buffer Structure (Extended Identifier)                   |               |

| Transmit Buffer Structure                                         |               |

| (Standard Identifier)                                             |               |

| Receive Buffer Structure Description                              |               |

| Receive Buffer Structure                                          |               |

| (Extended Identifier)                                             |               |

|                                                                   |               |

| Receive Buffer Structure                                          |               |

| (Standard Identifier)                                             | 10-23         |

|                                                                   |               |

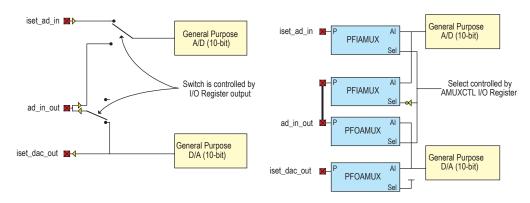

| Section 11: General Purpose A/D Interface                         | 11-1          |

| Introduction                                                      | 11-1          |

| Features                                                          | 11-1          |

| Specifications                                                    |               |

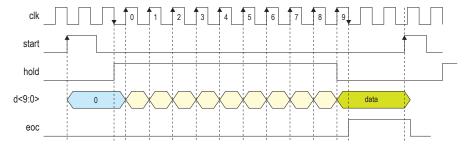

| Circuit Operation                                                 |               |

| General Purpose A/D Register Interface                            |               |

| ADC Registers                                                     |               |

| ADCSR (ADC Control and Status)                                    |               |

| ADRSLTHI (ADC Result High)                                        |               |

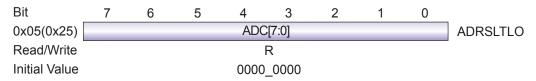

| ADRSLTLO (ADC Result Low)                                         |               |

| ADROLI LO (ADC Resul Low)                                         | 11-2          |

|                                                                   |               |

| Section 12: General Purpose D/A Interface                         | <i>12-1</i>   |

| Introduction                                                      | 12-1          |

| General Purpose D/A Register Interface                            | 12-1          |

| DAC Registers                                                     |               |

| DACVALHI (DAC Conversion Value High Byte)                         |               |

| DACVALLO (DAC Conversion Value Low Byte)                          |               |

| ( (                                                               |               |

| C .' 12 A .I C '. I                                               | 10 1          |

| Section 13: Analog Switch                                         |               |

| Introduction                                                      |               |

| Analog Switch Control                                             |               |

| Control Register                                                  |               |

| AMIXCTI (Angleg Mux Control)                                      |               |

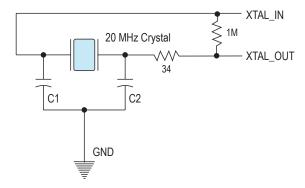

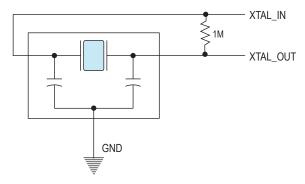

| section 14                                                                                                  | 14-1           |

|-------------------------------------------------------------------------------------------------------------|----------------|

| Crystal Oscillator                                                                                          | 14-1           |

| Introduction                                                                                                |                |

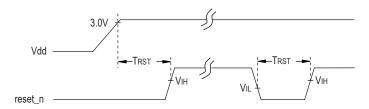

| section 15                                                                                                  |                |

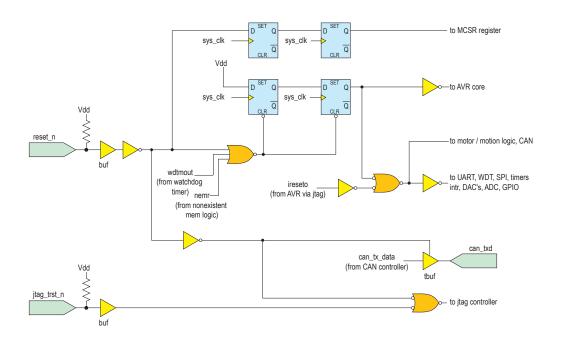

| Reset                                                                                                       | =              |

| Introduction                                                                                                |                |

| Reset Sources.                                                                                              |                |

| External                                                                                                    |                |

| Watchdog                                                                                                    |                |

| NEMR                                                                                                        |                |

| JTAG                                                                                                        |                |

| Operation                                                                                                   |                |

| MCSR Register                                                                                               |                |

| MCSK register                                                                                               | 1 )-2          |

| Continue 16 Minus Controller Ctatus Desiran                                                                 | 16.1           |

| Section 16: Micro Controller Status Register                                                                |                |

| Introduction                                                                                                |                |

| Micro Controller Status Register                                                                            |                |

| MCSR (Micro Controller Status)                                                                              | 16-1           |

|                                                                                                             |                |

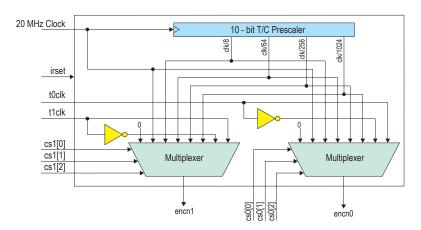

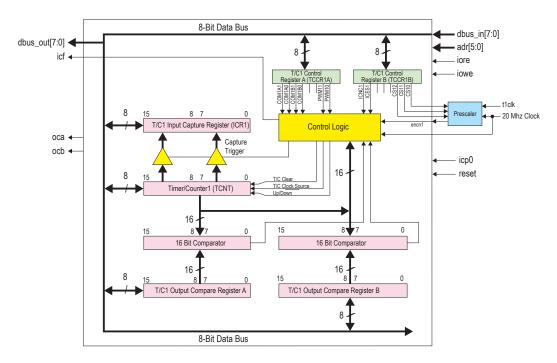

| Section 17: External and Internal Timer/Counters                                                            |                |

| Introduction                                                                                                | 17-1           |

| Features                                                                                                    |                |

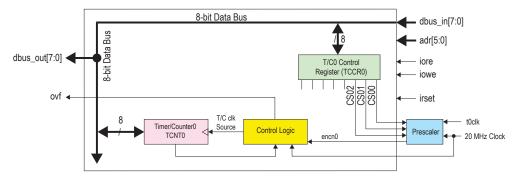

| 8-Bit Timer/Counter0                                                                                        | 17-1           |

| Timer/Counter Prescaler                                                                                     |                |

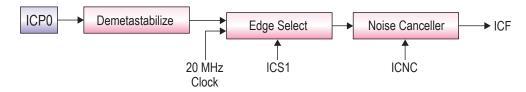

| 16-Bit Timer/Counter1                                                                                       |                |

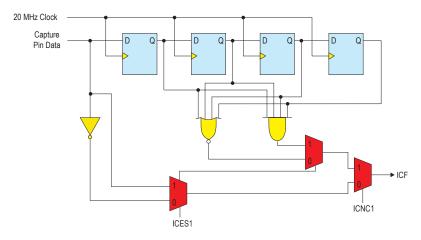

| Input Capture Noise Canceler                                                                                |                |

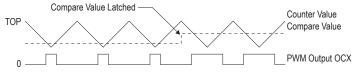

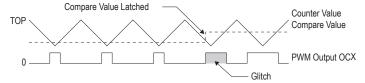

| Timer/Counter1 in PWM Mode                                                                                  |                |

| External Timer/Counter Registers                                                                            |                |

| EXTCCR0                                                                                                     |                |

| (External Timer/Counter0 Control Register)                                                                  |                |

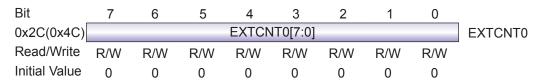

| EXTCNT (External Timer/Counter0)                                                                            |                |

| EXTCCR1A (External Timer/Counter1 Control Register A)                                                       |                |

| EXTCCR1B (External Timer/Counter1 Control Register B)                                                       |                |

| EXTCNT1H and EXTCNT1L (External Timer/Counter1 Register High By                                             | vte, Low Byte) |

| 17-8                                                                                                        | D              |

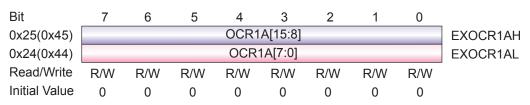

| EXOCR1AH and EXOCR1AL (External Timer/Counter1 Output Compar                                                |                |

| Byte, Low Byte)                                                                                             | 1/-8           |

| EXOCR1BH and EXOCR1BL (External Timer/Counter1 Output Compare                                               |                |

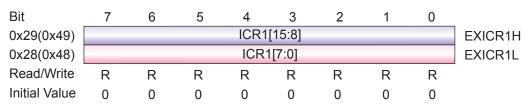

| Byte, Low Byte)<br>EXICR1H and EXICR1L (External Timer/Counter1 Input Capture Register                      |                |

|                                                                                                             |                |

| High Byte, Low Byte)                                                                                        |                |

| Internal Timer/Counter Registers                                                                            |                |

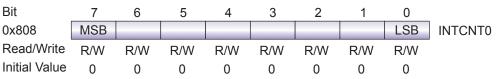

| INTCORO (Internal Timer/Counter0 Control Register)  INTCNTO (Internal Timer/Counter0)                       |                |

| INTCR1A (Internal Timer/Counter1 Control Register A)                                                        |                |

| INTCCRIA (Internal Timer/Counterl Control Register A) INTCCRIB (Internal Timer/Counterl Control Register B) |                |

|                                                                                                             |                |

| INTCNT1H and INTCNT1L(Internal Timer/Counter1 Register High Byte, Low Byte)                                 |                |

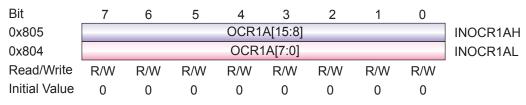

| (Internal Timer/CounterT Register High Byte, Low Byte)<br>INOCR1AH and INOCR1AL                             |                |

| (Internal Timer/Counter Compare Register A High Byte, Low Byte)                                             |                |

| INOCR1BH and INOCR1BL                                                                                       |                |

| (Internal Timer/Counter1 Output Compare Register B High Byte, Low Byte                                      |                |

| (1111/11111 1 1111/11 Counter 1 Curpus Compute Register D 1118/11 Dyle, Low Dyle                            | 1/-1 <b>T</b>  |

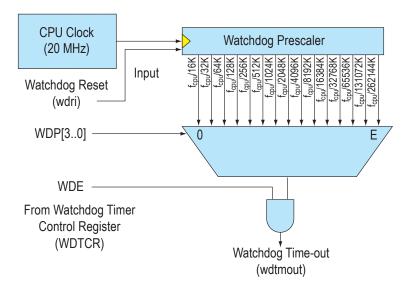

| ction 18: Watchdog Timer                            | . 18-1  |

|-----------------------------------------------------|---------|

| Introduction                                        |         |

| Features                                            |         |

| Functional Description                              |         |

| Code Examples                                       |         |

| C Code Example                                      |         |

| WDR Reset Instructions.                             |         |

| WDTCR (Watchdog Timer Control Register)             |         |

| w D I CR ( wateridog Tillier Collifor Register)     | 10-3    |

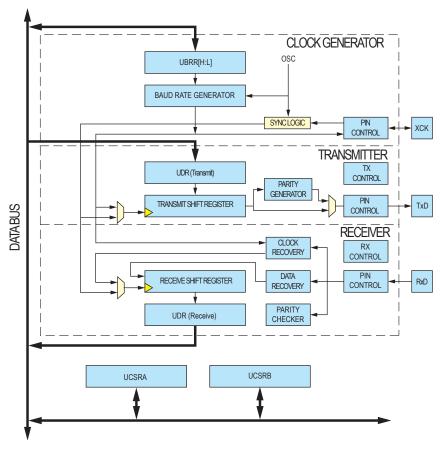

| ction 19: UART                                      | 19_1    |

| Introduction                                        |         |

| Features.                                           |         |

|                                                     |         |

| Function of the UART                                |         |

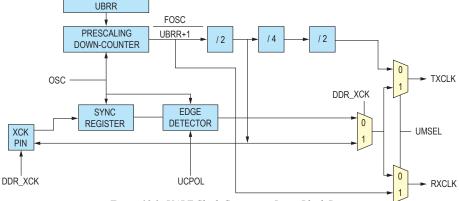

| Clock Generation                                    |         |

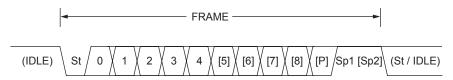

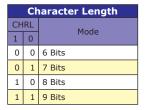

| Frame Formats                                       |         |

| Parity Bit Calculation                              | 19-3    |

| UART Initialization                                 | 19-3    |

| Code Example - UART Initialization                  | 19-4    |

| UART Data Transmitter                               | 19-4    |

| Introduction                                        | 19-4    |

| Sending Frames                                      |         |

| with 5 to 8 Data Bit                                |         |

| Code Example - UART Transmit Function               |         |

| Code Example - Sending Frames with 9 Data Bits      |         |

| Transmitter Flags and Interrupts                    |         |

| Parity Generator                                    |         |

|                                                     |         |

| Disabling the Transmitter                           |         |

| UART Data Receiver                                  |         |

| Introduction                                        |         |

| Receiving Frames with 5 to 8 Data Bits              |         |

| Code Example - UART Receive Function                | 19-0    |

| Receiving Frames                                    | 19-0    |

| with 9 Databits                                     | 19-0    |

| Code Examples - Receiving Frames with 9 Data Bits   | 19-7    |

| Receive Compete Flag and Interrupt                  |         |

| Receiver Error Flags                                |         |

| Parity Checker                                      |         |

| Disabling the Receiver                              |         |

| Flushing the                                        |         |

| Receive Buffer                                      |         |

| Code Example - Flushing the                         |         |

| 1 0                                                 |         |

| Receive Buffer                                      |         |

| Asynchronous Data Reception                         |         |

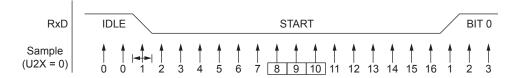

| Asynchronous Clock Recovery                         |         |

| Start Bit Sampling                                  |         |

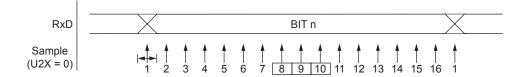

| Asynchronous Data Recovery                          | . 19-10 |

| Sampling of Data and Parity Bit                     | . 19-10 |

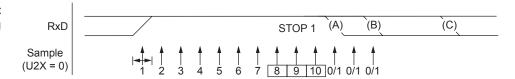

| Stop Bit Sampling and Next Start Bit Sampling       | . 19-10 |

| Asynchronous Operational Range                      | . 19-10 |

| Maximum Receiver Baud Rate Error                    |         |

| Multiprocessor Communication Mode                   | . 19-12 |

| Using MPCM                                          |         |

| Accessing UBRRH/UCSRC Registers                     |         |

| Write Access                                        |         |

| Code Example - Writing to the UBRRH/UCSRC Registers |         |

| Read AccessRead Access                              |         |

|                                                     |         |

| Code Example - Reading the UBRRH/UCSRC Registers    | . 17-13 |

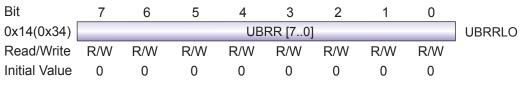

| UART Registers                  |                 | 19-14 |

|---------------------------------|-----------------|-------|

|                                 | Rate High)      |       |

| UBRRLO (UART Baud               | Rate Low)       | 19-14 |

| UCRB (UART Control Regis        | ster B)         |       |

|                                 | ister A)        |       |

|                                 | ))              |       |

|                                 | zister)         |       |

|                                 | ••••••          |       |

|                                 |                 |       |

|                                 |                 |       |

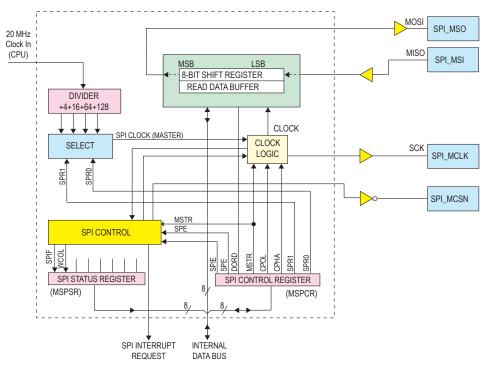

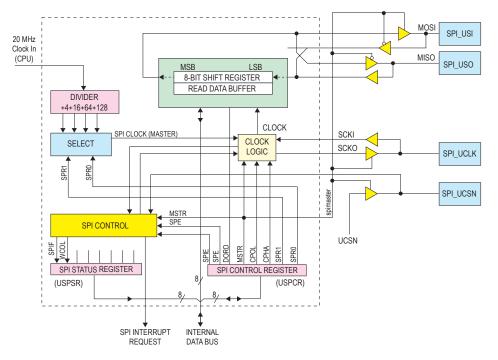

| Section 20: Serial Peripheral I | Interface (SPI) | 20-1  |

| _                               |                 |       |

|                                 |                 |       |

|                                 |                 |       |

|                                 | ity             |       |

|                                 |                 |       |

|                                 | SPI as a Master |       |

|                                 | SPI as a Slave  |       |

|                                 |                 |       |

|                                 | Register)       |       |

|                                 | Register)       |       |

|                                 | ol Register)    |       |

|                                 |                 |       |

|                                 | rister)         |       |

|                                 | vister)         |       |

|                                 | Register)       |       |

|                                 |                 |       |

|                                 | ality           |       |

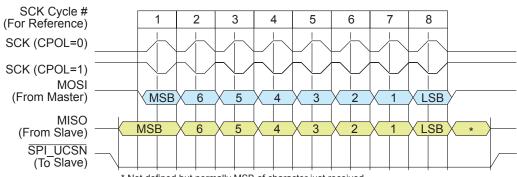

|                                 | PHA = 0         |       |

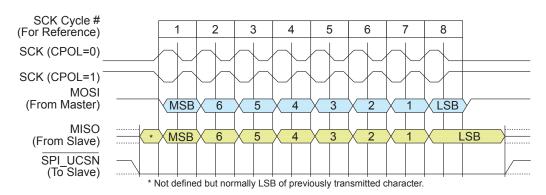

|                                 | PHA = 1         |       |

|                                 |                 |       |

## LIST OF FIGURES

| Figure 1.1: M3000 Motor & Motion Controller ASIC Block Diagram1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|