# PRELIMINARY DATA SHEET

# AGC AMPLIFIER

# UPC3211GR

### **FEATURES**

NE

• WIDE GAIN CONTROL RANGE: 55 dB (TYP)

- LOW DISTORTION: IM3 = 57 dBc (TYP) at POUT = -10 dBm IM2 = 44 dBc (TYP) at POUT = -10 dBm

- SUPPLY VOLTAGE: 9 V

- PACKAGED IN 20 PIN SSOP SUITABLE FOR HIGH-DENSITY SURFACE MOUNT

### DESCRIPTION

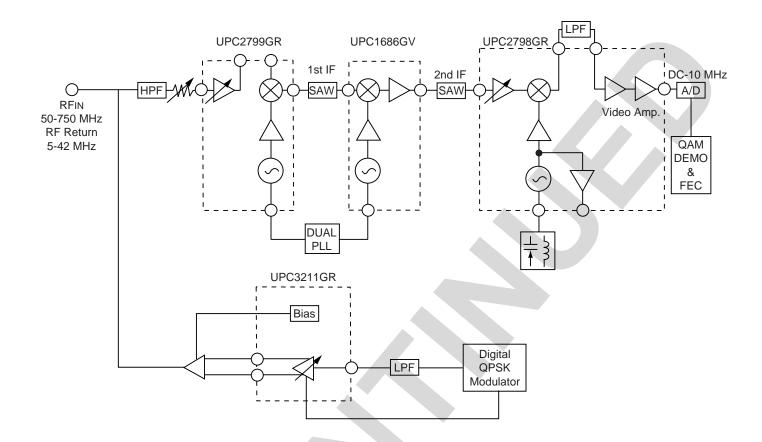

The UPC3211GR is a Silicon RFIC designed as an AGC amplifier for digital CATV return path applications. This IC consists of an AGC amplifier with 55 dB gain control range which is packaged in a 20 pin SSOP.

NEC's stringent quality assurance and test procedures ensure the highest reliability and performance.

### ELECTRICAL CHARACTERISTICS (TA = 25°C, Vcc = 9 V, VAGc = 0 V, VPs = 9 V, unless otherwise specified)

|            | PART NUMBER<br>PACKAGE OUTLINE                                                     |          |     | UPC3211GR<br>S20 |     |

|------------|------------------------------------------------------------------------------------|----------|-----|------------------|-----|

| SYMBOLS    | PARAMETERS AND CONDITIONS                                                          | UNITS    | MIN | TYP              | MAX |

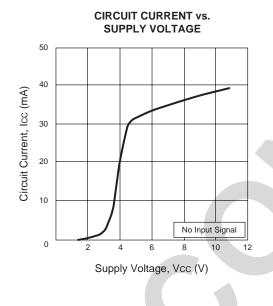

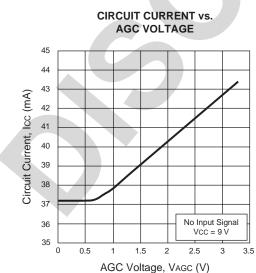

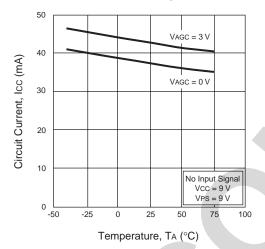

| Icc        | Circuit Current (no input signal), VAGC = 0 V<br>VAGC = 3 V                        | mA<br>mA | 29  | 38<br>43         | 51  |

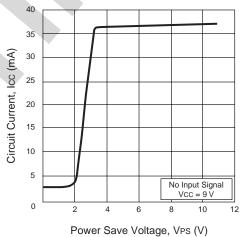

| ICC(PS)    | Circuit Current in Power Save Mode (no input signal), $V_{PS} = 0 V^1$             | mA       |     | 3                |     |

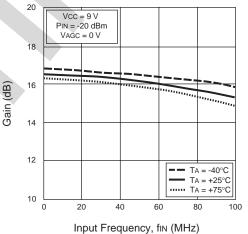

| GMAX       | Maximum Gain <sup>2</sup>                                                          | dB       | 14  | 16               | 18  |

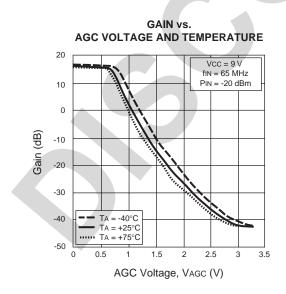

| GCR        | Gain Control Range <sup>2</sup> , VAGC = 0 to 3 V                                  | dB       | 47  | 55               |     |

| GFLAT      | Gain Flatness, fin = 5 to 100 MHz, 6 MHz Bandwidth                                 | dB       |     | ±0.1             |     |

| PSAT       | Saturated Output Power, PIN = -5 dBm                                               | dBm      |     | +5               |     |

| ISOL       | Isolation in Sleep Mode, VPs = 0 V <sup>1</sup>                                    | dB       | 60  | 65               |     |

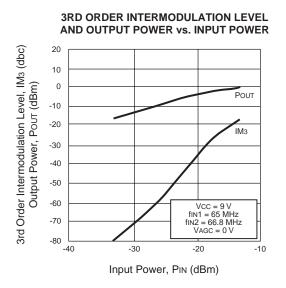

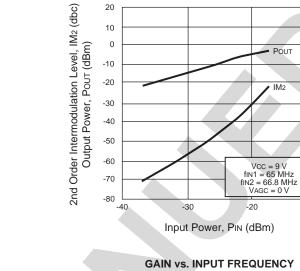

| IM2        | 2nd Order Intermodulation Level, fin1 = 65 MHz, fin2 = 66.8 MHz,<br>Pout = -10 dBm | dBc      |     | 44               | 40  |

| ІМз        | 3rd Order Intermodulation Level, fin1 = 65 MHz, fin2 = 66.8 MHz,<br>Pout = -10 dBm | dBc      |     | 57               | 50  |

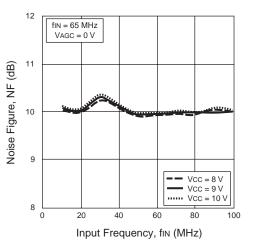

| NF         | Noise Figure, fin = 65 MHz                                                         | dB       |     | 10               |     |

| OIP3       | Output 3rd Order Intercept Point, fin1 = 65 MHz, fin2 = 66.8 MHz                   | dBm      |     | +16              |     |

| TPS (RISE) | Power Save Rise Time, VPS(OFF) $\rightarrow$ VPS(ON)                               | μs       |     | 200              |     |

| TPS (FALL) | Power Save Fall Time, VPS(ON) $\rightarrow$ VPS(OFF)                               | mS       |     | 1.7              |     |

Notes:

1. Bias VPs through a 5 k $\Omega$  Resistor.

2.  $f_{IN} = 65 \text{ MHz}$ ,  $P_{IN} = -20 \text{ dBm}$ .

# **California Eastern Laboratories**

| SYMBOLS  | PARAMETERS                      | UNITS | RATINGS     |  |  |

|----------|---------------------------------|-------|-------------|--|--|

| Vcc      | Supply Voltage                  | V     | 11.0        |  |  |

| Vps      | Power Save Voltage <sup>3</sup> | V     | 11.0        |  |  |

| VAGC     | AGC Control Voltage             | V     | 3.6         |  |  |

| PD       | Power Dissipation <sup>2</sup>  | mW    | 500         |  |  |

| TA       | Operating Ambient Temp.         | °C    | -40 to +75  |  |  |

| TSTG     | Storage Temp. Range             | °C    | -55 to +150 |  |  |

| PIN(MAX) | Maximum Input Level             | dBm   | +5          |  |  |

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup> (TA = 25°C)

#### Notes:

1. Operation in excess of any one of these conditions may result in permanent damage.

- 2. TA = 75°C Mounted on a 50x50x1.6 mm double epoxy glass board.

- 3. Bias VPs through 5 k  $\Omega$  resistor.

### RECOMMENDED OPERATING CONDITIONS

| SYMBOLS  | PARAMETERS              | UNITS | MIN | TYP | MAX  |

|----------|-------------------------|-------|-----|-----|------|

| Vcc      | Supply Voltage          | V     | 8.0 | 9.0 | 10.0 |

| Vps      | Power Save Voltage      | V     | 0   | -   | 10.0 |

| VAGC     | AGC Control Voltage     | V     | 0   | -   | 3.3  |

| TA       | Operating Ambient Temp. | °C    | -40 | +25 | +75  |

| fin      | Input Frequency         | MHz   | 5   | 7   | 100  |

| PIN(MAX) | Maximum Input Level     | dBm   | -   | -   | 0    |

# TYPICAL PERFORMANCE CURVES (TA = 25°C)

CIRCUIT CURRENT vs. POWER SAVE VOLTAGE

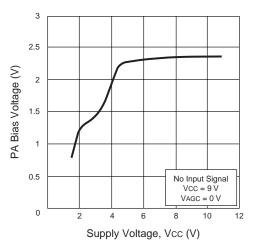

#### PA BIAS VOLTAGE vs. SUPPLY VOLTAGE

# TYPICAL PERFORMANCE CURVES (TA = 25°C)

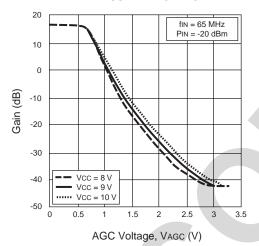

GAIN vs. AGC VOLTAGE AND SUPPLY VOLTAGE

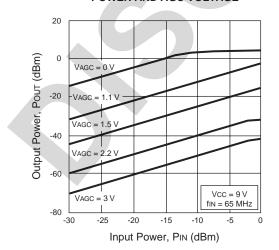

OUTPUT POWER vs. INPUT POWER AND AGC VOLTAGE

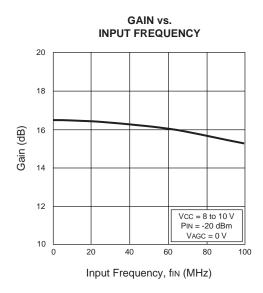

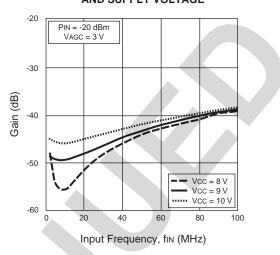

GAIN vs. INPUT FREQUENCY AND SUPPLY VOLTAGE

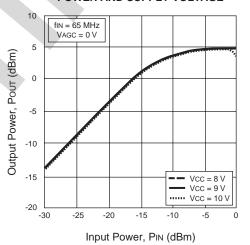

OUTPUT POWER vs. INPUT POWER AND SUPPLY VOLTAGE

NOISE FIGURE vs. INPUT FREQUENCY AND SUPPLY VOLTAGE

# STANDARD PERFORMANCE CURVES (TA = 25°C)

20

10

0

-10

AND TEMPERATURE

2ND ORDER INTERMODULATION LEVEL

AND OUTPUT POWER vs. INPUT POWER

POUT

IM<sub>2</sub>

-10

# STANDARD PERFORMANCE CURVES (TA = 25°C)

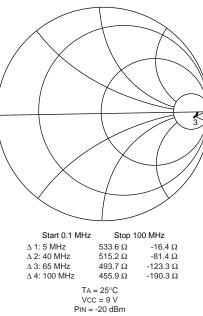

#### **INPUT IMPEDANCE (PIN 19)**

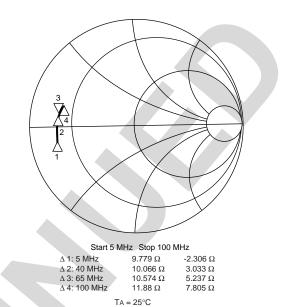

**OUTPUT IMPEDANCE (PIN 11)**

VCC = 9 VPIN = -20 dBm

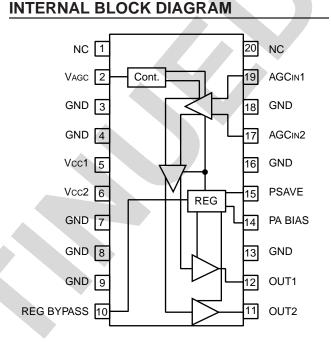

# **PIN FUNCTIONS**

| Pin No.     | Symbol     | Pin<br>Voltage<br>(V) | Description                                                                                                                                                                                                                                                                                               | Equivalent Circuit                    |

|-------------|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 1           | NC         | -                     | No connection. This pin should be left open.                                                                                                                                                                                                                                                              |                                       |

| 2           | VAGC       | 0 to 3                | Automatic gain control pin. VAGC Up = Gain Down.                                                                                                                                                                                                                                                          |                                       |

| 3<br>4      | GND        | 0                     | Differential amp ground pins. These pins must be<br>connected to system ground. Form ground<br>pattern as wide as possible to minimize ground<br>impedance.                                                                                                                                               |                                       |

| 5           | Vcc1       | 9.0                   | Supply voltage pin for the AGC amp. This pin<br>should be connected with a bypass capacitor to<br>minimize ground impedance.                                                                                                                                                                              |                                       |

| 6           | Vcc2       | 9.0                   | Supply voltage pin for the differential amp and output block. This pin should be connected with a bypass capacitor to minimize ground impedance.                                                                                                                                                          |                                       |

| 7<br>8<br>9 | GND        | 0                     | Differential amp ground pins. These pins must be<br>connected to system ground. Form ground pattern<br>as wide as possible to minimize ground<br>impedance.                                                                                                                                               |                                       |

| 10          | REG BYPASS | 1.64                  | Bypass pin of regulator block. This pin should be bypassed to ground through a capacitor.                                                                                                                                                                                                                 |                                       |

| 11          | OUT2       | 6.9                   | Signal output pins. These are emitter-follower outputs, which feature low impedance. In case of                                                                                                                                                                                                           |                                       |

| 12          | OUT1       | 6.9                   | single-ended output, the unused pin should be connected to ground through a load resistor.                                                                                                                                                                                                                |                                       |

| 13          | GND        | 0                     | Output block ground pin. This pin must be<br>connected to system ground. Form ground<br>pattern as wide as possible to minimize ground<br>impedance.                                                                                                                                                      |                                       |

| 14          | PA_BIAS    | 2.45                  | This pin provides the base bias voltage to transis-<br>tors configured as a power amplifier.                                                                                                                                                                                                              |                                       |

| 15          | VPS        | 9.0                   | $\begin{array}{c c} \mbox{Power save control pin can control the On/Sleep} \\ \mbox{state with bias as follows:} \\ \hline \hline $V_{PS}\left(V\right)$ STATE \\ \hline $3-9$ ON \\ \hline $0-2$ SLEEP \\ \hline $1$ is recommended to use a 5 k\Omega in series with this pin. \\ \hline \end{tabular}$ | VPS<br>5 kΩ<br>15-W-<br>14<br>14<br>π |

| 16<br>18    | GND        | 0                     | AGC amp ground pin. This pin must be connected<br>to system ground. Form ground pattern as wide as<br>possible to minimize ground impedance.                                                                                                                                                              |                                       |

| 17          | AGCIN2     | 2.43                  | Signal input pins. In the case of single-ended input, bypass the unused pin to ground through a capacitor.                                                                                                                                                                                                | 5                                     |

| 19          | AGCIN1     | 2.43                  |                                                                                                                                                                                                                                                                                                           |                                       |

| 20          | NC         | _                     | No connection. This pin should be left open.                                                                                                                                                                                                                                                              |                                       |

## **TYPICAL APPLICATION**

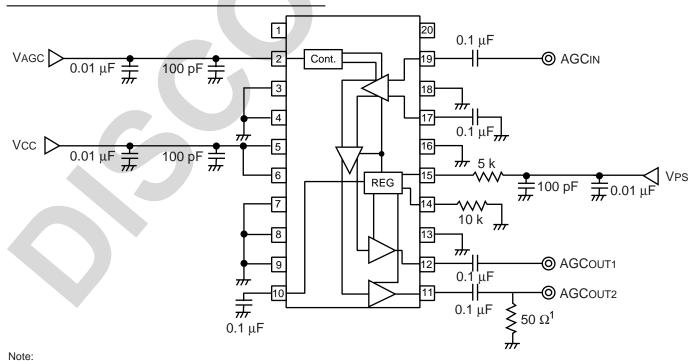

### **MEASUREMENT CIRCUIT**

1. The pin that is not connected to the 50  $\Omega$  test system should be grounded through a 50  $\Omega$  resistor.

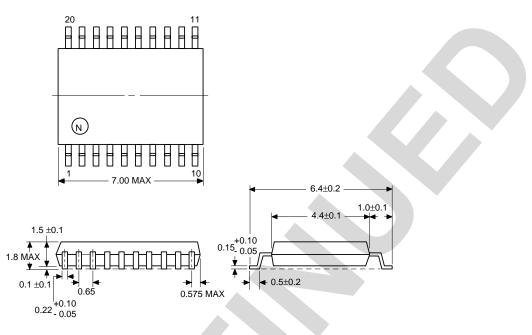

## PACKAGE DIMENSIONS (Units in mm)

PACKAGE OUTLINE S20

Note:

1. All dimensions are typical unless otherwise specified.

### **ORDERING INFORMATION**

| PART NUMBER  | QUANTITY   |  |

|--------------|------------|--|

| UPC3211GR-E1 | 2.5 k/Reel |  |

Notes:

Embossed tape, 12 mm wide. Pin 1 indicates pull-out direction of tape.