# ConnectCore<sup>™</sup> 9P 9215 and Wi-9P 9215 Hardware Reference

90000879\_F

Release date: March 2009

©2008 Digi International Inc.

All rights reserved.

Digi, Digi International, the Digi logo, a Digi International Company, Digi JumpStart Kit, ConnectCore, NET+, NET+OS and NET+Works are trademarks or registered trademarks of Digi International, Inc. in the United States and other countries worldwide. All other trademarks are the property of their respective owners.

Information in this document is subject to change without notice and does not represent a commitment on the part of Digi International.

Digi provides this document "as is," without warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of fitness or merchantability for a particular purpose. Digi may make improvements and/or changes in this manual or in the product(s) and/or the program(s) described in this manual at any time.

This product could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes may be incorporated in new editions of the publication.

# **Contents**

| Customer support                 | 9  |

|----------------------------------|----|

| Chapter 1: About the Module      | 11 |

| Features and functionality       | 12 |

| Module variant                   | 12 |

| Module pinout                    | 13 |

| Pinout legend: Type              | 13 |

| X1 pinout                        | 13 |

| X2 pinout                        | 17 |

| Configuration pins — CPU         | 25 |

| Default module CPU configuration | 25 |

| Configuration pins — Module      | 26 |

| Identification of the module     | 26 |

| Module pin configuration         | 26 |

| Clock generation                 | 27 |

| Clock frequencies                | 27 |

| Changing the CPU speed           | 28 |

| Boot process                     | 28 |

| Chip selects                     | 29 |

| Chip select memory map           | 29 |

| SDRAM banks                      | 29 |

| Multiplayed CDIO pips            | 20 |

| GPIO multiplex table30                 |

|----------------------------------------|

| Module LEDs34                          |

| Description35                          |

| ConnectCore Wi-9P default use35        |

| External interrupts35                  |

| Interfaces36                           |

| 10/100 Mbps Ethernet port              |

| UART36                                 |

| SPI                                    |

| 12C bus                                |

| RTC37                                  |

| WLAN                                   |

| ADC37                                  |

| FIM37                                  |

| External Address/Data Bus37            |

| WLAN                                   |

| Antenna                                |

| Power                                  |

| Power supply38                         |

| Internal voltage                       |

| Chapter 2: About the Development Board |

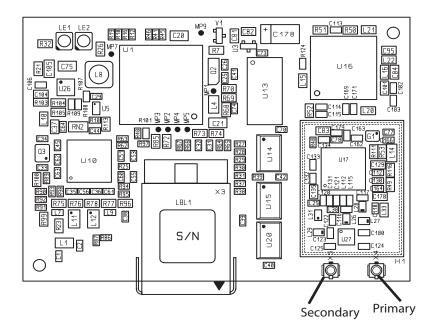

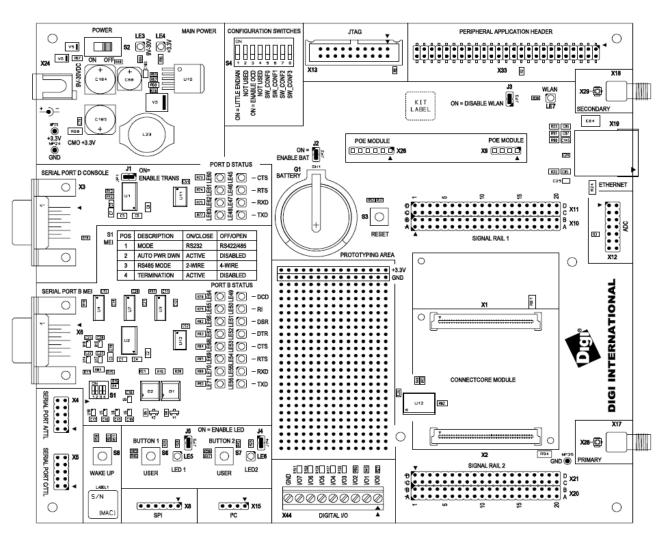

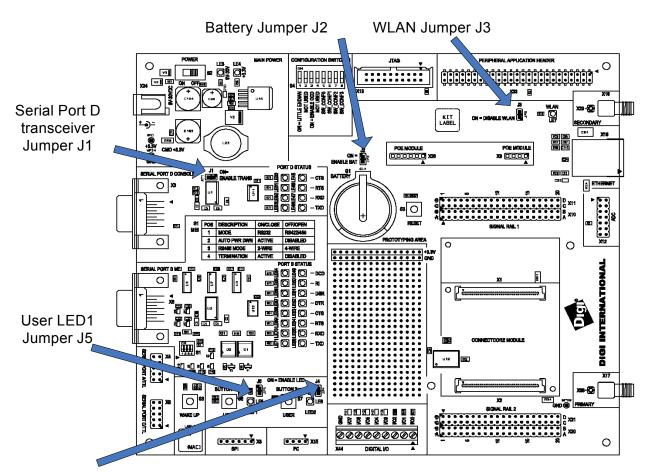

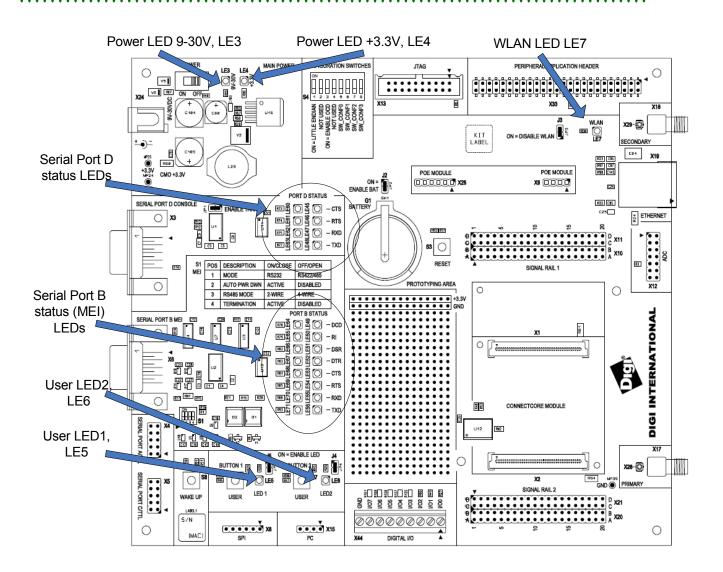

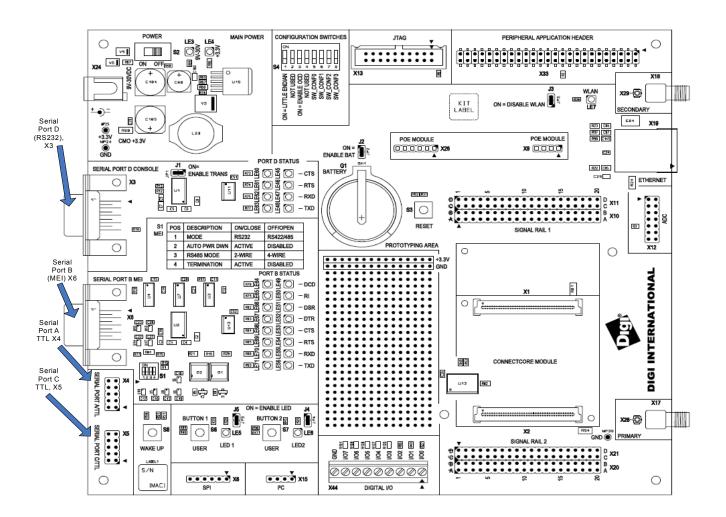

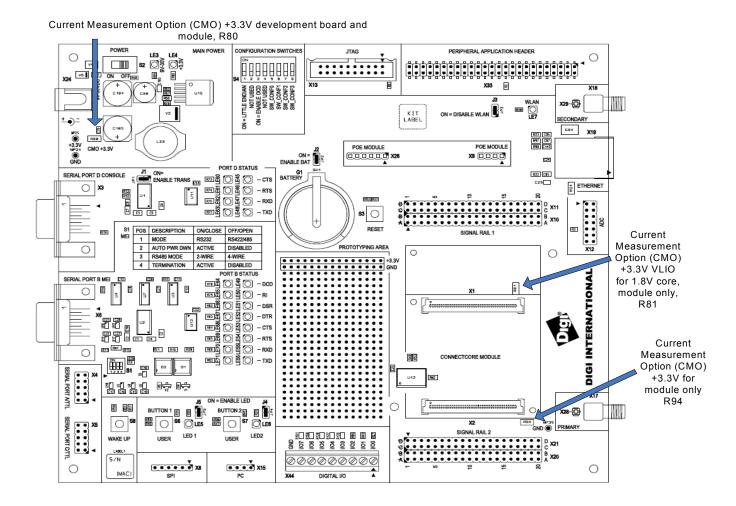

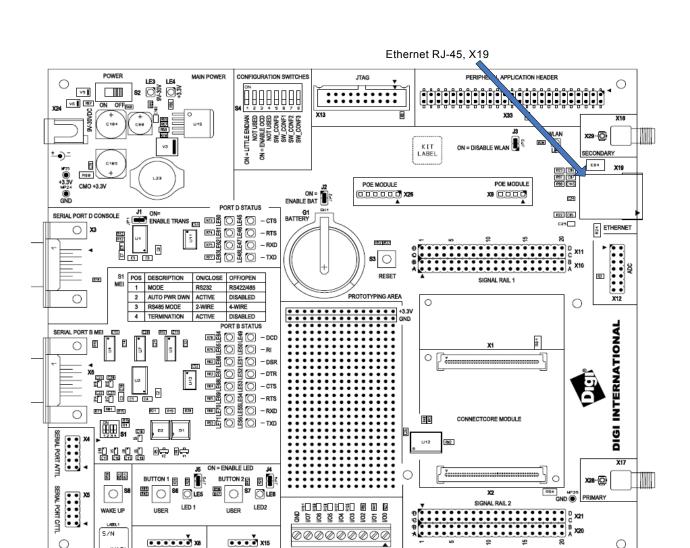

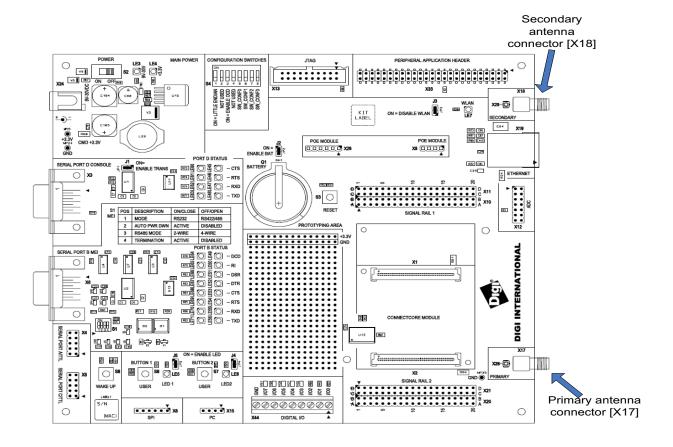

| What's on the development board?39     |

| The development board40                |

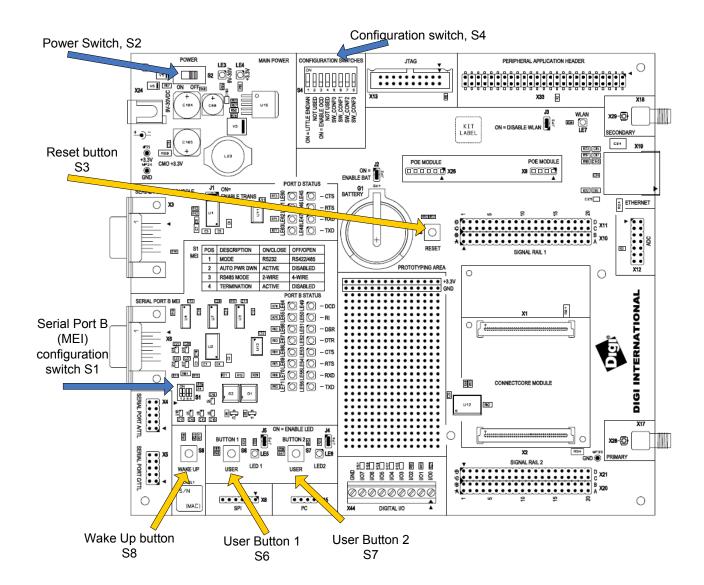

| User interface41                       |

| General information41                  |

| Antenna switch                               | 41 |

|----------------------------------------------|----|

| Switches and pushbuttons                     | 42 |

| Reset control, S3                            | 42 |

| Power switch, S2                             | 42 |

| User pushbuttons, S6 and S7                  | 43 |

| Legend for multi-pin switches                | 43 |

| Module configuration switches, S4            | 43 |

| Wake-up button, S8                           | 43 |

| Serial Port B MEI configuration switches, S1 | 43 |

| Jumpers                                      | 45 |

| Jumper functions                             | 45 |

| Battery and Battery Holder                   | 46 |

| LEDs                                         | 47 |

| WLAN LED LE7                                 | 47 |

| Power LEDs, LE3 and LE4                      | 47 |

| User LEDs, LE5 and LE6                       | 47 |

| Serial status LEDs                           | 48 |

| Status LEDs Serial Port D LEDs               | 48 |

| Status LEDs Serial Port B LEDs               | 48 |

| Serial UART ports                            | 49 |

| Serial port D, RS232                         | 49 |

| Serial port A TTL interface                  | 50 |

| Serial port C TTL interface                  | 50 |

| Serial port B, MEI interface                 | 51 |

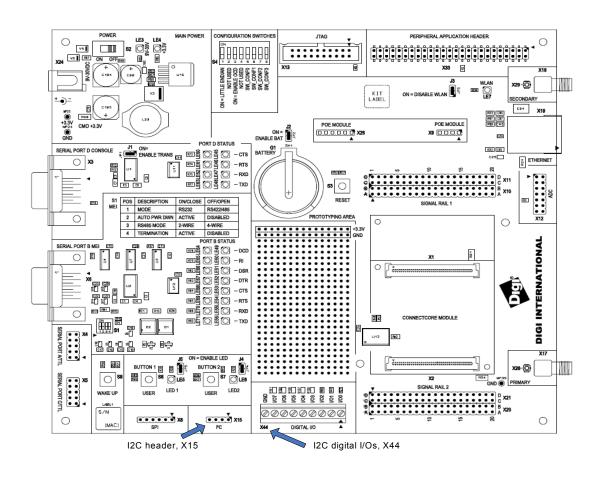

| I2C interface                                |    |

| I <sup>2</sup> C header                      | 53 |

| I2C digital I/O expansion           | 53 |

|-------------------------------------|----|

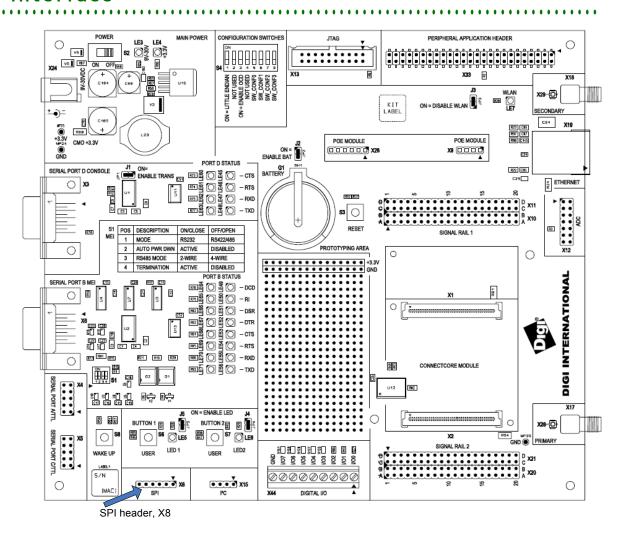

| SPI interface                       | 54 |

| Pin allocation                      | 55 |

| Current Measurement Option          | 55 |

| How the CMO works                   | 56 |

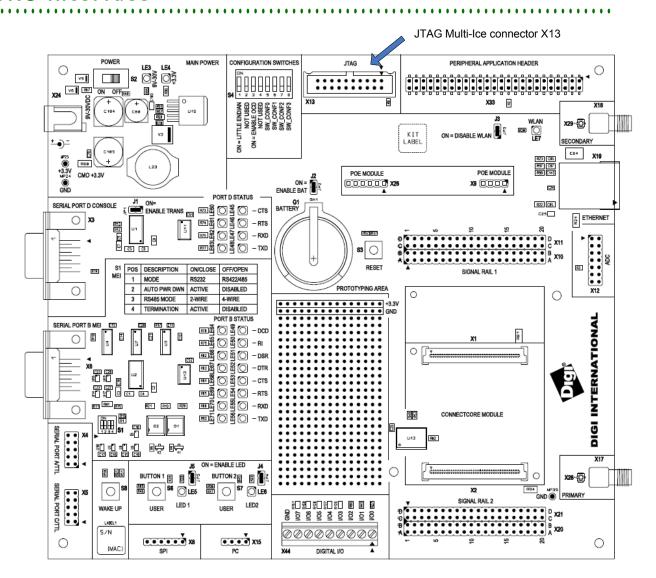

| JTAG interface                      | 57 |

| Standard JTAG ARM connector, X13    | 57 |

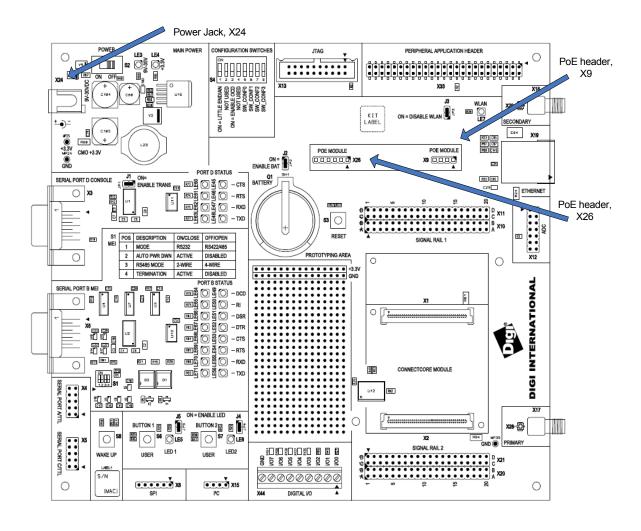

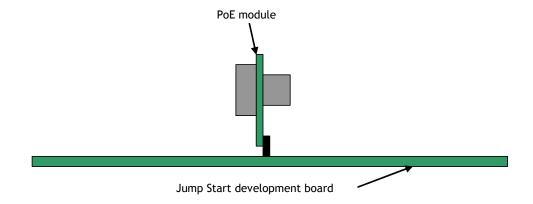

| PoE module connectors - IEEE802.3af | 58 |

| The PoE module                      | 59 |

| X9                                  | 60 |

| X26                                 | 60 |

| POE_GND                             | 60 |

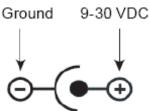

| Power Jack, X24                     | 60 |

| Ethernet interface                  | 60 |

| RJ-45 pin allocation, X19           | 61 |

| LEDs                                | 62 |

| WLAN interface                      | 62 |

| Peripheral (expansion) headers      | 63 |

| Peripheral application header, X33  | 63 |

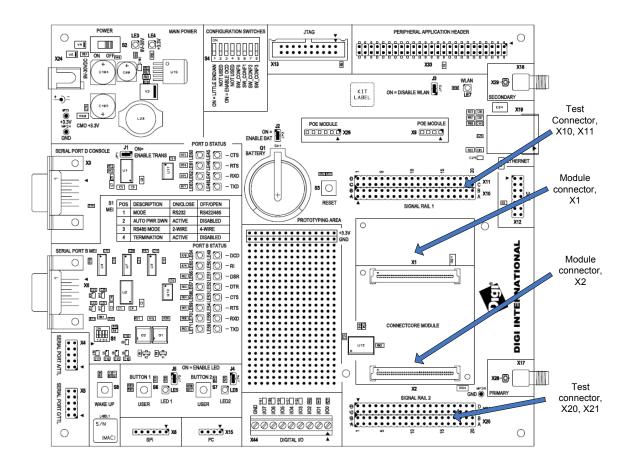

| Module and test connectors          | 64 |

| Module connectors                   | 65 |

| Test connectors                     | 65 |

| X10 pinout                          | 66 |

| X11 pinout                          | 66 |

| X20 pinout                          | 67 |

| X21 pinout                          | 68 |

| Appendix A:Specifications69                        |

|----------------------------------------------------|

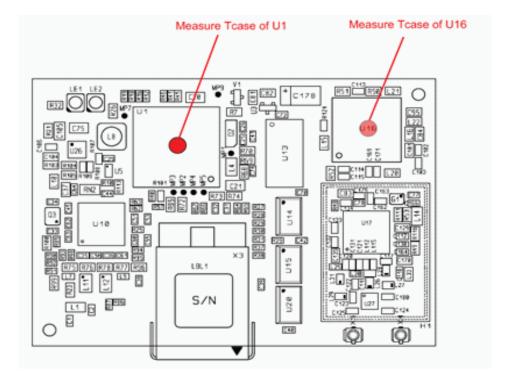

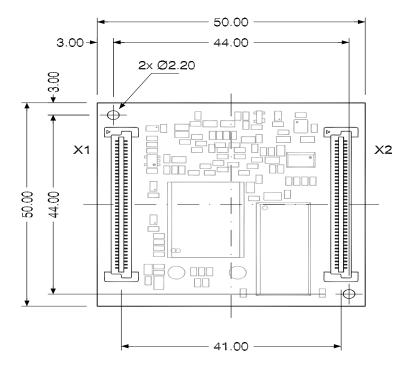

| Mechanical information                             |

| Network interface                                  |

| Ethernet                                           |

| WLAN                                               |

| Environmental information                          |

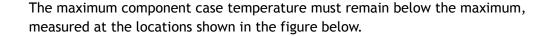

| Thermal specifications                             |

| Additional design recommendations                  |

| Safety statements                                  |

| Power requirements                                 |

| IEEE802.11 a/b/g WLAN                              |

| Typical module current / power measurements        |

| Typical power save current / power measurements    |

| ConnectCore 9P 9215 Module77                       |

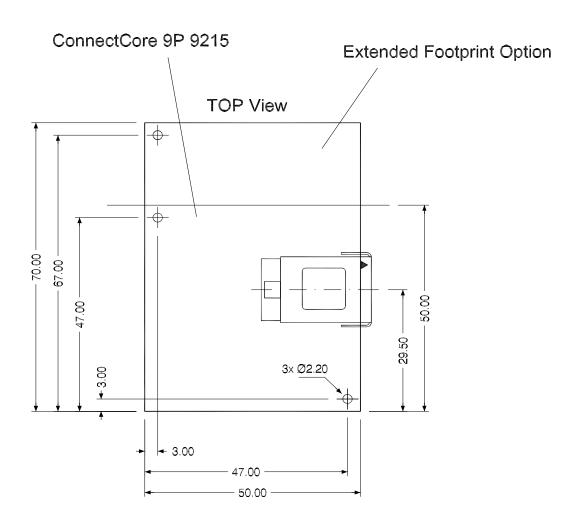

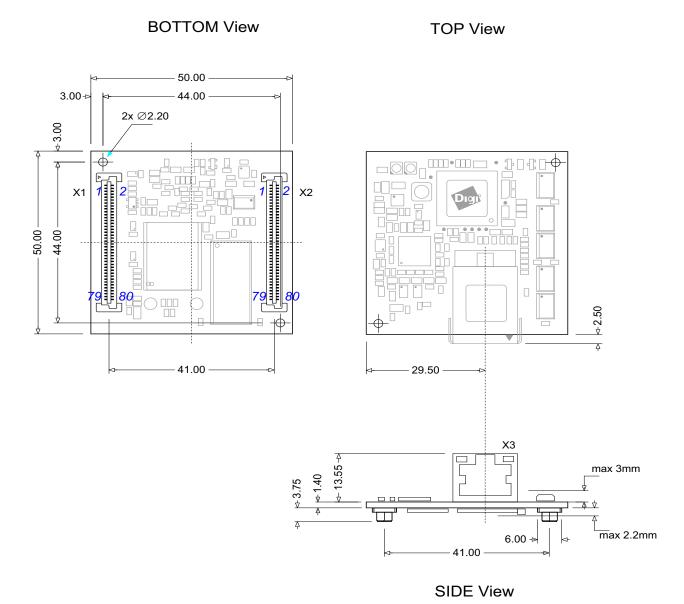

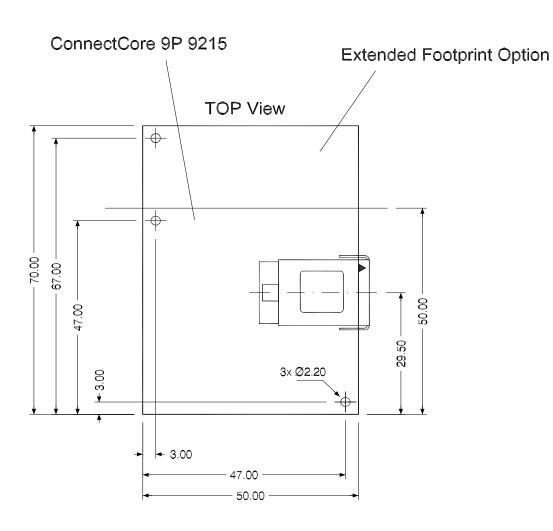

| Top view                                           |

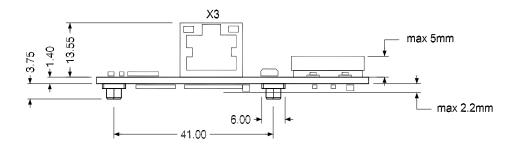

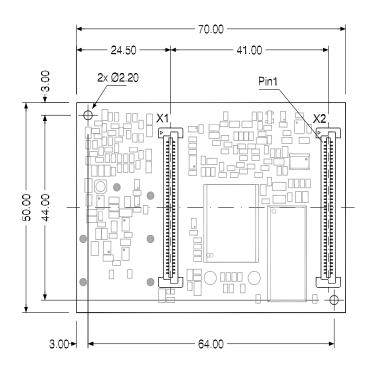

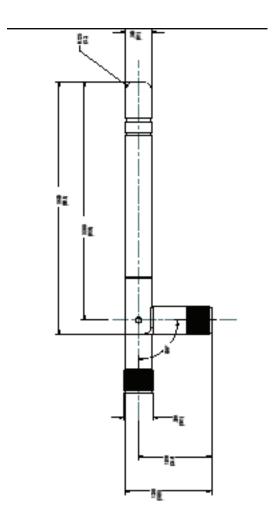

| Module, side view                                  |

| ConnectCore Wi-9P 9215 Module                      |

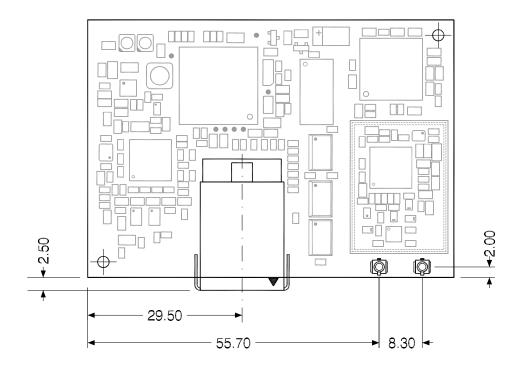

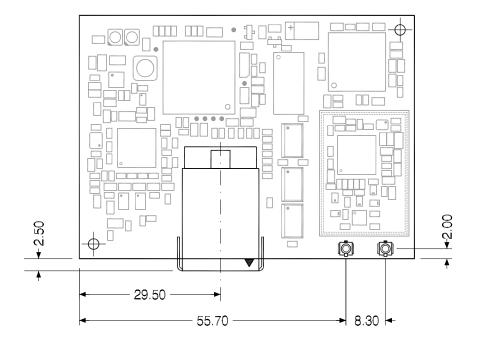

| Module, top view                                   |

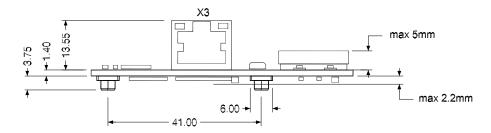

| Module, side view                                  |

| Layout recommendation                              |

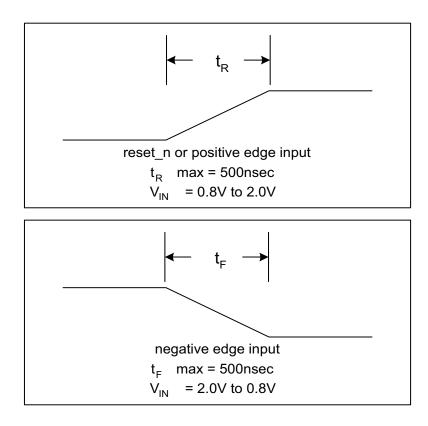

| Reset and edge sensitive input timing requirements |

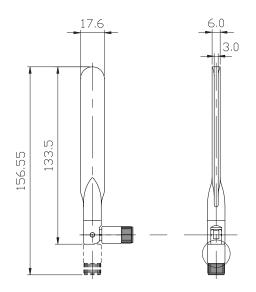

| Antenna specifications: 2 dBi Dipole               |

| Attributes                                         |

| Dimensions                                         |

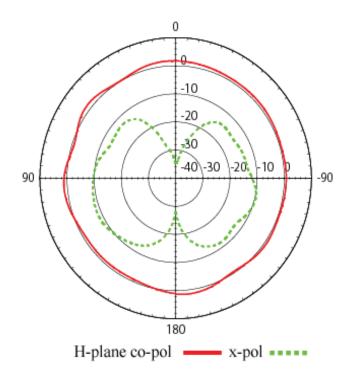

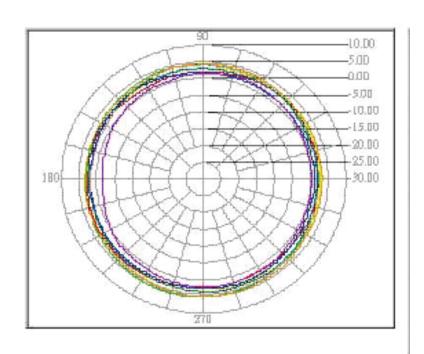

| Antenna strength (radiation pattern) diagram       |

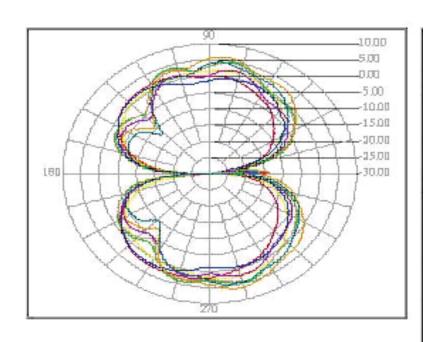

| Antenna specifications: 5.5 dBi Dipoles            |

| . 88<br>. 88<br>. 89 |

|----------------------|

|                      |

| 89                   |

|                      |

| 91                   |

| .91                  |

| 97                   |

| .97                  |

| .97                  |

| .97                  |

| .98                  |

| .98                  |

|                      |

This guide provides information about the Digi ConnectCore 9P 9215 embedded core module.

# Conventions used in this guide

This table describes the typographic conventions used in this guide:

| This convention Is used for |                                                      |

|-----------------------------|------------------------------------------------------|

| italic type                 | Emphasis, new terms, variables, and document titles. |

| monospaced type             | Filenames, pathnames, and code examples.             |

#### Digi information

## Related documentation

For additional documentation, see the Documentation folder under the Digi JumpStart kit Start menu tab.

# Documentation updates

Be aware that if you see differences between the documentation you received in your package and the documentation on the web site, the web site content is the latest version.

#### **Customer support**

To get help with a question or technical problem with this product, or to make comments and recommendations about our products or documentation, use the following contact information:

| To contact Digi International by | Use                        |

|----------------------------------|----------------------------|

| United States telephone:         | 1 877 912 3444             |

| International telephone:         | 1 952 912 3444             |

| Address:                         | Digi International         |

|                                  | 11001 Bren Road East       |

|                                  | Minnetonka, MN 55343 U.S.A |

| Web site:                        | www.digiembedded.com       |

# About the Module

$C\quad H\quad A\quad P\quad T\quad E\quad R\qquad \quad 1$

The ConnectCore 9P 9215 family of modules delivers powerful network-enabled core processor solutions with up to 16 MB of NOR flash, up to 32 MB SDRAM, a rich set of integrated peripherals, and superior design flexibility.

At the heart of the modules is a Digi 32-bit ARM9-based NS9215 processor running at 150 MHz. Key features include 10/100 Mbit Ethernet, two on-chip Flexible Interface Modules (FIMs), 256-bit AES accelerator, power management modes with dynamic clock scaling, and a rich set of on-chip peripherals. Based on Digi 802.11 baseband technology, the ConnectCore Wi-9P 9215 also provides an additional 802.11a/b/g interface with enterprise-grade WPA2/802.11i support.

The unique FIMs on the NS9215 processor are two independent 300 MHz DRPIC165X processor cores that allow customers to dynamically select application-specific interfaces in software. The growing list of supported interfaces includes UART, SD/SDIO, CAN bus, USB-device low-speed, 1-Wire®, USB device low-speed, parallel bus interface, and others.

Utilizing the Digi NET+ARM processor and secure 802.11a/b/g WLAN technology, the family of ConnectCore 9P 9215 modules offers the industry's only network-enabled core module with true long-term product availability to meet the extended life cycle requirements of embedded product designs.

For further information about the NS9215, see the NS9215 Hardware Reference.

### Features and functionality

- 32-bit NET+ARM (ARM926EJ-S) RISC processor NS9215 @ 150MHz

- ARM9 core with memory management unit (MMU)

- 4K data cache/4K instruction cache

- 8MB SDRAM (can support a maximum of 64MB SDRAM)

- 4MB NOR Flash (can support a maximum of 16MB NOR flash)

- 10 general purpose timers; ConnectCore 9P 9215 supports 7 as timer/counters and one quadrature decoder

- 64 GPIOs signals with up to five different multiplexing schemes (all are on connector X2)

- Two 80-pin connectors

- Up to four UARTs

- One SPI channel, multiplexed on different places

- Integrated 10/100Mbps Ethernet MAC/PHY

- Integrated IEEE802.11a/b/g WLAN with U.FL connectors on module (ConnectCore Wi-9P 9215 specific)

- I<sup>2</sup>C interface

- JTAG signals available on module connector

- 8 ADC (analog to digital converter) inputs

- 2x flexible interface modules (FIMs) running at max. 300 MHz, integrated in NS9215 processor

- 2 LEDs (LE1: green, and LE2:orange) available on module

- 16-bit data and 17-bit address buses, both are buffered

- Single +3.3V power supply

#### Module variant

The ConnectCore 9P 9215 module is currently available in standard variants below.

| Product numbers: | Features                                                                                                                               |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| CC-9P-V502-C     | $150\mathrm{MHz}\mathrm{CPU}$ speed, $8\mathrm{MB}\mathrm{SDRAM}, 4\mathrm{MB}\mathrm{NOR}$ flash, RTC, $10/100\mathrm{Mbps}$ Ethernet |

| CC-9P-V501-C     | 150 MHz CPU speed, 8MB SDRAM, 2MB NOR flash, RTC, 10/100 Mbps Ethernet                                                                 |

Please visit the Digi website or contact us for additional population options.

.

### Module pinout

The module has two 80 pins connectors, X1 and X2. The next tables describe each pin, its properties, and its use on the development board.

#### Pinout legend:

Type

I Input

O Output

I/O Input or output

P Power

#### X1 pinout

| X1 pin<br>number | Type | Module functionality         | Usage on<br>Development board | Comments                                                                             |

|------------------|------|------------------------------|-------------------------------|--------------------------------------------------------------------------------------|

| 1                | P    | GND                          | GND                           |                                                                                      |

| 2                | P    | GND                          | GND                           |                                                                                      |

| 3                | I    | RSTIN#                       | RSTIN#                        | 10k pull-up on module                                                                |

| 4                | 0    | PWRGOOD                      | PWRGOOD                       | Output of the reset controller push pull with 470R current limiting resistor         |

| 5                | O    | RSTOUT#                      | RSTOUT#                       | Output of logical AND function<br>between NS9215 RESET_DONE<br>and NS9215 RESET_OUT# |

| 6                | I    | TCK                          | TCK                           | JTAG - 10k pull-up on module                                                         |

| 7                | I    | TMS                          | TMS                           | JTAG - 10k pull-up on module                                                         |

| 8                | I    | TDI                          | TDI                           | JTAG - 10k pull-up on module                                                         |

| 9                | O    | TDO                          | TDO                           | JTAG - 10k pull-up on module                                                         |

| 10               | I    | TRST#                        | TRST#                         | JTAG - 2k2 pull-down on module                                                       |

| 11               | О    | RTCK                         | RTCK                          | JTAG - Optional                                                                      |

| 12               | I    | CONF2/OCD_EN#                | CONF2/OCD_EN#                 | 10k pull-up on module                                                                |

| 13               | I    | LITTLE# / BIG<br>ENDIAN      | LITTLE# / BIG<br>ENDIAN       | 2k2 series resistor on module                                                        |

| 14               | I    | WLAN_LED#<br>(CC Wi-9P 9215) | WLAN_LED#<br>(CC Wi-9P 9215)  | Low active WLAN Disable signal                                                       |

| 15               | I    | SOFT_CONF0                   | SOFT_CONF0                    | 2k2 series resistor on module                                                        |

| 16               | I    | SOFT_CONF1                   | SOFT_CONF1                    | 2k2 series resistor on module                                                        |

| 17               | I    | SOFT_CONF2                   | SOFT_CONF2                    | 2k2 series resistor on module                                                        |

| X1 pin<br>number | Type | Module functionality    | Usage on<br>Development board | Comments                                                                                                                      |

|------------------|------|-------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 18               | I    | SOFT_CONF3              | SOFT_CONF3                    | 2k2 series resistor on module                                                                                                 |

| 19               | 0    | Reserved<br>(WLAN_LED#) | Reserved<br>(WLAN_LED#)       | Active low signal coming from low-active WLAN signal. This signal comes directly from the Piper chip without series resistor. |

| 20               | P    | GND                     | GND                           |                                                                                                                               |

| 21               | I/O  | D0                      | D0                            | Buffered Data - only active when either CS0# or CS2# is active NS9215 D[31:16]                                                |

| 22               | I/O  | D1                      | D1                            |                                                                                                                               |

| 23               | I/O  | D2                      | D2                            |                                                                                                                               |

| 24               | I/O  | D3                      | D3                            |                                                                                                                               |

| 25               | I/O  | D4                      | D4                            |                                                                                                                               |

| 26               | I/O  | D5                      | D5                            |                                                                                                                               |

| 27               | I/O  | D6                      | D6                            |                                                                                                                               |

| 28               | I/O  | D7                      | D7                            |                                                                                                                               |

| 29               | I/O  | D8                      | D8                            |                                                                                                                               |

| 30               | I/O  | D9                      | D9                            |                                                                                                                               |

| 31               | I/O  | D10                     | D10                           |                                                                                                                               |

| 32               | I/O  | D11                     | D11                           |                                                                                                                               |

| 33               | I/O  | D12                     | D12                           |                                                                                                                               |

| 34               | I/O  | D13                     | D13                           |                                                                                                                               |

| 35               | I/O  | D14                     | D14                           |                                                                                                                               |

| 36               | I/O  | D15                     | D15                           |                                                                                                                               |

| 37               | P    | GND                     | GND                           |                                                                                                                               |

| 38               | О    | AO                      | AO                            | Buffered Address always active                                                                                                |

| 39               | О    | A1                      | A1                            |                                                                                                                               |

| 40               | О    | A2                      | A2                            |                                                                                                                               |

| 41               | О    | A3                      | A3                            |                                                                                                                               |

| 42               | О    | A4                      | A4                            |                                                                                                                               |

| 43               | О    | A5                      | A5                            |                                                                                                                               |

| 44               | О    | A6                      | A6                            |                                                                                                                               |

| 45               | О    | A7                      | A7                            |                                                                                                                               |

| 46               | О    | A8                      | A8                            |                                                                                                                               |

| X1 pin<br>number | Type | Module functionality     | Usage on<br>Development board | Comments                                             |

|------------------|------|--------------------------|-------------------------------|------------------------------------------------------|

| 47               | O    | A9                       | A9                            |                                                      |

| 48               | О    | A10                      | A10                           |                                                      |

| 49               | О    | A11                      | A11                           |                                                      |

| 50               | O    | A12                      | A12                           |                                                      |

| 51               | O    | A13                      | A13                           |                                                      |

| 52               | O    | A14                      | A14                           |                                                      |

| 53               | O    | A15                      | A15                           |                                                      |

| 54               | O    | A16                      | A16                           |                                                      |

| 55               | O    | GND                      | GND                           |                                                      |

| 56               | O    | EXT_OE#                  | EXT_OE#                       |                                                      |

| 57               | O    | EXT_WE#                  | EXT_WE#                       |                                                      |

| 58               | О    | CSO#                     | CSO#                          |                                                      |

| 59               | О    | CS2#                     | CS2#                          |                                                      |

| 60               | О    | BLE#                     | BLE#                          | NS9215 BE2#                                          |

| 61               | О    | BHE#                     | BHE#                          | NS9215 BE3#                                          |

| 62               | I    | EXT_WAIT#                | EXT_WAIT#                     | 10k pull-up on module                                |

| 63               | О    | BCLK                     | BCLK                          | Connected over a 22R resistor to NS9215 CLK_OUT1 pin |

| 64               | P    | GND                      | GND                           |                                                      |

| 65               | I    | ETH_TPIN                 | ETH_TPIN                      |                                                      |

| 66               | О    | ETH_ACTIVITY#            | ETH_ACTIVITY#                 | Low active signal with 330R resistor on module       |

| 67               | I    | ETH_TPIP                 | ETH_TPIP                      |                                                      |

| 68               | О    | ETH_LINK#                | ETH_LINK                      | Low active signal with 330R resistor on module       |

| 69               | О    | ETH_TPON                 | ETH_TPON                      |                                                      |

| 70               | О    | ETH_TROP                 | ETH_TROP                      |                                                      |

| 71               | P    | GND                      | GND                           |                                                      |

| 72               | P    | Reserved (USB_VBUS)      | Reserved (USB_VBUS)           |                                                      |

| 73               | I    | Reserved (USB_OC#)       | Reserved (USB_OC#)            |                                                      |

| 74               | I/O  | Reserved (USB_P)         | Reserved (USB_P)              |                                                      |

| 75               | I/O  | Reserved (USB_N)         | Reserved (USB_N)              |                                                      |

| 76               | О    | Reserved<br>(USB_PWREN#) | Reserved<br>(USB_PWREN#)      |                                                      |

| X1 pin<br>number | Type | Module functionality     | Usage on<br>Development board | Comments                                         |

|------------------|------|--------------------------|-------------------------------|--------------------------------------------------|

| 77               | I    | Reserved<br>(USB_OTG_ID) | Reserved<br>(USB_OTG_ID)      |                                                  |

| 78               | P    | VRTC                     | VRTC                          | Backup Battery for RTC, for 3V cell.             |

|                  |      |                          |                               | Can be left floating, if RTC backup not needed.  |

| 79               | P    | VLIO                     | VLIO                          | Mobile: Power from Li-Ion<br>Battery (2.5V-5.5V) |

|                  |      |                          |                               | Non-Mobile: connected to 3.3V                    |

| 80               | P    | GND                      | GND                           |                                                  |

### X2 pinout

| X2 pin<br>number | Type | Module functionality                                       | Usage on<br>Development board | Comments |

|------------------|------|------------------------------------------------------------|-------------------------------|----------|

| 1                | P    | GND                                                        |                               |          |

| 2                | P    | GND                                                        |                               |          |

| 3                | I/O  | DCDA#/ DMA0_DONE/ PIC_0_GEN_IO[0] GPIO0/ SPI_EN (dup)      |                               |          |

| 4                | I/O  | CTSA#/ EIRQ0/ PIC_0_GEN_IO[1] GPIO1/ -reserved-            |                               |          |

| 5                | I/O  | DSRA#/ EIRQ1/ PIC_0_GEN_IO[2] GPIO2/ -reserved-            |                               |          |

| 6                | I/O  | RXDA/ DMA0_PDEN/ PIC_0_GEN_IO[3] GPIO3/ SPI_RX (dup)       |                               |          |

| 7                | I/O  | RIA#/ EIRQ2/ Timer6_in/ GPIO4 SPI_CLK (dup)/               |                               |          |

| 8                | I/O  | RTSA#/ RS485CTLA EIRQ3/ Timer6_Out/ GPIO5/ SPI_CLK (dup)/  |                               |          |

| 9                | I/O  | DTRA#/TXCLKA  DMA0_REQ/ Timer7_In/ GPIO6/ PIC_DBG_DATA_OUT |                               |          |

| X2 pin<br>number | Type | Module functionality                                         | Usage on<br>Development board | Comments                                                                                                                                                        |

|------------------|------|--------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10               | I/O  | TXDA/ Timer8_In/ Timer7_Out/ GPIO7/ SPI_TX (dup)             |                               |                                                                                                                                                                 |

| 11               | I/O  | DCDC#/ DMA1_DONE/ Timer8_Out/ GPIO8/ SPIB_EN (dup)/          |                               |                                                                                                                                                                 |

| 12               | I/O  | CTSC#/ I2C_SCK/ EIRQ0 (dup)/ GPIO9/ PIC_DBG_DATA_IN          |                               |                                                                                                                                                                 |

| 13               | I/O  | DSRC#/ QDCI/ EIRQ1 (dup) GPIO10/ PIC_DBG_CLK                 |                               |                                                                                                                                                                 |

| 14               | I/O  | RXDC/ DMA1_DP/ EIRQ2 (dup)/ GPIO11/ SPI_RXboot               |                               |                                                                                                                                                                 |

| 15               | I/O  | RIC#/ RXCLKC I2C_SDA/ RST_DONE/ GPIO12/ SPI_CLK (dup)        |                               | When booting, NS9215 RIC# signal is default configured as Output, RST_DONE. To avoid input/output conflicts, put a series resistor on this signal if necessary. |

| 16               | I/O  | RTSC#/ QDCQ/ Ext Timer Event Out Ch 9/ GPIO13/ SPI_CLKboot   |                               |                                                                                                                                                                 |

| 17               | I/O  | DTRC#/ TXCLKC  DMA1_REQ/ PIC_0_CAN_RXD  GPIO14/  SPI_TXDboot |                               |                                                                                                                                                                 |

. . . . . .

| X2 pin<br>number | Type | Module functionality                                                             | Usage on<br>Development board | Comments |

|------------------|------|----------------------------------------------------------------------------------|-------------------------------|----------|

| 18               | I/O  | TXDC/ Timer9_In/ PIC_0_CAN_TXD GPIO15/ SPI_ENboot                                |                               |          |

| 19               | I/O  | DCDB# (dup)/ PIC_0_BUS_1[8] PIC_1_BUS_1[8] GPIO51/                               |                               |          |

| 20               | I/O  | CTSB# (dup)/ PIC_0_BUS_1[9] PIC_1_BUS_1[9] GPIO52/                               |                               |          |

| 21               | I/O  | DSRB# (dup)/ PIC_0_BUS_1[10] PIC_1_BUS_1[10] GPIO53/                             |                               |          |

| 22               | I/O  | RXDB (dup)/ PIC_0_BUS_1[11] PIC_1_BUS_1[11] GPIO54/                              |                               |          |

| 23               | I/O  | RIB# (dup)/ PIC_0_BUS_1[12] PIC_1_BUS_1[12] GPIO55/                              |                               |          |

| 24               | I/O  | RTSB# (dup) / RS485CTLB (dup) /<br>PIC_0_BUS_1[13]<br>PIC_1_BUS_1[13]<br>GPIO56/ |                               |          |

| 25               | I/O  | TXCLKB (dup)/ DTRB# (dup) / PIC_0_BUS_1[14] PIC_1_BUS_1[14] GPIO57/              |                               |          |

| 26               | I/O  | TXDB (dup)/ PIC_0_BUS_1[15] PIC_1_BUS_1[15] GPIO58/                              |                               |          |

| X2 pin<br>number | Type | Module functionality                                                   | Usage on<br>Development board | Comments |

|------------------|------|------------------------------------------------------------------------|-------------------------------|----------|

| 27               | I/O  | DCDD# (dup) / PIC_0_BUS_1[16] PIC_1_BUS_1[16] GPIO59/                  |                               |          |

| 28               | I/O  | CTSD# (dup)/ PIC_0_BUS_1[17] PIC_1_BUS_1[17] GPIO60/                   |                               |          |

| 29               | I/O  | DSRD# (dup)/ PIC_0_BUS_1[18] PIC_1_BUS_1[18] GPIO61/                   |                               |          |

| 30               | I/O  | RXDD (dup)/ PIC_0_BUS_1[19] PIC_1_BUS_1[19] GPIO62/                    |                               |          |

| 31               | I/O  | RID# (dup)/<br>PIC_0_BUS_1[20]<br>PIC_1_BUS_1[20]<br>GPIO63/           |                               |          |

| 32               | I/O  | RTSD# (dup) / RS485CTLD(dup) / PIC_0_BUS_1[21] PIC_1_BUS_1[21] GPIO64/ |                               |          |

| 33               | I/O  | TXCLKD (dup) / DTRD# (dup) / PIC_0_BUS_1[22] PIC_1_BUS_1[22] GPIO65    |                               |          |

| 34               | I/O  | TXDD (dup) / PIC_0_BUS_1[23] PIC_1_BUS_1[23] GPIO66                    |                               |          |

| 35               | I/O  | PIC_0_CLK[I] PIC_0_CLK[0] EIRQ3 (dup)/ GPIO67                          |                               |          |

| 36               | I/O  | PIC_0_GEN_IO[0] PIC_1_GEN_IO[0] PIC_1_CAN_RXD GPIO68                   |                               |          |

•

| X2 pin<br>number | Type | Module functionality                                 | Usage on<br>Development board | Comments |

|------------------|------|------------------------------------------------------|-------------------------------|----------|

| 37               | I/O  | PIC_0_GEN_IO[1] PIC_1_GEN_IO[1] PIC_1_CAN_TXD GPIO69 |                               |          |

| 38               | I/O  | PIC_0_GEN_IO[2] PIC_1_GEN_IO[2] PWM0/ GPIO70         |                               |          |

| 39               | I/O  | PIC_0_GEN_IO[3] PIC_1_GEN_IO[3] PWM1/ GPIO71         |                               |          |

| 40               | I/O  | PIC_0_GEN_IO[4] PIC_1_GEN_IO[4] PWM2/ GPIO72         |                               |          |

| 41               | I/O  | PIC_0_GEN_IO[5] PIC_1_GEN_IO[5] PWM3/ GPIO73         |                               |          |

| 42               | I/O  | PIC_0_GEN_IO[6] PIC_1_GEN_IO[6] Timer0_In/ GPIO74    |                               |          |

| 43               | I/O  | PIC_0_GEN_IO[7] PIC_1_GEN_IO[7] Timer1_In/ GPIO75    |                               |          |

| 44               | I/O  | PIC_0_CTL_IO[0] PIC_1_CTL_IO[0] Timer2_In/ GPIO76    |                               |          |

| 45               | I/O  | PIC_0_CTL_IO[1] PIC_1_CTL_IO[1] Timer3_In/ GPIO77    |                               |          |

| 46               | I/O  | PIC_0_CTL_IO[2] PIC_1_CTL_IO[2] Timer4_In/ GPIO78    |                               |          |

| X2 pin<br>number | Type | Module functionality                                                | Usage on<br>Development board | Comments |

|------------------|------|---------------------------------------------------------------------|-------------------------------|----------|

| 47               | I/O  | PIC_0_CTL_IO[3] PIC_1_CTL_IO[3] Timer5_In/ GPIO79                   |                               |          |

| 48               | I/O  | PIC_0_BUS_0[0] PIC_1_BUS_0[0] Timer6_In (dup)/ GPIO80               |                               |          |

| 49               | I/O  | PIC_0_BUS_0[1] PIC_1_BUS_0[1] Timer7_In (dup)/ GPIO81               |                               |          |

| 50               | I/O  | PIC_0_BUS_0[2] PIC_1_BUS_0[2] Timer8_In (dup)/ GPIO82               |                               |          |

| 51               | I/O  | PIC_0_BUS_0[3] PIC_1_BUS_0[3] Timer9_In (dup)/ GPIO83               |                               |          |

| 52               | I/O  | PIC_0_BUS_0[4] PIC_1_BUS_0[4] Timer0_Out/ GPIO84                    |                               |          |

| 53               | I/O  | PIC_0_BUS_0[5] PIC_1_BUS_0[5] Timer1_Out/ GPIO85                    |                               |          |

| 54               | I/O  | PIC_0_BUS_0[6] PIC_1_BUS_0[6] Timer2_Out/ GPIO86                    |                               |          |

| 55               | I/O  | PIC_0_BUS_0[7] PIC_1_BUS_0[7] Timer3_Out/ GPIO87                    |                               |          |

| 56               | I/O  | PIC_0_BUS_0[13]/<br>PIC_1_BUS_0[13]/<br>Timer9_Out (dup)/<br>GPIO93 |                               |          |

•

| X2 pin<br>number | Type | Module functionality                                            | Usage on<br>Development board | Comments              |

|------------------|------|-----------------------------------------------------------------|-------------------------------|-----------------------|

| 57               | I/O  | PIC_0_BUS_0[14]/<br>PIC_1_BUS_0[14]/<br>QDCI (dup)/<br>GPIO94   |                               |                       |

| 58               | I/O  | PIC_0_BUS_0[15]/<br>PIC_1_BUS_0[15]/<br>QDCQ (dup)/<br>GPIO95   |                               |                       |

| 59               | I/O  | PIC_0_BUS_1[0]/ PIC_1_BUS_1[0]/ PIC_0_CAN_RXD GPIO96            |                               |                       |

| 60               | I/O  | PIC_0_BUS_1[1]/ PIC_1_BUS_1[1]/ PIC_0_CAN_TXD GPIO97            |                               |                       |

| 61               | I/O  | PIC_0_BUS_1[2]/ PIC_1_BUS_1[2]/ PIC_1_CAN_RXD GPIO98            |                               |                       |

| 62               | I/O  | PIC_0_BUS_1[3]/ PIC_1_BUS_1[3]/ PIC_1_CAN_TXD GPIO99            |                               |                       |

| 63               | I/O  | PIC_0_BUS_1[4]/<br>PIC_1_BUS_1[4]/<br>PWM4/<br>GPIO100          |                               |                       |

| 64               | I/O  | PIC_0_BUS_1[5]/ PIC_1_BUS_1[5]/ EIRQ3/ GPIO101                  |                               |                       |

| 65               | I/O  | PIC_0_BUS_1[6]/<br>PIC_1_BUS_1[6]/<br>I2C_SCL (dup)/<br>GPIO102 |                               | 4k7 pull-up on module |

| 66               | I/O  | PIC_0_BUS_1[7]/<br>PIC_1_BUS_1[7]/<br>I2C_SDA (dup)/<br>GPIO103 |                               | 4k7 pull-up on module |

| X2 pin<br>number | Type | Module functionality | Usage on<br>Development board | Comments                                                      |

|------------------|------|----------------------|-------------------------------|---------------------------------------------------------------|

| 67               | I    | VIN0_ADC             |                               |                                                               |

| 68               | I    | VIN1_ADC             |                               |                                                               |

| 69               | I    | VIN2_ADC             |                               |                                                               |

| 70               | I    | VIN3_ADC             |                               |                                                               |

| 71               | I    | VIN4_ADC             |                               |                                                               |

| 72               | I    | VIN5_ADC             |                               |                                                               |

| 73               | I    | VIN6_ADC             |                               |                                                               |

| 74               | I    | VIN7_ADC             |                               |                                                               |

| 75               | P    | VSS_ADC              |                               | Connected on module to AGND through $0\Omega$ resistor        |

| 76               | P    | VREF_ADC             |                               | 100nF decoupling capacitor<br>between VREF_ADC and<br>VSS_ADC |

| 77               | P    | 3.3V                 |                               |                                                               |

| 78               | P    | 3.3V                 |                               |                                                               |

| 79               | P    | GND                  |                               |                                                               |

| 80               | P    | GND                  |                               |                                                               |

#### Configuration pins - CPU

None of the 64 GPIO pins on connector X2 disturb CPU boot strap functions. The boot strap functions are controlled by address signals; the user can not disturb boot strap functions from outside, if the module configuration signals, described below, are correctly configured.

# Default module CPU configuration

The user has access to six configuration signals:

- LITTLE#/BIG\_ ENDIAN which allows the user to select the endianess of the module

- OCD\_EN# which allows the user to activate on-chip debugging

- SW\_CONF [3:0] which are reserved for the user; the user software can read out these signals through the GEN ID register (@ 0xA090 0210).

#### Configuration pins — Module

The ConnectCore 9P 9215 and Wi-9P 9215 support the following JTAG signals: TCK, TMS, TDI, TDO, TRST#, and RTCK. Selection can be made between ARM debug mode and boundary scan mode with the signal OCD\_EN#.

### Identification of the module

In order to make it easier for software to recognize a module and especially a hardware variant of the module, a specific bit field made of 4-bits has been reserved on the module. This bit field can be read out through GEN ID register and correspond to A[12:9]. These configuration signals use the internal CPU pull-up resistor and can be pulled down through external population option 2k2 resistors.

In the same way, 3 bits have been available on the module to identify the SDRAM configuration scheme. This bits correspond to A[19:17]. It is impossible for the user to disturb either the variant specific or SDRAM configuration specific bits from outside.

The ConnectCore 9P 9215 and Wi-9P 9215 have also available 4-bit for platform identification. This bit field can be read out through GEN ID register and correspond to A[16:13]. Configuration of these signals is done through the SW\_CONF pins. SW\_CONF0 is connected to A13 through a 2k2 series resistor, and so on for the further SW\_CONF pins. So this bit can be set high by leaving the corresponding SW\_CONF pin unconnected and set low by connecting the corresponding SW\_CONF pin directly low. The user can benefit from these pins to support application or platform specific software configurations.

## Module pin configuration

| Signal name            | Function                                                                                                                     | PU/PD  | Comment                                                                                        |

|------------------------|------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------|

| LITTLE#/BIG_<br>ENDIAN | Set module endianess. 0 module<br>boots in little endian mode. 1<br>module boots in big endian mode.                         | PU     | Signal LITTLE#/BIG_ENDIAN is connected to GPIO_A3/A27 through a 2k2 series resistor.           |

| OCD_EN#                | JTAG / Boundary scan function<br>select  O ARM debug mode,<br>BISTEN# set to high  Boundary scan mode,<br>BISTEN# set to low | PU 10K |                                                                                                |

| SW_CONF0               | User-defined software<br>configuration pin; can be read in<br>GEN_ID register bit 4, default<br>high                         |        | Connected to A13 through a 2k2 series resistor.  Read bit 4 of GEN ID register (@ 0xA0900210). |

| Signal name | Function                                                                                             | PU/PD | Comment                                                                                       |

|-------------|------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------|

| SW_CONF1    | User-defined software<br>configuration pin; can be read in<br>GEN ID register bit 5, default<br>high |       | Connected to A14 through a 2k2 series resistor.Read bit 5 of GEN ID register (@ 0xA0900210).  |

| SW_CONF2    | User-defined software<br>configuration pin; can be read in<br>GEN ID register bit 6, default<br>high |       | Connected to A15 through a 2k2 series resistor. Read bit 6 of GEN ID register (@ 0xA0900210). |

| SW_CONF3    | User-defined software<br>configuration pin; can be read in<br>GEN ID register bit 7, default<br>high |       | Connected to A16 through a 2k2 series resistor. Read bit 7 of GEN ID register (@ 0xA0900210). |

#### Clock generation

#### **Clock frequencies**

Hardware strapping determines the initial powerup PLL settings. The table below summarizes the default clock frequencies for the ConnectCore 9P 9215 and Wi-9P 9215 modules:

#### Hardware strapping:

"PLL reference clock divider setting:

A[4:0] = 0x1D (0b11101)

NR = 5

"PLL output divider setting:

A[6:5] = 0x3 (0b11)

OD = 0

"PLL bypass setting:

A[7] = 0x1 (0b1)

Normal operation

#### PLL frequency formula:

PLL Vco = (RefClk / NR+1) \* (NF+1)

$ClkOut = PLL \ Vco / (OD+1)$

RefClk (Crystal) = 29.4912MHz

NF = 0x3C (reset value - can only be changed by software).

PLL  $V_{co} = (29.4912 / 6) * 61 = 299.8272 \text{ MHz}$

ClkOut = 299.8272 MHz

#### Resulting clock settings:

PIC clock = 299.8272 MHz

CPU clock = 299.8272 MHz / 2 = 149.9136 MHz

AHB clock = 149.9136 MHz / 2 = 74.9568 MHz

# Changing the CPU speed

After powerup, software can change the PLL settings by writing to the PLL configuration register (@ 0xA090\_0188)

Important: When PLL parameters are changed, a reset is provided for the PLL to stabilize. Applications using this feature need to be aware the SDRAM contents will be lost. See reset behavior in the table below.

| Reset Behavior               | RESET<br>_n pin | SRESET<br>_n pin | PLL<br>Config<br>Reg.<br>Update | Watchdog<br>Time-Out<br>Reset |

|------------------------------|-----------------|------------------|---------------------------------|-------------------------------|

| SPI boot                     | YES             | YES              | YES                             | YES                           |

| Strapping PLL                | YES             | NO               | NO                              | NO                            |

| Other strappings (Endianess) | YES             | NO               | NO                              | NO                            |

| GPIO configuration           | YES             | NO               | NO                              | NO                            |

| Other (ASIC) registers       | YES             | YES              | YES                             | YES                           |

| SDRAM keeps its contents     | NO              | YES              | NO                              | YES                           |

#### **Boot process**

The ConnectCore 9P 9215 and Wi-9P 9215 modules boot directly from NOR flash. The start-up code is located at address 0x00000000 during the boot process. When the system is booted, the SDRAM is remapped to address 0x00000000 and NOR Flash to 0x50000000 by modifying the address map in the AHB decoder.

Chip selects

The module has eight chip selects: four for dynamic memory and four for static memory. Each chip select has a 256MB range.

# Chip select memory map

| Name     | CPU<br>Sig.<br>name | Pin | Address range             | Size<br>[Mb] | Usage          | Comments                    |

|----------|---------------------|-----|---------------------------|--------------|----------------|-----------------------------|

| SDM_CS0# | CS1#                | D6  | 0x00000000—<br>0x0FFFFFFF | 256          | SDRAM bank 0   | First bank on module        |

| SDM_CS1# | CS3#                | В5  | 0x10000000—<br>0x1FFFFFFF | 256          | not used       |                             |

| SDM_CS2# | CS5#                | A4  | 0x20000000-<br>0x2FFFFFFF | 256          | not used       |                             |

| SDM_CS3# | CS7#                | B4  | 0x30000000-<br>0x3FFFFFFF | 256          | not used       |                             |

| EXT_CS0# | CS0#                | C6  | 0x40000000–<br>0x4FFFFFFF | 256          | external, CS0# |                             |

| INT_CS1# | CS2#                | В6  | 0x50000000–<br>0x5FFFFFFF | 256          | NOR-Flash      | Program memory on module    |

| EXT_CS2# | CS4#                | C5  | 0x60000000–<br>0x6FFFFFFF | 256          | external, CS2# |                             |

| INT_CS3# | CS6#                | A3  | 0x70000000—<br>0x7FFFFFF  | 256          | internal, CS3# | Reserved for internal usage |

#### SDRAM banks

The module provides connection to 1 SDRAM chip, connected to CS1# (SDM\_CS0#). The other SDRAM chip selects are not used.

The standard module has one of these SDRAM onboard: 1Mx16x4-banks. A13 is the highest address connected. BA0 and BA1 are connected to A21 and A22, respectively.

# Multiplexed GPIO pins

The 64 GPIOs pins available on the module connector are multiplexed with other functions like:

- UART

- SPI

- Ethernet

- DMA

- I<sup>2</sup>C port

- Timers and interrupt inputs

- Memory bus data

#### Pin notes

- GPIO [15:0] allow five multiplex modes.

- GPIO [103:16] and GPIO\_A [3:0] have four multiplex modes.

- Using a pin as GPIO means always to give up other functionalities. Some functions are duplicated to enhance the chance to use them without giving up other vital functions.

- Using original and (dup) functions in parallel is not recommended.

- Default function of GPIOs after CPU power up is function 03, except GPIO12 (function 02-reset\_done) and GPIO [31:16] (function 00 DATA[15:0]).

# **GPIO** multiplex table

In the GPIO multiplex table below,

- the default function is written bold,

- # means low active signal,

- (dup) means function is available multiple times.

| Port<br>name,<br>Function<br>03 | Alternate function<br>00 | Alternate function<br>01 | Alternate<br>function 02 | Alternate<br>function 04 (only<br>GPIO00GPIO15) | On module, default<br>used as |

|---------------------------------|--------------------------|--------------------------|--------------------------|-------------------------------------------------|-------------------------------|

| GPIO0                           | DCDA#                    | DMA0_DONE                | PIC_0_GEN_IO[0]          | SPI_EN# (dup)                                   | DCDA# / SPI_EN#               |

| GPIO1                           | CTSA#                    | EIRQ0                    | PIC_0_GEN_IO[1]          | Reserved                                        | CTSA#                         |

| GPIO2                           | DSRA#                    | EIRQ1                    | PIC_0_GEN_IO[2]          | Reserved                                        | DSRA#                         |

| GPIO3                           | RXDA#                    | DMA0_PDEN                | PIC_0_GEN_IO[3]          | SPI_RXD (dup)                                   | RXDA / SPI_RXD                |

| GPIO4                           | RIA#                     | EIRQ2                    | Timer6_In                | SPI_CLK (dup)                                   | RIA# / SPI_CLK                |

| GPIO5                           | RTSA# / 485CTLA          | EIRQ3                    | Timer6_Out               | SPI_CLK (dup)                                   | RTSA#                         |

| GPIO6                           | TXCLKA / DTRA#           | DMA0_REQ                 | Timer7_In                | PIC_DBG_DATA_OUT                                | DTRA#                         |

| GPIO7                           | TXDA                     | Timer8_In                | Timer7_Out               | SPI_TXD (dup)                                   | TXDA / SPI_TXD                |

| GPIO8                           | DCDC# / TXCLKC           | DMA1_DONE                | Timer8_Out               | SPI_EN# (dup)                                   | DCDC#                         |

| GPIO9                           | CTSC#                    | I2C_SCL                  | EIRQ0 (dup)              | PIC_DBG_DATA_IN                                 | CTSC#                         |

| GPIO10                          | DSRC#                    | QDCI                     | EIRQ1 (dup)              | PIC_DBG_CLK                                     | DSRC#                         |

| Port<br>name,<br>Function<br>03 | Alternate function<br>00   | Alternate function 01 | Alternate<br>function 02 | Alternate<br>function 04 (only<br>GPIO00GPIO15) | On module, default<br>used as |

|---------------------------------|----------------------------|-----------------------|--------------------------|-------------------------------------------------|-------------------------------|

| GPIO11                          | RXDC#                      | DMA1_PDEN             | EIRQ2 (dup)              | SPI_RXD (boot)                                  | RXDC                          |

| GPIO12                          | RXCLKC / RIC#              | I2C_SDA               | RESET_DONE               | SPI_CLK (dup)                                   | RIC# 1                        |

| GPIO13                          | RXCLKC / RTSC#<br>/485CTLC | QDCQ                  | Timer9_out               | SPI_CLK (boot)                                  | RXCLKC / RTSC#                |

| GPIO14                          | TXCLKC / DTRC#             | DMA1_REQ              | PIC_0_CAN_RXD            | SPI_TXD (boot)                                  | TXCLKC                        |

| GPIO15                          | TXDC                       | Timer9_In             | PIC_0_CAN_TXD            | SPI_EN# (boot)                                  | TXDC                          |

| GPIO16                          | D0                         | DCDB#                 | EIRQ0 (dup)              |                                                 | Reserved for upper data lines |

| GPIO17                          | D1                         | CTSB#                 | EIRQ1 (dup)              |                                                 | Reserved for upper data lines |

| GPIO18                          | D2                         | DSRB#                 | EIRQ2 (dup)              |                                                 | Reserved for upper data lines |

| GPIO19                          | D3                         | RXDB                  | EIRQ3 (dup)              |                                                 | Reserved for upper data lines |

| GPIO20                          | D4                         | RIB#                  | DMA0_DONE (dup)          |                                                 | Reserved for upper data lines |

| GPIO21                          | D5                         | RTSB# / 485CTLB       | DMA0_PDEN (dup)          |                                                 | Reserved for upper data lines |

| GPIO22                          | D6                         | TXCLKB / DTRB#        | DMA1_DONE (dup)          |                                                 | Reserved for upper data lines |

| GPIO23                          | D7                         | TXDB                  | PIC_1_CAN_RXD            |                                                 | Reserved for upper data lines |

| GPIO24                          | D8                         | DCDD#                 | PIC_1_CAN_TXD            |                                                 | Reserved for upper data lines |

| GPIO25                          | D9                         | CTSD#                 | RESET_DONE (dup)         |                                                 | Reserved for upper data lines |

| GPIO26                          | D10                        | DSRD#                 | PIC_1_GEN_IO[0]          |                                                 | Reserved for upper data lines |

| GPIO27                          | D11                        | RXDD                  | PIC_1_GEN_IO[1]          |                                                 | Reserved for upper data lines |

| GPIO28                          | D12                        | RID#                  | PIC_1_GEN_IO[2]          |                                                 | Reserved for upper data lines |

| GPIO29                          | D13                        | RTSD# / 485CTLD       | PIC_1_GEN_IO[3]          |                                                 | Reserved for upper data lines |

| GPIO30                          | D14                        | TXCLKD / DTRD#        | Reserved                 |                                                 | Reserved for upper data lines |

| Port<br>name,<br>Function<br>03 | Alternate function<br>00      | Alternate function<br>01 | Alternate<br>function 02 | Alternate<br>function 04 (only<br>GPIO00GPIO15) | On module, default<br>used as |

|---------------------------------|-------------------------------|--------------------------|--------------------------|-------------------------------------------------|-------------------------------|

| GPIO31                          | D15                           | TXDD                     | Reserved                 |                                                 | Reserved for upper data lines |

| GPIO32                          | MII_MDC                       | PIC_0_GEN_IO[0]          | Reserved                 |                                                 | MII Interface                 |

| GPIO33                          | MII_TXC                       | PIC_0_GEN_IO[1]          | Reserved                 |                                                 | MII Interface                 |

| GPIO34                          | MII_RXC                       | PIC_0_GEN_IO[2]          | Reserved                 |                                                 | MII Interface                 |

| GPIO35                          | MII_MDIO                      | PIC_0_GEN_IO[3]          | Reserved                 |                                                 | MII Interface                 |

| GPIO36                          | MII_RXDV                      | PIC_0_GEN_IO[4]          | Reserved                 |                                                 | MII Interface                 |

| GPIO37                          | MII_RXER                      | PIC_0_GEN_IO[5]          | Reserved                 |                                                 | MII Interface                 |

| GPIO38                          | MII_RXD0                      | PIC_0_GEN_IO[6]          | Reserved                 |                                                 | MII Interface                 |

| GPIO39                          | MII_RXD1                      | PIC_0_GEN_IO[7]          | Reserved                 |                                                 | MII Interface                 |

| GPIO40                          | MII_RXD2                      | PIC_1_GEN_IO[0]          | Reserved                 |                                                 | MII Interface                 |

| GPIO41                          | MII_RXD3                      | PIC_1_GEN_IO[1]          | Reserved                 |                                                 | MII Interface                 |

| GPIO42                          | MII_TXEN                      | PIC_1_GEN_IO[2]          | Reserved                 |                                                 | MII Interface                 |

| GPIO43                          | MII_TXER                      | PIC_1_GEN_IO[3]          | Reserved                 |                                                 | MII Interface                 |

| GPIO44                          | MII_TXD0                      | PIC_1_GEN_IO[4]          | Reserved                 |                                                 | MII Interface                 |

| GPIO45                          | MII_TXD1                      | PIC_1_GEN_IO[5]          | Reserved                 |                                                 | MII Interface                 |

| GPIO46                          | MII_TXD2                      | PIC_1_GEN_IO[6]          | Reserved                 |                                                 | MII Interface                 |

| GPIO47                          | MII_TXD3                      | PIC_1_GEN_IO[7]          | Reserved                 |                                                 | MII Interface                 |

| GPIO48                          | MII_COL                       | Reserved                 | Reserved                 |                                                 | MII Interface                 |

| GPIO49                          | MII_CRS                       | Reserved                 | Reserved                 |                                                 | MII Interface                 |

| GPIO50                          | MII_PHY_Int                   | PIC_1_CLK (I)            | PIC_1_CLK(0)             |                                                 | MII Interface                 |

| GPIO51                          | DCDB# (dup)                   | PIC_0_BUS_1[8]           | PIC_1_BUS_1[8]           |                                                 | DCDB#                         |

| GPIO52                          | CTSB# (dup)                   | PIC_0_BUS_1[9]           | PIC_1_BUS_1[9]           |                                                 | CTSB#                         |

| GPIO53                          | DSRB# (dup)                   | PIC_0_BUS_1[10]          | PIC_1_BUS_1[10]          |                                                 | DSRB#                         |

| GPIO54                          | RXDB (dup)                    | PIC_0_BUS_1[11]          | PIC_1_BUS_1[11]          |                                                 | RXDB                          |

| GPIO55                          | RIB# (dup)                    | PIC_0_BUS_1[12]          | PIC_1_BUS_1[12]          |                                                 | RIB#                          |

| GPIO56                          | RTSB# / 485CTLB (dup)         | PIC_0_BUS_1[13]          | PIC_1_BUS_1[13]          |                                                 | RTSB#                         |

| GPIO57                          | TXCLKB (dup) /<br>DTRB# (dup) | PIC_0_BUS_1[14]          | PIC_1_BUS_1[14]          |                                                 | DTRB#                         |

| GPIO58                          | TXDB (dup)                    | PIC_0_BUS_1[15]          | PIC_1_BUS_1[15]          |                                                 | TXDB                          |

| GPIO59                          | DCDD# (dup)                   | PIC_0_BUS_1[16]          | PIC_1_BUS_1[16]          |                                                 | DCDD#                         |

| GPIO60                          | CTSD# (dup)                   | PIC_0_BUS_1[17]          | PIC_1_BUS_1[17]          |                                                 | CTSD#                         |

| Port<br>name,<br>Function<br>03 | Alternate function 00         | Alternate function<br>01 | Alternate<br>function 02 | Alternate<br>function 04 (only<br>GPIO00GPIO15) | On module, default<br>used as      |

|---------------------------------|-------------------------------|--------------------------|--------------------------|-------------------------------------------------|------------------------------------|

| GPIO61                          | DSRD# (dup)                   | PIC_0_BUS_1[18]          | PIC_1_BUS_1[18]          |                                                 | DSRD#                              |

| GPIO62                          | RXDD (dup)                    | PIC_0_BUS_1[19]          | PIC_1_BUS_1[19]          |                                                 | RXDD                               |

| GPIO63                          | RID# (dup)                    | PIC_0_BUS_1[20]          | PIC_1_BUS_1[20]          |                                                 | RID#                               |

| GPIO64                          | RTSD# / 485CTLD (dup)         | PIC_0_BUS_1[21]          | PIC_1_BUS_1[21]          |                                                 | RTSD#                              |

| GPIO65                          | TXCLKD (dup) /<br>DTRD# (dup) | PIC_0_BUS_1[22]          | PIC_1_BUS_1[22]          |                                                 | DTRD#                              |

| GPIO66                          | TXDD (dup)                    | PIC_0_BUS_1[23]          | PIC_1_BUS_1[23]          |                                                 | TXDD                               |

| GPIO67                          | PIC_0_CLK (I)                 | PIC_0_CLK (O)            | EIRQ3 (dup)              |                                                 | PIC_0_CLK                          |

| GPIO68                          | PIC_0_GEN_IO[0]               | PIC_1_GEN_IO[0]          | PIC_1_CAN_RXD            |                                                 | PIC_0_GEN_IO[0]                    |

| GPIO69                          | PIC_0_GEN_IO[1]               | PIC_1_GEN_IO[1]          | PIC_1_CAN_TXD            |                                                 | PIC_0_GEN_IO[1]                    |

| GPIO70                          | PIC_0_GEN_IO[2]               | PIC_1_GEN_IO[2]          | PWM0                     |                                                 | PIC_0_GEN_IO[2]                    |

| GPIO71                          | PIC_0_GEN_IO[3]               | PIC_1_GEN_IO[3]          | PWM1                     |                                                 | PIC_0_GEN_IO[3]                    |

| GPIO72                          | PIC_0_GEN_IO[4]               | PIC_1_GEN_IO[4]          | PWM2                     |                                                 | PIC_0_GEN_IO[4]                    |

| GPIO73                          | PIC_0_GEN_IO[5]               | PIC_1_GEN_IO[5]          | PWM3                     |                                                 | PIC_0_GEN_IO[5]                    |

| GPIO74                          | PIC_0_GEN_IO[6]               | PIC_1_GEN_IO[6]          | Timer0_In                |                                                 | PIC_0_GEN_IO[6]                    |

| GPIO75                          | PIC_0_GEN_IO[7]               | PIC_1_GEN_IO[7]          | Timer1_In                |                                                 | PIC_0_GEN_IO[7]                    |

| GPIO76                          | PIC_0_CTL_IO[0]               | PIC_1_CTL_IO[0]          | Timer2_In                |                                                 | PIC_0_CTL_IO[0]                    |

| GPIO77                          | PIC_0_CTL_IO[1]               | PIC_1_CTL_IO[1]          | Timer3_In                |                                                 | PIC_0_CTL_IO[1]                    |

| GPIO78                          | PIC_0_CTL_IO[2]               | PIC_1_CTL_IO[2]          | Timer4_In                |                                                 | PIC_0_CTL_IO[2]                    |

| GPIO79                          | PIC_0_CTL_IO[3]               | PIC_1_CTL_IO[3]          | Timer5_In                |                                                 | PIC_0_CTL_IO[3]                    |

| GPIO80                          | PIC_0_BUS_0[0]                | PIC_1_BUS_0[0]           | Timer6_In (dup)          |                                                 | Timer6_In                          |

| GPIO81                          | PIC_0_BUS_0[1]                | PIC_1_BUS_0[1]           | Timer7_In (dup)          |                                                 | Timer7_In                          |

| GPIO82                          | PIC_0_BUS_0[2]                | PIC_1_BUS_0[2]           | Timer8_In (dup)          |                                                 | Timer8_In                          |

| GPIO83                          | PIC_0_BUS_0[3]                | PIC_1_BUS_0[3]           | Timer9_In (dup)          |                                                 | Timer9_In                          |

| GPIO84                          | PIC_0_BUS_0[4]                | PIC_1_BUS_0[4]           | Timer0_Out               |                                                 | Timer0_Out                         |

| GPIO85                          | PIC_0_BUS_0[5]                | PIC_1_BUS_0[5]           | Timer1_Out               |                                                 | Timer1_Out                         |

| GPIO86                          | PIC_0_BUS_0[6]                | PIC_1_BUS_0[6]           | Timer2_Out               |                                                 | Timer2_Out                         |

| GPIO87                          | PIC_0_BUS_0[7]                | PIC_1_BUS_0[7]           | Timer3_Out               |                                                 | Timer3_Out                         |

| GPIO88                          | PIC_0_BUS_0[8]                | PIC_1_BUS_0[8]           | Timer4_Out               |                                                 | User LED 0 => LED 1 (on module)    |

| GPIO89                          | PIC_0_BUS_0[9]                | PIC_1_BUS_0[9]           | Timer5_Out               |                                                 | User LED 1 => LED 2<br>(on module) |

| Port<br>name,<br>Function<br>03 | Alternate function<br>00 | Alternate function<br>01 | Alternate<br>function 02 | Alternate<br>function 04 (only<br>GPIO00GPIO15) | On module, default<br>used as |

|---------------------------------|--------------------------|--------------------------|--------------------------|-------------------------------------------------|-------------------------------|

| GPIO90                          | PIC_0_BUS_0[10]          | PIC_1_BUS_0[10]          | Timer6_Out (dup)         |                                                 | GPIO reserved on module       |

| GPIO91                          | PIC_0_BUS_0[11]          | PIC_1_BUS_0[11]          | Timer7_Out (dup)         |                                                 | Reserved NAND_R/B#            |

| GPIO92                          | PIC_0_BUS_0[12]          | PIC_1_BUS_0[12]          | Timer8_Out (dup)         |                                                 | GPIO reserved on module       |

| GPIO93                          | PIC_0_BUS_0[13]          | PIC_1_BUS_0[13]          | Timer9_Out (dup)         |                                                 | Timer9_Out                    |

| GPIO94                          | PIC_0_BUS_0[14]          | PIC_1_BUS_0[14]          | QDCI (dup)               |                                                 | QDCI                          |

| GPIO95                          | PIC_0_BUS_0[15]          | PIC_1_BUS_0[15]          | QDCQ (dup)               |                                                 | QDCQ                          |

| GPIO96                          | PIC_0_BUS_1[0]           | PIC_1_BUS_1[0]           | PIC_0_CAN_RXD            |                                                 | PIC_0_CAN_RXD                 |

| GPIO97                          | PIC_0_BUS_1[1]           | PIC_1_BUS_1[1]           | PIC_0_CAN_TXD            |                                                 | PIC_0_CAN_TXD                 |

| GPIO98                          | PIC_0_BUS_1[2]           | PIC_1_BUS_1[2]           | PIC_1_CAN_RXD            |                                                 | PIC_1_CAN_RXD                 |

| GPIO99                          | PIC_0_BUS_1[3]           | PIC_1_BUS_1[3]           | PIC_1_CAN_TXD            |                                                 | PIC_1_CAN_TXD                 |

| GPIO100                         | PIC_0_BUS_1[4]           | PIC_1_BUS_1[4]           | PWM4                     |                                                 | PWM4                          |

| GPIO101                         | PIC_0_BUS_1[5]           | PIC_1_BUS_1[5]           | EIRQ3                    |                                                 | EIRQ3                         |