# EZ-USB<sup>®</sup> FX3<sup>™</sup> Technical Reference Manual

Spec No.: 001-76074 Rev. \*E

May 31, 2017

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2012-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO. THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PUR-POSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities. including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

EZ-USB® is a registered trademark and FX3™ is a trademark of Cypress Semiconductor Corporation (Cypress), along with Cypress® and Cypress Semiconductor™. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

# Contents

| 1. | Intro | duction to EZ-USB FX3                         | 19 |

|----|-------|-----------------------------------------------|----|

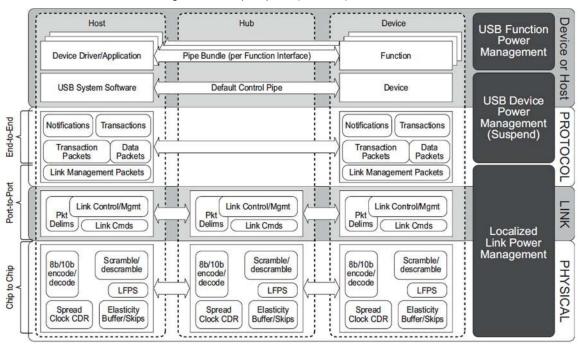

|    | 1.1   | Overview of USB 3.0                           | 19 |

|    |       | 1.1.1 Physical Layer                          | 19 |

|    |       | 1.1.2 Link Layer                              | 20 |

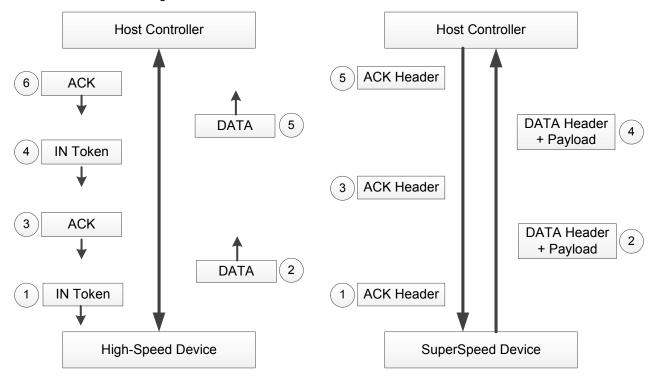

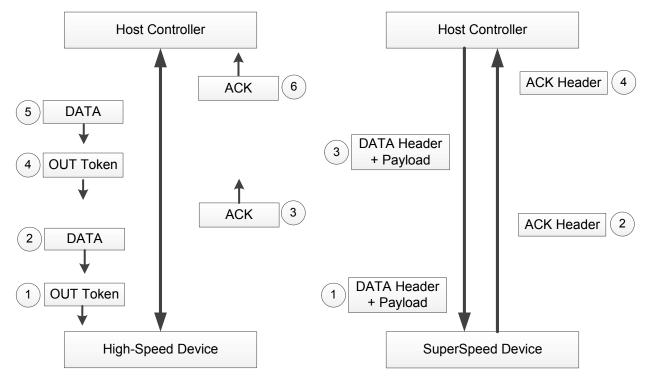

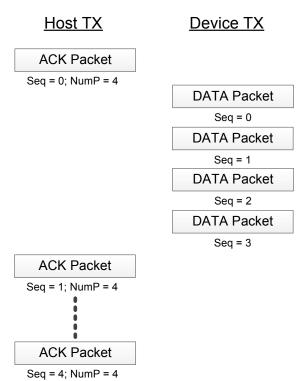

|    |       | 1.1.3 Protocol Layer                          | 21 |

|    |       | 1.1.3.1 Unicast Transactions                  |    |

|    |       | 1.1.3.2 Token/ Data/Handshake Sequences       |    |

|    |       | 1.1.3.3 Data Bursting                         |    |

|    |       | 1.1.3.4 End-to-End Flow Control               |    |

|    |       | 1.1.3.5 Streams                               | 25 |

|    | 1.2   | SuperSpeed Power Management                   | 25 |

|    |       | 1.2.1 Function Power Management               | 26 |

|    | 1.3   | FX3/FX3S Features                             | 26 |

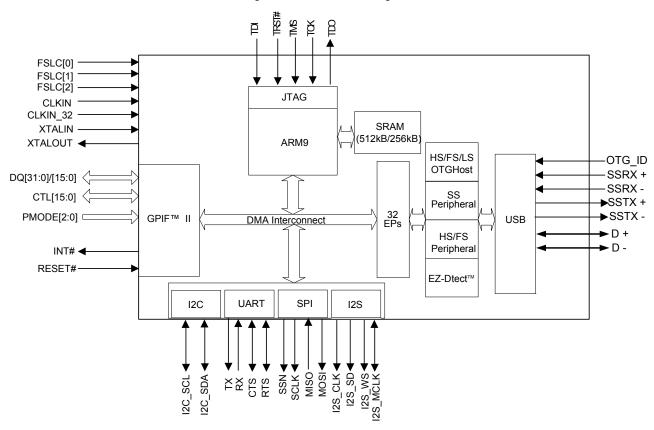

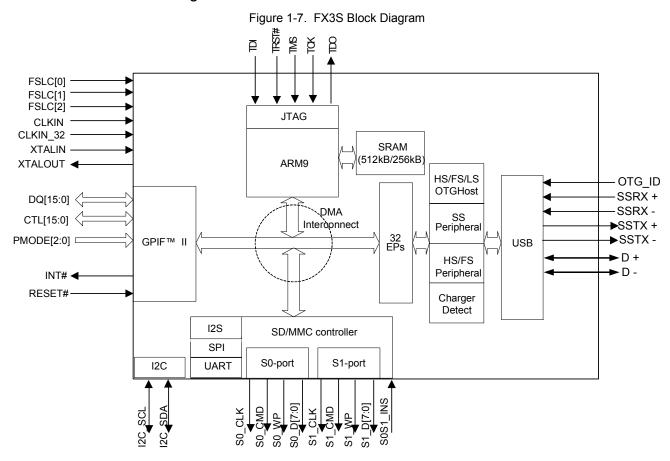

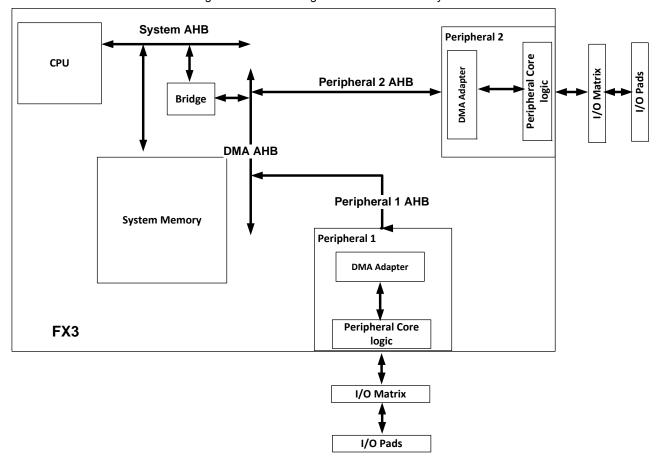

|    |       | 1.3.1 FX3 Block Diagram                       | 28 |

|    |       | 1.3.2 FX3S Block Diagram                      | 29 |

|    | 1.4   | Functional Overview                           | 29 |

|    |       | 1.4.1 CPU                                     | 29 |

|    |       | 1.4.2 DMA                                     | 30 |

|    |       | 1.4.3 USB Interface                           | 30 |

|    |       | 1.4.4 GPIF II                                 | 30 |

|    |       | 1.4.5 UART Interface                          | 31 |

|    |       | 1.4.6 I2C Interface                           | 31 |

|    |       | 1.4.7 I2S Interface                           | 31 |

|    |       | 1.4.8 SPI Interface                           | 31 |

|    |       | 1.4.9 JTAG Interface                          |    |

|    |       | 1.4.10 Storage Interface                      | 31 |

|    |       | 1.4.10.1 SD/MMC Clock Stop                    |    |

|    |       | 1.4.10.2 SD_CLK Output Clock Stop             | 32 |

|    |       | 1.4.10.3 Card Insertion and Removal Detection |    |

|    |       | 1.4.10.4 Write Protection (WP)                |    |

|    |       | 1.4.10.5 SDIO Interrupt                       |    |

|    |       | 1.4.10.6 SDIO Read-Wait Feature               |    |

|    |       | 1.4.10.7 Boot Options                         |    |

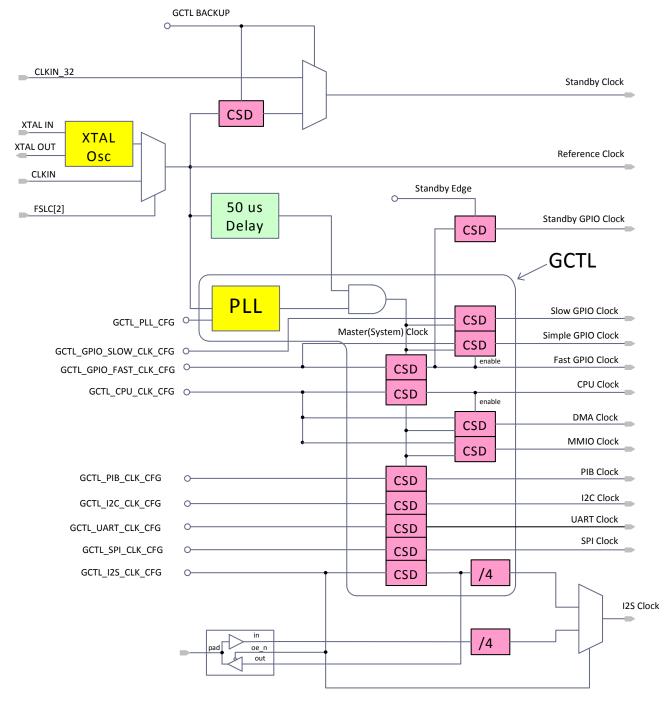

|    |       | 1.4.11 Clocking                               | 33 |

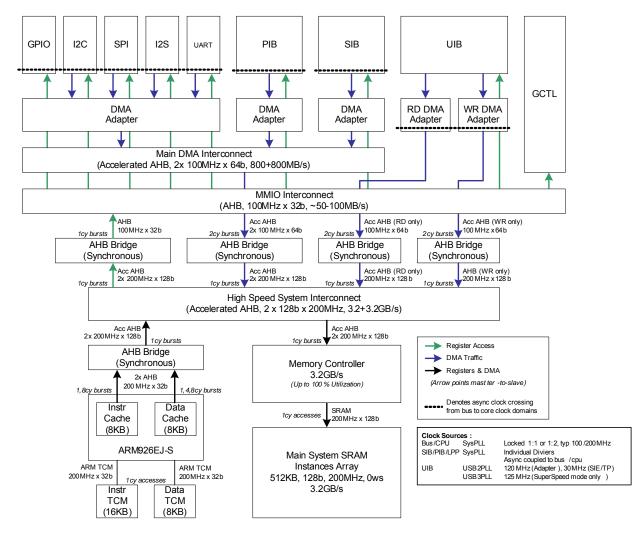

| 2. | FX3 ( | CPU Subsystem                                 | 35 |

|    | 2.1   | Features                                      | 35 |

|    | 2.2   | Block Diagram                                 |    |

|    | 2.3   | Functional Overview                           |    |

|    | ۷.5   | 2.3.1 ARM926EJ-S CPU                          |    |

|    |       | 2.3.1 AINW20L0-3 OF U                         | 30 |

|    |       |        | 2.3.1.1     | Processor Modes               |    |

|----|-------|--------|-------------|-------------------------------|----|

|    |       |        | 2.3.1.2     | Processor Registers           |    |

|    |       |        | 2.3.1.3     | Exception Vectors             |    |

|    |       |        | 2.3.1.4     | MMU                           |    |

|    |       |        | 2.3.1.5     | Cache Memories                |    |

|    |       |        | 2.3.1.6     | Tightly Coupled Memories      |    |

|    |       |        | 2.3.1.7     | JTAG Interface                |    |

|    |       |        | 2.3.1.8     | Vectored Interrupt Controller |    |

|    |       |        | 2.3.1.9     | CPU Operating Frequency       |    |

|    |       |        |             | CPU Power Modes               |    |

|    |       |        | 2.3.1.11    | Timers                        | 42 |

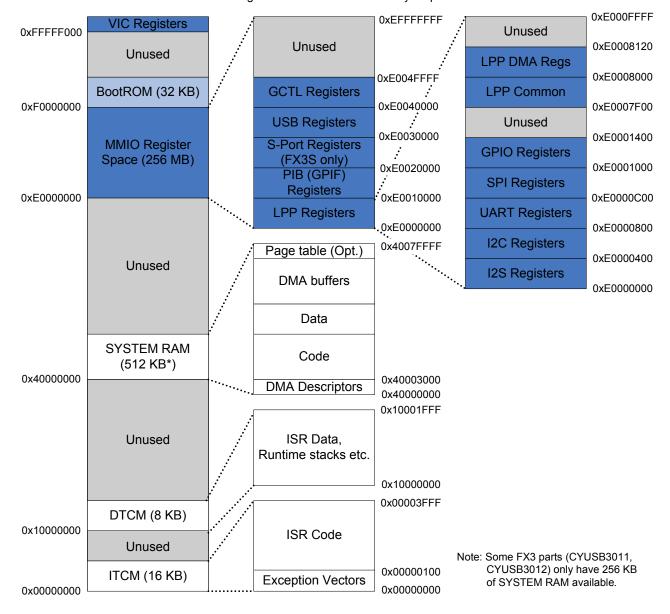

| 3. | Memo  | ory an | d Syster    | n Interconnect                | 45 |

|    | 3.1   | Featu  | res         |                               | 45 |

|    | 3.2   | Block  | Diagram     |                               | 45 |

|    | 3.3   |        | •           | /iew                          |    |

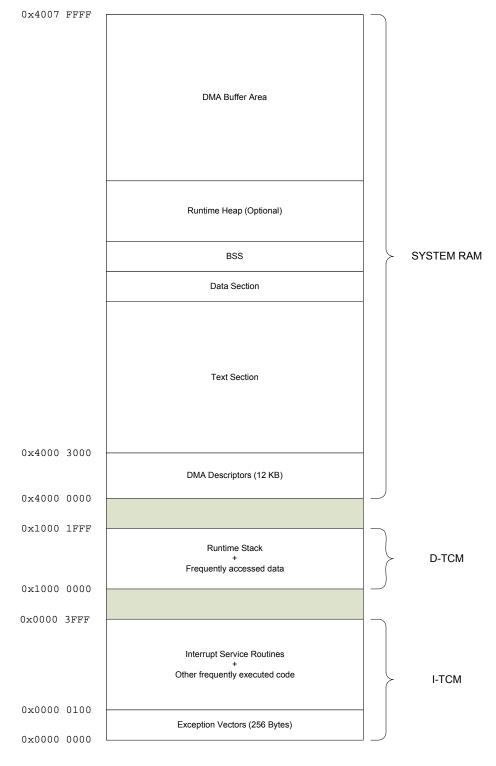

|    | 0.0   | 3.3.1  |             | Regions                       |    |

|    |       |        | -           | nterconnect                   |    |

|    |       |        | -           | er Operations                 |    |

|    |       |        |             | perations                     |    |

|    |       | 3.3.4  |             | Cache Coherency               |    |

|    |       | 3.3.5  |             | Usage                         |    |

|    |       | 3.3.3  | Memory      | Usaye                         |    |

| 4. | Globa |        | troller (0  | •                             | 53 |

|    | 4.1   |        |             |                               |    |

|    |       | 4.1.1  | I/O Matri   | Configuration                 | 53 |

|    |       | 4.1.2  | I/O Drive   | Strength                      | 55 |

|    |       | 4.1.3  | GPIO Pu     | II-up and Pull-down           | 55 |

|    |       | 4.1.4  |             | PIO Override                  |    |

|    |       | 4.1.5  | •           | GPIO Override                 |    |

|    |       | 4.1.6  | •           | r Observability               |    |

|    |       |        | 4.1.6.1     |                               |    |

|    |       |        | 4.1.6.2     | GCTL_IOPWR_INTR               |    |

|    |       |        | 4.1.6.3     | GCTL_IOPWR_INTR_MASK          |    |

|    | 4.2   | Clock  | Managem     | ent                           | 56 |

|    | 4.3   |        | _           | nent                          |    |

|    | 7.5   | 4.3.1  | _           | omains                        |    |

|    |       |        |             | odes                          |    |

|    |       |        |             | oues                          |    |

|    |       |        |             |                               |    |

|    |       |        |             | set                           |    |

|    |       | 4.3.5  | Son Res     | et                            | 58 |

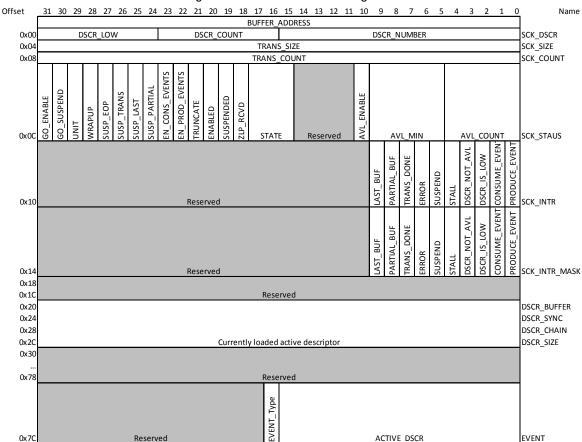

| 5. | FX3 [ | OMA S  | ubsyste     | m                             | 61 |

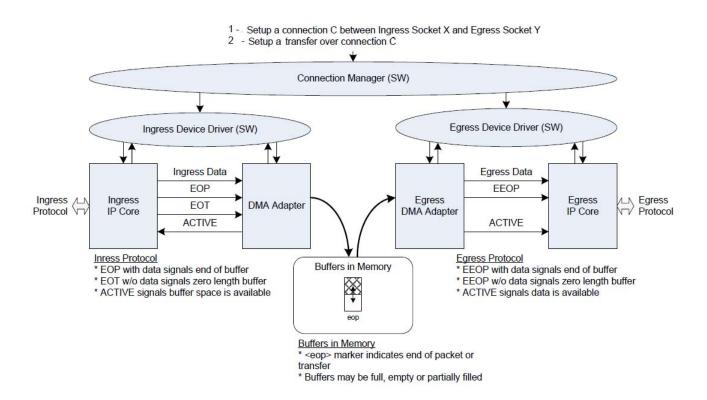

|    | 5.1   | DMA I  | Introductio | n                             | 61 |

|    | 5.2   | DMA I  | Features    |                               | 61 |

|    | 5.3   | DMA I  | Block Diag  | ram                           | 61 |

|    | 5.4   |        | _           |                               |    |

|    | 5.5   |        |             | Components                    |    |

|    |       |        | -           |                               |    |

|    |            | 5.5.2                                                                                           | Descriptors Buffers, and Sockets                                                                                                                                                                                                                                                                                                                           |                                                                            |

|----|------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|    |            | 5.5.3                                                                                           | DMA Descriptors                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|    |            | 5.5.4                                                                                           | DMA Buffer                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

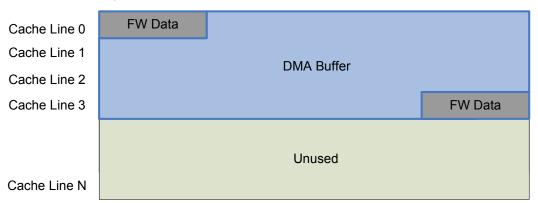

|    |            |                                                                                                 | 5.5.4.1 Implications of Data Cache Usage                                                                                                                                                                                                                                                                                                                   |                                                                            |

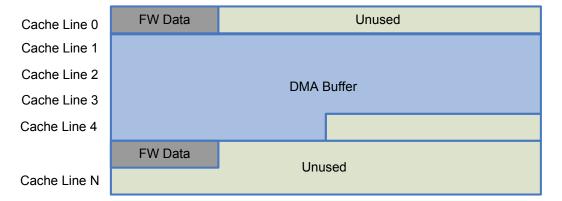

|    |            |                                                                                                 | 5.5.4.2 Memory Corruption Due to Cache Line Overlap                                                                                                                                                                                                                                                                                                        |                                                                            |

|    |            |                                                                                                 | 5.5.4.3 Safe Usage of Data Cache 5.5.4.4 ALIGNMENT REQUIREMENT - How Not To Share Cache Lines                                                                                                                                                                                                                                                              |                                                                            |

|    |            | 5.5.5                                                                                           | Sockets                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

|    |            | 5.5.5                                                                                           | 5.5.5.1 Software Manipulation of Sockets                                                                                                                                                                                                                                                                                                                   |                                                                            |

|    |            |                                                                                                 | 5.5.5.2 Initializing a Socket                                                                                                                                                                                                                                                                                                                              |                                                                            |

|    |            |                                                                                                 | 5.5.5.3 Terminating a Socket                                                                                                                                                                                                                                                                                                                               |                                                                            |

|    |            |                                                                                                 | 5.5.5.4 Modifying or Suspending a Socket                                                                                                                                                                                                                                                                                                                   |                                                                            |

|    |            |                                                                                                 | 5.5.5.5 Inspecting a Socket                                                                                                                                                                                                                                                                                                                                |                                                                            |

|    |            |                                                                                                 | 5.5.5.6 Wrapping Up a Socket                                                                                                                                                                                                                                                                                                                               |                                                                            |

|    |            | 5.5.6                                                                                           | Illustration of Descriptor, Buffer and Socket Usage                                                                                                                                                                                                                                                                                                        |                                                                            |

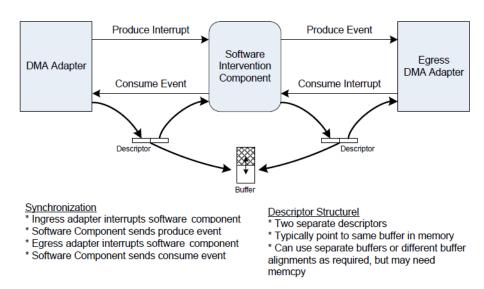

|    |            | 5.5.7                                                                                           | Understanding DMA Operation: Peripheral to Peripheral                                                                                                                                                                                                                                                                                                      |                                                                            |

|    |            | 5.5.8                                                                                           | Interrupt Requests                                                                                                                                                                                                                                                                                                                                         |                                                                            |

|    |            | 5.5.9                                                                                           | DMA Interrupts                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|    | 5.6        |                                                                                                 | amming Sequence                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|    | 5.0        | 5.6.1                                                                                           | Initialization                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|    |            | 5.0.1                                                                                           | 5.6.1.1 Producer Half                                                                                                                                                                                                                                                                                                                                      |                                                                            |

|    |            |                                                                                                 | 5.6.1.2 Consumer Half                                                                                                                                                                                                                                                                                                                                      |                                                                            |

|    |            | 5.6.2                                                                                           | Peripheral to Peripheral Transfer                                                                                                                                                                                                                                                                                                                          |                                                                            |

|    | <b>5</b> 7 |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|    | 5.7        |                                                                                                 | Intervention In Between Ingress and Egress                                                                                                                                                                                                                                                                                                                 |                                                                            |

|    | 5.8        | Conce                                                                                           | ept of DMA Channels                                                                                                                                                                                                                                                                                                                                        | 80                                                                         |

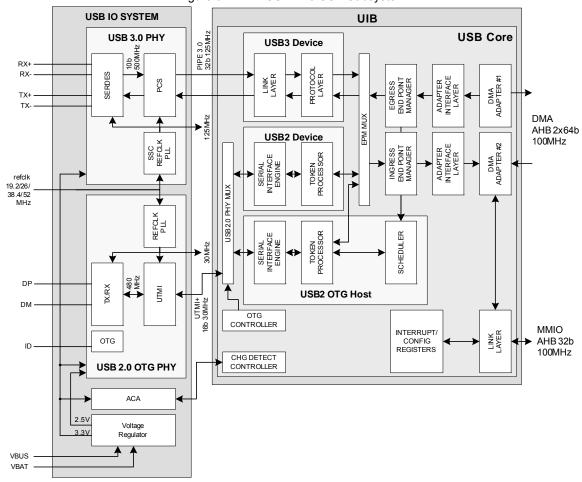

| 6. | Unive      | ersal S                                                                                         | Serial Bus (USB)                                                                                                                                                                                                                                                                                                                                           | 81                                                                         |

|    | 6.1        | Introdu                                                                                         | uction                                                                                                                                                                                                                                                                                                                                                     | 81                                                                         |

|    | 0.0        |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|    | 6.2        | Featu                                                                                           | res                                                                                                                                                                                                                                                                                                                                                        | 81                                                                         |

|    |            |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|    | 6.3        | Block                                                                                           | Diagram                                                                                                                                                                                                                                                                                                                                                    | 81                                                                         |

|    |            | Block<br>Overv                                                                                  | Diagramiew                                                                                                                                                                                                                                                                                                                                                 | 81                                                                         |

|    | 6.3        | Block<br>Overv<br>6.4.1                                                                         | DiagramiewUSB Interface Block                                                                                                                                                                                                                                                                                                                              | 81<br>82                                                                   |

|    | 6.3        | Block<br>Overv<br>6.4.1<br>6.4.2                                                                | Diagram  iew  USB Interface Block  USB 3.0 Function Controller                                                                                                                                                                                                                                                                                             | 81<br>82<br>82                                                             |

|    | 6.3        | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3                                                       | Diagram  iew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller                                                                                                                                                                                                                                                                | 81828282                                                                   |

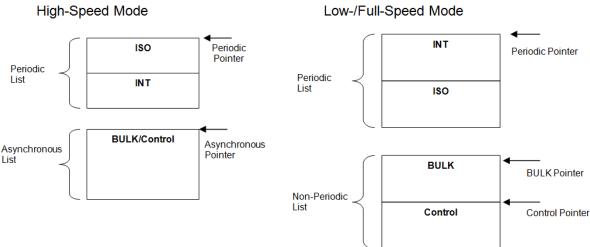

|    | 6.3        | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4                                              | Diagram  iew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 2.0 Embedded Host                                                                                                                                                                                                                                         | 81<br>82<br>82<br>82                                                       |

|    | 6.3        | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5                                     | Diagram  iew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 2.0 Embedded Host  USB OTG Controller                                                                                                                                                                                                                     | 81<br>82<br>82<br>82<br>82                                                 |

|    | 6.3        | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6                            | Diagram  iew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 2.0 Embedded Host  USB OTG Controller  Charger Detect Controller                                                                                                                                                                                          | 81<br>82<br>82<br>82<br>82<br>83                                           |

|    | 6.3        | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7                   | Diagram  iew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 2.0 Embedded Host  USB OTG Controller  Charger Detect Controller  End-Point Memory                                                                                                                                                                        | 81<br>82<br>82<br>82<br>83<br>83                                           |

|    | 6.3        | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8          | Diagram  Tiew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 2.0 Embedded Host  USB OTG Controller  Charger Detect Controller  End-Point Memory  DMA Adapters                                                                                                                                                         | 81<br>82<br>82<br>82<br>83<br>83                                           |

|    | 6.3        | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8          | Diagram  Tiew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 2.0 Embedded Host  USB OTG Controller  Charger Detect Controller  End-Point Memory  DMA Adapters  USB I/O System                                                                                                                                         | 81<br>82<br>82<br>83<br>83<br>83                                           |

|    | 6.3        | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8          | Diagram  iew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 2.0 Embedded Host  USB OTG Controller  Charger Detect Controller  End-Point Memory  DMA Adapters  USB I/O System  6.4.9.1 USB 2.0 OTG PHY                                                                                                                 | 81<br>82<br>82<br>83<br>83<br>83<br>83                                     |

|    | 6.3<br>6.4 | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9 | Diagram  iew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 0TG Controller  Charger Detect Controller  End-Point Memory  DMA Adapters  USB I/O System  6.4.9.1 USB 2.0 OTG PHY  6.4.9.2 USB 3.0 PHY                                                                                                                   | 8182828383838383                                                           |

|    | 6.3<br>6.4 | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9 | Diagram  Tiew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 2.0 Embedded Host  USB OTG Controller  Charger Detect Controller  End-Point Memory  DMA Adapters  USB I/O System  6.4.9.1 USB 2.0 OTG PHY  6.4.9.2 USB 3.0 PHY                                                                                           | 81<br>82<br>82<br>83<br>83<br>83<br>83<br>83                               |

|    | 6.3<br>6.4 | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9 | Diagram  iew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB OTG Controller  Charger Detect Controller  End-Point Memory  DMA Adapters  USB I/O System  6.4.9.1 USB 2.0 OTG PHY  6.4.9.2 USB 3.0 PHY  op-Level Register Interface  Function Controllers                                                                | 81828283838383838484                                                       |

|    | 6.3<br>6.4 | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9 | Diagram  iew  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Embedded Host  USB OTG Controller  Charger Detect Controller  End-Point Memory  DMA Adapters  USB I/O System  6.4.9.1 USB 2.0 OTG PHY  6.4.9.2 USB 3.0 PHY  op-Level Register Interface  Function Controllers  USB 3.0 Function                                                    | 81828283838383838484                                                       |

|    | 6.3<br>6.4 | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9 | Diagram  Diagram  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 0.0 Embedded Host  USB OTG Controller  Charger Detect Controller  End-Point Memory  DMA Adapters  USB I/O System  6.4.9.1 USB 2.0 OTG PHY  6.4.9.2 USB 3.0 PHY  op-Level Register Interface  Function Controllers  USB 3.0 Function  6.6.1.1 Clocking |                                                                            |

|    | 6.3<br>6.4 | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9 | Diagram  Jiew                                                                                                                                                                                                                                                                                                                                              | 81<br>82<br>82<br>82<br>83<br>83<br>83<br>83<br>83<br>84<br>84<br>86<br>86 |

|    | 6.3<br>6.4 | Block<br>Overv<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9 | Diagram  Diagram  USB Interface Block  USB 3.0 Function Controller  USB 2.0 Function Controller  USB 0.0 Embedded Host  USB OTG Controller  Charger Detect Controller  End-Point Memory  DMA Adapters  USB I/O System  6.4.9.1 USB 2.0 OTG PHY  6.4.9.2 USB 3.0 PHY  op-Level Register Interface  Function Controllers  USB 3.0 Function  6.6.1.1 Clocking | 8182828383838384868686                                                     |

|    |      |                | •          |                      |          | 89      |

|----|------|----------------|------------|----------------------|----------|---------|

|    |      |                |            | •                    |          | 90      |

|    | 6.7  |                |            |                      |          | 92      |

|    |      | 6.7.1          |            |                      |          | 92      |

|    |      | 6.7.2<br>6.7.3 |            |                      |          | 92      |

|    |      | 0.7.3          | 6.7.3.1    | •                    |          | 92      |

|    |      |                |            |                      |          | 92      |

|    |      | 6.7.4          |            |                      |          | 93      |

|    |      |                |            | •                    |          | 93      |

|    |      |                |            |                      |          | 93      |

|    |      | 6.7.7          | USB Res    | ume                  |          | <br>93  |

|    |      | 6.7.8          | Start of F | rame                 |          | <br>93  |

|    |      | 6.7.9          | SETUP F    | Packet               |          | <br>93  |

|    |      | 6.7.10         | IN Packe   | t                    |          | <br>94  |

|    |      | 6.7.11         | OUT Pac    | ket                  |          | <br>94  |

|    | 6.8  | USB 3          | .0 and US  | B 2.0 Function Coor  | dination | <br>92  |

|    | 6.9  | USB F          | unction P  | rogramming Model     |          | <br>95  |

|    |      |                |            | _                    |          | 95      |

|    |      | 6.9.2          | USB 3.0    | Enable               |          | <br>96  |

|    |      | 6.9.3          | USB 3.0    | Fallback to USB 2.0. |          | <br>97  |

|    |      | 6.9.4          | USB Res    | et                   |          | <br>98  |

|    |      | 6.9.5          | USB Con    | nect                 |          | <br>99  |

|    |      |                |            |                      |          | 101     |

|    |      |                |            | •                    |          | 102     |

|    |      | 6.9.8          |            |                      |          | 109     |

|    |      |                | 6.9.8.1    | _                    |          | 109     |

|    |      | 6.9.9          | •          |                      |          | 109     |

|    |      | 6.9.10         |            | •                    |          | 110     |

|    |      |                |            |                      |          | 110     |

|    |      | 6 9 11         |            |                      |          |         |

|    |      | 0.5.11         |            |                      |          | 112     |

|    |      |                |            |                      |          | 112     |

|    |      |                |            |                      |          | 113     |

|    | 6.10 | USB C          | TG Contr   | oller                |          | <br>115 |

|    |      |                |            |                      |          | 115     |

|    |      | 6.10.2         | USB OT     | G Programming Mod    | el       | <br>115 |

|    |      |                |            |                      | •        | 115     |

|    |      |                |            |                      |          | 119     |

|    |      |                |            | •                    |          | 121     |

|    | 6.11 |                | _          |                      |          | 122     |

|    |      |                |            | -                    |          | 122     |

|    |      |                |            |                      |          | 122     |

|    |      | 6.11.3         | USB ID S   | Signal Detection     |          | <br>123 |

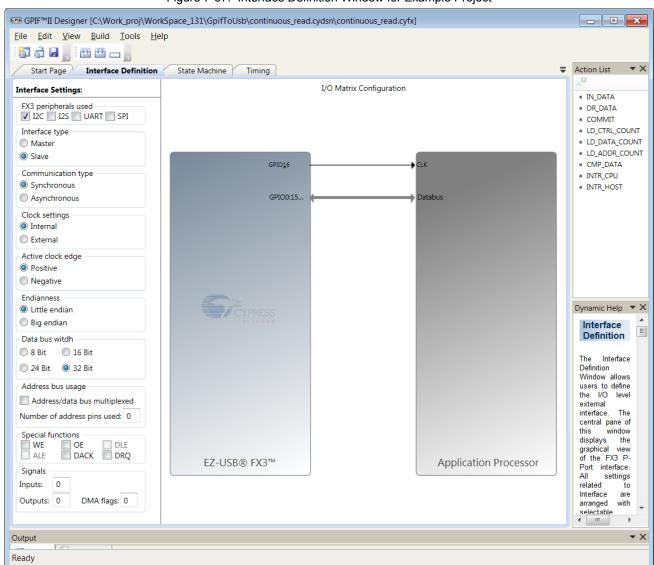

| 7. | Gene | ral Pro        | gramma     | able Interface II (  | GPIF II) | 125     |

|    | 7.1  |                | _          | •                    | •        | <br>125 |

|    | 7.2  |                |            |                      |          | 126     |

|    | · ·- |                |            |                      |          |         |

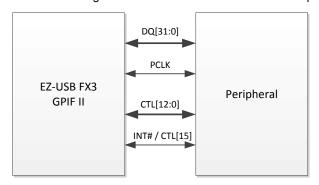

| 7.3 | Typica      | Typical GPIF II interface |                                              |     |  |  |

|-----|-------------|---------------------------|----------------------------------------------|-----|--|--|

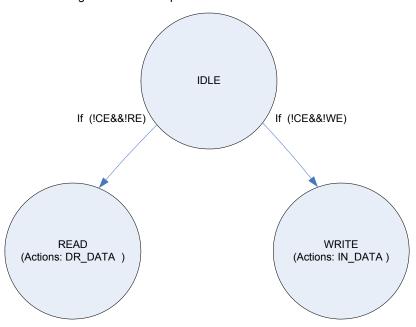

| 7.4 | Functi      | onal Over                 | view                                         | 127 |  |  |

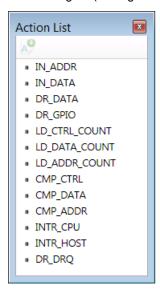

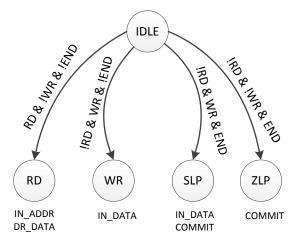

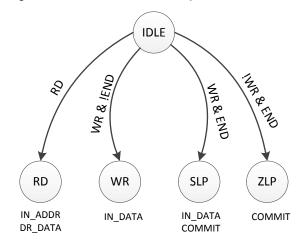

|     | 7.4.1       |                           |                                              |     |  |  |

|     |             | 7.4.1.1                   | Action - IN DATA                             |     |  |  |

|     |             | 7.4.1.2                   | Action - IN ADDR                             |     |  |  |

|     |             | 7.4.1.3                   | Action - DR DATA                             |     |  |  |

|     |             | 7.4.1.4                   | Action - DR_ADDR                             | 131 |  |  |

|     |             | 7.4.1.5                   | Action - COMMIT                              | 132 |  |  |

|     |             | 7.4.1.6                   | Action - DR_GPIO                             | 132 |  |  |

|     |             | 7.4.1.7                   | Action - LD_ADDR_COUNT                       | 133 |  |  |

|     |             | 7.4.1.8                   | Action - LD_DATA_COUNT                       |     |  |  |

|     |             | 7.4.1.9                   | Action - LD_CTRL_COUNT                       |     |  |  |

|     |             |                           | Action - COUNT_ADDR                          |     |  |  |

|     |             |                           | Action - COUNT_DATA                          |     |  |  |

|     |             |                           | Action - COUNT_CTRL                          |     |  |  |

|     |             |                           | Action - CMP_ADDR                            |     |  |  |

|     |             |                           | Action - CMP_DATA                            |     |  |  |

|     |             |                           | Action - CMP_CTRL                            |     |  |  |

|     |             |                           | Action - INTR_CPU                            |     |  |  |

|     |             |                           | Action - INTR_HOST                           |     |  |  |

|     |             |                           | Action - DR_DRQ                              |     |  |  |

|     | 7.4.2       |                           |                                              |     |  |  |

|     |             |                           | n Conditions                                 |     |  |  |

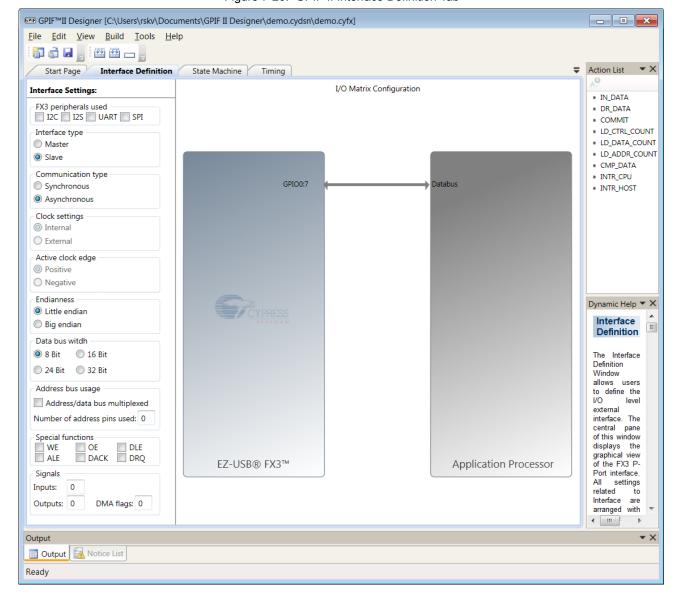

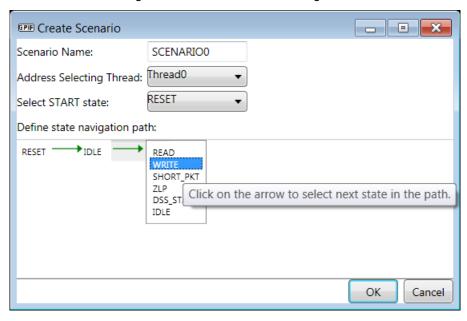

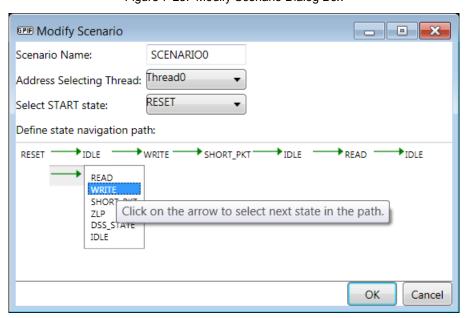

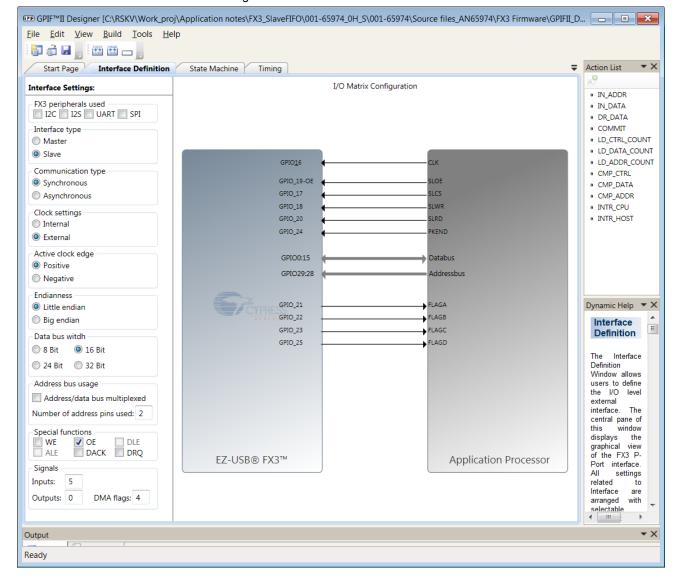

|     | 7.4.4       | GPIF II D                 | Designer Tool                                | 139 |  |  |

|     | 7.4.5       | GPIF II H                 | lardware Resources                           |     |  |  |

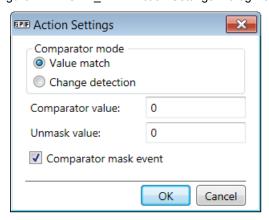

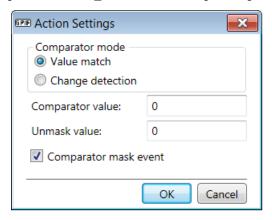

|     |             | 7.4.5.1                   | Comparators                                  |     |  |  |

|     |             | 7.4.5.2                   |                                              |     |  |  |

|     |             | 7.4.5.3                   | GPIF II Interrupt                            |     |  |  |

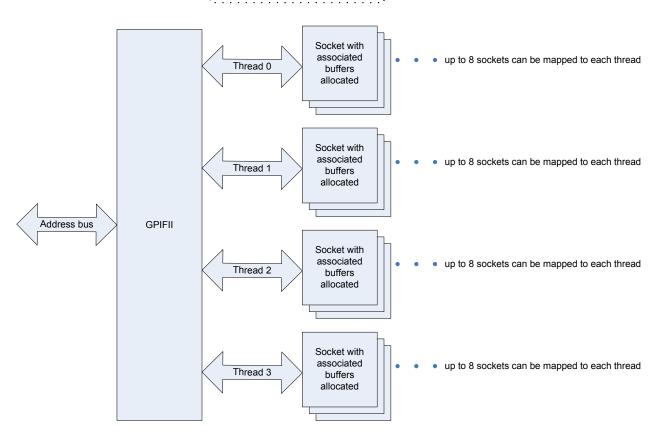

|     | 7.4.6       | Threads                   | and Sockets                                  |     |  |  |

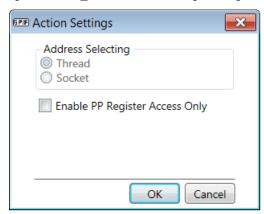

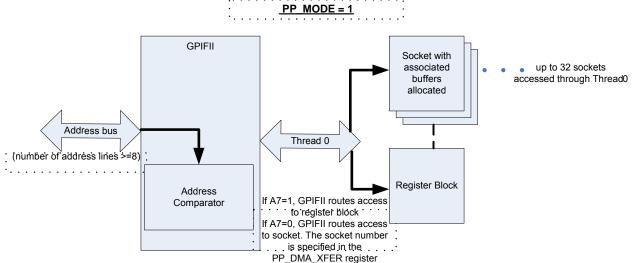

|     |             | 7.4.6.1                   | Difference Between PP_MODE=0 and PP_MODE=1   |     |  |  |

|     | 7.4.7       | Addressi                  | ng                                           |     |  |  |

|     |             | 7.4.7.1                   | Number of Address Lines                      |     |  |  |

|     |             | 7.4.7.2                   | Assigning Sockets to Threads                 |     |  |  |

|     |             | 7.4.7.3                   | Addressing Methods                           |     |  |  |

|     | 7.4.8       | Async/Sy                  | /nc                                          | 143 |  |  |

|     |             |                           | ation of Flags                               |     |  |  |

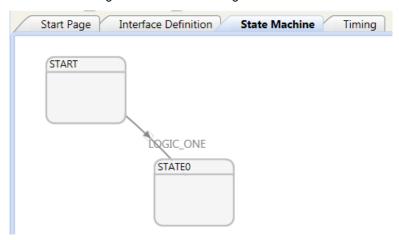

|     | 7.4.10      | Developi                  | ng the GPIF II State Machine                 | 143 |  |  |

| 7.5 | Desia       | ning a GPI                | IF II Interface                              | 143 |  |  |

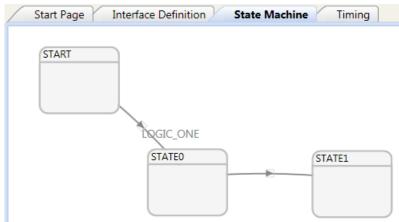

| 7.6 | •           | •                         | achine Implementation                        |     |  |  |

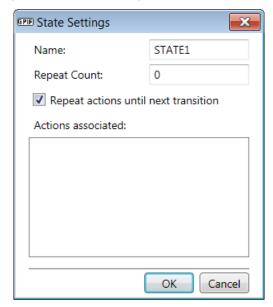

| 7.0 | 7.6.1       |                           | ate                                          |     |  |  |

|     | 7.6.2       |                           | ons to a State                               |     |  |  |

|     |             |                           | nsitions Between Actions                     |     |  |  |

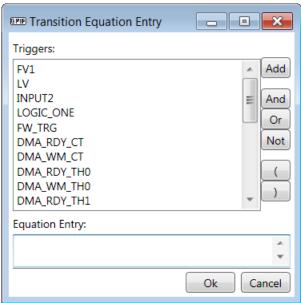

|     |             |                           |                                              |     |  |  |

|     |             |                           | ansition Equation                            |     |  |  |

|     |             |                           | Properties                                   |     |  |  |

|     | 7.6.6       |                           | g the Signal Timing of the GPIF II Interface |     |  |  |

|     |             | 7.6.6.1                   | Selection of Time Frame                      |     |  |  |

|     |             | 7.6.6.2                   | Automatic Timing Scale Selection             |     |  |  |

|     | 7.6.7       |                           | Entry                                        |     |  |  |

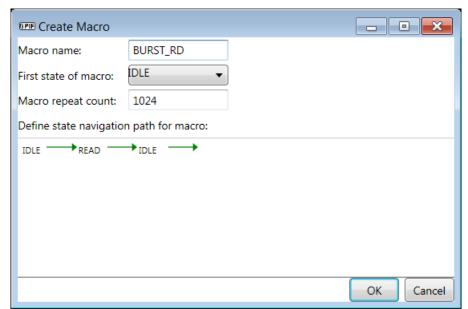

|     | 7.6.8       | Macro                     |                                              | 151 |  |  |

| 7.7 | <b>GPIF</b> | II Constrai               | nts                                          | 151 |  |  |

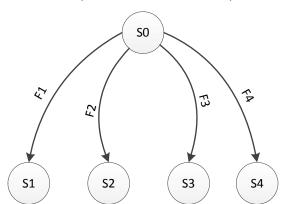

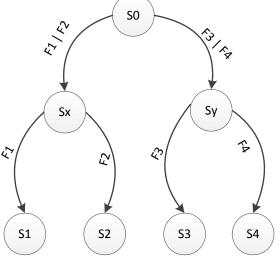

|    |       |            |                    | ates                                                              |     |

|----|-------|------------|--------------------|-------------------------------------------------------------------|-----|

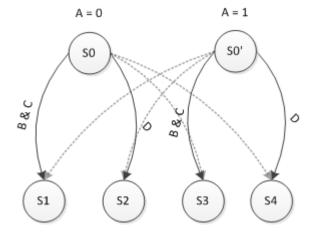

|    |       | 7.7.2 N    | Mirror Sta         | ate Rules                                                         | 152 |

|    |       | 7.7.3 N    | Mirror Sta         | ate Example                                                       | 153 |

|    |       | 7.7.4      | Guideline          | es for Transition Equation Entry                                  | 154 |

|    |       | 7.7.5 I    | ntermed            | liate States                                                      | 155 |

|    | 7.8   | Initializa | tion and           | Configuration of GPIF II Block                                    | 156 |

|    |       | 7.8.1      | SPIF II S          | State Machine Control                                             | 156 |

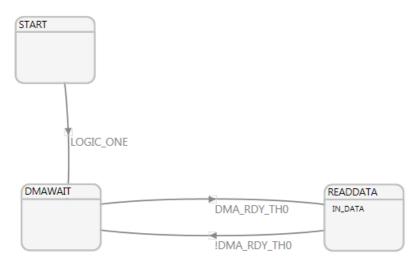

|    | 7.9   | Perform    | ing Rea            | d and Write Operations Using GPIF II                              | 156 |

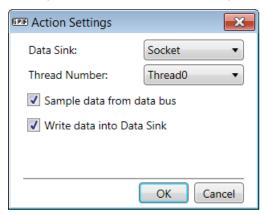

|    | 7.10  |            |                    | Creation in FX3 Firmware to Perform GPIF II to USB Data Transfers |     |

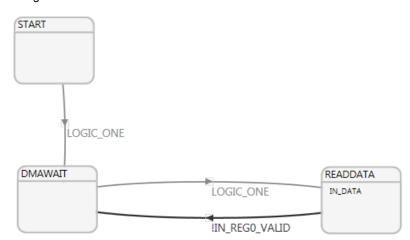

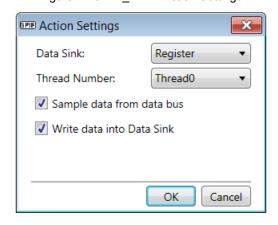

|    | 7.11  |            |                    | achine to Read Data into a Socket                                 |     |

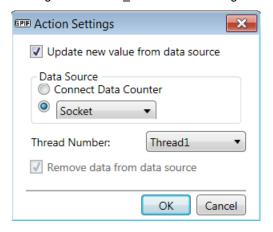

|    | 7.11  |            |                    | Creation in FX3 Firmware to Perform USB to GPIF II Data Transfers |     |

|    | –     |            |                    |                                                                   |     |

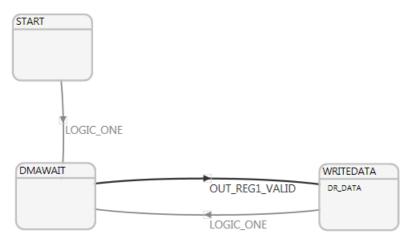

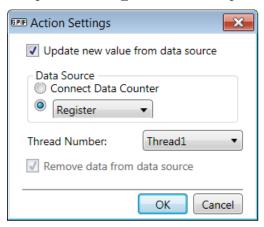

|    | 7.13  |            |                    | achine to Drive Data from Socket as Data Source                   |     |

|    |       |            | •                  | alues                                                             |     |

|    | 7.14  |            |                    | nd Write over Registers                                           |     |

|    | 7.15  | Impleme    | enting Sy          | ynchronous Slave FIFO Interface                                   | 162 |

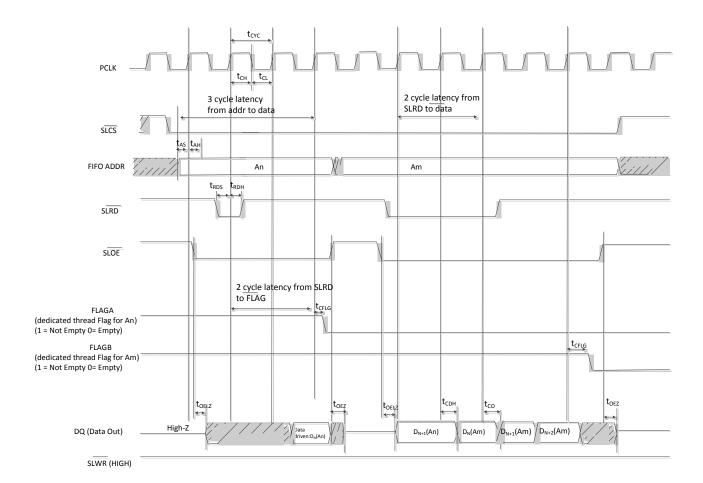

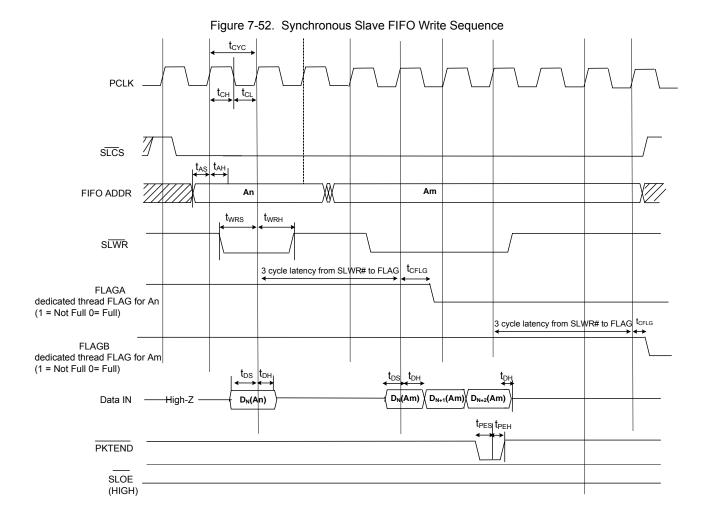

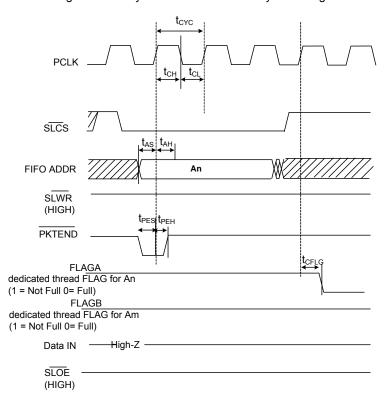

|    | 7.16  | Synchro    | nous Sl            | ave FIFO Access Sequence and Interface Timing                     | 166 |

|    |       |            |                    | nous Slave FIFO Read Sequence Description                         |     |

|    |       | 7.16.2     | Synchror           | nous Slave FIFO Write Sequence Description                        | 169 |

|    |       | 7.16.3     | Slave FII          | FO Interface Logical Diagram                                      | 170 |

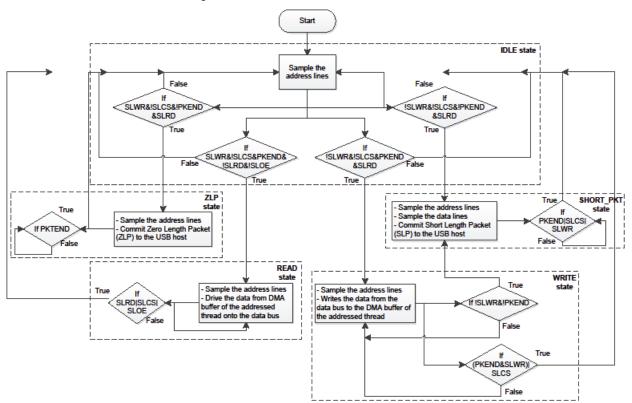

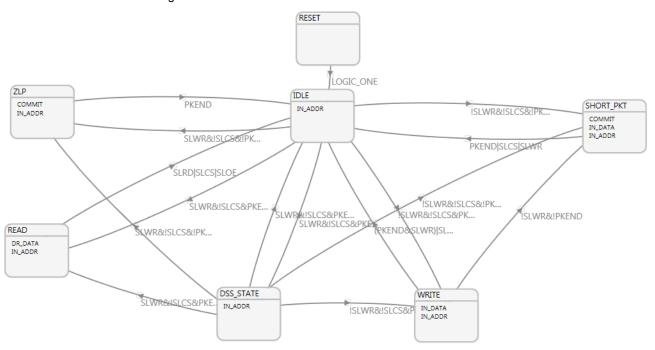

|    |       | 7.16.4     | SPIF II S          | State Machine of Slave FIFO Interface                             | 170 |

| 0  | l a [ | )          | <b>-</b>           | Devinherale (LDD)                                                 | 470 |

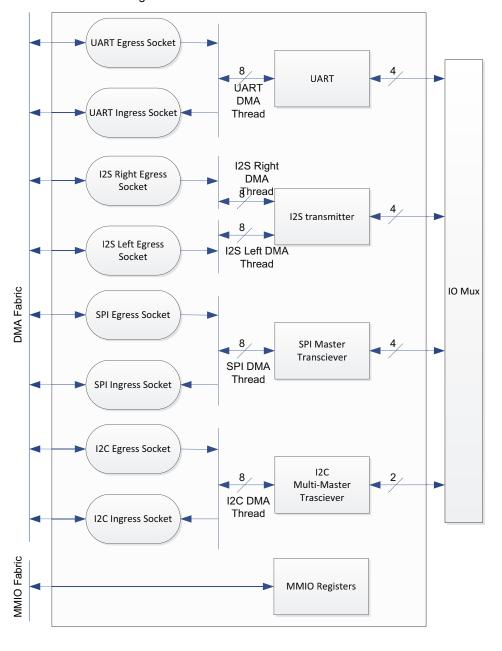

| 8. |       |            |                    | Peripherals (LPP)                                                 | 173 |

|    | 8.1   |            |                    |                                                                   |     |

|    |       |            |                    | k Features                                                        |     |

|    |       |            |                    | face Overview                                                     |     |

|    | 8.2   |            | •                  | ions Overview                                                     |     |

|    |       |            |                    | nd Initialization                                                 |     |

|    |       |            |                    | e                                                                 |     |

|    |       |            |                    | nsfer                                                             |     |

|    |       | -          | 3.2.3.1            | Programming Model                                                 |     |

|    |       |            | 3.2.3.2<br>3.2.3.3 | Register-Based I2C Transfers  DMA-Based I2C Transfers             |     |

|    |       |            | 3.2.3.4            | Starting a Transaction                                            |     |

|    |       | _          | 3.2.3.5            |                                                                   |     |

|    |       | _          | 3.2.3.6            | Multimaster Arbitration                                           |     |

|    |       | 8          | 3.2.3.7            | Error Conditions                                                  |     |

|    |       | 8.2.4 E    | Example            | S                                                                 | 178 |

|    |       | 8          | 3.2.4.1            | Initialize I2C Block                                              | 178 |

|    |       | 8          | 3.2.4.2            | Configure I2C Block                                               |     |

|    |       | _          | 3.2.4.3            | Reads and Writes Using Register Transfers                         |     |

|    |       |            | 3.2.4.4            | Reads and Writes Using DMA Transfers                              |     |

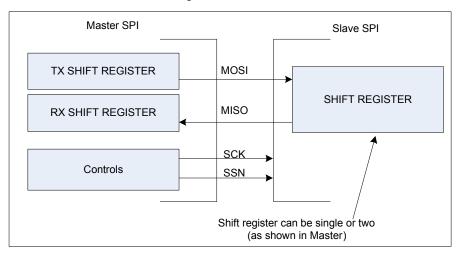

|    | 8.3   |            | •                  | ıl Interface                                                      |     |

|    |       |            |                    | k Features                                                        |     |

|    |       |            |                    | face Overview                                                     |     |

|    |       |            |                    | Operations Overview                                               |     |

|    |       | -          | 3.3.3.1            | Reset and Initialization                                          |     |

|    |       | _          | 3.3.3.2            | Modes Governing Transfers                                         |     |

|    |       | 8.3.4      | SSIN COR           | ntrol Configurations                                              | 183 |

|     | 8.3.5  | Data Tra    | insfers                                                             | 184        |

|-----|--------|-------------|---------------------------------------------------------------------|------------|

| 8.4 | Progra | amming M    | lodel                                                               | 184        |

|     | 8.4.1  |             | -Based Transfers                                                    |            |

|     | 8.4.2  | •           | sed Transfers                                                       |            |

| 8.5 |        |             |                                                                     |            |

| 0.5 | 8.5.1  | •           | SPI Block                                                           |            |

|     |        |             | e SPI Block                                                         |            |

|     |        | •           | nd Writes Using Register Transfers                                  |            |

|     |        |             | nd Writes Using DMA Transfers                                       |            |

|     |        |             | <u> </u>                                                            |            |

| 8.6 |        | •           | chronous Receiver Transmitter                                       |            |

|     | 8.6.1  |             | lock features                                                       |            |

|     |        |             | verview                                                             |            |

| 8.7 | FX3 L  | JART Ope    | rations Overview                                                    | 190        |

|     | 8.7.1  | Reset ar    | nd Initialization                                                   | 190        |

|     | 8.7.2  | Program     | ming Model                                                          | 190        |

|     | 8.7.3  | Register    | -Based Transfers                                                    | 190        |

|     |        | 8.7.3.1     |                                                                     |            |

|     |        | 8.7.3.2     | Error Conditions                                                    | 191        |

|     | 8.7.4  | Example     | 9\$                                                                 | 191        |

|     |        | 8.7.4.1     | Initialize UART Block                                               |            |

|     |        | 8.7.4.2     | FX3 Firmware to Send UART Messages and to Receive Fixed Byt         | es of Text |

|     |        |             | 191                                                                 |            |

| 8.8 | Integr | ated Interd | chip Sound Interface                                                | 193        |

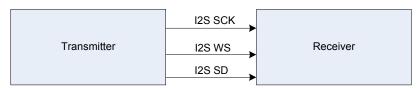

|     | 8.8.1  | I2S Bloc    | k Features                                                          | 193        |

|     | 8.8.2  | I2S Ove     | rview                                                               | 193        |

|     | 8.8.3  | FX3 I2S     | Operations Overview                                                 | 194        |

|     | 8.8.4  | Program     | ming Model                                                          | 194        |

|     |        | 8.8.4.1     | Start Transmission                                                  | 194        |

|     |        | 8.8.4.2     | Mute Condition                                                      | 194        |

|     |        | 8.8.4.3     | Pause Condition                                                     |            |

|     |        | 8.8.4.4     | Buffer Underflow                                                    |            |

|     |        | 8.8.4.5     | Stop Event                                                          |            |

|     |        | 8.8.4.6     | Fixed Clock Mode                                                    |            |

|     |        | 8.8.4.7     | Data Shift Mode                                                     |            |

|     |        | 8.8.4.8     | Padding                                                             |            |

|     |        |             | Error Conditions                                                    |            |

|     |        |             | Examples                                                            |            |

|     |        |             | Initialize I2S Block                                                |            |

|     |        |             | Configure I2S Interface                                             |            |

|     |        | 0.0.4.13    | Transferring Data from USB Interface to I2S Interface Using DMA 196 | rransiers  |

| 8.9 | GPIO   |             |                                                                     | 198        |

|     | 8.9.1  | GPIO Fe     | eatures                                                             | 198        |

|     |        |             | verview                                                             |            |

|     | 8.9.3  |             | ming Model                                                          |            |

|     |        | 8.9.3.1     | Reset and Initialization                                            |            |

|     | 8.9.4  |             | 98                                                                  |            |

|     | 2.2    | 8.9.4.1     | Initialize GPIO Block                                               |            |

|     |        | 8.9.4.2     |                                                                     |            |

|     |        |             | Configure GPIO[50] to Generate PWM Output                           |            |

| 9. 8  | otora | ge Po  | rts                |                                                          | 203 |

|-------|-------|--------|--------------------|----------------------------------------------------------|-----|

|       | 9.1   | Storag | ge Interfac        | ce Block Features                                        | 203 |

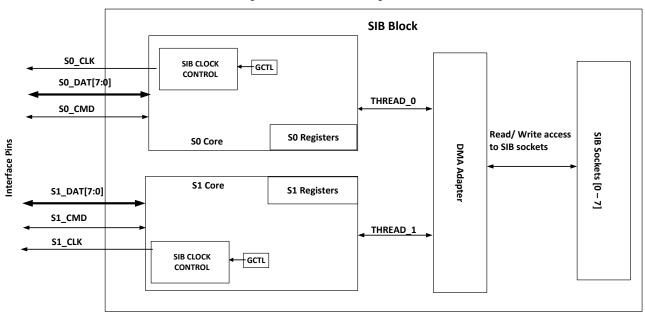

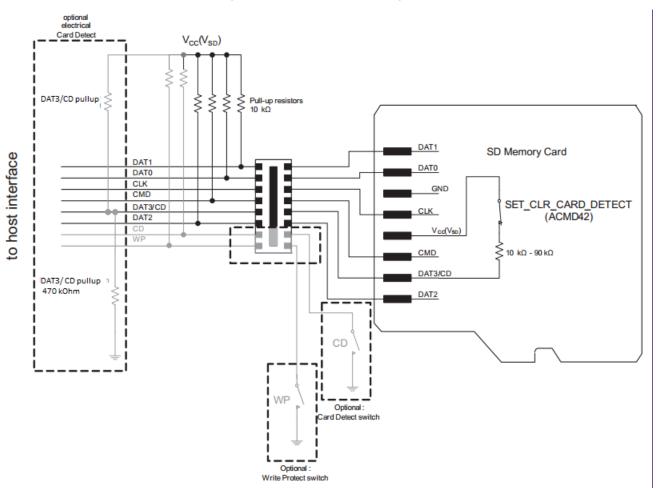

|       | 9.2   | Block  | Diagram.           |                                                          | 203 |

|       | 9.3   | Storag | ge Interfac        | ce (S-Port)                                              | 205 |

|       | 9.4   | _      |                    | O Interface                                              |     |

|       | • • • | 9.4.1  |                    | C Interface Overview                                     |     |

|       |       | 9.4.2  |                    | terface Overview                                         |     |

|       | 9.5   | FX3S   |                    | perations Overview                                       |     |

|       | 5.5   | 9.5.1  |                    | nitialization and Configuration                          |     |

|       |       | 5.5.1  | 9.5.1.1            | Configuring the FX3S I/O Matrix                          |     |

|       |       |        | 9.5.1.2            | Setting S-Port Interface Parameters                      |     |

|       |       |        | 9.5.1.3            | Starting the Storage Driver                              |     |

|       |       |        | 9.5.1.4            | Setting the S-Port Clock                                 |     |

|       |       |        | 9.5.1.5            | Sending SD/MMC/SDIO Commands                             |     |

|       |       |        | 9.5.1.6            | Handling SIB Events                                      | 214 |

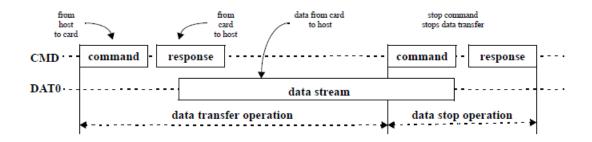

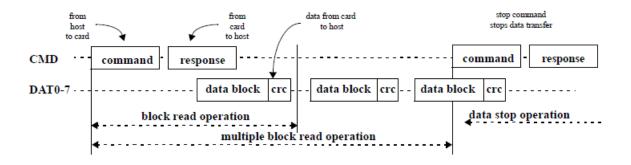

|       |       | 9.5.2  | Reads a            | and Writes to SD/ MMC Using DMA Transfers                |     |

|       |       |        | 9.5.2.1            | Sending Vendor Commands to SD/ MMC                       |     |

|       |       |        | 9.5.2.2            | Setting the Granularity of Write Operations              |     |

|       |       |        | 9.5.2.3            | Checking Card Status                                     |     |

|       |       |        | 9.5.2.4            | Aborting Ongoing Transaction to S-Port                   |     |

|       |       | 9.5.3  |                    | with SDIO Cards                                          |     |

|       |       |        | 9.5.3.1            | Configuration and Initialization                         |     |

|       |       |        | 9.5.3.2<br>9.5.3.3 | Reads and Writes from SDIO Card Registers                |     |

|       |       |        | 9.5.3.4            | IO_RW_DIRECT Command (CMD52) Setting Function Block Size |     |

|       |       |        | 9.5.3.4            | Initialization and Operation of SDIO Functions           |     |

|       |       |        | 9.5.3.6            | SDIO Interrupts                                          |     |

|       |       |        | 9.5.3.7            | Enabling and Disabling SDIO Interrupts                   |     |

|       |       |        | 9.5.3.8            | Handling SDIO Interrupts                                 |     |

|       | 9.6   | FX3S-  |                    | Features                                                 |     |

|       | 5.0   | 9.6.1  |                    | sertion and Removal Detection Mechanism                  |     |

|       |       | 9.6.2  |                    | g Card Detection in Software                             |     |

|       |       | 9.6.3  |                    | otection                                                 |     |

|       |       | 9.6.4  |                    | C CLOCK STOP                                             |     |

|       |       | 9.6.5  |                    | COutput Clock Stop                                       |     |

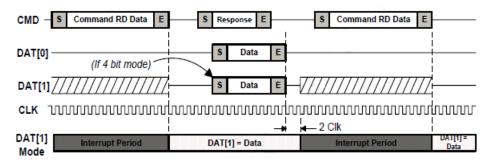

|       |       |        |                    | ead-Wait/ Suspend-Resume Feature                         |     |

|       |       | 3.0.0  | 9.6.6.1            | Read-Wait                                                |     |

|       |       |        | 9.6.6.2            | Suspend-Resume Feature                                   |     |

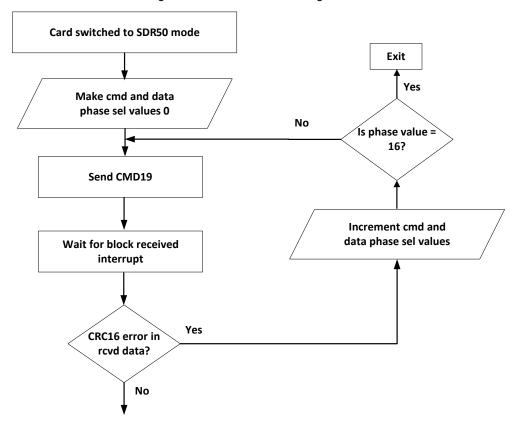

|       |       |        | 9.6.6.3            | SD3.0 Host Tuning Feature                                |     |

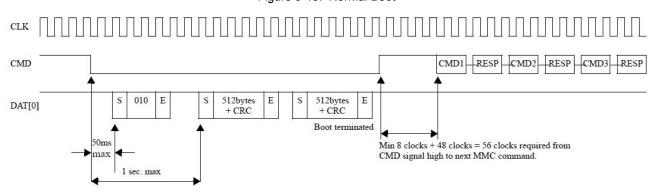

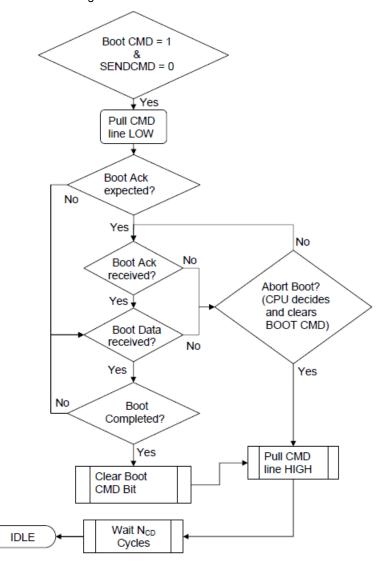

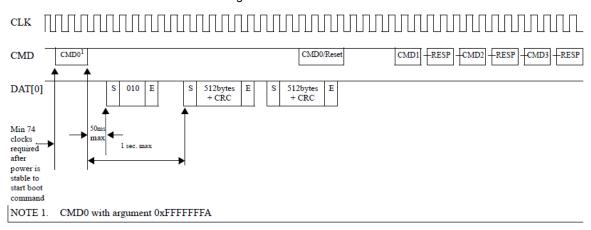

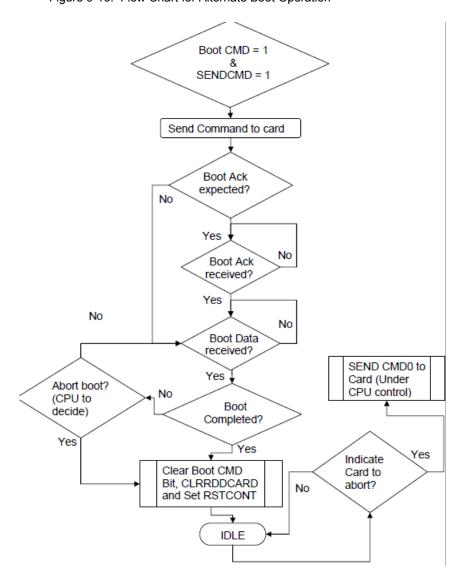

|       |       |        | 9.6.6.4            | Normal and Alternate eMMC4.4 Boot                        |     |

|       | _     |        |                    |                                                          |     |

| 10. F | Regis |        |                    |                                                          | 235 |

|       | 10.1  |        |                    |                                                          |     |

|       |       | -      |                    | ntions                                                   |     |

|       | 10.3  |        |                    | upt Controller (VIC) Registers                           |     |

|       |       | 10.3.1 | _                  | RQ_STATUS                                                |     |

|       |       | 10.3.2 | _                  | FIQ_STATUS                                               |     |

|       |       | 10.3.3 | _                  | RAW_STATUS                                               |     |

|       |       | 10.3.4 | · VIC II           | NT_SELECT                                                | 240 |

|      | 10.3.5   | VIC_INT_ENABLE                | 241 |

|------|----------|-------------------------------|-----|

|      | 10.3.6   | VIC_INT_CLEAR                 | 242 |

|      | 10.3.7   | VIC_PRIORITY_MASK             | 243 |

|      | 10.3.8   | VIC VEC ADDRESS               | 244 |

|      | 10.3.9   | VIC_VECT_PRIORITY             | 245 |

|      | 10.3.10  | VIC_ADDRESS                   | 246 |

| 10.4 | Global C | ontroller Registers           | 247 |

|      | 10.4.1   | GCTL_IOMATRIX                 | 247 |

|      | 10.4.2   | GCTL_GPIO_SIMPLE              | 248 |

|      | 10.4.3   | GCTL_GPIO_COMPLEX             | 250 |

|      | 10.4.4   | GCTL_DS                       | 252 |

|      | 10.4.5   | GCTL_WPU_CFG                  | 254 |

|      | 10.4.6   | GCTL_WPD_CFG                  | 256 |

|      | 10.4.7   | GCTL_IOPOWER                  | 258 |

|      | 10.4.8   | GCTL_IOPOWER_INTR             | 260 |

|      | 10.4.9   | GCTL_IOPOWER_INTR_MASK        | 262 |

|      | 10.4.10  | GCTL_SW_INT                   | 264 |

|      | 10.4.11  | GCTL_PLL_CFG                  |     |

|      | 10.4.12  | GCTL_CPU_CLK_CFG              | 267 |

|      | 10.4.13  | GCTL_UIB_CORE_CLK             | 268 |

|      | 10.4.14  | GCTL_PIB_CORE_CLK             | 269 |

|      | 10.4.15  | GCTL_GPIO_FAST_CLK            | 270 |

|      | 10.4.16  | GCTL_GPIO_SLOW_CLK            | 272 |

|      | 10.4.17  | GCTL_I2C_CORE_CLK             | 273 |

|      | 10.4.18  | GCTL_UART_CORE_CLK            |     |

|      | 10.4.19  | GCTL_SPI_CORE_CLK             | 275 |

|      | 10.4.20  | GCTL_I2S_CORE_CLK             | 276 |

| 10.5 | Global C | ontroller Always On Registers | 277 |

|      | 10.5.1   | GCTL_WAKEUP_EN                | 277 |

|      | 10.5.2   | GCTL_WAKEUP_POLARITY          | 279 |

|      | 10.5.3   | GCTL_WAKEUP_EVENT             | 281 |

|      | 10.5.4   | GCTL_FREEZE                   | 283 |

|      | 10.5.5   | GCTL_WATCHDOG_CS              | 284 |

|      | 10.5.6   | GCTL_WATCHDOG_TIMER0          | 286 |

|      | 10.5.7   | GCTL_WATCHDOG_TIMER1          | 287 |

| 10.6 | PIB Regi | sters                         | 288 |

|      | 10.6.1   | PIB CONFIG                    |     |

|      | 10.6.2   | PIB INTR                      | 290 |

|      | 10.6.3   | PIB_INTR_MASK                 | 292 |

|      | 10.6.4   | PIB CLOCK DETECT              | 294 |

|      | 10.6.5   | PIB RD MAILBOX                | 295 |

|      | 10.6.6   | PIB_WR_MAILBOX                |     |

|      | 10.6.7   | PIB_ERROR                     |     |

|      | 10.6.8   | PIB_EOP_EOT                   |     |

|      | 10.6.9   | PIB DLL CTRL                  |     |

|      | 10.6.10  | PIB WR THRESHOLD              |     |

|      | 10.6.11  | PIB_RD_THRESHOLD              |     |

|      |          | PIB_ID                        |     |

|      |          |                               |     |

|      | 10.6.13 | PIB_POWER                    | 307 |

|------|---------|------------------------------|-----|

| 10.7 | GPIF Re | gistersgisters               | 308 |

|      | 10.7.1  | GPIF_CONFIG                  | 308 |

|      | 10.7.2  | GPIF_BUS_CONFIG              | 310 |

|      | 10.7.3  | GPIF BUS CONFIG2             | 312 |

|      | 10.7.4  | GPIF_AD_CONFIG               | 313 |

|      | 10.7.5  | GPIF_STATUS                  | 315 |

|      | 10.7.6  | GPIF_INTR                    | 317 |

|      | 10.7.7  | GPIF_INTR_MASK               |     |

|      | 10.7.8  | GPIF_CTRL_BUS_DIRECTION      |     |

|      | 10.7.9  | GPIF_CTRL_BUS_DEFAULT        | 322 |

|      | 10.7.10 | GPIF_CTRL_BUS_POLARITY       | 323 |

|      | 10.7.11 | GPIF_CTRL_BUS_TOGGLE         | 324 |

|      | 10.7.12 | GPIF_CTRL_BUS_SELECT         | 325 |

|      | 10.7.13 | GPIF_CTRL_COUNT_CONFIG       | 326 |

|      | 10.7.14 | GPIF_CTRL_COUNT_RESET        |     |

|      | 10.7.15 | GPIF_CTRL_COUNT_LIMIT        | 328 |

|      | 10.7.16 | GPIF_ADDR_COUNT_CONFIG       | 329 |

|      | 10.7.17 | GPIF_ADDR_COUNT_RESET        | 330 |

|      | 10.7.18 | GPIF_ADDR_COUNT_LIMIT        | 331 |

|      | 10.7.19 | GPIF_STATE_COUNT_CONFIG      |     |

|      | 10.7.20 | GPIF_STATE_COUNT_LIMIT       |     |

|      | 10.7.21 | GPIF_DATA_COUNT_CONFIG       | 334 |

|      | 10.7.22 | GPIF_DATA_COUNT_RESET        | 335 |

|      | 10.7.23 | GPIF_DATA_COUNT_LIMIT        | 336 |

|      | 10.7.24 | GPIF_CTRL_COMP_VALUE         | 337 |

|      | 10.7.25 | GPIF_CTRL_COMP_MASK          | 338 |

|      | 10.7.26 | GPIF_DATA_COMP_VALUE         | 339 |

|      | 10.7.27 | GPIF_DATA_COMP_MASK          | 340 |

|      | 10.7.28 | GPIF_ADDR_COMP_VALUE         | 341 |

|      | 10.7.29 | GPIF_ADDR_COMP_MASK          | 342 |

|      | 10.7.30 | GPIF_DATA_CTRL               | 343 |

|      | 10.7.31 | GPIF_INGRESS_DATA            | 344 |

|      | 10.7.32 | GPIF_EGRESS_DATA             | 345 |

|      | 10.7.33 | GPIF_INGRESS_ADDRESS         | 346 |

|      | 10.7.34 | GPIF_EGRESS_ADDRESS          | 347 |

|      | 10.7.35 | GPIF_THREAD_CONFIG           | 348 |

|      | 10.7.36 | GPIF_LAMBDA_STAT             | 350 |

|      | 10.7.37 | GPIF_ALPHA_STAT              | 351 |

|      | 10.7.38 | GPIF_BETA_STAT               | 352 |

|      | 10.7.39 | GPIF_WAVEFORM_CTRL_STAT      | 353 |

|      | 10.7.40 | GPIF_WAVEFORM_SWITCH         | 355 |

|      | 10.7.41 | GPIF_WAVEFORM_SWITCH_TIMEOUT | 357 |

|      | 10.7.42 | GPIF_CRC_CONFIG              | 358 |

|      | 10.7.43 | GPIF_CRC_DATA                | 359 |

|      | 10.7.44 | GPIF_BETA_DEASSERT           | 360 |

|      | 10.7.45 | GPIF_FUNCTION                | 361 |

|      | 10.7.46 | GPIF_LEFT_WAVEFORM           | 362 |

|      | 10.7.47 | GPIF_RIGHT_WAVEFORM          | 365 |

| 10.8  | P-Port R | egisters                         | 368 |

|-------|----------|----------------------------------|-----|

|       | 10.8.1   | PP_ID                            | 368 |

|       | 10.8.2   | PP_INIT                          | 369 |

|       | 10.8.3   | PP_CONFIG                        | 370 |

|       | 10.8.4   | PP_INTR_MASK                     | 372 |

|       | 10.8.5   | PP_DRQR5_MASK                    | 373 |

|       | 10.8.6   | PP_SOCK_MASK                     | 374 |

|       | 10.8.7   | PP_ERROR                         | 375 |

|       | 10.8.8   | PP_DMA_XFER                      | 376 |

|       | 10.8.9   | PP_DMA_SIZE                      | 377 |

|       | 10.8.10  | PP_WR_MAILBOX                    | 378 |

|       | 10.8.11  | PP_MMIO_ADDR                     | 380 |

|       | 10.8.12  | PP_MMIO_DATA                     | 381 |

|       | 10.8.13  | PP_MMIO                          | 382 |

|       | 10.8.14  | PP_EVENT                         | 383 |

|       | 10.8.15  | PP_RD_MAILBOX                    |     |

|       |          | PP_SOCK_STAT                     |     |

|       | 10.8.17  | PP_BUF_SIZE_CNT                  | 388 |

| 10.9  | USB Por  | t Registers                      | 389 |

|       | 10.9.1   | UIB_INTR                         | 389 |

|       | 10.9.2   | UIB_INTR_MASK                    | 391 |

|       | 10.9.3   | UIB_ID                           | 393 |

|       | 10.9.4   | UIB_POWER                        | 394 |

| 10.10 | USB2 HS  | S/FS/LS PHY Registers            | 395 |

|       | 10.10.1  | PHY_CLK_AND_TEST                 | 395 |

|       | 10.10.2  | PHY_CONF                         | 397 |

|       | 10.10.3  | PHY_CHIRP                        | 399 |

| 10.11 | USB2 De  | evice Controller Registers       | 400 |

|       |          | DEV_CS                           |     |

|       |          | DEV FRAMECNT                     |     |

|       | 10.11.3  | DEV PWR CS                       | 403 |

|       | 10.11.4  | DEV_SETUPDAT                     |     |

|       | 10.11.5  | DEV_TOGGLE                       | 406 |

|       | 10.11.6  | DEV_EPI_CS                       | 408 |

|       | 10.11.7  | DEV_EPI_XFER_CNT                 | 410 |

|       | 10.11.8  | DEV_EPO_CS                       | 411 |

|       | 10.11.9  | DEV_EPO_XFER_CNT                 | 413 |

|       | 10.11.10 | DEV_CTRL_INTR_MASK               | 414 |

|       | 10.11.11 | DEV_CTRL_INTR                    | 415 |

|       | 10.11.12 | DEV_EP_INTR_MASK                 | 416 |

|       | 10.11.13 | DEV_EP_INTR                      | 417 |

| 10.12 | USB Cor  | ntroller Miscellaneous Registers | 418 |

|       | 10.12.1  | CHGDET_CTRL                      |     |

|       | 10.12.2  | CHGDET_INTR                      | 420 |

|       |          | CHGDET_INTR_MASK                 |     |

|       |          | OTG_CTRL                         |     |

|       | 10.12.5  | OTG_INTR                         | 424 |

|       | 10.12.6  | OTG_INTR_MASK                    | 425 |

| 10.12.7        | OTG_TIMER                | 426 |

|----------------|--------------------------|-----|

| 10.13 USB End  | Point Manager Registers  | 427 |

|                | EEPM_CS                  |     |

|                | IEPM CS                  |     |

| 10.13.3        | IEPM MULT                | 430 |

| 10.13.4        | EEPM_ENDPOINT            | 431 |

| 10.13.5        | IEPM_ENDPOINT            | 432 |

| 10.13.6        | IEPM_FIFO                | 433 |

| 10.14 USB2 Ho  | ost Controller Registers | 434 |

|                | HOST CS                  |     |

|                | HOST_EP_INTR             |     |

|                | HOST_EP_INTR_MASK        |     |

|                | HOST_TOGGLE              |     |

| 10.14.5        | HOST_SHDL_CS             | 439 |

| 10.14.6        | HOST_SHDL_SLEEP          | 441 |

| 10.14.7        | HOST_RESP_BASE           | 442 |

| 10.14.8        | HOST_RESP_CS             | 443 |

|                | HOST_ACTIVE_EP           |     |

| 10.14.10       | OHCI_REVISION            | 445 |

| 10.14.11       | OHCI_CONTROL             | 446 |

| 10.14.12       | OHCI_COMMAND_STATUS      | 447 |

| 10.14.13       | OHCI_INTERRUPT_STATUS    | 448 |

| 10.14.14       | OHCI_INTERRUPT_ENABLE    | 449 |

| 10.14.15       | OHCI_INTERRUPT_DISABLE   | 450 |

| 10.14.16       | OHCI_FM_INTERVAL         | 451 |

| 10.14.17       | OHCI_FM_REMAINING        | 452 |

| 10.14.18       | OHCI_FM_NUMBER           | 453 |

|                | OHCI_PERIODIC_START      |     |

| 10.14.20       | OHCI_LS_THRESHOLD        | 455 |

| 10.14.21       | OHCI_RH_PORT_STATUS      | 456 |

|                | OHCI_EOF                 |     |

| 10.14.23       | EHCI_HCCPARAMS           | 459 |

|                | EHCI_USBCMD              |     |

|                | EHCI_USBSTS              |     |

|                | EHCI_USBINTR             |     |

|                | EHCI_FRINDEX             |     |

|                | EHCI_CONFIGFLAG          |     |

|                | EHCI_PORTSC              |     |

|                | EHCI_EOF                 |     |

|                | SHDL_CHNG_TYPE           |     |

|                | SHDL_STATE_MACHINE       |     |

|                | SHDL_INTERNAL_STATUS     |     |

|                | SHDL_OHCI                |     |

| 10.14.35       | SHDL_EHCI                | 477 |

| 10.15 USB3 Lin | k Controller Registers   | 481 |