SERIES

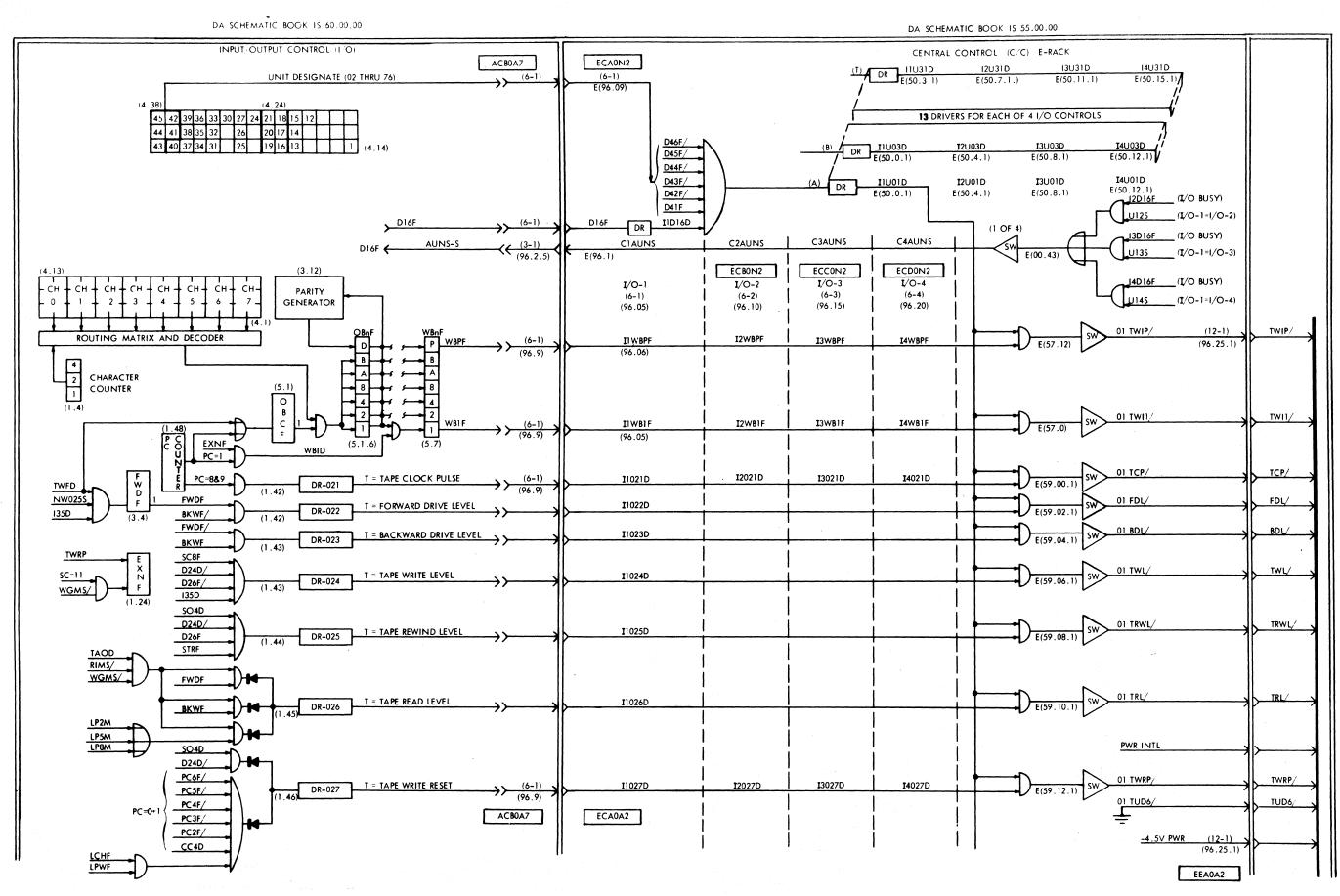

# B5500 B5283 INPUT/OUTPUT

# **TRAINING MANUAL**

PROPERTY OF AND TO BE RETURNED TO

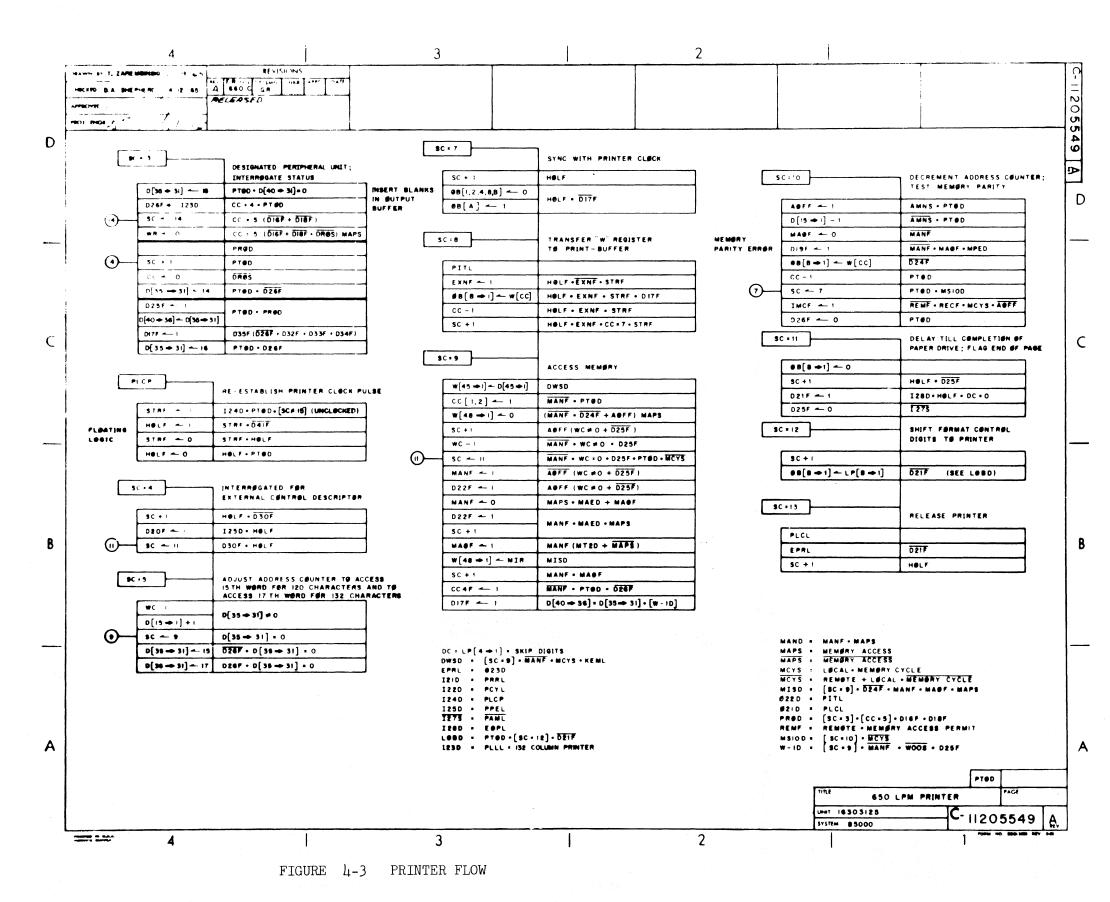

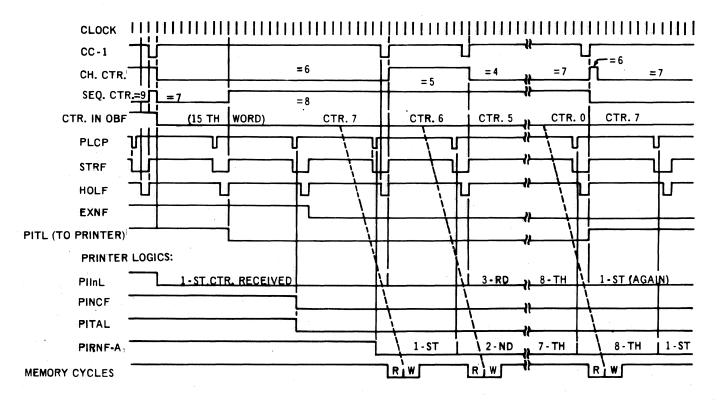

Burroughs

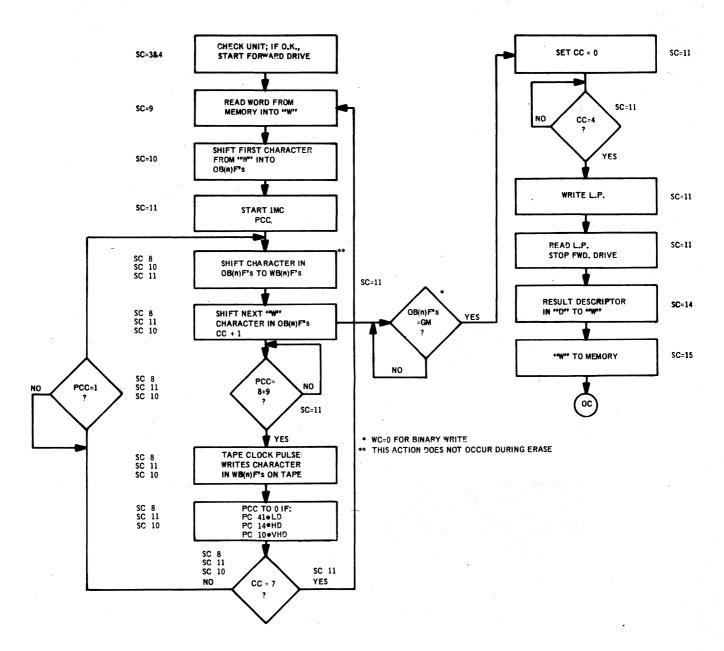

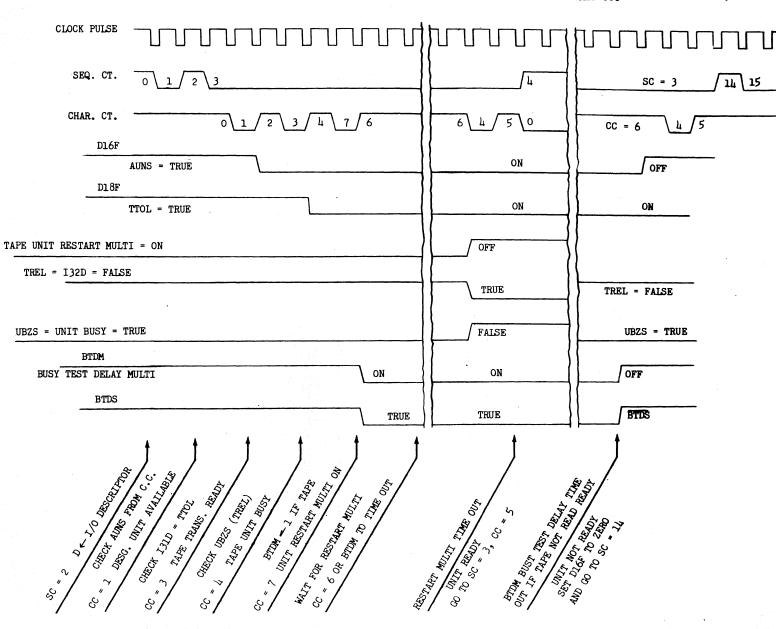

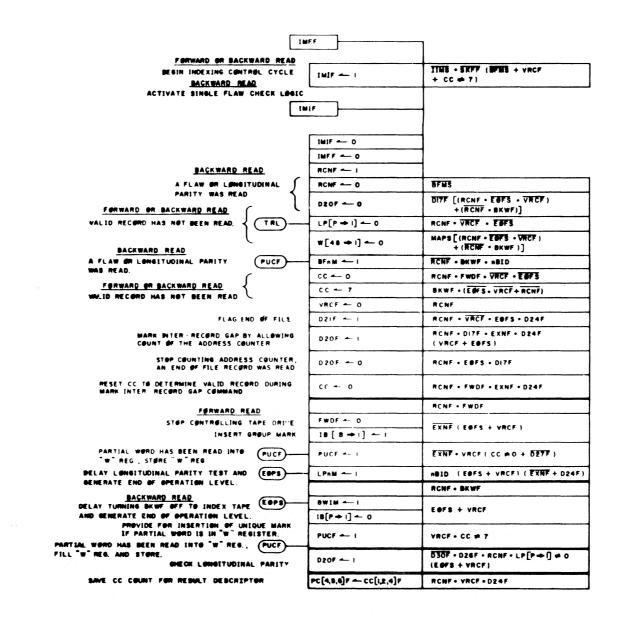

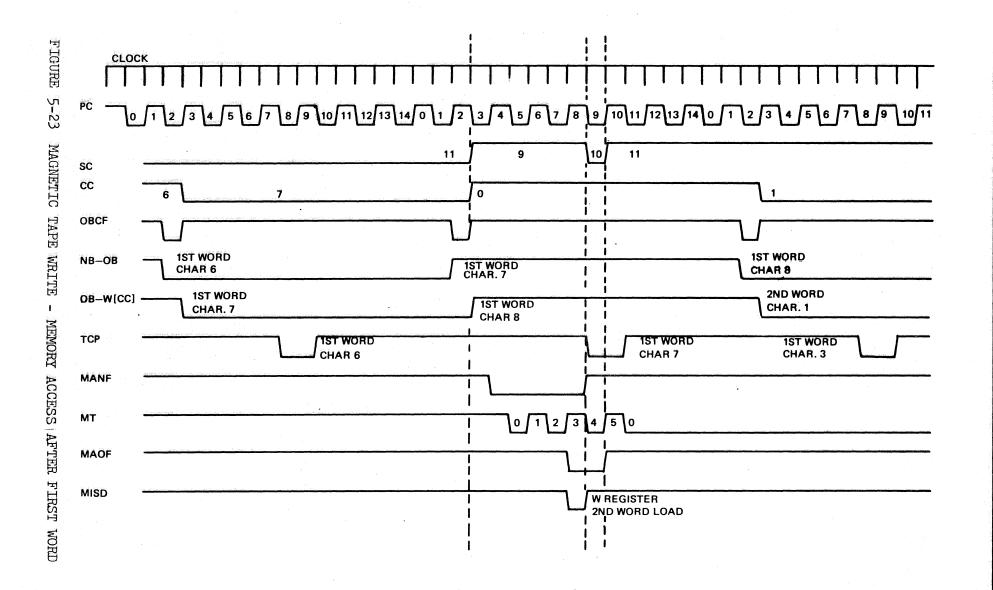

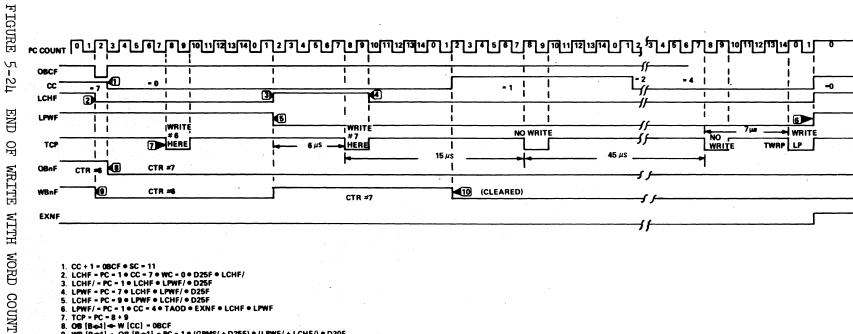

### TABLE OF CONTENTS

| SECTION | TITLE                                                                                                                                                                                                                                                                                                                                                                                                      | PAGE                                                                                              |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| l       | INTRODUCTION OF I/O SYSTEM<br>General                                                                                                                                                                                                                                                                                                                                                                      | 1-1<br>1-2<br>1-6<br>1-7<br>1-16<br>1-25<br>1-26                                                  |

| 2       | CARD READER CONTROL<br>General                                                                                                                                                                                                                                                                                                                                                                             | 2-1<br>2-1<br>2-6<br>2-7<br>2-8                                                                   |

| 3       | CARD PUNCH CONTROL<br>Introduction                                                                                                                                                                                                                                                                                                                                                                         | 3-1<br>3-2<br>3-5<br>3-5<br>3-10<br>3-10<br>3-11                                                  |

| 4       | LINE PRINTER CONTROL<br>General                                                                                                                                                                                                                                                                                                                                                                            | 4-1<br>4-3<br>4-4<br>4-5<br>4-7                                                                   |

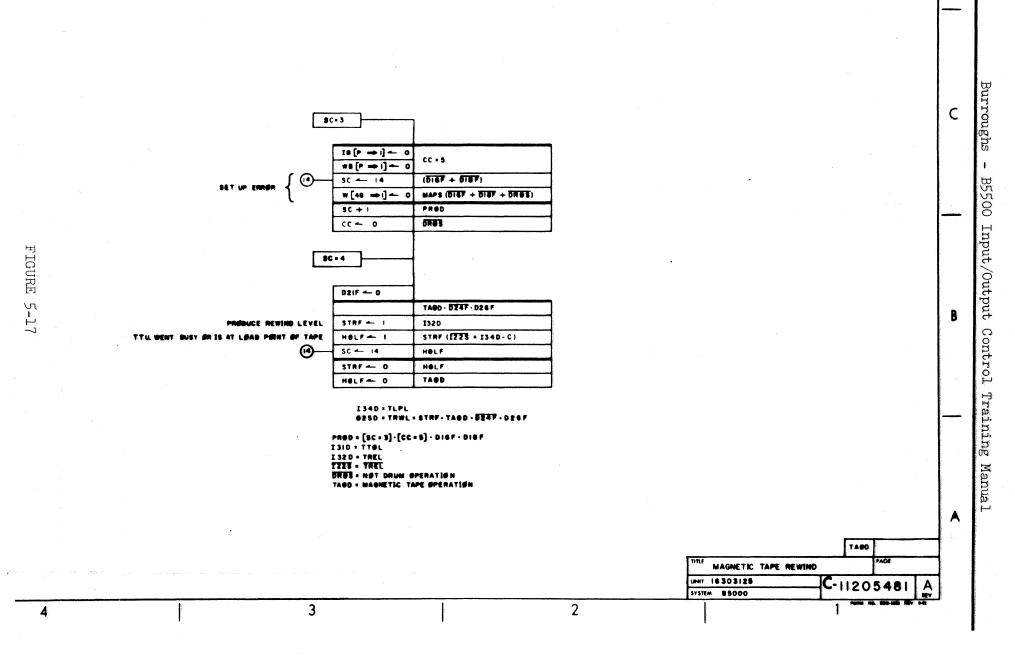

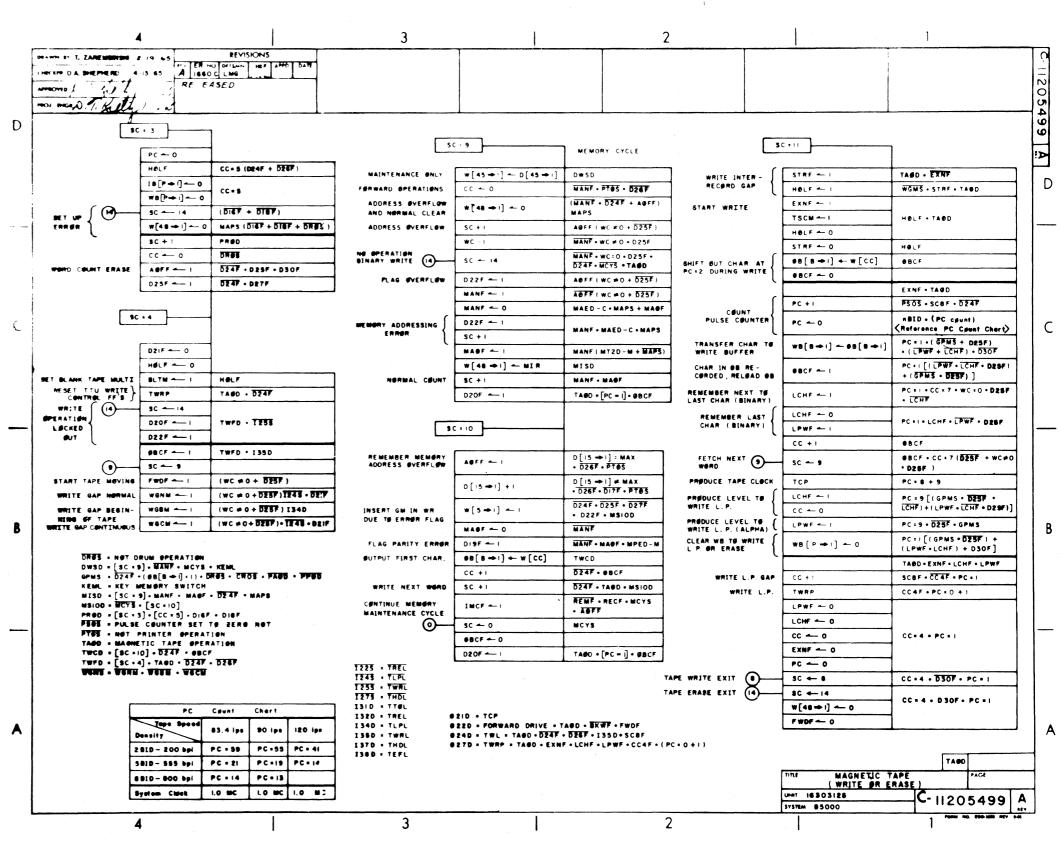

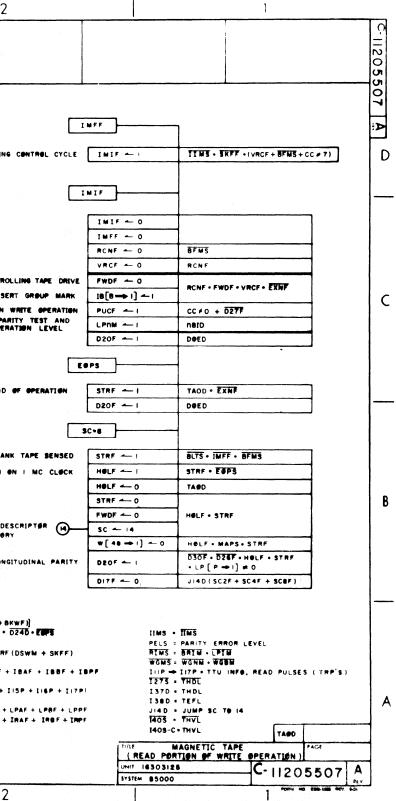

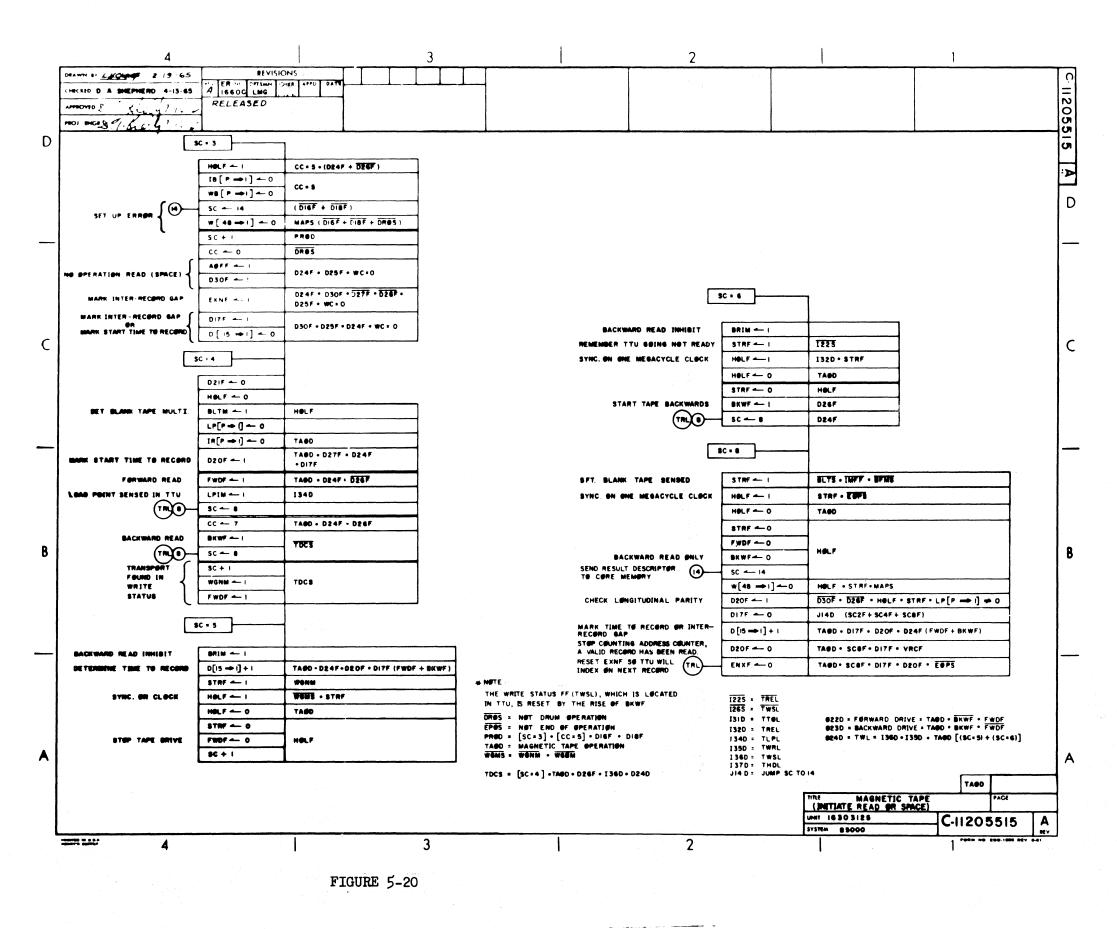

| 5       | MAGNETIC TAPE CONTROLOperational CharacteristicsInformation CharacteristicsPhysical and Dimensional CharacteristicsTape Operation DescriptorsTape Operations Containing Question MarksGlossary of TermsBasic Write OperationBinary Write - No OperationAlpha Write With Group Mark TerminationWord Count TerminationPost-Write Read OperationBasic Read OperationEnd of File Record - ForwardBackward Read | 5-1<br>5-2<br>5-5<br>5-11<br>5-18<br>5-18<br>5-47<br>5-60<br>5-66<br>5-66<br>5-66<br>5-79<br>5-79 |

i

## TABLE OF CONTENTS CONTINUED

| SECTION | TITLE                                           | PAGE                                      |

|---------|-------------------------------------------------|-------------------------------------------|

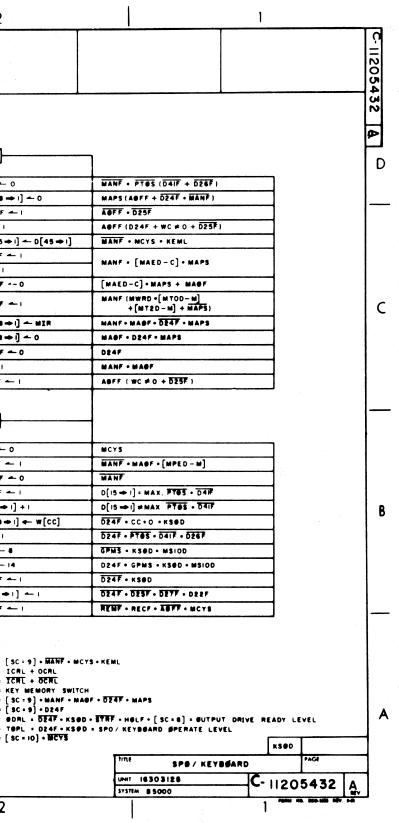

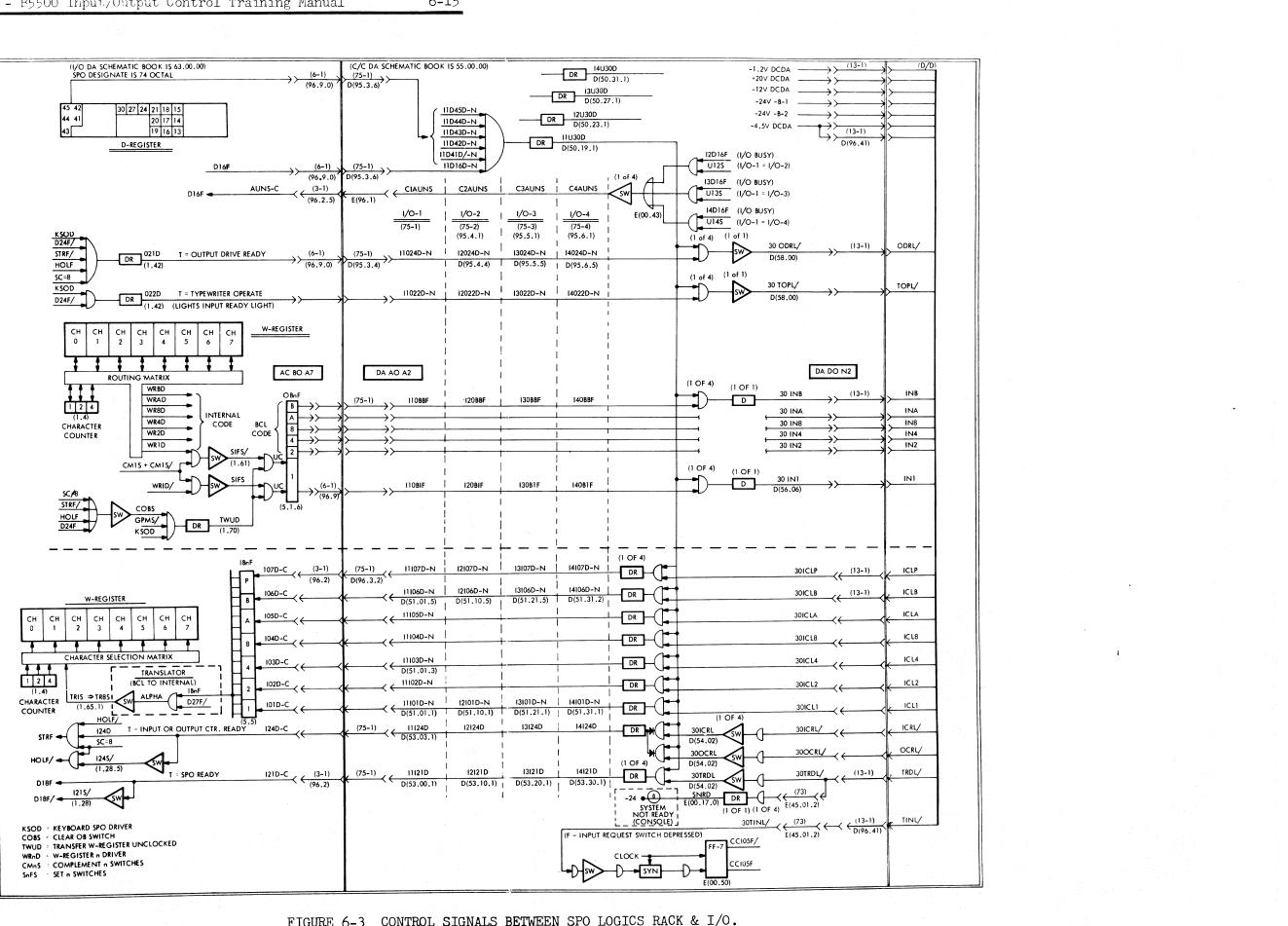

| 6       | MODEL II SUPERVISORY PRINTER CONTROL<br>General | 6-2<br>6-3                                |

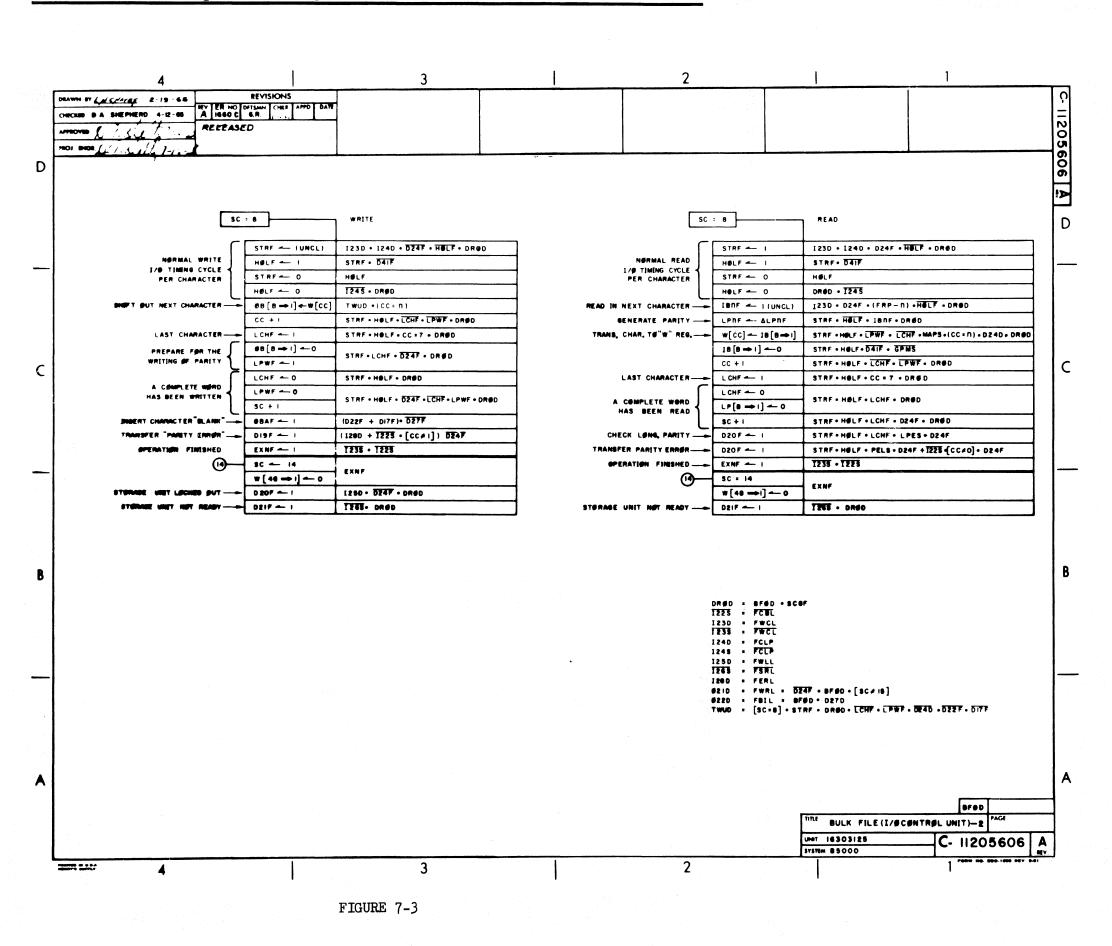

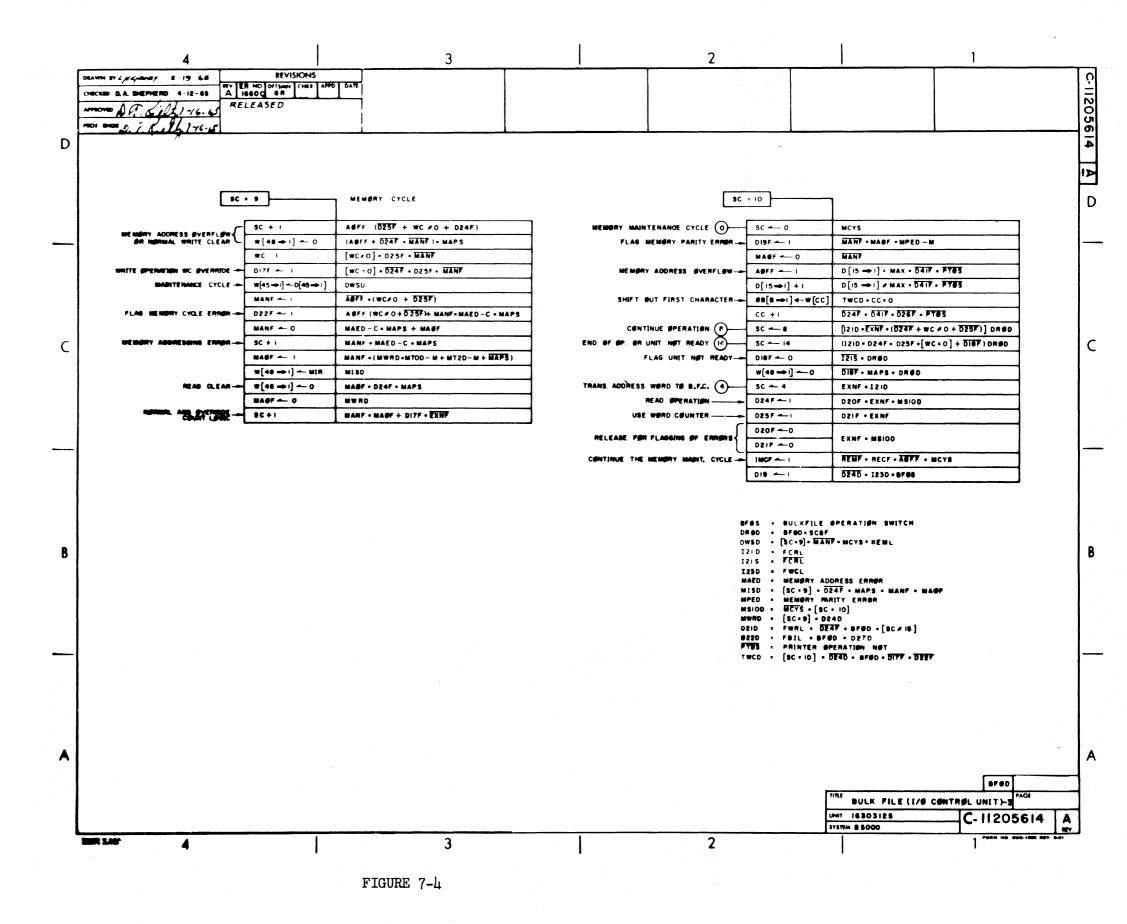

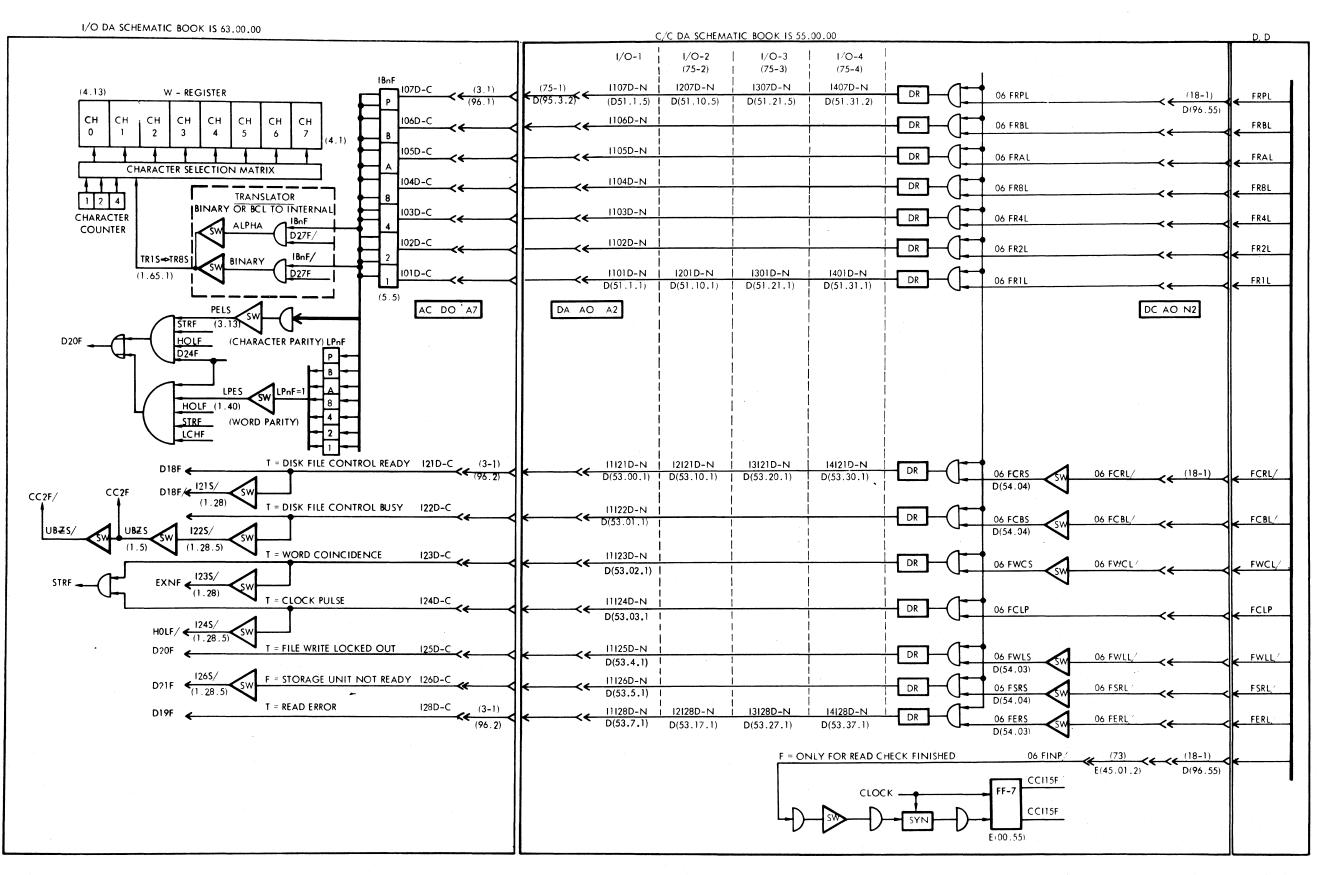

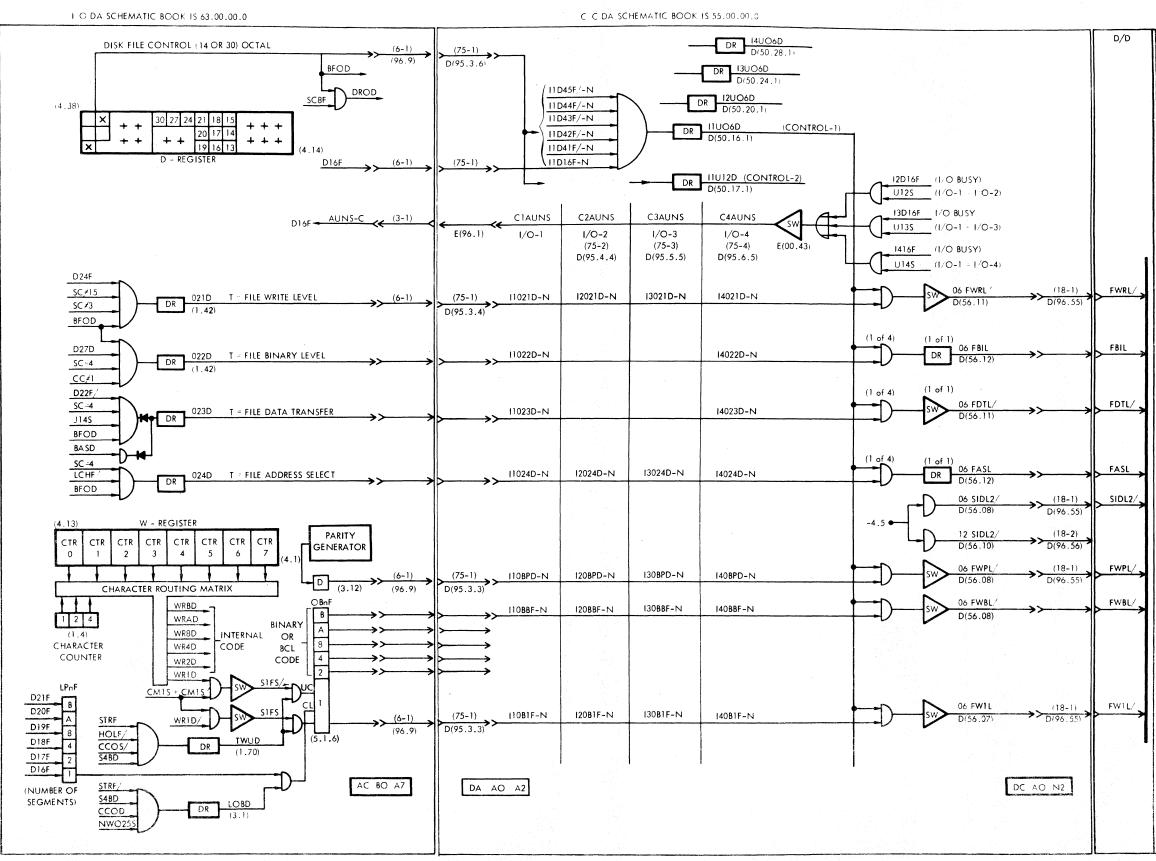

| 7       | DISK FILE CONTROL<br>General                    | 7-2<br>7-4<br>7-5<br>7-22<br>7-24<br>7-26 |

i. W

#### SECTION 1

#### INTRODUCTION OF I/O SYSTEM

#### GENERAL

The primary function of the 5282 Input/Output Control Unit (I/O Control Unit), shown in Figure 1-1, is to synchronize and control the flow of information in one direction at any one time between any Memory Module and any peripheral device attached to the system.

|     |                                                                |     |     |       |       | $\geq$ |

|-----|----------------------------------------------------------------|-----|-----|-------|-------|--------|

| P-1 | 1/0                                                            | D/D | C/C | MEM-1 | MEM-2 | P-2    |

|     | CONTROL<br>UNIT<br>B5282<br>CABINET<br>PLUS<br>POWER<br>SUPPLY |     |     |       |       |        |

FIGURE 1-1. B5282 I/O CONTROL SUBSYSTEM

A B5500 System must have at least one I/O Control Unit (B5283); and, depending on the predicted volume, can incorporate up to a maximum of four independently controlled units. The number of I/O Control Units included in a system determines the number of simultaneous input/output operations which may take place; that is, if there are four I/O Control Units, there can be as many as four <u>simultaneous</u> operations. The type and quantity of peripheral devices which may be incorporated in a system are listed in Figure 1-2.

The simultaneity of separate input/output operations is accomplished by the use of an "interrupt" system in which the processing function of the system is interrupted and the specified input/output operation initiated.

The term "interrupt" is used in a special sense in the B5500. It does not imply that processing is halted during the input/output operation or that the system is held static in any way. Rather, a transfer of control is taking place, during which the Master Control Program (MCP) may initiate certain types of operations that can proceed simultaneously with computation by the Processor.

Input/output operations, for example, are conventionally controlled by the individual program currently being processed. However, the relatively slow speed of input/ output devices normally cause a certain amount of idleness (usually excessive) of the Processor while controlling the input/output operation. This, in turn, results in a serious reduction of actual processing time. This situation is especially prominent in business applications where input/output operations, under control of the Processor, may constitute a large percentage of the computers operating time.

The B5500 has been designed to preclude this condition by permitting maximum use of all peripheral equipments concurrent with computation by the Processor. The simul-taneous operation of both input/output equipment and the Processor is accomplished through a centralized communications control which causes a temporary interrupt in

computation when an input/output operation is required. Each time an interrupt condition occurs, processing pauses momentarily while the MCP initiates the specified input/output operation. Control is then returned to the object program being processed. The minute amount of processing time that is lost through MCP control during the interrupt condition can be considered insignificant when compared to the increase of computation time as a result of simultaneous input/output and Processor operation.

All input/output operations are performed and synchronized by the I/O Control Unit after initiation by the Processor. Actually, the initiation is a result of an "Initiate I/O" operator of the MCP. The Processor, in turn, provides the necessary logic to Central Control, which selects an I/O Control Unit and provides the initiation logic levels. Control information for the I/O Control Unit is in the form of a standard 48-bit word which contains all the information pertinent to effecting the I/O operation. This word is called an I/O Data Descriptor.

During the input/output operation possible error conditions are monitored; e.g., correct memory parity, address error conditions, and peripheral unit errors in the form of non-availability levels. These error conditions are recorded in the form of a Result Descriptor word similar in structure to the Data Descriptor. When the specified operation has been completed or an error condition detected, the I/O Control Unit sends the Result Descriptor to Memory for subsequent interrogation by the MCP. This I/O Result Descriptor then indicates whether or not the operation was completed successfully and provides information regarding the type of operation performed. The I/O Control Unit signals the system that the operation has been completed and that the Result Descriptor has been stored in Memory by setting an "I/O Finished" interrupt.

An I/O Control Unit also has the capacity of being placed in local mode: independent of system control and unavailable for system use. While in this mode, the I/O Control Unit may be used to control repetitive operation of any peripheral unit for diagnostic purposes, such that it will not interfere with normal operation of the remainder of the system.

| PERIPHERAL UNIT           | MINIMUM                                                                                                         | MAXIMUM              |

|---------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------|

| Magnetic Drum Unit        | 0                                                                                                               | 2                    |

| Magnetic Tape Unit        | 0                                                                                                               | 16                   |

| SPO/Keyboard              |                                                                                                                 | 1                    |

| Line Printer              | 0                                                                                                               | 2                    |

| Card Reader               | $\mathbb{E}_{\mathcal{A}} = \mathbb{E}_{\mathcal{A}} \mathbb{E}_{\mathcal{A}}$                                  | 2                    |

| Card Punch                | 0                                                                                                               | 1                    |

| Paper Tape Reader         | 0                                                                                                               | 2*                   |

| Paper Tape Punch          | i de la companya de l | 2*                   |

| Disk File Control         | <b>1</b>                                                                                                        | 2                    |

| Data Transmission Control | 0                                                                                                               | n se k <b>i</b> nger |

\* Paper Tape Units have a combined maximum of 3 units.

FIGURE 1-2. PERIPHERAL UNIT CONFIGURATION LIMITS

#### THE I/O CONTROL UNIT

The B5282 I/O Control Subsystem cabinet includes the physical hardware necessary to enclose from one to four B5283 I/O Channels. In all operational descriptions of a

Printed in U.S. America 1 15-69

FIGURE 1-3 D & D I/O DISPLAY PANEL

Ε B С D Ν A G ĸ L P W REGISTER UNI COUNT CONTRO RESULT MEMORY ADDRESS ¢  $\mathbf{\Phi}$ ക Ø Ф Φ Ф Ф Ф ዏ Q Ø Ð 0 Ф Ф Ф \$ -\$ Ф Ф Ф Ð Ф ं Ð Ð 0 ф, ф **∲** \*377 -\$ \*\* \$ \$ \*\* \$ ∲ ₩28F ¢ \*\*\* -040F **O** -∲ ₽24F -∲ 02 2F Ф D19F **( (**) 04.34 -034F 013F ф 1015 Ф Ф **O** -\$ ф рюғ **O**  $\odot$ s •\$ MAG TAPE TES1 РСС PC 2F PC 2F VRCF Ф ф Ф ି INCF ᠿ᠍ᡷᠿ᠍ᠿ<u>ᡷ</u>ᠿᡷ ¢ ¢ Ф -\$ Ф Þ ERR STOP FEY MEM RECYC .⊕ ₩.2<sup>25</sup> ф w19ғ -**()** w16<sup>#</sup> ∲ w01F т **(** ÷ WIOF -\$ w07f 04F Φ Φ Φ M 14 4 ੇ ੇ ¢ φ **♦** 3**♦** 5<sup>2</sup> ¢.;\* LOCAL MEMINH MEM CYC CLEAR ۲ (Ŧ) \* υ 0 0 MENIAC STAP 1/0 BIT RESET PUSH BUTTON TOGGLE SWITCH NEON SWITCH LIGHT

Burroughs

B5500 Input/Output

Control

Training Manual

B5283 I/O Channel, the term "I/O Control Unit" is used and should be interpreted to mean both: the B5282 I/O Control Subsystem (Cabinet and Power Supply) and one B5283 I/O Channel (logics racks).

All B5283 I/O Channels are identical in operation, appearance, and physical hardware orientation, and differ only in their physical placement within the B5282 I/O Control Subsystem cabinet.

Each B5283 I/O Channel (I/O Control Unit) is completely independent of the others in operation and is capable of controlling the transfer of information between any peripheral device attached to the B5500 system and any Memory Module.

Transfer of information between core Memory and an I/O Control Unit is accomplished by a parallel transfer, to or from, the peripheral units, a transfer of one character, or a partial character at a time. Essentially, therefore, the I/O Control Unit may be considered as a one word buffer between two different transfer rates.

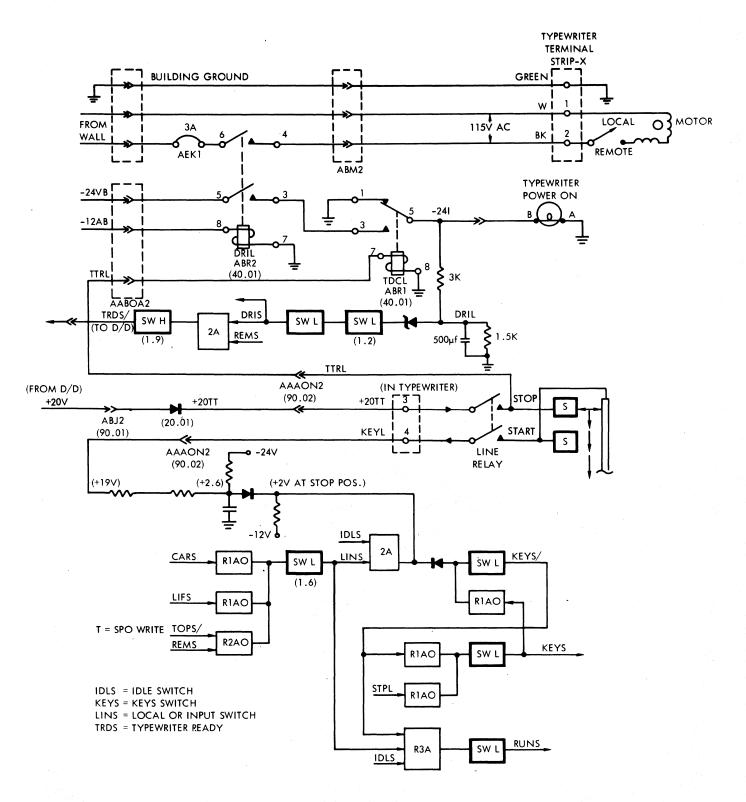

Illustrated in Figure 1-3 is the I/O display panel located in the Display and Distribution Cabinet. There is one I/O display panel for each B5283 logics rack. Elements within the I/O control unit may be divided into three general areas according to the function of the elements. They are:

| 1. Functional Areas:   | Those logical elements used for information and/or control storage and manipulation.                     |

|------------------------|----------------------------------------------------------------------------------------------------------|

| 2. Control Areas:      | Logical elements controlling the flow of information and/or generation of control or information levels. |

| 3. Input/Output Areas: | Include both internally and externally generated control inputs or outputs.                              |

A listing of the indicated elements according to these described general areas is as listed below. Included is the appropriate paragraph of the manual describing each.

Functional Areas:

- 1. W Register

- 2. D Register

- 3. Input Parity Generator

- 4. Longitudinal Parity Buffer (LPnF)

- 5. Input Alpha/Binary Decoder

- 6. Output Binary/Alpha Encoder

- 7. Output Parity Generator

- 8. Character Routing Matrix

- 9. Input Read Buffer (IRnF)

- 10. Input Buffer (IBnF)

- 11. Output Buffer (ØBnF)

- 12. Write Output Buffer (WBnF)

#### Control Areas:

- 13. Sequence Counter

- 14. Character Counter

- 15. Pulse Counter

- 2. D Register Word and Address Counters

Input/Output Areas:

- 16. Sensing Matrix

- 17. Control Matrix

- 2. D Register Address and Unit Designate

Elements of the I/O maintenance panel are grouped according to function as follows:

- 1. W-Register: WOLF W48F

- 2. D-Register: DOLF D22F, D24F D27F, D30F D45F

- a. Memory Address Field

- b. Result or Error Field

- c. Control Field

- d. Word Count Field

- e. Unit Designate Field

- 3. IB (Input Buffer): IBLF IBPF

- 4. IR (Tape Input Read Buffer): IR1F IRPF

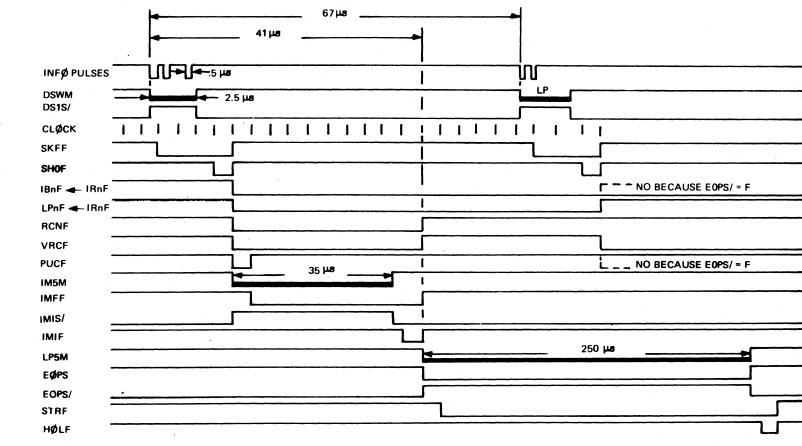

- 5. ØB (Output Buffer): ØBLF ØBBF, ØBPD

- 6. WB (Tape Write Output Buffer): WBlF WBPF

- 7. Magnetic Tape Control

- a. RCNF: Record Control

- b. PUCF: Pile-Up Control

- c. FWDF: Forward

- d. BKWF: Backward

- e. SKFF: Skew

- f. SHØF: Skew Holdover

- g. IMFF: Information

- h. IMIF: Information Index

- i. VRCF: Valid Record

- 8. General Synchronization and Control

a. HØLF: Holdover

b. STRF: Strobe

c. MANF: Memory Access Needed

d. MAØF: Memory Access Obtained

e. EXNF: External

1-5

- 8. General Synchronization and Control (Continued)

- f. AØFF: Address Overflow

- g. ØBCF: Output Buffer Call

- h. LCHF: Last Character

- i. LPWF: Longitudinal Parity Write

- 9. LP (Longitudinal Parity Buffer) LPIF LPPF

- 10. Counters

- a. Sequence Counter: SC8F, SC4F, SC2F, SC1F

- b. Character Counter: CC4F, CC2F, CC1F

- c. Pulse Counter: PC6F, PC5F, PC4F, PC3F, PC2F, PC1F

- 11. Manual Control

- a. Clear: I/O Control Unit; W Registers: D Register b. Bit Reset:

- 12. Test

- a. IMCF: Initiate Maintenance Cycle

- b. REMF: Remote-Local

- c. RECF: Recylde

- d. ERR/STOP: Stop on Error

- e. KEY MEMORY:

- f. RECYC: Recycle

- g. LOCAL-REMOTE:

- h. START

- i. MEM INH-MEM ACC: Memory; Inhibit Memory Access

- j. MEM CYC: Memory Cycle

#### SIGNAL LINES BETWEEN I/O AND MEMORY

The interconnecting lines between the I/O Control Unit, Central Control and Memory are defined as follows:

MANF A Memory Access is needed by the I/O Control Unit.

- A00S Start Memory Cycle. This level is generated by Central Control when a MANF is received from the I/O Control Unit. A00S will be true when the appropriate crosspoint flip-flops are set and its associated MCYF is reset.

- MWRD Generated in the I/O Control Unit. Indicates that a Memory write operation is to be performed (D24F set).

- WOOD Composed of MWRD and AOOS. Indicates when true that a write operation is to be performed. When false, a read operation will follow.

- MTOD Memory Time O. A timing interval generated by Central Control during the first microsecond of a Memory access, signals the I/O Control Unit that a Memory cycle has started. MTO also indicates during a write operation, that the write operation has been completed, thus allowing the release of the requesting I/O Control Unit.

- MT2D Memory Time 2. States that the read information levels are available to the I/O Control Unit, allowing release of the I/O Control Unit and enabling the set of MAØF (Memory Access Obtained). In the four microsecond memories MT2D is generated by MP=1.

- MPED Memory Parity Error. Indicates, when true, that a parity error exists in the word presently contained in the MIR (Memory Information Register).

- MAED Memory Address Error. When true, this level indicates to Central Control that the designated Memory Module is nonexistent; i.e., the designated unit is in LOCAL, not up to power or is not part of the system. This level is developed as a result of MNAL (Memory Not Available).

- DOLF'-DL2F' Core Address Levels. Specify a particular word in a Memory Module. These levels originate from the reset side of the flip-flops in the ADDRESS field of the D register.

- D15F'-D13F' Memory Module Designate Levels. Specify and Memory Module from 0-7.

- WOLF'-W48F' I/O Control Unit Information Levels. Originate from the reset side of the W-Register Flip-flops.

- AO1S-A12S Core Address Levels. These levels are the DO1F'-D12F' levels in their switched form and enable the MAR (Memory Address Register).

- WOLS-W48S Memory Module Input Information Levels. These are the levels WOLF'-W48F' in their switched form.

- ROLS-RU8S I/O Control Unit Input Information Levels. Switched information levels originating in MIR and switched in Central Control.

- IO1F'-I48F' Memory Module Output Information Levels. Originate from the reset side of the MIR Flip-flops. They are sent to Central Control and switched to the form RO1S - R48S.

#### I/O OPERATION AS A PROGRAM FUNCTION

The Master Control Program contains instructions which initially starts a particular input/output operation. In turn, the MCP is notified that an input/output operation is needed by the object program which transfers control to the MCP by generating a "Program Release Interrupt" or a "Continuity Bit Interrupt". At this time the Processor is halted.

After the I/O Control Unit is initiated by the MCP, the Processor is restarted and continues processing the object program.

When the I/O operation is completed, the I/O Control Unit sets an "I/O Finished Interrupt" which, again, interrupts the Processor and transfers control to the MCP. The MCP interrogates the I/O Result Descriptor to see if the input/output operation was completed successfully. If the operation was successful, the MCP allows the Processor to continue; otherwise, control is transferred to another portion of the MCP so necessary corrective action may be initiated.

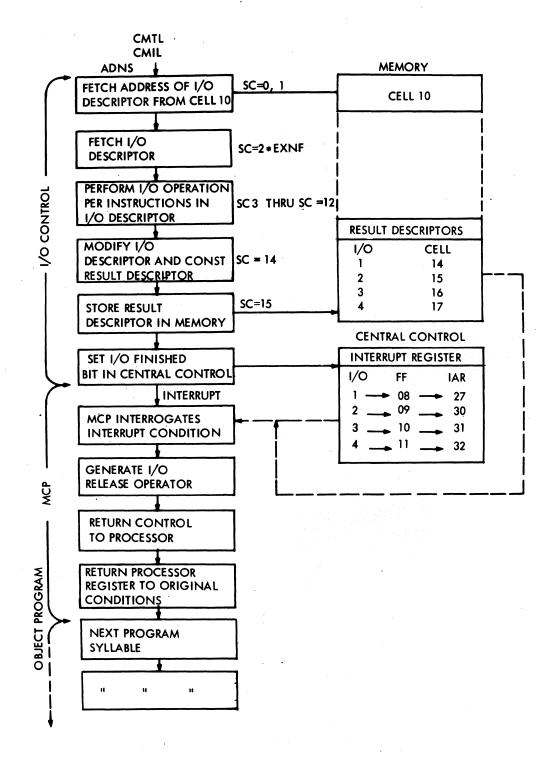

Figure 1-4 illustrates the general flow of an input/output operation from the time that an I/O operation is needed by an object program until the I/O operation is completed and the object program processing continues. The program processing that occurs in parallel with the I/O operation may or may not be the same object program that needed the I/O operation. This is determined by the priority of the program and whether the program can be continued before the I/O operation is completed. In general, the I/O operation can be divided into three parts:

- A. Programmatic initiation of the I/O Operation.

- B. Actual I/O operation under control of the I/O Control Unit.

- C. Programmatic termination of the I/O operation.

PROGRAM INITIATION - FIGURE 1-4.

When the Object program encounters a Read or Write statement, indicating an input or output operation is required, the process of retrieving the I/O Data Descriptor from Memory is initiated by a Program Release Operator which, through the Processor, performs the following:

- 1. Fetches the specified I/O Data Descriptor.

- 2. Alters the Status Bit (46) indicating the specified area is not available as a memory area.

- 3. Sets a Program Release Interrupt.

- 4. Stores the address of the Descriptor in R +11.

Following a Store for Interrupt Operator, the system is forced into the Control State under supervision of the MCP. Next, the MCP examines the interrupt condition and starts the I/O operation by generating an Initiate I/O Operator which stores the address of the I/O Data Descriptor in absolute cell address 10.

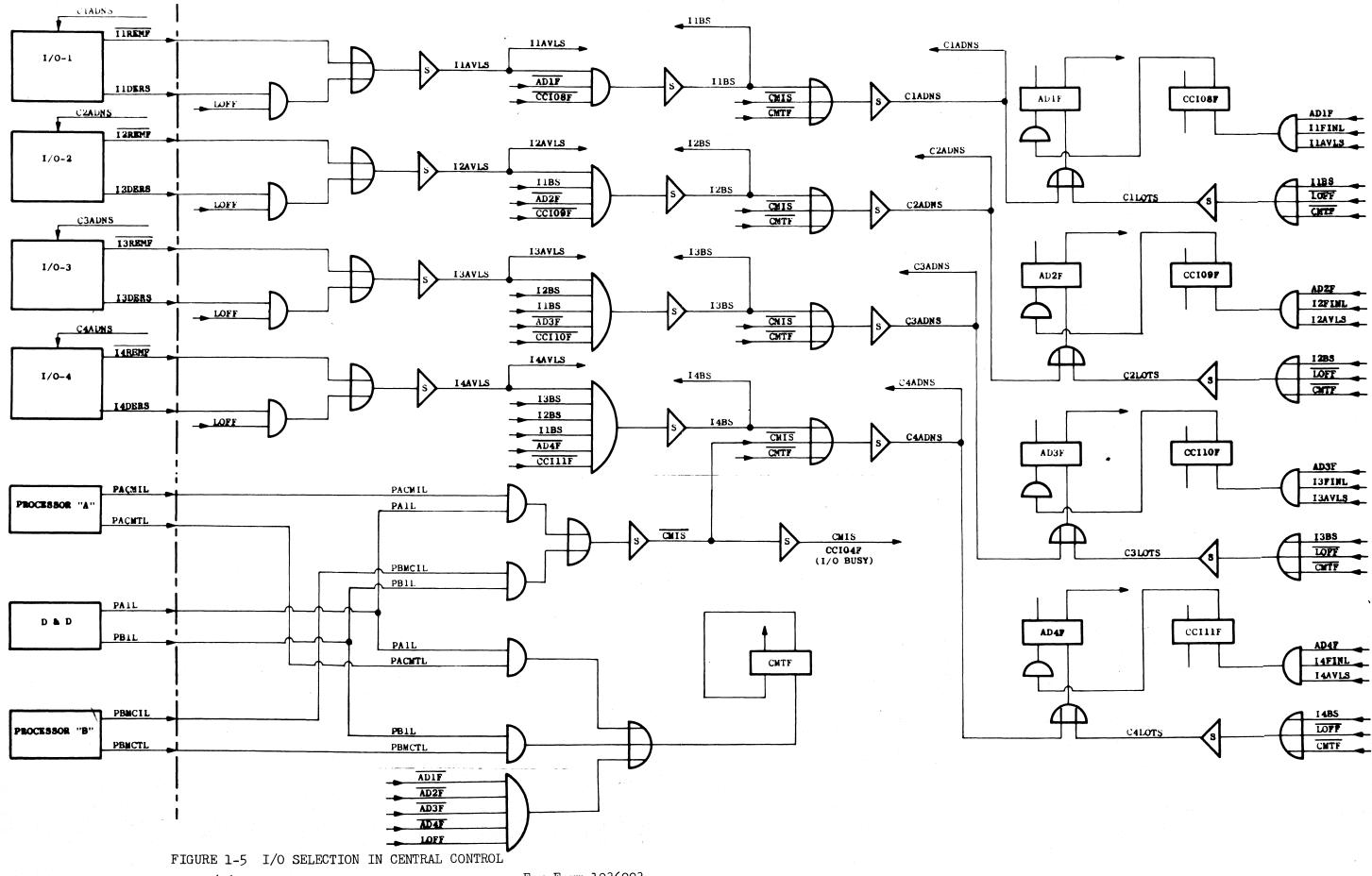

In addition to this transfer and storage of the I/O Data Descriptor address, the Initiate I/O Operator generates the control levels CMTL (Commence Timing Level) and CMIL (Commence I/O) which are used as primary logic to develop the actual I/O initiate signal, ADNS (Admit Descriptor Now) which is shown in Figure 1-5.

#### I/O OPERATION

ADNS, in turn, causes the I/O Control Unit to perform a standard Memory access of cell 10 for the address of the designated I/O Data Descriptor. A second Memory access is then performed and the actual I/O Data Descriptor is transferred to the I/O Control Unit. The I/O operation is then performed under instructions contained in the Data Descriptor and the success or failure of the operation recorded in the form of a Result Descriptor word which is then returned to a specific location in memory for interrogation by the MCP. Also, to signal that the I/O operation has been completed, the I/O Control Unit sets a specific "finished" bit in Central Control which develops an address in the Interrupt Address Register (IAR) referencing an "interrogate interrupt routine".

FIGURE 1-4 I/O OPERATION

#### PROGRAMMATIC TERMINATION

Control now branches to the MCP which, using the specified "interrogate interrupt routine" examines the Result Descriptor for future action. At this point, three courses of action are possible.

- 1. If the operation was successfully completed, the I/O Control Unit is made available immediately. If another Data Descriptor is ready for processing, the MCP initiates the specified operation before returning control to a program segment in the object program or to the next one scheduled by the MCP.

- 2. If the operation was not successfully completed, the MCP examines the Result Descriptor for the cause of failure and attempts to rectify the situation. For example, in the event of incorrect reading from tape, the tape is automatically positioned backward and reread. Persistent failure results in operator notification. The program is then interrogated to determine whether to bypass the faulty record or to exit the program at that point. When an I/O operation is unsuccessful, the MCP prevents the destruction to any transferred information.

- 3. If the Result Descriptor indicates that a Drum transfer operation has just been completed, the MCP determines whether a part of the MCP has been loaded into Memory. (If so, control is transferred to itself.) It should be emphasized that processing is interrupted only when an I/O Control Unit is ready and only long enough to initiate the specified operation, after which the I/O Control Unit together with the designated peripheral unit proceed independently of Processor control. After initiation of any I/O operation, control is immediately returned to a program segment.

In the example shown in Figure 1-4, the result of interrogation of the Result Descriptor (successful operation) is to generate an I/O Release operator which ultimately returns control to the Processor, places the Processor's registers in their pre-interrupt condition, and transfers control to the next program syllable in the object program.

#### DEVELOPMENT OF ADNS

To initiate an I/O Control Unit, it is necessary to develop an ADNS (Admit Descriptor Now) level for the particular I/O Control Unit designated, that is,

|    | ADNS-1 | I/O #1 |

|----|--------|--------|

|    | ADNS-2 | I/O #2 |

|    | ADNS-3 | I/O #3 |

| or | ADNS-4 | I/O #4 |

To simplify the explanation of the generation of ADNS by Central Control, we will limit the description to I/O Control Unit #1 (ADNS-1). Selection of the I/O Control Unit to be initiated is determined in Central Control and identical logic is used to initiate the respective ADNS.

Printed in U.S. America 1-15-69

1.255 Mar

For Form 1036993

Referring to Figure 1-5, as indicated in this figure, whether or not ADNS-1 will be true depends directly upon the state of:

|     | ILBS | (I/O #1 Busy Switch) |

|-----|------|----------------------|

|     | CMIS | (Commence I/O)       |

| and | CMTF | (Commence Timing).   |

All three of these levels must be false in order for ADNS-1 switch to be true.

Development of these levels is as follows:

1. IIBS: The state of the I/O #1 Busy Switch will be true if any one of the following exists:

| ILAVIS' | (I/0 # l not available) |

|---------|-------------------------|

| AD1F    | (I/O #1 busy)           |

| or      |                         |

| CCI08F' | (I/O #l not finished)   |

#### where

ILAVIS generally indicates the physical availability of the I/OControl Unit and will be true to indicate the I/O is available if the term ILREMF' (not remote) is held false by the I/O Control Unit. This level is developed in turn by a manual switch which places the unit either in local or remote. If the REMF line is true or not present, the ILAVIS switch will be false and indicate the nonavailability of the unit. Also, ILAVIS will go false during a LOAD operation (LØFF) if an error should occur during the load cycle and is detected in the ERROR field of the D register. ILDERS (D Register Error).

ADlF (I/O Busy Flip-flop) will normally be false prior to an input/ output operation having been reset at the termination of the previous I/O operation by CCIO8F (I/O #1 Finished). ADlF is set true when ADNS-1 goes true and indicates an I/O operation has started.

CCI08F (Finished Interrupt Flip-flop) is set true when it receives an IlFINL (I/O #l Finished) from the I/O Control Unit at the termination of an operation. CCI08F will be false prior to the generation of ADNS.

- 2. CMTF: CMTF (Commence Timing Flip-flop) is used to allow the generation of ADNS-1. CMTF is set from the level CMTL which is generated as a result of an "Initiate I/O Operator".

- 3. CMIL: CMIL (Commence I/O Level) is used in conjunction with CMTL to differentiate between an I/O Control Unit and a Processor.

Briefly, the generation of ADNS may be summarized as follows:

Initially, all flip-flops are cleared, CCIO8F had been set to indicate the previous input/output operation was completed but is reset at the next clock pulse. ADIF had been reset when CCIO8F was set. Also, CMTF was reset at the pulse following the previous CMTL.

Therefore, the IIBS switch will be false, since all three of its input conditions are true. That is,

ILAVLS \* CCIO8F' \* ADLF' = 1

In turn, ADNS-1 will go true when the levels CMTL and CMIL are generated by Central Control from the logic,

ILBS \* CMIS' \* CMTF' = 0.

ADNS-1 is returned to the I/O Control Unit and the I/O operation initiated. ADNS-1 also sets AD1F indicating that the I/O Control Unit is engaged in an I/O operation. As will be seen later, ADNS-1 is true for only one microsecond, going false when CMIL is terminated, it allows the I/O Control Unit to initiate the first of two memory cycles required to fetch the I/O Data Descriptor.

NOTE

ADNS sets D17F which, in turn, initiates MANF (Memory Access Needed Flip-flop).

The second memory cycle is generated internal to the I/O Control Unit by EXNF (External Flip-flop).

When the I/O operations end, the event is signalled by IlFINL which is generated by the I/O Control Unit after construction of the Result Descriptor. IlFINL, together with AVLS and ADLF (true during the input/output operation) set CCI08F.

If a Card Load or Drum Load operation is to be performed, then the action of CMTL and CMIL is generating an ADNS is simulated by the Load Flip-flop (LOFF), which initiates the I/O Control Unit with its generated level, LOTS. LOFF is set when the LOAD push button is pressed on the Operators Console.

Initially, AVLS will be true since all four terms on the input to AVLS are false, that is;

ADLF • ILDERS • LOFF • ILREMF = 0.

When the LOAD push button is pressed, LOFF will be set at the next clock pulse (note that the same level which sets LOFF previously clears all other flip-flops).

LOFF then sets CMTF from the logic,

CMTF = LOFF \* AD1F.

At this same time, LØTS will go true from,

LØTS = I1BS' \* CMTF \* LØFF,

where LØTS had been previously held false by CMTF and LØFF.

IØTS sets AD1F, indicating the I/O operation has started, which then causes I1BS to go true from the logic:

ILBS = ILAVLS' + CCIO8F + ADLF.

In this section, LØTS becomes the primary logic in initiating the load cycle where the function of ADNS is replaced and the construction of a Data Descriptor forced directly in the I/O Control Unit by LØTS itself.

IØTS is held true for  $l \mu s$  and goes false when IlBS goes true. CMTF goes false at the same pulse time being reset, by itself, at the pulse following the set condition.

ERROR ON LOAD

If, during the load operation an error is detected and recognized by setting the appropriate bit in the D Register ERROR field, then the level IlDERS (I/O #1 D Register Error) will go true. In turn, AVLS will be forced to go false. If this should occur, then the I/O Finished Flip-flop CCI08F will not be allowed to be set at the end of the operation. This may be seen from the logic to set the I/O #1 Finished Interrupt, as follows:

CCIO8F to 1 = AVLS \* AD1F \* I1FINL.

The load operation then idles until corrective action is taken. This situation is signalled by the fact that the CONTROL state lamp on the Operator's Console stays lit; i.e., the system never enters NORMAL state operation.

I/O CONTROL UNIT MEMORY ACCESS - STANDARD MEMORY CYCLE

The I/O Control Unit has the ability to read from, and write into any Memory Module (0-7) designated by the three higher order bits of the ADDRESS field in the I/O Data Descriptor.

When a Memory access is needed by the I/O Control Unit the level MANF (Memory Access Needed) is generated alone, indicating a "read from Memory" information or with MWRD (Memory Write) specifying a "write into Memory". These levels, in turn, are sent to Central Control Memory Exchange and initiate the respective read or write operation.

Memory Module selection is then determined by Central Control which decodes the Module Address bits (D15F-D13F), examines this address and determines the following:

- 1. Is more than one I/O Control Unit requesting the same Memory Module; i.e., is there a conflict in address designations?

- 2. If #1 is true, determine the priority of the requesting I/O Control Units and allow that I/O Control Unit with the highest priority access to the designated Memory Module.

3. Before the actual selection of the Memory Module occurs (through crosspoint control), the addressed module is interrogated to determine if it is presently engaged in a memory cycle. If it is, crosspoint selection is delayed until the current access has ended (delay will be under  $\mu \mu s$ ).

Assuming that all the conditions of 1, 2, and 3 have been satisfied, the designated Memory Module is logically connected to the requesting I/O Control Unit by setting the appropriate crosspoint flip-flops. This allows the transfer, to Memory, of the address and information levels, the Memory Start level (AOOS), and the type of operation to be performed; i.e., WOOD (Write) or WOOD' (Read).

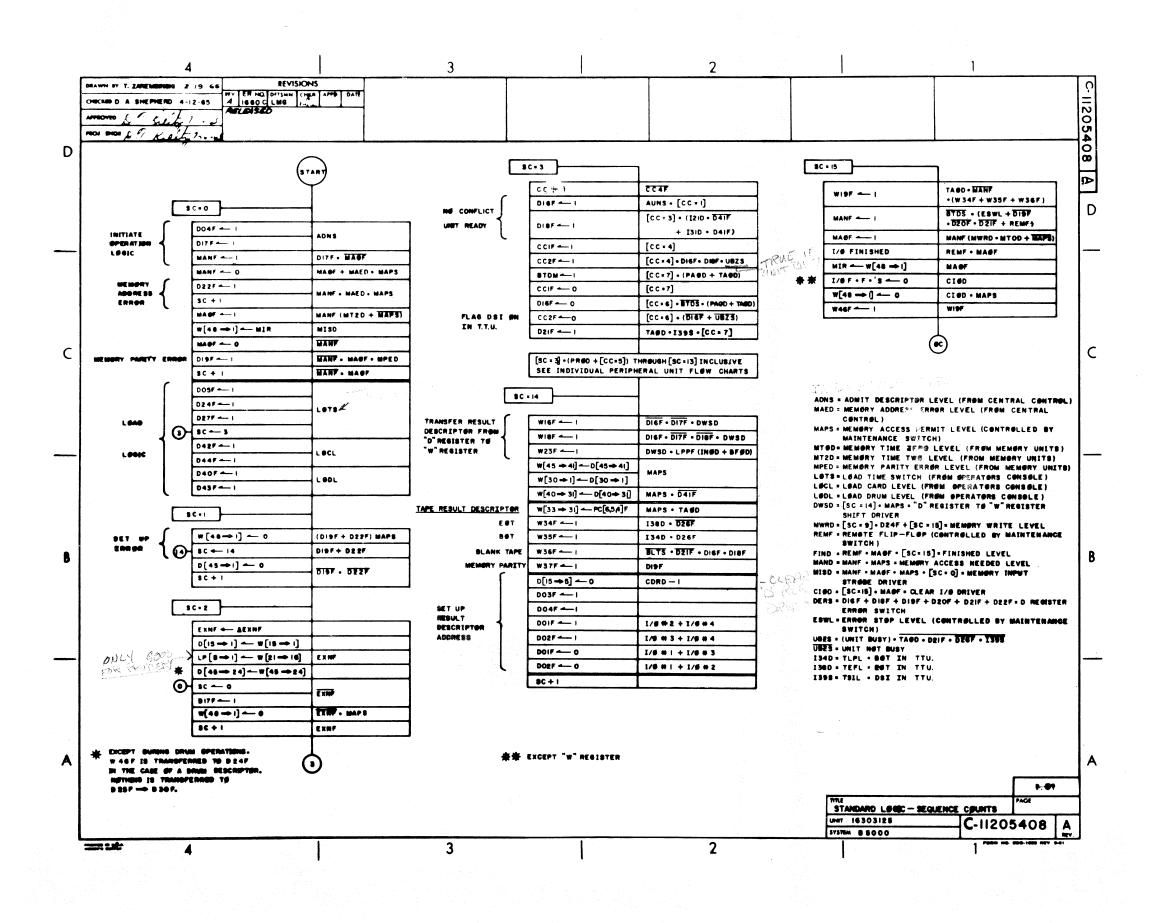

#### STANDARD LOGIC

#### GENERAL

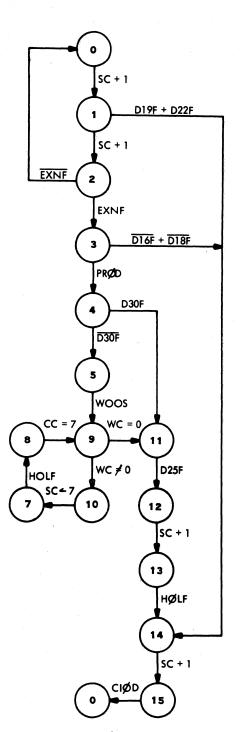

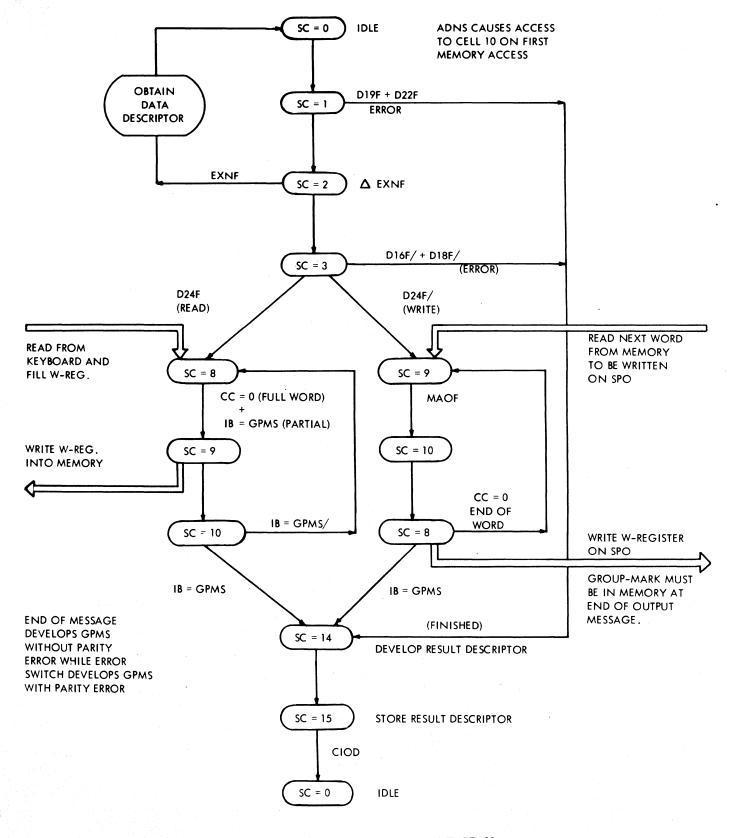

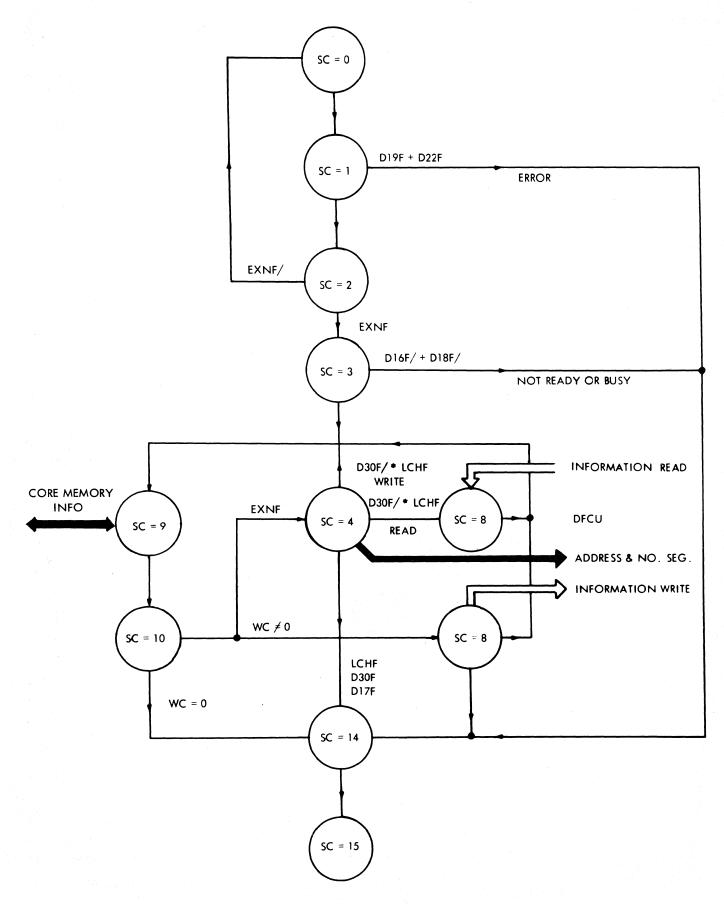

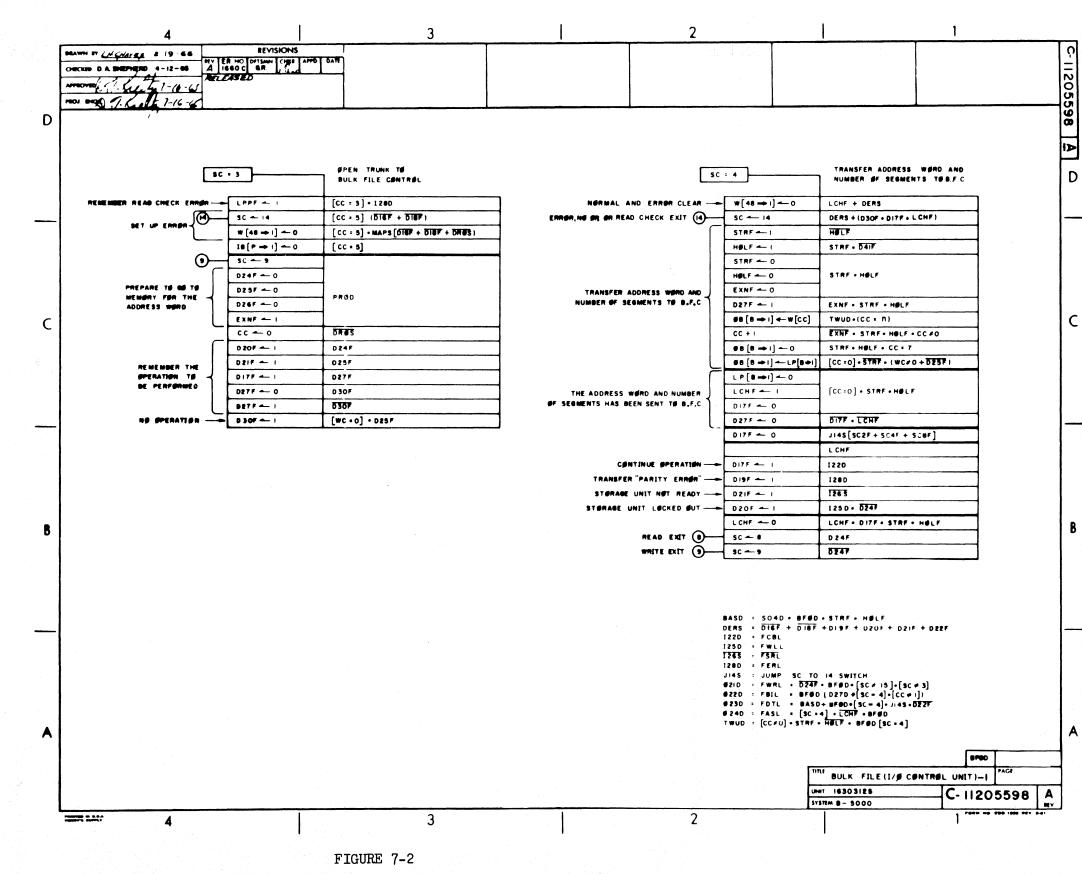

Standard logic is defined as those Sequence Count intervals which are common to the initiation and termination of an I/O Operation for all peripheral equipment. Generally, Sequence Counts (SC's) 0, 1, 2, 14, and 15 are assigned to initiate certain logical procedures and establish communication between Memory, a designated peripheral unit, Central Control, and the I/O Control Unit.

Specifically, Sequence Counts 0, 1, and 2 are assigned the task of performing certain logical operations to initiate an I/O Operation, while Sequence Counts 14 and 15 are used to terminate the I/O operation. Briefly, the function of the standard SC's are summarized as follows:

| SC 0, 1, | 2: A | . Initial    | load of an I/O Data Descriptor            |

|----------|------|--------------|-------------------------------------------|

|          | E    | B. Construct | t Descriptor for memory load              |

|          | C    | Construct    | t Card Reader Descriptor for memory load. |

SC 14, 15: A. Construct Result Descriptor and return to Memory.

All operations are started when an ADNS (Admit Descriptor Now) level is received from Central Control. ADNS indicates that the particular I/O Control Unit addressed by Central Control is ready for normal operation.

#### INITIAL LOAD OF I/O DATA DESCRIPTOR

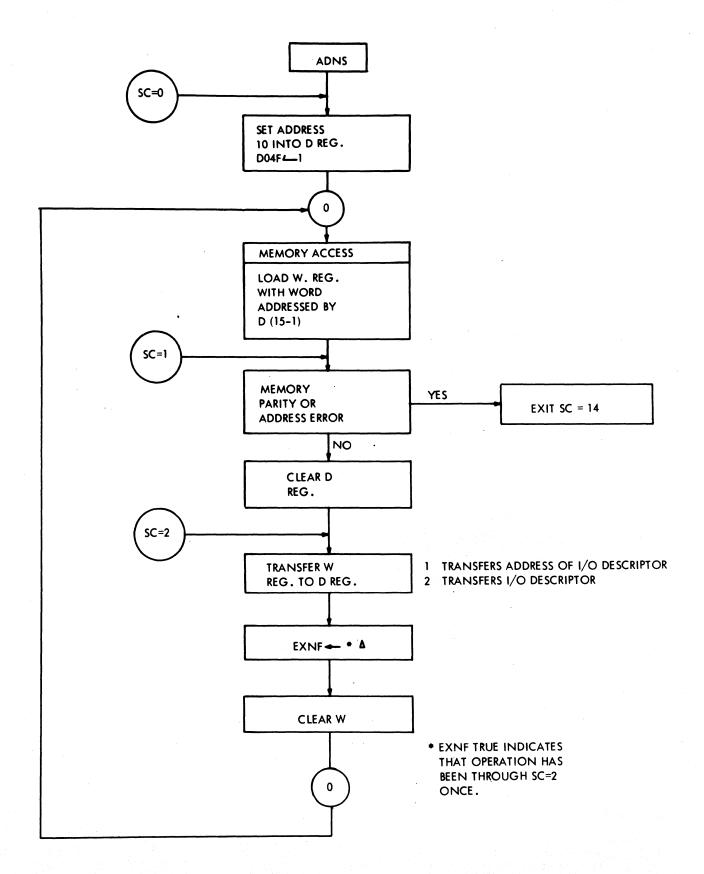

During this operation, a specified I/O Data Descriptor will be addressed, called from Memory, and placed in the I/O Control Unit. The operational Sequence Count cycle involved in this process is in the order SC=0, 1, 2, 0, 1, 2 at the end of which control is transferred to SC=3 of the designated peripheral unit.

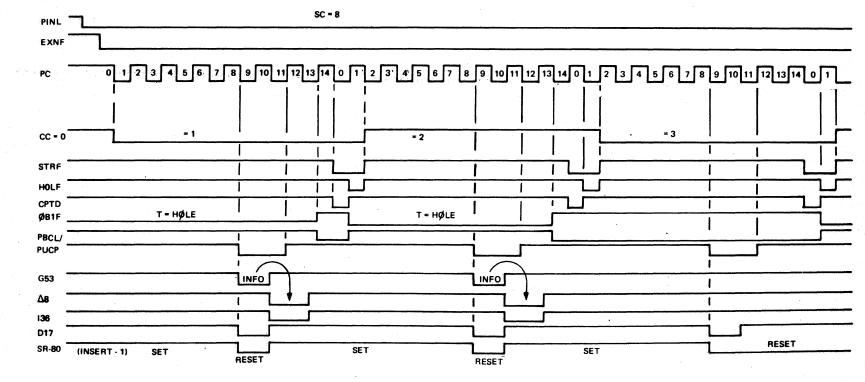

When an ADNS level is received from Central Control, the following general events occur. Applicable logic for this operation may be found in Figure 1-8. The entire operation is summarized in a decisional flow chart shown in Figure 1-7.

| CO | _ | $\sim$ |

|----|---|--------|

| SU |   | υ      |

- A. Generate memory cell address 10. (Cell 10 contains the address of the desired I/O Data Descriptor.

- B. Initiate a memory cycle.

- C. Load word in cell 10 into the W register.

- D. Check for memory parity and address error (from Memory to I/0).

- E. SC+1.

FIGURE 1-6 I/O DATA DESCRIPTOR LOAD 0, 1, 2, 0, 1, AND 2

Printed in U.S. America 1-15-69

For Form 1036993

| SC=1: | A.<br>B.<br>C. | SC=14. If a normal load occurred,<br>Clear the D-register.                                                                                      |

|-------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| SC=2: | * A.           | Transfer W(15-1) to D(15-1). The address of the desired $I/O$ Data Descriptor is now in the ADDRESS field of the D register.                    |

|       | * B.           | Transfer $W(45-24)$ to $D(45-24)$ . Information transferred is insignificant since the word presently in the W register                         |

|       | C.             |                                                                                                                                                 |

|       | D.             | transferred from the W register to the D register.<br>Return control to SC=0.                                                                   |

| SC=0: | A.<br>B.       |                                                                                                                                                 |

|       | С.             | Check for memory parity and address error (from memory to                                                                                       |

|       | D.             | I/O).<br>SC+l.                                                                                                                                  |

| SC=1: | Α.             | If either a memory parity or an address error exists, exit to SC=14. If a normal load occurred,                                                 |

|       | B.<br>C.       | Clear the D register (Address 8 information erased).                                                                                            |

| SC=2: | * A.           | memory address where the transfer of information is to                                                                                          |

|       | * B.           | start. (Read or Write)<br>Transfer W (45-24) to D(45-24). D(45-24) now contains the<br>UNIT DESIGNATE number and other information pertinent to |

|       | C.             | the characteristics of the information to be transferred.                                                                                       |

|       | 0.             | six bits of the Drum Address. For the Drum Printer this is<br>a portion of the format control field. In all other                               |

|       |                | Descriptors this area is not used. This transfer is made                                                                                        |

|       | D.             | in order to insure that the ERROR field is clear in subse-<br>quent error interrogations.<br>SC+1.                                              |

|       | • <i>ل</i> ا   |                                                                                                                                                 |

\*NOTE

Except Drum where W 25 - 30 are not transferred and D24 is set from W46.

This completes the load of the specified I/O Data Descriptor. Control is now transferred to the designated peripheral unit at Sequence Count =3.

Illustrated in Figure 1-7 is the symbolic representation of the logical units used during Sequence Counts 0, 1, and 2.

Burroughs - B5500 Input/Output Control Training Manual

Printed in U.S. America 1-15-69

For Form 1036993

1-19

~

SC=0: Upon receipt of an ADNS from Central Control, DO4F and D17F will be set from the logic:

$$DO4F = ADNS * SC = OO$$

$D17F = ADNS * SC = OO$

DOLF logically sets the ADDRESS field of the D register to an absolute address of 10. Cell 10 contains the address of the desired I/O Data Descriptor.

D17 is initially set to allow the set of MANF (Memory Access Needed) and logically indicates that an ADNS has been received. Since the level ADNS is true for only l $\mu$ s D17F allows a second memory access to be performed when the I/O Data Descriptor is brought from Memory.

The pulse following the set of D17F sets MANF from the logic:

MANF, in turn, initiates a standard memory access and the word addressed by the ADDRESS field of the D register will be accessed and transferred into the W register. Briefly, this memory access is performed as follows.

Memory Access. Initially, MANF and MAØF are reset. MAPS (Memory Access Permit) will be true when the I/O Control Unit is in the remote mode. As previously explained, the first pulse following the set of D17F sets MANF. As soon as MANF goes true, MAND (Memory Access Needed) level is developed and sent to high speed memory where a standard memory cycle is initiated. The memory clock is started (MTO-MT3) and the crosspoint flip-flops set with the address contained in the D register (Cell 10). Prior to setting the crosspoint flip-flops, the Memory Unit Address (enabled as soon as the D register was set with an address) is interrogated; and if an error in address designation is detected, e.g., addressing a non-existent module, the level MAED (Memory Address Error) is returned to the I/O Control Unit. If MAED is true, then the event is flagged by setting D22F in the error field of the Result Descriptor and the SC counted +1.

$$D22F = MANF * MAED * MAPS$$

Also, to disable the current request for a memory access, MANF is reset from the logic:

$$MANF / = MAED * MAPS$$

In absence of a MAED condition, the memory access proceeds normally; and when Memory Time 2 is generated, (MT2) MAØF will be set. (Notice that MAØF is set with the pulse when MT2 is true--or at the set of (MT1).

$$MAOF = MANF * (MT2D + MAPS/)$$

In turn, the Memory Information Strobe (MISD) goes true (Gate "r"); and at the next pulse, the information in MIR (Memory Information Register) is shifted into the W register. This transfer occurs at MT2 time.

Printed in U.S. America 1-15-69

For Form 1036993

FIGURE 1-8 INITIATE MAINTENANCE

1-22

Burroughs B5500 Input/Output Control Training Manual

The same clock pulse which sets the W register with memory information resets MANF indicating a memory access is no longer needed.

#### MANF / = MAØF

At the next pulse, the completion of the memory access is signalled by resetting MAØF:

#### MAOF / = MANF /

The only remaining action involved in accessing a word from memory is detecting whether a Memory Parity Error (MPED) existed when the transfer from memory was accomplished. If an MPED does exist, the level MPED (detected at MT3) is returned to the I/O Control Unit and at the next pulse will set D19F in the error field of the Result Descriptor.

D19F = MANF / \* MAOF \* MPED

This completes the memory access of the word addressed by the ADDRESS field of the D register. In this case, the W register now contains the address of the specified I/O Data Descriptor.

Normal exit from SC=O is accomplished at the pulse following the set of the W register with memory information from the logic:

SC=1: To this point, operations performed or conditions detected may be summarized as follows:

The address of the specified I/O Data Descriptor was constructed in the ADDRESS field of the D register and the word specified by this address (Cell 10) accessed by a standard memory cycle and placed in the W register. If a MAED was detected, (non-existent memory module) D22F was set. If a MPED was detected, D19 was set.

If either a Memory Parity Error (MPED) or a Memory Address Error (MAED) was detected in the previous SC=0, the W register is cleared by:

$W[48 \implies 1] / = (D19F + D22F) * MAPS$

and control transferred to SC=14.

In normal operation the D register is cleared, erasing the address of the address now contained in the W register. Also, the SC is counted +1.

SC=2: The first clock pulse following entry to SC=2 complements (Δ) EXNF (External Flip-flop). EXNF, originally reset, is a logical flip-flop used in Standard Logic SC 0, 1, 2 to indicate, when set, that SC=0 and l of the first half cycle (0, 1, 2) have been completed. As will be shown later, EXNF allows transfer of control to SC=3, after the second half cycle of Standard Logic has been completed. EXNF is set, ungated, from the logic:

$$\triangle$$

EXNF = SO2D

Essentially, all of the W register is transferred to the D register with the exception of W(16-23). Information in the area of W48 - W16 is insignificant at this point, since the word in the W register contains only the address located in W(15-1).

Control is now transferred back to SC=O and D17F is set to enable another memory access. (D17F had been reset during SC=1). This transfer of control is accomplished through the following logic:

> SC/ = EXNF/ \* SO2DD17F = EXNF/ \* SO2D

As control is transferred to SC=0 the W register is cleared in anticipation of the next word load from memory. All of the actions described in SC=2 occur during the 1  $\mu$ s interval (SC=2 is true.)

- SC=0: Upon entering SC=0 and with D17F and MAØF/ true, a second memory cycle is initiated by setting MANF. The I/O Data Descriptor specified by the address in DO1-D15 is accessed and placed in the W register in the manner previously explained.

- SC=1: Actions performed during the second SC=1 are identical to those effected during the first half cycle.

- SC=2: Operations performed during SC=2 of the second half cycle are identical to those performed during SC=2 of the first half cycle with the exception of actions whose secondary logic is dependent upon the control EXNF/. EXNF is now true as a result of complementing logic performed during the previous SC=2.

Termination of the Standard Logic cycle for an initial I/O Data Descriptor load is performed as follows. Note that all actions occur at the first pulse following entry to SC=2.

> △ EXNF = SO2D W[15 => 1] to D[15 => 1] = SO2D W[45 => 24] to D[45 => 24] = SO2D

In addition to, and as a result of complementing EXNF/ at the previous SC=2, the following transfer and exiting logic is enabled:

$W[21 \Rightarrow 16]$  to  $LP[B \Rightarrow 1] = EXNF * SO2D$

The final result of the Standard Logic Cycle 0, 1, 2, 0, 1, 2---3 is illustrated in Figure 1-6.

All bit positions of the I/O Data Descriptor have been shifted to the D register except for the PERIPHERAL CONTROL field D21-D16 which is temporarily stored in the LP Buffer Register. This action is necessary since this field contains information in Magnetic Drum and Drum Printer operation which would be destroyed by ERROR field information developed in subsequent operations.

PERIPHERAL CONTROL information is retained in the LP Buffer until needed by the Drum or Drum Printer at later SC's.

#### LOAD LOGIC

#### General

The purpose of initial Load Logic is to load high speed core memory with a portion, or all, of the MCP or, alternately, a diagnostic program. Input to the I/O Control Unit is either from cards or drum and depends upon the physical location of the LOAD SELECT switch on the operator's console. TWO control levels are generated from this switch, termed:

LODL = Load Drum Level LOCL = Load Card Level

In order to read the MCP into core memory from the Drum or Card Reader it is first necessary to construct an appropriate I/O Data Descriptor specifying details of the operation to be performed; e.g., Unit Designate Number, starting core memory address, mode of operation and the number of words to be transferred. Also, if an LØDL operation is to be performed, the starting Drum address must also be specified.

Construction of an I/O Data Descriptor for the Drum or Card Reader is accomplished by setting certain significant flip-flops in the D register whose bit position and assigned weight correspond to the commands necessary to effect the load of memory.

Essentially, the D register is placed in a condition comparable to the terminal state of a standard I]O Data Descriptor load from memory. (SC=2 second half-cycle). When the proposed input operation has been completely described by the constructed Data Descriptor, control is transferred to SC=3 of the applicable unit and the operation commences.

Initiation of LODL or LOCL occurs when LOTS (load time switch) goes true at the depression of the LOAD pushbutton. The following operations will occur, depending upon whether a card load (LOCL) or Drum load (LODL) has been selected.

- A. DRUM LOAD = LOTS and LODL: Depressing the LOAD switch initiates the generation of an I/O Drum Descriptor which, in turn, loads high speed core memory from Band O of the Drum. The load of memory will start from memory cell 20 and ascend in address location to a specified 1000 words. Additional loading of further information is dependent on instructions contained in the already loaded portion of the MCP. Although the MCP can consist of 16,384 words, additional load instructions are required since the number of words to be read is specified and, therefore, limited by the capacity of the WORD COUNT field of the I/O Data Descriptor, or 1023 words (D40-D31).

- B. CARD READER Load = IOTS and IOCL: Depressing the IOAD switch causes one binary card to be read from the Card Reader with the lowest UNIT DESIGNATE number. Card information is loaded into core memory, starting from cell 20 octal in ascending address location to a specified maximum of 20 words (Cell 43). Additional load instructions are dependent upon internal control instructions contained in the first twenty words.

1-26

At the end of both LODL and LOCL a check is made to insure that information transfer has been performed without error. If the transfer is not complete or an error occurs, control is branched to memory cell 16 and the system left in such condition to allow another attempted load operation when the LOAD switch is again depressed. If transfer has been completed, without error, and Processor 1 is idle; then subsequent control of Processor 1 is transferred to cell 20.

Detailed Operation.

DRUM Load. Initially, both the D and W registers are cleared. When the LOAD pushbutton is depressed with the LOAD select switch in the LOAD DRUM position, the levels LOTS (Load Time) and LODL (Load Drum) will go true. As indicated in the Standard Logic Flow Chart in Figure 1-7, certain flip-flops in the D register will be set, forcing the construction of an I/O Drum Descriptor. Simultaneously, control is transferred to SC=3 of Drum operation. Applicable Drum load logic contained in the Standard Logic flow is shown in Figure 1-7.

The significance of this logic is explained as follows:

Address Field. Setting DO5F specifies that the starting core memory address (where the load of memory is to commence) is equal to absolute cell address 20.

I/O Control Filed. D24F indicates that this is a Drum read operation. Normally, a DRUM Descriptor contains this information in the W46F position which is then transferred to the D24F position, during the final W to D shift in SC=2 of the Standard Logic Cycle for an I/O Data Descriptor Load.

D27F signifies that the DRUM read operation will be performed in binary mode.

Word Count Field. D4OF specified that 512 words are to be read from the DRUM.

Unit Designate Field. D43F indicates the DRUM O4 shall be used in this operation.

The starting DRUM address is specified in the D16F-D30F field of the W register and in this case is equal to 0. The DRUM read will, therefore, start from Band 0 on the DRUM.

#### RESULT DESCRIPTOR

Terminate I/O Operation General. SC=14 and 15 of this Standard Logic Routine are used to terminate an I/O operation by constructing a Result Descriptor and returning this Descriptor to a specified address in Memory. This exit routine may be initiated by a number of logical situations arising during the processing of information through a peripheral device, but in general, is started as a result of two main conditions. Either:

1. An error condition has been detected during the course of an I/O operation and further information transfer is to be inhibited, or 2. The specified number of words have been transferred successfully (or unsuccessfully) and a normal exit from the I/O operation is to be performed.

In either case, a J14D (Jump to SC=14) level is generated and control transferred to SC=14.

The generation and storage of the I/O Result Descriptor is performed in two logical intervals as follows:

- SC=14: Transfer the Result Descriptor from the D register to the W register and set up a Result Descriptor Address for the particular I/O Control Unit used for the I/O operation.

- SC=15: Perform a Memory access write operation and transfer the Result Descriptor to the address specified in SC=14. After storage, clear the I/O Control Unit for the next operation.

Detailed Operation - SC=14. Transfer, upon entry to SC14, the D register contains the original I/O Data Descriptor modified in form and contents to include various results of error interrogations performed during the I/O operation. In order to transfer the Result Descriptor to Memory, it is necessary to shift all pertinent information from the D register to the W register (only W accesses memory directly). This action is accomplished at the first pulse following entrance to SC=14 through the generation of DWSD (D to W register shift) from the logic:

DWDS = S14S • MAPS

This is not a direct 45-bit transfer (as indicated) for all bits; however, since the state of Dl6F and Dl8F reflect the complement state of the corresponding W register flip-flop. That is, Wl6F and Wl8F are specified as true in the Result Descriptor when the designated unit is BUSY and NOT-READY; the opposite state of the logical conditions are established for Dl6F and Dl8F at the time of the BUSY-Ready test performed during SC=3.

As previously stated, W16F is set with D16F' and indicates that the designated unit is BUSY. D17F' is also included and logically indicates that a BUSY test was performed. If D17F' was not included, W16F would be set, even though the BUSY test was not performed since D16F is normally in the reset state.

NOTE

D17F, when set and recognized as such at  $SC=l_4$ , indicates, logically, that either MPED (Memory Parity Error) or a MAED (Memory Address Error) occurred while accessing the Descriptor address of the Descriptor itself. Normally, D17F is used as enabled logic for MANF and is set twice during the Standard Logic Cycle to allow the two memory accessed required to fetch the I/O Data Descriptor. At SC=l of each access, if no MPED or MAED (D19F/ or D22F/) error occurred, D17F is normally reset when the D register is cleared with the operation continuing normally into SC=2 and then SC=3. If, however, an error is detected (D19F or D22F) the operation exits immediately to SC=l4; and the D-Register is not cleared. Thus, upon entry to SC=14, D17F will still be set indicating that an MPED or MAED occurred while accessing the Data Descriptor or its address. Burroughs - B5500 Input/Output Control Training Manual

Conversely, if D17F is reset, it indicates that two memory accesses were performed successfully and that the operation did continue into SC=3--the logical interval where the BUSY and READY tests were performed. Therefore, upon entry to SC=14, D17F reset implies that a BUSY and READY test was performed and valid information is stored in D16F and D18F.

W18F is set with D18F' and D16F and signifies that the designated unit is NOT-READY although NOT-BUSY. As with W16F, D17F' is included in the logic to indicate that a READY test has been performed at SC=3.

#### CONSTRUCTING MEMORY ADDRESS

Concurrent with the transfer of the D-Register to the W-Register is the construction of an absolute address for returning the Result Descriptor to Core Memory. Each I/O Control Unit has a specific location in Memory for storage of its particular Result Descriptor as follows:

| I/0 | Address |

|-----|---------|

| 1   | 12,0    |

| 2   | 13,0    |

| 3   | 14,0    |

| 4   | 15,0    |

Since all addresses contain the common configuration DO3F and DO4F, these bits are set with the level CDRD-1 (Clear D-Register).

| D03F   | = | CDRD-1 |

|--------|---|--------|

| DOLF   | = | CDRD-1 |

| CDRD-1 | = | S14S   |

NOTE

#### DO3F and DO4F specify Address 12 for I/O #1.

The remaining addresses (13, 14, and 15) are defined by DOLF and DO2F which will be set according to the particular I/O Control Unit in use.

SC=14 operations (1  $\mu$ s) are terminated by transferring control to SC=15 with the same pulse which effects the register transfer and address construction operations.

Detailed Operation SC=15

Upon entry to SC=15, the following situations exist:

- 1. The Result Descriptor has been transferred to the W register.

- 2. An address has been constructed in the ADDRESS field of the D register to which the Result Descriptor is to be returned.

The purpose of SC=15 is to generate a memory access cycle and write the Result Descriptor into the address specified by DOIF-DI5F. Upon completion of the transfer an I/O Finished Level is generated and returned to Central Control and the I/O Control Unit cleared for the next I/O operation.

When the SC is counted to 15 MWRD (Memory Write) is generated. At the clock pulse following entry to SC=15, a Memory Access Needed (MANF) is enabled which, in turn, generates MAND which is sent to core memory.

MAND initiates a standard memory cycle by starting the memory clock (MTO - MT3). The next pulse sets the crosspoint flip-flops in Central Control connecting the I/O Control Unit to the Memory Module addressed (in this case Memory Module O or D13F-D15F=O).

MTO (Memory Time = 0) is now true; and with the next clock pulse, the address of the desired core location is set into MAR (Memory Address Register) from information contained in DOLF-DL2F. The same pulse transfers the  $\mu$ 8-bit Result Descriptor into MIR (Memory Information Register). The transfer of information into MAR and MIR is signaled by setting MAOF from the logic:

MAOF = MANF \* (MWRD \* MTOD + MAPS/)

MAPS/, in this expression, is concerned with maintenance operations and is not pertinent to this operation.

#### SECTION 2

#### CARD READER CONTROL

#### GENERAL

The purpose of this section is to describe the tie-in of the Card Reader to the B5500 I/0 Channel. It is written with the assumption that the reader does not have a detailed knowledge of either the Central Control or I/0 Control Exchange Channel logic. The intention is to enable a preliminary observation of the Card Reader operation from the I/0 Channel, and thereby help to ascertain whether a malfunction is within the Card Reader or is external to the Card Reader. Sufficient detail is presented to enable operation of the I/0 Channel and cause the reading of a card and the subsequent interrogation of the I/0 Result Descriptor.

The following is a list of card readers compatible to the Model III Input/Output Controls:

B9110 or B122 - Card Reader 200 cards/minute.

- B123 Card Reader 475 cards/minute. B124 transport speed and stacker blower removed; electronics adjusted to card speed.

- B9111 or B124 Card Reader 800 cards/minute. B129 transport speed slowed down and stacker blower removed; electronics adjusted to card speed.

- B9112 or B129 Card Reader 1400 cards/minute. Electronics adjusted to card speed.

- B9918 Postal Money Order Feature is available on B123, B124 or B129.

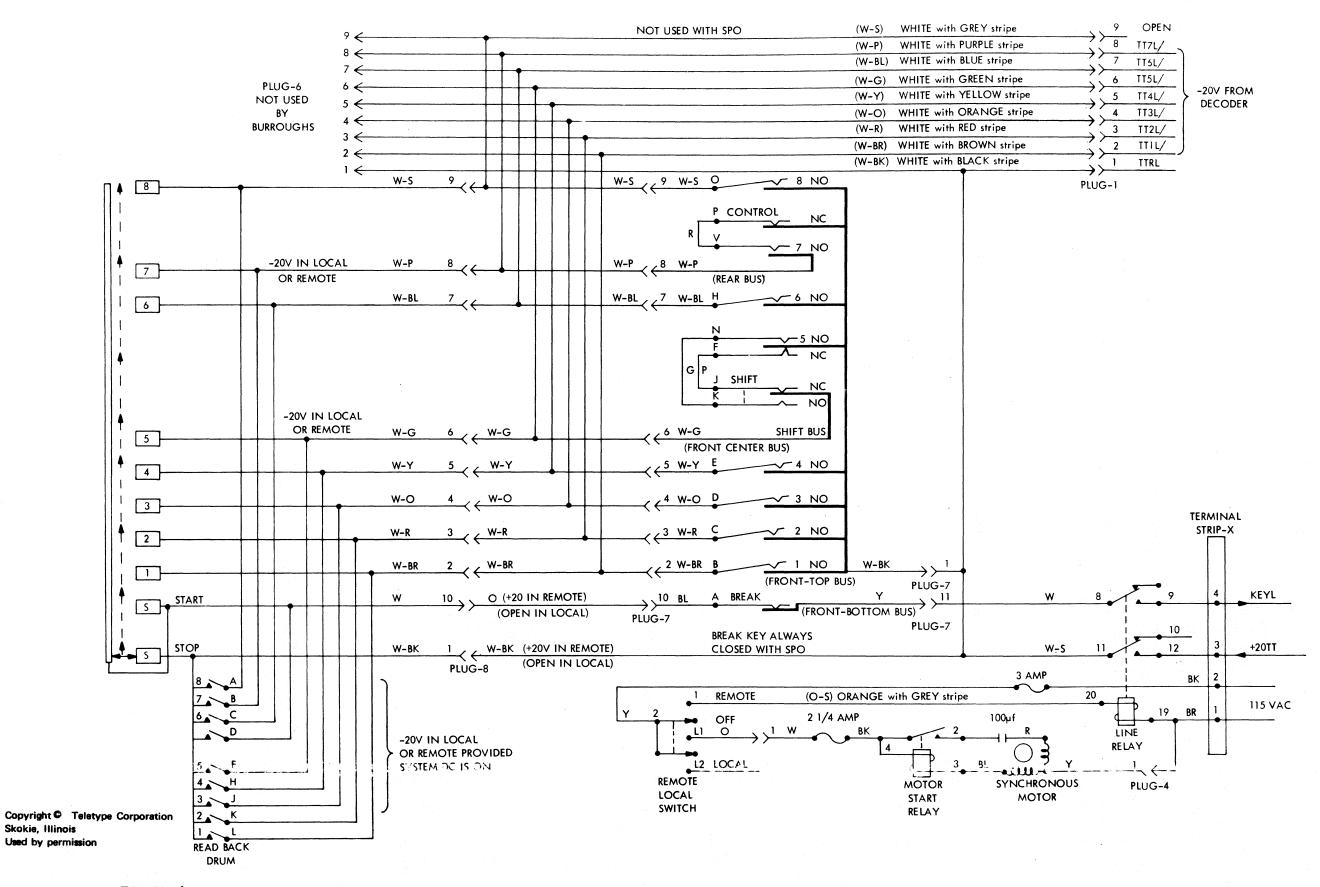

#### INTERCONNECTING LINES

The Card Reader cables are plugged into Winchester type connectors which are located at the rear of the Display and Distribution panel. Two connectors are provided for Card Reader use; one labeled Card Reader-1, the other labeled Card Reader-2. It should be noted that if only one Card Reader is incorporated within a system, it must be plugged into the connector labeled Card Reader-1. This requirement is due to the fact that when a load operation is initiated (i.e., IOAD button is pressed with Select switch in Card Load position), the logic assumes a Reader plugged into the Card Reader-1 connector.

The interconnecting lines which make up the cable from the Card Reader, may, for discussion purposes, be sub-divided into three groups:

- 1. Power supply and power control lines

- 2. Information lines

- 3. Logical control lines; to and from the Card Reader

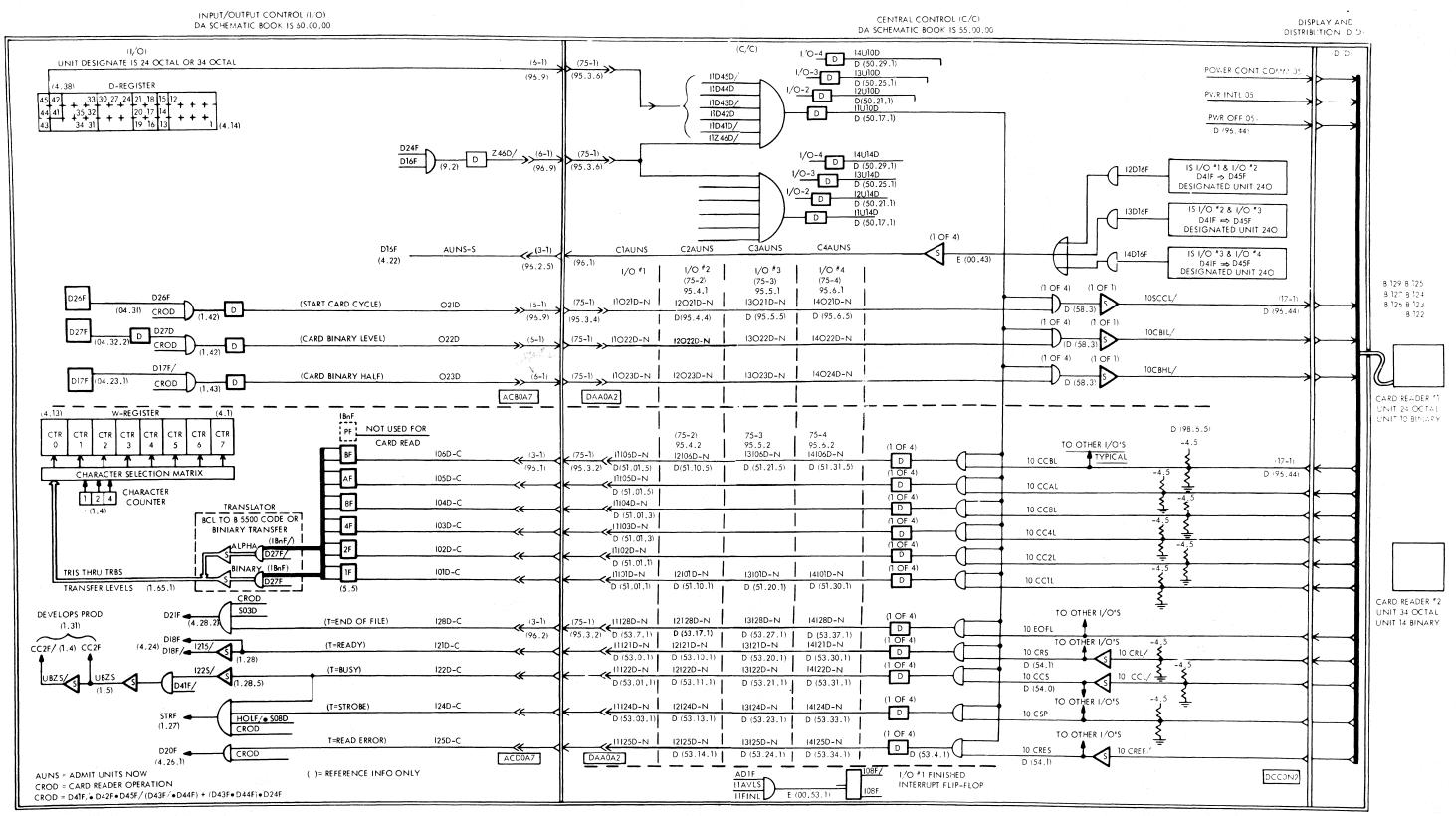

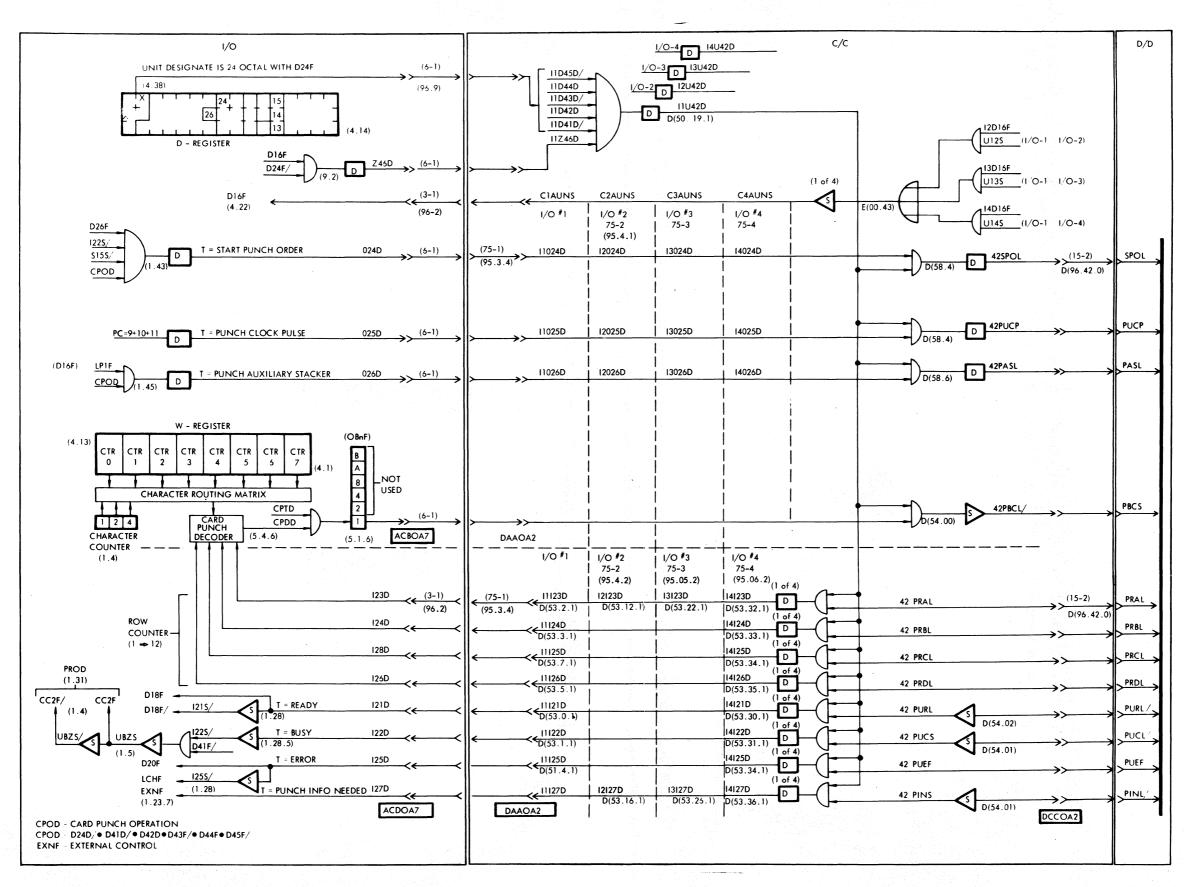

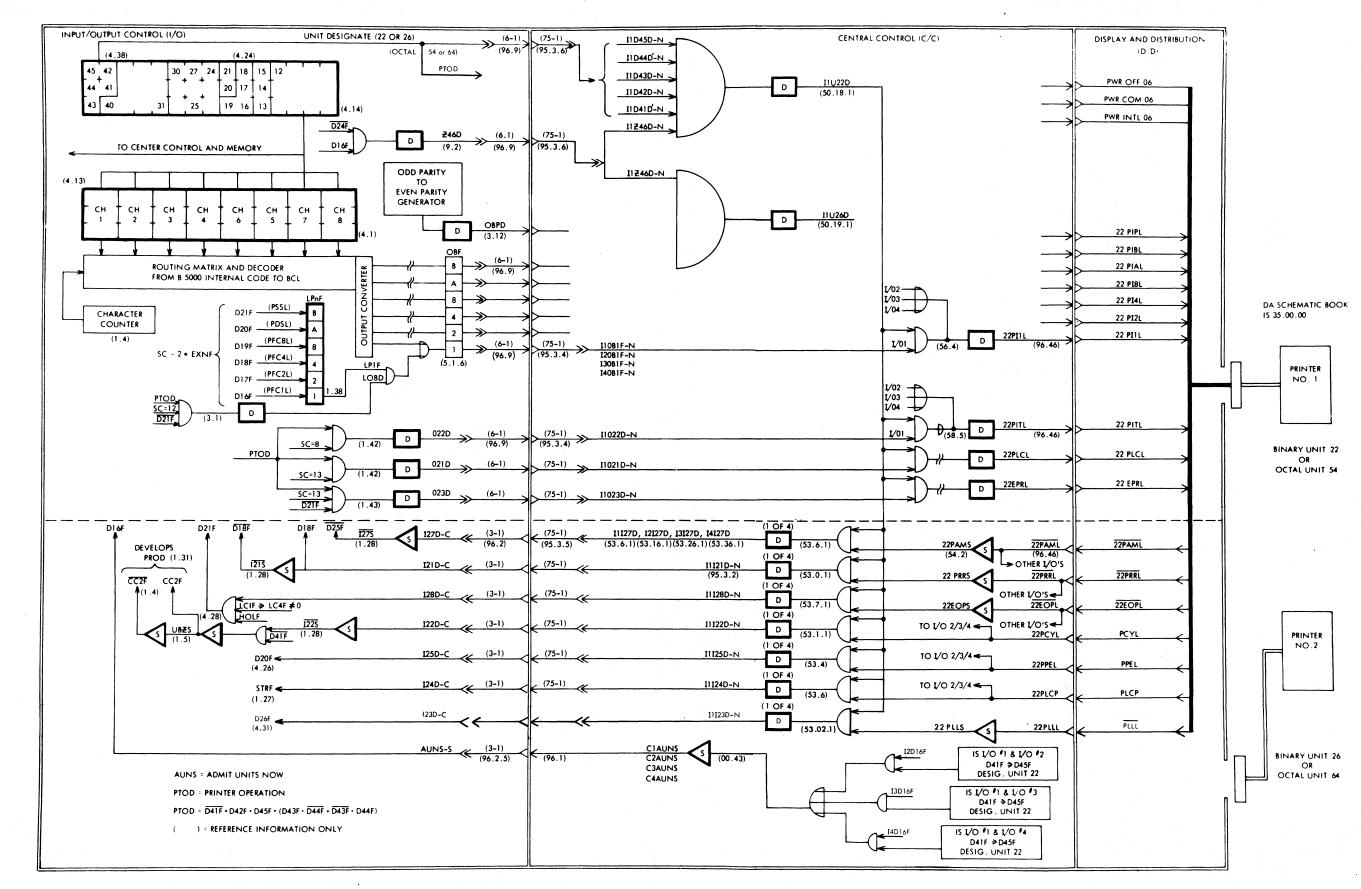

Figure 2-3 illustrates the Card Reader cable plugged into the Winchester connector at the rear of the Display and Distribution panel. The figure, as drawn, assumes the Card Reader plugged into the Card Reader-1 connector with I/O Channel #4 selecting (via I/O Exchange logic of Central Control) Card Reader-1.

2-1

#### POWER SUPPLY AND POWER CONTROL LINES

Six lines make up the power supply and power control lines (illustrated in Figure 2-3). The six lines are routed from the Winchester connector to the power control distribution unit which is located at the top rear panel of the Display and Distribution unit.

#### INFORMATION LINES

The information lines (CClL through CCBL) are externally cabled to a connector at Display and Distribution and then into the I/O Exchange area of Central Control. The internal cables for the Card Readers from Display and Distribution to Central Control are numbered 17-1 and 17-2; corresponding to Card Reader-1 connector and Card Reader-2 connector, respectively. Figure 2-3 assumes a Reader plugged into Card Reader-1, hence cable 17-1 lines are illustrated. The information lines are gated through the I/O Exchange area to the requesting I/O Channel via the Unit Designate level; in the example illustrated, UlOD from I/O Channel #4. On the D.A. Schematics, the mnemonics utilized by each I/O Channel to designate Card Reader-1 are IlUIOD, I2U10D, I3U10D and I4U10D, respectively. Likewise, for Card Reader-2, the mnemonics are IlU14D, I2U14D, I3U14D and I4U14D.

The information lines CClL through CCBL pass through drivers in the I/O Exchange area of Central Control. Thereafter, the names of the information lines become IOLD through IO6D. On the D.A. Schematics, the information line designation for I/O Channel #1 is IIIOLD through IIIO6D. Only one peripheral unit may be connected to any I/O Control Unit at any one time. The information lines IOLD through IO6D are gated, unclocked, into the Input Buffer (IB) of the designated I/O Control Unit.

If the Card Reader has been plugged into the Card Reader-2 Winchester connector instead of Card Reader-1, as illustrated, the information lines would have been gated through to the requesting I/O Control Unit via the level ILULLD (assuming I/O Channel #4 is the requesting Control Unit).

#### LOGICAL CONTROL LINES

The logical control lines from the Card Reader to the specified I/O Channel are gated through the I/O Exchange area of Central Control in a manner similar to the gating of the information lines. The levels  $\overline{CRL}$ ,  $\overline{CCL}$  and  $\overline{CREF}$  are switched in Central Control to become CRS, CCS and CRES, respectively. The output levels from the drivers to the specified I/O Control Unit are I21D, I22D, I24D, I25D and I28D. (Figure 2-3)

The logical control lines which are sent to the Card Reader ( $\overline{\text{SCCL}}$ ,  $\overline{\text{CBIL}}$  and  $\overline{\text{CBHL}}$ ) are gated through I/O Exchange of Central Control via the enabling level UlOD or UlLD; in Figure 2-3, the level UlOD is illustrated.

#### LOGICAL DESCRIPTION

#### NOTE

All address cells in this section refer to absolute addressing which is octal base.

#### INFORMATION AND CONTROL

An I/O Control Unit, when it receives an initiate level from Central Control, obtains from cell 10 of Memory "O" the address of the I/O Descriptor. Then the I/O Descriptor is accessed and subsequently placed in the D register of the I/O Control Unit. Once the D register contains the I/O Descriptor, the unit designate field, in conjunction with Dl6F and D24F, specifies (in the case of a Card Reader Descriptor) Card Reader-1 or Card Reader-2. Note that Dl6F does not appear in the original Descriptor but is set as an internal function of the I/O Control Unit operation. Dl6F is set as a result of the I/O Control Unit ascertaining that the specified Card Reader is not busy; this enables the start of a Card Reader operation. The enabling level developed via the Unit Designate field, Dl6F and D24F is termed Ul0D for Card Reader-1 and UL4D for Card Reader-2. This enabling level, Ul0D or UL4D, effectively connects the Card Reader to the requesting I/O Control Unit through I/O Exchange in Central Control. Figure 2-3 illustrates I/O Control Unit #4 selecting Card Reader-1.

The initiation of a card feed occurs when the I/O Control Unit sets bit D26F, causing the Start Card Cycle "not" line (SCCL) to go false. Once the Card Reader has been initiated as indicated by the level CCL going false, the D register bit D26F is reset. This removes the initiating start level to the Card Reader (SCCL goes true).

As each column of a card is read, the information lines are gated, unclocked, into the Input Buffer (IB) register. The column strobe pulse, going true, indirectly gates the transfer of a character from the IB register to the specified character position of the W register. The character positions of the W register are specified by the character counter which counts from 0 through 7. In the case of alphanumeric read, the BCL character code is converted to internal B5500 code in conjunction with the IB to W transfer. When a complete word has been assembled in the W register, a memory cycle is initiated to store the W register contents into the cell specified by the address field of the I/O Descriptor contained in the D register. As each word is stored into memory, the address field in the D register contents occurs after the eighth character transfers to the W register and prior to the next character transfer to the W register. In alphanumeric mode, 10 words are stored. In binary mode, 20 words are stored.

In the event of a card read error (CREL goes false), bit D2OF is set for subsequent indication in the Result Descriptor. For an END-OF-FILE condition, bit D21F is set in the Result Descriptor for EOF indication.

The D register bits D27F and D17F are utilized to determine the status of the level  $\overline{\text{CBIL}}$  and  $\overline{\text{CBHL}}$  to the Card Reader. The setting of D17F is an internal logical function of the I/O Control Unit. In the binary mode of operation, D17F, when set with the trailing edge of the column strobe pulse (CSP), results in the level  $\overline{\text{CBHL}}$  going true for subsequent reading of the lower half of a column. In this case, the I/O Control Unit developes its own sync to gate the transfer of a character from IB to the W register.

I/O CONTROL PANEL CONTROL

Reading a Result Descriptor

A function of the I/O Control logics is to construct an I/O Result Descriptor which is stored in memory. I/O Control Unit #1 stores its result descriptor in cell  $l_{4}$ .

Unit #2 in cell #15, Unit #3 in cell #16, and Unit #4 in cell #17. If it is desired to manually interrogate the I/O Result Descriptor, following an I/O operation, the following procedure may be utilized:

- 1. Place the I/O Control Unit in the local status.

- 2. Place the appropriate descriptor address in the address field of the D register.

- 3. Place the Memory Cycle switch in the memory cycle position (UP).

- 4. Insure that the system clock is running.

- 5. Press the I/O Channel START button.

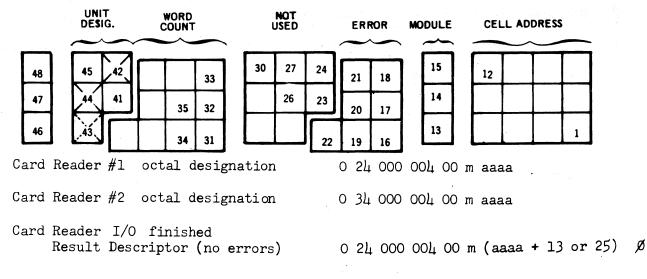

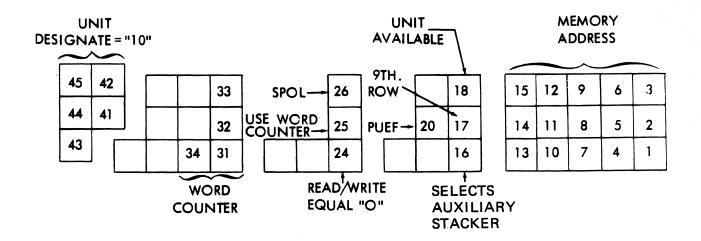

The word addressed by the 15 low order bits of the D register will be brought to the W register where interrogation may be accomplished. The interpretation of the various bit positions is as follows: (See Figure 2-1)

| Bits 48 | through | 46 -       | These bits are all off in the Result Descriptor                                           |

|---------|---------|------------|-------------------------------------------------------------------------------------------|

| Bits 45 | through | 41 -       | Unit designate; 24 for Reader-1, 34 for Reader-2                                          |

| Bits 40 | through | 23 -       | Bits 24 and 27 retain their original status; remaining bits will be reset                 |

| Bits 15 | through | 01 -       | Core storage address of last word stored plus one                                         |

| Bit 16  |         | · <u>-</u> | If set indicates designated unit (Card Reader) was not busy                               |

| Bit 17  |         |            | Descriptor Parity Error; either on access of Descriptor,<br>or address of Data Descriptor |

| Bit 18  |         | -<br>      | Designated unit (Card Reader) was ready                                                   |

| Bit 19  |         |            | Set if invalid character sensed by IB                                                     |

| Bit 20  |         |            | Read check error; set by CREL from the Reader                                             |

| Bit 21  |         | ~          | End-of-File; set by EOFL from the Reader                                                  |

| Bit 22  |         | <u></u>    | Memory address error; memory overflow of non-existent address                             |

#### Initiating a Read

The initiation of a card read cycle may be accomplished from the I/O Control Unit. The procedure to be described requires that an I/O Descriptor be constructed in the W register and stored in memory. Thereafter, the address at which the I/O Descriptor was stored is placed in cell 10 of memory. The card read I/O operation may then be initiated. The complete procedure to be followed is given below:

STEP 1 - Construct I/O Descriptor and store

1. Place I/O Channel in the local status

2-4

- 2. Construct I/O Descriptor in the W register

- 3. Place address at which it is desired to store descriptor in the D register

- 4. Set D register bit D24F to specify memory write operation

- 5. Place Memory Cycle switch in memory cycle position (UP)

- 6. Insure system clock is running

- 7. Press the I/O Control Unit START button

- STEP 2 Store Address of I/O Descriptor in Cell 10

- 1. Place address at which I/O Descriptor was stored in W register

- 2. Place cell address of 10 in the D register

- 3. Set D24F to specify memory write

- 4. Press I/O Control Unit START button

STEP 3 - Initiate I/O operation

- 1. Place the Memory Cycle switch in the down position

- 2. If desired, to perform repetitive card read cycles, place the Recycle switch UP; otherwise, leave it down

- 3. Press the I/O Control Unit START button

Upon completion of STEP 3 the I/O Channel will cause the card read cycle to take place. The I/O Result Descriptor may then be interrogated by the procedure previously described.

#### Error Stop

If repetitive card read cycles are initiated via the Recycle switch being placed in the UP position, the Error Stop switch may also be placed in the UP position. Utilizing this procedure, cards will continue to be fed (provided cards in the hopper and stacker not full) until an ERROR is detected in the Result Descriptor.

FIGURE 2-1 CARD READER DESCRIPTOR

DETAILED DESCRIPTION OF OPERATION CONTROL

#### NOTE

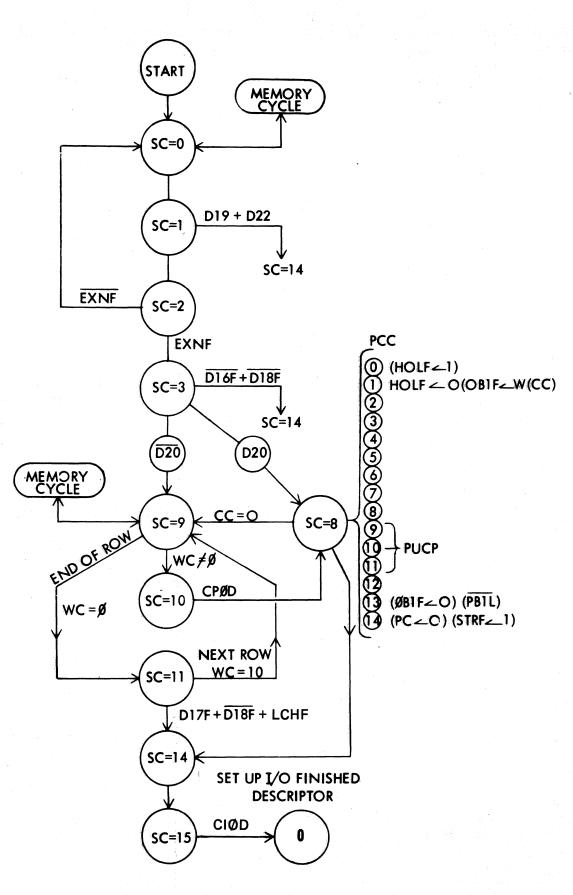

Use the Standard Flow and the Card Reader flow in conjunction with this writeup. See Figure 2-4.

Sequence Count Equals Zero (Standard Logic 1.01)

Obtain Descriptor Address. The Admit Descriptor level (ADnS-C) sets D17F to one and D04F to one. The latter operation establishes memory address 10 as the location to be accessed. D17F with Memory Access Obtained Flip-flop off (MAØF) allows Memory Access Needed Flip-flop (MANF) to be set. This initiates a memory read cycle which sets the Data Descriptor address into Memory Information Register (MIR). When MAØF is set by Memory Access Needed and Memory Timing Two Driver, MANF will be reset and also Memory Information Strobe drive (MISD) will place the information into the W register. With MANF, reset MAØF; with MANF and MAØF, count Sequence Counter up one.

Obtain Descriptor. With  $\overline{MA \# P}$  and D17F (from SC = 2), set MANF. Since the above operation placed the address of the descriptor in D, this memory operation brings up the descriptor. When MA # F is set, MISD will place the word in W and MANF is reset. With MANF, reset MA # F and count the Sequence Counter up one.

If there is a Memory Address Error (MAED-C), set D22F and reset MANF, and if there is a Memory Parity Error (MPED-M), set D19F.

If a card load cycle is to be initiated, the switch on the Operator's Console must be in the Load Card position, (LØCL-C) and when the LOAD pushbutton is depressed, the Load Timing switch (LØTS-C) initiates the setting of Sequence Counter to 3, setting D24F to signify a read, setting D27F to read in binary mode, and D05F to place the first word read in memory location 20. With LØCL-C, D44F and D42F set, this designates a Card Reader Unit. From this point on, the Card Reader flow is normal. Sequence Count Equals One (Standard Logic 1.01)

If previously detected error conditions exist, set Sequence Counter to 14 and clear "W", if not, clear "D" and count Sequence Counter up one.

Sequence Counter Equals Two (Standard Logic 1.10)

Unconditionally, complement the External Control Flip-flop (EXNF) and place the contents of the "W" register in "D" register. If the address is being transferred (first time through),  $\overline{\text{EXNF}}$  will set D17F and set the Sequence Counter to zero. Memory Access Permitted switch output will clear the "W" register in remote operation. If the descriptor is being transferred (second time through), W goes to D and EXNF is reset but Sequence Counter is counted up one. The Longitudinal Parity Decade (LP [B  $\rightarrow$  1]) is not used during the card read operation.

GLOSSARY OF I/O TERMS:

- D17F During the binary card cycle, it is used to indicate to the Card Reader which half of the card column is needed by the I/O Unit.

- D19F If an invalid character should be read from a card, this flip-flop remembers it. It is part of the Result Descriptor

- D2OF If a Card Reader Error Level has occurred during the card read cycle, this flip-flop is set for this indication in the result descriptor.

- D21F If an End-of-File condition is initiated in the Card Reader, this flip-flop remembers it.

- D31F-D40F These flip-flops are part of the D register. They make up the Word Counter for all operations. The Card Reader operation uses D31F-D35F only.

- EØFL End-of-File Level This level is sent to the Central Control Unit when an End-of-File condition exists in the Card Reader. This level comes from the Central Control in the I/O Unit as I23D.

- HØLF Hold Over Flip-flop Used to allow only one group of actions to take place for any one CSP during alpha card read. Allows two groups of actions to take place for any one CSP during binary card read.

- IOLD=IO6D These are the 6 drivers in the Central Control Unit that send across the six information bits of a character to the I/O Unit.

- LCHF Last Character Flip-flop This flip-flop is used to cause the Result Descriptor to be sent back to Core Memory. Also causes the Read Error Flip-flop (D2OF) to be set. This flip-flop is set only when a card has been read, but all 80 CSP's were not received in the I/O Control Unit.

- LØCL-C Load Card Level Derived from a toggle switch, used to cause a card read operation. The card is read binary mode.

- LØTS-C Load Timing Switch Used to initiate a card read cycle or an operation.

- SCCL Start Card Cycle Level Sent to the Card Reader by Ø21D at SC = 3 if the Card Reader is not busy and is ready.

- STRF Strobe Flip-flop This flip-flop is used for control purposes in the I/O Control Unit. It is turned on with every CSP from the Card Reader in alpha mode, twice in binary mode.

## GENERAL DESCRIPTION OF OPERATION

The function of the I/O Control Unit for a card read operation is to provide the external logics necessary to read a punched card in either alphanumeric or binary mode with either the 200 CPM, 800 CPM or the 1400 CPM Reader.

Information is read in from the card serially, by column, starting with column one. The word is formed in the W register of I/O Control, with the most significant character first. Memory is counted up as each word is stored. In alphanumeric mode, one card column reads in as one character and eight characters fill one word in memory, making a total of ten words from one card. In binary mode, each column of the card makes two characters, four columns make one word and twenty words make one card. The upper half of the column is the most significant character of the two characters. Any unpunched column of the card is read as a binary zero.

When the object program finds that the memory area designated for input information is empty, the Master Control Program (MCP) will call for a Data Descriptor to fill this area in memory from the Card Reader. The Unit Designate Field of the Data Descriptor (bit positions 45 - 41) designates the Card Reader. If there are two Card Readers on the system, it also designates which one. Unit designate number (octal) 24 is for Card Reader #1, (octal) 34 is for Card Reader #2.

When the MCP finds the Data Descriptor for the Card Reader, it will store the address of the descriptor in cell (octal) 10. At the same time the Processor will signal the Central Control that an I/O operation is needed. Central Control will signal the lowest numbered I/O Unit which is not busy, to access cell 10 for the address of the Data Descriptor. This action will initiate the I/O Control into action to load from the Card Reader the requested area in memory.

## BASIC FLOW

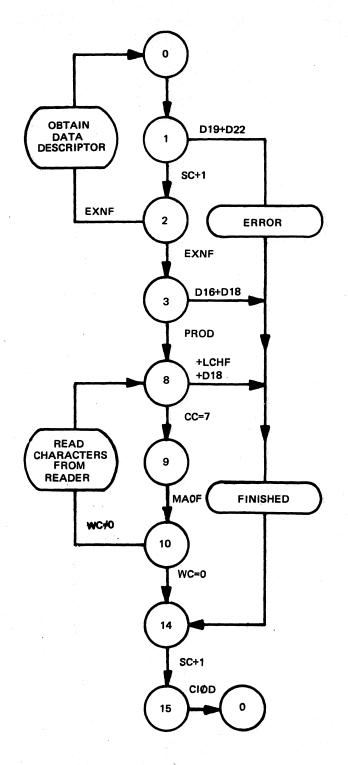

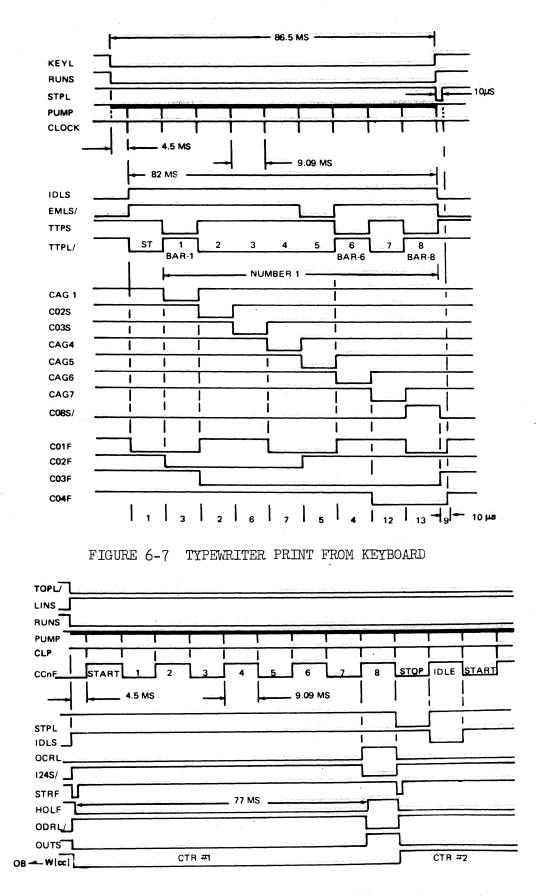

The card read sequence of operations is shown in Figure 2-2, while a general block diagram of signal and control paths is contained in Figure 2-3.

- SC = 0, 1 & 2: Operation initiated by ADNS or LØTS signal from Central Control. Two memory accesses are performed:

- 1. Read Descriptor Address from Memory cell 10

- 2. Read Descriptor from Memory

- SC = 3: Interrogate peripheral unit trunk, Designate peripheral unit, and interrogate peripheral unit's status (READY BUSY).