HP 13220 PROCESSOR MODULE Manual Part No. 13220-91088 REVISED AUG-14-81

# DATA TERMINAL TECHNICAL INFORMATION

#### 1.0 INTRODUCTION

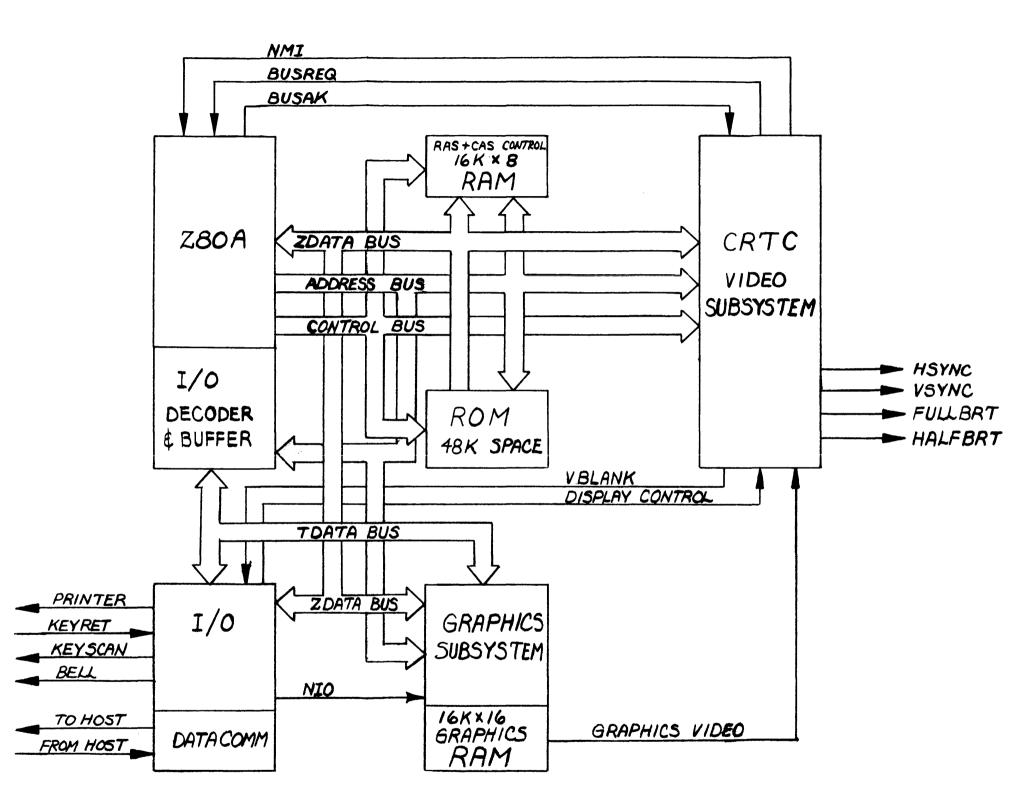

The 02620-60088 Processor PCA performs the terminal logic functions for the 2623A terminal. Its operation is based on the Z80A microprocessor, National Semiconductor 8367 CRT Controller (CRTC), and a prom based microsequenced graphics controller.

The control and I/O section of the Processor PCA provides control signals, input/output and data processing functions. The memory section provides 16K bytes of dynamic RAM for character display memory, scratch pad memory, data buffers and space for up to six 4K or 8K byte ROMs of which 40K are used for complete terminal operation (4K of ROM optional with integral printer). The Graphics memory subsystem contains 16K words (16K X 16) of vector display memory. The Graphics subsystem is responsible for both write and display refresh of the graphics memory. The video control section provides timing signals for driving the sweep circuitry and video logic as well as performing direct memory access (DMA) of display data. A detailed description of the operation of each of these sections follows in section 3.0.

2.0 OPERATING PARAMETERS.

A summary of operating parameters for the Processor Module is contained in tables 1.0 through 4.0

|               |                 |                     | 21 JEJ 221 121 121 121 121 121 121 121 121 12 |

|---------------|-----------------|---------------------|-----------------------------------------------|

| l Part        | 1               | I Size (L x W x D)  | l Weight l                                    |

| l Number      | l Nomenclature  | +/-0.1 Inches       | l (Pounds) l                                  |

|               |                 |                     | =   =======                                   |

| 1             | 1               | 1                   | 1                                             |

| 1             | 1               | 1                   | 1                                             |

| 1 02620-60088 | I Processor PCA | 1 12.3 x 10.9 x 0.5 | 1 1.4 1                                       |

| 1             | 1               | 1                   | 1 1                                           |

|               | 1               | 1                   | 1 1                                           |

| ł             | 1               | 1                   | 1                                             |

|               |                 |                     |                                               |

#### Table 1.0 Physical Parameters

# HP 13220

# PROCESSOR MODULE

# Manual Part No. 13220-91088

# REVISED

# AUG-14-81

| 1 |                                                                         |

|---|-------------------------------------------------------------------------|

| 1 | NOTICE                                                                  |

|   | NUTICE                                                                  |

| 1 | The impension approximation described and in anti-                      |

| 1 | The information contained in this document is subject to change without |

| 1 | notice.                                                                 |

| 1 |                                                                         |

| 1 | HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS       |

| 1 | MATERIAL, INCLUDING, BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF       |

| I | MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard   |

| I | shall not be liable for errors contained herein or for incidental or    |

| 1 | consequential damages in connection with the furnishing, performance,   |

| 1 | or use of this material.                                                |

| 1 |                                                                         |

| ł | This document contains proprietary information which is protected by    |

| 1 | copyright. All rights are reserved. No part of this document may be     |

| 1 | photocopied or reproduced without the prior written consent of Hewlett- |

| 1 | Packard Company.                                                        |

| 1 |                                                                         |

| i |                                                                         |

# Copyright c 1981 by HEWLETT-PACKARD

NOTE: This document is part of the 262XX DATA TERMINAL product series Technical Information Package (HP 13220).

#### 1.0 INTRODUCTION

The 02620-60088 Processor PCA performs the terminal logic functions for the 2623A terminal. Its operation is based on the Z80A microprocessor, National Semiconductor 8367 CRT Controller (CRTC), and a prom based microsequenced graphics controller.

The control and I/O section of the Processor PCA provides control signals, input/output and data processing functions. The memory section provides 16K bytes of dynamic RAM for character display memory, scratch pad memory, data buffers and space for up to six 4K or 8K byte ROMs of which 40K are used for complete terminal operation (4K of ROM optional with integral printer). The Graphics memory subsystem contains 16K words (16K X 16) of vector display memory. The Graphics subsystem is responsible for both write and display refresh of the graphics memory. The video control section provides timing signals for driving the sweep circuitry and video logic as well as performing direct memory access (DMA) of display data. A detailed description of the operation of each of these sections follows in section 3.0.

2.0 OPERATING PARAMETERS.

A summary of operating parameters for the Processor Module is contained in tables 1.0 through 4.0

| 1     | Part        | 1              | I Size (L x W x D)                    | l Weight I   |

|-------|-------------|----------------|---------------------------------------|--------------|

| 1     | Number      | l Nomenclature | l +/-0.1 Inches                       | l (Pounds) l |

| == == |             |                | ===================================== |              |

| 1     |             | 1              | 1                                     | 1 1          |

| t     |             | 1              | 1                                     | 1 1          |

| I     | 02620-60088 | Processor PCA  | 1 12.3 x 10.9 x 0.5                   | 1 1.4 I      |

| 1     |             | 1              | 1                                     | 1 1          |

| 1     |             | 1              | 1                                     | 1 1          |

| ł     |             | 1              | 1                                     | 1            |

|       |             |                |                                       |              |

#### Table 1.0 Physical Parameters

Table 2.0 Reliability and Environmental Information

```

1

1

1

I Environmental: HP Class B

1

1

I Restrictions: Type tested at product level

1

1

1

1

1

Failure Rate: 3.71 (percent per 1000 hours)

1

1

I

1

```

| Table | 3.  | 0 | Powe | er Supp | 1 y | Requirer | nents |    | Measured |

|-------|-----|---|------|---------|-----|----------|-------|----|----------|

| 1     | (At | + | /5%  | Unless  | Öt  | herwise  | Speci | fi | .ed)     |

| <br>  +i6 Volt Supply   +i2 Volt Supply | +5 Volt Supply   -12 Volt Supply |

|-----------------------------------------|----------------------------------|

| I @ 0 mA I @ 475 mA I                   | 65.0A 677 mA 1                   |

| I NOT APPLICABLE I                      |                                  |

|                                         |                                  |

| 1                                       | I I                              |

| l 115 volts ac                          | 220 volts ac                     |

|                                         |                                  |

|                                         | I @ A I                          |

|                                         | NOT APPLICABLE                   |

| I NOT APPLICABLE                        |                                  |

|                              | 10010 Y. 0 0011 | nector Information                                        |

|------------------------------|-----------------|-----------------------------------------------------------|

| Connector  <br>  and Pin No. | Signal<br>Name  | Signal  <br>  Description                                 |

| J1                           |                 | ** PRINTER **                                             |

| Pin 1                        | PRINTER         | Negative True, Printer Strobe                             |

| -2                           | PWR ON/FAIL     | Negative True,Power On/Failing                            |

| -3                           | WRITE           | Negative True, Write signal                               |

|                              | A1              | Negative True, Select bit 1                               |

|                              |                 |                                                           |

|                              | DATA 0          | LSB - Negative True, Data                                 |

| -7                           | DATA 1          |                                                           |

| · -8                         | DATA 2          |                                                           |

| -9                           | DATA 3          |                                                           |

|                              | DATA 4          |                                                           |

| -11                          | DATA 5          |                                                           |

| -12                          | DATA 6          |                                                           |

| -13                          | DATA 7          | I MSB - Negative True, Data I                             |

| 14                           | GND             | I Set printer contrast                                    |

| -16                          | PINT            | Negative True, Printer Interrupt                          |

| -17                          | A0              | Negative True, Select bit 0                               |

| -18                          | +5V             | I Vac Power I                                             |

| -19                          | +5V             | l . I                                                     |

| -20                          | +5V             | 1                                                         |

| -21 i                        |                 | 1                                                         |

| -22                          |                 | I Power Return                                            |

| -23                          | CND             | 1 1 9 97 56 1 15 6 1 97 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| -24                          |                 |                                                           |

| -25 1                        |                 |                                                           |

|                              |                 |                                                           |

| -26                          |                 |                                                           |

| Table | 4.0 | Connector | Information | (Cont'd) |

|-------|-----|-----------|-------------|----------|

|       |     |           |             |          |

| I Connector 1                         | Signal      | I Signal I                                    |

|---------------------------------------|-------------|-----------------------------------------------|

| I and Pin No. I                       |             | l Description l                               |

|                                       |             |                                               |

| I J2                                  |             | I ** POWER SUPPLY **                          |

| 1                                     |             | 1                                             |

| Pin -1                                | +5V         | 1 +5V Power I                                 |

| 1 -2 1                                |             | I N/C I                                       |

| 1 -3 1                                | +5V         | 1 +5V Power 1                                 |

| 4                                     | +12V        | 1 +12V Power 1                                |

| -5                                    | GND         | 1 Return for Power 1                          |

| -6                                    | GND         | Return for Power                              |

|                                       |             |                                               |

| -7                                    | PWR ON/FAIL | Negative True, Power On/Failing               |

| 1 -8 1                                | -12V        | 1 -12V Power I                                |

| -9                                    | BATTERY     | Positive Battery Terminal                     |

| I                                     | BATRET      | I Negative Battery Terminal I                 |

| • • • • • • • • • • • • • • • • • • • |             |                                               |

| 1 J3                                  |             | I ** SWEEP ** I                               |

| 1<br>1 10 dan - 4 1                   | HLFBRT      | l<br>I Manadalan Anasa Materia Madana - I     |

| Pin -1                                | FILF BR I   | I Negative true, Half Bright Video I          |

|                                       | RETURN      | I N/C I<br>I Return for half bright twisted I |

| 1                                     | RETORIA     | -                                             |

|                                       |             | l pair l                                      |

| 14 1                                  | FULLBRT     | Negative true, Full Bright Video              |

| 1 -5 1                                | RETURN      | I Return for Video twisted pair               |

| I -6 I                                | RETURN      | I Return for Drive signals                    |

|                                       |             |                                               |

| -7                                    | VERDR       | Negative True, Vertical Drive                 |

| 1 -8 1                                | HORDR       | Horizontal Drive                              |

|                                       |             |                                               |

| I J4 I                                |             | I ** KEYBOARD **                              |

| 1                                     |             | 1                                             |

| 1 Pin -1 1                            | KEY0        | i Key Data (LSB) i                            |

|                                       | KEYI        | I Key Data I                                  |

|                                       | KEY2        | I Key Data I                                  |

|                                       | KEY3        | I Key Data I                                  |

| 1 -5 1                                | KEY4        | I Key Data I                                  |

| 1 -6 1                                |             | I N/C                                         |

| i7 i                                  | KEYS        | I Key Data I                                  |

| I -8 I                                | KEY6        | I Key Data (MSB)                              |

| 1                                     |             |                                               |

| I -9 I                                | KEYACT      | I Key Active (Status, key selected)           |

| I -10                                 | GND         | I Power Return                                |

| -11                                   | BELL        | I Bell Line I                                 |

|                                       | +5v         | 1 +5v Power                                   |

| -13                                   | +120        | 1 +12v Power                                  |

| 1 -14                                 | -12v        | 1 -12v Power                                  |

|                                       |             |                                               |

|                | Table 4.0 Con | nector Information            |

|----------------|---------------|-------------------------------|

| 1 Connector    |               | I Signal I                    |

| l and Pin No.  |               | l Description I               |

|                |               | I ** EXTERNAL PRINTER PORT ** |

| 1 Pin -1       | I SHIELD      | I Shield ground I             |

| -2<br>1        | SD            | I Transmitted Data I          |

|                | IRD           | Received Data                 |

| l4             | I RS          | Request to Send               |

| -5             | i CS          | Clear to Send                 |

| l –6           | I DM<br>I     | I Data Set Ready I            |

| -7             |               | Signal Ground                 |

| l -8           | 1             |                               |

| 9              |               |                               |

| 1              | <br>          |                               |

| 1 -11          |               |                               |

| -12            | OCR2          | I Secondary Receive Ready I   |

| -13            |               | IN/C I                        |

| l              |               |                               |

| l –16          |               |                               |

| -17            | i<br>1        | I N/C I                       |

| I -18          |               | I N/C I                       |

| -19            |               | I Secondary Request to Send I |

| 1 -20          |               |                               |

| l –21<br>l –22 |               | 1 N/C I<br>1 N/C I            |

| -23            |               |                               |

| 1 -24          |               |                               |

| -25            |               |                               |

| I -26 (        |               | I N/C I                       |

|                |               |                               |

| Table | 4.0 | Connector | Information | (Cont'd) |

|-------|-----|-----------|-------------|----------|

| I Connector I                           |                   | Signal I               |

|-----------------------------------------|-------------------|------------------------|

| l and pin No. I                         | Name              | l Description  <br>    |

| J 56 I                                  |                   | ** DATA COMM **        |

| <br>  Pin -1                            |                   |                        |

|                                         | +5V               | +5V Pod Power          |

|                                         | +5V               | I +5V Pod Power        |

|                                         | GND               | Power Return           |

| · -5                                    | GND               | l Power Return         |

|                                         | GND               | Power Return           |

|                                         | OCD1              | Rate Select (23)       |

| I -8 I                                  |                   | N/C                    |

| I -9 I                                  | RD                | Received Data (3)      |

| I -10 I                                 |                   | N/C                    |

| · -11                                   |                   | Clear To Send (5)      |

| I -12 I                                 |                   | Data Set Ready (6)     |

| i –13 i                                 |                   | I N/C                  |

| ·                                       |                   |                        |

| i –15 i                                 |                   | Signal Ground (7)      |

| -16                                     |                   | N/C                    |

| i –17 i                                 |                   |                        |

| -18                                     | OCR1              | Ring Indicator (22)    |

| -19 I                                   |                   | +12V Pod Power         |

| -20                                     |                   | -12V Pod Power         |

| I -21 I                                 | SD                | Transmitted Data (2)   |

| 1 -22 1                                 | RS                | Request To Send (4)    |

| 1 –23 1                                 | TR                | Ready (20)             |

| 1 -24 1                                 |                   |                        |

| I –25 I                                 | Ĩ                 | IN/C I                 |

| -26                                     |                   | I N/C I                |

| I –27 I                                 | 1                 | IN/C I                 |

| I –28 I                                 |                   | I N/C I                |

| I –29 I                                 | 1                 | IN/C I                 |

| I -30 I                                 | 1                 | IN/C I                 |

| I –31 I                                 |                   | I N/C I                |

| I -32 I                                 | GND               | l Return l             |

| I –33 I                                 |                   | Shield Ground (1)      |

| 1 – 34 I                                | 1                 |                        |

| I                                       |                   |                        |

| I Notes                                 | ;: (n) denotes th | ne RS-232 pin number l |

| 121 121 121 121 121 121 121 121 122 122 |                   |                        |

# 3.0 FUNCTIONAL DESCRIPTION

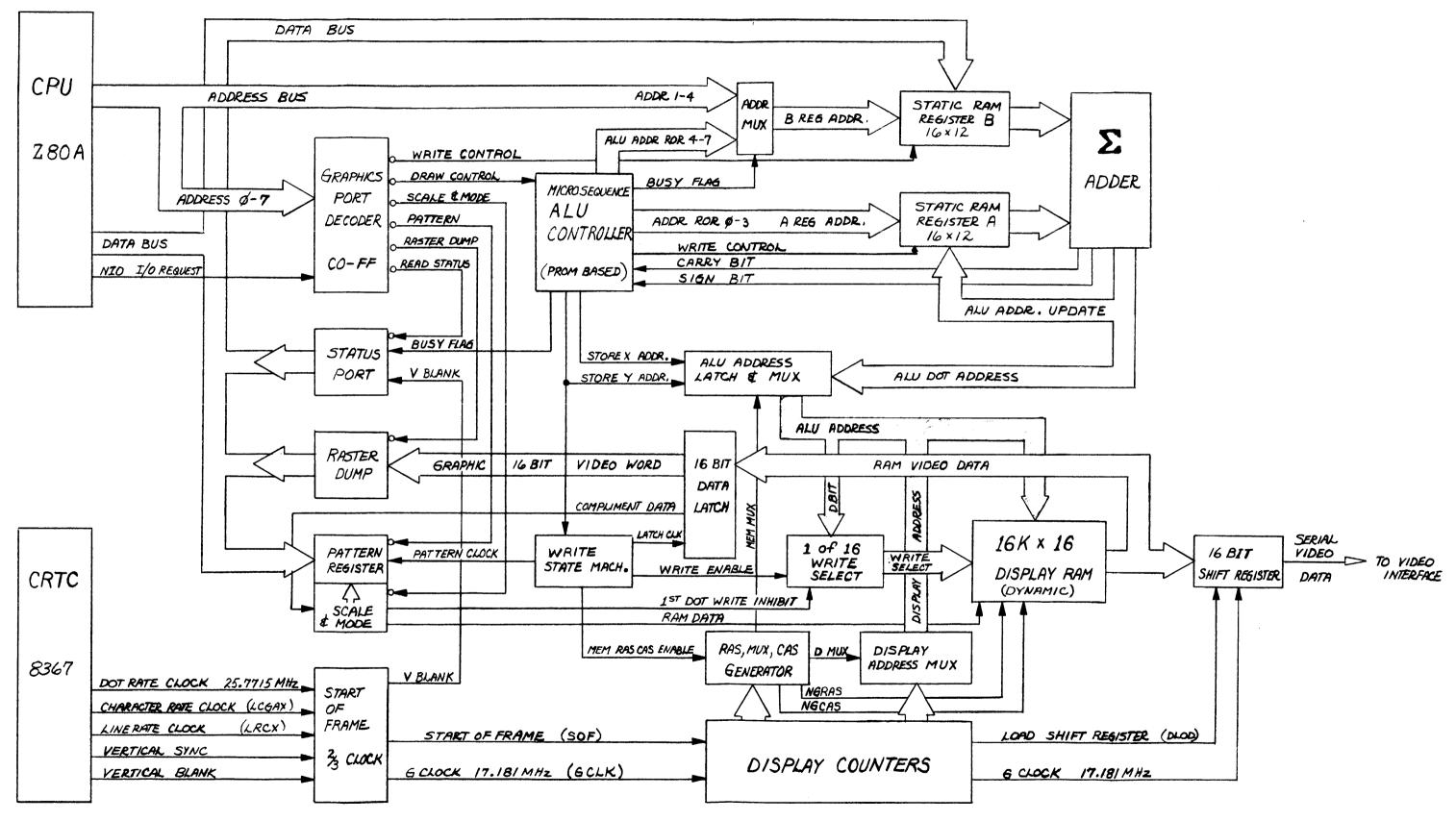

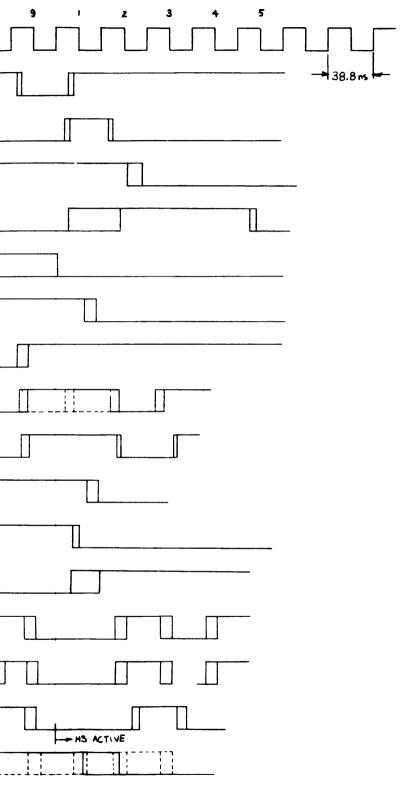

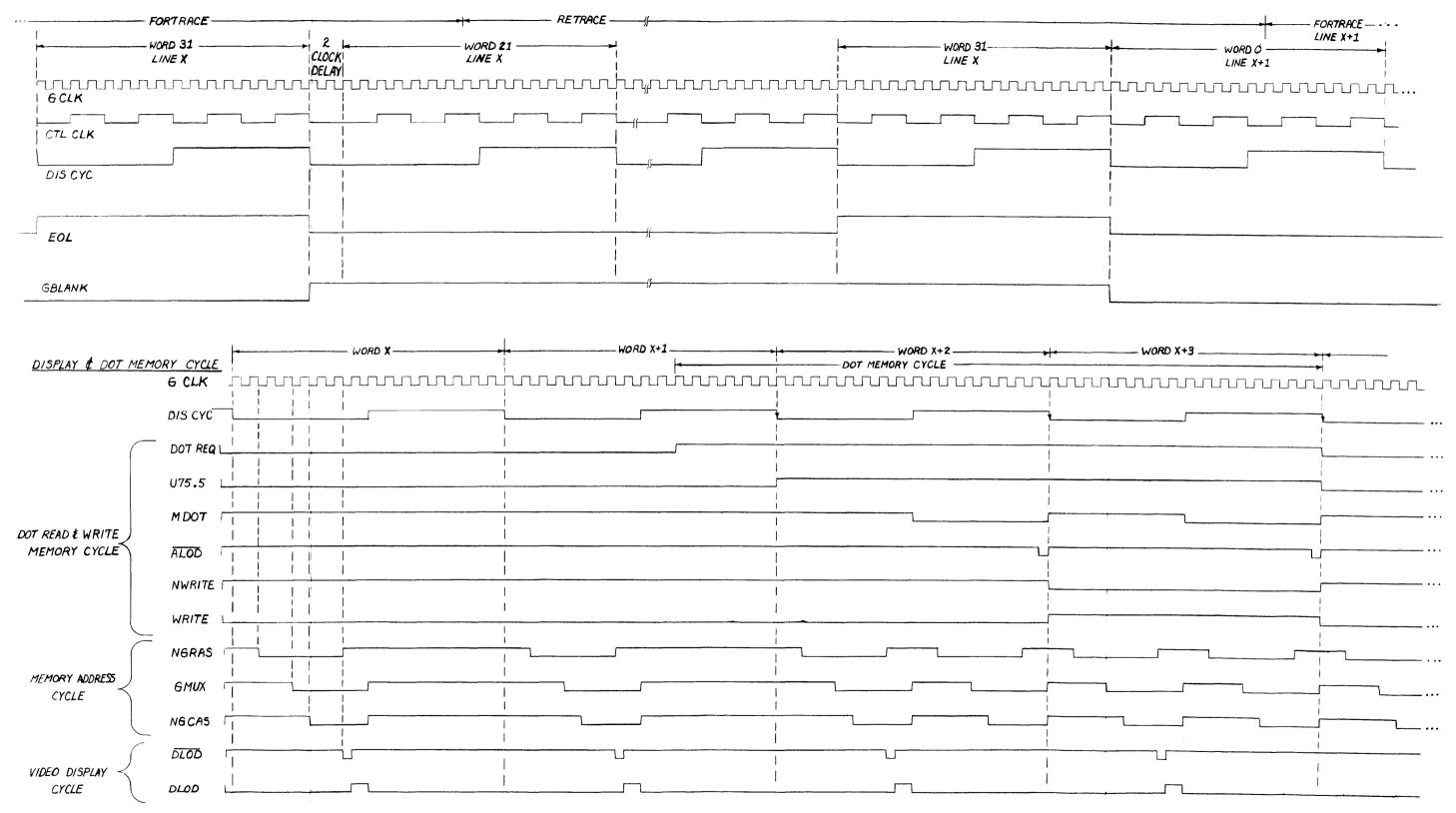

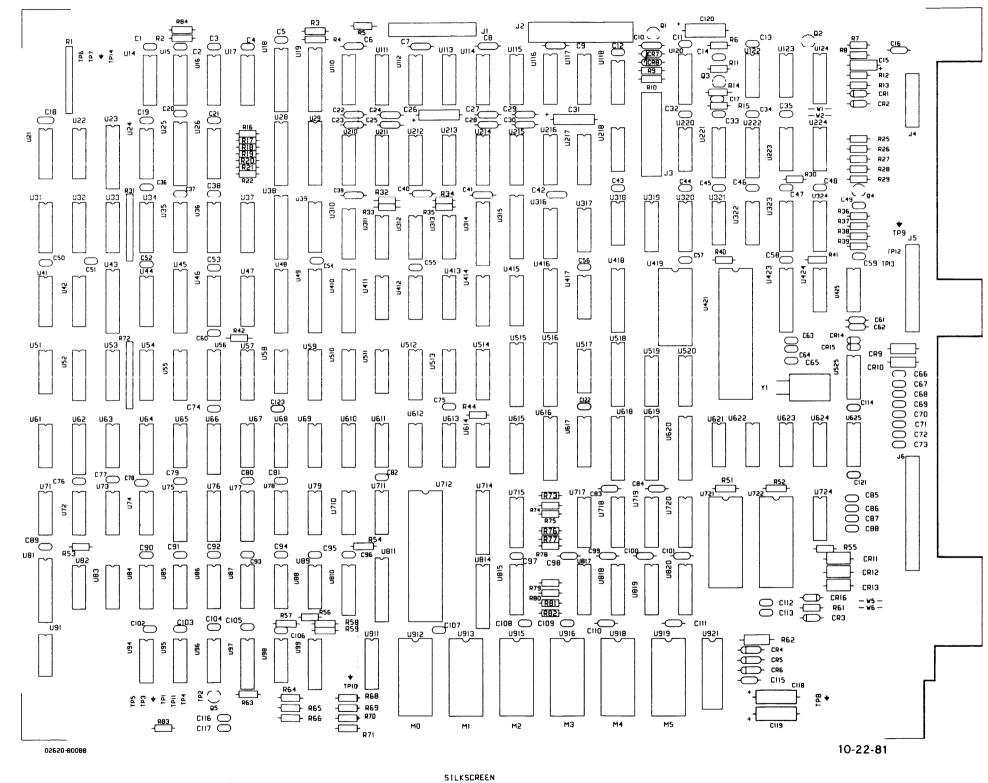

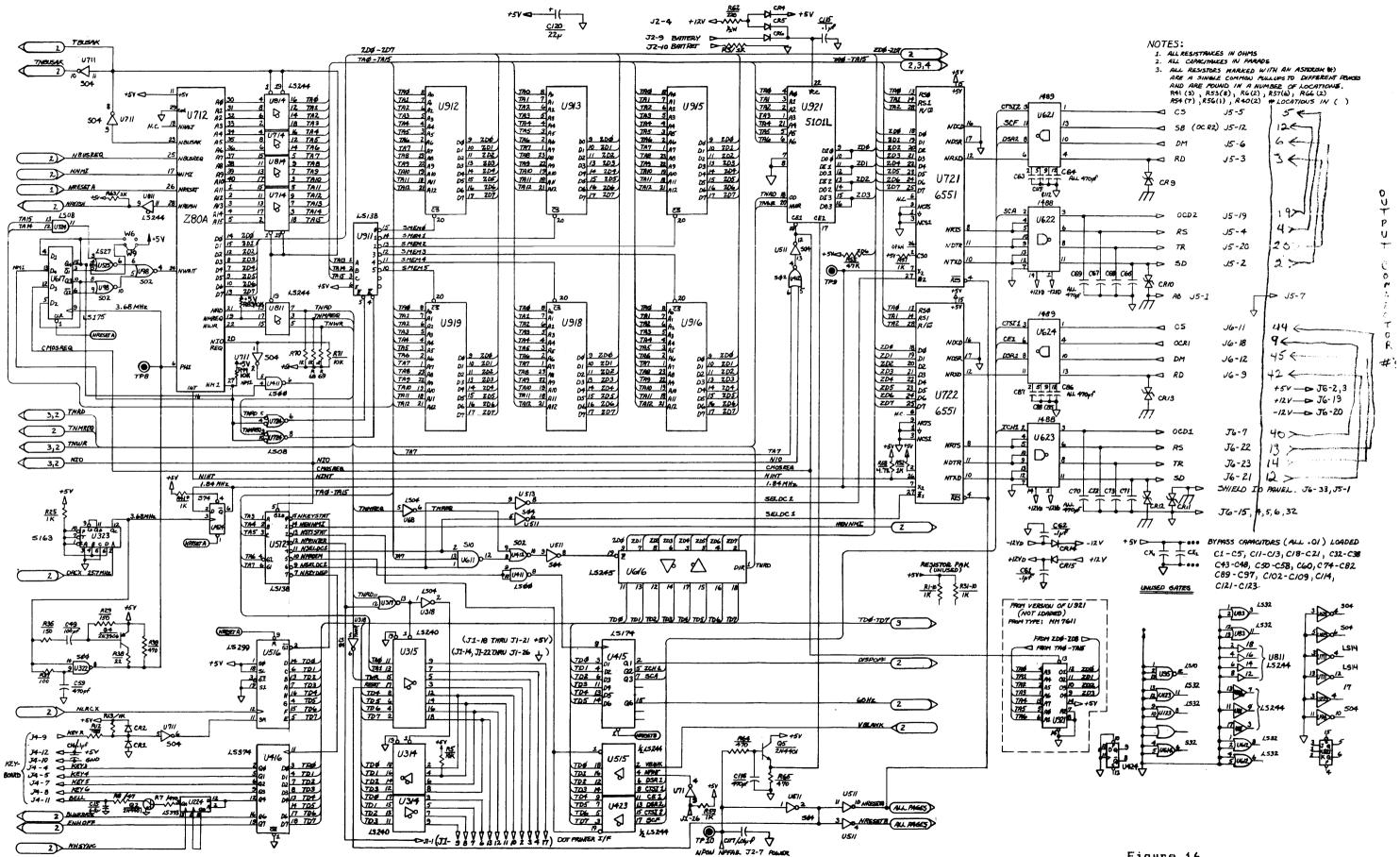

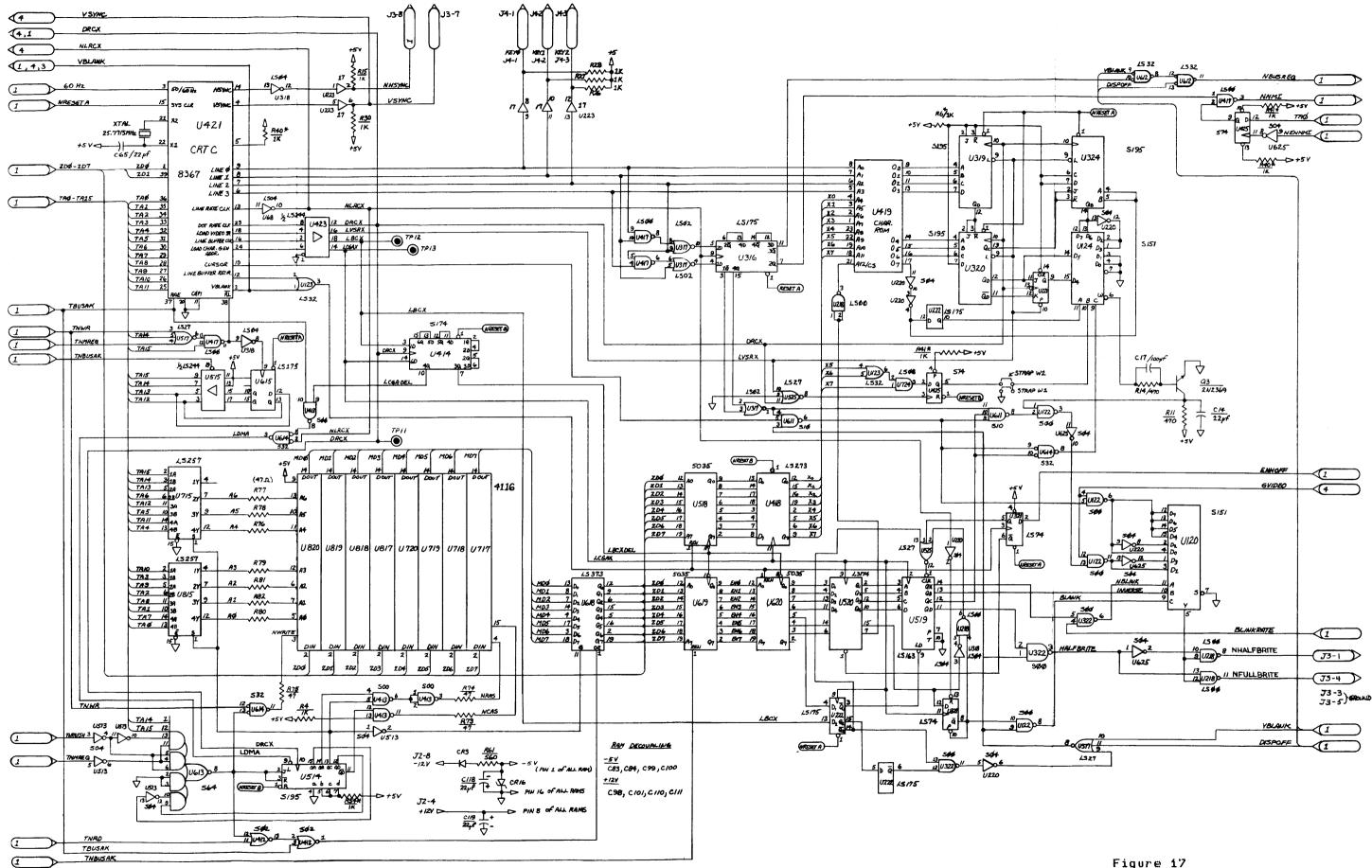

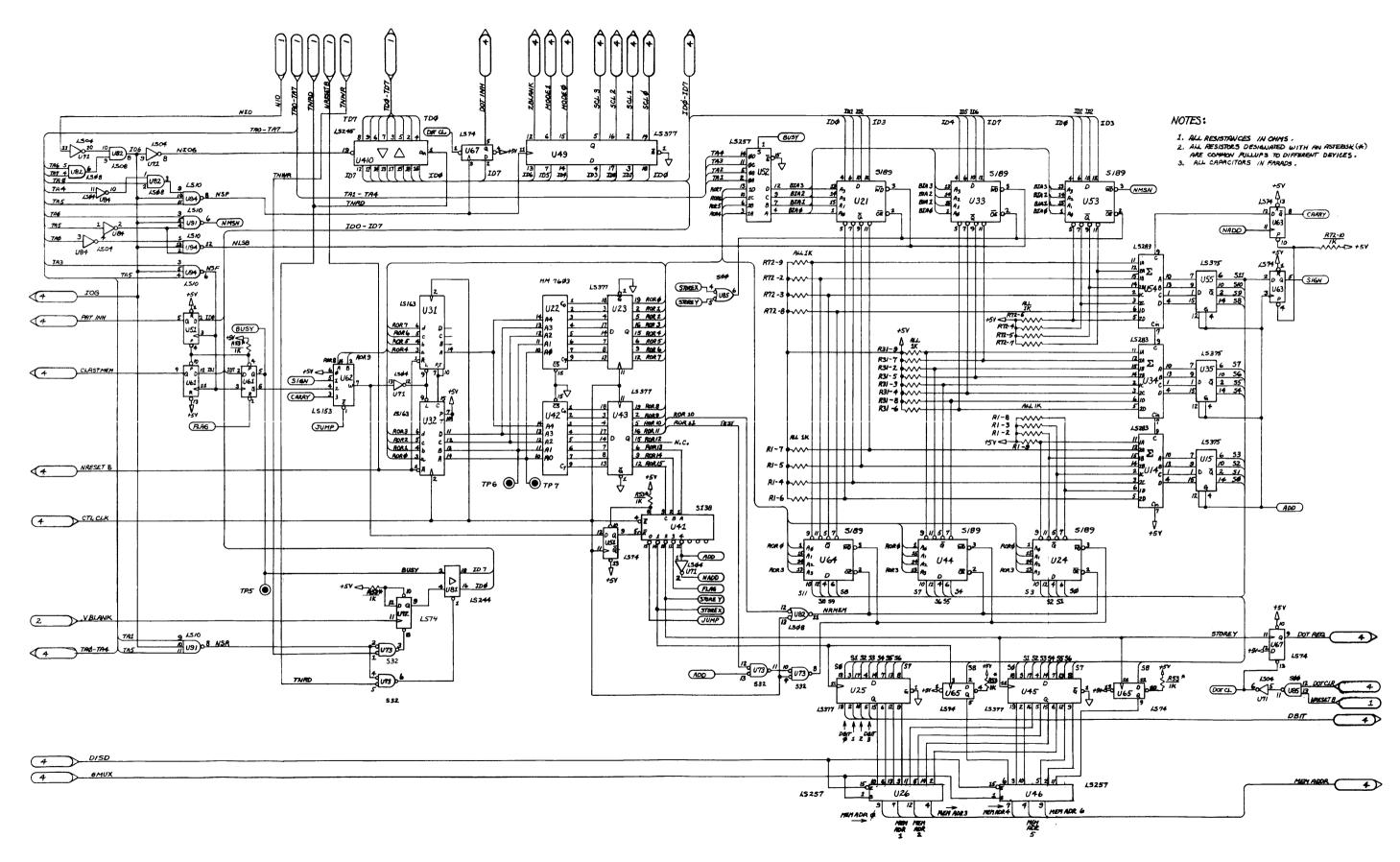

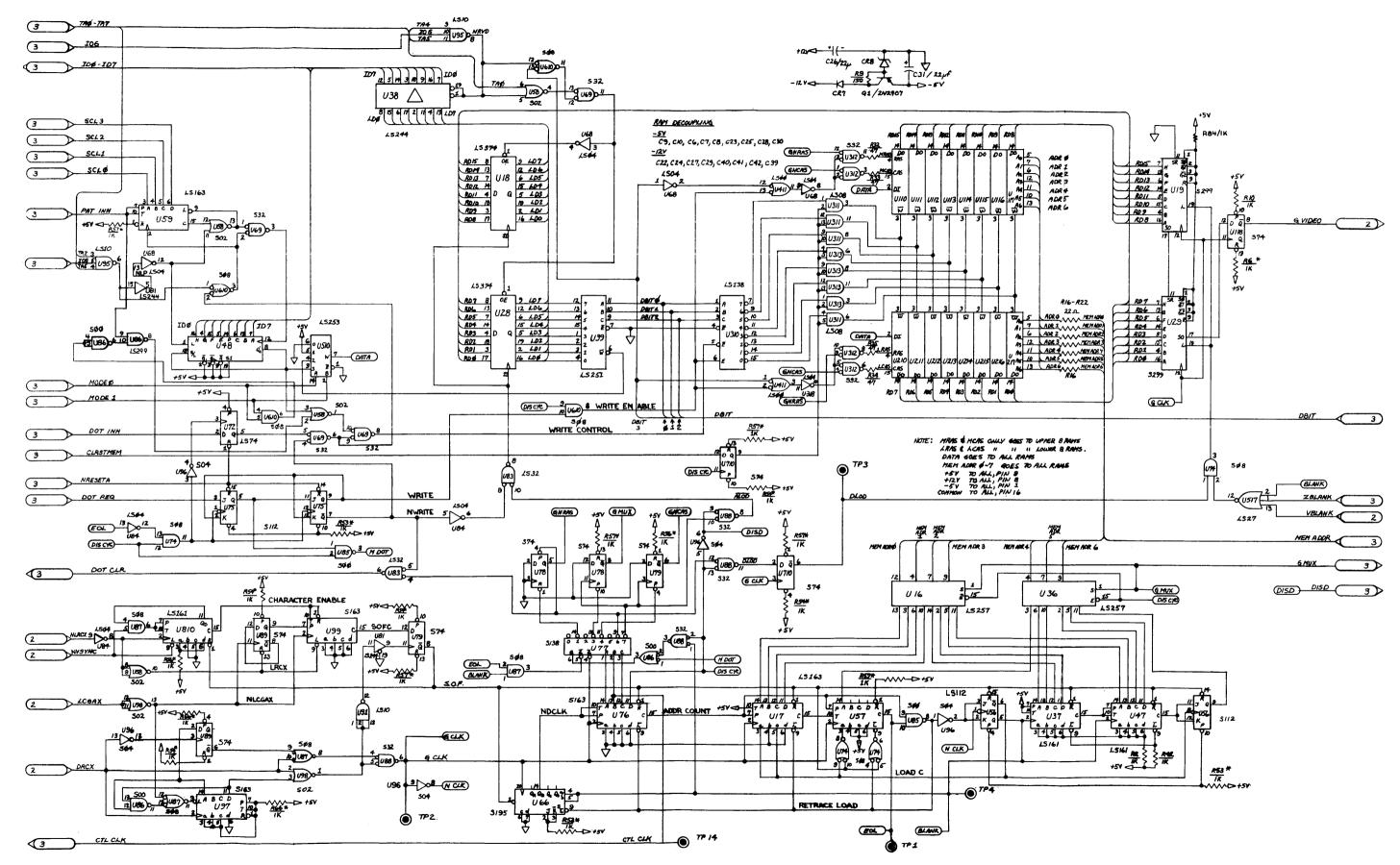

Refer to block diagrams (figs. 1-3), schematic diagrams (figs. 21,22,23,24), timing diagrams (figs. 4-14), component layout diagram (fig. 20), and parts list (fig. 25) located in the appendix. The following describes the operation of the five major sections of the Processor PCA; control and I/O, terminal character memory, character video control, graphics controller, and graphics display control and memory.

- 3.1 CONTROL AND I/O SECTION

- 3.1.1 Clock

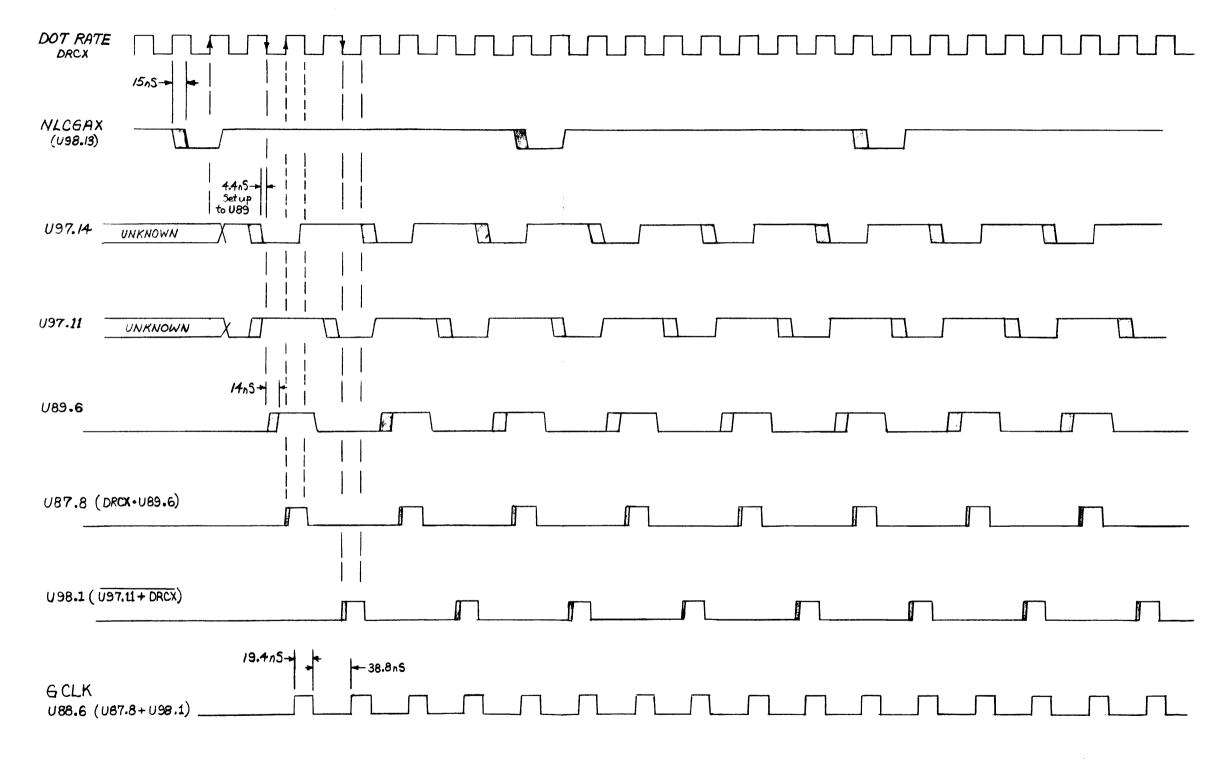

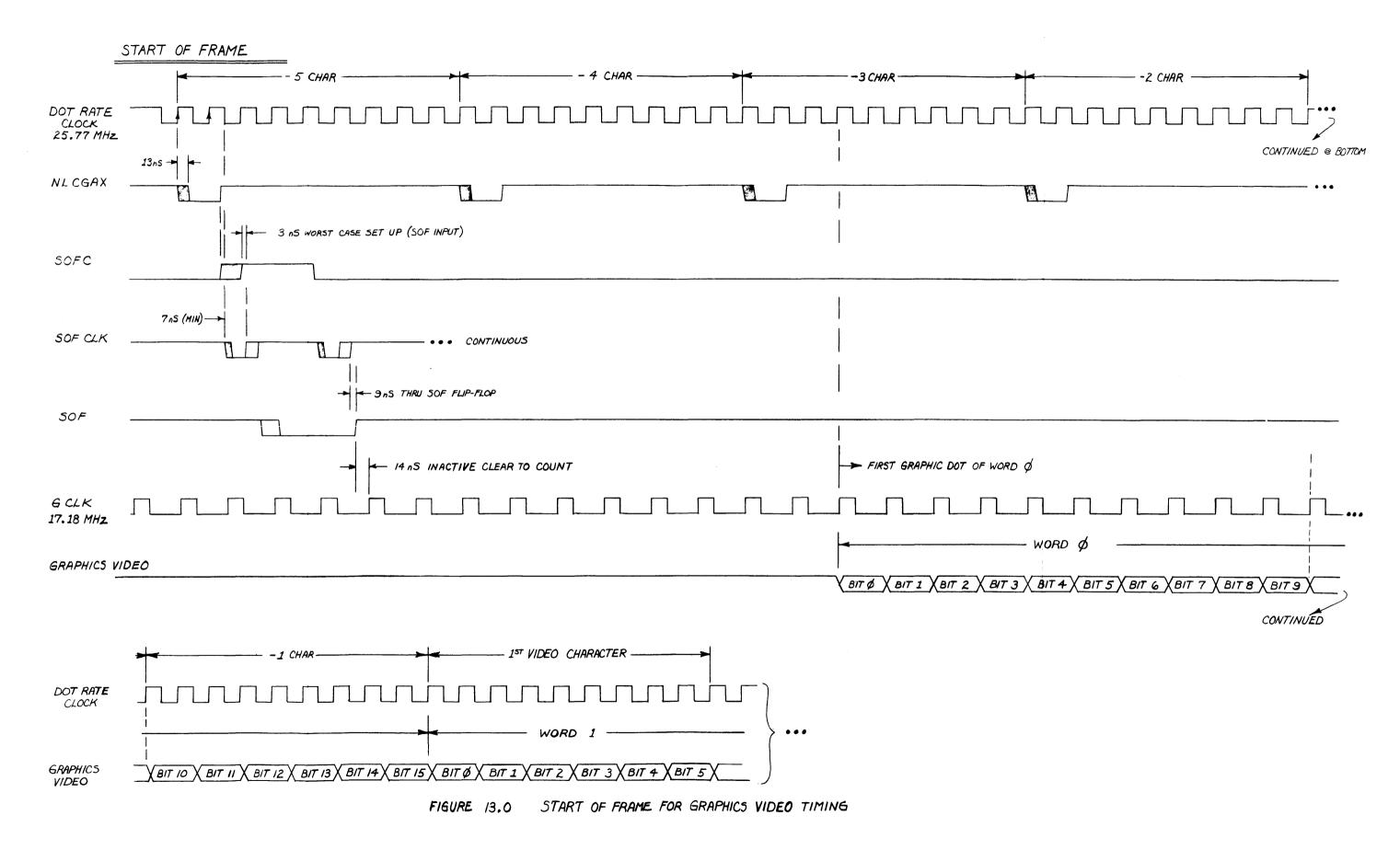

A 25.7715 MHz crystal is attached to the CRTC which oscillates at the video dot frequency. This is buffered by the CRTC and again by a 74LS244 (U423) to become DRCX, buffered dot rate clock. This clock is then divided by seven by the 74S163 (U323) to produce 3.6816 MHz, which is shaped by Q4 and its associated circuitry to produce a symmetrical clock for the Z80A, which has a zero level < 0.45V and a one level > 4.4V. This clock is also divided by two to produce a 1.8408 MHz clock which the datacomm chip (U424) uses to produce baud rates.

3.1.2 Z80A

The Z80A microprocessor performs the major control and data manipulation functions of the processor PCA. It provides addresses and control signals to read and write data from and to both memory and I/O ports. It also responds to two externally generated interrupts, NNMI and NINT, which, when enabled, interrupt current execution and cause the Z80A to branch to its interrupt service routine. The Z80A also responds to a bus request signal, NBUSREQ, allowing the CRTC control of the system buses.

At power up (or reset) the Z80A begins executing instructions from program memory beginning at address 0000H. A routine is executed which initializes variables and devices according to information contained in non-volatile memory (CMOS) and performs a self test of ROM and RAM. If an error is detected a series of beeps are issued to the keyboard which indicate the failing ROM or RAM. After inintialization the program enters a major loop responding to inputs from the keyboard and datacomm ports. Three 74LS244's (U714,U811,U814) buffer the address and control lines from the Z80A. The 1 of 8 decoder, U911, is used to seperate program memory into six blocks, each 8K bytes long. The addressed ROM is enabled during a memory read by the TNRD and TNMREQ signals or during an instruction fetch by the NM1 signal. Since the time to read the data in an instruction fetch is less than that for a memory read, the NM1 signal was used to provide an early enable of the ROM allowing it to respond within the required time. ROMs with access times of 350 ns from address or 300 ns from enable are required to run the system at full speed. EPROMs or ROMs with 450 ns access times from address may be used by installing jumper W6 and removing jumper W5, which causes the Z80A to wait one cycle longer during instruction fetches. The quad latch U617 and associated gating provides the required wait signal to the Z80A.

### 3.1.3 I/O Ports

#### CMOS

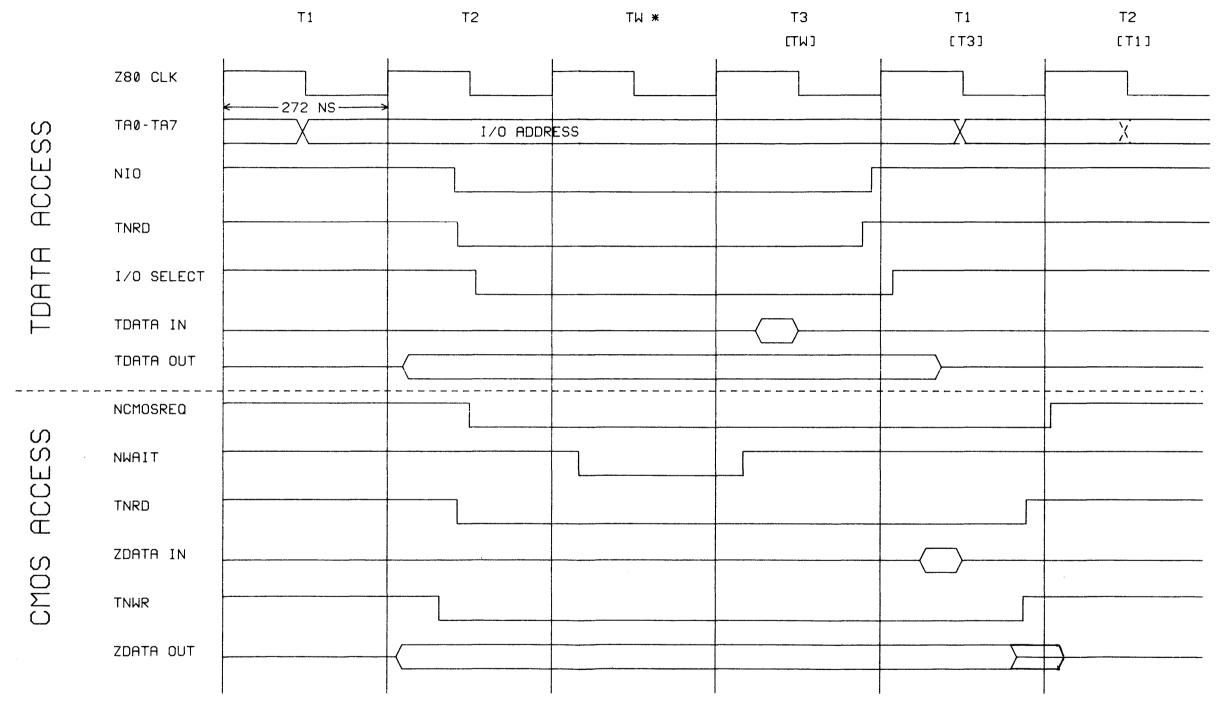

The Z80A is capable of addressing 256 different input/output ports. I/O addresses from the Z80A appear on address bits A0-A7 and the accumulator contents appear on bits A8-A15. I/O addresses 0-7FH are used to access locations in the nonvolatile CMOS RAM, U921, where configuration data is stored. Since the CMOS RAM is not fast enough to respond within the I/O cycle time a wait state is generated (by U617) each time the CMOS RAM is accessed. Diodes CR4-CR6 ensure that around 5 volts is always on the CMOS supply pin. Emmitter follower circuit, Q5, makes sure that during a power off the CMOS is always disabled before the Z80A buses become undefined and remains so until buses become defined at power on. During power off the battery maintains CMOS contents. If power on configuration is to be fixed, the COMS RAM may be replaced by an HM7611 PROM (however it must be realized that the standard read/complement/write test for the CMOS self test would show a CMOS error since the prom cannot be written).

#### DATACOMM

The SY6551 Asynchronous Communications Interface Adapter performs the parallel to serial conversion, error detection and baud rate generation functions required for serial data communication. It appears to the Z80A as four read only and four write only ports with address bit TA2 selecting the read/write function. This is done to compensate for the unique timing of the 6500 series devices. The SY6551 is selected by the rising edge of SELDC1 which is inverted from U512, the 1 of 8 decoder. The addresses of the SY6551 (U722) are A0-A7H.

The status inputs of the SY6551 produce undesirable results and therefore are forced to their active low states while the necessary status signals are routed through another port. RS-232 line driver, U623, and receiver, U624, are used to convert from TTL levels to RS-232 levels (+-12V) and vice versa. Transmitted signals are: send data (SD), terminal ready (TR), request to send (RS) and optional control driver 1 (OCD1). Received signals are: receive data (RD), data mode (DM), optional control receiver 1 (OCR1), and clear to send (CS).

The datacomm subsystem operates in an asynchronous, full-duplex, pointto-point environment. Characters may be transmitted and received simultaneously (full-duplex) with

character flow occurring over random time intervals (asynchronous). To achieve hardware synchronization each character is framed by a start bit and a stop bit (2 stop bits at 110 baud). The addition of the framing bits for transmitted characters and the detection of framing bits for the received characters are done by the SY6551. The parity (for error detection) of the character is selectable (in the datacomm configuration menu) and is also generated and detected by the SY6551 which reports errors (parity, framing, and overrun) to the Z80A by means of a status register in the SY6551 which is read when a character is received. The data transmission and reception rates are set by the Z80A in an internal register within the SY6551. Rates are selectable (in the datacomm configuration menu) from 110 to 9600 baud.

The datacomm status inputs and outputs provide the necessary control lines to connect the terminal to a host computer via a modem, or to provide direct hardware handshaking between the terminal and host. At power-on the TR and RS lines are activated to indicate that the terminal is ready. Upon receipt of a modem disconnect escape sequence (esc f) the TR line is brought inactive for about two seconds to The presence of a modem connection is detected disconnect the modem. by DM which causes the indicator "LED" (an asterisk '\*') to be displayed on the bottom center of the display. The CS signal from the host when active allows the terminal to transmit data and goes inactive to halt transmission (the terminal may ignore CS depending on datacomm configuration). The state of OCD1 is controlled by a configuration strap with its default state being low (inactive). This line selects the modem rate for dual speed modems. DCR1 is monitored in datacomm self test to detect the presence of the loopback test hood. All modem status lines are active high (+12V).

Upon receipt of a character from datacomm the SY6551 generates an interrupt signal (NINT) to the Z80A. This causes the Z80A to branch to the datacomm interrupt service routine which reads the SY6551 status, clearing the interrupt , and if no errors are present, inputs the character and places it into the datacomm buffer in RAM. Characters for which errors (parity, framing or overrun) are present cause a delete character to be placed in the buffer.

#### EXTERNAL PRINTER PORT

The SY6551 ACIA which is used for datacomm also performs the parallel to serial conversion, error detection, and baud rate generation functions required for the external printer communication. It appears to the Z80A as four read only and four write only ports with address bit TA2 selecting the read/write function. This is done to compensate for the unique timing of the 6500 series devices. The SY6551 is selected by the rising edge of SELDC2 which is inverted from U512, the i of 8 decoder. The addresses of the SY6551 (U721) are B0-B7H.

The status inputs of the SY6551 produce undesirable results and therefore are forced to their active low states while the necessary status signals are routed through another port. RS-232 line driver, U622, and receiver, U621, are used to convert from TTL levels to RS-232 levels (+-12V) and vice versa. Transmitted signals are: send data (SD), terminal ready (TR), request to send (RS) and optional control driver 2 (UCD2). Received signals are: receive data (RD), data mode (DM), optional control receiver 2 (UCR2), and clear to send (CS).

Although we use the same 6551, the terminal uses it as an output device only. The hardware is set up much like the datacomm. The difference is the external printer port must be poled for internal status while the datacomm drives an interupt line to the Z80A processor telling it status of the internal receive register has changed.

OCR2 and OCD2 are used as a secondary receive ready and a secondary request to send on the external printer port. All other transmit and receive signals are handled similar to that of the datacomm.

TBUS PORTS

The remaining I/O ports are buffered to the Z80A data bus by the bidirectional bus driver, U616. This was done because of data bus loading. The signal TNRD selects the direction of the driver which is enabled for all I/O accesses except CMOS RAM and datacomm.

US16 forms the keystatus port located at address 80H. The keystatus port returns the status of B keys at a time, which keys are determined by the keyboard/display port (U416). Four bits of the key address (column address) are supplied by U416 (located at address BBH) and three more from the CRTC scan line outputs (row address). As the row address (scan line count) from the CRTC change, keystates are clocked into the keystatus shift register (a high bit indicating key active) from which they are later read. The column address is incremented (during an NMI) for each of the first sixteen display rows thereby scanning the entire range of keyboard addresses. The keyboard/display port also enables a counter (U224) which counts horizontal sync pulses down to a bell frequency. The bell signal is then shaped by Q2 and its associated circuit. The remaining bits of the keyboard/ display port determine whether enhancements will be enabled and latches the signal which determines the blinkrate of blinking characters.

The NNMI (non-maskable interrupt) signal to the Z80A is masked externally by a D flip-flop (half of U425). Port addresses 88H to 8FH select the NENNMI signal of the port decoder, clocking the latch while address bit TAO is the data input. This means that a write to port 88H clears the latch, disabling NMI, while a write to port 89H sets the latch enabling NMI.

The system status port, US15 and U423, at address 90H allows the Z80A to read the vertical blank signal (VBLANK) for synchronizing the software with the hardware. It also provides the inputs for the datacomm status signals discussed above and also monitors the integral printer status.

The integral printer port at address 98H buffers data continuously to the printer bus, the data being latched in the printer when the NPRINTER signal is active. The processor writes data and commands to the printer via U315 and half of U314. Printer control is specified by performing a write operation to the printer with address lines TAO and TA1 and data lines TDO-TD7 selecting the particular function. Printer status is read back from the printer on the upper half of U15 which is enabled for read operations from the printer port. The presence of the printer is detected by reading status from the printer and checking data bit TD1. TD1 will be low if the printer is not connected due to the pullup resistor R1. When the printer is connected to the processor J1 pin 11 is pulled low by the printer therby indicating connection.

Each character in the printer is formed by 30 bytes of dot data, each pair of bytes being made up of the dot data needed to form the character if the character cell is scanned horizontally. The first byte in the pair indicates the state of every other dot while seven bits of the following byte indicate the state of the interstitial dots for the same horizontal scan. Thus fifteen pairs of bytes correspond to fifteen horizontal scans of the character. In this way any character font in a 15 by 15 cell may be created. The printer buffers the data and translates the horizontal dot information into vertical dots for printing. Each 30 bytes of dot data are followed by a print command to print the character. The printer is also able to print in expanded and compressed modes.

The TBUS port located at A8H latches two signals to the video section and two for the datacomm section. The NMODEM signal is inverted to provide the clock for the latch (U415).

# GRAPHICS SUBSYSTEM

The Graphics Controller occupies address port locations C0 to FF completing the full range of addressable I/O. The Z80A processes the necessary vector parameters needed for the graphics controller. The Z80A downloads to the graphics arithmetic logic unit (ALU) registers these parameters. After the vector has been described by the Z80A, it tells the graphics controller to calculate and draw the described vector into graphics memory. The graphics hardware supports set, clear, compliment and jam pattern drawing modes. See section 3.4 and 3.5 for a full technical report of the graphics subsystem.

#### 3.2 MEMORY SECTION

.

The Z80A is capable of addressing 65536 (64K) bytes of memory data. The memory map for this processor is shown in the table below.

| 0000H | I Initialization, NMI Routine, Main Scan Loop,<br>Range Tables, Support Routines, Block Mode<br>Tear Aparts, Datacomm, Test Routines. | <br> -<br> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|------------|

|       | U912                                                                                                                                  | 8K         |

| 2000H | User Soft Keys Routine, Configuration Menus,<br>Keyboard Mapper, Translator Routines,<br>Language Tables.                             |            |

|       | U913                                                                                                                                  | 16K        |

| 4000H | Graphics Routines.                                                                                                                    |            |

|       | I . U915 I                                                                                                                            | 24K        |

| 6000H | I Integral and External Printer Routines.                                                                                             |            |

|       | U916                                                                                                                                  | 32K        |

| 8000H | Video Intrinsics<br>(CRTC map)                                                                                                        |            |

|       |                                                                                                                                       | 40K        |

| A000H | Character Dot Information for the Printer.<br>(lower 4K used, upper 4K is empty)<br>(CRTC map)                                        | 5<br>      |

|       |                                                                                                                                       | 48K        |

| C000H | Dynamic RAM<br>- buffers<br>- display memory<br>- stack<br>- system variables                                                         |            |

|       | I ZD0 : ZD1 : ZD2 : ZD3 : ZD4 : ZD5 : ZD6 : ZD7  <br>IU820 :U819 :U818 :U817 :U720 :U719 :U718 :U717                                  | l<br>64K   |

TABLE 5.0 Terminal Memory Map

# 3.2.1 Read-only-memory

As can be seen from the memory map 48 K of address space has been allocated for read-only-memory (ROM). This memory contains the Z80A programs which controls the terminal operation. The ROM space is decoded into six 8K byte blocks by the 74LS138 decoder U911.

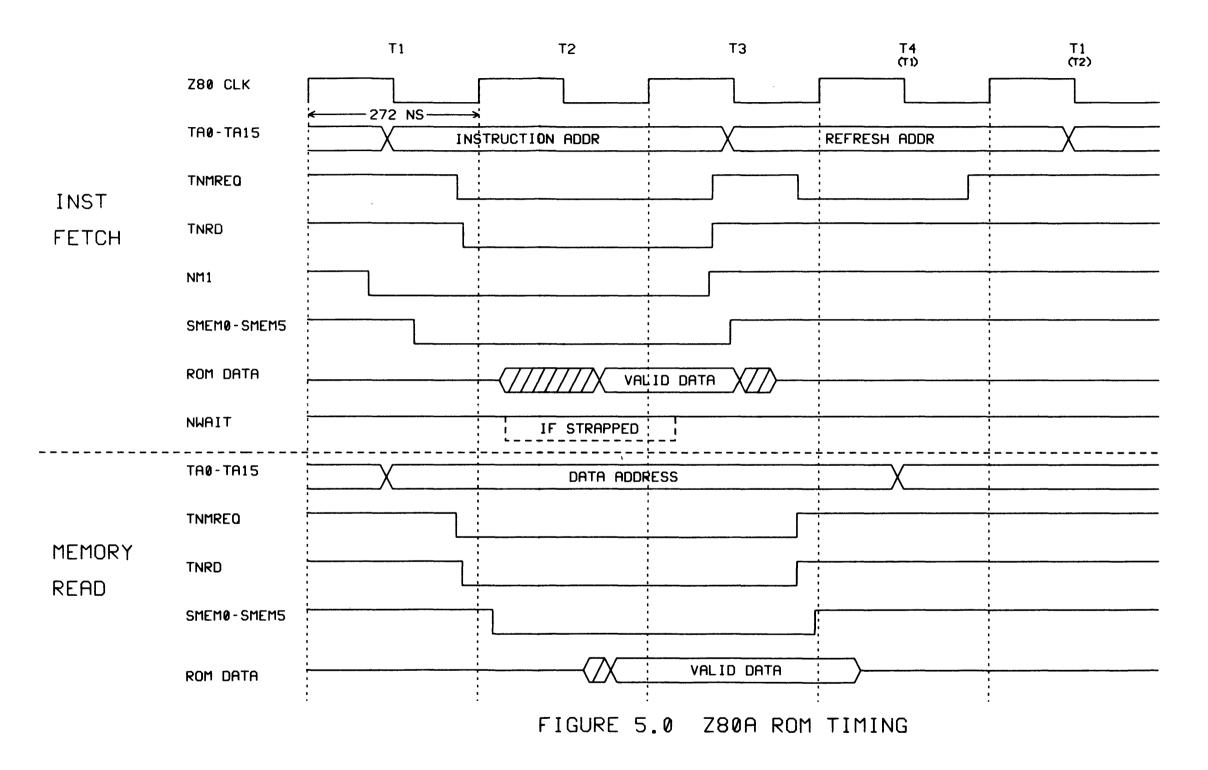

During an instruction (opcode) fetch the Z80A activates the NM1 signal to indicate that an instruction fetch cycle is in process. This signal is used to provide an early enable of the ROM being addressed during an opcode fetch therby allowing the use of ROMs with an access time on 350 ns from address or 300 ns from enable (note that an opcode fetch is one clock cycle shorter than a memory read operation) without wait states. During a memory read from ROM the

TNMREQ and TNRD signals go active enabling the addressed ROM. Data is required valid approximately 470 ns from address, therefore no wait states are required for memory reads even when using 450 ns EPROMS. Note that data is placed directly on the Z80A data bus without buffering.

# 3.2.2 Random-access-memory

The RAM subsystem has been designed around the MK4116-2 (or equivalent) 16K x 1 bit dynamic RAMs. The MK4116-2 has a minimum access time of 150 ns and minimum cycle time of 320 ns. U820-817 and U720-717 supply data bits ZD0-ZD7 respectively to provide the 16K bytes of RAM data storage.

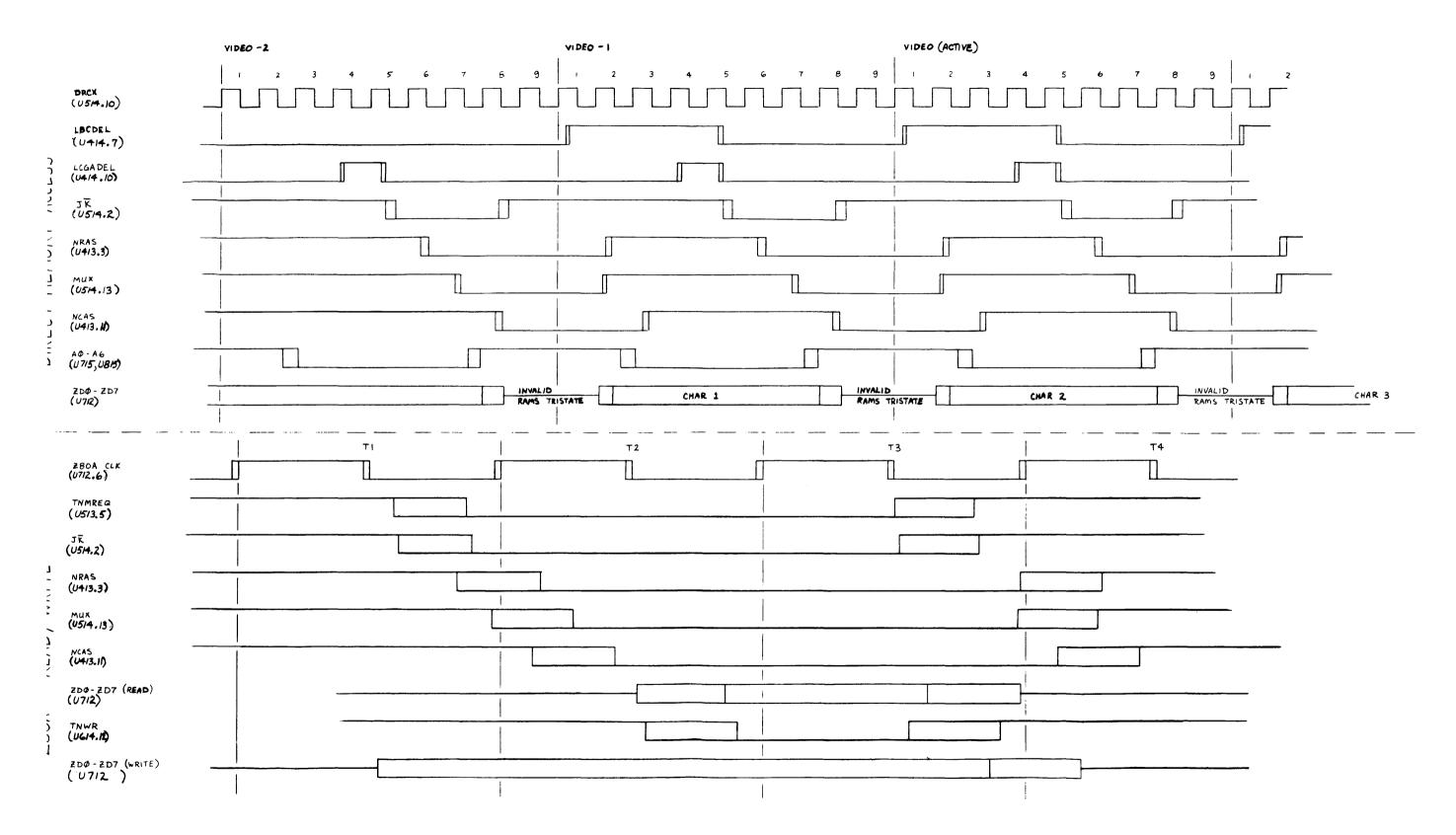

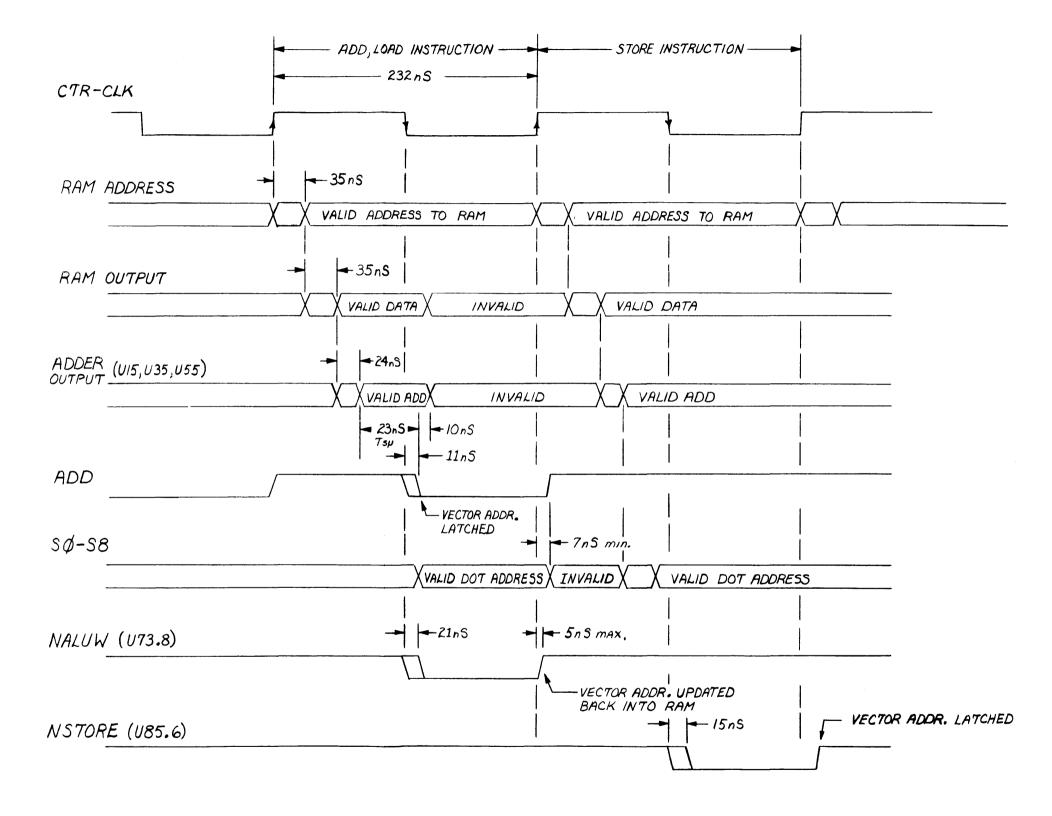

The RAMs are accessed in three ways: by the Z80A for memory read or write accesses, by the Z80A during a refresh cycle and by the CRTC during a DMA (direct-memory-access) cycle. Each of the three is discussed below. Refer to figure 6.0 for RAM timing.

#### Z80A READ/WRITE

A Z80A access to RAM is initiated by lowering the TNMREQ signal at an address location between C000H and FFFFH (RAM address range). Prior to TNMREQ going low the output of U613 would be high causing 1's to be shifted through the shift register, U514, by DRCX. As TNMREQ goes low (TNRFSH is high) the output of U613 goes low also. As the clock occurs, 0's are shifted through the shift register causing outputs QA-QD to go low in turn. This produces the RAM timing sequence as follows: NRAS-strobes in row address, MUX-changes RAM address inputs to column address, NCAS-strobes in column address and activates internal RAM circuitry to access the addressed cell. Data ouput on MD0-MD7 is vaild 100 ns from NCAS. When the Z80A is finished accessing the RAM the TNMREQ signal goes high and 1's are shifted through the shift register completing the RAM cycle.

If the Z80A is performing a read operation the TNRD line is lowered along with TNMREQ (TNWR remains high). The TNRD signal is gated with the output of U613 to enable the transparent latch, U618, during the read operation. When the NMUX signal goes high (as MUX goes low) the transparent latch becomes transparent, that is, the outputs follow the inputs, placing the RAM outputs on the Z80A data bus. The latch outputs are enabled until TNRD and TNMREQ go high again.

For a write operation, the Z80A lowers TNMREQ and places the output data on the data bus. Approximately one Z80A clock later the TNWR line goes low strobing the data into the internal data latch in the RAM. The TNRD signal will be high disabling the transparent latch so RAM outputs will never be on the Z80A data bus. The cycle proceeds as for a read operation with TNMREQ going high, shifting 1's through the shift register to complete the cycle.

#### **Z80A REFRESH**

The nature of dynamic RAMs requires that each row must be accessed every two milliseconds to guarantee the contents of that row are held. The Z80A has a built-in refresh function to provide signals which perform dynamic RAM refresh without requiring extra processor overhead. The Z80A maintains a 7 bit memory refresh counter which is incremented following each instruction fetch. While the instruction is being decoded and executed the refresh counter is output on address bits TAO-TA7 while the TNRFSH and TNMREQ signals are brought low, initiating the RAS-MUX-CAS sequence, refreshing that row. Since the TNRD and TNWR signals remain high during the refresh cycle, the memory contents are unaltered and the transparent latch is not enabled so that the accessed byte does not appear on the bus. CRTC DMA

Twice per video row, on scan lines 6 and 14 (if starting to count from 0), the NBUSREQ signal to the Z80A is activated to allow the CRTC to perform DMA of enhancement and character data (see section 3.3 for more information on the CRTC). The Z80A responds to NBUSREQ at the end of the current machine cycle by tristating its address and control lines and activating the NBUSAK line signalling that the bus is available and will remain so until NBUSREQ is raised. The NBUSAK signal is inverted and buffered by U711 to provide both TBUSAK (active high) and TNBUSAK (active low, buffered). These signals are used to tristate the address and control buffers U814, U714 and U811 and enable the video subsystem for DMA action. TBUSAK enables the CRTC to place the lower 12 bits of the DMA address on the bus and enables the output of the transparent latch, U618, as well as enable the load signal to the shift register, U514. TNBUSAK enables the upper four bits of the DMA address from US15 onto the bus and takes the recirculating line buffer, U619, out of the recirculate mode (see section 3.3 for more information on DMA addressing).

Approximately four character times before the start of the video row the line rate clock (NLRC) output of the CRTC goes high enabling the load signal to the shift register through the OR gate U614. The load signal is derived from the character rate clock, LCGAX, which is delayed three dot times through U414 in order to synchronize the RAM access to the video timing and guarantee sufficient address set up time to the RAMs. The load signal causes RAS-CAS shift register , US14, to be parallel loaded on the next rising edge of DRCX (dot rate clock). Upon loading, the shift register output QD is high and QA is low. THis condition forces the output of U613 to go low, causing 0's to be shifted through the shift register. The next three occurances of DRCX produce the NRASMUX-NCAS sequence, accessing the addressed byte. Data is available 100 ns from NCAS, and, since NMUX is high, is placed directly on the Z80A data bus (U618 is in transparent mode), and therefore on the line buffer inputs. As the shift register output QD goes low the output of U613 is forced high and i's are shifted through the shift register completing the RAM cycle. As MUX goes high again, NMUX goes low causing the data out from the RAM to be latched in the transparent latch, U618, where it is held until the next memory access. As LBCDEL (delayed line buffer clock) goes low the data is clocked into the line buffer U619. The CRTC increments the address and the next load signal occurs 9 dot times from the first, repeating the DMA cycle. In this way 80 sequential bytes of data are fetched from the RAM and loaded into the line buffer during the 80 active video character times of the display.

Note: Although the shift register load signal is enabled four character times before active video, the CRTC holds the starting address until active video and then increments it during active video. In addition, the data is not clocked into the line buffer until the line buffer clock transitions low during active video.

On the last scan line of a character row, scan line 14, the CRTC lowers the LBRE (line buffer recirculate enable) output, taking line buffers U620 and U518 out of the recirculate mode (where the output is shifted back into the input) thereby allowing data to be clocked into the inputs. During the DMA cycle of scan line 14, as characters are being output from line buffer U518 to the display, characters for the next row are fetched from memory and loaded into line buffer U518. At the same time, as enhancement data is shifted out from U620, the data which was previously stored in the temporary line buffer U619 (during the DMA cycle of scan line 6) is shifted into U620. In this way the display data for the next row of characters is loaded into the line buffers during the last scan line of the previous row as it is being displayed on the screen.

#### 3.3 VIDEO CONTROL SECTION

#### 3.3.1 Overview

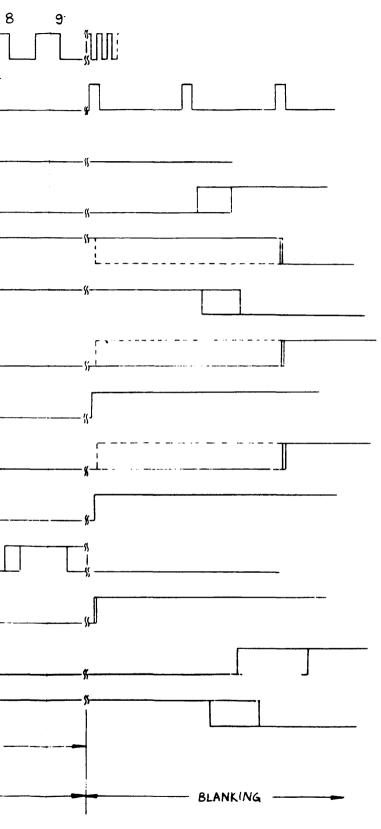

The video control section generates the timing signals required to fetch character and enhancement data from memory and drive the analog sweep circuitry to display that information on the CRT.

The display is divided into 26 rows of 80 character cells each. Each character cell is a rectangle, 15 dots vertical by nine dots horizontal. Any character to be displayed is produced by selectively lighting the dots of the character cell which shape that character, leaving the others blank. Dots are left blank on either side and on the top and bottom of the character cell to provide horizontal and vertical separation between normal characters. This is not true of characters which are continuous across the character boundary, such as line drawing characters (used to display forms).

The analog sweep circuitry sweeps the electron beam from left to right and from top to bottom across the display. As the beam is swept horizontally it is turned on to produce a lighted dot and off to blank a dot position. As the beam reaches the end of its scan a horizontal sync signal is sent to the sweep causing the beam to retrace horizontally and begin sweeping again. During this time the beam is also being swept vertically. The combination of these two produces the display raster. As the beam reaches the bottom of the display a vertical sync signal is sent to the sweep causing the beam to retrace from the bottom right to the top left corner. In this manner the CRT display is written 60 times per second (when configured at 60 Hz) or optionally 50 times per second (configured at 50 Hz).

#### HORIZONTAL TIMING

After the 80th character position of a scan line the beam is turned off (blanked) and remains so as the horizontal retrace takes place. The beam is enabled again as it reaches the position for the first character of the next scan. This blanking interval is called "horizontal blanking". This blanking allows time for the beam to retrace, settle at the left side and begin tracing again. The portion of the scan where the beam is enabled is known as "active video". The horizontal scan time consists of the 80 character times of active video plus 35 character times of horizontal blanking for a total of 115 character times per scan (1 character time = 349 ns). This produces a horizontal scan frequency of 24.9 KHz. The horizontal sync signal is activated 16 character times before the last video character of the scan and is active for 7 character times. It is produced in advance of the last character to compensate for the delay in the sweep horizontal centering circuit.

#### VERTICAL TIMING

The 26 active video rows of the display each require 15 horizontal scans for a total of 390 active video scans. After the last scan line of the last row is displayed, a vertical blank signal is activated which disables the electron beam during the vertical retrace time. The beam is enabled again on the first scan line of the first row. The duration of the vertical blank interval depends upon the occurance of the vertical sync signal which triggers the vertical retrace. This vertical sync timing depends in turn on the frequency with which the frame (one entire display) is refreshed. This frame rate may be configured to either 50 or 60 Hz corresponding to the AC line frequencies in foreign countries or the U.S. to eliminate display interference between the power supply and CRT. The following table describes the timing relationships between the vertical blank and vertical sync signals and the frame rate.

TABLE 6.0 Frame Timing

|                                                   |     | eRate<br>I 50 Hz |

|---------------------------------------------------|-----|------------------|

| Delay after v. blank to<br>v. sync (# scan lines) | 0   | <br>  38         |

| v. sync width (# scan lines)                      | 19  | 1 64             |

| v. blank duration (# scan lines)                  | 25  | 1 108            |

| Total # scan lines per frame                      | 415 | 1 498            |

# 3.3.2 Display memory addressing

Section 3.2.2 describes how the CRTC performs DMA to load the line buffers with character and enhancement data for display. Before it performs DMA, the CRTC must be loaded with a starting address (called the row-start address). Each time the CRTC is enabled it fetches 80 consecutive bytes of data starting from the row start address and places it into one of the recirculating line buffers.

The Z80A maintains a table of 24 row start addresses in memory indicating the addresses of the first byte of character data for each of the character rows being displayed. Rows 25 and 26 contain the soft key labels and are always accessed from fixed locations. This table is actually a subset of a larger table which contains row-start addresses for all 48 display rows. The address of the first enhancement byte of a row is the first character byte address offset by 80.

Two scan lines prior to the NBUSREQ signal being activated a nonmaskable interrupt (NMI) is generated which causes the Z80A to branch to the NMI service routine after completing the current instruction. Part of this service routine writes the row-start address for the next DMA into the rowstart register of the CRTC. The row-start address is written into the CRTC via the address bus itself. At the same time, bits TA13 and TA12 are written into the 74LS175 U615, which provides the upper bits of the RAM address for DMA. The Z80A reads the row start address from the table, adds the 80 byte offset for enhancement data DMA, masks bits TA15 and TA14 to a 1 and 0 respectively and then writes a 02H to this address. By masking bits TA15 and TA14 the address corresponds to a ROM location, which of course can't be written. These bits are decoded by part of US17 and U417, along with TNMREQ and TNWR to generate the register load signal (U421 pin 38) which latches the address into the CRTC and U75 for use during the next DMA cycle. The data bits ZDO and ZDi select the register to be written to, in this case, the row-start register. The NMI service routine keeps count of the next row to be displayed in order to determine which row start address to send to the CRTC next. Since NMI can be disabled for an indefinate period (for example during a RAM test) it is resynchronized every frame by reading the VBLANK signal through the system status port.

# 3.3.3 Character display

At any given time the characters for the current row being displayed are held in the recirculating line buffer US18. The character codes output from this line buffer are resynchronized to the character clock through the octal latch, U418, from which they are sent to the character ROM, U419. This ROM contains the dot pattern for each scan line of each each possible character code. The standard character set uses the ASCII character code to represent the 128 possible characters in the set. The first 32 characters of the set are the control characters (escape, line feed, carriage return, etc.) while those remaining are the alphanumeric and punctuation characters. These 128 characters are represented in bits X0-X6 with X7 being a 0. These bits along with the scan line count become addresses for the dot data from the character ROM. Therefore, 11 address bits are required, meaning that a 2K byte ROM may be used to contain the dot data for the standard character set. Bit X7 will then serve as an active low chip select.

By using a 4K byte character ROM, two complete character sets may be displayed. In this case bit X7 selects between the two character sets. Likewise an 8K byte ROM can store four complete, 128 character, character sets. The schematic shows a signal from the enhancement data latch, US20 pin 15, which is inverted by U218, and sent to U419 pin 21. This signal is used to address the 8K byte character ROM on 4K boundaries. This combined with bit X7 from the character data latch allows selection of any of the four character sets. This uppermost address bit becomes a chip select for 2K or 4K character ROMs. As the character code and scan line count is issued to the character ROM an access time delay is encountered before the dot data is available at the outputs. The character ROM has an access time of 300 ns, therefore one full character time (349 ns) delay is introduced.

As the dot data becomes available out of the character ROM the LVSRX (load video shift register, buffered) signal is brought low which, on the rising edge of DRCX, parallel loads the data from the character ROM into the character shift registers U319 and U320 (and U324 as explained later). Since only seven dots per scan line are required for standard characters, seven dots are loaded from the character ROM (low output means dot is lit) into the shift registers. The MSB (most significant bit) output from the character ROM is latched by U222 (on LCGAX clock) and is used to enable the half-shift function (described below). The MSB output of U319 is connected to the serial input of U320 essentially forming an 8 bit shift register. At the same time that the seven dots are loaded into the shift register a 1 is loaded into the MSB.

The QD output of U320 goes to the character multiplexor, U124. This multiplexor selects one of several inputs to gate to the dot stream. For a normal scan (not half-shift) the multiplexor select inputs will be 101 (C input is most significant) selecting the D5 input. As the dots are loaded into the shift register the first dot (which is high) appears on the D5 input of the multiplexor and is gated to the dot stream. On each of the next 8 dot rate clocks (DRCX) dot data is shifted one bit position in the shift register and therefore to the D5 multiplexor input and to the dot stream. Since the serial input of U319 is tied high, a 1 (blank dot) is shifted into the shift register as the dot data is shifted out. Therefore at the end of the 9 dot clocks comprising the horizontal scan for a standard character, the first and last dots are blanked (1's) with the 7 dots from the character ROM in between.

HALF-SHIFT

To avoid the "stairstep" appearance of characters with long diagonals, a feature known as "half-shift" is implemented which allows and scan line of a character to be delayed by half a dot time. This halfshifted scan line, placed between two normal scan lines, fills in the diagonal as shown below.

| х | normal       | Х |

|---|--------------|---|

| Х | half-shifted | X |

| Х | normal       | X |

| Х | half-shifted | Х |

| Х | normal       | Х |

| x | half-shifted | X |

(no half-shift)

#### (with half-shift)

In the standard character set the MSB output of the character ROM indicates that a scan line is to be halfshifted. This output is latched (by LCGAX) into U18 where it is held for the 9 dots of the character time. The output of U222 is fed to the character multiplexor select input A which, for half-shifted scan lines, selects the D4 input (U124 pin 15). The QD output of the dot shift register, U320, is sent to the JK flip-flop, U221, clocked on the falling edge of DRCX, which performs the half-shift of the dot data. The output of this flip-flop goes to the D4 input of the character multiplexor. The half-shift flip-flop is preset by LVSRX at the time new dots are loaded into the shift registers.

COPY BIT

Some alternate character sets such as line drawing set or large character set require all nine dots an a scan line to be active. This allows for continuous dots across a character boundary as required for drawing forms, etc. on the display. In order to get nine dots out of eight outputs from the character ROM, a copy bit circuit is activated which copies the MSB output into the first two dots while the remaining seven ROM outputs form the remaining seven dots.

The seven least significant ouputs from the character ROM are loaded into shift registers U319 and U320 as for standard characters. The most significant output is loaded into both the A and B inputs of shift register U324 at the same time as the least significant seven bits. Thus, the MSB is "copied" in shift register U324. The remaining dots are brought from the QC output of U320 into the serial inputs of U324 thereby forming a nine bit shift register with U319, U319, and U320. The QB output from U324 is then fed to the D7 and D6 inputs of the character multiplexor which are selected when the select inputs are 11X. Note that the select A input is a don't care since half-shift cannot be used in these character sets. The copy bit circuit is activated whenever the X7 output of of the character latch U418 is active. Remember that this bit is activated to select the second character set in a 4K character ROM or the second and fourth sets in an 8K character ROM. The first 32 character of any of the four posible character sets are reserved for control characters and therefore copy bit is deactivated when these positions are accessed. This condition is decoded by bits X5 or X6 being gated with X7 (U123 and U724) to enable copy bit only for the upper 96 characters of the set. The result of this decoding is latched in the D flip-flop, U425, which allows for the access time of the character ROM. The flip-flop is clocked by the combination of LVSRX and DRCX which are gated together by U525. The output of the copy bit enable latch is then used to select the copy bit shift register output and gate it to the dot stream.

#### CURSOR

The generation of the cursor for the display is performed by a combination of hardware and software. The CRTC activates its cursor output when the address of the character being fetched during a DMA cycle matches the contents of its internal cursor address register. This output is active for all scan lines. The software maintains and updates this register in the CRTC corresponding to the position of the cursor on the display. In order to make the cursor blink the software alternately writes a valid cursor address and then an invlaid one.

The cursor signal, CUR, output from the CRTC is gated with another signal, ULTIME, to produce a cursor signal, NCUR, which is active on the 13th scan line. ULTIME is decoded from the scan line count by U316 and U317. This signal also enables the underline enhancement during the 13th scan line.

In the normal situation, where the cursor does not lie in an underline field, the NCUR signal is propogated thru U614 to become NCURSOR which is fed to the select C input of the character multiplexor. This input goes low to activate the cursor which for normal characters (not copy bit) selects the D0 or D1 inputs which are tied low. This causes the dot stream to be active for the 13 scan line of the character position in which the cursor lies. In effect this OR's the cursor with the character in the cell (a non-destructive cursor). If the copy bit circuit is active however, the D2 of D3 inputs of the character multiplexor are selected. These inputs provide the inverted series of dots from the copy bit shift register. In essence this inverts the 13th scan line of the character when the cursor is active. This is necessary rather than the OR'd cursor used above due to the fact that some of the characters may have all dots of the 13th scan line lit and the cursor would never be seen.

#### DOT STRETCH

The dots are inverted by U124, the character multiplexor, to provide an active high dot stream output. This dot stream is then passed through Q3 and its associated circuitry which performs a "dot stretch" function. This dot stretch is used to provide an elongated active dot which has a more pleasant appearance when displayed. It essentially "fattens up" the dots composing a character. The switching time of the transistor from saturation to cutoff is dependent upon the parasitic collector to base capacitance and the external capacitor C14. This capacitance limits the switching speed, essentially stretching the amount of time the transistor is active (in saturation). Capacitor C17 is included to compensate for parasitic base to emitter capacitance. Note that an inversion is introduced by this dot stretch circuit.

After being stretched, the dot stream is gated through U122 where it picks up the underline enhancement and then is sent to the enhancement multiplexor where graphics video and the remaining enhancements are added before sending the information to the analog sweep circuitry.

### 3.3.4 Enhancement Display

A one-to-one correspondence exists between each byte of character data and each byte of enhancement data held in recirculating line buffers US18 and U620 respectively. As a byte of character data is sent to the character ROM its corresponding enhancement byte is sent to the enhancement section where it is decoded and recombined with the dot stream in the enhancement multiplexor, U120.

Of the eight available bits in the enhancement byte, only seven are used. Four of these, ENO-EN3, select the blink, inverse, underline and halfbright attributes which may be selected in any combination. Bit EN4 is the set enhancement bit which, when high, causes the current enhancement to be latched and held until another enhancement is set or until the end of the current row. Bit EN5 is the end-of-line bit which causes the display to be from the current character to the end of the row. In this way, to clear the display, end-of-line is set in the first character postion of each row. Bit EN6 as described above forms the most significant address bit for an 8K byte character ROM.

As a character is latched into U418, six of the seven enhancement bits are latched into the hex latch, U520. The set enhancement bit is latched at the same time (by LCGAX) into U222. At this time EN6 is fed to the character ROM to provide the character ROM address selection for its corresponding character. The attribute bits, EN0-EN3, output from U520 are then sent to the 74LS163, U519. In this mode, with the count enable inputs P and T grounded, it acts as a latch with a synchronous load and clear. This latch provides the additional character time delay to compensate for the character ROM access time. If the set enhancement bit, EN4, is set, the output, U222 pin 3, will go low as the bit is latched. This activates the load input of U519 causing the attributes to be loaded on the next character clock (when the character ROM outputs are loaded into the shift register).

#### **VIDEO ATTRIBUTES**

The blink attribute output (US19 pin 14) is gated with the blinkrate signal from the I/O section, which alternates high and low to produce the active low NBLINK signal. When active the NBLINK signal allows only the cursor to be displayed, blanking the character. In this way, the blinking characters are alternately displayed and blanked. The inverse bit simply selects the inverted dot stream (ALPHA) or cursor signals.

The underline signal, ULINE, under normal conditions (when cursor is not active) simply causes the dot stream to be turned on during scan line 13. This is accomplished by gating the ULINE signal with ULTIME and using the results to force U122 pin 3 high, thereby activating the dot stream. A problem exists, however, when we want to position the cursor at a character position where underline is active. We can no longer merely "OR" in the cursor into the dot stream because it lies on the same scan line as the underline and therefore would never be seen. What is done instead is that when both are active (NCUR is low and ULINE is high), neither the cursor nor underline appear on the display. This essentially disables the underline at the cursor position on the display producing a blinking hole in the underline. The NCUR signal is sent into U611 pin 9 which, when active, prevents the underline signal from being gated into the dot stream. At the same time the ULINE signal is sent into U614 pin 9 disabling the NCURSOR signal which normally generates the cursor. Thus, both are disabled.

The last attribute, halfbright, selects which of the video inputs on the analog sweep board will receive the dot information. When the halfbright attribute is activated the dot information is inhibited from the NFULLBRT output (which gives full intensity characters), U218 pin 11, by pulling U218 pin 13 low, and is enabled through U218 pin 8 which sends the active low dot information on NHALFBRT to the sweep.

#### END-OF-LINE

The remaining enhancement bit, ENS, performs the end-of-line function. When set, this bit causes the display to be blanked from the current character position to the end of the row. This eliminates the need to clear both character and enhancement data in order to clear the display. After being latched in US20 the end-of-line signal is gated through U218 and US25 to lower the clear input of US19 (pin i). This causes the enhancements to be cleared at the next character clock (when character ROM outputs are loaded into the shift registers). At the same time that US19 is cleared, the endof-line signal is latched into U321. The Q' output (U321 pin 8) is sent back to the preset input to hold the flip-flop in the cleared state for the rest of the scan line. At the end of the scan line the NLRCX (inverted line rate clock) clears the flip-flop (clear overrides preset). At the same time the Q' output, NEOLDEL, is gated through U122 to activate the BLANK signal. This signal blanks the display by deselecting the alpha input, only allowing the cursor signal to be gated to the sweep. The cursor signal is allowed since it is necessary to be able to position the cursor even in a blanked field. The Q NOT output, U321 pin 8, is gated to the clear input of U519 in order to hold the enhancement latch in the cleared state.

The horizontal blank signal causes the dot stream to be disabled (blanked) after the 80th character of a row and holds it in the blanked state until the first character of the next row. This signal is obtained by latching the LBCX (line buffer clock) signal in U222 pin 13 and adding a one character delay in U222 pin 5. The LBCX signal is active high at the rising edge of LCGAX during the 80 active video characters. HBLANK is then gated through U517 to activate BLANK and disable NCUR. VBLANK and DISPOFF also blank the display in a similar fashion.

The last part of the video section to consider is the enhancement off circuit which allows the enhancement latches to be disabled. The Z80A sets the ENHOFF signal, output from U416, which is latched by the RECIRC signal into U321. The Q output (U321 pin 5) is gated through US25 to clear U519 while the Q' output (U321 pin 6) clears U520. The RECIRC signal goes low to take the line buffers out of the recirculate mode as they are loaded during scan line 14. This means that the ENHOFF bit is always latched at the start of a new row. The software can then change ENHOFF during an NMI service routine to disable enhancement display on the next row.

### 3.4 GRAPHICS SUBSYSTEM

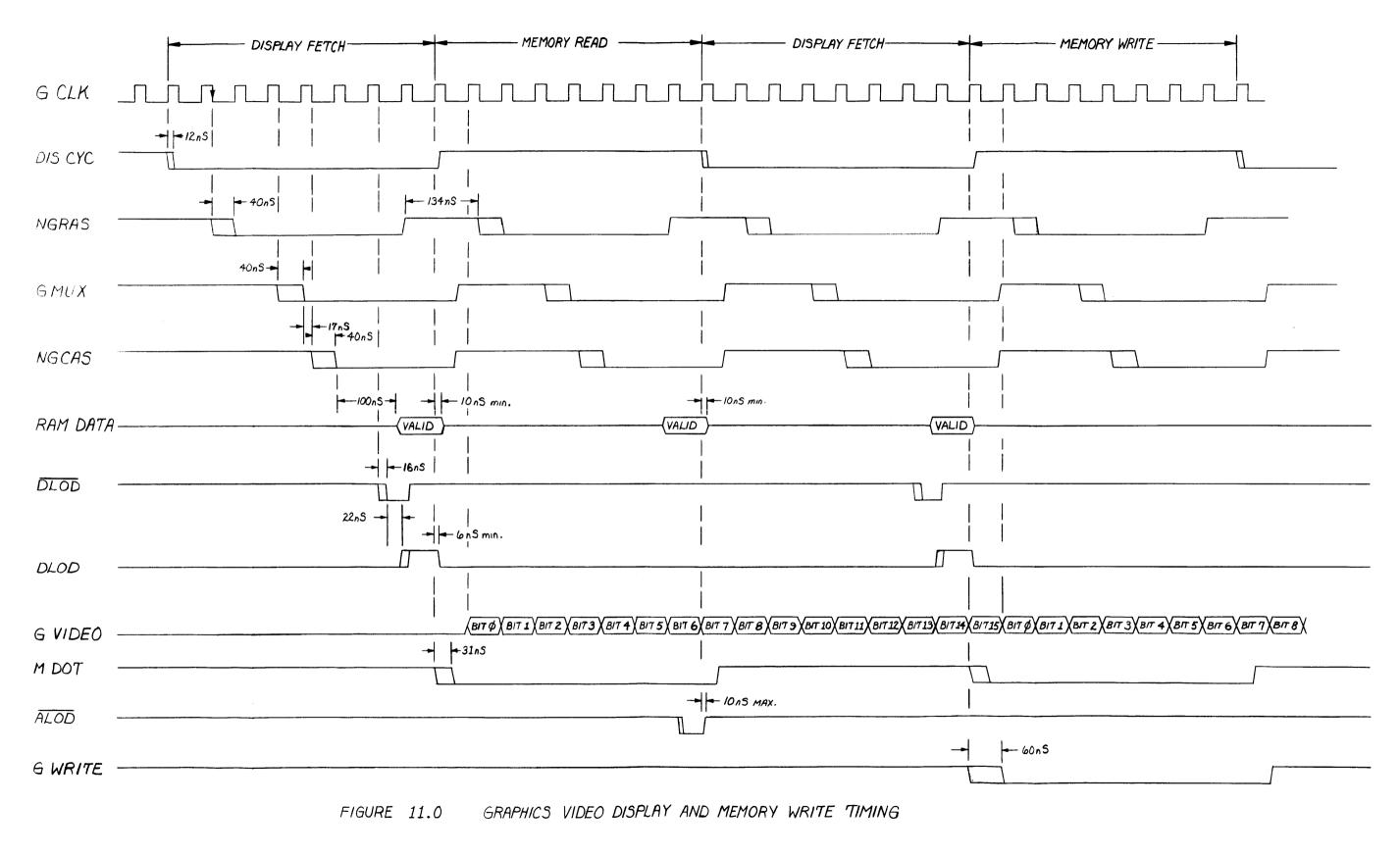

Graphics Subsystem is a complete entity apart from The the alphanumerics portion of the terminal. The Z80A sees the the graphics hardware as a read and write I/O port. The hardware consists of a graphics controller, ALU, write and read display circuitry, and 16K Words (16K X 16) diśplay of memory. Graphics vidéo is multiplexed with the character video just before the sweep circuitry sees it. To draw a vector, the Z80A download vector parameters describing the point to point location in which the vector is to be drawn. From there the graphics controller takes over and calculates the addresses of each dot position which makes up the line path of the vector. Each dot is stored into the graphics memory one dot at a time. After a vector has been drawn the graphics controller set a status flag at a port location telling the Z80A the controller is done drawing. At this point the Z80A can go ahead and download vector paramemeters of another line to be drawn.

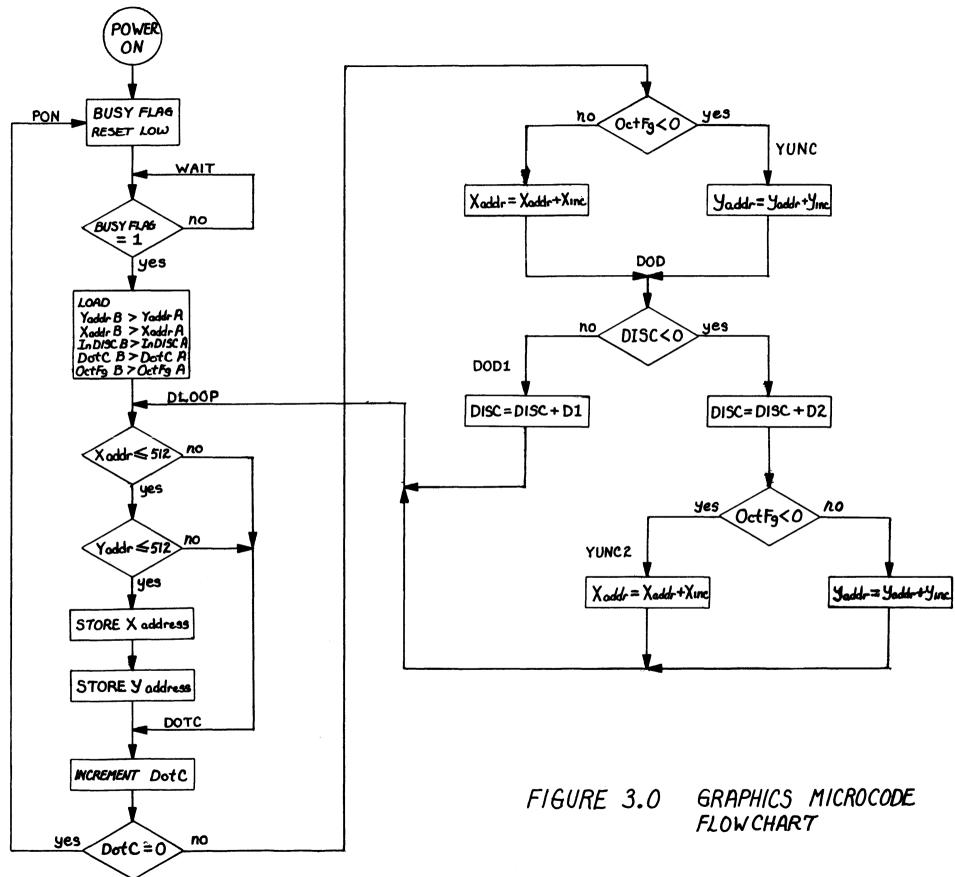

#### 3.4.1 Vector Algorithym

If we use Cartisian coordinates in the positive right half plane, we can define an algorithym that will give us a incremented line path:

Delta X = X old - X new Delta Y = Y old - Y new

The unconditional direction is the direction in which the position is aways incremented. If Delta X was greater than Delta Y it would make sense to increment the X direction for every iteration and let the Y be incremented if it is needed. This makes the Y direction conditional because it is dependent on the X position for it's incrementation.

The following algorithym assumes:

Delta X is greater than or equal to Delta Y is greater than or equal to  $\boldsymbol{0}_{\perp}$

This says that the X direction is always the unconditional direction and the Y direction is the conditional.

The conditional direction is the direction that is dependent on an error term "e" which checks if the conditional direction has exceeded the unconditional directions unit length. If it has, it is then incremented and the error checking is repeated until the path of the vector length is completed.

The error term is described as follows: e = (Delta Y / Delta X) - 0.5

By following the preceeding algorithym we can determine when to increment the unconditional and conditional directions.

START> is e > O (checks to see if the conditional direction should be incremented) if not true -> go to COND Y = Y + i(increment the conditional direction) e = e - i (reinitialize the error term) X = X + 1(increment the unconditional direction) go to START CONDY X = X + i(increment the unconditional direction) e = e + (Delta Y / Delta X) (add slope differential to error term as an increment for unconditional unit length detection) go to START

end

This algorithym has two problems, it has a divide in it's operation which can be slow or hard for our microprocessor to do and it only describes a line from 0 to 45 degrees.

To get rid of the divive function, we multipling the error term by a constant, 2 Delta X. We can do the same algorithym but now with adds, subtracts and multiply by 2's which is easy for a microprocessor to do by shifting one bit space.

To be able to draw in all the quadrants we must define three more variables. By being able to specify the X and Y increment as positive and or negative, we can draw a vector in any four quadrants from 0 to 45 degrees with respect to the specified quadrant. The third variable needed is a check to see which direction is unconditional . This determines which octant in a given quadrant to draw in.

Octant flag = abs/Delta Xi - abs/Delta Yi

If the sign of the results is negative, we know the Y direction is greater so it is the unconditional direction.

The vector length or the number of dots to be drawn is determined by the unconditional direction's value. Since it is this direction that is incremented every iteration, the integer value of the Delta will be it's length.

The resulting algorithym is the one that is used. Please refer to the flow chart figure 3.0.

Note: The error terms are now called discriminants.

- START> is DCTANT FLAG < 0 yes, then increment Y with Yinc no , then increment X with Xinc

- is DISCRIMINANT ( 0 yes, then increment DISCRIMINANT WITH D1 GO TO START

- no , then increment DISCRIMINANT with D2 and increment the conditional direction with it's increment GO TO START

D1 and D2 are incremental discriminants used for slope detection and error term reinitialization, respectively. Initial Discriminant = -1 Delta X I + 2 | Delta Y | D1 = 2 | Delta Y | D2 = 2 | Delta Y | - 2 | Delta X |

# 3.4.2 Graphics I/O allocations

| I I/O PORT      | I DESCRIPTION I                                                 |

|-----------------|-----------------------------------------------------------------|

| I ADDRESS (HEX) |                                                                 |

| 1               |                                                                 |

|                 | Write to static ram- Y starting address <br>  (LSB)             |

|                 |                                                                 |

| 1 C1            | <pre>I Write to static ram- Y starting address  I (MSN) I</pre> |

|                 |                                                                 |

| I CS            | Write to static ram- X starting address <br>  (LSB)             |

|                 |                                                                 |

| I C3            | Write to static ram- X starting address <br>  (MSN)             |

|                 |                                                                 |

|                 | Write to static ram- Dot count (LSB)                            |

| •               |                                                                 |

|                 | Write to static ram- Dot count (MSN)                            |

| 1               |                                                                 |

| I C6            | Write to static ram- Initial Descrimi-  <br>  nant (LSB)        |

|                 |                                                                 |

| I C7            | Write to static ram- Initial Descrimi-  <br>  nant (MSN)        |

|                 |                                                                 |

| I C8            | Write to static ram- Increment Di (LSB)                         |

|                 |                                                                 |

| C9              | Write to static ram- Increment Di (MSN)                         |

| •               |                                                                 |

| I CA            | Write to static ram- Increment D2 (LSB)                         |

| •               |                                                                 |

| I CB            | Write to static ram- Increment D2 (MSN)                         |

|                 |                                                                 |

| I CC            | Write to static ram- Yinc (LSB)                                 |

|                 |                                                                 |

| I CD            | Write to static ram- Yinc (MSN)                                 |

| •               |                                                                 |

| continued       |                                                                 |

| I/O PORT      | I DESCRIPTION                                               |

|---------------|-------------------------------------------------------------|

| ADDRESS (HEX) | 1                                                           |