лалалалалалалалалалалалал הההההההההההההההההההההה

## **Advanced Micro Devices**

### **Am9500 Family Interface Manual**

Copyright © 1980 by Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O. Box 453, Sunnyvale, California 94086 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

> > Printed in U.S.A. 11-80 RMC-10

·

. . .

### TABLE OF CONTENTS

يل.

| INTF | RODUCTION                               |

|------|-----------------------------------------|

|      | HIP SELECT – DEVICE ENABLING            |

| V    | /ait State Generation         1-3       |

| 2. 1 | ITERFACE CIRCUITS                       |

| A    | m9511A 2-1                              |

| A    | m9512 2-5                               |

| Α    | m9513                                   |

| A    | m9517A                                  |

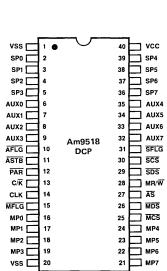

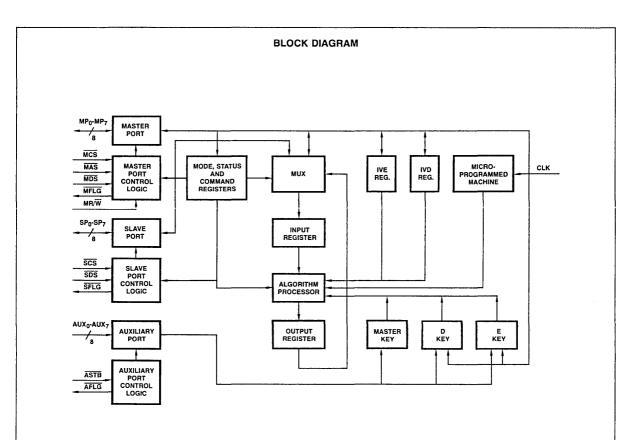

| A    | m9518                                   |

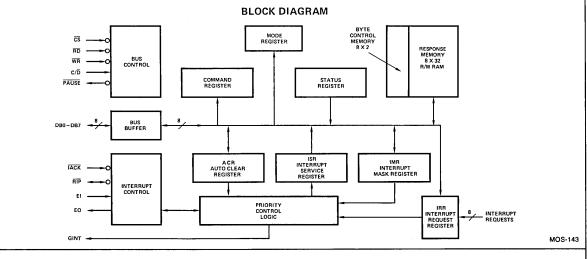

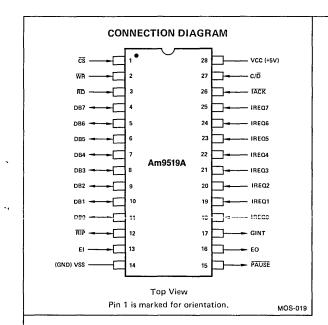

| A    | m9519A                                  |

| 3. S | UMMARY                                  |

| P    | rocessor/Peripheral Selection Chart 3-1 |

| 4. A | m9500 FAMILY DATA SHEETS                |

| A    | m9511A 4-1                              |

| Α    | m9512                                   |

|      | m9513                                   |

| A    | m9517A                                  |

| A    | m9518                                   |

| A    | m9519A                                  |

| 5. N | ICROPROCESSORS                          |

| A    | mZ8002 5-1                              |

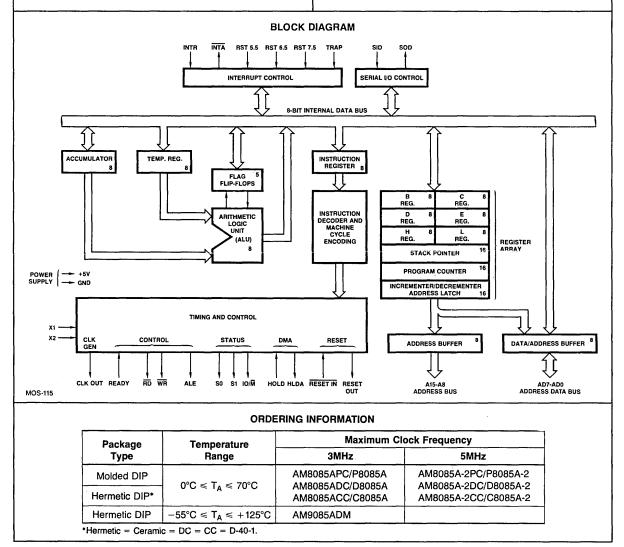

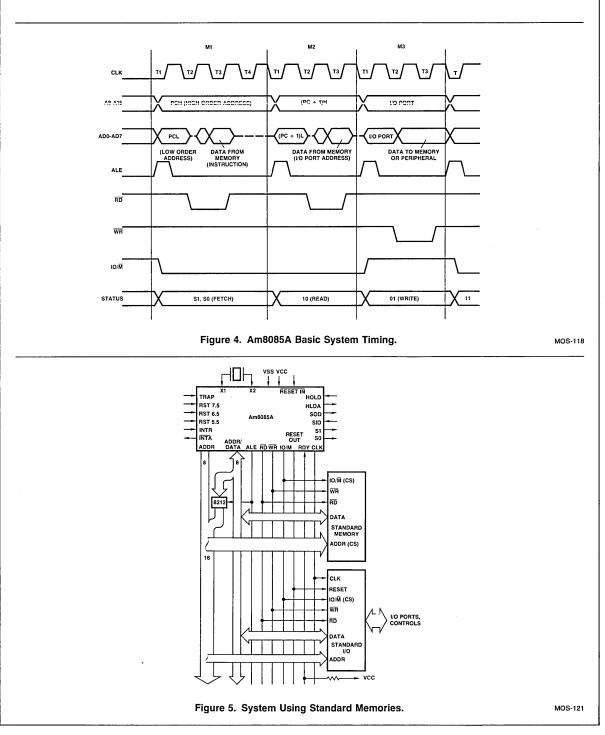

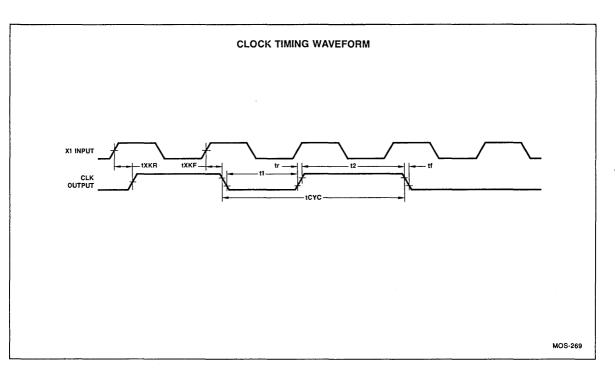

| A    | m8085A/Am8085A-2/Am9085ADM5-22          |

| APP  | ENDIX                                   |

| Co   | mmitment to Excellence                  |

r ₹.

#### INTRODUCTION

In todays' world of increasing demands placed on microcomputer-based system applications, the "smart," high-performance peripheral can offer significant advantages. These products can, in many cases, expand the application and extend the life cycle of the system without the extensive hardware and software changes required by a full system redesign.

Advanced Micro Devices recognized these system needs and in 1978 began introduction of a second generation family of high-peformance intelligent peripheral products designed for use with all general-purpose 8-bit CPUs and our AmZ8000 Family of 16-bit machines. This manual describes various interfaces between the AmZ8000, Am8085A, Z80 and 6800 microprocessors and AMD's 9500 Family of proprietary peripheral products.

This manual also presumes a basic familiarity with the microprocessors and peripheral circuits mentioned. We suggest that data sheets be handy for quick reference when referring to the various interface circuits.

## **Chip Select** – **Device Enabling**

¥

e,

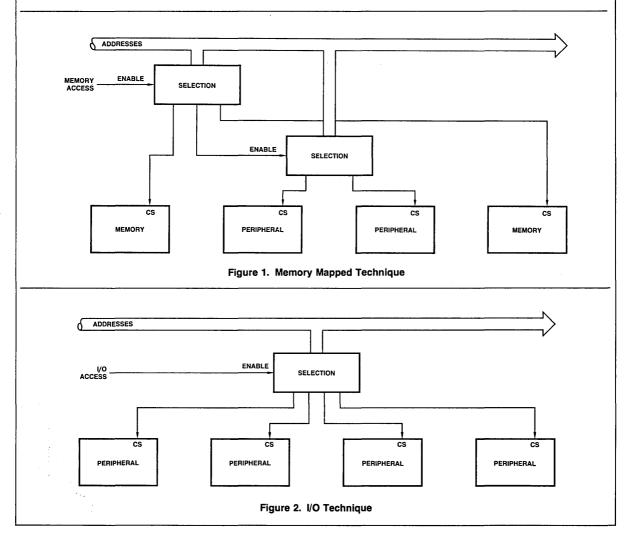

In order for the CPU or host system to access and communicate with other peripherals and support devices, some method must be used to select and manipulate these devices in a controlled manner. The CPU or host can control the peripheral and support devices through two types of conventions: memory-mapped or input/output (I/O).

Essentially, the memory-mapped technique is an I/O handling procedure where the peripherals are accessed as memory locations; it assigns areas of memory address space as I/O addresses. This architecture allows the CPU to manipulate devices by using the same instructions used to handle memory operations. Referring to Figure 1, note that both the peripherals and memory share the same common address and data busses. Each peripheral and memory location has a unique address which distinctively selects a device.

Figure 2 shows the second method which treats the peripheral device as an I/O peripheral. This method isolates peripheral devices from memory devices, but provides a direct means of communications with the CPU. In most general-purpose CPU systems, however, the flexibility of the software is limited by the

type of instructions available to manipulate I/O devices. The I/O instructions usually available are IN and OUT, which deal directly with the CPU's accumulator only. Thus, this technique becomes less effective due to the constraints of the simple I/O instructions.

Both conventions require some form of selecting one or more devices depending on the CPU requirements. Four different selecting techniques could be used, they are random logic, decoders, comparators and mapping PROMs. Since the random logic technique using SSI, gates, inverters, etc., can be implemented more easily than the other techniques, it will not be discussed.

As for decoders, AMD manufactures many different types of decoding devices, including the following:

| Am25LS138  | 1-of-8 Decoder                              |

|------------|---------------------------------------------|

| Am25LS139  | Dual 1-of-4 Decoder                         |

| Am25LS2438 | 1-of-8 Decoder with Three-State Output      |

| Am25LS2536 | 1-of-8 Decoder with Control Storage         |

| Am25LS2537 | 1-of-10 Decoder with Three-State Output     |

| Am25LS2539 | Dual 1-of-4 Decoder with Three-State Output |

#### Chip Select – Device Enabling

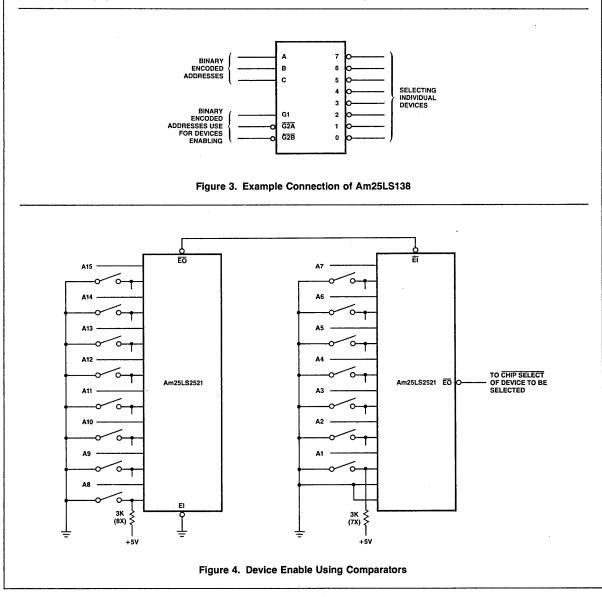

Decoder logic is used to create individual gated signals which selectively enable one device. The decoder normally connects to the address bus with its inputs tied to the proper individual address bit lines for the required address range.

Figure 3 uses an Am25LS138 to show the decoding of the lower bit addresses.

Note that the G1, G2A and G2B inputs determine where in the address space these eight device locations will reside. Assume, in the example, that G2A and G2B are connected to address bits  $A_3$  and  $A_4$ , while  $A_5$  through  $A_{15}$  are NOR'd together and tied to G1. This configuration would then insure that the devices are decoded for the lowest eight address locations. Besides selecting devices, decoders could also be used to decoder control signals as seen in AmZ8002 to Am9511A interface example on page 2-1.

Comparators offer another method to enable devices by providing an "equal to" condition when two patterns are compared. Depending on the type of comparator, 4- or 8-bit words can be compared to obtain a "greater than," "less than" or "equal to" logic expression. Figure 4 shows two Am25LS2521 8-bit comparators handling a 16-bit address range. By selecting the switch positions, a device can be enabled anywhere within a 65K addressing range.

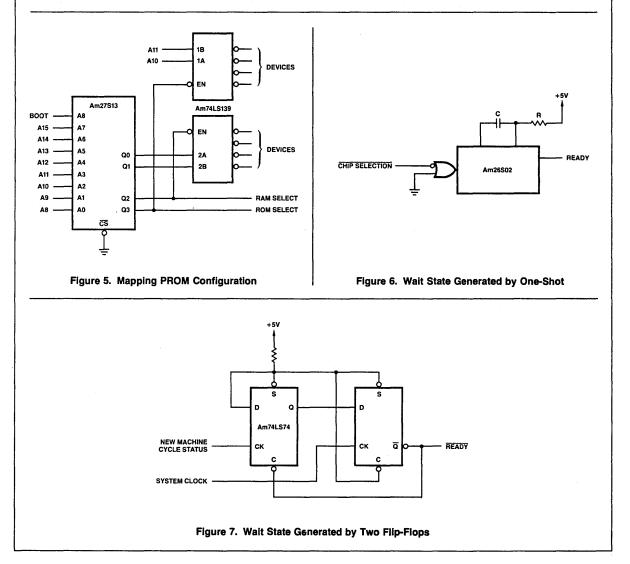

The last technique mentioned makes use of the mapping PROM to control the device address to memory location relationship. Mapping PROMs translate (map) sequential addresses into different independent memory locations as opposed to the logical binary pattern restriction of decoders. In fact, any device can be accessed from any memory location by simply changing the PROM program.

Figure 5 shows an Am27S13 512 x 4-bit PROM that can enable four separate devices within a 512 address range. Within this range, any of the four devices could be enabled in any random combination.

One of the address inputs of the PROM could be used to force a condition known as "booting" which initializes the system to a known operating state. For example, a known device could contain the starting address of a system monitor. The device could even retain the monitor in a ROM device and recall it only when the device is addressed. However, as in the example shown above, this reduces the device address range from 512 to 256 locations.

#### WAIT GENERATION

÷

Wait state generation is performed on microprocessors to retard the speed of the microprocessor so that slower memories and peripherals could be used. In the wait state, the microprocessor enters into an idle loop or a complete halt condition. Thereafter, the microprocessor cannot resume normal operation until the control signal that caused the wait state is negated. Usually this control signal is called the "READY" line.

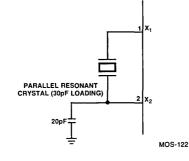

There are different methods to generate the wait state. One method uses a resettable monostable (one-shot) multivibrator. Figure 6, shows an Am26S02 one-shot used to produce a wait signal. The duration of the wait state is determined by the RC constant. The one-shot would be triggered when the Chip Select (CS) line of the peripheral is selected (goes LOW). This causes the READY line to go LOW and the processor enters a wait state for the specified period. Some microprocessors may require the system clock to be halted in a known state to perform this wait state operation.

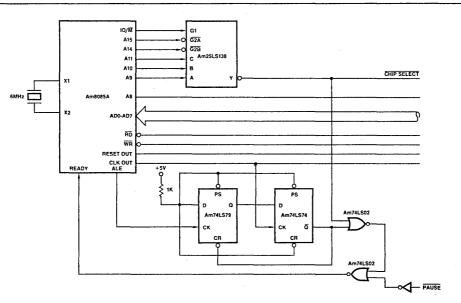

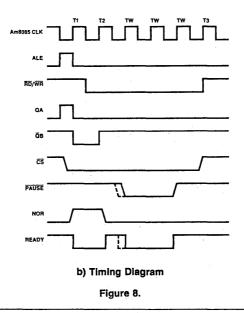

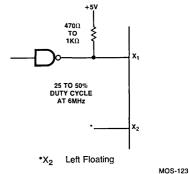

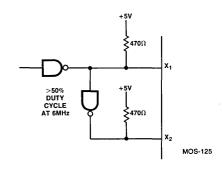

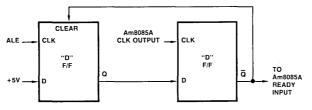

A more digital synchronous method can be performed by using two positive D-type flip-flops as shown in Figure 7. The clock input of the first flip-flop connects to a signal which contains unique information that indicates the start of a new machine cycle. The second flip-flop clock is tied to the system clock.

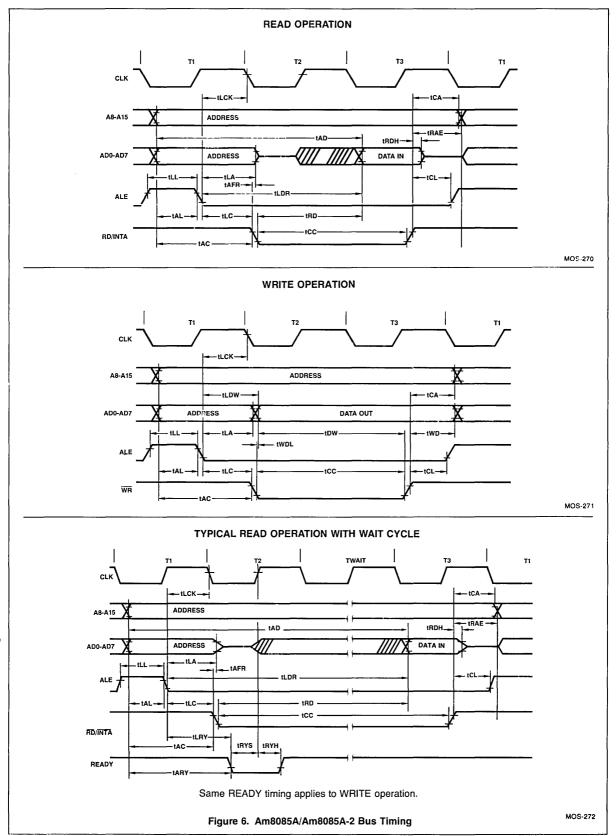

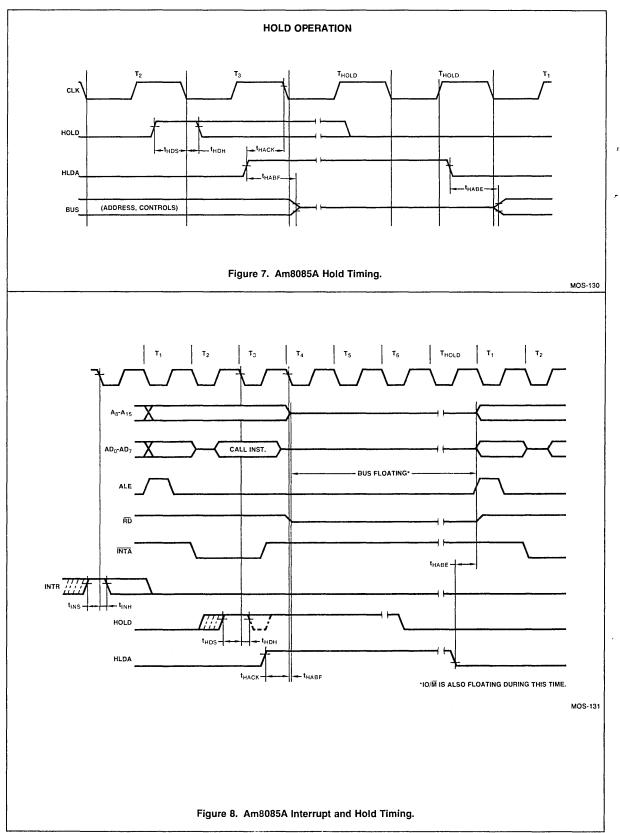

A better explanation of its operation uses the Am8085A example shown in Figure 8. The Am8085A samples the READY line at the rising edge of  $T_2$  to determine if any wait states are required. The RD and WR signals become true after address lines are stable. The RD to PAUSE delay is 150nsec max. To extend these control signals to Am9511A, the external logic shown must insert an initial wait state, because PAUSE may not become true early enough (at the  $T_2$  state rising clock) to meet the requirements of the Am8085A.

Address Line Enable (ALE) goes HIGH, the Q output of D flip-flop A goes HIGH. The  $\overline{Q}$  output of the D flip-flop B goes LOW at the rising edge of clock in state  $T_1$  and clears A. The READY goes LOW when  $\overline{Q}$  of B goes LOW, early enough to be sampled at  $T_2$  rising edge. At the next rising edge of the clock in the in  $T_2$  state the "not Ready" condition is sensed by the processor and the  $\overline{Q}$  output of flip-flop B goes HIGH. PAUSE may become true sometime after  $\overline{Q}$  of B goes HIGH and will thereafter introduce further wait states. The READY will be deactivated when PAUSE becomes inactive (HIGH) thus stopping the insertion of wait states.

To insert a wait state when the device is accessed, the PAUSE output is inverted and fed into one input of NOR gate 1. When

a) Example Wait Generation in an Am8085A System

# **Interface Circuits**

.

س.

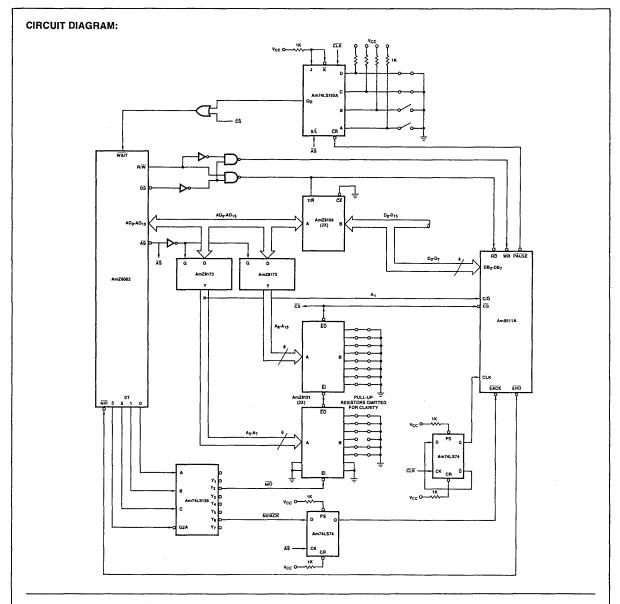

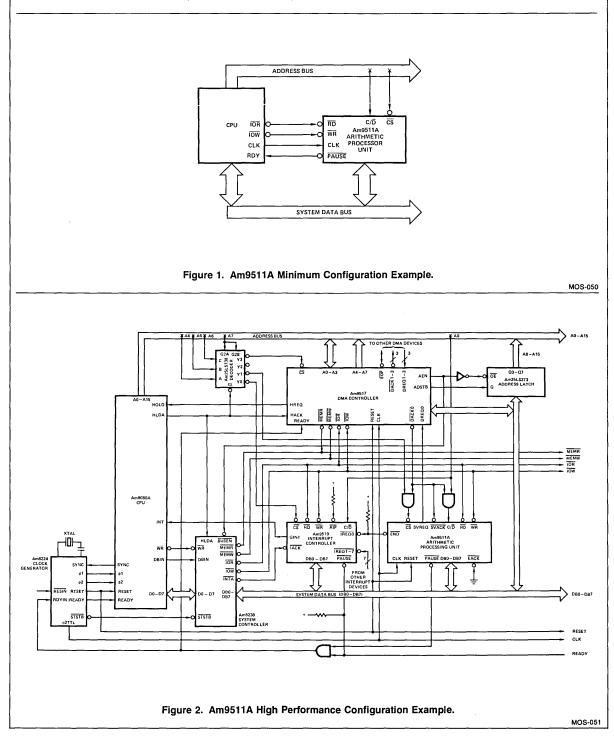

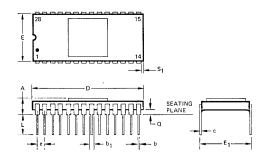

## Am9511A to AmZ8002 Interface

#### DESCRIPTION OF INTERFACE:

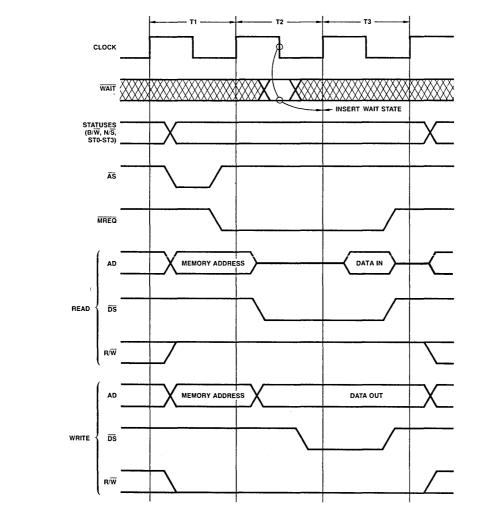

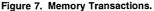

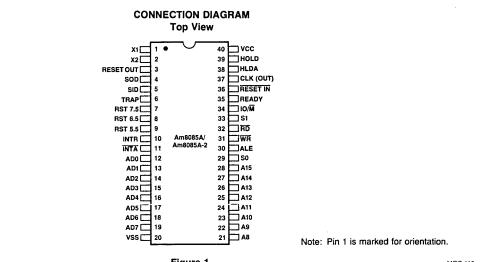

In this interface, the 16-bit AmZ8002 accesses the Am9511A in the byte mode during I/O transactions. The Am9511A data bus may be connected to either the upper or lower eight bits of the AmZ8002 bus (it is connected to the lower bits in this diagram). Therefore, I/O address should be odd.

Since the read access time of the Am9511A is relatively long, the AmZ8002 must wait during each read access. The PAUSE output, however, cannot be tied directly to the wait input (PAUSE would arrive too late to wait state AmZ8002). The Am25LS195A

4-bit shift register is used to issue a wait state to the CPU immediately at address strobe if chip select to the Am9511A is present. The  $Q_D$  output will remain LOW for two clock periods. If  $\overrightarrow{PAUSE}$  is LOW during this period, the  $\overrightarrow{WAIT}$  line will remain LOW. After the  $\overrightarrow{PAUSE}$  line returns HIGH, the  $Q_D$  output will go HIGH after two clock periods.

The circuit diagram shows an interrupt driven configuration. The END signal goes LOW and activates the Non-Vectored Interrupt NVI at the end of an Am9511A operation.

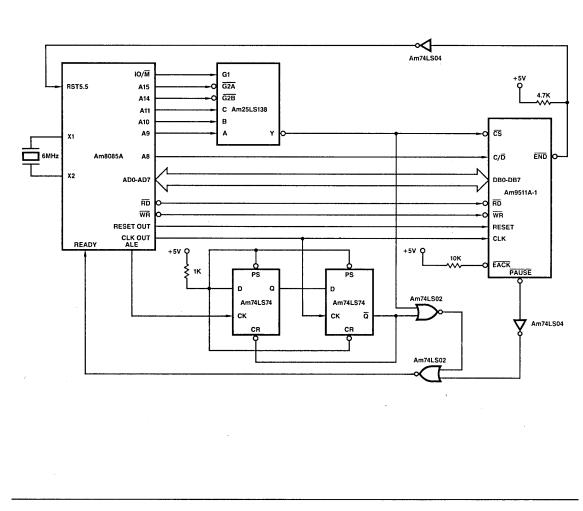

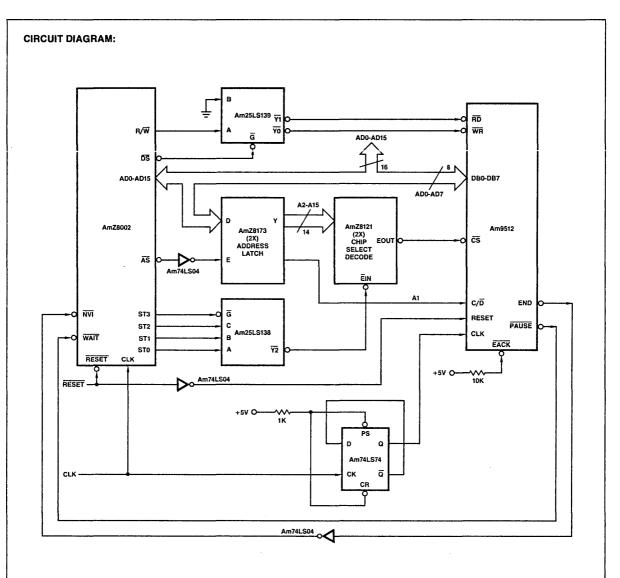

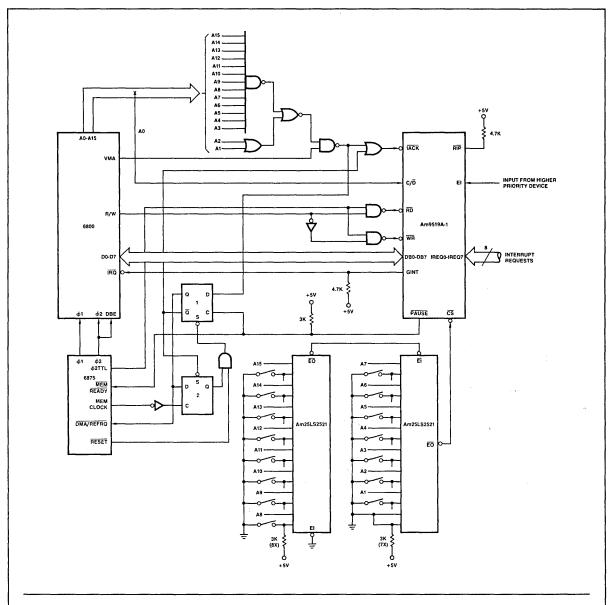

## Am9511A-1 to Am8085A Interface

#### **CIRCUIT DIAGRAM:**

#### **DESCRIPTION OF INTERFACE:**

In a typical Am8085A system, the system clock rate is 3MHz and requires the use of an Am9511A-1 for this interface.

The Am8085A has an early ready set up window as compared to Am9080A systems. Therefore, the PAUSE signal cannot be directly connected to the READY input of the Am8085A. If it were, the READY line would be activated too late for the Am8085A to go into the wait state. The two Am74LS74 D flip-flops are used to

force one wait state whenever the Am9511A is accessed. After the first wait state, the Am74LS74's  $\overline{O}$  output is reset and the PAUSE of the Am9511A-1 controls any additional wait states, if necessary. The example shows an interrupt driven interface. At the end of every Am9511A-1 operation, the END signal goes low and activates the restart input to the Am8085A.

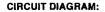

### Am9511A to Z80 Interface

#### DESCRIPTION OF INTERFACE:

The Am9511A responds to a Data Read, Data Write or Command Write Request received while the Am9511A is busy by pulling the PAUSE output LOW. This causes the Z80 to enter a wait state until the Am9511A has finished the current transaction. It should be noted that the Am9511A outputs a LOW on PAUSE 150nsec (max) after  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  has become active. The PAUSE remains LOW for (3.5 TCY + TO)nsec minimum during Status Read. (TCY is the clock period.) Therefore, the Z80 will insert one to two extra wait states. This interrupt-driven interface is straightforward and requires a minimum amount of external logic.

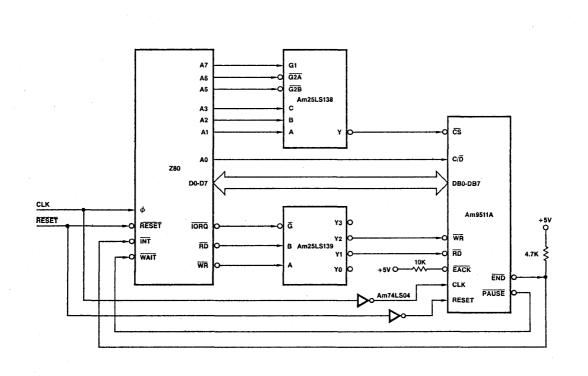

## Am9511A to 6800 Interface

#### **DESCRIPTION OF INTERFACE:**

In this example, the Am9511A must be accessed through a memory map technique since the 6800 does not have explicit I/O instructions. The decoder is strobed by VMA to produce a glitchfree output.

Since the Am9511A has a relatively long read access, the RD pulse must be stretched. This is done using the 6871A clock driver. The memory input stretches the  $\phi_2$  clock's HIGH time without affecting the 2XFC clock that is used as a clock for the Am9511A. When a  $\overline{CS}$  to the Am9511A is decoded, an Am26S02

one-shot is triggered and pulls the memory READY line LOW for approximately 500nsec. The one-shot is necessary because PAUSE will not go low soon enough to stretch  $\phi_2$  in the current cycle.

The programmer must take caution not to perform operations other than a status read while a current command is still in progress to avoid producing a PAUSE output longer than 4500nsec. The 6800 is a dynamic device and the clock input must not be stopped for more than 4500nsec.

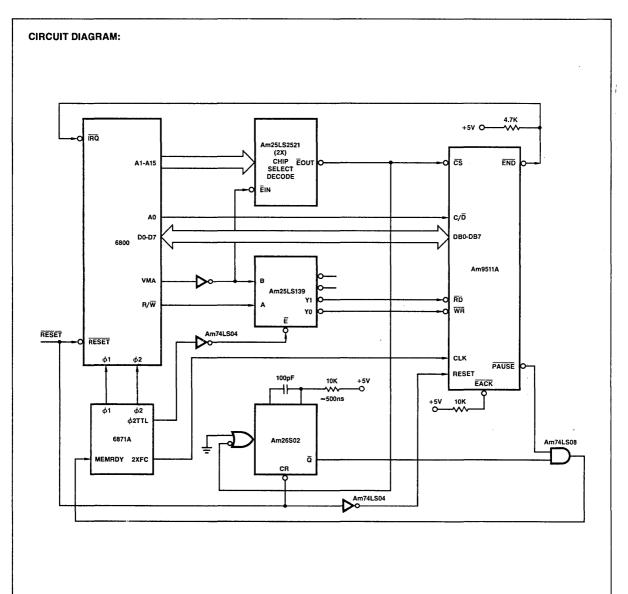

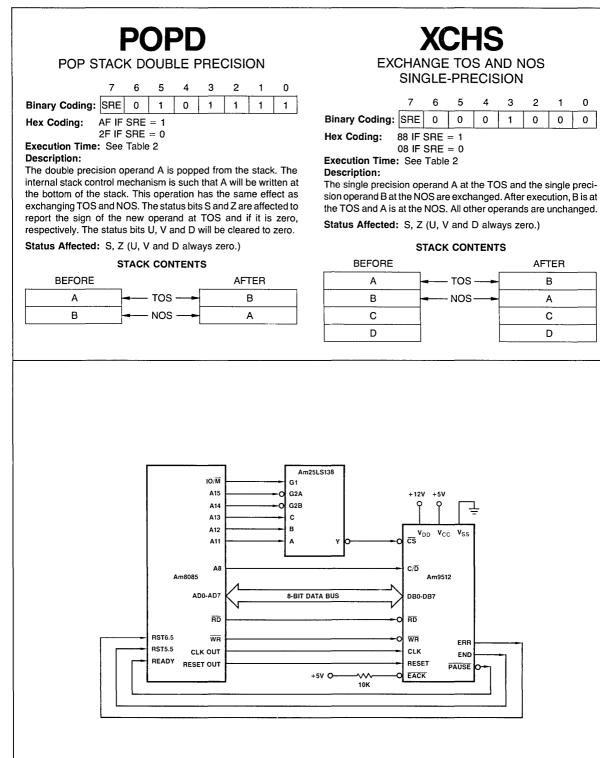

## Am9512 to AmZ8002 Interface

#### DESCRIPTION OF INTERFACE:

.

.....

This interface is similar to the Am9511A to AmZ8002 interface except that the PAUSE output can be connected directly to the WAIT input of the CPU. As in the Am9511A interface, the 4MHz CPU clock is divided by the Am74LS74 flip-flop to present a 2MHz clock to the Am9512.

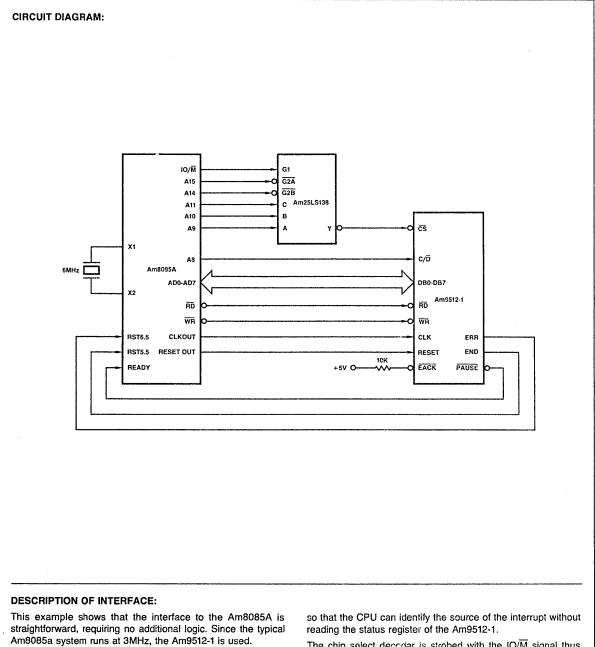

### Am9512-1 to Am8085A Interface

The ERR/END outputs are connected to separate interrupt inputs

The chip select deccder is strobed with the  $IO/\overline{M}$  signal thus enabling the Am9512-1 only during I/O operations.

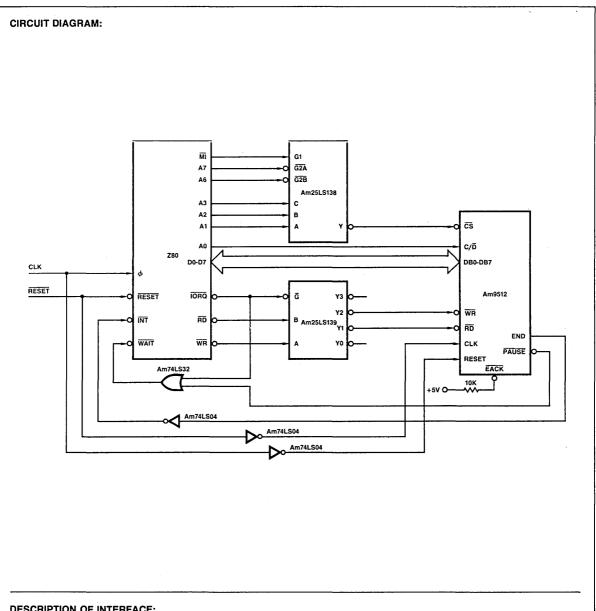

### Am9512 to Z80 Interface

#### **DESCRIPTION OF INTERFACE:**

In this interface, two more additional gates are needed than the number required for the Am9511A interface. An inverter is added to the Interrupt Request (INT) line because the polarity of the END signal is different. The Am74LS32 is added in the WAIT line to insure the Am9512 PAUSE will go LOW whenever the Chip Select on the Am9512 goes LOW. In the circuit above, the Chip Select input can go LOW during the second or third cycle of an

instruction when the memory address matches the Am9512 I/O address. If the OR Gate is omitted, the WAIT input on the Z80 will go LOW and the system will be forced into a deadlocked state. The Chip-Select Decoder in this example is strobed with M1. This is done to guarantee a Chip Select on every I/O cycle and it also prevents the Chip Select from going LOW during an interrupt acknowledge cycle.

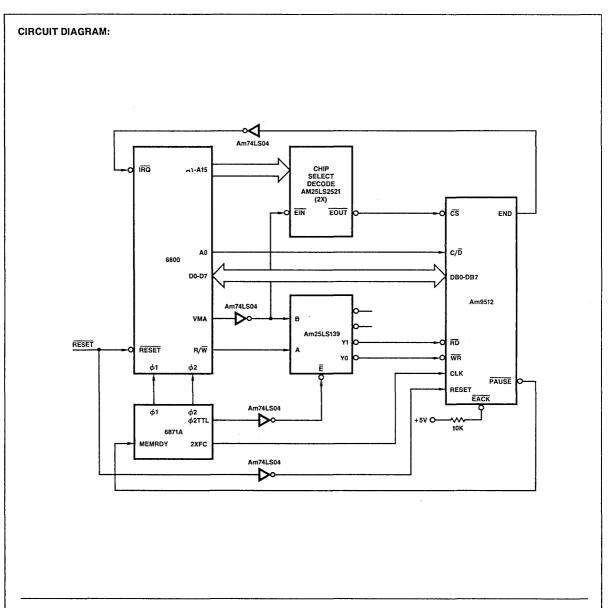

### Am9512 to 6800 Interface

#### **DESCRIPTION OF INTERFACE:**

This interface is similar to the Am9511A interface with the exception of the one-shot. Since the PAUSE output from the Am9512 follows the  $\overline{CS}$  instead of  $\overline{RD}$  or  $\overline{WR}$ . The Memory Ready

(MEMRDY) signal can be directly driven by the  $\overrightarrow{PAUSE}$  output. The only other addition is the inverter between the END output of the Am9512 and the  $\overrightarrow{IRQ}$  input.

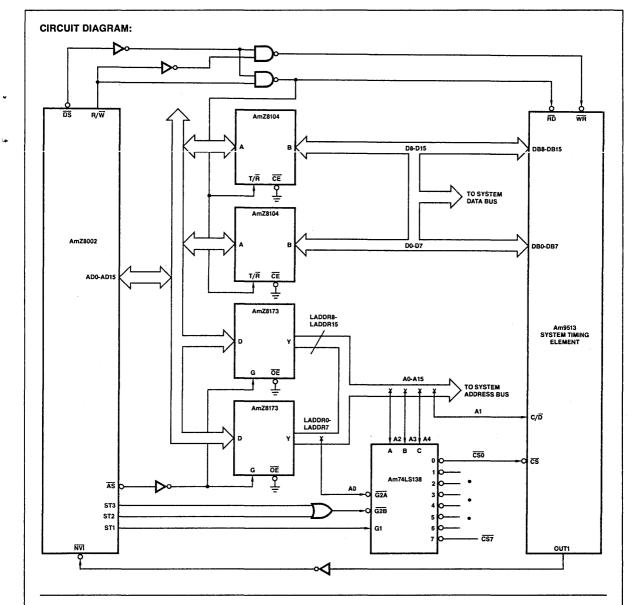

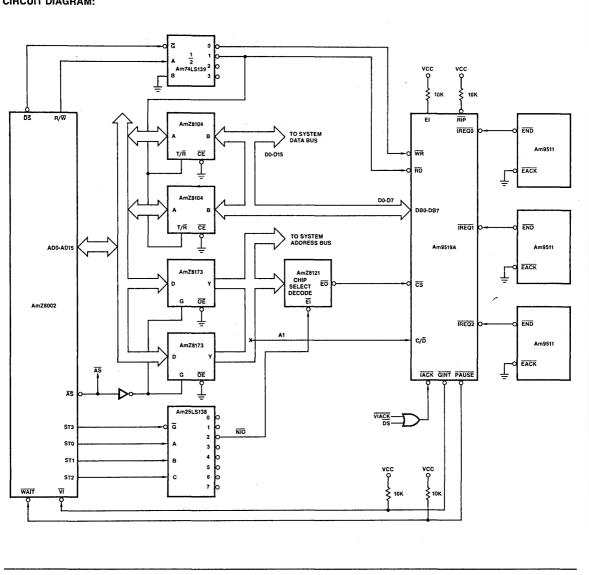

### Am9513 to AmZ8002 Interface

#### DESCRIPTION OF INTERFACE:

In this example, the Am9513 is connected to the 16-bit bus of the AmZ8002 via two AmZ8104 transceivers. Real-time interrupt capability is provided by connecting the Am9513 OUT1 output to the AmZ8002 NVI input. The address is latched into the AmZ8173, from the multiplexed bus during an Address Strobe

(AS). The inputs to the decoder come from the status output of the AmZ8002. The decoded status represents a normal I/O transaction. The  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  input signals of the Am9513 are generated by the  $\overline{\text{R/W}}$  and  $\overline{\text{D/S}}$  outputs on the AmZ8002.

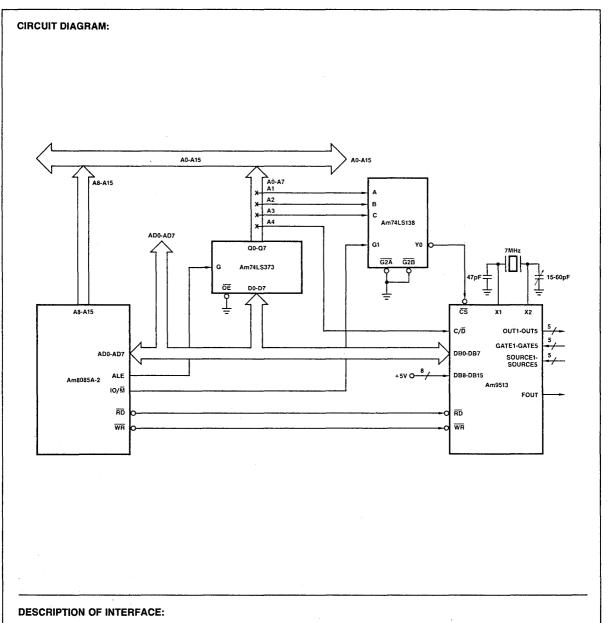

### Am9513 to Am8085A Interface

In this example, the Am9513 device address can be easily located into either the memory or I/O space by selecting the desired logic enable level from the Am8085A IO/M line to the decoder.

The Am25LS373 transparent 8-bit latch is not required to interface the Am9513 to the Am8085A. The latch is shown since most systems require some form of demultiplexing for the low order address bits to decode the device address.

The DB8-15 data bus lines of the Am9513 should be tied HIGH, unless some of the pins are used as auxiliary gating inputs to the Am9513.

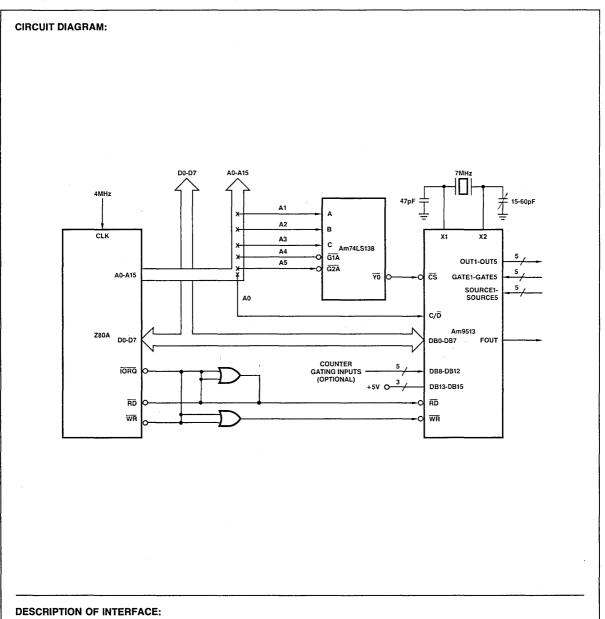

### Am9513 to Z80A Interface

Gating  $\overline{RD}$  and  $\overline{WR}$  with  $\overline{IORQ}$  from the Z80A allows mapping the Am9513 into the I/O space.

v

~

The least-significant address line ( $A_0$ ) is used to select the command or data port on the Am9513. The DB0-7 data bus lines of the

Am9513 interface directly to the Z80A data bus, while the DB13-15 lines should be tied HIGH. Pins DB8 through DB12 could be used as auxiliary gating inputs to the counters.

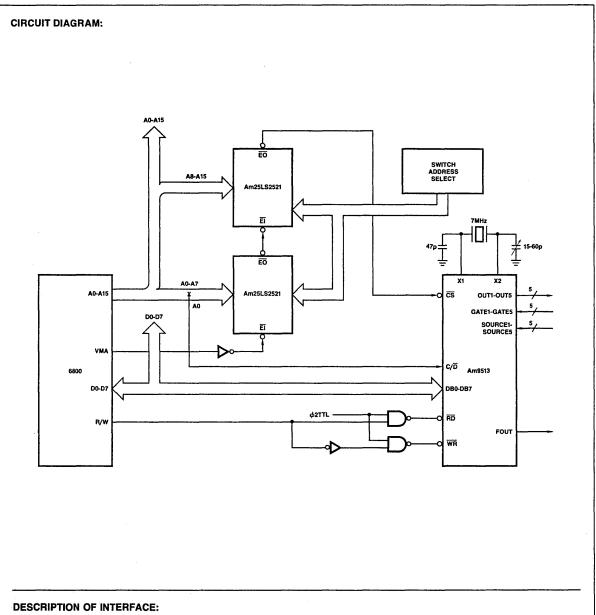

### Am9513 to 6800 Interface

This interface is an example of how to use two 8-bit comparators for chip selection. The peripheral address can be modified via dip switches.

The least significant address bit  $(A_0)$  is used to select the Command/Data (C/D) port of the Am9513.

The VMA signal is used to assure non-spurious Chip Selects (i.e., during interrupts, DMA, etc). The DB0-7 data bus lines on the

Am9513 are used to interface the part to the 6800 data bus. The DB8-15 lines on the Am9513 must be tied HIGH to insure proper operation.

The  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  signals are decoded from the 6800 R/W line and are gated with the  $\phi_2$  TTL clock high signal in order to assure valid data transfers.

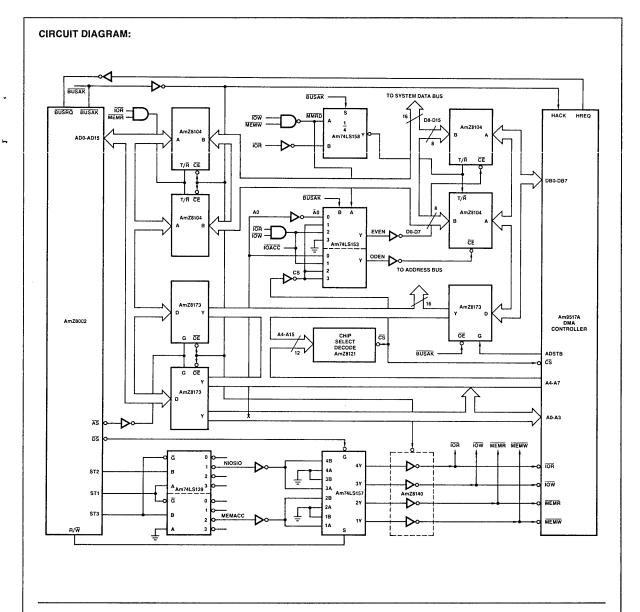

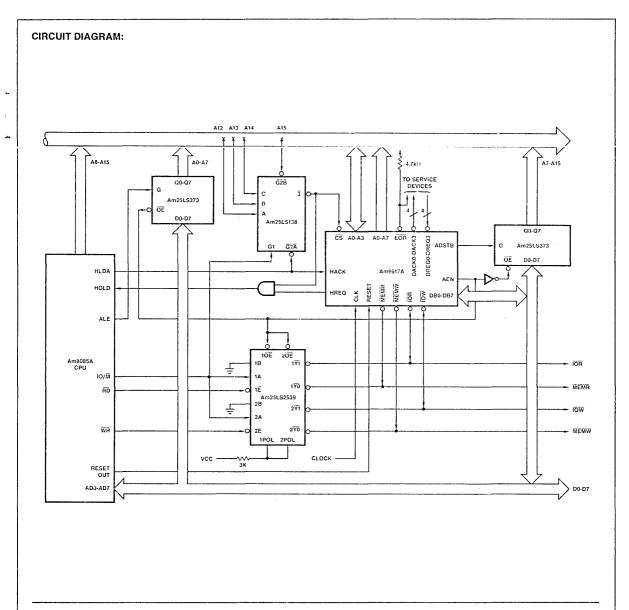

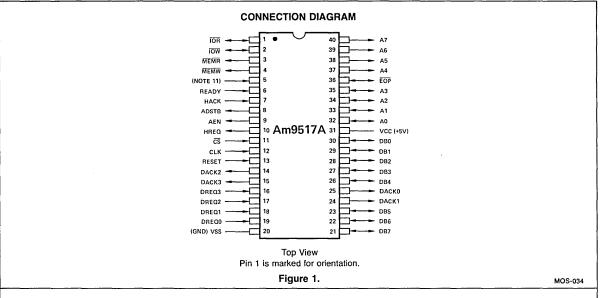

## Am9517A to AmZ8002 Interface

#### DESCRIPTION OF INTERFACE:

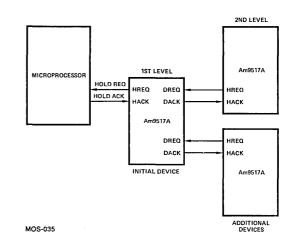

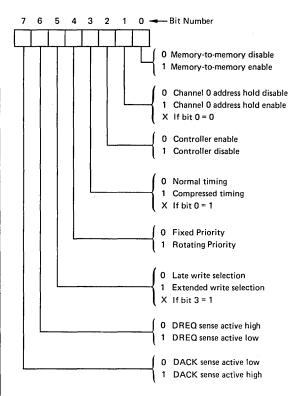

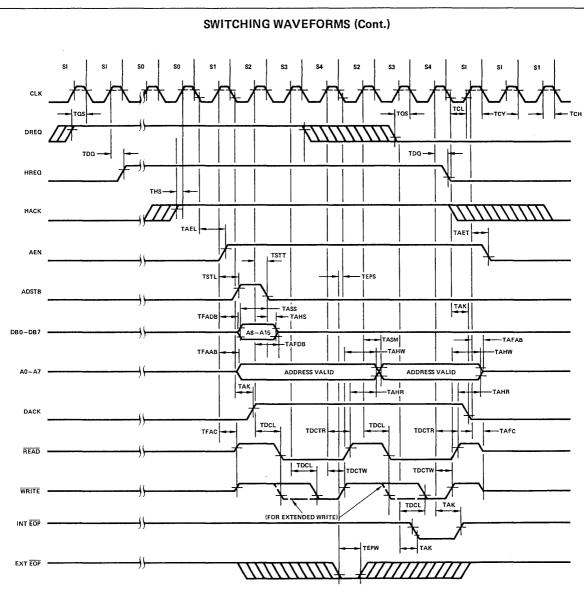

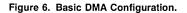

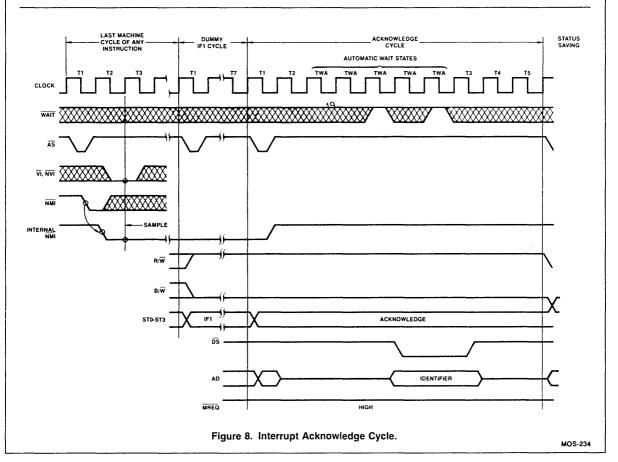

The Am9517A DMA Controller can provide some useful advantages to an AmZ8002 system, both in terms of increased throughput and reduced latency in responding to peripheral requests for attention. The DMAC performs transactions between memory and I/O (or memory-to-memory) by gaining bus mastership from the CPU. The DMAC then controls the bus by generating the necessary control and timing signals.

The bus exchanges between the CPU and DMAC are controlled by the Hold Request (HREQ) and Hold Acknowledge (HACK)

signals at the <u>DMAC</u> and the Bus Request (BUSRQ) and Bus Acknowledge (BUSAK) lines from the CPU.

The DMAC has separate 8-bit data and 8-bit address busses. The 8-bit address bus is used for outputting the lower half of the 16-bit memory address. The 8-bit data bus is buffered by two AmZ8104 transceivers, which fan the byte data to both halves of the 16-bit system bus during a DMAC output transaction. Similarly the buffers are used to steer either the upper or lower half of the bus onto the eight data lines of the DMAC during a DMAC input transaction. With this configuration, memory-to-memory transfers, which are inherently implemented using the DMAC dataflow, can take place between any two memory byte locations.

The Chip Select is generated from a comparison of the mostsignificant 12 address bits, since the least significant four address bits are input to the DMAC. The CS is only enabled when an I/O transaction is underway.

The DMAC carries out transactions using a set of four commands. Memory Read ( $\overline{MEMR}$ ) and Memory Write ( $\overline{MEMW}$ ) are DMAC outputs generated during memory accesses. I/O Read ( $\overline{IOR}$ ) and I/O Write ( $\overline{IOW}$ ) may be inputs or outputs for the DMAC. If the DMAC is in control of the bus,  $\overline{IOR}$  and  $\overline{IOW}$  are DMAC outputs generated during peripheral accesses. If the CPU is in control of the bus,  $\overline{IOR}$  and  $\overline{IOW}$  are inputs to the DMAC generated by the CPU when the latter is accessing the DMAC control registers. Command signals are generated using an Am74LS139 dual 2-to-4 decoder cascaded with an Am74LS157 quad 2-to-1 multiplexer.

The control requirements for the DMAC address and data buffers are different for both cases and thus the final stage of control generation is implemented through an Am74LS153 multiplexer. The multiplexer select lines are driven from the CPU BUSAK line (which defines whether the CPU or DMAC is in control of the bus) and an OR of MEMW and IOW which defines a write transaction.

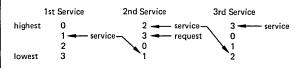

When BUSRQ is HIGH the CPU controls the bus. If LOW, the DMAC can take control of the bus. The peripheral can gain the attention of the DMAC when service is required by means of the DREQ and DACK lines which implement a request/acknowledge handshake with the peripheral device. For more detailed information on the DMAC peripheral interface, see AM-PUB073 – "The Am9517 Multimode Direct Memory Access Controller."

2-14

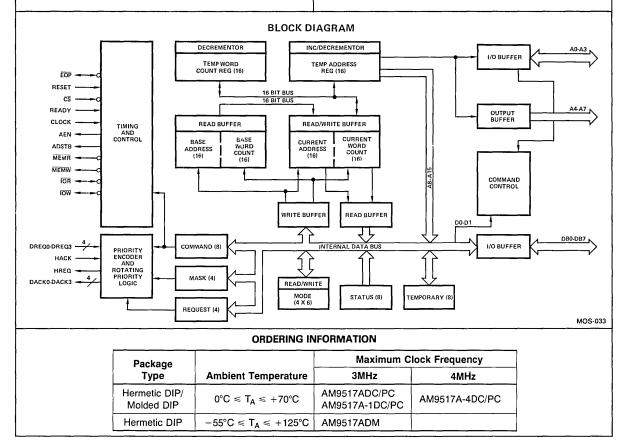

### Am9517A to Am8085A Interface

#### DESCRIPTION OF INTERFACE:

The Am9517A DMA controller is conveniently configured in an Am8085A microprocessor system. The multimode DMA controller issues a Hold Request whenever there is at least one valid DMA Request from a peripheral device. When the processor replies with a Hold Acknowledge signal, the Am9517A takes control of the address bus, data bus and control bus. The Am25LS2539 dual one-of-four decoder with three-state outputs easily decodes the IO and MEM space control lines from the processor, and also isolates the Am8085A processor when DMA

operations are in process. The address for the first transfer operation comes out of the DMA Controller in two bytes, the leastsignificant eight bits on the eight address outputs and the mostsignificant eight bits on the data bus. The contents of the data bus are conveniently latched into the Am25LS373 register to complete the full 16 bits of the address bus. After the initial transfer takes place, the register is updated only after a carry or borrow is generated in the least-significant address byte.

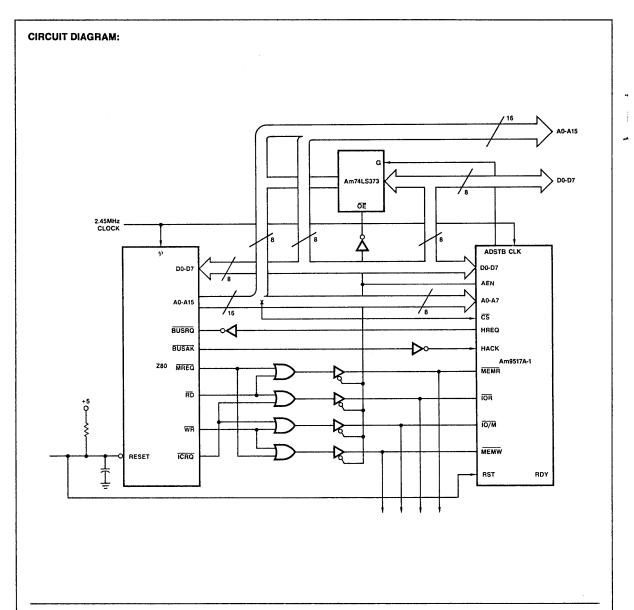

## Am9517A-1 to Z80 Interface

#### **DESCRIPTION OF INTERFACE:**

In this example, the high order  $A_8$ - $A_{15}$  memory <u>address is</u> latched by an 8-bit Am74LS373 latch, while the IOR, IO/M, MEMR and MEMW signals are decoded from appropriate Z80 outputs. Note that a 4MHz Am9517A-4 could be used with a

$4 \rm MHz$  Z80A if an additional circuit consisting of two D flip-flops are used to insert a wait state to the Z80A during I/O read and write operations.

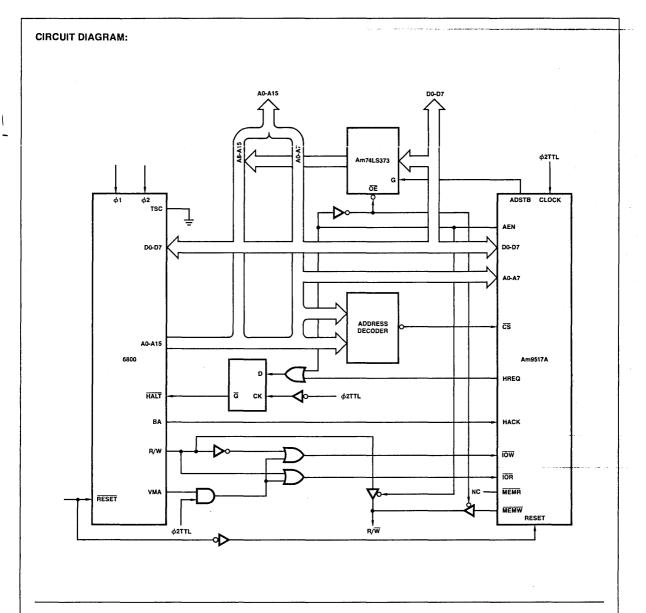

## Am9517A to 6800 Interface

#### DESCRIPTION OF INTERFACE:

The Am9517A DMA controller is conveniently interfaced to a 6800 microprocessor system. An Am74LS373 type 8-bit latch holds the high order A8 to A15 addresses during DMA transfers.

A D-type flip-flop synchronizes the Am9517A Hold Request (HREQ) signal with the  $\phi_2$  clock "low" as required by the 6800. The HREQ and AEN (Address Enable) outputs from the Am9517A are ORed together to simplify giving back the bus to the 6800 at the end of the DMA operation because the DMA is still active on the bus for about one clock period following HREQ going inactive. This method also allows unlimited periods of DMA transfers, since the 6800 is not stopped by using its TSC input. Usage of the TSC input requires holding the  $\phi_1$  and  $\phi_2$  clocks to the 6800 high and low, respectively, for not longer than 4500nsec (1MHz 6800).

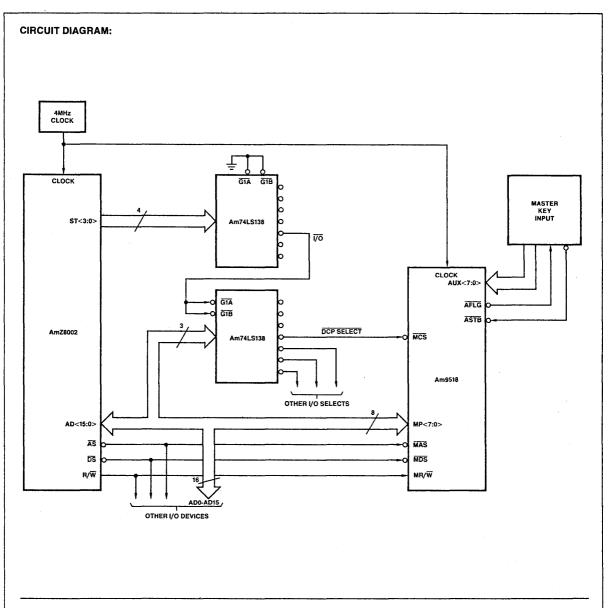

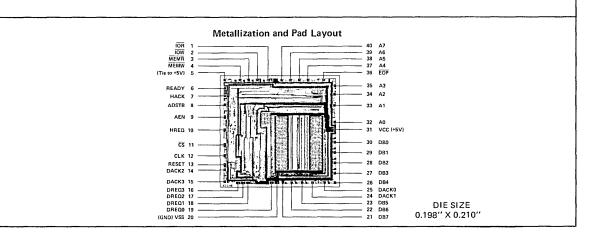

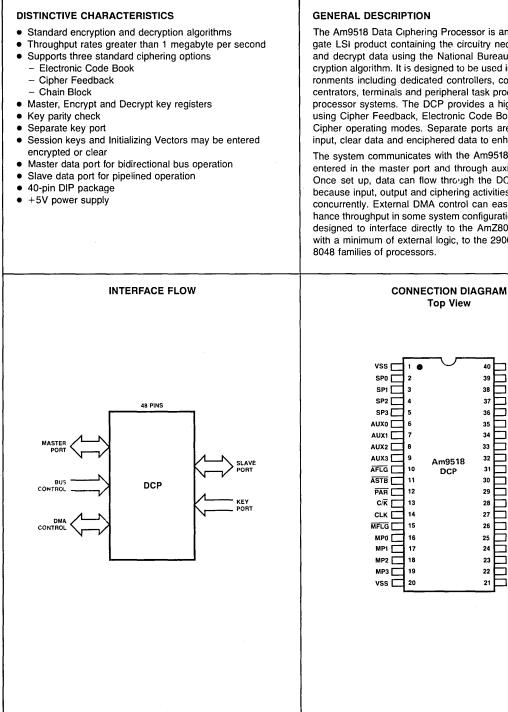

## Am9518 to AmZ8002 Interface

#### **DESCRIPTION OF INTERFACE:**

The Am9518 Data Cyphering Processor interfaces very conveniently to an AmZ8002 bus structure. The I/O address space access is decoded from the ST0 to ST3 status pins of the AmZ8002 processor while, simultaneously, the three upper address lines (A<sub>13</sub>-A<sub>15</sub>) are being decoded by another Am74LS138

type decoder for activation of the Am9518 chip select input. The example is sufficient for a small system configuration.

The AD0-15 bus lines are shown as an 8-bit interface to the Am9518.

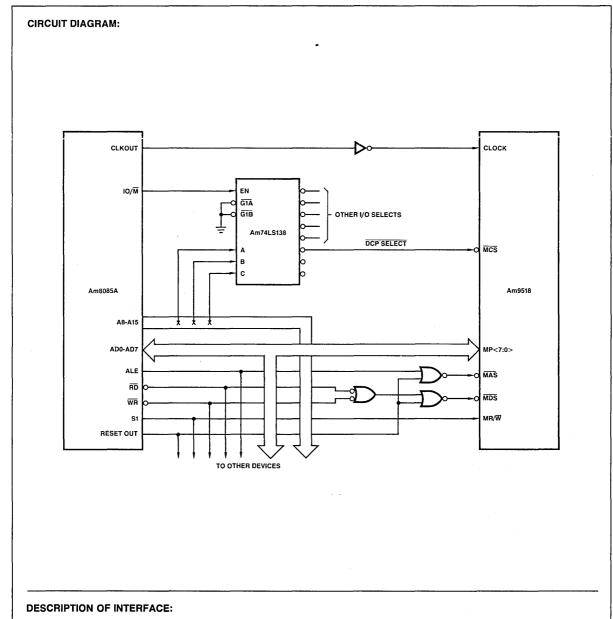

## Am9518 to Am8085A Interface

The Am9518 Data Cyphering Processor interfaces very simply to the Am8085A microprocessor. The Am9518 is shown mapped in an IO address space with its Chip Select input being decoded from three suitable lines of the A<sub>8</sub> to A<sub>15</sub> address and AD<sub>0</sub> to AD<sub>7</sub> address/data bus. The ALE output generates the required AS strobe, while either the  $\overline{\text{RD}}$  or  $\overline{\text{WR}}$  outputs generate the DS

strobe. The S1 output of the Am8085A is used to specify a read or write operation.

The Am8085A microprocessor cycle time should not be greater than 2MHz in this configuration in order to allow Am9518 to synchronize to the processor.

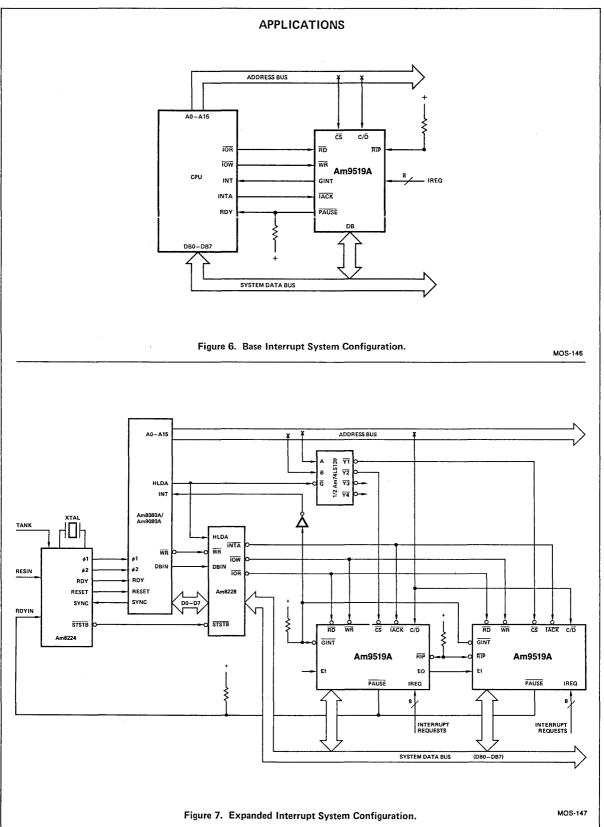

## Am9519A to AmZ8002 Interface

CIRCUIT DIAGRAM:

#### **DESCRIPTION OF INTERFACE:**

The application involving the connection of the Am9511A to the Am28002 (pg. 2-1) highlights the limitations of a direct interrupt connection to the CPU. The inclusion of the Am9519A Interrupt Controller in the system relieves the CPU of a large part of this task and also serves to prioritize multiple interrupts.

The AmZ8173 latches and AmZ8104 bidirectional buffers generate separate address and data busses from the CPU address/data bus. The latched address is input to two 8-bit comparators to generate a Chip Select ( $\overline{CS}$ ) for the Am9519A if a normal I/O transaction is being executed. Latched address bit A1 drives the C/ $\overline{D}$  input to the Am9519A.

The lower half of the buffered data bus is shown driving the bidirectional data bus of the Am9519A. This is applicable with the choice of odd port addresses, should byte I/O operations be executed. The read and write commands required by the Am9519A ( $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  respectively) are generated with half of

an Am74LS139 decoder.  $\overline{DS}$  is applied to the enable input and  $\overline{R/W}$  to the least-significant select line. This is an alternative solution to a discrete gate implementation.

The Am9519A makes a vectored interrupt request to the CPU using the Group Interrupt line ( $\overline{GINT}$ ) which should be a LOW active output from the Am9519A.  $\overline{GINT}$  is reset by the CPU Vectored Interrupt Acknowledge ( $\overline{VIACK}$ ). The latter is decoded from the status lines and is or'ed with DS to generate IACK to the Am9519A.

The Am9519A should be programmed to respond to a single interrupt acknowledge, which in turn results in the transfer of one byte of interrupt status to the CPU. This is sufficient since the vectored interrupt mechanism in the CPU requires only one byte of status to form the vector. The interrupts input to the Am9519A from the devices may be levels or pulses. If levels are employed, then some form of request reset will have to be included. In the implementation shown, pulsed interrupt requests are assumed.

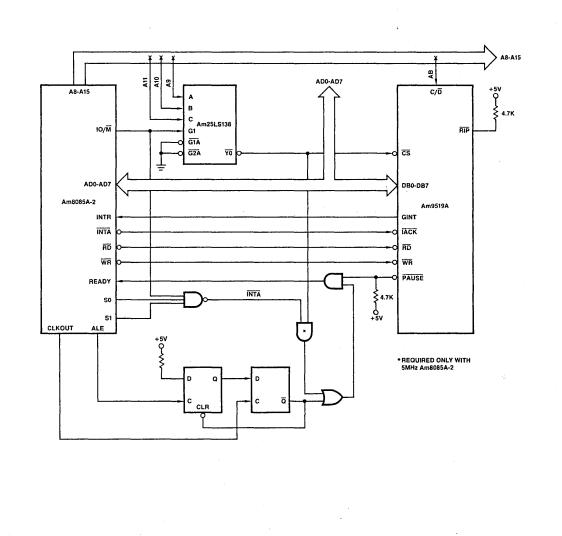

# Am9519A to Am8085 Interface

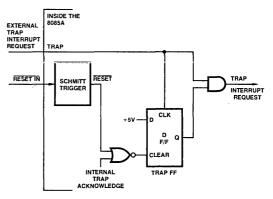

#### **DESCRIPTION OF INTERFACE:**

The two D-type flip-flops in conjunction with S0, S1 and  $10/\overline{M}$  insert a wait state to the Am8085A whenever the microprocessor acknowledges an interrupt. The circuitry is required since the Am8085A samples a READY (wait) signal on the rising edge of CLK OUT during T2, and ready requires a 100nsec minimum set up time prior to the rising edge of T2. The 3-input NAND gate predecodes an  $\overline{INTA}$  active signal using the two status outputs (S0, S1) and the IO/M address pin. This is required since the INTA output from the Am8085A becomes valid too late to meet the

100nsec setup time of READY. The Am9519A's PAUSE output takes over control of the ready line following T2.

Insertion of a wait during the read and write operation to the Am9519A with  $\overline{CS}$  is required only when the 5MHz Am8085A-2 part is used. The wait state is needed because the minimum  $\overline{RD}$  and  $\overline{WR}$  pulse width of the Am8085A-2 is 230nsec, while the Am9519A-1, as example, requires 250nsec minimum and the Am9519A, 300nsec minimum.

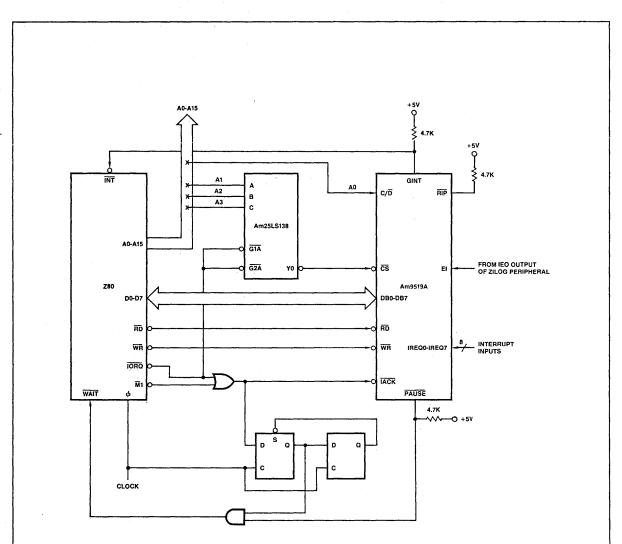

# Am9519A to Z80 Interface

#### **DESCRIPTION OF INTERFACE:**

The Am9519A can be configured as the sole interrupting device to the Z80 or in conjunction with other devices (such as the SIO, CIO, CTC, etc.) in a daisy chain interrupt nest. When the Am9519A is part of a nested daisy chain, it must be the lowest priority device because the Am9519 activates its Enable Out (EO) output after receipt of the interrupt acknowledge signal ( $\overline{IORQ} \cdot \overline{M1}$ ) from the microprocessor, while the Zilog parts require their IEI (Interrupt Enable In) signal to setup at least 200nsec (2.5MHz Z80) prior to the Interrupt Acknowledge going active.

A wait state is inserted in the CPU whenever an Interrupt Acknowledge sequence begins since the Am9519A begins resolving its interrupt priorities after the interrupt acknowledge signal goes active. The flip-flops assert a wait state at the second TW falling clock edge and allow the PAUSE output to extend the wait state as required.

For the 4MHz Z80A CPU, a wait state must be asserted whenever the CPU performs a read or write operation to the Am9519A in order to meet the RD and WR pulse width requirements. Either an Am9519A or Am9519A-1 can be used with the Z80A.

# Am9519A to 6800 Interface

#### DESCRIPTION OF INTERFACE:

The Am9519A interfaces to a 1MHz 6800 microprocessor by using two sets of address decoders and a scheme to insert wait states during both  $\phi_1$  and  $\phi_2$  of the clock. Comparators provide the means of memory mapping the Am9519A device in order to access its internal registers. The Am9519A requires only two addresses for access, therefore the least-significant bit, A0, of the address bus drives the Command/Data (C/D) input directly.

For interrupt acknowledges, the addresses FFF8 and FFF9 are decoded because the 6800 fetches its interrupt vector (PC ad-

dress or jump address) from the above memory locations. The output of two bytes from the Am9519 provides the proper jump address for each interrupting device.

The Am9519A begins resolving its highest priority interrupt following the active edge of Interrupt Acknowledge IACK which is the address FFF8 in a 6800 system, and requires a 500 to 1000nsec delay before the first vector address appears on the data bus. The delay is accomplished by stretching the  $\phi_2$  clock high via the PAUSE active signal to the MEM READY input of the 6875 clock device. The only constraint is for the PAUSE signal to be active before the rising edge of  $\phi_2$  clock. The Am9519A-1 device may be preferred because the PAUSE output goes active within 125nsec following IACK active vs. 175nsec for the Am9519.

Flip-flops are used to create a 500nsec minimum  $\overrightarrow{IACK}$  HIGH pulse width between the rising edge of the first  $\overrightarrow{IACK}$  active (PAUSE going inactive and  $\phi_2$  clock going LOW) and the falling

edge of the second IACK active. This is done by stretching the pulse width of  $\phi_1$  clock. The rising of PAUSE causes flip-flop 1 to assert a DMA/REF RQ to the 6875 before address FFF9 is valid on the 6800 address bus in order to meet the setup time requirement of the 6875. The falling edge of the next MEM clock ( $\phi_2$  TTL ungated) from the 6875 causes stretching of  $\phi_1$  clock HIGH to terminate, IACK to become active now, and a second valid byte to be present on the data bus during the  $\phi_2$  clock HIGH period.

# SUMMARY

and the first product of a second part of the second second second second second second second second second se

### **PROCESSOR/PERIPHERAL SELECTION CHART**

| Processor                  | Am8085A                | Am8085A-2                                 | AmZ8001/2             | Z80A                  | 6800                             |

|----------------------------|------------------------|-------------------------------------------|-----------------------|-----------------------|----------------------------------|

| Clock Period               | 320ns                  | 200ns                                     | 250ns                 | 250ns                 | 1.0µs                            |

| Clock Generator            | N/A                    | N/A                                       | AmZ8127               | AmZ8127               | N/A                              |

| Data Cypher. Processor     | Am9518<br>(Note 3)     | Am9518<br>(Note 3)                        | Am9518                | (Note 4)              | (Note 4)                         |

| System Timing Controller   | Am9513                 | Am9513                                    | Am9513                | Am9513                | Am9513                           |

|                            | Am9511A-1              | Am9511A-1                                 | Am9511A-1             | Am9511A-1             | Am9511A                          |

| Arithmetic Processor       | Am9512-1<br>(Note 2)   | Am9512-1<br>(Notes 1 and 2)               | Am9512-1<br>(Note 1)  | Am9512-1<br>(Note 1)  | Am9512                           |

| Univ. Interrupt Controller | Am9519A-1              | Am9519A-1<br>(Note 2)                     | Am9519A-1<br>(Note 2) | Am9519A-1<br>(Note 2) | Am9519A-1<br>Am9519A<br>(Note 2) |

| Multimode DMA Controller   | Am9517A-1<br>Am9517A-4 | Am9517A-1<br>Am9517A-4<br>(Notes 1 and 2) | Am9517A-4<br>(Note 2) | Am9517A-1<br>(Note 2) | Am9517A                          |

Notes: 1. Clock input cannot be driven directly from processor clock; peripheral required lower frequency (processor clock-2).

2. CPU/peripheral transfers require addition of wait state, using external circuitry.

Clock input cannot be greater than 2MHz in order to allow Am9518 synchronization.

Am9518 requires additional logic for demultiplexing.

# Am9500 Family Data Sheets

#### DISTINCTIVE CHARACTERISTICS

- Replaces Am9511

- Fixed point 16 and 32 bit operations

- Floating point 32 bit operations

- Binary data formats

- Add, Subtract, Multiply and Divide

- Trigonometric and inverse trigonometric functions

- Square roots, logarithms, exponentiation

- · Float to fixed and fixed to float conversions

- Stack-oriented operand storage

- DMA or programmed I/O data transfers

- End signal simplifies concurrent processing

- Synchronous/Asynchronous operations

- General purpose 8-bit data bus interface

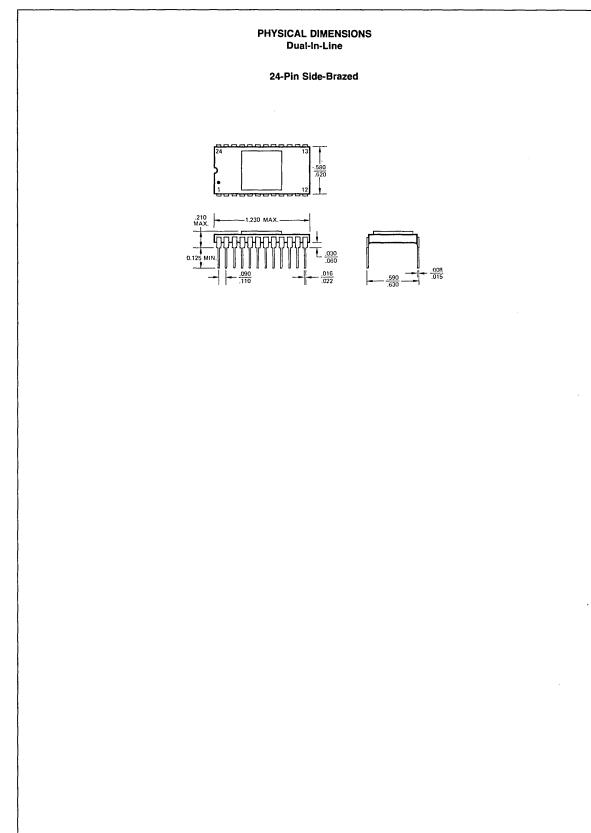

- Standard 24 pin package

- +12 volt and +5 volt power supplies

- Advanced N-channel silicon gate MOS technology

- 100% MIL-STD-883 reliability assurance testing

#### **GENERAL DESCRIPTION**

The Am9511A Arithmetic Processing Unit (APU) is a monolithic MOS/LSI device that provides high performance fixed and floating point arithmetic and a variety of floating point trigonometric and mathematical operations. It may be used to enhance the computational capability of a wide variety of processor-oriented systems.

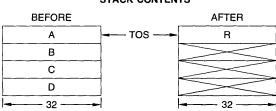

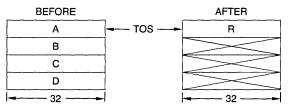

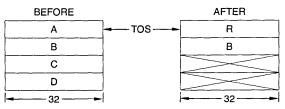

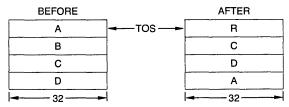

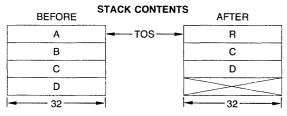

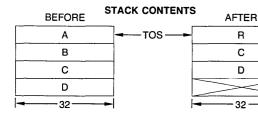

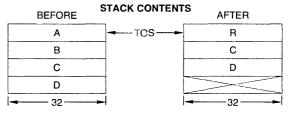

All transfers, including operand, result, status and command information, take place over an 8-bit bidirectional data bus. Operands are pushed onto an internal stack and a command is issued to perform operations on the data in the stack. Results are then available to be retrieved from the stack, or additional commands may be entered.

Transfers to and from the APU may be handled by the associated processor using conventional programmed I/O, or may be handled by a direct memory access controller for improved performance. Upon completion of each command, the APU issues an end of execution signal that may be used as an interrupt by the CPU to help coordinate program execution.

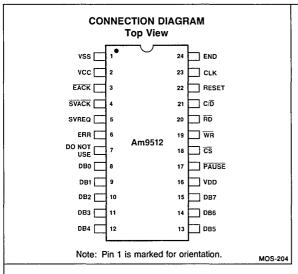

#### **ORDERING INFORMATION**

| Package      | Ambient                                      | Maximum Clock Frequency |             |  |  |  |  |

|--------------|----------------------------------------------|-------------------------|-------------|--|--|--|--|

| Туре         | Temperature                                  | 2MHz                    | 3MHz        |  |  |  |  |

|              | $0^{\circ}C \leq T_{A} \leq +70^{\circ}C$    | Am9511ADC               | Am9511A-1DC |  |  |  |  |

| Hermetic DIP | $-55^{\circ}C \leq T_{A} \leq +125^{\circ}C$ | Am9511ADM               | Am9511A-1DM |  |  |  |  |

#### INTERFACE SIGNAL DESCRIPTION

VCC: +5V Power Supply VDD: +12V Power Supply VSS: Ground

#### CLK (Clock, Input)

An external timing source connected to the CLK input provides the necessary clocking. The CLK input can be asynchronous to the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  control signals.

#### RESET (Reset, Input)

A HIGH on this input causes initialization. Reset terminates any operation in progress, and clears the status register to zero. The internal stack pointer is initialized and the contents of the stack may be affected but the command register is not affected by the reset operation. After a reset the END output will be HIGH, and the SVREQ output will be LOW. For proper initialization, the RESET input must be HIGH for at least five CLK periods following stable power supply voltages and stable clock.

#### C/D (Command/Data Select, Input)

The C/ $\overline{D}$  input together with the  $\overline{RD}$  and  $\overline{WR}$  inputs determines the type of transfer to be performed on the data bus as follows:

| C/D | RD | WR | Function                             |

|-----|----|----|--------------------------------------|

| L   | н  | L  | Push data byte into the stack        |

| Ļ   | L  | н  | Pop data byte from the stack         |

| н   | н  | L  | Enter command byte from the data bus |

| н   | L  | н  | Read Status                          |

| х   | L  | L  | Undefined                            |

L = LOW

H = HIGH

X = DON'T CARE

#### END (End of Execution, Output)

A LOW on this output indicates that execution of the current command is complete. This output will be cleared HIGH by activating the EACK input LOW or performing any read or write operation or device initialization using the RESET. If EACK is tied LOW, the END output will be a pulse (see EACK description). This is an open drain output and requires a pull up to +5V.

Reading the status register while a command execution is in progress is allowed. However any read or write operation clears the flip-flop that generates the END output. Thus such continuous reading could conflict with internal logic setting the END flip-flop at the completion of command execution.

#### EACK (End Acknowledge, Output)

This input when LOW makes the END output go LOW. As mentioned earlier HIGH on the END output signals completion of a command execution. The END output signal is derived from an internal flip-flop which is clocked at the completion of a command. This flip-flop is clocked to the reset state when EACK is LOW. Consequently, if the EACK is tied LOW, the END output will be a pulse that is approximately one CLK period wide.

#### **SVREQ (Service Request, Output)**

A HIGH on this output indicates completion of a command. In this sense this output is same as the END output. However, whether the SVREQ output will go HIGH at the completion of a command or not is determined by a service request bit in the command register. This bit must be 1 for SVREQ to go HIGH. The SVREQ can be cleared (i.e., go LOW) by activating the SVACK input LOW or initializing the device using the RESET. Also, the SVREQ will be automatically cleared after completion of any command that has the service request bit as 0.

#### **SVACK** (Service Acknowledge, Input)

A LOW on this input activates the reset input of the flip-flop generating the SVREQ output. If the SVACK input is permanently tied LOW, it will conflict with the internal setting of the flip-flop to generate the SVREQ output. Thus the SVREQ indication cannot be relied upon if the SVACK is tied LOW.

#### DB0-DB7 (Bidirectional Data Bus, Input/Output)

These eight bidirectional lines are used to transfer command, status and operand information between the device and the host processor. DB0 is the least significant and DB7 is the most significant bit position. HIGH on the data bus line corresponds to 1 and LOW corresponds to 0.

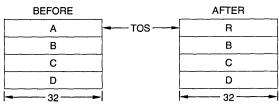

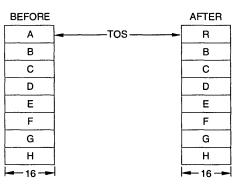

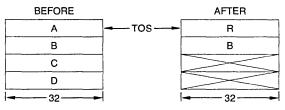

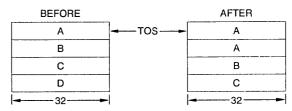

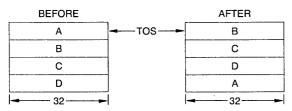

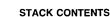

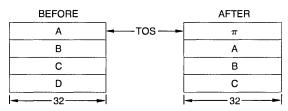

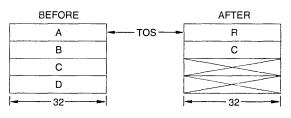

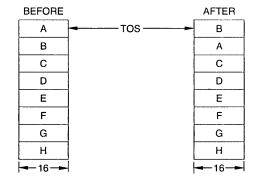

When pushing operands on the stack using the data bus, the least significant byte must be pushed first and most significant byte last. When popping the stack to read the result of an operation, the most significant byte will be available on the data bus first and the least significant byte will be the last. Moreover, for pushing operands and popping results, the number of transactions must be equal to the proper number of bytes appropriate for the chosen format. Otherwise, the internal byte pointer will not be aligned properly. The Am9511A single precision format requires 2 bytes, double precision and floating-point formats require 4 bytes.

#### CS (Chip Select, Input)

This input must be LOW to accomplish any read or write operation to the Am9511A.

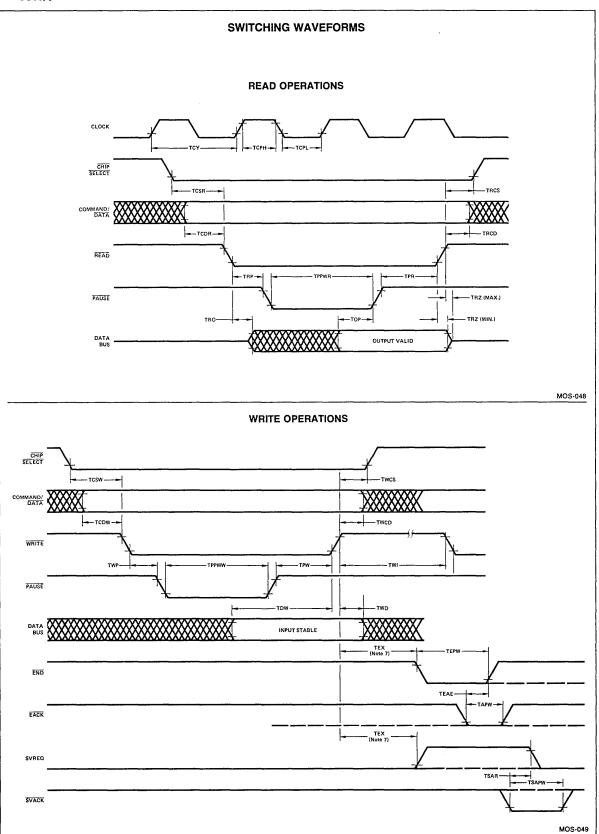

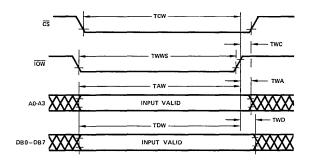

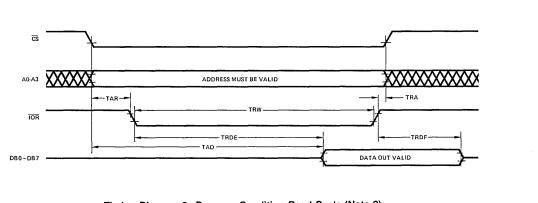

To perform a write operation data is presented on DB0 through DB7 lines,  $C/\overline{D}$  is driven to an appropriate level and the  $\overline{CS}$  input is made LOW. However, actual writing into the Am9511A cannot start until  $\overline{WR}$  is made LOW. After initiating the write operation by a  $\overline{WR}$  HIGH to LOW transition, the  $\overline{PAUSE}$  output will go LOW momentarily (TPPWW).

The  $\overline{WR}$  input can go HIGH after  $\overline{PAUSE}$  goes HIGH. The data lines, C/D input and the  $\overline{CS}$  input can change when appropriate hold time requirements are satisfied. See write timing diagram for details.

To perform a read operation an appropriate logic level is established on the C/D input and  $\overline{CS}$  is made LOW. The Read operation does not start until the RD input goes LOW. PAUSE will go LOW for a period of TPPWR. When PAUSE goes back HIGH again, it indicates that read operation is complete and the required information is available on the DB0 through DB7 lines. This information will remain on the data lines as long as RD input is LOW. The RD input can return HIGH anytime after PAUSE goes HIGH. The  $\overline{CS}$  input and  $C/\overline{D}$  inputs can change anytime after RD returns HIGH. See read timing diagram for details.

RD (Read, Input)

A LOW on this input is used to read information from an internal location and gate that information on to the data bus. The  $\overline{CS}$  input must be LOW to accomplish the read operation. The  $C/\overline{D}$  input determines what internal location is of interest. See  $C/\overline{D}$ ,  $\overline{CS}$  input descriptions and read timing diagram for details. If the END output was LOW, performing any read operation will make the END output go HIGH after the HIGH to LOW transition of the RD input (assuming  $\overline{CS}$  is LOW).

#### WR (Write, Input)

A LOW on this input is used to transfer information from the data bus into an internal location. The  $\overline{CS}$  must be LOW to accomplish the write operation. The  $C/\overline{D}$  determines which internal location is to be written. See  $C/\overline{D}$ ,  $\overline{CS}$  input descriptions and write timing diagram for details.

If the  $\overline{\text{END}}$  output was LOW, performing any write operation will make the  $\overline{\text{END}}$  output go HIGH after the LOW to HIGH transition of the  $\overline{\text{WR}}$  input (assuming  $\overline{\text{CS}}$  is LOW).

#### PAUSE (Pause, Output)

This output is a handshake signal used while performing read or write transactions with the Am9511A. A LOW at this output indicates that the Am9511A has not yet completed its information transfer with the host over the data bus. During a read operation, after  $\overline{CS}$  went LOW, the PAUSE will become LOW shortly (TRP) after  $\overline{RD}$  goes LOW. PAUSE will return high only after the data bus contains valid output data. The  $\overline{CS}$  and  $\overline{RD}$  should remain LOW when PAUSE is LOW. The RD may go high anytime after  $\overline{PAUSE}$  goes HIGH. During a write operation, after  $\overline{CS}$  went LOW, the PAUSE will be LOW for a very short duration (TPPWN) after  $\overline{WR}$  goes LOW. Since the minimum of TPPWW is 0, the PAUSE may not go LOW at all for fast devices.  $\overline{WR}$  may go HIGH anytime after PAUSE goes HIGH.

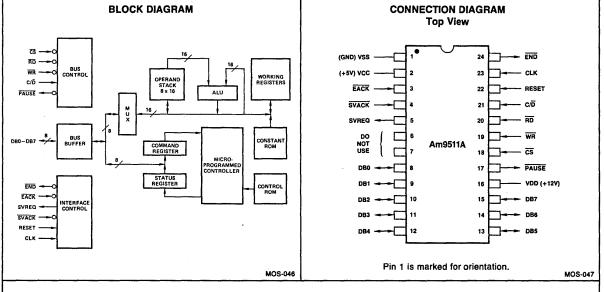

#### FUNCTIONAL DESCRIPTION

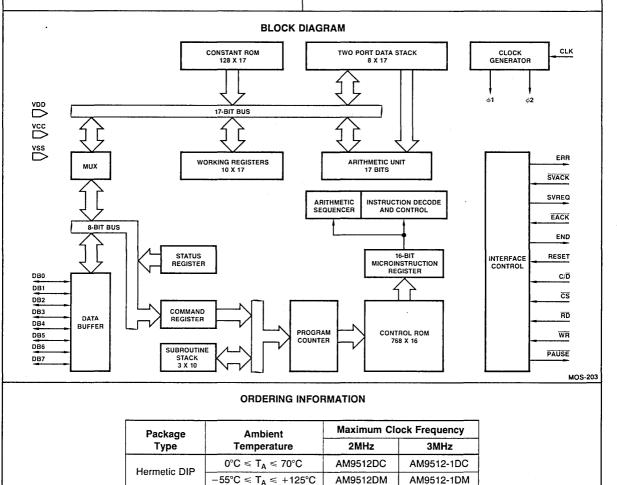

Major functional units of the Am9511A are shown in the block diagram. The Am9511A employs a microprogram controlled stack oriented architecture with 16-bit wide data paths.

The Arithmetic Logic Unit (ALU) receives one of its operands from the Operand Stack. This stack is an 8-word by 16-bit 2-port memory with last in-first out (LIFO) attributes. The second operand to the ALU is supplied by the internal 16-bit bus. In addition to supplying the second operand, this bidirectional bus also carries the results from the output of the ALU when required. Writing into the Operand Stack takes place from this internal 16-bit bus when required. Also connected to this bus are the Constant ROM and Working Registers. The ROM provides the required constants to perform the mathematical operations (Chebyshev Algorithms) while the Working Registers provide storage for the intermediate values during command execution.

Communication between the external world and the Am9511A takes place on eight bidirectional input/output lines DB0 through DB7 (Data Bus). These signals are gated to the internal eight-bit

bus through appropriate interface and buffer circuitry. Multiplexing facilities exist for bidirectional communication between the internal eight and sixteen-bit buses. The Status Register and Command Register are also accessible via the eight-bit bus.

The Am9511A operations are controlled by the microprogram contained in the Control ROM. The Program Counter supplies the microprogram addresses and can be partially loaded from the Command Register. Associated with the Program Counter is the Subroutine Stack where return addresses are held during subroutine calls in the microprogram. The Microinstruction Register holds the current microinstruction being executed. This register facilitates pipelined microprogram execution. The Instruction Decode logic generates various internal control signals needed for the Am9511A operation.

The Interface Control logic receives several external inputs and provides handshake related outputs to facilitate interfacing the Am9511A to microprocessors.

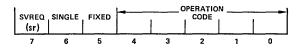

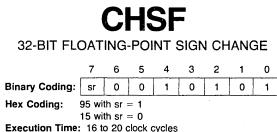

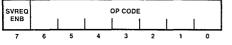

#### COMMAND FORMAT

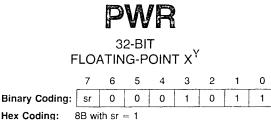

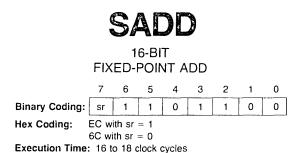

Each command entered into the Am9511A consists of a single 8-bit byte having the format illustrated below:

Bits 0-4 select the operation to be performed as shown in the table. Bits 5-6 select the data format for the operation. If bit 5 is a 1, a fixed point data format is specified. If bit 5 is a 0, floating point format is specified. Bit 6 selects the precision of the data to be operated on by fixed point commands (if bit 5 = 0, bit 6 must be 0). If bit 6 is a 1, single-precision (16-bit) operands are indicated; if bit 6 is a 0, double-precision (32-bit) operands are indicated. Results are undefined for all illegal combinations of bits in the command byte. Bit 7 indicates whether a service request is to be issued after the command is executed. If bit 7 is a 1, the service request output (SVREQ) will go high at the conclusion of the command and will remain high until reset by a low level on the service acknowledge pin (SVACK) or until completion of execution of a succeeding command where bit 7 is 0. Each command issued to the Am9511A requests post execution service based upon the state of bit 7 in the command byte. When bit 7 is a 0. SVREQ remains low.

|          |        |                                        |        |        |        |            |          | COMM         | AND SUMMARY                                                                                                                  |  |  |  |  |  |

|----------|--------|----------------------------------------|--------|--------|--------|------------|----------|--------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| <u> </u> |        | Co                                     | nma    | nd C   | ode    |            |          | Command      | Command Description                                                                                                          |  |  |  |  |  |

| 7        | 6      | 5                                      | 4      | 3      | 2      | 1          | 0        | Mnemonic     |                                                                                                                              |  |  |  |  |  |

|          |        |                                        |        |        |        |            |          | F            |                                                                                                                              |  |  |  |  |  |

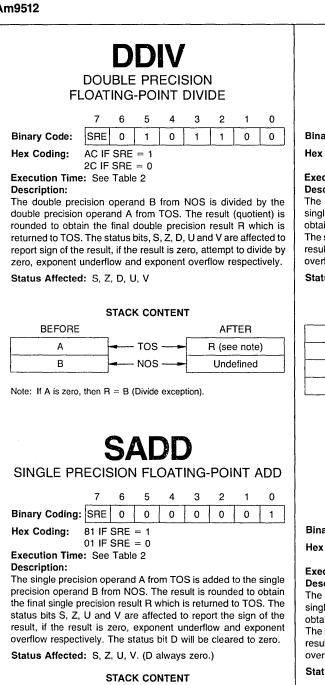

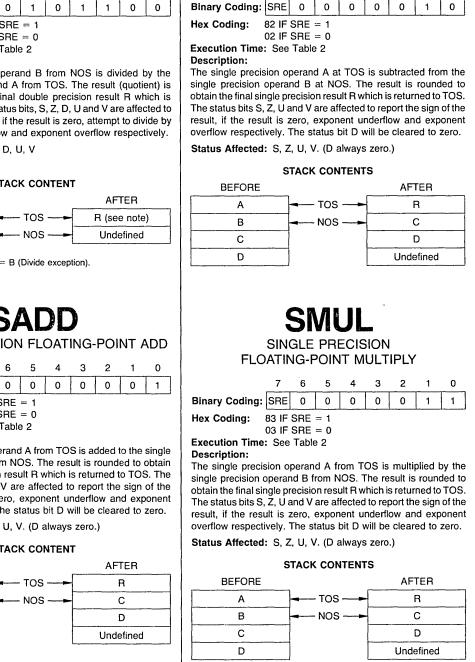

| sr       | 1      | 1                                      | 0      | 1      | 1      | 0          | 0        | SADD         | Add TOS to NOS. Result to NOS. Pop Stack.                                                                                    |  |  |  |  |  |

| sr       | 1      | $\begin{bmatrix} 1 \\ 1 \end{bmatrix}$ | 0<br>0 | 1      | 1      | 0          | 1        | SSUB<br>SMUL | Subtract TOS from NOS. Result to NOS. Pop Stack.<br>Multiply NOS by TOS. Lower half of result to NOS. Pop Stack.             |  |  |  |  |  |

| sr<br>sr | 1      | 1                                      | 1      | 0      | 1      | 1          | 0        | SMUU         | Multiply NOS by TOS. Lower half of result to NOS. Pop Stack.<br>Multiply NOS by TOS. Upper half of result to NOS. Pop Stack. |  |  |  |  |  |

| sr       | 1      | 1                                      | ò      | 1      | 1      | 1          | 1        | SDIV         | Divide NOS by TOS. Result to NOS. Pop Stack.                                                                                 |  |  |  |  |  |

| I        |        | 1                                      |        |        |        | L          |          | F            | IXED-POINT 32-BIT                                                                                                            |  |  |  |  |  |

| sr       | 0      | 1                                      | 0      | 1      | 1      | 0          | 0        | DADD         | Add TOS to NOS. Result to NOS. Pop Stack.                                                                                    |  |  |  |  |  |

| sr       | 0      | 1                                      | 0      | 1      | 1      | 0          | 1        | DSUB         | Subtract TOS from NOS. Result to NOS. Pop Stack.                                                                             |  |  |  |  |  |

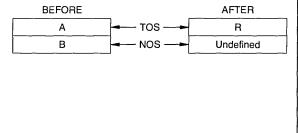

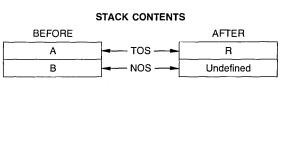

| sr       | 0      | 1                                      | 0      | 1      | 1      | 1          | 0        | DMUL         | Multiply NOS by TOS. Lower half of result to NOS. Pop Stack.                                                                 |  |  |  |  |  |

| sr       | 0      | 1                                      | 1      | 0      | 1      | 1          | 0        | DMUU         | Multiply NOS by TOS. Upper half of result to NOS. Pop Stack.                                                                 |  |  |  |  |  |

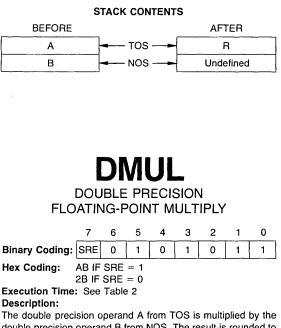

| sr       | 0      | 1                                      | 0      | 1      | 1      | 1          | 1        |              | Divide NOS by TOS. Result to NOS. Pop Stack.                                                                                 |  |  |  |  |  |

|          |        |                                        |        |        |        |            | <u> </u> |              | DATING-POINT 32-BIT                                                                                                          |  |  |  |  |  |

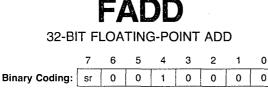

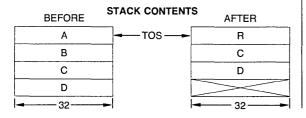

| sr       | 0      | 0                                      | 1      | 0      | 0      | 0          | 0        | FADD         | Add TOS to NOS. Result to NOS. Pop Stack.                                                                                    |  |  |  |  |  |

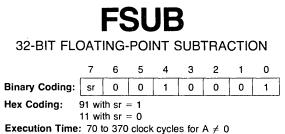

| sr       | 0      | 0<br>0                                 | 1      | 0      | 0      | 0<br>1     | 1        | FSUB<br>FMUL | Subtract TOS from NOS. Result to NOS. Pop Stack,<br>Multiply NOS by TOS. Result to NOS. Pop Stack.                           |  |  |  |  |  |

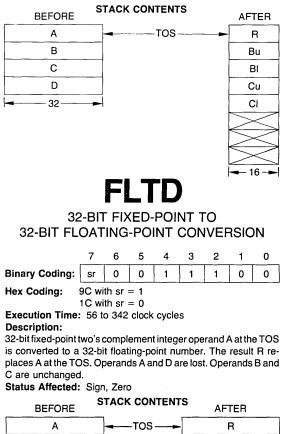

| sr<br>sr | 0      | 0                                      | 1      | 0      | 0      |            | 1        | FDIV         | Divide NOS by TOS. Result to NOS. Pop Stack.                                                                                 |  |  |  |  |  |

| 51       |        |                                        |        | 0      | 0      | <b></b>    | <u> </u> |              | LOATING-POINT FUNCTIONS                                                                                                      |  |  |  |  |  |

| -        |        |                                        |        |        | -      |            |          |              |                                                                                                                              |  |  |  |  |  |

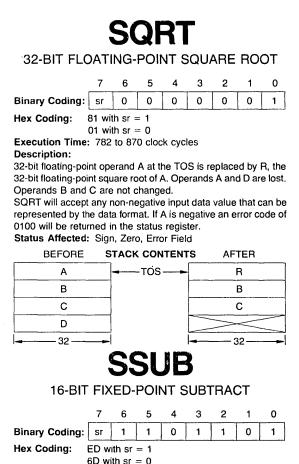

| sr<br>sr | 0      | 0                                      | 0<br>0 | 0<br>0 | 0<br>0 | 0          | 1<br>0   | SQRT<br>SIN  | Square Root of TOS. Result in TOS.<br>Sine of TOS. Result in TOS.                                                            |  |  |  |  |  |

| sr       | 0      | 0                                      | 0      | 0      | 0      | 1          | 1        | COS          | Cosine of TOS. Result in TOS.                                                                                                |  |  |  |  |  |

| sr       | ŏ      | ŏ                                      | ŏ      | ō      | 1      | o          | o        | TAN          | Tangent of TOS, Result in TOS.                                                                                               |  |  |  |  |  |

| sr       | ŏ      | ŏ                                      | ŏ      | ŏ      | 1      | ŏ          | 1        | ASIN         | Inverse Sine of TOS, Result in TOS.                                                                                          |  |  |  |  |  |

| sr       | 0      | 0                                      | 0      | 0      | 1      | 1          | 0        | ACOS         | Inverse Cosine of TOS. Result in TOS.                                                                                        |  |  |  |  |  |

| sr       | 0      | 0                                      | 0      | 0      | 1      | 1          | 1        | ATAN         | Inverse Tangent of TOS. Result in TOS.                                                                                       |  |  |  |  |  |

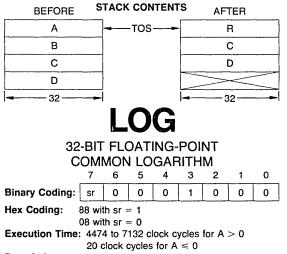

| sr       | 0      | 0                                      | 0      | 1      | 0      | 0          | 0        | LOG          | Common Logarithm (base 10) of TOS. Result in TOS.                                                                            |  |  |  |  |  |

| sr       | 0      | 0                                      | 0      | 1      | 0      | 0          |          | LN           | Natural Logarithm (base e) of TOS. Result in TOS.                                                                            |  |  |  |  |  |

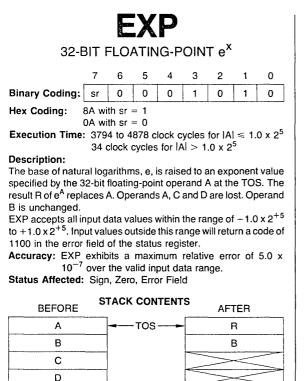

| sr       | 0      | 0<br>0                                 | 0      | 1      | 0      | 1          | 0        | EXP<br>PWB   | Exponential (e <sup>x</sup> ) of TOS. Result in TOS.<br>NOS raised to the power in TOS. Result in NOS. Pop Stack.            |  |  |  |  |  |

| sr       | 0      | 0                                      | 0      |        |        | L <b>.</b> |          |              |                                                                                                                              |  |  |  |  |  |

| — 1      |        |                                        |        |        |        |            |          |              |                                                                                                                              |  |  |  |  |  |

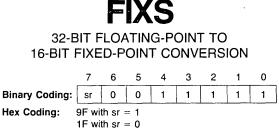

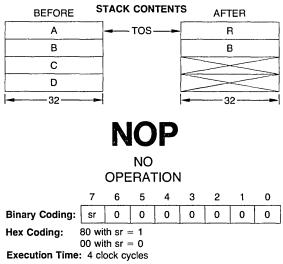

| sr       | 0<br>0 | 0<br>0                                 | 0      | 0      | 0      | 0          | 0        | NOP<br>FIXS  | No Operation<br>Convert TOS from floating point to 16-bit fixed point format.                                                |  |  |  |  |  |

| sr<br>sr | 0      | 0                                      | 1      | 1      | 1      |            | 0        | FIXD         | Convert TOS from floating point to 32-bit fixed point format.                                                                |  |  |  |  |  |

| sr       | ŏ      | õ                                      | 1      | 1      | 1      | o          | 1        | FLTS         | Convert TOS from 16-bit fixed point to floating point format.                                                                |  |  |  |  |  |

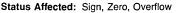

| sr       | ŏ      | ŏ                                      | 1      | 1      | 1      | ō          | o        | FLTD         | Convert TOS from 32-bit fixed point to floating point format.                                                                |  |  |  |  |  |

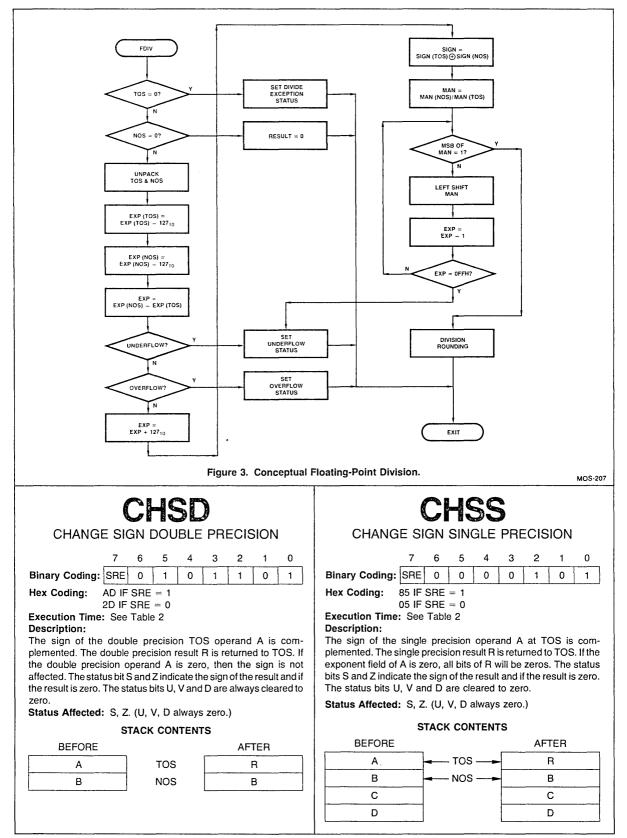

| sr       | 1      | 1                                      | 1      | ò      | 1      | 0          | 0        | CHSS         | Change sign of 16-bit fixed point operand on TOS.                                                                            |  |  |  |  |  |

| sr       | 0      | 1                                      | 1      | 0      | 1      | 0          | 0        | CHSD         | Change sign of 32-bit fixed point operand on TOS.                                                                            |  |  |  |  |  |

| sr       | 0      | 0                                      | 1      | 0      | 1      | 0          | 1        | CHSF         | Change sign of floating point operand on TOS.                                                                                |  |  |  |  |  |

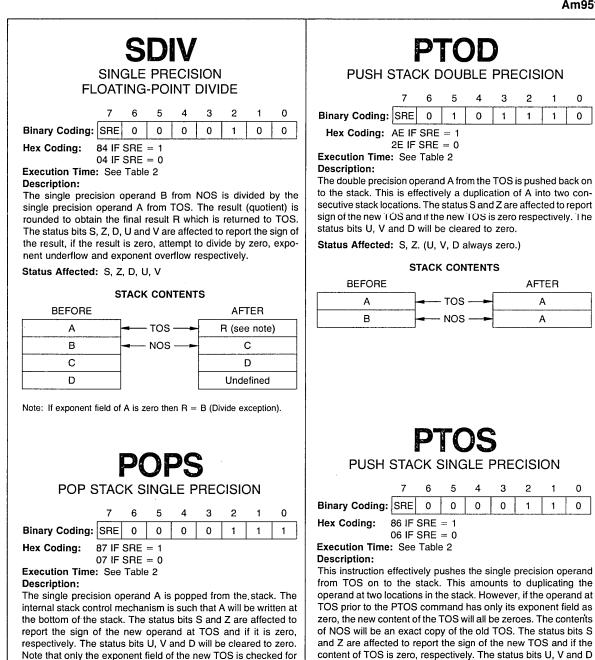

| sr       | 1      | 1                                      | 1      | 0      | 1      | 1          | 1        | PTOS         | Push 16-bit fixed point operand on TOS to NOS (Copy)                                                                         |  |  |  |  |  |

| sr       | 0      | 1                                      | 1      | 0      | 1      | 1          | 1        | PTOD         | Push 32-bit fixed point operand on TOS to NOS. (Copy)                                                                        |  |  |  |  |  |

| sr       | 0      | 0                                      | 1      | 0      | 1      | 1          | 1        | PTOF         | Push floating point operand on TOS to NOS. (Copy)                                                                            |  |  |  |  |  |

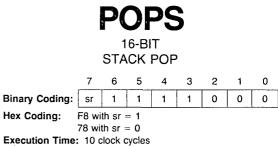

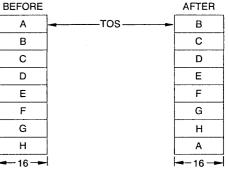

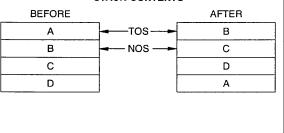

| sr       | 1<br>0 | 1                                      |        | 1      | 0      | 0          | 0        | POPS<br>POPD | Pop 16-bit fixed point operand from TOS. NOS becomes TOS.<br>Pop 32-bit fixed point operand from TOS. NOS becomes TOS.       |  |  |  |  |  |

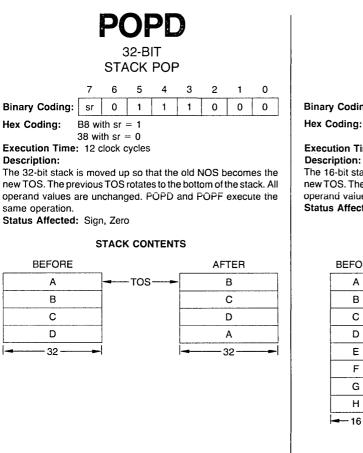

| sr<br>sr | 0      | 1<br>0                                 | 1      |        | 0      | 0          | 0        | POPD         | Pop 32-bit fixed point operand from TOS. NOS becomes TOS.<br>Pop floating point operand from TOS. NOS becomes TOS.           |  |  |  |  |  |

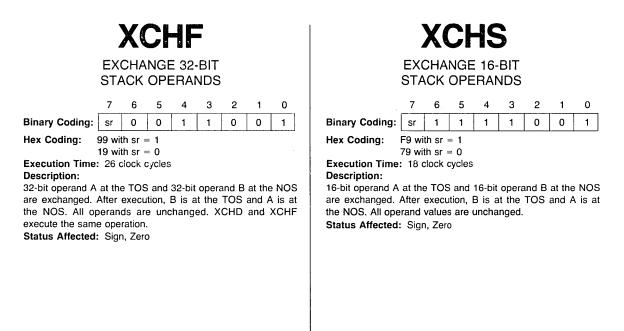

| sr<br>sr | 1      | 1                                      | 1      |        | o      | 0          | 1        | XCHS         | Exchange 16-bit fixed point operands TOS and NOS.                                                                            |  |  |  |  |  |

| sr       | ò      | 1                                      | 1      | 1      | 0      | o          |          | XCHD         | Exchange 32-bit fixed point operands TOS and NOS.                                                                            |  |  |  |  |  |

| sr       | ŏ      | ò                                      | 1      | 1      | ŏ      | ŏ          | i        | XCHF         | Exchange floating point operands TOS and NOS.                                                                                |  |  |  |  |  |

| sr       | ō      | Ō                                      | 1      | 11     | 0      | 1          | Ó        | PUPI         | Push floating point constant " $\pi$ " onto TOS. Previous TOS becomes NOS.                                                   |  |  |  |  |  |

#### NOTES:

- 1. TOS means Top of Stack. NOS means Next on Stack.

- AMD Application Brief "Algorithm Details for the Am9511A APU" provides detailed descriptions of each command function, including data ranges, accuracies, stack configurations, etc.

- Many commands destroy one stack location (bottom of stack) during development of the result. The derived functions may destroy several stack locations. See Application Brief for details.

- 4. The trigonometric functions handle angles in radians, not degrees.

- 5. No remainder is available for the fixed-point divide functions.

- 6. Results will be undefined for any combination of command coding bits not specified in this table.

#### COMMAND INITIATION

After properly positioning the required operands on the stack, a command may be issued. The procedure for initiating a command execution is as follows:

- 1. Enter the appropriate command on the DB0-DB7 lines.

- 2. Establish HIGH on the C/D input.

- 3. Establish LOW on the CS input.

- Establish LOW on the WR input after an appropriate set up time (see timing diagrams).

- 5. Sometime after the HIGH to LOW level transition of WR input, the PAUSE output will become LOW. After a delay of TPPWW, it will go HIGH to acknowledge the write operation. The WR input can return to HIGH anytime after PAUSE going HIGH. The DB0-DB7, C/D and CS inputs are allowed to change after the hold time requirements are satisfied (see timing diagram).

An attempt to issue a new command while the current command execution is in progress is allowed. Under these circumstances, the PAUSE output will not go HIGH until the current command execution is completed.

#### **OPERAND ENTRY**

The Am9511A commands operate on the operands located at the TOS and NOS and results are returned to the stack at NOS and then popped to TOS. The operands required for the Am9511A are one of three formats – single precision fixed-point (2 bytes), double precision fixed-point (4 bytes) or floating-point (4 bytes). The result of an operation has the same format as the operands except for float to fix or fix to float commands.

Operands are always entered into the stack least significant byte first and most significant byte last. The following procedure must be followed to enter operands onto the stack:

- 1. The lower significant operand byte is established on the DB0-DB7 lines.

- A LOW is established on the C/D input to specify that data is to be entered into the stack.

- 3. The  $\overline{CS}$  input is made LOW.

- After appropriate set up time (see timing diagrams), the WR input is made LOW. The PAUSE output will become LOW.

- 5. Sometime after this event, the PAUSE will return HIGH to indicate that the write operation has been acknowledged.

- Anytime after the PAUSE output goes HIGH the WR input can be made HIGH. The DB0-DB7, C/D and CS inputs can change after appropriate hold time requirements are satisfied (see timing diagrams).

The above procedure must be repeated until all bytes of the operand are pushed into the stack. It should be noted that for single precision fixed-point operands 2 bytes should be pushed and 4 bytes must be pushed for double precision fixed-point or floating-point. Not pushing all the bytes of a quantity will result in byte pointer misalignment.

The Am9511A stack can accommodate 8 single precision fixed-point quantities or 4 double precision fixed-point or floating-point quantities. Pushing more quantities than the capacity of the stack will result in loss of data which is usual with any LIFO stack.

#### DATA REMOVAL

Result from an operation will be available at the TOS. Results can be transferred from the stack to the data bus by reading the stack. When the stack is popped for results, the most significant byte is available first and the least significant byte last. A result is always of the same precision as the operands that produced it except for format conversion commands. Thus when the result is taken from the stack, the total number of bytes popped out should be appropriate with the precision – single precision results are 2 bytes and double precision and floating-point results are 4 bytes. The following procedure must be used for reading the result from the stack:

- 1. A LOW is established on the  $C/\overline{D}$  input.

- 2. The  $\overline{CS}$  input is made LOW.

- After appropriate set up time (see timing diagrams), the RD input is made LOW. The PAUSE will become LOW.

- Sometime after this, PAUSE will return HIGH indicating that the data is available on the DB0-DB7 lines. This data will remain on the DB0-DB7 lines as long as the RD input remains LOW.

- 5. Anytime after PAUSE goes HIGH, the RD input can return HIGH to complete transaction.

- The CS and C/D inputs can change after appropriate hold time requirements are satisfied (see timing diagram).

- Repeat this procedure until all bytes appropriate for the precision of the result are popped out.

Reading of the stack does not alter its data; it only adjusts the byte pointer. If more data is popped than the capacity of the stack, the internal byte pointer will wrap around and older data will be read again, consistent with the LIFO stack.

#### STATUS READ

The Am9511A status register can be read without any regard to whether a command is in progress or not. The only implication that has to be considered is the effect this might have on the END output discussed in the signal descriptions.

The following procedure must be followed to accomplish status register reading.

- 1. Establish HIGH on the  $C/\overline{D}$  input.

- 2. Establish LOW on the CS input.

- After appropriate set up time (see timing diagram) RD input is made LOW. The PAUSE will become LOW.

- Sometime after the HIGH to LOW transition of RD input, the PAUSE will become HIGH indicating that status register contents are available on the DB0-DB7 lines. The status data will remain on DB0-DB7 as long as RD input is LOW.

- 5. The RD input can be returned HIGH anytime after PAUSE goes HIGH.

- The C/D input and CS input can change after satisfying appropriate hold time requirements (see timing diagram).

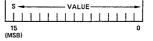

#### DATA FORMATS

The Am9511A Arithmetic Processing Unit handles operands in both fixed-point and floating-point formats. Fixed-point operands may be represented in either single (16-bit operands) or double precision (32-bit operands), and are always represented as binary, two's complement values.

#### **16-BIT FIXED-POINT FORMAT**

#### 32-BIT FIXED-POINT FORMAT

| s           |      |   |   |   |   |   |   |   |   | <br>VA |     | 15- |   |   |   |   |   |   |   |   |   |   | _ |

|-------------|------|---|---|---|---|---|---|---|---|--------|-----|-----|---|---|---|---|---|---|---|---|---|---|---|

| L           |      | 1 | I | ł | L | I | 1 | L | 1 | 1      | ÷., |     |   | 1 | I | 1 | L | 1 | 1 | 1 | 1 | 1 | ī |

| 31<br>(MSB) | <br> |   |   |   |   |   |   |   |   | <br>   |     |     | _ |   |   |   |   |   |   |   |   |   | 0 |

The sign (positive or negative) of the operand is located in the most significant bit (MSB). Positive values are represented by a sign bit of zero (S = 0). Negative values are represented by the two's complement of the corresponding positive value with a sign bit equal to 1 (S = 1). The range of values that may be accommodated by each of these formats is -32,768 to +32,767 for single precision and -2,147,483,648 to +2,147,483,647 for double precision.

Floating point binary values are represented in a format that permits arithmetic to be performed in a fashion analogous to operations with decimal values expressed in scientific notation.

$$(5.83 \times 10^2)(8.16 \times 10^1) = (4.75728 \times 10^4)$$

In the decimal system, data may be expressed as values between 0 and 10 times 10 raised to a power that effectively shifts the implied decimal point right or left the number of places necessary to express the result in conventional form (e.g., 47,572.8). The value-portion of the data is called the mantissa. The exponent may be either negative or positive.

The concept of floating point notation has both a gain and a loss associated with it. The gain is the ability to represent the significant digits of data with values spanning a large dynamic range limited only by the capacity of the exponent field. For example, in decimal notation if the exponent field is two digits wide, and the mantissa is five digits, a range of values (positive or negative) from 1.0000 x  $10^{-99}$  to 9.9999 x  $10^{+99}$  can be accommodated. The loss is that only the significant digits of the value can be represented. Thus there is no distinction in this representation between the values 123451 and 123452, for example, since each would be expressed as: 1.2345 x 10<sup>5</sup>. The sixth digit has been discarded. In most applications where the dynamic range of values to be represented is large, the loss of significance, and hence accuracy of results, is a minor consideration. For greater precision a fixed point format could be chosen, although with a loss of potential dynamic range.

The Am9511 is a binary arithmetic processor and requires that floating point data be represented by a fractional mantissa value between .5 and 1 multiplied by 2 raised to an appropriate power. This is expressed as follows:

value = mantissa x 2<sup>exponent</sup>

For example, the value 100.5 expressed in this form is 0.11001001 x  $2^7$ . The decimal equivalent of this value may be computed by summing the components (powers of two) of the mantissa and then multiplying by the exponent as shown below:

value =

$$(2^{-1} + 2^{-2} + 2^{-5} + 2^{-8}) \times 2^7$$

=  $(0.5 + 0.25 + 0.03125 + 0.00290625) \times 128$

=  $0.78515625 \times 128$

=  $100.5$

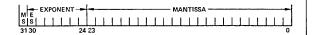

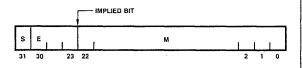

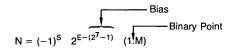

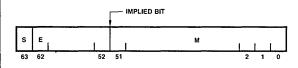

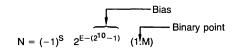

#### FLOATING POINT FORMAT

The format for floating-point values in the Am9511A is given below. The mantissa is expressed as a 24-bit (fractional) value; the exponent is expressed as an unbiased two's complement 7-bit value having a range of -64 to +63. The most significant bit is the sign of the mantissa (0 = positive, 1 = negative), for a total of 32 bits. The binary point is assumed to be to the left of the most significant mantissa bit (bit 23). All floating-point data values must be normalized. Bit 23 must be equal to 1, except for the value zero, which is represented by all zeros.

The range of values that can be represented in this format is  $\pm(2.7\times10^{-20}$  to 9.2  $\times10^{18})$  and zero.

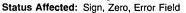

#### STATUS REGISTER

The Am9511A contains an eight bit status register with the following bit assignments:

| BUSY | SIGN | ZERO |   | ERROF | RCODE |   | CARRY |

|------|------|------|---|-------|-------|---|-------|

| 7    | 6    | 5    | 4 | 3     | 2     | 1 | 0     |

- BUSY: Indicates that Am9511A is currently executing a command (1 = Busy).

- SIGN: Indicates that the value on the top of stack is negative (1 = Negative).

- ZERO: Indicates that the value on the top of stack is zero (1 = Value is zero).

ERROR This field contains an indication of the validity of the

- CODE: result of the last operation. The error codes are:

- 0000 No error

- 1000 Divide by zero

- 0100 Square root or log of negative number

- 1100 Argument of inverse sine, cosine, or e<sup>x</sup> too large

- XX10 Underflow

- XX01 Overflow

- CARRY: Previous operation resulted in carry or borrow from most significant bit. (1 = Carry/Borrow, 0 = No Carry/No Borrow)

If the BUSY bit in the status register is a one, the other status bits are not defined; if zero, indicating not busy, the operation is complete and the other status bits are defined as given above. ÷.

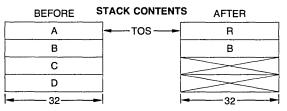

| Command<br>Mnemonic | Hex Code<br>(sr = 1) | Hex Code<br>(sr = 0) | Execution<br>Cycles | Summary<br>Description                                                |

|---------------------|----------------------|----------------------|---------------------|-----------------------------------------------------------------------|

|                     |                      | . <u></u>            | 16-BIT FIXED        | POINT OPERATIONS                                                      |

| SADD                | EC                   | 6C                   | 16-18               | Add TOS to NOS. Result to NOS. Pop Stack.                             |

| SSUB                | ED                   | 6D                   | 30-32               | Subtract TOS from NOS. Result to NOS. Pop Stack.                      |

| SMUL                | EE                   | 6E                   | 84-94               | Multiply NOS by TOS. Lower result to NOS. Pop Stack.                  |

| SMUU                | F6                   | 76                   | 80-98               | Multiply NOS by TOS. Upper result to NOS. Pop Stack.                  |

| SDIV                | EF                   | 6F                   | 84-94               | Divide NOS by TOS. Result to NOS. Pop Stack.                          |

|                     |                      |                      | 32-BIT FIXED        | POINT OPERATIONS                                                      |

| DADD                | AC                   | 2C                   | 20-22               | Add TOS to NOS. Result to NOS. Pop Stack.                             |

| DSUB                | AD                   | 2D                   | 38-40               | Subtract TOS from NOS. Result to NOS. Pop Stack.                      |

| DMUL                | AE                   | 2E                   | 194-210             | Multiply NOS by TOS. Lower result to NOS. Pop Stack.                  |

| DMUU                | B6                   | 36                   | 182-218             | Multiply NOS by TOS. Upper result to NOS. Pop Stack.                  |

| DDIV                | AF                   | 2F                   | 196-210             | Divide NOS by TOS. Result to NOS. Pop Stack.                          |

|                     |                      | 32-BI                | T FLOATING-PC       | DINT PRIMARY OPERATIONS                                               |

| FADD                | 90                   | 10                   | 54-368              | Add TOS to NOS. Result to NOS. Pop Stack.                             |

| FSUB                | 91                   | 11                   | 70-370              | Subtract TOS from NOS. Result to NOS. Pop Stack.                      |

| FMUL                | 92                   | 12                   | 146-168             | Multiply NOS by TOS. Result to NOS. Pop Stack.                        |

| FDIV                | 93                   | 13                   | 154-184             | Divide NOS by TOS. Result to NOS. Pop Stack.                          |

|                     |                      | 32-B                 | T FLOATING-PC       | DINT DERIVED OPERATIONS                                               |

| SQRT                | 81                   | 01                   | 782-870             | Square Root of TOS. Result to TOS.                                    |

| SIN                 | 82                   | 02                   | 3796-4808           | Sine of TOS. Result to TOS.                                           |

| cos                 | 83                   | 03                   | 3840-4878           | Cosine of TOS. Result to TOS.                                         |

| TAN                 | 84                   | 04                   | 4894-5886           | Tangent of TOS. Result to TOS.                                        |

| ASIN                | 85                   | 05                   | 6230-7938           | Inverse Sine of TOS. Result to TOS.                                   |

| ACOS                | 86                   | 06                   | 6304-8284           | Inverse Cosine of TOS. Result to TOS.                                 |

| ATAN                | 87                   | 07                   | 4992-6536           | Inverse Tangent of TOS. Result to TOS.                                |

| LOG                 | 88                   | 08                   | 4474-7132           | Common Logarithm of TOS. Result to TOS.                               |