ADVANCED MICRO DEVICES

#

# **Advanced Micro Devices**

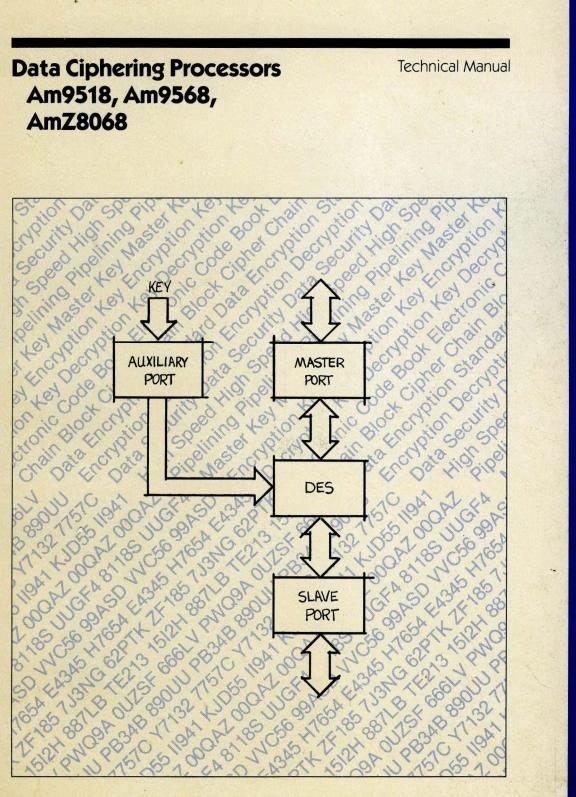

# Am9518/AmZ8068/Am9568 Data Ciphering Processors

# **Technical Manual**

© 1984 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

> > Printed in U.S.A.

#### ACKNOWLEDGEMENTS:

This technical manual was written by Juergen Stelbrink, Headquarters Applications Engineer.

Chapter 4.12 HIGH SPEED SERIAL DATA CIPHERING IN NETWORK SYSTEMS was contributed by Al Sussman, Field Applications Engineer in Burlington, Massachusetts.

| TABLE OF CON | IТ | EN | тs |

|--------------|----|----|----|

|--------------|----|----|----|

| 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 2. DATA CIPHERING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                                                                                   |

| <ul><li>2.1. DATA ENCRYPTION STANDARD</li><li>2.2. PUBLIC/PRIVATE KEY SYSTEM</li><li>2.3. THE DCP FAMILY</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9<br>14<br>15                                                                                                       |

| 3. FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21                                                                                                                  |

| <pre>3.1. PORTS<br/>3.1.1 Master Port<br/>3.1.2 Slave Port<br/>3.1.3. Auxiliary Port<br/>3.1.4 Key and Data Load in Direct Control M<br/>3.2. REGISTERS<br/>3.3. COMMANDS<br/>3.4. PARITY CHECKING OF KEYS<br/>3.5. INITIALIZATION<br/>3.6. MULTIPLEXED CONTROL MODE<br/>3.6.1. ECB Operation<br/>3.6.2. CBC Operation<br/>3.6.3. CFB Operation<br/>3.7. DIRECT CONTROL MODE<br/>3.7.1. ECB Operation<br/>3.7.2. CBC and CFB Operation<br/>3.8. OUTPUT FEEDBACK AND ONE-BIT CFB<br/>3.9. THROUGHPUT<br/>3.10 KEY TRANSFER VIA THE COMMUNICATION LINK</pre> | 21<br>24<br>25<br>10de 28<br>33<br>38<br>39<br>41<br>41<br>41<br>44<br>45<br>45<br>45<br>45<br>48<br>49<br>51<br>55 |

| 4. INTERFACES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57                                                                                                                  |

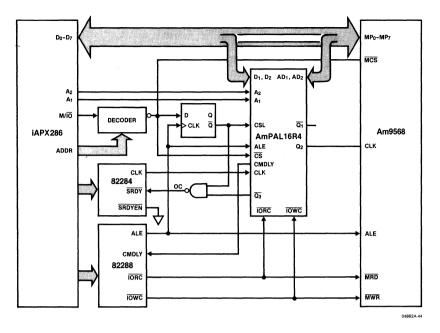

| <ul> <li>4.1. 8086 - Am9518/AmZ8068/Am9568</li> <li>4.2. iAPX186 - AmZ8068</li> <li>4.3. iAPX286 - Am9568</li> <li>4.4. 68000 - AmZ8068</li> <li>4.5. Z8000 - Am9518/AmZ8068</li> <li>4.6. Z80 - Am9518/AmZ8068</li> <li>4.7. 8085 - Am9518/AmZ8068</li> <li>4.8. Z80-DMA - Am9568</li> <li>4.9. 8088-DMA - Am28068</li> <li>4.10. iSBX Bus - Am9568</li> <li>4.11. 8051 - Am9518/AmZ8068</li> <li>4.12. HIGH SPEED SERIAL DATA CIPHERING IN NETWORK</li> </ul>                                                                                            | 61<br>71<br>73<br>79<br>85<br>89<br>101<br>103<br>111<br>119<br>131<br>0RK SYSTEMS 134                              |

| APPENDIXES<br>A. ECB Test Data<br>B. CBC Test Data<br>C. CFB Test Data<br>D. Certification by National Bureau of Standar<br>E. Timing Diagrams<br>F. Literature                                                                                                                                                                                                                                                                                                                                                                                            | 141<br>142<br>:ds 143<br>156<br>158                                                                                 |

Page

#### CHAPTER 1. INTRODUCTION

Cryptography is almost as old as civilization. The human desire for privacy when communicating leads inevitably to cryptography. Webster's Dictionary describes cryptography as: "the art or practice of preparing messages in a form intended to prevent their being read by those not privy to secrets of the form; also: the science of devising methods and means for this". The word cryptography combines the Greek "kryptos" (secret) and "graphos" (writing).

The Spartans established one of the first military cryptographic systems in the fifth century B.C. They developed a simple tool consisting of a strip of parchment wrapped around a staff of wood. The original message was written on the parchment down the length of the staff. Once unwrapped, the message becomes unreadable and can be transferred by messenger to the receiver, who decrypts the message by rewrapping it around a staff of the same thickness. The Spartans used it to transfer secret information during the Persian Wars.

There are two basic kinds of encrypting or ciphering methods: transposition and substitution. Data ciphering by transposition takes the characters of the original message (the plain text) and scrambles them to form the encrypted message (the cipher text). The scrambling changes the position of characters in the text only and not the characters themselves. "CIPHER" written as "HCERPI" is an example of transposition ciphering.

The substitution method replaces each character of the original text by another character, number or special symbol. Julius Caesar designed a cryptographic algorithm where the characters were shifted a fixed number of positions; for a shift of three positions, an "a" becomes a "d" and a "b" becomes an "e". His name is substituted as "Mxolxv Fdhvdu". He employed this algorithm to protect an exchange of letters with Cicero during the Gallic Wars.

The fundamental weakness of Caesar's algorithm is that it always encrypts the same letter in the same manner. Codebreaking techniques introduced in the second half of the nineteenth century take advantage of the fact that each language has its own character frequency spectrum. The most common letter in the English language is the "e"; the most frequently recurring double letters are "th". Spectrum analysis can easily break Caesar's code.

More sophisticated algorithms developed in the Renaissance eliminated the weakness of Caesar's code. The encrypted character becomes a function of the original character and its position in the text. The same character in two different text locations is replaced by different encrypted characters.

German intelligence in World War I employed a code where a list of words organized in a dictionary were linked to a set of numbers. The linkage was not organized in numerical or alphabetical order; it was a giant substitution. In January 1917, the German Foreign Minister, A. Zimmermann, sent a top-secret encrypted telegram to his ambassador in Washington. The British Post Office intercepted this wireless telegram and sent it to the codebreaking branch of British Naval Intelligence. The decoding of the "Zimmermann telegram" was probably the most important single codebreaking task in intelligence history. It caused the United States to join the war.

Until the early Sixties, most cryptographic equipment was based on complicated machines consisting of many mechanical disks and gears. Today, the use of electronic devices increased the capabilities of cryptography. The algorithms are now more sophisticated; but, on the other hand, cryptoanalysts are also able to break more sophisticated codes using computers.

The extensive use of data communication over radio or telephone lines makes it easy for someone to listen to masses of sensitive information without being detected. Great quantities of confidential data, stored on disks or transmitted over various communication links, need protection from unauthorized access. Using any home computer with a modem, an outsider can dial many phone numbers automatically to find a connection where a computer system answers. By trying random passwords he might then gain access to the system, but this access would be worthless if the sensitive data were stored in encrypted form.

A U.S. government department, the National Bureau of Standards, developed an algorithm designed to protect sensitive computer data. Advanced Micro Devices implemented this algorithm into silicon. The result, the Data Ciphering Processor (DCP), is a one-chip 40-pin LSI device, best suited for use in high-speed electronic data ciphering systems and certified by the National Bureau of Standards. The two major application areas of this device are:

- to protect mass data storage (files on tape or disk),

- to protect data communication links to keep the transferred information private (voice encryption, home banking, bank tellers, satellite communication).

This handbook is organized into three parts. First, it gives the reader an overview about data ciphering in general and the DES algorithm supported by the DCP in particular. Differences between two cryptography systems, the public and the private key system, are discussed. Further, it outlines the differences between the three members of the AMD DCP family.

Chapter 3 provides a detailed description of all features and functions of the DCP. It introduces the reader to the internal structure of the DCP and explains the data ciphering instruction set. Timing information can be found in Appendix E. Detailed program flowcharts show the operation of the DCP in the different modes.

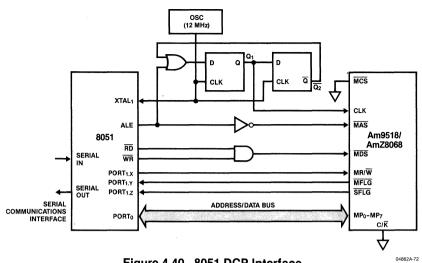

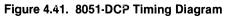

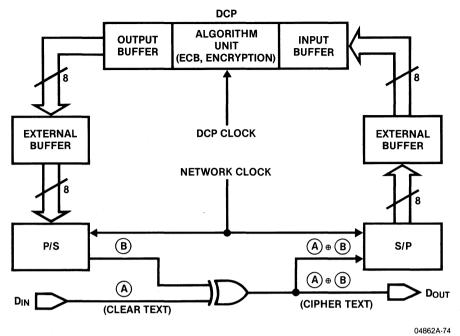

Chapter 4 addresses the system designer, providing hints and ideas for designing the DCP into a specific system environment. It shows interfaces to most 8-bit and 16-bit microprocessors. Chapter 4.11 shows what is probably the simplest data ciphering system. It consists of a microcomputer and a DCP built in a "black box". This box provides data ciphering inserted in a serial communication line, for example between a terminal and a modem. Chapter 4.12 shows an application of the DCP in highspeed, serial data-communication environments such as Ethernet.

7

#### CHAPTER 2. DATA CIPHERING

The data ciphering algorithm supported by the DCP was tested and accepted by the US government. The technique works by passing original data through a circuit whose output is a complex, nonlinear function of the data and a user-supplied, 56-bit key, involving XORing, substitution, block swapping, and key subset selection. The resultant encoded data is called "cipher text".

It is virtually impossible to regenerate the original data without knowing the key. The DES specifies that the algorithm be implemented in hardware rather than software for maximum security. The DCP can execute both encryption and decryption. The device can hold three different keys: one for encryption, one to decrypt a received encoded message and a third one called Master Key to generate session keys or to transfer keys over the line. Refer to Chapter 3.2 (Master Key Register) for more information about the usage of the Master Key. Each key is entered into the DCP as a series of eight bytes, each byte consisting of seven key bits and one parity bit. The chip checks the parity on each byte of the key as entered. To enhance system security, the keys cannot be read back.

The DCP supports three data encryption modes to satisfy the requirements of most applications. Electronic Code Book (ECB) is best suited for high-speed disk applications. Chain Block Cipher (CBC) provides an extra degree of data security over ECB in that it detects any insertion or deletion in the cipher text. It also implements one of the basic cryptography rules: Never encode the same message the same way twice. Data ciphering in disk applications cannot follow this rule because it requires that records be decrypted randomly. The third data ciphering mode is Cipher Feedback (CFB). It is designed for medium-speed, character-based applications. Data is handled on a byte-by-byte basis without waiting to form 64-bit blocks, as in the other two methods.

#### 2.1 DATA ENCRYPTION STANDARD

In January 1977, the National Bureau of Standards published a Data Encryption Standard (DES) in the Federal Information Processing Standards Publication (FIPS PUB 46). The DES specifies an algorithm to be implemented in electronic hardware devices to protect computer data cryptographically. That publication provides a complete description of the mathematical background of the DES algorithm.

Although the DES encryption/decryption algorithm is public information, the individual privacy is insured with a private key. The user can chose any 56-bit key; thus, he can select one of 7.2 x  $10^{16}$  possible keys. The same key is used for encryption and decryption. The DES is a private key system.

9

The DES algorithm takes a data block through 18 data-manipulation stages. Sixteen of these stages are identical. They execute complex series of bit manipulations depending on the key.

The first and the last stage do only simple bit transpositions. This overview of the internal operation makes it obvious that this algorithm is well-suited for implementation in electronic hardware.

The DES algorithm translates a 64-bit binary block into a unique 64-bit output block. It is important for some applications that this ciphering algorithm does not add information. Input and output blocks have the same length. Each bit of the result is a function of each and any bit of the input data as well as the key. In other words, a change of any single input bit has approximately equal probability of changing any output bit.

The National Bureau of Standards has defined four implementations of the DES algorithm to be used in a wide variety of applications. These implementations are called Modes of Operation.

Advanced Micro Devices' Data Ciphering Processor was certified by the National Bureau of Standards in January 1981 (see Appendix D). The DCP has passed the DES test and 4 million iterations of the Monte Carlo test. (Since the DES is a complex nonlinear algorithm, it cannot be fully tested with a limited set of test vectors. To verify the correct hardware implementation, the National Bureau of Standards has created a statistical procedure -- the Monte Carlo routine.)

#### Modes of Operation

The National Bureau of Standards has defined four implementations of the DES algorithm. Each of them is designed for specific applications.

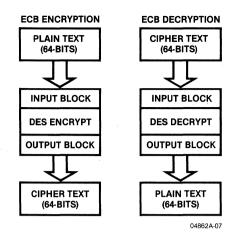

ECB The Electronic Code Book (Figure 2.1) is a direct implementation of the DES algorithm. The analogy to a code book arises because the same plain text always generates the same ciphered text for a given cryptographic key. The DCP determines the codebook entries each time. A single bit error or change, in either the input text block or the key, causes an average bit error rate of 50% for its output block. However, an error in one text block will not affect any other block. In other words, there is no error extention between ECB blocks.

The input and output block size is 64 bits. Since data blocks are independently ciphered, this mode is qualified for disk applications.

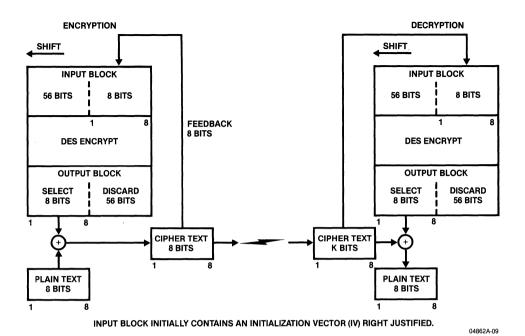

Figure 2.3. 8-Bit Cipher Feedback (CFB) Mode

04862A-10

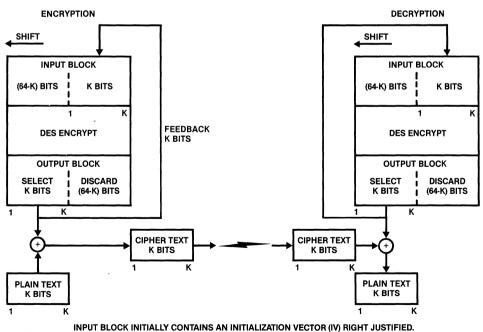

### Figure 2.4. K-Bit Output Feedback (OFB) Mode

The ECB mode has the weakness that identical blocks of plain text generate identical blocks of ciphered text. This violates one of the basic laws of encryption security: Never encrypt information the same way twice because this makes it easier for the opponent to break the code. This problem is solved by the CBC mode.

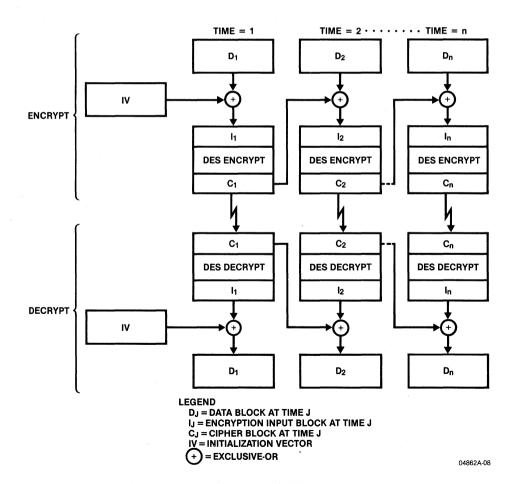

- CBC Chain Block Cipher (Figure 2.2) also operates on 64-bit data blocks. The input data block is EXORed with an 64bit Initial Vector (IV) before being processed by the DES algorithm. The resulting ciphered-output block is loaded into the IV Register, to be ORed with the next input block. This chaining of cipher text blocks provides different outputs for identical input blocks. It also gives an error extention characteristic which protects against fraudulent data insertion, deletion or alteration in a block sequence. A one-bit error in the input text block, the key or the Initial Vector causes an average error rate of 50% in all subsequent output blocks. These features make CBC best suited for high-speed data communications.

- CFB Cipher Feedback (Figure 2.3) operates on n-bit data blocks, "n" being any value from 1 to 64. The content of the IV Register is processed by the DES algorithm. The most significant n-bits of the result are EXORed with the n-bit input data block. The result is the n-bit ciphered output block. This output block is shifted into the "n" least significant bits of the IV Register.

The DCP supports 8-bit CFB. Character-based, low-speed to medium-speed data communications is best done by 8-bit CFB. In CFB Mode, the throughput of the DCP is lower than in CBC or ECB because each algorithm pass provides only 8 bits compared to 64 bits in the two high-speed modes.

The error extention characteristic is the same as in CBC.

OFB Under some circumstances, such as a noisy, narrowband digital signal in an encrypted speech application, it is best to use a data-independent stream cipher. Output Feedback (Figure 2.4) is the best technique in this environment. The advantage of OFB is that the output data is a function of only the input data and the number of preceding blocks. It is independent of the actual data contained in the blocks. An error in an input block causes a 50% bit error probability in its output block, but it does not influence subsequent outputs. There is no error extention.

> OFB differs from CFB in that the feedback path is dataindependent; a part of the output of the DES algorithm is fed back directly. The DES algorithm operates like a pseudo-random number generator.

The DCP does not support OFB directly, but with some external hardware 1-bit and 8-bit OFB can be implemented as shown in Chapter 3.8. No additional hardware is needed to perform 64-bit OFB.

#### 2.2 PUBLIC VERSUS PRIVATE KEY CRYPTOSYSTEMS

The classical single-key cryptosystem, such as DES, operates on the premise that the sender and receiver of messages use the same key for the dual purpose of encryption and decryption. Although such a scheme is adequate for most purposes, it is deficient from the point of view of true "authentication". Authenticity assures that the message has not been tampered with during transmission, and also that the true identity of the sender (also called signature) can be extracted from the encrypted message. In schemes involving sharing of a secret key there is scope for "forgery" since the receiver of a message can generate authenticators that are indistinguishable from those generated by the sender. Furthermore, single-key systems require some form of key distribution prior to activation of the system.

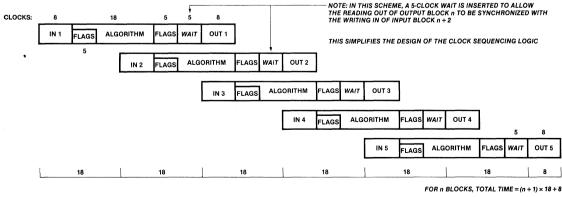

Public key cryptosystems have evolved as an answer to the needs of digital signatures and also to overcome some of the shortcomings of DES. They were first introduced by Diffie and Hellman in 1976. In contrast to DES, these systems use a matched pair of keys (one private and the other public) for the sender and the receiver. Both pairs are generated independently. The private keys are retained by the individual users while their respective public keys are maintained in a common directory possibly managed by a network key server. This scheme separates the encryption and decryption keys. It can transmit encryption messages without prior exchange of keys and can implement digital signatures that are legally binding.

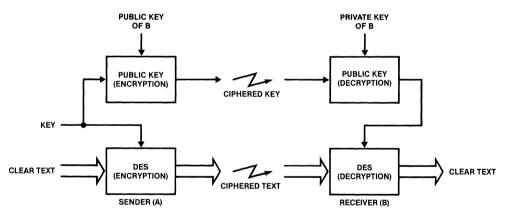

Public key cryptosystems are slow since they involve multipleprecision arithmetic on very large numbers (>100 digits). The functional advantages of a public key cryptosystem can, however, be combined with the advantages of a private key cryptosystem (speed and availability of dedicated VLSI circuits) to form a hybrid system (Figure 2.5).

To transmit a secret text, the sender (A) first generates a random key for encrypting the clear text by means of the fast DES algorithm. The random key is then encrypted using the complicated and slow public key method. Both the encrypted key and text are then transmitted to the receiver. The receiver first decrypts the key and then uses the decrypted key to decrypt the ciphered text. The authenticity of the text can be checked in a second pass.

Splitting the job between the public key and DES algorithm makes sense since the protection of a standard message requires many more DES encryptions than public key encryptions. For more information on Public Key Systems see:

- Burton, C. E. "RSA: A Public Key Cryptography System." Dr. Dobb's Journal, Mar 1984, 16-21.

- Diffie, W. and Hellman, M. "New Directions in Cryptography." IEEE Transactions on Information Theory, IT→22(6), Nov 1976,

- Gardner, M. "Mathematical Games." Scientific American, 237(2), Aug 1977, 120~124

- Mueller-Schloer, Christian. "A Microprocessor-based Cryptoprocessor". IEEE Micro, Oct 1983, 5-15.

- Rivest, R.L., A. Shamir and L. Adleman. "A Method for Obtaining Digital Signatures and Public-Key Cryptosystems." Communications of the ACM, 21(2), Feb 1978, 120-126.

04862A-11

#### Figure 2.5. Hybrid System

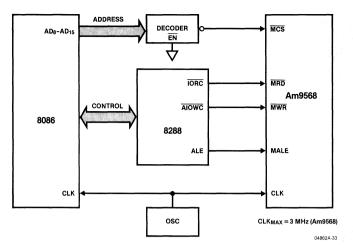

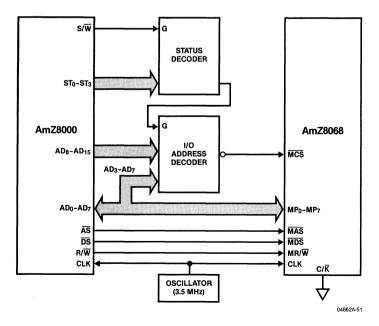

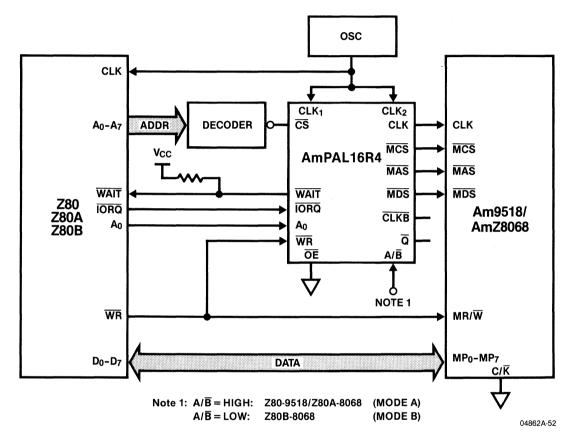

#### 2.3. THE DCP FAMILY

The DCP family consists of three devices:

Am9518 3-MHz version, Z8000\*-type bus interface up to 1.3 Mbyte/s ciphering throughput

AmZ8068\* 4-MHz version, Z8000-type bus interface up to 1.7 Mbyte/s ciphering throughput

Am9568 4-MHz version, 8086-type bus interface up to 1.5 Mbyte/s ciphering throughput

\*Z8000 is a trademark of Zilog, Inc. \*AmZ8068 is a trademark of Advanced Micro Devices, Inc.

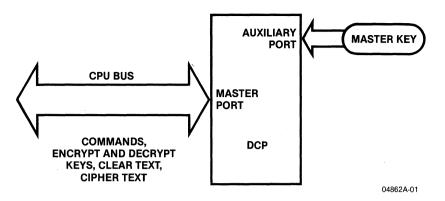

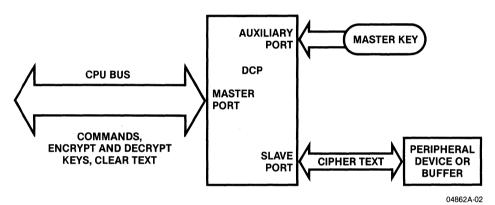

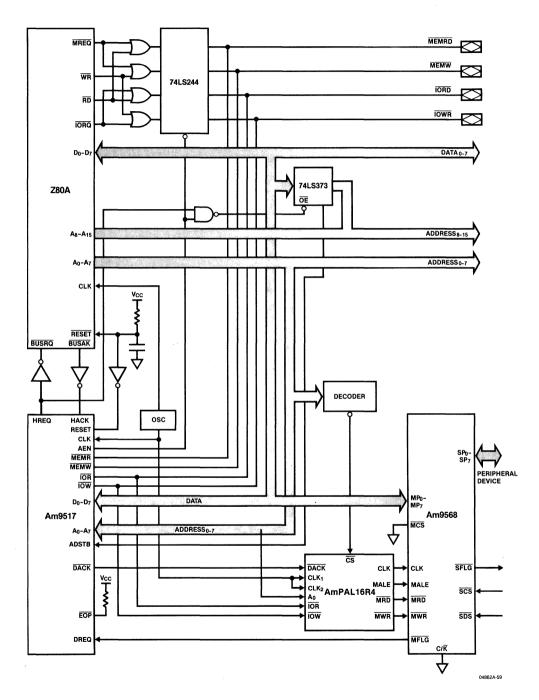

Figure 2.6. Data Flow for Single Port Configuration, Multiplexed Control Mode

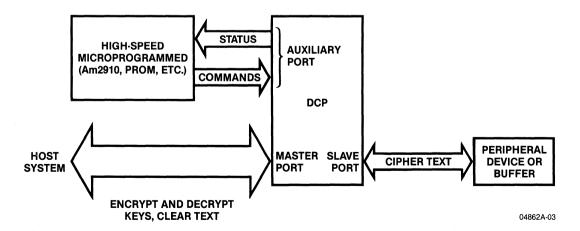

Figure 2.7. Data Flow for Dual Port Configuration, Multiplexed Control Mode

Figure 2.8. Data Flow for Dual Port Configuration, Direct Control Mode

#### General Description Applicable to All Three Devices

All three devices are designed to be used in a large variety of environments, including dedicated controllers, communication concentrators, terminals and peripheral task processors in general processor systems. Usually the DCP will be controlled by a standard microprocessor. In this kind of environment, the DCP is interfaced similarly to other peripherals with a multiplexed address/data bus (e.g., AmZ8030, AmZ8036\*, and AmZ8073). This mode is called Multiplexed Control Mode. In data storage applications, the data can be passed from the CPU bus through the DCP to the mass storage controller. Most of the tape or hard disk controllers are based on microprogrammed logic. The DCP can be programmed to provide a special microprogrammed interface. This mode is called Direct Control Mode.

The Multiplexed Control Mode provides a standard microprocessor interface. Chapters 4.1 to 4.11 show applications where the DCP operates in Multiplexed Control Mode. Figure 2.6 shows the most straightforward interface configuration; it is the single port configuration in Multiplexed Control Mode. In this configuration, all commands and data transferred between the CPU and DCP are passed through the Master Port. The keys for encryption and decryption may be entered through either the Master Port or the Auxiliary Port. The Master Key can only be entered through the Auxiliary Port. The Auxiliary Port is a separate port for key input only. It enhances the system security by separating the data path and the key path. Τn higher-speed data ciphering applications, the Master Port becomes the bottleneck of the system. Both the original text and the encrypted text have to be passed through this 8-bit port.

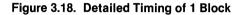

The dual port configuration (Figure 2.7) eliminates this bottleneck. The text now flows through the devices. The CPU passes the original text through the Master Port, while the peripheral device removes the encrypted text from the Slave Port. The internal architecture of the DCP is highly pipelined. The CPU may enter one block of data, while a previously entered block is ciphered and while a third previously ciphered block may be read out. This pipelining yields data ciphering rates between 10.6 and 14.2 Mbit/s.

The **Direct Control Mode** (Figure 2.8) provides a special microprogrammed logic interface. In Direct Control Mode the Auxiliary Port becomes a control port for the microprogrammed logic. Unlike Multiplexed Control Mode, where the DCP is now controlled by programming internal registers, the DCP is controlled by three pins of the Auxiliary Port. Two pins reflect the status of the device. In this mode, the DCP can execute only a subset of its data ciphering commands, such as loading encryption or decryption keys and initiating encryption or decryption.

\*Z8030 and Z8036 are trademarks of Zilog, Inc.

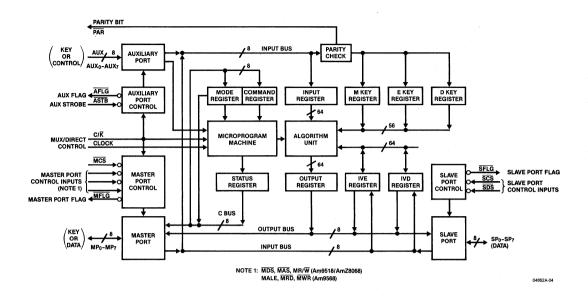

Figure 2.9. DCP Block Diagram

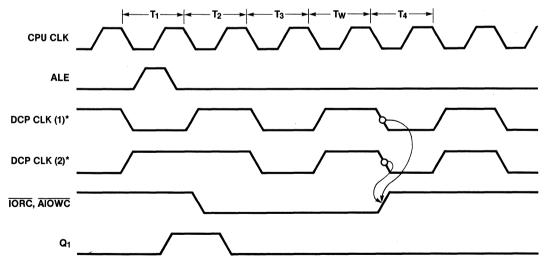

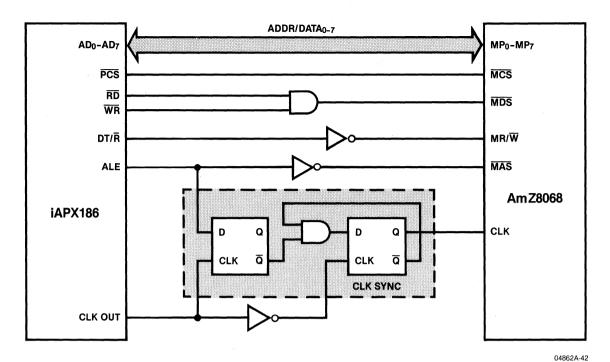

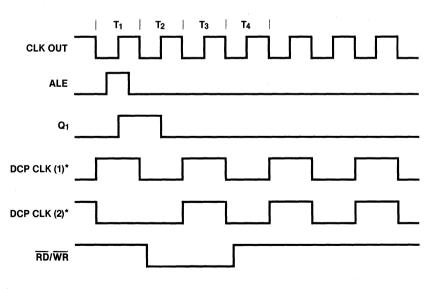

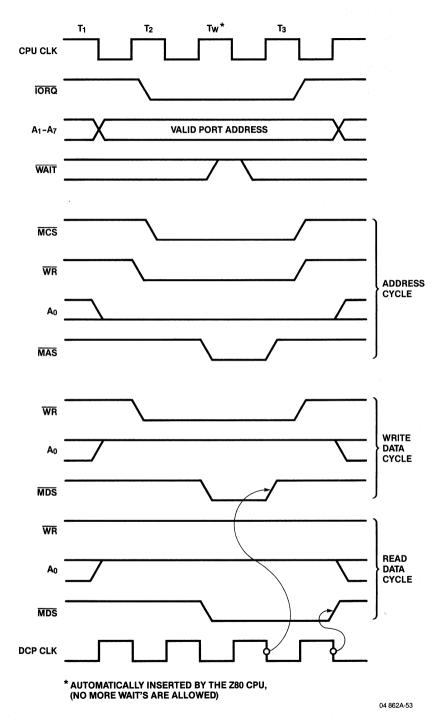

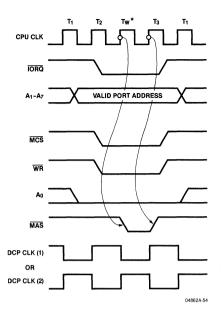

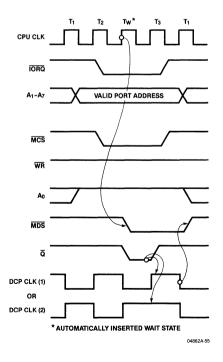

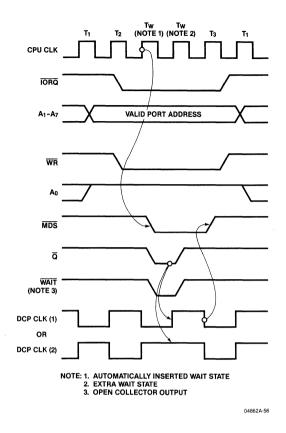

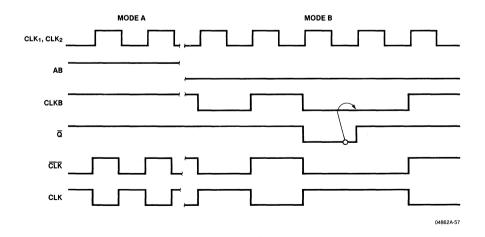

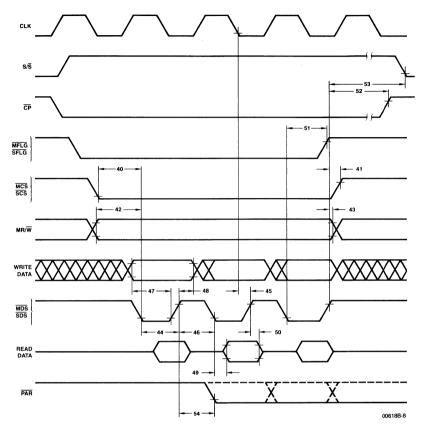

Figure 2.10. Z8000-Type Master Port Timing (Am9518, AmZ8068)

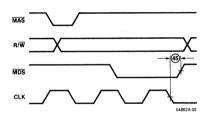

Figure 2.11. 8086-Type Master Port Timing (Am9568)

The Mode Register defines the basic operating parameters such as ciphering mode (ECB, CBC, and CFB) and port configuration. In Direct Control Mode this register cannot be programmed. However, a reset sets this register to its default value (see Chapter 3.5). To operate the DCP in modes different from the default mode, the DCP has to be switched to Multiplexed Control Mode to modify the Mode Register. Therefore, the C/K pin (selecting Multiplexed Control Mode or Direct Control Mode) should be mode programmable. Other operations such as loading the Master Key and the Initial Vector (IV) Registers require also that the DCP is switched to Multiplexed Control Mode. In Multiplexed Control Mode, the full data ciphering instruction set is provided.

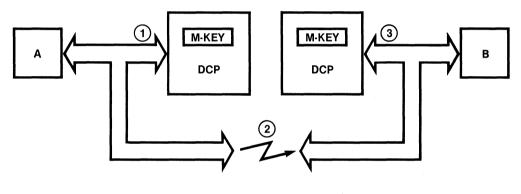

In Multiplexed Control Mode, the devices of the DCP family support two different types of microprocessor interfaces as shown below:

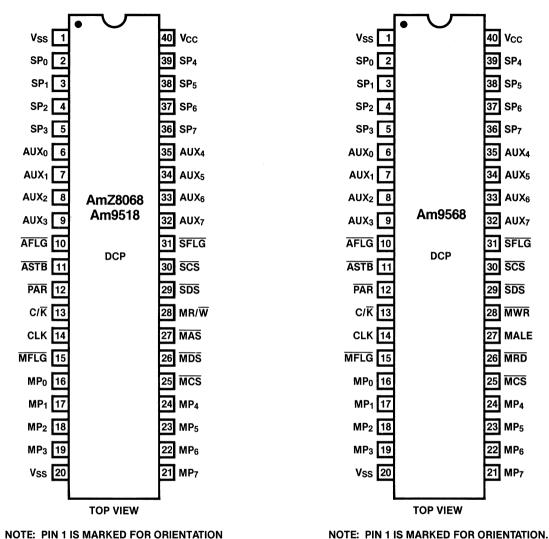

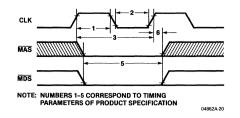

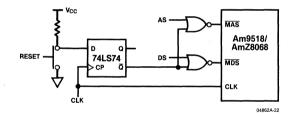

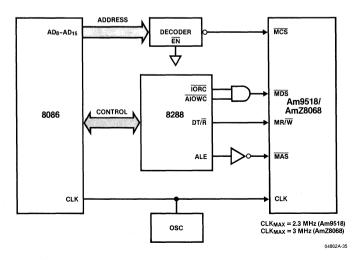

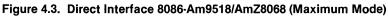

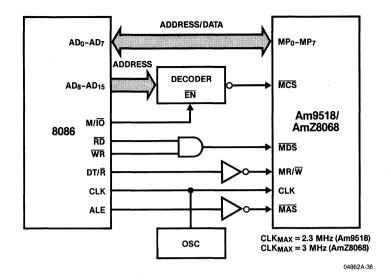

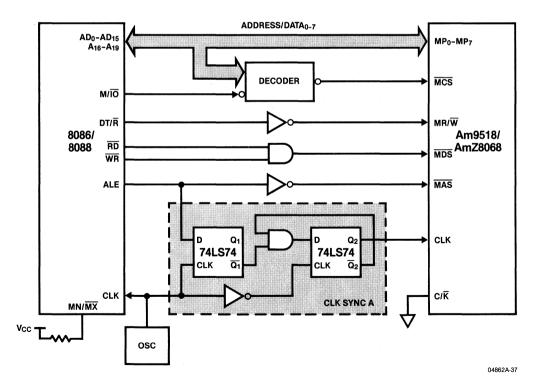

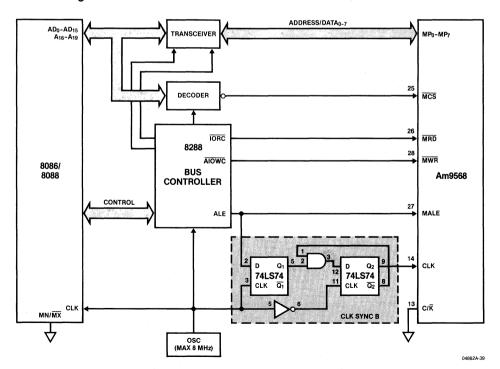

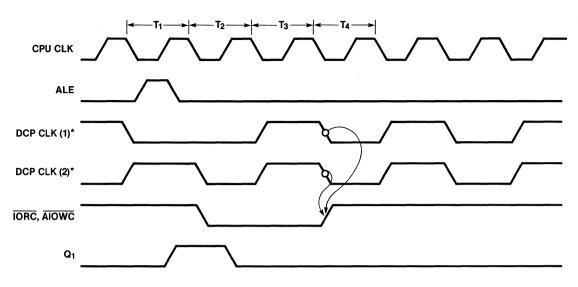

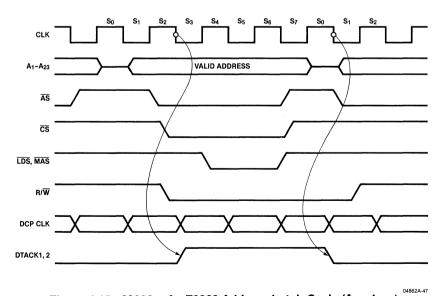

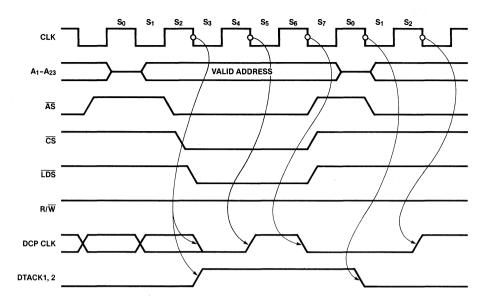

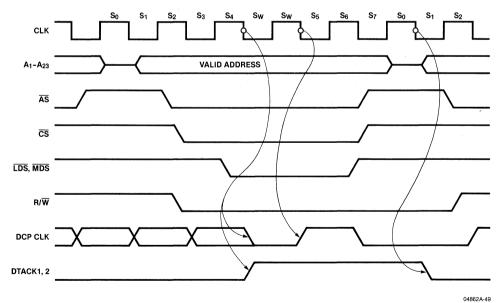

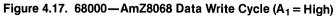

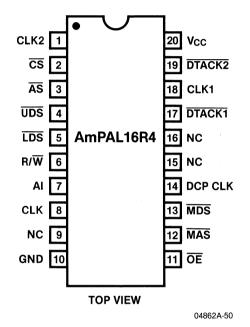

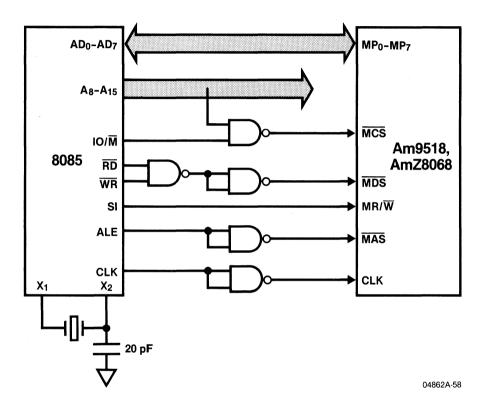

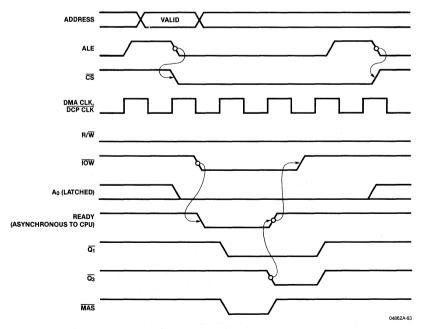

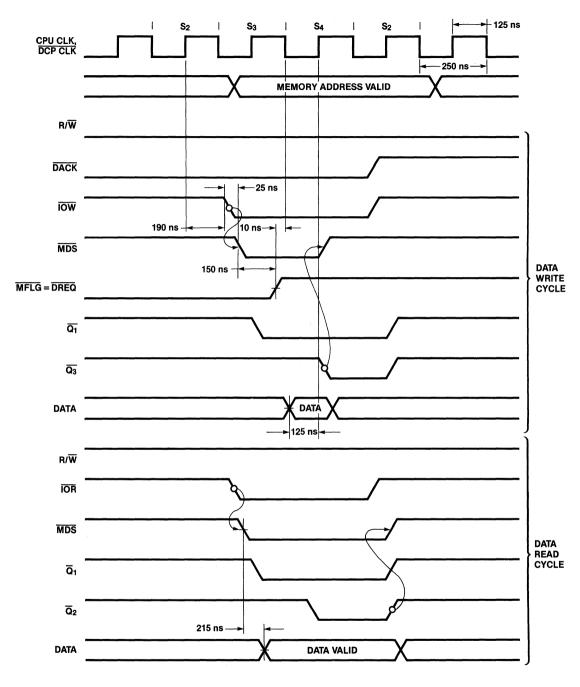

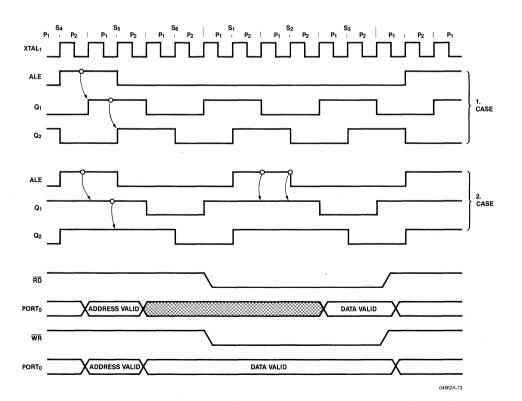

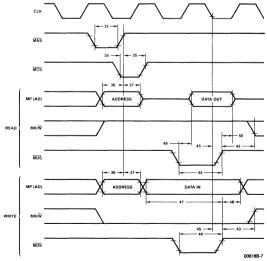

#### Am9518/AmZ8Ø68

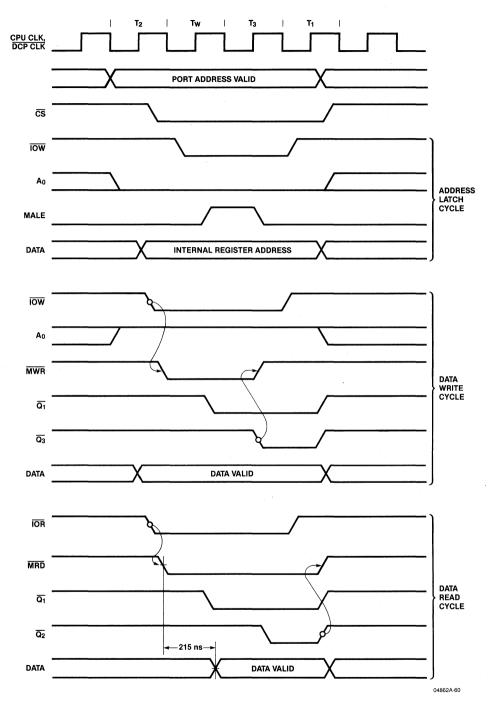

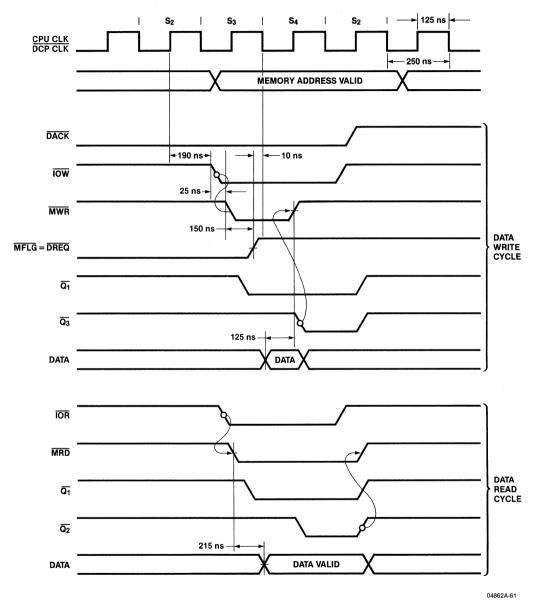

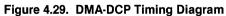

The Am9518 and AmZ8068 (Figure 2.10) support a Z8000-type interface. Figure 2.10 shows the basic timing. The Master Port Address Strobe (MAS) is active Low. The rising (i.e. trailing) edge latches the level of Master Port Chip Select (MCS) and the 2-bit register address on MP<sub>1</sub> and MP<sub>2</sub>. Master Port Data Strobe (IMDS) provides the timing for the data transfer. The level on Read/Write (R/W) defines the data transfer direction. Timing parameter 42 of the product specification defines the set-up time of R/W to MDS. The rising edge of MDS must be synchronous to the falling edge of the clock. Most CPUs do not meet the specified narrow time range, so external synchronization logic must be added to satisfy this parameter. The interfaces in Chapter 4 show some approaches.

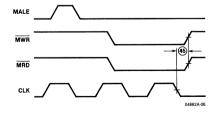

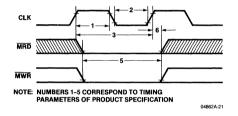

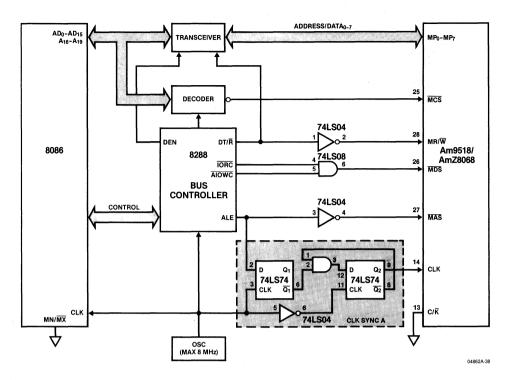

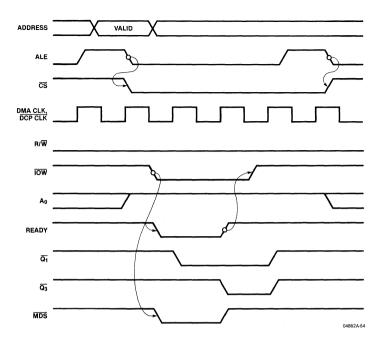

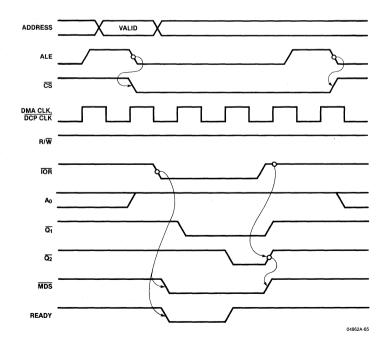

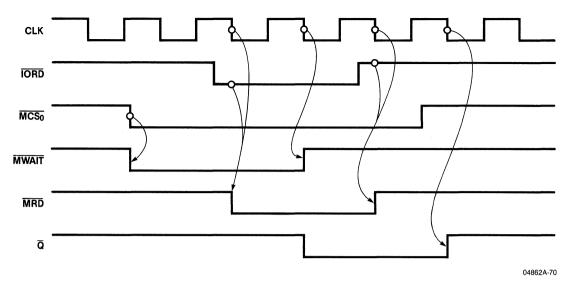

#### Am9568

The Am9568 (Figure 2.11) has a host CPU interface which is optimized for the iAPX microprocessor family. Figure 2.11 shows the basic bus timing. Master Port Address Latch Enable (MALE) is active High. The falling (i.e. trailing) edge of ALE latches MCS and the register address on MP<sub>1</sub> and MP<sub>2</sub>. Master Port Write (MWR) provides timing for a data write transfer, Master Port Read (MRD) provides timing for read transfers. Both strobes must be synchronous to the clock. The range is smaller than with the Am9518 or AmZ8068. The Am9568 has advantages in applications requiring narrow address strobes or where it is difficult to satisfy the set-up time of R/W.

19

04862A-12

40 Vcc

39 SP₄

38 SP5

37 SP6

34 AUX5

33 AUX6

32 AUX7

31 SFLG

30 <u>SCS</u>

29 SDS

28 MWR

27 MALE

26 MRD

25 MCS

24 MP4

23 MP5

21 MP7

04862A-13

22 MP<sub>6</sub>

36 SP<sub>7</sub>

35 AUX4

### Figure 3.2 Am9568 Connection Diagram

#### CHAPTER 3. FUNCTIONAL DESCRIPTION

The heart of the DCP is the Data Encryption Standard (DES) algorithm unit that encrypts 64-bit blocks of clear text into corresponding 64-bit blocks of cipher text using a 56-bit key. The DCP can hold three keys simultaneously: a Master Key to generate session keys, an Encryption Key, and a Decryption Key. A block diagram of the internal structure is shown in Figure 2.4.

The DCP has two 64-bit data registers: the Input and the Output Register. Transfers between these registers and the Master or Slave Port occur on the 8-bit input/output buses. The dual ports, separate internal buses and separate input and output registers compose a highly pipelined data path that maximizes the throughput by allowing simultaneous input, ciphering and output operation.

The 8-bit ports handle the 64-bit blocks of data one byte at a time. Each block is strobed into the Input Register with eight Data Strobes. The most significant byte is entered first. The result block can be read from the 64-bit Output Register, also one byte at a time with the most significant byte first.

#### 3.1. PORTS

#### 3.1.1. MASTER PORT

The Master Port is an 8-bit wide  $(MP_{\emptyset}-MP_7)$  bidirectional port. The Mode, Command, and Status Register can be accessed only through this port. The port operation is associated with four control lines, which are defined differently for the two groups of devices.

#### Am9518/AmZ8Ø68:

- MCS Master Port Chip Select

- MAS Master Port Address Strobe

- MDS Master Port Data Strobe

- R/W Read/Write

#### Am9568:

- MCS Master Port Chip Select

- MALE Master Port Address Latch Enable

- MRD Master Port Read

- MWR Master Port Write

The DCP executes a hardware reset when two specific control lines are pulled active Low simultaneously. Namely:

For the Am9518/AmZ8068 - MAS and MDS

For the Am9568 - MRD and MWR

In Direct Control Mode the address strobe (MAS or MALE) is a "don't care". To prevent hardware resets by mistake, tie MAS High for Am9518/AmZ8068 Direct Control Mode applications.

In <u>Multiplexed</u> Control Mode the address strobe latches the level of  $\overline{\text{MCS}}$  and the two-bit pointer address into one of the five internal registers. In systems with a multiplexed address/data bus, this relieves the external address decode circuitry of the responsibility for latching Chip Select.

The Master Port Flag (MFLG) shows the status of the device. It corresponds to the Master Port Flag bit of the Status Register. Figure 3.3 shows the association of the Master Port Flag with the Input and Output Register. In dual port configuration, the Flag reflects the status of the Master Port; it is active if data can be transferred to or from the Master Port. Input or Output Operation depends on the Mode (Encryption or Decryption) and clear or ciphered text, at the Master Port. In single port configuration, this flag always reflects the status of the Input Register, independent of the mode.

#### Master Port in Multiplexed Control Mode

The terminology of the "strobes" is defined below:

| Address strobe      | Am9518/Am28068 | MAS is strobed Low                        |

|---------------------|----------------|-------------------------------------------|

|                     | Am9568         | MALE is strobed High                      |

| <u>Write</u> strobe | Am9518/AmZ8068 | MDS is strobed Low,<br>while MR/W is Low  |

|                     | Am9568         | MWR is strobed Low                        |

| Read strobe         | Am9518/AmZ8068 | MDS is strobed Low,<br>while MR/W is High |

|                     | Am9568         | $\overline{\text{MRD}}$ is strobed Low    |

#### Entering encryption/decryption keys (clear or encrypted):

The key registers are loaded by a command/data sequence. The following sequence of operations must be performed:

<sup>-</sup> Provide MCS, address the Command Register (MP1=High, MP2=High) and issue address strobe.

- Enter command code (see Figure 3.7) by presenting the appropriate one-byte command at the Master Port and issuing a write strobe.

- Provide MCS, address the Input Register (MP1=Low, MP2=Low) and issue address strobe.

- Load eight bytes of key data, one byte at a time, through Master Port. Keys are loaded one byte per write strobe, the most significant byte first.

If the key is in encrypted form, the Master Key must be loaded first through the Auxiliary Port. Then the encrypted key can be loaded. The DCP decrypts this key internally using the Master Key and the ECB method. The clear session key is then stored in the appropriate key register. After loading the last byte of the encrypted key, no read/write to the internal registers is allowed for the subsequent 70 clock cycles.

A key can only be entered into the DCP; for security reasons it cannot be read back. Parity check logic in the DCP verifies that the key is entered correctly. The least significant bit of each byte of key is the parity check bit (odd parity). Flags in the Status Register are set if a parity error occurs during a key load sequence.

# Entering/reading the Initial Vector for Encryption (IVE) or Decryption (IVD):

When using the Chain Block Cipher (CBC) or Cipher Feed Back (CFB) mode, the 64-bit IV Register must be initialized. The command/data sequence is similar to the sequence for entering keys.

Similar to the key, the IV can be loaded in either clear or encrypted form. The encrypted IV is decrypted using the Decryption Key (D Key) and ECB mode before loading the appropriate IV Register. The D Key must be loaded first.

When the IV should be read out in encrypted form, it is first encrypted using the E Key and ECB mode. It takes 70 clock cycles to encrypt or decrypt the IV.

#### Entering or removing data:

Depending on the Mode, either clear or encrypted data can be entered or removed from the Master Port. Data entered through the Master Port goes into the Input Register. Data removed from the Master Port comes from the Output Register. Data is transferred by the following sequence:

- Provide MCS, address data register

- Transfer data bytes, one byte per write strobe or read strobe, starting with most significant byte. The data transfer is not limited to only one block. The device accepts data whenever the corresponding flag shows that the device is ready for a data transfer.

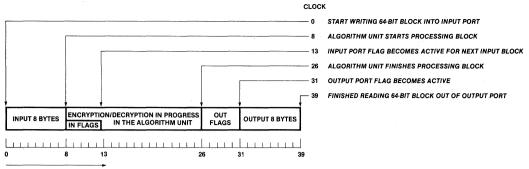

After entering one block of data, the input flag becomes inactive for 5 clock cycles if the data can be transferred to the algorithm unit. If the algorithm unit is still busy or if the device is blocked because the output data is not read out, the input flag stays inactive.

The output flag becomes active whenever data is in the Output Register. After removing one block, the output flag becomes inactive for 5 clocks if the algorithm unit can provide another block. If the algorithm unit is empty, the output flag stays inactive until data is ready again.

#### Master Port in Direct Control Mode

Master Port Chip Select  $(\overline{MCS})$  is not latched internally. It is passed directly to the internal circuitry.

#### Enter clear E or D Key using the following sequence:

- Provide MCS.

- Set up appropriate code at the Auxiliary Port for E/D Key load (see Auxiliary Port description).

- Strobe in eight bytes of the key, one byte per write strobe, most significant byte first.

#### Enter or remove data:

Depending on the configuration chosen by loading the Mode Register, the Master Port can be an input port, an output port or both. The mode determines the direction of data flow. The data access must agree with the mode. Thus data can only be read from the Master Port if the mode defines the Master Port as an Output Port, and data can only be written to the Master Port if it is defined as an Input Port.

- Provide  $\overline{MCS}$ .

- Provide appropriate code at the Auxiliary Port.

- Read or write one byte of data per read or write strobe starting with the most significant byte of a block.

#### 3.1.2. SLAVE PORT

The Slave Port is an 8-bit-wide, bidirectional port controlled by the Slave Port Chip Select (SCS) and the Slave Port Data Strobe (SDS). The direction of the data flow is determined by control

bits in the Mode Register. In both Multiplexed and Direct Control Mode, the Slave Port may be used for either data input or output operation. The Slave Port is only active if the dual port configuration is chosen. In dual port configuration, the Slave Port Flag (SFLG) reflects the status of the Slave Port (Figure 3.3). If the flag is active, data can be strobed in or removed depending on the programmed data flow direction. In single port configuration (Master Port only) the Slave Port Flag represents the status of the Output Register. The Slave Port Flag corresponds to one bit of the Status Register.

- Provide SCS.

- Read or write one byte of data per strobe (SDS) beginning with the most significant byte.

SCS is not latched internally, and may be tied permanently Low without impairing Slave Port operation.

#### 3.1.3. AUXILIARY PORT

The Auxiliary Port has fundamentally different functions in Multiplexed Control Mode and in Direct Control Mode.

#### Auxiliary Port in Multiplexed Control Mode

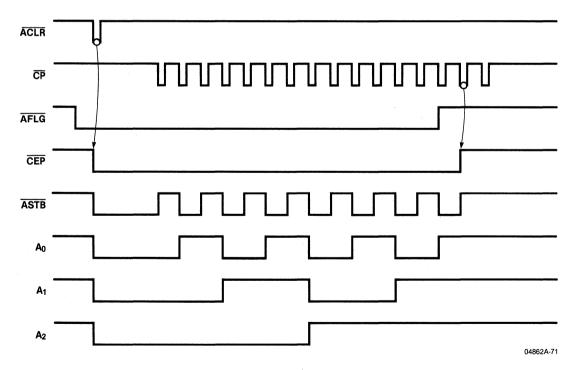

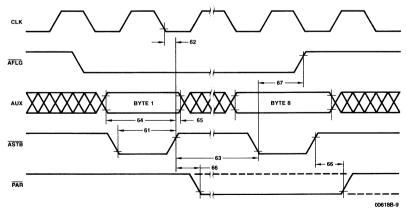

The port is 8-bits wide and can be used for key input only. The status signal Auxiliary Port Flag (AFLG) becomes active whenever key data can be entered. The rising edge of the control signal Auxiliary Port Strobe (ASTB) strobes in the key data one byte at a time. ASTB is ignored unless AFLG and C/K are both Low. To use the Auxiliary Port for key entry, the following sequence can be performed:

- Enter an appropriate command through the Master Port into the Command Register that requires Auxiliary Port operation; e.g., "Load Encrypted E Key through Auxiliary Port".

- In response to these commands, the Auxiliary Flag (AFLG) becomes active Low. Eight bytes of key can then be entered by strobing Auxiliary Strobe (ASTB). AFLG becomes inactive shortly after the falling edge of the eighth strobe.

The Master Key, which is needed to generate session keys, can only be loaded through the Auxiliary Port. A key loaded in encrypted form is decrypted using the Master Key and ECB mode. To guarantee the system security, a key cannot be read back.

#### Auxiliary Port in Direct Control Mode

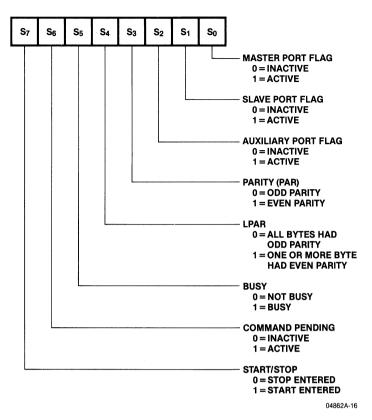

In this mode, the Auxiliary Port operates as a control port for the microprogrammed logic. A subset of the cipher processing commands can be executed. Three pins are control inputs, two pins are status outputs:

| Encrypt/<br>Decrypt | Port<br>Configuration |                | Input<br>Register | Output<br>Register |

|---------------------|-----------------------|----------------|-------------------|--------------------|

| M4                  | M <sub>3</sub>        | M <sub>2</sub> | Flag              | Flag               |

| 0                   | 0                     | 0              | MFLG              | SFLG               |

| 0                   | 0                     | 1              | SFLG              | MFLG               |

| 0                   | 1                     | 0              | MFLG              | SFLG               |

| 1                   | 0                     | 0              | SFLG              | MFLG               |

| 1                   | 0                     | 1              | MFLG              | SFLG               |

| 1                   | 1                     | 0              | MFLG              | SFLG               |

04862A-14

# Figure 3.3. Association of Master Port Flag (MFLG) and Slave Port Flag (SFLG) with Input and Output Registers

| C/K | MP <sub>2</sub> | $\mathbf{MP}_{1}$ | MR/W | MCS | Register Addressed   |

|-----|-----------------|-------------------|------|-----|----------------------|

| 0   | Х               | 0                 | 0    | 0   | Input Register       |

| 0   | Х               | 0                 | 1    | 0   | Output Register      |

| 0   | 0               | 1                 | 0 0  |     | Command Register     |

| 0   | 0               | 1                 | 1    | 0   | Status Register      |

| 0   | 1               | 1                 | Х    | 0   | Mode Register        |

| X   | Х               | Х                 | X    | 1   | No Register Accessed |

| 1   | Х               | Х                 | 0    | 0   | Input Register       |

| 1   | Х               | Х                 | 1    | 0   | Output Register      |

### Am9518/AmZ8068

#### Am9568

| C/K | $MP_2$ | $MP_1$ | MRD | MWR | MCS | Register Addressed   |

|-----|--------|--------|-----|-----|-----|----------------------|

| 0   | Х      | 0      | 1   | 0   | 0   | Input Register       |

| 0   | Х      | 0      | 0   | 1   | 0   | Output Register      |

| 0   | 0      | 1      | 1   | 0   | 0   | Command Register     |

| 0   | 0      | 1      | 0   | 1   | 0   | Status Register      |

| 0   | 1      | 1      | Х   | Х   | 0   | Mode Register        |

| Х   | Х      | Х      | Х   | Х   | 1   | No Register Accessed |

| 1   | Х      | Х      | 1   | 0   | 0   | Input Register       |

| 1   | Х      | Х      | 0   | 1   | 0   | Output Register      |

04862A-15

# Figure 3.4. Master Port Register Addresses

#### AUX7-K/D (Key/Data, Input)

When this signal goes High, the DCP initiates a key-data input sequence as if a Load Clear E or D Key through Master Port command has been entered. The level on  $AUX_6$ -E/D determines whether the subsequently entered clear-key bytes are written into the E Key Register (E/D High) or into the D Key Register (E/D Low).

AUX<sub>7</sub>-K/D and AUX<sub>5</sub>-S/S are mutually exclusive control lines; when one goes active (High), the other must be and remain inactive (Low) until the first returns to an inactive state. In addition, both lines must be inactive (Low) whenever a transition occurs on  $C/\overline{K}$  (entering or exiting Direct Control Mode).

#### AUX6-E/D (Encrypt/Decrypt, Input)

When  $AUX_5-S/\overline{S}$  goes High, initiating a normal data ciphering operation, this input specifies whether the ciphering algorithm is to encrypt (E/D High) or decrypt (Low).

When  $AUX_7-K/\overline{D}$  goes High, initiating entry of key bytes, the level on  $AUX_6-E/\overline{D}$  specifies whether the bytes are to be written into the E Key Register (E/ $\overline{D}$  High) or the D Key Register (E/ $\overline{D}$  Low).

The AUX<sub>6</sub>-E/D input is not latched internally, and must <u>be</u> held constant whenever one or more of AUX<sub>5</sub>-S/S, AUX<sub>7</sub>-K/D, AUX<sub>2</sub>-BSY, or AUX<sub>3</sub>-CP are active. Failure to maintain the proper level on AUX<sub>6</sub>-E/D during loading or ciphering operations will result in scrambled data in the internal registers.

# AUX<sub>5</sub>-S/S (Start/Stop, Input)

When this pin goes Low (Stop) the DCP will follow the sequence that would normally occur were a Stop command to be entered. Conversely, when this pin goes High, a sequence equivalent to a Start Encryption or Start Decryption command will be followed. At the time AUX<sub>5</sub>-S/S goes High, the level on AUX<sub>6</sub>-E/D (see above) selects either the Start Encryption or Start Decryption interpretation.

# AUX<sub>3</sub>- $\overline{CP}$ (Command Pending Output)

This active Low status output gives a hardware indication that the DCP is ready to accept input of key bytes following a Low-to-High transition on  $AUX_{7-K/D}$ .  $AUX_{3-CP}$  is driven by the CP bit in the Status Register (see Register Description), such that when the CP bit is "1" (active),  $AUX_{3-CP}$  is Low.

#### $AUX_{2}-\overline{BSY}$ (Busy, Output)

This active Low status output gives a hardware indication that the ciphering algorithm is in operation.  $AUX_2$ -BSY is driven by the BSY bit in the <u>Status</u> Register, such that when the BSY bit is "1" (active),  $AUX_2$ -BSY is Low.

#### AUXg,1,4 -Not used.

The Mode, Command, or Status Registers are not directly accessible in Direct Control Mode. A subset of commands can be executed by controlling pins of the Auxiliary Port as described above.

In most Direct Control Mode applications, the  $C/\overline{K}$  input pin, which selects Multiplexed or Direct Control Mode, must be programmable. It allows the user to initialize the DCP in Multiplexed Control Mode, to choose a mode other than the default mode, to load the Master Key, to generate session keys, or to load the Initial Vectors. After doing this the device can be switched to Direct Control Mode by raising the level at the C/K input pin to High.

C/K can be tied High if the user wants the DCP to operate in the default mode (i.e. ECB, dual port configuration, Master Port handles clear text, and Slave Port handles encrypted text).

#### 3.1.4. KEY AND DATA LOAD IN DIRECT CONTROL MODE

In Direct Control Mode, keys can only be entered through the Master Port. This is accomplished in the following manner:

- Hold  $AUX_6$ -E/D High when loading the encryption key or hold it Low when loading the decryption key.

- Keep AUX5-S/S Low.

- Hold  $AUX_7-K/\overline{D}$  High and issue eight write strobes at the Master Port as described in the Master Port section.

The levels of  $AUX_{5-7}$  should be held constant throughout the entire operation.

The data transfer is similar to the key load.  $AUX_6-E/\overline{D}$  and the selected mode determine the data flow direction. In the default mode where the Master Port handles clear data while the Slave Port handles encrypted data, a High on  $AUX_6-E/\overline{D}$  (encryption mode) defines the Master Port as an input port for the clear data and the Slave Port as an output port for the ciphered data. If  $AUX_6-E/\overline{D}$  is switched to Low (decryption mode) the data flow direction is turned around. The Slave Port is now the input port for the encrypted data. The Master Port becomes the output port of the deciphered or clear data. A data ciphering session is set up as follows:

- Set  $AUX_6-E/\overline{D}$  to the appropriate level.

- Keep AUX<sub>7-K/D</sub> Low the entire session.

- Set  $AUX_5 S/\overline{S}$  High to start the ciphering session.

#### 3.2. REGISTERS

In Multiplexed Control Mode, five internal registers can be directly accessed:

| - | Command Register | (write only) |

|---|------------------|--------------|

| - | Status Register  | (read only)  |

| - | Mode Register    | (read/write) |

| - | Input Register   | (write only) |

|   |                  |              |

- Output Register (read only)

In Direct Control Mode, only the Input and Output Registers are addressable through the Master Port. The register addresses are shown in Figure 3.4. The Input and Output Registers and the Command and Status Registers each have the same address. A read or write access determines which register is selected.

To gain access to any of these registers in Multiplexed Control Mode, execute the following sequence:

- Provide MCS and the register address.

- Provide address strobe.

- Read or write the addressed register by issuing a read or write strobe.

#### Command Register

Data written to the 8-bit, write-only Command Register through the Master Port is interpreted as an instruction. The commands and their hexadecimal representations are summarized in Figure 3.7. A detailed description of these commands is given in the section "Commands".

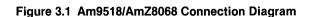

#### Status Register

The 8-bit, read-only Status Register (see Figure 3.5) has the same address as the Command Register. The status bits PAR, AFLG, SFLG, and MFLG indicate the status on the like-named output pins. Note, however, the status bits are active High, whereas the status pins are active Low. Additionally, in Direct Control Mode two pins of the Auxiliary Port reflect the flag bits CP and BUSY.

Figure 3.5. Status Register Bit Assignments

Figure 3.6. Mode Register Bit Assignments

The parity bit (PAR) indicates the parity of the most recently entered key byte. If this byte had even parity, the parity bit is set to signal a parity error.

The second parity bit (LPAR) stores the parity error. It is set if any one key byte had even parity since the last Reset or Load Key command.

The Busy bit will be a "1" whenever the ciphering algorithm unit is actively encrypting or decrypting data, either as a response to a command such as Load Encrypted Key (in which case the Command Pending bit will be a "1"), or in the ciphering of regular text (indicated by the Start/Stop bit being a "1"). The Busy bit will remain a "1", even after ciphering is complete, if the ciphered data cannot be transferred to the Output Register because it contains output from a previous ciphering cycle. Busy will be "0" at all other times, including the case where no ciphering is possible because no data has been written to the Input Register.

The Command Pending bit will be set to "1" by a command that requires the transfer of data to or from a non-addressable internal register, such as when writing key bytes to the E Key Register or reading bytes from the IVE Register. Thus, Command Pending will be set following all commands except the three Start commands, the Stop command and the Software Reset command. Command Pending will return to "0" after all eight bytes have been transferred following Load Clear, Read Clear or Read Encrypted commands; and after data has been transferred, decrypted and loaded into the desired register following Load Encrypted commands.

The Start/Stop bit is set to "1" when one of the Start commands is entered, and is reset to " $\emptyset$ " whenever a reset occurs or when a command other than a Start is entered.

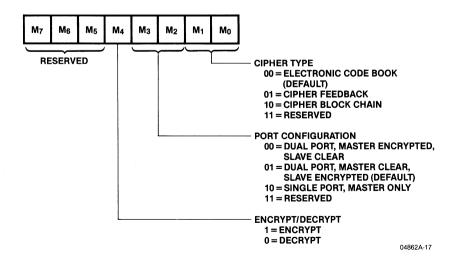

#### Mode Register

Bit Assignments in the 5-bit read/write register are shown in Figure 3.6. The Cipher Type bits  $(M_1, M_{\emptyset})$  indicate to the DCP which ciphering algorithm is used. On reset, the Cipher Type defaults to Electronic Code Book.

Configuration bits  $(M_3, M_2)$  indicate which data ports are associated with the Input and Output Registers and flags. When these bits are set to the Single Port, Master Port-only configuration  $(M_3, M_2=10_B)$  the Slave Port is disabled and no manipulation of Slave Port Chip Select (SCS) or Data Strobe (SDS) can result in data movement through the Slave Port; all <u>data</u> transfers are accomplished through the <u>Master</u> Port. Both MFLG and SFLG are used in this configuration; MFLG gives the status of the Input Register and SFLG, the status of the Output Register.

When the Configuration Bits are set to one of the Dual Port configurations ( $M_3$ ,  $M_2=\emptyset \emptyset_B$  or  $\emptyset l_B$ ), both the Master and Slave

Ports are available for input and output. When  $M_3$ ,  $M_2=\emptyset l_B$  (the default configuration), the Master Port handles clear data while the Slave Port handles encrypted data. Configuration  $M_3$ ,  $M_2=\emptyset B$  reverses this assignment. Actual data direction at any particular moment is controlled by the Encrypt/Decrypt bit.

The Encrypt/Decrypt bit (M4) instructs the DCP algorithm processor to encrypt or decrypt the data from the Input Register using the ciphering method specified by the Cipher Type bits. The Encrypt/Decrypt bit also controls data flow within the DCP. For example, when the configuration bits are "Ø1B" (Dual Port, Master Clear, Slave encrypted) and the Encrypt/Decrypt bit is "1" (encrypt), clear data will flow into the DCP through the Master Port and encrypted data will flow out through the Slave Port. When the Encrypt/Decrypt bit is set to "Ø" (decrypt), data flow reverses.

#### Input Register

The 64-bit, write-only Input Register is organized to appear to the user as eight bytes of push-down storage. A status circuit monitors the number of bytes that have been stored. The register is considered empty when the data stored in it has been or is being processed; it is considered full when one byte of data has been entered in cipher feedback or when eight bytes of data have been entered in Electronic Code Book or Cipher Block Chain. If the user attempts to write data into the Input Register when it is full, the Input Register will disregard this attempt; no data in the register will be destroyed.

#### Output Register

The 64-bit, read-only Output Register is organized to appear to the user as eight bytes of pop-up storage. A status circuit detects the number of bytes stored in the Output Register. The register is considered empty when all the data stored in it has been read out. It is considered full if it contains one or more bytes of output data. If a user attempts to read data from the Output Register when it is empty, the buffers driving the output bus will remain in a three-state condition.

The following multibyte registers cannot be directly addressed, but are loaded or read in response to commands written to the Command Register. (See Commands.)

| - | Master Key Register           | (write only) |

|---|-------------------------------|--------------|

| - | Encryption Key Register       | (write only) |

| _ | Decryption Key Register       | (write only) |

| - | Initial Vector for Encryption | (read/write) |

| - | Initial Vector for Decryption | (read/write) |

#### Master Key Register

The 56-bit Master Key Register can be loaded only with clear data through the Auxiliary Port. The load has to be preceded by the command "Load Clear M Key through Auxiliary Port". The Master Key is used to generate session keys. The correctness of entering the key can be verified by checking the LPAR bit of the Status Register.

#### Encryption and Decryption Key Register

The 56-bit Encryption Key or the 56-bit Decryption Key can be loaded through the Master Port or Auxiliary Port, in clear or in encrypted form. If the key is loaded in encrypted form, it is first routed to the Input Register, to be decrypted using the Master Key. It is then transferred to the appropriate key register.

#### Initial Vector Registers

Two 64-bit Initial Vector Registers are provided to store feedback values for CBC and CFB mode. Both registers can be loaded or read out through the Master Port in either clear or encrypted form. The E Key is used to decrypt the IV and the D Key to encrypt the IV utilizing the ECB mode. These registers have to be initialized only for CBC and CFB. The value is exclusive OR'ed with the first data block. Then the register is reloaded or modified. For detailed information refer to the section "Modes of Operation" in Chapter 2.2.

For test purposes these registers can be read out. Before reading the Initial Vectors, the Output Register must be flushed out by removing all data or by issuing a Reset. The IVs are eight bytes long and loaded one byte at a time with the most significant byte first. No parity check is done on these vectors.

#### 3.3. COMMANDS

All operations of the DCP result from command inputs, which are entered in Multiplexed Control Mode by writing a command byte to the Command Register. Commands are entered in Direct Control Mode by raising and lowering the logic levels on the AUX7<sup>-K/D</sup>, AUX6-E/D and AUX5-S/S pins. Figure 3.7 shows all commands that may be given in Multiplexed Control Mode. Figure 3.8 shows that subset executable in Direct Control Mode.

| Hex<br>Code | Command                                     |

|-------------|---------------------------------------------|

| 90          | Load Clear M Key through Auxiliary Port     |

| 91          | Load Clear E Key through Auxiliary Port     |

| 92          | Load Clear D Key through Auxiliary Port     |

| 11          | Load Clear E Key through Master Port        |

| 12          | Load Clear D Key through Master Port        |

| B1          | Load Encrypted E Key through Auxiliary Port |

| B2          | Load Encrypted D Key through Auxiliary Port |

| 31          | Load Encrypted E Key through Master Port    |

| 32          | Load Encrypted D Key through Master Port    |

| 85          | Load Clear IVE through Master Port          |

| 84          | Load Clear IVD through Master Port          |

| A5          | Load Encrypted IVE through Master Port      |

| A4          | Load Encrypted IVD through Master Port      |

| 8D          | Read Clear IVE through Master Port          |

| 8C          | Read Clear IVD through Master Port          |

| A9          | Read Encrypted IVE through Master Port      |

| A8          | Read Encrypted IVD through Master Port      |

| 39          | Encrypt with Master Key                     |

| 41          | Start Encryption                            |

| 40          | Start Decryption                            |

| C0          | Start                                       |

| E0          | Stop                                        |

| 00          | Software Reset                              |

04862A-18

Figure 3.7. Command Codes in Multiplexed Control Mode

|     |                   | Command |          |                                         |

|-----|-------------------|---------|----------|-----------------------------------------|

| C/K | AUX7-K/DAUX6-E/DA |         | AUX₅-S/Ŝ | Initiated                               |

| н   | L                 | L       | t        | Start Decryption                        |

| н   | L                 | н       | t        | Start Encryption                        |

| н   | L                 | Х       | <b>↓</b> | Stop                                    |

| н   | t                 | L       | L        | Load D Key Clear<br>through Master Port |

| н   | t                 | Н       | L        | Load E Key Clear<br>through Master Port |

| н   | 1                 | х       | L        | End Load Key<br>Command                 |

| н   | н                 | х       | Н        | Not Allowed                             |

| L   | Data              | Data    | Data     | AUX Pins Become<br>Key-Byte Inputs      |

04862A-19

# Figure 3.8. Implicit Command Sequences in Direct Control Mode

Load Clear M Key Through Auxiliary Port (90 H) Load Clear E Key Through Auxiliary Port (91 H) Load Clear D Key Through Auxiliary Port (92 H)

These commands override the data flow specifications set in the Mode Register and cause the Master (M), Encrypt (E), or Decrypt (D) Key Register to be loaded with eight bytes written to the Auxiliary Port. After the Load command is written to the Command Register, the Auxiliary Port Flag ( $\overline{AFLG}$ ) will go active (Low), and the corresponding bit in the Status Register (S<sub>2</sub>) will go to "1", indicating that the device is able to accept key bytes at the Auxiliary Port pins. Additionally, the Command Pending bit (S<sub>6</sub>) will go to "1" during the entire loading process.

Each byte is written by placing an active Low signal on the Auxiliary Port Strobe (ASTB) once data has been set up on the Auxiliary Port pins. The actual write process occurs on the rising (trailing) edge of ASTB.

The Auxiliary Port Flag ( $\overline{AFLG}$ ) will go inactive immediately after the eighth strobe goes active (Low), but, the Command Pending bit (S<sub>6</sub>) will remain "1" for several more clock cycles, until the key loading process is completed. All key bytes are checked for correct (odd) parity as they are entered (see Parity Checking).

#### Load Clear E Key Through Master Port $(11_H)$ Load Clear D Key Through Master Port $(12_H)$

These commands are available in both Multiplexed Control and Direct Control Modes. They override the data flow specifications set in the Mode Register and attach the Master Port inputs to the Encrypt (E) or Decrypt (D) Key Register, as appropriate, until eight key bytes have been written. In Multiplexed Control Mode, the command is initiated by writing the Load command to the Command Register. In Direct Control Mode, the command is initiated by raising the AUX<sub>7-K/D</sub> control input while the AUX<sub>5-</sub> S/S input is Low. In this later case, the level on AUX<sub>6</sub>-E/Ddetermines which key register is written (High=E-Key Register, Low=D-Key Register).

Once the command has been recognized, the Command Pending bit (S<sub>6</sub> in the Status Register) will go to "l", and in Direct Control Mode AUX<sub>3</sub>- $\overline{CP}$  will go active (Low), indicating that key entry may proceed. The host system then writes exactly eight bytes to the Master Port (at the Input Register address in Multiplexed Control Mode). When the key register has been loaded, Command Pending will return to "0", and in Direct Control Mode the AUX<sub>3</sub>- $\overline{CP}$  output will go inactive, indicating that the DCP can accept the next command.

Chapter 3

# Load Encrypted E Key Through Auxiliary Port $(Bl_{H})$ Load Encrypted D Key Through Auxiliary Port $(B2_{H})$

Execution of these commands (in Multiplexed Control Mode only) is similar to the Load Clear E (D) Key Through Auxiliary Port, except that key bytes are first decrypted using the Electronic Code Book algorithm and the Master (M) key, and then loaded into the appropriate key register, after having passed through the parity check logic (see Parity Checking).

The Command Pending bit  $(S_6)$  will be "1" during the entire decrypt-and-load operation. In addition, the Busy bit  $(S_5)$  will be "1" during the actual decryption process.

## Load Encrypted E Key Through Master Port $(31_H)$ Load Encrypted D Key Through Master Port $(32_H)$

These commands (in Multiplexed Control Mode only) are similar in effect to the Load Clear E (D) Key Through Master Port, except that key bytes are initially decrypted using the Electronic Code Book algorithm and the Master (M) Key, and then loaded byte-bybyte into the target key register, after having passed through the parity check logic (see Parity Checking).

The Command Pending bit (S6) will be "1" during the entire decrypt-and-load operation. In addition, the Busy bit (S5) will be "1" during the actual decryption process.

# Load Clear IVE Register Through Master Port $(85_H)$ Load Clear IVD Register Through Master Port $(84_H)$

These commands (in Multiplexed Control Mode only) are almost identical to Load Clear E (or D) Key Through Master Port except that the data written to the Input Register address is routed to the Encryption Initial Vector (IVE) or Decryption Initial Vector (IVD) Register instead of a key register, and no parity checking occurs. Command Pending (S<sub>6</sub>) is a "1" during the entire loading process.

# Load Encrypted IVE Register Through Master Port $(A5_{H})$ Load Encrypted IVD Register Through Master Port $(A4_{H})$

These commands are analogous to the Load Encrypted E (or D) Key Through Master Port commands. The data flow specifications set in the Mode Register are overridden and the eight vector bytes are decrypted using the Decryption (D) Key and the Electronic Code Book algorithm. The resulting clear vector bytes are loaded into the target Initial Vector Register, and no parity checking occurs. The Busy bit (S<sub>5</sub>) does not go to "1" during the decryption process, but Command Pending (S<sub>6</sub>) will be "1" during the entire decryption-and-load operation.

# Read Clear IVE Register Through Master Port $(8D_H)$ Read Clear IVD Register Through Master Port $(8C_H)$

The effect of these commands (in Multiplexed Control Mode only) is to override the data flow specifications set in the Mode Register and to connect the appropriate Initial Vector Register to the Master Port at the Output Register address. In this state, each IV Register appears as eight bytes of FIFO storage. The first byte of data will be available 6 clocks after the loading the Command Register. The Command Pending bit will be set to "1" and will remain a "1" until sometime after the eighth byte is read out. The host system has the responsibility to read out exactly eight bytes.

# Read Encrypted IVE Register Through Master Port $(A9_{H})$ Read Encrypted IVD Register Through Master Port $(A8_{H})$

The effect of these commands (in Multiplexed Control Mode only) is to override the specifications set in the Mode Register and to encrypt the contents of the specified Initial Vector Register using the Electronic Code Book algorithm and the Encrypt (E) Key. The resulting cipher text is placed in the Output Register, from which it can be read out as eight bytes through the Master Port. During the actual encryption process the Busy bit  $(S_5)$  will be "1". When Busy goes to "0", the encrypted vector bytes are ready to be read out. Command Pending  $(S_6)$  will be "1" during the encryption-and-output process, and will go to "0" when the eighth byte is read out. The host system is responsible for reading out exactly eight bytes.

## Encrypt with Master (M) Key (39<sub>H</sub>)

This command, in Multiplexed Control Mode only, overrides the data flow specifications set in the Mode Register and causes the DCP to accept eight bytes from the Master Port, written to the Input Register. When eight bytes have been received, the DCP encrypts the input using the Master (M) Key. The encrypted data is loaded into the Output Register, where it may be read out through the Master Port. The Command Pending ( $S_6$ ) and Busy ( $S_5$ ) bits are used to sense the three phases of this operation. Command Pending goes to "1" as soon as the Input Register can accept data. When exactly eight bytes have been entered, the Busy bit will go to "1" until the encryption process is complete.

When Busy goes to "Ø", the encrypted data is available to be read out. Command Pending will return to "Ø" when the eighth byte has been read.

## Start Encryption $(41_{H})$ Start Decryption $(40_{H})$ Start $(C0_{H})$

The three "Start" commands begin normal data ciphering by setting the Start/Stop bit (S7) in the Status Register to "1". The Start Encryption and Start Decryption commands explicitly specify the

#### Chapter 3

ciphering direction by forcing the Encrypt/Decrypt bit  $(M_4)$  in the Mode Register to "1" or " $\emptyset$ ", respectively, whereas Start uses the current state of the Encrypt/Decrypt bit, as specified in a previous Mode Register load.

When a Start command has been entered, the Port Status Flag ( $\overline{\text{MFLG}}$  or  $\overline{\text{SFLG}}$ ) associated with the Input Register will become active (Low), indicating that data may be written to the Input Register to begin ciphering.

In Direct Control Mode, the Start command is issued by raising the level on the AUX<sub>5</sub>-S/S input (see Figure 3.8). The ciphering direction is specified by the level on AUX<sub>6</sub>-E/D. If AUX<sub>6</sub>-E/D is High when\_AUX<sub>5</sub>-S/S goes High, the command is Start Encryption. If AUX<sub>6</sub>-E/D is Low, it is Start Decryption.

## Stop (E $\emptyset_H$ )

The Stop command clears the Start/Stop bit  $(S_7)$  in the Status Register. This causes the input flag (MFLG or SFLG) to become inactive and inhibits the loading of any further input into the algorithm unit. If ciphering is in progress (Busy bit  $(S_5)$  is "1" or AUX<sub>2</sub>-BSY is active), the ciphering process is terminated. Any data in the Output Register will remain accessible (except in CFB mode). In CFB mode, the last byte of data must be read out before issuing the Stop command.

In Direct Control Mode, the Stop command is implied when the signal level on the  $AUX_5-S/S$  input goes from High to Low (see Figure 3.8).

# Software Reset (00<sub>H</sub>)

This command has the same effect as a hardware reset; it forces the DCP back to its default configuration, and all processing flags go inactive. In the default configuration the Mode Register is set to Electronic Code Book cipher type, and Dual Port Configuration with Master Port clear, Slave Port encrypted.

### 3.4. PARITY CHECKING OF KEYS

To enhance system security, the DCP provides no way to read back the keys. A parity check on each byte of key input guarantees the user that the key is entered correctly.

Key bytes are considered to contain seven bits of key information and one parity bit. The parity checking circuit is enabled whenever a byte is written to one of three key registers. The output of the parity detection circuit is connected to pin  $\overrightarrow{PAR}$ and the state of this pin is reflected in Status Register bit PAR (S<sub>3</sub>). Status Register bit PAR goes to "1" whenever a byte with even parity (an even number of "1s") is detected. In addition to the PAR bit, the Status Register has a Latched Parity Bit (LPAR,  $S_4$ ) which is set to "l" whenever the Status Register PAR bit goes to "l". Once set, the LPAR bit is not cleared until a reset occurs or a new Load Key command is issued.

When an encrypted key is entered, the parity detect logic operates only after the decrypted key is available. The encrypted data is not checked for parity. The PAR signal will reflect the state of the decrypted bytes on a byte-to-byte basis, as they are clocked through the parity check logic on their way to the Key Register. Thus, the time PAR indicates the status of a byte of decrypted key data may be as short as four clock cycles. The LPAR bit in the Status Register will indicate if any erroneous bytes of key were entered.

## 3.5. INITIALIZATION

After power up the DCP must be reset in one of several possible ways. Under some conditions the DCP is reset automatically (e.g., aborting a command).

## Hardware Reset:

| Am9518/AmZ8Ø68: | MAS | and | MDS | are | Low | simultaneously |

|-----------------|-----|-----|-----|-----|-----|----------------|

|                 |     |     |     |     |     |                |

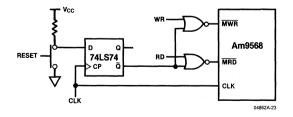

Am9568: MRD and MWR are Low simultaneously

Figures 3.9 and 3.10 show the reset timings. Parameter 5 specifies the minimum strobe widths; parameter 6 the hold time to the rising edge of the clock. The strobe width may be wider than specified by parameter 5. In this case the strobe has to meet only the set-up time (parameter 5 minus parameter 6) and hold time (parameter 6) to at least one rising edge of the clock. This means, for strobes wider than one clock period, the trailing edge does not have to be synchronized to the rising edge of the clock.

### Software Reset:

The DCP can be reset by software in three ways:

- Issue the Software Reset command  $(\emptyset \emptyset_H)$ .

- Load the Mode Register.

- The DCP is reset by aborting any command, i.e., by entering any command before the previous command is completely executed or terminated. The abort does not destroy the Mode Register; it only resets the flags.

A reset sets the Mode Register to the default value " $14_{\rm H}$ ". It selects encryption, ECB mode, and dual port configuration with Master Port clear data and Slave Port encrypted data. The reserved bits of the Mode Register are read back as "ls".

Figure 3.9. Am9518/AmZ8068 Clock and Reset

Figure 3.10. Am9568 Clock and Reset

Figure 3.11. Am9518/AmZ8068 Reset Logic

Figure 3.12. Am9568 Reset Logic

Figures 3.11 and 3.12 show hardware reset circuits which guarantee that the strobes are synchronous to the rising edge of the clock.

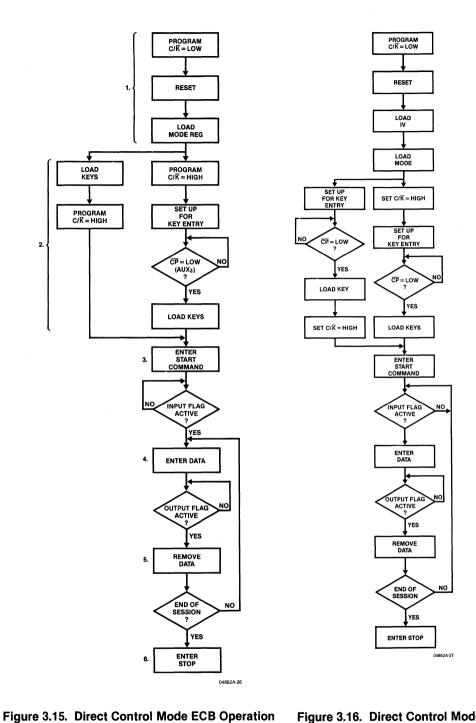

#### 3.6. MULTIPLEXED CONTROL MODE

This chapter describes in detail which steps must be executed to operate the DCP using ECB, CBC, and CFB in Multiplexed Control Mode. All the program sequences are set up for a Master Port-only configuration. The device at the Master Port handles both input and output data. To set the DCP up for pipelined operation, strobe in additional data after initializing the device and before entering the data transfer loop (see Chapter 3.9).

For dual port configuration, the same basic program sequence can be executed, modifying only the data transfer session. Now the CPU handles either input or output data, so one transfer task must be removed from the command sequence. The high-speed peripheral connected to the Slave Port executes the remaining task. Data can be put in or read back concurrently.

#### 3.6.1. ECB OPERATION

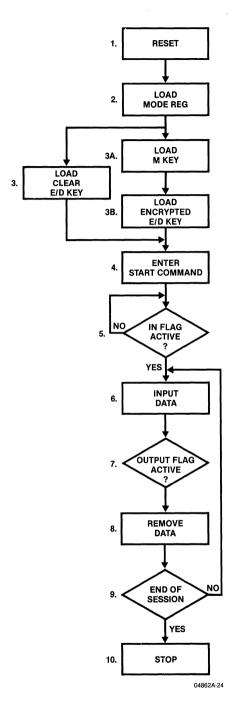

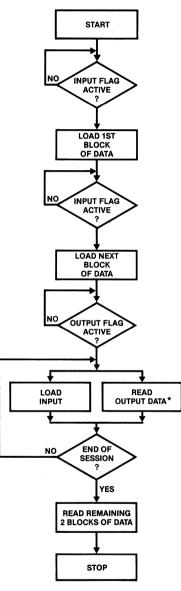

Figure 3.13 shows the program sequence.

- Step 1: A hardware or software reset clears all Status Register flags and sets the Mode Register to the default condition.

- Step 2: The Mode Register is loaded via the Master Port. The loaded value determines the port configuration, the mode of operation (ECB, CBC, or CFB) and encryption or decryption. For example, to enter clear data through the Slave Port and remove encrypted data from the Master Port using ECB mode for encryption, the Mode Register is loaded with  $10_{\rm H}$  (see Chapter 3.2, "Mode Register").

- Step 3: The clear encryption or decryption key can be loaded through either the Master Port or the Auxiliary Port. After entering the appropriate command, the Command Pending bit of the Status Register becomes active (High) until the entire 8-byte key is entered with the most significant byte first.

- Step 3A: Step 3A and 3B can be performed as an alternative to Step 3. In these two steps, the keys are loaded in encrypted form. The Master Key Register has to be loaded first for decrypting encrypted keys. The appropriate command is "Load M Key Through Auxiliary Port"  $(9\emptyset_H)$ . When this command is entered, the Auxiliary Flag in the Status Register goes active High and the AFLG output pin goes Low. The DCP expects data input through the

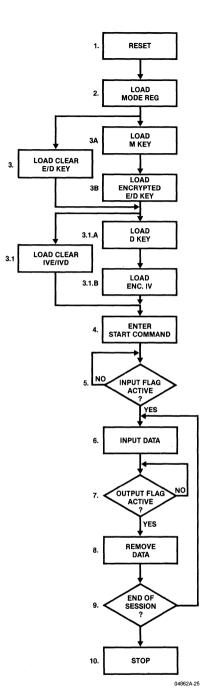

Figure 3.14. CBC Operation Flow Chart

Auxiliary Port. The Master Key is entered by strobing in eight bytes, one byte per Auxiliary Strobe (ASTB), most significant byte first.

- Step 3B: The encrypted E or D Key can be loaded through the Master or Auxiliary Port. Chapter 3.3 lists the commands.

- Step 4: The DCP recognizes three start commands: "Start Encryption", "Start Decryption" and "Start". The first commands set or reset the Encryption/Decryption bit of the Mode Register. If the "Start" command is issued, the Mode Register stays unchanged and the DCP is ready to process data according to the existing Mode Register bit configuration.

- Step 5: After entering a Start command, the DCP indicates readiness for data input by activating the Input Register flag. Data then can be entered through the assigned input port.

NOTE: Ports are assigned on a Clear or Encrypted text basis. In dual port configuration, a change from encryption to decryption reverses the data flow direction. The ports are reassigned; the former input port becomes now an output port and vice versa. This reflects the logical situation in most applications. A good example is a hard disk application: For data security the data is stored in encrypted form on the hard disk. When writing to the disk, the data is encrypted by flowing through the DCP to the disk controller. When reading back, the DCP is programmed for decryption mode, and the data flows in the reverse direction from the disk controller to the system memory.

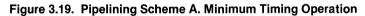

Two flags are associated with the data registers, the MFLG and the SFLG. For flag description see Chapter 3.1. These flags can be sensed by software or hardware. The CPU can monitor the bits of the Status Register by software; the two output pins can drive a Ready/Wait or DMA Request logic. Note that the Status Register bits are active High, whereas the flag output pins are active Low.