Data Book .....

1

9

8

9

## TAARCOM, INC. Manufacturers Representatives 451 N. Shoreline Blvd. Mt. View, CA 94043

(415) 960-1550

# **Table of Contents**

# EEPROMS

1

2

3

4

5

**EEPROMS** (Electrically Erasable Programmable Read Only Memories)

| EEPROM Alternate Source                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 1-1                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| EEPROM Replacement Chart                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 1 <b>-2</b>                                                                                                |

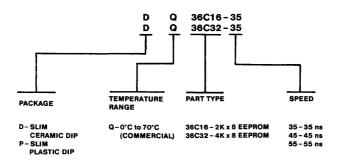

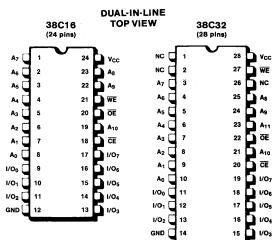

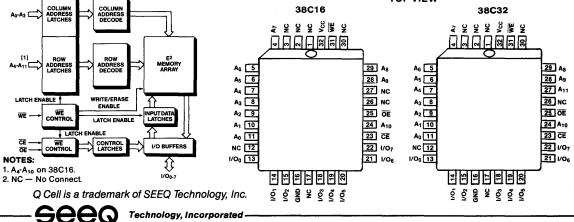

| 52B13/52B13H<br>52B33/52B33H<br>2804A<br>2816A/2816AH<br>5516A/5516AH<br>2817A/2817AH<br>5517A<br>2864/2864H<br>28C64<br>28C65<br>28C256<br>28C256<br>28C256A<br>36C16/32<br>38C16/32<br>28C010<br>Modules Q/E28C010 | 16K Latched64K Latched, 10K cycles/byte4K Latched & Timed, 10K cycles/byte16K Latched & Timed, 10K cycles/byte16K Latched & Timed, 1 M cycles/byte16K Latched & Timed, rdy/busy, 10K cycles/byte16K Latched & Timed, rdy/busy, 10K cycles/byte16K Latched & Timed, rdy/busy, 1 M cycles/byte64K Latched & Timed, rdy/busy64K CMOS Page Mode64K CMOS Page Mode64K CMOS Page ModeHigh Speed CMOS 64K EEPROMHigh Speed CMOS Bipolar PROM ReplacementHigh Speed CMOS EEPROMCMOS Timer E <sup>2</sup> Timer E <sup>2</sup> | 1-11<br>1-19<br>1-25<br>1-31<br>1-31<br>1-37<br>1-43<br>1-51<br>1-59<br>1-67<br>1-69<br>1-71<br>1-77<br>1-83 |

| FLASH                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                              |

| 48F512<br>48F010<br>27F010<br>KT48                                                                                                                                                                                   | 512K CMOS FLASH EEPROM<br>1024K CMOS FLASH EEPROM<br>1024K CMOS FLASH EEPROM<br>FLASH™ EEPROM PROGRAMMER                                                                                                                                                                                                                                                                                                                                                                                                              | 2-13<br>2-25                                                                                                 |

| EPROMS                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                              |

| EPROMS (Erasable Programmable R                                                                                                                                                                                      | Read Only Memories)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

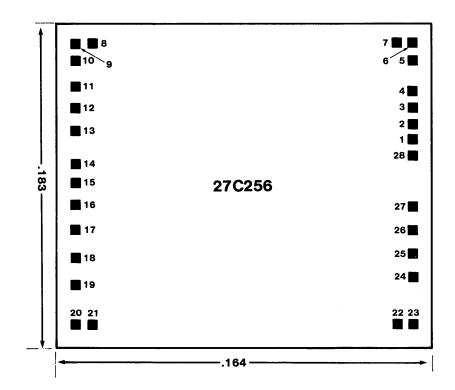

| 2764<br>27128<br>27C256                                                                                                                                                                                              | 64K<br>128K<br>256K CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 3-1                                                                                                        |

| DATA COM                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                              |

| DATA COMMUNICATIONS                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                              |

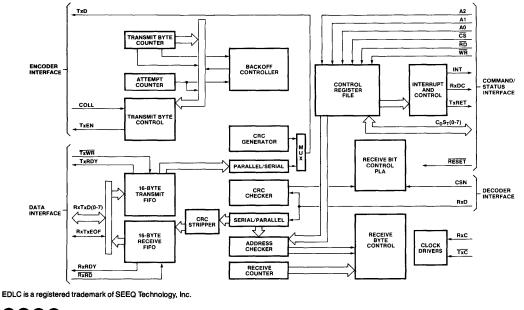

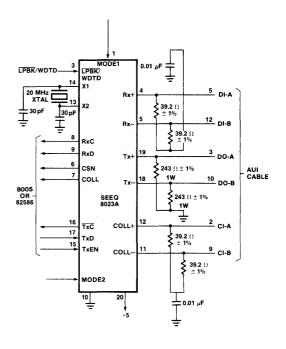

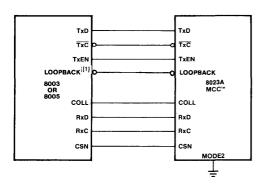

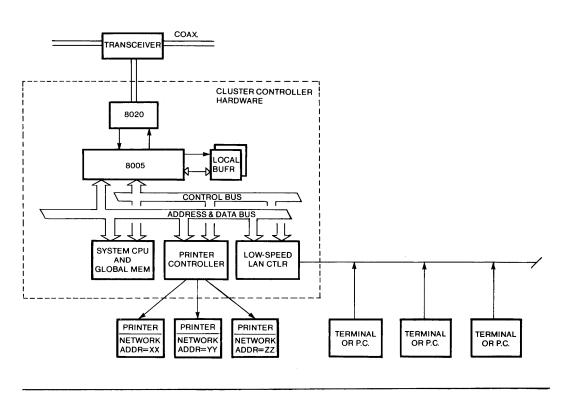

| 0000                                                                                                                                                                                                                 | Ethomat Data Link Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |

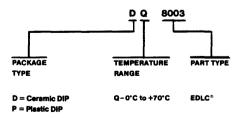

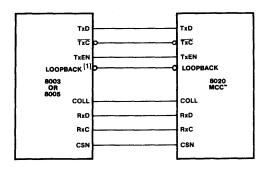

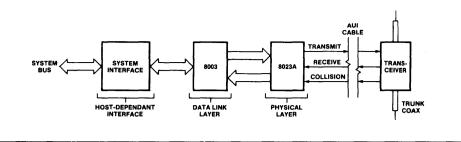

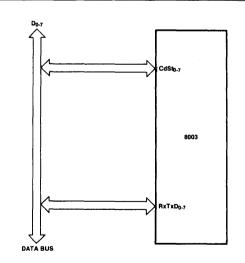

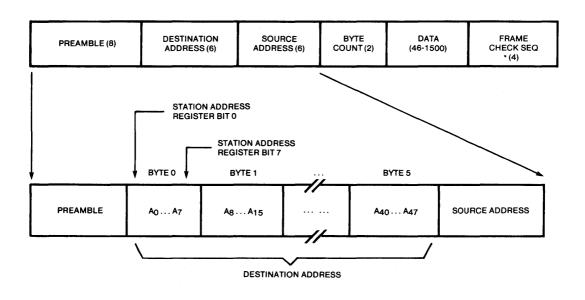

| 8003  | Ethernet Data Link Controller          |

|-------|----------------------------------------|

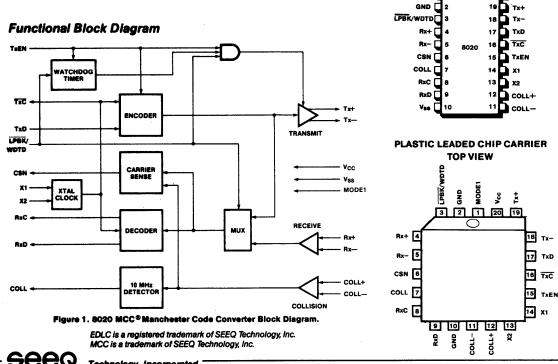

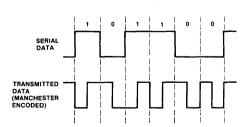

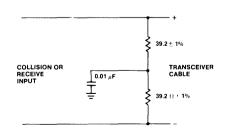

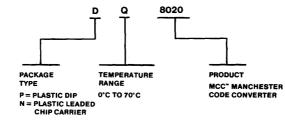

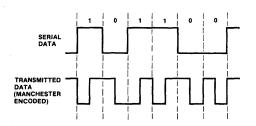

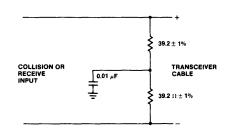

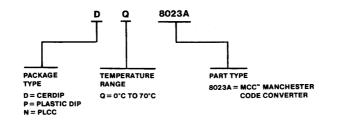

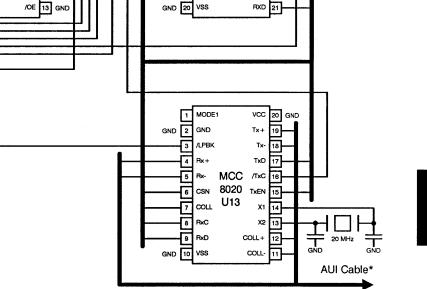

| 8020  | Manchester Code Converter              |

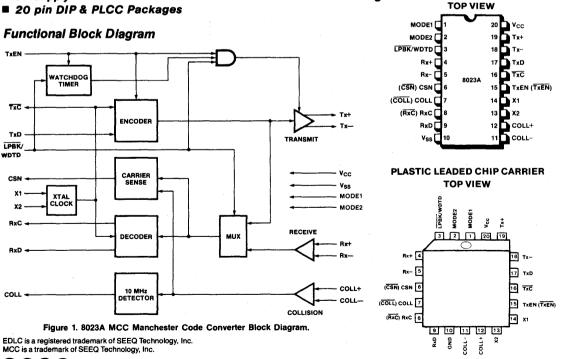

| 8023A | Manchester Code Converter              |

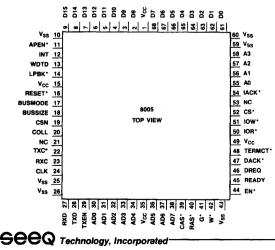

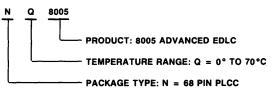

| 8005  | Advanced Ethernet Data Link Controller |

|       |                                        |

|       | EEPLD                                  |

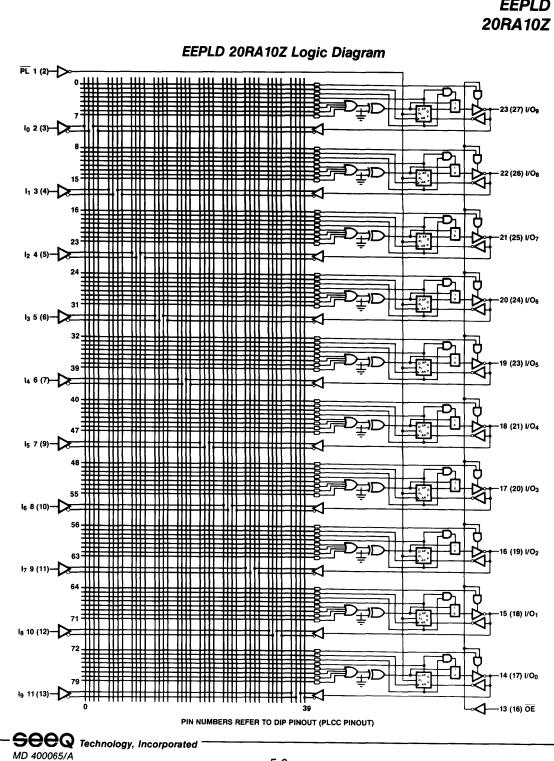

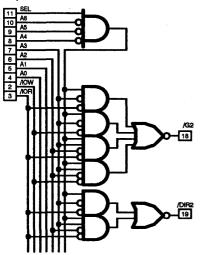

| 20RA10Z | Registered Asynchronous CMOS EEPLD | <br>5-1 |

|---------|------------------------------------|---------|

## MILITARY

#### **EEPROMs**

| M52B13/M52B13H          | 16K Latched                                           |

|-------------------------|-------------------------------------------------------|

| E52B13/E52B13H          |                                                       |

| M52B33/M52B33H          | 64K Latched                                           |

| E52B33/E52B33H          | 64K Latched, ( – 40° to 85°C)6-15                     |

| M2816A/E2816A           | 16K Latched & Timed                                   |

| M2817A/E2817A           | 16K Latched & Timed, rdy/busy pin                     |

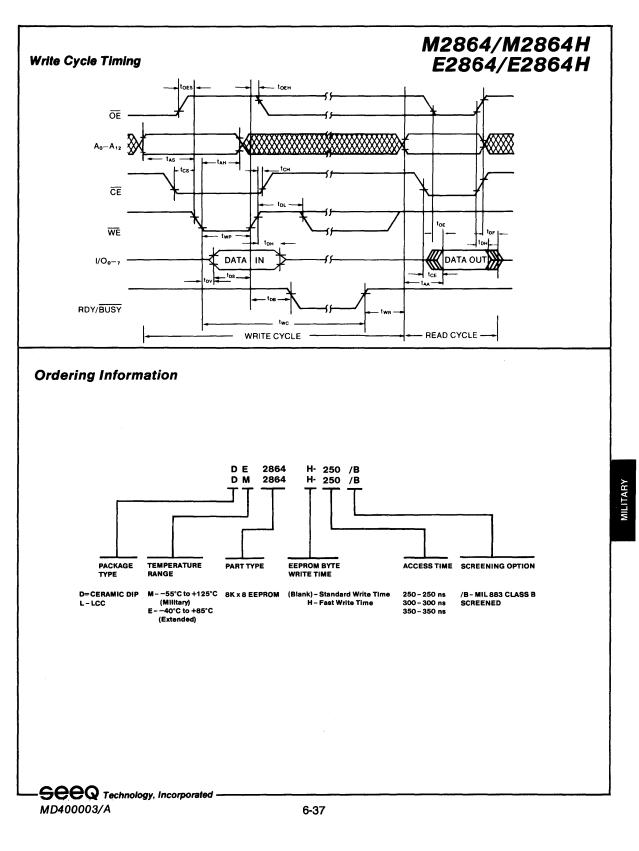

| M2864/2864H-E2864/2864H | 64K Latched and Timed, rdy/busy pin                   |

| M28C64/E28C64           | 64K CMOS Latched & Timed                              |

| M28C65/E28C65           | 64K CMOS Page Mode, Latched & Timed rdy/busy pin 6-46 |

| M28C256/E28C256         | 256K CMOS Page Mode, Latched & Timed                  |

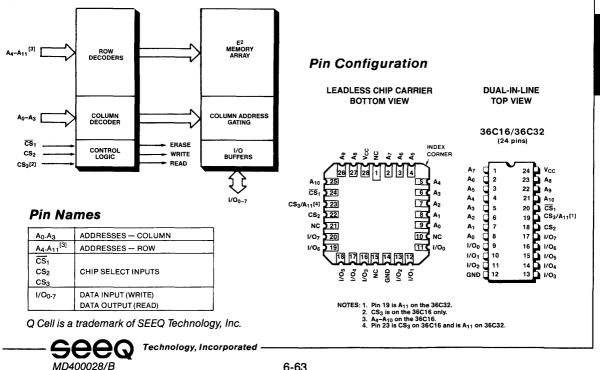

| M36C16/M36C32           | High Speed CMOS Bipolar PROM Replacement 6-63         |

| E36C16/E36C32           | High Speed CMOS Bipolar PROM Replacement              |

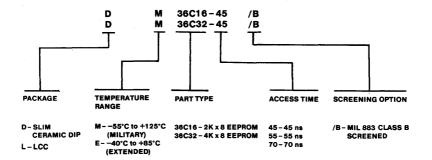

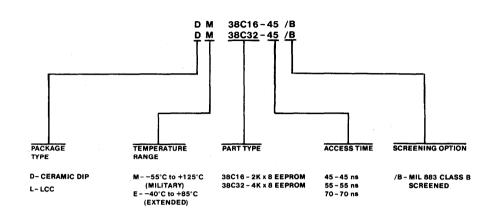

| M38C16/M38C32           | High Speed CMOS                                       |

| E38C16/E38C32           | High Speed CMOS                                       |

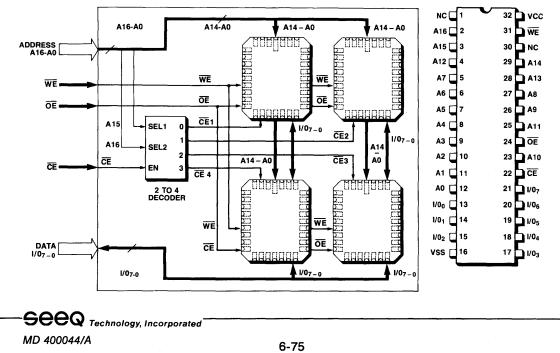

| Module M28C010          | 1024K Electrically Erasable PROM6-75                  |

#### **EPROMs**

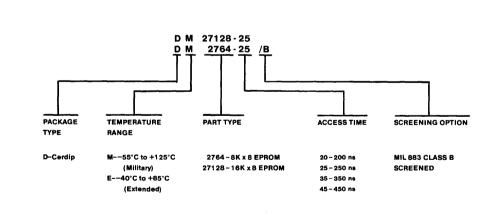

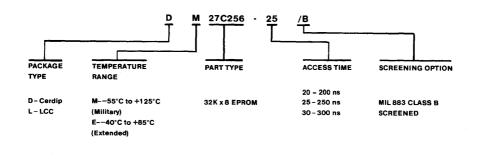

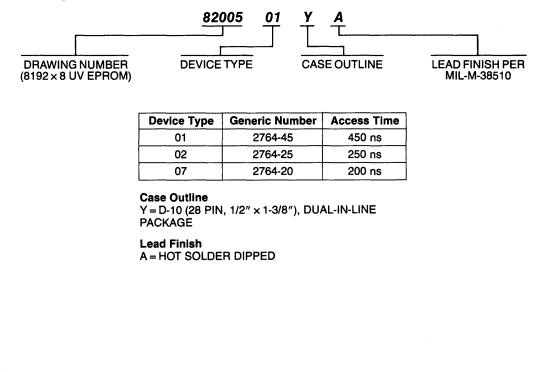

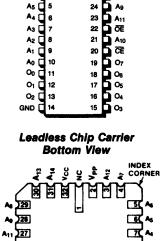

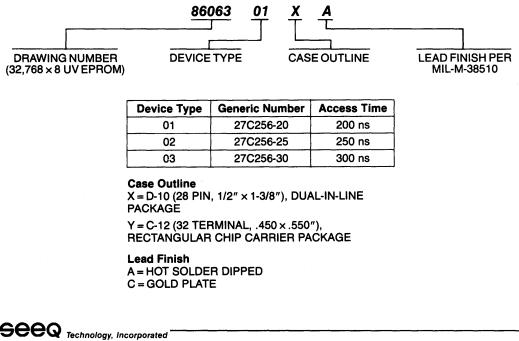

M2764 E2764 M27128 E27128 M27C256 E27C256 82005 82025 86063

| 64K                                         |

|---------------------------------------------|

| 64K ( – 40° to 85°C)                        |

| 128K                                        |

| 128K ( – 40° to 85°)6-83                    |

| 256K CMOS                                   |

| 256K CMOS (-40° to 85°C)                    |

| DESC SMD-Compliant 64K ÚV EPROM6-99         |

| DESC SMD-Compliant 122K UV EPROM6-103       |

| DESC SMD-Compliant 256K CMOS UV EPROM 6-107 |

#### FLASH

7

| E/M48F512 | 512K CMOS FLASH EEPROM  |       |

|-----------|-------------------------|-------|

| E/M48F010 | 1024K CMOS FLASH EEPROM | 6-123 |

# RELIABILITY

| SEEQ EEPROM Reliability Report          | <br> | <br> |  |

|-----------------------------------------|------|------|--|

| Radiation and MOS Non-Volatile Memories |      |      |  |

| Memory Products Reliability Note 1      | <br> | <br> |  |

ဂ္ဂ

Ĵ

# APPLICATIONS

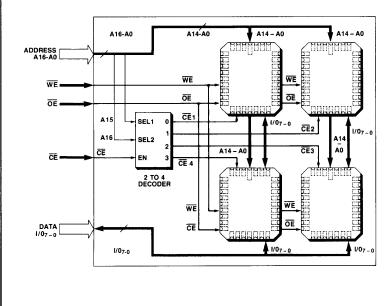

| Note 2  | Microprocessor Interfacing With                        |

|---------|--------------------------------------------------------|

|         | SEÈQ's Latched EEPROM8-1                               |

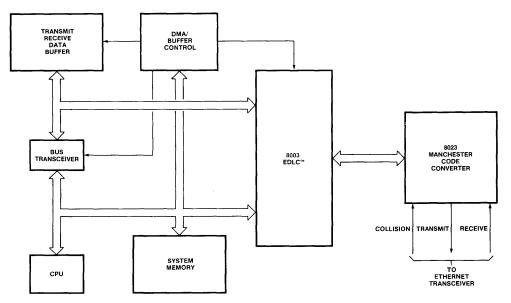

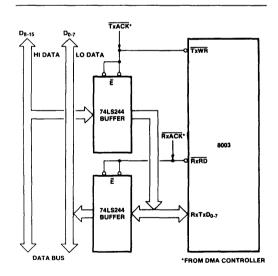

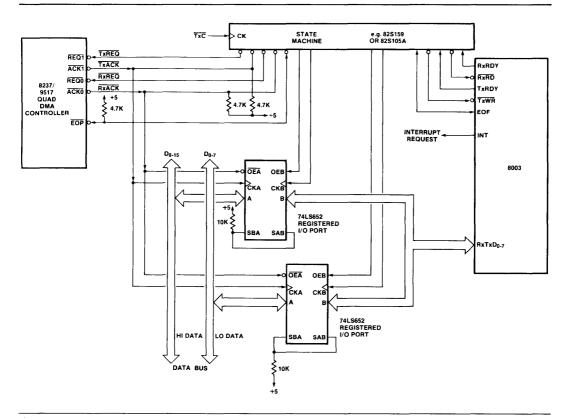

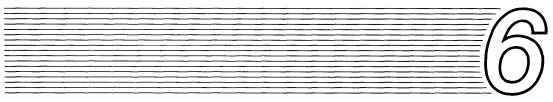

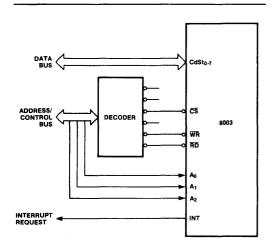

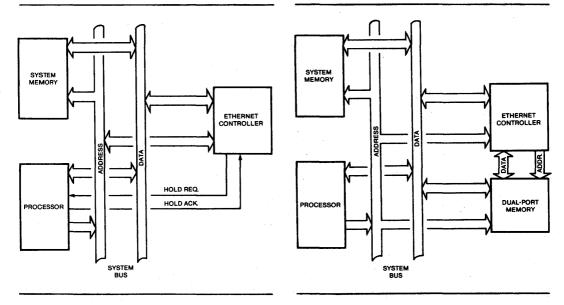

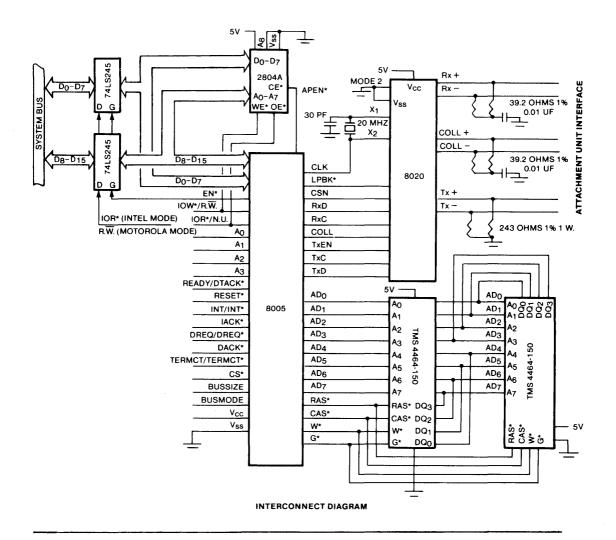

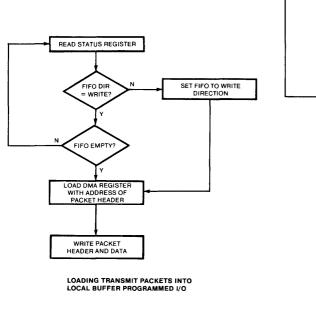

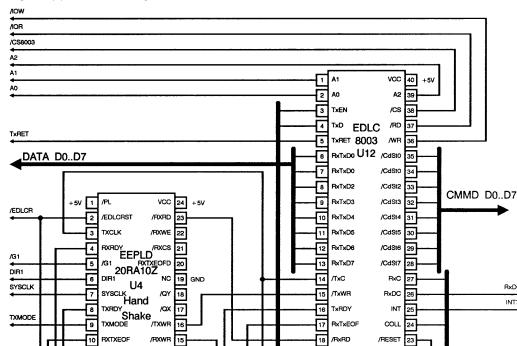

| Note 5  | Interfacing The 8003 EDLC <sup>®</sup> To A 16-Bit Bus |

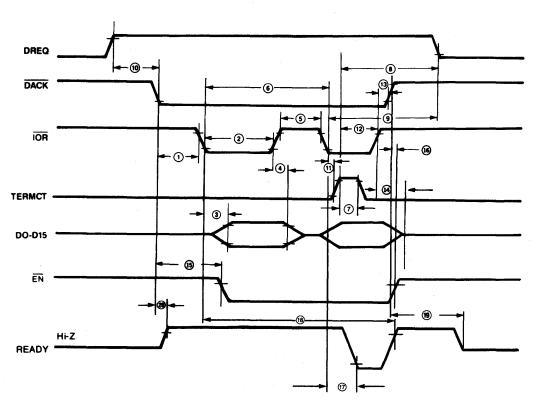

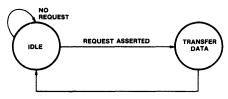

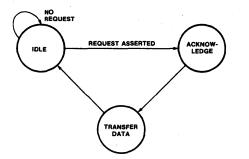

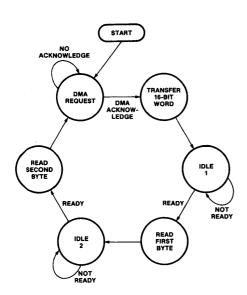

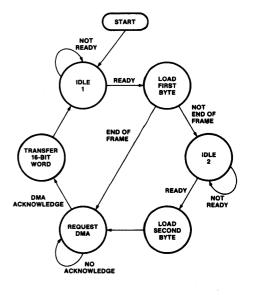

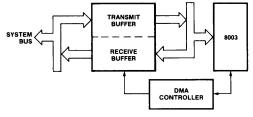

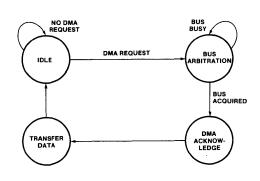

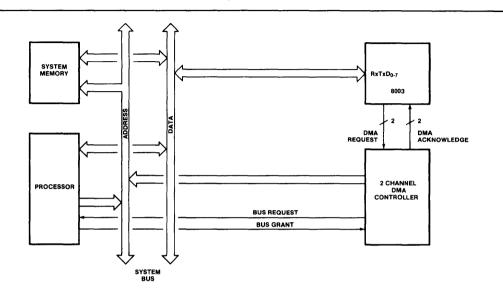

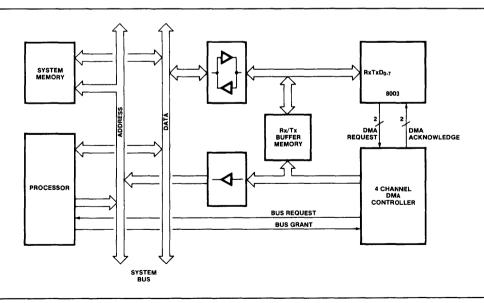

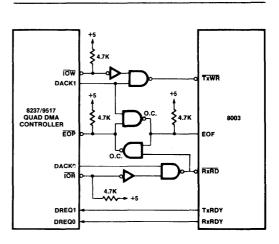

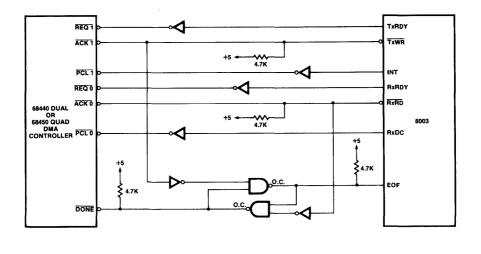

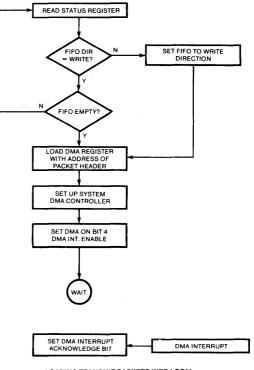

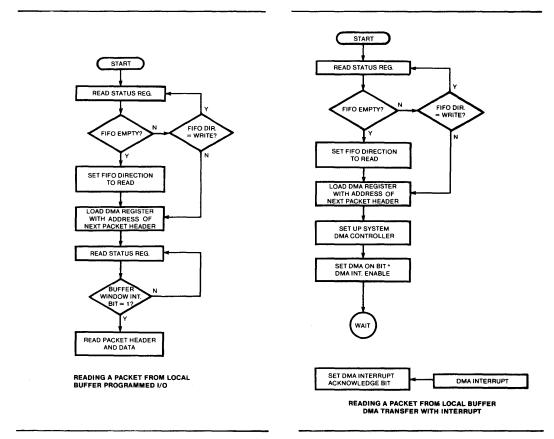

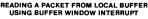

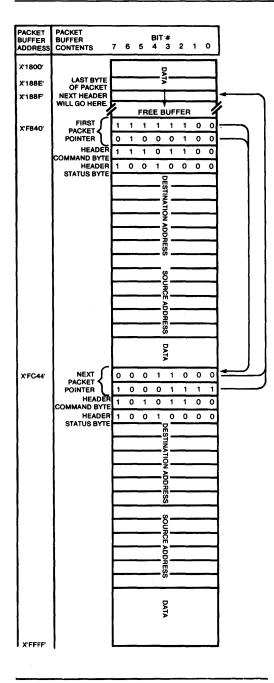

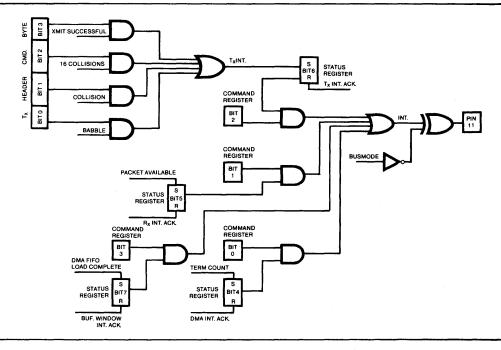

| Note 6  | DMA Interconnection To The 8003 EDLC <sup>®</sup> 8-19 |

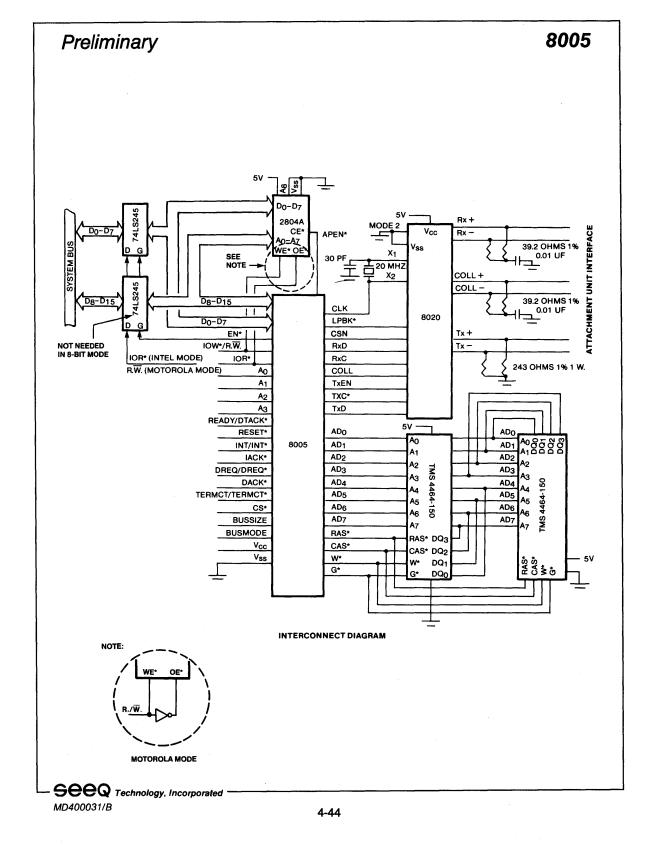

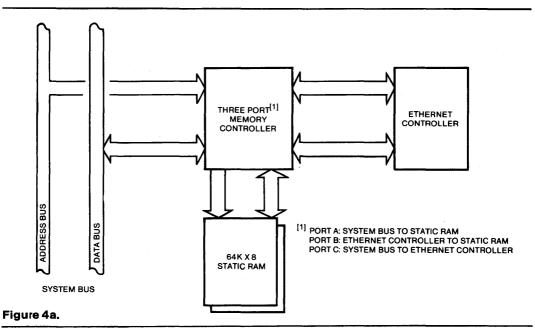

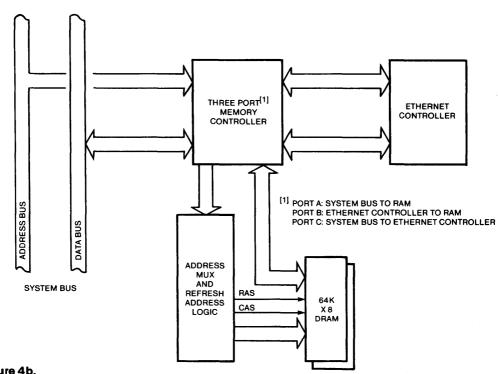

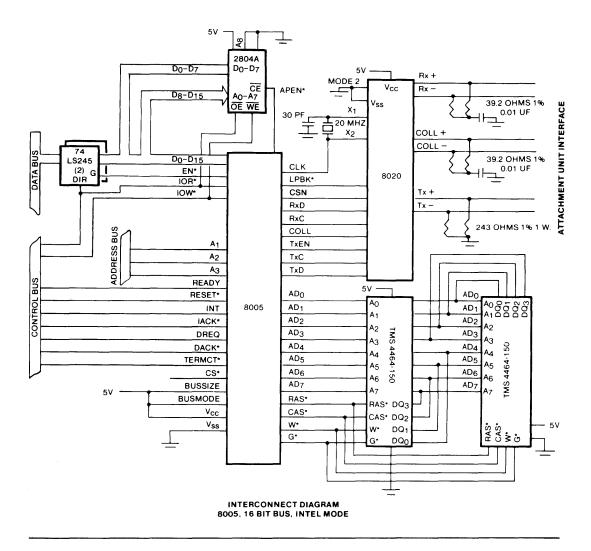

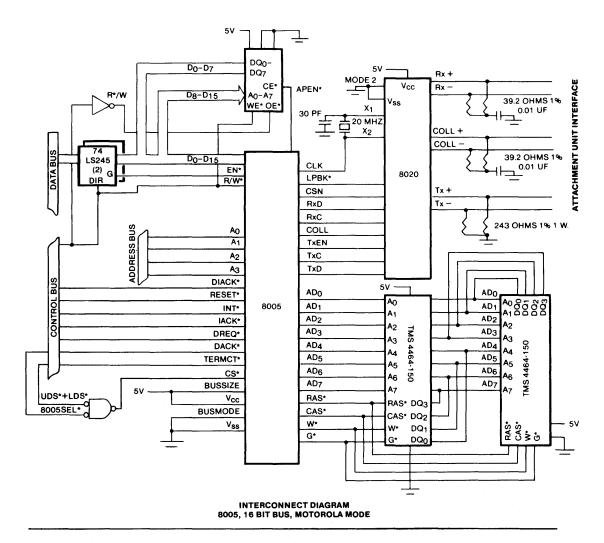

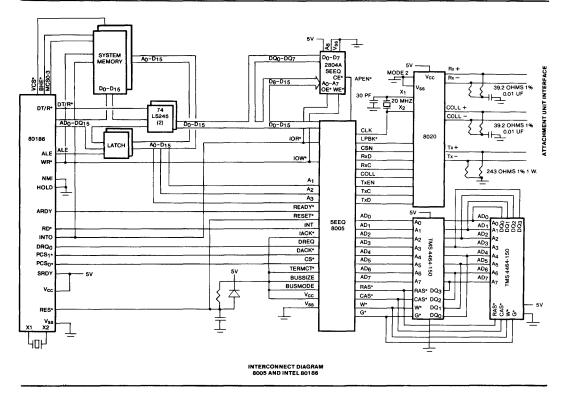

| Note 7  | 8005 Advanced EDLC <sup>®</sup> Users Guide            |

| Note 8  | EEPROM Interfacing8-49                                 |

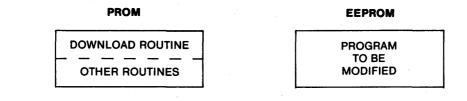

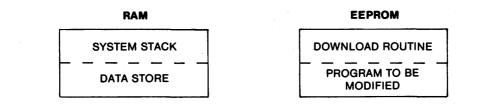

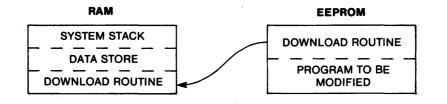

| Note 9  | Software Downline Load Using                           |

|         | SEEQ'S CMOS EEPROMS                                    |

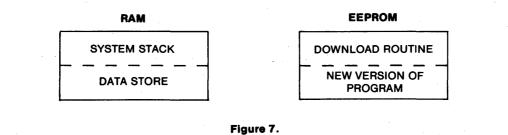

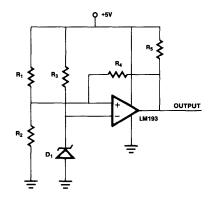

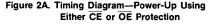

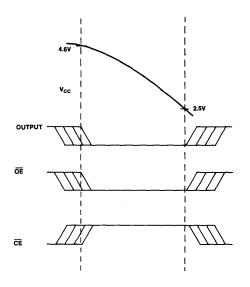

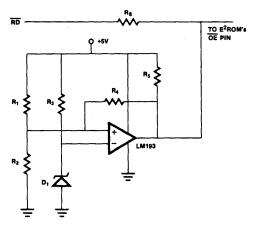

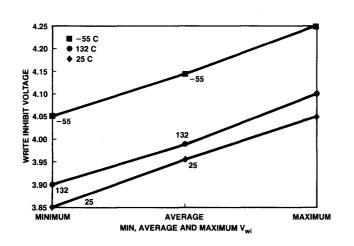

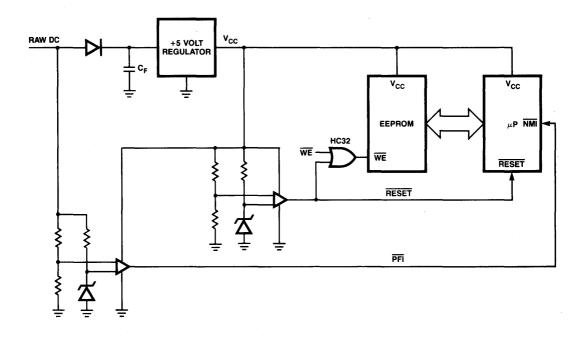

| Note 10 | Power-Up/Down With SEEQ's EEPROM                       |

| Note 11 | Power Fail Protection With SEEQ's CMOS EEPROMs         |

| Note 24 | EEPROM As A Substitute For Bubble Memory               |

| Note 27 | Using High Speed CMOS EEPROMs With                     |

|         | High Performance Microprocessors                       |

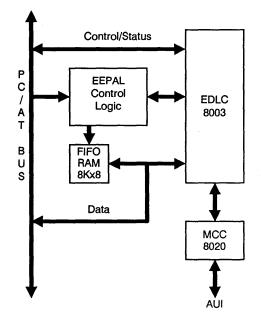

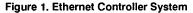

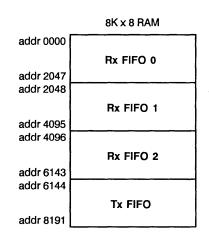

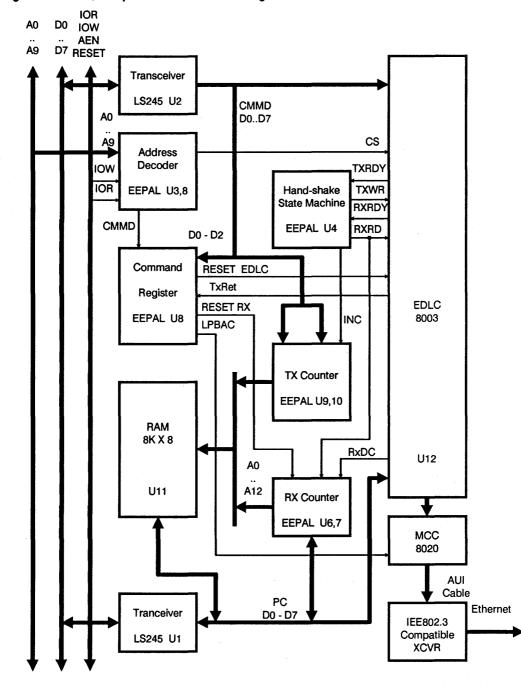

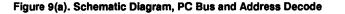

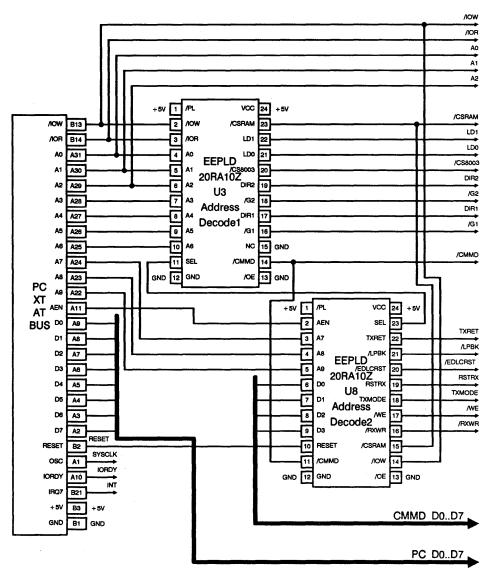

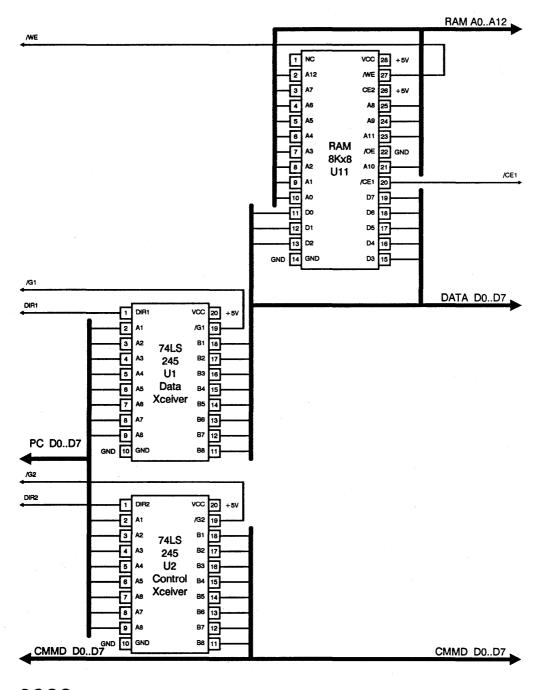

| Note 28 | EEPLDs Interface IBM PC BUS With The EDLC® 80038-103   |

|         |                                                        |

# GENERAL INFORMATION

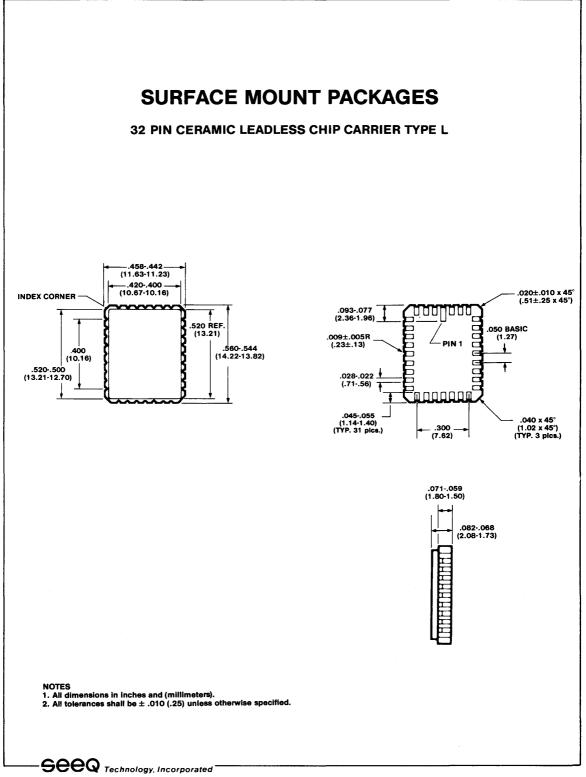

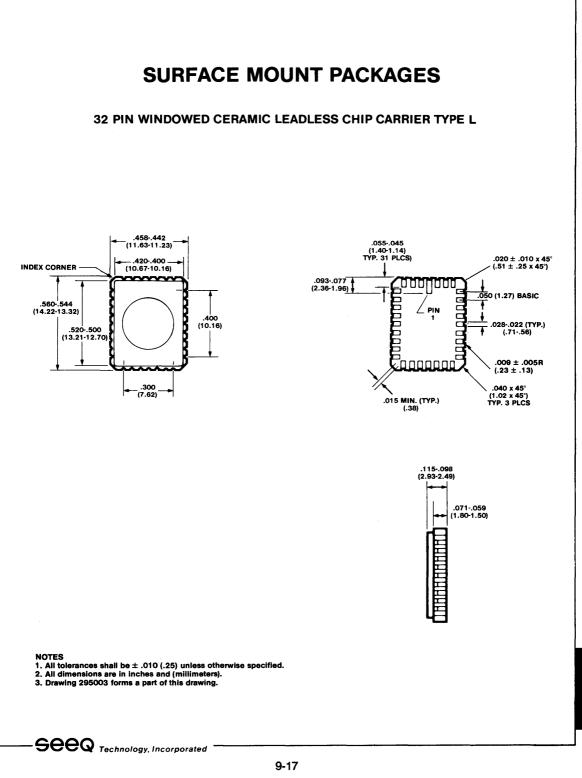

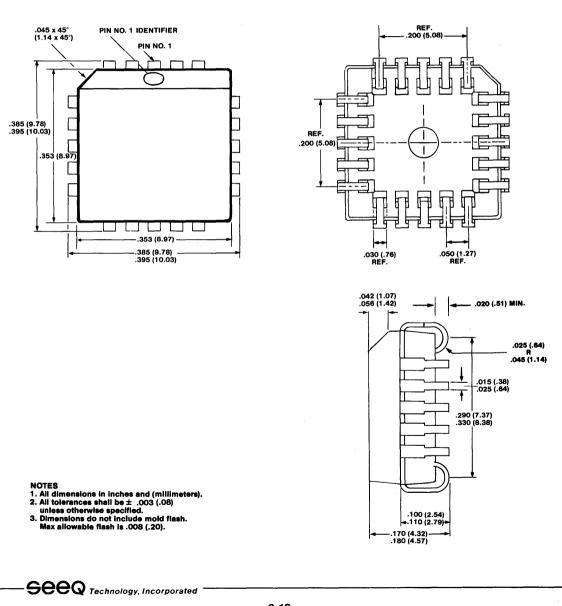

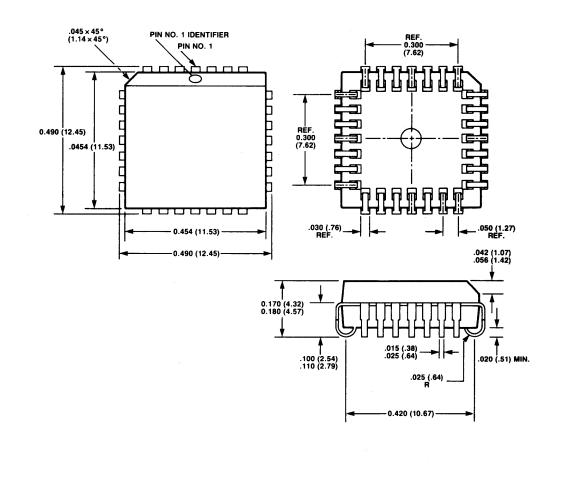

| Thermal Resistance                      |     |

|-----------------------------------------|-----|

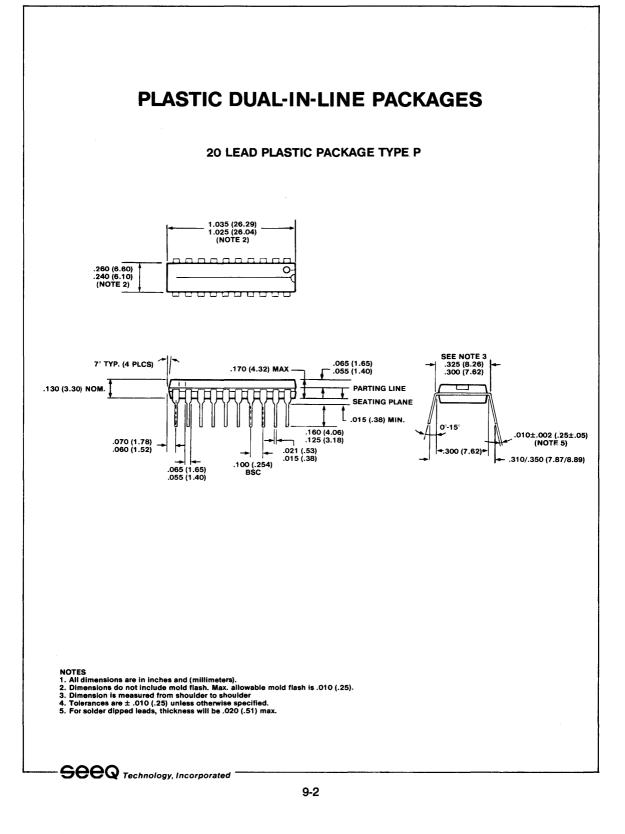

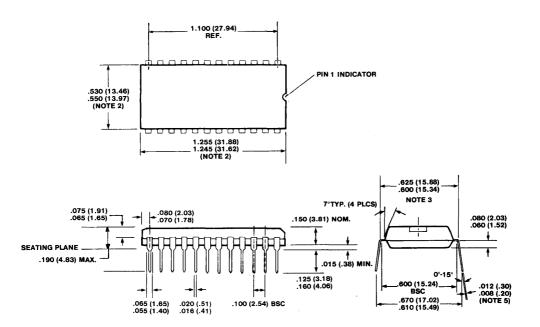

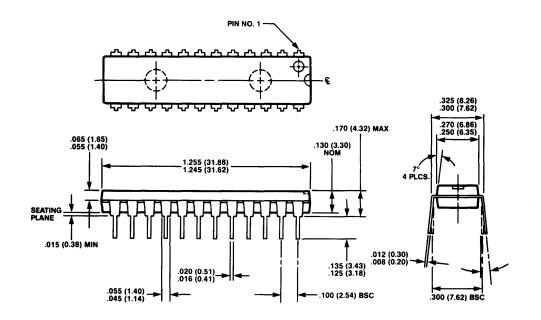

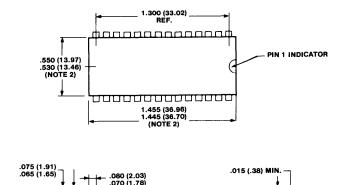

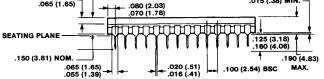

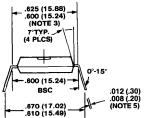

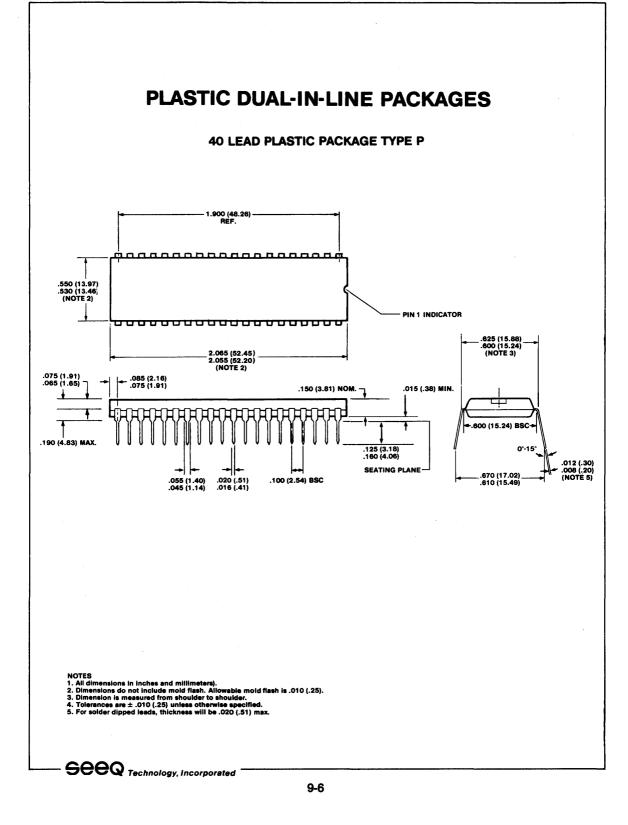

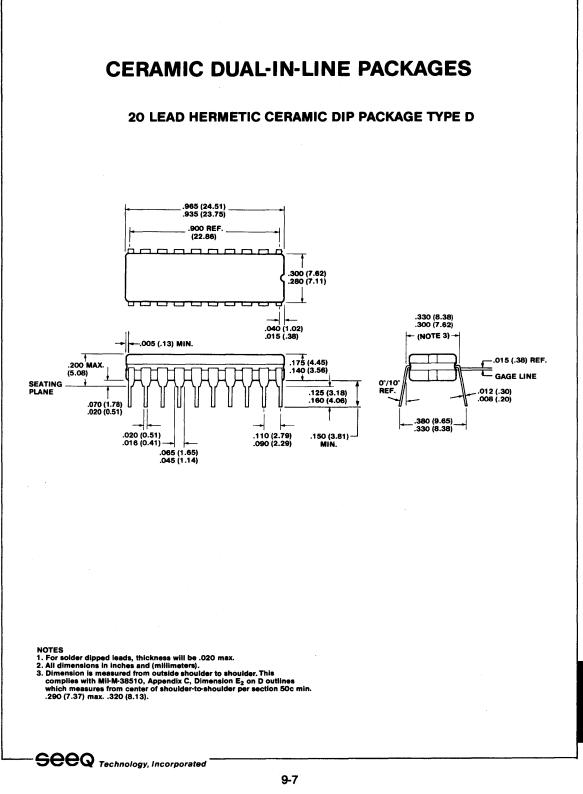

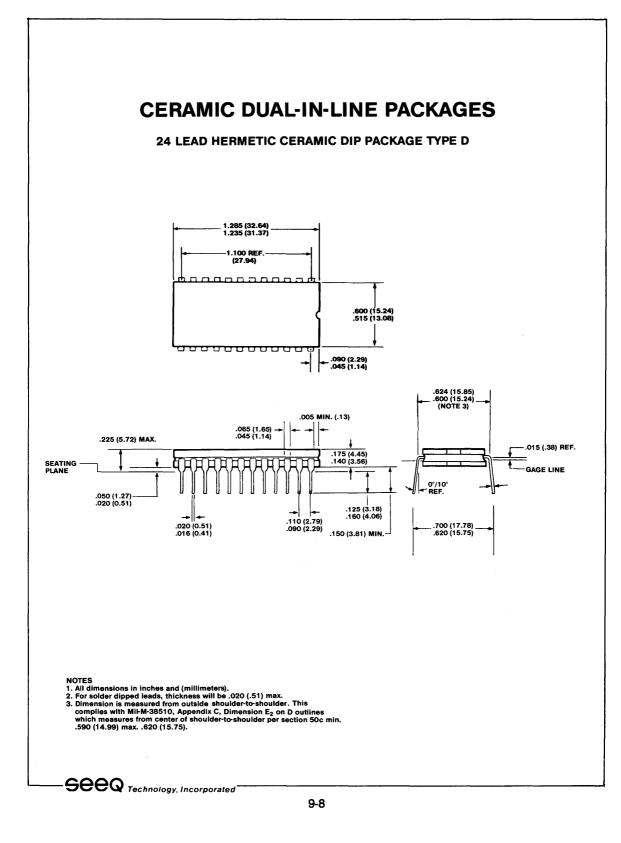

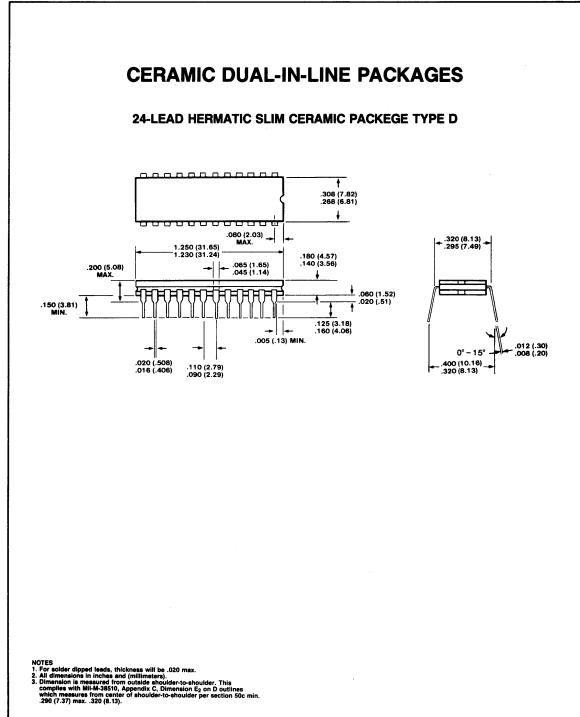

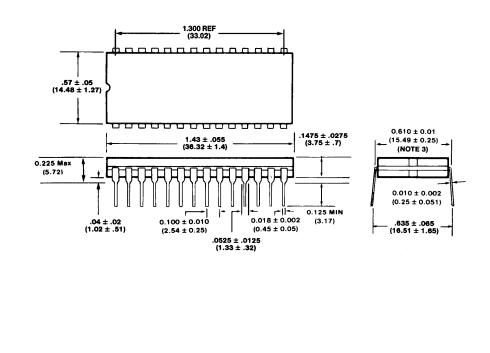

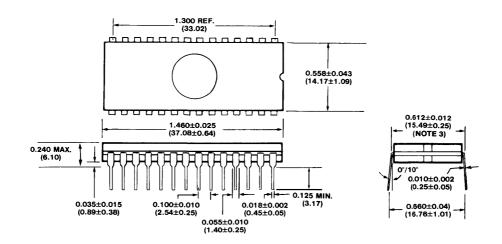

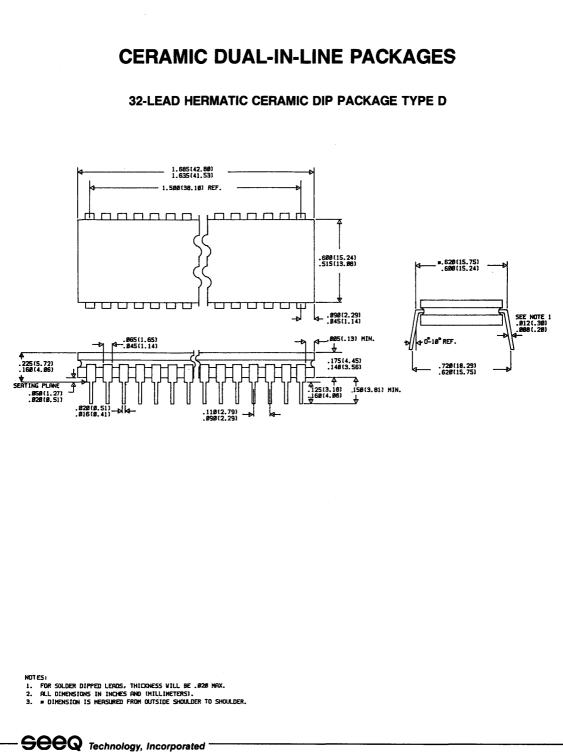

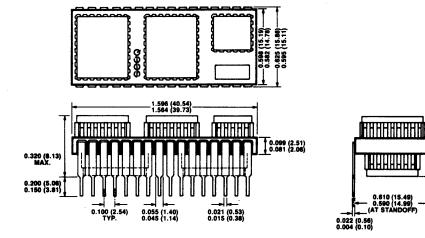

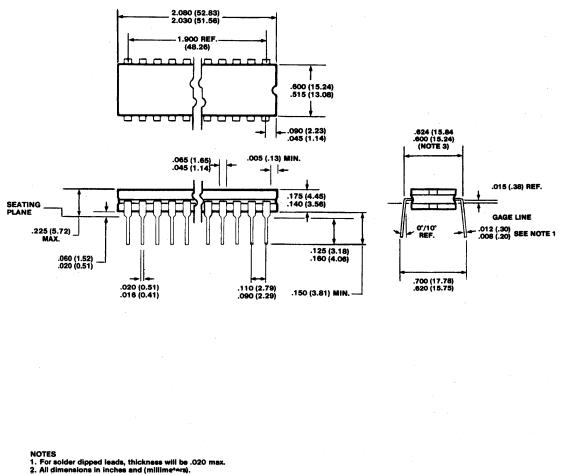

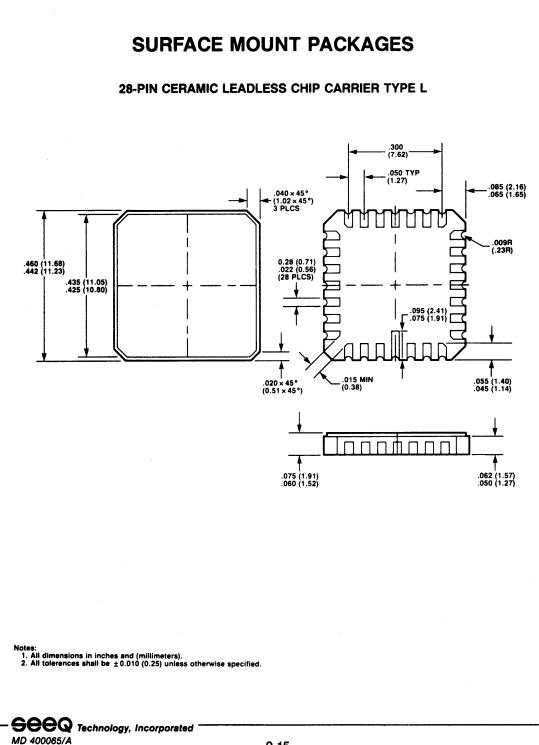

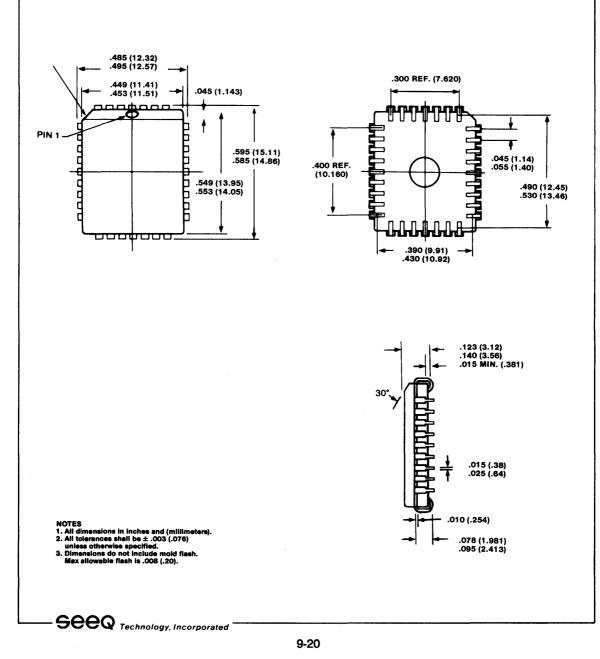

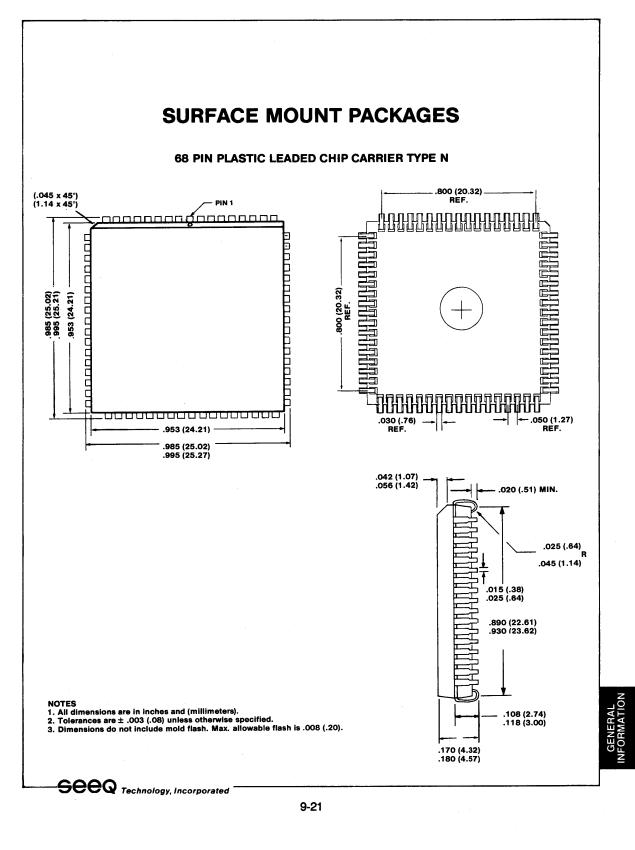

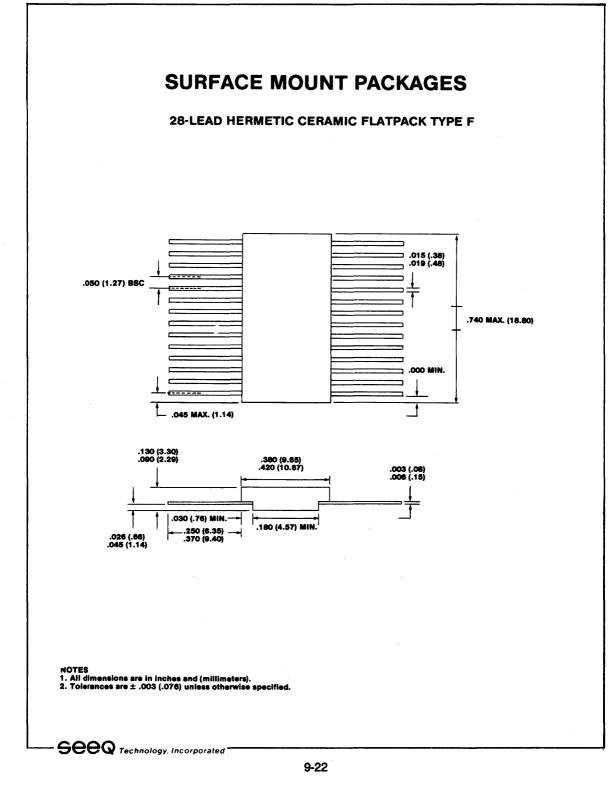

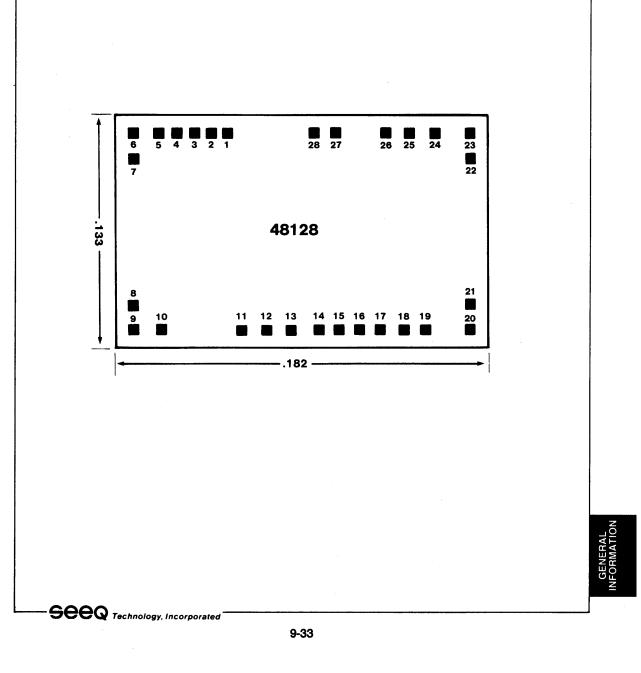

| Packaging Information                   | 9-1 |

| Package Diagrams                        |     |

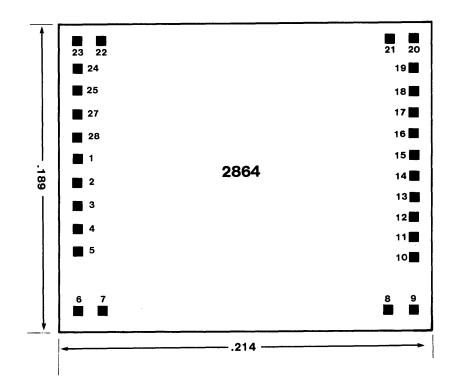

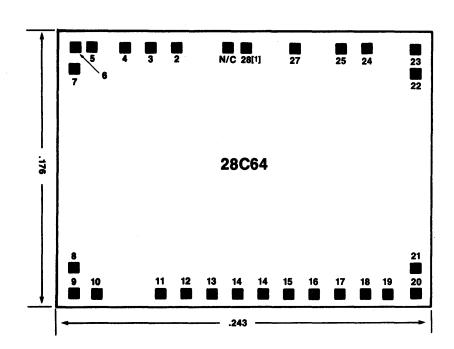

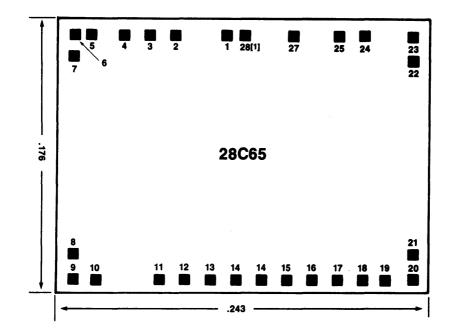

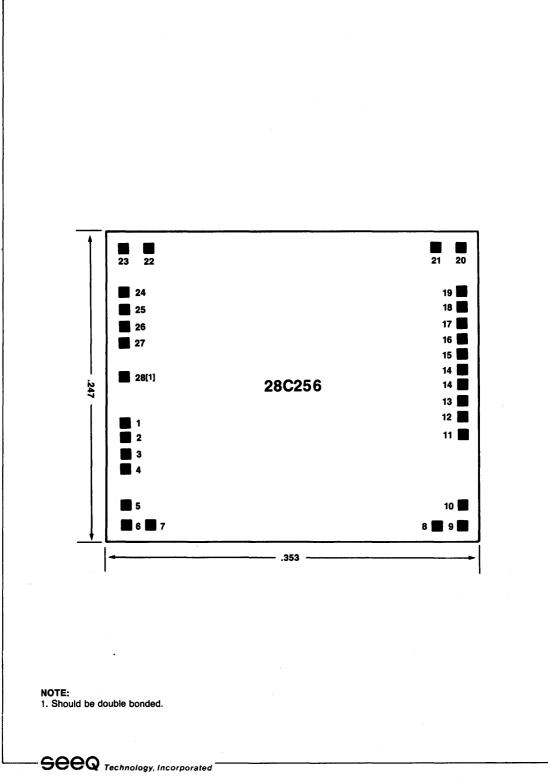

| Bonding Diagrams                        |     |

| Domestic Sales/Rep. Office Listing      |     |

| Distributor Listing                     |     |

| International Sales/Rep. Office Listing |     |

vi

SEEQ is your link to the future.

As the acknowledged leader in thin film EEPROM technology, we continue to advance the state of the art. SEEQ's full-featured EEPROM family leads the industry— and enhances your system applications through ever-greater performance and higher endurance.

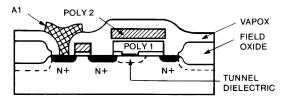

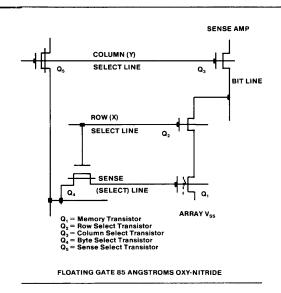

Our clustered product strategy uses this EE technology to tie together a group of focused system solutions, high-density EEPROMs and EPROMs, our popular new high-speed FLASH<sup>™</sup> EEPROMs, EEPLDs and more. Each of these product disciplines uses the proprietary SEEQ base memory technology, as well as versions of our proprietary Q Cell memory design.

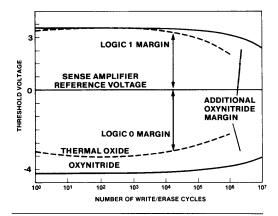

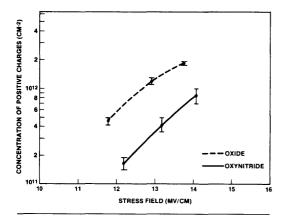

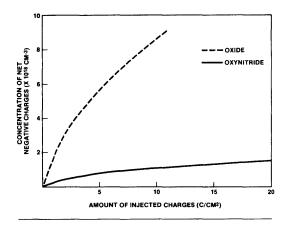

This unique cell design, combined with our proprietary oxynitride process, results in the most reliable EEPROMs available. For example, endurance failure rates on our 5516A ( $2K \times 8$  EEPROM) are  $\leq .001\%$  per 1,000 cycles (guaranteed for a minimum of 1 million write/erase cycles). This represents a profound advance over typical failure rates of .05% per 1,000 hours with intrinsic MOS.

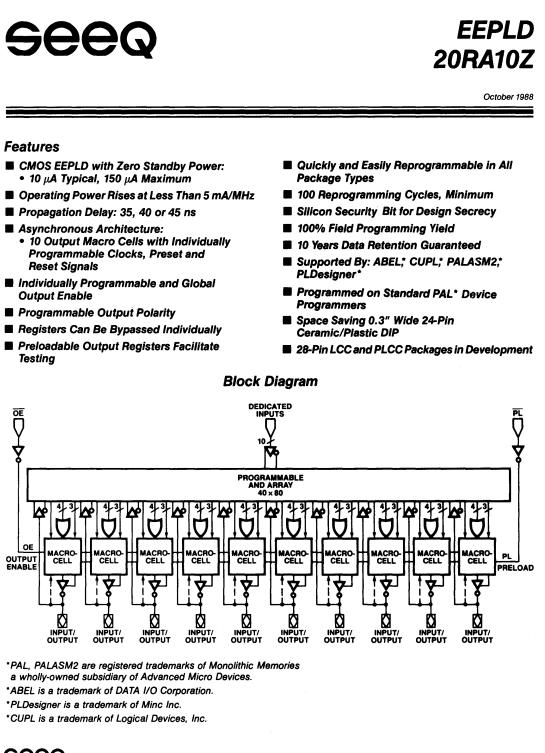

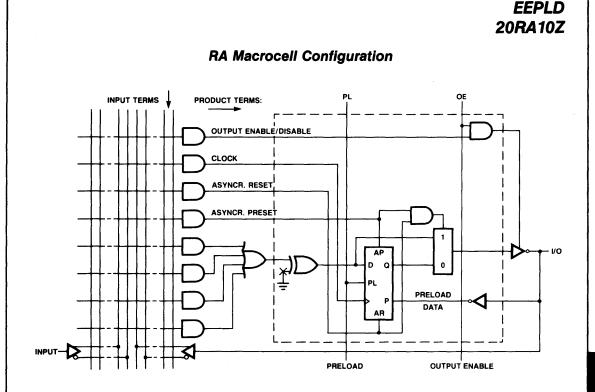

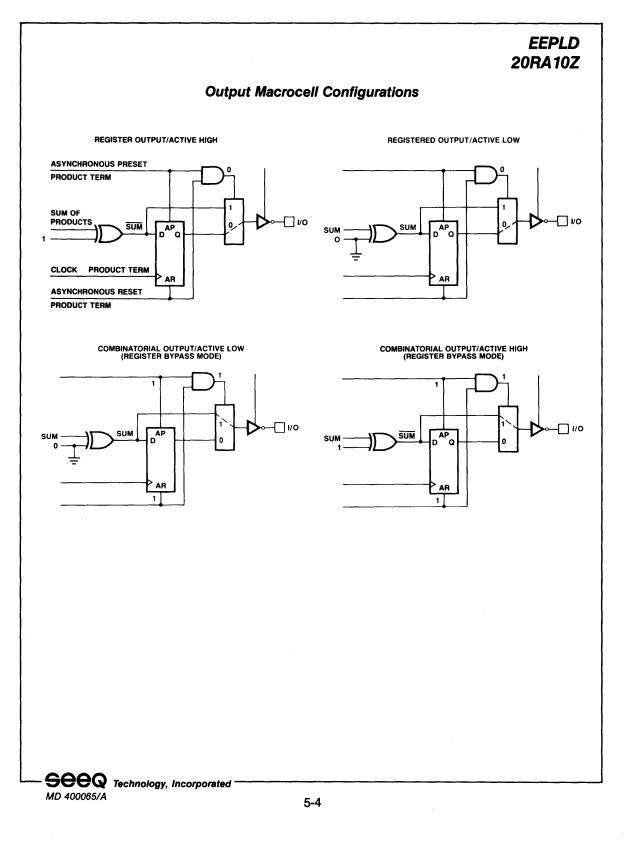

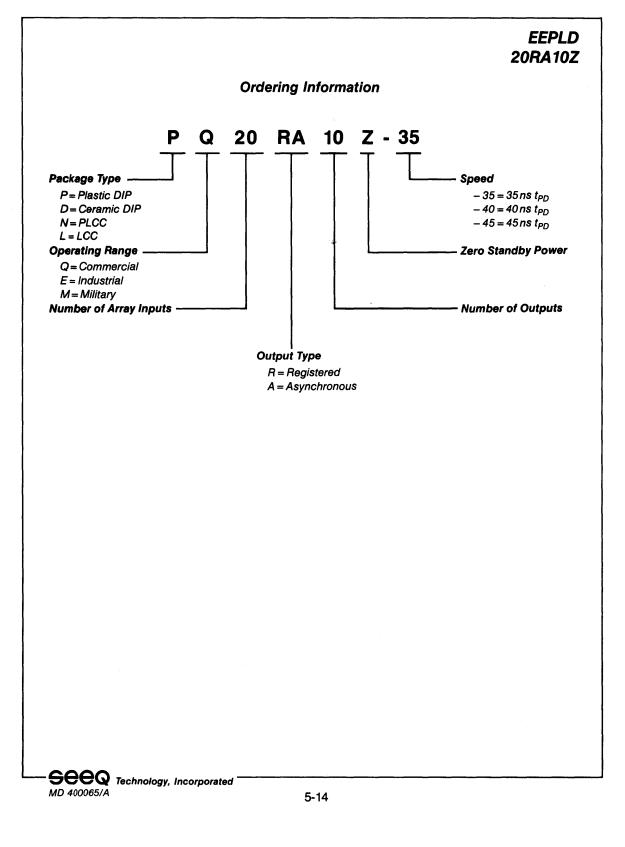

SEEQ has now also expanded into two important new product areas: bipolar PROM replacements and EEPALs (our new 20RA10Z). Keeping pace with our customer's needs, we have also developed an important new family of Ethernet controller parts—newest is the 8005 data link controller.

Best known of all is SEEQ's FLASH family of high-density EPROMs and EEPROMs. These devices combine the in-circuit reprogrammability of traditional EEPROMs with the high density until now associated only with UVEPROMs.

Packaging of our products includes standard dual in-line packages and a variety of surface mount options. SEEQ products may be ordered in plastic, ceramic dip, LCC, PLCC, flatpack or if you wish, unencapsulated die.

Serving our customers, advancing technology, opening new markets—these are what keep us at the forefront of our industry. Let SEEQ be your link to the future. Call us today for your design solution.

J. Daniel McCranie President and CEO

viii

**Product Previews** contain information on products under development. These specifications nay be changed at any time, without notice.

Advance Data Sheets contain target product specifications which are subject to change upon device characterization over the full specified temperature range. These specifications may be changed at any time, without notice.

**Preliminary Data Sheets** contain minimum and maximum limits specified over the full tempprature range based upon initial production device characterization. These specifications may be changed at any time, without notice.

Additional copies of this manual or other SEEQ literature may be obtained from:

SEEQ Technology Incorporated Literature Department 1849 Fortune Drive San Jose, CA 95131

The following are trademarks of SEEQ Technology and may only be used to identify SEEQ products:

SEEQ<sup>®</sup> Silicon Signature<sup>®</sup> EDLC<sup>®</sup> DiTrace<sup>®</sup> MCC<sup>™</sup> FLASH<sup>™</sup> Q Cell<sup>™</sup>

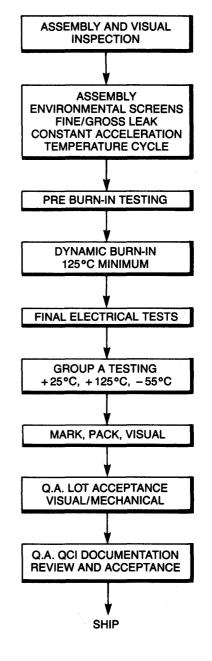

Assembly locations: Military products are assembled at SEEQ's offshore (Korea, Phillippines, Taiwan) and stateside assembly plants. The assembly plants are identified by a designated alpha code as part of the device backside marking. The alpha codes used are: Korea = K, Philippines = P, Taiwan = T, United States = US.A.

Applications for any integrated circuits contained in this publication are for illustration purposes only and SEEQ makes no representation or waranty that such applications will be suitable for the use specified.

Circuit diagrams are included as a means of illustrating typical applications, and complete information for construction purposes is not necessarily given. The information presented here has been carefully checked, and is believed to be entirely reliable, but no responsibility is assumed for inaccuracies. Furthermore, no responsibility is assumed by SEEQ Technology, Inc., for use; not for any infringements of patents or other rights of third parties, which may result from its use. No license is granted by implication, or otherwise, under any patent or patent rights of SEEQ Technology, Inc.

Products of SEEQ may not be used as critical components in Life Support Systems without the express written authorization of the President and Vice-President of Quality/Reliability of SEEQ Technology, Inc.

A critical component is any component whose failure to perform its intended function, could possibly lead to loss of life, or bodily harm.

Life Support Systems that may include but are not necessarily limited to:

- 1) Surgical implants in a human body,

- 2) Equipment used to sustain human life, or

- 3) Equipment used to monitor and/or measure human body conditions.

SEEQ Technology makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

SEEQ retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

A "For Reference Only" specification on a purchase order denotes the designated specification is for reference by the customer and is not invoked on the manufacturer.

х

# SEEQ Technology Product Selection Guide

#### **4K EEPROMs**

| PART   | ORGANIZATION | 1 .      |        |         |       |   |   | DATA SHEET |              |        |

|--------|--------------|----------|--------|---------|-------|---|---|------------|--------------|--------|

| NUMBER |              | TIME(ns) | ACTIVE | STANDBY | RANGE | P | D | IN         | ILF          | PAGE # |

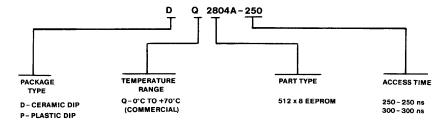

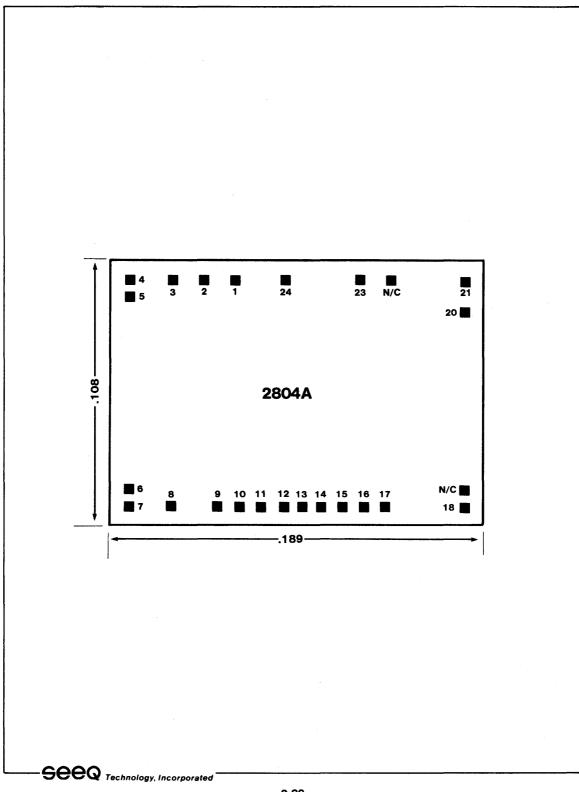

| 2804A  | 512 x 8      | 250      | 80     | 40      | C,E,M | • | • |            |              | 1-19   |

| 2804A  | 512 x 8      | 300      | 80     | 40      | C,E,M | • | • |            |              | 1-19   |

| 2804A  | 512 x 8      | 350      | 80     | 40      | C,E,M | • | • |            | $\mathbf{T}$ | 1-19   |

#### **16K EEPROMs**

| PART<br>NUMBER | ORGANIZATION | ACCESS<br>TIME(ns) | ICC MA | X. (mA*)<br>STANDBY | TEMP<br>RANGE |   |   |   |   | <br>DATA SHEET<br>PAGE # |

|----------------|--------------|--------------------|--------|---------------------|---------------|---|---|---|---|--------------------------|

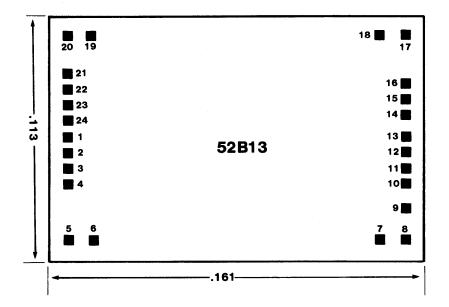

| 52B13          | 2K x 8       | 200                | 80     | 30                  | С             | • | • |   | Γ | 1-3                      |

| 52B13          | 2K x 8       | 250                | 80     | 30                  | C, E, M       | • | • |   |   | 1-3, 6-7                 |

| 52B13          | 2K x 8       | 300                | 80     | 30                  | м             | • | • |   |   | 1-3, 6-7                 |

| 52B13          | 2K x 8       | 350                | 80     | 30                  | C, E          | • | • | Γ |   | 1-3, 6-7                 |

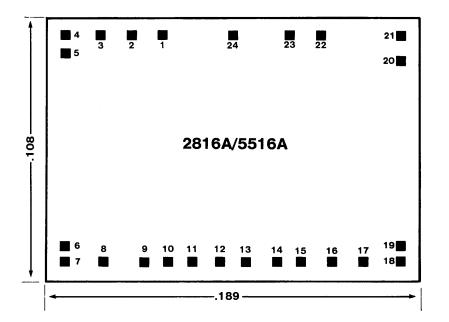

| 2816A          | 2K x 8       | 200                | 110    | 40                  | С             | • | • |   |   | 1-25                     |

| 2816A          | 2K x 8       | 250                | 110    | 40                  | C, E, M       | • | • |   |   | 1-25, 6-21               |

| 2816A          | 2K x 8       | 300                | 110    | 40                  | C, E, M       | • | • |   |   | 1-25, 6-21               |

| 2816A          | 2K x 8       | 350                | 110    | 40                  | С             | • | • |   |   | 1-25                     |

| 5516A          | 2K x 8       | 200                | 110    | 40                  | С             |   | • |   |   | 1-25                     |

| 5516A          | 2K x 8       | 250                | 110    | 40                  | С             | Τ | • | Γ |   | 1-25                     |

| 5516A          | 2K x 8       | 300                | 110    | 40                  | С             |   | • | Γ |   | 1-25                     |

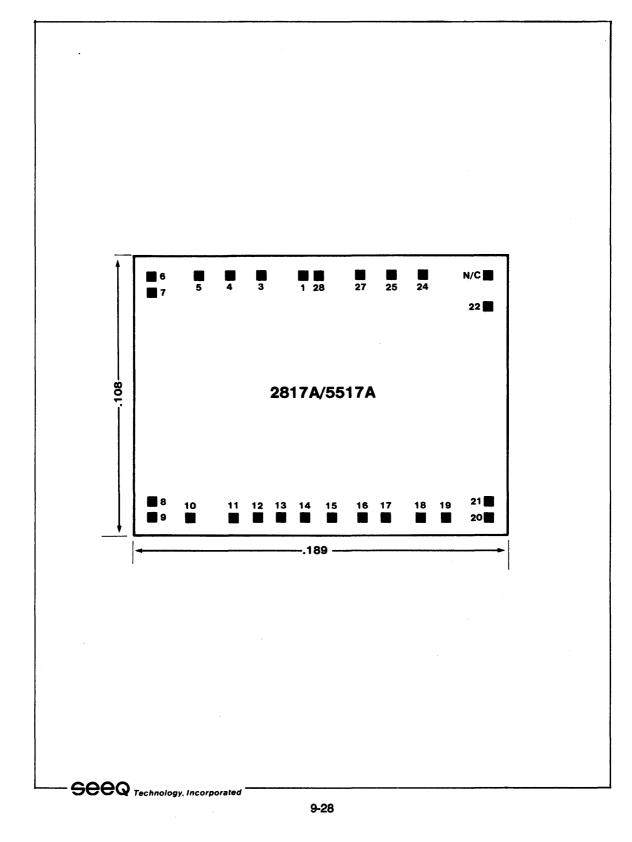

| 2817A          | 2K x 8       | 200                | 110    | 40                  | С             | • | • |   |   | 1-31                     |

| 2817A          | 2K x 8       | 250                | 110    | 40                  | C, E, M       | • | • |   |   | 1-31, 6-27               |

| 2817A          | 2K x 8       | 300                | 110    | 40                  | C, E, M       | • | • |   |   | 1-31, 6-27               |

| 2817A          | 2K x 8       | 350                | 110    | 40                  | С             | • | • |   |   | 1-31                     |

| 5517A          | 2K x 8       | 250                | 110    | 40                  | С             |   | • |   |   | 1-31                     |

| 5517A          | 2K x 8       | 300                | 110    | 40                  | C             |   | • |   |   | 1-31                     |

#### **TEMPERATURE RANGE**

$C = Commercial 0^{\circ}C to +70^{\circ}C$

$E = Extended - 40^{\circ}C \text{ to } + 85^{\circ}C$

M = Military -55°C to +125°C

TBD = To Be Determined

\*Commercial Temperature Range

#### PACKAGE

P = Plastic Dip

- D = Ceramic Dip

- N = Plastic Leaded Chip Carrier

- L = Ceramic Leadless Chip Carrier

- F = Flat Pack

- M = Module

#### 64K EEPROMs

| PART<br>NUMBER | ORGANIZATION | ACCESS<br>TIME (ns) | ICC M<br>ACTIVE | AX. (mA*)<br>STANDBY | TEMP<br>RANGE |   |   |   |   | DATA SHEET<br>PAGE # |            |

|----------------|--------------|---------------------|-----------------|----------------------|---------------|---|---|---|---|----------------------|------------|

| 52B33          | 8K x 8       | 200                 | 110             | 40                   | С             | • | • |   |   |                      | 1-11       |

| 52B33          | 8K x 8       | 250                 | 110             | 40                   | C, E, M       | • | • |   | • |                      | 1-11, 6-15 |

| 52B33          | 8K x 8       | 300                 | 110             | 40                   | C, E, M       | • | • | Ι | • |                      | 1-11, 6-15 |

| 52B33          | 8K x 8       | 350                 | 110             | 40                   | С             | • | • | Ι | Ι |                      | 1-11       |

| 2864           | 8K x 8       | 250                 | 110             | 40                   | C, E, M       | • | • | • | • | •                    | 1-37, 6-33 |

| 2864           | 8K x 8       | 300                 | 110             | 40                   | C, E, M       | • | • | • | • | •                    | 1-37, 6-33 |

| 2864           | 8K x 8       | 350                 | 110             | 40                   | C, E, M       | • | • | • | • | •                    | 1-37, 6-33 |

| 28C64          | 8K x 8       | 200                 | 50              | .150                 | C, E, M       | • | • | • | • |                      | 1-43, 6-39 |

| 28C64          | 8K x 8       | 250                 | 50              | .150                 | C, E, M       | • | • | • | • |                      | 1-43, 6-39 |

| 28C64          | 8K x 8       | 300                 | 50              | .150                 | C, E, M       | • | • | • | • |                      | 1-43, 6-39 |

| 28C64          | 8K x 8       | 350                 | 50              | .150                 | C, E, M       | • | • | • | • |                      | 1-43, 6-39 |

| 28C65          | 8K x 8       | 200                 | 50              | .150                 | C, E, M       | • | • | • | • |                      | 1-51, 6-46 |

| 28C65          | 8K x 8       | 250                 | 50              | .150                 | C, E, M       | • | • | • | • |                      | 1-51, 6-46 |

| 28C65          | 8K x 8       | 300                 | 50              | .150                 | C, E, M       | • | • | • | • |                      | 1-51, 6-46 |

| 28C65          | 8K x 8       | 350                 | 50              | .150                 | C, E, M       | • | • | • | • |                      | 1-51, 6-46 |

#### 256K EEPROMs

| PART   | ORGANIZATION | ACCESS    | ICC M  | AX. (mA*) | TEMP PACK |   |   |   | AG | E | DATA SHEET |

|--------|--------------|-----------|--------|-----------|-----------|---|---|---|----|---|------------|

| NUMBER |              | TIME (ns) | ACTIVE | STANDBY   | RANGE     | Ρ | D | Ν | L  | F | PAGE #     |

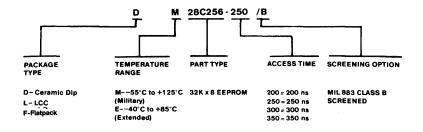

| 28C256 | 32K x 8      | 200       | 60     | .150      | C, E, M   | • | • | • | •  | • | 1-59, 6-55 |

| 28C256 | 32K x 8      | 250       | 60     | .150      | C, E, M   | • | • | • | •  | • | 1-59, 6-55 |

| 28C256 | 32K x 8      | 300       | 60     | .150      | C, E, M   | • | • | • | •  | ٠ | 1-59, 6-55 |

| 28C256 | 32K x 8      | 350       | 60     | .150      | C, E, M   | • | • | • | •  | • | 1-59, 6-55 |

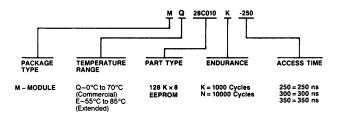

#### 1024K EEPROMs

| PART<br>NUMBER | ORGANIZATION | ACCESS<br>TIME (ns) |    |   |         |   |            |

|----------------|--------------|---------------------|----|---|---------|---|------------|

| M28C010        | 128K x 8     | 250                 | 70 | 2 | C, E, M | • | 1-85, 6-75 |

| M28C010        | 128K x 8     | 300                 | 70 | 2 | C, E, M | • | 1-85, 6-75 |

| M28C010        | 128K x 8     | 350                 | 70 | 2 | C, E, M | • | 1-85, 6-75 |

#### **TEMPERATURE RANGE**

$C = Commercial 0^{\circ}C to + 70^{\circ}C$

- $E = Extended 40^{\circ}C to + 85^{\circ}C$

- $M = Military 55^{\circ}C to + 125^{\circ}C$

TBD = To Be Determined

\*Commercial Temperature Range

## PACKAGE

- P = Plastic Dip

- D = Ceramic Dip

- N = Plastic Leaded Chip Carrier

- L = Ceramic Leadless Chip Carrier

- F = Flat Pack

- $\mathbf{M} = \mathbf{Module}$

## FLASH<sup>™</sup> EEPROMS

| PART   | ORGANIZATION             | ACCESS    | ICC M  | AX. (mA*) | TEMP    | F | A | ж | ٩G | E | DATA SHEET  |

|--------|--------------------------|-----------|--------|-----------|---------|---|---|---|----|---|-------------|

| NUMBER |                          | TIME (ns) | ACTIVE | STANDBY   | RANGE   | P | D | N | L  | F | PAGE #      |

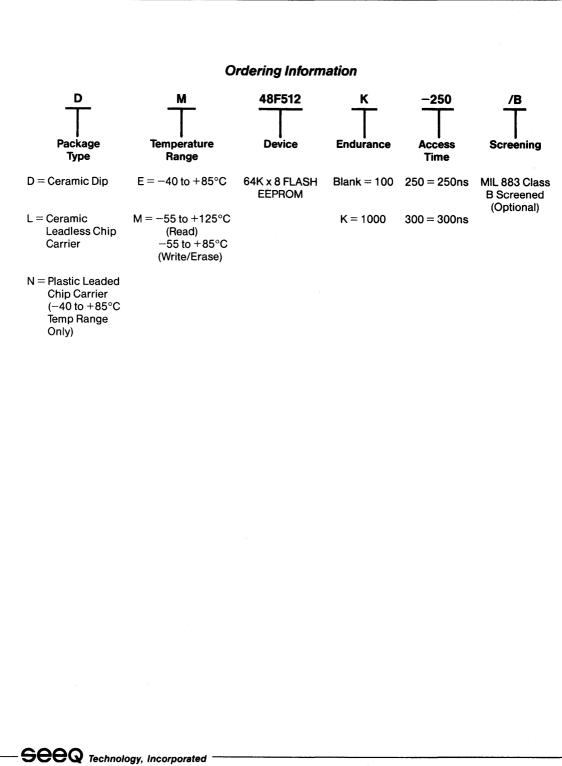

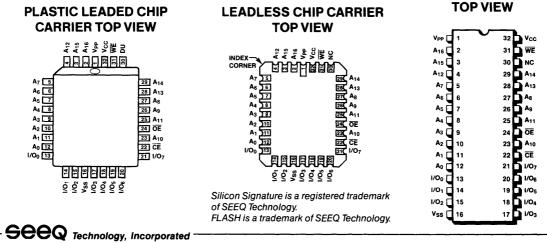

| 48F512 | 64K x 8                  | 200       | 60     | .100      | С       | • | • | • |    |   | 2-1         |

| 48F512 | 64K x 8                  | 250       | 60     | .100      | C, E, M | • | • | • | •  |   | 2-1, 6-111  |

| 48F512 | 64K x 8                  | 300       | 60     | .100      | C, E, M | • | • | ٠ | •  |   | 2-1, 6-111  |

| 48F010 | 128K x 8                 | 200       | 60     | .100      | С       | • | • | • |    |   | 2-13        |

| 48F010 | 128K x 8                 | 250       | 60     | .100      | C, E, M | • | • | • | •  |   | 2-13, 6-123 |

| 48F010 | 128K x 8                 | 300       | 60     | .100      | C, E, M | • | • | • | •  |   | 2-13, 6-123 |

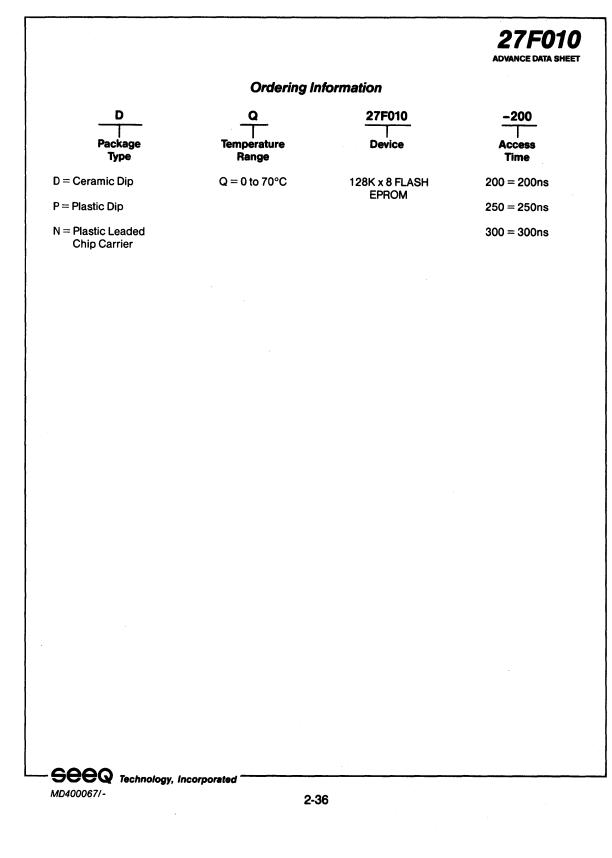

| 27F010 | 128K x 8                 | 200       | 60     | .100      | С       | • | • | ٠ |    |   | 2-25        |

| 27F010 | 128K x 8                 | 250       | 60     | .100      | С       | • | • | • |    |   | 2-25        |

| 27F010 | 128K x 8                 | 300       | 60     | .100      | С       | • | • | ٠ |    |   | 2-25        |

| KT48   | FLASH<br>PROGRAMMING KIT |           |        |           |         |   |   |   |    |   | 2-37        |

## HIGH SPEED 16K EEPROMs

| PART<br>NUMBER | ORGANIZATION | ACCESS<br>TIME (ns) | ICC M | AX. (mA*)<br>STANDBY | TEMP<br>RANGE | 1 - |   | СК/<br> N |   |           | DATA SHEET<br>PAGE # |

|----------------|--------------|---------------------|-------|----------------------|---------------|-----|---|-----------|---|-----------|----------------------|

| 36C16          | 2K x 8       | 35                  | 80    | -                    | С             | •   | • | t         | T | $\square$ | 1-71                 |

| 36C16          | 2K x 8       | 40                  | 80    | _                    | С             | •   | • |           | Ī | $\square$ | 1-71                 |

| 36C16          | 2K x 8       | 45                  | 80    | _                    | C, E, M       | •   | • | 1         | • |           | 1-71, 6-63           |

| 36C16          | 2K x 8       | 55                  | 80    | _                    | C, E, M       | •   | • |           | • |           | 1-71, 6-63           |

| 36C16          | 2K x 8       | 70                  | 80    | -                    | E, M          |     | ٠ |           | • |           | 6-63                 |

| 38C16          | 2K x 8       | 35                  | 80    | 40                   | С             | •   | ٠ | ٠         |   |           | 1-77                 |

| 38C16          | 2K x 8       | 40                  | 80    | 40                   | С             | •   | • | •         |   | Π         | 1-77                 |

| 38C16          | 2K x 8       | 45                  | 80    | 40                   | C, E, M       | •   | ٠ | •         | • |           | 1-77, 6-69           |

| 38C16          | 2K x 8       | 55                  | 80    | 40                   | C, E, M       | •   | • | •         | • | Π         | 1-77, 6-69           |

| 38C16          | 2K x 8       | 70                  | 80    | 40                   | E, M          |     | • | T         | • |           | 6-69                 |

## HIGH SPEED 32K EEPROMs

| PART<br>NUMBER | ORGANIZATION | ACCESS<br>TIME (ns) | ICC M | AX. (mA*)<br>STANDBY | TEMP<br>RANGE | - |   | CK/ |   | E<br> F | DATA SHEET<br>PAGE # |

|----------------|--------------|---------------------|-------|----------------------|---------------|---|---|-----|---|---------|----------------------|

| 36C32          | 4K x 8       | 35                  | 80    | _                    | С             | • | • | T   | t |         | 1-71                 |

| 36C32          | 4K x 8       | 40                  | 80    | -                    | С             | • | • |     |   | Π       | 1-71                 |

| 36C32          | 4K x 8       | 45                  | 80    | _                    | C, E, M       | • | • |     | • | Π       | 1-71, 6-63           |

| 36C32          | 4K x 8       | 55                  | 80    | -                    | C, E, M       | • | • |     | • | Π       | 1-71, 6-63           |

| 36C32          | 4K x 8       | 70                  | 80    | -                    | E, M          |   | • | T   | • | Π       | 6-63                 |

| 38C32          | 4K x 8       | 35                  | 80    | 40                   | С             | • | • | •   |   | Π       | 1-77                 |

| 38C32          | 4K x 8       | 40                  | 80    | 40                   | С             | • | • | •   |   | Π       | 1-77                 |

| 38C32          | 4K x 8       | 45                  | 80    | 40                   | C, E, M       | • | • | •   | • | Π       | 1-77, 6-69           |

| 38C32          | 4K x 8       | 55                  | 80    | 40                   | C, E, M       | • | • | •   | • |         | 1-77, 6-69           |

| 38C32          | 4K x 8       | 70                  | 80    | 40                   | E, M          | • | • | •   | • |         | 6-69                 |

FLASH is a trademark of SEEQ Technology Inc.

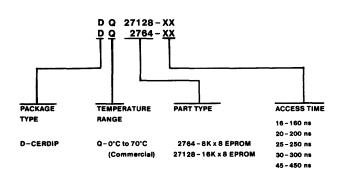

# 64K/128K/256K UVEPROMs

| PART<br>NUMBER | ORGANIZATION | ACCESS<br>TIME (ns) | ICC M<br>ACTIVE | AX. (mA*)<br>STANDBY | TEMP<br>RANGE | 1. |   | K/<br>N |   | <br>DATA SHEET<br>PAGE # |

|----------------|--------------|---------------------|-----------------|----------------------|---------------|----|---|---------|---|--------------------------|

| 2764           | 8K x 8       | 160                 | 100             | 30                   | С             |    | • |         |   | 3-1                      |

| 2764           | 8K x 8       | 200                 | 100             | 30                   | C, E, M       |    | • |         |   | 3-1, 6-83                |

| 2764           | 8K x 8       | 250                 | 100             | 30                   | C, E, M       | Τ  | • |         |   | 3-1, 6-83                |

| 2764           | 8K x 8       | 300                 | 100             | 30                   | С             |    | • |         |   | 3-1                      |

| 2764           | 8K x 8       | 350                 | 100             | 30                   | E, M          | Ţ  | • |         |   | 6-83                     |

| 2764           | 8K x 8       | 450                 | 100             | 30                   | C, E, M       | Τ  | • |         |   | 3-1, 6-83                |

| 27128          | 16K x 8      | 200                 | 100             | 30                   | C, E, M       |    | • |         | • | 3-1, 6-83                |

| 27128          | 16K x 8      | 250                 | 100             | 30                   | C, E, M       |    | • |         | • | 3-1, 6-83                |

| 27128          | 16K x 8      | 300                 | 100             | 30                   | С             |    | • |         |   | 3-1                      |

| 27128          | 16K x 8      | 350                 | 100             | 30                   | E, M          |    | • |         | • | 6-83                     |

| 27128          | 16K x 8      | 450                 | 100             | 30                   | C, E, M       |    | • |         | • | 3-1, 6-83                |

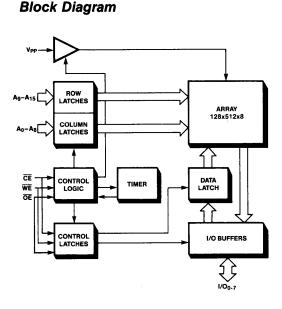

| 27C256         | 32K x 8      | 200                 | 50              | .150                 | C, E, M       |    | • |         | • | 3-9, 6-91                |

| 27C256         | 32K x 8      | 250                 | 50              | .150                 | C, E, M       |    | • |         | • | 3-9, 6-91                |

| 27C256         | 32K x 8      | 300                 | 50              | .150                 | C, E, M       |    | • |         | • | 3-9, 6-91                |

| 27C256         | 32K x 8      | 450                 | 50              | .150                 | С             |    | • |         |   | 3-9                      |

## **DESC-COMPLIANT UVEPROMS**

| PART   | ORGANIZATION | ACCESS    | ICC M  | AX. (mA*) | TEMP  | P | ٩C | KA | GE DATA S |   | DATA SHEET |

|--------|--------------|-----------|--------|-----------|-------|---|----|----|-----------|---|------------|

| NUMBER |              | TIME (ns) | ACTIVE | STANDBY   | RANGE | P | D  | Ν  | L         | F | PAGE #     |

| 82005  | 8K x 8       | 200       | 100    | 30        | М     |   | •  |    |           |   | 6-99       |

| 82005  | 8K x 8       | 250       | 100    | 30        | М     |   | •  |    |           |   | 6-99       |

| 82005  | 8K x 8       | 450       | 100    | 30        | М     |   | •  |    |           |   | 6-99       |

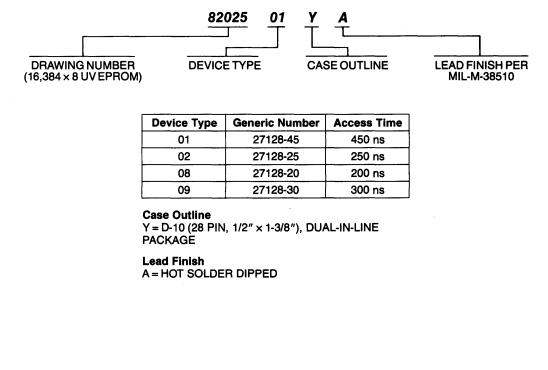

| 82025  | 16K x 8      | 200       | 100    | 30        | М     |   | •  |    | •         |   | 6-103      |

| 82025  | 16K x 8      | 250       | 100    | 30        | М     |   | •  |    | •         |   | 6-103      |

| 82025  | 16K x 8      | 300       | 100    | 30        | М     |   | •  |    | •         |   | 6-103      |

| 82025  | 16K x 8      | 450       | 100    | 30        | М     |   | •  |    | •         |   | 6-103      |

| 86063  | 32K x 8      | 200       | 50     | .150      | М     |   | •  |    | •         |   | 6-107      |

| 86063  | 32K x 8      | 250       | 50     | .150      | М     |   | •  |    | •         |   | 6-107      |

| 86063  | 32K x 8      | 300       | 50     | .150      | М     |   | •  |    | •         |   | 6-107      |

## **COMMUNICATION PRODUCTs**

| PART<br>NUMBER | ICC MAX.         TEMP         PACKA           ACTIVE (mA*)         RANGE         P D N |   | <br> | DATA SHEET<br>PAGE # |                                           |      |

|----------------|----------------------------------------------------------------------------------------|---|------|----------------------|-------------------------------------------|------|

| 8003           | 200                                                                                    | С | ••   |                      | Ethernet Data Link<br>Controller          | 4-1  |

| 8020           | 75                                                                                     | С | ••   | •                    | 10 MHz Manchester<br>Encoder/Decoder      | 4-13 |

| 8023A          | 75                                                                                     | C | ••   | •                    | 10 MHz Manchester<br>Encoder/Decoder      | 4-27 |

| 8005           | 350                                                                                    | С |      | •                    | Advanced Ethernet Data<br>Link Controller | 4-43 |

#### **CMOS EEPLDs**

| PART       | DESCRIPTION  | PINS | SPEED                | ICC MA | AX. (mA*) | TEMP       | PACKAGE |   |   | AG | ìΕ | DATA SHEET |

|------------|--------------|------|----------------------|--------|-----------|------------|---------|---|---|----|----|------------|

| NUMBER     |              |      | t <sub>PD</sub> (ns) | ACTIVE | STANDBY   | RANGE      | Ρ       | D | N | L  | F  | PAGE #     |

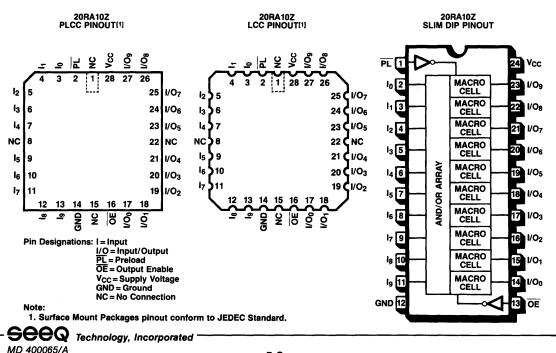

| 20RA10Z-35 | Asynchronous | 24   | 35                   | 25**   | .150      | C***       | •       | • | • | •  |    | 5-1        |

| 20RA10Z-40 | Asynchronous | 24   | 40                   | 25**   | .150      | C;*** E, M | •       | • | • | •  |    | 5-1        |

| 20RA10Z-45 | Asynchronous | 24   | 45                   | 25**   | .150      | C;*** E, M | •       | • | • | •  |    | 5-1        |

|            |              |      |                      |        |           |            |         |   |   |    |    |            |

|            |              |      |                      |        |           |            |         |   |   |    |    |            |

|            |              |      |                      |        |           |            |         |   |   |    |    |            |

#### **TEMPERATURE RANGE**

$C = Commercial 0^{\circ}C to +70^{\circ}C$  $E = Extended -40^{\circ}C to +85^{\circ}C$

$M = Military - 55^{\circ}C to + 125^{\circ}C$

TBD = To Be Determined

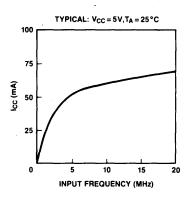

\*Commercial Temperature Range \*\*f = 1 MHz; 5mA/Additional MHz \*\*\*Commercial 0°C to 75°C

#### PACKAGE

P = Plastic Dip

D = Ceramic Dip

N = Plastic Leaded Chip Carrier

L = Ceramic Leadless Chip Carrier

F = Flat Pack

M = Module

xvi

(Electrically Erasable Programmable Read Only Memories)

# SEEQ Technology EEPROM Alternate Source

| MFG.     | Part No. | Description    | SEEQ Part No. |

|----------|----------|----------------|---------------|

| A.M.D.   | 2817A    | 2K X 8 EEPROM  | 2817A         |

| A.M.D.   | 9864     | 8K X 8 EEPROM  | 2864          |

| A.M.D.   | 2864B    | 8K X 8 EEPROM  | 28C64         |

| ATMEL    | 28C64    | 8K X 8 EEPROM  | 28C64         |

| EXEL     | 2804A    | 512 X 8 EEPROM | 2804A         |

| EXEL     | 46C16-55 | 2K X 8 EEPROM  | 36C16-55      |

| EXEL     | 2816A    | 2K X 8 EEPROM  | 2816A         |

| EXEL     | 2864     | 8K X 8 EEPROM  | 28C64         |

| EXEL     | 2865     | 8K X 8 EEPROM  | 28C65         |

| FUJITSU  | 28C64    | 8K X 8 EEPROM  | 28C64         |

| FUJITSU  | 28C65    | 8K X 8 EEPROM  | 28C65         |

| G.I.     | 28C64    | 8K X 8 EEPROM  | 28C64         |

| HITACHI  | 58064    | 8K X 8 EEPROM  | 52B33         |

| INTEL    | 2816     | 2K X 8 EEPROM  | 52B13         |

| INTEL    | 2816A    | 2K X 8 EEPROM  | 52B13         |

| INTEL    | 2817A    | 2K X 8 EEPROM  | 2817A         |

| NATIONAL | 9816A    | 2K X 8 EEPROM  | 2816A         |

| NATIONAL | 9817A    | 2K X 8 EEPROM  | 2817A         |

| SAMSUNG  | 2816A    | 2K X 8 EEPROM  | 2816A         |

| SAMSUNG  | 2817A    | 2K X 8 EEPROM  | 2817A         |

| XICOR    | 2616     | 2K X 8 EEPROM  | 36C16-45      |

| XICOR    | 2816H    | 2K X 8 EEPROM  | 38C16-45      |

| XICOR    | 2804A    | 512 X 8 EEPROM | 2804A         |

| XICOR    | 2816A    | 2K X 8 EEPROM  | 2816A         |

| XICOR    | 2864A    | 8K X 8 EEPROM  | 28C64         |

| XICOR    | 2864B    | 8K X 8 EEPROM  | 28C64         |

| XICOR    | 28256    | 32K X 8 EEPROM | 28C256        |

SEEQ Technology, Incorporated

# SEEQ Technology PROM Replacement Chart

| MFG.      | Part No.     | Description | SEEQ Part No. |

|-----------|--------------|-------------|---------------|

| A.M.D.    | AM27PS291DC  | 2K X 8 PROM | 36C16-45      |

| A.M.D.    | AM27PS291DM  | 2K X 8 PROM | 36C16-55      |

| A.M.D.    | AM27PS291ADM | 2K X 8 PROM | 36C16-55      |

| A.M.D.    | AM27S291ADC  | 2K X 8 PROM | 36C16-35      |

| CYPRESS   | CY7C291-35   | 2K X 8 PROM | 36C16-35      |

| CYPRESS   | CY7C291-50   | 2K X 8 PROM | 36C16-45      |

| FUJITSU   | MB7138Y-SKZ  | 2K X 8 PROM | 36C16-35      |

| FUJITSU   | MB7138H-SKZ  | 2K X 8 PROM | 36C16-45      |

| FUJITSU   | MB7138E-WZ   | 2K X 8 PROM | 36C16-45      |

| HARRIS    | 6-76161      | 2K X 8 PROM | 36C16-45      |

| M.M.I.    | 63S1681NS    | 2K X 8 PROM | 36C16-45      |

| M.M.I.    | 63S1681ANS   | 2K X 8 PROM | 36C16-35      |

| NATIONAL  | DM77S291     | 2K X 8 PROM | 36C16-55      |

| NATIONAL  | DM87S291     | 2K X 8 PROM | 36C16-55      |

| RAYTHEON  | 29681ASM     | 2K X 8 PROM | 36C16-55      |

| RAYTHEON  | 29681ASC     | 2K X 8 PROM | 36C16-55      |

| RAYTHEON  | 29681SC      | 2K X 8 PROM | 36C16-55      |

| RAYTHEON  | 29683ASC     | 2K X 8 PROM | 36C16-45      |

| RAYTHEON  | 29683ASM     | 2K X 8 PROM | 36C16-55      |

| SIGNETICS | 82S291       | 2K X 8 PROM | 36C16-45      |

| T.I.      | 27C291-35    | 2K X 8 PROM | 36C16-45      |

| T.I.      | 27C291-50    | 2K X 8 PROM | 36C16-45      |

| T.I.      | TBP28S166N   | 2K X 8 PROM | 36C16-45      |

| WAFRSCAL  | 57C291-40    | 2K X 8 PROM | 36C16-35      |

| WAFRSCAL  | 57C291-55    | 2K X 8 PROM | 36C16-55      |

| NATIONAL  | DM87S421     | 4K X 8 PROM | 36C32-55      |

| NATIONAL  | DM87S421A    | 4K X 8 PROM | 36C32-45      |

| NATIONAL  | DM77S421     | 4K X 8 PROM | 36C32-55      |

| NATIONAL  | DM77S421A    | 4K X 8 PROM | 36C32-55      |

| RAYTHEON  | 29671ASC     | 4K X 8 PROM | 36C32-45      |

| RAYTHEON  | 29671ASM     | 4K X 8 PROM | 36C32-55      |

| RAYTHEON  | 29673SC      | 4K X 8 PROM | 36C32-55      |

| RAYTHEON  | 29673SM      | 4K X 8 PROM | 36C32-55      |

SCCQ Technology, Incorporated

1-2

16K Electrically Erasable PROM

October 1988

#### Features

- Input Latches

- **TTL Byte Erase/Byte Write**

Seeg

- 1 ms(52B13H) or 9 ms Byte Erase/Byte Write

- Power Up/Down Protection

- 10,000 Erase/Write Cycles per Byte Minimum

- 5V ± 10% Operation

- Fast Read Access Time 200 ns

- Infinite Number of Read Cycles

- Chip Erase and Byte Erase

- **■** DiTrace<sup>™</sup>

- JEDEC Approved Byte Wide Memory Pinout

- Military And Extended Temperature Range Available

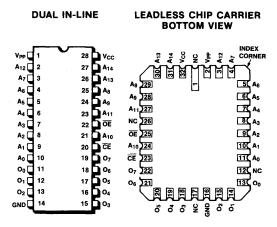

- Direct Replacement For Intel 2816/2816A

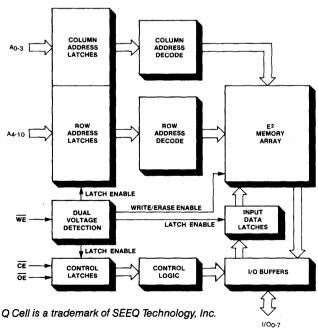

## Description

SEEQ's 52B13 and 52B13H are 2048 x 8 bit, 5 volt electrically erasable programmable read only memories (EEPROM) with input latches on all address, data and control (chip and output enable) lines. Data is latched and electically written by either a TTL or a 21V pulse on the Write Enable pin. Once written, which requires under 10 ms, there is no limit to the number of times data may be read. Both byte and chip erase modes are available. The erasure time in either mode is under 10 ms, and each byte may be erased and written a minimum of 10,000 times. They are direct pin-for-pin replacement for SEEQ's 5213 and Intel 2816/2816A.

The 52B13 and 52B13H are ideal for applications that require a non-volatile memory with in-system write and erase capability. Dynamic reconfiguration (the alteration of operating software in real-time) is made possible by this device. Applications for the 52B13 and 52B13H will be found in military avionics systems, programmable character generators, self-calibrating instruments/

(continued on next page)

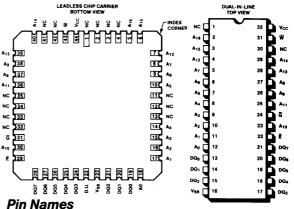

#### Pin Names

| A0-A10 | ADDRESSES                                            |

|--------|------------------------------------------------------|

| CE     | CHIP ENABLE                                          |

| ŌĒ     | OUTPUT ENABLE                                        |

| WE     | WRITE ENABLE                                         |

| 1/00-7 | DATA INPUT (WRITE OR<br>ERASE)<br>DATA OUTPUT (READ) |

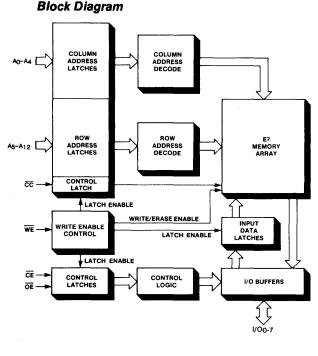

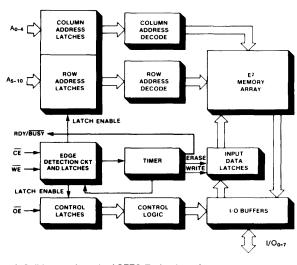

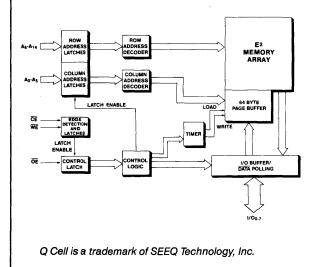

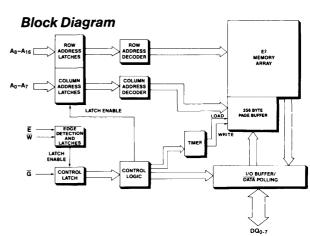

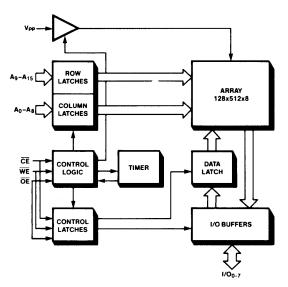

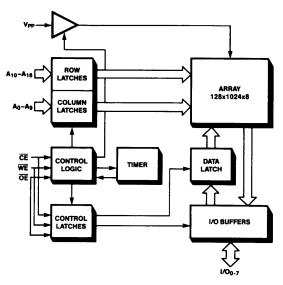

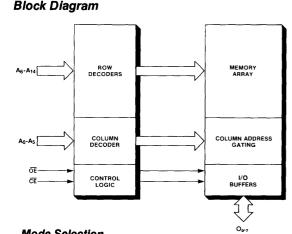

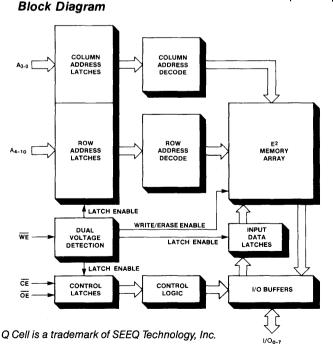

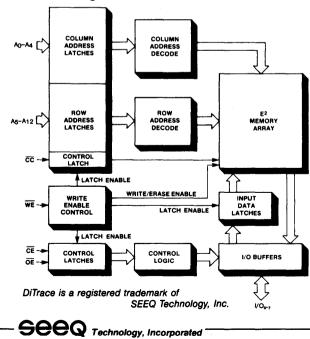

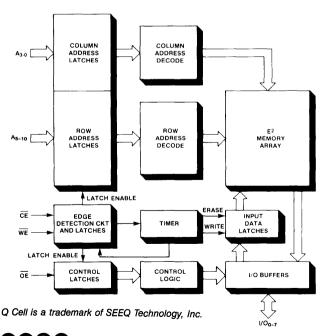

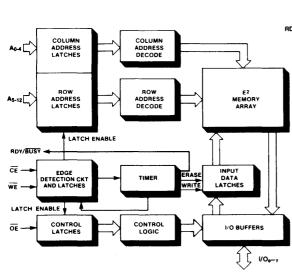

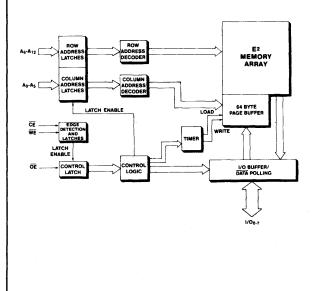

#### Block Diagram

# **SEEQ** т мD400006/В

machines, programmable industrial controllers, and an assortment of other systems. Designing the 52B13 and 52B13H into eight and sixteen bit microprocessor systems is also simplified by utilizing the fast access time with zero wait states. The addition of the latches on all data, address and control inputs reduces the overhead on the system controller by eliminating the need for the controller to maintain these signals. This reduces IC count on the board and improves the system performance. Extended temperature and military grade versions are available.

#### **Device Operation**

SEEQ's 52B13 and 52B13H have six modes of operation (see Table 1) and except for the chip erase mode they require only TTL inputs to operate these modes.

To write into a particular location of the 52B13 or 52B13H, that byte must first be erased. A memory location is erased by presenting the 52B13 or 52B13H with Chip Enable at a TTL low while Output Enable is at TTL high, and TTL highs (logical 1s) are being presented to all the I/O lines. These levels are latched and the data written when write enable is brought to a TTL low level. The erase operation requires under 10 ms. A write operation is the same as an erase except true data is presented to the I/O lines. The 52B13H performs the same as the 52B13 except that the device byte erase/byte write time has been enhanced to 1 ms.

The 52B13 is compatible to prior generation EEPROMs which required a high voltage signal for writing and erasing. In the 52B13 there is an internal dual level detection circuit which allows either a TTL low or 21V signal to be applied to  $\overline{WE}$  to execute an erase or write operation. The 52B13 specifies no restriction on the rising edge of  $\overline{WE}$ .

For certain applications, the user may wish to erase the entire memory. A chip erase is performed in the same manner as a byte erase except that Output Enable is between 14V and 22V. All 2K bytes are erased in under 10 ms.

A characteristic of all EEPROMs is that the total number of write and erase cycle is not unlimited. The 52B13 and 52B13H have been designed for applications requiring up to 10,000 write and erase cycles per byte. The write and erase cycling characteristic is completely byte independent. Adjacent bytes are not affected during write/erase cycling.

After the device is written, data is read by applying a TTL high to  $\overline{WE}$ , enabling the chip, and enabling the outputs. Data is available  $t_{CE}$  time after Chip Enable is applied or  $t_{AA}$  time from the addresses. System power may be reduced by placing the 52B13 or 52B13H into a standby mode. Raising Chip Enable to a TTL high will reduce the power consumption by over 60%.

#### **DiTrace**®

SEEQ's family of EEPROMs incorporate a DiTrace field. The DiTrace feature is a method for storing production flow information to wafer level in an extra column of EEPROM cells. As each major manufacturing operation is performed the DiTrace field is automatically updated to reflect the results of that step. These features establish manufacturing operation traceability of the packaged device back to the wafer level. Contact SEEQ for additional information on these features.

DiTrace is a registered trademark of SEEQ Technology, Inc.

| PIN                       | CE<br>(18) | ÖĒ<br>(20) | WE<br>(21) | I/O<br>(9-11, 13-17) |

|---------------------------|------------|------------|------------|----------------------|

| Read <sup>[1]</sup>       | ViL        | VIL        | ViH        | Dout                 |

| Standby <sup>[1]</sup>    | Viн        | Don't Care | ViH        | High Z               |

| Byte Erase <sup>[2]</sup> | VIL        | ViH        | VIL        | DIN = VIH            |

| Byte Write <sup>[2]</sup> | VIL        | Viн        | VIL        | Din                  |

| Chip Erase  2             | VIL        | VOE        | VIL        | DIN = VIH            |

| Write/Erase Inhibit       | Viн        | Don't Care | Don't Care | High Z               |

#### Table 1. Mode Selection (V\_{CC} = 5V $\pm$ 10%)

#### NOTES:

1.  $\overline{\text{WE}}$  may be from V<sub>IH</sub> to 6V in the read and standby mode.

Technology, Incorporated

2. We may be at VIL (TTL WE Mode) or from 15 to 21V (High Voltage WE Mode) in the byte erase, byte write, or chip erase mode of the 52813/52813H

1-4

## Power Up/Down Considerations

SEEQ's "52B"  $E^2$  family has internal circuitry to minimize false erase or write during system V<sub>CC</sub> power up or down. This circuitry prevents writing or erasing under any one of the following conditions:

- 1. Vcc is less than 3 V.<sup>[1]</sup>

- 2. A negative Write Enable transition has not occurred when  $V_{CC}$  is between 3 V and 5 V.

Writing will also be prevented if  $\overline{CE}$  or  $\overline{OE}$  are in a logical state other than that specified for a byte write in the mode selection table.

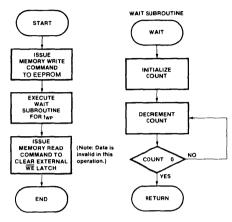

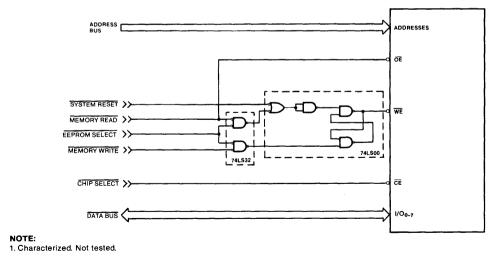

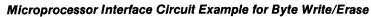

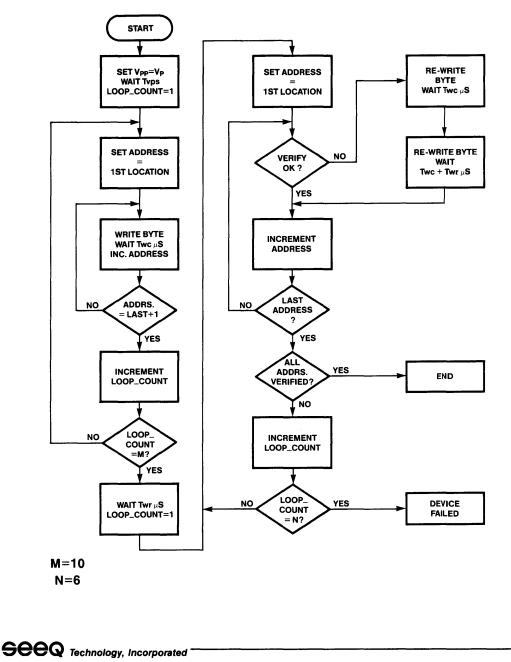

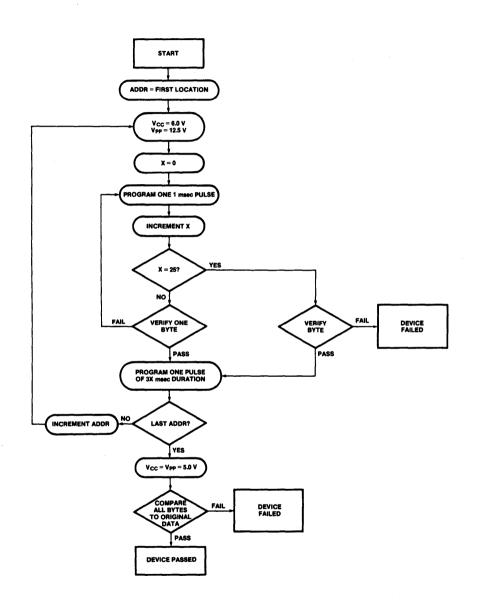

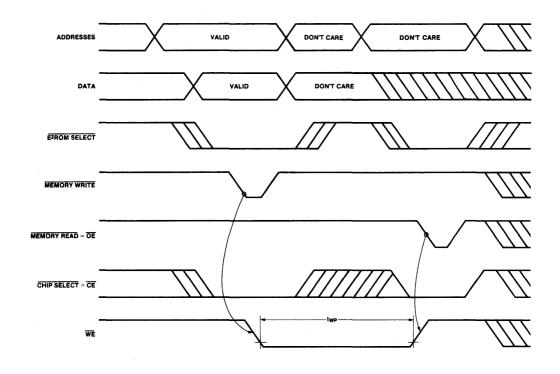

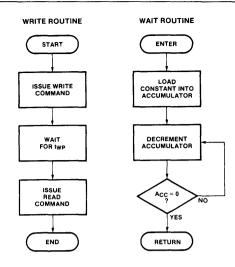

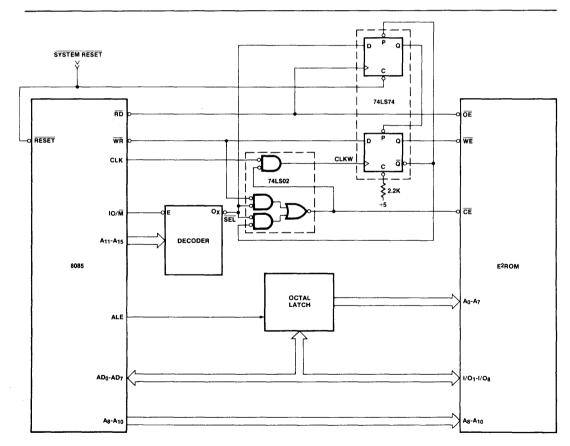

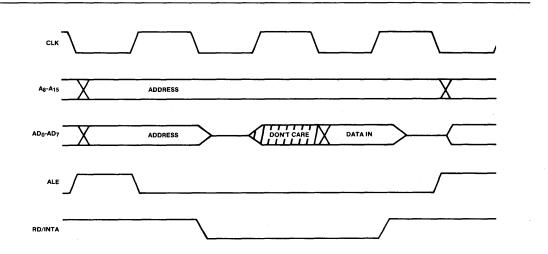

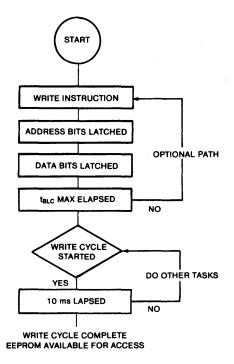

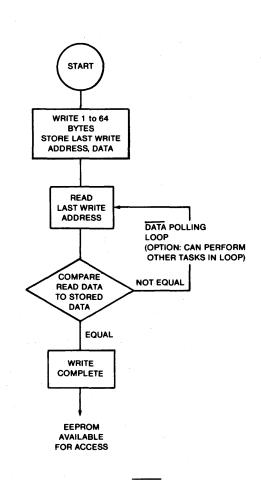

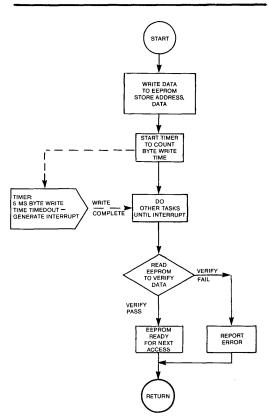

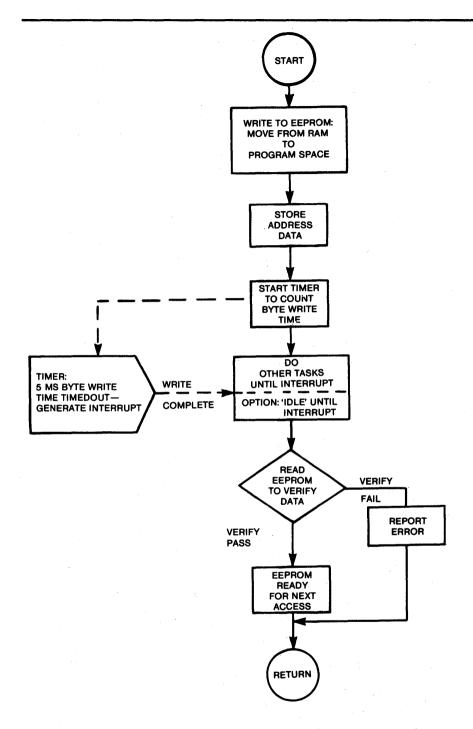

# Typical EEPROM Write/Erase Routine

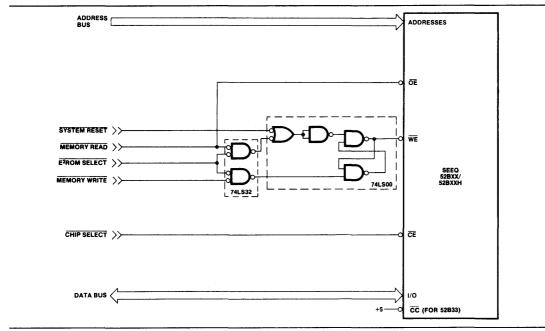

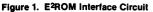

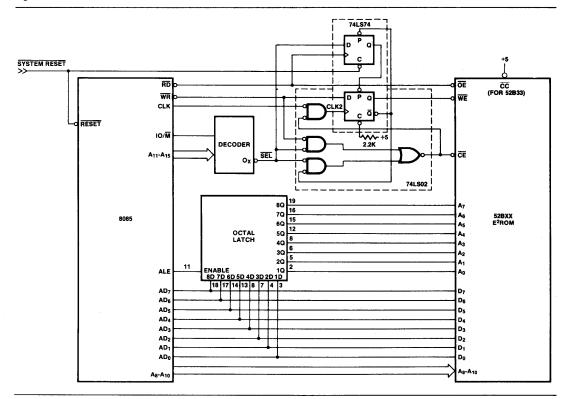

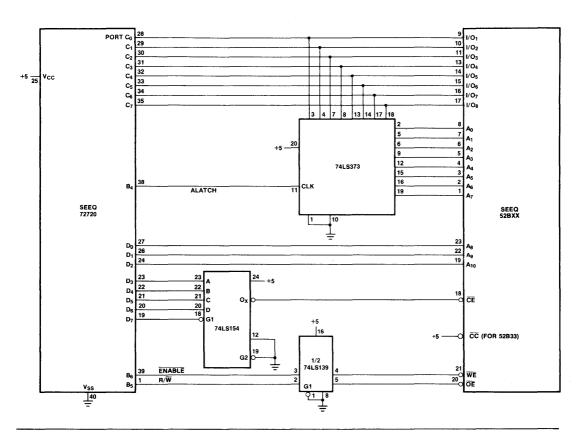

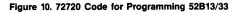

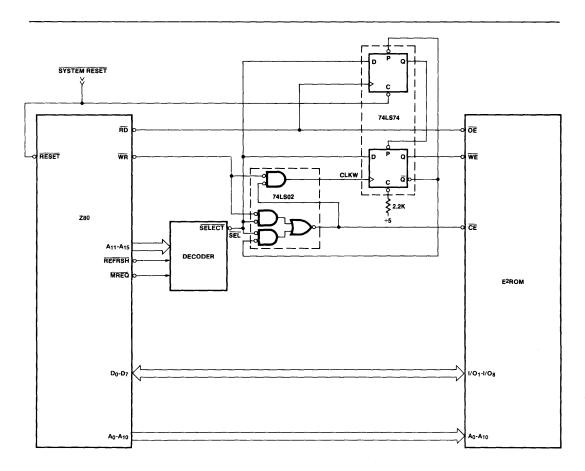

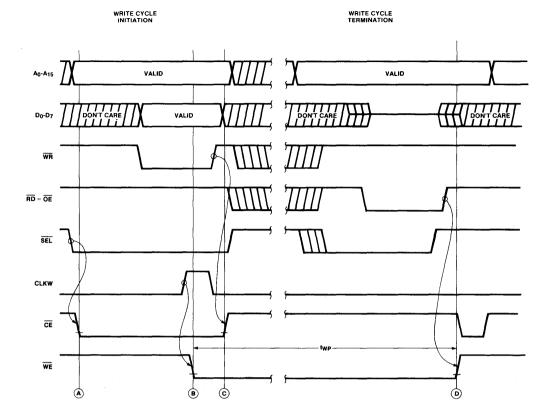

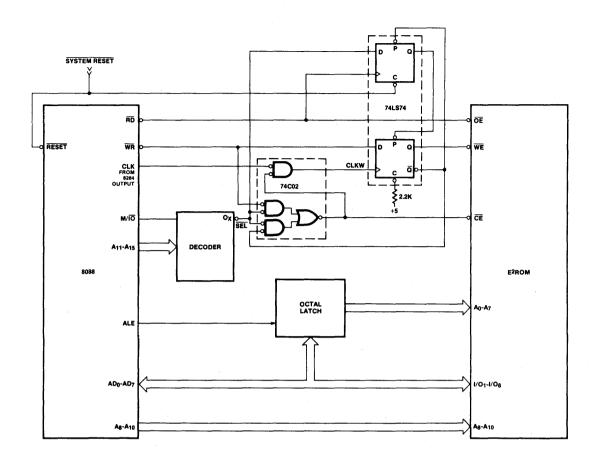

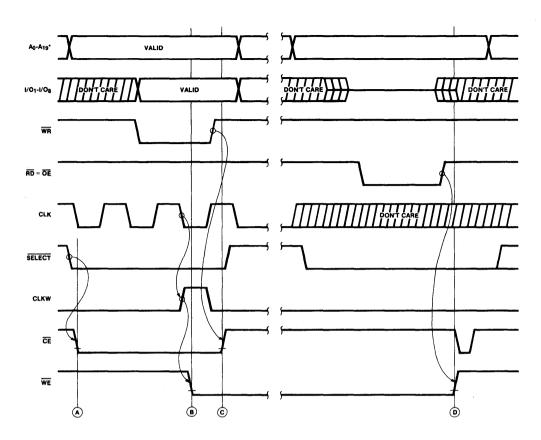

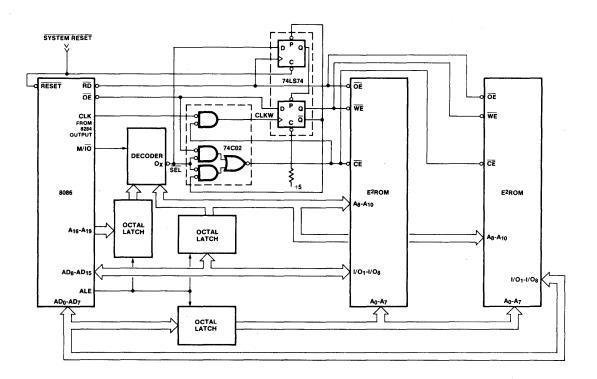

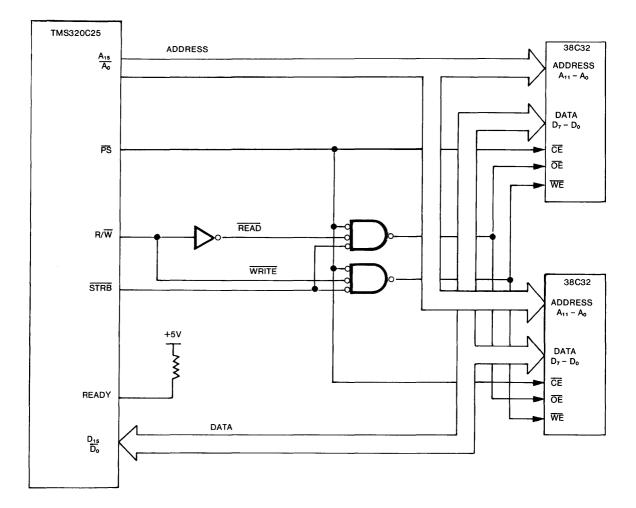

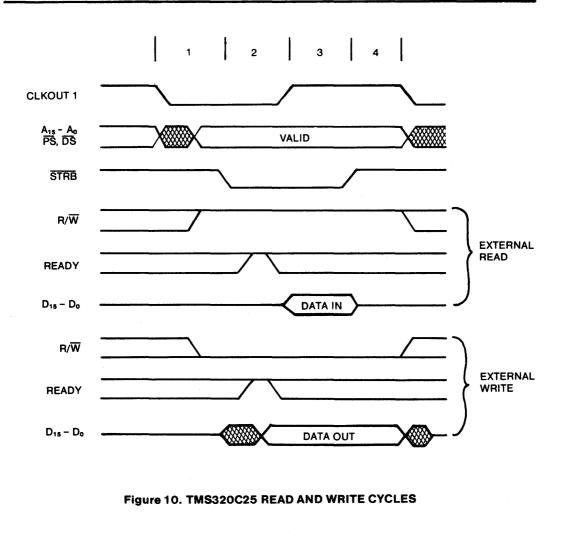

#### Microprocessor Interface Circuit Example for Byte Write/Erase

## Absolute Maximum Stress Ratings\*

| Temperature                |                   |

|----------------------------|-------------------|

| Storage                    | -65° C to +150° C |

| Under Bias                 | -10° C to +80° C  |

| All Inputs or Outputs with |                   |

| Respect to Ground          | +6V to -0.3V      |

| WE During Writing/Erasing  |                   |

| with Respect to Ground     | +22.5V to -0.3V   |

|                            |                   |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Recommended Operating Conditions**

|                                | 52B13-200/-250/-350<br>52B13H-200/-250/-350 |

|--------------------------------|---------------------------------------------|

| V <sub>CC</sub> Supply Voltage | 5 V ± 10%                                   |

| Temperature Range (Ambient)    | 0°C to 70°C                                 |

#### **Endurance and Data Retention**

| Symbol          | Parameter         | Value  | Units       | Condition                       |

|-----------------|-------------------|--------|-------------|---------------------------------|

| N               | Minimum Endurance | 10,000 | Cycles/Byte | MIL-STD 883 Test<br>Method 1033 |

| T <sub>DR</sub> | Data Retention    | > 10   | Years       | MIL-STD 883 Test<br>Method 1008 |

#### D.C. Operating Characteristics During Read or Write/Erase (Over the operating Vcc and temperature range)

| Symbol | Parameter                         | Min. | Nom. <sup>[1]</sup> | Max.    | Unit | Test Conditions                               |

|--------|-----------------------------------|------|---------------------|---------|------|-----------------------------------------------|

| lin    | Input Leakage Current             |      |                     | 10      | μA   | VIN = VCC Max.                                |

| lo     | Output Leakage Current            |      |                     | 10      | μA   | VOUT = VCC Max.                               |

| IWE    | Write Enable Leakage<br>Read Mode |      |                     | 10      | μA   | WE = VIH                                      |

|        | TTL W/E Mode                      |      |                     | 10      | μA   | $\overline{WE} = V_{IL}$                      |

|        | High Voltage W/E Mode             |      |                     | 1.5     | mA   | $\overline{WE} = 22V, \overline{CE} = V_{IL}$ |

|        | High Voltage W/E Inhibit Mode     |      |                     | 1.5     | mA   | $\overline{WE} = 22V, \overline{CE} = V_{iH}$ |

|        | Chip Erase — TTL Mode             |      |                     | 10      | μA   | $\overline{WE} = V_{IL}$                      |

|        | Chip Erase — High Voltage<br>Mode |      |                     | 1.5     | mA   | WE = 22V                                      |

| ICC1   | V <sub>CC</sub> Standby Current   |      | 15                  | 30      | mA   | ĈĒ = VIH                                      |

| ICC2   | Vcc Active Current                |      | 50                  | 80      | mA   | $\overline{CE} = \overline{OE} = V_{IL}$      |

| VIL    | Input Low Voltage                 | -0.1 |                     | 0.8     | V    |                                               |

| Viн    | Input High Voltage                | 2    |                     | Vcc + 1 | V    |                                               |

| Vwe    | WE Read Voltage                   | 2    |                     | Vcc + 1 | V    |                                               |

|        | WE Write/Erase Voltage            | -0.1 |                     | 0.8     | v    |                                               |

|        | High Voltage Mode                 | 14   |                     | 22      | V    |                                               |

| Vol    | Output Low Voltage                |      |                     | 0.45    | V    | I <sub>OL</sub> = 2.1 mA                      |

| Voн    | Output High Voltage               | 2.4  | 1                   |         | V    | I <sub>OH</sub> = -400 µA                     |

| Voe    | OE Chip Erase Voltage             | 14   | 1                   | 22      | v    | $I_{OE} = 10 \ \mu A$                         |

Notes:

1. Nominal values are for  $T_A = 25^{\circ}C$  and  $V_{CC} = 5.0V$

|                    |                                 | Device<br>Number |      | 52B13<br>52B13H |      |                                          |  |

|--------------------|---------------------------------|------------------|------|-----------------|------|------------------------------------------|--|

| Symbol             | Parameter                       | Extension        | Min. | Max.            | Unit | Test Conditions                          |  |

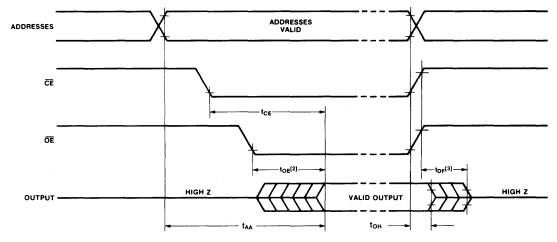

| t <sub>AA</sub>    | Address Access Time             | -200             |      | 200             | ns   | $\overline{CE} = \overline{OE} = V_{IL}$ |  |

|                    |                                 | -250             |      | 250             | ns   |                                          |  |

|                    |                                 | -350             |      | 350             | ns   |                                          |  |

| tCE                | Chip Enable to Data Valid       | -200             |      | 200             | ns   | OE = VIL                                 |  |

|                    |                                 | -250             |      | 250             | ns   |                                          |  |

|                    |                                 | -350             |      | 350             | ns   |                                          |  |

| toe <sup> 1 </sup> | Output Enable to Data Valid     | -200             |      | 80              | ns   | $\overline{CE} = V_{IL}$                 |  |

|                    |                                 | -250             |      | 90              | ns   |                                          |  |

|                    |                                 | -350             |      | 100             | ns   |                                          |  |

| t <sub>DF</sub>  2 | Output Enable to High Impedance | -200             | 0    | 60              | ns   | CE = VIL                                 |  |

|                    |                                 | -250             | 0    | 70              | ns   |                                          |  |

|                    |                                 | -350             | 0    | 80              | ns   |                                          |  |

| tон                | Output Hold                     | All              | 0    |                 | ns   | $\overline{CE} = \overline{OE} = V_{IL}$ |  |

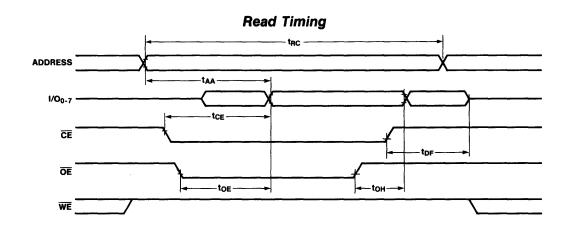

#### A.C. Operating Characteristics During Read (Over the operating VCC and temperature range)

## Capacitance<sup>[3]</sup> T<sub>A</sub>=25°C, f=1 MHz

| Symbol           | Parameter          | Max. | Unit | Conditions                               |

|------------------|--------------------|------|------|------------------------------------------|

| CIN              | Input Capacitance  | 10   | pF   | $V_{IN} = 0V$                            |

| Соит             | Output Capacitance | 10   | pF   | Vout = 0V                                |

| Cv <sub>cc</sub> | Vcc Capacitance    | 500  | pF   | $\overline{OE} = \overline{CE} = V_{IH}$ |

| CVwE             | VwE Capacitance    | 10   | pF   | $\overline{OE} = \overline{CE} = V_{IH}$ |

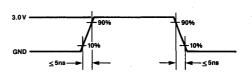

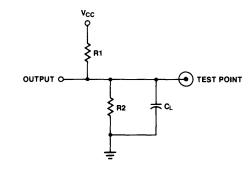

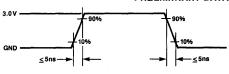

#### A.C. Test Conditions

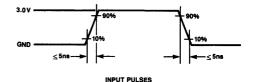

Output Load: 1 TTL gate and  $C_L = 100 \, pF$ Input Rise and Fall Times:  $\leq 20$ ns Input Pulse Levels: 0.45V to 2.4V Timing Measurement Reference Level: Inputs 1V and 2V Outputs 0.8V and 2V

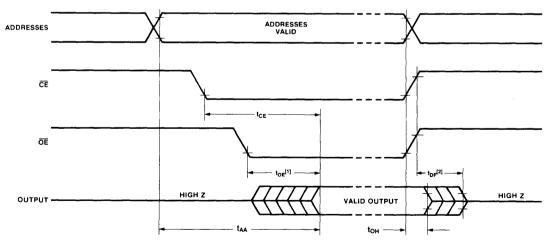

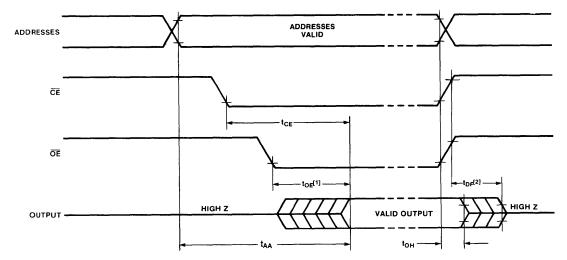

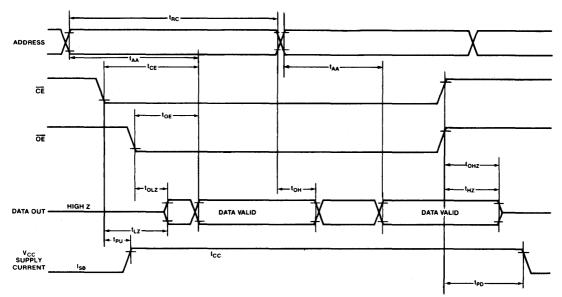

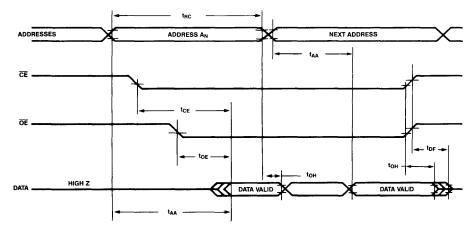

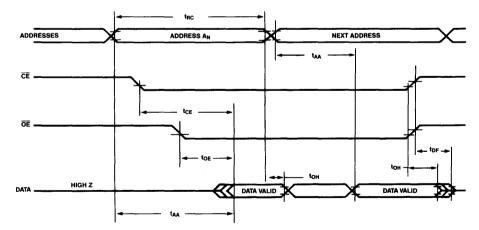

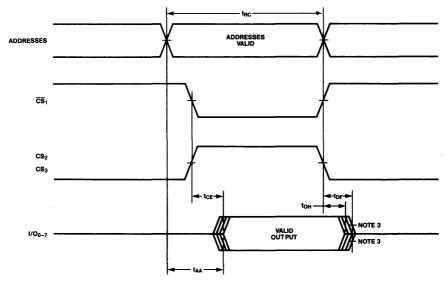

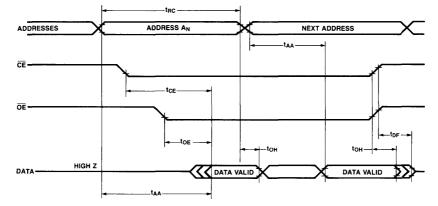

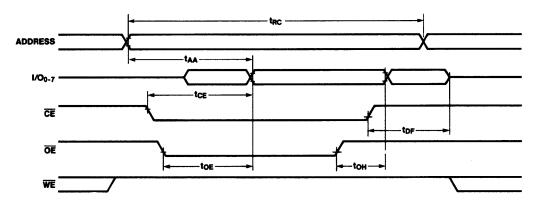

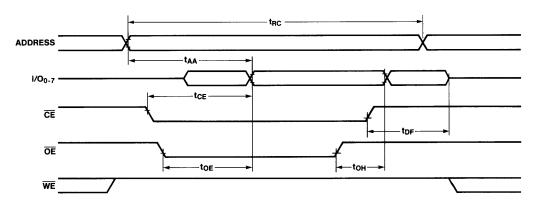

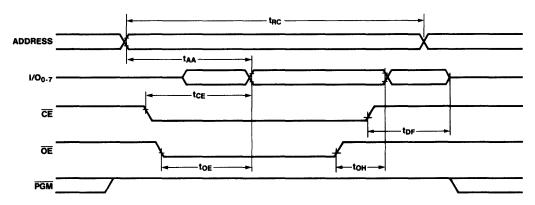

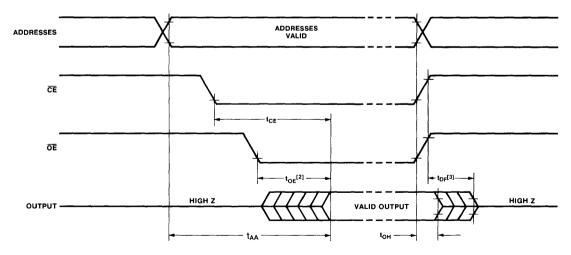

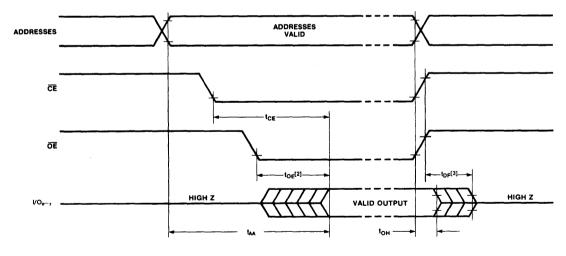

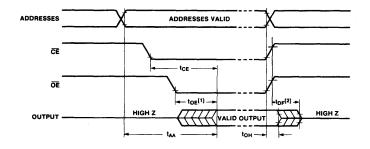

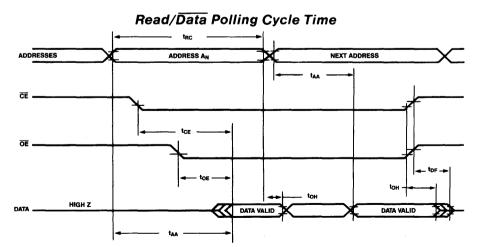

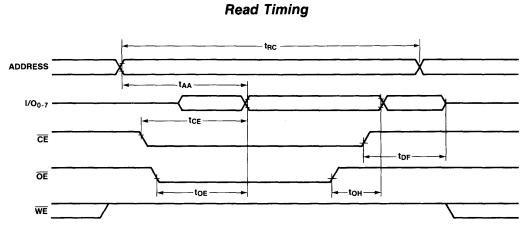

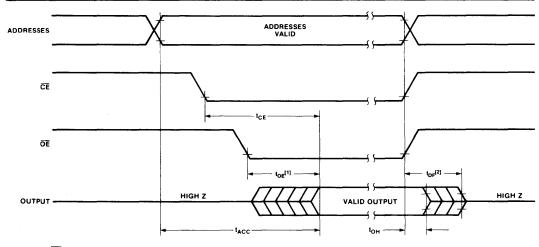

#### **Read Timing**

#### NOTES:

1.  $\overrightarrow{OE}$  may be delayed to  $t_{AA} - t_{OE}$  after the falling edge of  $\overrightarrow{CE}$  without impact on  $t_{AA}$ . 2.  $t_{DE}$  is specified from  $\overrightarrow{OE}$  or  $\overrightarrow{CE}$ , whichever occurs first.

3. This parameter is measured only for the initial qualification and after process or design changes which may affect capacitance.

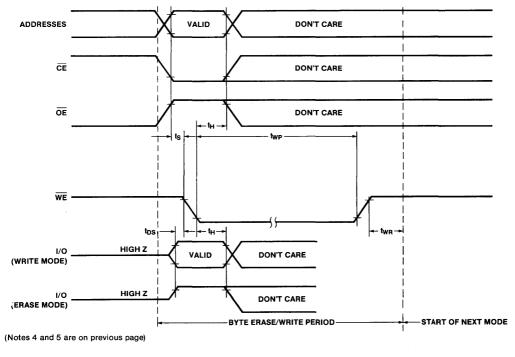

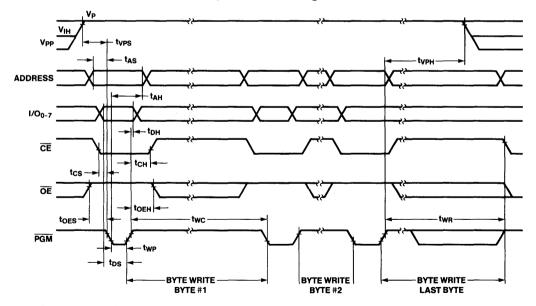

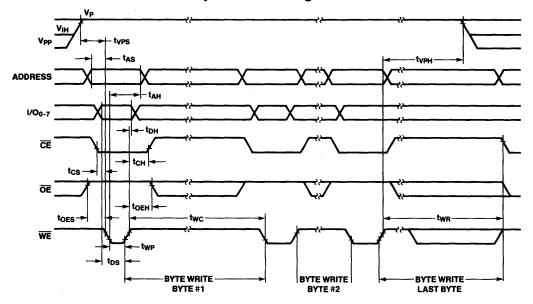

| Symbol                                              | Parameter                                              |        | Min. | Max. | Units |

|-----------------------------------------------------|--------------------------------------------------------|--------|------|------|-------|

| ts                                                  | CE, OE or A <sub>N</sub> Setup to WE                   |        | 50   |      | ns    |

| t <sub>DS</sub>                                     | Data Setup to WE                                       |        | 15   |      | ns    |

| tH <sup>[1]</sup>                                   | WE to CE, OE, AN or Data Change                        |        | 50   |      | ns    |

| twp <sup>[1]</sup> Write Enable, WE,<br>Pulse Width | Write Enable, WE,                                      | _52B13 | 9    |      | ms    |

|                                                     | 52B13H                                                 | 1      |      | ms   |       |

| twr <sup>[2]</sup>                                  | WE to Mode Change<br>WE to next Byte Write/Erase Cycle |        | 50   |      | ns    |

|                                                     | WE to start of a Read Cycle                            |        |      | 2    | μs    |

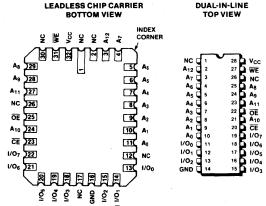

#### A.C. Operating Characteristics During Write/Erase (Over the operating Voc and temperature range)

#### 52B13/52B13H High Voltage Write Specifications

Except for the functional differences noted here, the 52B13 and 52B13H operate to the same specifications, including the TTL W/E mode.

|        |                                                | 52B13 52B13H |      | B13H |      |       |

|--------|------------------------------------------------|--------------|------|------|------|-------|

| Symbol | Function/Parameter                             | Min.         | Max. | Min. | Max. | Units |

| twp    | Write Enable Pulse Width<br>Byte Write/Erase 9 | 9            | 20   | 1    | 10   | ms    |

|        | Chip Erase                                     | 9            | 20   | 9    | 20   | ms    |

| Vwe    | WE Write/Erase Voltage<br>High Voltage Mode    | 14           | 22   | 14   | 22   | v     |

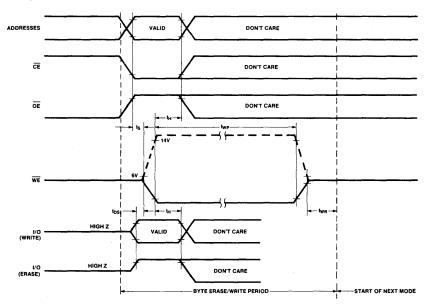

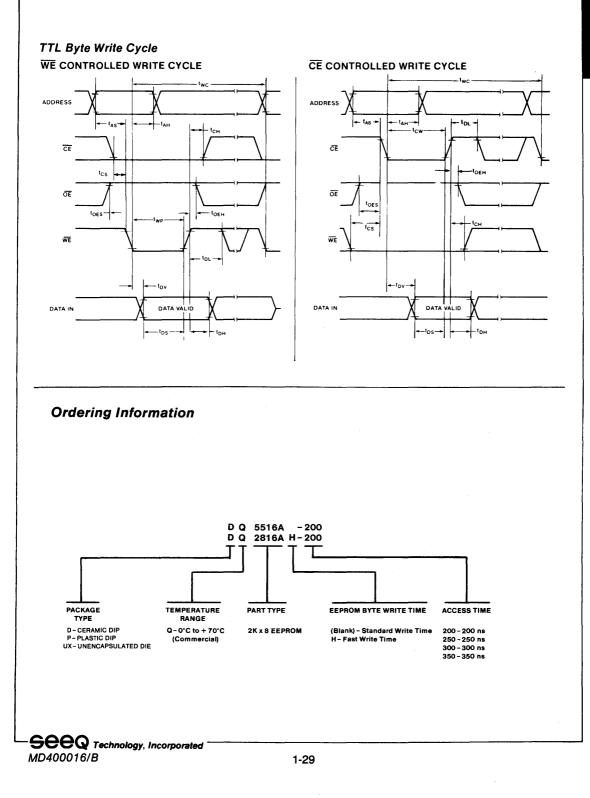

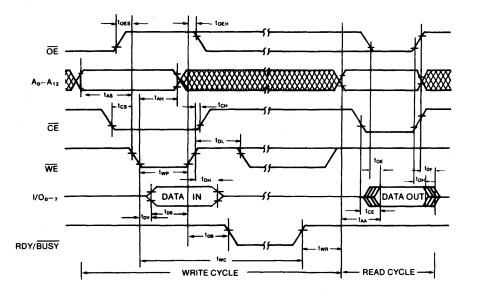

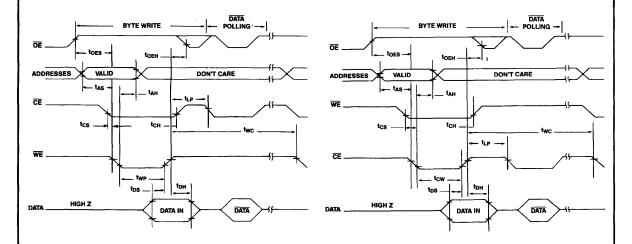

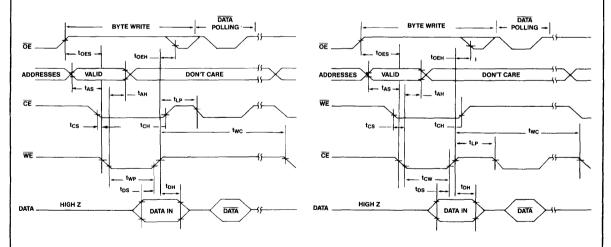

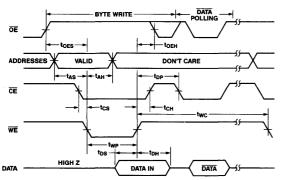

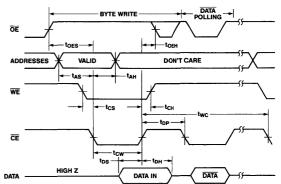

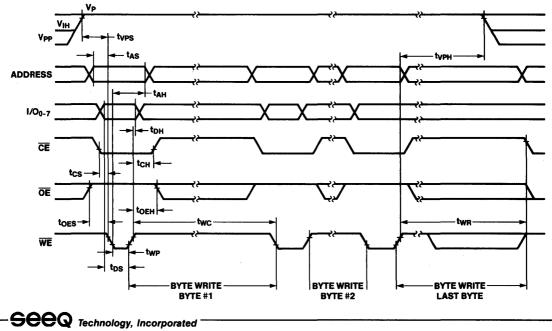

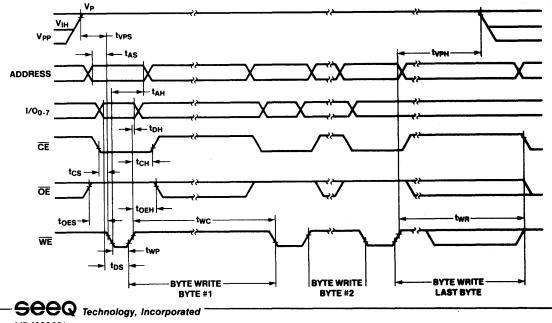

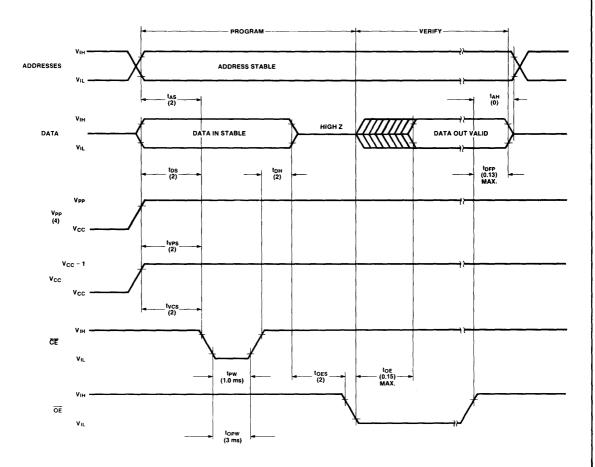

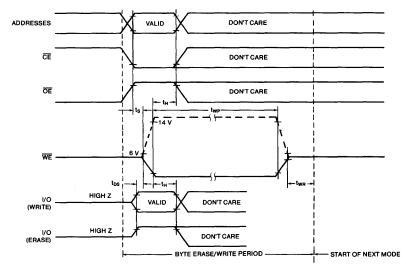

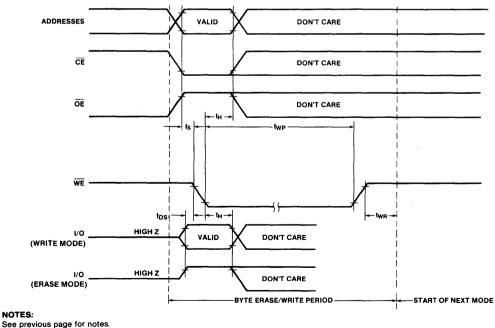

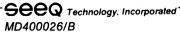

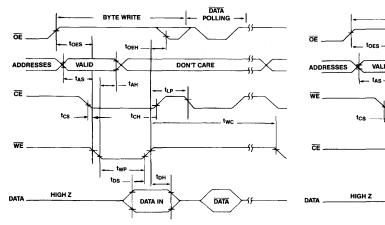

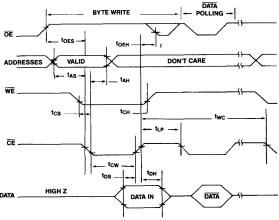

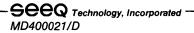

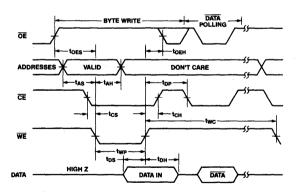

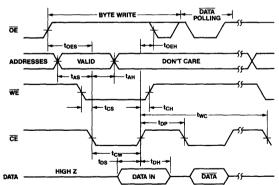

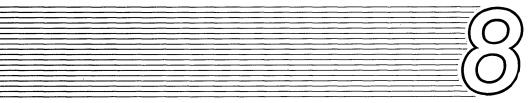

#### Byte Erase or Byte Write Timing

#### NOTES:

1. After ty, hold time, from WE, the inputs, CE, OE, address and Data are latched and are "Don't Cares" until two, write recovery time, after the trailing edge of WE.

2. The Write Recovery Time, two, is the time after the trailing edge of WE that the latches are open and able to accept the next mode set-up conditions. Reference Table 1 (page 2) for mode control conditions.

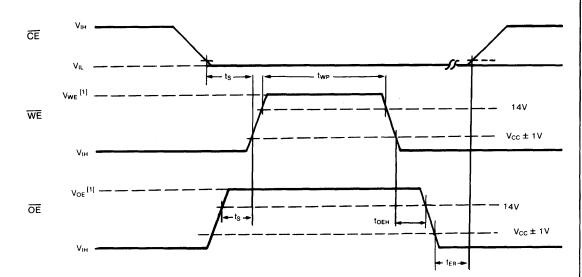

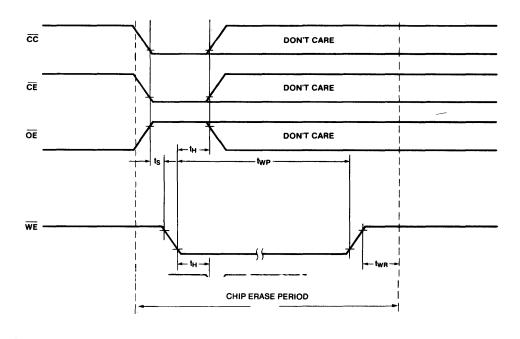

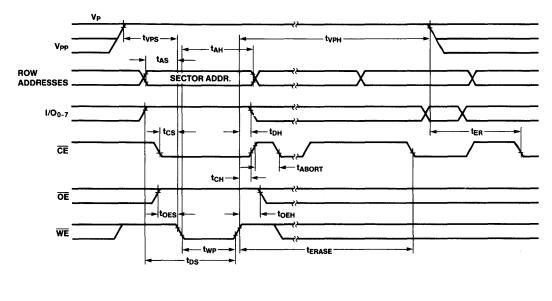

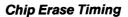

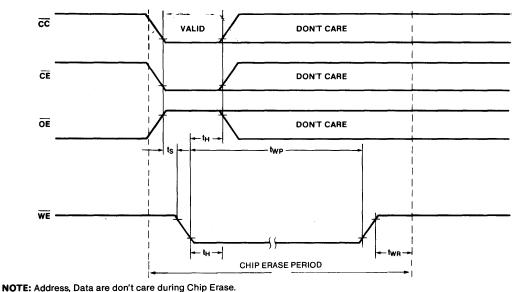

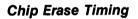

### **Chip Erase Specifications**

| Symbol | Parameter           | Min. | Max. | Units |

|--------|---------------------|------|------|-------|

| ts     | CE, OE Setup to WE  | 1    |      | μs    |

| tоен   | OE Hold Time        | 1    |      | μs    |

| twp    | WE Pulse Width      | 10   |      | ms    |

| ter    | Erase Recovery Time |      | 10   | μs    |

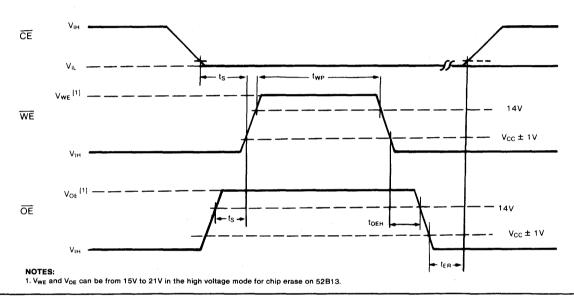

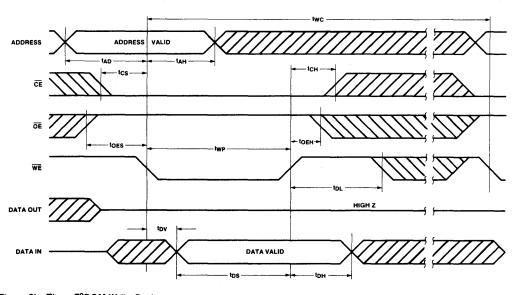

# Chip Erase Timing

#### NOTES:

1. VwE and VoE can be from 15V to 21V in the high voltage mode for chip erase on 52B13.

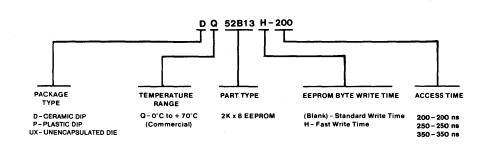

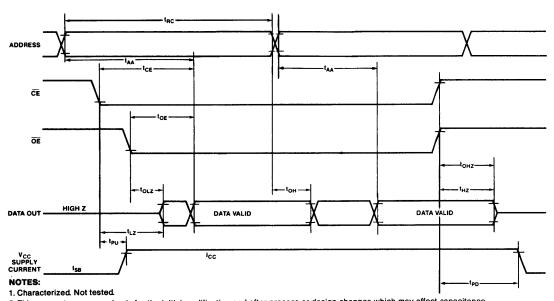

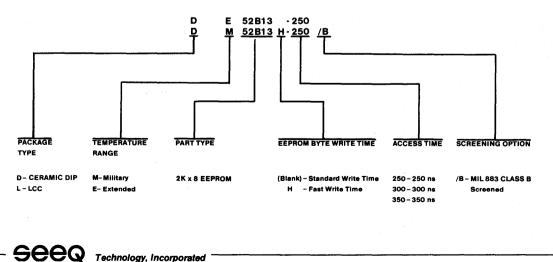

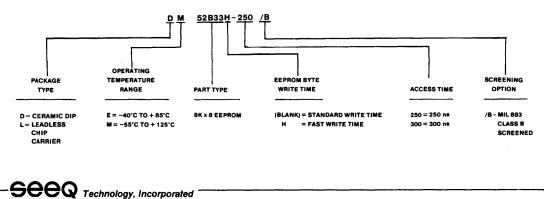

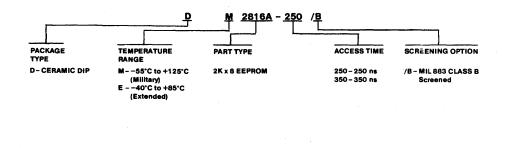

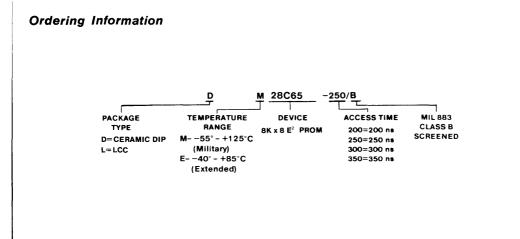

# **Ordering Information**

# **SEEQ 52B33/52B33H** 64K Electrically Erasable PROM

October 1987

#### Features

- High Write Endurance Over Temperature

Range

Range

Keppering (keta)

- 52B33/52B33H; 10,000 cycles/byte minimum

- Input Latches

- Fast TTL Byte Write Time — 1 ms for 52B33H

- 9 ms for 52B33

- 5 V ± 10% V<sub>cc</sub>

- Power Up/Down Protection

- 200 ns Read Access Time

- DiTrace®

- Infinite Number of Read Cycles

- JEDEC Approved Byte Wide Memory Pinout

- Military And Extended Temperature Range Available

## Description

SEEQ's 52B33 is a8192 x8 bit, 5 volt electrically erasable programmable read only memory (EEPROM) which is specified over a 0°C to 70°C temperature range. Data retention is specified to be greater than 10 years. The device has input latches on all addresses, data, and control (chip and output) lines. Data is latched and electrically written by a TTL pulse on the Write Enable pin. Once written there is no limit to the number of times data may be read. The erasure time is under 10 ms, and each byte may be erased and written a minimum of 10,000 times. For applications requiring a faster byte write or erase time, a 52B33H is available at 1 ms, giving a 10 times speed increase.

(continued on next page)

SEEQ Technology, Incorporated

MD400008/A

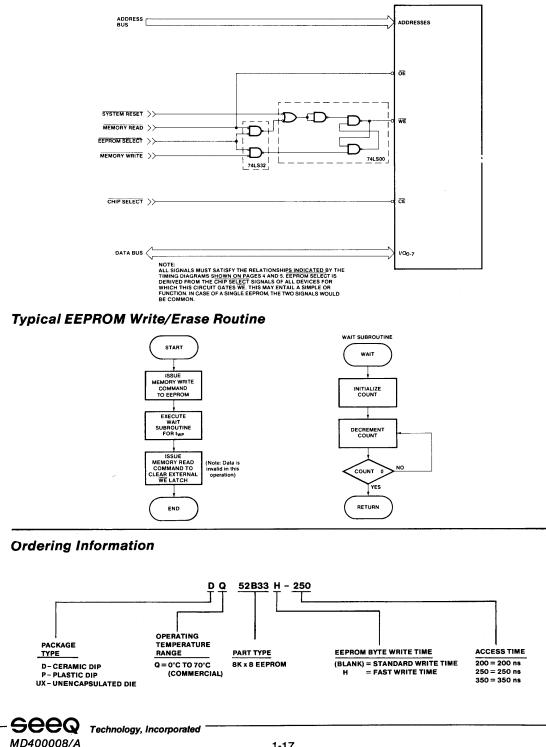

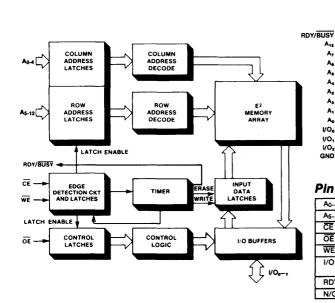

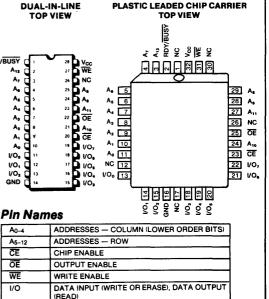

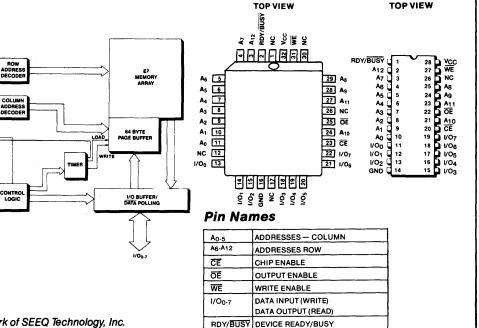

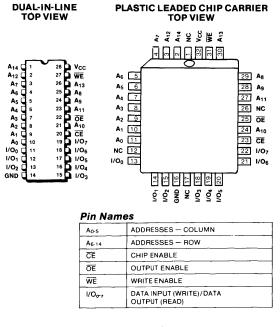

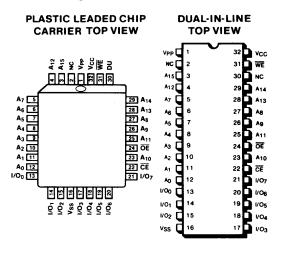

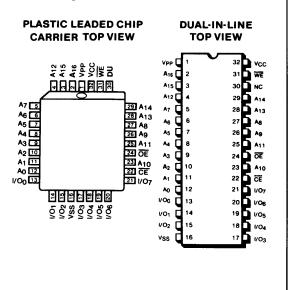

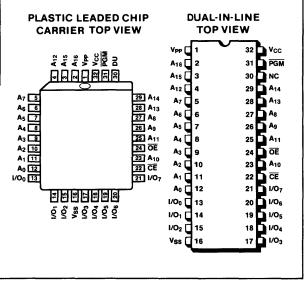

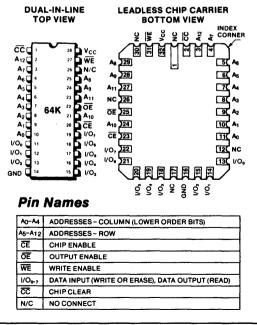

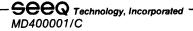

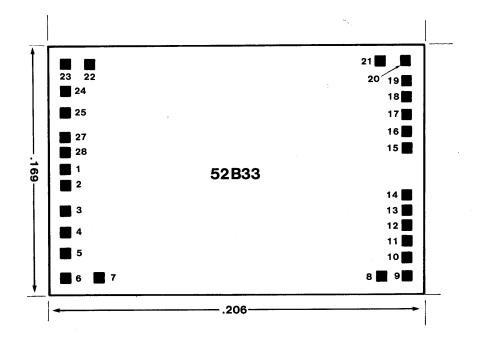

#### Pin Configuration

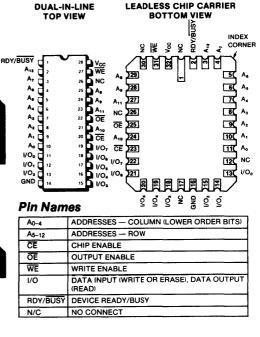

## Pin Names

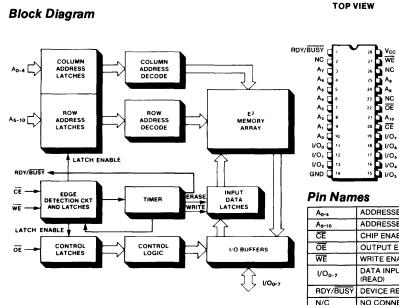

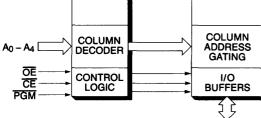

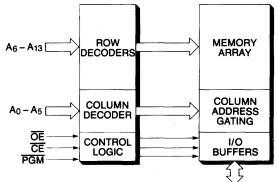

| A0-A4  | ADDRESSES - COLUMN (LOWER ORDER BITS)           |

|--------|-------------------------------------------------|

| A5-A12 | ADDRESSES - ROW                                 |

| ĈĒ     | CHIP ENABLE                                     |

| ŌĒ     | OUTPUT ENABLE                                   |

| WE     | WRITE ENABLE                                    |

| 1/00-7 | DATA INPUT (WRITE OR ERASE), DATA OUTPUT (READ) |

| CC     | CHIP CLEAR                                      |

| N/C    | NO CONNECT                                      |

1-11

The pin configuration is to the JEDEC approved byte wide memory pinout. EEPROMs are ideal for applications that require a non-volatile memory with in-system write and erase capability. Dynamic configuration (the alteration of opening software in real-time) is made possible by EEPROMs. Applications will be found in military avionics systems, programmable character generators, self-calibrating instrument/machines, programmable industrial controllers, and an assortment of other systems. Designing the EEPROMs into these systems is simplified because of the fast access time and input latches. The specified 200 ns access time eliminates or reduces the number of microprocessor wait states. The addition of the latches on all data, address and control inputs reduces the overhead on the system controller by eliminating the need for the controller to maintain these signals. This reduces IC count on the board and improves the system performance.

#### **Device Operation**

SEEQ's 52B33 has six modes of operation (see Table1) and requires only TTL inputs to operate these modes. The "H" members of the family operate in the same manner as the other devices except that a faster write enable pulse width of 1 ms is specified during byte erase or write.

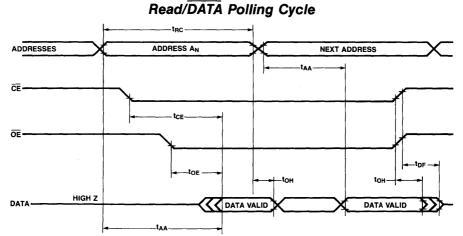

#### Read

A read is accomplished by presenting the address of the desired byte to the address inputs. Once the address is stable,  $\overline{CE}$  is bought to a TTL low in order to enable the chip. The write enable ( $\overline{WE}$ ) pin must be at a TTL high during the entire read cycle. The output drivers are made active by bringing output enable ( $\overline{OE}$ ) to a TTL low. During read, the address,  $\overline{CE}$ ,  $\overline{OE}$ , and I/O latches are transparent.

Technology, Incorporated

#### Mode Selection (Table 1)

#### Write

To write in to a particular location, that byte must first be erased. A memory location is erased by having valid addresses, Chip Enable at a TTL low, Output Enable at TTL high, and TTL highs (logical 1's) presented to all the I/O lines. Write Enable is then brought to a TTL low level to latch all the inputs and I/O lines. All inputs can be released after the write enable hold time ( $t_H$ ) and the next input conditions can be established while the byte is being erased. During this operation, the write enable must be held at a TTL low for 9 ms ( $t_{WP}$ ). A write operation is the same as an erase except true data is presented to the I/O lines. The 52B33H performs the same as the 52B33 except that the byte erase/byte write time has been enhanced to 1 ms.

#### Chip Clear

Certain applications may require all bytes to be erased simultaneously. See A.C. Operating Characteristics for TTL chip erase timing specifications.

#### DITrace®

SEEQ's family of EEPROMs incorporate a DiTrace field. The DiTrace feature is a method for storing production flow information in an extra row of EEPROM cells. As each major manufacturing operation is performed the DiTrace field is automatically updated to reflect the results of that step. These features establish manufacturing operation traceability of the packaged device back to the wafer level. Contact SEEQ for additional information on these features.

#### **Power Up/Down Considerations**

SEEQ's "52B"  $E^2$  family has internal circuitry to minimize false erase or write during system V<sub>CC</sub> power up or down. This circuitry prevents writing or erasing under any one of the following conditions:

- 1. Vcc is less than 3 V.<sup>[1]</sup>

- 2. A negative Write Enable transition has not occurred when  $V_{CC}$  is between 3 V and 5 V.

Writing will also be prevented if  $\overline{CE}$  or  $\overline{OE}$  are in a logical state other than that specified for a byte write in the mode selection table.

| F                 | unction | CE   | CC         | ŌĒ         | WE         | I/O            |

|-------------------|---------|------|------------|------------|------------|----------------|

| Mode              | (Pin)   | (20) | (1)        | (22)       | (27)       | (11-13, 15-19) |

| Read              |         | VIL  | Viн        | VIL        | ViH        | DOUT           |

| Standby           |         | VIH  | Don't Care | Don't Care | Don't Care | High Z         |

| Byte Erase        |         | ViL  | Viн        | ViH        | VIL        | DIN = VIH      |

| Byte Write        |         | VIL  | Viн        | ViH        | VIL        | Din            |

| Chip Clear        |         | ViL  | VIL        | ViH        | VIL        | VIL or VIH     |

| Write/Erase Inhib | oit     | Viн  | Don't Care | Don't Care | Don't Care | High Z         |

#### NOTE:

1. Characterized. Not tested.

SEEQ MD400008/A DiTrace is a registered trademark of SEEQ Technology, Inc.

# Absolute Maximum Stress Rating\*

| Temperature |                  |

|-------------|------------------|

| Storage     | -65°C to +100°C  |

| Under Bias  | . −10°C to +80°C |

|             |                  |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

|                                | 52B33, 52B33H |

|--------------------------------|---------------|

| V <sub>CC</sub> Supply Voltage | 5 V ± 10%     |

| Temperature Range (Ambient)    | 0°C to 70°C   |

# Endurance and Data Retention

| Symbol          | Parameter         | Value  | Units       | Condition                       |

|-----------------|-------------------|--------|-------------|---------------------------------|

| N               | Minimum Endurance | 10,000 | Cycles/Byte | MIL-STD 883 Test<br>Method 1033 |

| T <sub>DR</sub> | Data Retention    | > 10   | Years       | MIL-STD 883 Test<br>Method 1008 |

#### D.C. Operating Characteristics During Read or Erase/Write (Over the operating Vcc and temperature range)

| Symbol | Parameter                       | Min. | Nom. | Max.    | Unit | Test Conditions                          |

|--------|---------------------------------|------|------|---------|------|------------------------------------------|

| lin    | Input Leakage Current           |      |      | 10      | μA   | VIN = VCC Max.                           |

| lo     | Output Leakage Current          |      |      | 10      | μA   | VOUT = VCC Max.                          |

| IWE    | Write Enable Leakage            |      |      | 10      | μA   | $\overline{\text{WE}} = V_{\text{IL}}$   |

| Icc1   | V <sub>CC</sub> Standby Current |      | 18   | 40      | mA   | CE = VIH                                 |

| ICC2   | V <sub>CC</sub> Active Current  |      | 60   | 110     | mA   | $\overline{CE} = \overline{OE} = V_{IL}$ |

| VIL    | Input Low Voltage               | -0.1 |      | 0.8     | V    |                                          |

| Viн    | Input High Voltage              | 2    |      | Vcc + 1 | V    |                                          |

| Vol    | Output Low Voltage              |      |      | 0.45    | v    | $I_{OL} = 2.1 \text{ mA}$                |

| Vон    | Output High Voltage             | 2.4  |      |         | V    | Іон = -400 μА                            |

Notes:

1. Nominal values are for  $T_A=25^{\circ}\,C$  and  $V_{CC}=5.0\,\,V$

|                             |                                    | Device<br>Number     | 52E         | B33<br> 33 H      |                |                                                                                      |  |

|-----------------------------|------------------------------------|----------------------|-------------|-------------------|----------------|--------------------------------------------------------------------------------------|--|

| Symbol                      | Parameter                          | Extension            | Min. Max.   |                   | Unit           | Test Conditions                                                                      |  |

| taa                         | Address Access Time                | -200<br>-250<br>-350 |             | 200<br>250<br>350 | ns<br>ns<br>ns | CE = OE = VIL                                                                        |  |

| t <sub>CE</sub>             | Chip Enable to Data Valid          | -200<br>-250<br>-350 |             | 200<br>250<br>350 | ns<br>ns<br>ns | OE = VIL                                                                             |  |

| toe <sup>[1]</sup>          | Output Enable to Data Valid        | -200<br>-250<br>-350 |             | 80<br>90<br>100   | ns<br>ns<br>ns | CE = VIL                                                                             |  |

| tof <sup>[2]</sup>          | Output Enable to High<br>Impedance | -200<br>-250<br>-350 | 0<br>0<br>0 | 60<br>70<br>80    | ns<br>ns<br>ns | CE = VIL                                                                             |  |

| tон                         | Output Hold                        | All                  | 0           |                   | ns             | $\overline{CE} = \overline{OE} = V_{IL}$                                             |  |

| Cin/<br>Cout <sup>[3]</sup> | Input and Output<br>Capacitance    | All                  |             | 10                | pF             | $V_{IN} = 0 V \text{ for}$ $C_{IN}, V_{OUT} = 0 V$ for C_OUT,<br>$T_A = 25^{\circ}C$ |  |

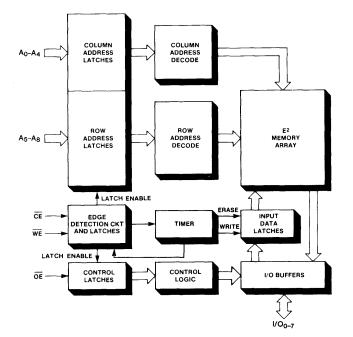

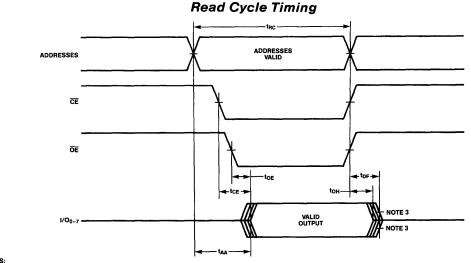

#### AC Operating Characteristics During Read (Over the operating Vcc and temperature range)

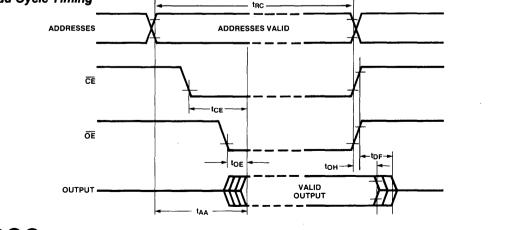

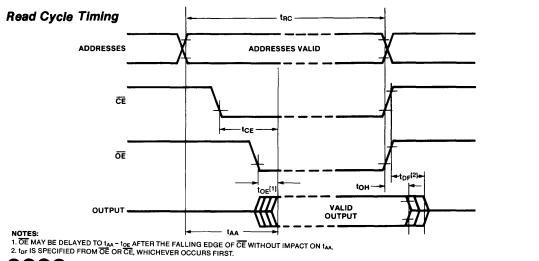

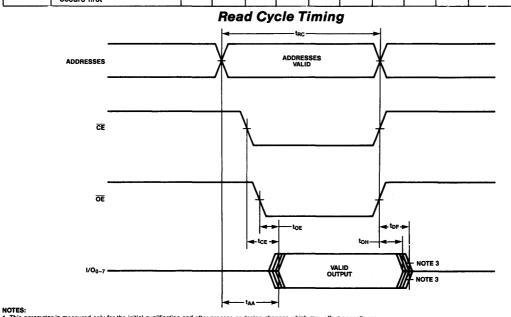

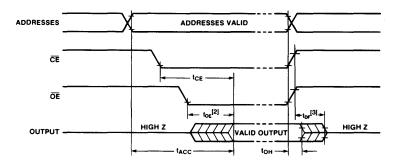

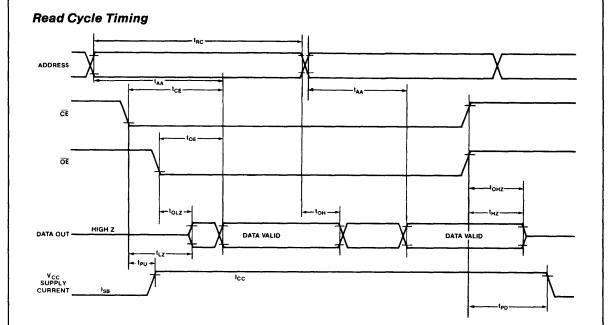

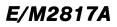

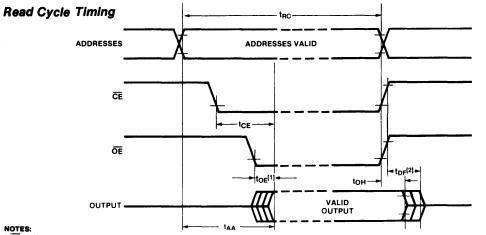

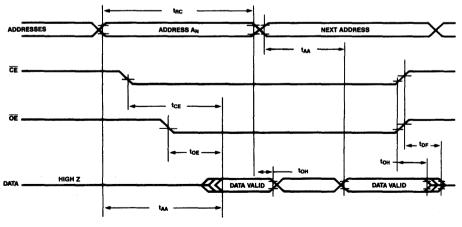

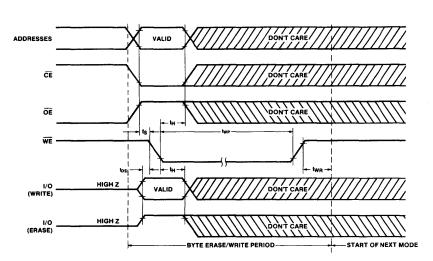

**Read Cycle Timing**

#### NOTES:

- 1.  $\overline{OE}$  may be delayed to  $t_{AA} t_{OE}$  after the falling edge of  $\overline{CE}$  without impact on  $t_{AA}$ . 2.  $t_{DE}$  is specified from  $\overline{OE}$  or  $\overline{CE}$ , whichever occurs first

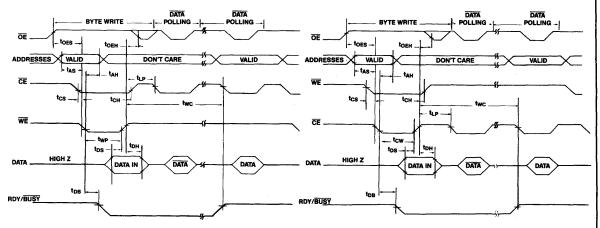

- 3. This parameter is measured only for the initial gualification and after process or design changes which may affect capacitance. 4. After t<sub>H</sub>, hold time, from WE, the inputs CE, OE, CC, Address and Data are latched and are "Don't Cares" until t<sub>WP</sub>. Write Recovery Time, after the trailing edge of WE.

- 5. The Write Recovery Time, twr, is the time after the trailing edge of WE that the latches are open and able to accept the next mode set-up conditions. Reference Table 1 (page 2) for mode control conditions.

#### A.C. Test Conditions

Output Load: 1 TTL gate and  $C_L = 100 \text{ pF}$ Input Rise and Fall Times:  $\leq 20 \text{ ns}$ Input Pulse Levels: 0.45 V to 2.4 V Timing Measurement Reference Level: Inputs 1 V and 2 V Outputs 0.8 V and 2 V

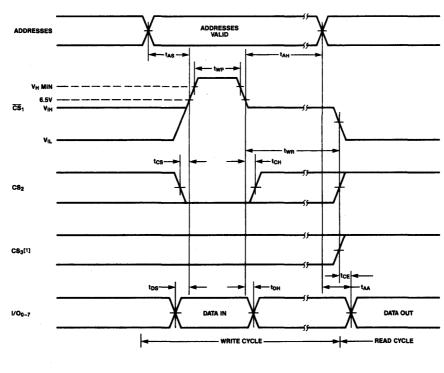

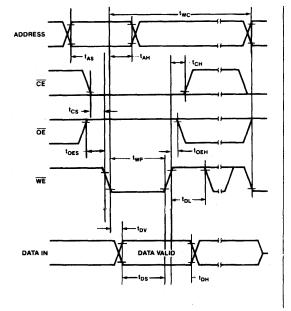

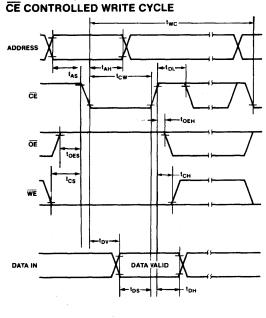

#### A.C. Operating Characteristics During Write/Erase (Over the operating V<sub>CC</sub> and temperature range)