# FUJITSU

## **Dynamic RAM Products**

**1991** FUJITSU

|   | NMOS DRAMs                       |

|---|----------------------------------|

| 2 | CMOS DRAMs                       |

| 3 | Application-Specific DRAMs       |

| 4 | Quality and Reliability          |

| 5 | Ordering and Package Information |

| 6 | Sales Information                |

| 7 | Appendices – Design Information  |

## FUJITSU

## **Dynamic RAM Products**

1991 Data Book

Fujitsu Limited Tokyo, Japan

Fujitsu Microelectronics, Inc. San Jose, California, U.S.A.

Fujitsu Mikroelektronik GmbH Frankfurt, Germany

Fujitsu Microelectronics Asia PTE Limited Singapore

Copyright© 1991 Fujitsu Microelectronics, Inc., San Jose, California

#### All Rights Reserved.

Circuit diagrams using Fujitsu products are included to illustrate typical semiconductor applications. Information sufficient for construction purposes may not be shown.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu Microelectronics, Inc. assumes no responsibility for inaccuracies.

The information conveyed in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu Limited, its subsidiaries, or Fujitsu Microelectronics, Inc.

Fujitsu Microelectronics, Inc. reserves the right to change products or specifications without notice.

No part of this publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu Microelectronics, Inc.

This document is published by the Publications Department, Fujitsu Microelectronics, Inc., 3545 North First Street, San Jose, California, U.S.A. 95134–1804; U.S.A.

Printed in the U.S.A.

Edition 1.0

#### PREFACE

This data book contains the latest product information for Fujitsu's line of DRAM ICs. This year's edition, however, does not include a section for DRAM modules. Both DRAM and SRAM modules are now in a Modules Data Book which you can obtain from your nearest Fujitsu Sales Office or Sales Rep. (See the Sales Information listing in this book.)

In addition to the collection of DRAM data sheets, you will find valuable information on ordering and expanded packaging descriptions, both in the Order Information section.

The Design Information section contains two new technical papers. *The 3D Stacked Capacitor Cell for Mega Bit DRAM* is a reprint of a technical paper from the **Fujitsu Scientific and Technical Journal**. We are pleased to be able to include an article from this highly respected journal. The second new paper is *The Soft Error Rate for 4M DRAM Devices*, a significant article on these new DRAM devices.

If you are interested in obtaining other Fujitsu product information, you will find the publications listing on the following pages quite useful. Once again, call one of our sales offices to obtain a copy of any of the documents.

## **FUJITSU PRODUCT PUBLICATIONS**

The following is a list of the product publications available from Fujitsu. Call your nearest Fujitsu Sales Office or Sales Representative to order any document(s) you need. (See the Sales Information section for phone numbers.)

#### MEMORY PRODUCTS

| Dynamic RAM Products Data Book                   | Contains product data sheets for NMOS and CMOS DRAMs,<br>including 1M and 4M devices, and MOS application-specific<br>RAMs.                                                                                                            |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Static RAM Products Data Book                    | Contains product data sheets for high-speed CMOS and BiCMOS SRAMs, low-power CMOS SRAMs and application-specific SRAMs.                                                                                                                |

| ECL RAM Products Data Book                       | Contains product data sheets for ECL and TTL bipolar ECL<br>RAMs, BiCMOS ECL RAMs, and application-specific RAMS<br>including self-timed RAMs (STRAMs).                                                                                |

| Programmable Memory Products Data<br>Book        | Contains product data sheets for programmable ROMs (including<br>registered and wide-temperature range PROMs); CMOS mask-<br>programmable ROMS, OTP ROMs, erasable PROMs, and EE-<br>PROMs; NMOS erasable PROMs and non-volatile RAMs. |

| Memory Modules Data Book                         | Contains product data sheets for CMOS DRAM modules (includ-<br>ing high density and low profile) and CMOS SRAM modules.                                                                                                                |

| Memory Card Products Data Book                   | Contains product data sheets and programming information for<br>68-pin JEIDA and PCMCIA standard memory cards and connec-<br>tors and for 38-pin memory cards.                                                                         |

| Power Transistor Products Data Book              | Contains product data sheets for RETs, Darlington arrays, and FETs.                                                                                                                                                                    |

| Linear Products Data Book                        | Contains product data sheets for op amps, comparators, automo-<br>tive audio amps, power supply controls, motor drivers, disk driv-<br>ers, and converters (A/D, D/A, A/D-D/A, and F/V).                                               |

| Linear Products Selector Guide                   | Presents an overview of linear products.                                                                                                                                                                                               |

| Telecommunication Devices Data Book              | Contains product data sheets for bipolar prescalers and VCOs,<br>CMOS PLLs, BiCMOS single-chip PLLs and Prescalers,<br>CODECs, CMOS telephone ICs, and cellular mobile radio ICs.                                                      |

| Telecommunication Devices Selector<br>Guide      | Presents an overview of telecommunication products and piezo-<br>electric devices.                                                                                                                                                     |

| Interface and Logic Products Selector<br>Guide   | Presents an overview of logic and interface devices.                                                                                                                                                                                   |

| CMOS 4-bit Microcontrollers Data Book,<br>Vol. I | Contains product information, including the development tool for<br>the MB8850 and MB88200 families of 4-bit microcontrollers.                                                                                                         |

| CMOS 4-bit Microcontrollers Data Book, Vol. II   | Contains product information, including the development tool for<br>the MB88500 family of 4-bit microcontrollers.                                                                                                                      |

| CMOS 4-bit Microcontrollers Selector<br>Guide    | Presents an overview of the MB88500 (high end), MB8850 (mid-<br>range), and MB88200 (low end) families of 4-bit microcontrollers.                                                                                                      |

## FUJITSU PRODUCT PUBLICATIONS (Continued)

#### ASIC PRODUCTS

| CMOS Channeled Gate Arrays Data Book<br>and Design Evaluation Guide   | Contains product information for UHB Series High Drive CMOS<br>Gate Arrays and CG10 Series High Drive CMOS Gate Arrays.                                            |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMOS Channelless Gate Arrays Data<br>Book and Design Evaluation Guide | Contains product information for AU Series CMOS Series Gate Arrays and CG21 Series CMOS Gate Arrays.                                                               |

| CMOS Standard Cell Data Book and<br>Design Evaluation Guide           | Contains product information for AU Series Standard Cells.                                                                                                         |

| ASIC CMOS Products Selector Guide                                     | Presents an overview of CMOS channeled and channelless gate arrays and standard cell products.                                                                     |

| BiCMOS Gate Arrays Data Book and<br>Design Evaluation Guide           | Contains product information for BC Series BiCMOS Gate<br>Arrays and BC-H Series BiCMOS Gate Arrays.                                                               |

| ECL Gate Arrays Data Book and Design<br>Evaluation Guide              | Contains product information for ET Series ECL Gate Arrays, H<br>Series ECL Gate Arrays, Ultra-High Performance ECL Gate<br>Arrays, and VH Series ECL Gate Arrays. |

| ASIC Bipolar Products Selector Guide                                  | Presents an overview of BiCMOS and ECL gate array products.                                                                                                        |

| ASIC SOFTWARE                                                         |                                                                                                                                                                    |

#### ASIC SOFTWARE

| The ASIC Gallery (catalog)                   | Discusses the trend in ASICs: migration from using gates as<br>primitives to using LSI and even VLSI macros as design ele-<br>ments.                                                                                                                                                        |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The ASIC Design Environment (catalog)        | Provides an overview of the third-party tools that work in concert<br>with Fujitsu's proprietary tools, ViewCAD <sup>TM</sup> , BankCAD <sup>TM</sup> ,<br>ZephCAD, and FAME. Also included are product profiles explain-<br>ing how the third-party tools fit within the design framework. |

| ViewCAD User's Guide                         | Provides a basic understanding of Fujitsu's proprietary CAD/CAE system, ViewCAD. This book provides information necessary to design, test, simulate, and analyze circuits using Fujitsu's unit cell libraries for AU, UHB, CG10, CG21, and CG31 CMOS technologies.                          |

| ViewCAD Installation Guide                   | Explains how to install Fujitsu's proprietary CAD/CAE system, ViewCAD.                                                                                                                                                                                                                      |

| CMOS ASIC Reference Manual for<br>Validation | Provides a basic understanding of the Valid System on the Sun<br>platform as it interfaces with Fujitsu programs to build circuits<br>using Fujitsu's unit cell libraries for AU and UHB CMOS technolo-<br>gies.                                                                            |

| FAME User's Guide                            | Provides a basic understanding of the Fujitsu ASIC Management<br>Environment (FAME) software as it interfaces with third-party<br>tools (Sun or PC) to build circuits using Fujitsu's unit cell libraries.                                                                                  |

| FAME Reference Manual                        | Provides installation and directory information for the Fujitsu<br>ASIC Management Environment (FAME) software, which uses<br>third-party tools (Sun or PC) to build circuits using Fujitsu's unit<br>cell libraries.                                                                       |

| Synopsys User's Guide                        | Provides a basic understanding of the Synopsys® system as it<br>interfaces with Fujitsu programs to build circuits using Fujitsu's<br>unit cell libraries.                                                                                                                                  |

## FUJITSU PRODUCT PUBLICATIONS (Continued)

#### ASIC SOFTWARE (Continued)

| Verilog-XL User's Guide                     | Provides a basic understanding of the Verilog-XL® system as it<br>interfaces with Fujitsu programs to build circuits using Fujitsu's<br>unit cell libraries.                                                                                                                                                                                  |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Future Publications                         |                                                                                                                                                                                                                                                                                                                                               |

| For Fujitsu Microelectronics, Inc.:         |                                                                                                                                                                                                                                                                                                                                               |

| Master Product Guide/Catalog (1991)         | Presents an overview of the entire range of products offered by<br>Fujitsu Microelectronics.                                                                                                                                                                                                                                                  |

| For Memory Products:                        |                                                                                                                                                                                                                                                                                                                                               |

| Hybrid Products (1991)                      | Presents Fujitsu's hybrid products and discusses thick- and thin-film capabilities.                                                                                                                                                                                                                                                           |

| For ASIC Software:                          |                                                                                                                                                                                                                                                                                                                                               |

| ASIC Design Environment<br>Data Book (1991) | Provides detailed information about the ASIC Design Methodology<br>at Fujitsu. It contains an overview of the third-party tools that work<br>in concert with Fujitsu's proprietary tools, ViewCAD, BankCAD,<br>ZephCAD, and FAME. Also included are product profiles explaining<br>how the third-party tools fit within the design framework. |

| ASICOpen™ Catalog (1991)                    | Provides a small-scale ASIC Design Methodology at Fujitsu. It<br>explains the design processes between two third-party tools, Syn-<br>opsys and Verilog-XL, and Fujitsu's proprietary tools, ViewCAD,<br>BankCAD, and ZephCAD.                                                                                                                |

Synopsys® is a registered trademark of Synopsys, Inc. Verilog-XL® is a registered trademark of Cadence Design Systems, Inc. ViewCAD<sup>™</sup> and BankCAD<sup>™</sup> are trademarks of Fujitsu Limited. ASICOpen<sup>™</sup> is a trademark of Fujitsu Microelectronics, Inc.

## **Contents and Alphanumeric Product List**

#### DRAM PRODUCTS

| Section 1 – NMOS DRAMs – At a Gl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MB81256-10/-12/-15<br>MB81256-80<br>MB81257-10/-12/-15<br>MB81257-80<br>MB81464-10/-12/-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 262144 x 1 bit DRAM       1-3         262144 x 1 bit DRAM       1-25         262144 x 1 bit DRAM       1-45         262144 x 1 bit DRAM       1-69         65536 x 4 bits DRAM       1-93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Section 2 – CMOS DRAMs – At a Gl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

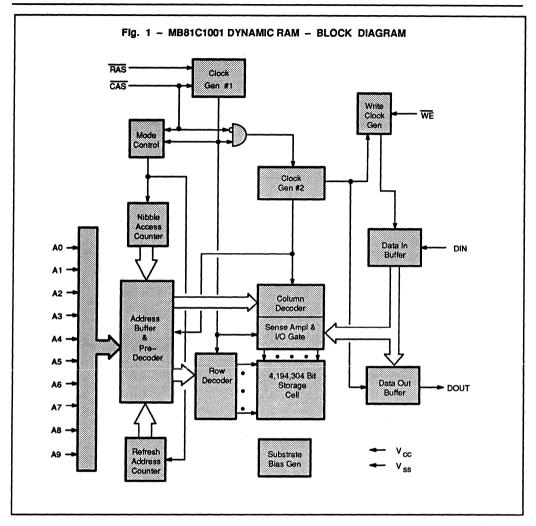

| MB81C1000-70/-80/-10/-12<br>MB81C1000-70L/-80L/-10L/-12L<br>MB81C1000A-60/-70/-80/-10<br>MB81C1000A-70L/-80L/-10L<br>MB81C1001-70/-80/-10/-12<br>MB81C1001A-70L/-80L/-10L/-12L<br>MB81C4256-70L/-80L/-10L<br>MB81C4256-70L/-80L/-10L/-12L<br>MB81C4256A-60/-70/-80/-10<br>MB81C4256A-70L/-80L/-10L<br>MB81C4256A-70L/-80L/-10L<br>MB81C4256A-70L/-80L/-10L<br>MB81C4256A-70L/-80L/-10L<br>MB81C4256A-70L/-80L/-10L<br>MB81C4256A-70L/-80L/-10L<br>MB81C4256A-70L/-80L/-10L<br>MB81C4256A-70L/-80L/-10L<br>MB81C4256A-70L/-80L/-10L<br>MB81C4256A-70L/-80L/-10L/-12L<br>MB81C4101-80L/-10L/-12L<br>MB81C400-80L/-10L/-12L<br>MB81C400-80L/-10L/-12L<br>MB81C400-80L/-10L/-12L<br>MB81C400-80L/-10L/-12L<br>MB81C400-80L/-10L/-12L | 1048576 x 1 bit Fast Page Mode DRAM2-351048576 x 1 bit Fast Page Mode Low Power DRAM2-251048576 x 1 bit Fast Page Mode DRAM2-471048576 x 1 bit Fast Page Mode Low Power DRAM2-471048576 x 1 bit Nibble Mode DRAM2-951048576 x 1 bit Nibble Mode DRAM2-951048576 x 1 bit Nibble Mode Low Power DRAM2-1351048576 x 1 bit Nibble Mode Low Power DRAM2-1351048576 x 1 bit Nibble Mode Low Power DRAM2-165262144 x 4 bits Fast Page Mode DRAM2-165262144 x 4 bits Fast Page Mode DRAM2-235262144 x 4 bits Fast Page Mode Low Power DRAM2-2614M x 1 bit Fast Page Mode DRAM2-2634M x 1 bit Fast Page Mode Low Power DRAM2-3054M x 1 bit Fast Page Mode Low Power DRAM2-3054M x 1 bit Nibble Mode DRAM2-3054M x 1 bit Sast Page Mode DRAM2-3054M x 1 bit Nibble Mode DRAM2-3254M x 1 bit Sast Page Mode DRAM2-3254M x 1 bit Sast Page Mode DRAM2-3254M x 1 bit Nibble Mode DRAM2-3264M x 1 bit Sast Page Mode DRAM2-3254M x 1 bit Sast Page Mode DRAM2-3254M x 1 bit Sast Page Mode DRAM2-3554M x 1 bit Sast Page Mode DRAM2-3554M x 1 bit Sast |

| Section 3 – MOS Application-Specif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | i <b>c RAMs</b> — At a Glance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MB81461-12/-15<br>MB81461B-12/-15<br>MB81C1501                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NMOS 65536 x 4 bits Dual-Port DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

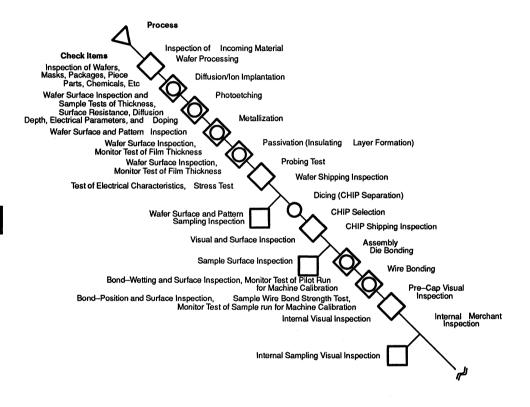

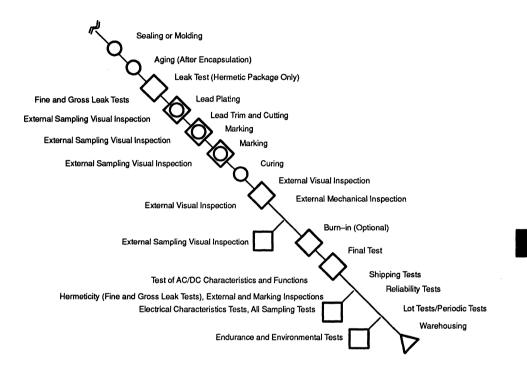

| Section 4 – Quality and Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | — At a Glance 4–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

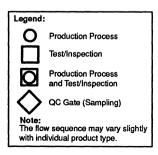

| Quality Control at Fujitsu<br>Quality Control Processes at Fujit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## Contents and Alphanumeric Product List (Continued)

#### DRAM PRODUCTS

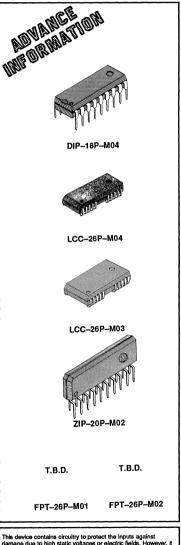

| Section 5 – Ordering and Package Information — At a Glance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

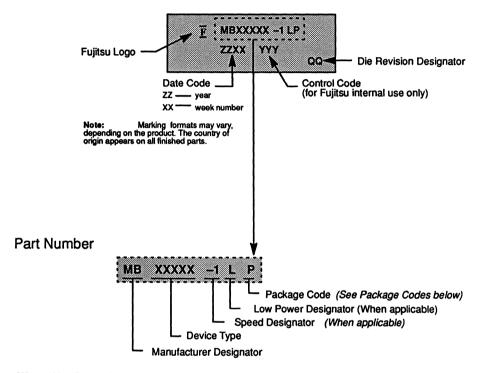

| Product Marking       5–3         Ordering Code (Part Number)       5–3         Package Codes – Plastic       5–4         Package Codes – Ceramic       5–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Section 6 – Sales Information — At a Glance 6–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Introduction to Fujitsu       6–3         Fujitsu Limited (Japan)       6–3         Fujitsu Microelectronics, Inc. (U.S.A.)       6–4         Fujitsu Bectronics Devices Europe       6–6         Fujitsu Microelectronics Asia PTE Ltd. (Singapore)       6–8         Integrated Circuits Corporate Headquarters – Worldwide       6–9         FMI Sales Offices for North and South America       6–10         FMI Representatives – USA       6–11         FMI Representatives – Canada       6–13         FMI Representatives – Mexico       6–13         FMI Representatives – Nerico       6–13         FMI Representatives – Canada       6–14         FMI Distributors – USA       6–14         FMI Distributors – Canada       6–13         FMI Distributors – USA       6–14         FMI Distributors – Canada       6–16         FMG Sales Offices for Europe, FML and FMIL       6–19         FMG Sales Offices for Europe, FML and FMIL       6–20         FMAP Sales Offices for Asia, Australia, and Oceania       6–22         FMAP Representatives – Asia and Australia       6–24 |

| Section 7 – Appendices – Design Information —At a Glance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Appendix 1.       Application Note:       Various Features of Fujitsu DRAMs       7–3         Appendix 2.       Application Note:       The Soft Error Rate for 4M DRAM Devices       7–27         Appendix 3.       Technical Paper:       3D Stacked Capacitor Cell for Mega Bit DRAM       7–35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## Contents and Alphanumeric Product List (Continued)

#### DRAM PRODUCTS

#### Alphanumeric List of Fujitsu Part Numbers

| MB81256-10/-12/-15       1–3         MB81256-80       1–25         MB81257-10/-12/-15       1–45         MB81257-80       1–69                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MB81461-12/-15                                                                                                                                                                                                                                   |

| MB814100-80/-10/-12       2-287         MB814100-80L/-10L/-12L       2-307         MB814101-80/-10/-12       2-309         MB814101-80L/-10L/-12L       2-329         MB814400-80/-10/-12       2-331         MB814400-80L/-10L/-12L       2-353 |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| MB81C4256-70/-80/-10/-12 2–187<br>MB81C4256-70L/-80L/-10L/-12L . 2–211<br>MB81C4256A-60/70/-80/-10 2–235<br>MB81C4256A-70L/-80L/-10L 2–261 |

x

## Introduction

| Page | Title                  |

|------|------------------------|

| xiil | Fujitsu's Dynamic RAMs |

Introduction

Dynamic RAM Data Book

#### Fujitsu's Dynamic RAM Products

#### Introduction

Fujitsu manufactures a wide range of integrated circuits that includes linear products, microprocessors, telecommunications circuits, ASICs, high–speed ECL logic, power components (consisting of both discrete transistors and transistor arrays), and both static and dynamic RAMs. An extensive line of memory products includes volatile and non-volatile CMOS and ECL devices.

Fujitsu's Dynamic RAM product line offers devices for use in a wide range of applications. These memories are manufactured to meet the high standard of quality and reliability that is found in all Fujitsu products.

This data book includes product information on all of Fujitsu's currently available DRAM products.

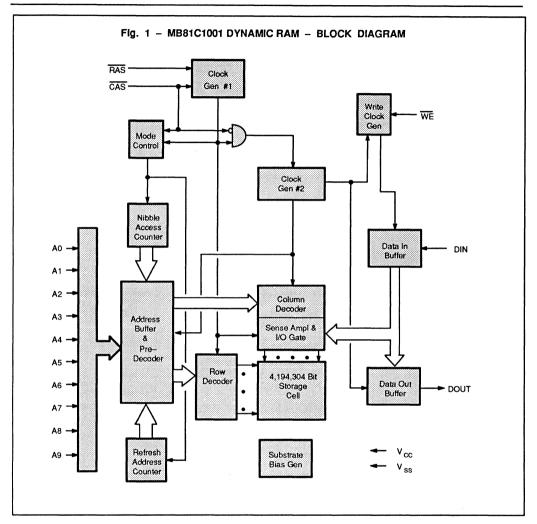

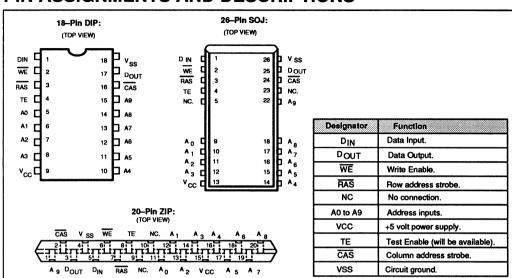

#### NMOS and CMOS DRAMs

Fujitsu manufactures a complete family of leading technology dynamic random access memories for the data processing, telecom, and industrial markets. This family consists of the highest density devices currently available with a broad selection of organizations, access modes, and packages.

#### Application-Specific DRAMs

Fujitsu offers a family of multi-port dynamic random access memories tailored for video imaging and graphics applications. These devices adhere to JEDEC standards where applicable and are available in the popular packages.

xiv

## Section 1

1

\_\_\_\_\_

| THEOD DITAMS |                          | 111 u Om                       |                             |                         |                                  |                                |  |

|--------------|--------------------------|--------------------------------|-----------------------------|-------------------------|----------------------------------|--------------------------------|--|

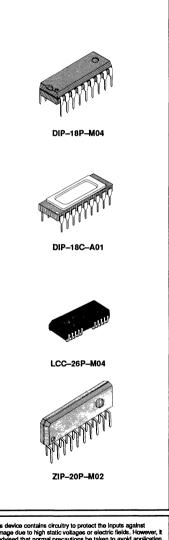

| Page         | Device                   | Maximum<br>Access<br>Time (ns) | Capacity                    | Package<br>Options      |                                  |                                |  |

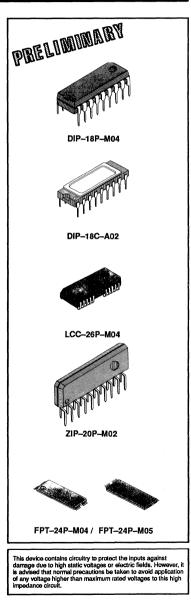

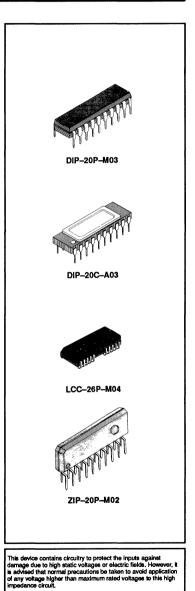

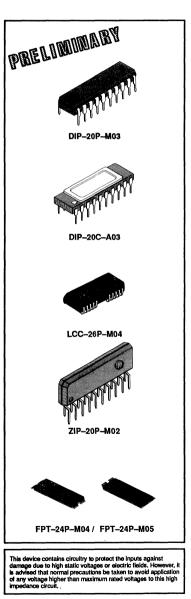

| 1–3          | MB81256–10<br>–12<br>–15 | 100<br>120<br>150              | 262144 bits<br>(262144 x 1) | 16-pin Ce               | istic<br>ramic<br>istic<br>ramic | DIP, ZIP<br>DIP<br>PLCC<br>LCC |  |

| 1–25         | MB81256-80               | 80                             | 262144 bits<br>(262144 x 1) | 16-pin Ce               | istic<br>ramic<br>istic          | DIP, ZIP<br>DIP<br>PLCC        |  |

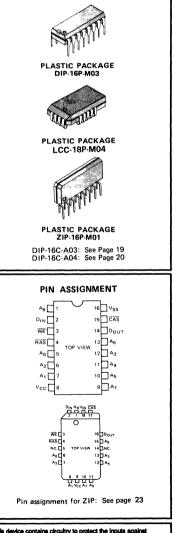

| 1-45         | MB81257–10<br>–12<br>–15 | 100<br>120<br>150              | 262144 bits<br>(262144 x 1) | 16-pin Ce<br>18-pin Pla | astic<br>ramic<br>astic<br>ramic | DIP, ZIP<br>DIP<br>PLCC<br>LCC |  |

| 1–69         | MB81257-80               | 80                             | 262144 bits<br>(262144 x 1) | 16-pin Ce               | astic<br>ramic<br>astic          | DIP, ZIP<br>DIP<br>PLCC        |  |

| 1–93         | MB81464-12<br>-15        | 120<br>150                     | 262144 bits<br>(65536 x 4)  | 18-pin Ce               | astic<br>ramic<br>astic          | DIP, PLCC<br>DIP<br>ZIP        |  |

## NMOS DRAMs — At a Glance

DATA SHEET =

## **MB81256**-10/-12/-15

## MOS 262,144 BIT DYNAMIC RANDOM ACCESS MEMORY

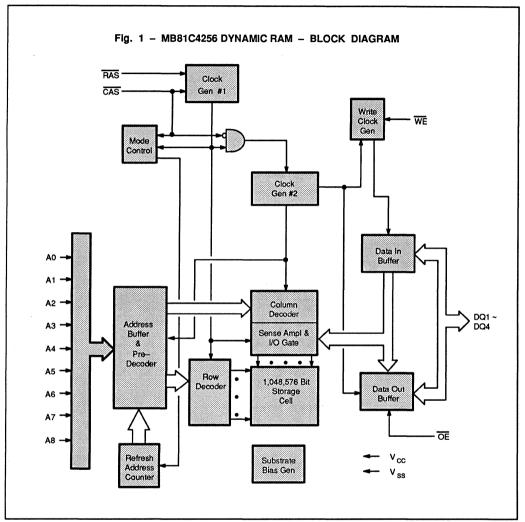

#### 262,144 Bit Dynamic Random Access Memory

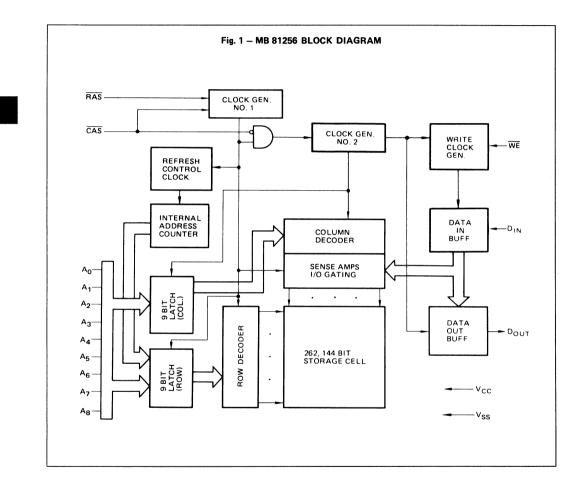

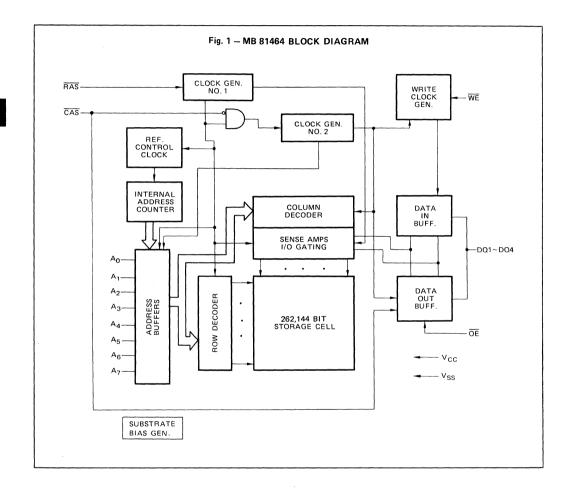

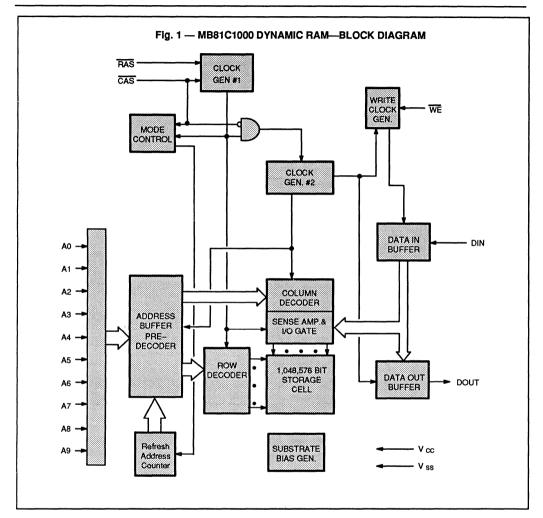

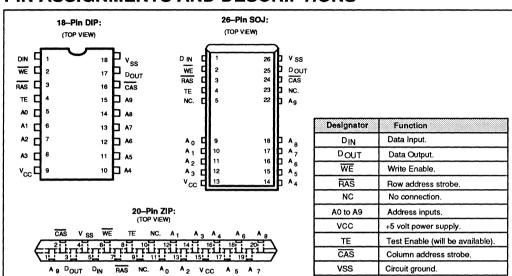

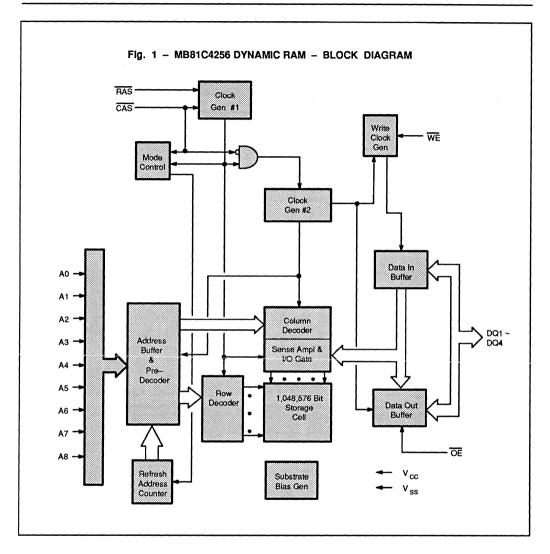

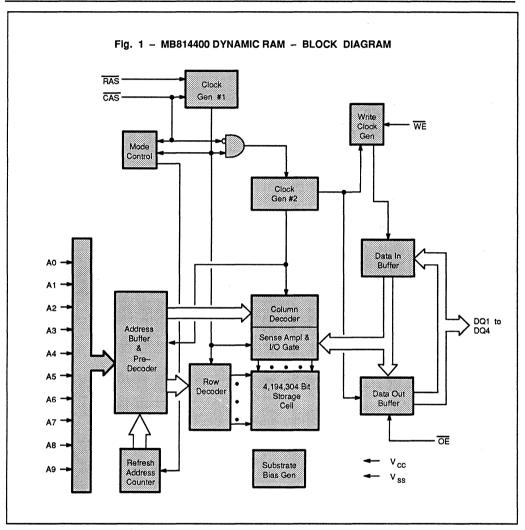

The Fujitsu MB81256 is a fully decoded, dynamic NMOS random access memory organized as 262,144 one-bit words. The design is optimized for high speed, high performance applications such as mainframe memory, buffer memory, peripheral storage, and environments where low power dissipation and a compact layout are required.

Multiplexed row and column address inputs permit the MB81256 to be housed in standard 16-pin DIP and ZIP packages or an 18-pin PLCC package. Pinouts conform to JEDEC-approved pinouts. Additionally, the MB81256 offers new functional enhancements that make it more versatile than previous dynamic RAMs. CAS-before-RAS refresh provides an on-chip refresh capability that is upwardly compatible with the MB8266A. The MB81256 also features page mode which allows high speed random access of up to 512 bits of data within the same row.

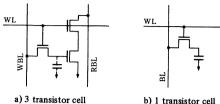

The MB81256 is fabricated using silicon gate NMOS and Fujitsu's advanced Triple-layer Polysilicon process. This process, coupled with single-transistor memory storage cells, permits maximum circuit density and minimal chip size. Dynamic circuitry is used in the design, including the sense amplifiers. Clock timing requirements are noncritical, and power supply tolerance is very wide. All inputs are TTL compatible.

- 262,144 x 1 RAM organization

- Silicon-gate, Triple Poly NMOS, single transistor cell

- Row Access Time 100 ns max. (MB 81256-10) 120 ns max. (MB 81256-12) 150 ns max. (MB 81256-15)

- Cycle Time 200 ns min. (MB 81256-10) 220 ns min. (MB 81256-12) 260 ns min. (MB 81256-15)

- Page Cycle Time 100 ns max. (MB 81256-10) 120 ns max. (MB 81256-12) 145 ns max. (MB 81256-15)

- Single +5 V Supply, ±10% tolerance

- Low Power 385 mW max. (MB 81256-10) 358 mW max. (MB 81256-12) 314 mW max. (MB 81256-15) 25 mW max. (standby)

#### Absolute Maximum Ratings

| Parameter                                                                                  |         | Symbol           | Value       | Unit |

|--------------------------------------------------------------------------------------------|---------|------------------|-------------|------|

| Voltage at any pin relative to $V_{SS}$<br>Voltage of $V_{CC}$ supply relative to $V_{SS}$ |         | VIN, VOUT        | -1 to +7    | v    |

|                                                                                            |         | V <sub>CC</sub>  | -1 to +7    | v    |

| Storage Temperature                                                                        | Ceramic | T <sub>STG</sub> | -55 to +150 | °C   |

|                                                                                            | Plastic |                  | -55 to +125 |      |

| Power Dissipation                                                                          | ·       | PD               | 1.0         | w    |

| Short Circuit Output Current                                                               |         |                  | 50          | mA   |

Note: Permanent device damage may occur if absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operation sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Copyright C 1990 by FUJITSU LIMITED and Fujitsu Microelectronics, Inc.

- 256 refresh cycles every 4 ms

- CAS-before-RAS, RAS-only, Hidden refresh capability

- High speed Read-white-Write cycle

- tAR, twcR, toHR, tRWD are eliminated

- Output unlatched cycle end allows two-dimensional chip select

- Common I/O capability using Early Write operation

- On-chip latches for Addresses and Data-in

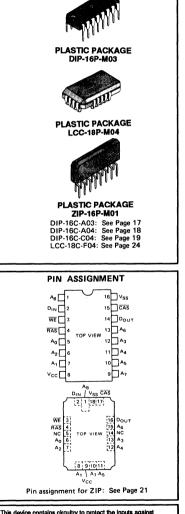

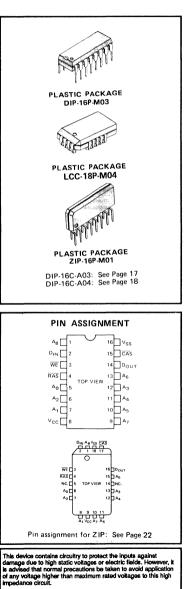

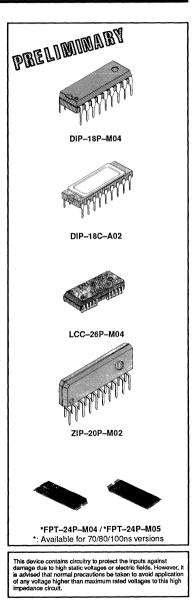

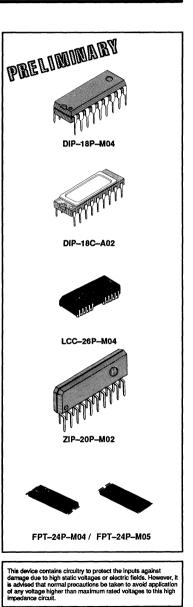

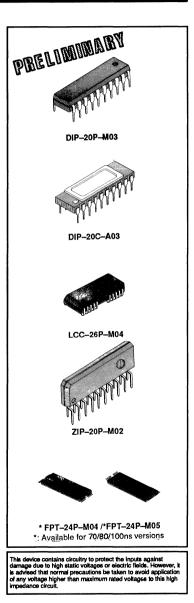

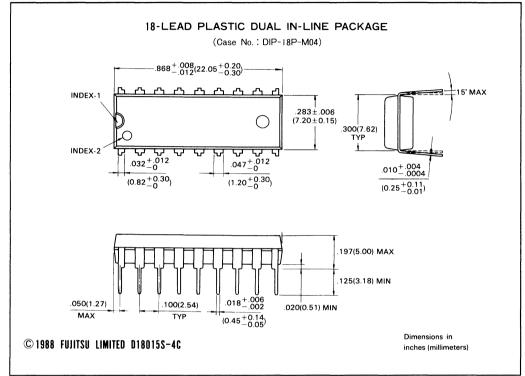

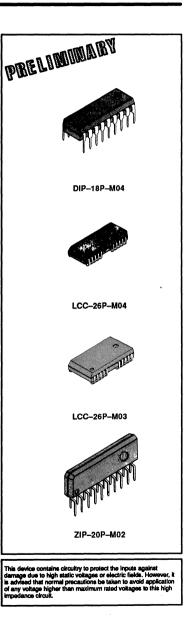

- Standard 16-Pin Plastic Packages: DIP (MB81256-XXP) ZIP (MB81256-XXPSZ) Standard 18-Pin Plastic Package: PLCC(MB81256-XXPV) Standard 16-Pin Ceramic Packages: DIP (MB81256-XXC) Seam Weld DIP (MB81256-XXZ) Cerdip Standard 18-Pad Ceramic Package: LCC (MB81256-XXTV)

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

## **CAPACITANCE** $(T_A = 25^{\circ}C)$

| Parameter                                   | Symbol           | Тур | Max | Unit |

|---------------------------------------------|------------------|-----|-----|------|

| Input Capacitance $A_0$ to $A_8$ , $D_{IN}$ | C <sub>IN1</sub> |     | 7   | pF   |

| Input Capacitance RAS, CAS, WE              | C <sub>IN2</sub> |     | 10  | pF   |

| Output Capacitance D <sub>OUT</sub>         | Cout             |     | 7   | pF   |

1

## **RECOMMENDED OPERATING CONDITIONS**

(Referenced to V<sub>SS</sub>)

| Parameter                      | Symbol          | Min  | Тур | Max | Unit | Operating<br>Temperature |

|--------------------------------|-----------------|------|-----|-----|------|--------------------------|

| Supply Voltage                 | V <sub>cc</sub> | 4.5  | 5.0 | 5.5 | v    |                          |

| Suppry Voltage                 | V <sub>ss</sub> | Q    | 0   | 0   | v    |                          |

| Input High Voltage, all inputs | V <sub>IH</sub> | 2.4  |     | 6.5 | v    | 0°C to +70°C             |

| Input Low Voltage, all inputs  | VIL             | -2.0 |     | 0.8 | v    |                          |

## DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| Parameter                                                                                                                       |             |                   |     |     |     |      |

|---------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|-----|-----|-----|------|

|                                                                                                                                 |             | Symbol            | Min | Тур | Max | Unit |

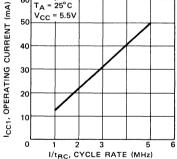

| OPERATING CURRENT*                                                                                                              | MB 81256-10 |                   |     |     | 70  |      |

| Average Power Supply Current                                                                                                    | MB 81256-12 | I <sub>CC1</sub>  |     | 65  | mA  |      |

| (RAS, CAS cycling; t <sub>RC</sub> = Min.)                                                                                      | MB 81256-15 |                   |     |     | 57  |      |

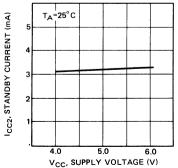

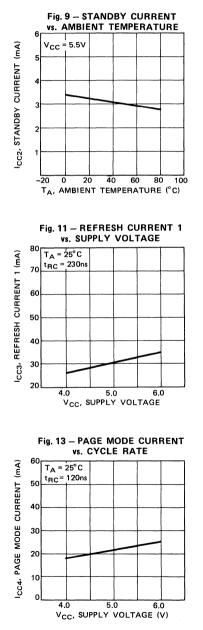

| STANDBY CURRENT<br>Standby Power Supply Current<br>(RAS, CAS=V <sub>IH</sub> )                                                  |             | I <sub>CC2</sub>  |     |     | 4.5 | mA   |

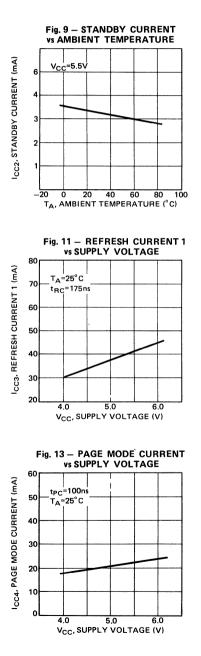

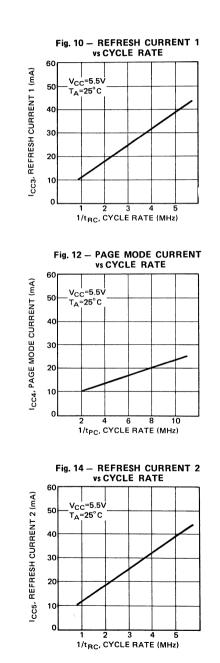

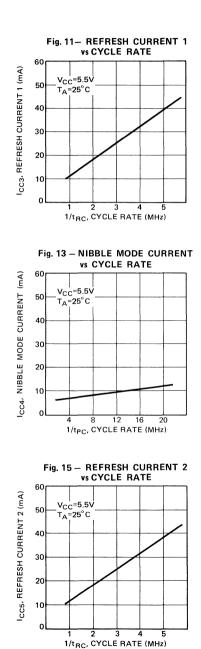

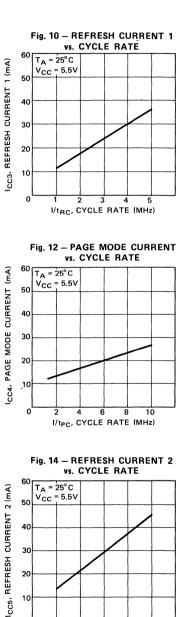

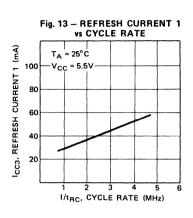

| REFRESH CURRENT 1*<br>Average Power Supply Current<br>(RAS cycling, CAS = V <sub>IH</sub> ; t <sub>RC</sub> = Min.)             | MB 81256-10 |                   |     |     | 60  |      |

|                                                                                                                                 | MB 81256-12 | I <sub>CC3</sub>  |     |     | 5,5 | mA   |

|                                                                                                                                 | MB 81256-15 | 1                 |     |     | 50  |      |

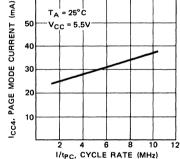

| PAGE MODE CURRENT*<br>Average Power Supply Current                                                                              | MB 81256-10 | I <sub>CC4</sub>  |     |     | 35  |      |

|                                                                                                                                 | MB 81256-12 |                   |     |     | 30  | mA   |

| (RAS = V <sub>IL</sub> , CAS cycling; t <sub>PC</sub> = Min.)                                                                   | MB 81256-15 |                   |     |     | 25  |      |

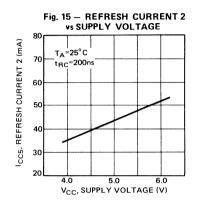

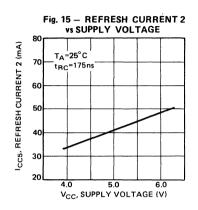

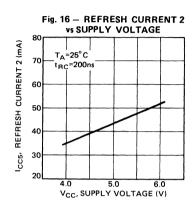

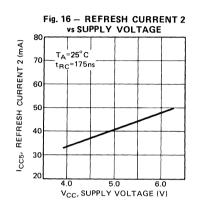

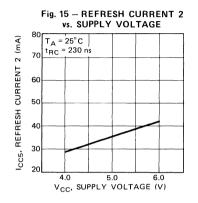

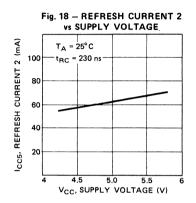

| REFRESH CURRENT 2*                                                                                                              | MB 81256-10 |                   |     |     | 65  |      |

| Average Power Supply Current                                                                                                    | MB 81256-12 | I <sub>CC5</sub>  |     |     | 60  | mA   |

| (CAS-before-RAS; t <sub>RC</sub> = Min.)                                                                                        | MB 81256-15 |                   |     |     | 55  |      |

| INPUT LEAKAGE CURRENT any input ( $V_{IN}$ = 0V to<br>5.5V, $V_{CC}$ = 5.5V, $V_{SS}$ = 0V, all other pins not under test = 0V) |             |                   | -10 |     | 10  | μΑ   |

| OUTPUT LEAKAGE CURRENT (Data is disabled, $V_{OUT} = 0V$ to 5.5V)                                                               |             | I <sub>O(L)</sub> | -10 |     | 10  | μΑ   |

| OUTPUT LEVEL Output Low Voltage (I <sub>OL</sub> = 4.2 mA)                                                                      |             | Vol               |     |     | 0.4 | v    |

| OUTPUT LEVEL Output high Voltage (I <sub>OH</sub> = -5.0 mA)                                                                    |             | V <sub>он</sub>   | 2.4 |     |     | v    |

NOTE \*: I<sub>CC</sub> is depended on output loading and cycle rates. Specified values are obtained with the output open.

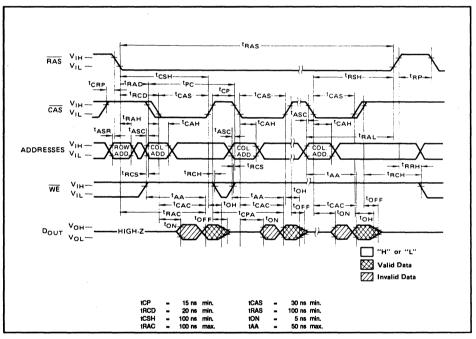

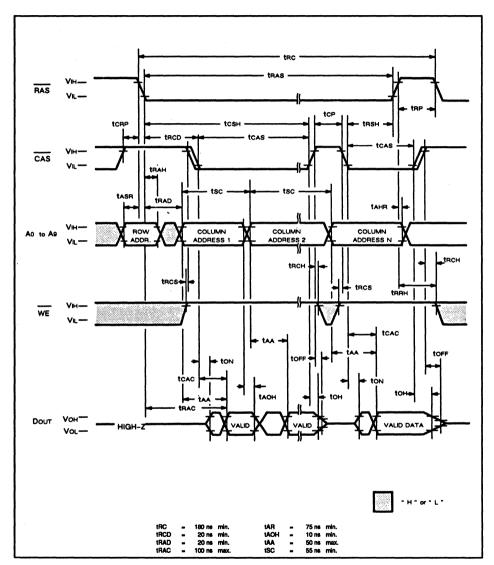

## AC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.) NOTES 1, 2, 3

| Parameter NOTES                                                         | Symbol           | MB 81256-10 |        | MB 81256-12 |        | MB 81256-15 |        | Unit |

|-------------------------------------------------------------------------|------------------|-------------|--------|-------------|--------|-------------|--------|------|

|                                                                         |                  | Min         | Max    | Min         | Max    | Min         | Max    | Onit |

| Time between Refresh                                                    | t <sub>REF</sub> |             | 4      |             | 4      |             | 4      | ms   |

| Random Read/Write Cycle Time                                            | t <sub>RC</sub>  | 200         |        | 220         |        | 260         |        | ns   |

| Read-Write Cycle Time                                                   | t <sub>RWC</sub> | 200         |        | 220         |        | 260         |        | ns   |

| Access Time from RAS 4 6                                                | t <sub>RAC</sub> |             | 100    |             | 120    |             | 150    | ns   |

| Access Time from CAS 5 6                                                | t <sub>CAC</sub> |             | 50     |             | 60     |             | 75     | ns   |

| Output Buffer Turn off Delay                                            | t <sub>OFF</sub> | 0           | 25     | 0           | 25     | 0           | 30     | ns   |

| Transition Time                                                         | t <sub>T</sub>   | 3           | 50     | 3           | 50     | 3           | 50     | ns   |

| RAS Precharge Time                                                      | t <sub>RP</sub>  | 85          |        | 90          |        | 100         |        | ns   |

| RAS Pulse Width                                                         | t <sub>RAS</sub> | 105         | 100000 | 120         | 100000 | 150         | 100000 | ns   |

| RAS Hold Time                                                           | t <sub>RSH</sub> | 55          |        | 60          |        | 75          |        | ns   |

| CAS Pulse Width                                                         | t <sub>CAS</sub> | 55          | 100000 | 60          | 100000 | 75          | 100000 | ns   |

| CAS Hold Time                                                           | t <sub>сsн</sub> | 105         |        | 120         |        | 150         |        | ns   |

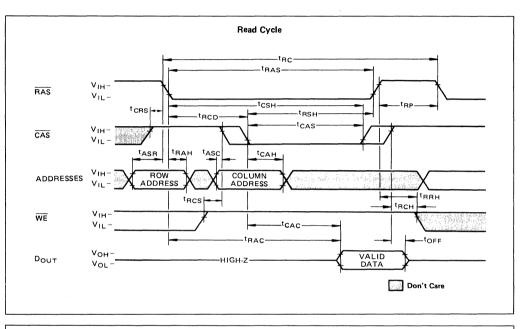

| RAS to CAS Delay Time 78                                                | t <sub>RCD</sub> | 20          | 50     | 22          | 60     | 25          | 75     | ns   |

| CAS to RAS Set Up Time                                                  | t <sub>CRS</sub> | 10          |        | 10          |        | 10          |        | ns   |

| Row Address Set Up Time                                                 | t <sub>ASR</sub> | 0           |        | 0           |        | 0           |        | ns   |

| Row Address Hold Time                                                   | t <sub>RAH</sub> | 10          |        | 12          |        | 15          |        | ns   |

| Column Address Set Up Time                                              | t <sub>ASC</sub> | 0           |        | 0           |        | 0           |        | ns   |

| Column Address Hold Time                                                | t <sub>CAH</sub> | 15          |        | 20          |        | 25          |        | ns   |

| Read Command Set Up Time                                                | t <sub>RCS</sub> | 0           |        | 0           |        | 0           |        | ns   |

| Read Command Hold Time Referenced g                                     | t <sub>RCH</sub> | 0           |        | 0           |        | 0           |        | ns   |

| Read Command Hold Time Referenced g                                     | t <sub>RRH</sub> | 20          |        | 20          |        | 20          |        | ns   |

| Write Command Set Up Time                                               | twcs             | 0           |        | 0           |        | 0           |        | ns   |

| Write Command Pulse Width                                               | t <sub>wP</sub>  | 15          |        | 20          |        | 25          |        | ns   |

| Write Command Hold Time                                                 | t <sub>wcн</sub> | 15          |        | 20          |        | 25          |        | ns   |

| Write Command to RAS Lead Time                                          | t <sub>RWL</sub> | 35          |        | 40          |        | 45          |        | ns   |

| Write Command to CAS Lead Time                                          | t <sub>CWL</sub> | 35          |        | 40          |        | 45          |        | ns   |

| Data In Set Up Time                                                     | t <sub>DS</sub>  | 0           |        | 0           |        | 0           |        | ns   |

| Data In Hold Time                                                       | t <sub>DH</sub>  | 15          |        | 20          |        | 25          |        | ns   |

| CAS to WE Delay 10                                                      | tcwp             | 15          |        | 20          |        | 25          |        | ns   |

| Refresh Set Up Time for CAS Referenced<br>to RAS (CAS-before-RAS cycle) | t <sub>FCS</sub> | 20          |        | 20          |        | 20          |        | ns   |

| Refresh Hold Time for CAS Referenced to RAS (CAS-before-RAS cycle)      | t <sub>FCH</sub> | 20          |        | 25          |        | 30          |        | ns   |

## AC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| Parameter NOTES                                      | Symbol            | MB 81256-10 |       | MB 81256-12 |       | MB 81256-15 |       | Unit |

|------------------------------------------------------|-------------------|-------------|-------|-------------|-------|-------------|-------|------|

|                                                      |                   | Min         | Max   | Min         | Max   | Min         | Max   | Unit |

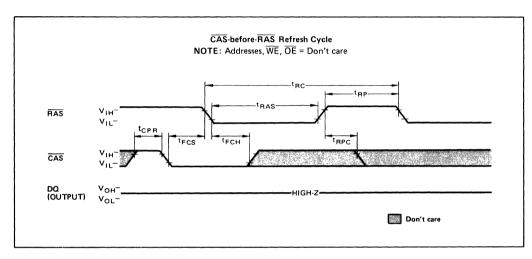

| CAS Precharge Time (CAS-before-RAS cycle)            | t <sub>CPR</sub>  | 20          |       | 25          |       | 30          |       | ns   |

| RAS Precharge to CAS Active Time<br>(Refresh cycles) | t <sub>RPC</sub>  | 20          |       | 20          |       | 20          |       | ns   |

| Page Mode Read/Write Cycle Time                      | t <sub>PC</sub>   | 100         |       | 120         |       | 145         |       | ns   |

| Page Mode Read-Write Cycle Time                      | t <sub>prwc</sub> | 100         |       | 120         |       | 145         |       | ns   |

| Page Mode CAS Precharge Time                         | t <sub>CP</sub>   | 40          |       | 50          |       | 60          |       | ns   |

| Refresh Counter Test Cycle Time                      | t <sub>rtc</sub>  | 330         |       | 375         |       | 430         |       | ns   |

| Refresh Counter Test RAS Pulse Width                 | t <sub>tras</sub> | 230         | 10000 | 265         | 10000 | 320         | 10000 | ns   |

| Refresh Counter Test CAS Precharge Time 11           | t <sub>CPT</sub>  | 50          |       | 60          |       | 70          |       | ns   |

#### Notes:

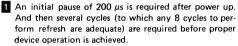

1 An initial pause of 200  $\mu$ s is required after power-up. And then several cycle (to which any 8 cycle to perform refresh are adequate) are required before proper device operation is achieved.

If internal refresh counter is to be effective, a minimum of 8  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycles are required.

- 2 AC characteristics assume  $t_T = 5$  ns.

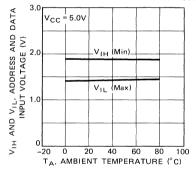

- $V_{IH}$  (min) and  $V_{IL}$  (max) are refrence levels for measuring timing of input signals. Also, transition times are measured between  $V_{IH}$  (min) and  $V_{IL}$  (max.).

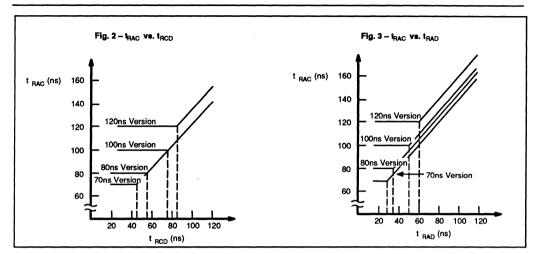

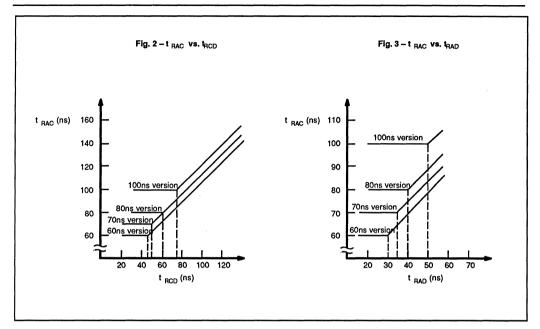

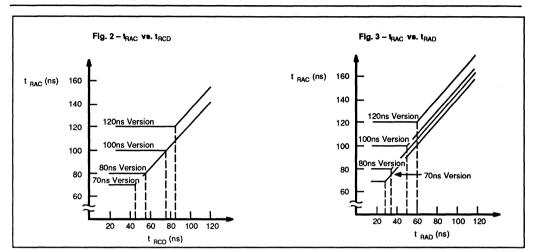

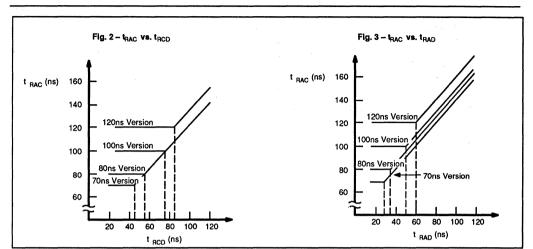

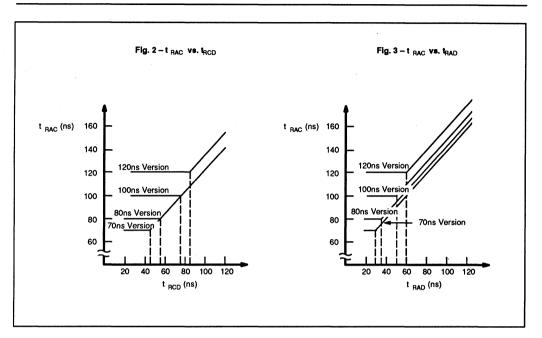

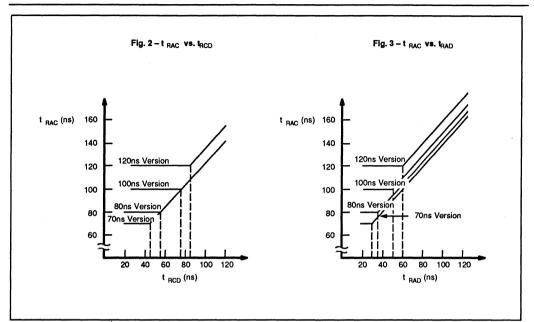

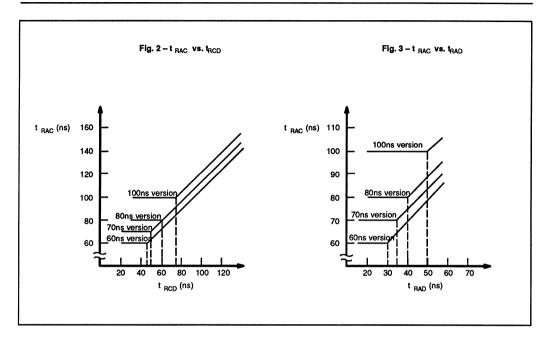

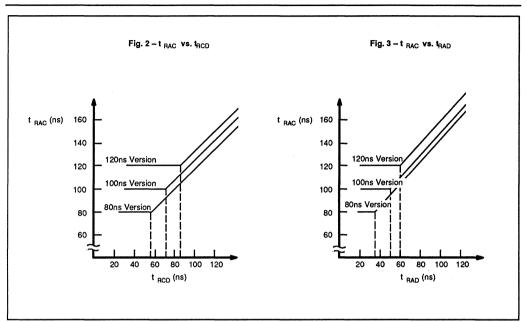

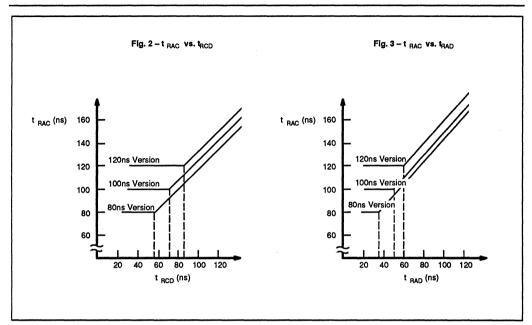

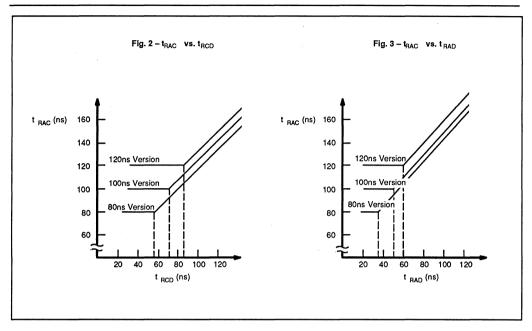

- 4 Assumes that  $t_{RCD} \leq t_{RCD}$  (max.) If  $t_{RCD}$  is greater than the maximum recommended value shown in this table,  $t_{RAC}$  will increase by the amount that  $t_{RCD}$  exceeds the value shown.

- 5 Assumes that  $t_{RCD} \ge t_{RCD}$  (max.).

- 6 Measured with a load equivalent to 2 TTL loads and 100 pF.

- 7 Operation within the  $t_{RCD}$  (max) limit insures that  $t_{RAC}$  (max) can be met.  $t_{RCD}$  (max) is specified as a reference point only; if  $t_{RCD}$  is greater than the specified  $t_{RCD}$  (max) limit, then access time is controlled exclusively by  $t_{CAC}$ .

- $B t_{RCD} (min) = t_{RAH} (min) + 2t_T (t_T = 5ns) + t_{ASC} (min).$

- 9 Either t<sub>RRH</sub> or t<sub>RCH</sub> must be satisfied for a read cycle.

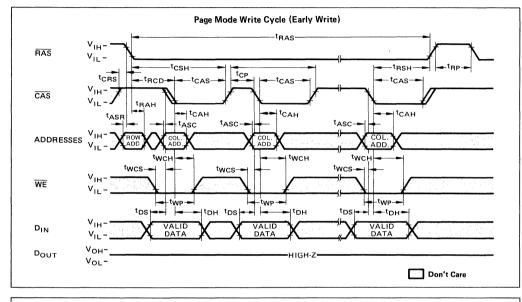

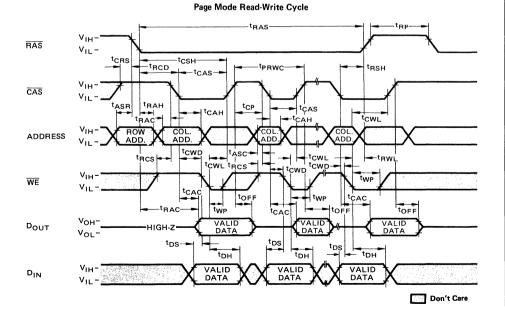

- **10**  $t_{WCS}$  and  $t_{CWD}$  are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If  $t_{WCS} \ge t_{WCS}$  (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout entire cycle.

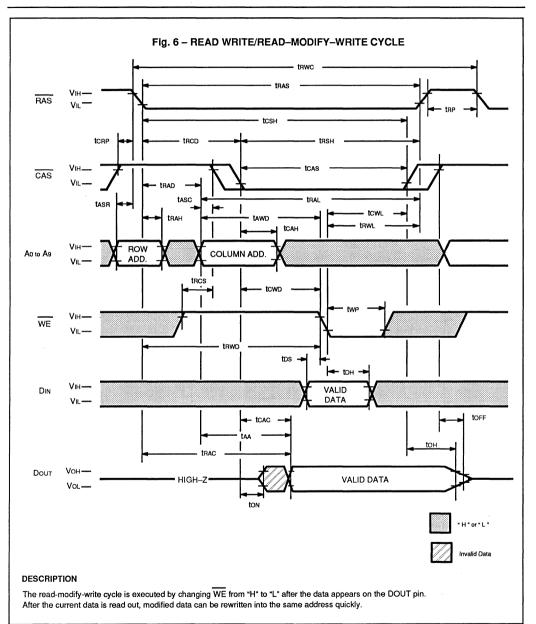

If  $t_{CWD} \ge t_{CWD}$  (min) the cycle is a read-write cycle and data out will contain data read from the selected cell. If neither of the above sets of conditions is satisfied the condition of the data out is indeterminate.

11 Test mode cycle only.

Í

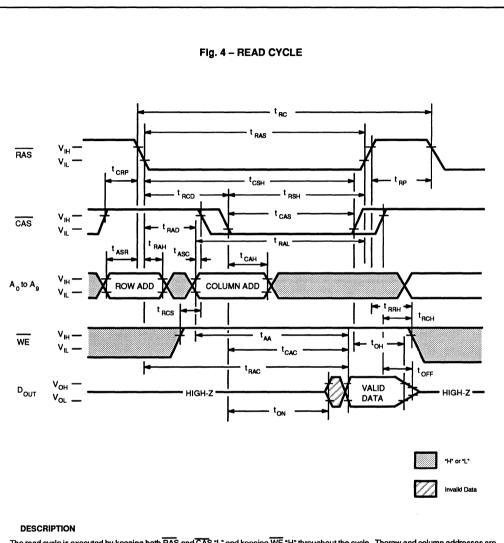

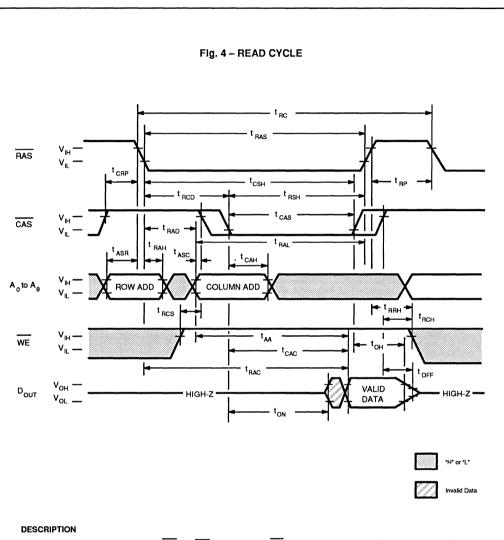

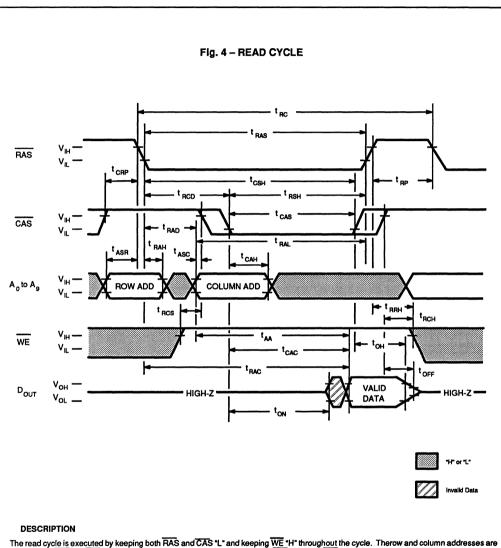

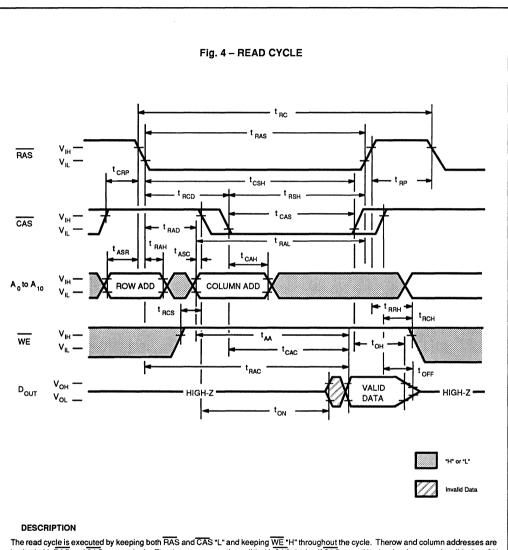

## DESCRIPTION

#### **Simple Timing Requirement**

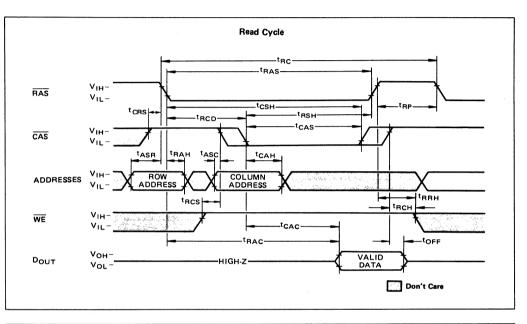

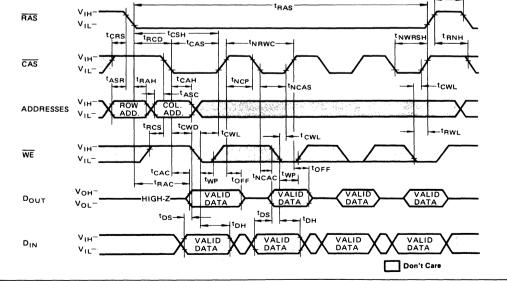

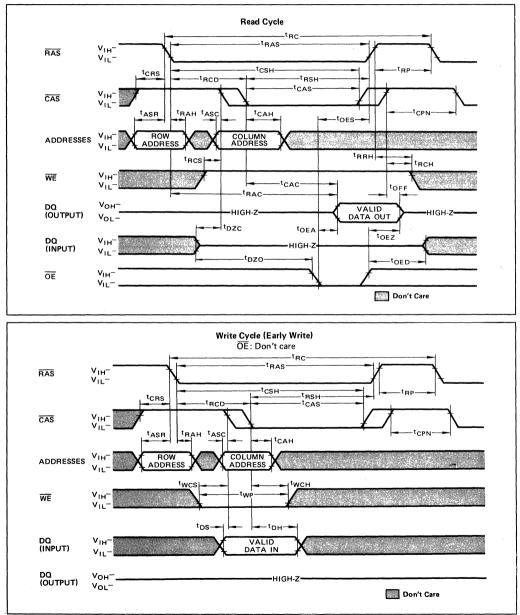

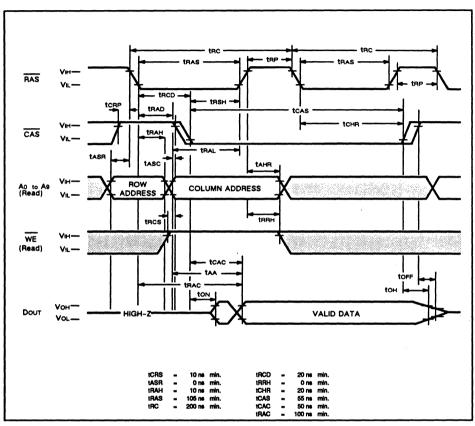

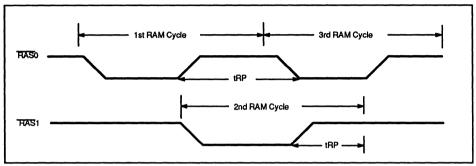

The MB 81256 has improved circuitry that eases timing requirements for high speed access operations. The MB 81256 can operate under the condition of t<sub>RCD</sub> (max) = t<sub>CAC</sub> thus providing optimal timing for address multiplexing. In addition, the MB 81256 has the minimal hold time of Address (t<sub>CAH</sub>), WE (twcH) and DIN (tpH). The MB 81256 provides higher throughput in inter-leaved memory system applications. Fujitsu has made timing requirements that are referenced to RAS nonrestrictive and deleted them from the data sheet, these include tAB, twcR, t<sub>DHR</sub> and t<sub>RWD</sub>. As a result, the hold times of the Column Address,  $D_{IN}$  and  $\overline{WE}$  as well as  $t_{CWD}$  (CAS to WE Delay) are not ristricted by tBCD.

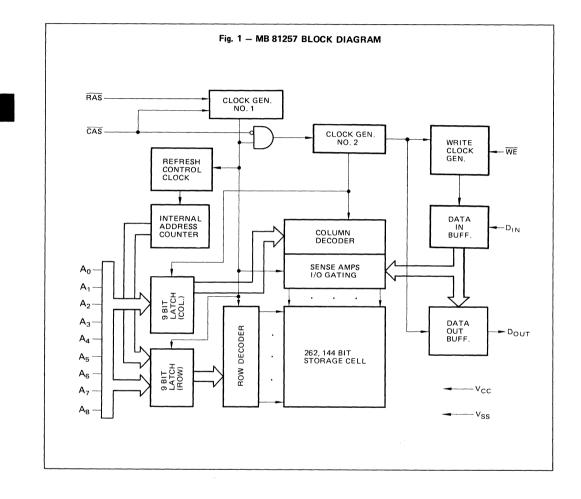

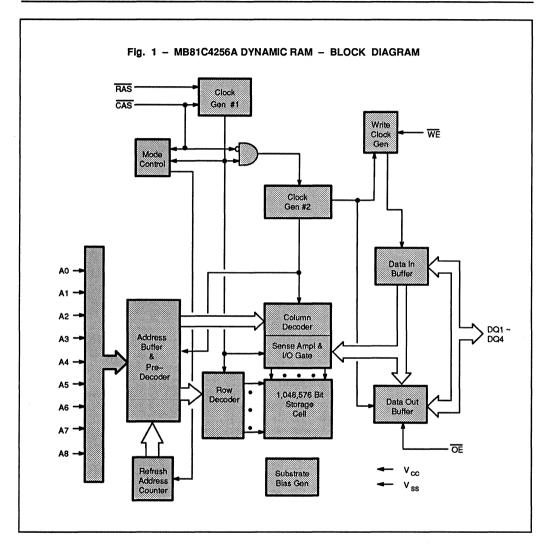

#### Address Inputs:

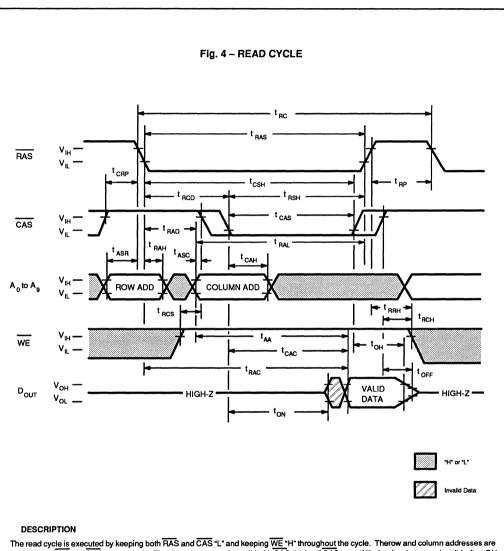

A total of eighteen binary input address bits are required to decode any 1 of 262.144 cell locations within the MB 81256. Nine row-address bits are established on the input pins (An to  $A_{R}$ ) and are latched with the Row Address Strobe (RAS), Nine columnaddress bits are established on the input pins and are latched with the Column Address Strobe (CAS). All row addresses must be stable on or before the falling edge of RAS. CAS is internally inhibited (or "gated") by RAS to permit triggering of CAS as soon as the Row Address Hold Time (t RAH) specification has been satisfied and the address inputs have been changed from row-addresses to column-address.

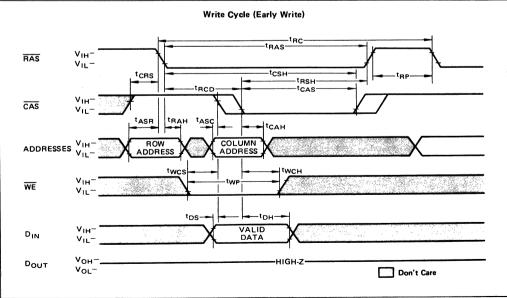

#### Write Enable:

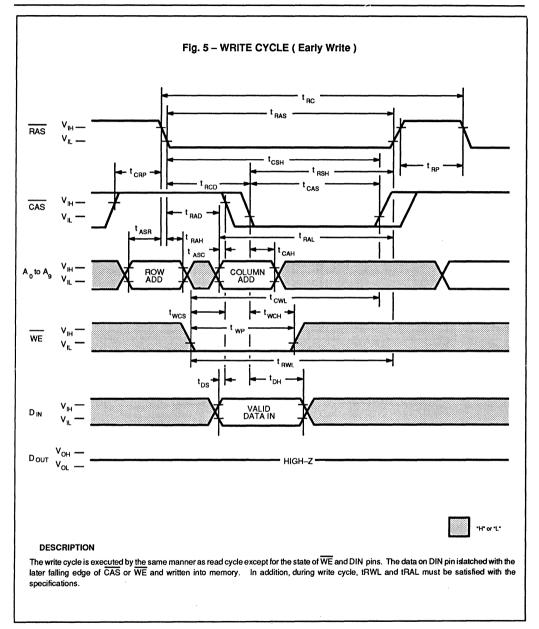

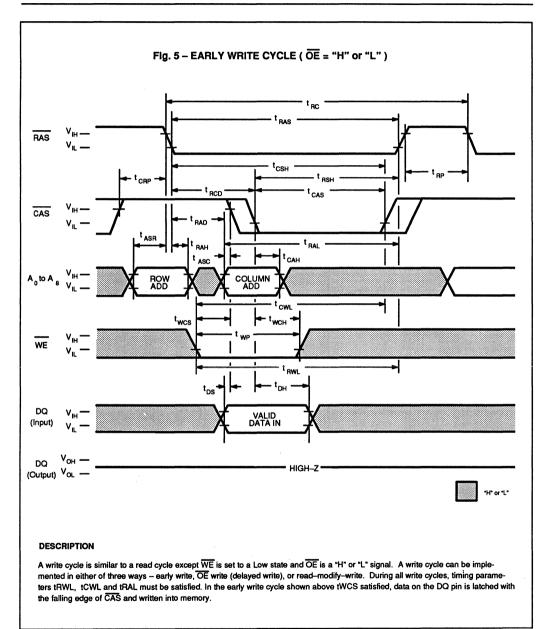

The read mode or write mode is selected with the  $\overline{WE}$  input. A high on  $\overline{WE}$  selects read mode; low selects write mode. The data input is disable when read mode is selected.

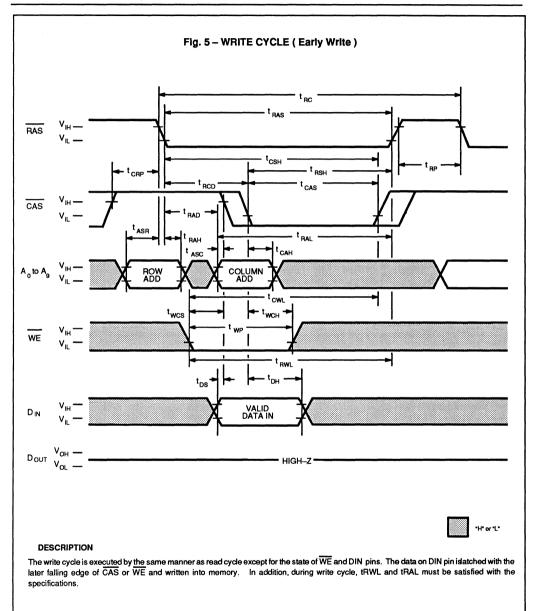

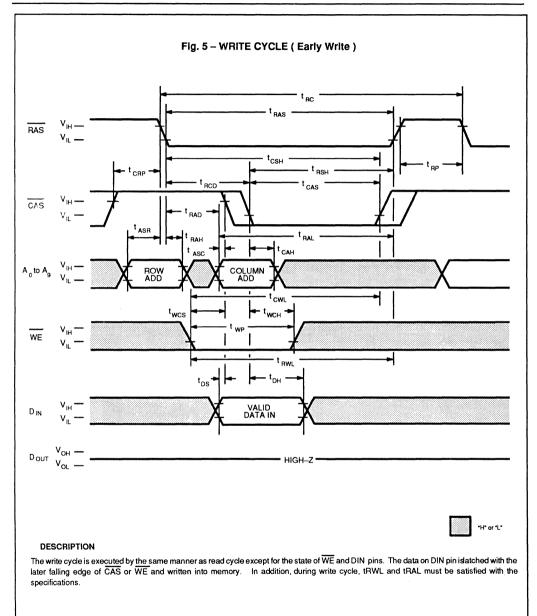

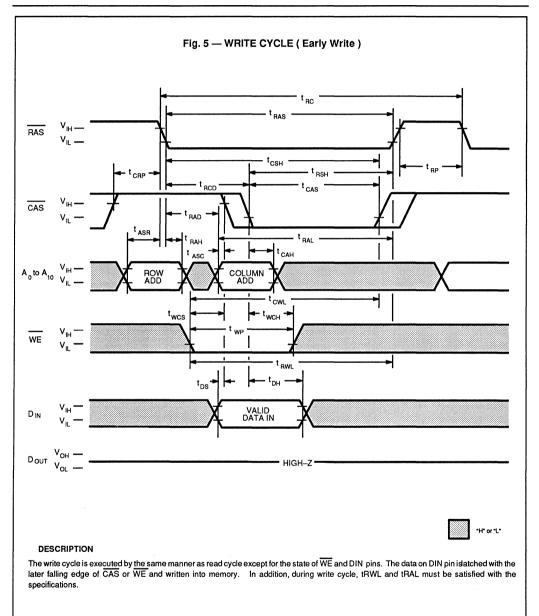

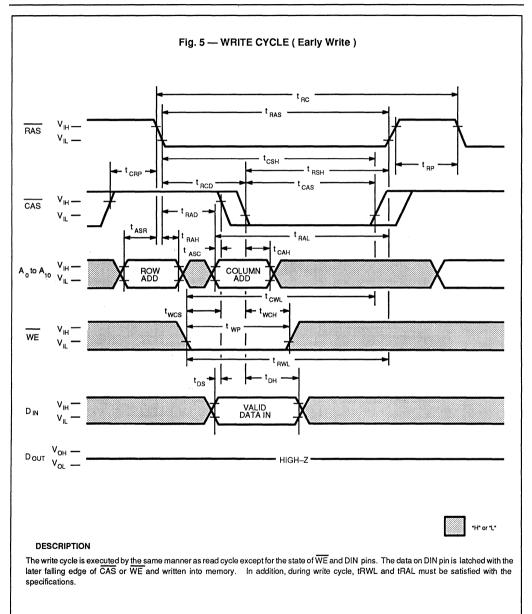

#### Data input:

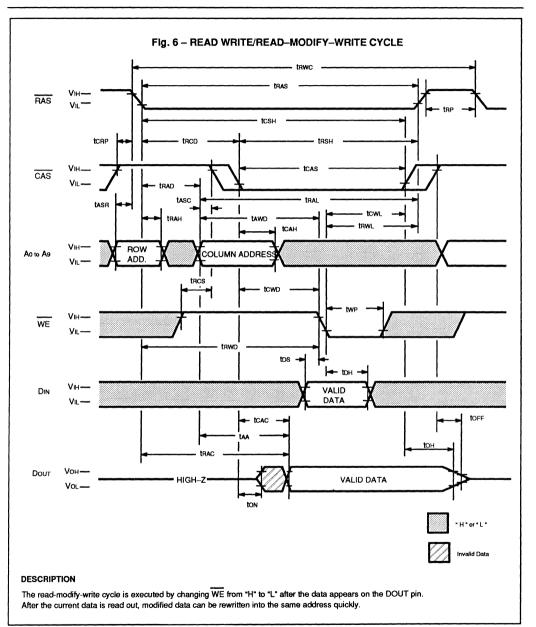

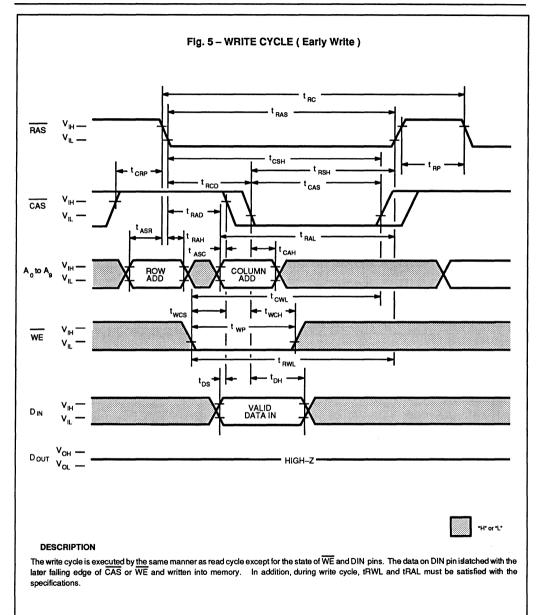

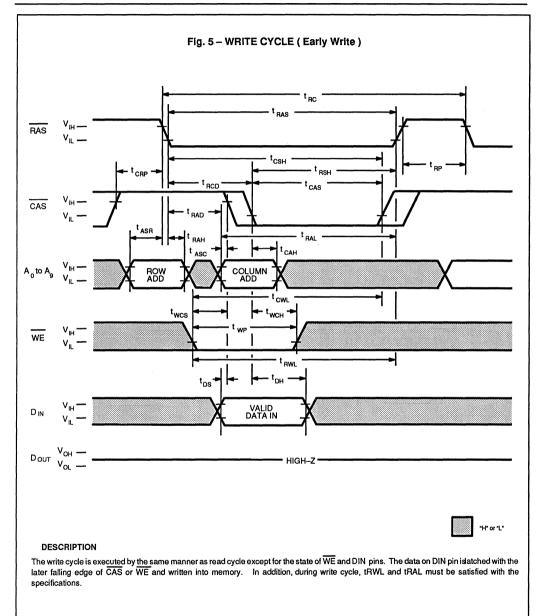

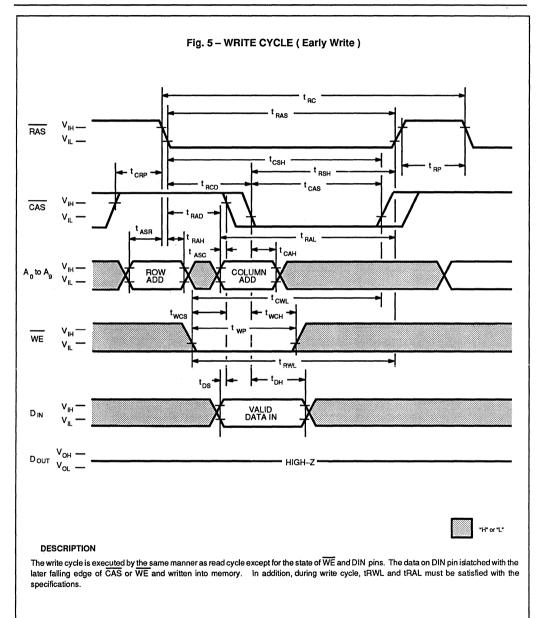

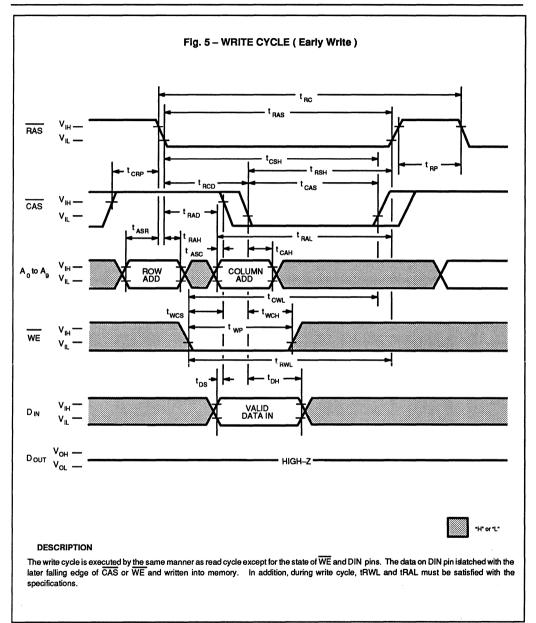

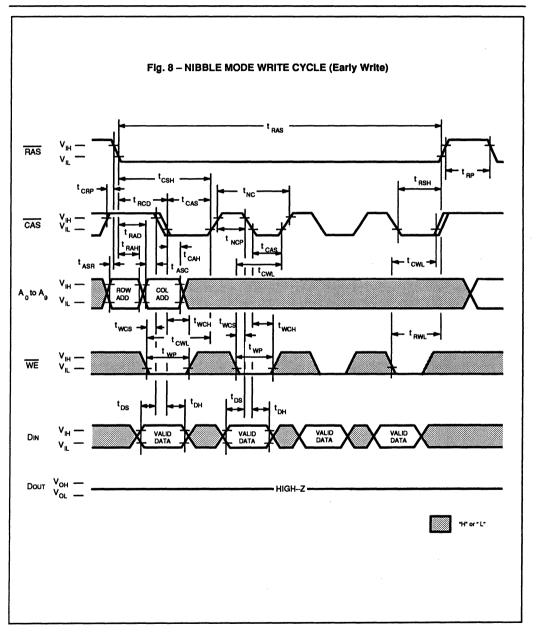

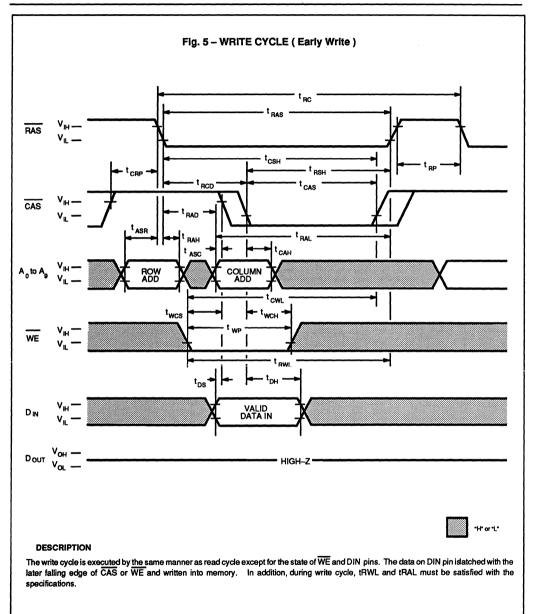

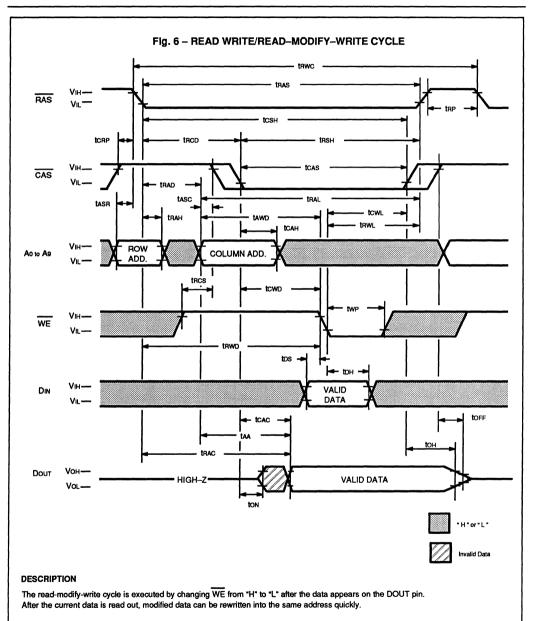

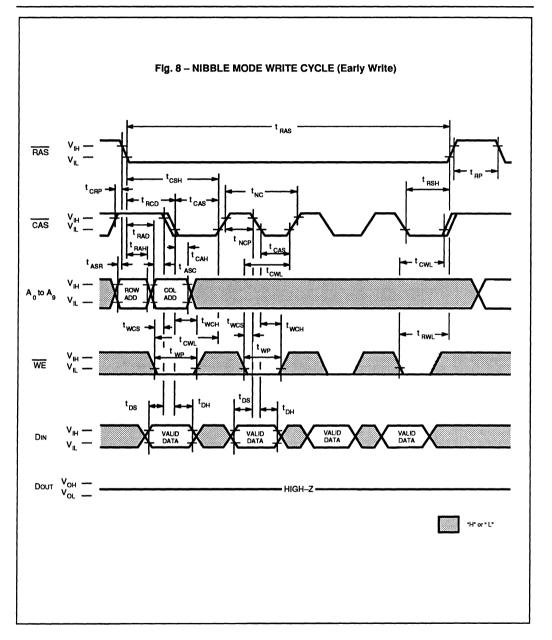

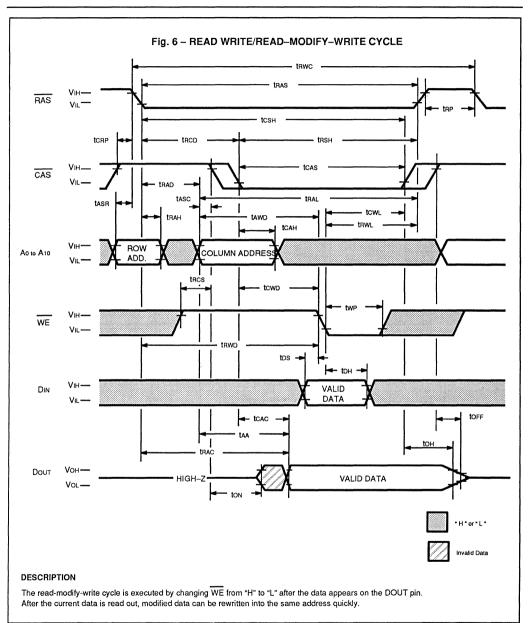

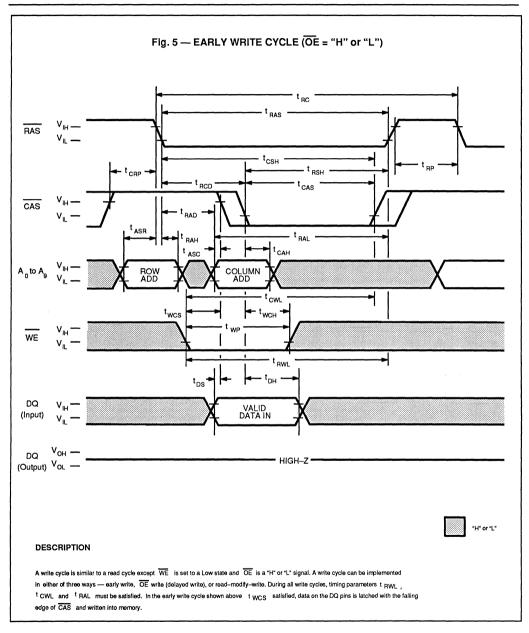

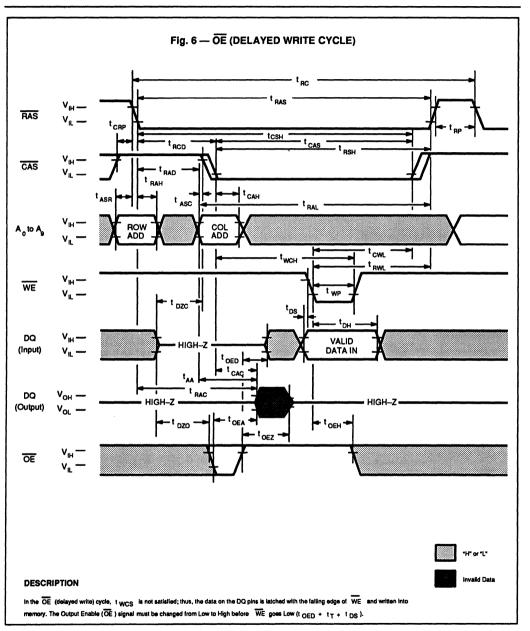

Data is written into the MB 81256 during a write or read-write cycle. The later falling edge of  $\overline{WE}$  or  $\overline{CAS}$  is a strobe for the Data In  $(D_{1N})$  register. In a write cycle, if  $\overline{WE}$  is brought low before

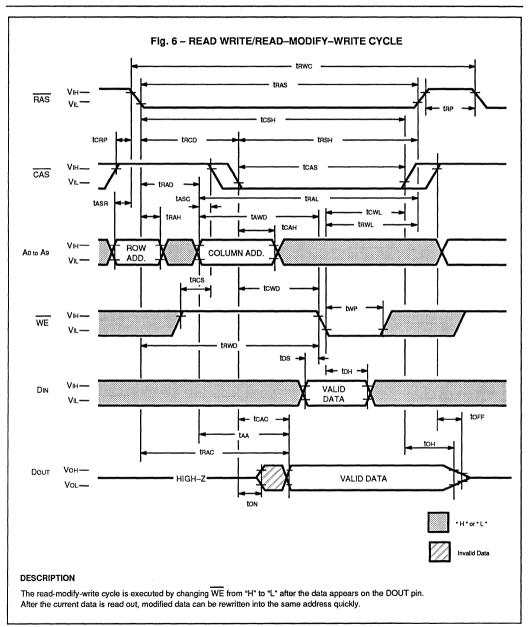

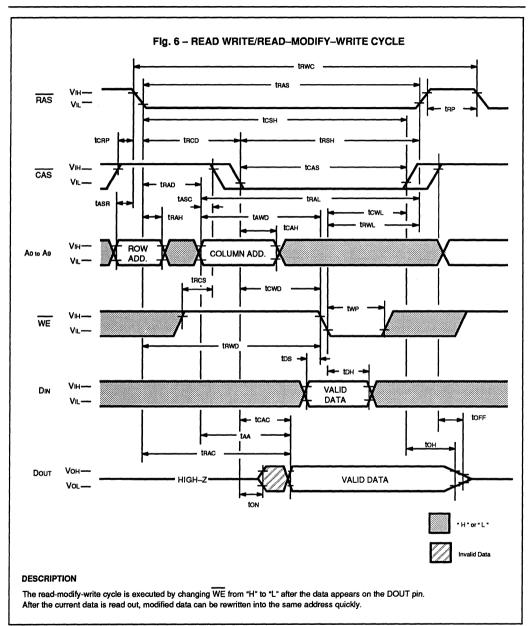

$\overline{CAS}$ ,  $D_{IN}$  is strobed by  $\overline{CAS}$ , and the set-up and hold times are referenced to  $\overline{CAS}$ . In a read-write cycle,  $\overline{WE}$  can be delayed after  $\overline{CAS}$  has been low and  $\overline{CAS}$  to  $\overline{WE}$  Delay Time ( $t_{CWD}$ ) has been satisfied. Thus  $D_{IN}$  is strobed by  $\overline{WE}$ , and set-up and hold times are referenced to  $\overline{WE}$ .

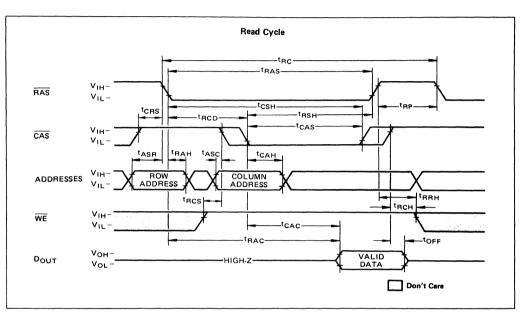

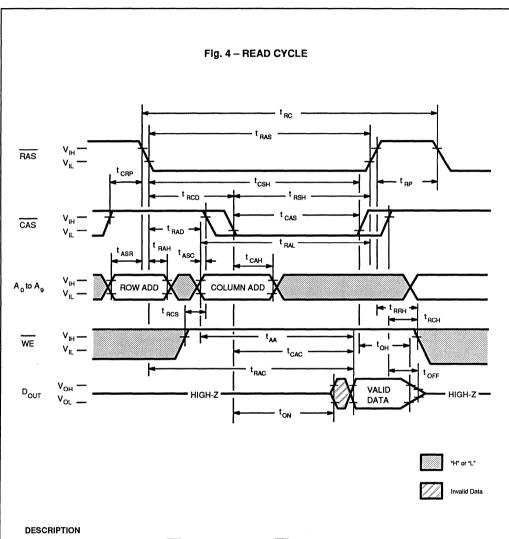

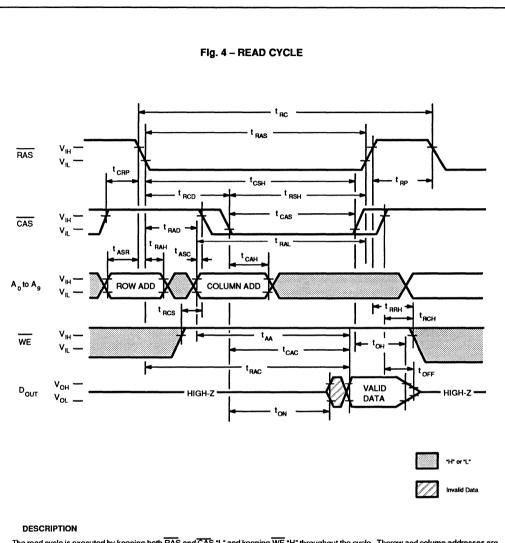

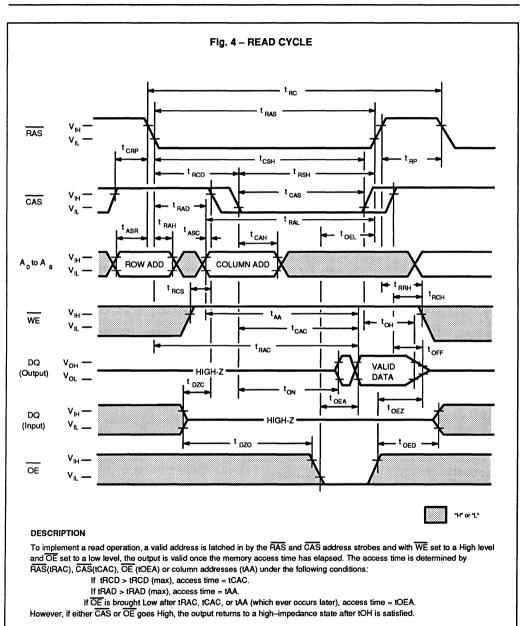

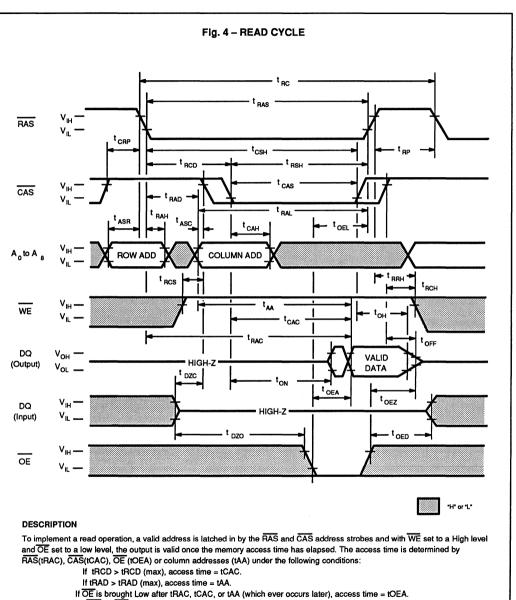

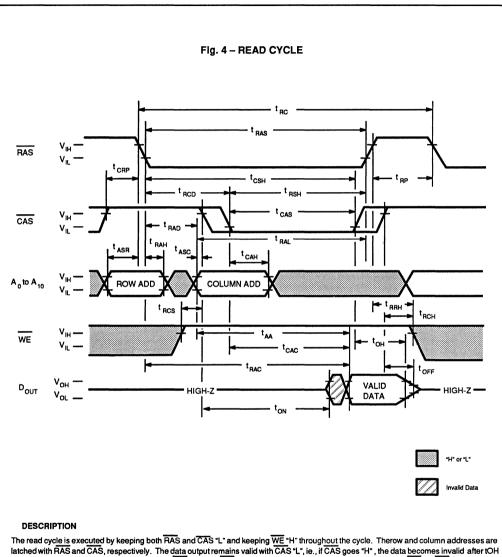

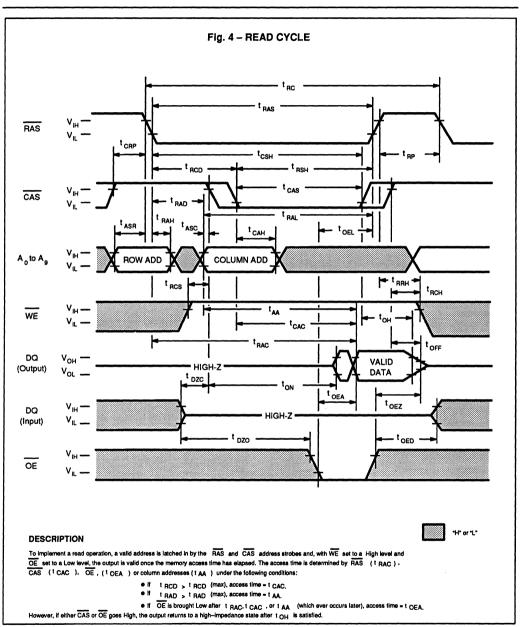

#### Data Output:

The output buffer is three-state TTL compatible with a fan-out of two standard TTL loads. Data out is the same polarity as data-in. The output is in a high impedance state until CAS is brought low. In a read cycle, or read-write cycle, the output is valid after  $t_{RAC}$  from transition of RAS when the transition occurs after  $t_{RCD}$  (max) is satisfied, or after  $t_{CAC}$  from transition of CAS when the transition occurs after  $t_{RCD}$  (max). Data remain valid until CAS is returned to a high level. In a write cycle the identical sequence occurs, but data is not valid.

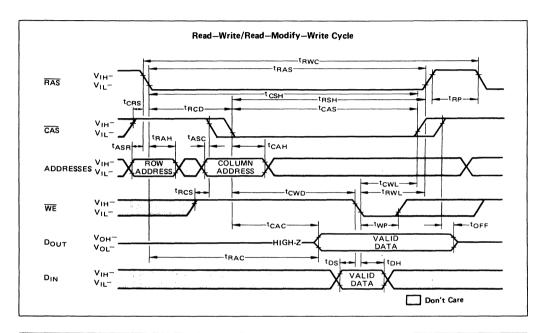

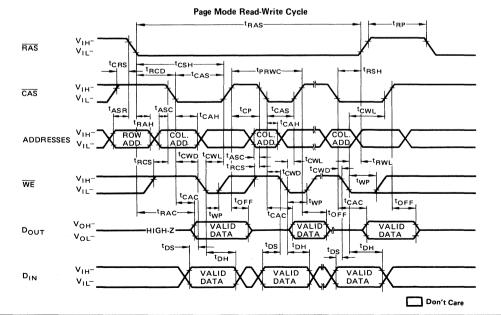

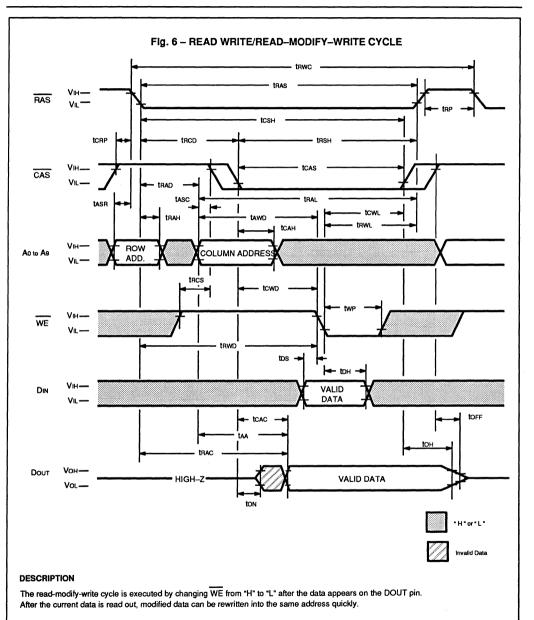

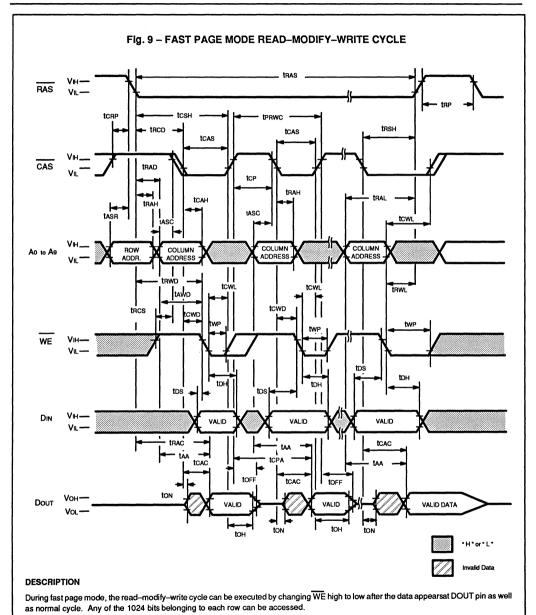

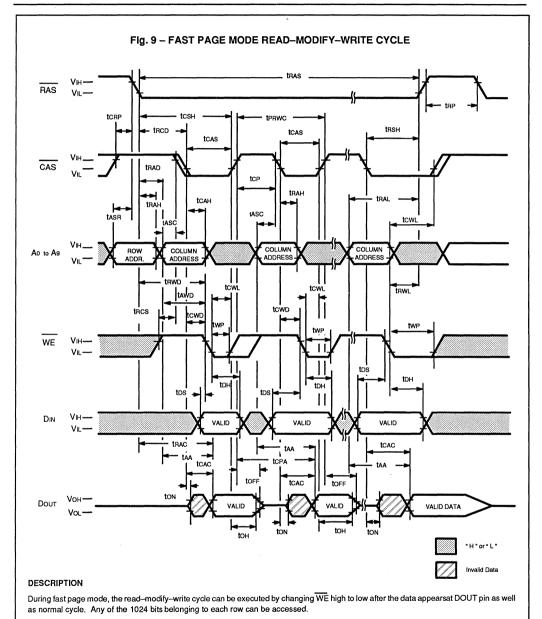

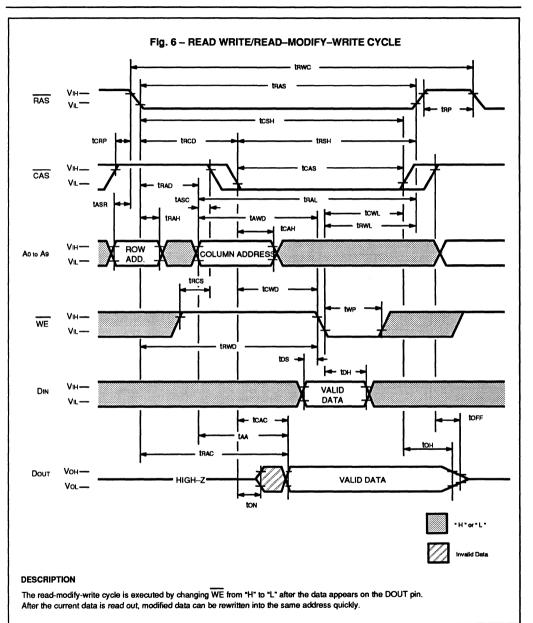

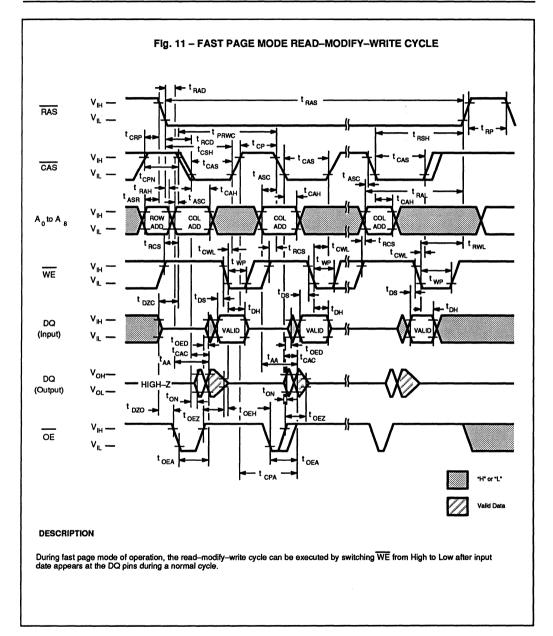

#### Fast Read-While-Write cycle

The MB 81256 has a fast read while write cycle which is achieved by precise control of the three-state output buffer as well as by the simplified timings described in the previous section. The output buffer is controlled by the state of WE when CAS goes low. When WE is low during CAS transition to low, the MB 81256 goes into the early write mode in which the output floats and the common I/O bus can be used on the system level. Whereas, when WE goes low after  $t_{CWD}$  following  $\overline{CAS}$  transition to low, the MB 81256 goes into the delayed write mode. The output then contains the data from the cell selected and the data from D<sub>IN</sub> is written into the cell selected. Therefore, a very fast read write cycle  $(t_{RWC} = t_{RC})$  is possible with the MB 81256.

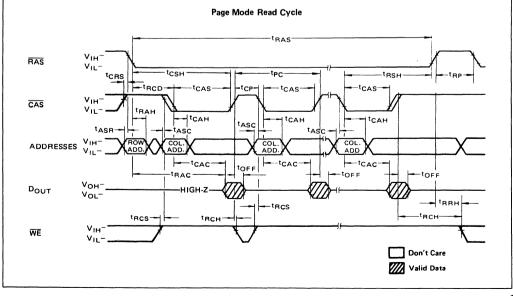

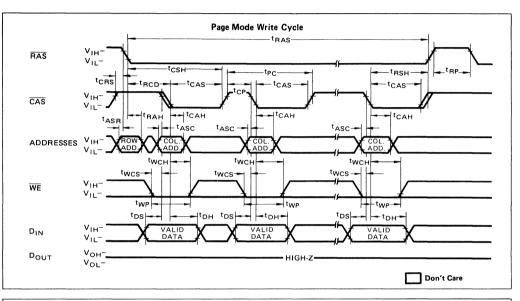

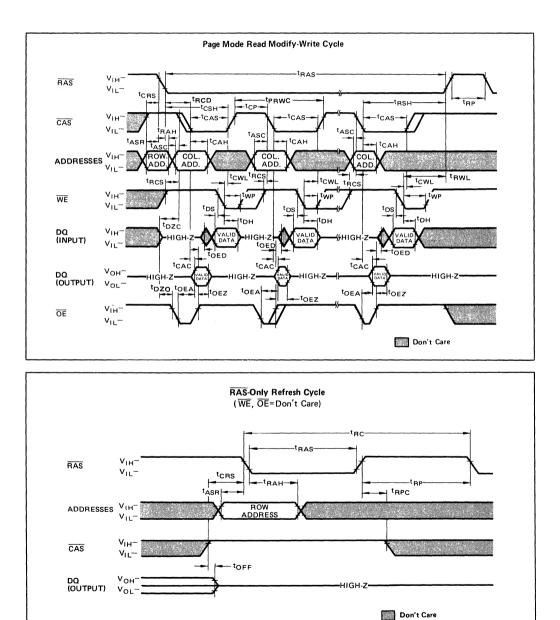

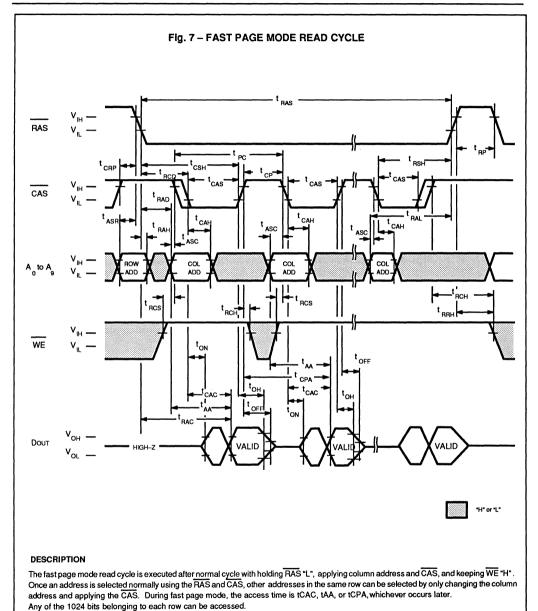

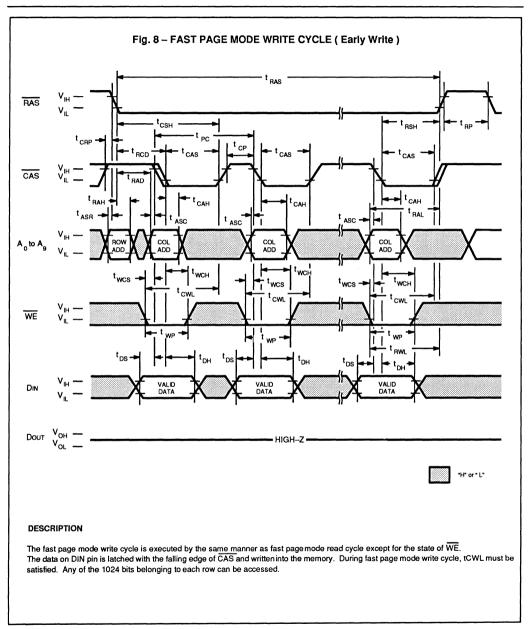

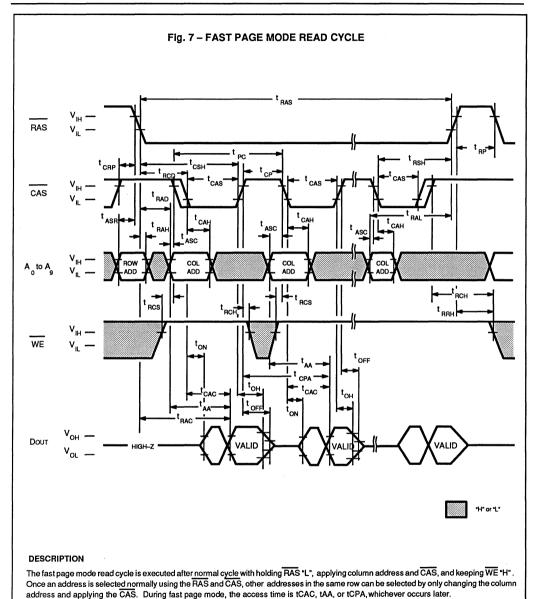

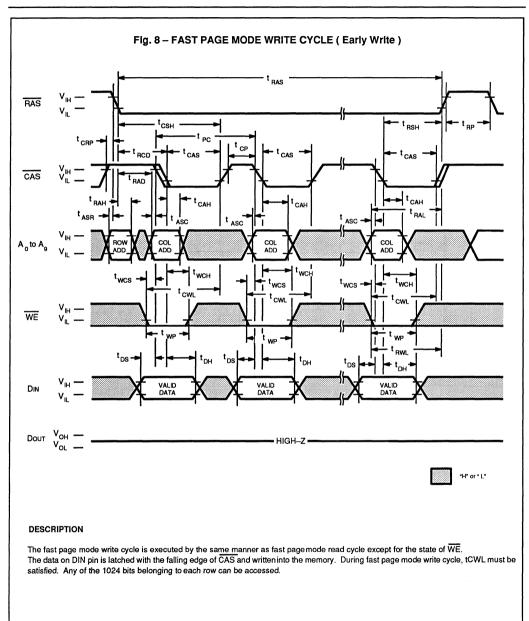

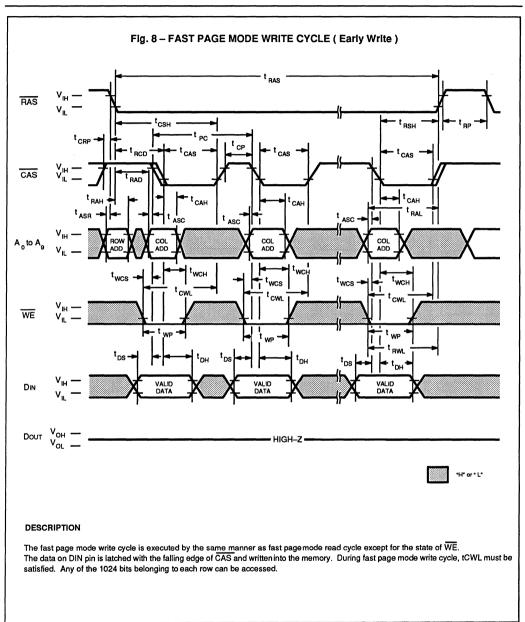

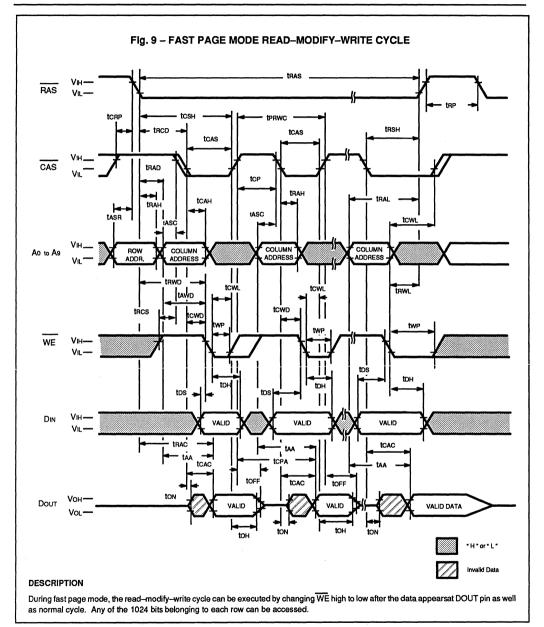

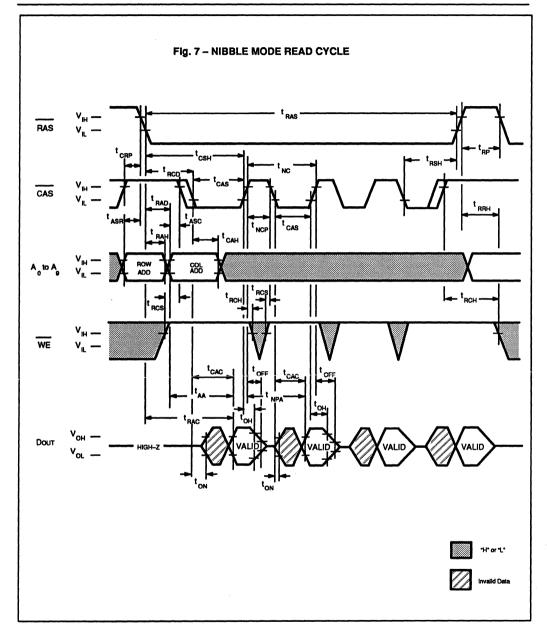

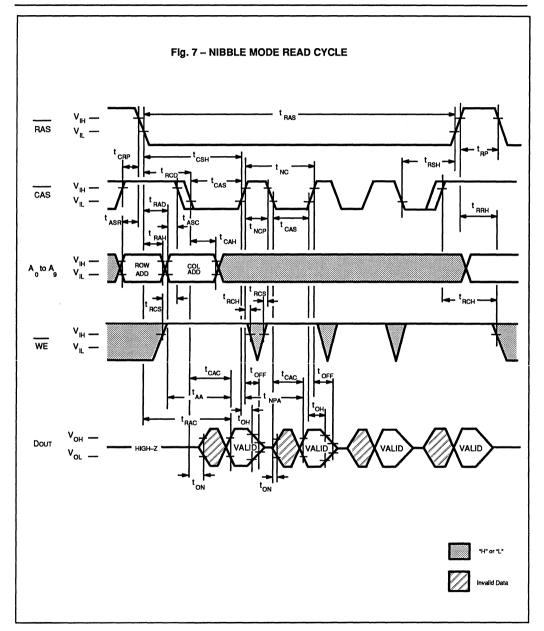

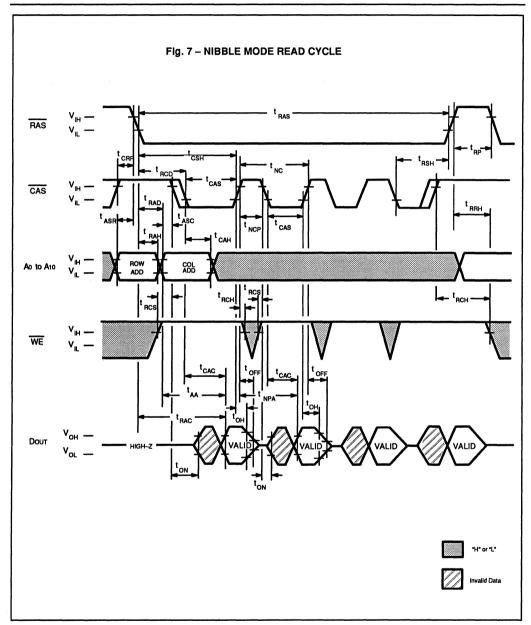

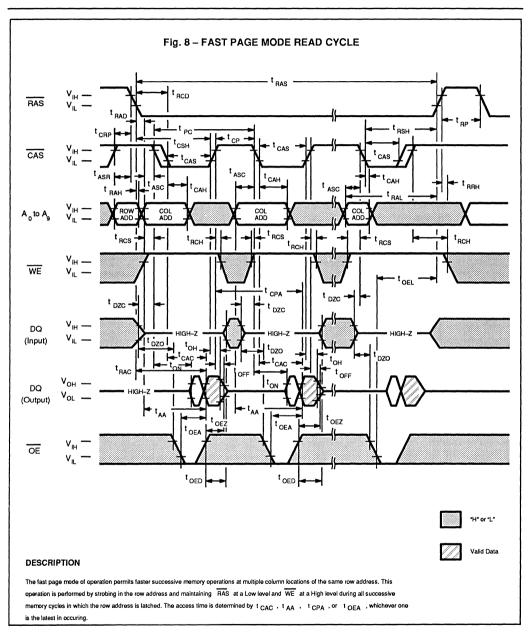

#### Page Mode:

Page-mode operation permits strobing the row-address into the MB 81256 while maintaining RAS at a low throughout all successive memory operations in which the row-address doesn't change. Thus the power dissipated by the falling edge of RAS is saved. Access and cycle times are decreased because the time normally required to strobe a new row address is eliminated.

#### Refresh:

Refresh of the dynamic memory cells is accomplished by performing a memory cycle at each of the 256 row-addresses ( $A_0$  to  $A_7$ ) at least every 4ms. The MB 81256 offers the following 3 types of refresh.

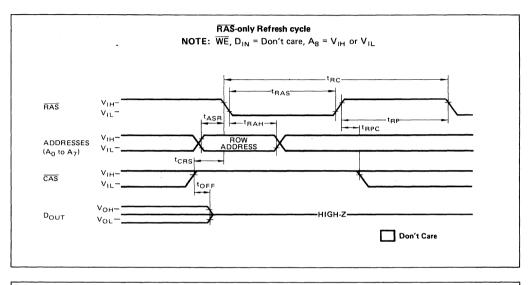

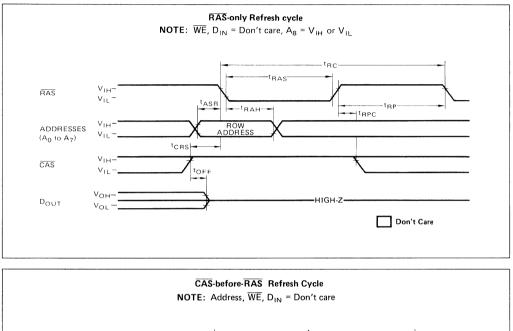

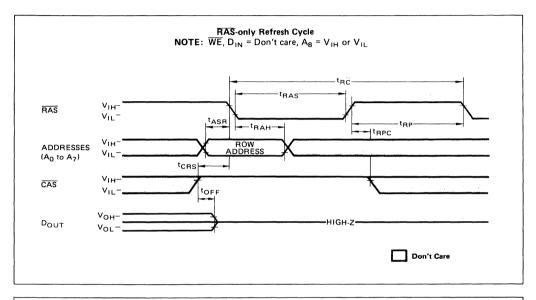

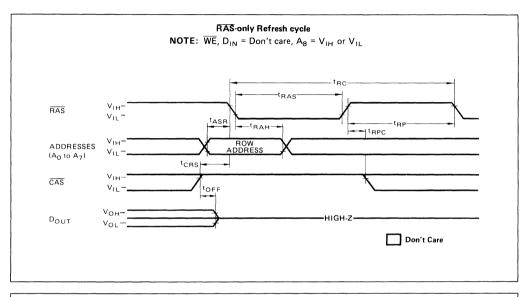

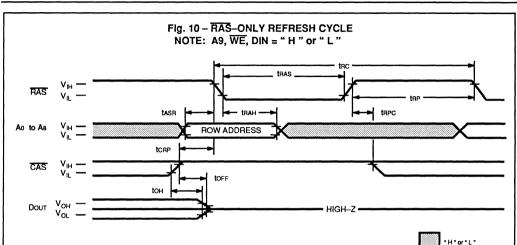

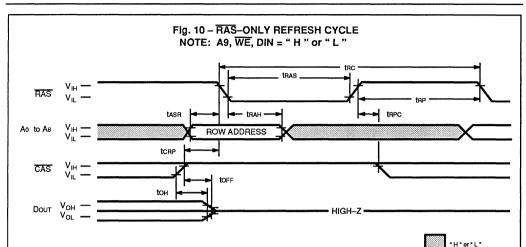

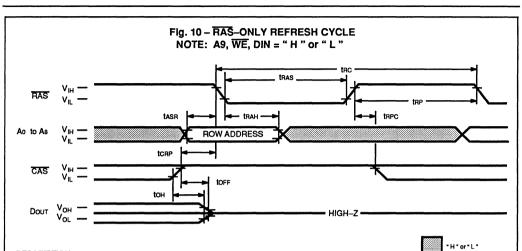

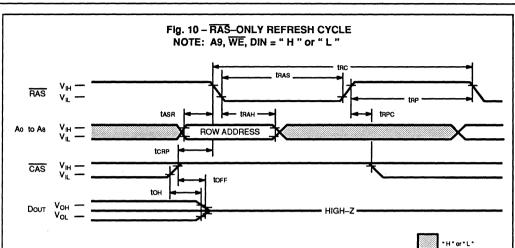

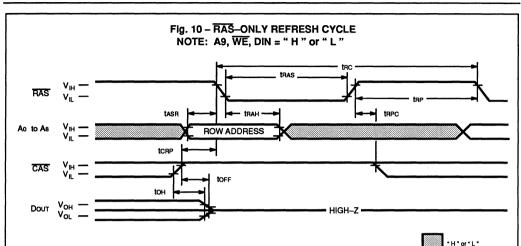

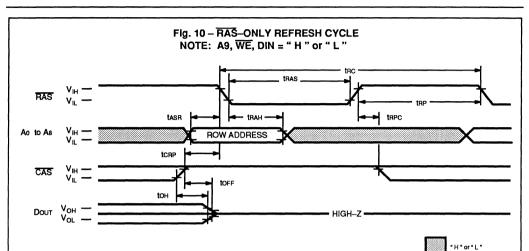

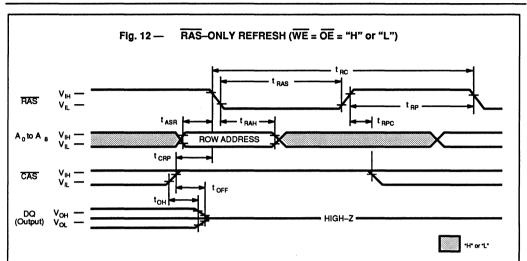

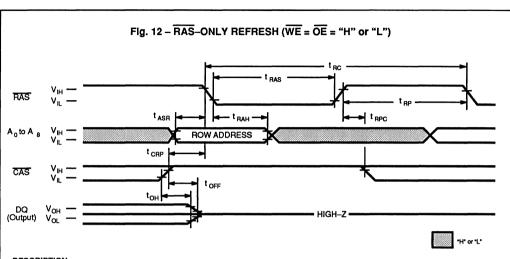

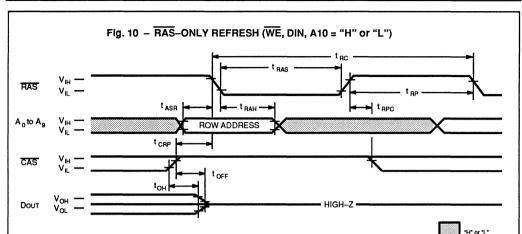

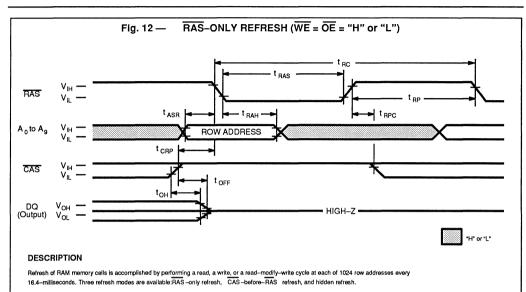

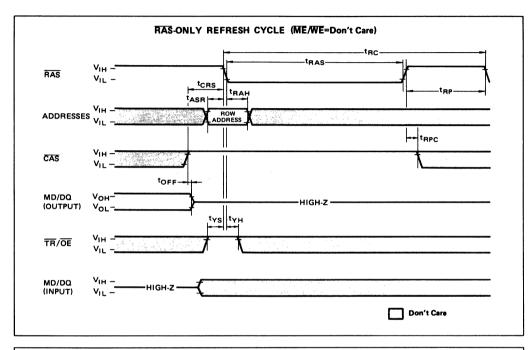

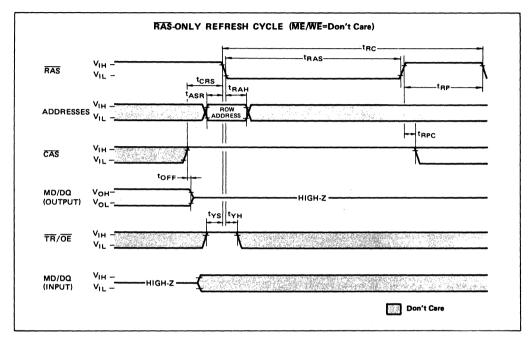

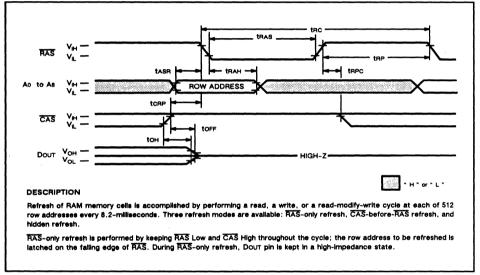

#### RAS-only Refresh;

$\overline{RAS}$ -only refresh avoids any output during refresh because the output buffer is in the high impedance state unless  $\overline{CAS}$  is brought low.

Strobing each of 256 row-addresses  $(A_0 \text{ to } A_7)$  with  $\overline{RAS}$  will cause all bits in each row to be refreshed. Further  $\overline{RAS}$ -only refresh results in a substantial reduction in power dissipation. During  $\overline{RAS}$ -only refresh cycle, either  $V_{1H}$  or  $V_{1L}$  is permitted to  $A_8$ .

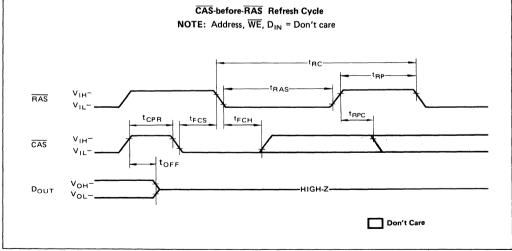

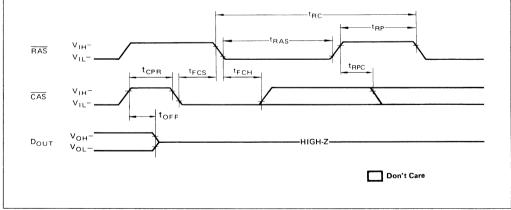

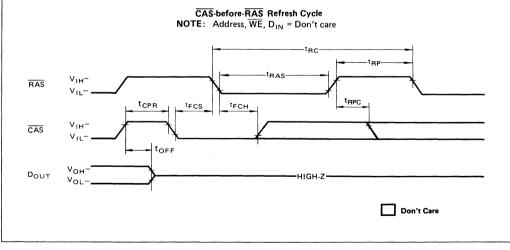

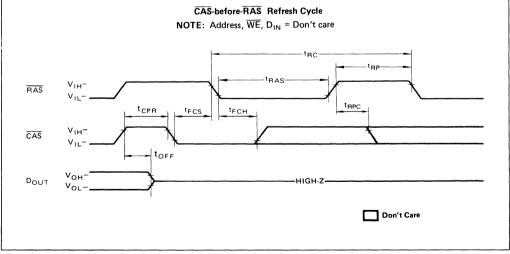

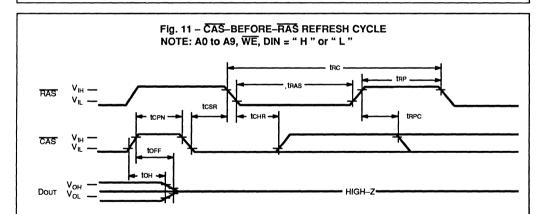

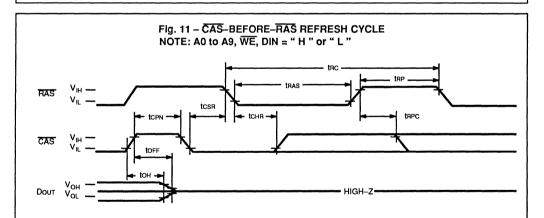

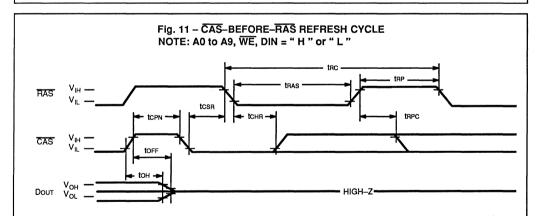

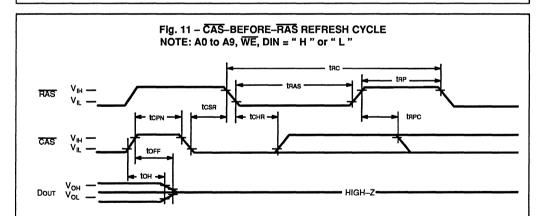

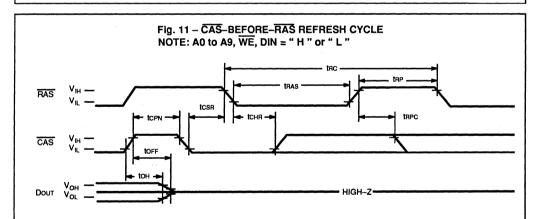

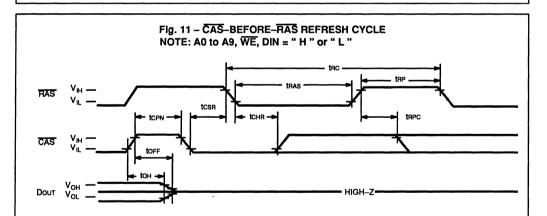

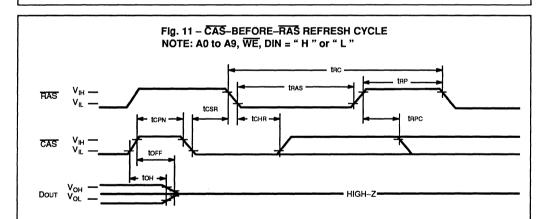

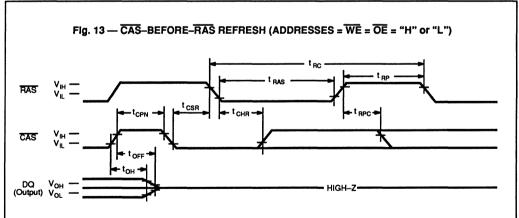

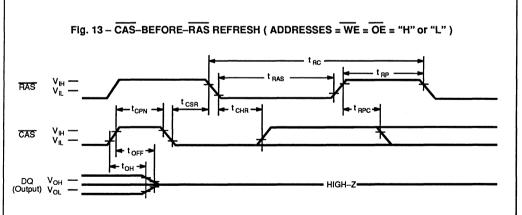

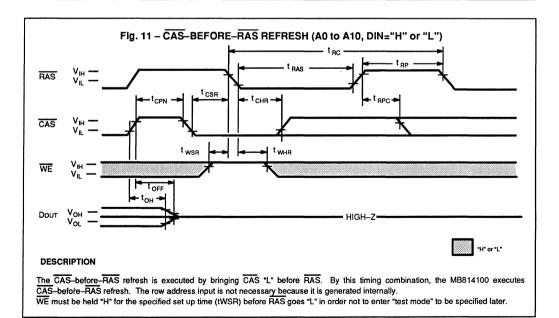

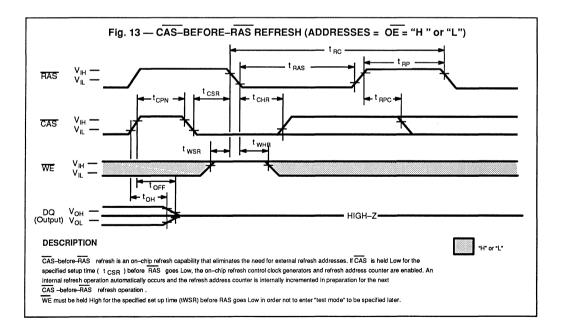

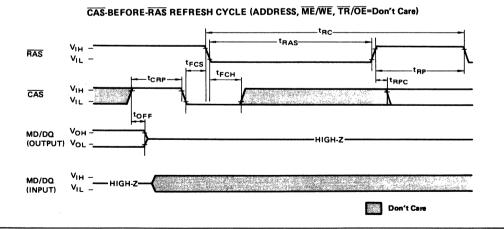

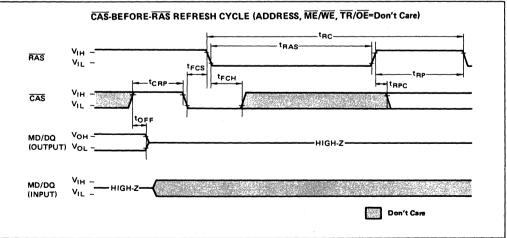

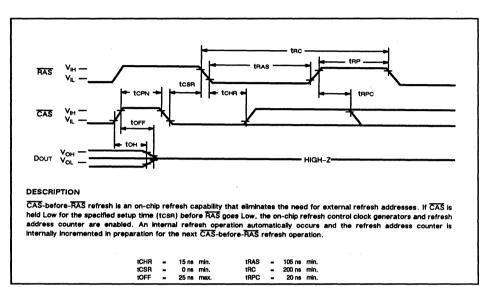

#### CAS-before-RAS Refresh;

$\overline{CAS}$ -before- $\overline{RAS}$  refreshing available on the MB 81256 offers an alternate refresh method. If  $\overline{CAS}$  is held "low" for the specified period ( $t_{FCS}$ ) before  $\overline{RAS}$  goes to "low", on-chip refresh control clock generators and the refresh address counter are enabled, and an internal refresh operation takes place. After the refresh operation is performed, the refresh address counter is automatically incremented in preparation for the next  $\overline{CAS}$ -before- $\overline{RAS}$ refresh operation.

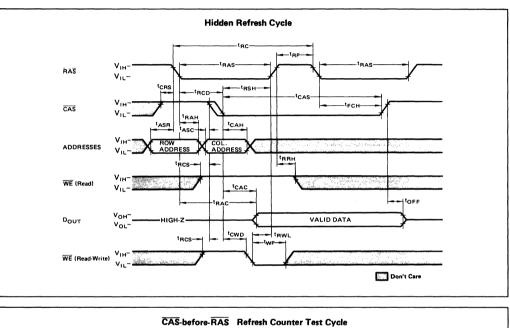

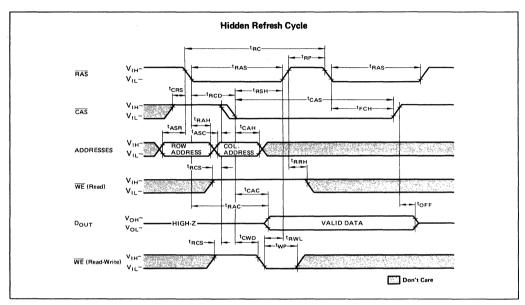

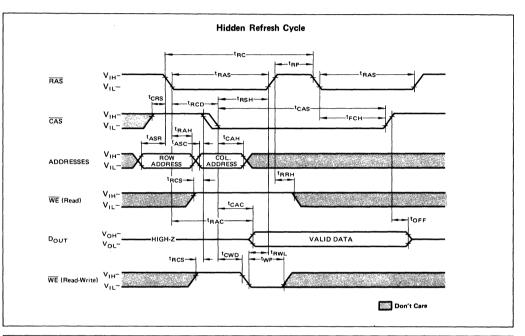

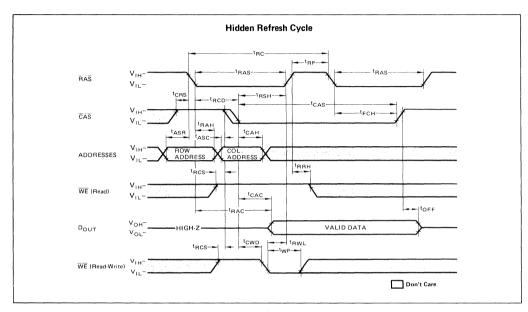

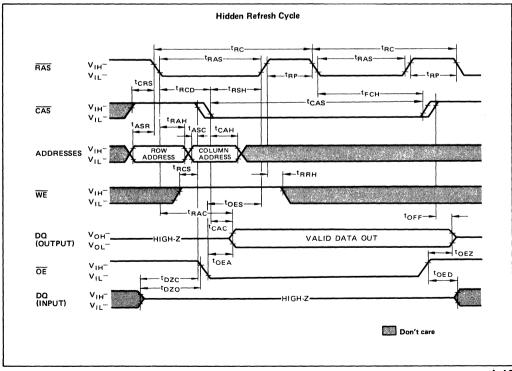

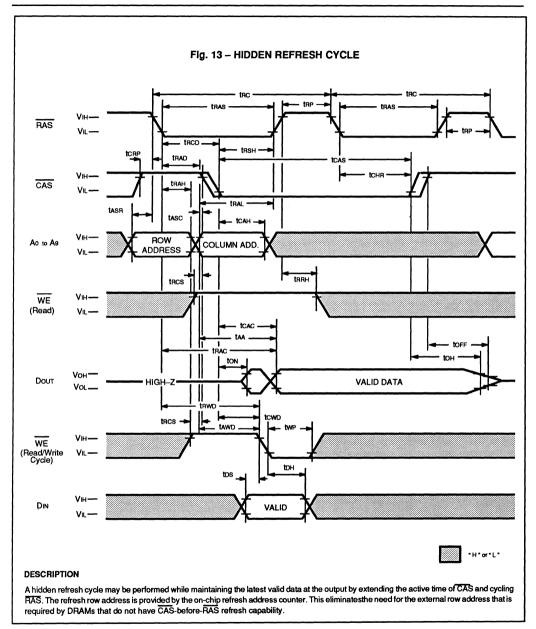

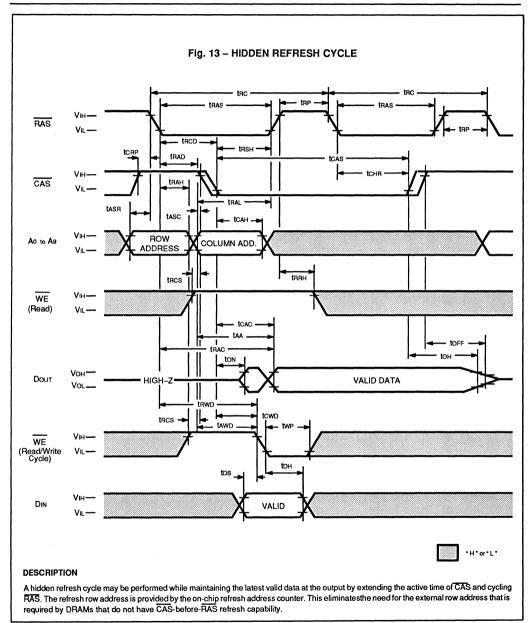

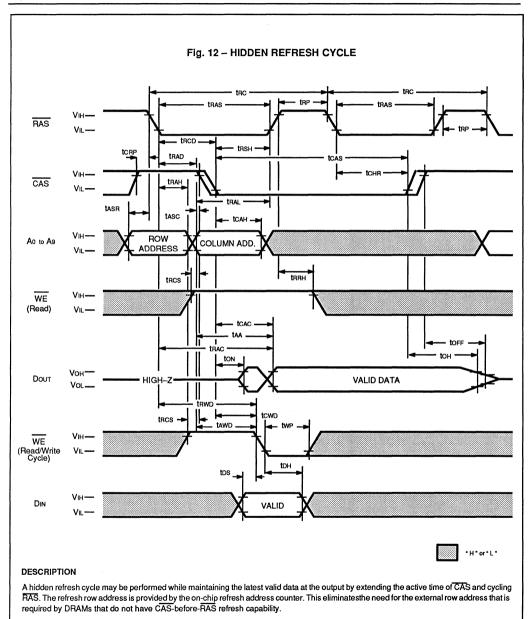

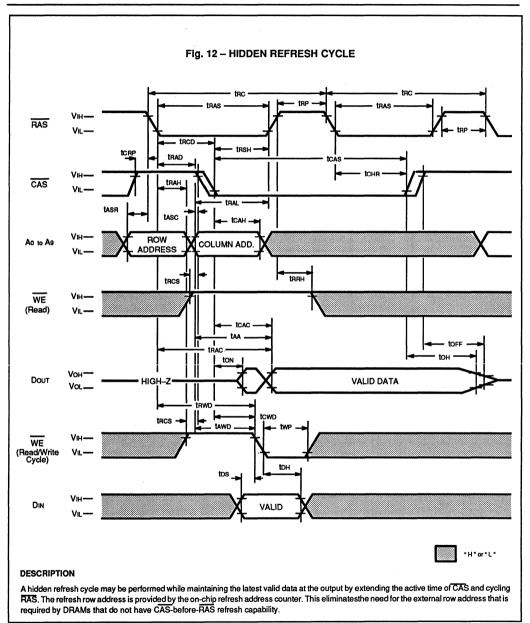

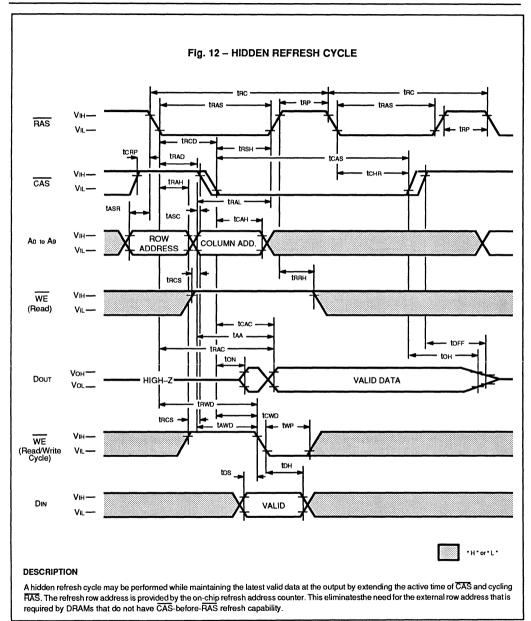

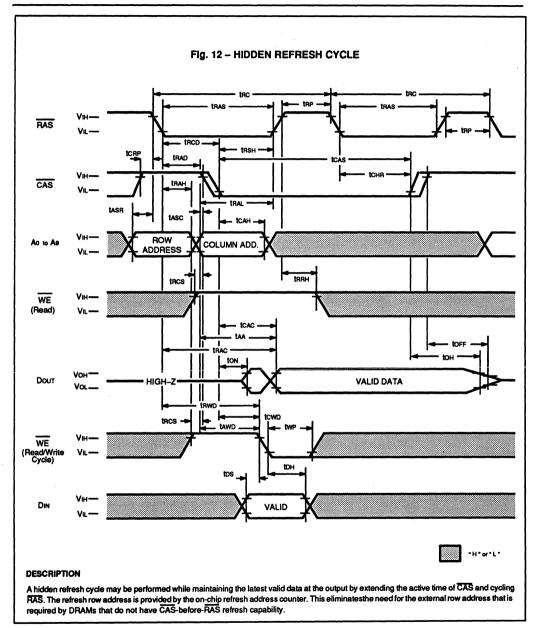

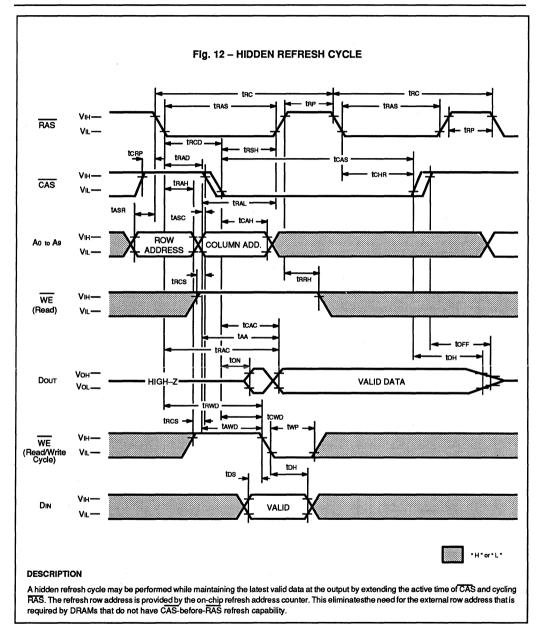

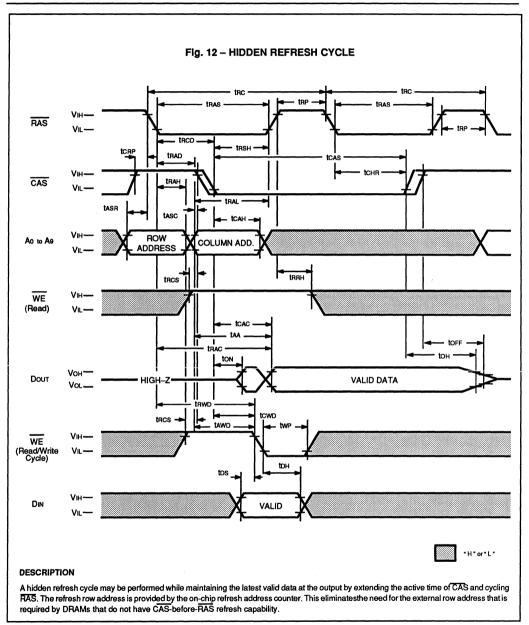

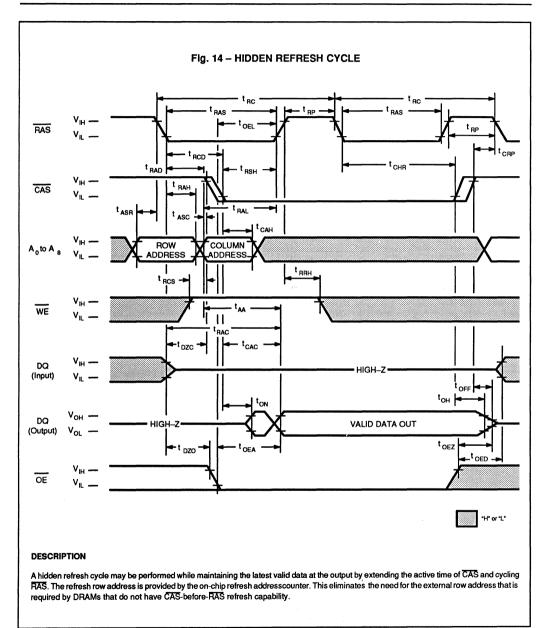

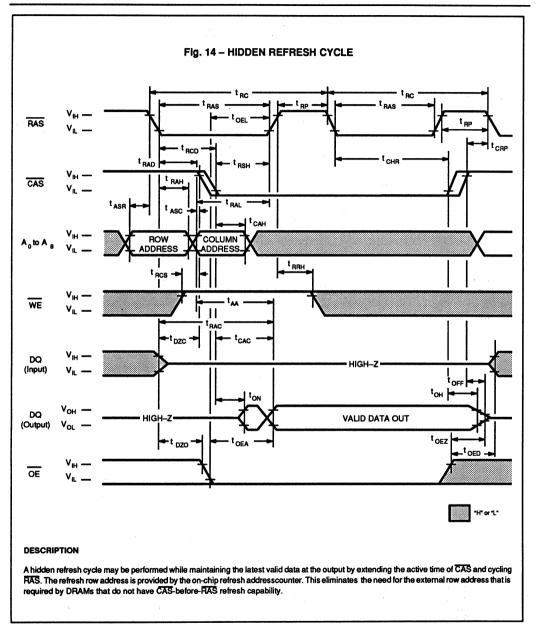

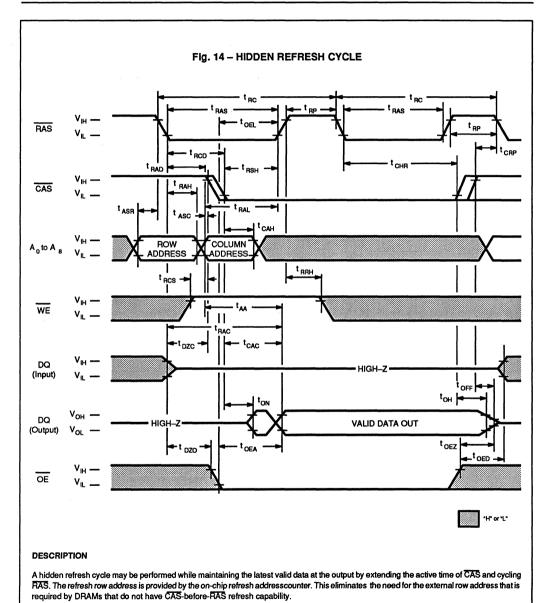

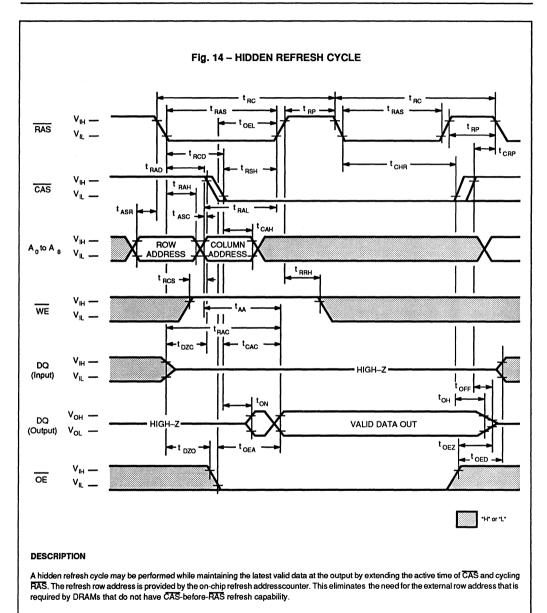

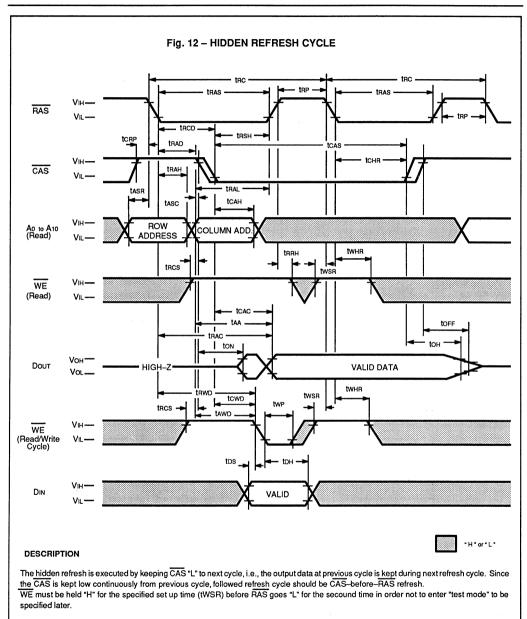

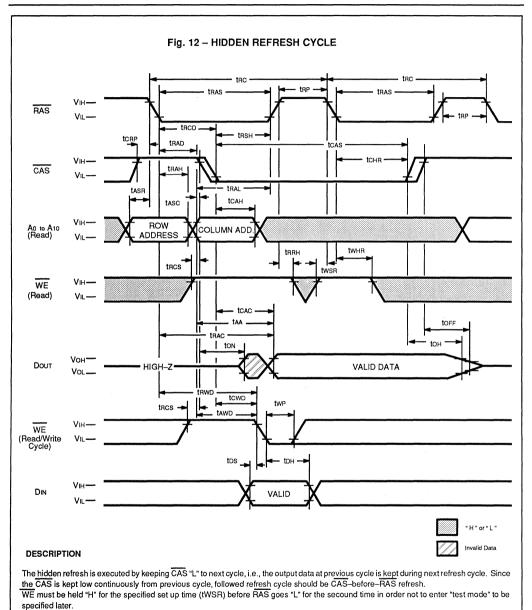

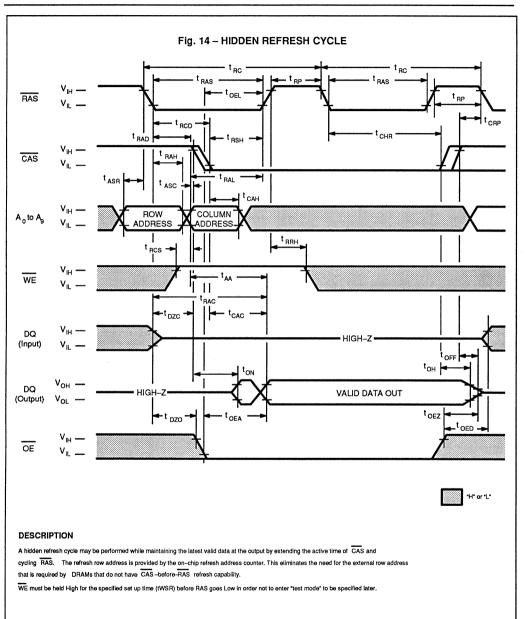

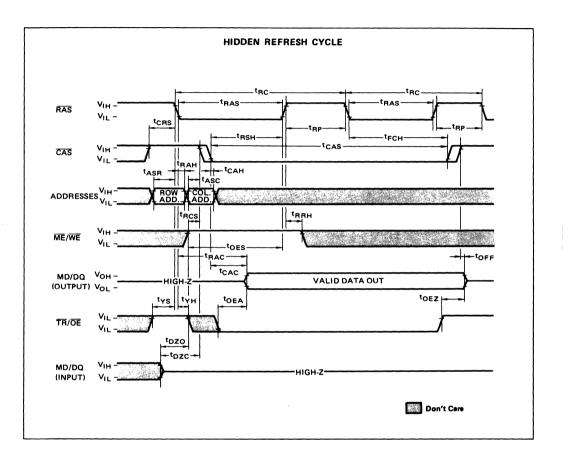

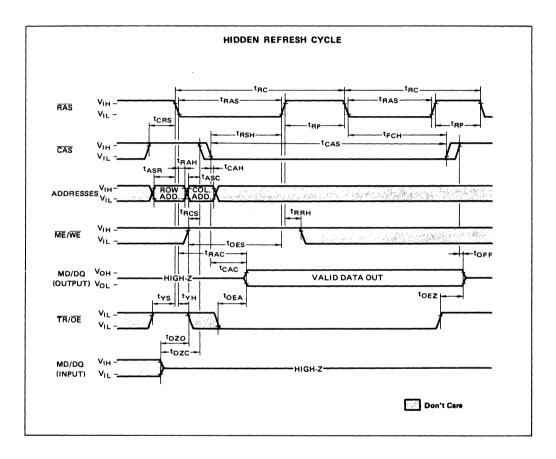

#### Hidden Refresh;

A hidden refresh cycle may takes place while maintaining the latest valid data at the output by extending  $\overline{CAS}$  active time.

For the MB 81256 a hidden refresh is a CAS-before-RAS refresh cycle. The internal refresh address counters provide the refresh addresses, as in a normal CAS-before-RAS refresh cycle.

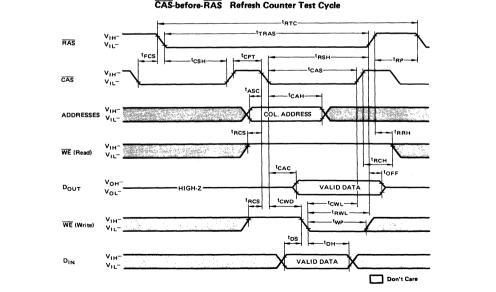

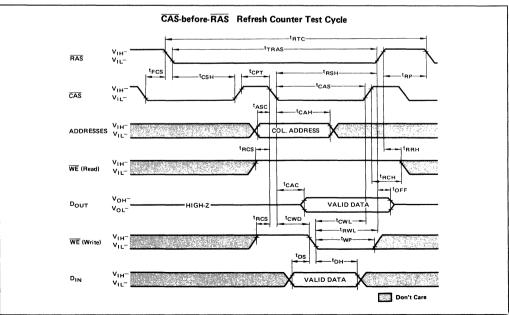

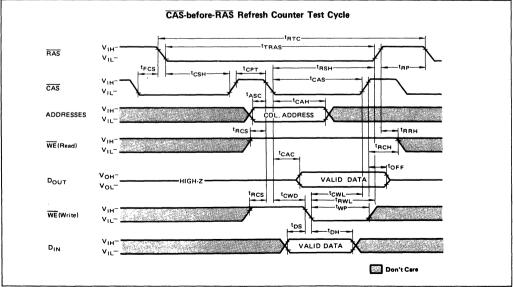

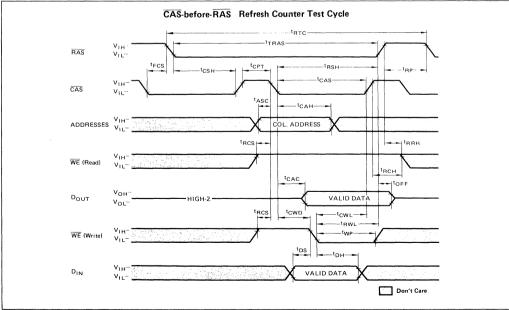

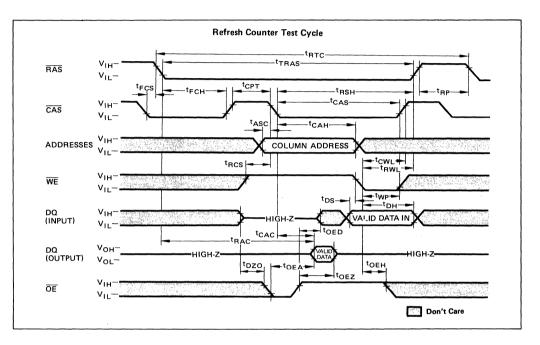

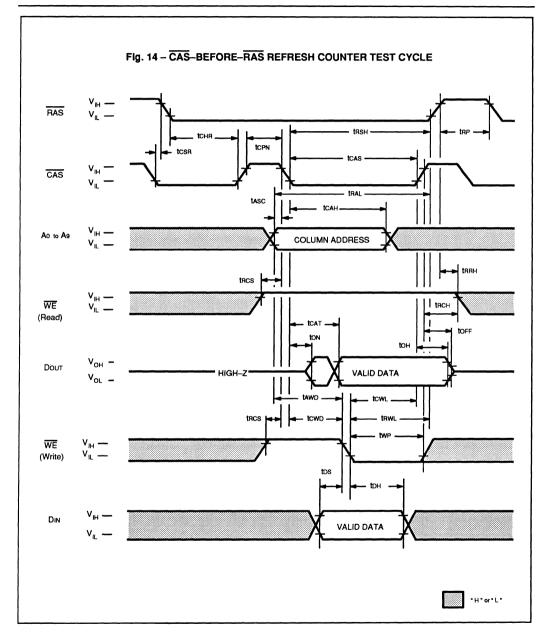

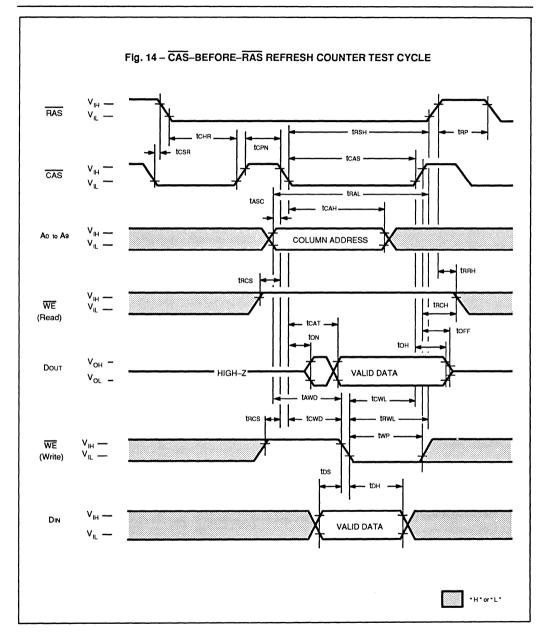

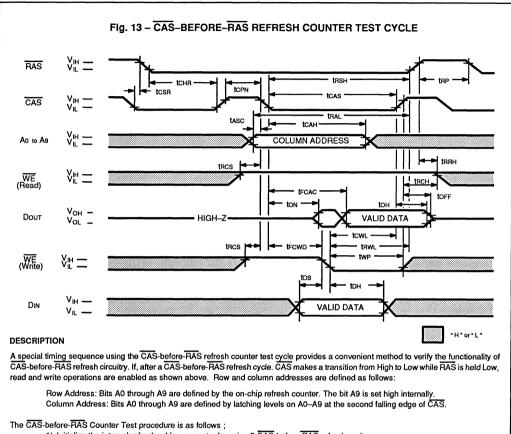

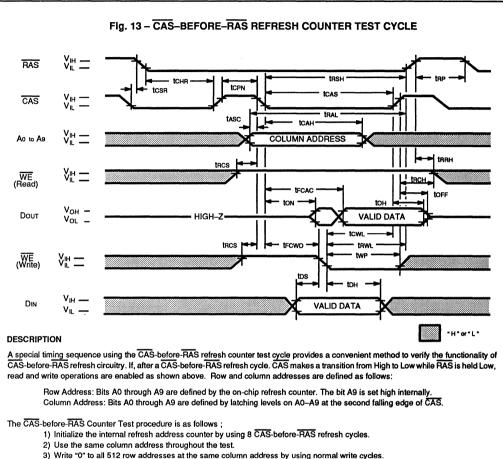

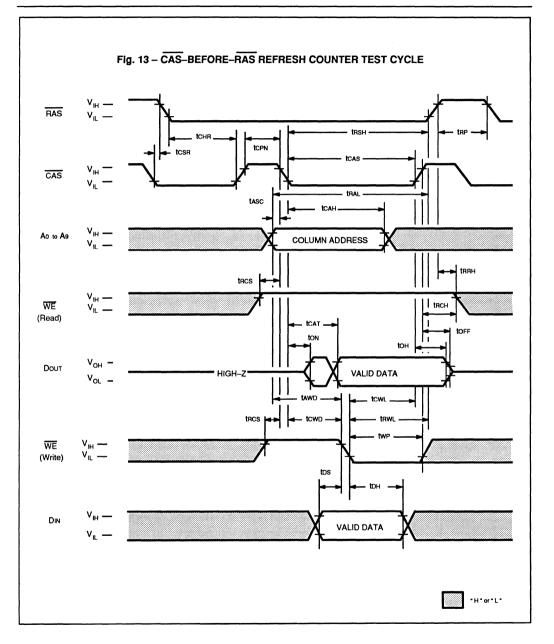

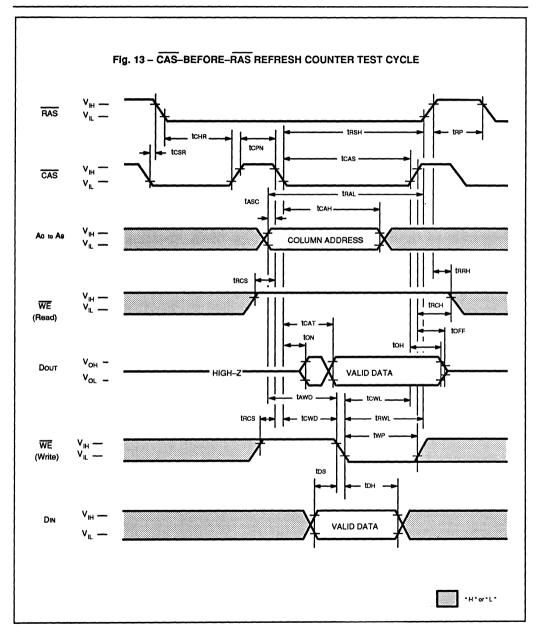

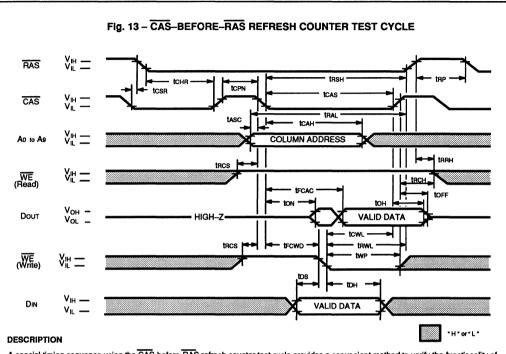

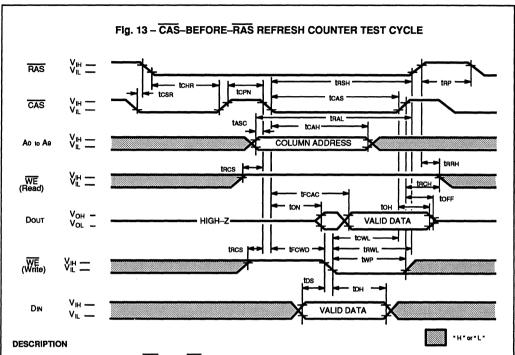

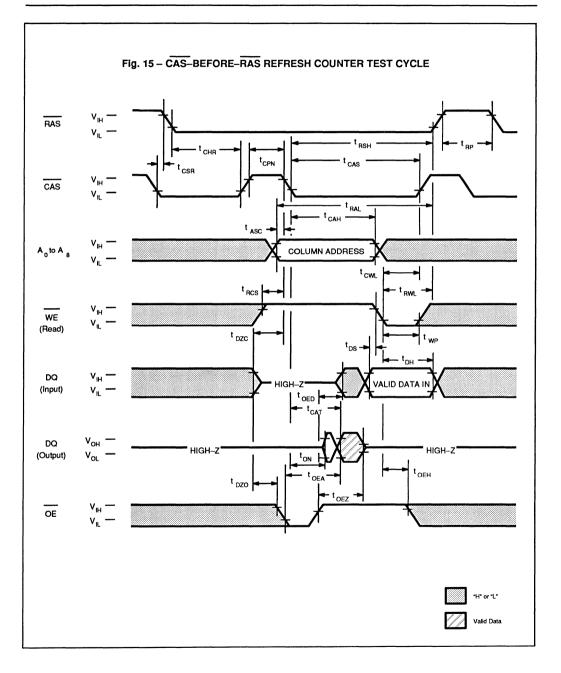

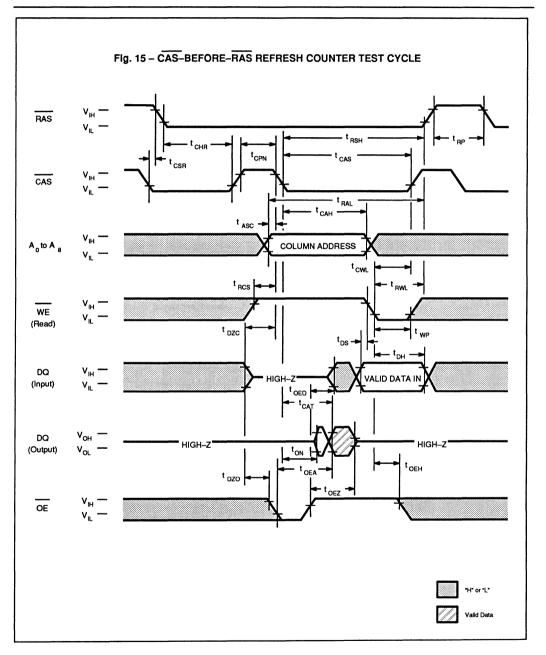

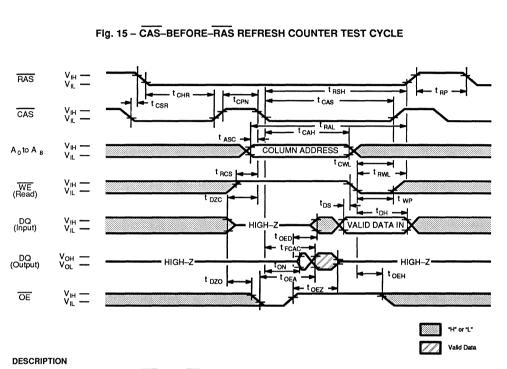

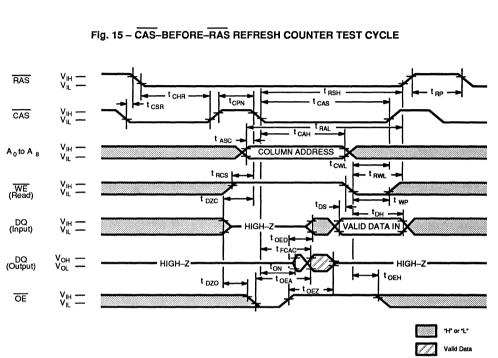

## CAS-before-RAS Refresh Counter Test Cycle:

A special timing sequence using CAS-

before-RAS counter test cycle provides a convenient method of verifying the functionality of the CAS-before-RAS refresh activated circuitry.

After the  $\overline{CAS}$ -befor- $\overline{RAS}$  refresh operation, if  $\overline{CAS}$  goes to high and then goes to low again while  $\overline{RAS}$  is held low, the read and write operations are enabled.

This is shown in the CAS-before-RAS counter test cycle timing diagram. A memory cell address (consisting of a row address (9 bits) and column address (9 bits) to be accessed can be defined as follows:

\*A ROW ADDRESS - Bits Ao to A7

are defined by the refresh counter. The bit  $A_8$  is set high internally.

\*A COLUMN ADDRESS – All the bits  $A_0$  to  $A_8$  are defined by latching levels on  $A_0$  to  $A_8$  at the second falling edge of CAS.

#### Suggested CAS-before-RAS Counter Test Procedure

The timing as shown in the CAS-before-RAS Counter Test cycles is used for the following operations:

- (1) Initialize the internal refresh address counter by using eight CASbefore-RAS refresh cycles.

- (2) Throughout the test, use the same

column address, and keep RA8 high.

- (3) Write "low" to all 256 row address on the same column address by using normal early write cycles.

- (4) Read "low" written in step 3) and check, and simultaneously write "high" to the same address by using internal refresh counter test readwrite cycles. This step is repeated 256 times, with the addresses being generated by internal refresh address counter.

- (5) Read "high" written in step 4) and check by using normal read cycle for all 256 locations.

- (6) Complement the test pattern and repeat step 3), 4) and 5).

80 100

6.0

6.0

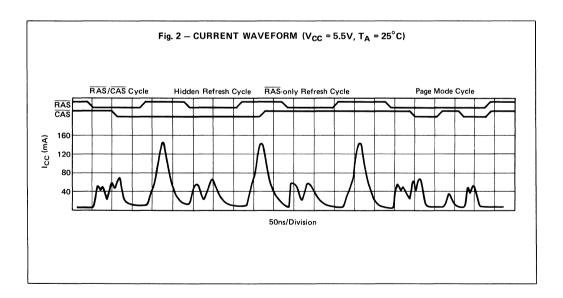

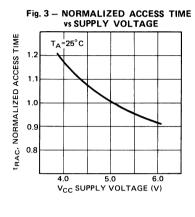

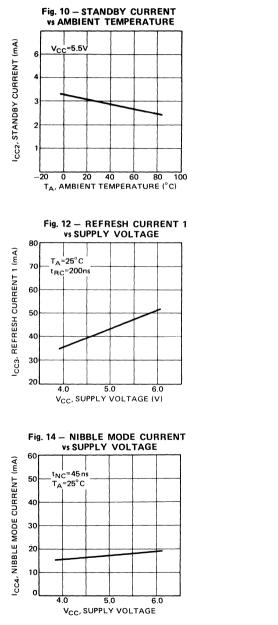

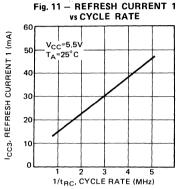

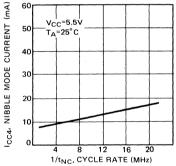

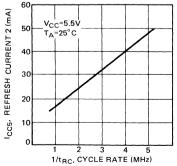

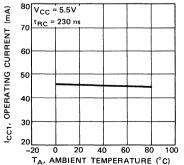

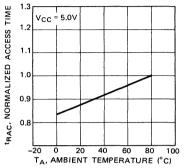

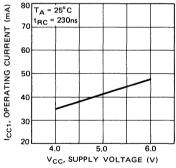

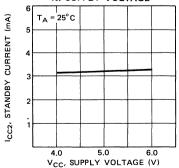

## **TYPICAL CHARACTERISTICS CURVES**

í

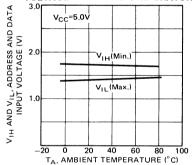

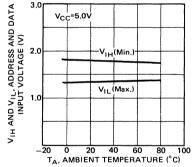

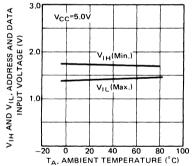

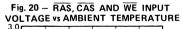

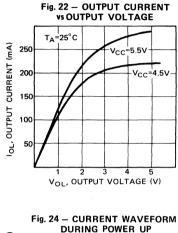

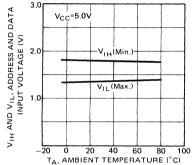

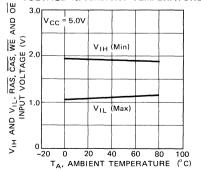

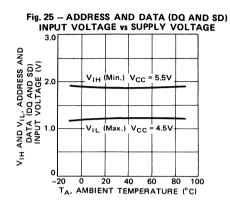

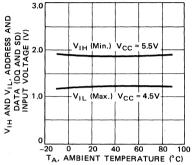

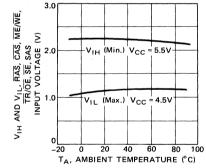

Fig. 17 – ADDRESS AND DATA INPUT VOLTAGE vs AMBIENT TEMPERATURE

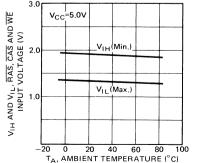

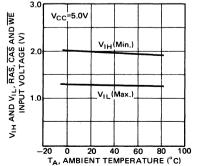

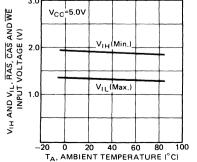

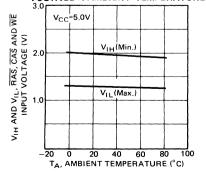

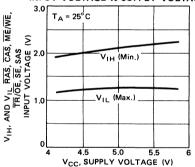

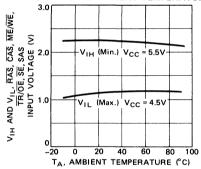

Fig. 19 –  $\overline{RAS}$ ,  $\overline{CAS}$  AND  $\overline{WE}$  INPUT VOLTAGE vs AMBIENT TEMPERATURE

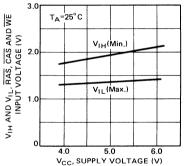

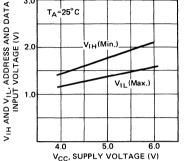

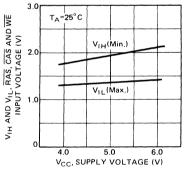

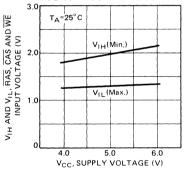

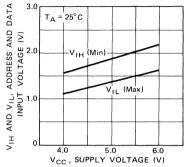

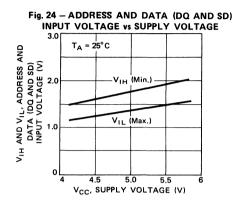

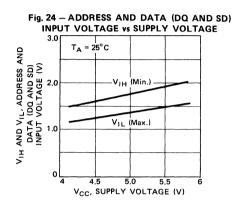

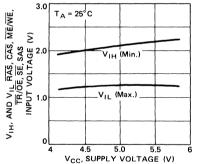

Fig. 16 – ADDRESS AND DATA INPUT VOLTAGE vs SUPPLY VOLTAGE 3.0  $T_A=25^{\circ}C$ (i) 30 2.0 VIH(Min.) VIL(Max.) 1.0 4.0 5.0 6.0

4.0 5.0 6.0 V<sub>CC</sub>, SUPPLY VOLTAGE (V)

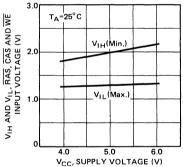

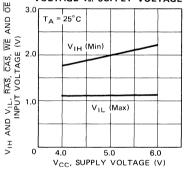

Fig. 18 – RAS, CAS AND WE INPUT VOLTAGE vs SUPPLY VOLTAGE

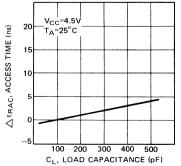

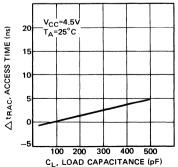

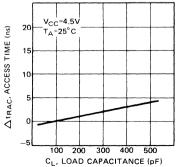

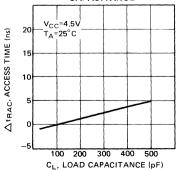

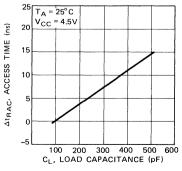

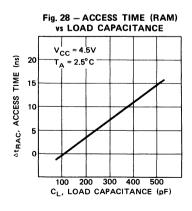

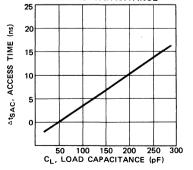

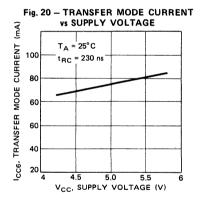

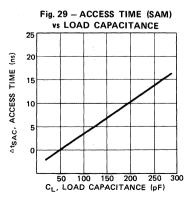

Fig. 20 – ACCESS TIME vs LOAD CAPACITANCE

1

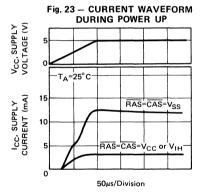

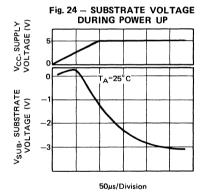

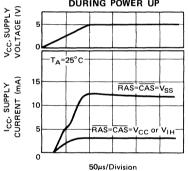

50µs/Division

1-18

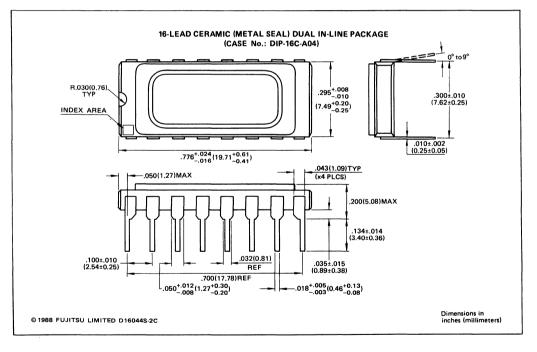

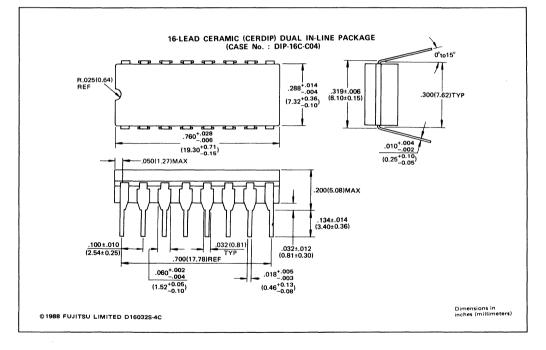

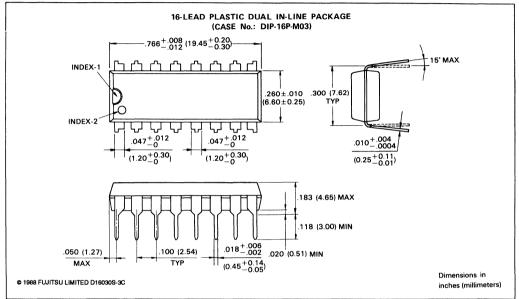

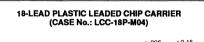

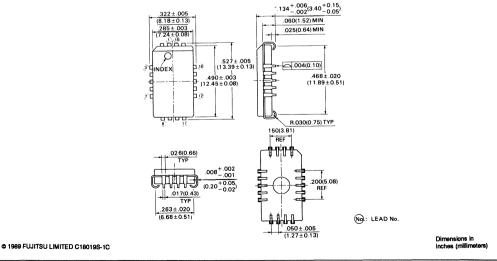

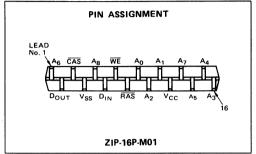

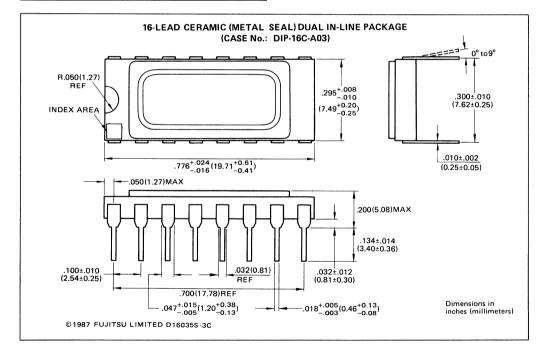

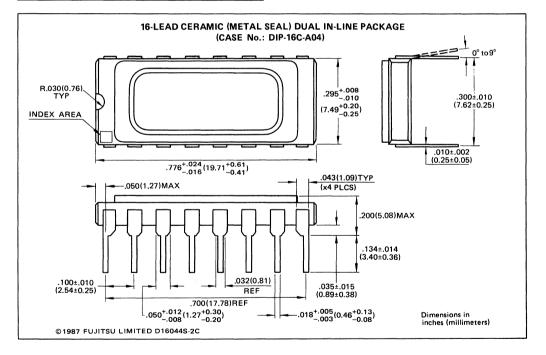

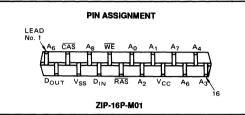

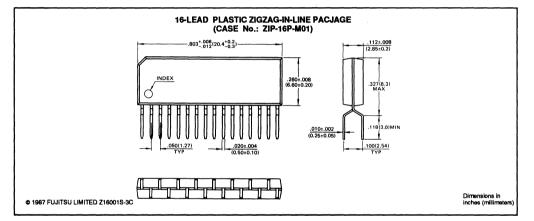

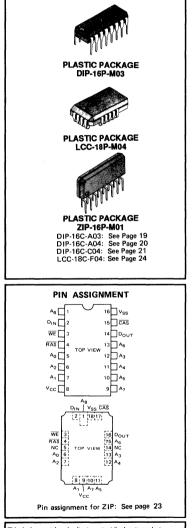

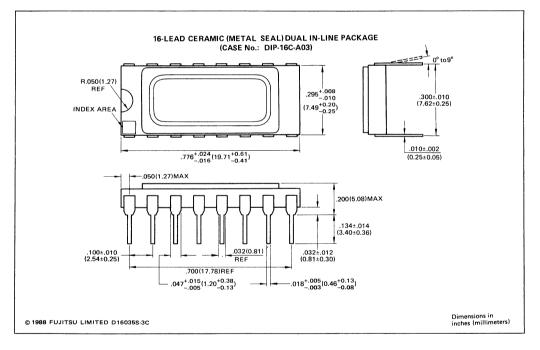

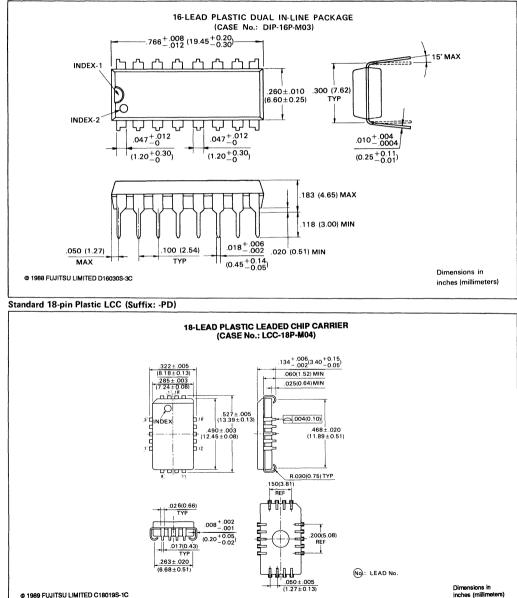

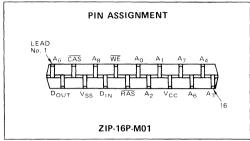

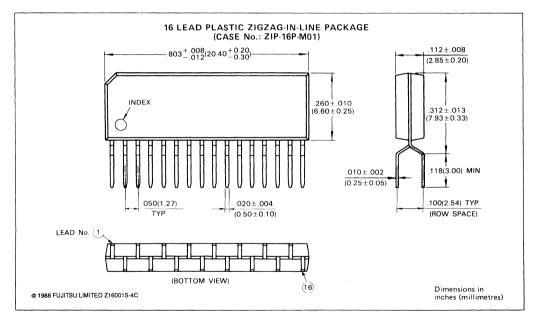

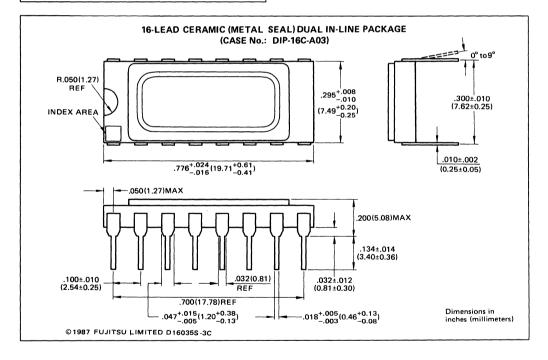

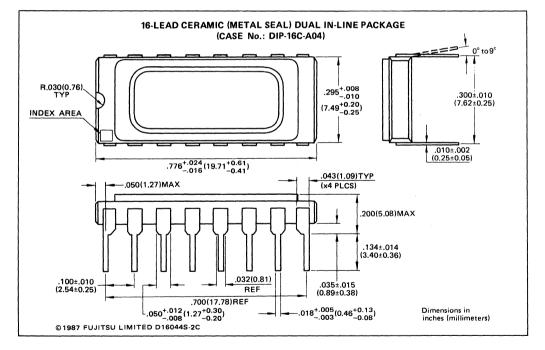

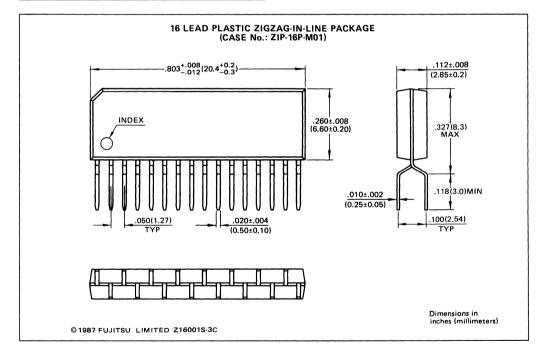

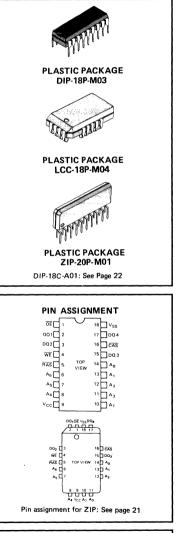

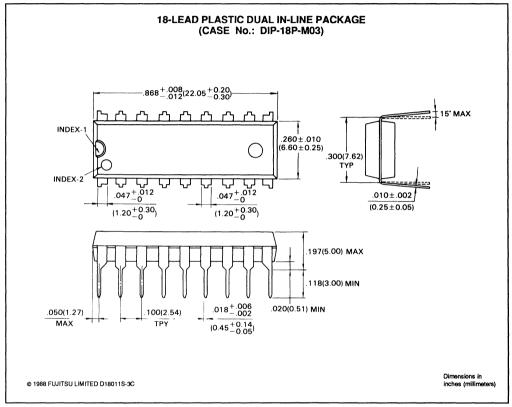

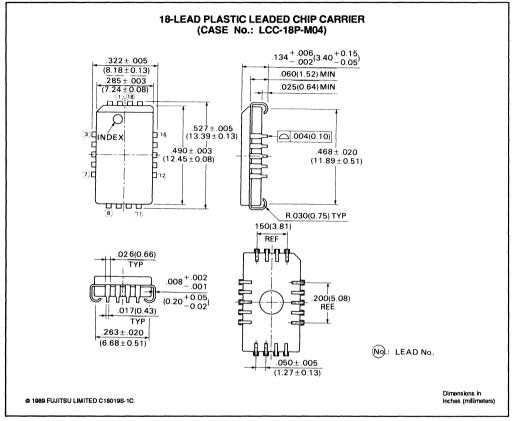

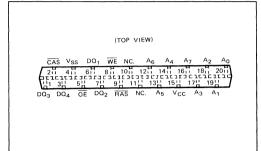

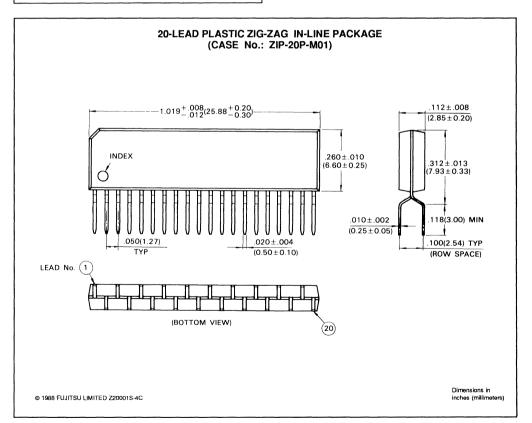

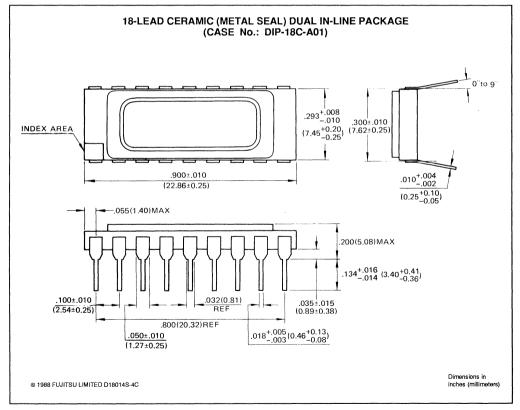

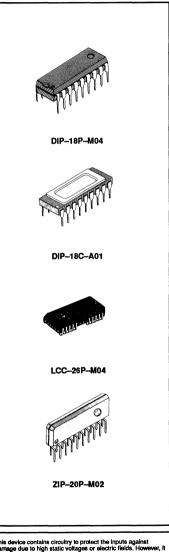

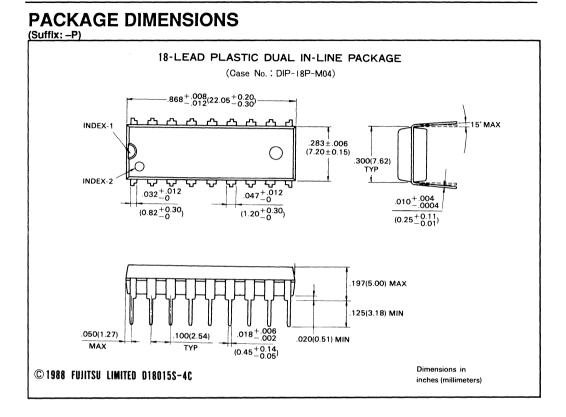

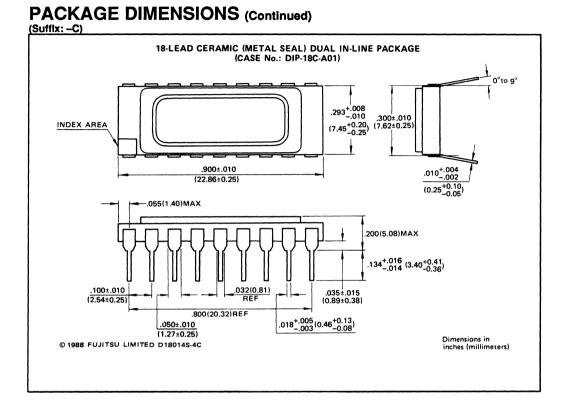

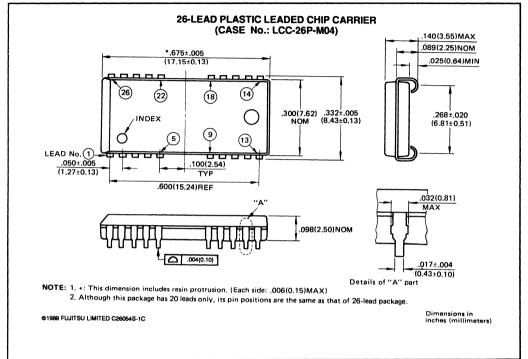

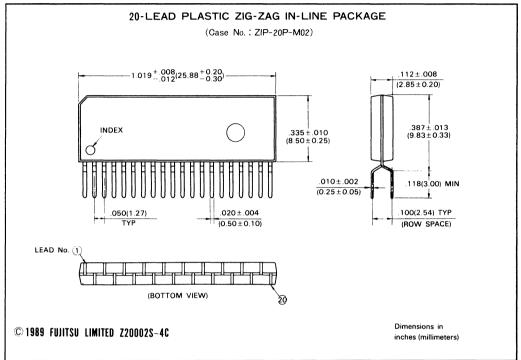

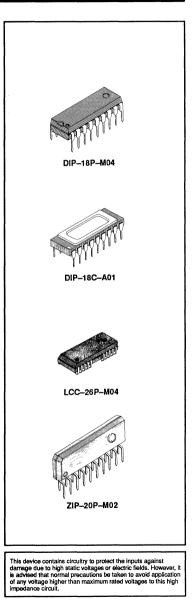

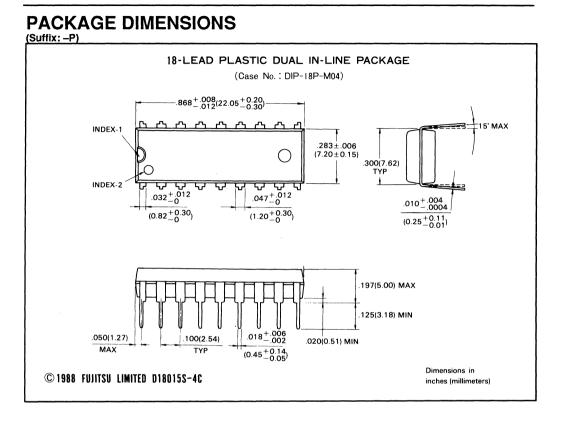

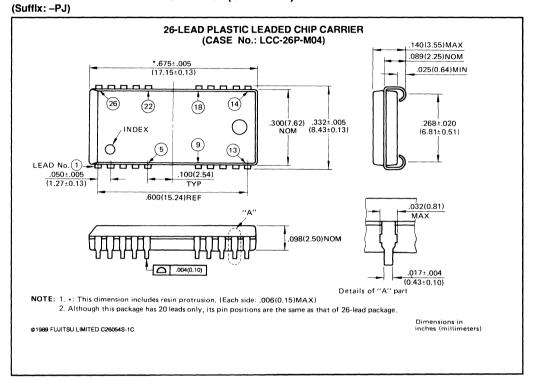

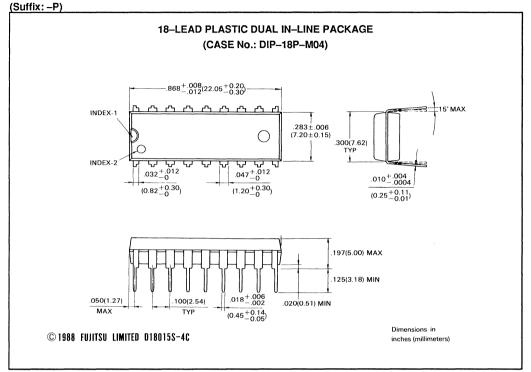

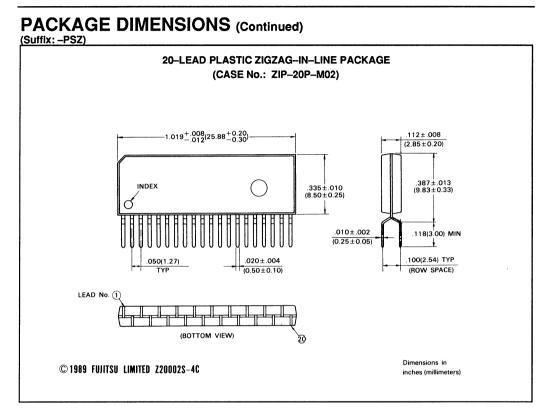

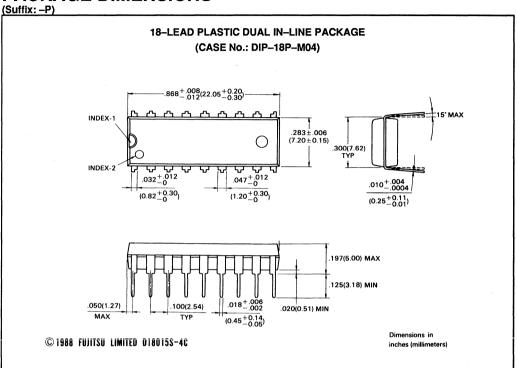

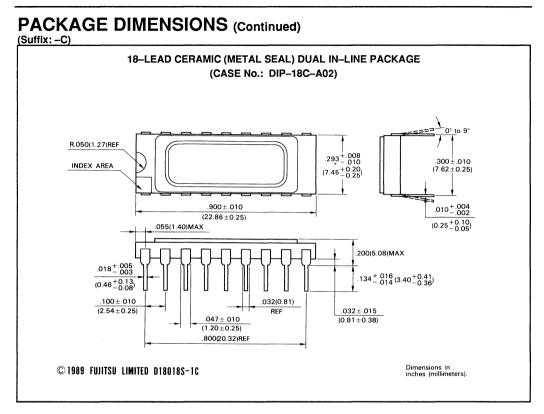

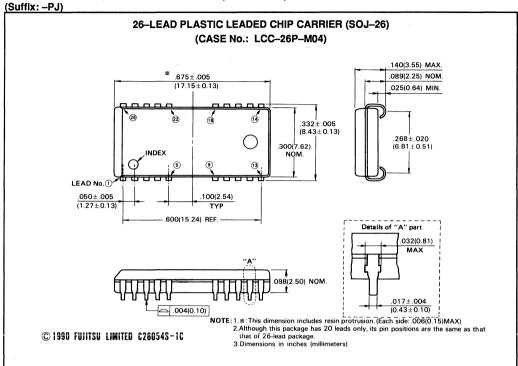

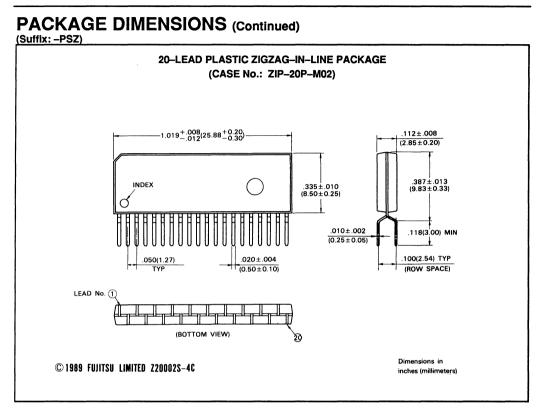

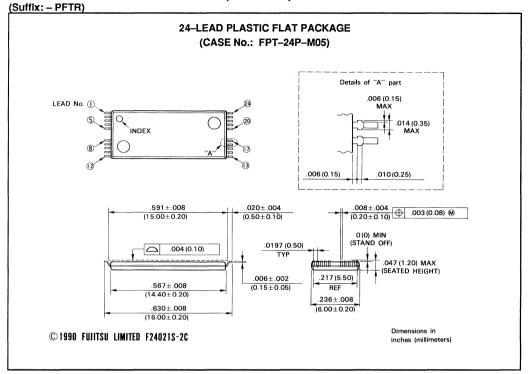

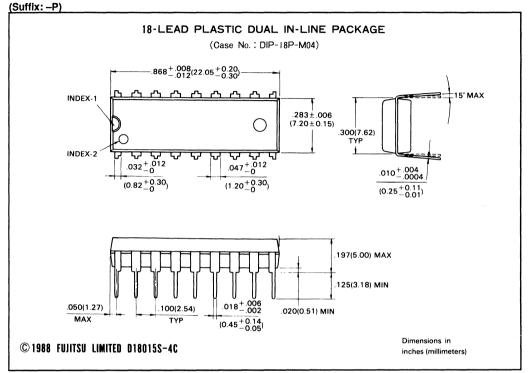

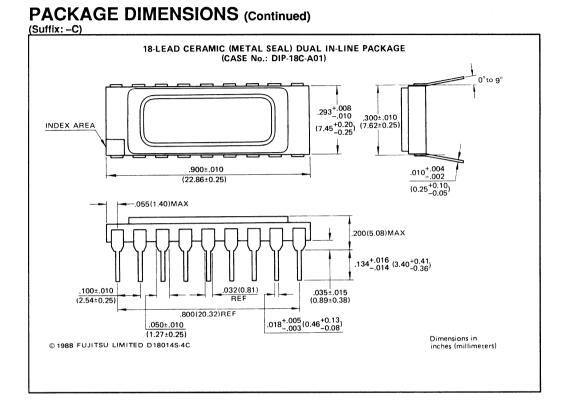

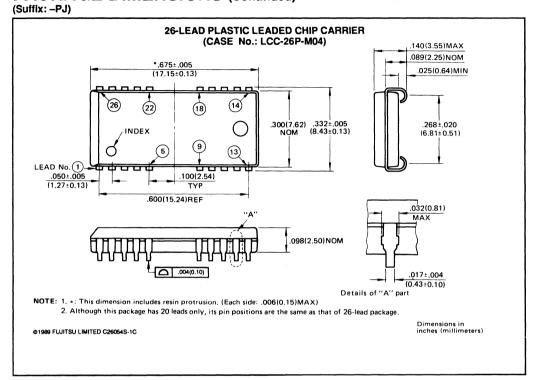

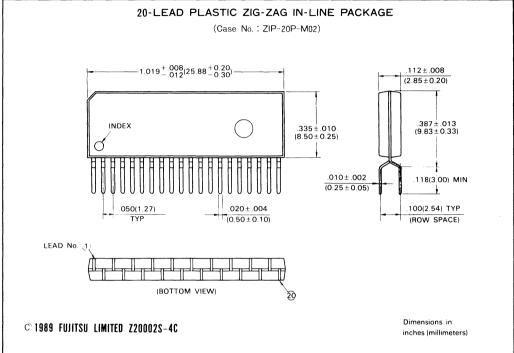

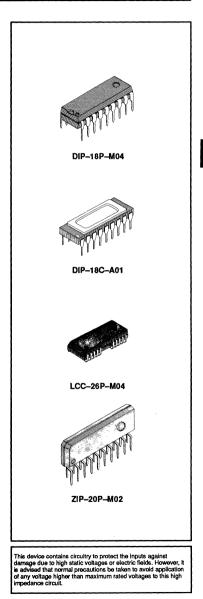

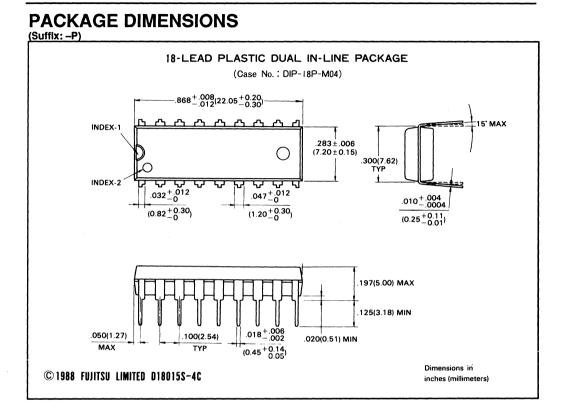

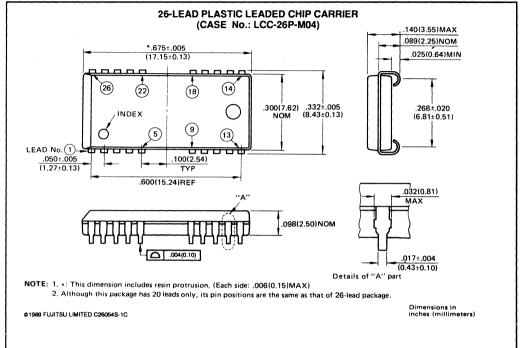

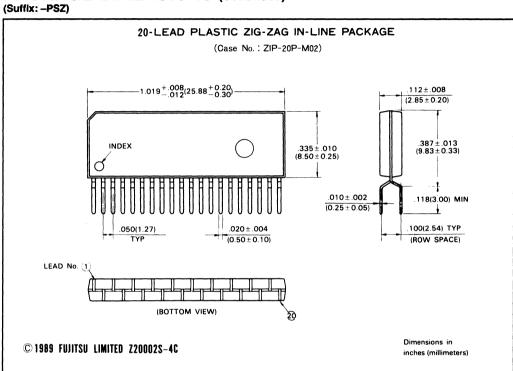

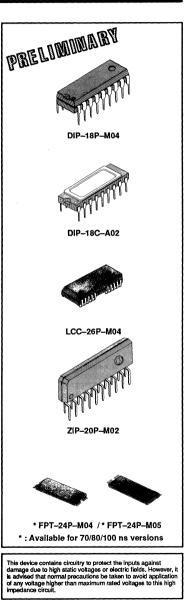

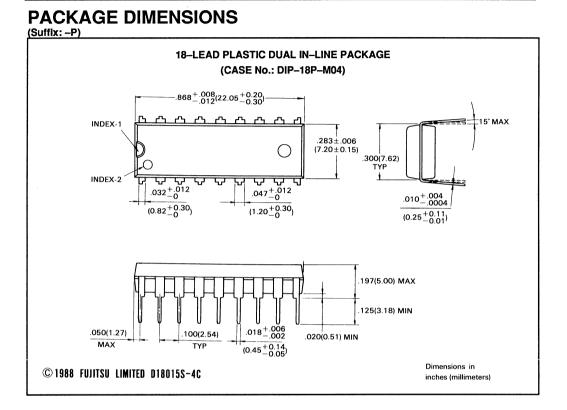

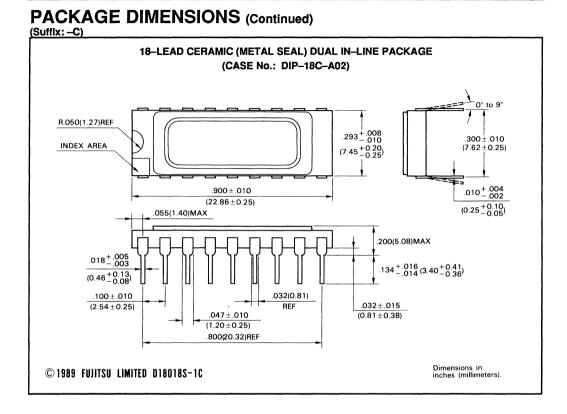

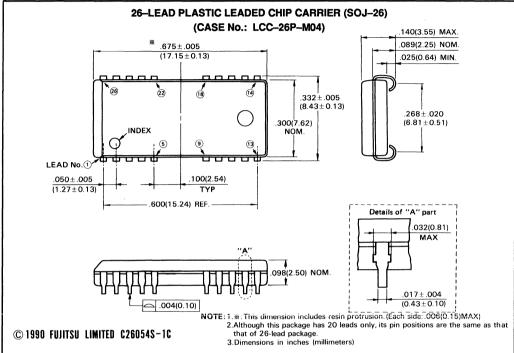

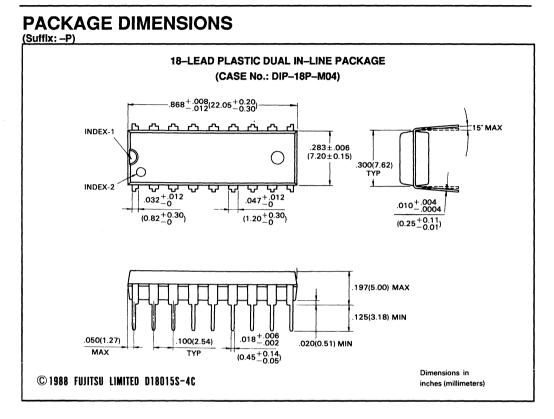

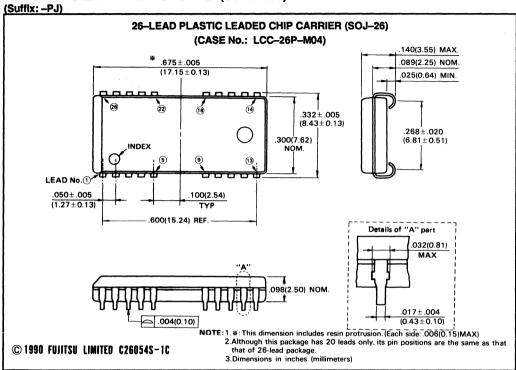

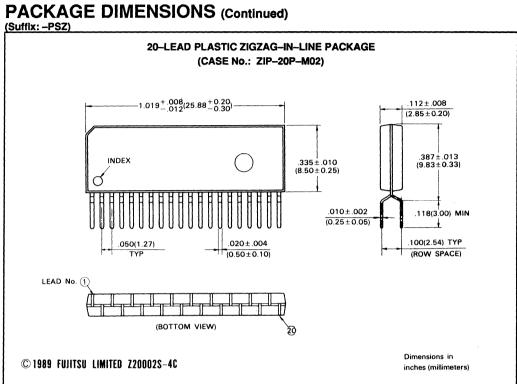

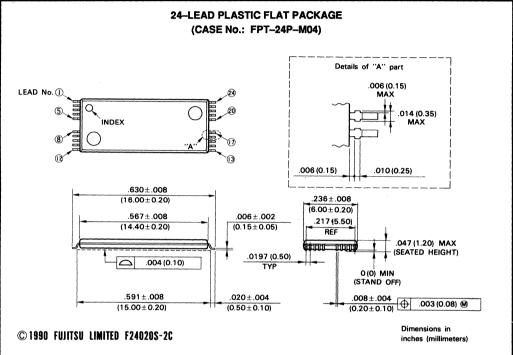

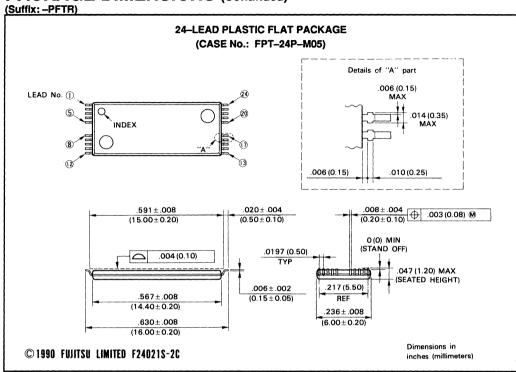

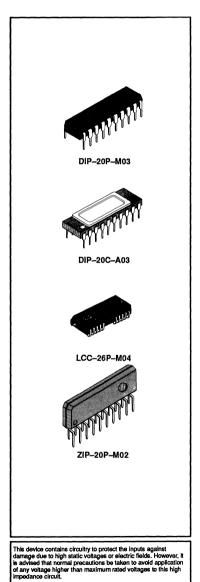

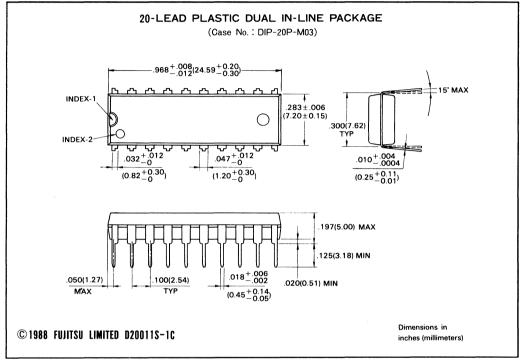

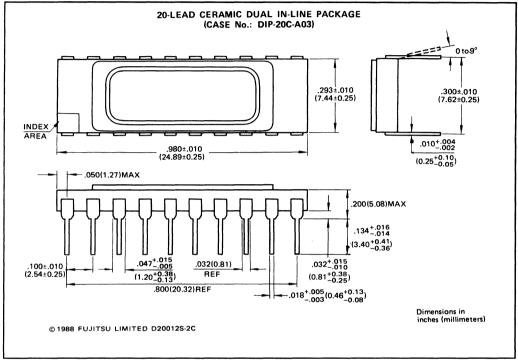

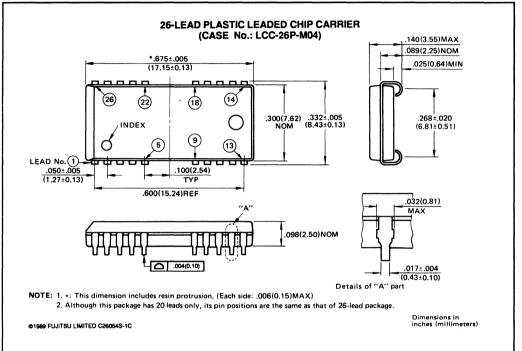

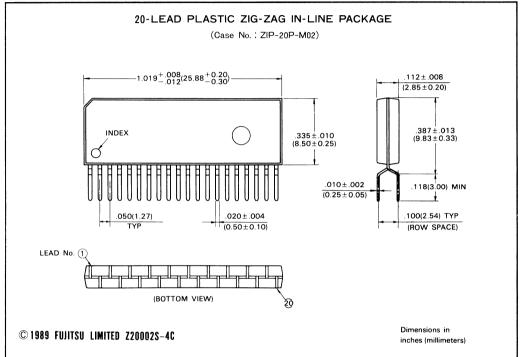

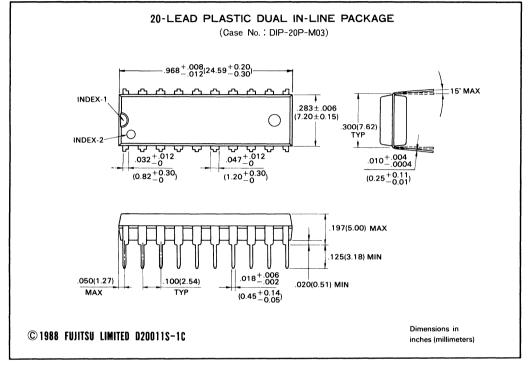

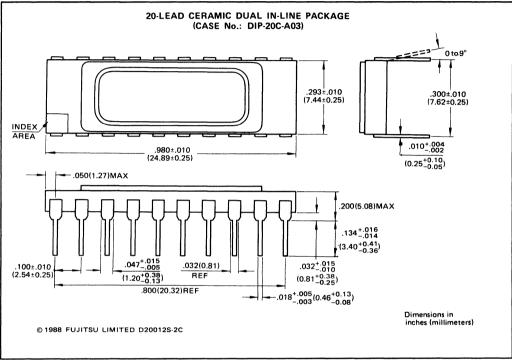

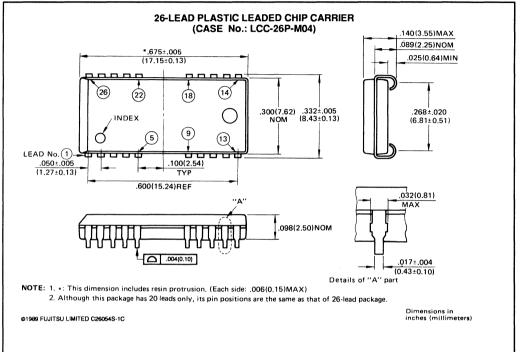

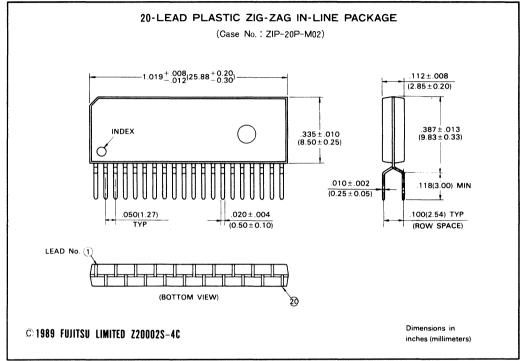

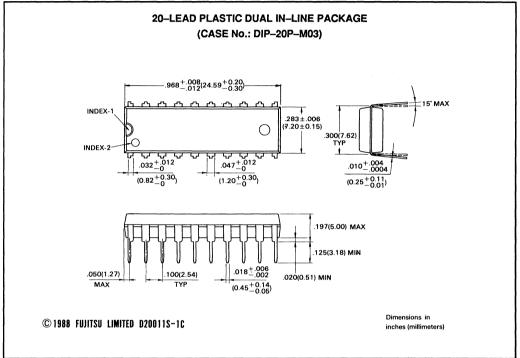

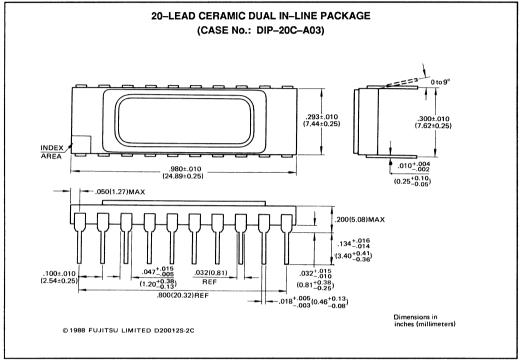

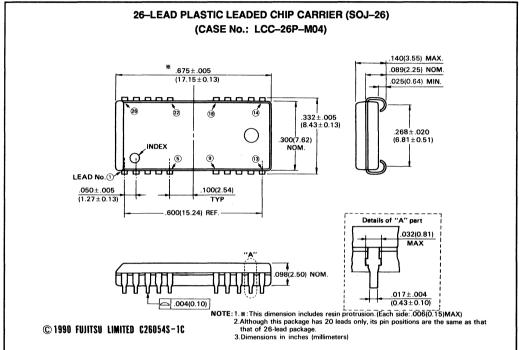

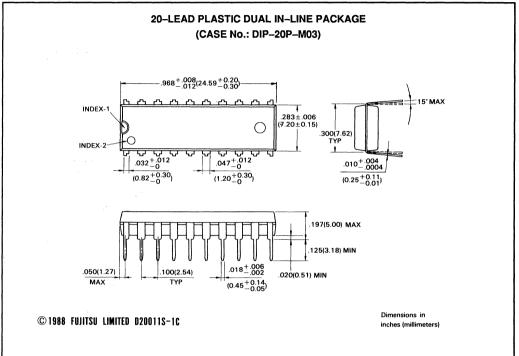

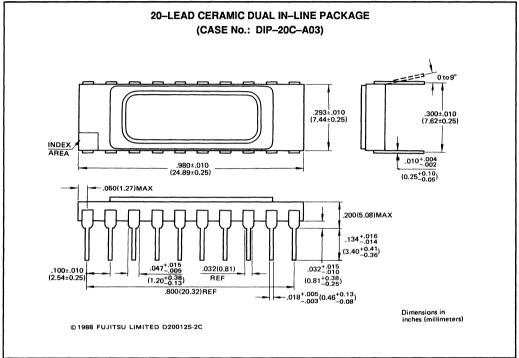

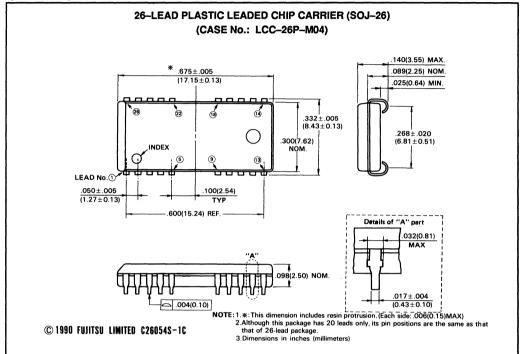

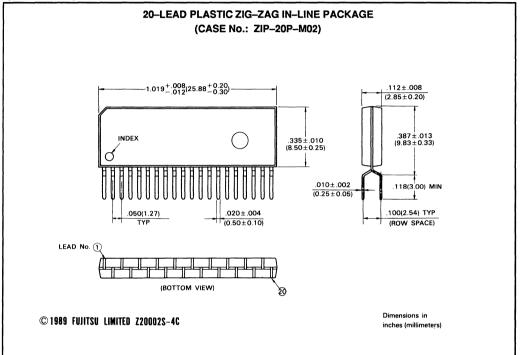

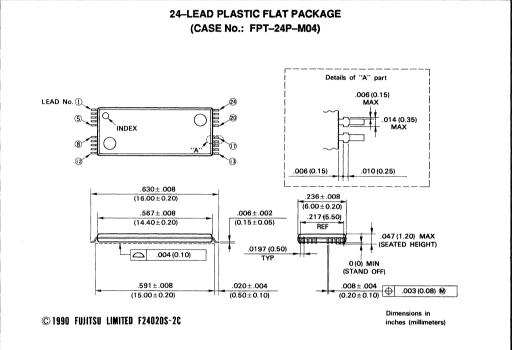

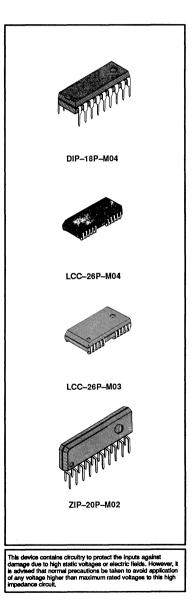

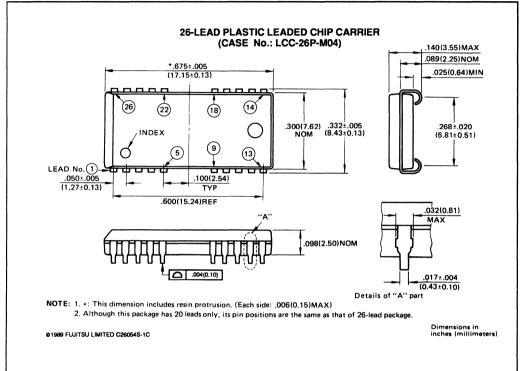

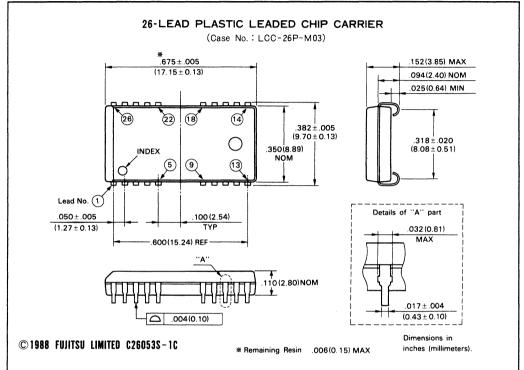

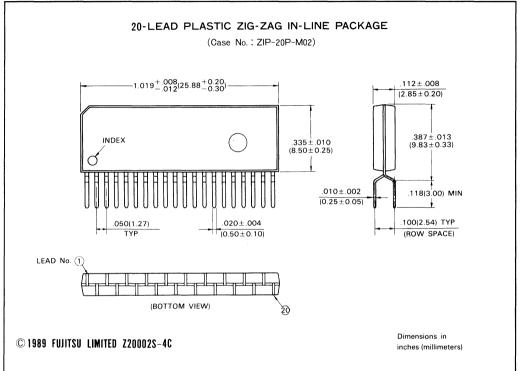

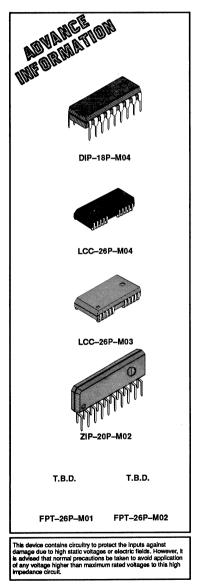

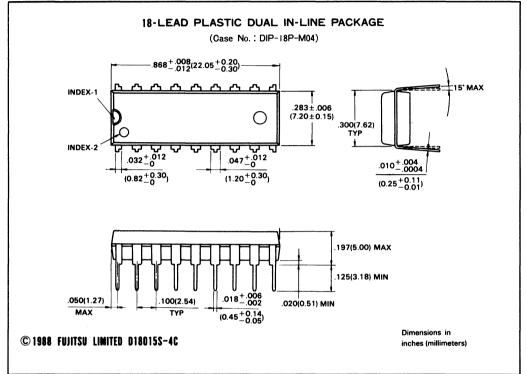

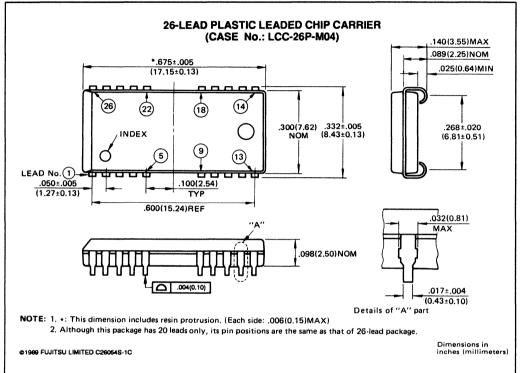

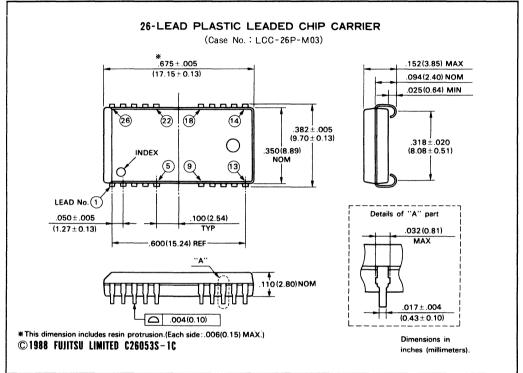

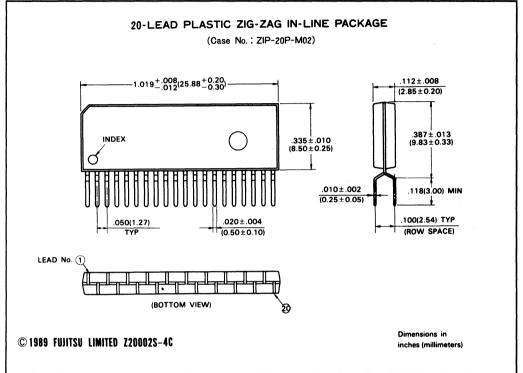

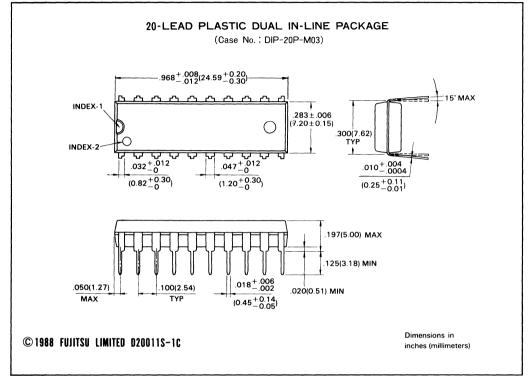

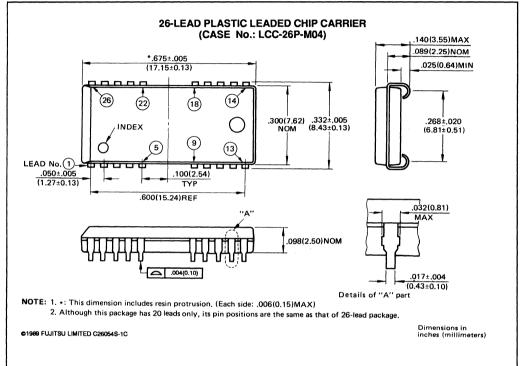

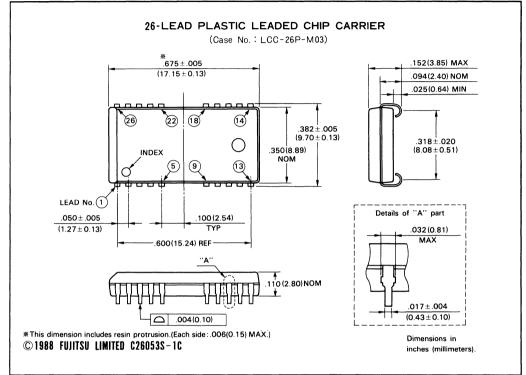

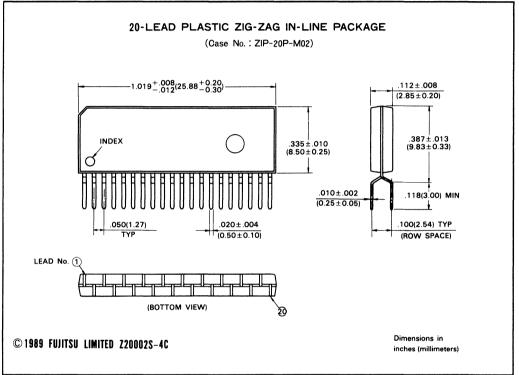

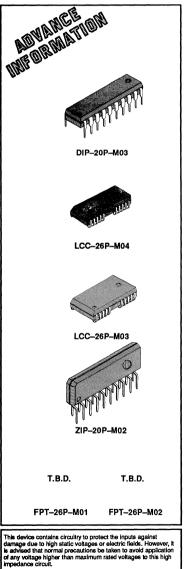

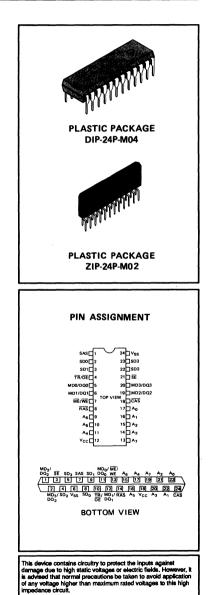

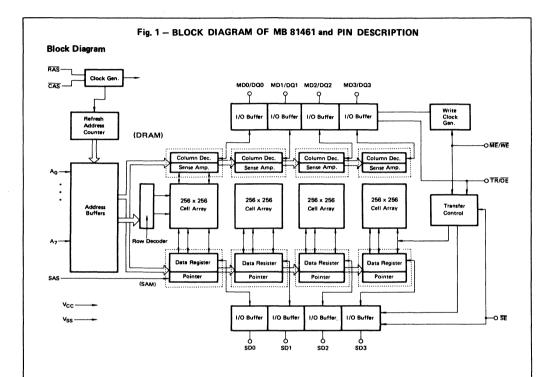

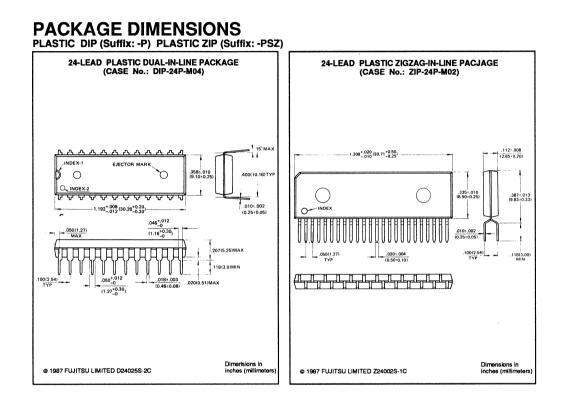

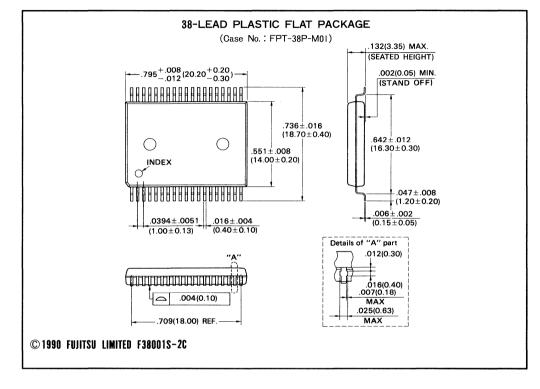

## PACKAGE DIMENSIONS

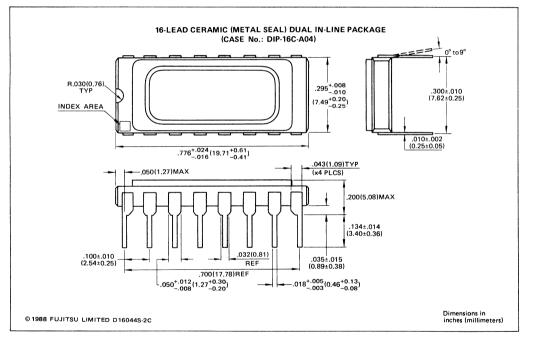

Standard 16-pin Ceramic DIP (Suffix: -C)

Standard 16-pin Ceramic DIP (Suffix: -C)

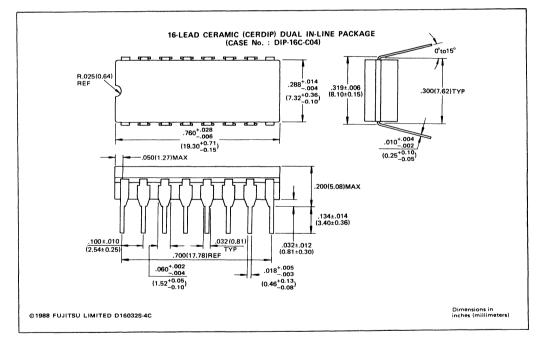

Standard 16-pin Ceramic DIP (Suffix: -Z)

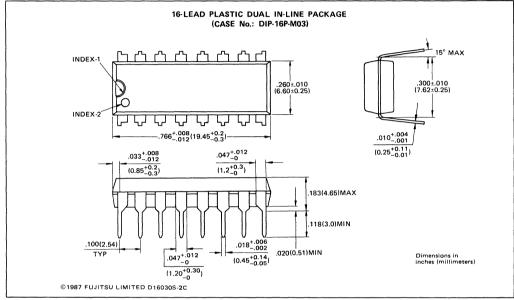

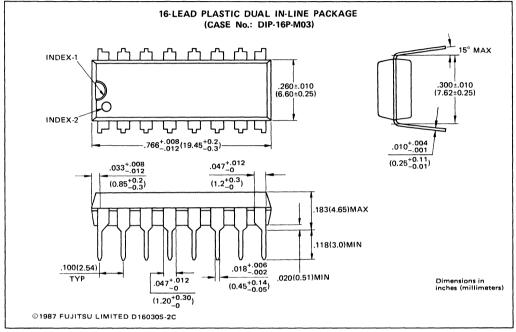

Standard 16-pin Plastic DIP (Suffix: -P)

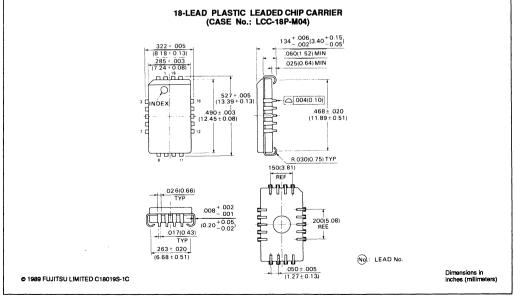

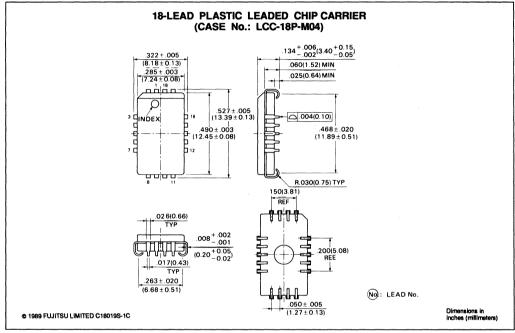

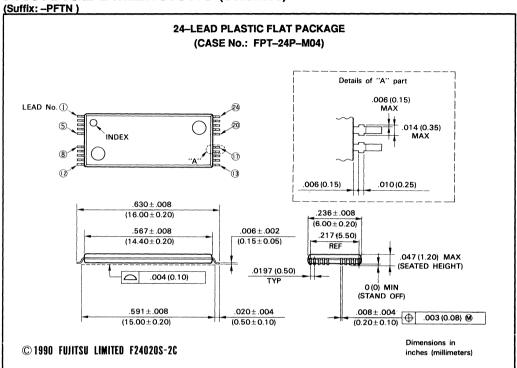

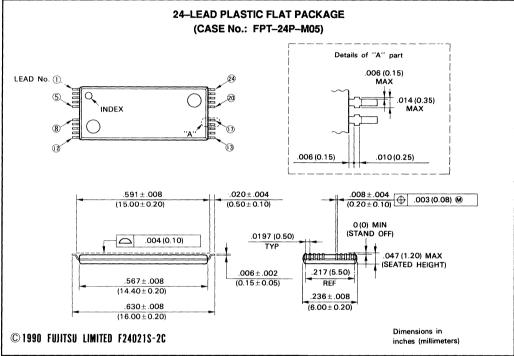

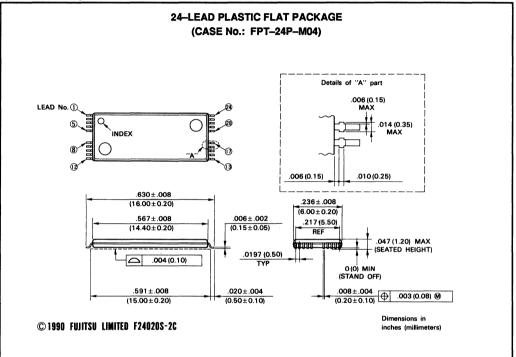

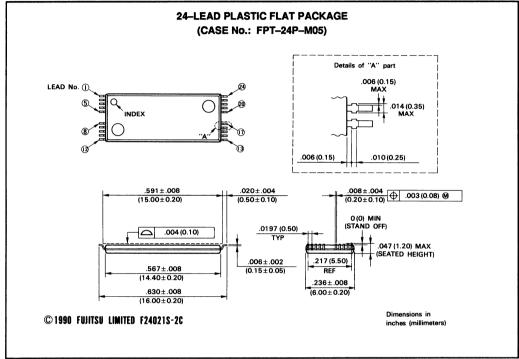

Standard 18-pin Plastic LCC (Suffix: -PD)

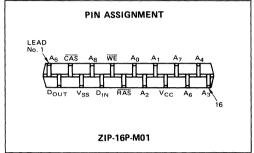

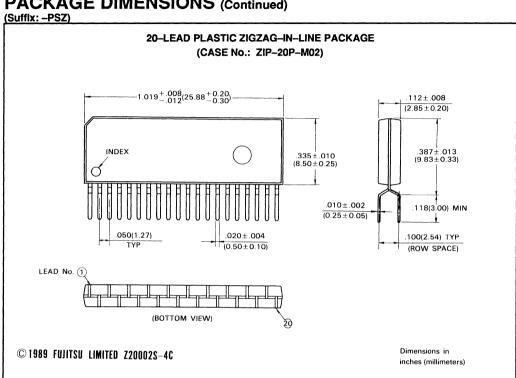

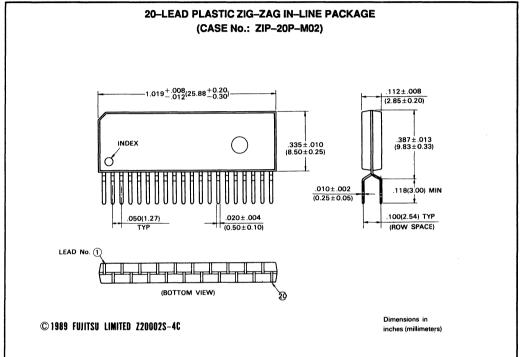

Standard 16-pin Plastic ZIP (Suffix: -PSZ)

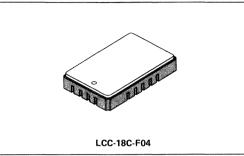

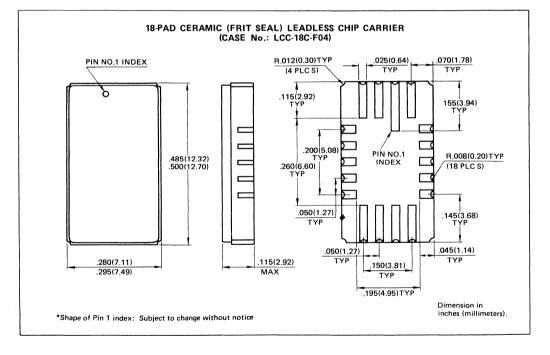

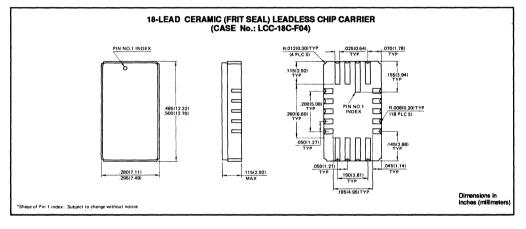

Standard 18-pad Ceramic LCC (Suffix: -TV)

DATA SHEET

## MB81256-80 MOS 262,144 BIT DYNAMIC RANDOM ACCESS MEMORY

### 262.144 Bit Dynamic Random Access Memory

The Fujitsu MB81256 is a fully decoded, dynamic NMOS random access memory organized as 262,144 one-bit words. The design is optimized for high speed. high performance applications such as mainframe memory, buffer memory, peripheral storage, and environments where low power dissipation and a compact layout are required.

Multiplexed row and column address inputs permit the MB81256 to be housed in standard 16-pin DIP and ZIP packages or an 18-pin PLCC package. Pinouts conform to the JEDEC-approved pinouts. Additionally, the MB81256 offers new functional enhancements that make it more versatile than previous dynamic RAMs. CAS-before-RAS refresh provides an on-chip refresh capability that is upwardly compatible with the MB8266A. The MB81256 also features page mode which allows high speed random access of up to 512 bits of data within the same row.

The MB81256 is fabricated using silicon gate NMOS and Fujitsu's advanced Triple-layer Polysilicon process. This process, coupled with single-transistor memory storage cells, permits maximum circuit density and minimal chip size. Dynamic circuitry is used in the design, including the sense amplifiers. Clock timing requirements are noncritical, and power supply tolerance is very wide. All inputs are TTL compatible.

- 262.144 x 1 RAM organization •

- Silicon-gate, Triple Poly NMOS, single transistor cell

- Row Access Time (t<sub>RAC</sub>) 80 ns max. (MB 81256-80)

- Random Cycle Time (t<sub>RC</sub>) 175 ns min. (MB 81256-80)

- Page Mode Cycle Time (tpc) 100 ns max. (MB 81256-80)

- Single +5 V Supply, ±10% tolerance

- Low Power 385 mW max. (MB 81256-80) 25 mW max. (standby)

- 256 refresh cycles every 4 ms

- CAS-before-RAS, RAS-only, Hidden refresh capability

- High speed Read-white-Write cvcle

- tAR, twcs, tohn, tewo are eliminated Output unlatched cycle end allows two-dimensional chip select

- Common I/O capability using

- Early Write operation

- On-chip latches for Addresses and Data-in

- Standard 16-Pin Plastic Packages: DIP (MB81256-XXP) ZIP (MB81256-XXPSZ) ZIP (MB61250-AAF 3C/ Standard 18-Pin Plastic Package: PLCC(MB81256-XXPV) Standard 16-Pin Ceramic Package: DIP (MB81256-XXC)

| Absolute Maximum Ratings (See | Note) |

|-------------------------------|-------|

|-------------------------------|-------|

| Parameter                                                                                  |         | Symbol           | Value       | Unit |  |

|--------------------------------------------------------------------------------------------|---------|------------------|-------------|------|--|

| Voltage at any pin relative to $V_{SS}$<br>Voltage of $V_{CC}$ supply relative to $V_{SS}$ |         | VIN, VOUT        | -1 to +7    | ٧    |  |

|                                                                                            |         | Vcc              | -1 to +7    | v    |  |

| Storage Temperature                                                                        | Ceramic | T <sub>STG</sub> | -55 to +150 | °C   |  |

|                                                                                            | Plastic | Γ                | -55 to +125 |      |  |

| Power Dissipation                                                                          |         | PD               | 1.0         | w    |  |

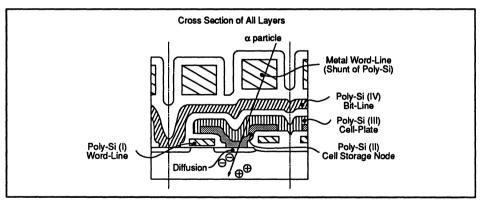

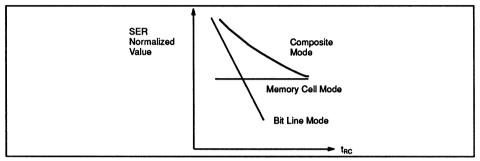

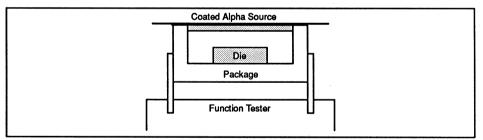

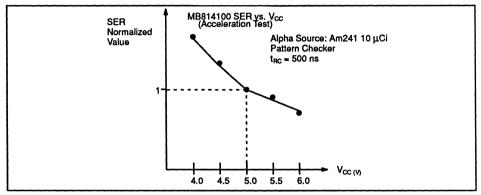

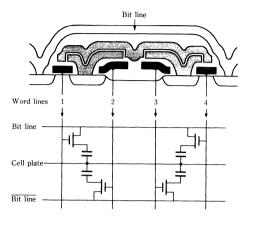

| Short Circuit Output Current                                                               |         |                  | 50          | mA   |  |