PHIR

# **Telecommunications Products**

**Nata Book**

**1992** FU<sup>ໍ</sup>ິາTSU

# Prescalers

1

2

3

4

5

6

7

8

9

10

11

12

- Phase-Locked Loops (PLLs)

- Single-Chip PLLs/Prescalers

- Single-Chip VCOs/Prescalers

- **Piezoelectric Devices**

- **Cordless Telephone Integrated Circuits**

- **Telephone Integrated Circuits**

- Coders/Decoders (CODECs)

- Quality and Reliability

- Ordering Information

- Sales Information

- Appendix: Design Information

# **Telecommunication Products**

1992 Data Book

Fujitsu Limited Tokyo, Japan

Fujitsu Microelectronics, Inc. San Jose, California, U.S.A.

Fujitsu Mikroelektronik GmbH Frankfurt, F.R. Germany

Fujitsu Microelectronics Asia PTE Limited Singapore

© 1991 Fujitsu Microelectronics, Inc., San Jose, California

#### All Rights Reserved.

Circuit diagrams using Fujitsu products are included to illustrate typical semiconductor applications. Information sufficient for construction purposes may not be shown.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu Microelectronics, Inc. assumes no responsibility for inaccuracies.

The information conveyed in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu Limited, its subsidiaries, or Fujitsu Microelectronics, Inc.

Fujitsu Microelectronics, Inc. reserves the right to change products or specifications without notice.

No part of this publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu Microelectronics, Inc.

This document is published by the Publications Department, Integrated Circuits Division, Fujitsu Microelectronics, Inc., 3545 North First Street, San Jose, California, U.S.A. 95134–1804; U.S.A.

Printed in the U.S.A.

Edition 1.0

### PREFACE

This data book contains the latest product information for Fujitsu's line of Telecommunications Products. This year's edition includes Piezoelectric Devices and IC Compandors, as well as sustaining products from the previous edition. Please note that the contents of this edition have been reorganized to better categorize products for your ease of use.

In addition to the collection of data sheets, you will find valuable information on ordering and expanded packaging descriptions, both in the *Order Information* section. One appendix, *Design Information*, is included as a guideline for selecting and designing Fujitsu prescalers and phase-locked loops for VHF and UHF frequency synthesis.

If you are interested in obtaining other Fujitsu product information, see the publication listing on the following pages for titles and brief descriptions of other Fujitsu product literature. To obtain a copy of any of the documents, contact one of our sales offices.

### **FUJITSU PRODUCT PUBLICATIONS**

The following is a list of the product publications available from Fujitsu Microelectronics, Inc. Call your nearest FMI Sales Office or Sales Representative to order any document(s) you need. (See the Sales Information section for phone numbers.)

### STANDARD PRODUCTS

| Dynamic RAM Products Data Book                    | Contains product data sheets for NMOS and CMOS DRAMs,<br>including 1M and 4M devices, and MOS application-specific<br>RAMs.                                                                                                |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Static RAM Products Data Book                     | Contains product data sheets for high-speed CMOS and<br>BiCMOS SRAMs, low-power CMOS SRAMs and application-<br>specific SRAMs.                                                                                             |

| ECL RAM Products Data Book                        | Contains product data sheets for ECL and TTL bipolar ECL<br>RAMs, BiCMOS ECL RAMs, and application-specific RAMS<br>including self-timed RAMs (STRAMs).                                                                    |

| Programmable Memory Products Data<br>Book         | Contains product data sheets for programmable ROMs (including registered and wide-temperature range PROMs); CMOS mask-programmable ROMS, OTP ROMs, erasable PROMs, and EEPROMs; NMOS erasable PROMs and non-volatile RAMs. |

| Memory Card Products Data Book                    | Contains product data sheets and programming information for<br>68-pin JEIDA and PCMCIA standard memory cards and connec-<br>tors and for 38-pin memory cards.                                                             |

| Power Transistor Products Data Book               | Contains product data sheets for RETs, Darlington arrays, and FETs.                                                                                                                                                        |

| Linear Products Data Book                         | Contains product data sheets for audio products, power supply<br>controls, motor drivers, disk drivers, and converters (A/D, D/A,<br>A/D-D/A, and F/V), and other linear products.                                         |

| Linear Products Selector Guide                    | Presents an overview of linear products.                                                                                                                                                                                   |

| Telecommunication Products Data Book              | Contains product data sheets for prescalers and VCOs, PLLs, single-chip PLLs and Prescalers, CODECs, telephone ICs, and cellular telephone ICs, cordless telephone ICs, and piezoelectric devices.                         |

| Telecommunication Devices Selector Guide          | Presents an overview of telecommunication products and piezo-<br>electric devices.                                                                                                                                         |

| Interface and Logic Products Selector<br>Guide    | Presents an overview of logic and interface devices.                                                                                                                                                                       |

| CMOS 4-bit Microcontrollers Data Book,<br>Vol. I  | Contains product information, including the development tool for the MB8850 and MB88200 families of 4-bit microcontrollers.                                                                                                |

| CMOS 4-bit Microcontrollers Data Book,<br>Vol. II | Contains product information, including the development tool for the MB88500 family of 4-bit microcontrollers.                                                                                                             |

| CMOS 4-bit Microcontrollers Selector<br>Guide     | Presents an overview of the MB88500 (high end), MB8850 (mid-<br>range), and MB88200 (low end) families of 4-bit microcontrollers.                                                                                          |

| Master Product Guide                              | Presents an overview of the entire range of products offered by the Integrated Circuits Division: Standard and ASIC products.                                                                                              |

### FUJITSU PRODUCT PUBLICATIONS (Continued)

#### ASIC PRODUCTS

CMOS Channeled Gate Arrays Data Book Contains product information for UHB Series High Drive CMOS and Design Evaluation Guide Gate Arrays and CG10 Series High Drive CMOS Gate Arrays. CMOS Channelless Gate Arrays Data Contains product information for AU Series CMOS Series Gate Book and Design Evaluation Guide Arrays and CG21 Series CMOS Gate Arrays. Presents an overview of CMOS, BiCMOS, ECL, and GaAs gate ASIC Products Selector Guide arrays and CMOS standard cell products. BiCMOS Gate Arrays Data Book and Contains product information for BC Series BiCMOS Gate Design Evaluation Guide Arrays and BC-H Series BiCMOS Gate Arrays. Contains product information for ET Series ECL Gate Arrays. ECL Gate Arrays Data Book and Design H Series ECL Gate Arrays, Ultra-High Performance ECL Gate Evaluation Guide Arrays, and VH Series ECL Gate Arrays. ASIC SOFTWARE Discusses the trend in ASICs: migration from using gates as The ASIC Gallerv<sup>™</sup> (catalog) primitives to using LSI and even VLSI macros as design elements. The ASIC Design Environment (catalog) Provides an overview of the third-party tools that work in concert with Fujitsu's proprietary tools. ViewCAD™, BankCAD™, and FAME. Also included are product profiles explaining how the third-party tools fit within the design framework. ViewCAD User's Guide Provides a basic understanding of Fujitsu's proprietary CAD/CAE system, ViewCAD. This book provides information necessary to design, test, simulate, and analyze circuits using Fujitsu's unit cell libraries for AU, UHB, CG10, CG21, and CG31 CMOS technoloaies. ViewCAD Installation Guide Explains how to install Fujitsu's proprietary CAD/CAE system. ViewCAD. CMOS ASIC Reference Manual for Provides a basic understanding of the Valid System on the Sun Valid platform as it interfaces with Fujitsu programs to build circuits using Fujitsu's unit cell libraries for AU and UHB CMOS technoloaies. FAME User's Guide Provides a basic understanding of the Fujitsu ASIC Management Environment (FAME) software as it interfaces with third-party tools (Sun or PC) to build circuits using Fujitsu's unit cell libraries. FAME Reference Manual Provides installation and directory information for the Fujitsu ASIC Management Environment (FAME) software, which uses third-party tools (Sun or PC) to build circuits using Fujitsu's unit

Synopsys User's Guide Provides a basic understanding of the Synopsys® system as it interfaces with Fujitsu programs to build circuits using Fujitsu's unit cell libraries.

cell libraries.

## FUJITSU PRODUCT PUBLICATIONS (Continued)

### ASIC SOFTWARE (Continued)

| Verilog-XL User's Guide                     | Provides a basic understanding of the Verilog-XL® system as it<br>interfaces with Fujitsu programs to build circuits using Fujitsu's<br>unit cell libraries.                                                                                                                                                                          |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Future Publications                         |                                                                                                                                                                                                                                                                                                                                       |

| For Memory Products:                        |                                                                                                                                                                                                                                                                                                                                       |

| Hybrid Products (1992)                      | Presents Fujitsu's hybrid products and discusses thick- and thin-film capabilities.                                                                                                                                                                                                                                                   |

| For ASIC Software:                          |                                                                                                                                                                                                                                                                                                                                       |

| ASIC Design Environment<br>Data Book (1992) | Provides detailed information about the ASIC Design Methodology<br>at Fujitsu. It contains an overview of the third-party tools that work<br>in concert with Fujitsu's proprietary tools, ViewCAD, BankCAD, and<br>FAME. Also included are product profiles explaining how the third-<br>party tools fit within the design framework. |

Synopsys® is a registered trademark of Synopsys, Inc. Verilog-XL® is a registered trademark of Cadence Design Systems, Inc. ViewCAD<sup>TM</sup> and BankCAD<sup>TM</sup> are trademarks of Fujitsu Limited. ASIC Gallery<sup>TM</sup> is a trademark of Fujitsu Microelectronics, Inc.

## **Contents and Alphanumeric Product List**

### **Fujitsu's Telecommunication Products**

| Introdu | uction          | vii                                                                |

|---------|-----------------|--------------------------------------------------------------------|

| Sectio  | on 1 – Prescale | ers — At a Glance                                                  |

|         | MB467           | 200 MHz Low Power High Frequency Prescaler                         |

|         | MB501/L         | 1.0/1.1 GHz Two Modulus Prescaler                                  |

|         | 503             | 200 MHz Two Modulus Prescaler                                      |

|         | 504/L           | 520 MHz Two Modulus Prescaler                                      |

|         | MB501LV         | 1.1 GHz Low Voltage/Low Power Two Modulus Prescaler                |

|         | MB504LV         | 520 GHz Low Voltage/Low Power Two Modulus Prescaler                |

|         | MB501SL         | 1.1 GHz Super Low Power Two Modulus Prescaler                      |

|         | MB50516         | 1.6 GHz Ultra-high Frequency Prescaler                             |

|         | MB506           | 2.4 GHz Ultra-high Frequency Prescaler                             |

|         | MB507           | 1.6 GHz Two Modulus Prescaler                                      |

|         | MB508           | 2.3 GHz Two Modulus Prescaler                                      |

|         | MB509           | 1.1 GHz Two Modulus Prescaler with Stand-by Mode                   |

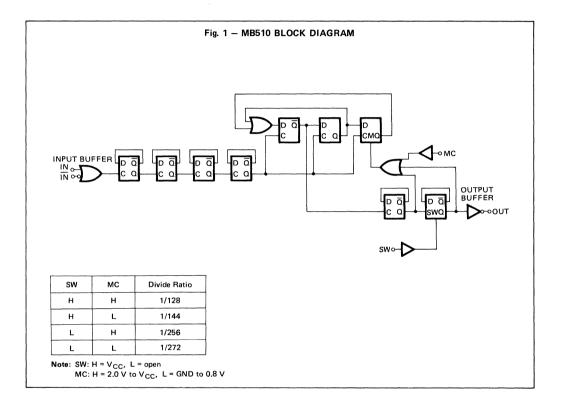

|         | MB510           | 2.7 GHz Two Modulus Prescaler                                      |

|         | MB511           | 1.0 GHz High-speed Prescaler                                       |

| Sectio  | on 2 – Phase-L  | ocked Loops (PLLs) — At a Glance                                   |

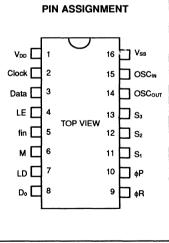

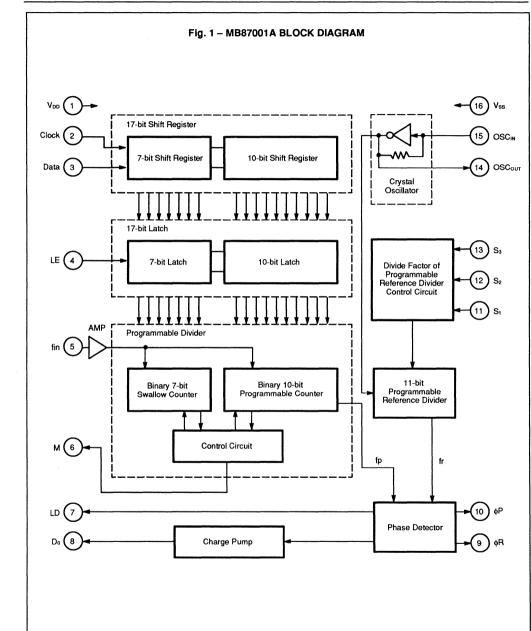

|         | MB87001A        | 13 MHz CMOS Serial Input PLL Frequency Synthesizer                 |

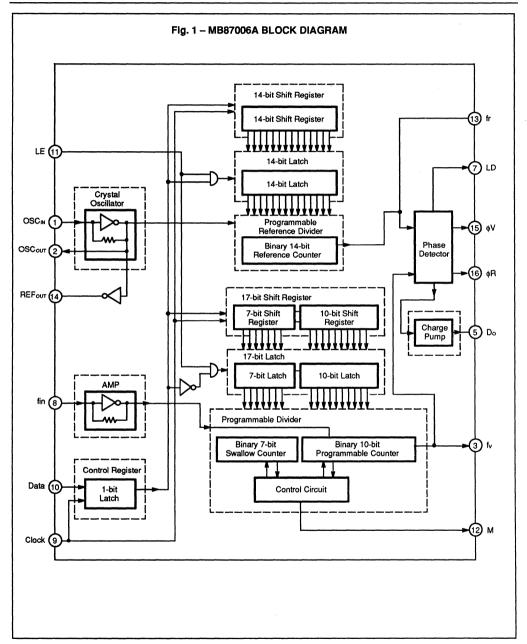

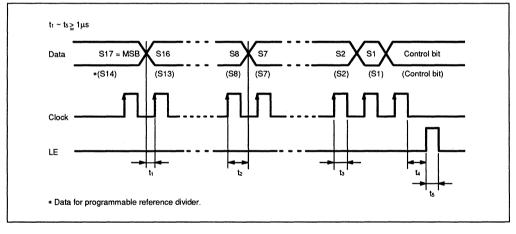

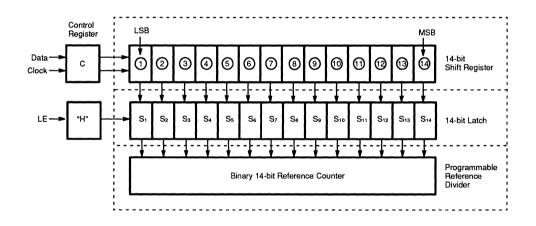

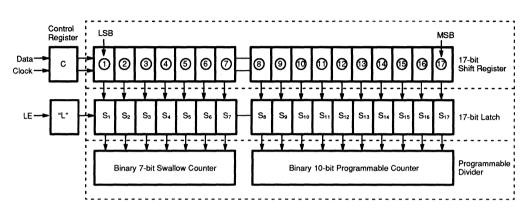

|         | MB87006A        | 17 MHz CMOS Serial Input PLL Frequency Synthesizer                 |

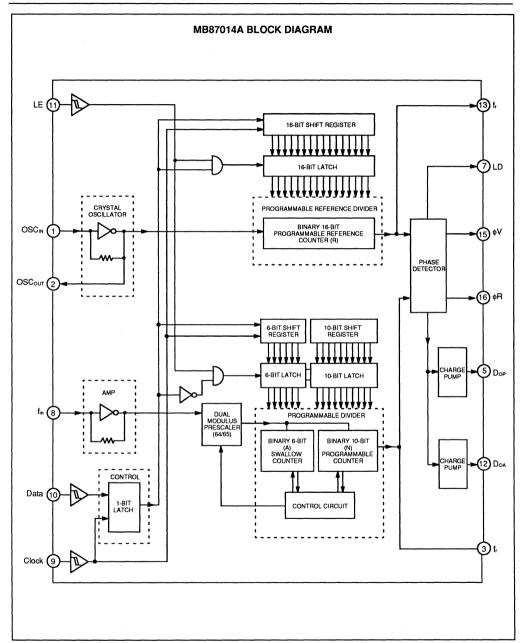

|         | MB87014A        | CMOS Serial Input PLL Frequency Synthesizer                        |

|         |                 | with 180 MHz Prescaler                                             |

|         | MB87076         | 13 MHz CMOS Serial Input PLL Frequency Synthesizer                 |

|         |                 | With Power Down Mode                                               |

|         | MB87086A        | 15 MHz CMOS Serial Input PLL Frequency Synthesizer                 |

|         | MB87087         | 17 MHz CMOS Serial Input PLL Frequency Synthesizer                 |

|         | MB87090         | 13 MHz CMOS Serial Input PLL Frequency                             |

|         |                 | Synthesizer with Constant Current Output Charge Pump 2-73          |

| Sectio  | on 3 – Single-C | Chip PLLs/Prescalers — At a Glance                                 |

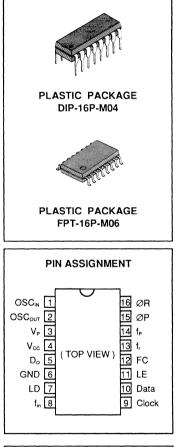

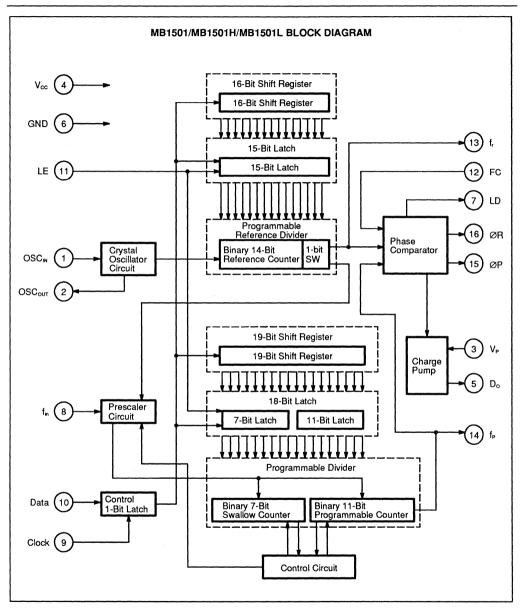

|         | MB1501          | Serial Input PLL Frequency Synthesizer with 1.1 GHz Prescaler 3–3  |

|         | 1501H           |                                                                    |

|         | 1501L           |                                                                    |

|         | MB1502          | Low Power Serial Input PLL Synthesizer with 1.1 GHz Prescaler 3–21 |

|         | MB1503          | Serial Input PLL Frequency Synthesizer with 1.1 GHz Prescaler 3–35 |

|         | MB1504          | Serial Input PLL Frequency Synthesizer with 520 MHz Prescaler 3–49 |

|         | 1504H           |                                                                    |

|         | 1504L           |                                                                    |

|         | MB1505          | Serial Input PLL Frequency Synthesizer with 600 MHz Prescaler 3–67 |

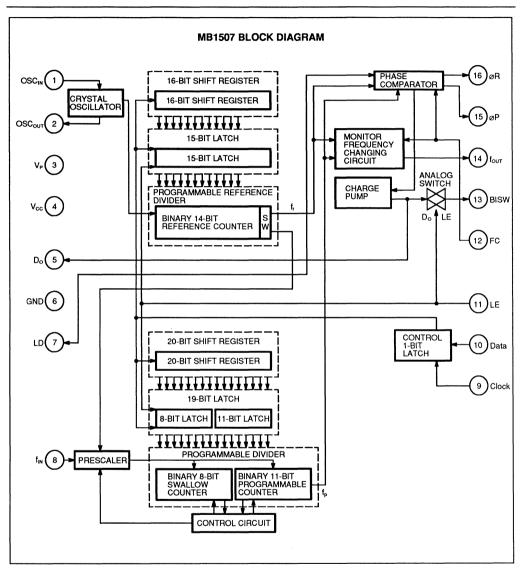

|         | MB1507          | Low Power Serial Input PLL Frequency Synthesizer with 2.0 GHz      |

## Contents and Alphanumeric Product List (Continued)

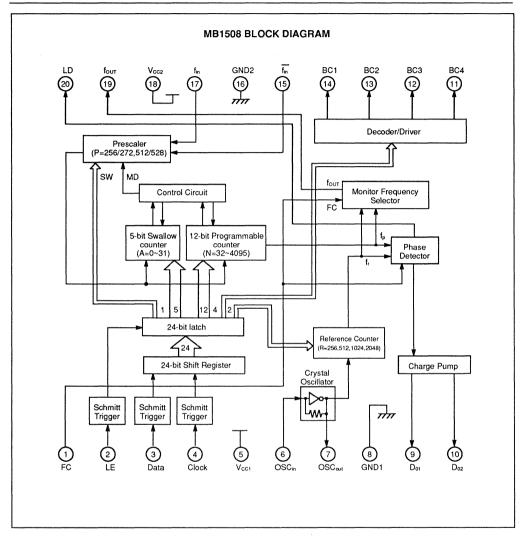

|         | MB1508                                                                                                                                                    | Serial Input PLL Frequency Synthesizer with 2.5 GHz Prescaler 3–91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

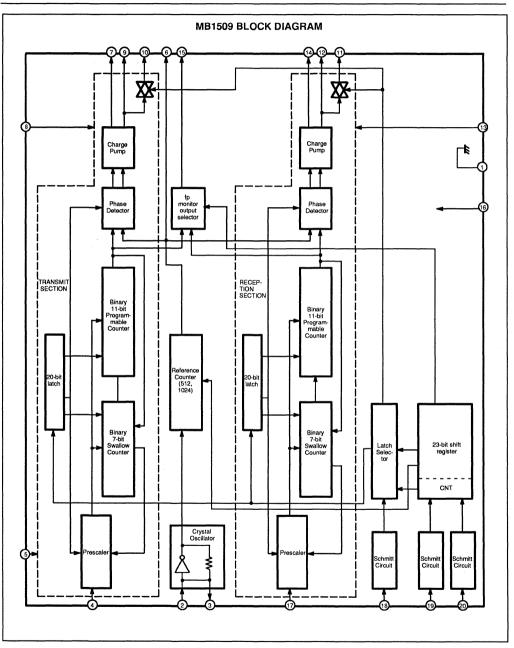

|         | MB1509                                                                                                                                                    | Dual Serial Input PLL Frequency Synthesizer with 400 MHz Prescaler 3-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | MB1511                                                                                                                                                    | Low Power and Low Voltage Serial Input PLL Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         |                                                                                                                                                           | Synthesizer with 1.1 GHz Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | MB1512                                                                                                                                                    | Low Power Serial Input PLL Frequency Synthesizer with 1.1 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                                                                                                                                                           | Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | MB1513                                                                                                                                                    | Serial Input PLL Frequency Synthesizer with 1.1 GHz Prescaler 3-139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | MB1518                                                                                                                                                    | Serial Input PLL Frequency Synthesizer with 2.5 GHz Prescaler 3–153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

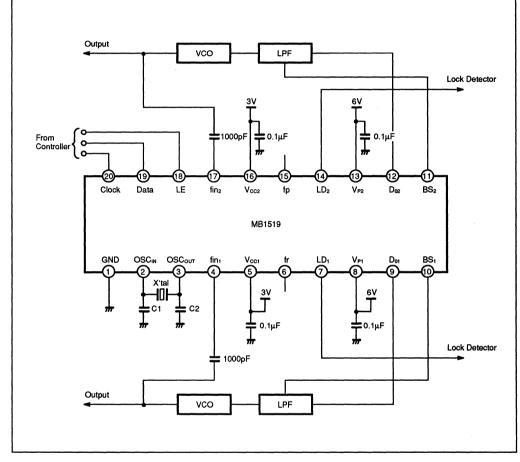

|         | MB1519                                                                                                                                                    | Dual Serial Input PLL Frequency Synthesizer with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |                                                                                                                                                           | 600 MHz Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Section | 4 – Single-C                                                                                                                                              | hip VCOs/Prescalers — At a Glance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | MB551                                                                                                                                                     | 1 GHz Dual Modulus Prescaler with VCO Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Section | 5 - Piezoele                                                                                                                                              | ctric Devices — At a Glance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

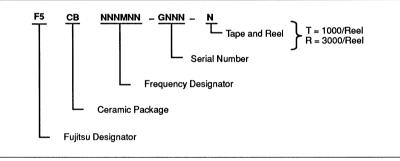

| 2001011 | F5CB Series                                                                                                                                               | SAW-Bandpass Filter Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | M2 Series                                                                                                                                                 | Piezoelectric Devices (D100) with VCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | M2 Series                                                                                                                                                 | Piezoelectric Devices (D100) with VCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | M3 Series                                                                                                                                                 | Piezoelectric Devices (D300) with VCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | M3 Series                                                                                                                                                 | Piezoelectric Devices (D001) with VCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | WO Genes                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Section | 6 - Cordless                                                                                                                                              | Telephone Integrated Circuits — At a Glance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Section | 6 – Cordless<br>MB86460A                                                                                                                                  | Modem with Internal Voice-Band Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Section |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

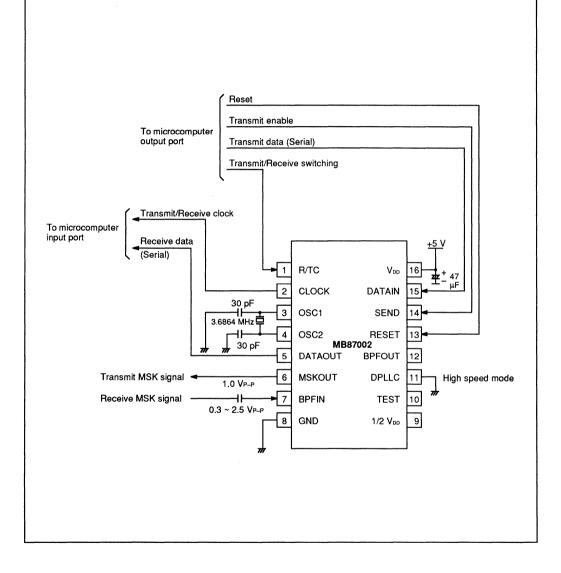

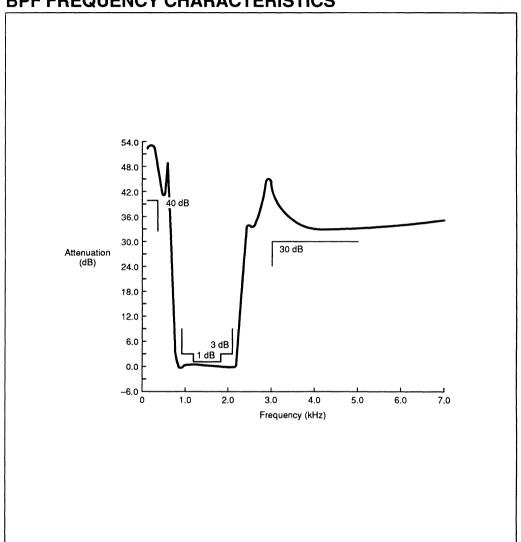

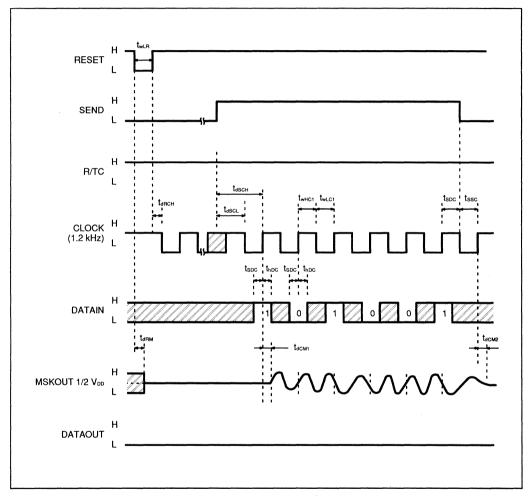

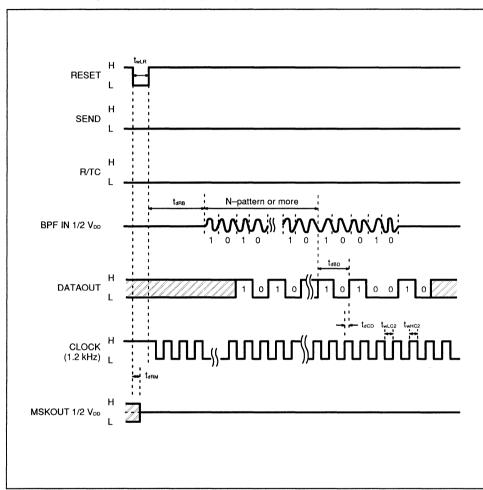

|         | MB86460A<br>MB87002                                                                                                                                       | Modern with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modern       6–25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | MB86460A<br>MB87002                                                                                                                                       | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25         Integrated Circuits       At a Glance         7–1       7–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | MB86460A<br>MB87002<br><b>7 – Telephor</b>                                                                                                                | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25         The Integrated Circuits       At a Glance       7–1         Compandor IC       7–3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | MB86460A<br>MB87002<br>7 – Telephor<br>MB3120                                                                                                             | Modem with Internal Voice-Band Filters       6-3         CMOS 1200 bps Minimum Shift Keying Modem       6-25         The Integrated Circuits       At a Glance         Compandor IC       7-3         Compandor IC       7-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | MB86460A<br>MB87002<br>7 – Telephor<br>MB3120<br>MB3121                                                                                                   | Modem with Internal Voice-Band Filters       6-3         CMOS 1200 bps Minimum Shift Keying Modem       6-25         The Integrated Circuits — At a Glance       7-1         Compandor IC       7-3         Compandor IC       7-15         Telephone Amplifier/Tone Ringer       7-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | MB86460A<br>MB87002<br>7 - Telephor<br>MB3120<br>MB3121<br>MB4513                                                                                         | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25         ne Integrated Circuits — At a Glance       7–1         Compandor IC       7–3         Compandor IC       7–15         Telephone Amplifier/Tone Ringer       7–19         Telecommunication Circuit       7–31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | MB86460A<br>MB87002<br>7 – Telephor<br>MB3120<br>MB3121<br>MB4513<br>MB4518<br>MB4752A                                                                    | Modem with Internal Voice-Band Filters       6-3         CMOS 1200 bps Minimum Shift Keying Modem       6-25         ne Integrated Circuits       At a Glance       7-1         Compandor IC       7-3       7-15         Telephone Amplifier/Tone Ringer       7-19       7-31         Subscriber Line Interface IC       7-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | MB86460A<br>MB87002<br>7 - Telephor<br>MB3120<br>MB3121<br>MB4513<br>MB4518<br>MB4752A<br>MB87007A                                                        | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25         ne Integrated Circuits — At a Glance       7–1         Compandor IC       7–3         Compandor IC       7–15         Telephone Amplifier/Tone Ringer       7–19         Telecommunication Circuit       7–31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | MB86460A<br>MB87002<br>7 - Telephor<br>MB3120<br>MB3121<br>MB4513<br>MB4518<br>MB4752A<br>MB87007A<br>87008A                                              | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25         The Integrated Circuits       — At a Glance       7–1         Compandor IC       7–3       7–15         Telephone Amplifier/Tone Ringer       7–19       7–31         Subscriber Line Interface IC       7–47       7–47         Dual Tone Multifrequency Pulse Dialer       7–57                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | MB86460A<br>MB87002<br>7 - Telephor<br>MB3120<br>MB3121<br>MB4513<br>MB4518<br>MB4752A<br>MB87007A<br>87008A<br>MB87009                                   | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25 <b>ne Integrated Circuits</b> — At a Glance       7–1         Compandor IC       7–3       7–15         Telephone Amplifier/Tone Ringer       7–19       7–31         Subscriber Line Interface IC       7–47       7–47         Dual Tone Multifrequency Pulse Dialer       7–57                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | MB86460A<br>MB87002<br>7 - Telephor<br>MB3120<br>MB3121<br>MB4513<br>MB4518<br>MB4752A<br>MB87007A<br>87008A<br>MB87009<br>MB87017B                       | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25 <b>ne Integrated Circuits</b> — At a Glance       7–1         Compandor IC       7–3       7–15         Telephone Amplifier/Tone Ringer       7–19       7–31         Subscriber Line Interface IC       7–47       7–47         Dual Tone Multifrequency Pulse Dialer       7–57       7–57         Dual Tone Multifrequency Receiver       7–111                                                                                                                                                                                                                                                                                                                                                                                |

|         | MB86460A<br>MB87002<br>7 - Telephor<br>MB3120<br>MB3121<br>MB4513<br>MB4518<br>MB4752A<br>MB87007A<br>87008A<br>MB87009<br>MB87017B<br>MB87029            | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25 <b>ne Integrated Circuits</b> — At a Glance       7–1         Compandor IC       7–3       7–15         Telephone Amplifier/Tone Ringer       7–19       7–13         Subscriber Line Interface IC       7–47       7–47         Dual Tone Multifrequency Pulse Dialer       7–57       7–57         Dual Tone Multifrequency Pulse Dialer       7–83       7–111         Dual Tone Multifrequency Pulse Dialer       7–111       7–11                                                                                                                                                                                                                                                                                            |

|         | MB86460A<br>MB87002<br>7 - Telephor<br>MB3120<br>MB3121<br>MB4513<br>MB4518<br>MB4752A<br>MB87007A<br>87008A<br>MB87009<br>MB87017B                       | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25 <b>ne Integrated Circuits</b> — At a Glance       7–1         Compandor IC       7–3       7–15         Telephone Amplifier/Tone Ringer       7–19       7–31         Subscriber Line Interface IC       7–47       7–47         Dual Tone Multifrequency Pulse Dialer       7–57       7–57         Dual Tone Multifrequency Receiver       7–111                                                                                                                                                                                                                                                                                                                                                                                |

| Section | MB86460A<br>MB87002<br>7 - Telephor<br>MB3120<br>MB3121<br>MB4513<br>MB4518<br>MB4752A<br>MB87007A<br>87008A<br>MB87009<br>MB87017B<br>MB87029<br>MB87057 | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25         The Integrated Circuits       — At a Glance       7–1         Compandor IC       7–3         Compandor IC       7–15         Telephone Amplifier/Tone Ringer       7–19         Telecommunication Circuit       7–31         Subscriber Line Interface IC       7–47         Dual Tone Multifrequency Pulse Dialer       7–57         Dual Tone Multifrequency Receiver       7–111         Dual Tone Multifrequency Pulse Dialer       7–123         Dual Tone Multifrequency Receiver       7–124         Dual Tone Multifrequency Receiver       7–112         Dual Tone Multifrequency Receiver       7–124         Dual Tone Multifrequency Receiver       7–149         Dual Tone Multifrequency Receiver       8–1 |

| Section | MB86460A<br>MB87002<br>7 - Telephor<br>MB3120<br>MB3121<br>MB4513<br>MB4518<br>MB4752A<br>MB87007A<br>87008A<br>MB87009<br>MB87017B<br>MB87029<br>MB87057 | Modem with Internal Voice-Band Filters       6–3         CMOS 1200 bps Minimum Shift Keying Modem       6–25 <b>ne Integrated Circuits</b> — At a Glance       7–1         Compandor IC       7–3         Compandor IC       7–15         Telephone Amplifier/Tone Ringer       7–19         Telecommunication Circuit       7–31         Subscriber Line Interface IC       7–47         Dual Tone Multifrequency Pulse Dialer       7–57         Dual Tone Multifrequency Pulse Dialer       7–111         Dual Tone Multifrequency Receiver       7–112         Dual Tone Multifrequency Pulse Dialer       7–123         Dual Tone Multifrequency Receiver       7–112         Dual Tone Multifrequency Receiver       7–123         Dual Tone Multifrequency Receiver       7–123         Dual Tone Multifrequency Receiver       7–149   |

### Contents and Alphanumeric Product List (Continued)

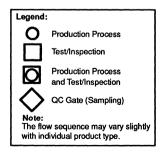

|              | Quality and Reliability — At a Glance                    |

|--------------|----------------------------------------------------------|

|              | ality Control at Fujitsu                                 |

| Section 10   | - Ordering Information — At a Glance                     |

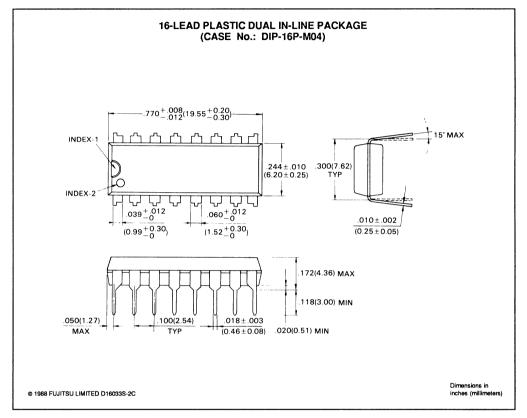

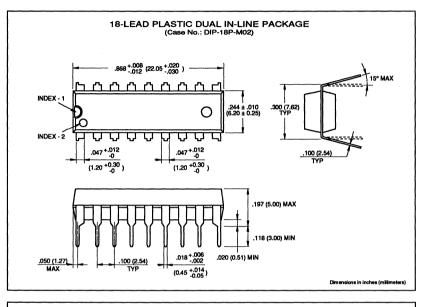

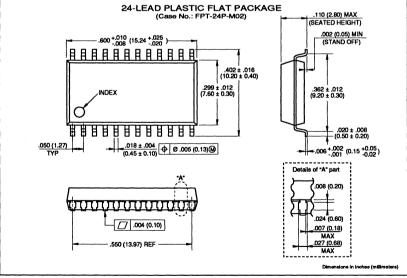

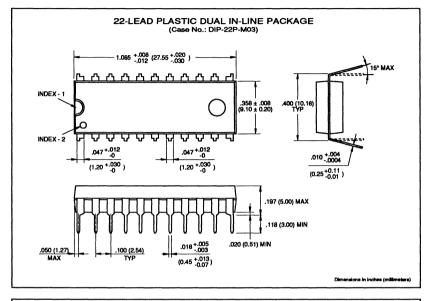

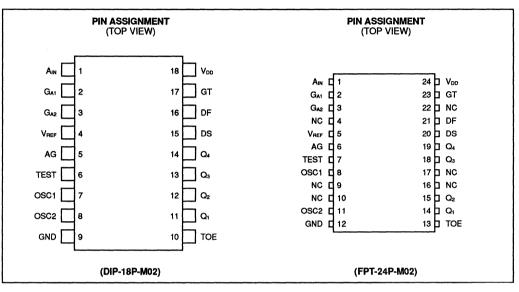

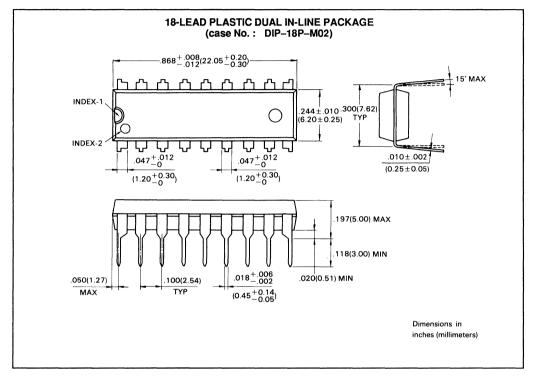

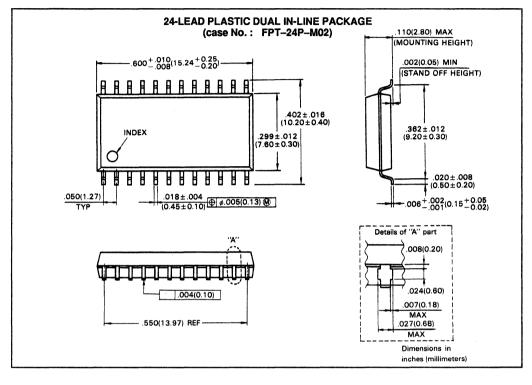

| IC           | Packages, Inserted Types                                 |

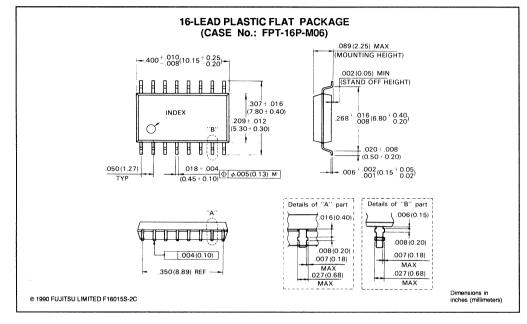

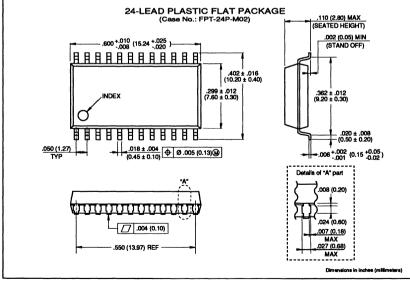

| IC           | Packages, Surface Mounted Types 10-4                     |

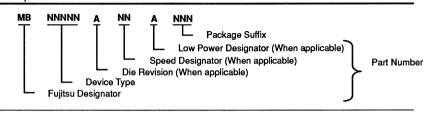

| Pa           | rt Number System                                         |

| Section 11 - | - Sales Information — At a Glance 11–1                   |

| Fu           | jitsu Worldwide Locations                                |

|              | Fujitsu Limited (Japan) 11-3                             |

|              | Fujitsu Microelectronics, Inc. (U.S.A.)                  |

|              | Fujitsu Electronic Devices Europe: 11-6                  |

|              | Fujitsu Mikroelektronik GmbH (West Germany)              |

|              | Fujitsu Microelectronics, Limited. (U.K.)                |

|              | Fujitsu Microelectronics, Italia S.R.L. (Italy)          |

|              | Fujitsu Microelectronics, Ireland, Ltd. (Ireland)        |

|              | Fujitsu Microelectronics Asia PTE Ltd. (Singapore) 11-8  |

| Int          | egrated Circuits Corporate Headquarters - Worldwide 11-9 |

| FN           | II Sales Offices for North and South America 11–10       |

| FN           | II Representatives – USA 11–11                           |

| FN           | II Representatives – Canada 11–14                        |

| FN           | II Representatives – Mexico 11–14                        |

| FN           | II Representatives – Puerto Rico 11–14                   |

| FN           | 11-15 Il Distributors - USA                              |

| FN           | II Distributors - Canada 11-17                           |

| FN           | IG, FML, FMIL Sales Offices for Europe 11–18             |

| FN           | IG, FML, FMIL Distributors – Europe 11–19                |

| FN           | AP Sales Offices for Asia, Australia and Oceania 11-20   |

| FN           | IAP Representatives – Asia and Australia 11–21           |

| FN           | IAP Distributors – Asia 11–21                            |

|              |                                                          |

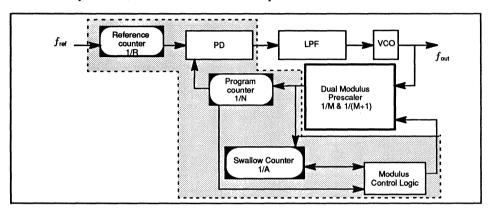

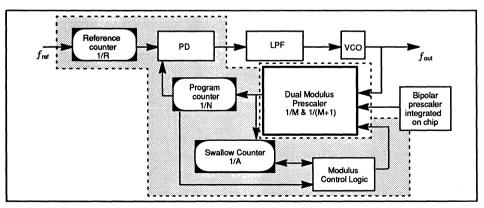

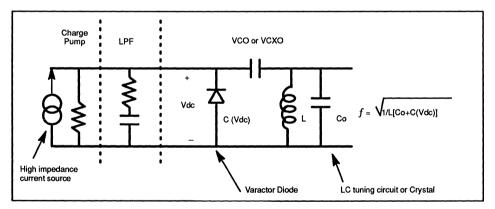

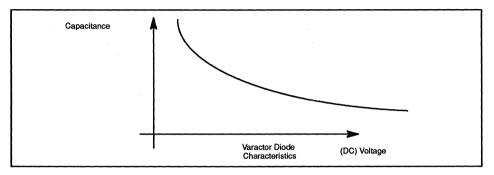

### Section 12 – Appendix – Design Information

Application Note: Prescalers and PLLs ...... 12-1

## **Contents and Alphanumeric Product List**

### **Telecommunications Products**

## Alphanumeric List of Fujitsu Part Numbers

| Device           | Page  |

|------------------|-------|

| F5 Series        | -     |

| M2 Series (D100) |       |

| M2 Series (D300) |       |

| M3 Series (D001) | 535   |

| M3 Series (D101) | 539   |

| MB467            | . 1–3 |

| MB501            | 111   |

| MB501L           | 111   |

| MB501LV          | 123   |

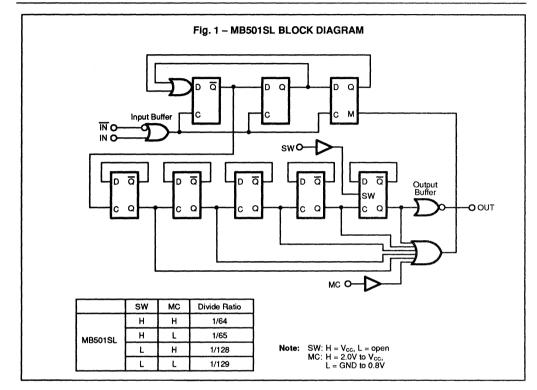

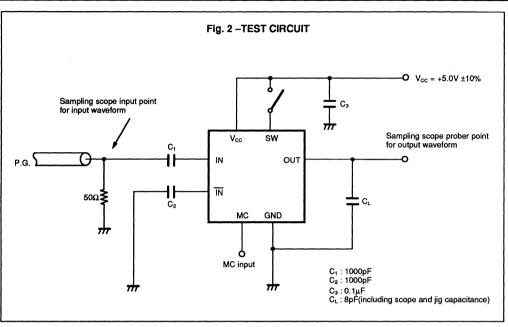

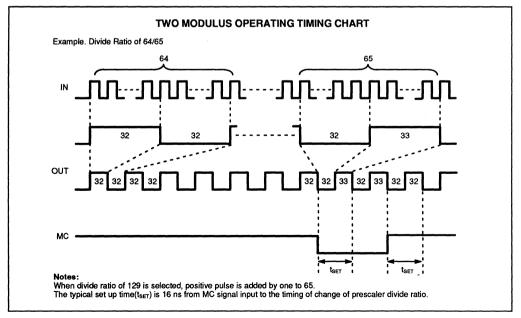

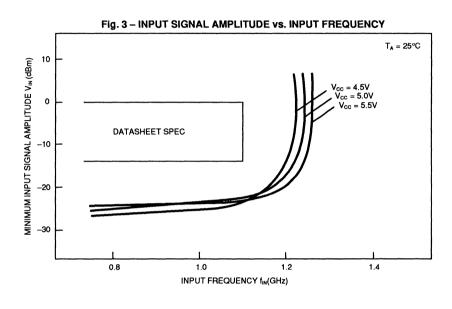

| MB501SL          | 133   |

| MB503            | 111   |

| MB504            | 111   |

| MB504L           | 1–11  |

| MB506            | 147   |

| MB507            | 151   |

| MB508            | 159   |

| MB509            | 167   |

| MB510            | 175   |

| MB511            | 183   |

| MB551            | . 4–3 |

| MB1501           | . 3–3 |

| MB1501H          | . 3–3 |

| MB1501L          | . 3–3 |

| MB1502           | 321   |

| MB1503           | 335   |

| MB1504           | 349   |

| MB1504H          | 349   |

| MB1504L          | 3-49  |

| MB1505           | 367   |

| MB1507           | 379   |

| Device     | Page  |

|------------|-------|

| MB1508     | 3–91  |

| MB1509 3   | -101  |

| MB1511 3   | -115  |

| MB1512 3   | 127   |

| MB1513 3   | -139  |

| MB1518 3   | -153  |

| MB1519 3   | -163  |

| MB3120     | 7–3   |

| MB3121     | 7–15  |

| MB4513     | 7–19  |

| MB4518     | 7–31  |

| MB4752A    | 7-47  |

| MB6021A    | 8–3   |

| MB6022A    | 8–3   |

| MB86460A   | 6–3   |

| MB87001A   | 2–3   |

| MB87002    | 6–25  |

| MB87006A   | 2–15  |

| MB87007A   | 7–57  |

| MB87008A   | 7–57  |

| MB87009    | 7–83  |

| MB87014A   | 2–27  |

| MB87017B 7 | 7–111 |

| MB87029 7  | -123  |

| MB87057 7  | '149  |

| MB87076    | 237   |

| MB87086A   | 2–51  |

| MB87087    | 2–61  |

| MB87090    | 2–73  |

## Introduction

Page Title

xiii

Fujitsu's Telecommunication Products

### **Fujitsu's Telecommunication Products**

#### Introduction

Fujitsu manufactures a wide range of integrated circuits that includes linear products, microprocessors, telecommunications circuits, ASICs, high-speed ECL logic, power components (consisting of both discrete transistors and transistor arrays), and both static and dynamic RAMs.

The telecommunication product line offers devices for use in a wide range of applications. These telecommunication products are manufactured to meet the high standard of quality and reliability that is found in all Fujitsu products.

#### Prescalers

Fujitsu offers a wide range of prescaler devices capable of satisfying the technical requirements of today's applications. Features such as the 200 MHz to 2.7 GHz frequency range, low power consumption, and a multitude of divide ratios are some of the advantages of Fujitsu's prescaler family.

#### Phase-Locked Loops (PLLs)

The Fujitsu family of PLLs offers a wide range of operating frequencies with low supply currents and voltages to meet design needs. The serial input capability of these devices is an outstanding feature of Fujitsu's PLLs.

#### Single-Chip PLLs/Prescalers

Fujitsu is one of only a few semiconductor manufacturers to offer single-chip PLL/Prescaler devices. Fujitsu is the only manufacturer with a BiCMOS version that combines high speed and low power consumption in a single chip. With the increasing emphasis on board space reduction (to improve cost), reliability, and overall product size, these single-chip devices provide solutions for designers.

#### Single-Chip VCOs/Prescalers

Fujitsu is the only semiconductor manufacturer with a single-chip VCO/Prescaler family of products. With the increasing emphasis on overall product size reduction and added on-chip functionality, this new family of devices provides the needed design solution.

Continued on next page

### **Fujitsu's Telecommunication Devices**

#### **Piezoelectric Devices**

Fujitsu's lithium tantalate peizoelectric bandpass SAW filters provide sharp roll-off characteristics and excellent stability over temperature in a tiny 5 mm x 5 mm surface mount package. Standard frequencies are available for AMPS, NTACS, NMT, and ETACS transmit and receive frequencies. This family of devices also includes a series of voltage controlled oscillators.

#### **Cordless Telephone Integrated Circuits**

Fujitsu's family of cordless telephone ICs offers low power consumption, ideal for application of this type. This family of products consists of minimum-shift keying modems for data transfer applications.

#### **Telephone Integrated Circuits**

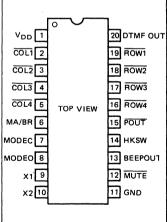

Fujitsu offers a complete family of telephone ICs as an application-specific product line. These devices are capable of performing advanced telephone functions such as SLIC, speech transmission/reception, DTMF, on-hook dialing, last number repeat, tone amplification, and companding functions.

#### Coder/Decoders (CODECs)

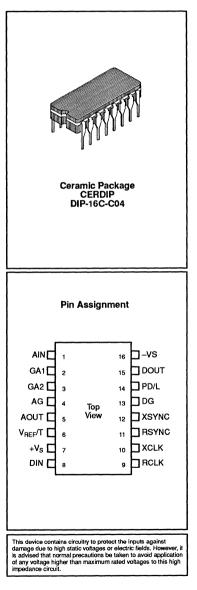

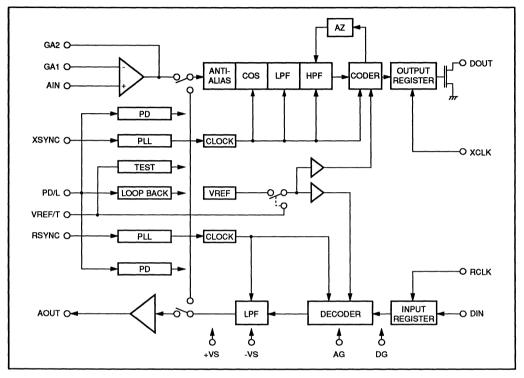

The Fujitsu family of CODECs consists of the MB6020 series. All devices conform to CCITT and AT&T specifications.

—— Section 1

1

|      |          | Maximum   | Supp    |     | Divide                          | Packa |         |          |

|------|----------|-----------|---------|-----|---------------------------------|-------|---------|----------|

| Page | Device   | Frequency | lcc     | Vcc | Ratio                           | Optio | 18      |          |

| 13   | MB467    | 200 MHz   | 6 mA    | 5 V | 10/20                           | 8-pin | Plastic | DIP, FPT |

| 111  | MB501    | 1.0 GHz   | 30 mA   | 5 V | 64/65,<br>128/129               | 8-pin | Plastic | DIP, FPT |

|      | 501L     | 1.1 GHz   | 10 mA   | 5 V | 64/65,<br>128/129               |       |         |          |

|      | 503      | 200 MHz   | 8 mA    | 5 V | 16/17,<br>32/33                 |       |         |          |

|      | 504      | 520 MHz   | 10 mA   | 5 V | 32/33,<br>64/65,                |       |         |          |

|      | 504L     | 520 MHz   | 5 mA    | 5 V | 32/33,<br>64/65                 |       |         |          |

| 123  | MB501LV  | 1.1 GHz   | 12 mA   | 3 V | 64/65,<br>128/129               | 8-pin | Plastic | DIP, FPT |

|      | 504LV    | 520 MHz   | 6 mA    | 3 V | 32/33,<br>64/65                 |       |         |          |

| 133  | MB501SL  | 1.1 GHz   | 5 mA    | 5 V | 64/65,<br>128/129               | 8-pin | Plastic | DIP, FPT |

| 143  | MB505-16 | 1.6 GHz   | 9 mA    | 5 V | 128/256                         | 8-pin | Plastic | DIP, FPT |

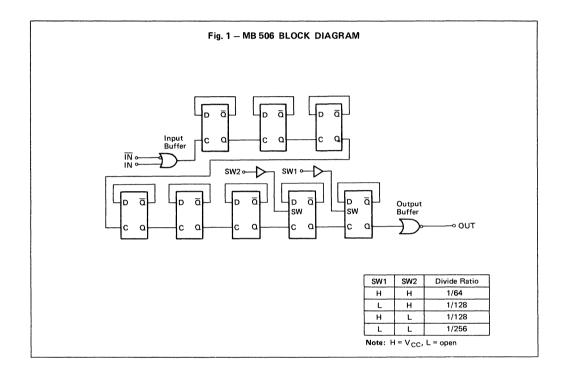

| 1-47 | MB506    | 2.4 GHz   | 18 mA   | 5 V | 64/128/256                      | 8-pin | Plastic | DIP, FPT |

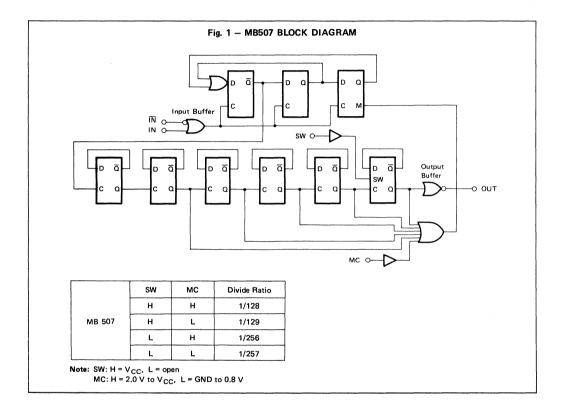

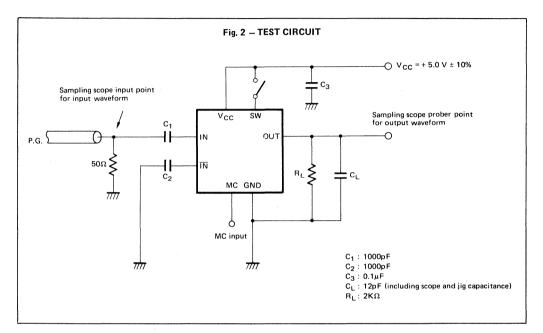

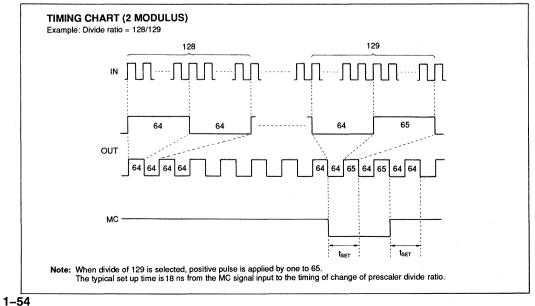

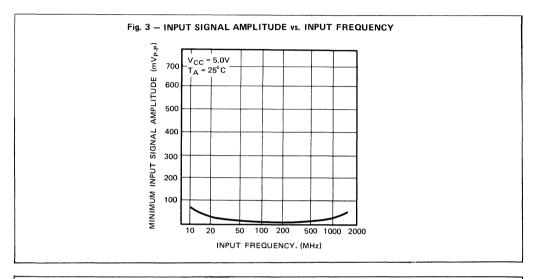

| 151  | MB507    | 1.6 GHz   | 18 mA   | 5 V | 128/129,<br>256/257             | 8-pin | Plastic | DIP, FPT |

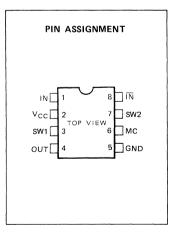

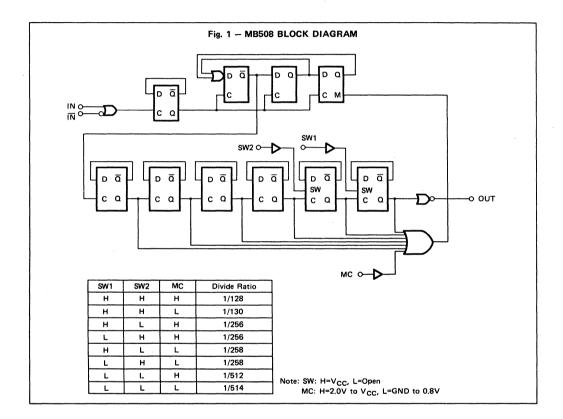

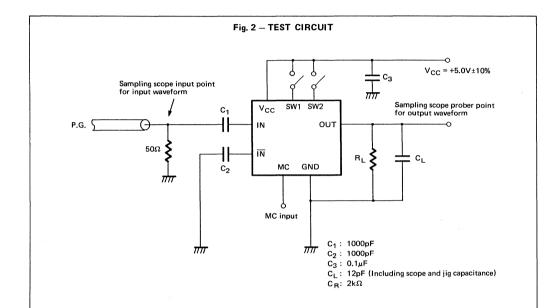

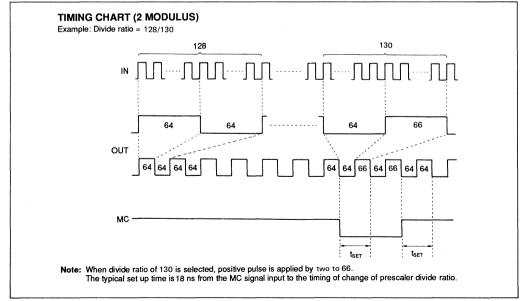

| 1–59 | MB508    | 2.3 GHz   | 24 mA   | 5 V | 128/130,<br>256/258,<br>512/514 | 8-pin | Plastic | DIP, FPT |

| 1–67 | MB509    | 1.1 GHz   | 11.6 mA | 5 V | 64/65,<br>128/129               | 8-pin | Plastic | DIP, FPT |

| 1–75 | MB510    | 2.7 GHz   | 10 mA   | 5 V | 128/144,<br>256/272             | 8-pin | Plastic | FPT      |

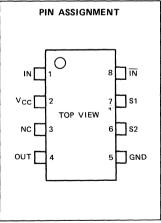

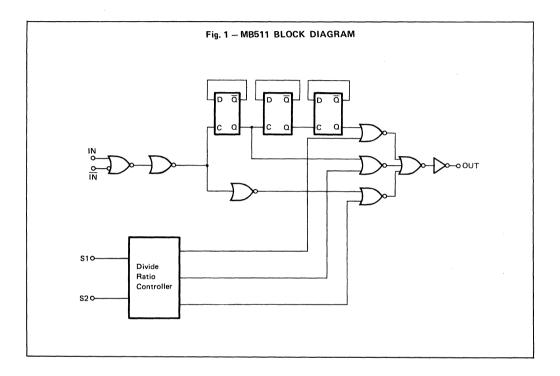

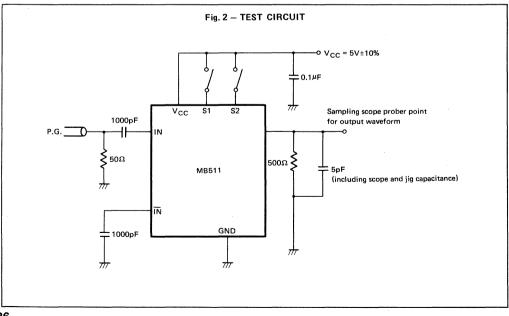

| 1-83 | MB511    | 1.0 GHz   | 23 mA   | 5 V | 1, 2, 8                         | 8-pin | Plastic | DIP, FPT |

## **Prescalers** — At a Glance

1-1

October 1989 Edition 2.0

DATA SHEET =

# *MB467 LOW POWER PRESCALER*

#### 200MHz, LOW POWER PRESCALER

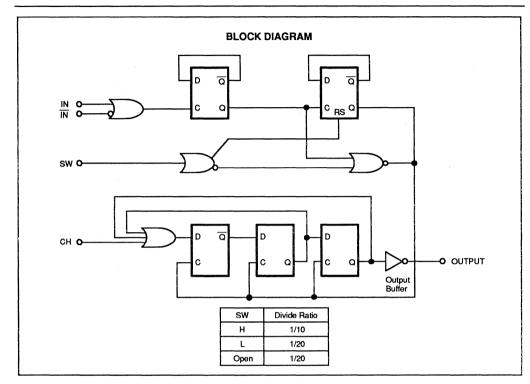

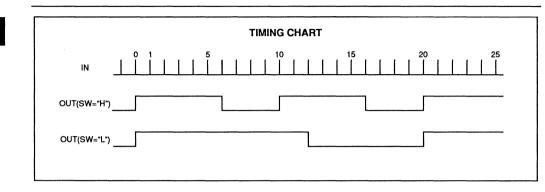

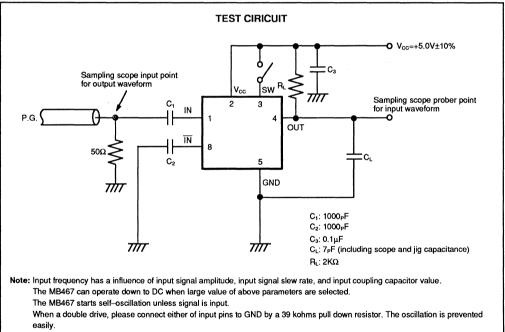

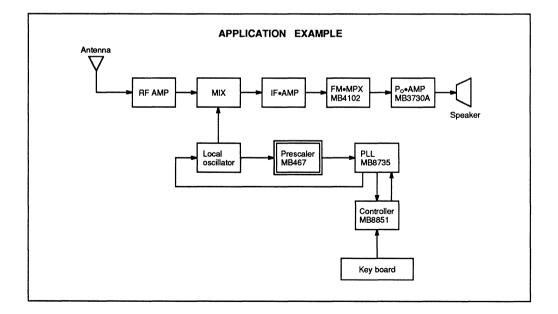

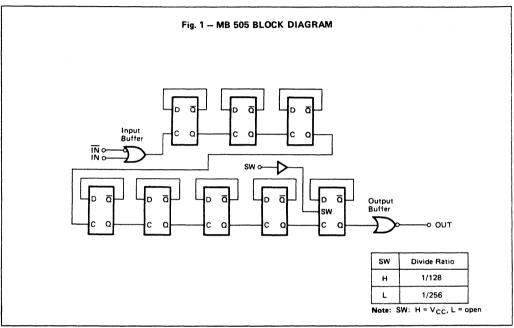

The Fujitsu MB467 is a prescaler, which is used in Phase Locked Loop (PLL) frequency synthesizer. The MB467 will divide by 10 when SW pin is high (Vcc level) and by 20 when SW pin is low (open or 1/2Vcc level). The output is an open collector output to drive TTL or CMOS logic circuit.

- Operating Frequency: 200MHz max.

- Low Power Comsumption: 30mW typ.

- Low Level Input Voltage: V<sub>IN</sub>≥150mV<sub>P-P</sub>

- Wide Operation Temperature: TA=-30°C to +85°C

- Power Supply Voltage: V<sub>cc</sub>=+5V±10%

- Interface

- Input: Capacitor coupling due to internal biased input Output: Open collector output

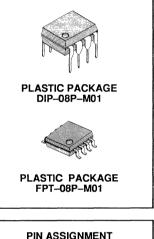

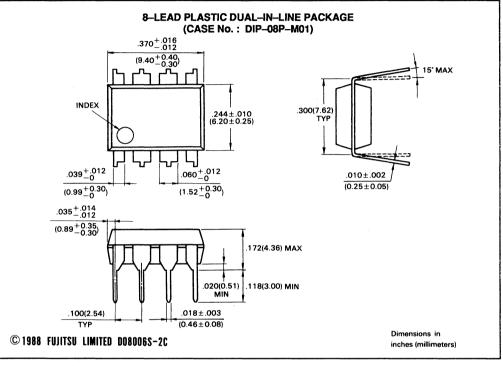

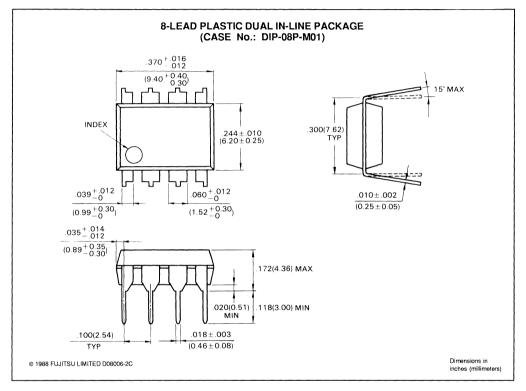

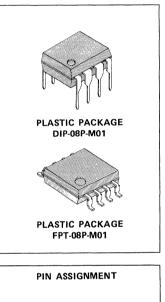

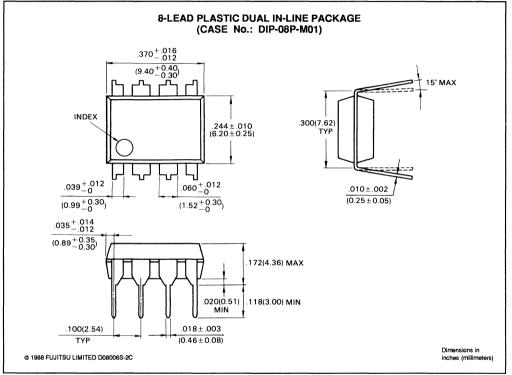

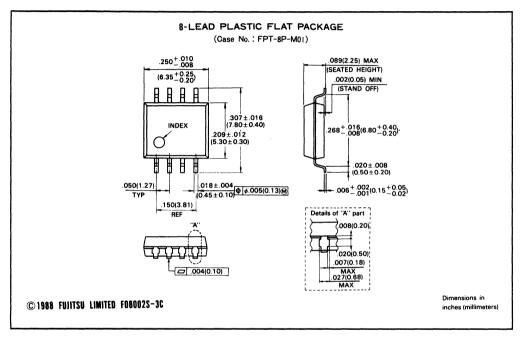

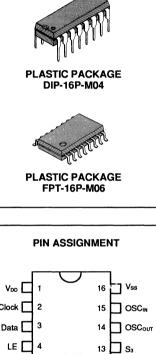

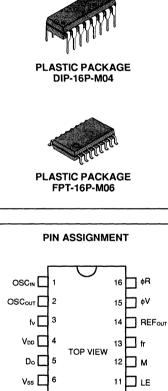

- Plastic 8--pin Standard Dual-In-Line Package: (Suffix: -P)

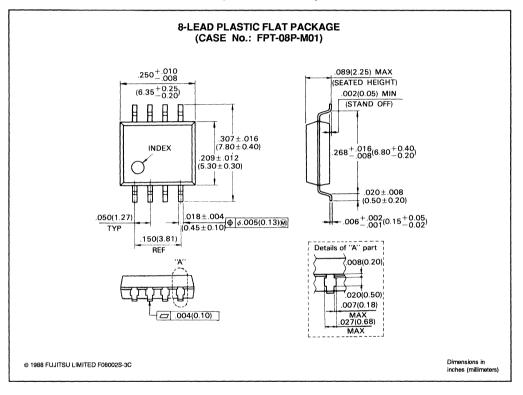

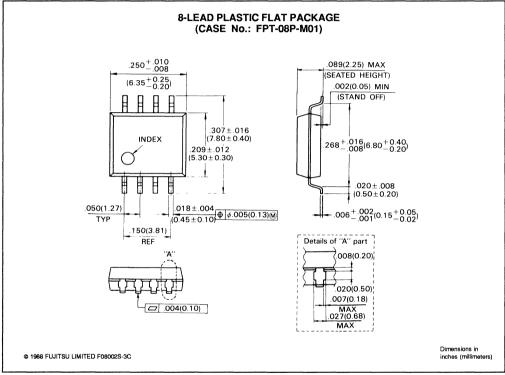

- Plastic 8-pin Standard Flat Package: (Suffix: --PF)

FU

#### **ABSOLUTE MAXIMUM RATINGS (See NOTE)**

| Rating               | Symbol           | Value                   | Unit |

|----------------------|------------------|-------------------------|------|

| Supply Voltage       | Vcc              | -0.5 to +7.0            | v    |

| Input Voltage        | V <sub>IN</sub>  | -0.5 to V <sub>cc</sub> | v    |

| Output Current       | l <sub>o</sub>   | 0 to +5                 | mA   |

| Junction Temperature | Tj               | +125                    | °C   |

| Storage Temperature  | T <sub>stg</sub> | -55 to +150             | °C   |

NOTE: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

**SU**

Copyright<sup>®</sup> 1969 by FUJITSU LIMITED

### MB467

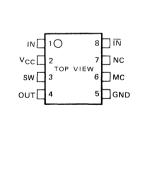

## **PIN DESCRIPTION**

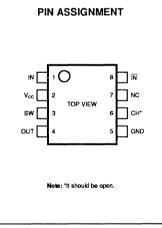

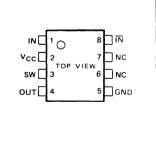

| Pin Number | Symbol          | Function                                            |

|------------|-----------------|-----------------------------------------------------|

| 1          | IN              | Input                                               |

| 2          | V <sub>cc</sub> | DC Supply Voltage Input                             |

| 3          | sw              | Divide Ratio Control Input (See Divide Ratio Table) |

| 4          | OUT             | Output                                              |

| 5          | GND             | Ground                                              |

| 6          | СН              | Check Input For Outgoing Test. It should be open.   |

| 7          | NC              | Non Connection                                      |

| 8          | ĪN              | Complementary Input                                 |

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter            | Symbol | Value |     |     | Unit |

|----------------------|--------|-------|-----|-----|------|

|                      |        | Min   | Тур | Max | Unit |

| Power Supply Voltage | Vcc    | 4.5   | 5.0 | 5.5 | v    |

| Ambient Temperature  | TA     | 30    |     | +85 | °C   |

| Load Capacitance     | CL     |       |     | 7   | pF   |

## **ELECTRICAL CHARACTERISTICS**

(Vcc=+5V±10%, Ta=-30 to +85°C)

| Parameter                     | Symbol Conditions | Oraditions                                          | Value |     |      | Unit              |

|-------------------------------|-------------------|-----------------------------------------------------|-------|-----|------|-------------------|

|                               |                   | Conditions                                          | Min   | Тур | Max  | Unit              |

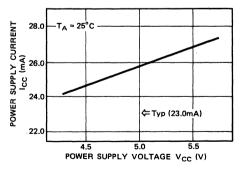

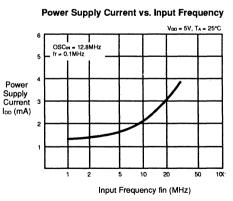

| Power Supply Current          | lcc               | V <sub>cc</sub> =5.0V,<br>T <sub>A</sub> =25°C      |       | 6   | 10   | mA                |

| High-level Output Voltage     | V <sub>он</sub>   | With $2k\Omega$ pull-up resistor to $V_{cc}$        | 4.0   |     |      | v                 |

| Low-level Output Voltage      | Vol               | With $2k\Omega$ pull-up resistor to $V_{cc}$        |       |     | 0.4  | v                 |

| Input Frequency               | f <sub>in</sub>   | VI <sub>N</sub> : 150mV <sub>P-P</sub><br>sine wave | 10    |     | 200  | MHz               |

| Input Signal Amplitude for IN | VIN               |                                                     | 150   |     | 2000 | mV <sub>P→P</sub> |

When a single drive, please connect a pull down resistor to unused pin.

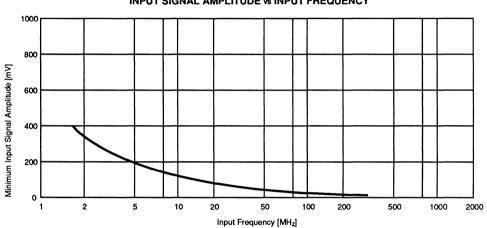

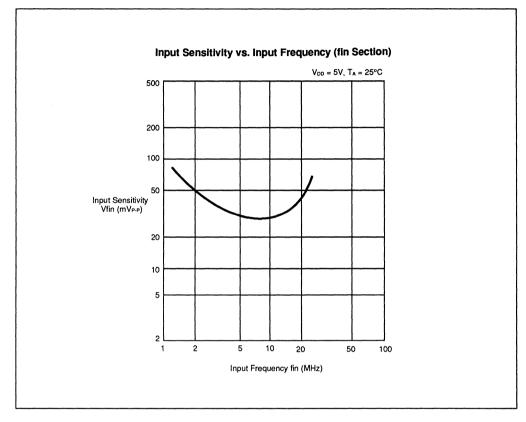

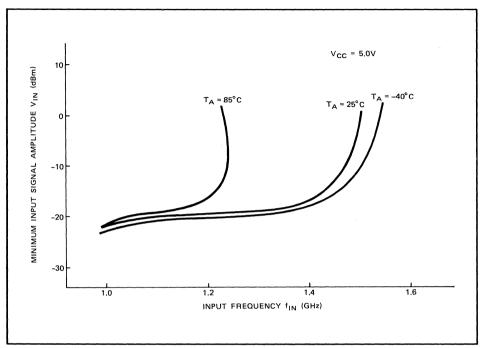

## **TYPICAL CHARACTERISTICS CURVE**

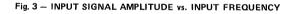

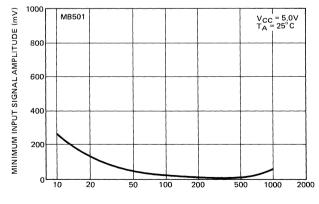

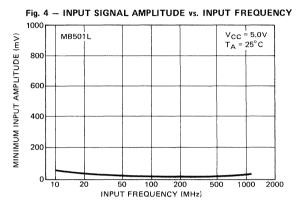

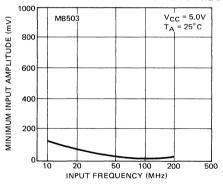

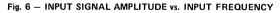

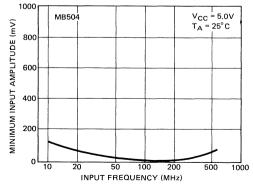

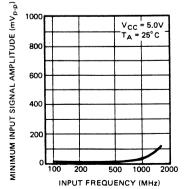

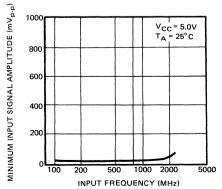

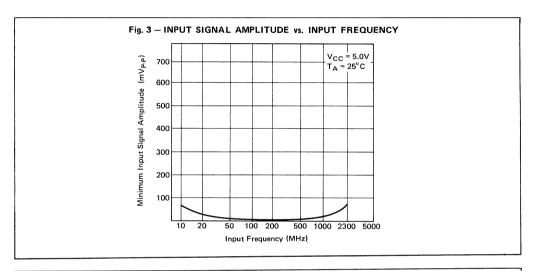

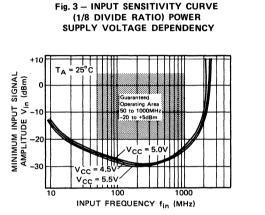

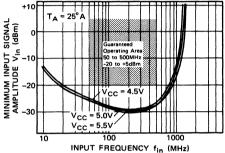

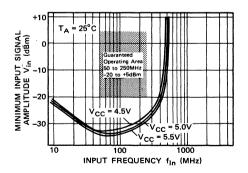

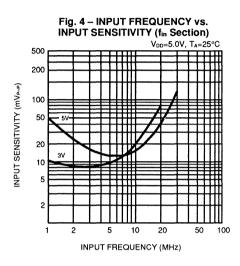

#### INPUT SIGNAL AMPLITUDE vs INPUT FREQUENCY

### MB467

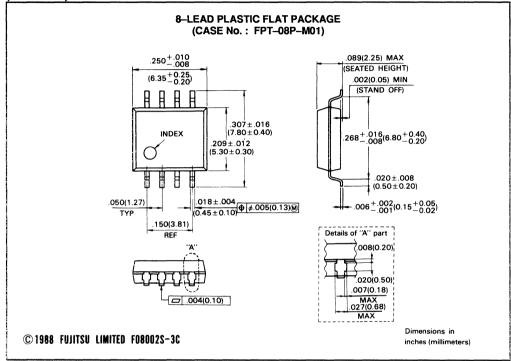

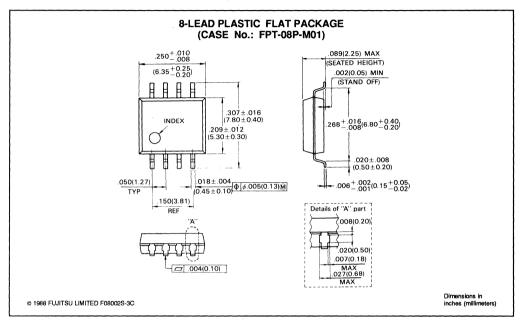

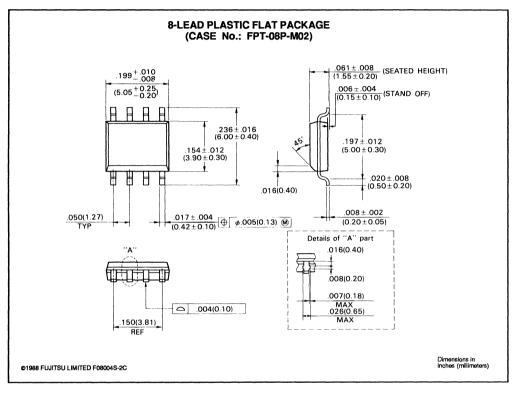

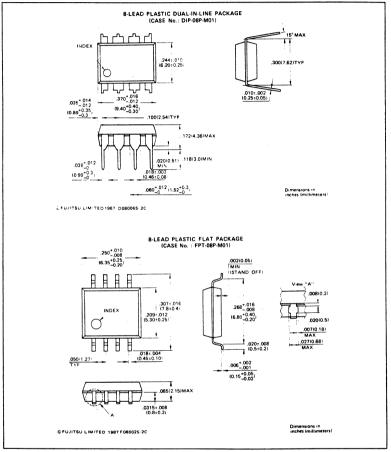

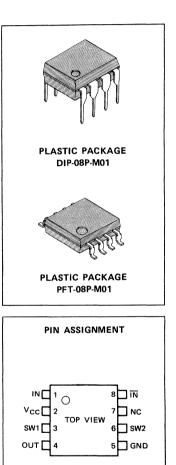

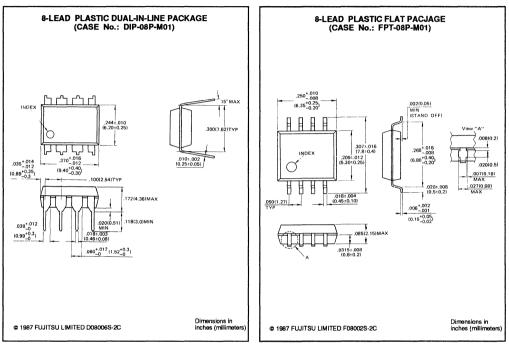

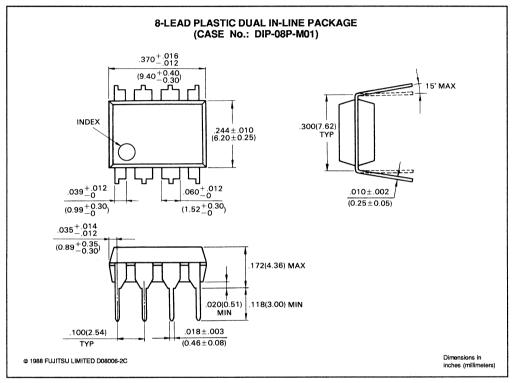

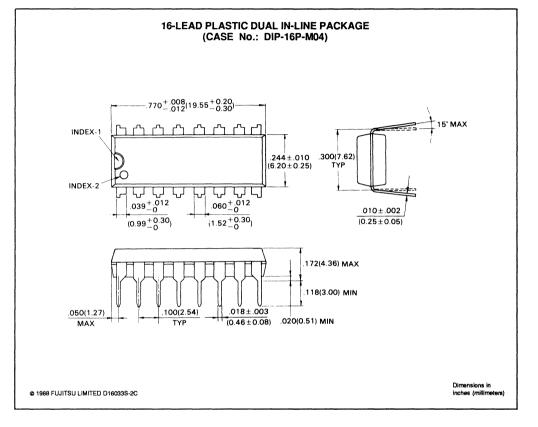

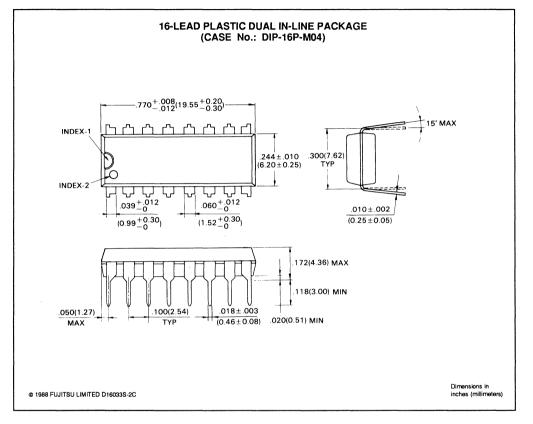

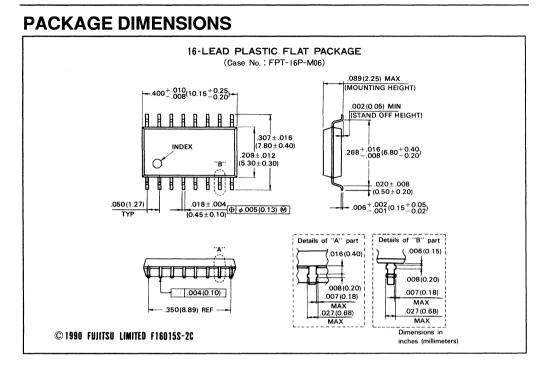

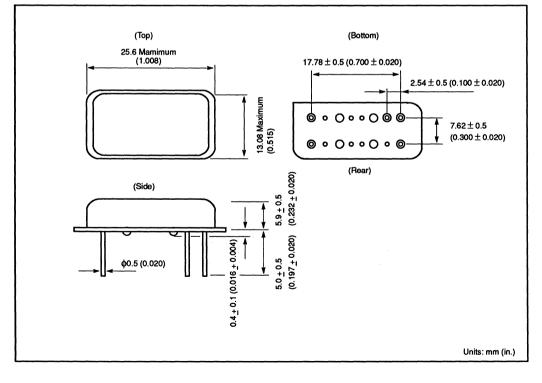

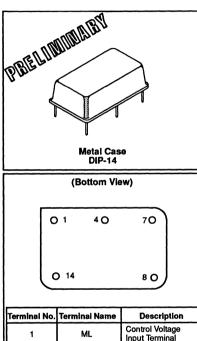

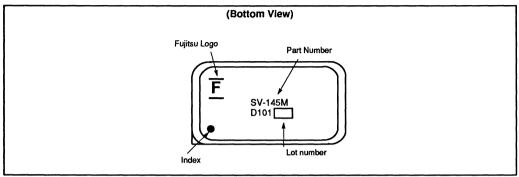

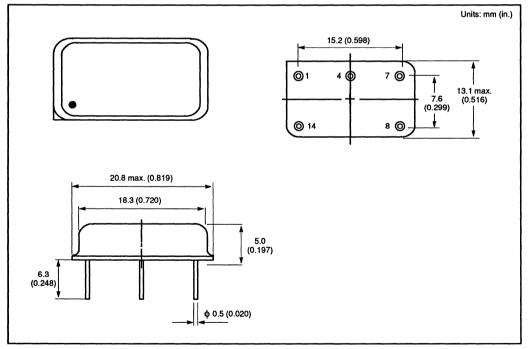

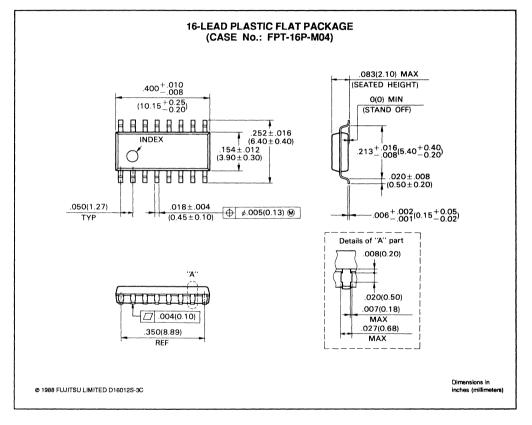

## **PACKAGE DIMENSIONS**

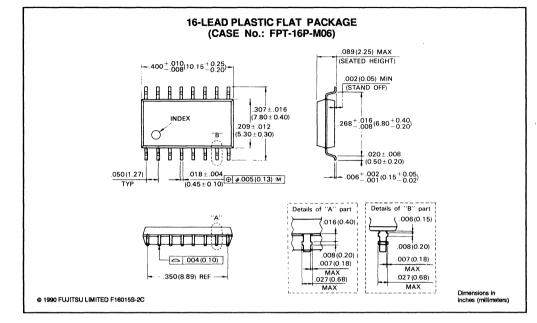

## **PACKAGE DIMENSIONS**

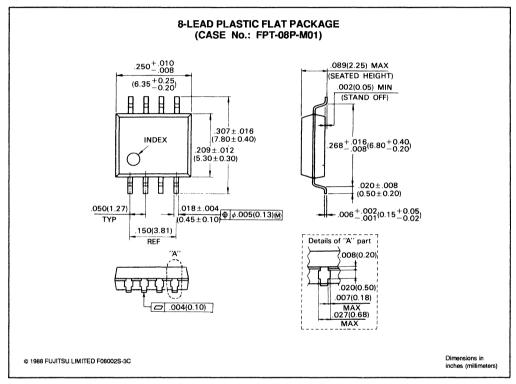

(Suffix: --PF)

**MB467**

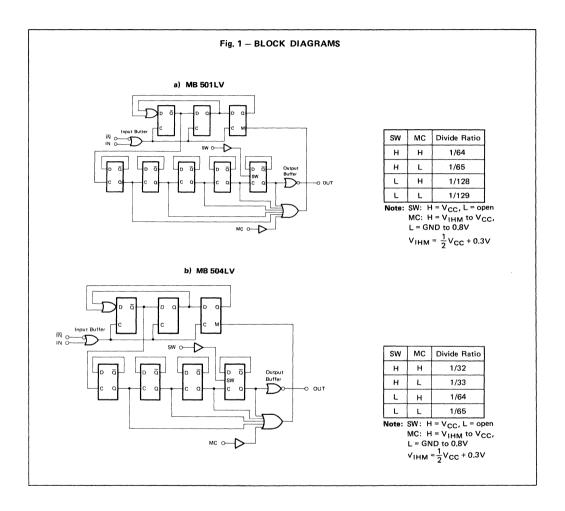

# MB501/501L/503/504/504L TWO MODULUS PRESCALERS

DATA SHEET

#### TWO MODULUS PRESCALERS

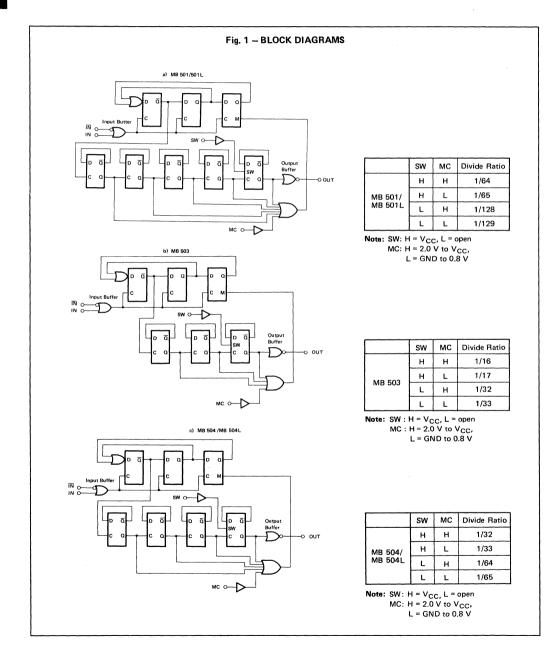

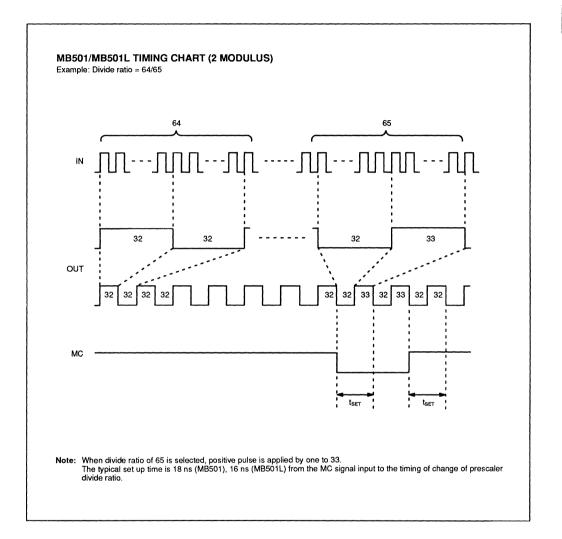

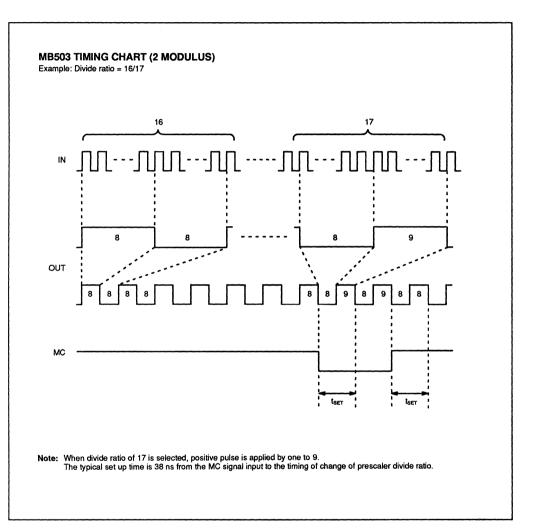

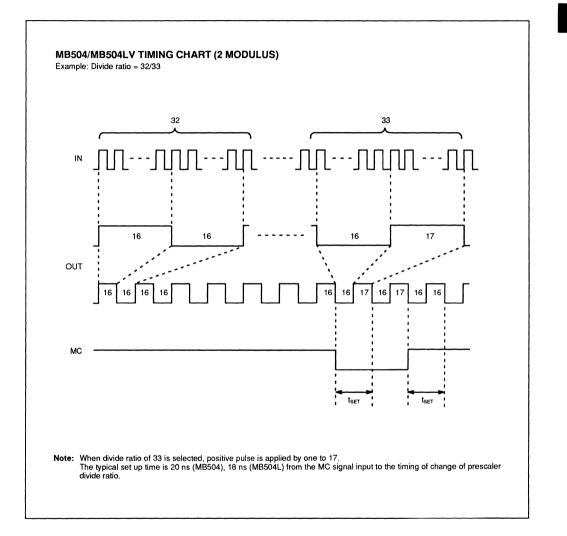

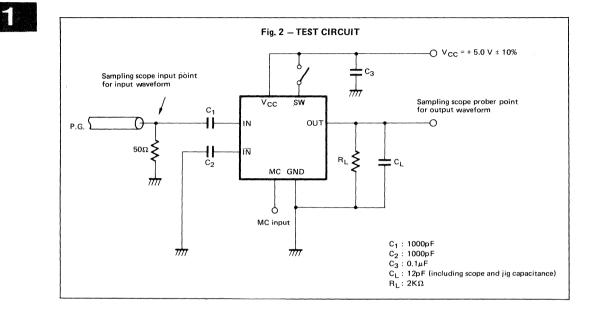

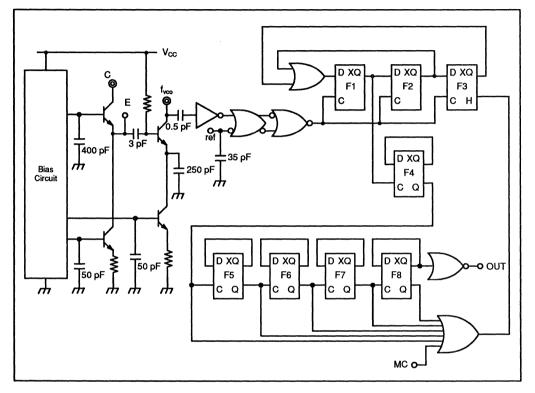

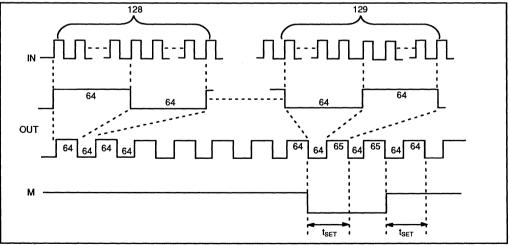

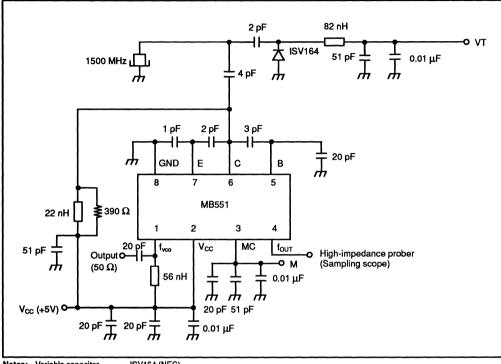

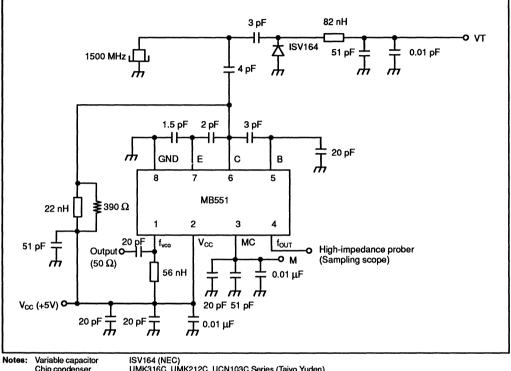

The Fujitsu MB 501/503/504 are two modulus prescalers, which are used in Phase Locked Loop (PLL) frequency synthesizer and will divide the input frequency by the modulus of 64/65 or 128/129, 16/17 or 32/33, and 32/33 or 64/65 respectively. MB 501L/MB 504L is the low-power version of MB 501/MB 504; it will perform exactly the same function as MB 501/MB 504 but with much lower power dissipation.

The output is 1.6 V peak to peak on ECL level.

- High Operating Frequency, Low Power Operation.

- 1.0 GHz at 150 mW typ. (MB 501)

- 1.1 GHz at 50 mW typ. (MB 501L)

- 200 MHz at 40 mW typ. (MB 503)

- 520 MHz at 50 mW typ. (MB 504)

- 520 MHz at 25 mW typ. (MB 504L)

- Pulse Swallow Function

- Wide Operation Temperature  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$

- Stable Output Amplitude V<sub>OUT</sub> = 1.6 V<sub>P-P</sub>

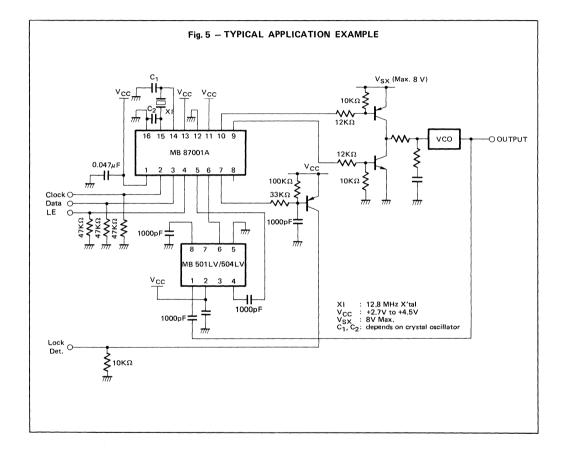

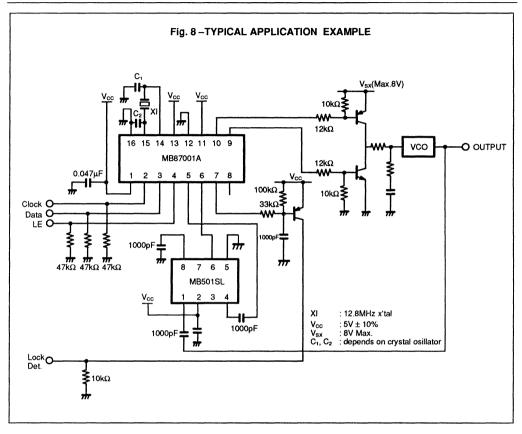

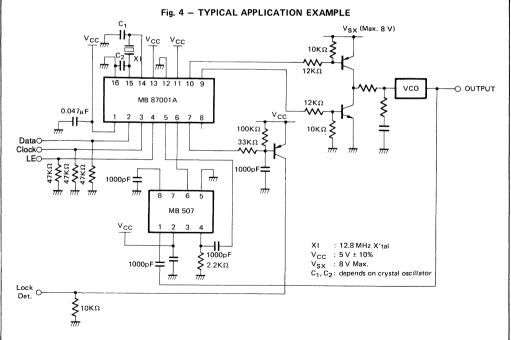

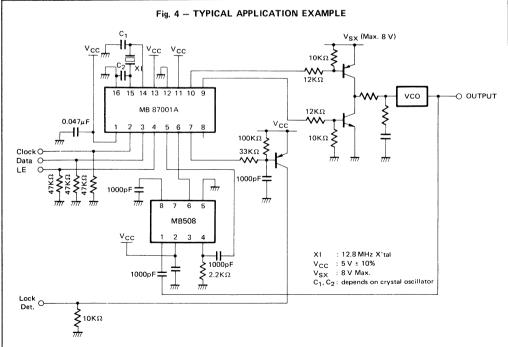

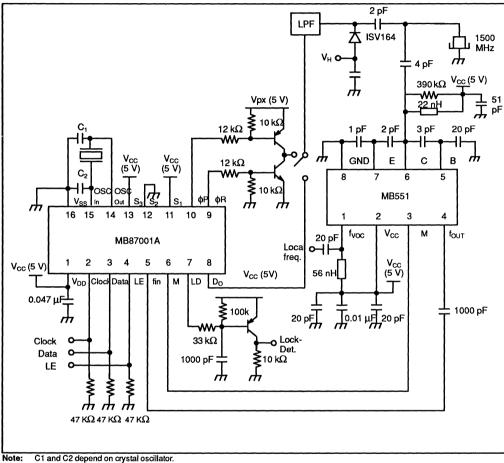

- Complete PLL synthesizer circuit with the Fujitsu MB 87001A, PLL synthesizer IC

- Plastic 8-pin Standard Dual-In-Line Package or space saving Flat Package

#### ABSOLUTE MAXIMUM RATINGS (See NOTE)

| Rating              |                  | Value            | Unit |

|---------------------|------------------|------------------|------|

| Supply Voltage      | V <sub>cc</sub>  | -0.5 to +7.0     | v    |

| Input Voltage       | V <sub>IN</sub>  | –0.5 to $V_{CC}$ | V    |

| Output Current      | Vo               | 10               | mA   |

| Ambient Temperature | TA               | -40 to +85       | °c   |

| Storage Temperature | T <sub>STG</sub> | -55 to + 125     | °c   |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

| MB501  |

|--------|

| MB501L |

| MB503  |

| MB504  |

| MB504L |

F

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter           | Sumbal          |     | Unit |     |      |  |

|---------------------|-----------------|-----|------|-----|------|--|

| Fatameter           | Symbol          | Min | Тур  | Мах | Unit |  |

| Supply Voltage      | V <sub>cc</sub> | 4.5 | 5.0  | 5.5 | v    |  |

| Output Current      | ۱ <sub>o</sub>  |     | 1.2  |     | mA   |  |

| Ambient Temperature | T <sub>A</sub>  | -40 |      | +85 | °C   |  |

| Load Capacitance    | CL              |     |      | 12  | pF   |  |

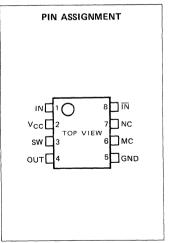

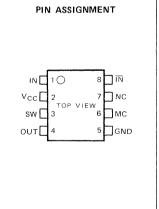

## **PIN DESCRIPTION**

| Pin Number | Symbol          | Function                                            |

|------------|-----------------|-----------------------------------------------------|

| 1          | IN              | Input                                               |

| 2          | V <sub>cc</sub> | DC Supply Voltage                                   |

| 3          | SW              | Divide Ratio Control Input (See Divide Ratio Table) |

| 4          | ουτ             | Output                                              |

| 5          | GND             | Ground                                              |

| 6          | МС              | Modulus Control Input (See Divide Ratio Table)      |

| 7          | NC              | Non Connection                                      |

| 8          | ĪŇ              | Complementary Input                                 |

| MB501         |   |

|---------------|---|

| <b>MB501L</b> |   |

| MB503         |   |

| MB504         |   |

| MB504L        | • |

# ELECTRICAL CHARACTERISTICS (Recommended Operating Conditions unless otherwise noted)

| Parameter                        |        | Symbol              | Conditions             | Value                |                 |                      |                  |

|----------------------------------|--------|---------------------|------------------------|----------------------|-----------------|----------------------|------------------|

|                                  |        |                     |                        | Min                  | Тур             | Max                  | Unit             |

| Power Supply Current             | MB501  | I <sub>cc</sub>     | I/O pins are<br>open   |                      | 30              | 42*                  | mA               |

|                                  | MB501L |                     |                        |                      | 10              | 14*                  | mA               |

|                                  | MB503  |                     |                        |                      | 8               | 12*                  | mA               |

|                                  | MB504  |                     |                        |                      | 10              | 14*                  | mA               |

|                                  | MB504L |                     |                        |                      | 5               | 7*                   | mA               |

| Output Amplitude                 |        | Vo                  |                        | 1.0                  | 1.6             |                      | V <sub>P-P</sub> |

|                                  | MB501  |                     |                        | 10                   |                 | 1000                 | MHz              |

|                                  | MB501L |                     | With input             | 10                   |                 | 1100                 | MHz              |

| Input Frequency                  | MB503  | f <sub>IN</sub>     | coupling<br>capacitor  | 10                   |                 | 200                  | MHz              |

|                                  | MB504  |                     | 1000pF                 | 10                   |                 | 520                  | MHz              |

|                                  | MB504L | 1                   |                        | 10                   |                 | 520                  | MHz              |

|                                  | MB501  |                     |                        | -4                   |                 | 5.5                  | dBm              |

|                                  | MB501L |                     |                        | -4                   |                 | 5.5                  | dBm              |

| Input Signal Amplitude<br>for IN | MB503  | V <sub>IN</sub>     |                        | -12                  |                 | 10                   | dBm              |

|                                  | MB504  |                     |                        | -12                  | <u></u>         | 10                   | dBm              |

|                                  | MB504L |                     |                        | -12                  |                 | 10                   | dBm              |

| High Level Input Voltage for MC  |        | V <sub>інм</sub>    |                        | 2.0                  |                 |                      | v                |