# INTEGRATED CIRCUITS

# PSD3XX Programmable Microcontroller Peripherals

# **Philips Semiconductors**

Philips Semiconductors and North American Philips Corporation reserve the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Philips Semiconductors and North American Philips Corporation Products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors and North American Philips Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and North American Philips Corporation customers using or selling Philips Semiconductors and North American Philips Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and North American Philips Corporation products for use or sale.

© Copyright North American Philips Corporation, 1993

# Preface

#### PSD3XX Programmable Microcontroller Peripherals

#### PSDX3XX Programmable Microcontroller Peripherals from Philips Semiconductors

Philips Semiconductors supplies a wide range of microcontrollers peripherals for use with all of the popular microcontroller architectures. By offering a wide range of peripheral products, we can meet a broad range of specific or unique application requirements. In addition, Philips Semiconductors supplies a full line of microcontrollers based on the 80C49 and 80C51 architectures. With over 50 derivatives of the 80C51 microcontroller available, Philips Semiconductors has the broadest offering on the market.

This data handbook covers the PSD3XX products. These programmable microcontroller peripherals contain 32K to 128K bytes of EPROM (UV erasable or One Time Programmable) external program memory, 2K bytes of SRAM external data memory, and memory paging and port reconstruction logic. Philips Semiconductors' PSD3XX products interface directly to our 80C51 microcontrollers without need of any other parts. This allows the memory of the microcontroller to be increased with the addition of only one part and without the loss of the functionality of the microcontroller ports used in the interface.

Philips Semiconductors supplies a wide range of microcontrollers based on mainstream architectures, spanning 8-, 16-, and 32-bit product lines. All of our microcontrollers are based on mainstream architectures to allow our customers to take advantage of existing software and a vast array of third-party support.

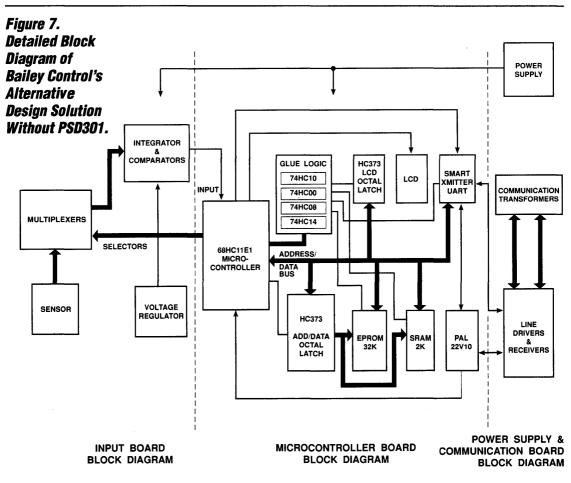

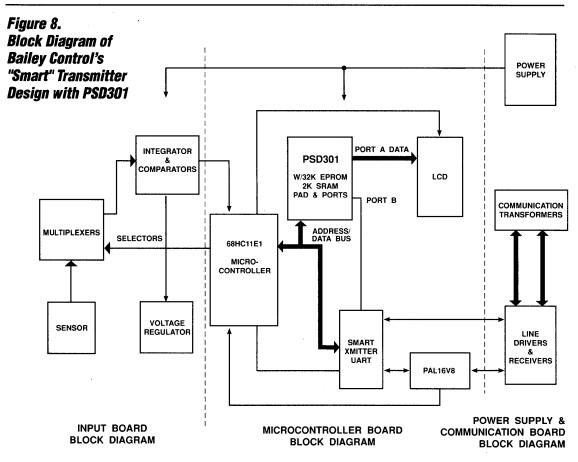

Philips Semiconductors' 8-bit microcontrollers are based on the popular 80C51 and 80C49 architectures. We offer most of the Industry Standard products as well as a large selection of powerful derivatives. Many of the derivatives have an I<sup>2</sup>C serial interface that allows them to be easily connected to over 70 other parts: this increases their capabilities even further. The 80C51 products are covered in the *80C51-Based 8-Bit Microcontrollers* data handbook (IC20) and the I<sup>2</sup>C parts that are most commonly used with microcontrollers are covered in the *1<sup>2</sup>C* Peripherals for Microcontrollers data handbook. Philips Semiconductors offers the most 80C51 derivatives in the world.

Philips Semiconductors' 16-bit microcontroller family is based on the powerful 68000 architecture. While these are called 16-bit microcontrollers, the 68000 CPU core architecture is 32-bit. This offers the user a great deal more processing power, when the need arises in a design to move from an 8-bit to a 16-bit microcontroller. Philips Semiconductors' 16-bit microcontrollers are software compatible with existing 68000 code. As with our popular 8-bit microcontrollers, EPROM and OTP versions of our 16-bit products are available. The 16-bit microcontrollers are covered in a separate data handbook, the IC21, 68000-Based 16-bit Microcontrollers.

Philips Semiconductors is developing a family of 32-bit microcontrollers based on the SPARC RISC architecture. This family of microcontrollers will offer the ultimate in processing power for those applications that are computation-intensive in a embedded control environment.

Philips Semiconductors offers uncompromising quality, service, and support with all of our microcontroller and microcontroller peripheral products. For a complete family and the best in microcontroller products, look to Philips Semiconductors.

Philips Semiconductors - Microcontroller Products

# **Product Status**

#### PSD3XX Programmable Microcontroller Peripherals

| DEFINITIONS                                            |                        |                                                                                                                                                                                                                                                                     |  |  |

|--------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data Sheet Product Status Definition<br>Identification |                        |                                                                                                                                                                                                                                                                     |  |  |

| <b>Objective Specification</b>                         | Formative or in Design | This data sheet contains the design target or goal specifications for<br>product development. Specifications may change in any manner<br>without notice.                                                                                                            |  |  |

| Preliminary Specification                              | Preproduction Product  | This data sheet contains preliminary data, and supplementary data<br>will be published at a later date. Philips Semiconductors reserves the<br>right to make changes at any time without notice in order to improve<br>design and supply the best possible product. |  |  |

| Product Specification                                  | Full Production        | This data sheet contains Final Specifications. Philips Semiconductors<br>reserves the right to make changes at any time without notice, in order<br>to improve design and supply the best possible product.                                                         |  |  |

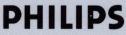

#### **Ordering Information**

#### PART NUMBER EXPLANATION

# Contents

PSD3XX Programmable Microcontroller Peripherals

| Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iii                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Product Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | iv                                      |

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | v                                       |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3<br>33<br>55<br>73<br>95<br>113<br>133 |

| Section 2       PSD3XXL Family         PSD3XXL Family 3-volt single-chip microcontroller peripherals       PSD301 <sup>®</sup> L 3-volt single-chip microcontroller peripheral (x8/x16; 256Kb EPROM, 16Kb SRAM)         PSD311L 3-volt single-chip microcontroller peripheral (x8; 256Kb EPROM, 16Kb SRAM)       PSD301 <sup>®</sup> L 3-volt single-chip microcontroller peripheral (x8/x16; 512Kb EPROM, 16Kb SRAM)         PSD302L 3-volt single-chip microcontroller peripheral (x8/x16; 512Kb EPROM, 16Kb SRAM)       PSD3012L 3-volt single-chip microcontroller peripheral (x8/x16; 512Kb EPROM, 16Kb SRAM)         PSD303L 3-volt single-chip microcontroller peripheral (x8/x16; 10Mb EPROM, 16Kb SRAM)       PSD303L 3-volt single-chip microcontroller peripheral (x8/x16; 10Mb EPROM, 16Kb SRAM)         PSD313L 3-volt single-chip microcontroller peripheral (x8/x16; 10Mb EPROM, 16Kb SRAM)       PSD313L 3-volt single-chip microcontroller peripheral (x8/x16; 10Mb EPROM, 16Kb SRAM) | 181<br>203<br>221<br>243                |

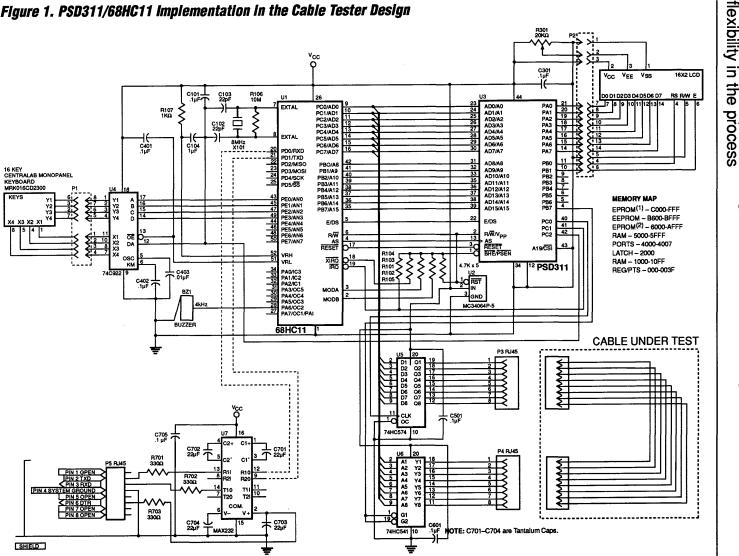

| Section 3       Application Notes         Application Note 011 The PSD3XX Device Description       2         Application Note 013 The PSD301 Streamlines a Microcontroller-Based Smart Transmitter Design       2         Application Note 013 The PSD3XX PAD for System Logic Replacement       2         Application Note 015 Using Memory Paging with the PSD3XX       2         Application Note 016 Power Considerations in the PSD3XX       2         Application Note 018 Security of Design in the PSD3XX       2         Application Note 019 The PSD311 Simplifies an Eight Wire Cable Tester Design and Increases Flexibility       2         Application Note 020 Benefits of 16-Bit Design with PSD3XX       2                                                                                                                                                                                                                                                                            | 357<br>371<br>385<br>399<br>413<br>417  |

| Section 4         Developing Systems           PSD Gold/PSD Silver Development System         4           WS6000 MagicPro® Memory and Programmable Peripheral Programmer         4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |

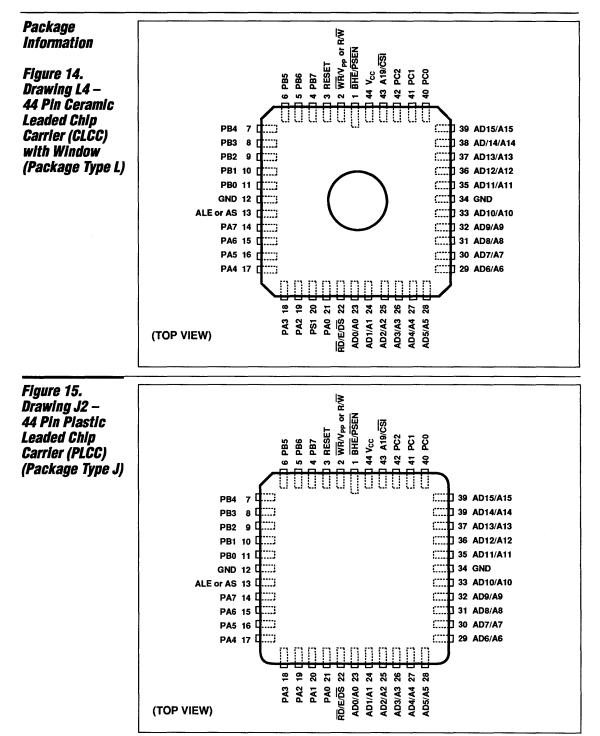

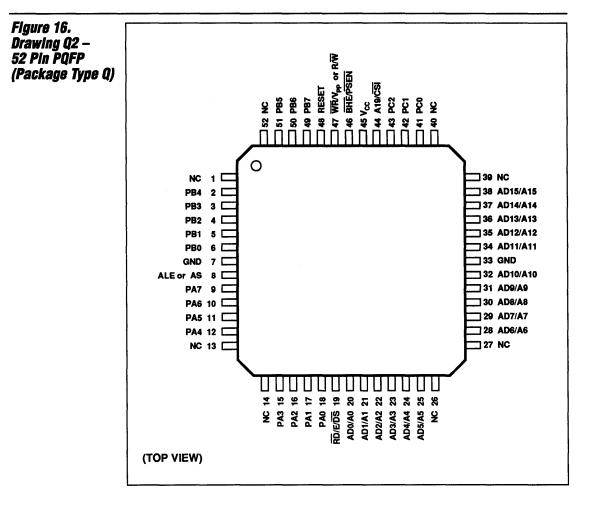

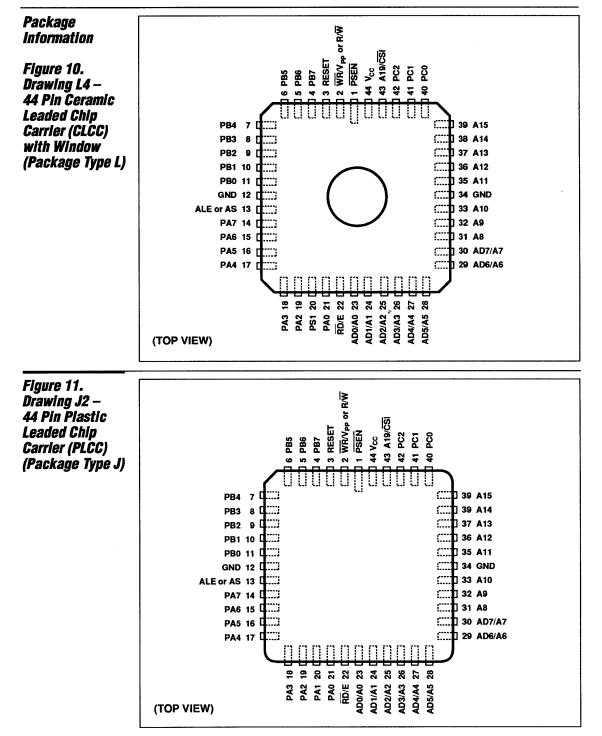

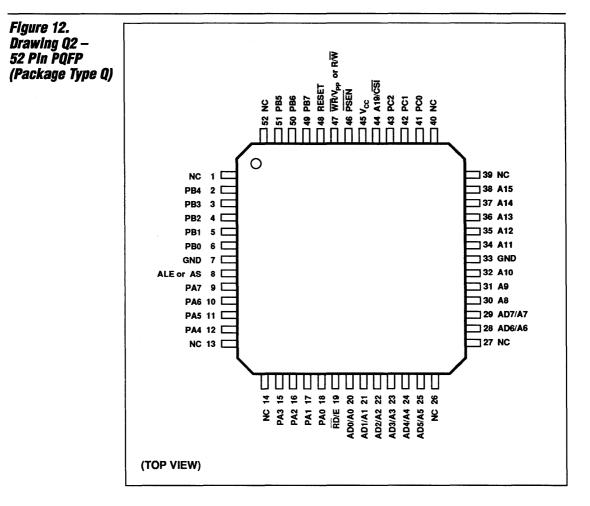

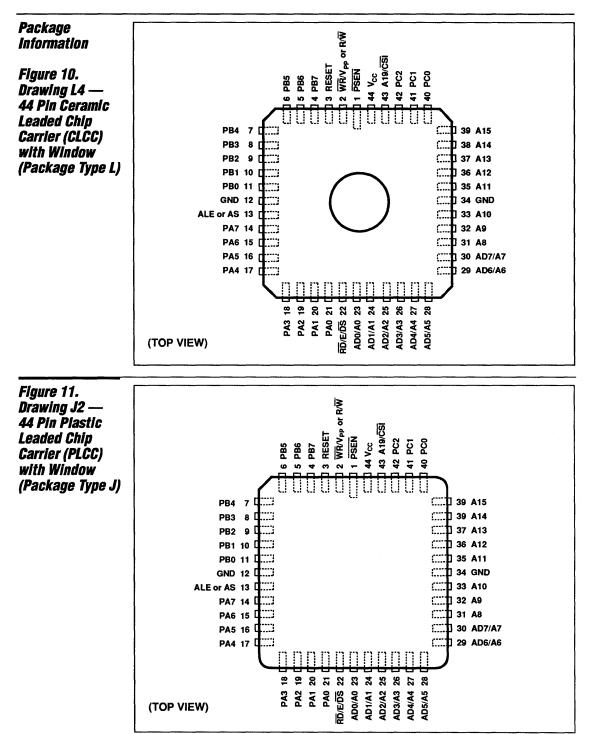

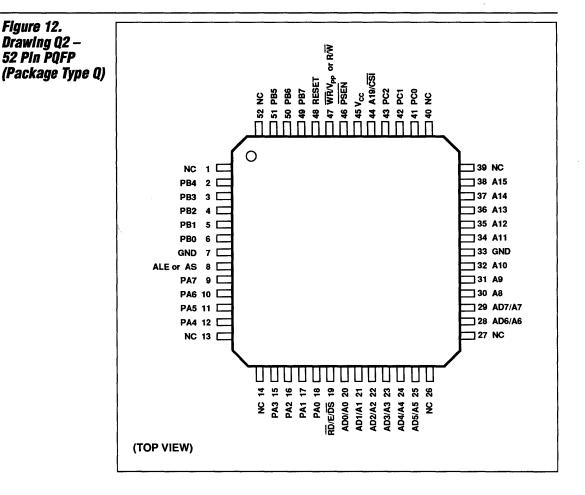

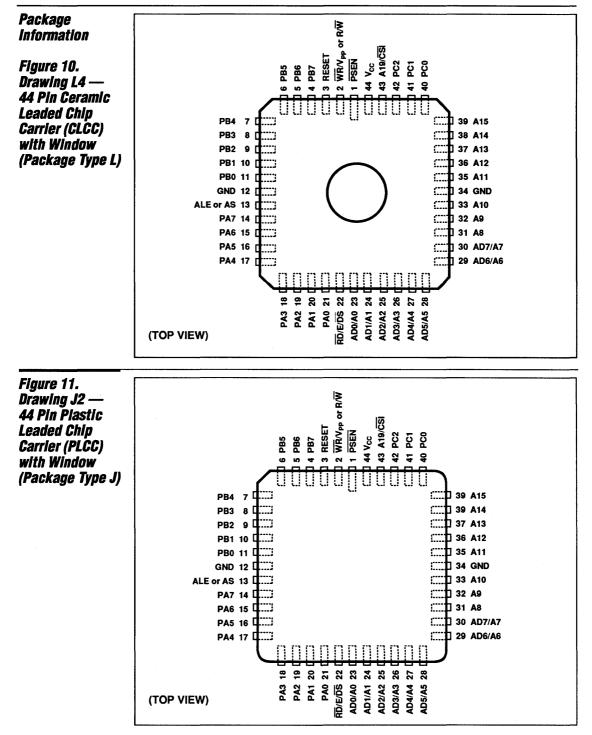

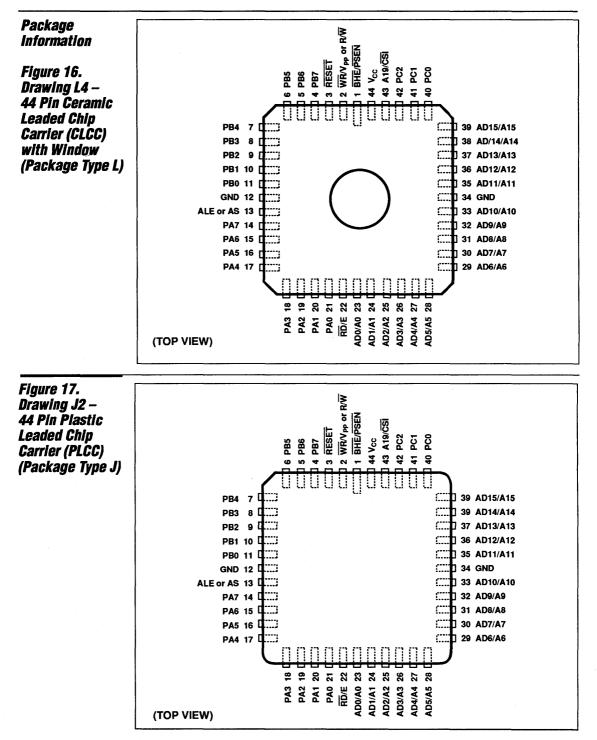

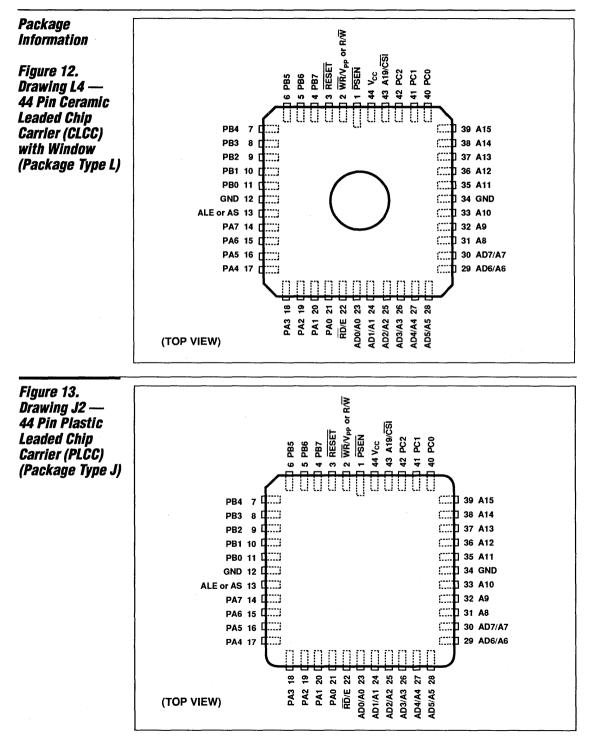

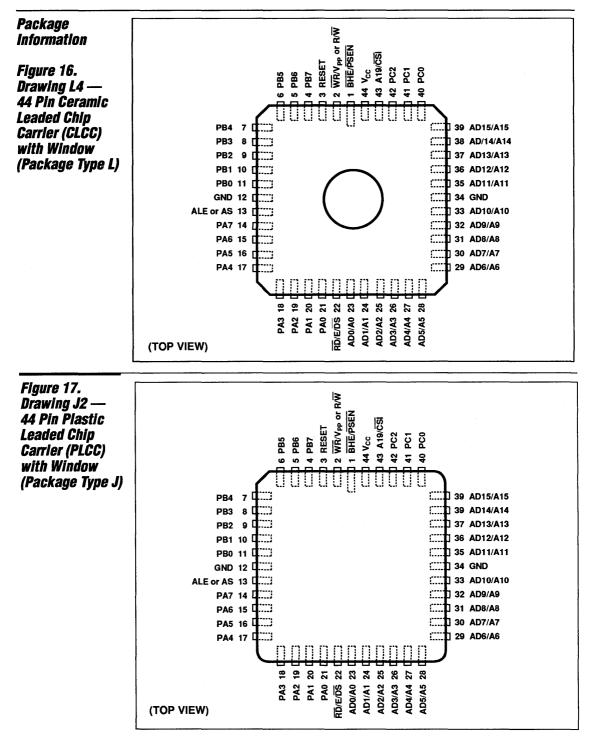

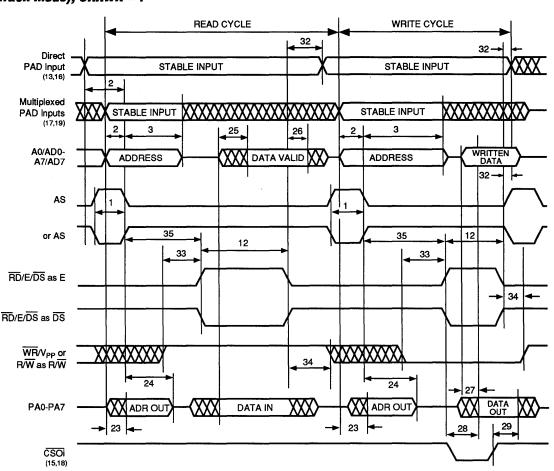

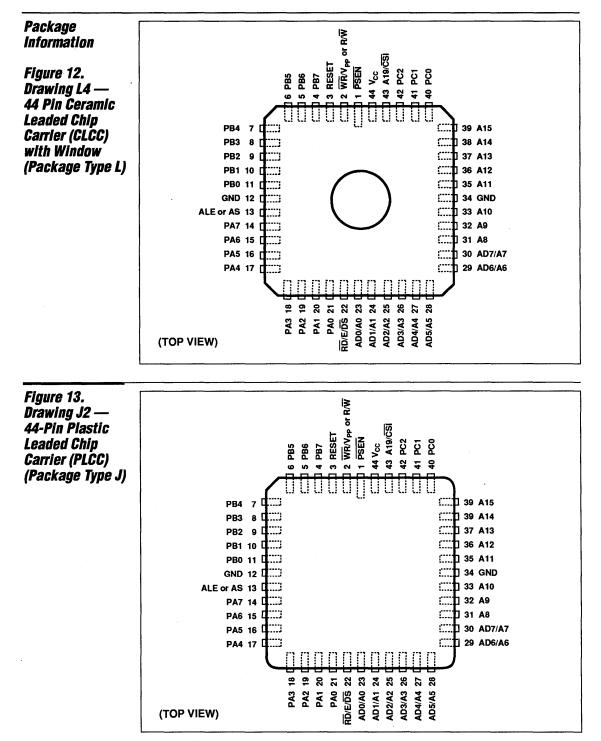

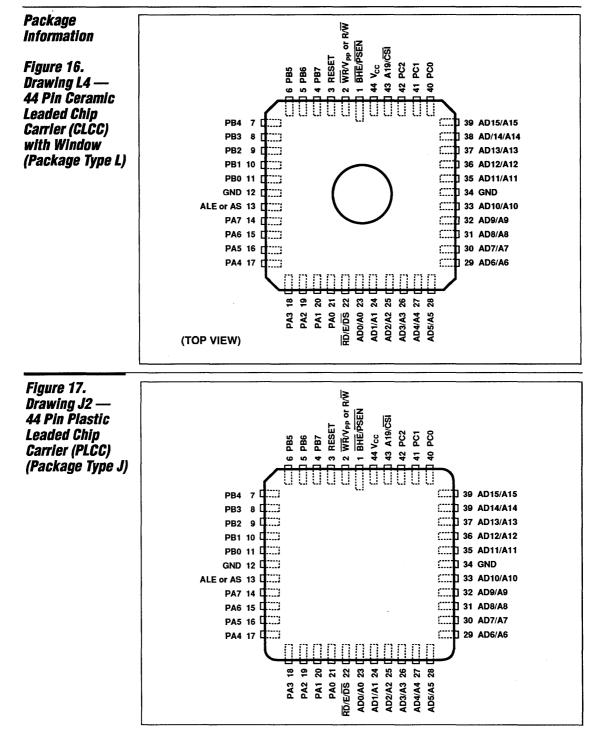

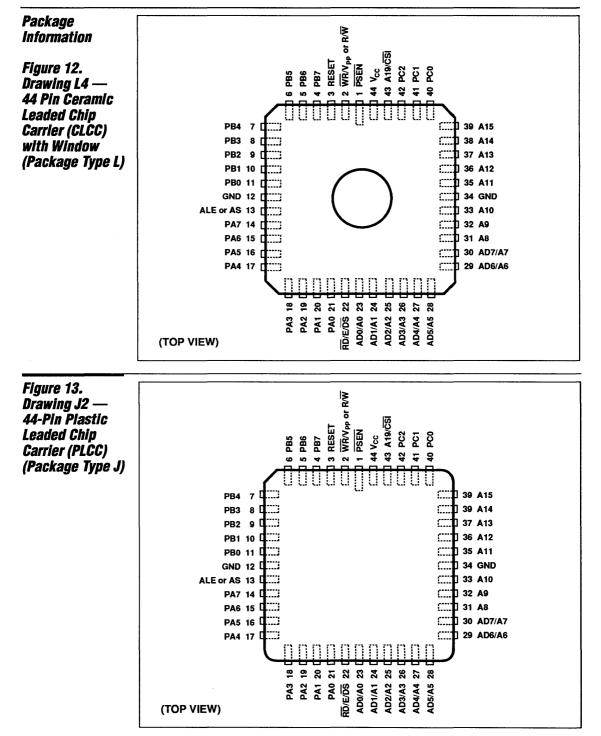

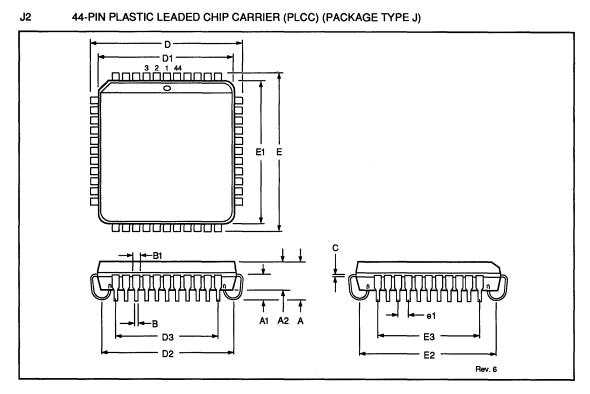

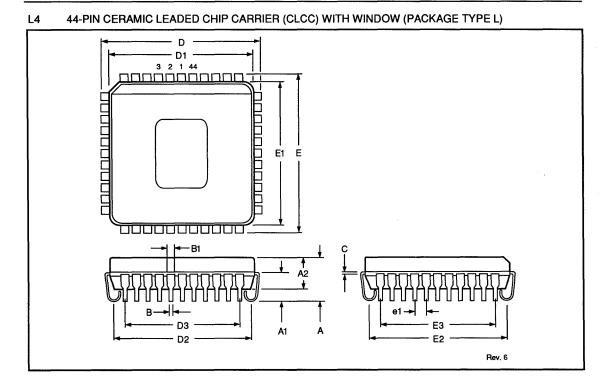

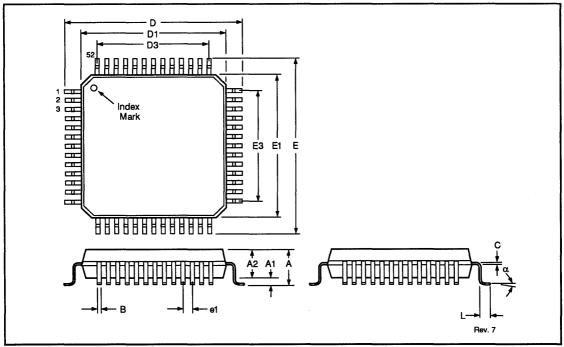

| Section 5       Package Outlines         J2 44-Pin Plastic Leaded Chip Carrier (PLCC)       4         L4 44-Pin Ceramic Leaded Chip Carrier (CLCC) with Window (Package Type L)       4         Q2 52-Pin Plastic Quad Flatpack (PQFP)       4         Section 6       Sales Offices, Representatives & Distributors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 462<br>463                              |

PSD301 is a registered trademark of WaferScale Integration, Inc. MagicPro is a registered trademark of WaferScale Integration, Inc.

# Section 1 PSD3XX Family

PSD3XX Programmable Microcontroller Peripherals

#### INDEX

| PSD3XX<br>Family    | Field-programmable microcontroller peripherals                                         |

|---------------------|----------------------------------------------------------------------------------------|

| PSD301 <sup>®</sup> | Field-programmable<br>microcontroller peripheral<br>(x8/x16; 256Kb EPROM, 16Kb SRAM)   |

| PSD311              | Field-programmable<br>microcontroller peripheral<br>(x8; 256Kb EPROM, 16Kb SRAM)55     |

| PSD302              | Field-programmable<br>microcontroller peripheral<br>(x8/x16; 512Kb EPROM, 16Kb SRAM)73 |

| PSD312              | Field-programmable<br>microcontroller peripheral<br>(x8; 512Kb EPROM, 16Kb SRAM)95     |

| PSD303              | Field-programmable<br>microcontroller peripheral<br>(x8/x16; 1Mb EPROM, 16Kb SRAM)113  |

| PSD313              | Field-programmable<br>microcontroller peripheral<br>(x8; 1Mb EPROM, 16Kb SRAM)133      |

#### **Key Features**

- □ Single Chip Programmable Peripheral for Microcontroller-based Applications

- 19 Individually Configurable I/O pins that can be used as

- Microcontroller I/O port expansion

- Programmable Address Decoder (PAD) I/O

- Latched address output

- Open drain or CMOS

- Two Programmable Arrays (PAD A and PAD B)

- Total of 40 Product Terms and up to 16 Inputs and 24 Outputs

- Address Decoding up to 1 MB

- Logic replacement

- "No Glue" Microcontroller Chip-Set

- Built-in address latches for multiplexed address/data bus

- Non-multiplexed address/data bus mode

- ALE and Reset polarity programmable

- Selectable modes for read and write control bus as RD/WR or R/W/E

- 256 Kbits of UV EPROM

- Configurable as 32K x 8 or as 16K x 16

- Divides into 8 equal mappable blocks for optimized mapping

- Block resolution is 4K x 8 or 2K x 16

- 120 ns EPROM access time, including input latches and PAD address decoding.

- 16 Kbit Static RAM

- Configurable as 2K x 8 or as 1K x 16

- 120 ns SRAM access time, including input latches and PAD address decodina

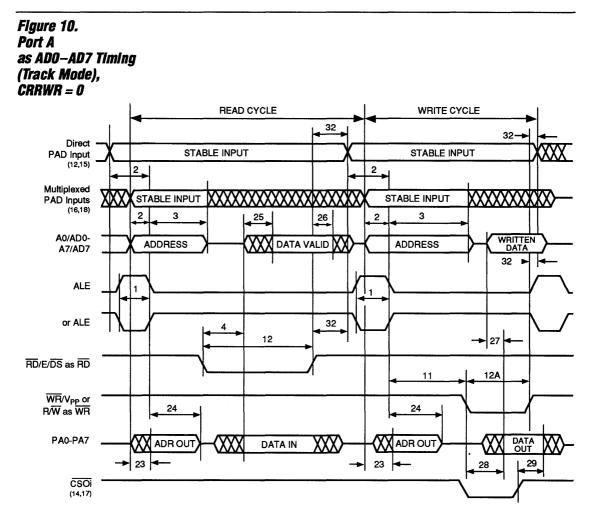

- Address/Data Track Mode

- Enables easy Interface to Shared Resources (Mail Box SRAM) with other Microcontrollers or a Host Processor

- Built-In Security

- Locks the PSD3XX Configuration and PAD Decoding

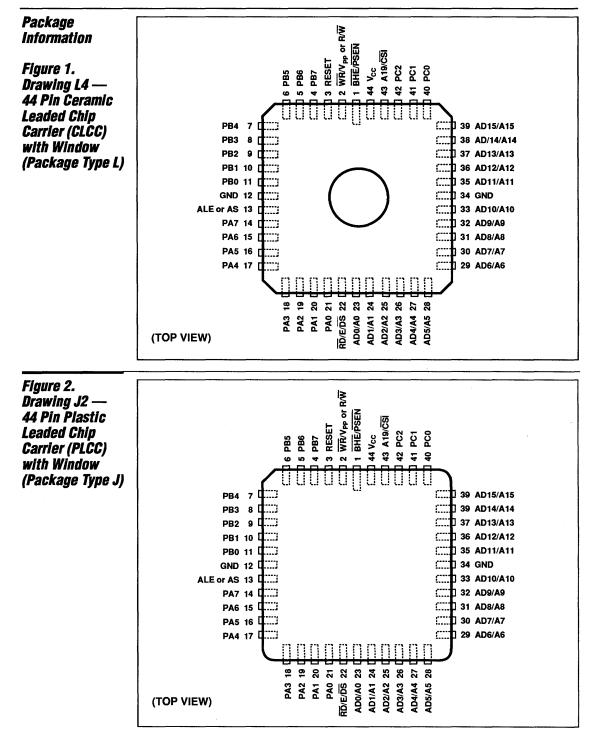

- Available in a Variety of Packaging

- 44 Pin PLDCC and CLDCC

- Simple Menu-Driven Software: Configure the PSD3XX on an IBM PC

| <i>PSD3XX<br/>Family<br/>Feature<br/>Summary</i> | Part                | PLD<br>Inputs/<br>Product<br>Terms | Ports | EPROM<br>Size | SRAM<br>Size | Configuration | Memory<br>Paging | C-Miser<br>Bit | Security<br>Bit |

|--------------------------------------------------|---------------------|------------------------------------|-------|---------------|--------------|---------------|------------------|----------------|-----------------|

|                                                  | PSD301 <sup>®</sup> | 14/40                              | 19    | 256 Kb        | 16 Kb        | x8 or x16     |                  | X              | х               |

|                                                  | PSD311              | 14/40                              | 19    | 256 Kb        | 16 Kb        | x8            |                  | х              | х               |

|                                                  | PSD302              | 18/40                              | 19    | 512 Kb        | 16 Kb        | x8 or x16     | x                | х              | х               |

|                                                  | PSD312              | 18/40                              | 19    | 512 Kb        | 16 Kb        | x8            | х                | х              | x               |

|                                                  | PSD303              | 18/40                              | 19    | 1 Mb          | 16 Kb        | x8 or x16     | х                | х              | х               |

|                                                  | PSD313              | 18/40                              | 19    | 1 Mb          | 16 Kb        | x8            | X                | x              | х               |

3

#### Preliminary specification

| Field-program                                          | nable microcontroller peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PSD3XX Family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Partial Listing<br>of<br>Microcontrollers<br>Supported | <ul> <li>Motorola family:<br/>M6805, M68HC11, M68HC16,<br/>M68000/10/20, M60008, M683XX</li> <li>Intel family:<br/>8031/8051, 8096/8098, 80186/88,<br/>80196/98</li> <li>Signetics:<br/>SC80C451, SC80552</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>TI:<br/>SC80C451, TMS320C14</li> <li>Zilog:<br/>Z8, Z80, Z180</li> <li>National:<br/>HPC16000, HPC46400</li> </ul>                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Applications                                           | <ul> <li>Computers (Notebook and Portable PCs)</li> <li>Fixed Disk Control, Modem, Imaging,<br/>Laser Printer Control</li> <li>Telecommunications</li> <li>Modem, Cellular Phone, Digital PBX,<br/>Digital Speech, FAX,<br/>Digital Signal Processing</li> </ul>                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>Portable Industrial Equipment</li> <li>Measurement Meters, Data Recorders</li> <li>Medical Instrumentation</li> <li>Hearing Aids, Monitoring Equipment,<br/>Diagnostic Tools</li> </ul>                                                                                                                                                                                                                                                                                                          |  |  |

| Introduction                                           | The PSD3XX Series are members of the<br>rapidly growing family of PSD devices. They<br>are the market's first low-voltage single-chip<br>solution for microcontroller-based<br>applications where consistent specifications<br>for design, fast time-to-market, small form<br>factor, and low power consumptions are<br>essential. When combined in an 8- or 16-bit<br>system, virtually any microcontroller<br>(68HC11, 8051, 80186, etc.) and the<br>PSD3XX device work together to create a<br>very powerful chip-set solution. This<br>implementation eliminates mixing and<br>matching low voltage specifications for | various discrete components. It also<br>provides all the required control and<br>peripheral elements needed in a<br>microcontroller-based system with no<br>external discrete "glue" logic required.<br>The solution comes complete with simple<br>system software development tools for<br>integrating the PSD3XX with the<br>microcontroller. Hosted on IBM PC<br>platforms or compatibles, the easy to use<br>software enables the designer to quickly<br>configure the device and use it immediately. |  |  |

PSD301 is a registered trademark of WaterScale Integration, Inc. PAL is a registered trademark of Advanced Micro Devices, Inc.

#### PSD3XX Family

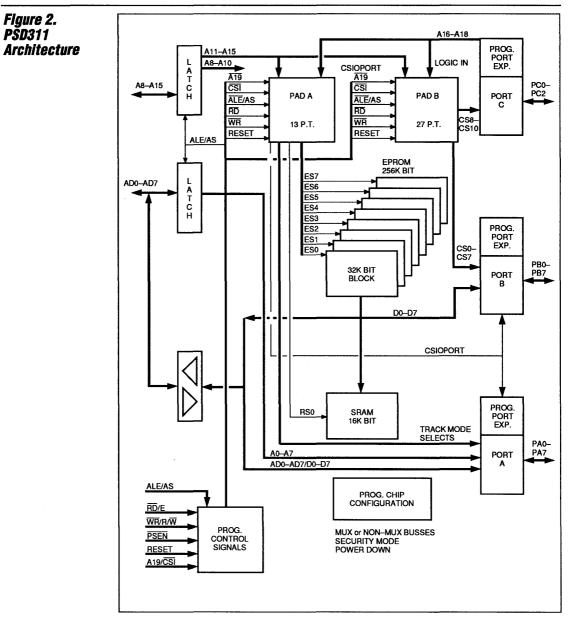

#### Product Description

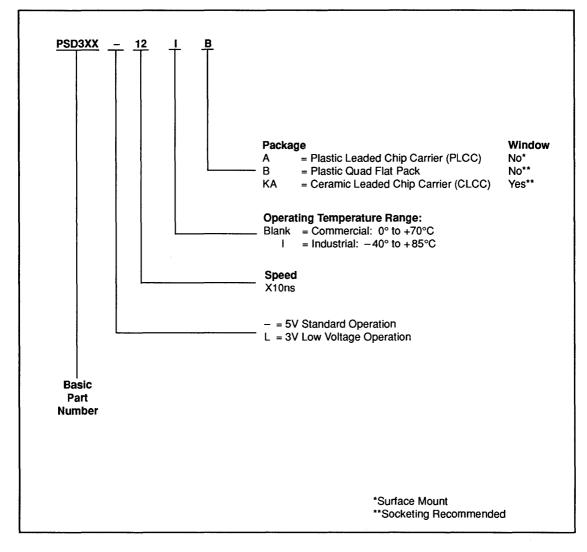

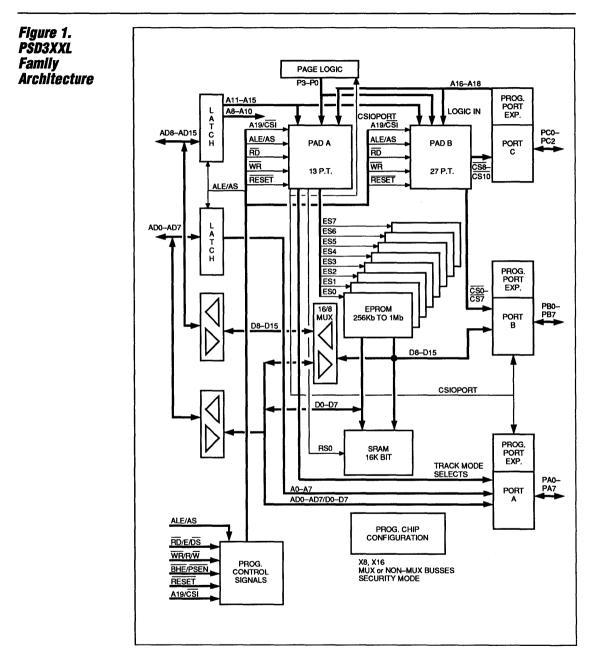

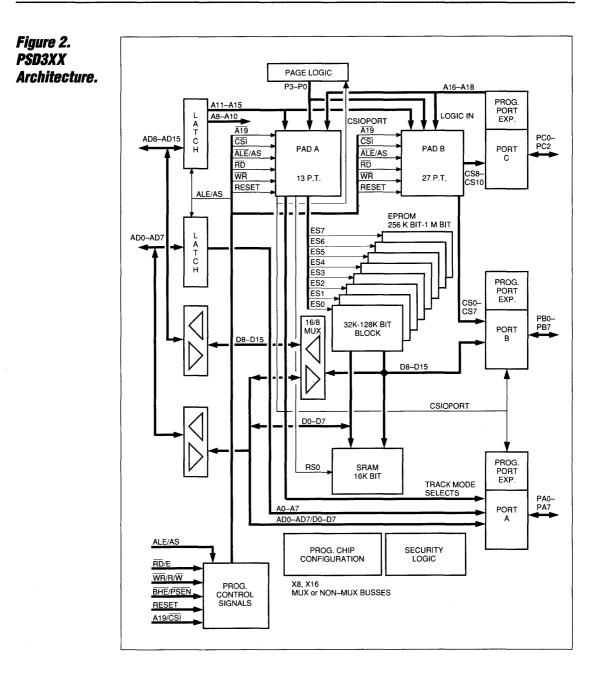

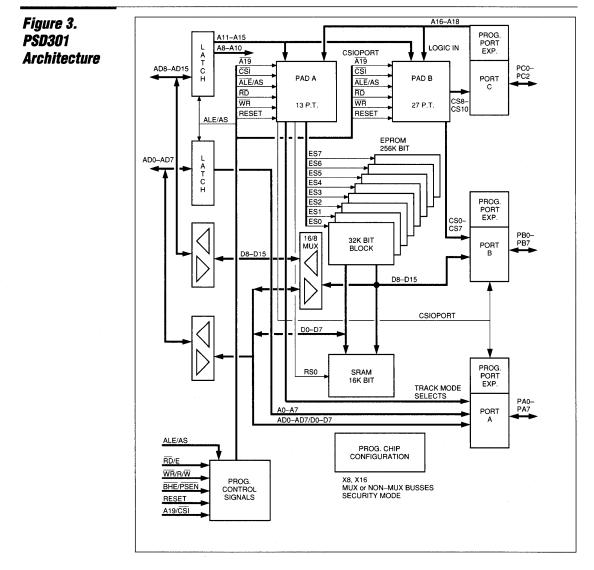

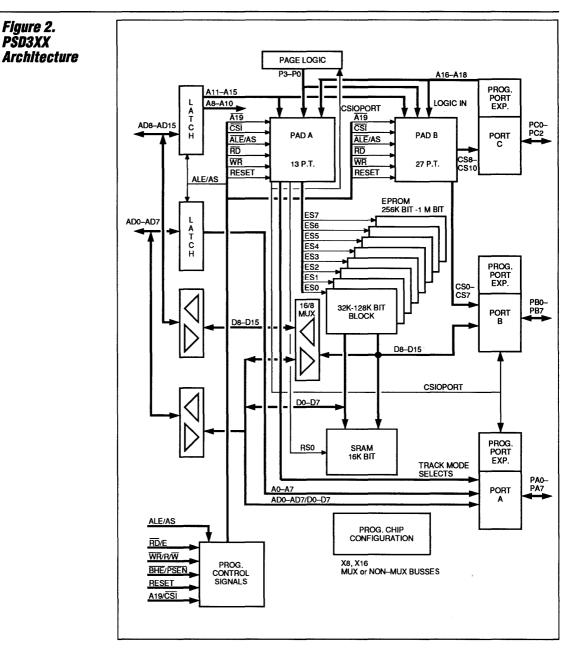

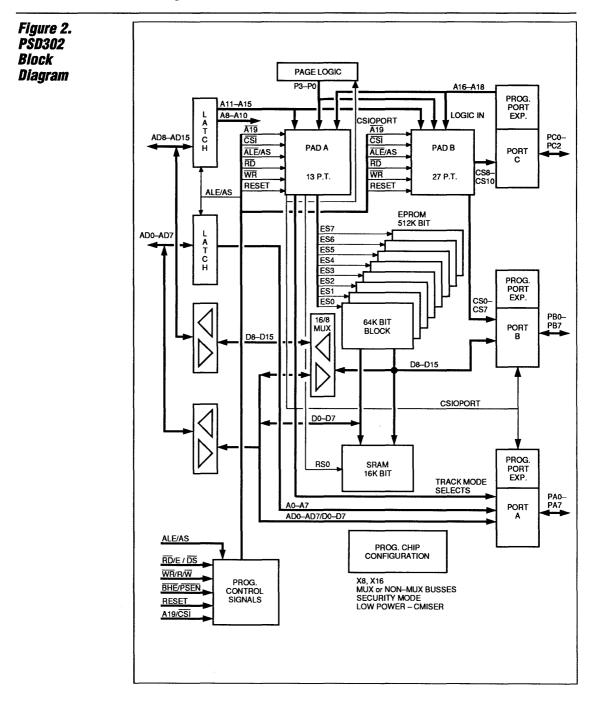

The PSD3XX family integrates high performance user-configurable blocks of EPROM, SRAM, and programmable logic. The major functional blocks include two programmable logic arrays, PAD A and PAD B, 256K to 1Mbit of EPROM, 16K bits of SRAM, input latches, and output ports. The PSD3XX family is ideal for applications requiring low power and very small form factors. These include hard disk control, modems, cellular telephones, instrumentation, computer peripherals, military and similar applications.

The PSD3XX family offers a unique singlechip solution for microcontrollers that need:

- I/O reconstruction (microcontrollers lose at least two I/O ports when accessing external resources).

- More EPROM and SRAM than the microcontroller's internal memory.

- Chip-select, control, or latched address lines that are otherwise implemented discretely.

- An interface to shared external resources.

- Expanded microcontroller address space.

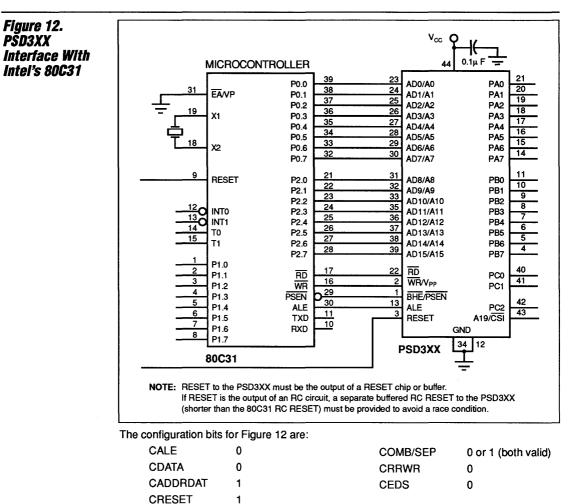

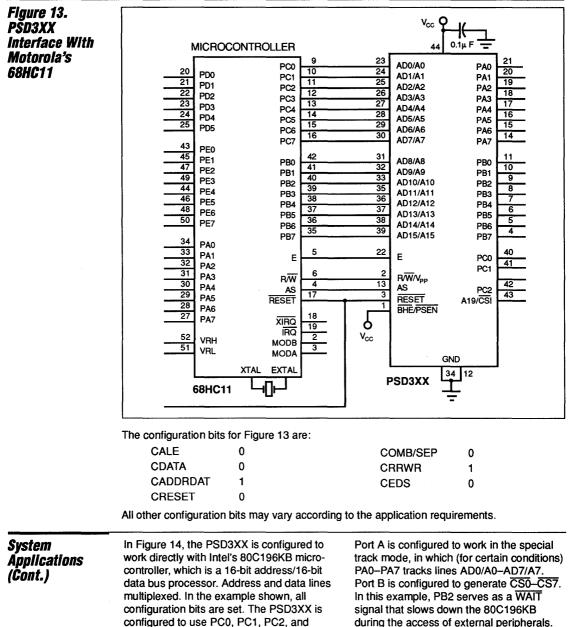

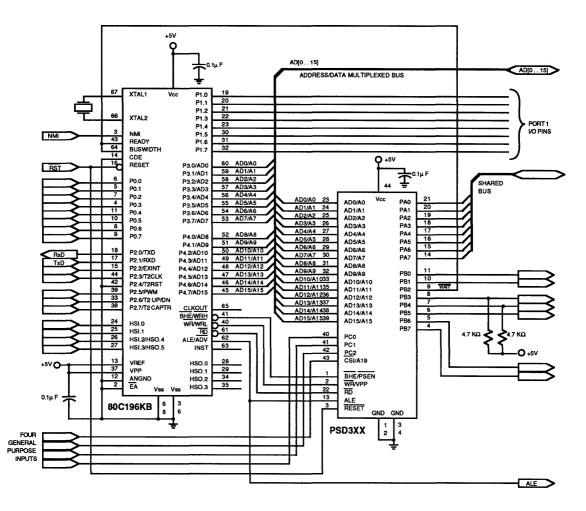

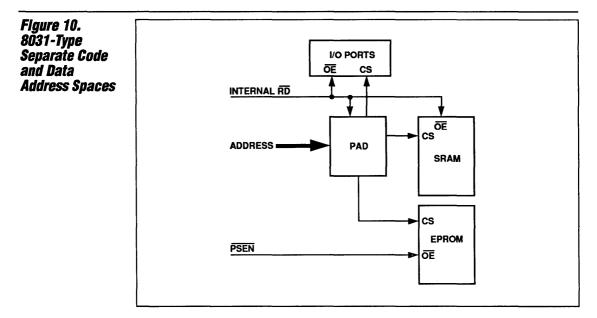

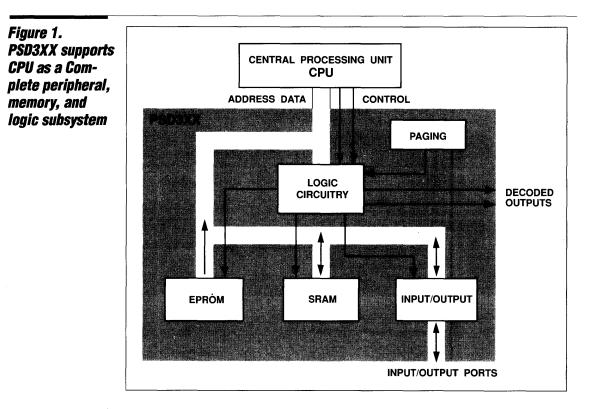

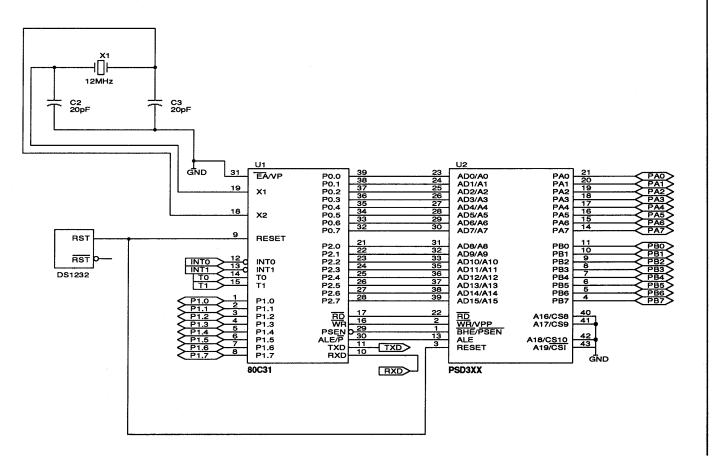

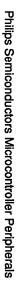

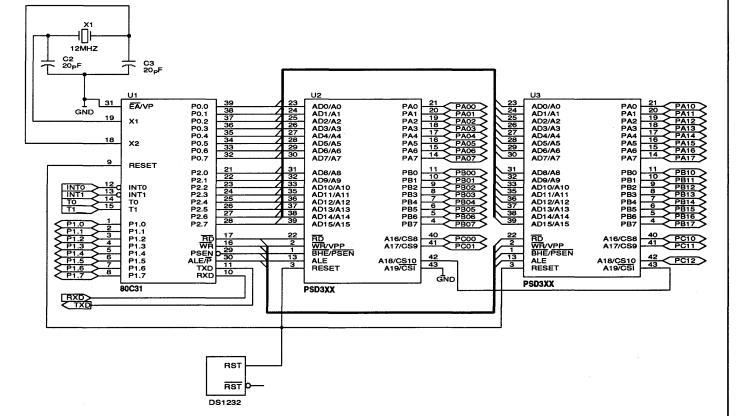

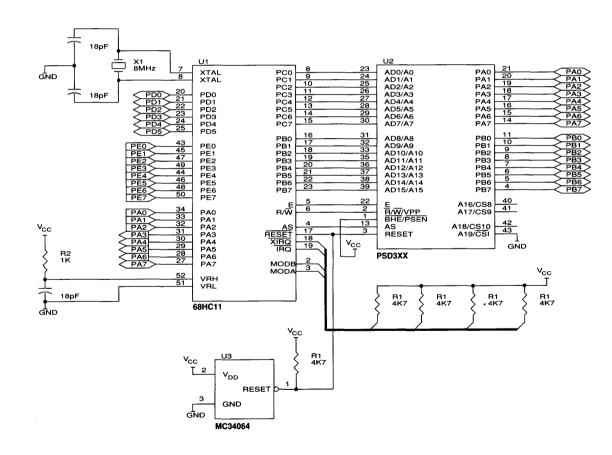

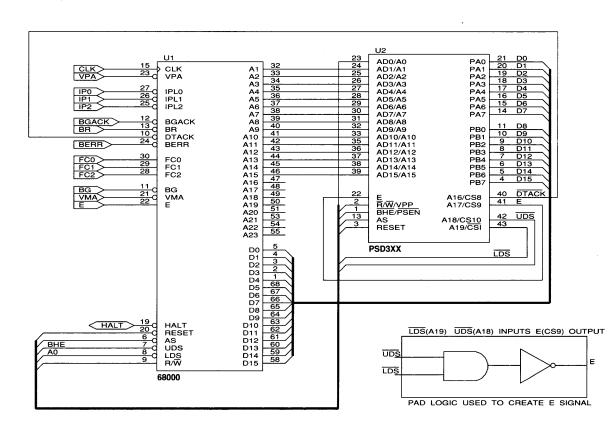

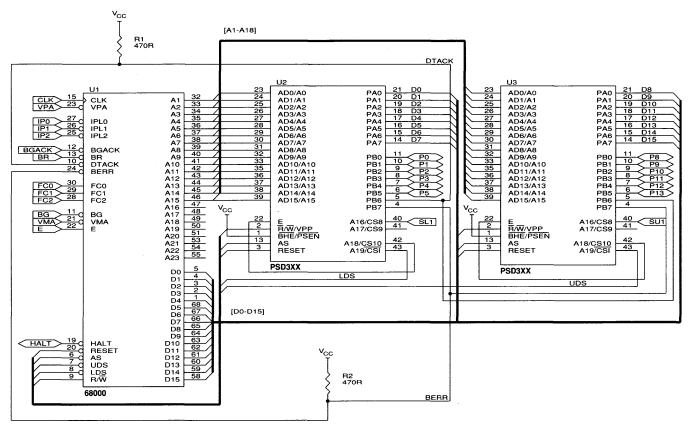

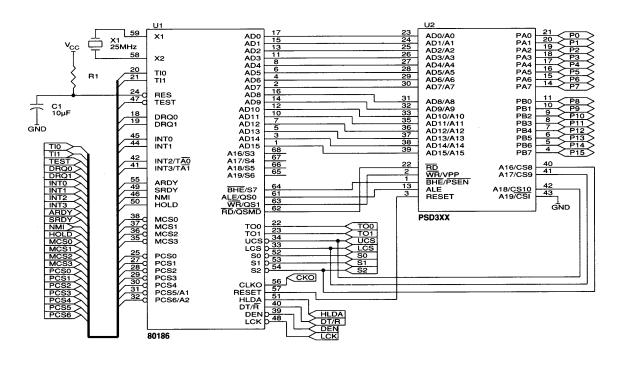

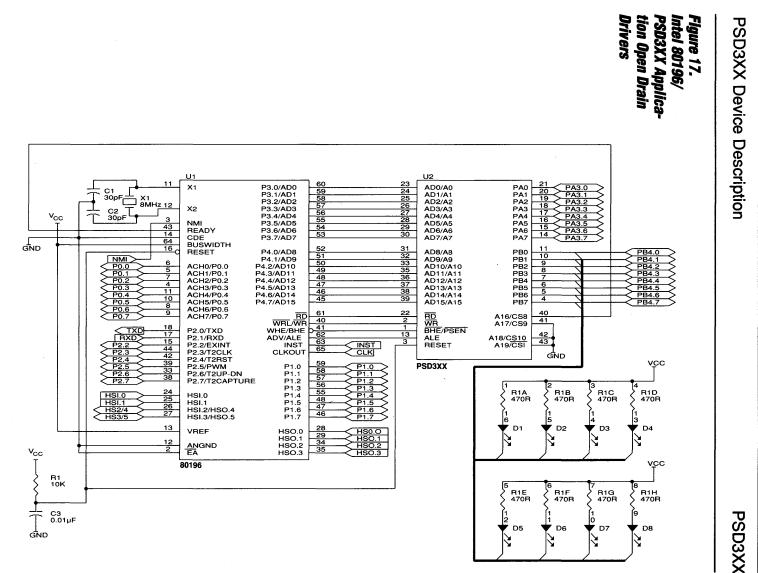

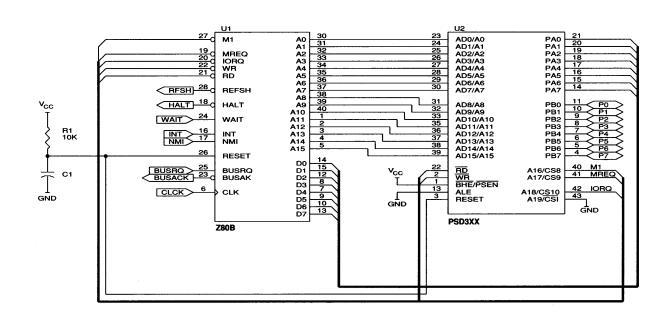

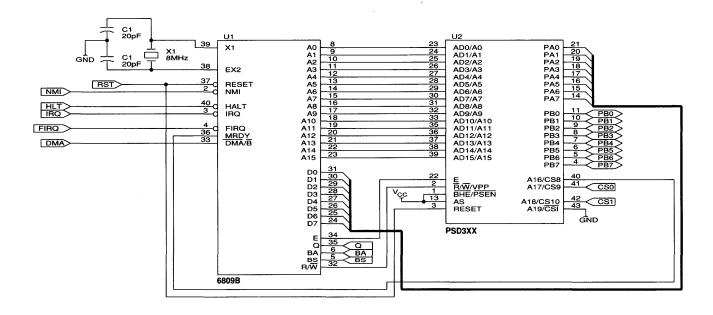

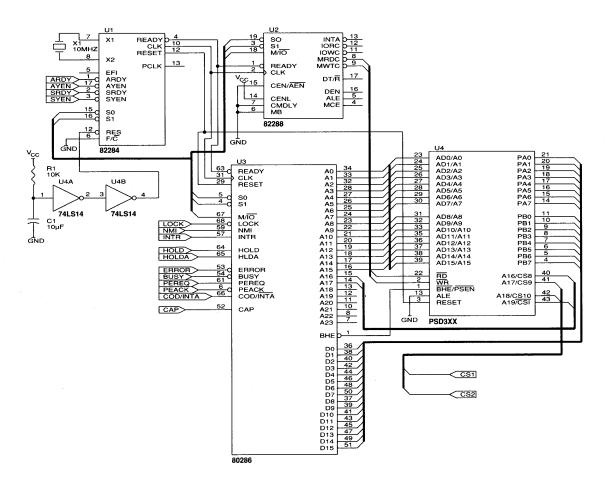

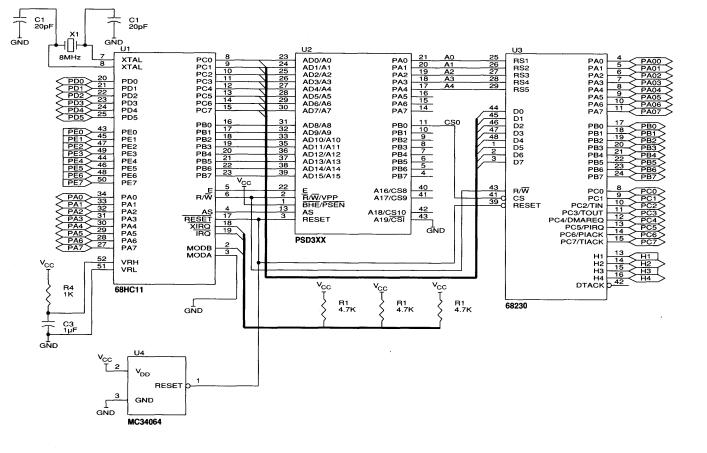

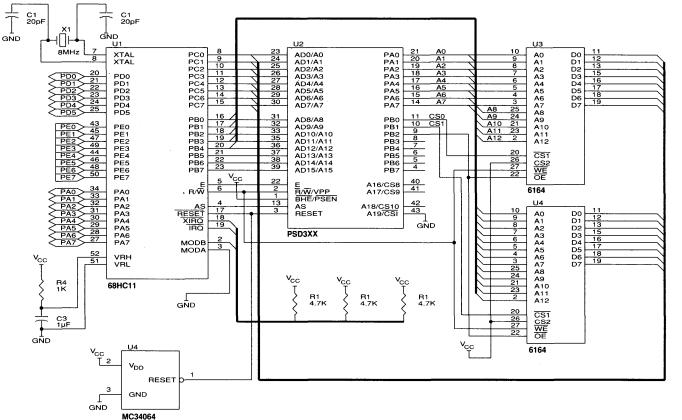

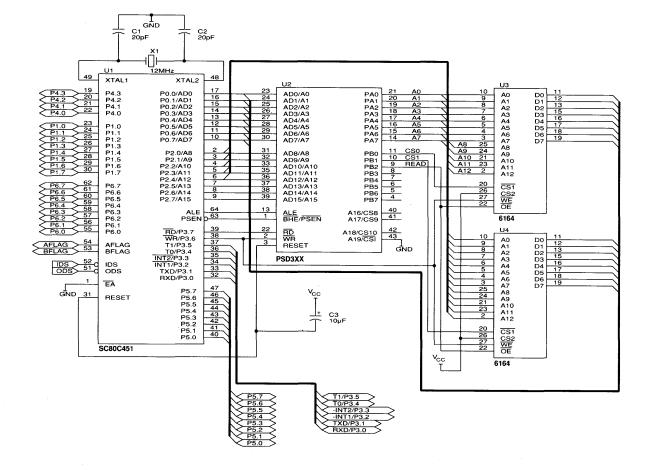

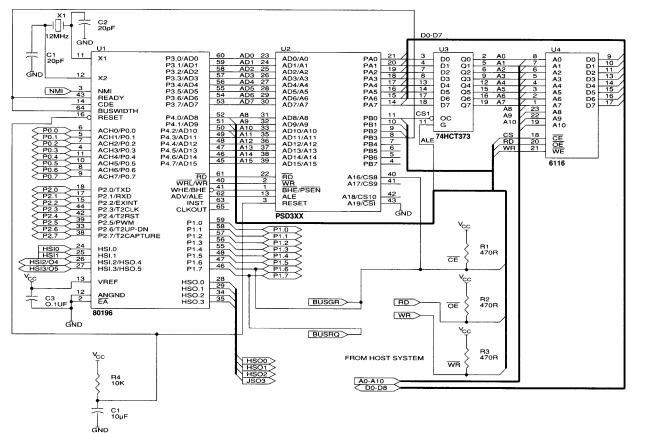

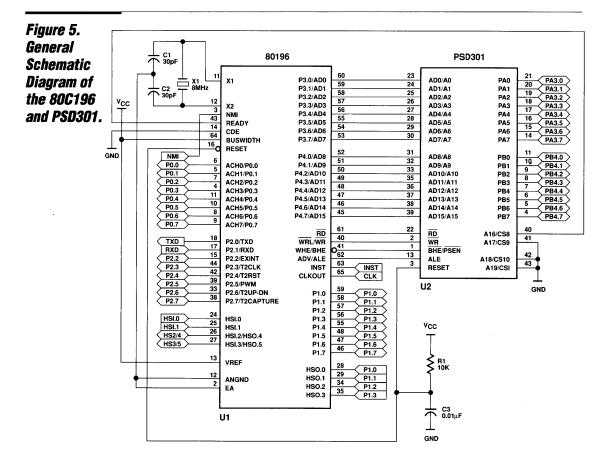

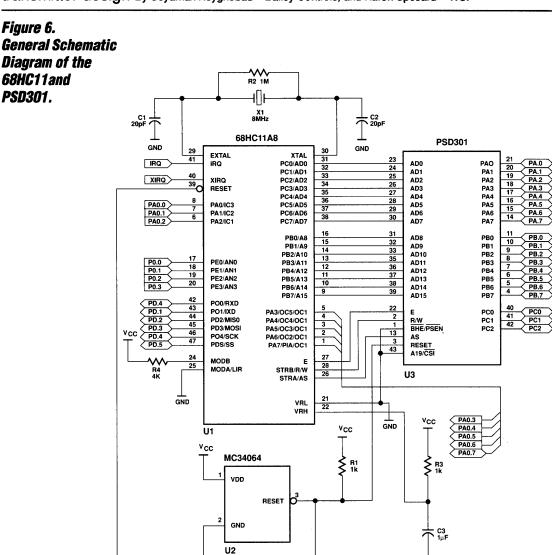

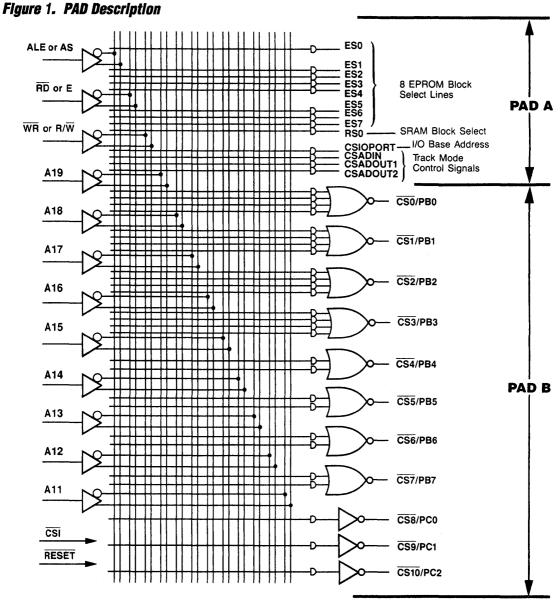

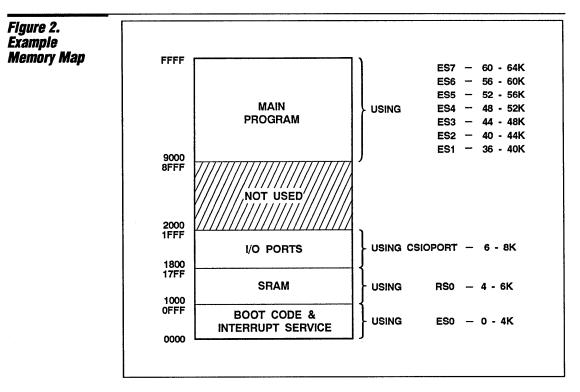

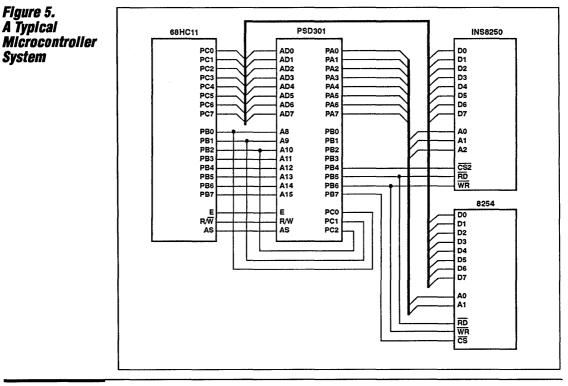

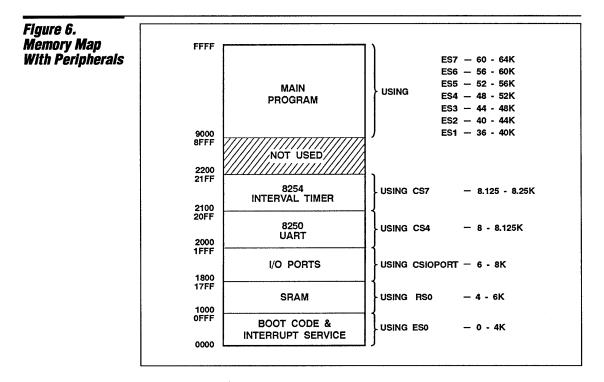

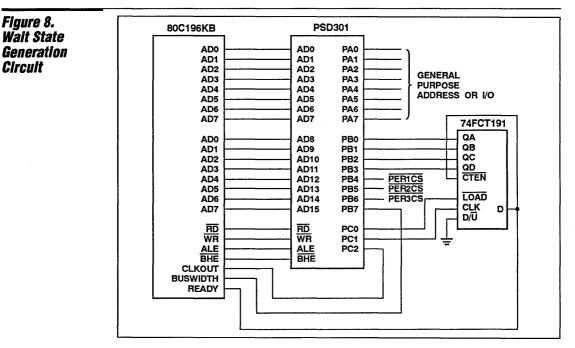

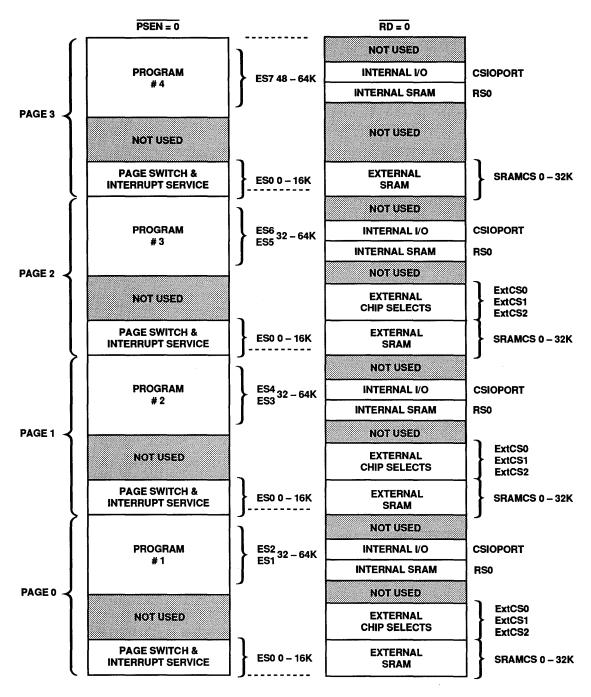

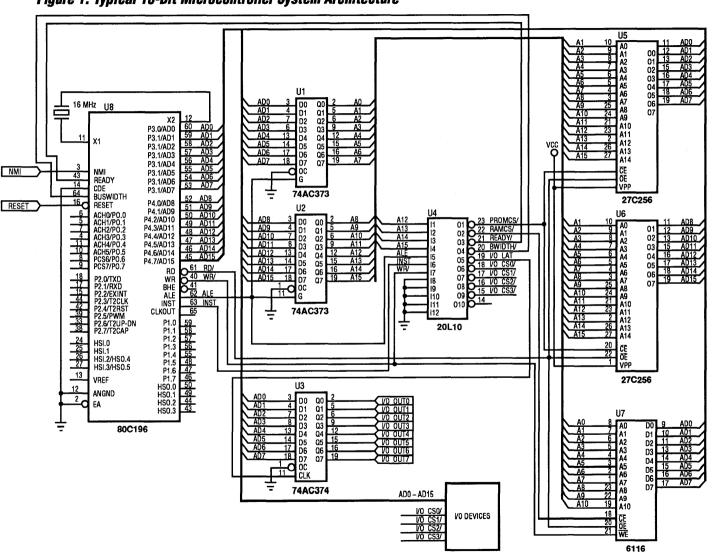

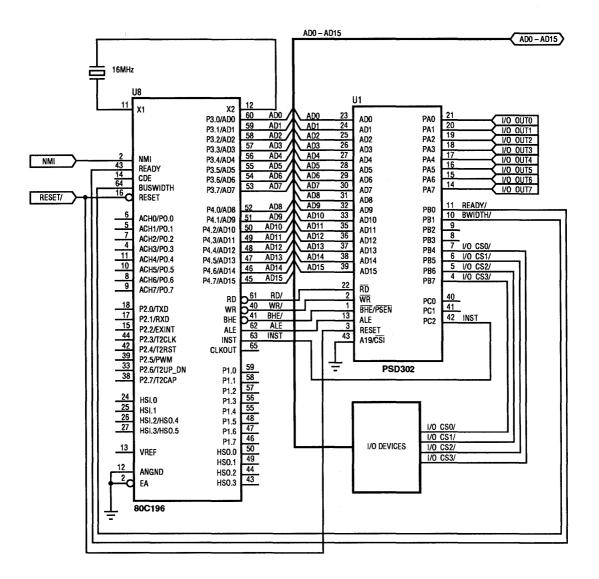

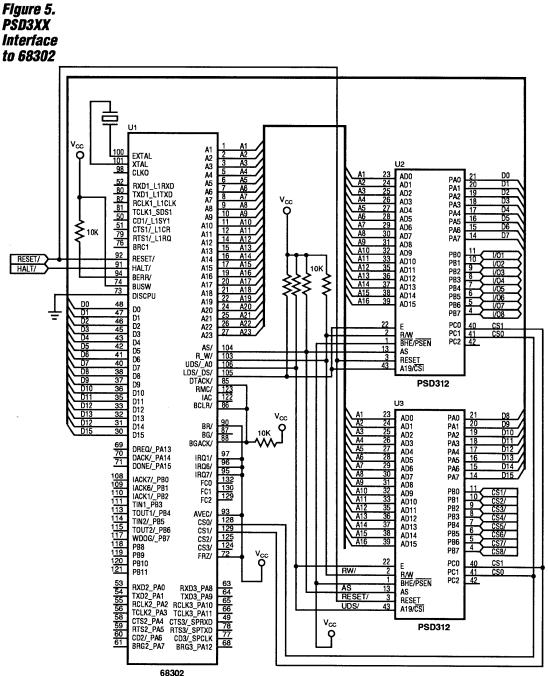

The PSD3XX Family Architecture (Figure 1) can efficiently interface with, and enhance, any low-voltage 8- or 16-bit microcontroller system. This is the first solution that provides microcontrollers with port expansion, latched addresses, page logic, two programmable logic arrays (PAD A and PAD B), an interface to shared resources, 256K, 512K or 1M bit EPROM, and 16K bit SRAM on a single chip. The PSD3XX family does not require any glue logic for interfacing to any 8- or 16-bit microcontroller. The 8051 microcontroller family can take full advantage of the PSD3XX's separate program and data address spaces. Users of the 68HCXX microcontroller family can change the functionality of the control signals and directly connect the R/W and E, or the R/W and DS signals. (Users of 16-bit microcontrollers, including the 80186, 8096, 80196 and 16XXX, can use the PSD301/302/303 in a 16-bit configuration). Address and data buses can be configured as separate or multiplexed, whichever is required by the host processor.

The flexibility of the PSD3XX I/O ports permits interfacing to shared resources. The arbitration can be controlled internally by PAD A outputs. The user can assign the following functions to these ports: standard I/O pins, chip-select outputs from PAD A and PAD B, or latched address or multiplexed low-order address/data byte. This enables users to design add-on systems such as disk drives, modems, etc., that easily interface to the host bus (e.g., IBM PC, SCSI).

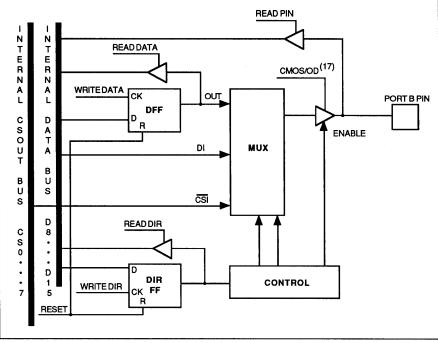

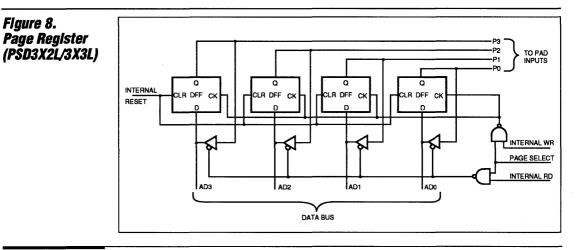

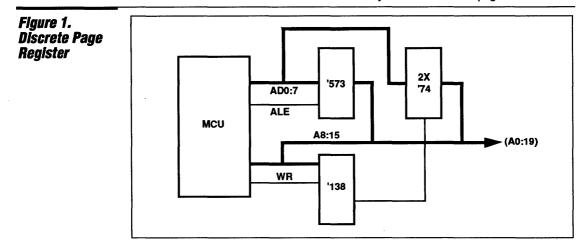

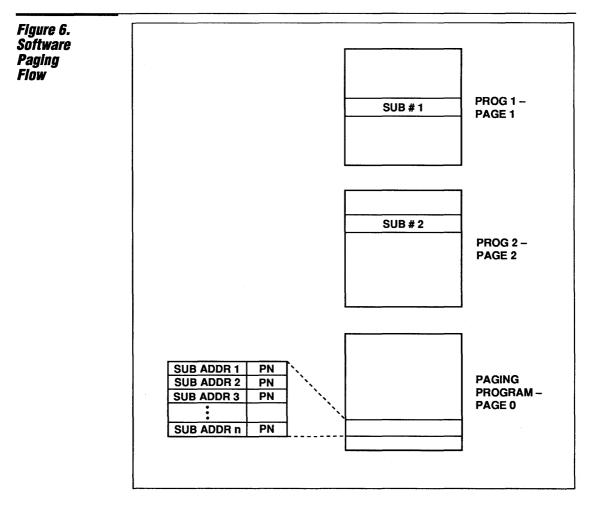

The page register extends the accessible address space of certain microcontrollers from 64 K to 1 M. There are 16 pages that can serve as base address inputs to the PAD, thereby enlarging the address space of 16 address line microcontrollers by a factor of 16.

#### Field-programmable microcontroller peripherals

#### **PSD3XX** Family

| Table 1.<br>PSD3XX Pin         | Name                                            | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------|-------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Descriptions                   | BHE/PSEN<br>(PSD30X<br>Devices)                 |      | When the data bus width is 8 bits (CDATA = 0), this pin is $\overrightarrow{PSEN}$ . In this mode, $\overrightarrow{PSEN}$ is the active low EPROM read pulse. The SRAM and <u>I/O</u> ports read signal is generated according to the description of the WR/V <sub>PP</sub> or R/W and $\overrightarrow{RD/E/DS}$ pins. If the host processor is a member of the 8031 family, $\overrightarrow{PSEN}$ must be connected to the corresponding host pin. In other 8-bit host processors that do not have a special EPROM-only read strobe, $\overrightarrow{PSEN}$ should be tied to V <sub>CC</sub> . In this case, $\overrightarrow{RD}$ or E and $\overrightarrow{R/W}$ provide the read strobe for the SRAM, I/O ports, and EPROM. When the data bus width is configured as 16 (CDATA = 1), this pin is $\overrightarrow{BHE}$ . When $\overrightarrow{BHE}$ is low, data bus bits D8–D15 are read from, or written into, the $\overrightarrow{PSD3XX}$ , depending on the operation being read or write, respectively. In programming mode, this pin is pulsed between V <sub>PP</sub> and 0. |

|                                | or<br>PSEN<br>(PSD31X<br>Devices<br>Only)       | 1    | The $\overrightarrow{PSEN}$ is the active low EPROM read pulse. The SRAM and I/O<br>ports read signal is generated according to the description of the<br>WR/V <sub>PP</sub> or R/W, and <u>RD</u> /E pins. If the host processor is a member<br>of the 8031 family, PSEN must be connected to the correspondinbg<br>host pin. In other 8-bit host processors that do not have a special<br>EPROM-only read strobe, PSEN should be tied to V <sub>CC</sub> . In this case,<br>RD or E and R/W provide the read strobe for the SRAM, I/O ports,<br>and EPROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

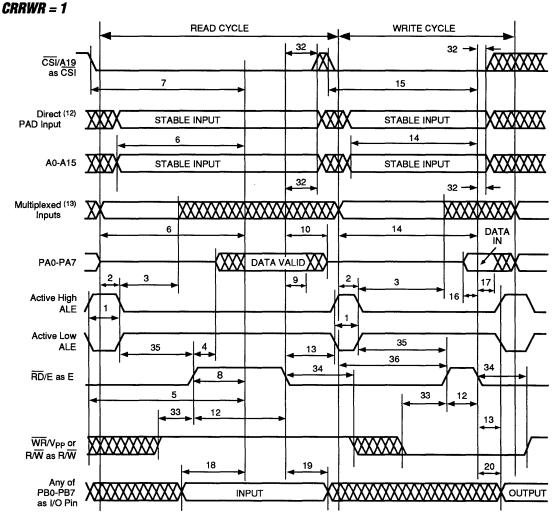

| or<br>R/W/V<br>RD/E/I<br>(Note | WR/V <sub>PP</sub><br>or<br>R/W/V <sub>PP</sub> | I    | In the operating mode this pin's function is $\overline{WR}$ (CRRWR = 0) or<br>R/W (CRRWR = 1) when configured as R/W. The following tables<br>summarize the read and write operations (CRRWR = 1):<br>$\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                | RD/E/DS<br>(Note 2)                             | I    | The pin function depends on the CRRWR and CEDS configuration<br>bits. If CRRWR = 0, $\overline{RD}$ is an active low read pulse. When<br>CRRWR = 1, this pin and the R/W pin define the following cycle type:<br>If CEDS = 0, E is an active high strobe. If CEDS = 1, $\overline{DS}$ is an active<br>low strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | OF<br>RD/E<br>(Note 3)                          | I    | When configured as $\overline{RD}$ (CRRWR = 0), this pin provides an active<br>low $\overline{RD}$ strobe. When configured as E (CRRWR = 1), this pin<br>becomes an active high pulse, which, together with $R/\overline{W}$ defines the<br>cycle type. Then, if $R/W$ = 1 and E = 1, a read operation is executed.<br>If $R/\overline{W}$ = 0 and E = 1, a write operation is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

**Legend:** The I/O column abbreviations are: I = input; I/O = input/output; P = power.

NOTE: 1. All the configuration bits mentioned in Table 1 appear in parentheses and are explained in the Configuration Register section.

- 2. PSD302/312/303/313 only.

- 3. PSD301/311 only.

| Table 1.<br>PSD3XX Pin         | Name                                                 | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------|------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

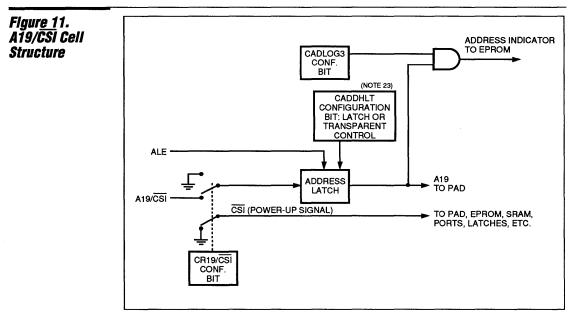

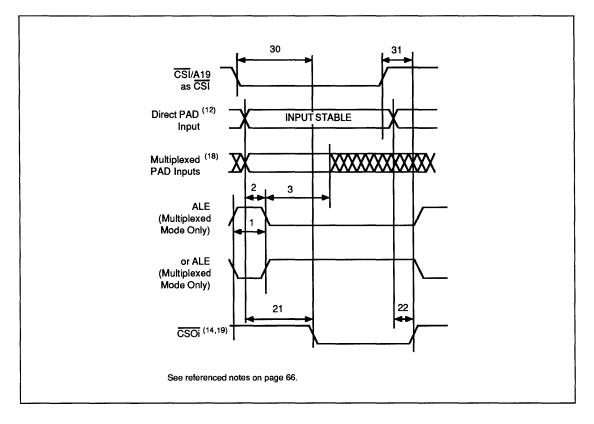

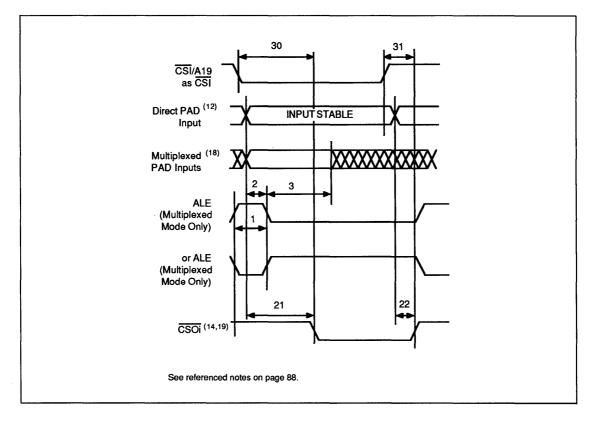

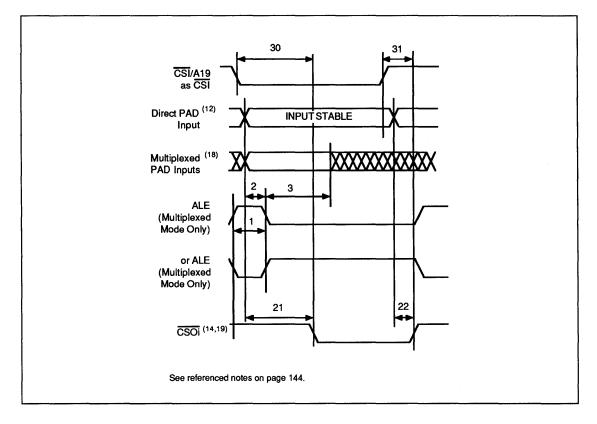

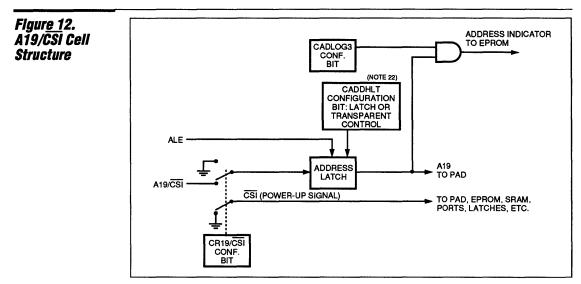

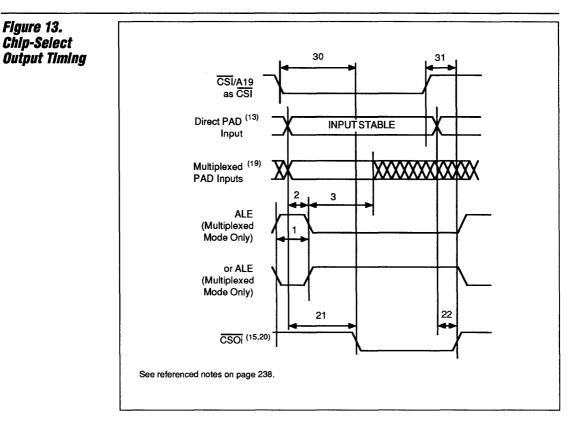

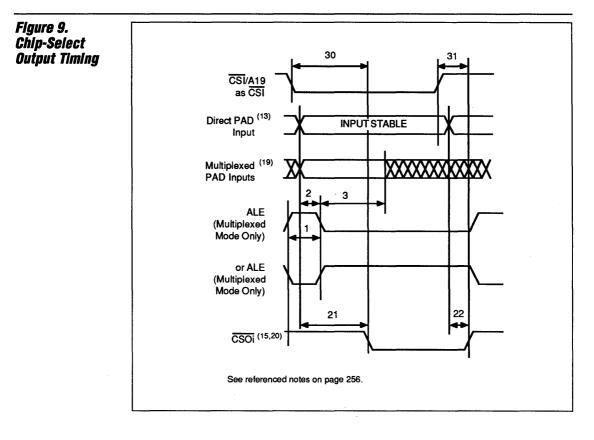

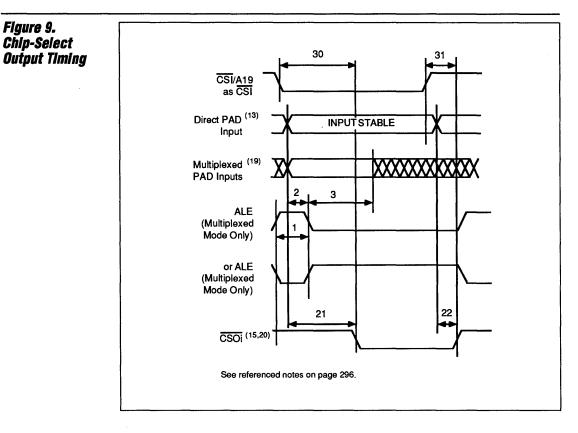

| <i>Descriptions</i><br>(Cont.) | CSI/A19                                              | I    | This pin has two configurations. When it is $\overline{CSI}$ (CA19/ $\overline{CSI}$ = 0) and the pin is asserted high, the device is deselected and powered down. (See Tables 12 and 13 for the chip state during power-down mode.) If the pin is asserted low, the chip is in normal operational mode. When it is configured as A19, (CA19/ $\overline{CSI}$ = 1), this pin can be used as an additional input to the PAD. CADLOG3 = 1 defines the pin as an address; CADLOG3 = 0 defines it as a logic input. If it is an address, A19 can be latched with ALE (CADDHLT = 1) or be a transparent logic input (CADDHLT = 0). In this mode, there is no power-down capability.                                                                                                                                                                                                                 |

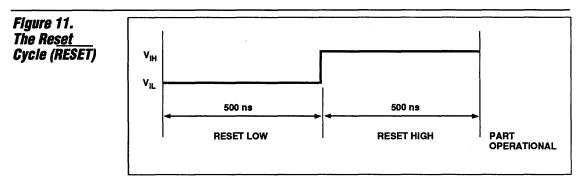

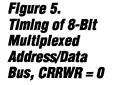

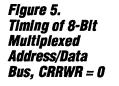

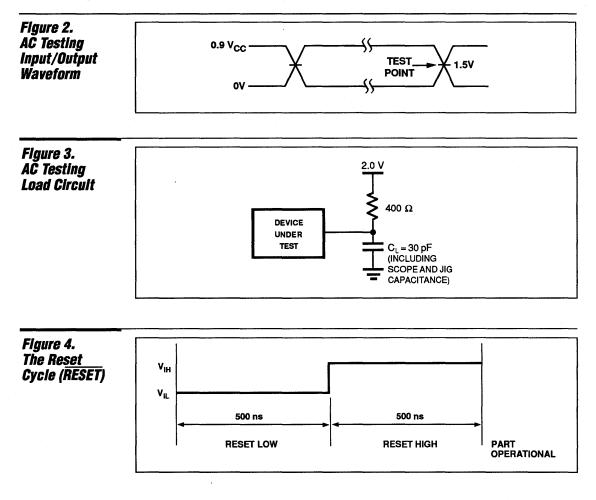

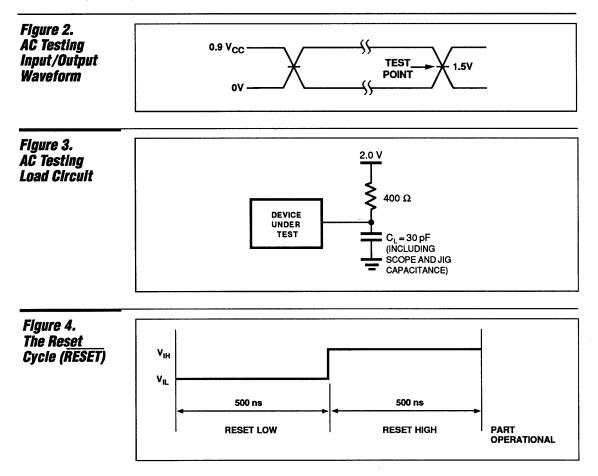

|                                | RESET                                                | 1    | The user-programmable pin can be configured to reset on high level (CRESET = 1) or on low level (CRESET = 0). It should remain active for at least 100 ns. See Tables 10a, 10b and 11 for the chip state after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

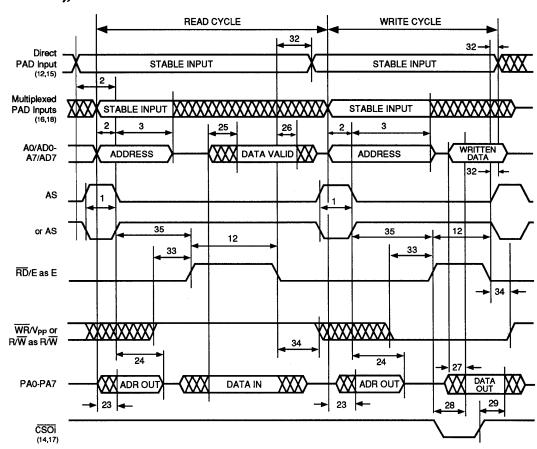

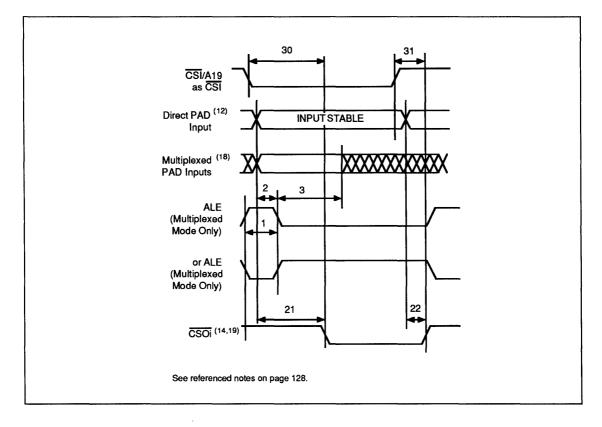

|                                | ALE<br>or<br>AS                                      | -    | In the multiplexed modes, the ALE pin functions as an Address<br>Latch Enable or as an Address strobe and can be configured as<br>an active high or active low signal. The ALE or AS trailing edge<br>latches lines AD15/A15–AD0/A0 and A16–A19 in 1 <u>6-bit</u> mode<br>(AD7/A7–AD0/A0 and A16–A19 in 8-bit mode) and BHE,<br>depending on the PSD3XX configuration. See Table 8. In the<br>non-multiplexed modes, it can be used as a general-purpose<br>logic input to the PAD.                                                                                                                                                                                                                                                                                                                                                                                                             |

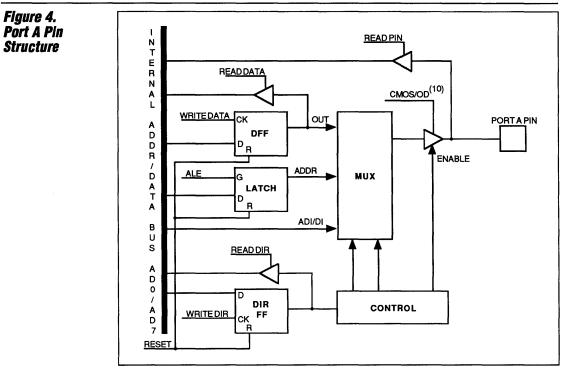

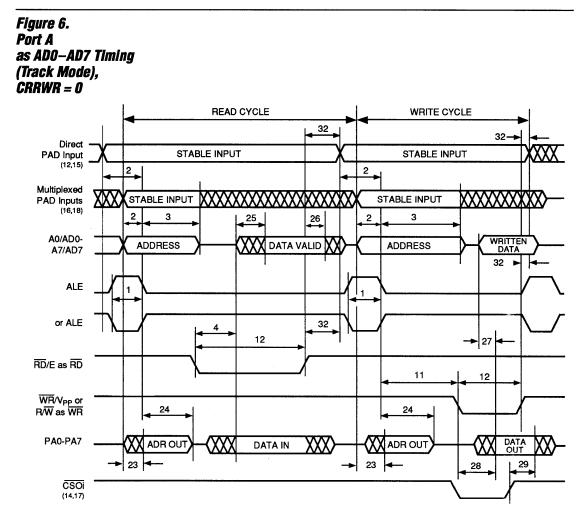

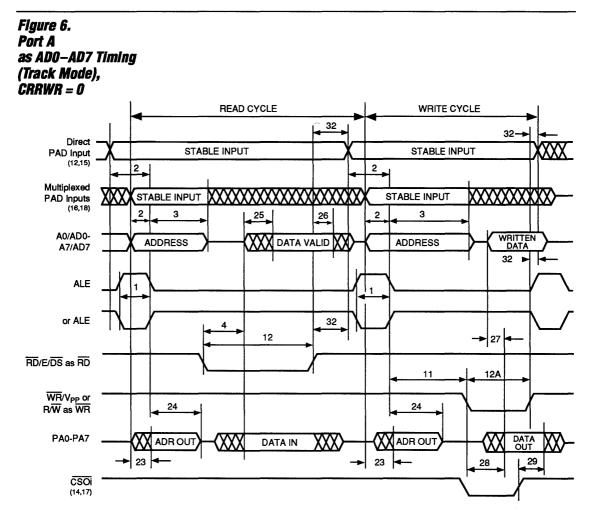

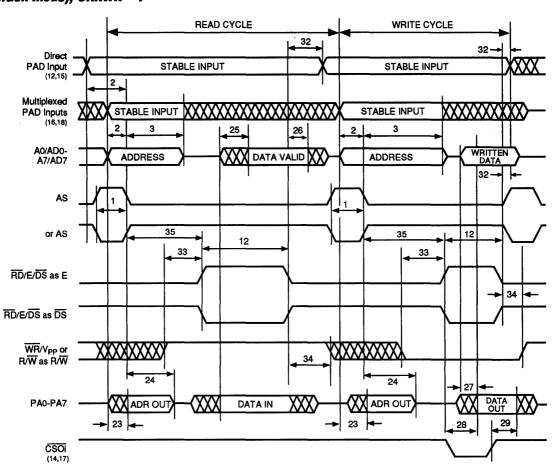

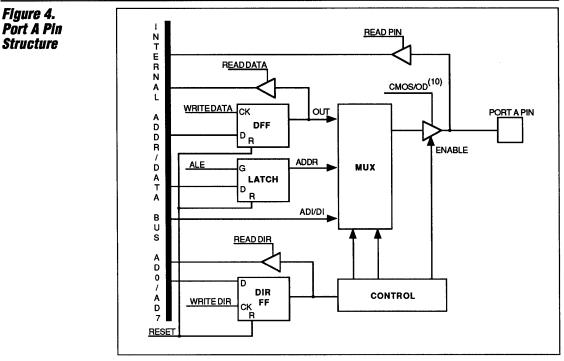

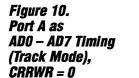

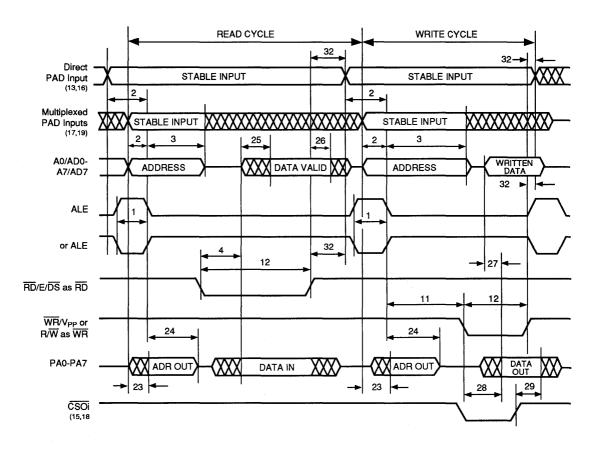

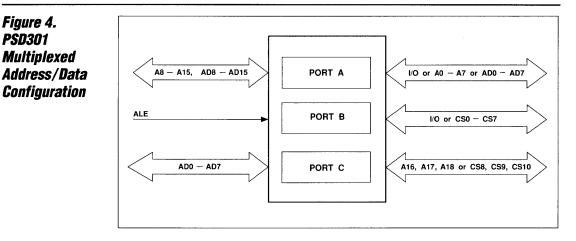

|                                | PA7<br>PA6<br>PA5<br>PA4<br>PA3<br>PA2<br>PA1<br>PA0 | I/O  | PA7–PA0 is an 8-bit port that can be configured to track<br>AD7/A7–AD0/A0 from the input (CPAF2 = 1). Otherwise<br>(CPAF2 = 0), each bit can be configured separately as an I/O or<br>lower-order latched address line. When configured as an I/O<br>(CPAF1 = 0), the direction of the pin is defined by its direction bit,<br>which resides in the direction register. If a pin is an I/O output, its<br>data bit (which resides in the data register) comes out. When it is<br>configured as a low-order address line (CPAF1 =1), A7–A0<br>can be made the corresponding output through this port (e.g., PA6<br>can be configured to be the A6 address line). Each port bit<br>can be a CMOS output (CPACOD = 0) or an open drain output<br>(CPACOD = 1). When the chip is in non-multiplexed mode<br>(CADDRAT = 0), the port becomes the data bus lines (D0–D7).<br>See Figure 4.            |

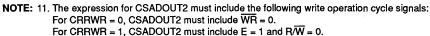

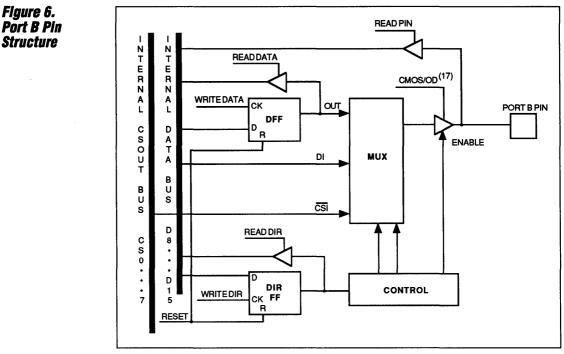

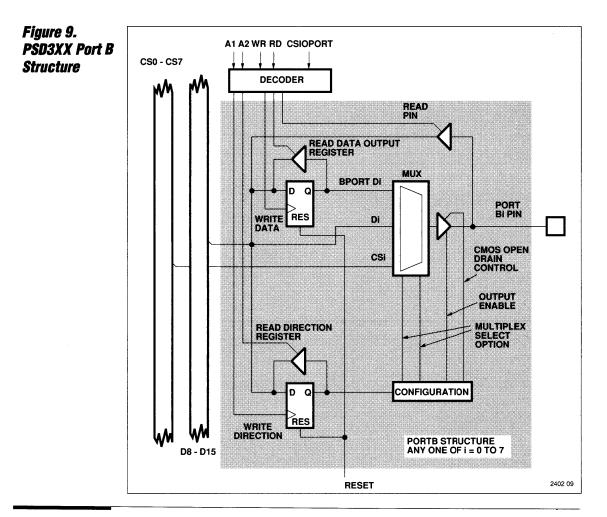

|                                | PB7<br>PB6<br>PB5<br>PB4<br>PB3<br>PB2<br>PB1<br>PB0 | I/O  | PB7–PB0 is an 8-bit port for which each bit can be configured as<br>an I/O (CPBF = 1) or chip-select output (CPBF = 0). Each port bit<br>can be a CMOS output (CPBCOD = 0) or an open drain output<br>(CPBCOD = 1). When configured as an I/O, the direction of the<br>pin is defined by its direction bit, which resides in the direction<br>register. If a pin is an I/O output, its data (which resides in the data<br>register) comes out. When configured as a chip-select output,<br>$\overline{CS0}$ – $\overline{CS3}$ are a function of up to four product terms of the inputs to<br>the PAD B; $\overline{CS4}$ ,– $\overline{CS7}$ then are each a function of up to two<br>product terms. On the PSD301L/302L/303L, when the chip is in<br>non-multiplexed mode (CADDRAT = 0) and the data bus width is<br>16 (CDATA = 1), the port becomes the data bus (D8–D15).<br>See Figure 6. |

| Table 1.<br>PSD3XX Pin                | Name                                                                                     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------|------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

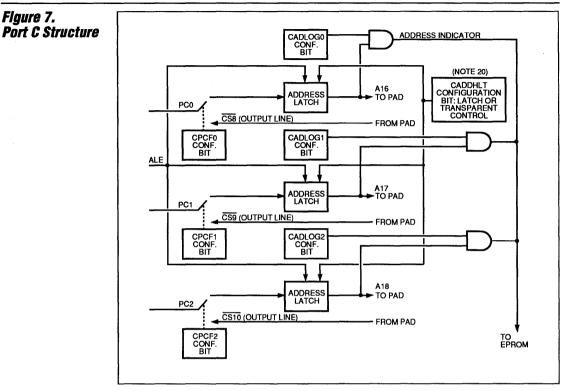

| PSDSXX FIN<br>Descriptions<br>(Cont.) | PC0<br>PC1<br>PC2                                                                        | 1/0  | This is a 3-bit port for which each bit is configurable as a PAD A<br>and B input or output. When configured as an input (CPCF = 0),<br>a bit individually becomes an address (CADLOG = 1) or a logic<br>input (CADLOG = 0). The addresses can be latched with ALE<br>(CADDHLT = 1) or be transparent inputs to the PADs<br>(CADDHLT = 0). When a pin is configured as an output (CPCF = 1),<br>it is a function of one product term of all PAD inputs.<br>See Figure 7. |

|                                       | AD0/A0<br>AD1/A1<br>AD2/A2<br>AD3/A3<br>AD4/A4<br>AD5/A5<br>AD6/A6<br>AD7/A7             | I/O  | In multiplexed mode, these pins are the multiplexed low-order<br>address/data byte. After ALE latches the addresses, these<br>pins input or output data, depending on the settings of the $\overline{RD}/E$<br>( $\overline{RD}/E/\overline{DS}$ on the PSD302/303), $\overline{WR}/V_{PP}$ or $R/\overline{W}$ , and $\overline{BHE}/\overline{PSEN}$<br>pins. In non-multiplexed mode, these pins are the low-order<br>address input.                                  |

|                                       | AD8/A8<br>AD9/A9<br>AD10/A10<br>AD11/A11<br>AD12/A12<br>AD13/A13<br>AD14/A14<br>AD15/A15 | I/O  | In 16-bit multiplexed mode, these pins are the multiplexed<br>high-order address/data byte. After ALE latches the addresses, these<br>pins input or output data, depending on the settings of the $\overline{RD}/E$ or<br>$\overline{RD}/E/DS$ , $\overline{WR}/V_{PP}$ or $R/W$ , and $\overline{BHE}/\overline{PSEN}$ pins. In all other modes,<br>these pins are the high-order address input.                                                                        |

|                                       | GND                                                                                      | Р    | V <sub>SS</sub> (ground) pin.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                       | V <sub>cc</sub>                                                                          | Р    | Supply voltage input.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

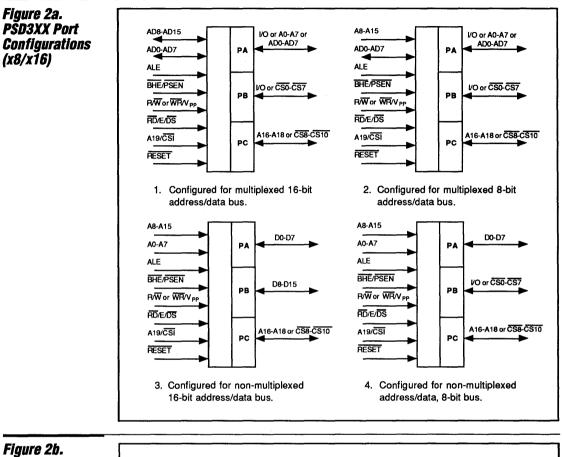

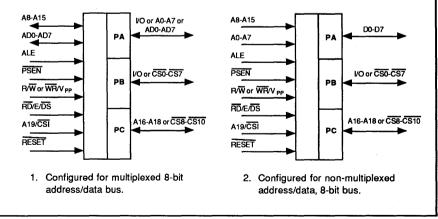

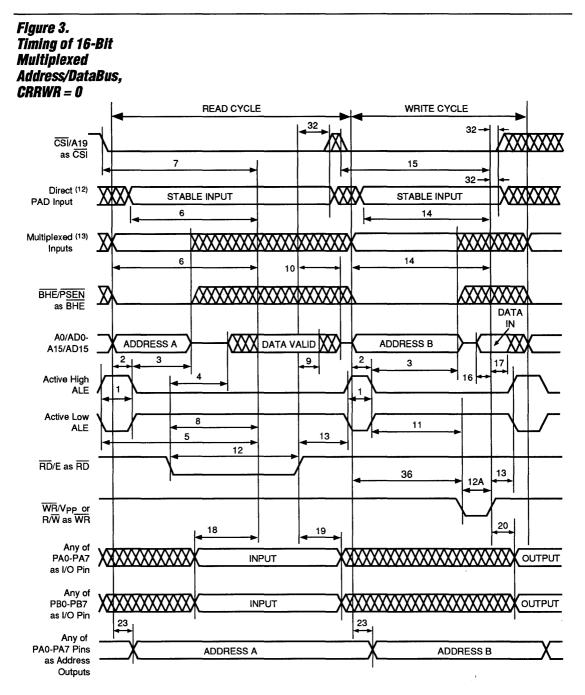

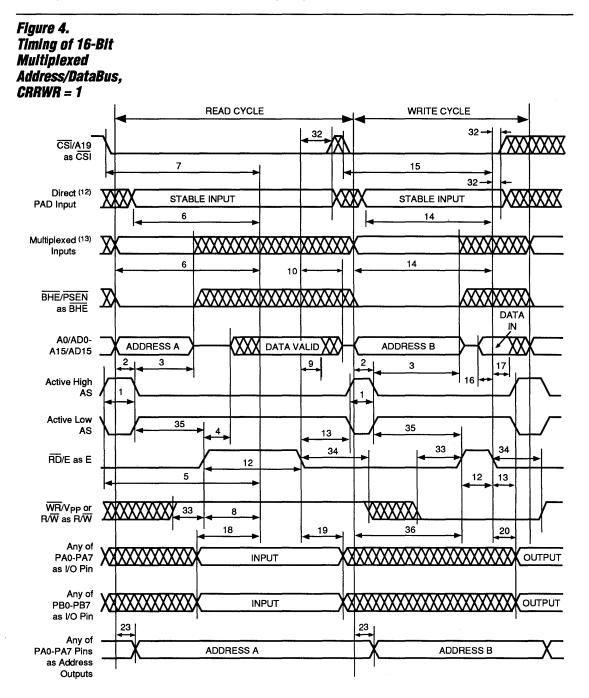

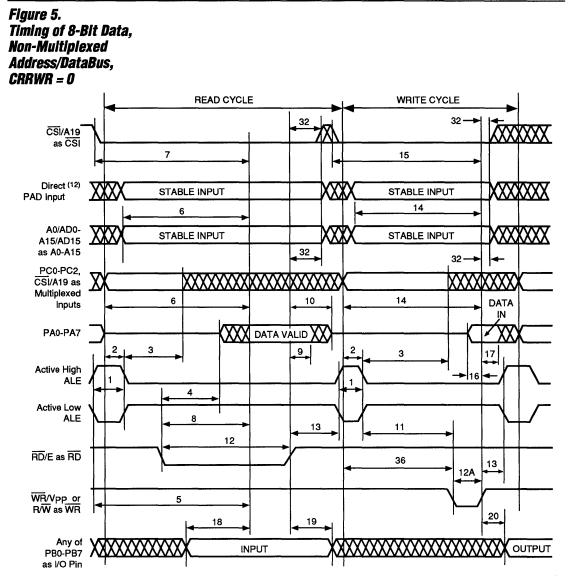

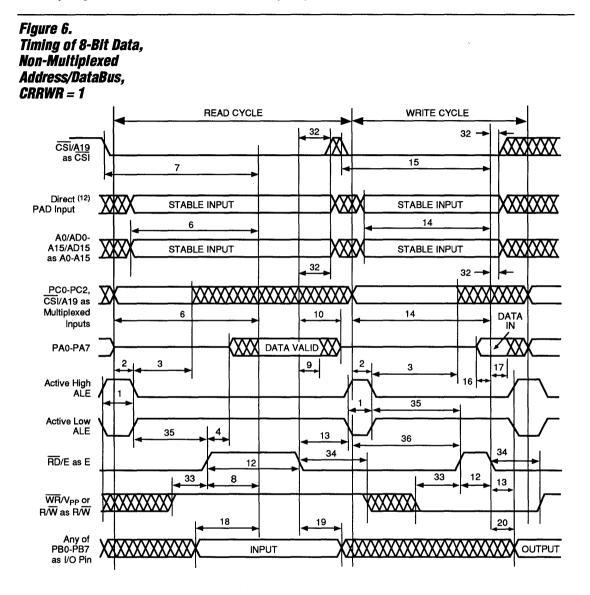

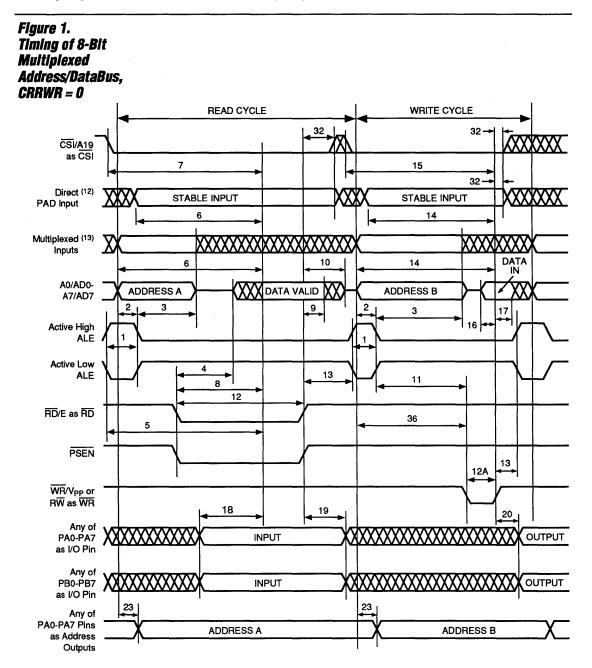

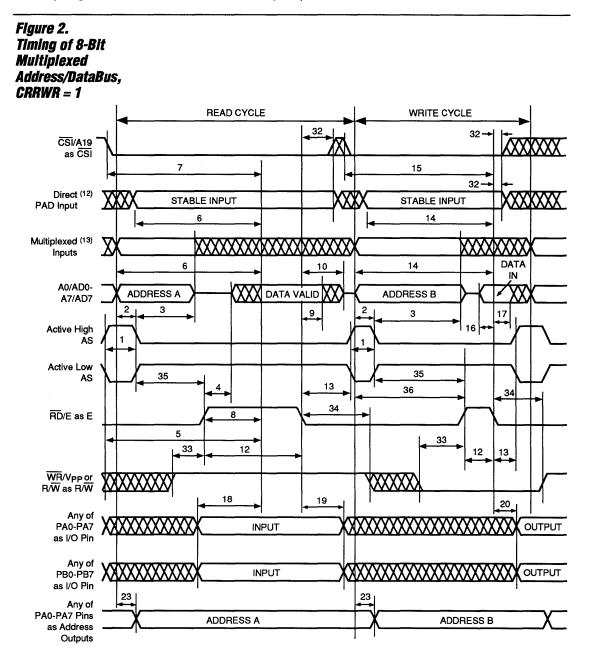

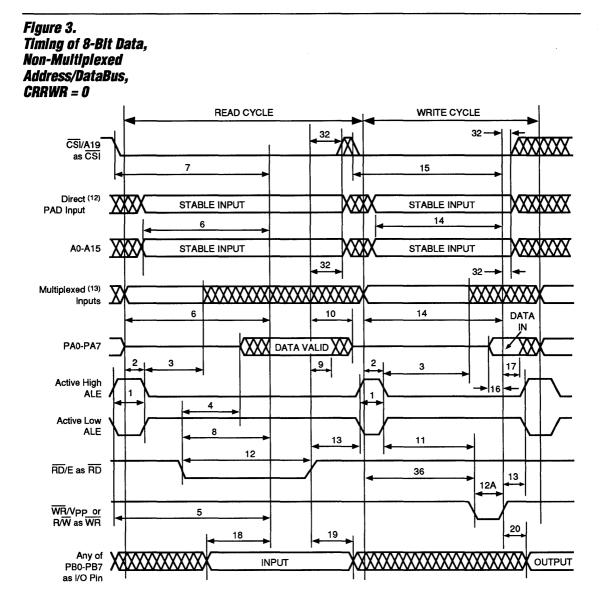

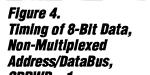

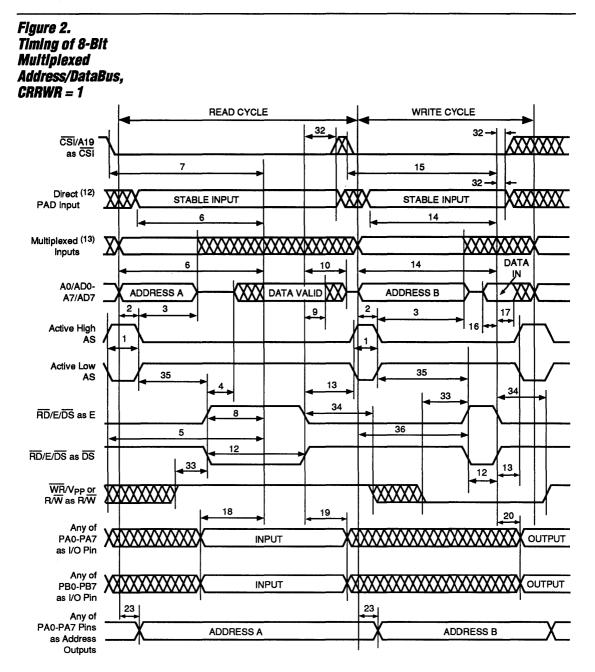

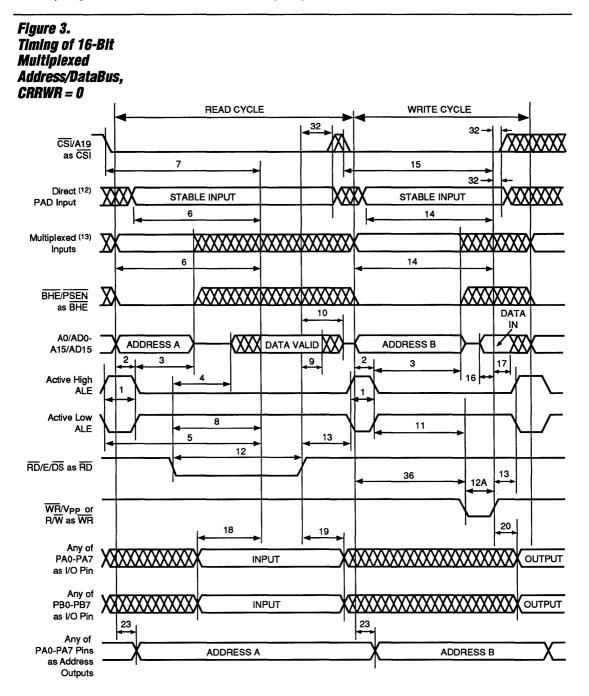

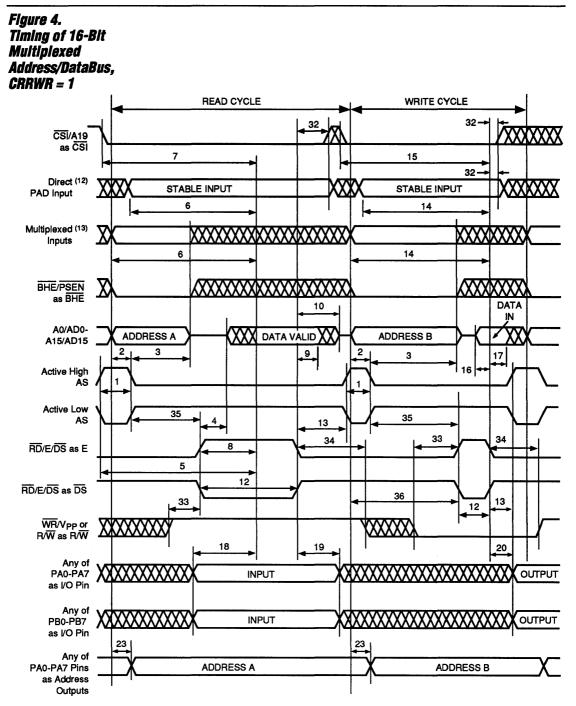

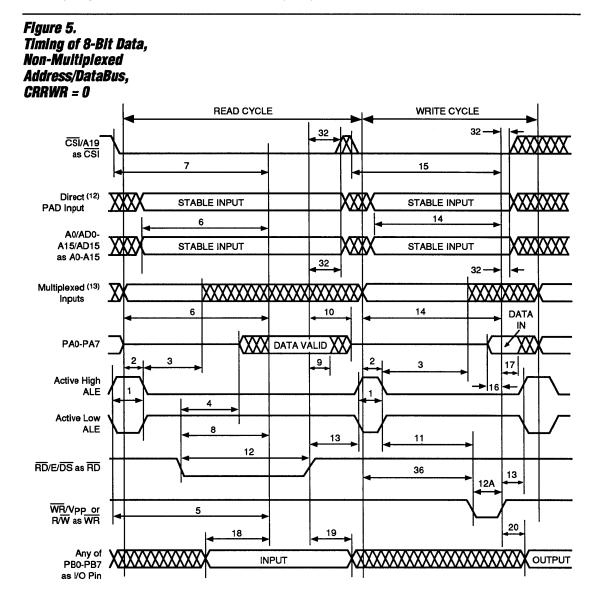

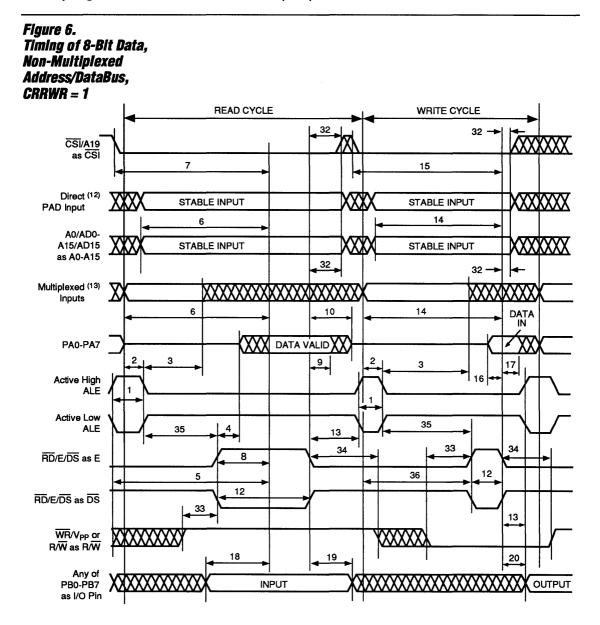

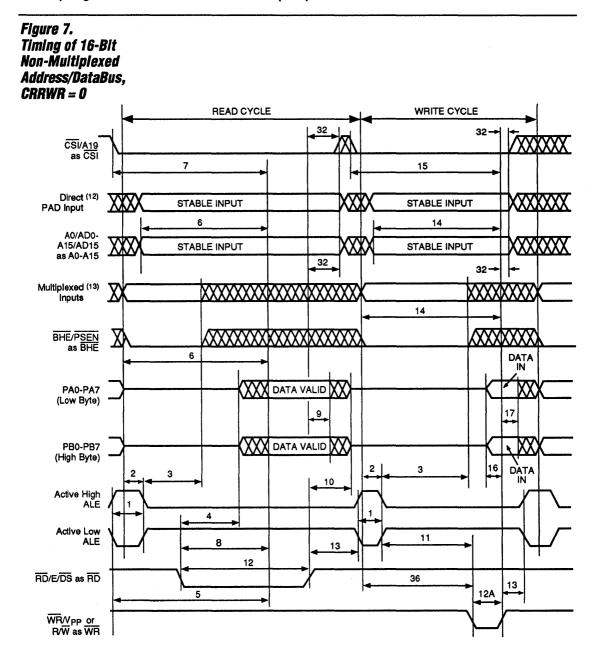

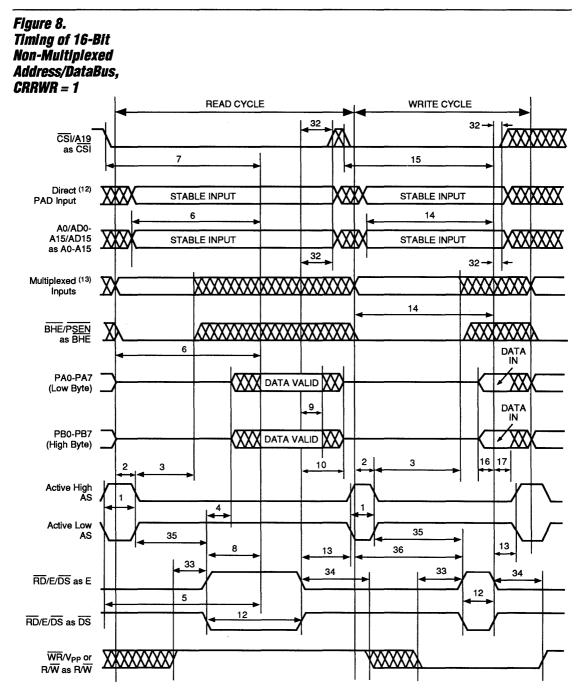

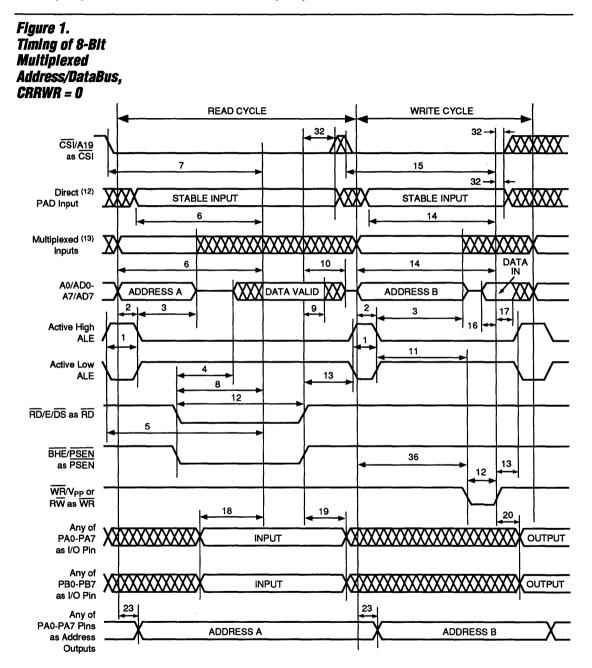

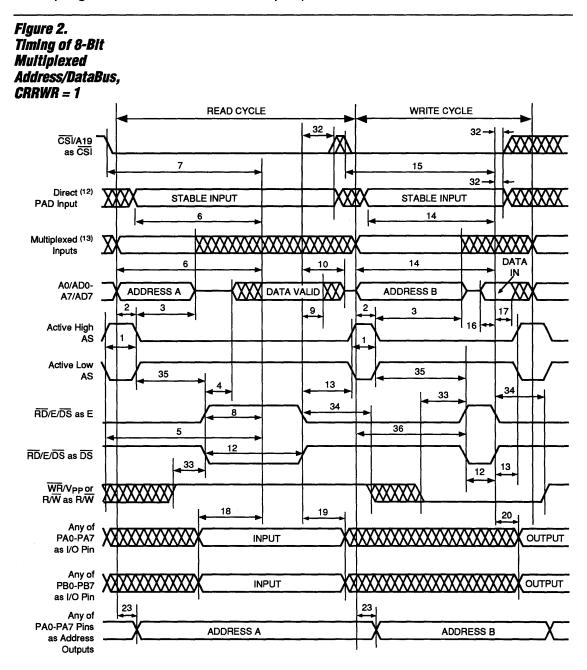

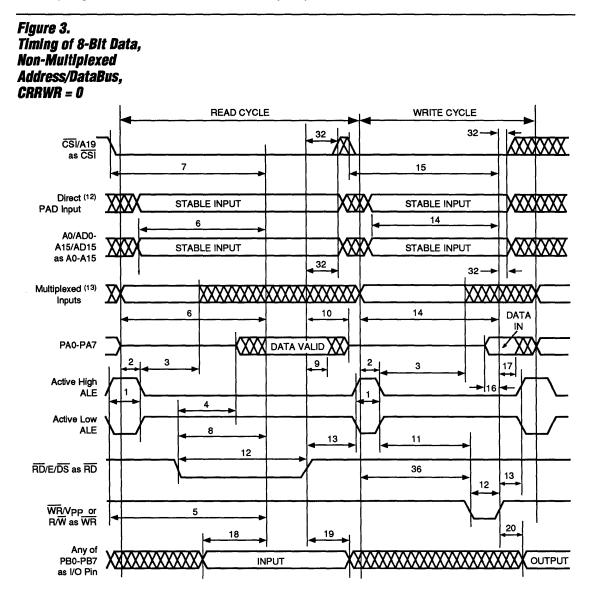

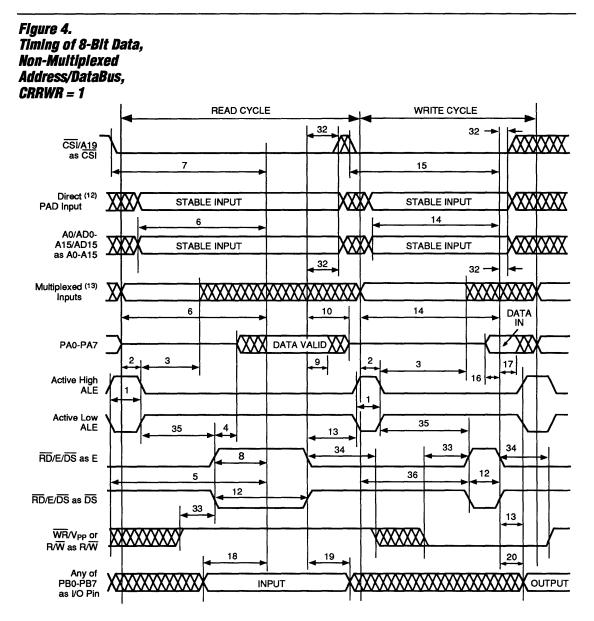

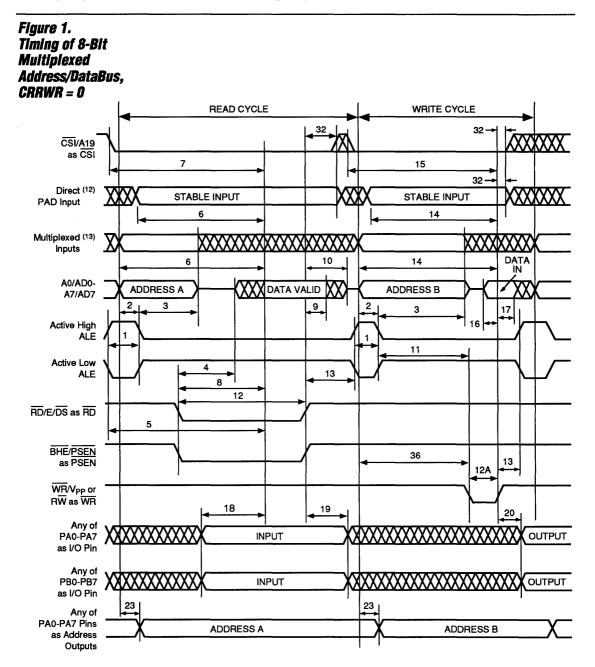

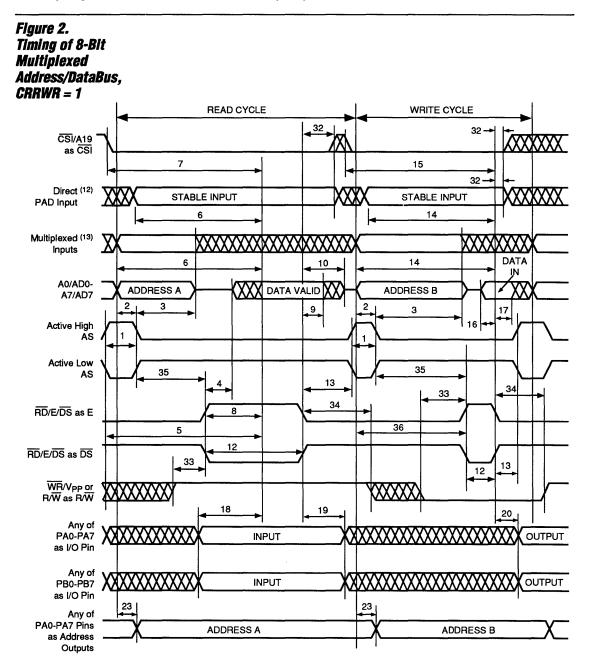

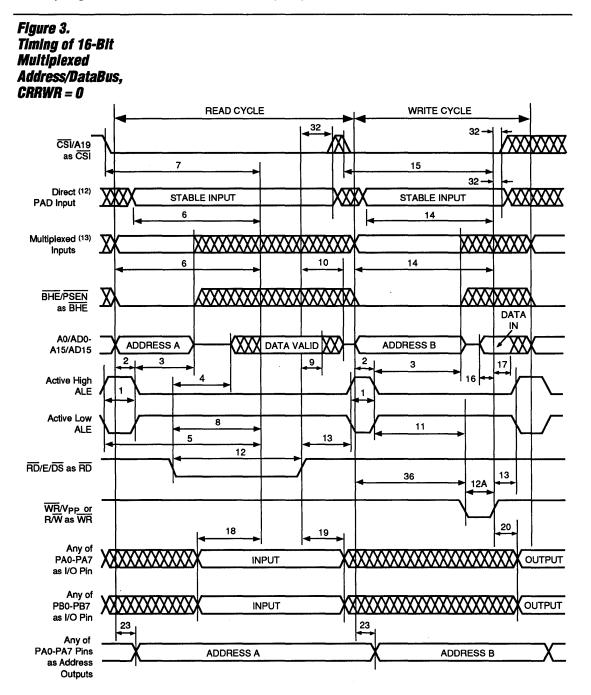

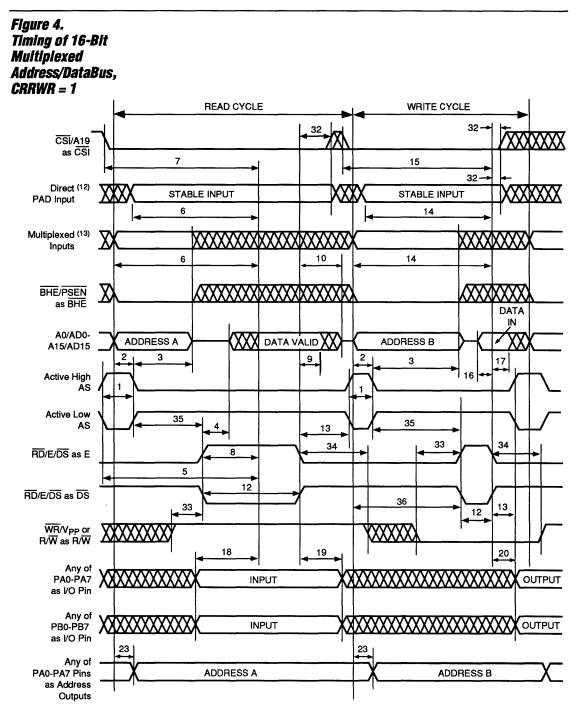

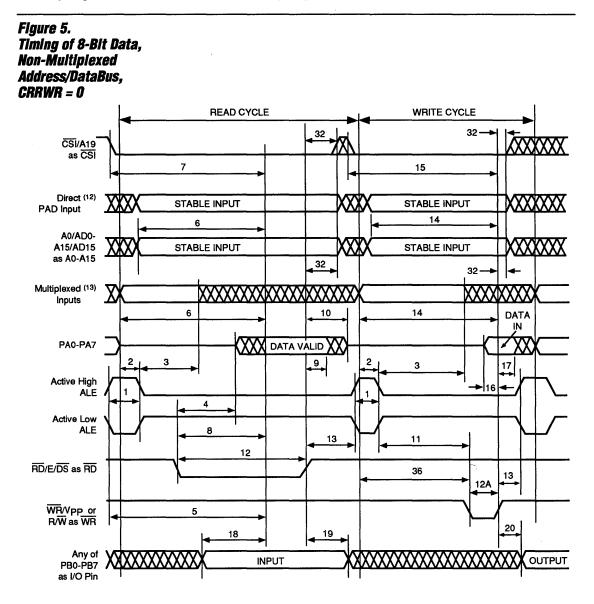

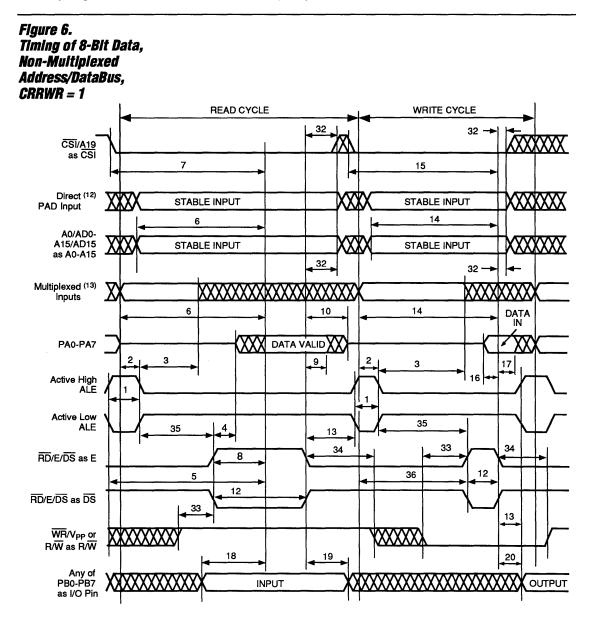

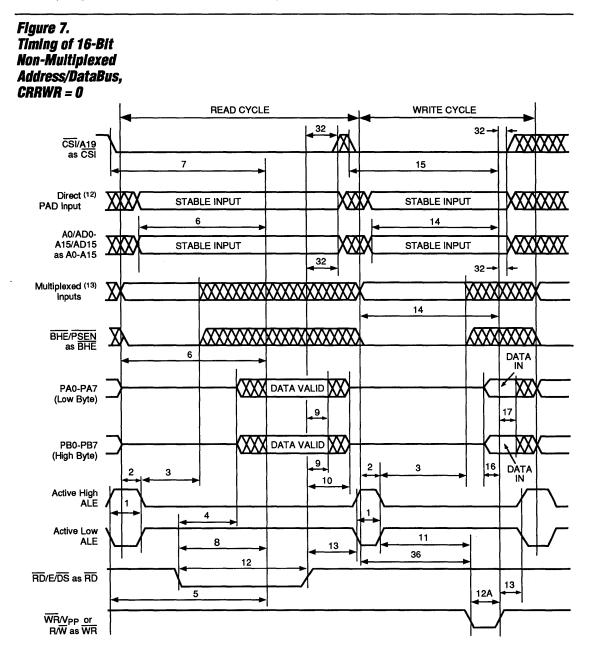

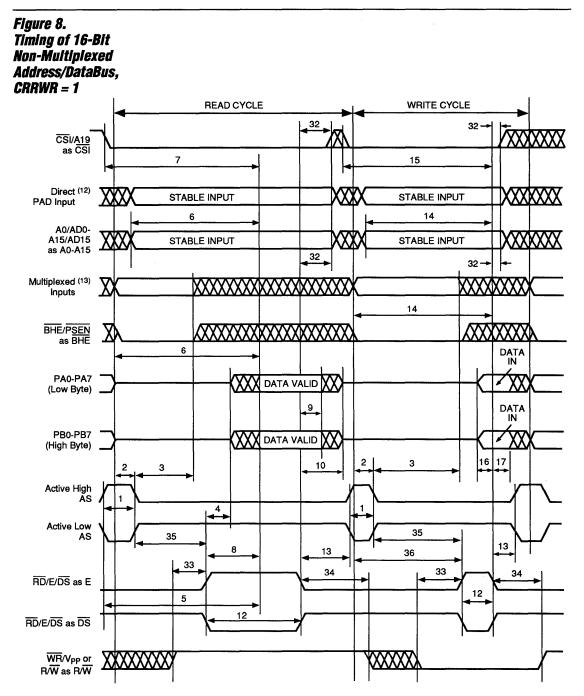

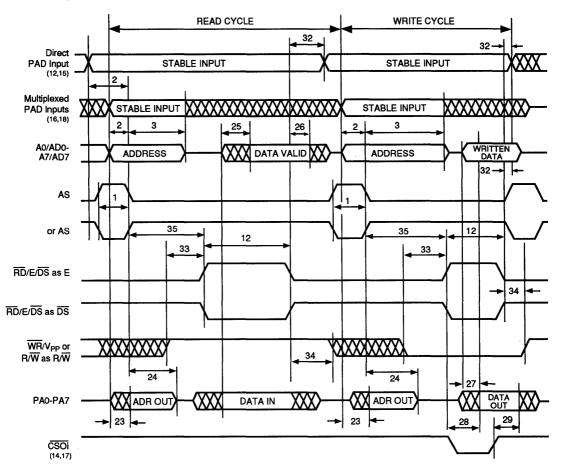

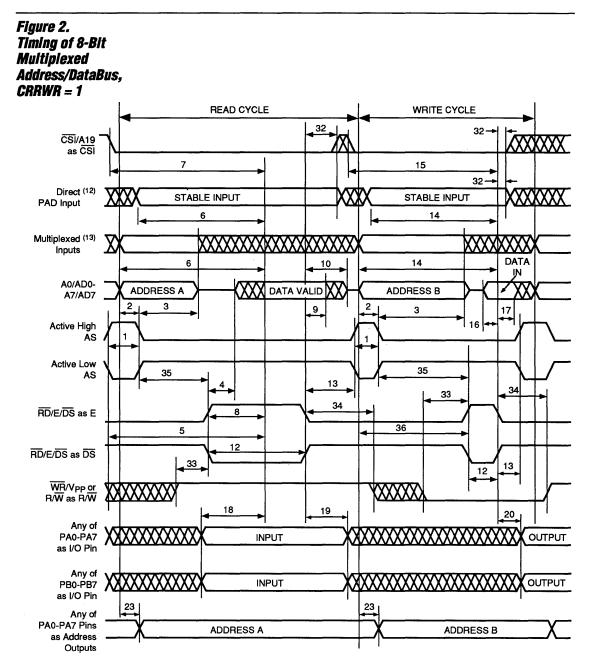

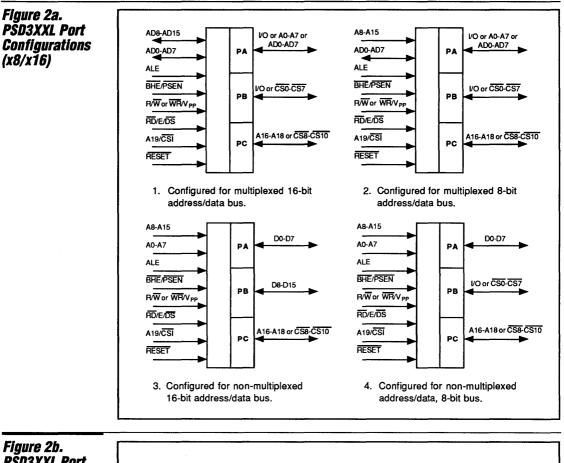

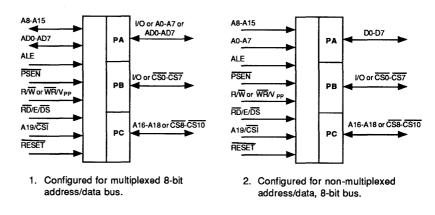

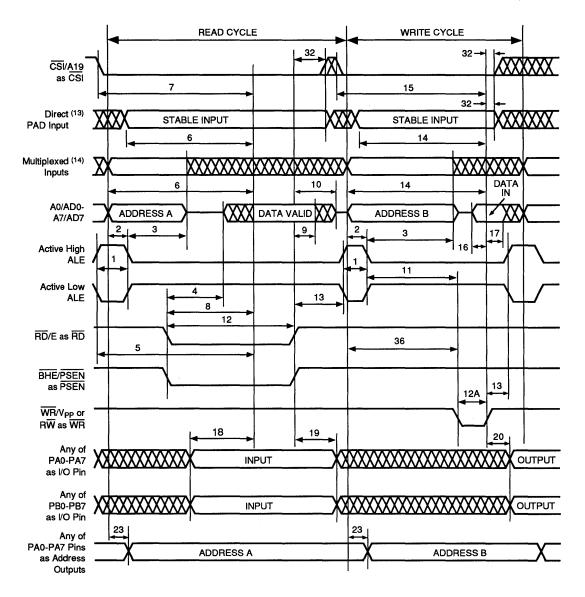

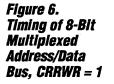

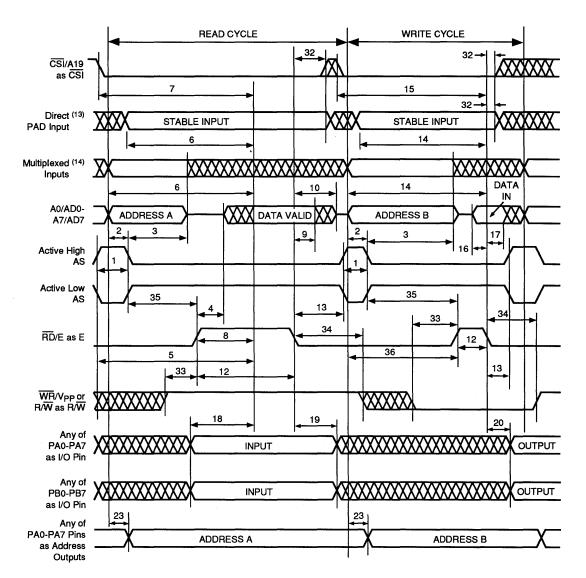

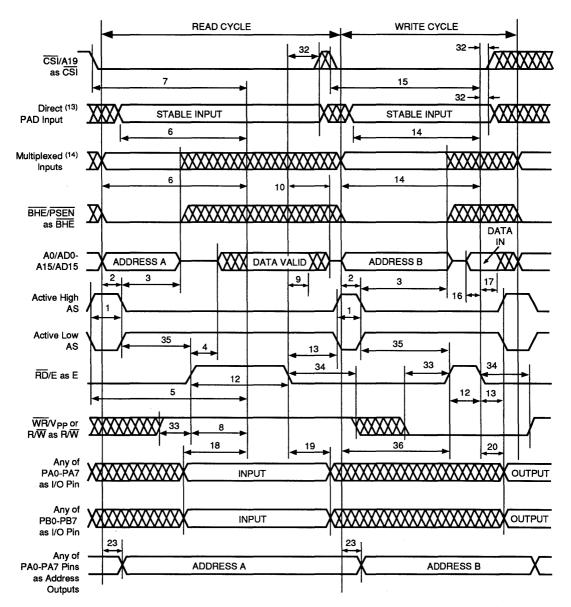

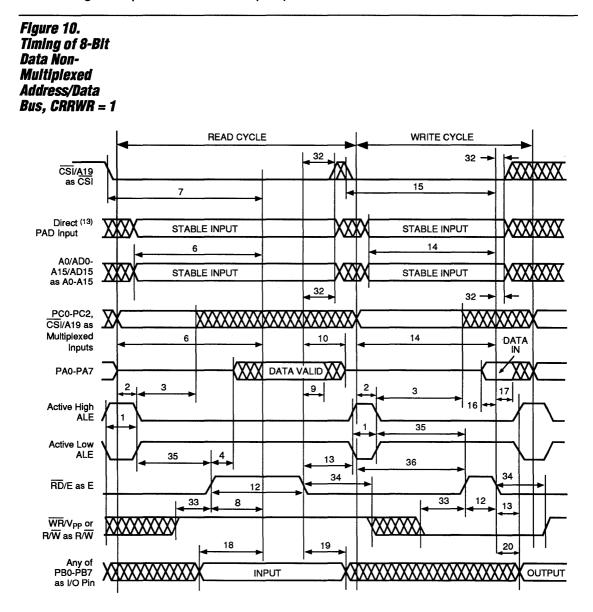

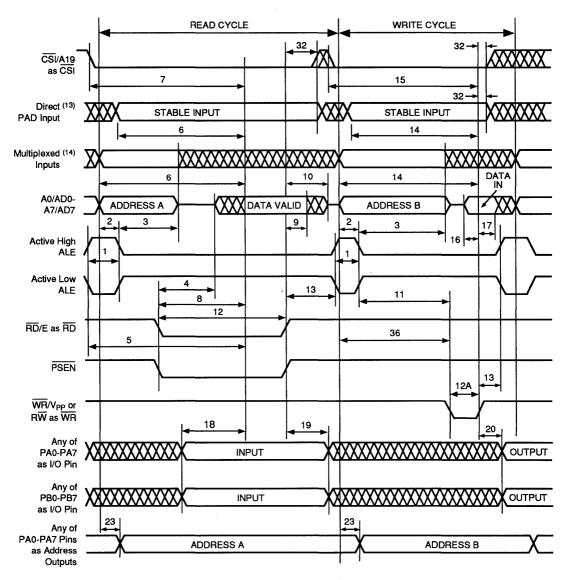

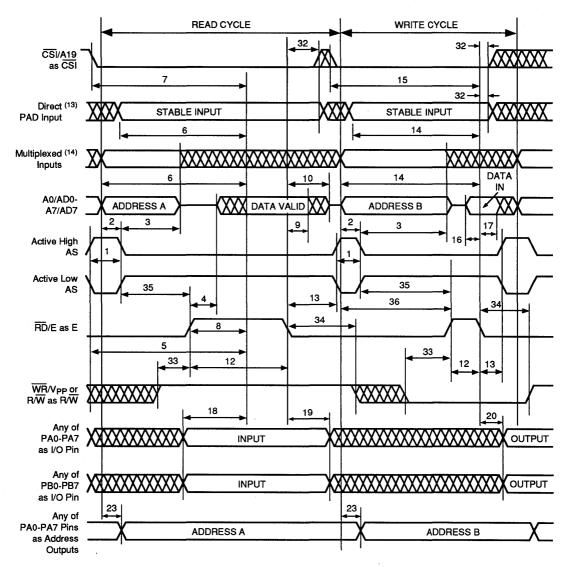

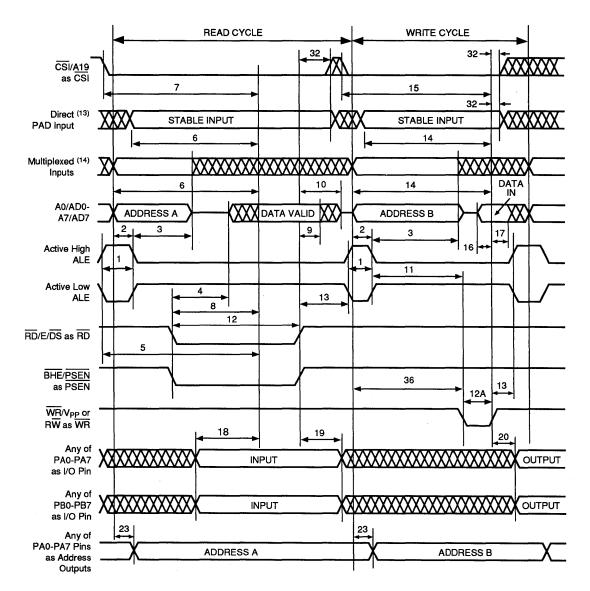

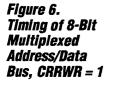

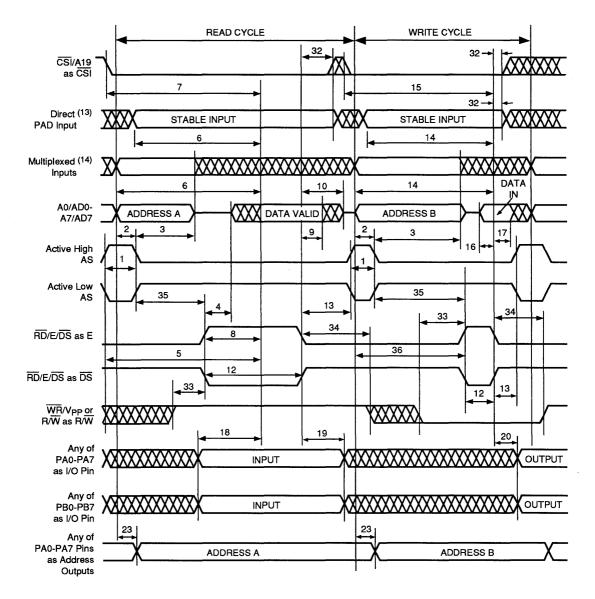

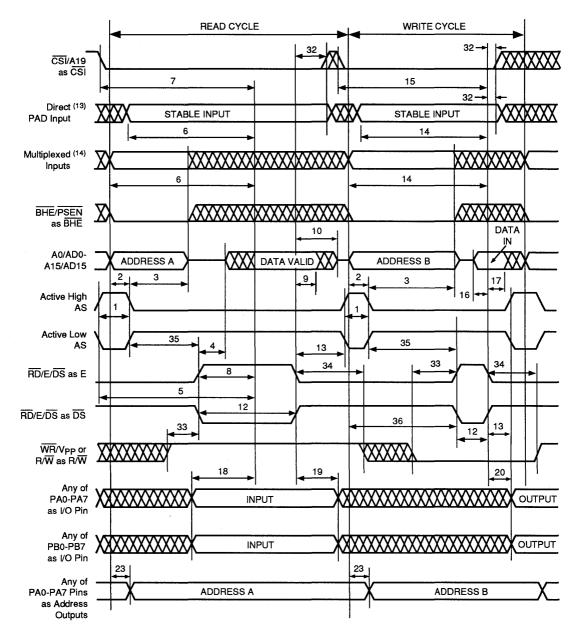

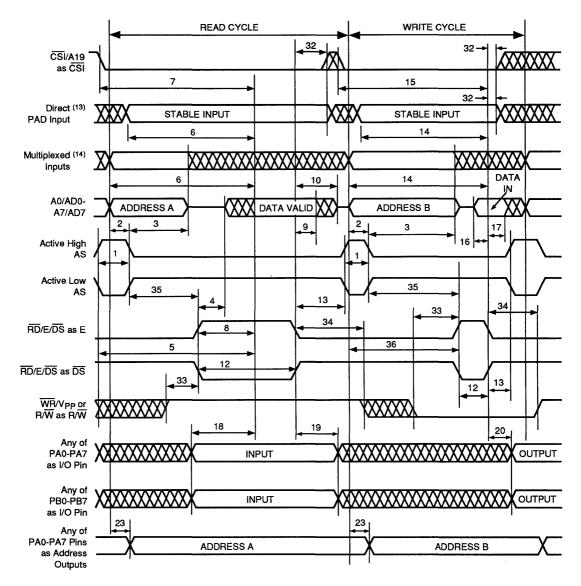

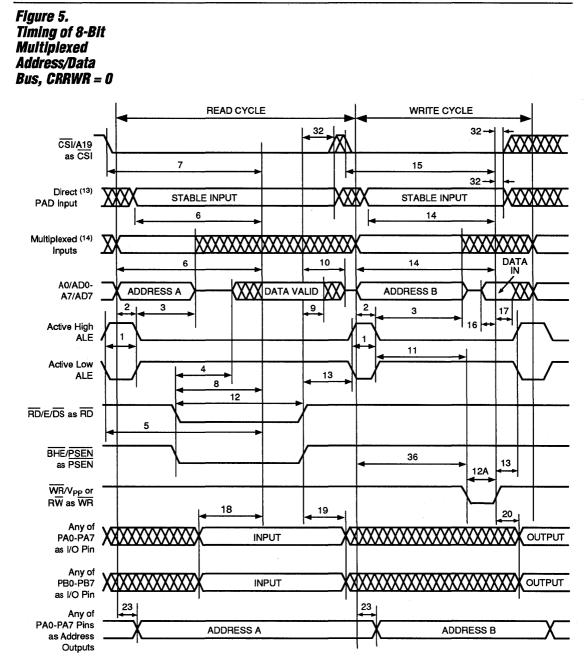

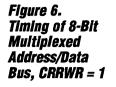

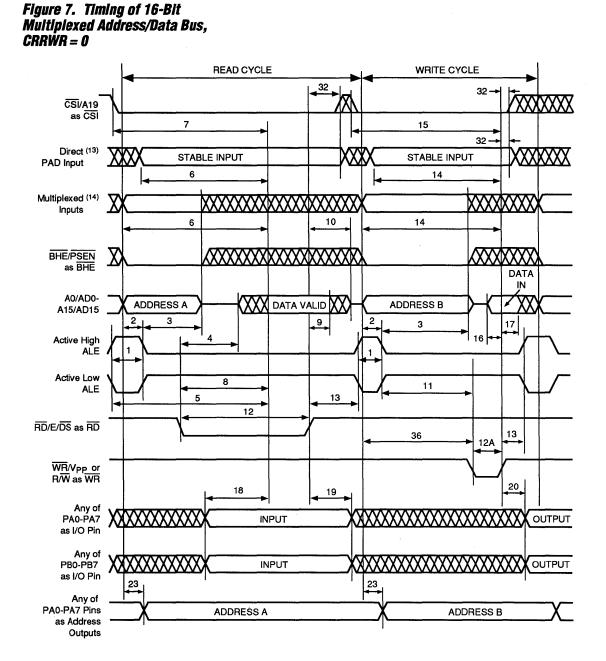

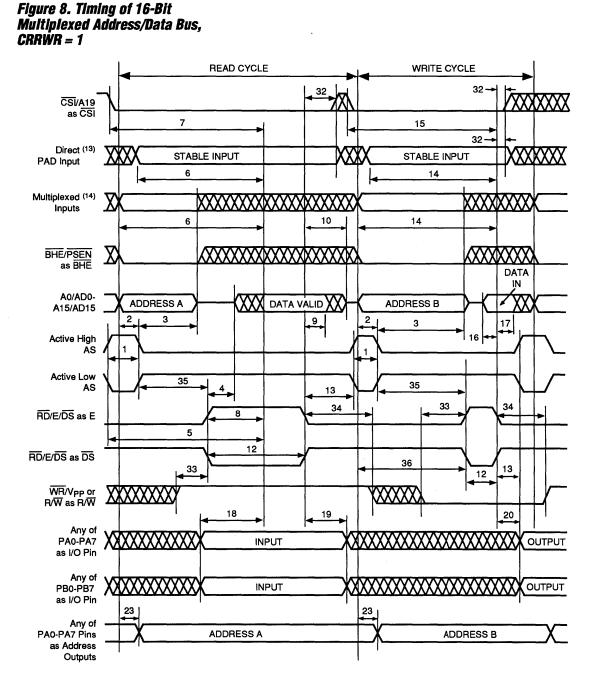

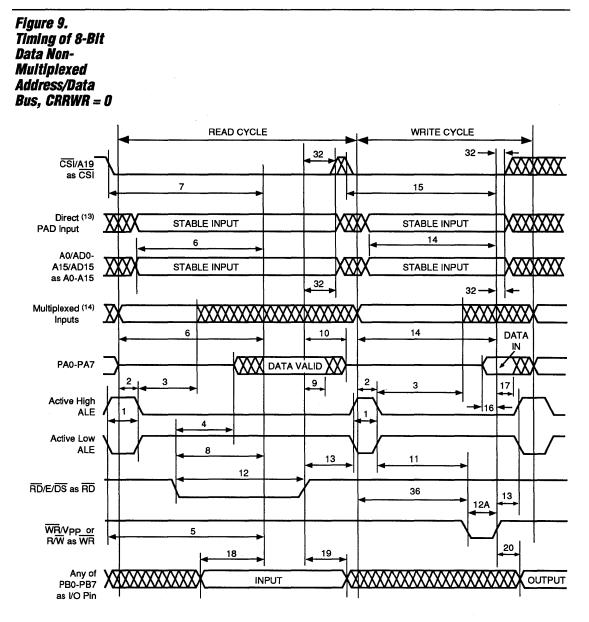

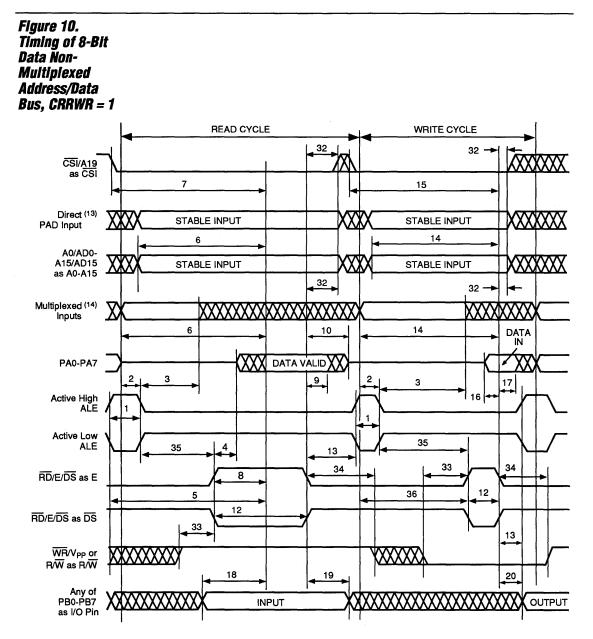

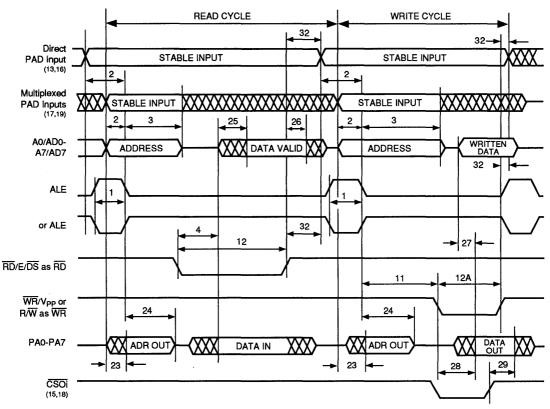

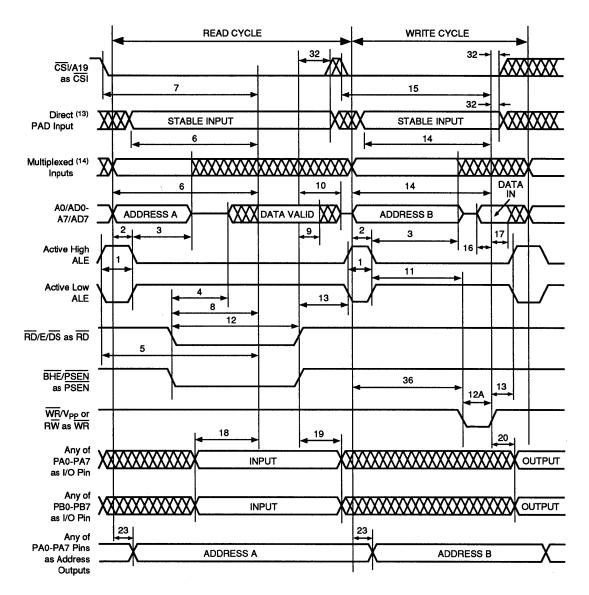

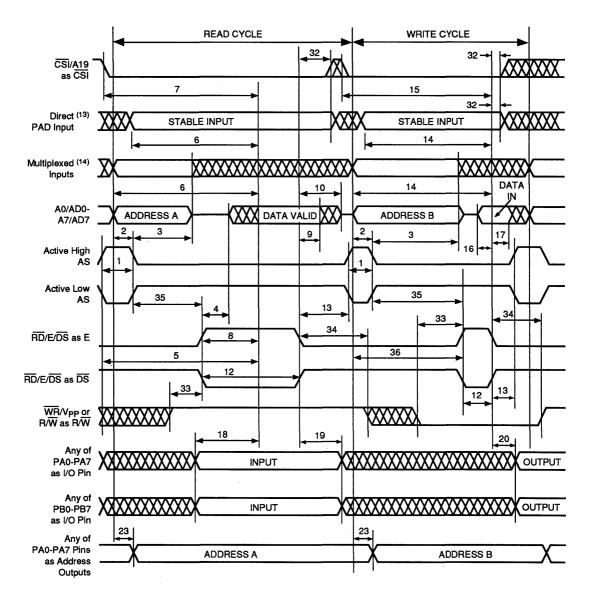

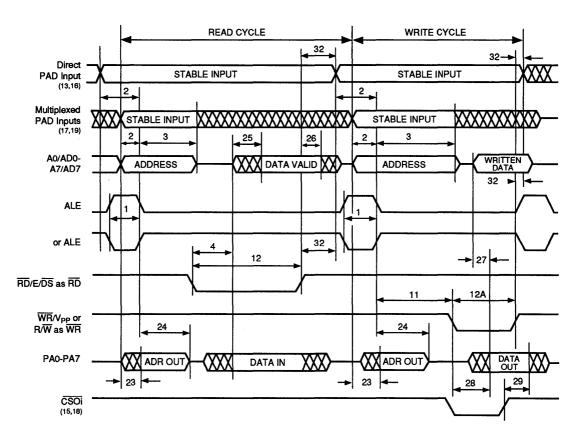

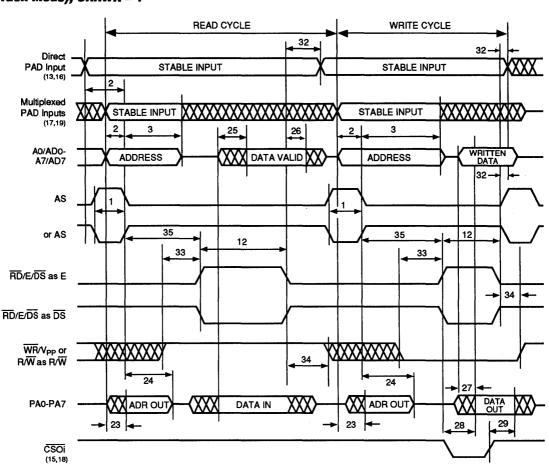

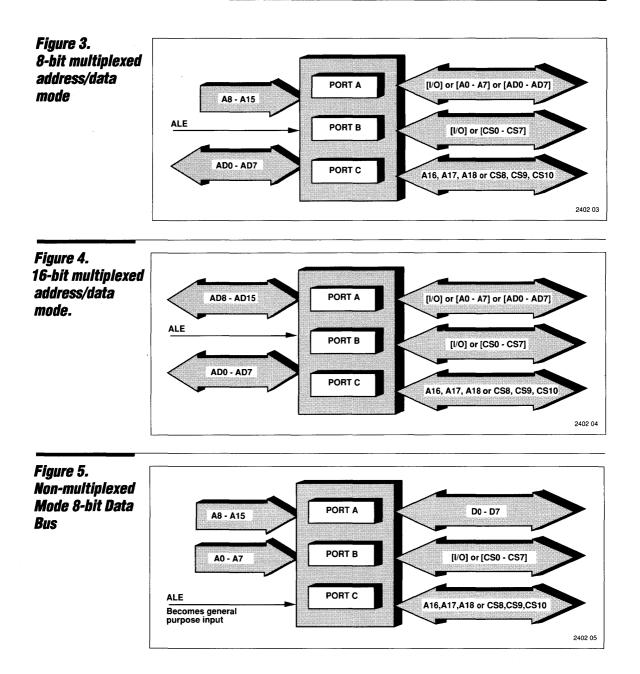

#### Operating The PSD3XX's four operating modes enable it to interface directly to 8- and 16-bit microcontrollers with multiplexed and non-multiplexed address/data buses. These operating modes are: Multiplexed 8-bit address/data bus

- Multiplexed 16-bit address/data bus (PSD30X)

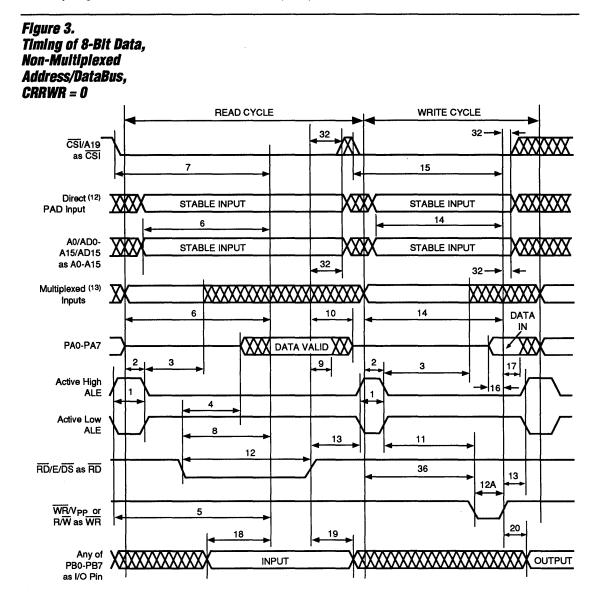

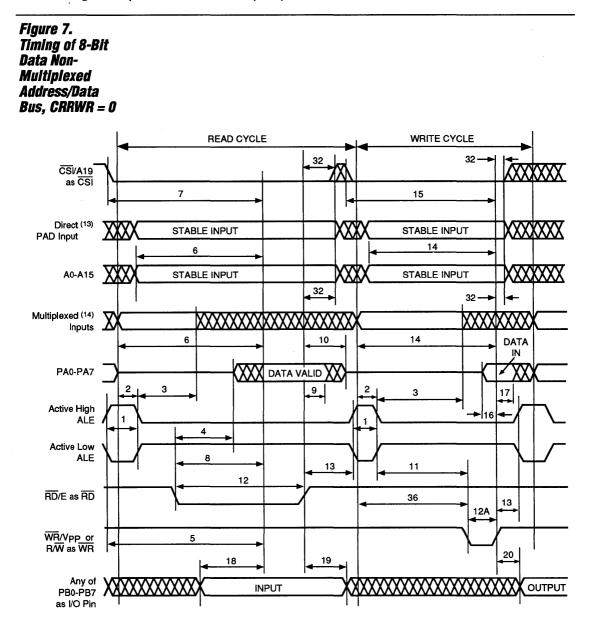

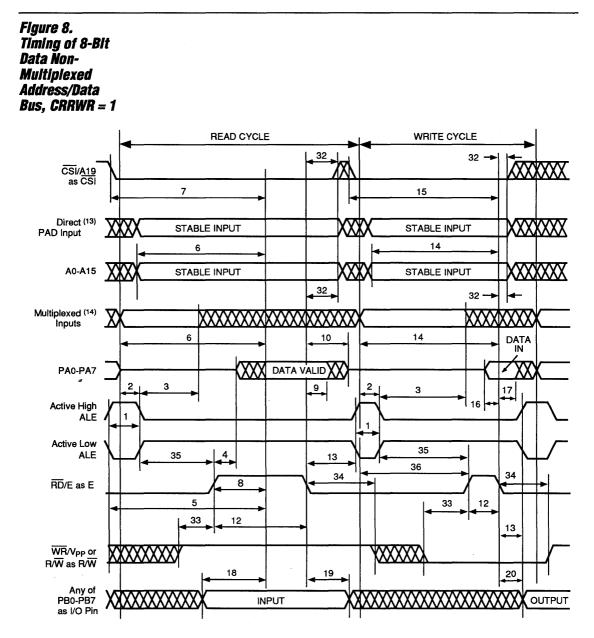

- Non-multiplexed address/data, 8-bit data bus

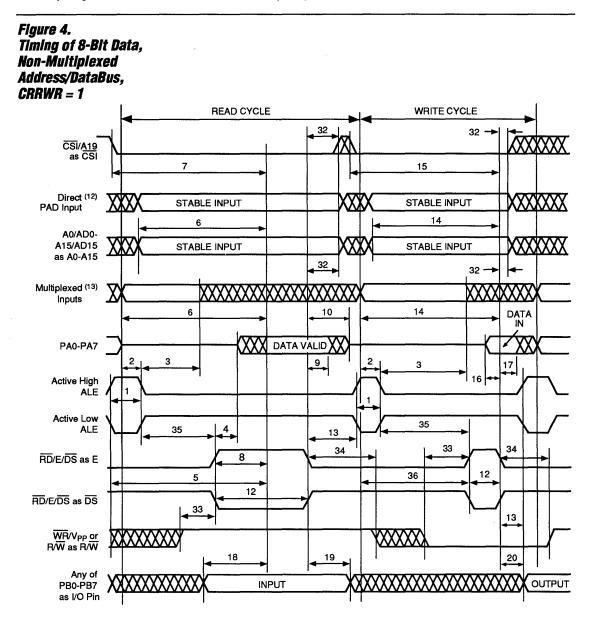

- Non-multiplexed 16-bit address/ data bus (PSD30X)

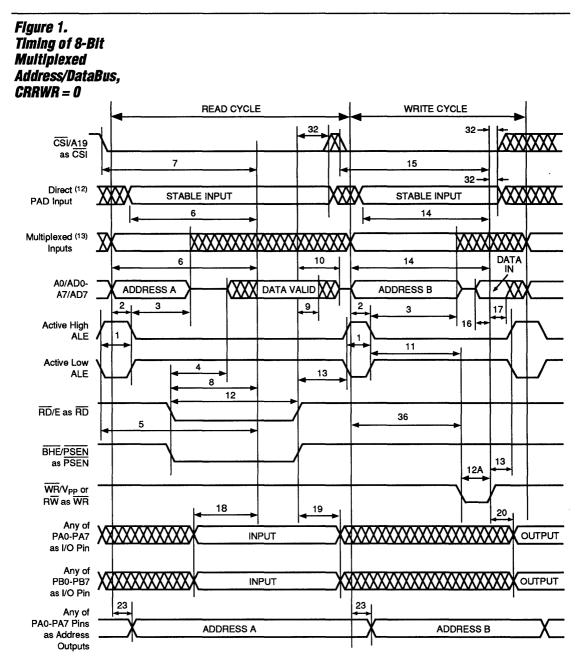

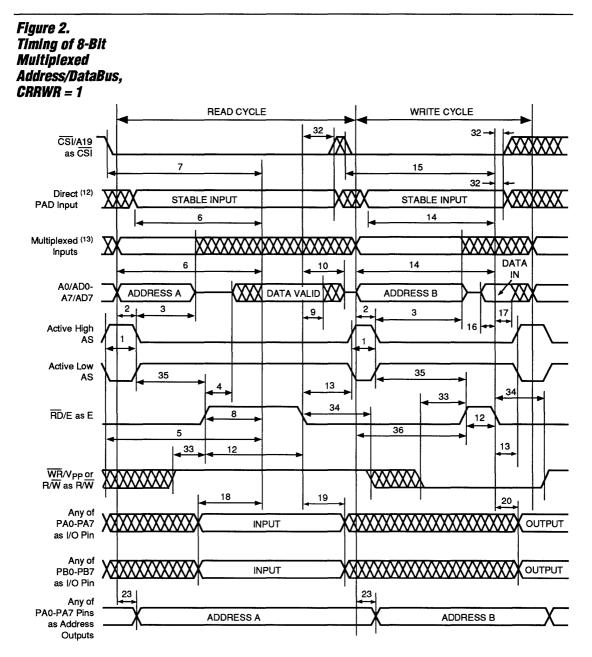

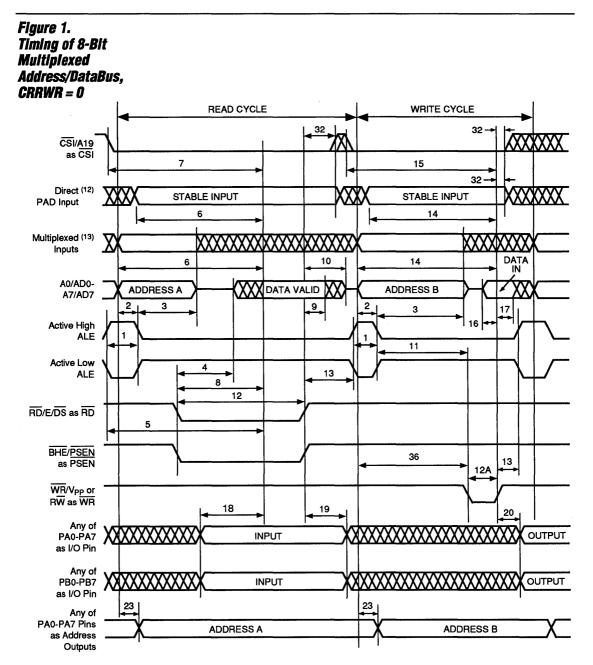

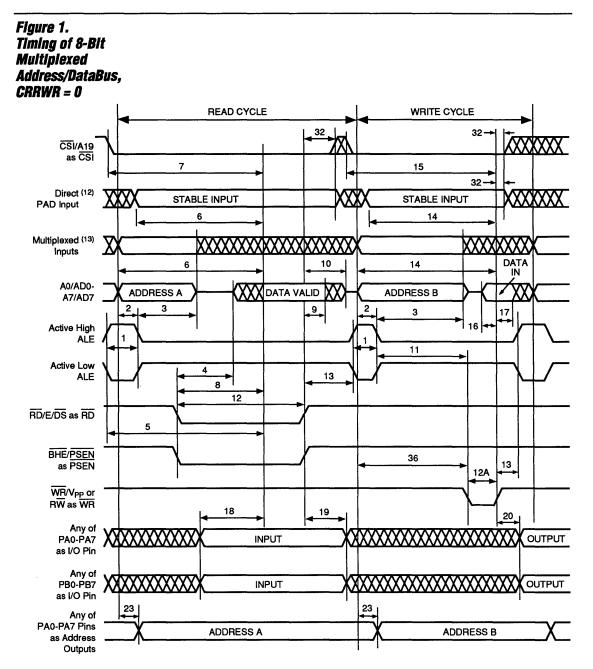

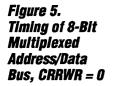

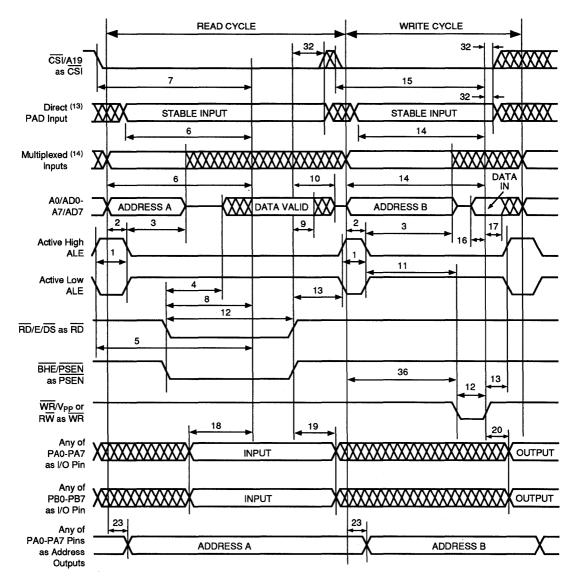

#### Multiplexed 8-bit Address/Data Bus

This mode is used to interface to microcontrollers with an 8-bit data bus and a 16-bit or larger address bus. The address/data bus (AD0/A0-AD7/A7) is bi-directional and permits the latching of the address when the ALE signal is active. On the same pins, the data is read from or written to the device; this depends on the state of the  $\overline{RD}/E$  or  $\overline{RD}/E/\overline{DS}$  pin, BHE/PSEN or PSEN pin and WR/VPP or R/W pins. The high-order address/data bus (AD8/A8-AD15/A15) contains the highorder address bus byte. Ports A and B can be configured as in Table 2.

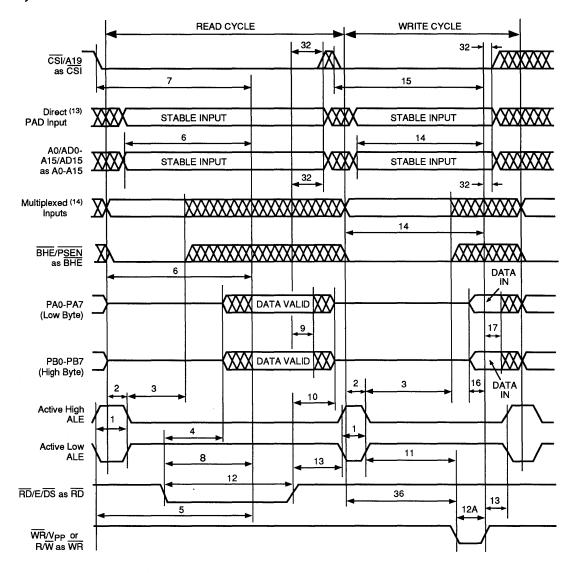

#### Multiplexed 16-bit Address/Data Bus

This mode is used to interface to microcontrollers with a 16-bit data bus and a 16bit or larger address bus. The low-order address/data bus (AD0/A0-AD7/A7) is bi-directional and permits the latching of the address when the ALE signal is active. On the same pins, the data is read from or written to the device; this depends on the state of the RD/E/DS, BHE/PSEN, and WR/VPP or R/W pins. The high-order address/data bus (AD8/A8-AD15/A15) is bi-directional and permits latching of the high-order address when the ALE signal is active on the same pins. The high-order data bus is read from or written to the device, depending on the state of the RD/E/DS, BHE/PSEN, and WR/VPP or R/W pins. Ports A and B can be configured as in Table 2.

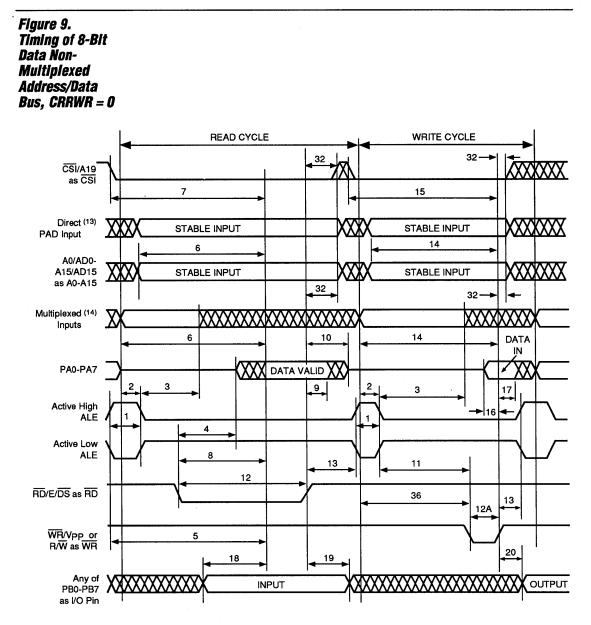

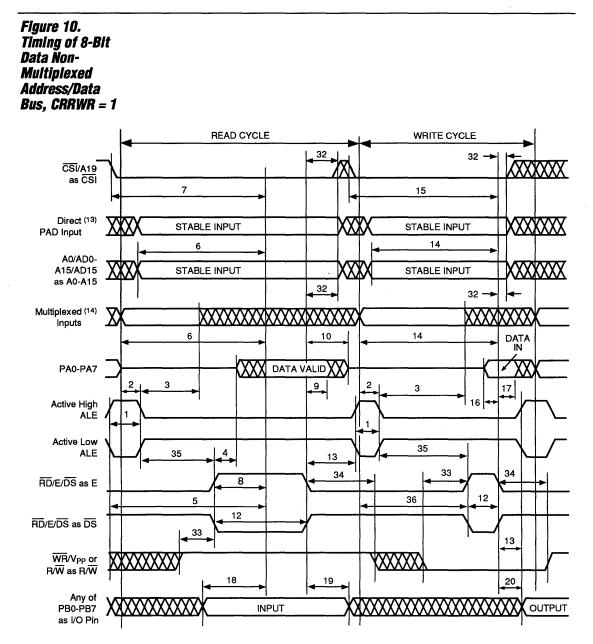

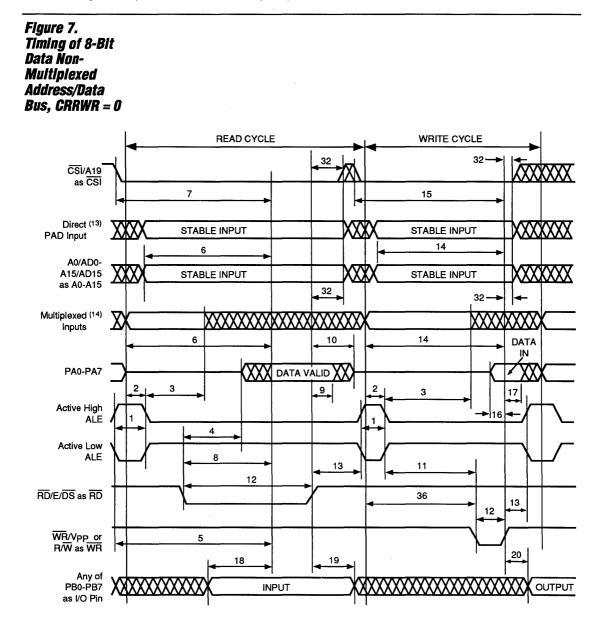

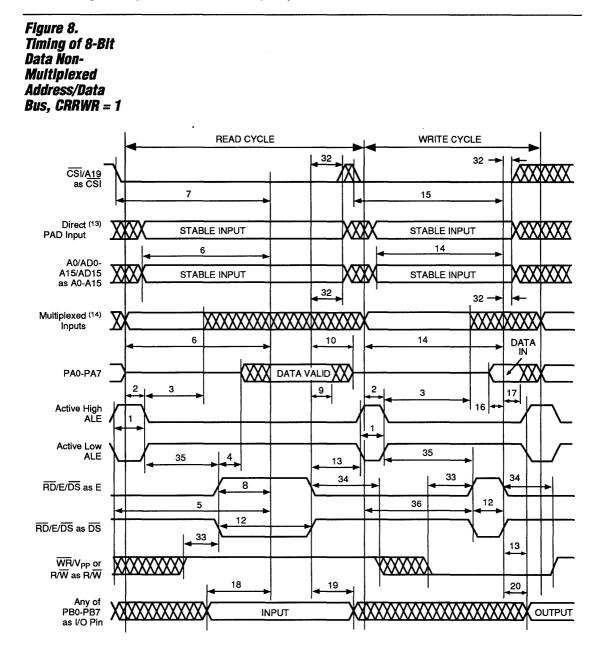

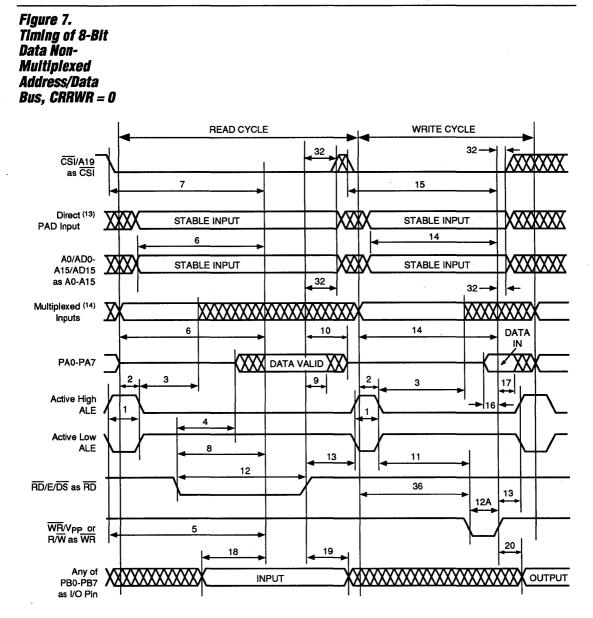

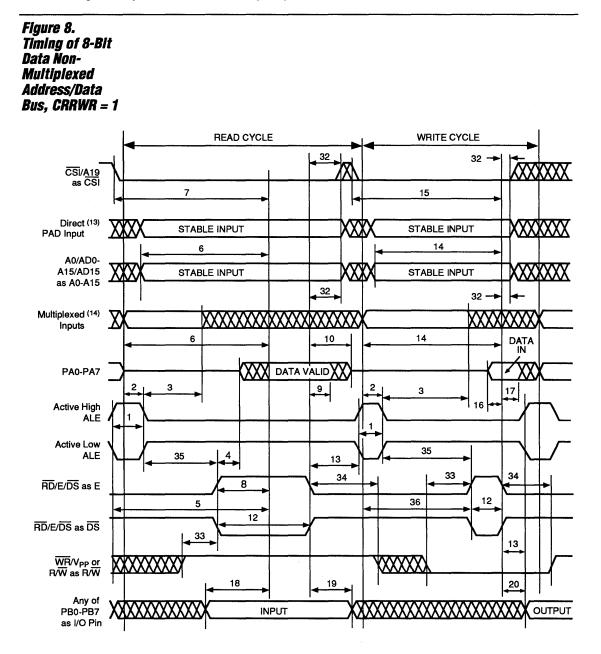

#### Non-Multiplexed Address/Data. 8-bit Data Bus

This mode is used to interface to nonmultiplexed 8-bit microcontrollers with an 8-bit data bus and a 16-bit or larger address bus. The low-order address/data bus (AD0/A0-AD7/A7) is the low-order address input bus. The high-order address/data bus (AD8/A8-AD15/A15) (A8-A15 on the PSD31X) is the high-order address bus byte. Port A is the low-order data bus. Port B can be configured as shown in Table 2.

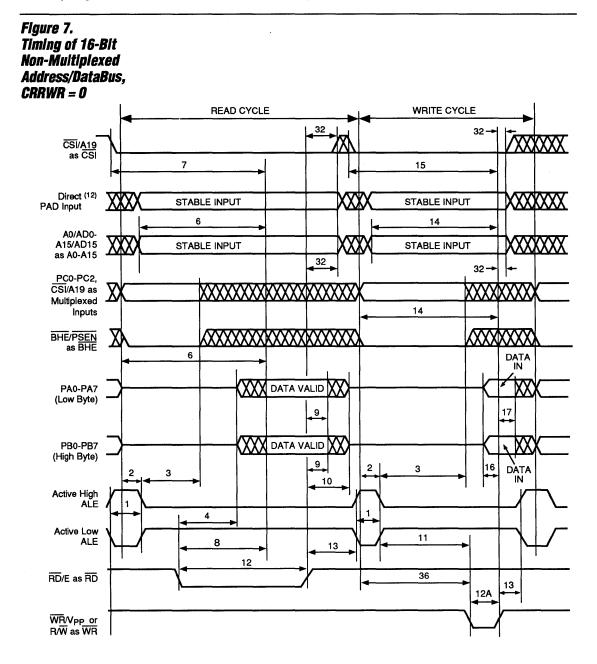

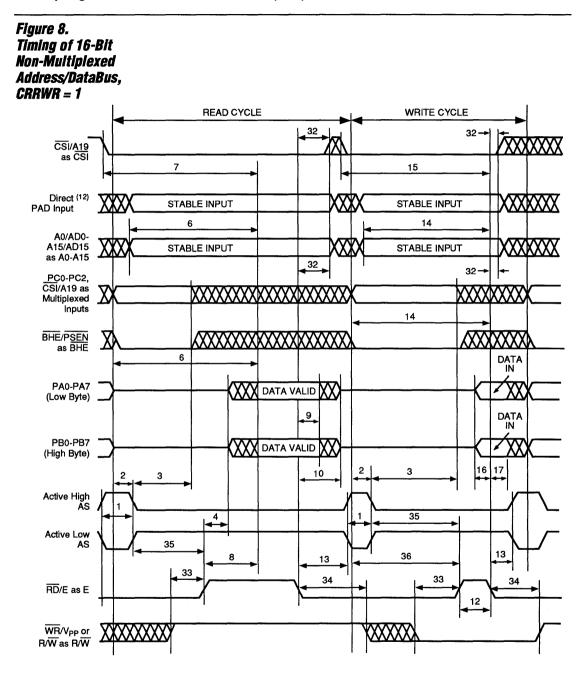

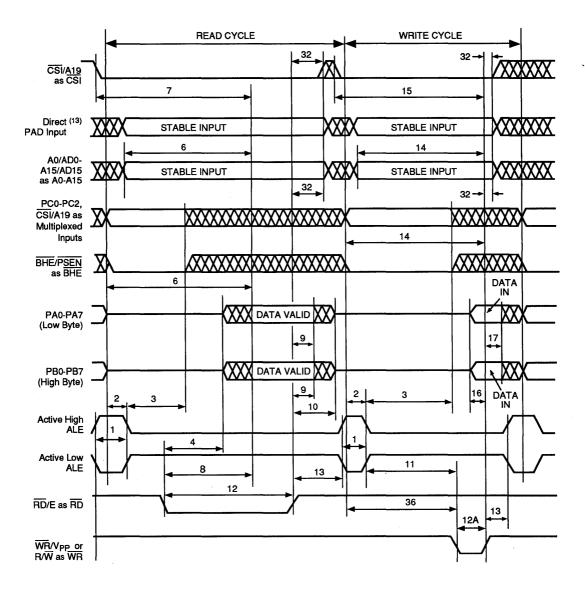

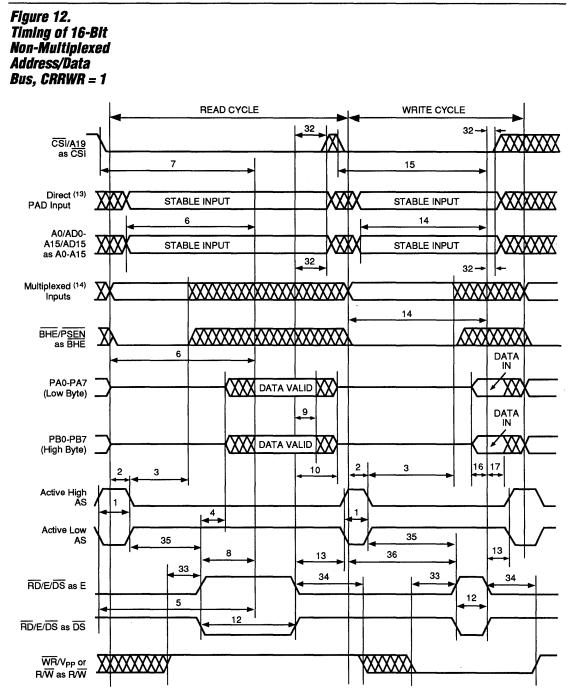

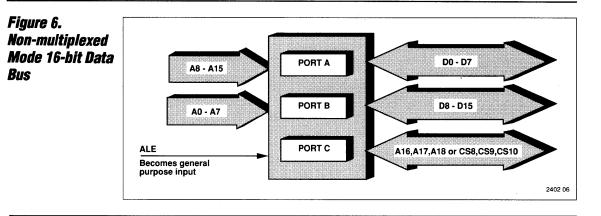

#### Non-Multiplexed Address/Data, 16-bit Data Bus

This mode is used to interface to nonmultiplexed 16-bit microcontrollers with a 16-bit data bus and a 16-bit or larger address bus. The low-order address/data bus (AD0/A0-AD7/A7) is the low-order address input bus. The high-order address/data bus (AD8/A8-AD15/A15) is the high-order address bus byte. Port A is the low-order data bus. Port B is the highorder data bus.

Table 2 summarizes the effect of the different operating modes on ports A, B, and the address/data pins. The configuration of Port C is independent of the four operating modes.

# Modes

# **PSD3XX** Family

#### Figure 20. PSD3XX Port Configurations (x8 Only)

**Legend:** AD8-AD15 = Addresses A8-A15 multiplexed with data lines D8-D15. AD0-AD7 = Addresses A0-A7 multiplexed with data lines D0-D7.

**PSD3XX** Family

| Table 2.                 |                 | Multiplexed Address/Data                                                        | Non-Multiplexed Address/Data |

|--------------------------|-----------------|---------------------------------------------------------------------------------|------------------------------|

| PSD30X Bus<br>and Port   | 8-bit Data Bus  |                                                                                 |                              |

| Configuration<br>Options | Port A          | I/O or low-order address<br>lines or Low-order multiplexed<br>address/data byte | D0–D7 data bus byte          |

|                          | Port B          | I/O or CSO-CS7                                                                  | I/O and/or CS0-CS7           |

|                          | AD0/A0-AD7/A7   | Low-order multiplexed address/data byte                                         | Low-order address bus byte   |

|                          | AD8/A8-AD15/A15 | High-order multiplexed<br>address data byte                                     | High-order address bus byte  |

|                          | 16-bit Data Bus |                                                                                 |                              |

|                          | Port A          | I/O or low-order address<br>lines or Low-order multiplexed<br>address/data byte | Low-order data bus byte      |

|                          | Port B          | I/O or CS0-CS7                                                                  | High-order data bus byte     |

|                          | AD0/A0-AD7/A7   | Low-order multiplexed address/data byte                                         | Low-order address bus byte   |

|                          | AD8/A8-AD15/A15 | High-order multiplexed address/data byte                                        | High-order address bus byte  |

| Table 2a.                |                | Multiplexed Address/Data                                                        | Non-Multiplexed Address/Data           |

|--------------------------|----------------|---------------------------------------------------------------------------------|----------------------------------------|

| PSD31X Bus               | 8-bit Data Bus | • <u></u>                                                                       | •••••••••••••••••••••••••••••••••••••• |

| Configuration<br>Options | Port A         | I/O or low-order address<br>lines or Low-order multiplexed<br>address/data byte | D0–D7 data bus byte                    |

|                          | Port B         | I/O or CS0-CS7                                                                  | I/O and/or CS0–CS7                     |

|                          | AD0/A0-AD7/A7  | Low-order multiplexed address/data byte                                         | Low-order address bus byte             |

|                          | A8–A15         | High-order address bus byte                                                     | High-order address bus byte            |

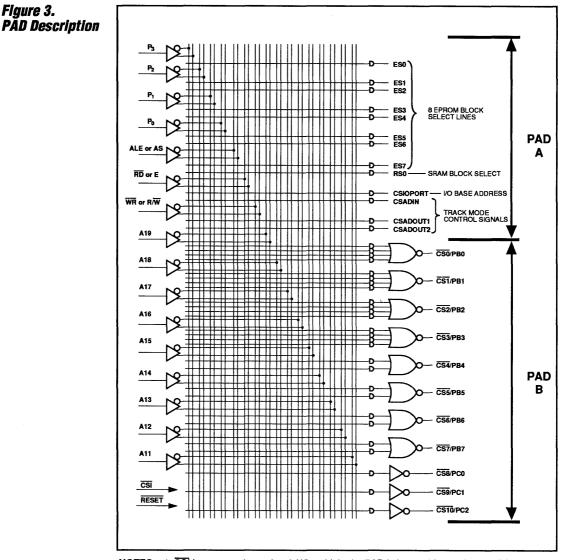

#### *Programmable Address Decoder (PAD)*

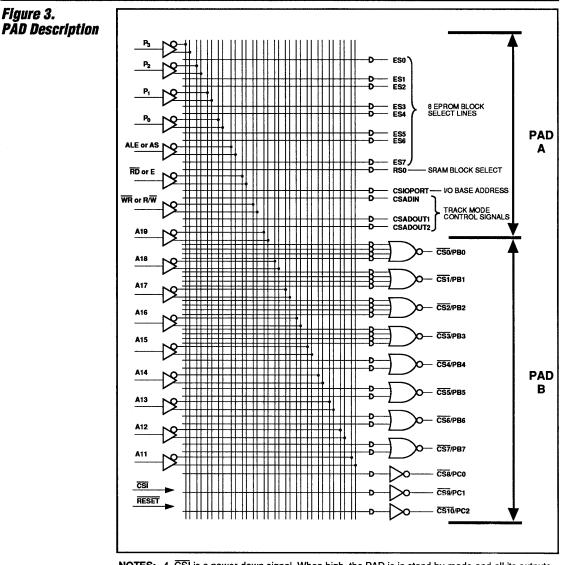

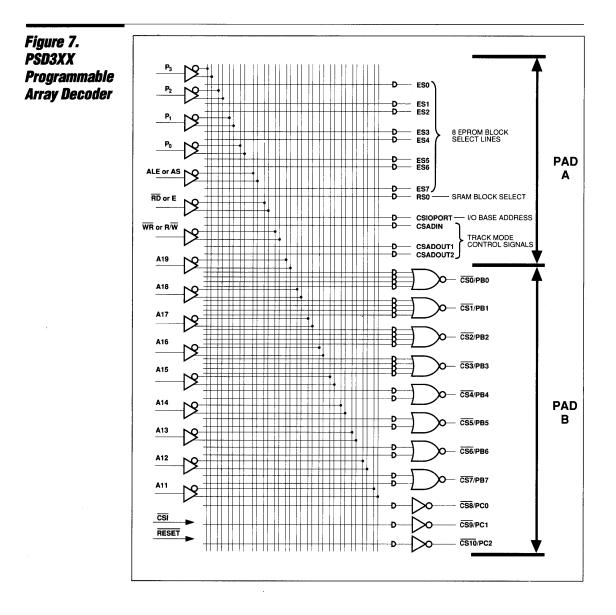

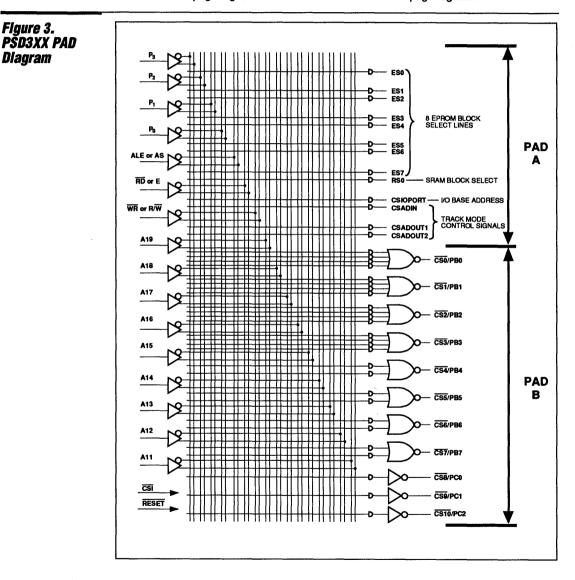

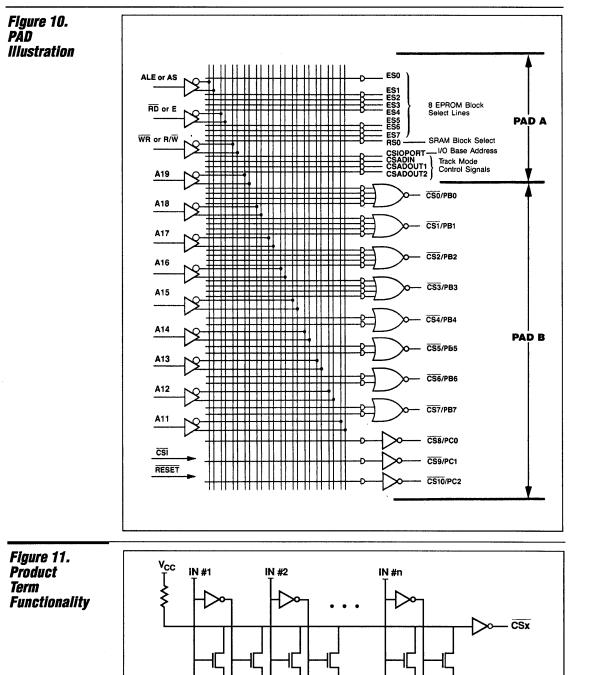

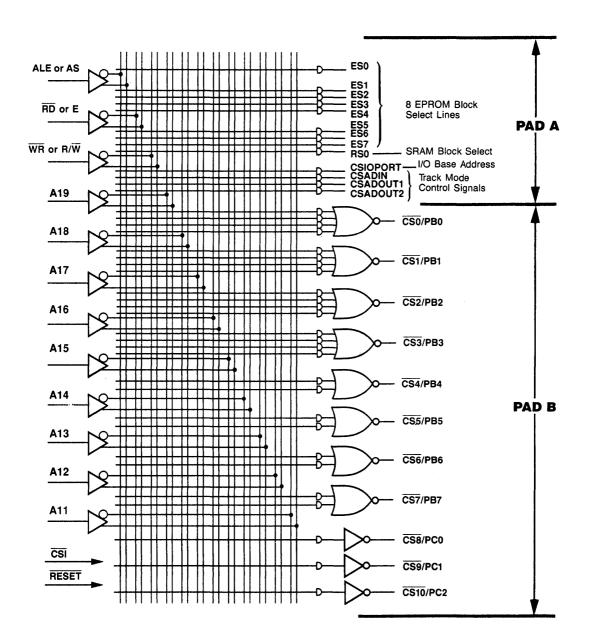

The PSD3XX consists of two programmable arrays referred to as PAD A and PAD B (Figure 3). PAD A is used to generate chip select signals derived from the input address to the internal EPROM blocks, SRAM, I/O ports, and Track Mode signals. All its I/O functions are listed in Table 3 and shown in Figure 3. PAD B outputs to Ports B and C for off-chip usage.

PAD B can also be used to extend the decoding to select external devices or as a random logic replacement. The input bus to both PAD A and PAD B is the same.

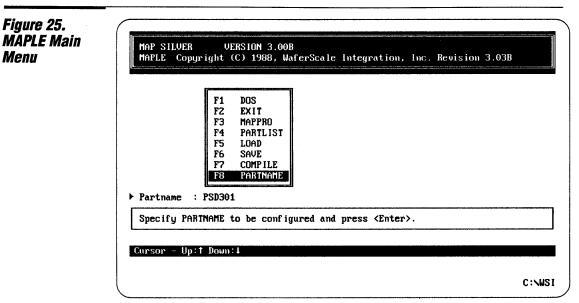

Using MAPLE software, each programmable bit in the PAD's array can have one of three logic states of 0, 1, and don't care (X). In a user's logic design, both PADs can share the same inputs using the X for input signals that are not supposed to affect other functions. The PADs use reprogrammable CMOS EPROM technology and can be programmed and erased by the user.

# **PSD3XX** Family

NOTES: 4. CSI is a power-down signal. When high, the PAD is in stand-by mode and all its outputs become non-active. See Tables 12 and 13.

- 5. RESET deselects all PAD output signals. See Tables 10 and 11.

- 6. A18, A17, and A16 are internally multiplexed with CS10, CS9, and CS8, respectively. Either A18 or CS10, A17 or CS9, and A16 or CS8 can be routed to the external pins of Port C. Port C can be configured as either input or output.

- 7. P<sub>0</sub>-P<sub>3</sub> are not included on PSD3X1 devices.

| Table 3.               |                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PSD3XX PAD A           | PAD A and PAD B Inputs |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| and PAD B<br>Functions | A19/CSI                | In CSI mode (when high), PAD deselects all of its outputs and enters a power-down mode (see Tables 12 and 13). In A19 mode, it is another input to the PAD.                                                                                                                                                                                                                                                                                              |  |  |  |

|                        | A16-A18                | These are general purpose inputs from Port C. See Figure 3, Note 4.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                        | A11–A15                | These are address inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                        | P0-P3                  | These are page number inputs (for the PSD302/312/303/313 only).                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                        | RD or E                | This is the read pulse or enable strobe input.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                        | WR or R/W              | This is the write pulse or $R/\overline{W}$ select signal.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                        | ALE                    | This is the ALE input to the chip.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                        | RESET                  | This deselects all outputs from the PAD; it can not be used in product term equations. See Tables 10 and 11.                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                        | PAD A Outputs          |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                        | ES0-ES7                | These are internal chip-selects to the 8 EPROM banks. Each bank can be located on any boundary that is a function of one product term of the PAD address inputs.                                                                                                                                                                                                                                                                                         |  |  |  |

|                        | RS0                    | This is an internal chip-select to the SRAM. Its base address location is a function of one term of the PAD address inputs.                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                        | CSIOPORT               | This internal chip-select selects the I/O ports. It can be placed on any boundary that is a function of one product term of the PAD inputs. See Tables 6 and 7.                                                                                                                                                                                                                                                                                          |  |  |  |

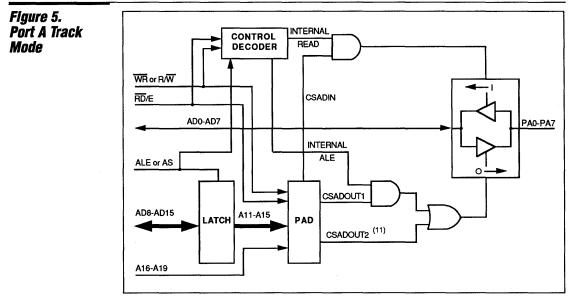

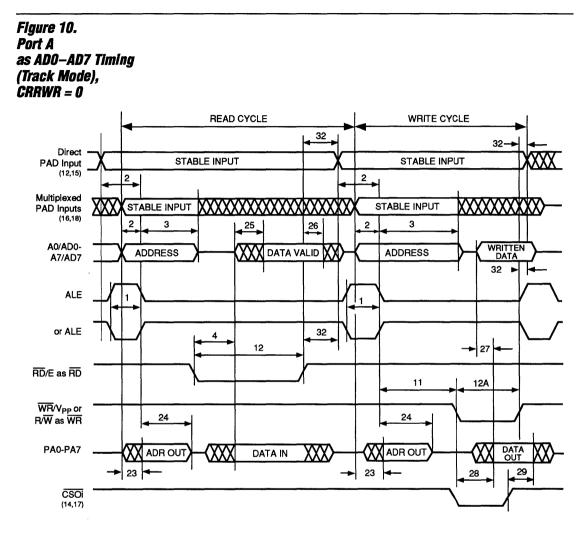

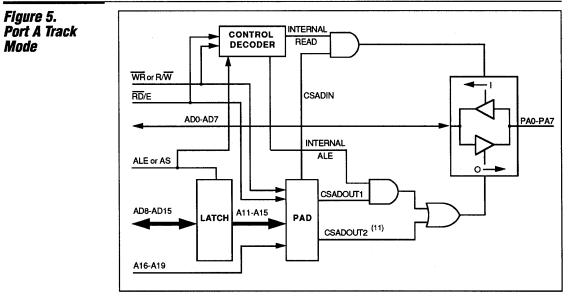

|                        | CSADIN                 | This internal chip-select, when Port A is configured as a low-order address/data bus in the track mode (CPAF2 = 1), controls the input direction of Port A. CSADIN is gated externally to the PAD by the internal read signal. When CSADIN and a read operation are active, data presented on Port A flows out of AD0/A0–AD7/A7. This chip-select can be placed on any boundary that is a function of one product term of the PAD inputs. See Figure 5.  |  |  |  |

|                        | CSADOUT1               | This internal chip-select, when Port A is configured as a low-order address/data bus in track mode (CPAF2 = 1), controls the output direction of Port A. CSADOUT1 is gated externally to the PAD by the ALE signal. When CSADOUT1 and the ALE signal are active, the address presented on AD0/A0–AD7/A7 flows out of Port A. This chip-select can be placed on any boundary that is a function of one product term of the PAD inputs. See Figure 5.      |  |  |  |

|                        | CSADOUT2               | This internal chip-select, when Port A is configured as a low-order address/data bus in the track mode (CPAF2 = 1), controls the output direction of Port A. CSADOUT2 must include the write-cycle control signals as part of its product term. When CSADOUT2 is active, the data presented on AD0/A0–AD7/A7 flows out of Port A. This chip-select can be placed on any boundary that is a function of one product term of the PAD inputs. See Figure 5. |  |  |  |

|                        | PAD B Outputs          |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                        | CS0-CS3                | These chip-select outputs can be routed through Port B. Each of them is a function of up to four product terms of the PAD inputs.                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                        | CS4-CS7                | These chip-select outputs can be routed through Port B. Each of them is a function of up to two product terms of the PAD inputs.                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                        | CS8-CS10               | These chip-select outputs can be routed through Port C. See Figure 3, Note 4. Each of them is a function of one product term of the PAD inputs.                                                                                                                                                                                                                                                                                                          |  |  |  |

# Field-programmable microcontroller peripherals

# **PSD3XX** Family

| Configuration<br>Bits | The configuration bits shown in Table 4 are<br>non-volatile cells that let the user set the<br>device, I/O, and control functions to the<br>proper operational mode. Table 5 lists all<br>configuration bits. The configuration bits<br>are programmed and verified during the | programming phase. In operational mode,<br>they are not accessible. To simplify<br>implementing a specific mode, use the<br>PSD3XX MAPLE software to set the bits. |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4.      |

|---------------|

| PSD3XX        |

| Non-Volatile  |

| Configuration |

| Bits          |

|               |

| Use This Bit       | То                                                                                                                                                                               |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDATA              | Set the data bus width to 8 or 16 bits (PSD30X only).                                                                                                                            |

| CADDRDAT           | Set the address/data buses to multiplexed or non-multiplexed mode.                                                                                                               |

| CEDS               | Determine the polarity and functionality of read and write. (Note 9)                                                                                                             |

| CA19/CSI           | Set A19/CSI to CSI (power-down) or A19 input.                                                                                                                                    |

| CALE               | Set the ALE polarity.                                                                                                                                                            |

| CPAF2              | Set Port A either to track the low-order byte of the address/data multiplexed bus or to select the I/O or address option.                                                        |

| CSECURITY          | Set the security on or off (a secured part can not be duplicated).                                                                                                               |

| CRESET             | Set the RESET polarity.                                                                                                                                                          |

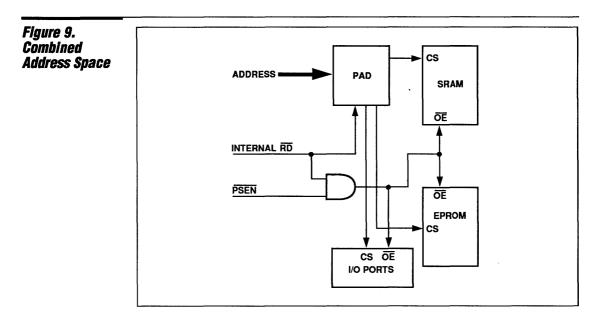

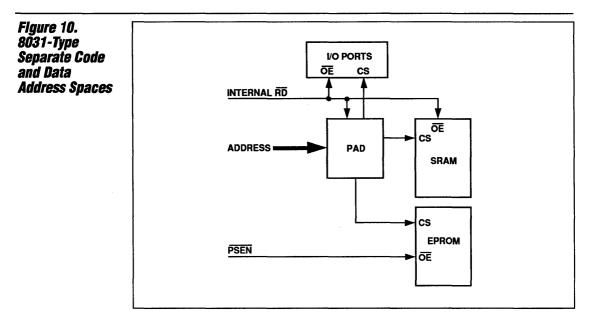

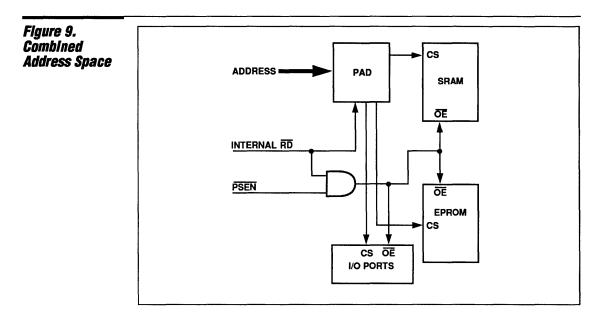

| COMB/SEP           | Set PSEN and RD for combined or separate address spaces (see Figures 9 and 10).                                                                                                  |

| CPAF1<br>(8 Bits)  | Configure each pin of Port A in multiplexed mode to be an I/O or address out.                                                                                                    |

| CPACOD<br>(8 Bits) | Configure each pin of Port A as an open drain or active CMOS pull-up output.                                                                                                     |

| CPBF<br>(8 Bits)   | Configure each pin of Port B as an I/O or a chip-select output.                                                                                                                  |

| CPBCOD<br>(8 Bits) | Configure each pin of Port B as an open drain or active CMOS pull-up output.                                                                                                     |

| CPCF<br>(3 Bits)   | Configure each pin of Port C as an address input or a chip-select output.                                                                                                        |

| CADDHLT            | Configure pins A16 – A19 to go through a latch or to have their latch transparent.                                                                                               |

| CADLOG<br>(4 Bits) | Configure A16 – A19 individually as logic or address inputs. (Note 9)                                                                                                            |

| CATD               | Configure pins A16–A19 as PAD logic inputs or high-order address inputs (Note 8).                                                                                                |

| CLOT               | Determine in non-multiplexed mode if address inputs are transparent or latched (Note 9).                                                                                         |

| CRRWR              | Set the $\overline{RD}/E$ and $\overline{WR}/V_{PP}$ or $\overline{R/W}$ pins to $\overline{RD}$ and $\overline{WR}$ pulse, or to E strobe and $\overline{R/W}$ status (Note 8). |

| CRRWR              | Configure the polarity and control methods of read and write cycles. (Note 9)                                                                                                    |

|                    |                                                                                                                                                                                  |

**Port Functions**

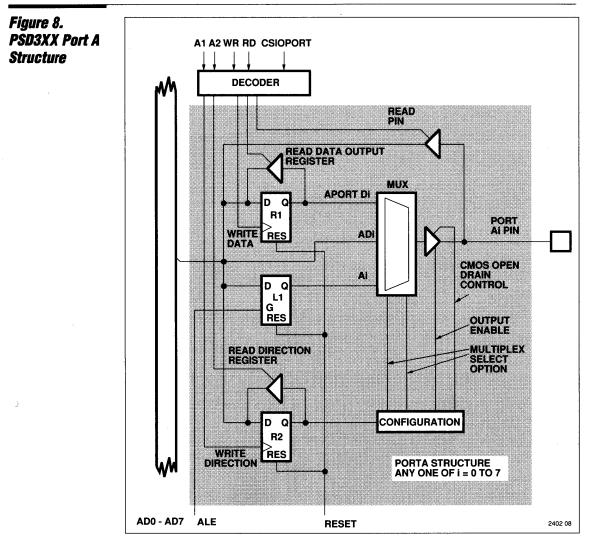

The PSD3XX has three I/O ports (Ports A, B, and C) that are configurable at the bit level. This permits great flexibility and a high degree of customization for specific

applications. The following is a description of each port. Figure 4 shows the pin structure of Port A.

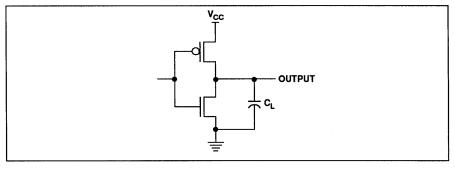

NOTE: 10. CMOS/OD determines whether the output is open drain or CMOS.

| Table 5.<br>PSD3XX                     | Configuration<br>Bits      | No.<br>of Bits | Function                                                                                                                                                                                                                                                  |

|----------------------------------------|----------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration<br>Bits <sup>12,13</sup> | CDATA<br>(Note 14)         | 1              | 8-bit or 16-bit Data Bus Width<br>CDATA = 0 eight bits<br>CDATA = 1 sixteen bits                                                                                                                                                                          |

|                                        | CADDRDAT                   | 1              | ADDRESS/DATA Multiplexed (separate buses)<br>CADDRDAT = 0, non-multiplexed<br>CADDRDAT = 1, multiplexed                                                                                                                                                   |

|                                        | CA19/CSI                   | 1              | A19 or $\overline{CSI}$<br>CA19/ $\overline{CSI}$ = 0, enable power-down<br>CA19/ $\overline{CSI}$ = 1, enable A19 input to PAD                                                                                                                           |

|                                        | CALE                       | 1              | Active HIGH or Active LOW<br>CALE = 0, Active high<br>CALE = 1, Active low                                                                                                                                                                                |

|                                        | CRESET                     | 1              | Active high or active low<br>CRESET = 0, active low reset signal<br>CRESET = 1, active high reset signal                                                                                                                                                  |

|                                        | COMB/SEP                   | 1              | Combined or Separate Address Space<br>for SRAM and EPROM<br>0 = Combined, 1 = Separate                                                                                                                                                                    |

|                                        | CPAF1                      | 8              | Port A I/Os or A0–A7<br>CPAF1 = 0, Port A pin = I/O<br>CPAF1 = 1, Port A pin = A0 – A7                                                                                                                                                                    |

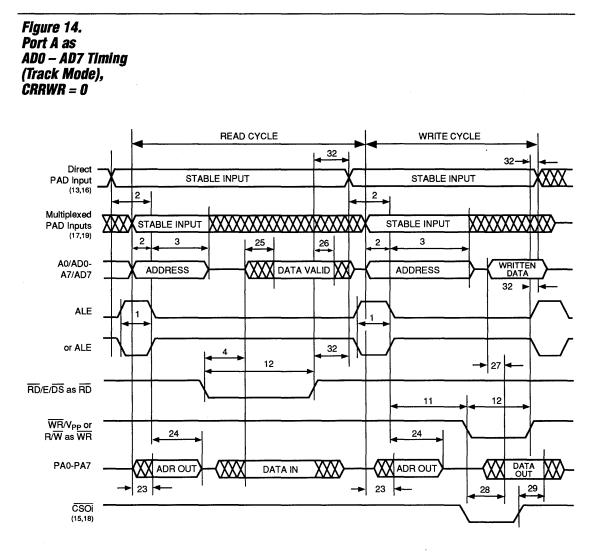

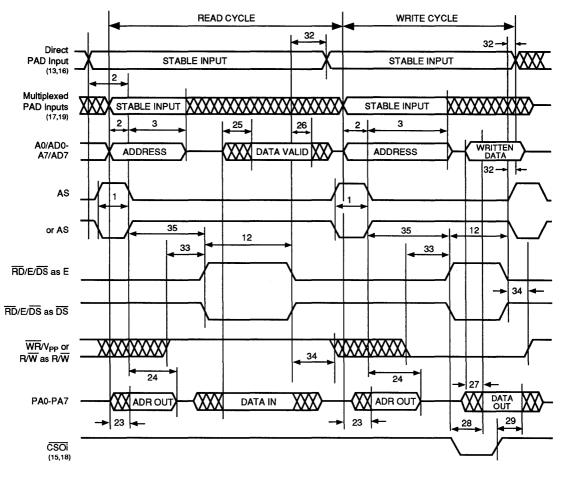

|                                        | CPAF2                      | 1              | Port A AD0–AD7 (address/data multiplexed bus)<br>CPAF2 = 0, address or I/O on Port A (according to CPAF1)<br>CPAF2 = 1, address/data multiplexed on Port A (track mode)                                                                                   |

|                                        | CATD<br>(Note 16)          | 1              | A16–A19 address or logic inputs<br>CATD = 0, logic inputs<br>CATD = 1, address inputs                                                                                                                                                                     |

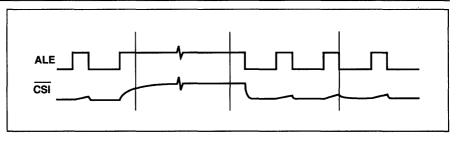

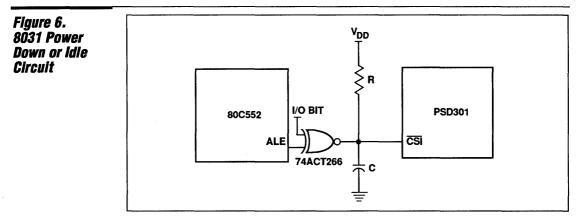

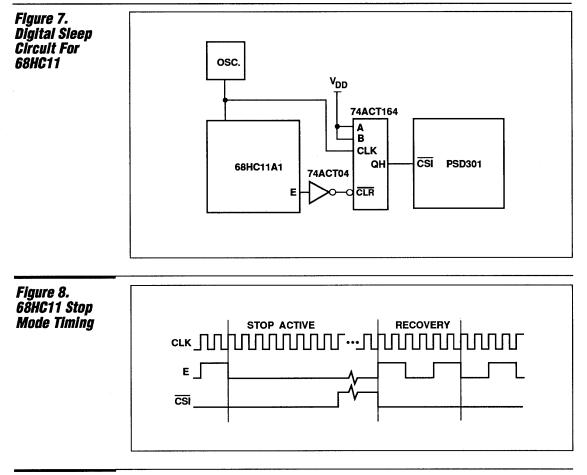

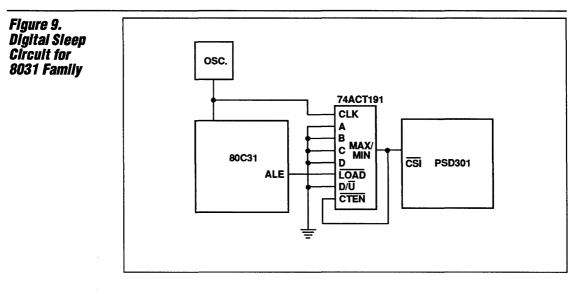

|                                        | CADDHLT                    | 1              | A16–A19 Transparent or Latched<br>CADDHLT = 0, Address latch transparent<br>CADDHLT = 1, Address latched (ALE dependent)                                                                                                                                  |