# Flash Memory Volume 1

Synchronous and DRAM-Interface Components

$FlashFile^{TM}$ Components

Boot Block Components

Bulk-Erase Components

intel

SANTA CLARA DIVISION 3000 Bowers Avenue Santa Clara, CA 95051-0919 (408) 727-2500 • (800) 866-9953

# 24-HOUR AUTOMATED TECHNICAL SUPPORT\*

Intel's Application Bulletin Board System (BBS) and FaxBack System are at your service, 24-hours a day, at no charge, and the information is updated frequently.

## FaxBack SYSTEM

Technical and product information are available 24-hours a day! Order documents containing:

- · Product Announcements

- Product Literature

- Intel Device Characteristics

- Design/Application Recommendations

- Stepping/Change Notifications

- Quality and Reliability Information

Information on the following subjects is also available:

- Microcontroller and Flash

- · OEM Branded Systems

- · Multibus/BBS Listing

- Multimedia

- · Development Tools

- · Quality and Reliability/Change Notification

- Microprocessor/PCI/Peripheral

- Intel Architecture Lab

To use FaxBack for Intel components and systems, dial (800) 628-2283 or (916) 356-3105 (U.S. and Canada) or +44{0} 1793-496646 (Europe) and follow the automated voice-prompt menu. Document orders will be faxed to the fax number you specify. Catalogs are updated twice a month, so call for the latest information!

## **BULLETIN BOARD SYSTEM**

Intel's Application Bulletin Board System (BBS) enables file retrieval 24-hours a day. The following can be located on the BBS:

- Software Drivers

- Tool Information

- · Software/Application Utilities

- Product/Technical Documentation

- · Firmware Upgrades

- · Quality and Reliability Data

To use the Intel Application BBS (components and systems), dial (916) 356-3600 for download access (U.S. and Canada) or +44{0} 1793-496340 (Europe). The BBS will support 1200–19200 baud rate modem. Typical modem configuration: 9600 baud rate, No Parity, 8 Data Bits, 1 Stop Bit. A directory listing of BBS files is also available through FaxBack or our 800 BBS (800-897-2536).

## **Retail Products**

Information on Intel's retail products (Coprocessors and wireless, video, personal conferencing and network products) is available through the following services:

Internet :

ftp.intel.com (143.185.65.2)

CompuServe : GO

GO INTELFORUM (modem settings: E-7-1, up to 14.4 Kbps)

| Country       | BBS (N-8-1, up to 14.4 Kbps) | FaxBack                             |

|---------------|------------------------------|-------------------------------------|

| North America | (503) 264-7999               | (800) 525-3019 or<br>(503) 264-6835 |

| Europe        | +44 1 793-432955             | +44 1 793-432509                    |

| Australia     | +61 2 975-3066               | +61 2 975-3922                      |

| Taiwan        | +886 2 718-6422              | +886 2 514-0815                     |

| Singapore     | +65 256-4776                 | +65 256-5350                        |

| Hong Kong     | +852 530-4116                | +852 844-4448                       |

| Korea         | +822 784-3430                | +822 767-2594                       |

<sup>\*</sup>Support services provided courtesy of Intel Application Support

# **LITERATURE**

For additional information on Intel products in the U.S. or Canada, call Intel's Literature Center at (800) 548-4725 or write to:

Intel Literature P.O. Box 7641 Mt. Prospect, II 60056-7641

To order literature outside of the U.S. and Canada contact your local international sales office.

# **CURRENT DATABOOKS**

Product line databooks contain datasheets, application notes, article reprints, and other design information. Databooks can be ordered in the U.S. and Canada by calling TAB/McGraw-Hill at 1-800-822-8158; outside of the U.S. and Canada contact your local international sales office.

| Title                                          | Intel Order Number | ISBN          |

|------------------------------------------------|--------------------|---------------|

| Automotive Products                            | 231792             | N/A           |

| Embedded Applications (2 vol. set)             | 270648             | 1-55512-242-6 |

| Embedded Microcontrollers                      | 270646             | 1-55512-230-2 |

| Embedded Microprocessors                       | 272396             | 1-55512-231-0 |

| Flash Memory (2 vol. set)                      | 210830             | 1-55512-232-9 |

| Intel486™ Microprocessors and Related Products | 241731             | 1-55512-235-3 |

| i960® Processors and Related Products          | 272084             | 1-55512-234-5 |

| Military and Special Products                  | 210461             | N/A           |

| Networking                                     | 297360             | 1-55512-236-1 |

| OEM Boards, Systems and Software               | 280407             | 1-55512-237-X |

| Packaging                                      | 240800             | 1-55512-238-8 |

| Pentium™ Processors and Related Products       | 241732             | 1-55512-239-6 |

| Peripheral Components                          | 296467             | 1-55512-240-X |

A complete set of this information is available on CD-ROM through Intel's Data on Demand program, order number 240897. For information about Intel's Data on Demand ask for item number 240952.

# Flash Memory Volume 1

Synchronous and DRAM-Interface Components, FlashFile TM Components, Boot Block Components, Bulk-Erase Components

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

©INTEL CORPORATION, 1995

# **DATASHEET DESIGNATIONS**

Intel uses various datasheet markings to designate each phase of the document as it relates to the product. The markings appear in the lower inside corner of each datasheet page. Following are the definitions of each marking:

| <b>Datasheet Marking</b> | Description                                                                                                                                                                                   |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Product Preview          | Contains information on products in the design phase of development. Do not finalize a design with the information. Revised information will be published when the product becomes available. |  |  |

| Advanced Information     | Contains information on products being sampled or in the initial production phase of development.*                                                                                            |  |  |

| Preliminary              | Contains preliminary information on new products in production.*                                                                                                                              |  |  |

| No Marking               | Contains information on products in full production.*                                                                                                                                         |  |  |

<sup>\*</sup> Specifications within these datasheets are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

| <b>Memory Overview</b>                                                        | 1   |

|-------------------------------------------------------------------------------|-----|

| Flash Memory Overview and Support Tools                                       | 2   |

| Synchronous & DRAM-Interface Flash Memory Components and FlashFile Components | 3   |

| <b>Boot Block Components</b>                                                  | 4   |

| Bulk-Erase Components                                                         | 5   |

| PCMCIA Flash Memory Cards                                                     | 6   |

| PCMCIA-ATA Flash Memory<br>Drives                                             | 7   |

| Flash Automotive Components                                                   | 8   |

| Process Engineering Reports                                                   | 9 ; |

Flash Memory SmartDie<sup>TM</sup> Products

Article Reprints

10

11

# **Table of Contents**

| Alphanumeric Index                                                             | χV             |

|--------------------------------------------------------------------------------|----------------|

| CHAPTER 1                                                                      |                |

| Memory Overview                                                                |                |

| Intel Memory Technologies                                                      | 1-1            |

| CHAPTER 2                                                                      |                |

| Flash Memory Overview and Support Tools                                        |                |

| Flash Memory Overview                                                          | 2-1            |

| SUPPORT TOOLS                                                                  |                |

| Flash Memory Customer Support                                                  | 2-7            |

| Sprint PLUS48/Intel Support Version                                            | 2-9            |

| Multi-APRO Programmer/Intel Support Version                                    | 2-13           |

| Flash Memory Card and Flash Drive Evaluation Kit Product Brief                 | 2-16           |

| Small Outline Package Guide Overview                                           | 2-18           |

| Intel FLASHBuilder Software Product Brief                                      | 2-20           |

| APPLICATION NOTES                                                              |                |

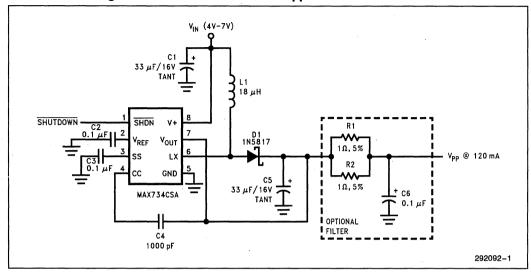

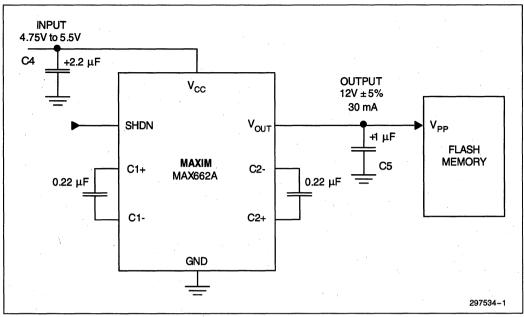

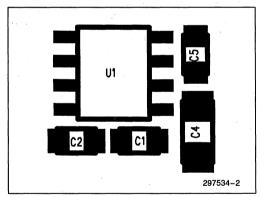

| AP-357 Power Supply Solutions for Flash Memory                                 | 2-22           |

| AP-374 Flash Memory Write Protection Techniques                                | 2-64<br>2-71   |

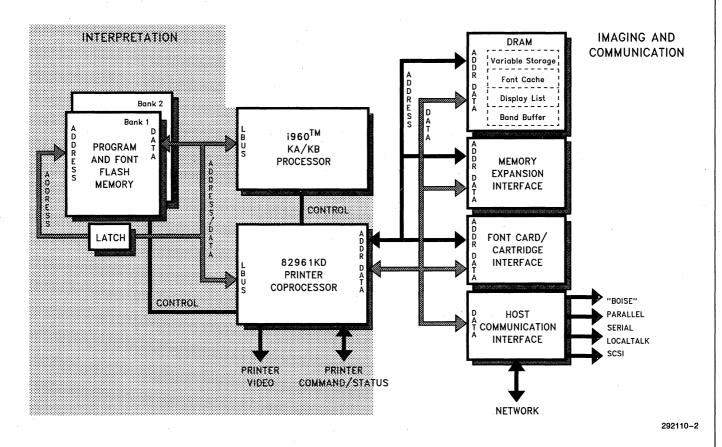

| AB-29 Flash Memory Applications in Laser Printers TECHNICAL PAPER              | 2-71           |

| Small and Low Cost Power Supply Solution for Intel's Flash Memory Products     | 2-78           |

|                                                                                | 2-70           |

| CHAPTER 3                                                                      |                |

| Synchronous and DRAM-Interface Flash Memory Components                         |                |

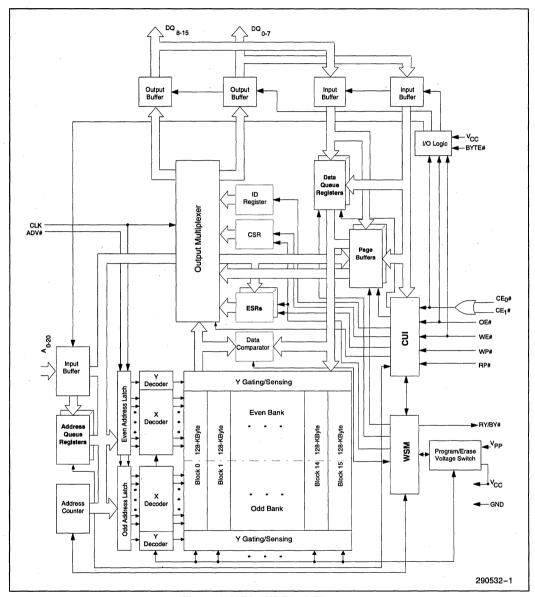

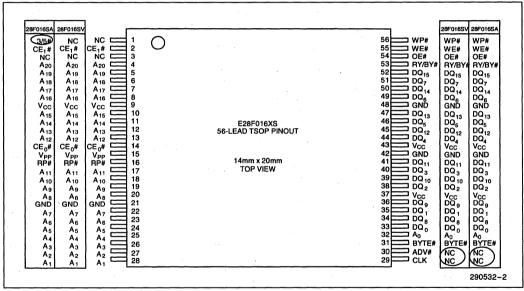

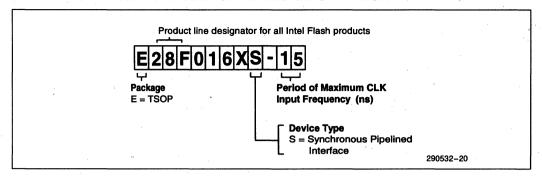

| PRODUCT BRIEFS Intel 28F016XS Embedded Flash RAM Product Brief                 | 0.4            |

| Intel 28F016XS Embedded Flash RAM Product Brief                                | 3-1<br>3-2     |

| DATA SHEETS                                                                    | 3-2            |

| 28F016XS 16-Mbit (1-Mbit x 16, 2-Mbit x 8) Synchronous Flash Memory            | 3-3            |

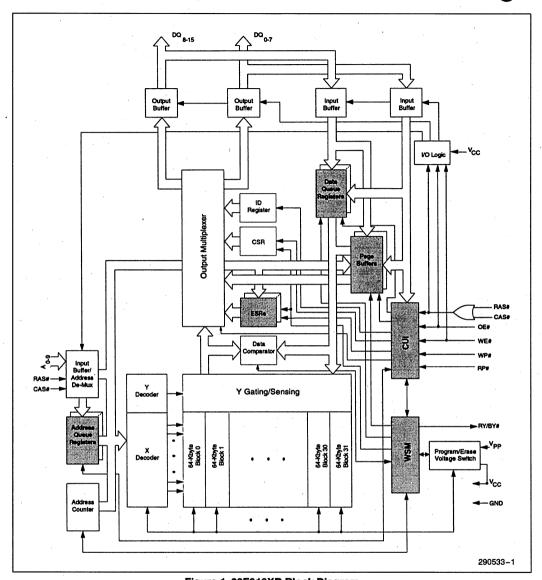

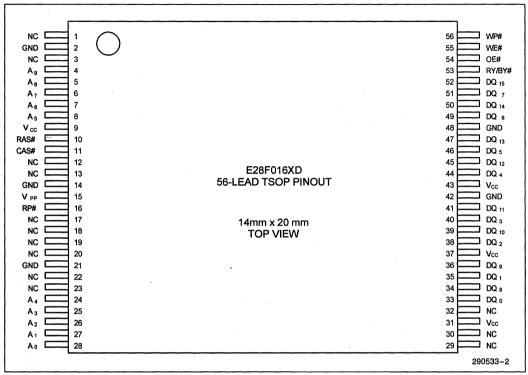

| 28F016XD 16-Mbit (1-Mbit x 16) DRAM - Interface Flash Memory                   | 3-50           |

| APPLICATION NOTES                                                              | 0 00           |

| AB-58 28F016XD - Based SIMM Designs                                            | 3-104          |

| AP-398 Designing with the 28F016XS                                             | 3-112          |

| AP-384 Designing with the 28F016XD                                             | 3-142          |

| AP-600 Performance Benefits and Power/Energy Savings of 28F016XS-Based         |                |

| System Designs                                                                 | 3-172          |

| TECHNICAL PAPERS                                                               |                |

| Interfacing the 28F016XS to the i960® Microprocessor Family                    |                |

| Interfacing the 28F016XS to the Intel486™ Microprocessor Family                | 3-238          |

| FlashFile <sup>TM</sup> Components                                             |                |

| DATA SHEETS  DD0050000A 00 Mhit (0 Mhit v 16 A Mhit v 0) FloobFile Memory      | 0.057          |

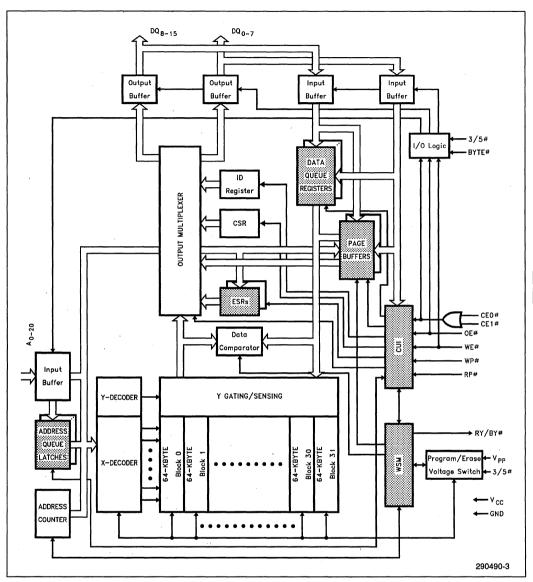

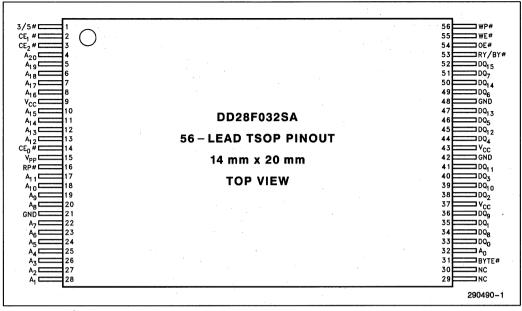

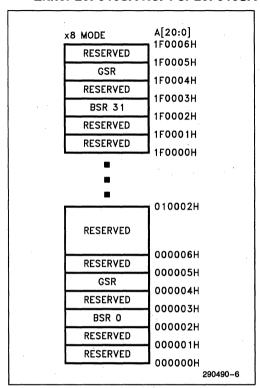

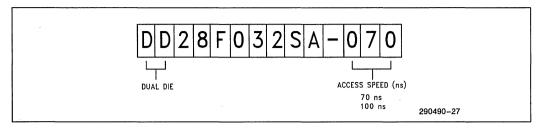

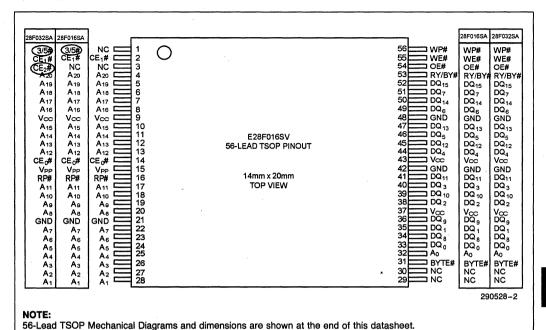

| DD28F032SA 32-Mbit (2-Mbit x 16, 4-Mbit x 8) FlashFile Memory                  | 3-257<br>3-303 |

| 28F016SA 16-Mbit (1-Mbit x 16, 2-Mbit x 8) FlashFile Memory                    | 3-359          |

| Extended Temperature 28F016SA 16-Mbit (1-Mbit x 16, 2-Mbit x 8) FlashFile      | 0-009          |

| Memory                                                                         | 3-403          |

| 28F008SA 8-Mbit (1-Mbit x 8) FlashFile Memory (Extended Temperature            | 0 100          |

| Specifications Included)                                                       | 3-443          |

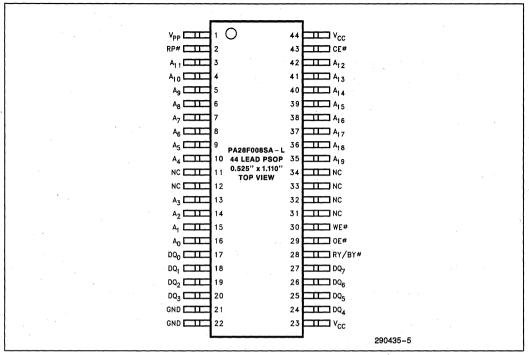

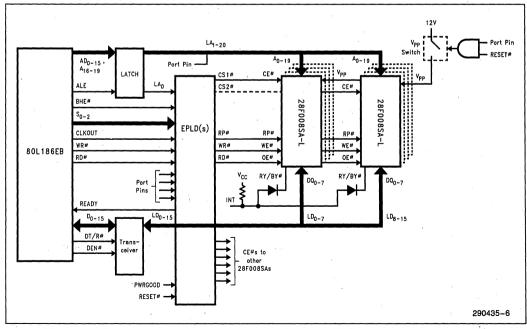

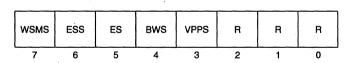

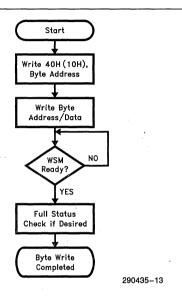

| 28F008SA-L 8 Mbit (1Mbit x 8) Flash Memory                                     | 3-476          |

| APPLICATION NOTES                                                              |                |

| AP-607 Multi-Site Layout Planning with Intel's FlashFile Components, Including |                |

| ROM Compatibility                                                              | 3-504          |

# Table of Contents (Continued)

| AP-393 28F016SV Compatibility with 28F016SA                                | 3-533   |

|----------------------------------------------------------------------------|---------|

| AP-359 28F008SA Hardware Interfacing                                       | 3-551   |

| AP-360 28F008SA Software Drivers                                           | 3-562   |

| AP-362 Implementing Mobile PC Designs Using High Density FlashFile         |         |

| Components                                                                 | 3-585   |

| AP-364 28F008SA Automation and Algorithms                                  | 3-640   |

| AP-375 Upgrade Considerations from the 28F008SA to the 28F016SA            | 3-654   |

| AP-377 16-Mbit Flash Product Family Software Drivers 28F016SA, 28F016SV,   |         |

| 28F016XS, 28F016XD                                                         | 3-667   |

| AP-378 System Optimization Using the Enhanced Features of the 28F016SA     | 3-722   |

| AP-399 Implementing Mobile Intel486 SX Microprocessor PC Designs Using     |         |

| FlashFile™ Components                                                      | 3-743   |

| ENGINEERING REPORT                                                         | 0 , ,0  |

| ER-27 The Intel 28F008SA Flash Memory                                      | 3-783   |

|                                                                            | 0 , 00  |

| CHAPTER 4                                                                  |         |

| Boot Block Components                                                      |         |

| DATA SHEETS                                                                |         |

| 8-Mbit (512K x 16, 1-Mbit x 8) SmartVoltage Boot Block Flash Memory Family | 4-1     |

| 4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family   |         |

| (Extended Temperature Specifications Included)                             | 4-13    |

| 2-Mbit (128K x 16, 256K x 8) SmartVoltage Boot Block Flash Memory Family   |         |

| (Extended Temperature Specifications Included)                             | 4-68    |

| 28F400BX-T/B, 28F004BX-T/B 4 Mbit (256K x 16, 512K x 8) Boot Block Flash   |         |

| Memory Family                                                              | 4-124   |

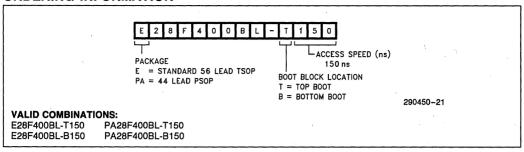

| 28F400BL-T/B, 28F004BL-T/B 4-Mbit (256K x 16, 512K x 8) Low Power Boot     |         |

| Block Flash Memory Family                                                  | 4-174   |

| 28F200BX-T/B, 28F002BX-T/B 2 Mbit (128K x 16, 256K x 8) Boot Block Flash   | 7-1/7   |

| Memory Family                                                              | 4-218   |

| 28F200BL-T/B, 28F002BL-T/B 2-Mbit (128K x 16, 256K x 8) Low Power Boot     | 4-210   |

| Block Flash Memory Family                                                  | 4-265   |

| 28F001BX-T/28F001BX-B 1M (128K x 8) CMOS Flash Memory                      | 4-307   |

| APPLICATION NOTES                                                          | 4-307   |

|                                                                            |         |

| AP-604 Using Intel's Boot Block Flash Memory Parameter Blocks to Replace   | 4 0 4 4 |

| EEPROM                                                                     | 4-341   |

| AB-60 2/4/8-Mbit SmartVoltage Boot Block Flash Memory Family Overview      | 4-349   |

| AP-341 Designing an Updatable BIOS Using Flash Memory                      | 4-357   |

| AP-363 Extended Flash Bios Concepts for Portable Computers                 | 4-400   |

| ENGINEERING REPORTS                                                        |         |

| ER-26 The Intel 28F001BX-T and 28F001BX-B Flash Memories                   | 4-422   |

| ER-29 The Intel 2/4-Mbit Boot Block Flash Memory Family                    | 4-437   |

| TECHNICAL PAPER                                                            |         |

| Boot Block Flash: The Next Generation White Paper                          | 4-466   |

| CHAPTER 5                                                                  |         |

| Bulk-Erase Components                                                      |         |

| DATA SHEETS                                                                |         |

| 28F020 2048K (256K x 8) CMOS Flash Memory                                  | 5-1     |

| 28F010 1024K (128K x 8) CMOS Flash Memory                                  |         |

|                                                                            | 5-64    |

| 28F512 512K (64K x 8) CMOS Flash Memory                                    | 5-04    |

# **Table of Contents (Continued)**

| 28F256A 256K (32K x 8) CMOS Flash Memory                                                                                                                | 5-92           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| AP-316 Using Flash Memory for In-System Reprogrammable Nonvolatile Storage . AP-325 Guide to First Generation Flash Memory Programming                  | 5-117<br>5-162 |

| ER-24 Intel Flash Memory 28F256A, 28F512, 28F010, 28F020                                                                                                | 5-184          |

| CHAPTER 6                                                                                                                                               |                |

| PCMCIA Flash Memory Cards                                                                                                                               |                |

| Series 2+ Flash Memory Card User's Manual OverviewDATA SHEETS                                                                                           | 6-1            |

| Series 2 + Flash Memory Cards 4-, 8-, 20- and 40-Megabyte                                                                                               | 6-2            |

| iMC020FLSA (Extended Temperature Specifications Included)                                                                                               | 6-42           |

| iMC004FLKA 4-Megabyte Flash Memory CardiMC002FLKA 2-Mbyte Flash Memory Card                                                                             | 6-80<br>6-110  |

| iMC001FLKA 1-Megabyte Flash Memory CardiMC001FLKA 1-Megabyte Flash Memory Card                                                                          | 6-140          |

| APPLICATION NOTES                                                                                                                                       | 0-140          |

| AP-606 Interchangeability of Series 1, Series 2 and Series 2+ Flash Memory                                                                              |                |

| Cards                                                                                                                                                   | 6-170          |

| AP-343 Solutions for High Density Applications Using Intel Flash Memory AP-361 Implementing the Integrated Registers of the Series 2 Flash Memory Card. | 6-185<br>6-215 |

| SUPPORT TOOLS                                                                                                                                           |                |

| Flash Memory Card and Flash Drive Evaluation Kit Product Brief                                                                                          | 6-232          |

| TECHNICAL PAPER Intel FlashFile Memory-The Key to Diskless Mobile PCs                                                                                   | 6.004          |

|                                                                                                                                                         | 6-234          |

| CHAPTER 7                                                                                                                                               |                |

| PCMCIA-ATA Flash Memory Drives                                                                                                                          |                |

| DATA SHEET iFD005P2SA/iFD010P2SA Flash Drive                                                                                                            | 7-1            |

| DESIGN GUIDE                                                                                                                                            | 7-1            |

| Flash Drive Design Guide (for iFD005P2SA/iFD010P2SA)                                                                                                    | 7-46           |

| SUPPORT TOOLS                                                                                                                                           |                |

| Flash Memory Card and Flash Drive Evaluation Kit Product Brief                                                                                          | 7-118          |

| CHAPTER 8                                                                                                                                               |                |

| Flash Automotive Components                                                                                                                             |                |

| DATA SHEETS  ACCEPTAGE TO A Maria (OFC) ( ) 40 F10 ( ) Constant ( ) It and Block Floor                                                                  |                |

| A28F400BR-T/B 4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family                                                                  | 8-1            |

| A28F400BX-T/B 4-Mbit (256K x 16, 512K x 8) Boot Block Flash Memory Family                                                                               | 8-35           |

| A28F200BR-T/B 2-Mbit (128K x 16, 256K x 8) SmartVoltage Boot Block Flash                                                                                | 0 00           |

| Memory Family                                                                                                                                           | 8-69           |

| A28F200BX-T/B 2-Mbit (128K x 16, 256K x 8) Boot Block Flash Memory Family                                                                               | 8-102          |

| A28F010 1024K (128K x 8) CMOS Flash Memory                                                                                                              |                |

| A28F512 512K (64K x 8) CMOS Flash Memory                                                                                                                | 8-158<br>8-182 |

| CHAPTER 9                                                                                                                                               | 0-102          |

|                                                                                                                                                         |                |

| Process Engineering Reports ER-20 ETOX II Flash Memory Technology                                                                                       | 9-1            |

| ER-28 ETOX III Flash Memory Technology                                                                                                                  | 9-6            |

# Table of Contents (Continued)

| ER-33 ETOX IV Flash Memory Technology: Insight to Intel's Fourth Generation Process Innovation | 9-19  |

|------------------------------------------------------------------------------------------------|-------|

| CHAPTER 10                                                                                     |       |

| Flash Memory SmartDie™ Products                                                                |       |

| DATA SHEETS                                                                                    |       |

| 28F010 1024K (128K x 8) Flash Memory                                                           | 10-1  |

| 28F020 2048K (256K x 8) Flash Memory                                                           | 10-9  |

| 28F008SA 8 Mbit (1 Mbit x 8) Flash Memory                                                      | 10-17 |

| 28F400BX-T 4 Mbit (256K x 16, 512K x 8) Boot Block Flash Memory                                | 10-25 |

| 28F001BX-T/B 1M (128K x 8) CMOS Flash Memory                                                   | 10-33 |

| CHAPTER 11                                                                                     |       |

| Article Reprints                                                                               | 1     |

| AR-710 Flash Solid-State Drive with 6 MBs Read/Write Channel and Data                          |       |

| Compression                                                                                    | 11-1  |

| AR-711 Flash: Big New in Storage?                                                              | 11-4  |

| AR-715 Flash Memory: Meeting the Needs of Mobile Computing                                     | 11-8  |

| AR-716 Flash Memory for Top Speeds in Mobile Computing Applications                            | 11-16 |

| AR-717 The Many Facts of Flash Memory                                                          | 11-18 |

| · · · · · · · · · · · · · · · · · · ·                                                          | 11-28 |

| AR-723 Interfacing BootBlock Flash Memories to the MCS 96 Family                               | 11-32 |

# Alphanumeric Index

| OREOUT DY TYPOCOUT DY DIAM (4 00)/ VION CHOCK Flock Marrian                         | 4 007 |

|-------------------------------------------------------------------------------------|-------|

| 28F001BX-T/28F001BX-B 1M (128K x 8) CMOS Flash Memory                               | 4-307 |

| 28F001BX-T/B 1M (128K x 8) CMOS Flash Memory                                        | 10-33 |

| 28F008SA 8 Mbit (1 Mbit x 8) Flash Memory                                           | 10-17 |

| 28F008SA 8-Mbit (1-Mbit x 8) FlashFile™ Memory (Extended Temperature Specifications |       |

| Included)                                                                           | 3-443 |

| 28F008SA-L 8 Mbit (1Mbit x 8) Flash Memory                                          | 3-476 |

| 28F010 1024K (128K x 8) CMOS Flash Memory                                           | 5-33  |

| 28F010 1024K (128K x 8) Flash Memory                                                | 10-1  |

| 28F016SA 16-Mbit (1-Mbit x 16, 2-Mbit x 8) FlashFile Memory                         | 3-359 |

| 28F016SV 16-Mbit (1-Mbit x 16, 2-Mbit x 8) FlashFile Memory                         |       |

| 20F0103VD 10-Mibit (1-Mibit X 10, 2-Mibit X 0) Flashfille Methods                   | 3-303 |

| 28F016XD 16-Mbit (1-Mbit x 16) DRAM - Interface Flash Memory                        | 3-50  |

| 28F016XS 16-Mbit (1-Mbit x 16, 2-Mbit x 8) Synchronous Flash Memory                 | 3-3   |

| 28F020 2048K (256K x 8) CMOS Flash Memory                                           | 5-1   |

| 28F020 2048K (256K x 8) Flash Memory                                                | 10-9  |

| 28F200BL-T/B, 28F002BL-T/B 2-Mbit (128K x 16, 256K x 8) Low Power Boot Block Flash  |       |

| Memory Family                                                                       | 4-265 |

| 28F200BX-T/B, 28F002BX-T/B 2 Mbit (128K x 16, 256K x 8) Boot Block Flash Memory     |       |

| Family                                                                              | 4-218 |

| 28F256A 256K (32K x 8) CMOS Flash Memory                                            | 5-92  |

| 28F400BL-T/B, 28F004BL-T/B 4-Mbit (256K x 16, 512K x 8) Low Power Boot Block Flash  | 3-32  |

|                                                                                     | 4 474 |

| Memory Family                                                                       | 4-174 |

| 28F400BX-T 4 Mbit (256K x 16, 512K x 8) Boot Block Flash Memory                     | 10-25 |

| 28F400BX-T/B, 28F004BX-T/B 4 Mbit (256K x 16, 512K x 8) Boot Block Flash Memory     |       |

| Family                                                                              | 4-124 |

| 28F512 512K (64K x 8) CMOS Flash Memory                                             | 5-64  |

| 2-Mbit (128K x 16, 256K x 8) SmartVoltage Boot Block Flash Memory Family (Extended  |       |

| Temperature Specifications Included)                                                | 4-68  |

| 4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family (Extended  | •     |

| Temperature Specifications Included)                                                | 4-13  |

| 8-Mbit (512K x 16, 1-Mbit x 8) SmartVoltage Boot Block Flash Memory Family          | 4-1   |

| A28F010 1024K (128K x 8) CMOS Flash Memory                                          | 8-135 |

| A28F200BR-T/B 2-Mbit (128K x 16, 256K x 8) SmartVoltage Boot Block Flash Memory     | 0-100 |

|                                                                                     | 8-69  |

| Family                                                                              |       |

|                                                                                     | 8-102 |

| A28F256A 256K (32K x 8) CMOS Flash Memory                                           | 8-182 |

| A28F400BR-T/B 4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory     |       |

| Family                                                                              | 8-1   |

| A28F400BX-T/B 4-Mbit (256K x 16, 512K x 8) Boot Block Flash Memory Family           | 8-35  |

| A28F512 512K (64K x 8) CMOS Flash Memory                                            | 8-158 |

| AB-29 Flash Memory Applications in Laser Printers                                   | 2-71  |

| AB-58 28F016XD - Based SIMM Designs                                                 | 3-104 |

| AB-60 2/4/8-Mbit SmartVoltage Boot Block Flash Memory Family Overview               | 4-349 |

| AP-316 Using Flash Memory for In-System Reprogrammable Nonvolatile Storage          | 5-117 |

| AP-325 Guide to First Generation Flash Memory Programming                           | 5-162 |

| AP 244 Designing on Undertable PLOS Height Floor Manner                             |       |

| AP-341 Designing an Updatable BIOS Using Flash Memory                               | 4-357 |

| AP-343 Solutions for High Density Applications Using Intel Flash Memory             | 6-185 |

| AP-357 Power Supply Solutions for Flash Memory                                      | 2-22  |

| AP-359 28F008SA Hardware Interfacing                                                | 3-551 |

| AP-360 28F008SA Software Drivers                                                    | 3-562 |

| AP-361 Implementing the Integrated Registers of the Series 2 Flash Memory Card      | 6-215 |

| AP-362 Implementing Mobile PC Designs Using High Density FlashFile Components       | 3-585 |

| AP-363 Extended Flash Bios Concepts for Portable Computers                          | 4-400 |

# Alphanumeric Index (Continued)

| AP-364 28F008SA Automation and Algorithms                                           | 3-640<br>2-64 |

|-------------------------------------------------------------------------------------|---------------|

| AP-375 Upgrade Considerations from the 28F008SA to the 28F016SA                     | 3-654         |

| AP-375 Opgrade Considerations from the 2010/08A to the 2010/08A                     | 3-054         |

| AP-377 16-Mbit Flash Product Family Software Drivers 28F016SA, 28F016SV, 28F016XS,  | 0.007         |

| 28F016XD                                                                            | 3-667         |

| AP-378 System Optimization Using the Enhanced Features of the 28F016SA              | 3-722         |

| AP-384 Designing with the 28F016XD                                                  | 3-142         |

| AP-393 28F016SV Compatibility with 28F016SA                                         | 3-533         |

| AP-398 Designing with the 28F016XS                                                  | 3-112         |

| AP-399 Implementing Mobile Intel486™ SX Microprocessor PC Designs Using FlashFile   |               |

| Components                                                                          | 3-743         |

| AP-600 Performance Benefits and Power/Energy Savings of 28F016XS-Based System       |               |

| Designs                                                                             | 3-172         |

| AP-604 Using Intel's Boot Block Flash Memory Parameter Blocks to Replace EEPROM     | 4-341         |

| AP-606 Interchangeability of Series 1, Series 2 and Series 2+ Flash Memory Cards    | 6-170         |

| AP-607 Multi-Site Layout Planning with Intel's FlashFile Components, Including ROM  |               |

| Compatibility                                                                       | 3-504         |

| AR-710 Flash Solid-State Drive with 6 MBs Read/Write Channel and Data Compression   | 11-1          |

| AR-711 Flash: Big New in Storage?                                                   | 11-4          |

| AR-715 Flash Memory: Meeting the Needs of Mobile Computing                          | 11-8          |

| AR-716 Flash Memory for Top Speeds in Mobile Computing Applications                 | 11-16         |

| AR-717 The Many Facts of Flash Memory                                               | 11-18         |

| AR-718 Standardizing on a Flash File System                                         | 11-28         |

| AR-723 Interfacing BootBlock Flash Memories to the MCS 96 Family                    | 11-32         |

| Boot Block Flash: The Next Generation White Paper                                   | 4-466         |

| DD28F032SA 32-Mbit (2-Mbit x 16, 4-Mbit x 8) FlashFile Memory                       | 3-257         |

|                                                                                     | 3-257<br>9-1  |

| ER-20 ETOX II Flash Memory Technology                                               |               |

| ER-24 Intel Flash Memory 28F256A, 28F512, 28F010, 28F020                            | 5-184         |

| ER-26 The Intel 28F001BX-T and 28F001BX-B Flash Memories                            | 4-422         |

| ER-27 The Intel 28F008SA Flash Memory                                               | 3-783         |

| ER-28 ETOX III Flash Memory Technology                                              | 9-6           |

| ER-29 The Intel 2/4-Mbit Boot Block Flash Memory Family                             | 4-437         |

| ER-33 ETOX IV Flash Memory Technology: Insight to Intel's Fourth Generation Process |               |

| Innovation                                                                          | 9-19          |

| Extended Temperature 28F016SA 16-Mbit (1-Mbit x 16, 2-Mbit x 8) FlashFile Memory    | 3-403         |

| Flash Drive Design Guide (for iFD005P2SA/iFD010P2SA)                                | 7-46          |

| Flash Memory Card and Flash Drive Evaluation Kit Product Brief                      | 7-118         |

| Flash Memory Card and Flash Drive Evaluation Kit Product Brief                      | 6-232         |

| Flash Memory Card and Flash Drive Evaluation Kit Product Brief                      | 2-16          |

| Flash Memory Customer Support                                                       | 2-7           |

| Flash Memory Overview                                                               | 2-1           |

| iFD005P2SA/iFD010P2SA Flash Drive                                                   | 7-1           |

| iMC001FLKA 1-Megabyte Flash Memory Card                                             | 6-140         |

| iMC002FLKA 2-Mbyte Flash Memory Card                                                | 6-110         |

| iMC004FLKA 4-Megabyte Flash Memory Card                                             | 6-80          |

| Intel 28F016XD Embedded Flash RAM Product Brief                                     | 3-2           |

| Intel 28F016XS Embedded Flash RAM Product Brief                                     | 3-1           |

| Intel FLASHBuilder Software Product Brief                                           | 2-20          |

| Intel FlashFile Memory-The Key to Diskless Mobile PCs                               | 6-234         |

|                                                                                     | 1-1           |

| Intel Memory Technologies                                                           | 3-238         |

| Interfacing the 20F016VS to the interface wildroprocessor Family                    |               |

| Interfacing the 28F016XS to the i960® Microprocessor Family                         | 3-196         |

### ALPHANUMERIC INDEX

# Alphanumeric Index (Continued)

| Multi-APRO Programmer/Intel Support Version                                | 2-13 |

|----------------------------------------------------------------------------|------|

| Series 2 Flash Memory Cards iMC002FLSA/iMC004FLSA/iMC010FLSA/iMC020FLSA    |      |

| (Extended Temperature Specifications Included)                             | 6-42 |

| Series 2+ Flash Memory Card User's Manual Overview                         |      |

| Series 2+ Flash Memory Cards 4-, 8-, 20- and 40-Megabyte                   | 6-2  |

| Small and Low Cost Power Supply Solution for Intel's Flash Memory Products | 2-78 |

| Small Outline Package Guide Overview                                       | 2-18 |

| Sprint PLUS48/Intel Support Version                                        | 2-9  |

intel<sub>®</sub>.

1

**Memory Overview**

Most of this handbook is devoted to techniques and information to help you design and implement semi-conductor memory in your application or system. In this section, however, the memory chip itself will be examined and the processing technology required to turn a bare slice of silicon into high performance memory devices is described. The discussion has been limited to the basics of MOS (Metal Oxide Semiconductor) technologies as they are responsible for the majority of memory devices manufactured at Intel.

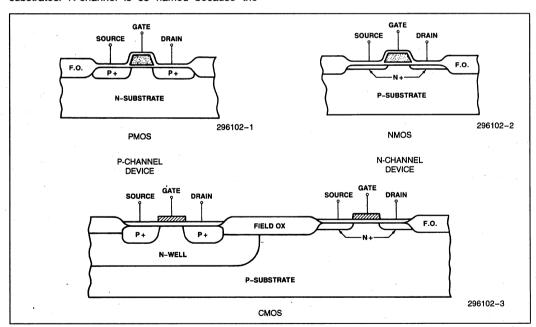

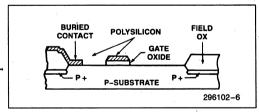

There are three major MOS technology families—PMOS, NMOS, and CMOS (Figure 1). They refer to the channel type of the MOS transistors made with the technology. PMOS technologies implement p-channel transistors by diffusing p-type dopants (usually boron) into an n-type silicon substrate to form the source and drain. P-channel is so named because the channel is comprised of positively charged carriers. NMOS technologies are similar, but use n-type dopants (normally phosphorus or arsenic) to make n-channel transistors in p-type silicon substrates. N-channel is so named because the

channel is comprised of negatively charged carriers. CMOS or Complementary MOS technologies combine both p-channel and n-channel devices on the same silicon. Either p- or n-type silicon substrates can be used, however, deep areas of the opposite doping type (called wells) must be defined to allow fabrication of the complementary transistor type.

Most of the early semiconductor memory devices, like Intel's pioneering 1103 dynamic RAM and 1702 EPROM were made with PMOS technologies. As higher speeds and greater densities were needed, most new devices were implemented with NMOS. This was due to the inherently higher speed of n-channel charge carriers (electrons) in silicon along with improved process margins. CMOS technology has begun to see widespread commercial use in memory devices. It allows for very low power devices used for battery operated or battery back-up applications. Historically, CMOS has been slower than any NMOS device. Today, CMOS technology has been improved to produce higher speed devices.

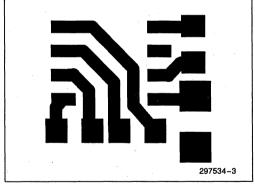

**Figure 1. MOS Process Cross-sections**

In the following section, the basic fabrication sequence for an HMOS circuit will be described. HMOS is a high performance n-channel MOS process developed by Intel for 5V single supply circuits. HMOS, and CHMOS, CHMOS-E (EPROM) and ETOX (Flash Memory), along with their evolutionary counterparts comprise the process family responsible for most of the memory components produced by Intel today.

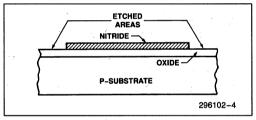

The MOS IC fabrication process begins with a slice (or wafer) of single crystal silicon. Typically, it's 150 or 200 millimeter in diameter, about a half millimeter thick, and uniformly doped p-type. The wafer is then oxidized in a furnace at around 1000°C to grow a thin layer of silicon dioxide (SiO2) on the surface. Silicon nitride is then deposited on the oxidized wafer in a gas phase chemical reactor. The wafer is now ready to receive the first pattern of what is to become a many layered complex circuit. The pattern is etched into the silicon nitride using a process known as photolithography, which will be described in a later section. This first pattern (Figure 2) defines the boundaries of the active regions of the IC, where transistors, capacitors, diffused resistors, and first level interconnects will be made.

Figure 2. First Mask

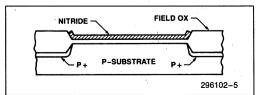

The patterned and etched wafer is then implanted with additional boron atoms accelerated at high energy. The boron will only reach the silicon substrate where the nitride and oxide was etched away, providing areas doped strongly p-type that will electrically separate active areas. After implanting, the wafers are oxidized again and this time a thick oxide is grown. The oxide only grows in the etched areas due to silicon nitride's properties as an oxidation barrier. When the oxide is grown, some of the silicon substrate is consumed and this gives a physical as well as electrical isolation for adjacent devices as can be seen in Figure 3.

Figure 3. Post Field Oxidation

Having fulfilled its purpose, the remaining silicon nitride layer is removed. A light oxide etch follows taking with it the underlying first oxide but leaving the thick (field) oxide.

Now that the areas for active transistors have been defined and isolated, the transistor types needed can be determined. The wafer is again patterned and then if special characteristics (such as depletion mode operation) are required, it is implanted with dopant atoms. The energy and dose at which the dopant atoms are implanted determines much of the transistor's characteristics. The type of the dopant provides for depletion mode (n-type) or enhancement mode (p-type) operation.

The transistor types defined, the gate oxide of the active transistors are grown in a high temperature furnace. Special care must be taken to prevent contamination or inclusion of defects in the oxide and to ensure uniform consistent thickness. This is important to provide precise, reliable device characteristics. The gate oxide layer is then masked and holes are etched to provide for direct gate to diffusion ("buried") contacts where needed.

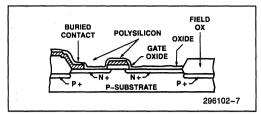

The wafers are now deposited with a layer of gate material. This is typically poly crystaline silicon ("poly") which is deposited in a gas phase chemical reactor similar to that used for silicon nitride. The poly is then doped (usually with phosphorus) to bring the sheet resistance down to  $10-20~\Omega/\mathrm{square}$ . This layer is also used for circuit interconnects and if a lower resistance is required, a refractory metal/poly-silicon composite or refractory metal silicide can be used instead. The gate layer is then patterned to define the actual transistor gates and interconnect paths (Figure 4).

Figure 4. Post Gate Mask

The wafer is next diffused with n-type dopant (typically arsenic or phosphorus) to form the source and drain junctions. The transistor gate material acts as a barrier to the dopant providing an undiffused channel self-aligned to the two junctions. The wafer is then oxidized to seal the junctions from contamination with a layer of SiO<sub>2</sub> (Figure 5).

Figure 5. Post Oxidation

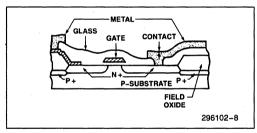

A thick layer glass is then deposited over the wafer to provide for insulation and sufficiently low capacitance between the underlying layers and the metal interconnect signals. (The lower the capacitance, the higher the inherent speed of the device.) The glass layer is then patterned with contact holes and placed in a high temperature furnace. This furnace step smooths the class surface and rounds the contact edges to provide uniform metal coverage. Metal (usually aluminum or aluminum/silicon) is then deposited on the wafer and the interconnect patterns and external bonding pads are defined and etched (Figure 6). The wafers then receive a low temperature (approximately 500°C) alloy that insures good ohmic contact between the aluminum and diffusion or poly.

Figure 6. Complete Circuit (without passivation)

At this point the circuit is fully operational, however, the top metal layer is very soft and easily damaged by handling. The device is also susceptible to contamination or attack from moisture. To prevent this the wafers are sealed with a passivation layer of silicon nitride or a silicon and phosphorus oxide composite. Patterning is done for the last time opening up windows only over the bond pads where external connections will be made.

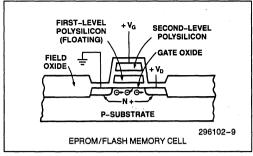

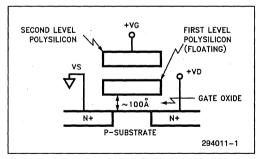

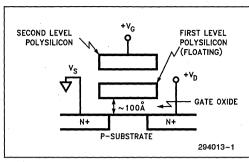

This completes basic fabrication sequence for a single poly layer process. Double poly processes such as those used for high density Dynamic RAMs, EPROMs, flash memories, and EEPROMs follow the same general process flow with the addition of gate, poly deposition, doping, and interlayer dielectric process modules required for the additional poly layer (Figure 7). These steps are performed right after the active areas have been defined (Figure 3) providing the capacitor or floating gate storage nodes on those devices.

Figure 7. Double Poly Structure

After fabrication is complete, the wafers are sent for testing. Each circuit is tested individually under conditions designed to determine which circuits will operate properly both at low temperature and at conditions found in actual operation. Circuits that fail these tests are noted to distinguish them from good circuits. From here the wafers are sent for assembly where they are sawed into individual circuits with a paper-thin diamond blade. The noted circuits are then separated out and the good circuits are sent on for packaging.

Packages fall into two categories—hermetic and non-hermetic. Hermetic packages are Cerdip, where two ceramic halves are sealed with a glass fritt, or ceramic with soldered metal lids. An example of hermetic package assembly is shown in Table 1. Non-hermetic packages are molded plastics.

The ceramic package has two parts, the base, which has the leads and die (or circuit) cavity, and the metal lid. The base is placed on a heater block and a metal alloy preform is inserted. The die is placed on top of the preform which bonds it to the package. Once attached, wires are bonded to the circuit and then connected to the leads. Finally the package is placed in a dry inert atmosphere and the lid is soldered on.

The cerdip package consists of a base, lead frame, and lid. The base is placed on a heater block and the lead frame placed on top. This sets the lead frame in glass attached to the base. The die is then attached and bonded to the leads. Finally the lid is placed on the package and it is inserted in a seal furnace where the glass on the two halves melt together making a hermetic package.

In a plastic package, the key component is the lead frame. The die is attached to a pad on the lead frame and bonded out to the leads with gold wires. The frame then goes to an injection molding machine and the package is formed around the lead frame. After mold the excess plastic is removed and the leads trimmed.

After assembly, the individual circuits are retested at an elevated operating temperature to assure critical operating parameters and separated according to speed and power consumption into individual specification groups. The finished circuits are marked and then readied for shipment.

The basic process flow described above may make VLSI device fabrication sound straightforward, however, there are actually hundreds of individual operations that must be performed correctly to complete a working circuit. It usually takes well over two months to complete all these operations and the many tests and measurements involved throughout the manufacturing process. Many of these details are responsible for ensuring the performance, quality, and reliability you expect from Intel products. The following sections will discuss the technology underlying each of the major process elements mentioned in the basic process flow.

## **PHOTOLITHOGRAPHY**

The photo or masking technology is the most important part of the manufacturing flow if for no other reason than the number of times it is applied to each wafer. The manufacturing process gets more complex in order to make smaller and higher performance circuits. As this happens the number of masking steps increases, the features get smaller, and the tolerance required becomes tighter. This is largely because the minimum size of individual pattern elements determine the size of the whole circuit, effecting its cost and limiting its potential complexity. Early MOS IC's used minimum geometries (lines or spaces) of 8-10 microns (1 micron =  $10^{-6}$ meter  $\approx 1/25.000$  inch). The n-channel processes of the mid 1970's brought this down to approximately 5 microns, and today minimum geometries of 0.8 and even 0.6 microns are in production. This dra-

**Table 1. Typical Hermetic Package Assembly**

| Flow               | Process/Materials                   | Typical Item                                                                               | Frequency                                | Criteria                             |

|--------------------|-------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------|

| Ŷ                  | Wafer                               |                                                                                            |                                          |                                      |

| ) þ                | Die saw, wafer break                | ·                                                                                          |                                          |                                      |

| <b> </b>           | Die wash and plate                  |                                                                                            |                                          |                                      |

| ļ ģ                | Die visual inspection               | Passivation, metal                                                                         | 100% of die                              |                                      |

|                    | QA gate                             |                                                                                            | Every lot                                | 0/76, LTPD = 5%                      |

|                    | Die attach<br>(Process monitor)     | Wet out                                                                                    | 4 × /operator/shift                      | 0/11 LTPD = 20%                      |

| ) · •              | Post die attach visual              |                                                                                            | 100% of devices                          |                                      |

|                    | Wire bond<br>(Process monitor)      | Orientation, lead dressing, etc.                                                           | 4 × /operator/<br>machine/shift          |                                      |

| ļģ                 | Post bond inspection                |                                                                                            | 100% devices                             |                                      |

|                    | QA gate                             | All previous items                                                                         | every lot                                | 1/129, LTPD = 3%                     |

|                    | Seal and Mark<br>(Process monitor)  | Cap align, glass<br>integrity, moisture                                                    | 4 x /furnace/shift                       | 0/15, LTPD = 15%                     |

| • •                | Temp cycle                          | '                                                                                          | 10 × to mil std.<br>883 cond. C          | 1/11, LTPD = 20%                     |

|                    | Hermeticity check (Process monitor) | F/G leak                                                                                   | 100% devices                             |                                      |

|                    | Lead Trim<br>(Process monitor)      | Burrs, etc. (visual)<br>Fine leak                                                          | 4 × /station/shift<br>2 × /station/shift | 0/15, LTPD = 15%<br>1/129, LTPD = 3% |

|                    | External visual                     | Solder voids, cap alignment, etc.                                                          | 100% devices                             |                                      |

| <del>-   -</del> > | QA gate                             | All previous items                                                                         | All lots                                 | 1/129, LTPD=3%                       |

|                    | Class test<br>(Process monitor)     | Run standards<br>(good and reject)<br>Calibrate every<br>system using<br>"autover" program | Every 48 hrs.                            | *                                    |

| امیا               | Mark and Pack                       |                                                                                            |                                          |                                      |

| 2.                 | Final QA                            | (See attached)                                                                             |                                          |                                      |

296102-11

#### NOTES:

- 1. Units for assembly reliability monitor.

- 2. Units for product reliability monitor.

matic reduction in feature size was achieved using the newer high resolution photo resists and optimizing their processing to match improved optical printing systems.

A second major factor in determining the size of the circuit is the registration or overlay error. This is how accurately one pattern can be aligned to a previous one. Design rules require that space be left in all directions according to the overlay error so that unrelated patterns do not overlap or interfere with one another. As the error space increases the circuit size increases dramatically. Only a few years ago standard alignment tolerances were  $\geq \pm 2$  microns; now advanced Intel processes have reduced this dramatically due mostly to the use of advanced projection and step and repeat exposure equipment.

The wafer that is ready for patterning must go through many individual steps before that pattern is complete. First the wafer is baked to remove moisture from its surface and is then treated with chemicals that ensure good resist adhesion. The thick photoresist liquid is then applied and the wafer is spun flat to give a uniform coating, critical for high resolution. The wafer is baked at a low temperature to solidify the resist into gel. It is then exposed with a machine that aligns a mask with the new pattern on it to a previously defined layer. The photo-resist will replicate this pattern on the wafer.

Negative working resists are polymerized by the light and the unexposed resist can be rinsed off with solvents. Positive working resists use photosensitive polymerization inhibitors that allow a chemically reactive developer to remove the exposed areas. The positive resists require much tighter control of exposure and development but yield higher resolution patterns than negative resistance systems.

The wafer is now ready to have its pattern etched. The etch procedure is specialized for each layer to be etched. Wet chemical etchants such as hydrofluoric acid for silicon oxide or phosphoric acid for aluminum are often used for this. The need for smaller features and tighter control of etched dimensions is increasing the use of plasma etching in fabrication. Here a reactor is run with a partial vacuum into which etchant gases are introduced and an electrical field is applied. This yields a reactive plasma which etches the required layer.

The wafer is now ready for the next process step. Its single journey through the masking process required the careful engineering of mechanics, optics, organic chemistry, inorganic chemistry, plasma chemistry, physics, and electronics.

### DIFFUSION

The picture of clean room garbed operators tending furnace tubes glowing cherry red is the one most often associated with IC fabrication. These furnace operations are referred to collectively as diffusion because they employ the principle of sold state diffusion of matter to accomplish their results. In MOS processing, there are three main types of diffusion operations: predeps, drives, and oxidations.

Predeposition, or "predep," is an operation where a dopant is introduced into the furnace from a solid, liquid, or gaseous source and at the furnace temperature (usually 900°C-1200°C) a saturated solution is formed at the silicon surface. The temperature of the furnace, the dopant atom, and rate of introduction are all engineered to give a specific dose of the dopant on the wafer. Once this is completed the wafer is given a drive cycle where the dopant left at the surface by the predep is driven into the wafer by high temperatures. These are generally at different temperatures than the predeps and are designed to give the required junction depth and concentration profile

Oxidation, the third category, is used at many steps of the process as was shown in the process flow. The temperature and oxidizing ambient can range from 800°C to 1200°C and from pure oxygen to mixtures of oxygen and other gases to steam depending on the type of oxide required. Gate oxides require high dielectric breakdown strength for thin layers (between 0.01 and 0.1 micron) and very tight control over thickness (typically  $\pm\,0.005$  micron or less than  $\pm\,1/5,000,000$  inch), while isolation oxides need to be quite thick and because of this their dielectric breakdown strength per unit thickness is much less important.

The properties of the diffused junctions and oxides are key to the performance and reliability of the finished device so the diffusion operations must be extremely well controlled for accuracy, consistency and purity.

## ION IMPLANT

Intel's high performance products require such high accuracy and repeatability of dopant control that even the high degree of control provided by diffusion operations is inadequate. However, this limitation has been overcome by replacing critical predeps with ion implantation. In ion implantation, ionized dopant atoms are accelerated by an electric field

## INTEL MEMORY TECHNOLOGIES

and implanted directly into the wafer. The acceleration potential determines the depth to which the dopant is implanted.

The charged ions can be counted electrically during implantation giving very tight control over dose. The ion implanters used to perform this are a combination of high vacuum system, ion source, mass spectrometer, linear accelerator, ultra high resolution current integrator, and ion beam scanner. You can see that this important technique requires a host of sophisticated technologies to support it.

## THIN FILMS

Thin film depositions make up most of the features on the completed circuit. They include the silicon nitride for defining isolation, polysilicon for the gate and interconnections, the glass for interlayer dielectric, metal for interconnection and external connections, and passivation layers. Thin film depositions are done by two main methods: physical deposition and chemical vapor deposition. Physical deposition is most common for deposition metal. Physical depositions are performed in a vacuum and are accomplished by vaporizing the metal with a high energy electron beam and redepositing it on the wafer or by sputtering it from a target to the wafer under an electric field.

Chemical vapor deposition can be done at atmospheric pressure or under a moderate vacuum. This type of deposition is performed when chemical gas-

es react at the wafer surface and deposit a solid film of the reaction product. These reactors, unlike their general industrial counterparts, must be controlled on a microscale to provide exact chemical and physical properties for thin films such as silicon dioxide, silicon nitride, and polysilicon.

The fabrication of modern memory devices is a long, complex process where each step must be monitored, measured and verified. Developing a totally new manufacturing process for each new product or even product line takes a long time and involves significant risk. Because of this, Intel has developed process families, such as HMOS, on which a wide variety of devices can be made. These families are scalable so that circuits need not be totally redesigned to meet your needs for higher performance.(1) They are evolutionary so that development time of new processes and products can be reduced without compromising Intel's commitment to consistency, quality, and reliability.

The manufacture of today's MOS memory devices requires a tremendous variety of technologies and manufacturing techniques, many more than could be mentioned here. Each requires a team of experts to design, optimize, control and maintain it. All these people and thousands of others involved in engineering, design, testing and production stand behind Intel's products.

(1)R. Pashley, K. Kokkonen, E. Boleky, R. Jecmen, S. Liu, and W. Owen, "H-MOS Scales Traditional Devices to Higher Performance Level," *Electronics*, August 18, 1977.

intel<sub>®</sub>

2

# Flash Memory Overview and Support Tools

2

# Flash Memory Overview

The ideal memory system optimizes density, nonvolatility, fast readability and cost effectiveness. While traditional memory technologies may individually exhibit one or more of these desired characteristics, no single memory technology has achieved all of them without major tradeoffs—until the introduction of Intel Flash Memory.

## WHAT IS FLASH MEMORY?

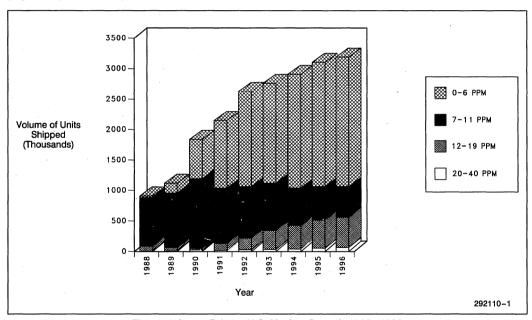

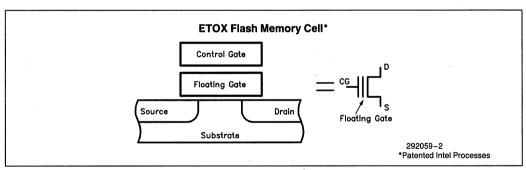

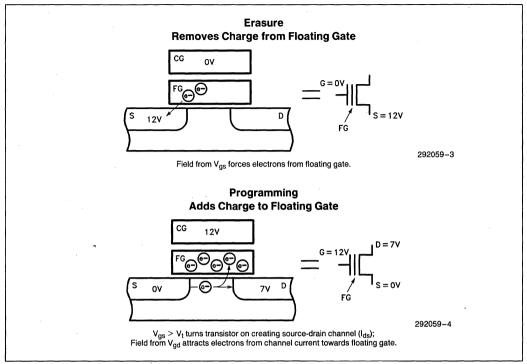

Introduced by Intel in 1988, ETOX flash memory is a high-density, truly nonvolatile and high performance read-write memory solution also characterized by low power consumption and extreme ruggedness and high reliability. The cost trend of Intel Flash Memory components continues to decline sharply due to: (1) manufacturing economies inherent in ETOX, Intel's industry-standard EPROM-based flash technology, (2) increases in memory density, and (3) rapid growth in production volume.

A comparison between Intel Flash Memory and other solid-state memory technologies underscores the fact that flash offers a design solution with distinct advantages. These advantages are key to future product differentiation for many applications requiring firmware updates or compact mass storage (Figure 1).

— ROM (read-only memory) is a mature, high density, nonvolatile, reliable and low cost memory technology widely used in PC and embedded applications. Once it is manufactured however, the contents of a ROM can never be altered. Additionally, initial ROM programming involves a time-consuming mask development process that requires stable code and is most cost-effective in high volumes.

Easy updatability makes flash memory clearly more flexible than ROM in most applications.

— SRAM (static random-access memory) is a high-speed, reprogrammable memory technology which is limited by its volatility and relatively low density. As a volatile memory technology, SRAM requires constant power to retain its contents. Built-in battery backup is therefore required when the main power source is turned off. Since battery failure is an inevitable fact of life, SRAM data loss is an everpresent danger. Additionally, SRAM requires four to six transistors to store one bit of information. This becomes a significant limitation in developing higher densities—effectively keeping SRAM cost relatively high.

Figure 1. Intel Flash Memory vs Traditional Memory Technologies

| Memory         | Inherently<br>Non-<br>Volatile | High<br>Density | Low<br>Power | One<br>Transistor<br>Cell | In-System<br>Re-<br>Writable | and Data | Alteranie | Blocking | Hands<br>off<br>Updates |

|----------------|--------------------------------|-----------------|--------------|---------------------------|------------------------------|----------|-----------|----------|-------------------------|

| Flash          | · 1                            | <u> </u>        | -            | <i>u</i>                  | 10                           | <i>u</i> |           | 10       | 10                      |

| SRAM + Battery |                                |                 |              |                           | ~                            | -        | ~         | <i>u</i> | <i>u</i>                |

| DRAM + Disk    |                                | <i>u</i>        |              |                           | -                            | <i>u</i> | <i>u</i>  | <i>u</i> | "                       |

| EEPROM         | ~                              |                 | "            |                           | "                            | -        | -         | -        | <i>u</i>                |

| OTP/EPROM      | ~                              | <i>u</i>        | <u></u>      | "                         |                              |          |           |          |                         |

| Masked ROM     | ~                              | "               | 1            | -                         |                              |          |           |          |                         |

### **FLASH MEMORY OVERVIEW**

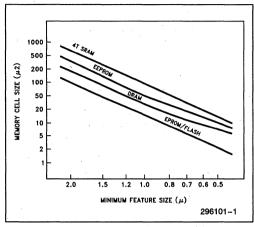

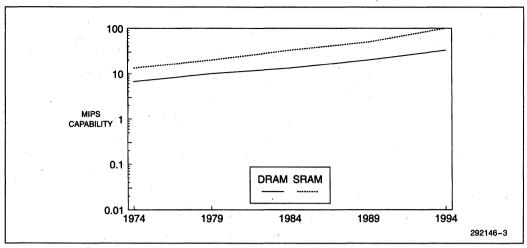

In contrast, Intel flash memory is inherently nonvolatile, and the single transistor cell design of Intel's ETOX manufacturing process is extremely scalable, allowing the development of continuously higher densities and steady cost improvement over SRAM (Figure 2).

Figure 2

— EPROM (electrically programmable read-only memory) is a mature, high-density, nonvolatile technology which provides a degree of updatability not found in ROM. An OEM may program EPROM as needed to accommodate code changes or varying manufacturing unit quantities. Once programmed, however, the EPROM may only be erased by removing it from the system and then exposing the memory component to ultraviolet light—an impractical and time-consuming procedure for many OEMs and a virtually impossible task for end-users.

Unlike EPROM, flash memory is electrically re-writable within the host system, making it a much more flexible and easier to use alternative. Flash memory offers OEMs not only high density and nonvolatility, but higher functionality and the ability to differentiate their systems.

— EEPROM (electrically erasable programmable read-only memory) is nonvolatile and electrically byte-erasable. Such byte-alterability is needed in certain applications but involves a more complex cell structure, and significant trade-offs in terms of limited density, lower reliability and higher cost, making it unsuitable as a mainstream memory.

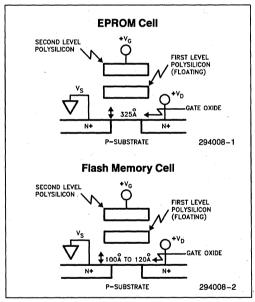

Unlike EEPROM, Intel flash memory technology utilizes a one-transistor cell, allowing higher densities, scalability, lower cost, and higher reliability, while taking advantage of in-system, electrical erasability (Figure 3).

| ·                                  | Intel<br>ETOX Flash | EEPROM |

|------------------------------------|---------------------|--------|

| Transistors                        | 1                   | 2      |

| Cell Size<br>(1-Micro Lithogrpahy) | 15μ                 | 38μ    |

| Cycling Features                   | 0.1%                | 5%     |

Figure 3

— DRAM (dynamic random access memory) is a volatile memory known for its density and low cost. Because of its volatility, however, it requires not only a constant power supply to retain data, but also an archival storage technology, such as disk, to back it up.

Partnered with hard disks for permanent mass storage, DRAM technology has provided a low-cost, yet space and power-hungry solution for today's PCs.

With ETOX process technology, Intel manufactures a flash memory cell that is 30% smaller than equivalent DRAM cells. Flash memory's scalability offers a price advantage as well, keeping price parity with DRAM, and also becoming more attractive as a hard disk replacement in portable systems as densities grow and costs decline.

Intel flash memory combines advantages from each of these memory technologies. In embedded memory applications, flash memory provides higher-performance and more flexibility than ROM and EPROM, while providing higher density and better cost effectiveness than battery-backed SRAM and EEPROM. Moreover, the true nonvolatility and low power consumption characteristics of flash memory make it a compelling alternative to DRAM in many applications.

## **ETOX III TECHNOLOGY**

Unlike other approaches to flash memory, Intel ETOX is a proven technology. As its name suggests, ETOX (or "EPROM tunnel oxide") technology evolved from EPROM. With 95% process compatibility with EPROM, ETOX taps experience gained from a mature high-volume manufacturing base pioneered by Intel in the 1970s.

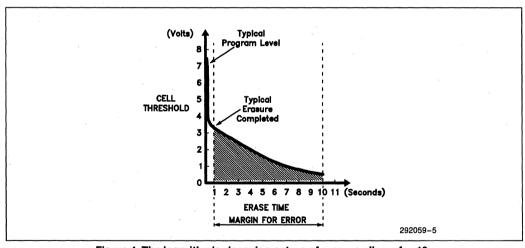

Data retention and lifetime reliability statistics for ETOX III flash are equivalent to those of EPROM. Representing the third generation of Intel flash memory technology, the ETOX III O.8µ process provides <100 FITS (failures in time) @ 55°C in a specification that delivers 100,000 write cycles per block. This capability significantly exceeds the cycling requirements of even the most demanding applications.

For example, code storage for embedded control programs used in standard computer applications is infrequently updated. Twenty-year system lifetimes may require fewer than 100 rewrites. Even routinely-changed data tables (used in navigational computers and black box controllers) only require about 1,000 write cycles over a 20-year period. The most demanding flash memory application of all, archival data storage in PC applications, typically requires about 5,000 write cycles in 20 years.

ETOX flash memory's simple single-transistor cell structure makes it smaller than other flash cells, allowing designers to create highly integrated systems which are more reliable and cost-effective than those based on more complex and less mature flash technologies. The inherent scalability of ETOX III Flash Memory and high-volume manufacturing is enabling a corresponding downtrend in flash cost.

Flash memory has added a new dimension to nonvolatile memory applications. Embedded systems, such as PC BIOS, hard disk drive controllers and cellular telephone applications take advantage of the easy update capability, high density and high performance of Intel Flash Memory. Today's new generation of portable computers require the optimum combination of performance, size, weight, low power and shock resistance. Whether implemented in memory cards, solid state disks or at the component level, Intel's Flash Memories are also enabling a whole new generation of mobile computers.

# IMPLEMENTING INTEL FLASH MEMORY

Today, Intel continues to serve both updatable nonvolatile memory applications as well as the rapidly emerging solid-state mass storage applications with flash memory solutions tailored to meet the needs of these markets.

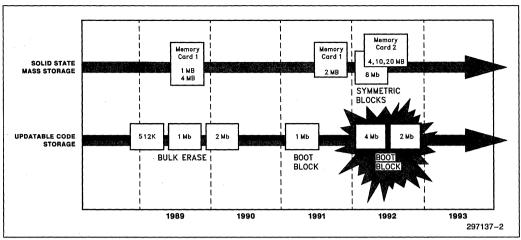

# **Updatable Code Storage**

Code and data storage comprise the updatable nonvolatile memory applications that require high performance, high density, and easy update capability. Because these applications are not updated as frequently as solid-state mass storage applications, erase/write cycles are not as critical as integration and performance requirements. This application segment is served effectively with full chip-erase or Boot Block products.

Intel's 28F001BX 1 Mbit Boot Block flash component. featuring a sectored architecture, has been widely accepted in embedded code storage applications, particularly in PC BIOS and cellular communications. By adopting Boot Block for their products, over 20 PC manufacturers have gained added flexibility and the ability to differentiate in a highly competitive market. End users also benefit from the ability to upgrade BIOS software quickly and securely. The blocked architecture allows the OEM to store critical system code securely in the lockable "boot block" of the device that can minimally bring up the system and download to other locations of the device to initialize the system. The hardware boot locking feature guarantees that even if the power is disrupted during a BIOS update, the system will be able to recover immediately.

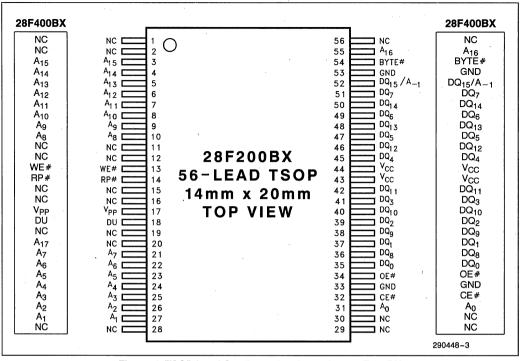

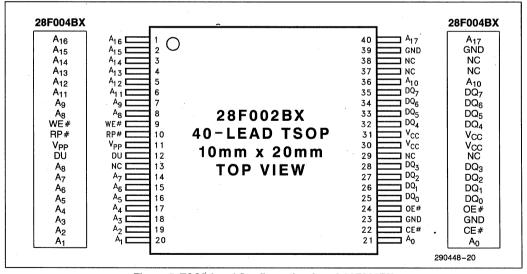

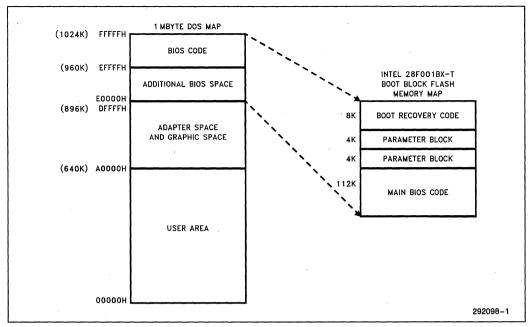

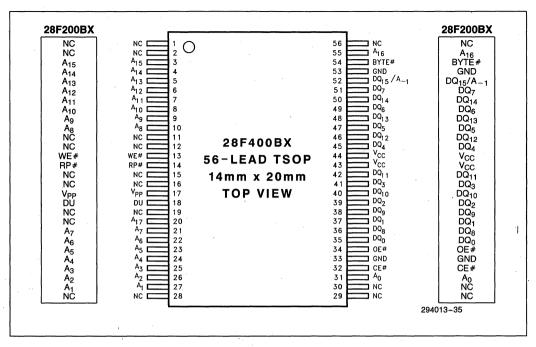

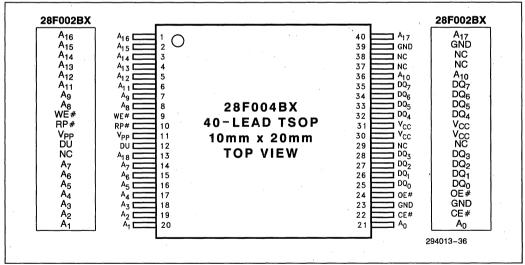

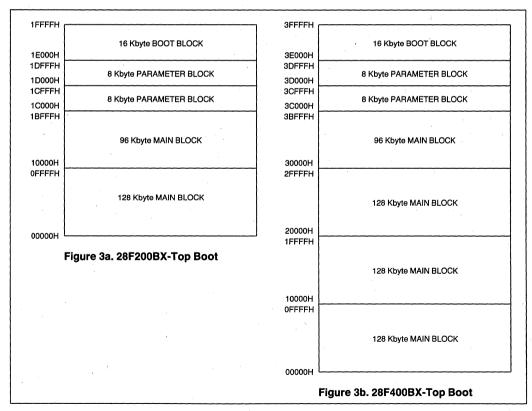

In response to customer requests for speed, density, low power, surface-mount options and an industry-standard upgrade path for portable computing and telecommunications, Intel more recently introduced the 2 Mbit 28F200BX and 4 Mbit 28F400BX Boot Block products