# **CBT Bus Switches Crossbar Technology**

-

**CBT Bus Switches Crossbar Technology**

1995

1995

Advanced System Logic Products

Data Book

| General Information                      | 1 |

|------------------------------------------|---|

| CBT Octals                               | 2 |

| <b>CBT Octals With Integrated Diodes</b> | 3 |

| CBT Widebus™                             | 4 |

| Application Note                         | 5 |

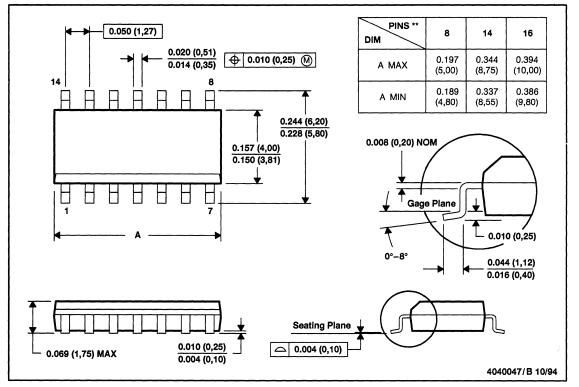

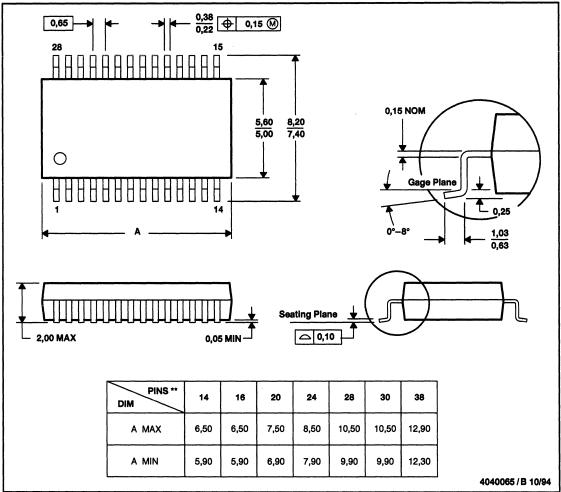

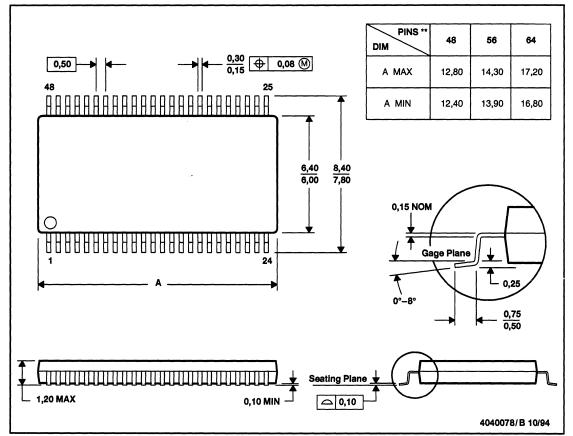

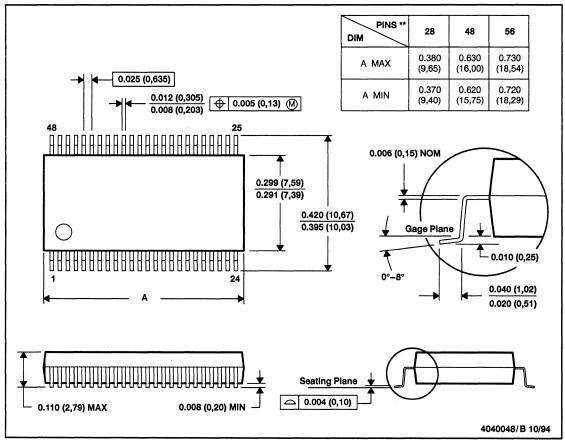

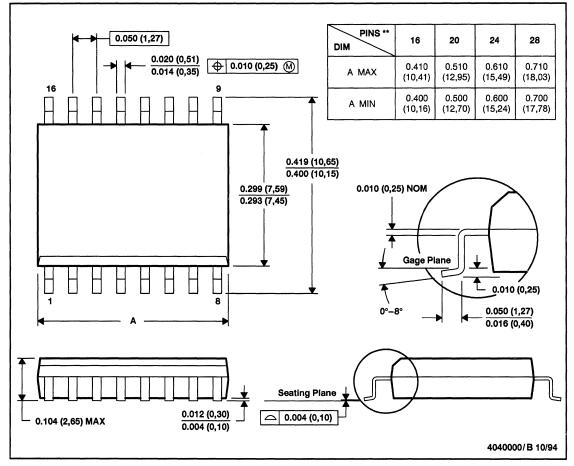

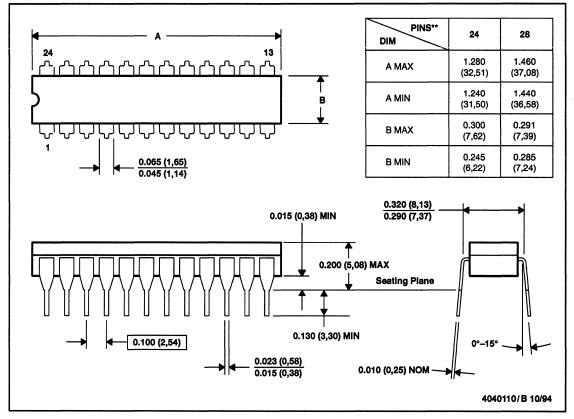

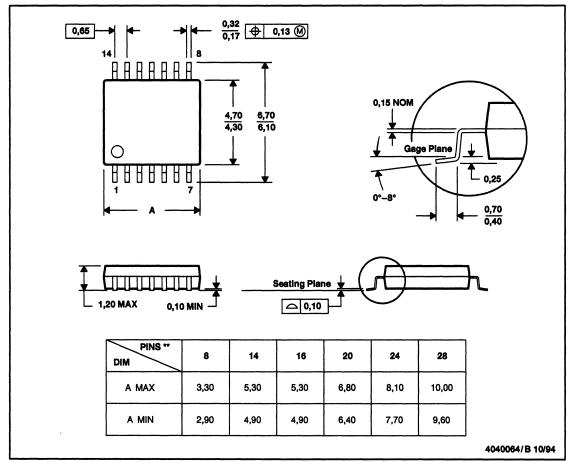

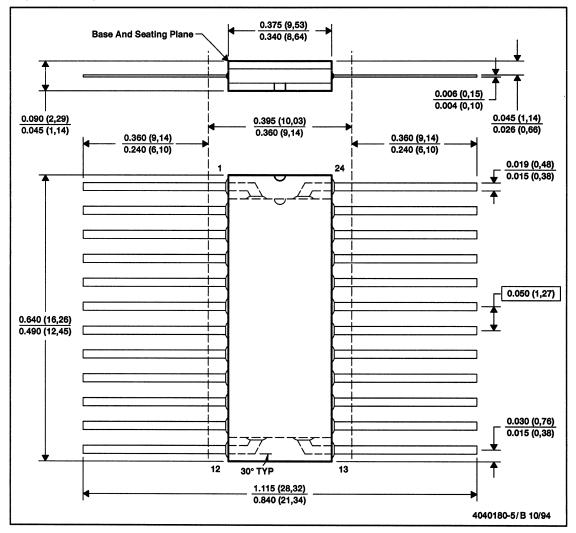

| Mechanical Data                          | 6 |

# CBT Bus Switches Crossbar Technology Data Book

•

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1995, Texas Instruments Incorporated

Printed in U.S.A. by Custom Printing Company Owensville, Missouri

### INTRODUCTION

Digital electronics are performing at ever higher speeds; therefore, every barrier to system performance must be removed. High-speed microprocessors, synchronous DRAMs, and new bus architectures require supporting logic that keeps data moving fast.

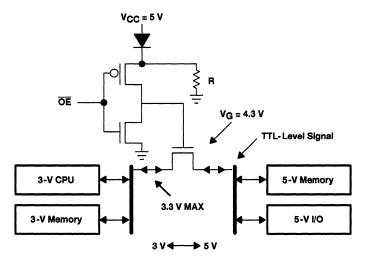

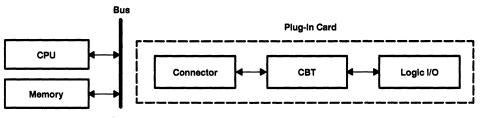

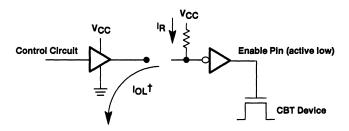

This edition of the Texas Instruments 1995 CBT Bus Switches Crossbar Technology Data Book includes the industry's most comprehensive line of integrated bus switches. With propagation delays of 250 ps, these high-speed bus switches bring greater system speed and reduced power consumption to today's advanced electronic equipment. These n-channel MOS transistors provide isolation (3-state) when the switch is open and near-zero propagation delay when the switch is closed. CBT switches also function as 5-V to 3.3-V level translators, helping designers mix low-cost DRAMs with high-performance 3-V processors.

The CBT family of bus switches consists of 4-, 8-, 10-, 16-, 18-, and 24-bit-wide switches, exchangers, and multiplexers. With pin-for-pin compatible devices, the migration from existing logic devices is easy. These products are offered in the industry's most extensive line of packaging including the world's smallest octal package and the distributed power and ground Widebus™ package.

Most of the products in this data book are available in production quantities. Please contact your local authorized distributor or Texas Instruments representative for details on any of these devices. Some of the devices in this data book are not yet available in production quantities; information on these devices is included as Advanced Information or Product Preview. For more information on these products including availability dates, pricing, and final timing specifications, please contact your local Texas Instruments representative, authorized distributor, or call the Advanced System Logic hotline at (903) 868-5202.

We hope that you agree that Texas Instruments has the most complete line of bus-switch products in the industry. We also hope that these products meet your system and design needs.

Widebus is a trademark of Texas Instruments Incorporated.

#### **PRODUCT STAGE STATEMENTS**

*Product stage statements* are used on Texas Instruments data sheets to indicate the development stage(s) of the product(s) specified in the data sheets.

If all products specified in a data sheet are at the same development stage, the appropriate statement from the following list is placed in the lower left corner of the first page of the data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

If not all products specified in a data sheet are at the PRODUCTION DATA stage, then the first statement below is placed in the lower left corner of the first page of the data sheet. Subsequent pages of the data sheet containing PRODUCT PREVIEW information or ADVANCE INFORMATION are then marked in the lower left-hand corner with the appropriate statement given below:

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

| General Information               | 1 |

|-----------------------------------|---|

| CBT Octals                        | 2 |

| CBT Octals With Integrated Diodes | 3 |

| CBT Widebus™                      | 4 |

| Application Note                  | 5 |

| Mechanical Data                   | 6 |

.

# Contents

|                       | Page   |

|-----------------------|--------|

| Alphanumeric Index    | . 1-3  |

| Cross-Reference Guide | . 1-5  |

| Glossary              | . 1-7  |

| Thermal Information   | . 1-11 |

#### DEVICE

# CBT Octals

| BT Octals          |    |

|--------------------|----|

| SN74CBT31252       | -3 |

| SN74CBT31262       | -7 |

| SN74CBT3244        | 11 |

| SN74CBT3245 2-     | 15 |

| SN74CBT3251 2-     | 19 |

| SN74CBT3253 2-2    | 23 |

| SN74CBT3257 2-2    | 27 |

| SN74CBT3306 2-3    | 31 |

| SN74CBT3345 2-3    | 35 |

| SN54/74CBT3383 2-3 | 39 |

| SN74CBT3384A 2-4   | 43 |

| SN74CBT3386 2-4    | 47 |

|                    |    |

PAGE

| DEVICE                            | PAGE  |

|-----------------------------------|-------|

| SN74CBT3388                       | 2-51  |

| SN74CBT6800                       | 2-55  |

| CBT Octals With Integrated Diodes |       |

| SN74CBTD3384                      | . 3-3 |

| SN74CBTS3384                      | 3-7   |

| CBT Widebus                       |       |

| SN54/74CBT16209                   | 4-3   |

| SN74CBT16211                      | 4 -7  |

| SN74CBT16212                      | 4-11  |

| SN74CBT16213                      | 4-15  |

| SN74CBT16214                      | 4-19  |

| SN74CBT16232                      | 4-23  |

| SN74CBT16233                      | 4-27  |

|                                   |       |

•

1-4

# INTRODUCTION

Replacements are based on similarity of electrical and mechanical characteristics shown in currently published data. Interchangeability in particular applications is not ensured. Before using a device as a substitute, the user should compare the specifications of the substitute device with the specifications of the original.

Texas Instruments makes no warranty as to the information furnished and the buyer assumes all risk in the use thereof. No liability is assumed for damages resulting from the use of the information contained herein.

#### **TEXAS INSTRUMENTS** QUALITY PERICOM SN74CBT3125 QS3125 PI5C3125 SN74CBT3126<sup>†</sup> PI5C3126 SN74CBT3244 QS3244 PI5C3244 SN74CBT3245 QS3245 PI5C3245 SN74CBT3251<sup>†</sup> QS3251 PI5C3251 SN74CBT3253<sup>†</sup> QS3253 PI5C3253 SN74CBT3257 QS3257 PI5C3257 SN74CBT3306 ----------SN74CBT3345 SN74CBT3383 QS3383, QS3L383 PI5C3383 SN74CBT3384A QS3384, QS3L384 PI5C3384 SN74CBT3386<sup>†</sup> QS3386 \_ SN74CBT3388<sup>†</sup> QS3388 \_ SN74CBT6800 QS3800 -

### **CBT** octal function cross-reference guide

<sup>†</sup> Please contact the Advanced System Logic hotline at (903) 868-5202 to learn more about plans for these devices.

#### package cross-reference guide

| TEXAS INSTRUMENTS | QUALITY | PERICOM |

|-------------------|---------|---------|

| D                 | S1      | W       |

| DB                |         | —       |

| DW                | SO      | S       |

| PW‡               |         | L       |

<sup>‡</sup>Smallest CBT package

1-6

### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

# **OPERATING CONDITIONS AND CHARACTERISTICS (IN SEQUENCE BY LETTER SYMBOLS)**

C<sub>i</sub> Input capacitance

The internal capacitance at an input of the device

Co Output capacitance

The internal capacitance at an output of the device

# C<sub>pd</sub> Power dissipation capacitance

Used to determine the no-load dynamic power dissipation per logic function (see individual circuit pages):  $P_D = C_{pd} V_{CC}^2 f + I_{CC} V_{CC}$ .

# f<sub>max</sub> Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification

#### I<sub>CC</sub> Supply current

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit

# △I<sub>CC</sub> Supply current change

The increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or  $V_{CC}$

# ICEX Output high leakage current

The maximum leakage current into the collector of the pulldown output transistor when the output is high and the output forcing condition  $V_{O}$  = 5.5 V

### Input hold current

Input current that holds the input at the previous state when the driving device goes to a high-impedance state

#### I<sub>IH</sub> High-level input current

The current into\* an input when a high-level voltage is applied to that input

# IIL Low-level input current

The current into\* an input when a low-level voltage is applied to that input

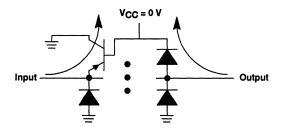

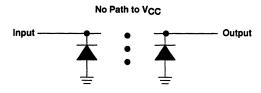

#### Input/output power-off leakage current

The maximum leakage current into/out of the input/output transistors when forcing the input/output to 4.5 V and V\_{CC} = 0 V

#### I<sub>OH</sub> High-level output current

The current into\* an output with input conditions applied that, according to the product specification, establish a high level at the output

#### IOL Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, establish a low level at the output

\*Current out of a terminal is given as a negative value.

# GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

| loz              | Off-state (high-impedance-state) output current (of a 3-state output) |                                                                                                                                                                                                                                                                                                  |  |  |

|------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                  |                                                                       | rent flowing into* an output having 3-state capability with input conditions established that, ig to the product specification, establish the high-impedance state at the output                                                                                                                 |  |  |

| ta               | Access                                                                |                                                                                                                                                                                                                                                                                                  |  |  |

|                  | The time<br>at an ou                                                  | e interval between the application of a specified input pulse and the availability of valid signals tput                                                                                                                                                                                         |  |  |

| t <sub>dis</sub> | Disable                                                               | time (of a 3-state or open-collector output)                                                                                                                                                                                                                                                     |  |  |

|                  |                                                                       | bagation time between the specified reference points on the input and output voltage waveforms<br>output changing from either of the defined active levels (high or low) to a high-impedance (off)                                                                                               |  |  |

|                  | NOTE:                                                                 | For 3-state outputs, $t_{dis} = t_{PHZ}$ or $t_{PLZ}$ . Open-collector outputs change only if they are low at the time of disabling so $t_{dis} = t_{PLH}$ .                                                                                                                                     |  |  |

| t <sub>en</sub>  | Enable                                                                | time (of a 3-state or open-collector output)                                                                                                                                                                                                                                                     |  |  |

|                  |                                                                       | bagation time between the specified reference points on the input and output voltage waveforms<br>output changing from a high-impedance (off) state to either of the defined active levels (high or                                                                                              |  |  |

|                  | NOTE:                                                                 | In the case of memories, this is the access time from an enable input (e.g., $\overline{OE}$ ). For 3-state outputs, $t_{en} = t_{PZH}$ or $t_{PZL}$ . Open-collector outputs change only if they are responding to data that would cause the output to go low so, for them $t_{en} = t_{PHL}$ . |  |  |

| t <sub>h</sub>   | Hold tin                                                              | ne                                                                                                                                                                                                                                                                                               |  |  |

|                  |                                                                       | e interval during which a signal is retained at a specified input terminal after an active transition<br>at another specified input terminal.                                                                                                                                                    |  |  |

|                  | NOTES:                                                                | 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is to be expected.                   |  |  |

|                  |                                                                       | 2. The hold time may have a negative value, in which case, the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is to be expected.                                                    |  |  |

| t <sub>pd</sub>  | Propaga                                                               | ation delay time                                                                                                                                                                                                                                                                                 |  |  |

|                  |                                                                       | e between the specified reference points on the input and output voltage waveforms with the hanging from one defined level (high or low) to the other defined level ( $t_{pd} = t_{PHL}$ or $t_{PLH}$ )                                                                                          |  |  |

| t <sub>PHL</sub> | Propaga                                                               | ation delay time, high-to-low level output                                                                                                                                                                                                                                                       |  |  |

|                  |                                                                       | e between the specified reference points on the input and output voltage waveforms with the hanging from the defined high level to the defined low level                                                                                                                                         |  |  |

| <sup>t</sup> PHZ |                                                                       | time (of a 3-state output) from high level                                                                                                                                                                                                                                                       |  |  |

|                  |                                                                       | e interval between the specified reference points on the input and the output voltage waveforms<br>3-state output changing from the defined high level to a high-impedance (off) state                                                                                                           |  |  |

| t <sub>PLH</sub> | Propaga                                                               | ation delay time, low-to-high level output                                                                                                                                                                                                                                                       |  |  |

|                  |                                                                       | e between the specified reference points on the input and output voltage waveforms with the hanging from the defined low level to the defined high level                                                                                                                                         |  |  |

| t <sub>PLZ</sub> | Disable                                                               | time (of a 3-state output) from low level                                                                                                                                                                                                                                                        |  |  |

|                  |                                                                       | e interval between the specified reference points on the input and the output voltage waveforms<br>3-state output changing from the defined low level to a high-impedance (off) state                                                                                                            |  |  |

# t<sub>PZH</sub> Enable time (of a 3-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to the defined high level

# tpzL Enable time (of a 3-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to the defined low level

# tsk(o) Output skew

The difference between any two propagation delay times when a single switching input or multiple inputs switching simultaneously cause multiple outputs to switch, as observed across all switching outputs. This parameter is used to describe the fanout capability of a clock driver and is of concern when making decisions on clock buffering and distribution networks.

# t<sub>su</sub> Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

- NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- 2. The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

# tw Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform

# VIH High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is to be expected.

# V<sub>IL</sub> Low-level input voltage

An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A maximum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is to be expected.

# V<sub>OH</sub> High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, establish a high level at the output

# V<sub>OL</sub> Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, establish a low level at the output

# V<sub>T+</sub> Positive-going threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage rises from a level below the negative-going threshold voltage,  $V_{T-}$

# V<sub>T</sub>\_\_\_\_ Negative-going threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage falls from a level above the positive-going threshold voltage,  $V_{T+}$

1-10

•

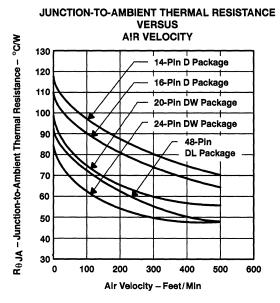

In digital-system design, consideration must be given to thermal management of components. The small size of the small-outline package makes this even more critical. Figure 1 shows the thermal resistance of these packages for various rates of air flow.

The thermal resistances in Figure 1 can be used to approximate typical and maximum virtual junction temperatures for the CBT family. In general, the junction temperature for any device can be calculated using the following equation:

$$T_{J} = R_{\Theta JA} \times P_{T} + T_{A}$$

Where:

T<sub>J</sub> = virtual junction temperature

$R_{\theta JA}$  = thermal resistance, junction to ambient

$P_T$  = total power dissipation of the device

$T_A$  = free-air temperature

Figure 1

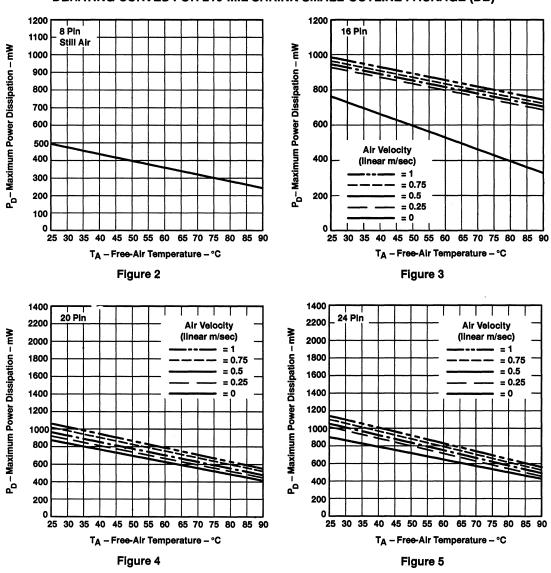

Figures 2 through 5 show power dissipation derating for the 8-, 16,-20-, and 24-pin DB packages.

DERATING CURVES FOR 210-MIL SHRINK SMALL-OUTLINE PACKAGE (DB)

| General Information               | 1 |

|-----------------------------------|---|

| CBT Octals                        | 2 |

| CBT Octals With Integrated Diodes | 3 |

| CBT Widebus™                      | 4 |

| Application Note                  | 5 |

| Mechanical Data                   | 6 |

# Contents

| • | 2     |

|---|-------|

|   | СВТ   |

|   | Ō     |

|   | ctals |

|           |                                                              | Page |

|-----------|--------------------------------------------------------------|------|

| 'CBT3125  | Quadruple Bus Switch                                         | 2-3  |

| 'CBT3126  | Quadruple Bus Switch                                         | 2-7  |

| 'CBT3244  | Octal Bus Switch                                             | 2-11 |

| 'CBT3245  | Octal Bus Switch                                             | 2-15 |

| 'CBT3251  | 8-Bit to 1-Bit FET Multiplexer/Demultiplexer                 | 2-19 |

| 'CBT3253  | Dual 4-Bit to 1-Bit FET Multiplexer/Demultiplexer            | 2-23 |

| 'CBT3257  | Quadruple 2-Bit to 1-Bit FET Multiplexer/Demultiplexer       | 2-27 |

| 'CBT3306  | Dual Bus Switch                                              | 2-31 |

| 'CBT3345  | 8-Bit Bus Switch                                             | 2-35 |

| 'CBT3383  | 10-Bit Bus-Exchange Switch                                   | 2-39 |

| 'CBT3384A | 10-Bit Bus Switch                                            | 2-43 |

| 'CBT3386  | 10-Bit Bus-Exchange Switch With Extended Voltage Range       | 2-47 |

| 'CBT3388  | 10-Bit Bus-Exchange Switch With Bus Hold                     | 2-51 |

| 'CBT6800  | 10-Bit Bus Switch With Precharged Outputs for Live Insertion | 2-55 |

# SN74CBT3125 QUADRUPLE BUS SWITCH

D, DB, OR PW PACKAGE

(TOP VIEW)

14 Vcc

13 4 OE

12 4A

11 1 4B

10 30E 9 3A

8**]** 3B

1OE

1A 2

1B 🛛 3

2A 🛛 5

2B**1**6

GND 7

20E 4

1

SCDS021 - MAY 1995

- Standard '125-Type Pinout

- 5-Ω Switch Connection Between Two Ports

- TTL-Compatible Input and Output Levels

- Package Options Include Plastic Small-Outline (D), Shrink Small-Outline (DB), and Thin Shrink Small-Outline (PW) Packages

#### description

The SN74CBT3125 quadruple bus switch features independent line switches. Each switch is disabled when the associated output-enable  $(\overline{OE})$  input is high.

The SN74CBT3125 is available in TI's shrink small-outline package (DB), which provides the same I/O pin count and functionality of standard small-outline packages in less than half the printed-circuit-board area.

The SN74CBT3125 is characterized for operation from -40°C to 85°C.

| FUNCTION TABLE |                    |  |

|----------------|--------------------|--|

|                | INPUTS/<br>OUTPUTS |  |

| ŬE             | A, B               |  |

| L              | A = B              |  |

| н              | z                  |  |

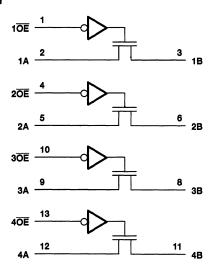

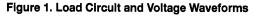

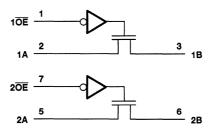

# logic diagram (positive logic)

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1995, Texas Instruments Incorporated

# SN74CBT3125 QUADRUPLE BUS SWITCH

SCDS021 - MAY 1995

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$ | / to 7 V<br>128 mA<br>-50 mA<br>1.25 W<br>0.5 W<br>0.5 W |

|-------------------------------------------------------|----------------------------------------------------------|

| Storage temperature range, T <sub>stg</sub>           | › 150°C                                                  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils. For more information, refer to the Package Thermal Considerations application note in the 1994 ABT Advanced BiCMOS Technology Data Book, literature number SCBD002B.

### recommended operating conditions

|     |                                  | MIN | MAX | UNIT |

|-----|----------------------------------|-----|-----|------|

| Vcc | Supply voltage                   | 4   | 5.5 | V    |

| VIH | High-level control input voltage | 2   | ,   | V    |

| VIL | Low-level control input voltage  |     | 0.8 | v    |

| TA  | Operating free-air temperature   | -40 | 85  | °C   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PA      | RAMETER      |                            | TEST CONDITION          | ONS                             | MIN | TYP‡ | MAX  | UNIT |

|---------|--------------|----------------------------|-------------------------|---------------------------------|-----|------|------|------|

| VIK     |              | $V_{CC} = 4 V,$            | lı = – 18 mA            |                                 |     |      | -1.2 | V    |

| 4       |              | $V_{CC} = 5.5 V,$          | VI = 5.5 V to GND       |                                 |     |      | ±1   | μA   |

| ICC     |              | V <sub>CC</sub> = 5.5 V,   | lO = 0,                 | VI = V <sub>CC</sub> or GND     |     |      | 3    | μA   |

| ∆lCC§   | Control pins | V <sub>CC</sub> = 5.5 V,   | One input at 3.4 V,     | Other inputs at $V_{CC}$ or GND |     |      | 2.5  | mA   |

| Ci      | Control pins | VI = 3 V or 0              |                         |                                 |     | 3    |      | pF   |

| Cio(OFF | F)           | V <sub>O</sub> = 3 V or 0, | OE = V <sub>CC</sub>    |                                 |     | 4    |      | pF   |

|         |              | $V_{CC} = 4 V,$            | V <sub>I</sub> = 2.4 V, | lj = 15 mA                      |     | 16   | 22   |      |

| ron¶    |              |                            | V <sub>1</sub> = 0,     | lj = 64 mA                      |     | 5    | 7    | Ω    |

| 'on "   |              | V <sub>CC</sub> = 4.5 V    | V <sub>1</sub> = 0,     | lj = 30 mA                      |     | 5    | 7    | 22   |

|         |              |                            | V <sub>1</sub> = 2.4 V, | lj = 15 mA                      |     | 10   | 15   |      |

<sup>‡</sup> All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

§ This is the increase in supply current for each input that is at the specified TTL voltage level rather than VCC or GND.

I Measured by the voltage drop between the A and the B terminals at the indicated current through the switch. On-state resistance is determined by the lower of the voltages of the two (A or B) terminals.

# SN74CBT3125 **QUADRUPLE BUS SWITCH**

SCDS021 - MAY 1995

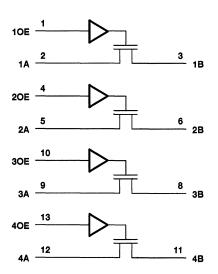

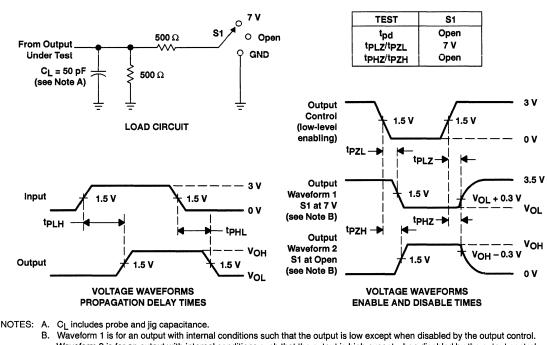

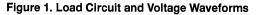

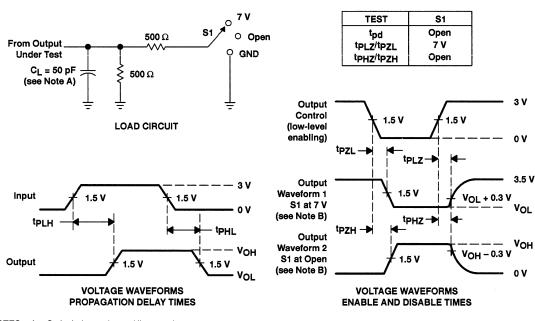

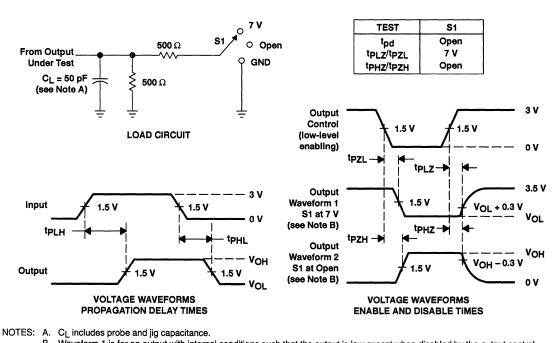

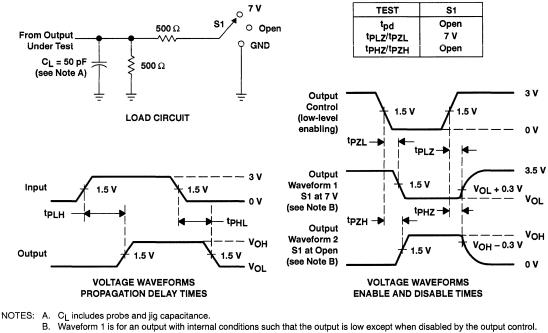

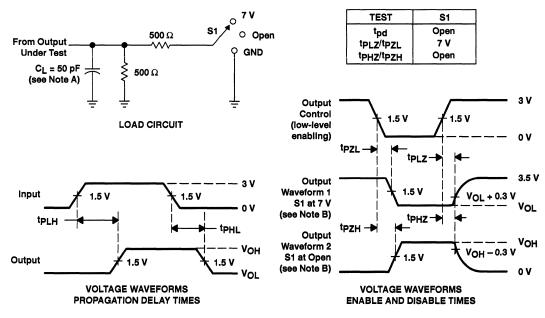

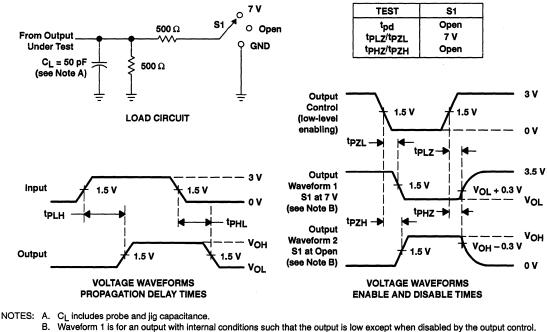

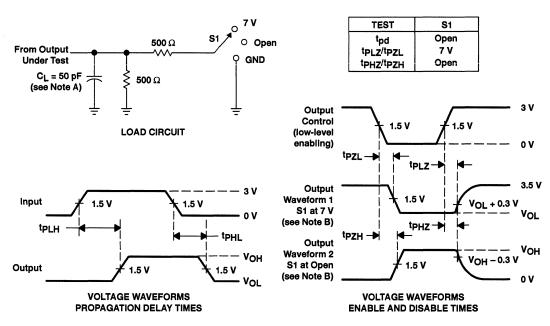

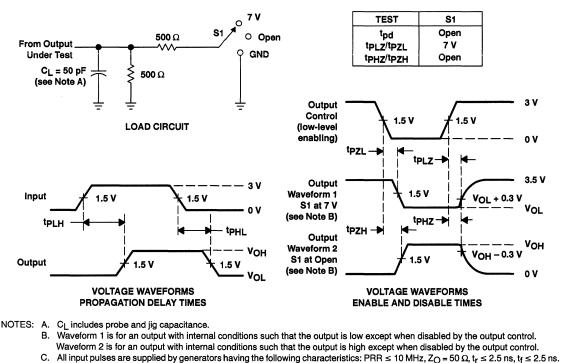

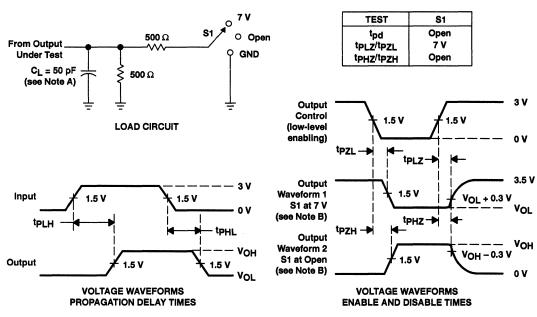

# switching characteristics over recommended operating free-air temperature range, CL = 50 pF (unless otherwise noted) (see Figure 1)

| PARAMETER         | FROM<br>(INPUT) | TO<br>(OUTPUT) | V <sub>CC</sub> :<br>± 0. | $V_{CC} = 5 V$<br>± 0.5 V | V <sub>CC</sub> = 5 V<br>± 0.5 V V <sub>CC</sub> = |      | V <sub>CC</sub> = 4 V |  |

|-------------------|-----------------|----------------|---------------------------|---------------------------|----------------------------------------------------|------|-----------------------|--|

|                   | (INPOT)         | (001901)       | MIN                       | MAX                       | MIN                                                | MAX  |                       |  |

| t <sub>pd</sub> † | A or B          | B or A         |                           | 0.25                      |                                                    | 0.25 | ns                    |  |

| ten               | ŌĒ              | A or B         | 1.6                       | 5.4                       |                                                    | 6    | ns                    |  |

| <sup>t</sup> dis  | ŌĒ              | A or B         | 1                         | 4.7                       |                                                    | 5.1  | ns                    |  |

† This parameter is characterized but not tested. This propagation delay is based on the RC time constant of the typical on-state resistance of the switch and a load capacitance of 50 pF.

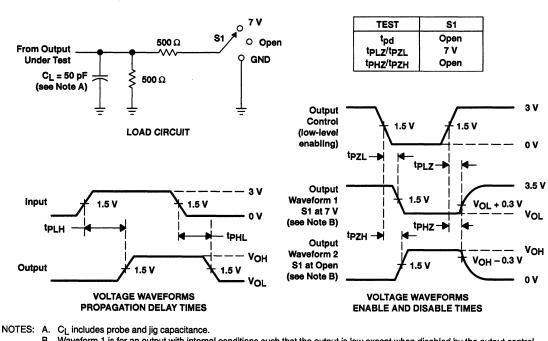

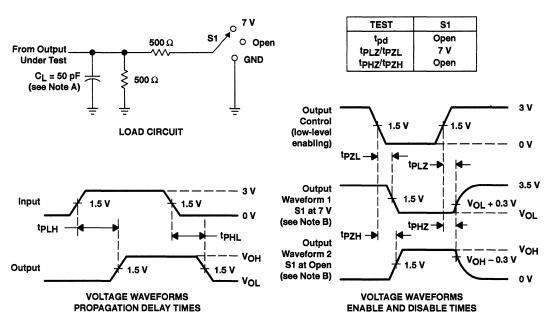

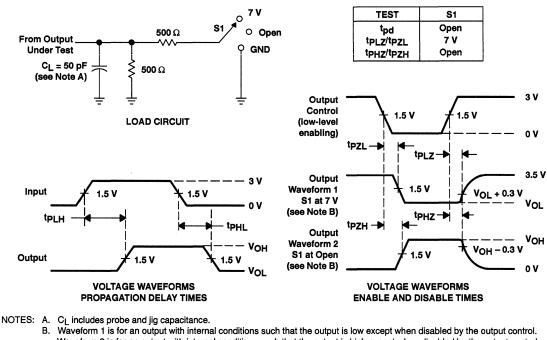

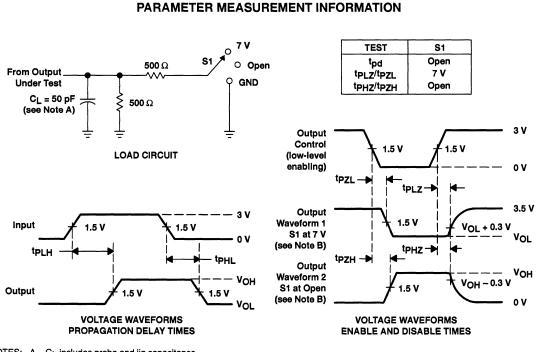

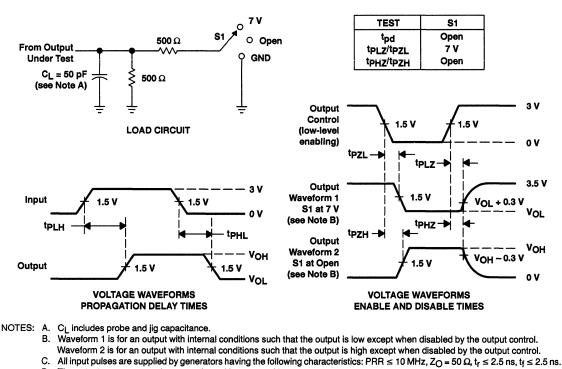

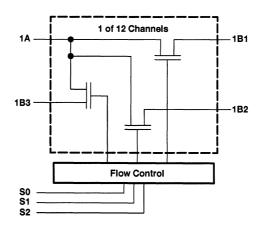

# PARAMETER MEASUREMENT INFORMATION

- - B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control. C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>r</sub>  $\leq$  2.5 ns, t<sub>f</sub>  $\leq$  2.5 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tpLZ and tpHZ are the same as tdis.

- F. tpzL and tpzH are the same as ten.

- G. tPLH and tPHL are the same as tpd.

# SN74CBT3126 QUADRUPLE BUS SWITCH

D, DB, OR PW PACKAGE (TOP VIEW)

10E

1A 🛛 2

1B**[**]3

2A 🛛 5

2B 🛛 6

GND 7

20E 🛛 4

14 🛛 V<sub>CC</sub>

13 🛛 40E

12**0**4A

11 🛛 4B

10 30E

9 🛛 3A

8**П** 3B

SCDS020 - MAY 1995

- Standard '126-Type Pinout

- 5-Ω Switch Connection Between Two Ports

- TTL-Compatible Input and Output Levels

- Package Options Include Plastic Small-Outline (D), Shrink Small-Outline (DB), and Thin Shrink Small-Outline (PW) Packages

#### description

The SN74CBT3126 quadruple bus switch features independent line switches. Each switch is disabled when the associated output-enable (OE) input is low.

The SN74CBT3126 is available in TI's shrink small-outline package (DB), which provides the same I/O pin count and functionality of standard small-outline packages in less than half the printed-circuit-board area.

The SN74CBT3126 is characterized for operation from -40°C to 85°C.

| FUNCTION TABLE |       |  |

|----------------|-------|--|

| INPUT OUTPUTS  |       |  |

| UE             | A, B  |  |

| н              | A = B |  |

| L              | z     |  |

# logic diagram (positive logic)

**PRODUCT PREVIEW**

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas instruments reserves the right to change or discontinue these products without notice.

# SN74CBT3126 QUADRUPLE BUS SWITCH

SCDS020 - MAY 1995

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub><br>Input voltage range, V <sub>I</sub> (see Note 1) |                |

|-------------------------------------------------------------------------------------------|----------------|

| Continuous channel current                                                                |                |

| Input clamp current, I <sub>K</sub> (V <sub>I/O</sub> < 0)                                |                |

| Maximum power dissipation at T <sub>A</sub> = 55°C (in still air) (see Note 2): D package |                |

| DB package                                                                                | 0.5 W          |

| PW package                                                                                | 0.5 W          |

| Storage temperature range, T <sub>stg</sub>                                               | -65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils. For more information, refer to the Package Thermal Considerations application note in the 1994 ABT Advanced BiCMOS Technology Data Book, literature number SCBD002B.

# recommended operating conditions

|     |                                  | MIN | MAX | UNIT |

|-----|----------------------------------|-----|-----|------|

| Vcc | Supply voltage                   | 4   | 5.5 | V    |

| VIH | High-level control input voltage | 2   |     | v    |

| VIL | Low-level control input voltage  |     | 0.8 | V    |

| TA  | Operating free-air temperature   | -40 | 85  | °C   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PA      | RAMETER      |                            | TEST CONDITIO           | ONS                                    | MIN | TYP‡ | MAX  | UNIT |

|---------|--------------|----------------------------|-------------------------|----------------------------------------|-----|------|------|------|

| VIK     |              | $V_{CC} = 4 V,$            | lj =18 mA               |                                        |     |      | -1.2 | V    |

| 4       |              | V <sub>CC</sub> = 5.5 V,   | VI = 5.5 V to GND       |                                        |     |      | ±5   | μA   |

| lcc     |              | V <sub>CC</sub> = 5.5 V,   | l <sub>O</sub> = 0,     | VI = V <sub>CC</sub> or GND            |     |      | 3    | μA   |

| ∆ICC§   | Control pins | V <sub>CC</sub> = 5.5 V,   | One input at 3.4 V,     | Other inputs at V <sub>CC</sub> or GND |     |      | 2.5  | mA   |

| Ci      | Control pins | VI = 3 V or 0              |                         |                                        |     | 3    |      | рF   |

| Cio(OFF | F)           | V <sub>O</sub> = 3 V or 0, | OE = V <sub>CC</sub>    |                                        |     | 6    |      | pF   |

|         |              | $V_{CC} = 4 V,$            | V <sub>1</sub> = 2.4 V, | lj = 15 mA                             |     |      |      |      |

| ron¶    |              |                            | V <sub>1</sub> = 0,     | lj = 64 mA                             |     | 5    | 7    | Ω    |

| 'on "   |              | V <sub>CC</sub> = 4.5 V    | V <sub>1</sub> = 0,     | lı = 30 mA                             |     | 5    | 7    | 22   |

|         |              |                            | V <sub>I</sub> = 2.4 V, | lj = 15 mA                             |     | 10   | 15   |      |

<sup>‡</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

I Measured by the voltage drop between the A and the B terminals at the indicated current through the switch. On-state resistance is determined by the lower of the voltages of the two (A or B) terminals.

# SN74CBT3126 QUADRUPLE BUS SWITCH

SCDS020 - MAY 1995

# switching characteristics over recommended operating free-air temperature range, $C_L = 50 \text{ pF}$ (unless otherwise noted) (see Figure 1)

| PARAMETER                    | FROM<br>(INPUT) | TO<br>(OUTPUT) | MIN MAX | UNIT |

|------------------------------|-----------------|----------------|---------|------|

| <sup>t</sup> pd <sup>†</sup> | A or B          | B or A         | 0.25    | ns   |

<sup>†</sup> This parameter is characterized but not tested. This propagation delay is based on the RC time constant of the typical on-state resistance of the switch and a load capacitance of 50 pF.

PARAMETER MEASUREMENT INFORMATION

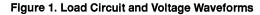

#### NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>f</sub>  $\leq$  2.5 ns, t<sub>f</sub>  $\leq$

- D. The outputs are measured one at a time with one transition per measurement.

- E. tPLZ and tPHZ are the same as tdis.

- F. tpzL and tpzH are the same as ten.

- G. tPLH andtPHL are the same as tpd.

Figure 1. Load Circuit and Voltage Waveforms

SCDS001C - NOVEMBER 1992 - REVISED MAY 1995

| <ul> <li>Functionally Equivalent to QS3244</li> <li>Standard '244-Type Pinout</li> </ul>                                                               | DB, DW, OR PW PACKAGE<br>(TOP VIEW)                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| <ul> <li>5-Ω Switch Connection Between Two Ports</li> <li>TTL-Compatible Control Input Levels</li> </ul>                                               | 10E 1 20 V <sub>CC</sub><br>1A1 2 19 20E                                         |

| <ul> <li>Package Options Include Plastic Shrink<br/>Small-Outline (DB), Small-Outline (DW), and<br/>Thin Shrink Small-Outline (PW) Packages</li> </ul> | 2B4 [] 3 18 ] 1B1<br>1A2 [] 4 17 ] 2A4<br>2B3 [] 5 16 ] 1B2<br>1A3 [] 6 15 ] 2A3 |

| description                                                                                                                                            | 2B2 7 14 1B3                                                                     |

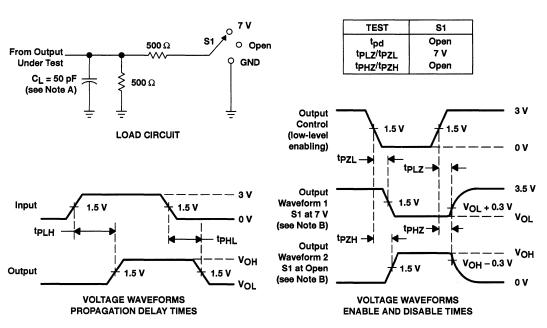

| The SN74CBT3244 provides eight bits of<br>high-speed TTL-compatible bus switching in a<br>standard '244 device pinout. The low on-state                | 1A4 [] 8 13 [] 2A2<br>2B1 [] 9 12 [] 1B4<br>GND [] 10 11 [] 2A1                  |

The device is organized as two 4-bit low-impedance switches with separate output-enable ( $\overline{OE}$ ) inputs. When  $\overline{OE}$  is low, the switch is on and data can flow from port A to port B, or vice versa. When  $\overline{OE}$  is high, the switch is open and a high-impedance state exists between the two ports.

The SN74CBT3244 is characterized for operation from 0°C to 70 °C.

resistance of the switch allows connections to be

made with minimal propagation delay.

| INF | UTS | INPUTS/       | OUTPUTS |  |  |

|-----|-----|---------------|---------|--|--|

| 10E | 20E | 1A, 1B 2A, 2B |         |  |  |

| L   | L   | 1A= 1B        | 2A = 2B |  |  |

| L   | н   | 1A= 1B        | z       |  |  |

| н   | L   | z             | 2A = 2B |  |  |

| н   | н   | z             | Z       |  |  |

FUNCTION TABLE

# SN74CBT3244 OCTAL BUS SWITCH

SCDS001C - NOVEMBER 1992 - REVISED MAY 1995

# logic diagram

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub>                                                    | to 7 V |

|------------------------------------------------------------------------------------------|--------|

| nput voltage range, V <sub>I</sub> (see Note 1)                                          |        |

| Continuous channel current                                                               |        |

| Clamp current, I <sub>K</sub> (V <sub>I/O</sub> < 0)                                     |        |

| Maximum power dissipation at $T_A = 55^{\circ}C$ (in still air) (see Note 2): DB package |        |

| DW package                                                                               | 1.6 W  |

| PW package                                                                               |        |

| Storage temperature range, T <sub>stg</sub> 65°C to                                      | 150°C  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils. For more information, refer to the Package Thermal Considerations application note in the 1994 ABT Advanced BiCMOS Technology Data Book, literature number SCBD002B.

# recommended operating conditions

|     |                                  | MIN | MAX | UNIT |

|-----|----------------------------------|-----|-----|------|

| VCC | Supply voltage                   | 4.5 | 5.5 | V    |

| VIH | High-level control input voltage | 2   |     | V    |

| VIL | Low-level control input voltage  |     | 0.8 | V    |

| TA  | Operating free-air temperature   | 0   | 70  | °C   |

# SN74CBT3244 OCTAL BUS SWITCH

SCDS001C - NOVEMBER 1992 - REVISED MAY 1995

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PA                | RAMETER      |                            | TEST CONDITI            | ONS                                    | MIN | TYP† | MAX  | UNIT |

|-------------------|--------------|----------------------------|-------------------------|----------------------------------------|-----|------|------|------|

| VIK               |              | V <sub>CC</sub> = 4.5 V,   | lj =18 mA               |                                        |     |      | -1.2 | V    |

| l <u>μ</u>        |              | V <sub>CC</sub> = 5.5 V,   | VI = 5.5 V to GND       |                                        |     |      | ±5   | μA   |

| ICC               |              | V <sub>CC</sub> = 5.5 V,   | I <sub>O</sub> = 0,     | VI = V <sub>CC</sub> or GND            |     |      | 50   | μA   |

| ∆lcc <sup>‡</sup> | Control pins | V <sub>CC</sub> = 5.5 V,   | One input at 3.4 V,     | Other inputs at V <sub>CC</sub> or GND |     |      | 3.5  | mA   |

| Ci                | Control pins | V <sub>1</sub> = 3 V or 0  |                         |                                        |     | 3    |      | рF   |

| Cio(OFF           | F)           | V <sub>O</sub> = 3 V or 0, | OE = V <sub>CC</sub>    |                                        |     | 6    |      | pF   |

|                   |              |                            | V <sub>1</sub> = 0,     | lj = 64 mA                             |     | 5    | 7    |      |

| r <sub>on</sub> § |              | V <sub>CC</sub> = 4.5 V    | V <sub>1</sub> = 0,     | lj = 30 mA                             |     | 5    | 7    | Ω    |

|                   |              |                            | V <sub>1</sub> = 2.4 V, | lj = 15 mA                             |     | 10   | 15   |      |

<sup>†</sup> All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

<sup>±</sup>This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

S Measured by the voltage drop between the A and the B terminals at the indicated current through the switch. On-state resistance is determined by the lower of the voltages of the two (A or B) terminals.

# switching characteristics over recommended operating free-air temperature range, $C_L = 50 \text{ pF}$ (unless otherwise noted) (see Figure 1)

| PARAMETER | FROM<br>(INPUT) | TO<br>(OUTPUT) | MIN | MAX  | UNIT |

|-----------|-----------------|----------------|-----|------|------|

| tpd¶      | A or B          | B or A         |     | 0.25 | ns   |

| ten       | ŌĒ              | A or B         | 1   | 8.9  | ns   |

| tdis      | ŌĒ              | A or B         | 1   | 7.4  | ns   |

This parameter is characterized but not tested. This propagation delay is based on the RC time constant of the typical on-state resistance of the switch and a load capacitance of 50 pF.

# SN74CBT3244 OCTAL BUS SWITCH

SCDS001C - NOVEMBER 1992 - REVISED MAY 1995

### PARAMETER MEASUREMENT INFORMATION

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>f</sub>  $\leq$  2.5 ns, t<sub>f</sub>  $\leq$  2.5 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tpLZ and tpHZ are the same as tdis.

- F. tpzL and tpzH are the same as ten.

- G. tpLH andtpHL are the same as tpd.

#### Figure 1. Load Circuit and Voltage Waveforms

SCDS002C - NOVEMBER 1992 - REVISED MAY 1995

| <ul> <li>Functionally Equivalent to QS3245</li> <li>Standard '245-Type Pinout</li> </ul>                                                      | DB, DW, OR PW PACKAGE<br>(TOP VIEW)                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| <ul> <li>5-Ω Switch Connection Between Two Ports</li> <li>TTL-Compatible Control Input Levels</li> </ul>                                      | NC $\begin{bmatrix} 1 & 20 \end{bmatrix}$ V <sub>CC</sub><br>A1 $\begin{bmatrix} 2 & 19 \end{bmatrix}$ OE |

| <ul> <li>Package Options Include Shrink<br/>Small-Outline (DB), Plastic Small-Outline<br/>(DW), and Thin Shrink Small-Outline (PW)</li> </ul> | A2 [] 3 18 ]] B1<br>A3 [] 4 17 ]] B2<br>A4 [] 5 16 ]] B3                                                  |

| Packages                                                                                                                                      | A5 6 15 B4<br>A6 7 14 B5                                                                                  |

| description                                                                                                                                   | A7 8 13 B6                                                                                                |

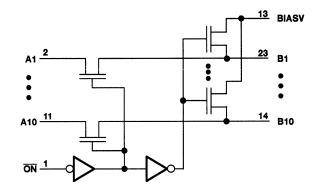

| The SN74CBT3245 provides eight bits of<br>high-speed TTL-compatible bus switching in a                                                        | A8 0 9 12 B7<br>GND 0 10 11 B8                                                                            |

The SN/4CB13245 provides eight bits of high-speed TTL-compatible bus switching in a standard '245 device pinout. The low on-state resistance of the switch allows connections to be made with minimal propagation delay.

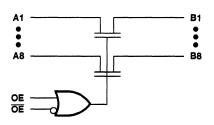

The device is organized as one 8-bit switch. When output enable ( $\overline{OE}$ ) is low, the switch is on and port A is connected to port B. When  $\overline{OE}$  is high, the switch is open and a high-impedance state exists between the two ports.

The SN74CBT3245 is characterized for operation from -40°C to 85°C.

| FUNCTION TABLE |                    |  |  |  |  |  |

|----------------|--------------------|--|--|--|--|--|

|                | INPUTS/<br>OUTPUTS |  |  |  |  |  |

| ŌĒ             | A, B               |  |  |  |  |  |

| L              | A = B              |  |  |  |  |  |

| н              | Z                  |  |  |  |  |  |

logic diagram

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

# SN74CBT3245 OCTAL BUS SWITCH

SCDS002C - NOVEMBER 1992 - REVISED MAY 1995

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$      |

|------------------------------------------------------------|

| Storage temperature range, T <sub>stg</sub> –65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils. For more information, refer to the Package Thermal Considerations application note in the 1994 ABT Advanced BiCMOS Technology Data Book, literature number SCBD002B.

# recommended operating conditions

|     |                                  | MIN | MAX | UNIT |

|-----|----------------------------------|-----|-----|------|

| VCC | Supply voltage                   | 4   | 5.5 | V    |

| VIH | High-level control input voltage | 2   |     | V    |

| VIL | Low-level control input voltage  |     | 0.8 | V    |

| TA  | Operating free-air temperature   | -40 | 85  | °C   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PA      | RAMETER      |                            | TEST CONDITIO                   | ONS                                    | MIN | TYP‡ | MAX  | UNIT |

|---------|--------------|----------------------------|---------------------------------|----------------------------------------|-----|------|------|------|

| VIK     |              | V <sub>CC</sub> = 4.5 V,   | lj = – 18 mA                    |                                        |     |      | -1.2 | V    |

| 1       |              | V <sub>CC</sub> = 5.5 V,   | VI = 5.5 V or GND               |                                        |     |      | ±5   | μA   |

| ICC     |              | V <sub>CC</sub> = 5.5 V,   | i <sub>O</sub> = 0,             | VI = V <sub>CC</sub> or GND            |     |      | 50   | μA   |

| ∆ICC§   | Control pins | V <sub>CC</sub> = 5.5 V,   | One input at 3.4 V,             | Other inputs at V <sub>CC</sub> or GND |     |      | 3.5  | mA   |

| Ci      | Control pins | VI = 3 V or 0              |                                 |                                        |     | 3    |      | pF   |

| Cio(OFF | -)           | V <sub>O</sub> = 3 V or 0, | <del>OE</del> = V <sub>CC</sub> |                                        |     | 6    | 6 p  |      |

|         |              | $V_{CC} = 4 V,$            | V <sub>I</sub> = 2.4 V,         | lj = 15 mA                             |     |      |      |      |

| ron¶    |              |                            | V <sub>I</sub> = 0,             | lj = 64 mA                             |     | 5    | 7    | Ω    |

| 'on "   |              | V <sub>CC</sub> = 4.5 V    | V <sub>I</sub> = 0,             | lj = 30 mA                             |     | 5    | 7    | 52   |

|         |              |                            | V <sub>I</sub> = 2.4 V,         | lj = 15 mA                             |     | 10   | 15   |      |

<sup>‡</sup> All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

§ This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

Image: Measured by the voltage drop between the A and B terminals at the indicated current through the switch. On-state resistance is determined by the lower of the voltages of the two (A or B) terminals.

# SN74CBT3245 **OCTAL BUS SWITCH**

SCDS002C - NOVEMBER 1992 - REVISED MAY 1995

### switching characteristics over recommended operating free-air temperature range, CL = 50 pF (unless otherwise noted) (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | MIN MAX | UNIT |

|------------------|-----------------|----------------|---------|------|

| tpd <sup>†</sup> | A or B          | B or A         | 0.25    | ns   |

| <sup>t</sup> en  | ŌĒ              | A or B         |         | ns   |

| <sup>t</sup> dis | ŌĒ              | A or B         |         | ns   |

<sup>†</sup> This parameter is characterized but not tested. This propagation delay is based on the RC time constant of the typical on-state resistance of the switch and a load capacitance of 50 pF.

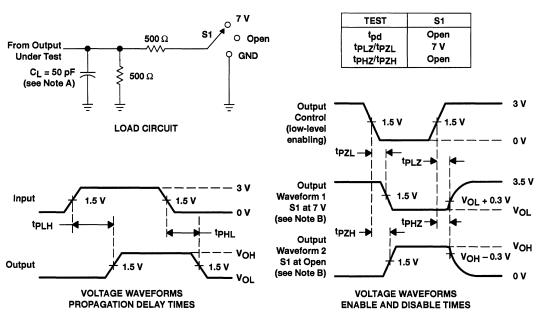

# PARAMETER MEASUREMENT INFORMATION

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z<sub>O</sub> = 50 Ω, t<sub>f</sub> ≤ 2.5 ns, t<sub>f</sub> ≤ 2.5 ns, C.

- The outputs are measured one at a time with one transition per measurement. D.

- E. tpLz and tpHz are the same as tdis.

- F. tpzL and tpzH are the same as ten.

- G. tpLH and tpHL are the same as tpd.

#### Figure 1. Load Circuit and Voltage Waveforms

B4 🛛

B3 🛛 2

B2 **[**]3

B1 []4

OE 17

GND 8

D, DB, OR PW PACKAGE (TOP VIEW)

16 VCC

15 B5

14 🛛 B6

13 B7

12 B8

11 SO

10 I S1

9] S2

SCDS019 - MAY 1995

- Functionally Equivalent to QS3251

- 5-Ω Switch Connection Between Two Ports

- TTL-Compatible Control Input Levels

- Package Options Include Plastic Small-Outline (D), Shrink Small-Outline (DB), and Thin Shrink Small-Outline (PW) Packages

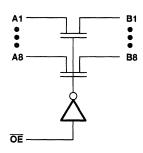

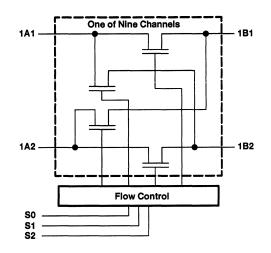

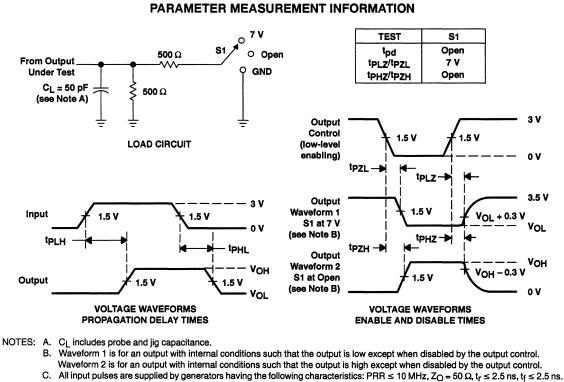

### description

The SN74CBT3251 is an 8-bit to 1-bit high-speed TTL-compatible FET multiplexer/ demultiplexer. The low on-state resistance of the switch allows connections to be made with minimal propagation delay.

When output enable ( $\overline{OE}$ ) is low, the SN74CBT3251 is enabled. S0, S1, and S2 select one of the B outputs for the A-input data.

The SN74CBT3251 is characterized for operation from -40°C to 85°C.

|    |    | FUN | CTION T | ABLE       |

|----|----|-----|---------|------------|

| S2 | S1 | S0  | ŌĒ      | FUNCTION   |

| Х  | Х  | Х   | н       | Disconnect |

| L  | L  | L   | L       | A to B1    |

| L  | L  | н   | L       | A to B2    |

| L  | н  | L   | L       | A to B3    |

| L  | н  | н   | L       | A to B4    |

| н  | L  | L   | L       | A to B5    |

| н  | L  | н   | L       | A to B6    |

| н  | н  | L   | L       | A to B7    |

| н  | н  | н   | L       | A to B8    |

**PRODUCT PREVIEW**

SCDS019 - MAY 1995

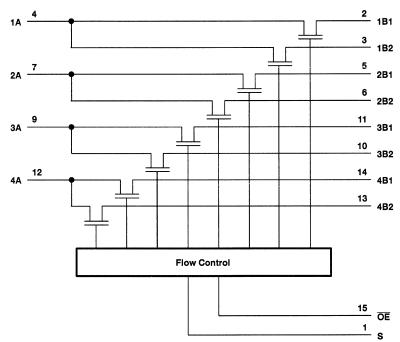

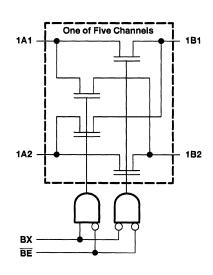

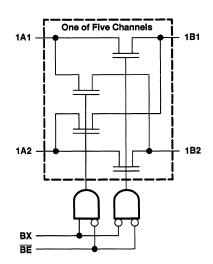

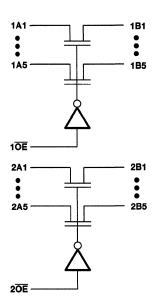

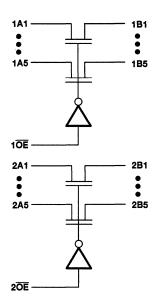

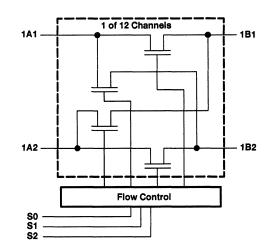

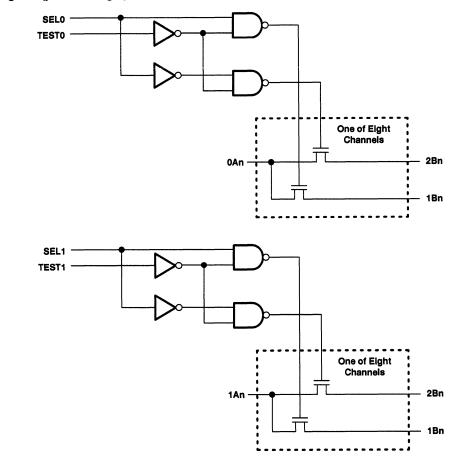

## logic diagram

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub><br>Input voltage range, V <sub>I</sub> (see Note 1) |                |

|-------------------------------------------------------------------------------------------|----------------|

| Continuous channel current                                                                |                |

| Input clamp current, I <sub>K</sub> (V <sub>I/O</sub> < 0)                                | –50 mA         |

| Maximum power dissipation at T <sub>A</sub> = 55°C (in still air) (see Note 2): D package | 1.3 W          |

|                                                                                           | 0.55 W         |

|                                                                                           | 0.5 W          |

| Storage temperature range, T <sub>stg</sub>                                               | –65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2. The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils. For more information, refer to the *Package Thermal Considerations* application note in the 1994 ABT Advanced BiCMOS Technology Data Book, literature number SCBD002B.

SCDS019 - MAY 1995

#### recommended operating conditions

|     |                                  | MIN | MAX | UNIT |

|-----|----------------------------------|-----|-----|------|

| Vcc | Supply voltage                   | 4   | 5.5 | V    |

| VIH | High-level control input voltage | 2   |     | V    |

| VIL | Low-level control input voltage  |     | 0.8 | V    |

| TA  | Operating free-air temperature   | -40 | 85  | °C   |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER         |              | TEST CONDITIONS            |                          | MIN                                    | TYPT | MAX | UNIT |    |

|-------------------|--------------|----------------------------|--------------------------|----------------------------------------|------|-----|------|----|

| VIK               |              | V <sub>CC</sub> = 4.5 V,   | lj = - 18 mA             |                                        |      |     | -1.2 | v  |

| 4                 |              | V <sub>CC</sub> = 5.5 V,   | Vi = 5.5 V to GND        |                                        |      |     | ±5   | μA |

| ICC               |              | V <sub>CC</sub> = 5.5 V,   | lO = 0,                  | VI = V <sub>CC</sub> or GND            |      |     | 3    | μA |

| ∆lCC <sup>‡</sup> | Control pins | V <sub>CC</sub> = 5.5 V,   | One input at 3.4 V,      | Other inputs at V <sub>CC</sub> or GND |      |     | 2.5  | mA |

| Ci                | Control pins | V <sub>1</sub> = 3 V or 0  |                          |                                        |      | 3   |      | pF |

| 0                 | A port       | N 01/10                    |                          |                                        |      |     |      | рF |

| Cio(OFF)          | B port       | V <sub>O</sub> = 3 V or 0, | $\overline{OE} = V_{CC}$ |                                        |      | 6   |      | рг |

|                   |              | $V_{CC} = 4 V,$            | V <sub>I</sub> = 2.4 V,  | lj = 15 mA                             |      |     |      |    |

| r <sub>on</sub> § |              |                            | V <sub>1</sub> = 0,      | lj = 64 mA (optional)                  |      | 5   | 7    | Ω  |

|                   |              | V <sub>CC</sub> = 4.5 V    | V <sub>1</sub> = 0,      | lj = 30 mA                             |      | 5   | 7    | 52 |

|                   |              |                            | V <sub>1</sub> = 2.4 V,  | lj = 15 mA                             |      | 10  | 15   |    |

<sup>†</sup> All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

<sup>‡</sup> This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

S Measured by the voltage drop between the A and the B terminals at the indicated current through the switch. On-state resistance is determined by the lower of the voltages of the two (A or B) terminals.

## switching characteristics over recommended operating free-air temperature range, $C_L = 50 \text{ pF}$ (unless otherwise noted) (see Figure 1)

| PARAMETER                    | FROM<br>(INPUT) | TO<br>(OUTPUT) | MIN | МАХ  | UNIT |

|------------------------------|-----------------|----------------|-----|------|------|

| <sup>t</sup> pd <sup>¶</sup> | A or B          | B or A         |     | 0.25 | ns   |

<sup>¶</sup> This parameter is characterized but not tested. This propagation delay is based on the RC time constant of the typical on-state resistance of the switch and a load capacitance of 50 pF.

SCDS019 - MAY 1995

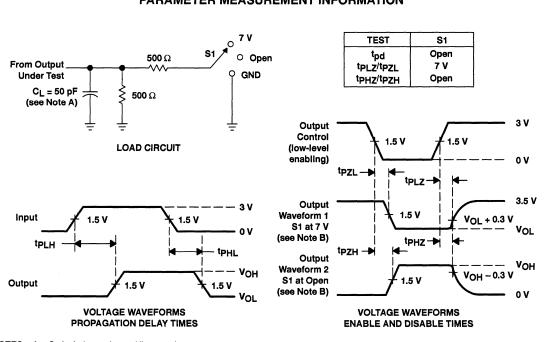

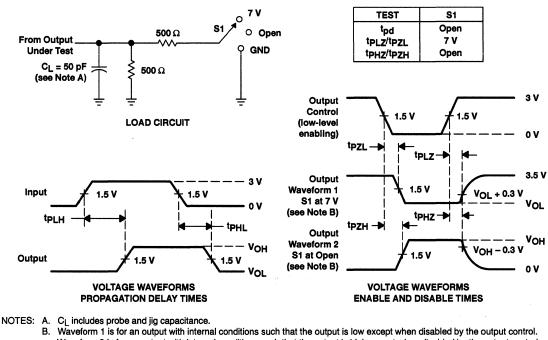

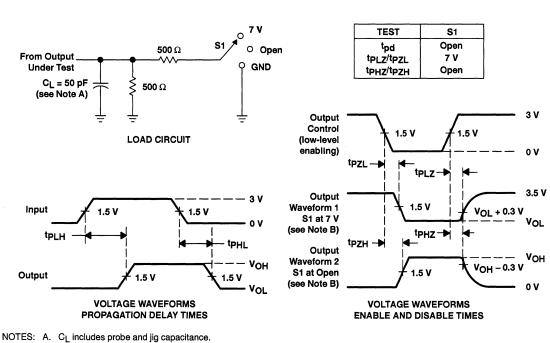

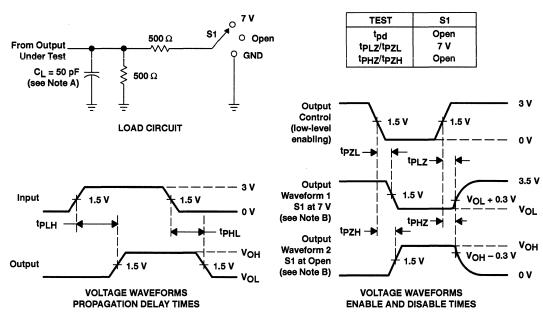

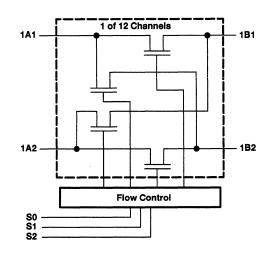

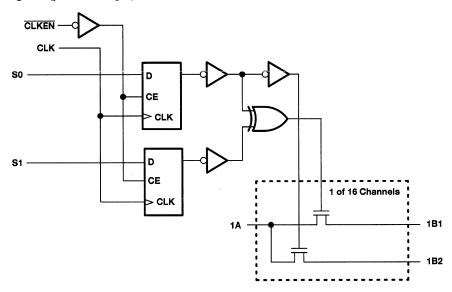

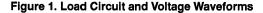

### PARAMETER MEASUREMENT INFORMATION

PRODUCT PREVIEW

- Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>r</sub>  $\leq$  2.5 ns, t<sub>f</sub>  $\leq$  2.5 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tPLZ and tPHZ are the same as tdis.

- F. tpzL and tpzH are the same as ten.

- G. tPLH and tPHL are the same as tpd.

#### Figure 1. Load Circuit and Voltage Waveforms

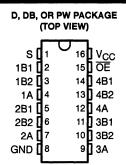

SCDS018 - MAY 1995

- Functionally Equivalent to QS3253

- 5-Ω Switch Connection Between Two Ports

- TTL-Compatible Control Input Levels

- Package Options Include Plastic Small-Outline (D), Shrink Small-Outline (DB), and Thin Shrink Small-Outline (PW) Packages

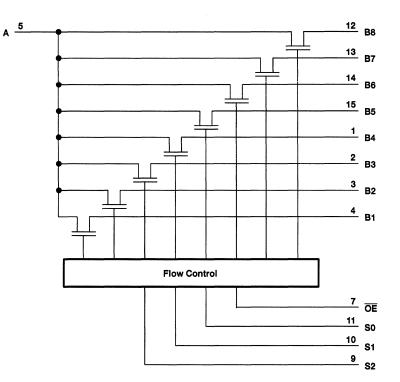

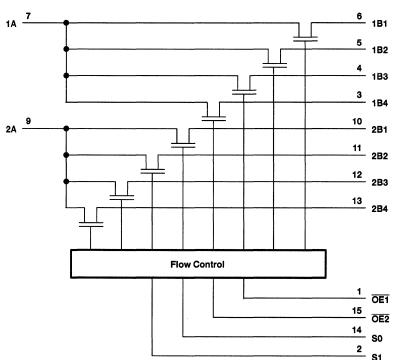

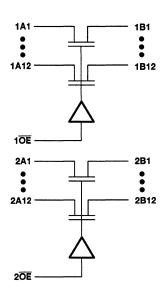

#### description

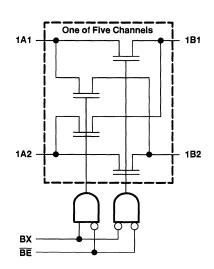

The SN74CBT3253 is a dual 4-bit to 1-bit high-speed TTL-compatible FET multiplexer/ demultiplexer. The low on-state resistance of the switch allows connections to be made with minimal propagation delay.

| D, DB, OR PW PACKAGE<br>(TOP VIEW) |   |                    |  |  |

|------------------------------------|---|--------------------|--|--|

|                                    |   |                    |  |  |

| OE1 [                              | 1 | 16 V <sub>CC</sub> |  |  |

| S1 [                               | 2 | 15 0E2             |  |  |

| 1B4 [                              |   | 14 🛛 S0            |  |  |

| 1B3 [                              | 4 | 13 <b>]</b> 2B4    |  |  |

| 1B2 [                              | 5 | 12 🛛 2B3           |  |  |

| 1B1 [                              | 6 | 11 🛛 2B2           |  |  |

| 1A [                               |   | 10 <b>]</b> 2B1    |  |  |

| GND [                              | 8 | 9 <b>]</b> 2A      |  |  |

|                                    | L |                    |  |  |

OE1, OE2, S0, and S1 select the appropriate B output for the A-input data.

The SN74CBT3253 is characterized for operation from -40°C to 85°C.

| FUNCTION TABLE |    |                    |   |                         |  |  |

|----------------|----|--------------------|---|-------------------------|--|--|

| S1             | S0 | 0 OE1 OE2 FUNCTION |   | FUNCTION                |  |  |

| X              | х  | х                  | н | Disconnect 1A           |  |  |

| x              | х  | н                  | х | Disconnect 2A           |  |  |

| L              | L  | L                  | L | 1A to 1B1 and 2A to 2B1 |  |  |

| L              | н  | L                  | L | 1A to 1B2 and 2A to 2B2 |  |  |

| н              | L  | L                  | L | 1A to 1B3 and 2A to 2B3 |  |  |

| н              | н  | L                  | L | 1A to 1B4 and 2A to 2B4 |  |  |

**PRODUCT PREVIEW**

Copyright © 1995, Texas Instruments Incorporated

SCDS018 - MAY 1995

### logic diagram

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub><br>Input voltage range, V <sub>I</sub> (see Note 1) |                    |

|-------------------------------------------------------------------------------------------|--------------------|

| Continuous channel current                                                                |                    |

| Input clamp current, I <sub>K</sub> (V <sub>I/O</sub> < 0)                                |                    |

| Maximum power dissipation at $T_A = 55^{\circ}C$ (in still air) (see Note 2)              | ): D package 1.3 W |

|                                                                                           | DB package 0.55 W  |

|                                                                                           | PW package 0.5 W   |

| Storage temperature range, T <sub>stg</sub>                                               | −65°C to 150°C     |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils. For more information, refer to the Package Thermal Considerations application note in the 1994 ABT Advanced BiCMOS Technology Data Book, literature number SCBD002B.

SCDS018 - MAY 1995

#### recommended operating conditions

|     |                                  | MIN | MAX | UNIT |

|-----|----------------------------------|-----|-----|------|

| Vcc | Supply voltage                   | 4   | 5.5 | V    |

| VIH | High-level control input voltage | 2   |     | V    |

| VIL | Low-level control input voltage  |     | 0.8 | V    |

| TA  | Operating free-air temperature   | -40 | 85  | °C   |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER         |              |                            | TEST CONDITIONS          |                                 |  | TYPT | MAX  | UNIT |

|-------------------|--------------|----------------------------|--------------------------|---------------------------------|--|------|------|------|

| VIK               |              | V <sub>CC</sub> = 4.5 V,   | lı = – 18 mA             |                                 |  |      | -1.2 | v    |

| ų                 |              | V <sub>CC</sub> = 5 V,     | VI = 5.5 V to GND        |                                 |  |      | ±5   | μA   |

| ICC               |              | V <sub>CC</sub> = 5.5 V,   | lO = 0,                  | VI = V <sub>CC</sub> or GND     |  |      | 3    | μA   |

| ∆lCC‡             | Control pins | V <sub>CC</sub> = 5.5 V,   | One input at 3.4 V,      | Other inputs at $V_{CC}$ or GND |  |      | 2.5  | mA   |

| Ci                | Control pins | V <sub>I</sub> = 3 V or 0  |                          |                                 |  | 3    |      | pF   |

| 0                 | A port       |                            |                          |                                 |  |      |      | pF   |

| Cio(OFF)          | B port       | V <sub>O</sub> = 3 V or 0, | $\overline{OE} = V_{CC}$ |                                 |  |      |      | p۴   |

|                   |              | $V_{CC} = 4 V,$            | V <sub>1</sub> = 2.4 V,  | lj = 15 mA                      |  | _    |      |      |

| r <sub>on</sub> § |              |                            | V <sub>1</sub> = 0,      | lı = 64 mA (optional)           |  | 5    | 7    | Ω    |

| 'on <sup>3</sup>  |              | V <sub>CC</sub> = 4.5 V    | V <sub>1</sub> = 0,      | lj = 30 mA                      |  | 5    | 7    | 52   |

|                   |              |                            | V <sub>1</sub> = 2.4 V,  | lj = 15 mA                      |  | 10   | 15   |      |

<sup>†</sup> All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

<sup>+</sup> This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

§ Measured by the voltage drop between the A and the B terminals at the indicated current through the switch. On-state resistance is determined by the lower of the voltages of the two (A or B) terminals.

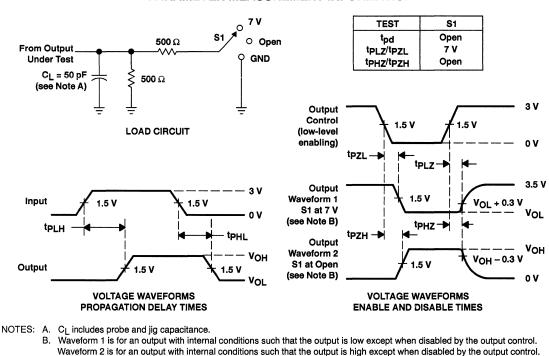

### switching characteristics over recommended operating free-air temperature range, CL = 50 pF (unless otherwise noted) (see Figure 1)

| PARAMETER         | FROM<br>(INPUT) | TO<br>(OUTPUT) | MIN MAX | UNIT |

|-------------------|-----------------|----------------|---------|------|

| t <sub>pd</sub> ¶ | A or B          | B or A         | 0.25    | ns   |

This parameter is characterized but not tested. This propagation delay is based on the RC time constant of the typical on-state resistance of the switch and a load capacitance of 50 pF.

SCDS018 - MAY 1995

#### PARAMETER MEASUREMENT INFORMATION

- Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.