# **Data Communications**

BI 04+

LOGIC

DATA BOOK

# Data Communications Data Book

Cypress Semiconductor is a trademark of Cypress Semiconductor Corporation. Cypress Semiconductor, 3901 North First St., San Jose, CA 95134 (408) 943–2600 Telex: 821032 CYPRESS SNJ UD, TWX: 910 997 0753, FAX: (408) 943–2741 Web Address: http://www.cypress.com

# How To Use This Book

# **Overall Organization**

This book has been organized by product type, beginning with Product Information. The products are next, starting with SRAMs, then Modules, Non-Volatile Memories, FIFOs, Dual-Ports, Data Communications, Bus Interface Products, FCT Logic, Timing Technology Products, and PC Chip Sets. A section containing military information is next, followed by Quality and Reliability aspects, then Thermal Data and Packages. Within each section, data sheets are arranged in order of part number.

# **Recommended Search Paths**

| To search by:                    | Use:                                                                                                                       |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Product line                     | Table of Contents or flip<br>through the book using the<br>tabs on the right-hand pages.                                   |

| Size                             | The Product Selector Guide in section 1.                                                                                   |

| Numeric part number              | Numeric Device Index fol-<br>lowing the Table of Con-<br>tents. The book is also ar-<br>ranged in order of part<br>number. |

| Other manufacturer's part number | The Cross Reference Guide in section 1.                                                                                    |

| Military part number             | The Military Selector Guide in section 12.                                                                                 |

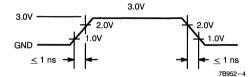

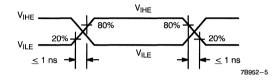

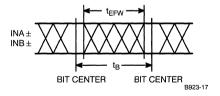

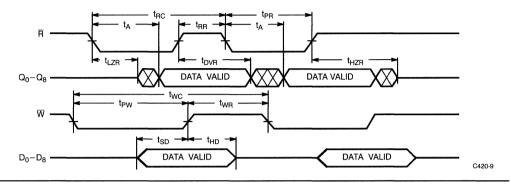

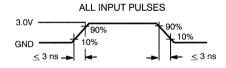

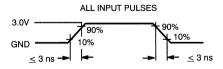

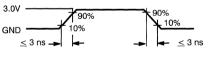

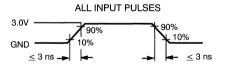

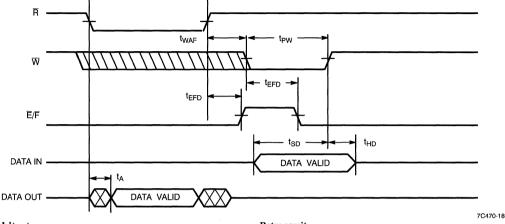

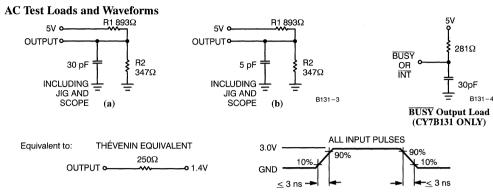

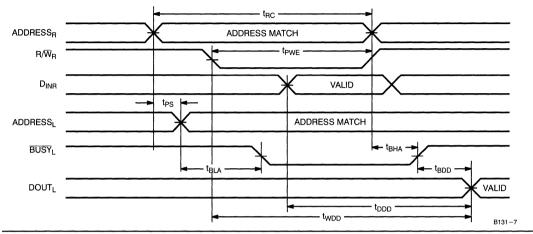

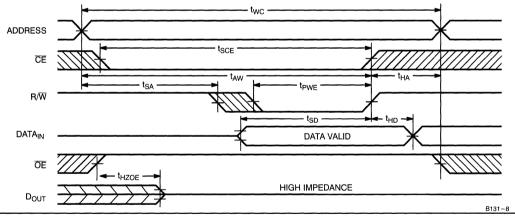

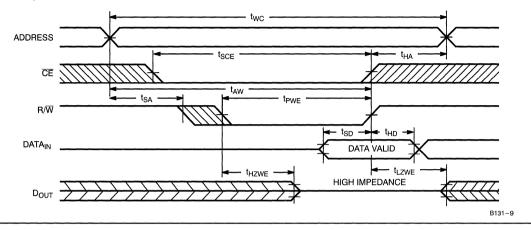

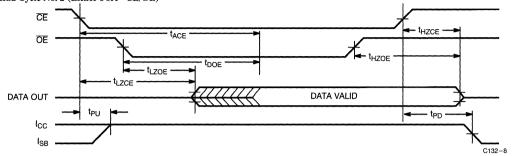

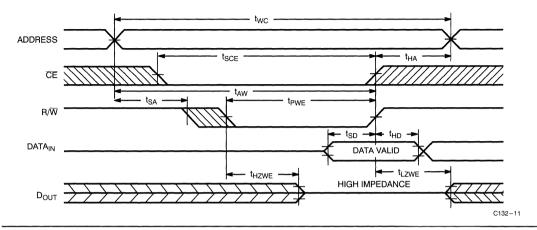

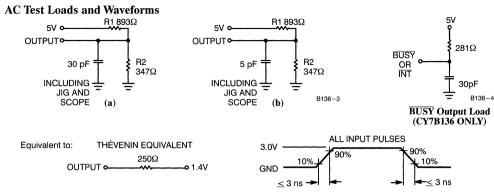

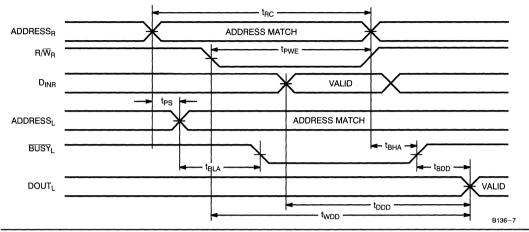

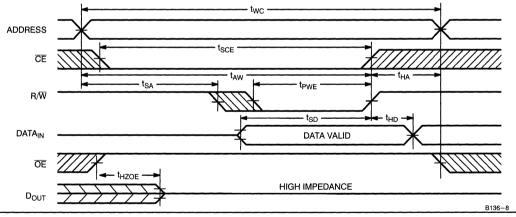

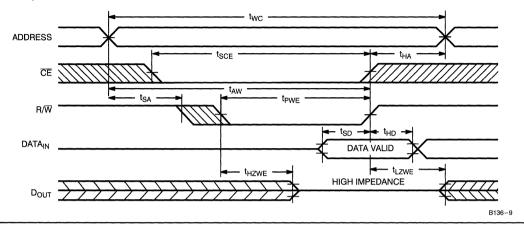

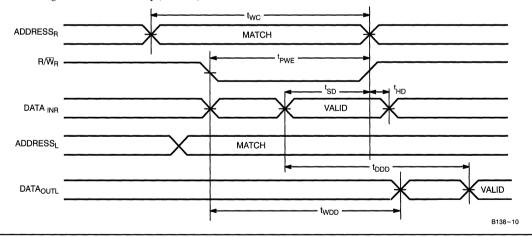

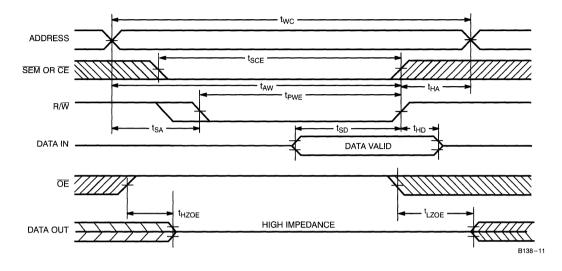

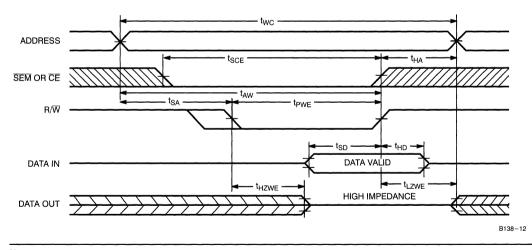

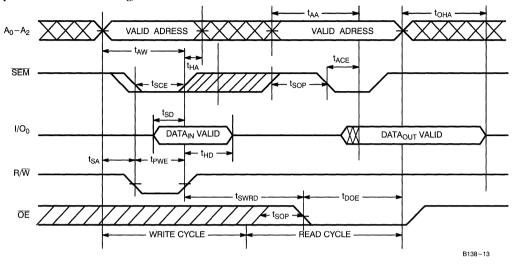

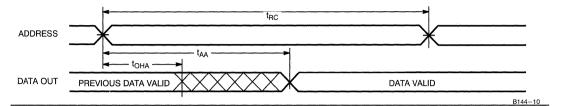

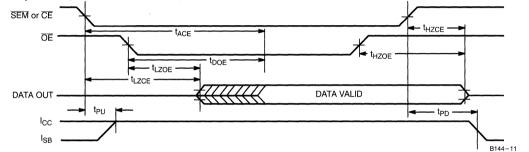

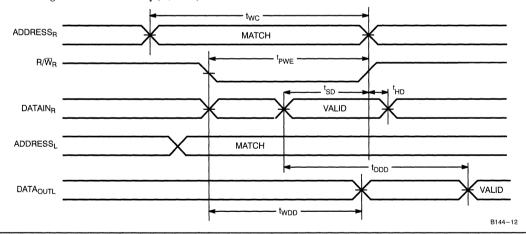

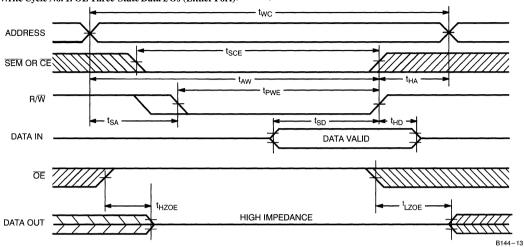

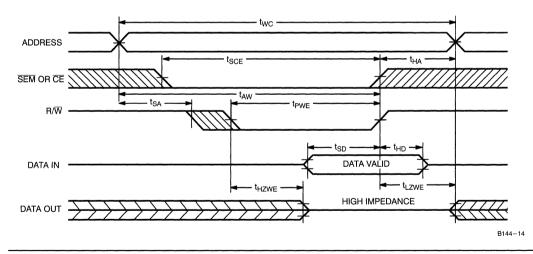

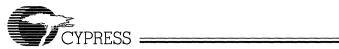

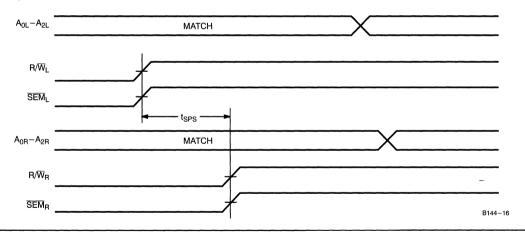

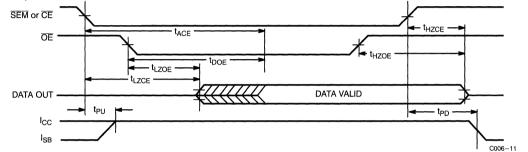

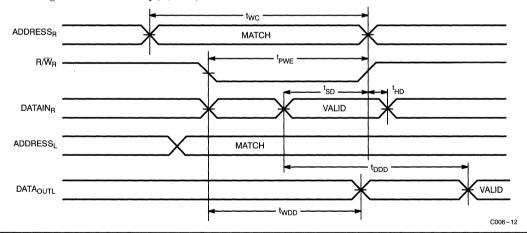

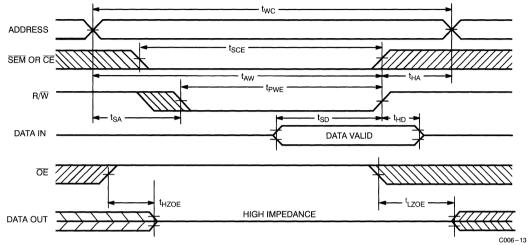

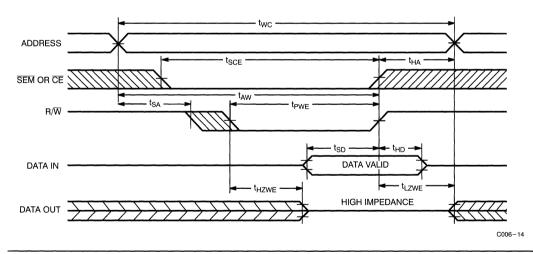

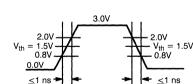

# **Key to Waveform Diagrams**

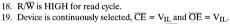

----

=

occur during this time. Falling edge of signal will

Rising edge of signal will

= Failing edge of signal w occur during this time.

Signal may transition during this time (don't care condition).

Signal changes from highimpedance state to valid logic level during this time.

Signal changes from valid logic level to high-impedance state during this time.

<sup>©</sup> Cypress Semiconductor Corporation, 1996. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor Corporation product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor advortable is products for use as critical components in life-support systems where a malifunction or failure of the product may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies Cypress Semiconductor agins at all damages.

# **Table of Contents**

# **Page Number**

| General Product Information                                    | Page Number |

|----------------------------------------------------------------|-------------|

| Cypress Semiconductor Background                               | 1–1         |

| DataCom Background                                             | 1-4         |

| Ordering Information                                           | 1–5         |

| Product Selector Guide                                         | 1-6         |

| Cypress Semiconductor Bulletin Board System (BBS) Announcement | 1–13        |

# Ethernet

# **Page Number**

**Page Number**

**Page Number**

| Device Number     | Description                                               |

|-------------------|-----------------------------------------------------------|

| CY7C971           | 100BASE-T4/10BASE-T Fast Ethernet Transceiver (CAT 3) 2–1 |

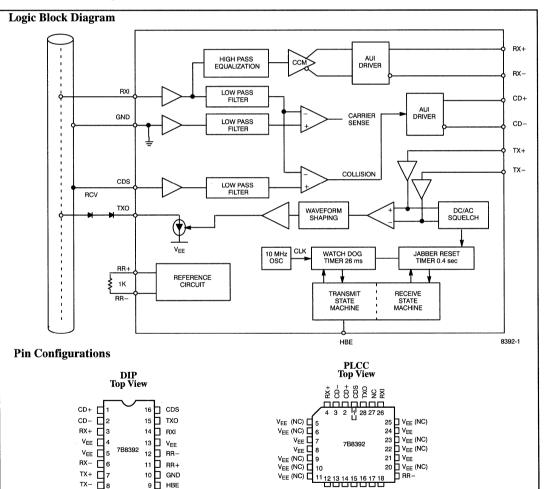

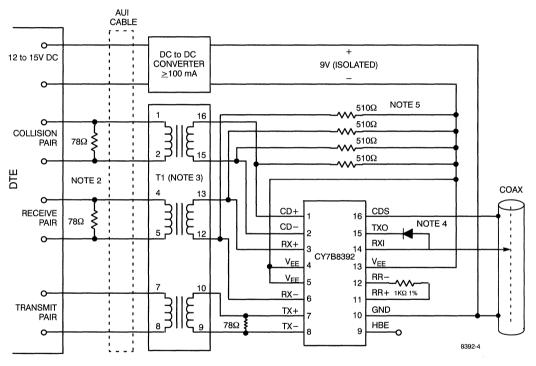

| CY7B8392          | Ethernet Coax Transceiver Interface                       |

| CY7B4663          | Integrated 10BASE-FL Ethernet Transceiver                 |

| Application Notes |                                                           |

| CY7B8392          | Low Power Ethernet Coaxial Transceiver Application        |

| CY7C971           | 100BASE-T4/10BASE-T Ethernet Transceiver Application      |

| CY7C971           | 100BASE-T4 /10BASE-T Ethernet PCI Network Adapter         |

| CY7C971/CY7C388P  | 100BASE-T4 Ethernet Repeater                              |

# ATMs

| Device Number     | Description                                        |

|-------------------|----------------------------------------------------|

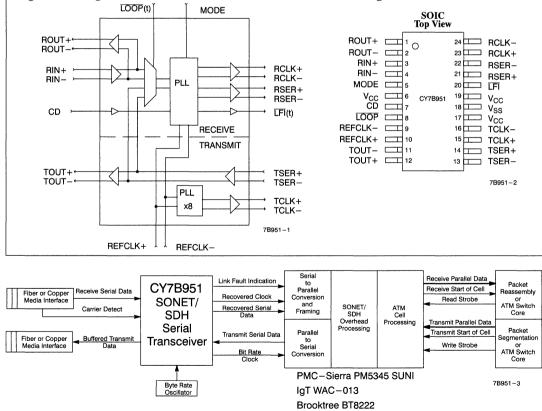

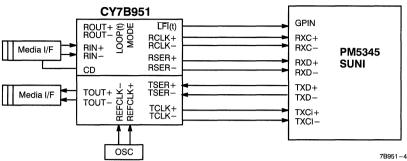

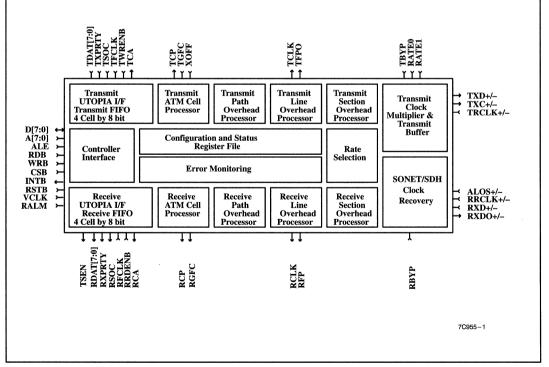

| CY7B951           | Local Area Network ATM Transceiver 3-1             |

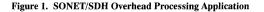

| CY7B952           | SST <sup>™</sup> SONET/SDH Serial Transceiver      |

| CY7B955           | ATM SONET/SDH Transceiver 3-16                     |

| Application Notes |                                                    |

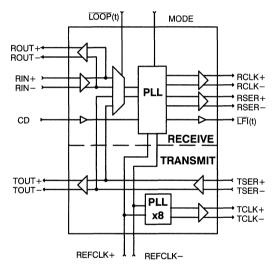

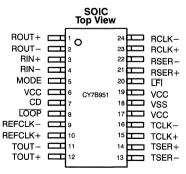

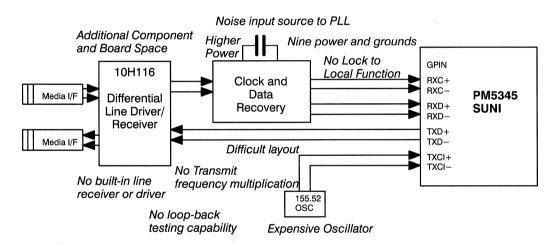

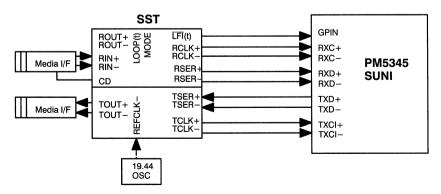

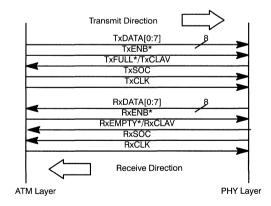

| CY7B951           | Interfacing with the SST <sup><math>M</math></sup> |

# Fibre Channel/ESCON™

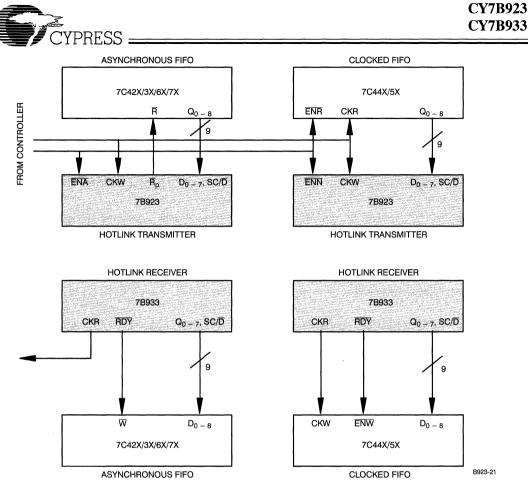

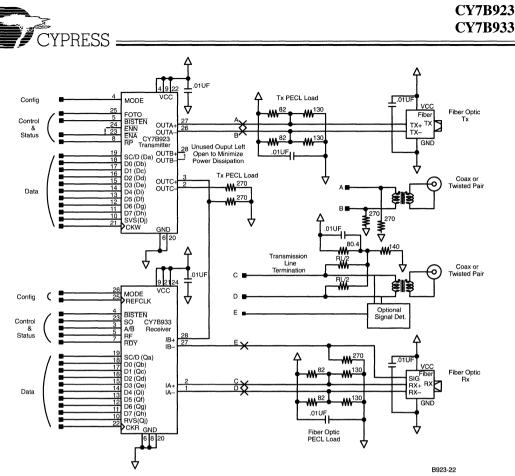

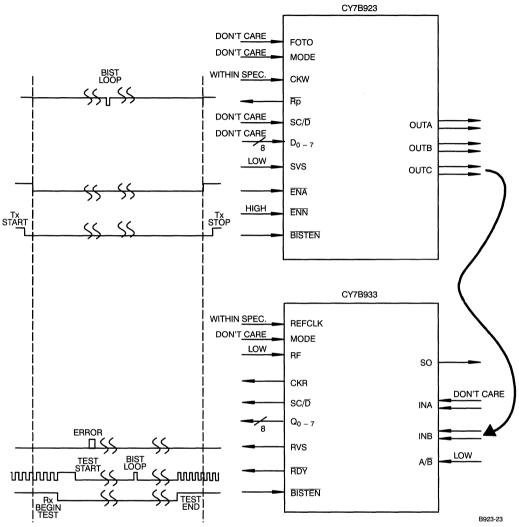

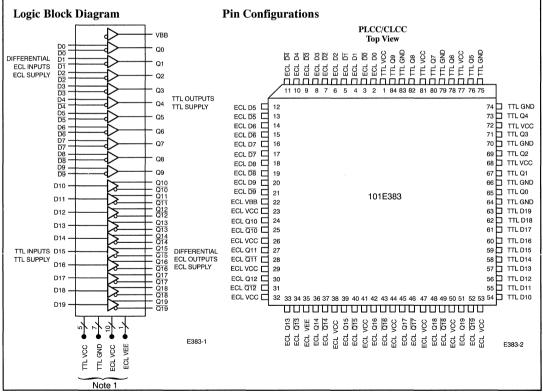

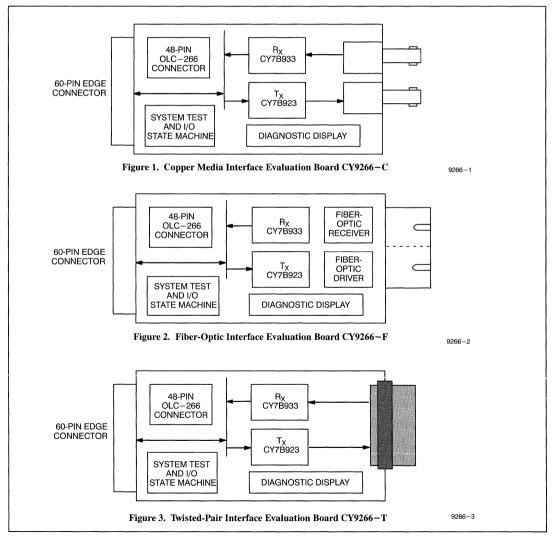

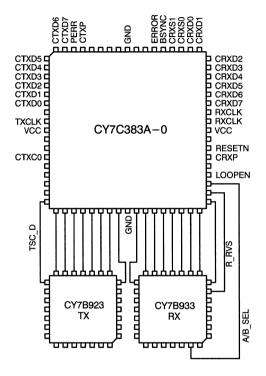

### Device Number Description CY7B923/CY7B933 CY101E383 CY9266-T/C/F **Application Notes** CY7B923/CY7B933 CY7B923/CY7B933 Frequently Asked Questions about HOTLink<sup>™</sup> Evaluation Serializing High Speed Parallel Buses to Extend Their Operational CY7B923/CY7B933

# CY7B923/CY7B933 CY7B923/CY7B933

# FIFOs

# Page Number

| Device Number       | Description                                              |

|---------------------|----------------------------------------------------------|

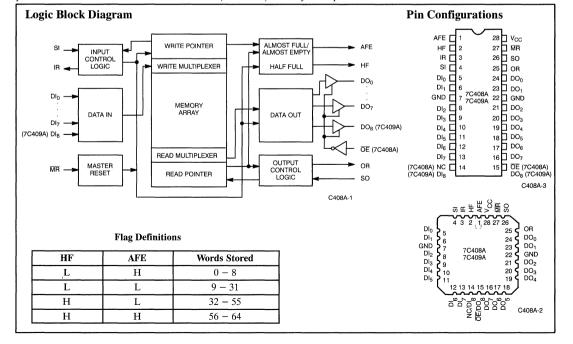

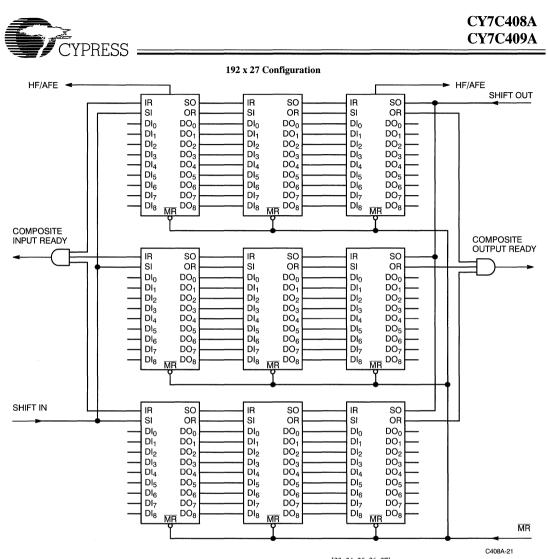

| CY7C408A/CY7C409A   | 64 x 8 Cascadable FIFO 64 x 9 Cascadable FIFO 5-1        |

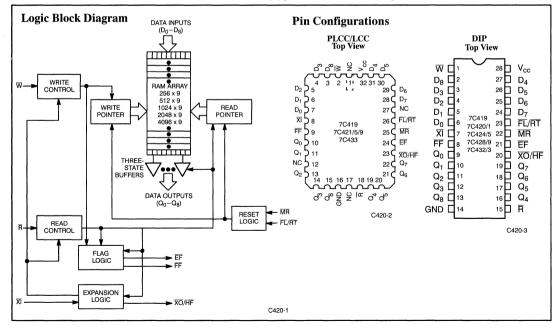

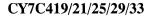

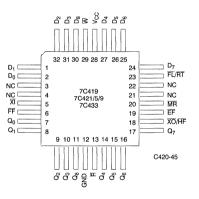

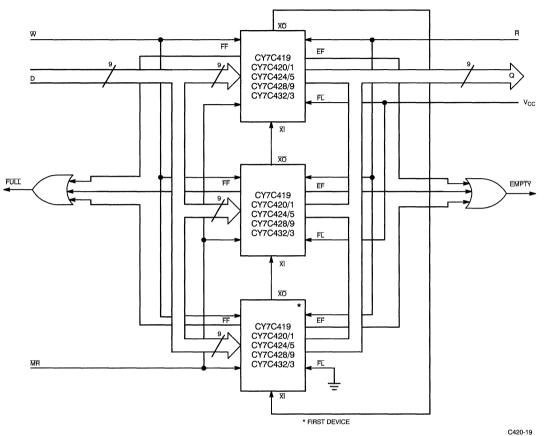

| CY7C419/21/25/29/33 | 256 x 9, 512 x 9, 1K x 9, 2K x 9, 4K x 9 Cascadable FIFO |

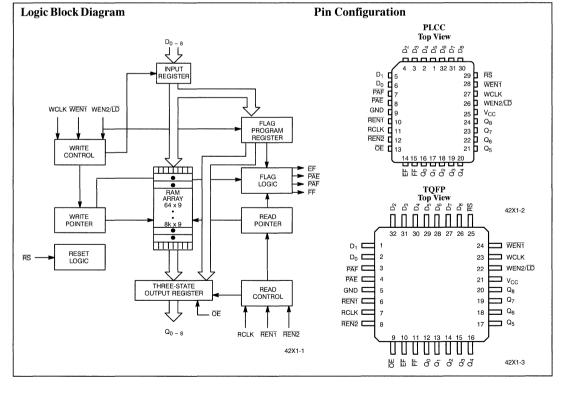

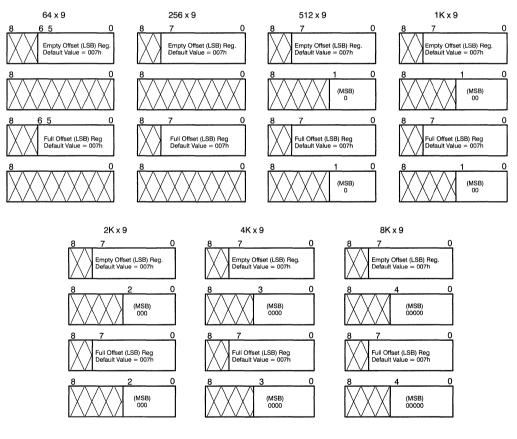

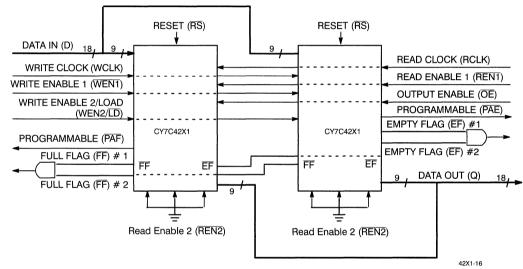

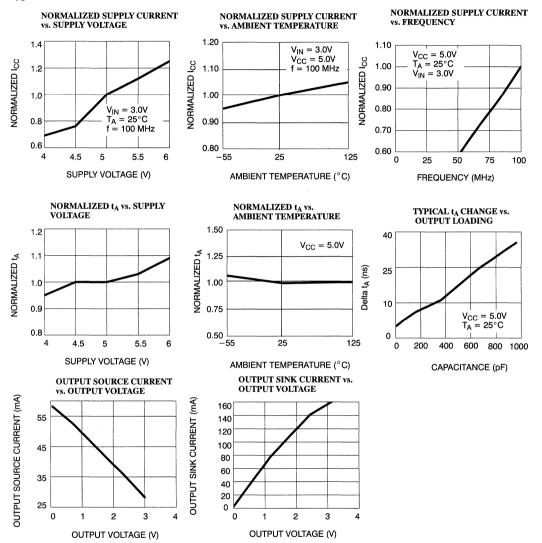

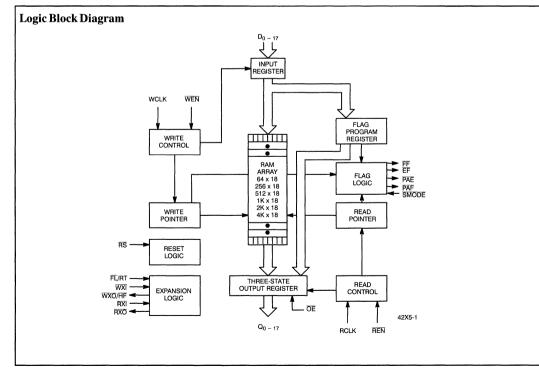

| CY7C42X1            | 64/256/512/1K/2K/4K/8K x 9 Synchronous FIFO              |

| CY7C42X5            | 64/256/512/1K/2K/4K/ x 18 Synchronous FIFO 5-57          |

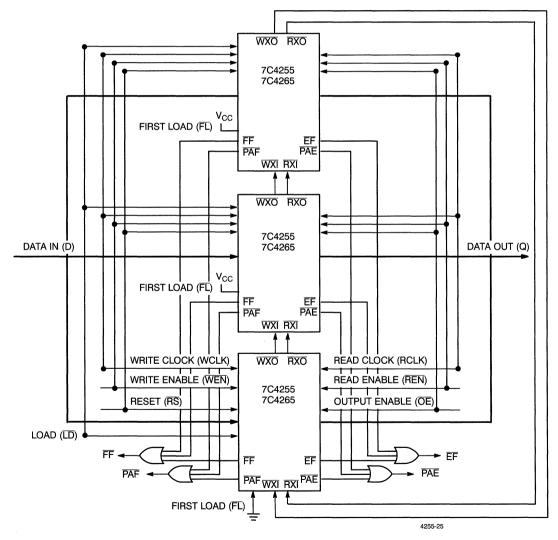

| CY7C4255/65         | 8K/16K x 18 Synchronous FIFO 5-77                        |

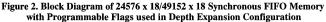

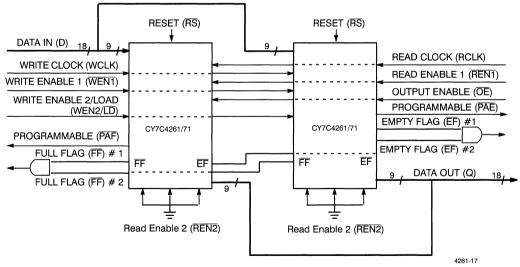

| CY7C4261/71         | 16K/32K Synchronous FIFO                                 |

**Table of Contents**

| FIFOs (continued) | Page N                                                                                   | lumber |

|-------------------|------------------------------------------------------------------------------------------|--------|

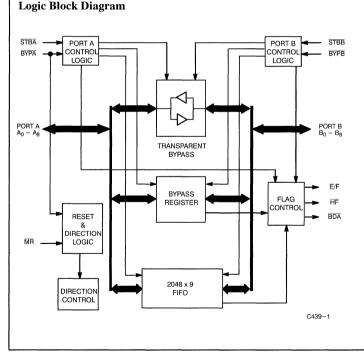

| CY7C439           | Bidirectional 2K x 9 FIFO                                                                | 5-109  |

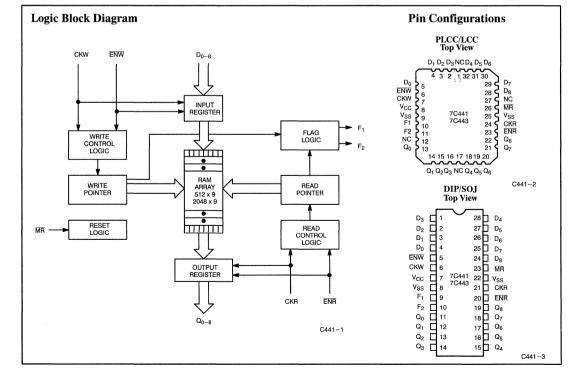

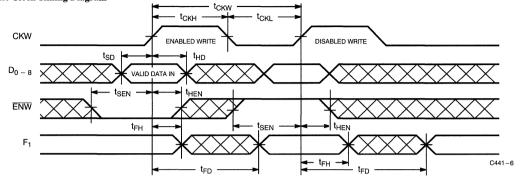

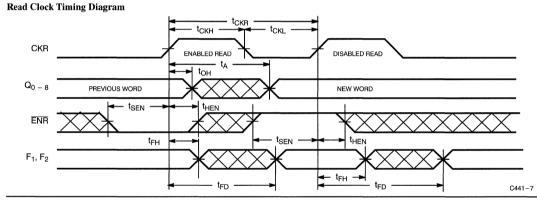

| CY7C441/43        | 512 x 9 Cascadable Clocked and 2K x 9 Cascadable Clocked<br>FIFO with Programmable Flags | 5-138  |

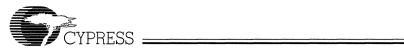

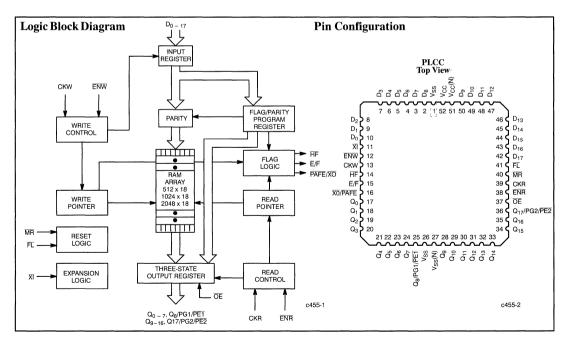

| CY7C455/56/57     | 512 x 18, 1K x 18, and 2K x 18 Cascadable Clocked FIFO<br>with Programmable Flags        | 5-161  |

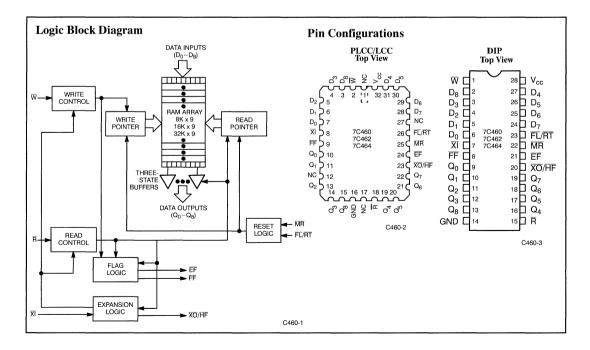

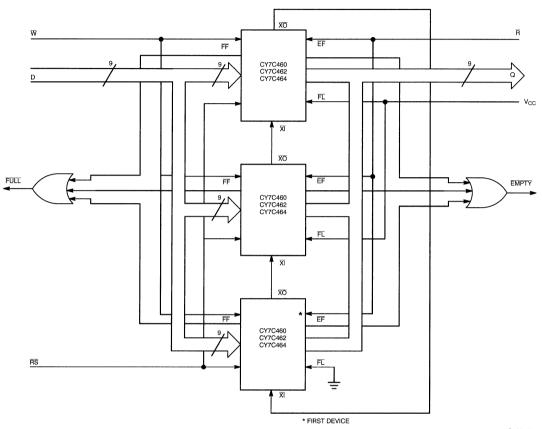

| CY7C460/62/64     | Cascadable 8K x 9 FIFO/Cascadable 16K x 9 FIFO/Cascadable 32K x 9 FIFO                   | 5-181  |

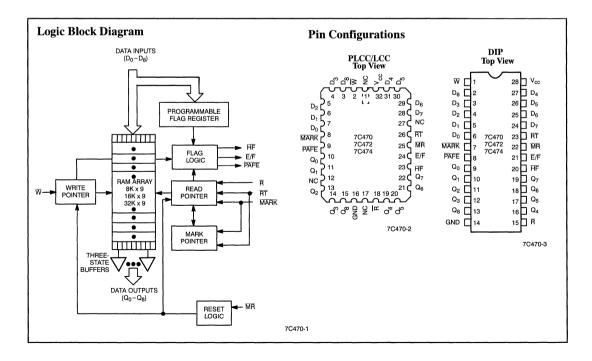

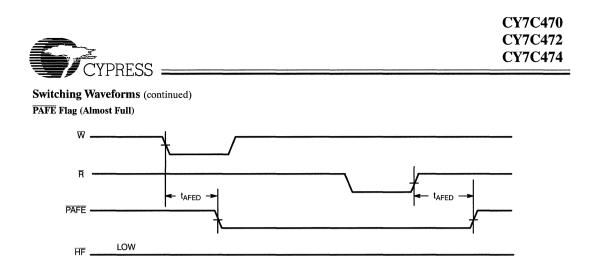

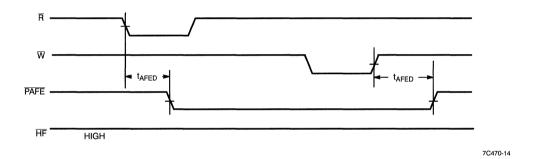

| CY7C470/72/74     | 8K x 9 FIFO, 16K x 9 FIFO/32K x 9 FIFO with Programmable Flags                           | 5-194  |

# Page Number

| Device Number         | Description                                                                       |

|-----------------------|-----------------------------------------------------------------------------------|

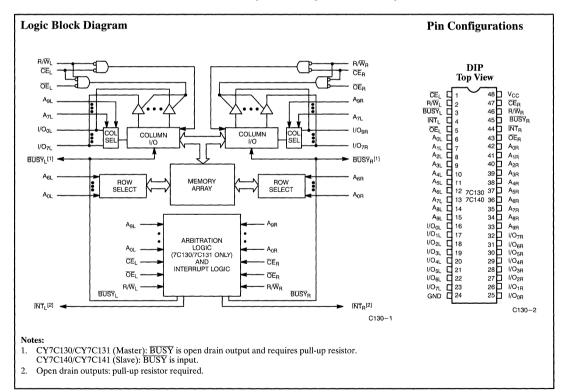

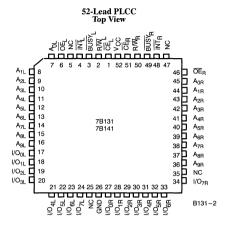

| CY7C130/31/40/41      | 1K x 8 Dual-Port Static RAM                                                       |

| CY7B131/41            | 1K x 8 Dual-Port Static RAM                                                       |

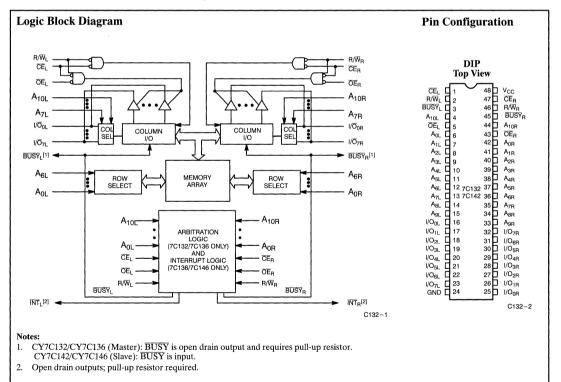

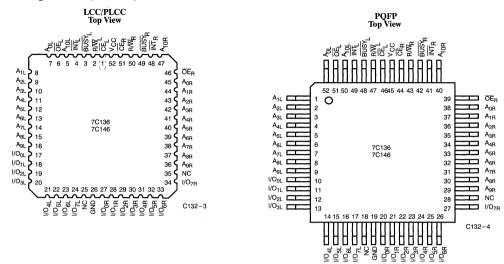

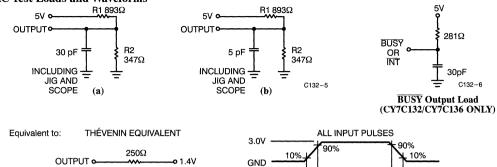

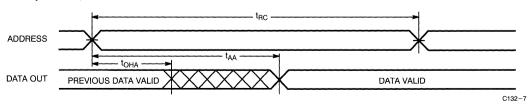

| CY7C132/136/142/146   | 2K x 8 Dual-Port Static RAM                                                       |

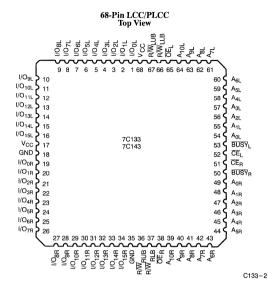

| CY7C133/CY7C143       | 2K x 16 Dual-Port Static RAM                                                      |

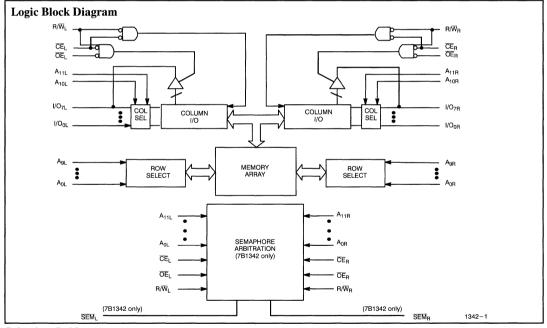

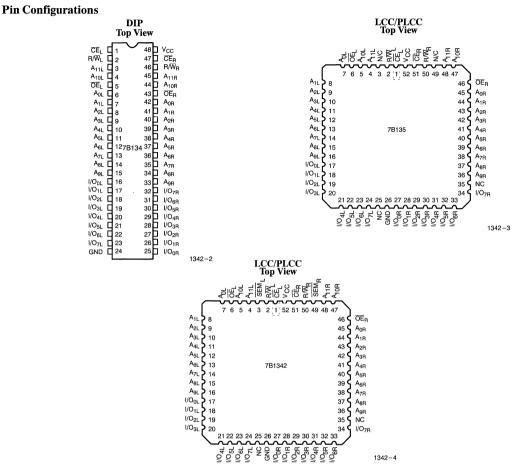

| CY7B134/135/1342      | 4K x 8 Dual-Port Static RAMs and 4K x 8 Dual-Port Static RAM with Semaphores 6-51 |

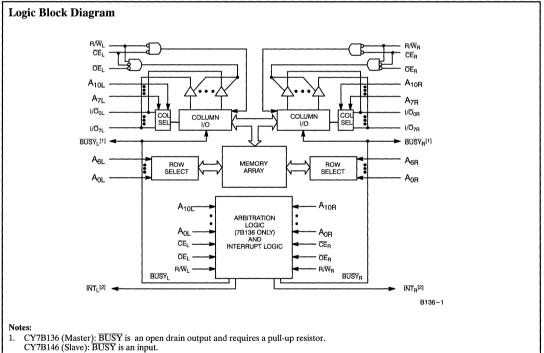

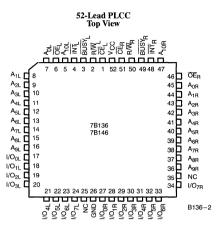

| CY7B136/CY7B146       | 2K x 8 Dual-Port Static RAM                                                       |

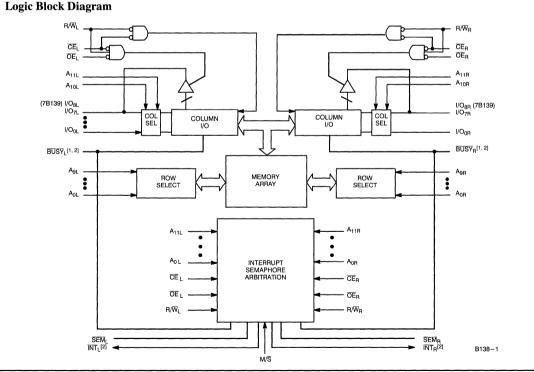

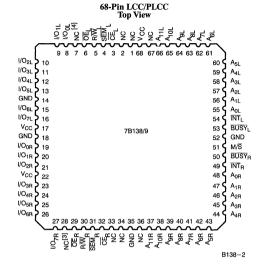

| CY7B138/CY7B139       | 4K x 8/9 Dual-Port Static RAM with Sem, Int, Busy                                 |

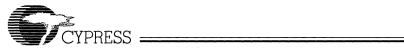

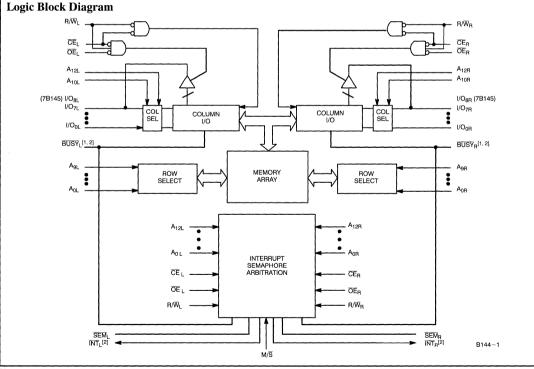

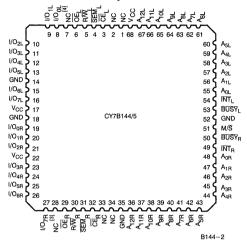

| CY7B144/145           | 8K x 8/9 Dual-Port Static RAMwith Sem, Int, Busy                                  |

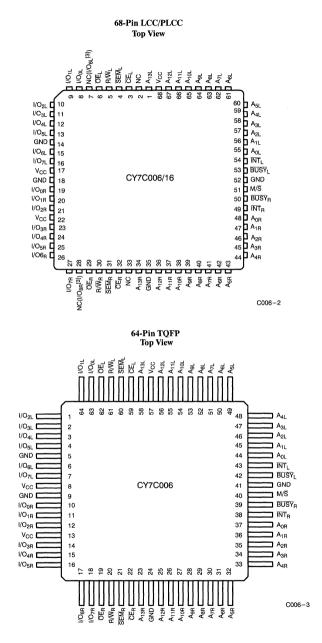

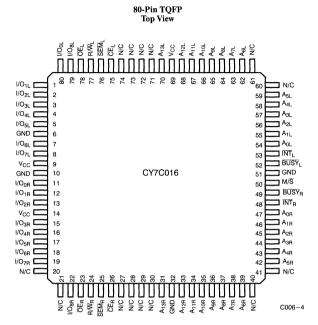

| CY7C006/016           | 16K x 8/9 Dual-Port Static RAM with Sem, Int, Busy                                |

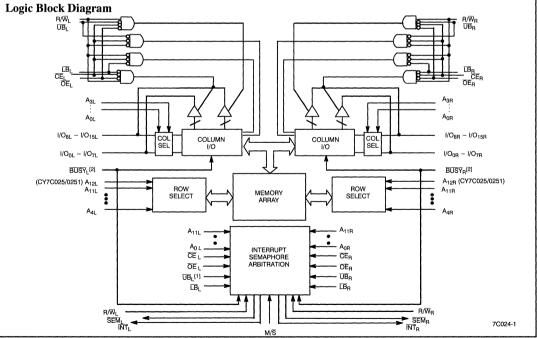

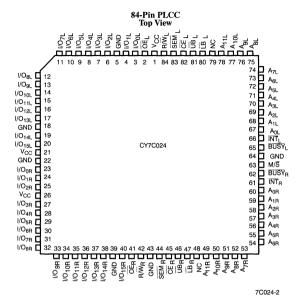

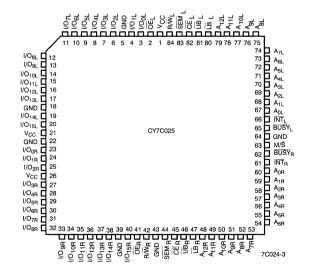

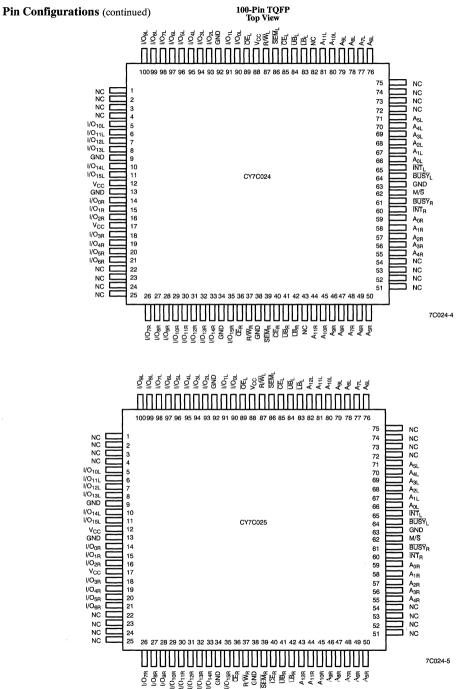

| CY7C024/0241/025/0251 | 4K x 16/18 and 8K x 16/18 Dual-Port Static RAM with Sem, Int, Busy                |

# **Timing Technology**

# **Page Number**

| Device Number     | Description                           |

|-------------------|---------------------------------------|

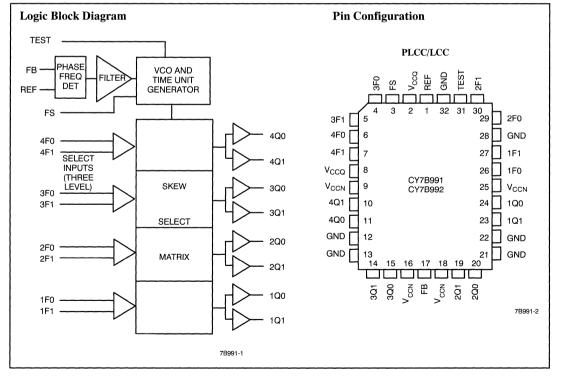

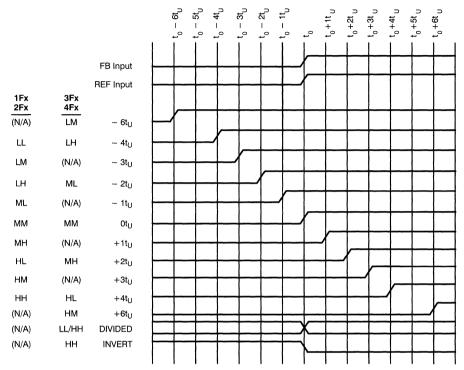

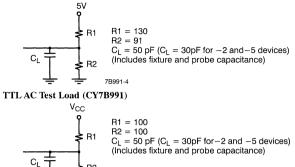

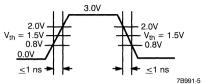

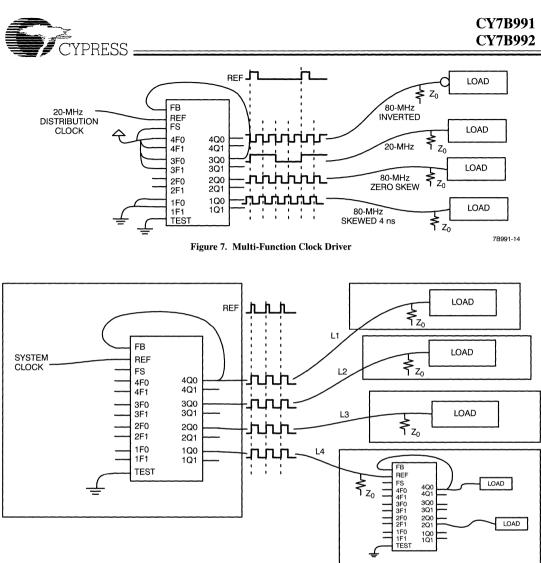

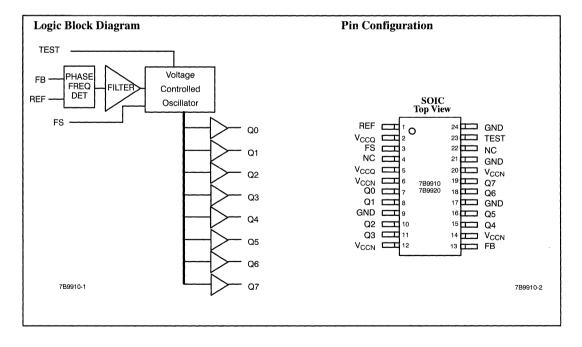

| CY7B991/CY7B992   | Programmable Skew Clock Buffer (PSCB) |

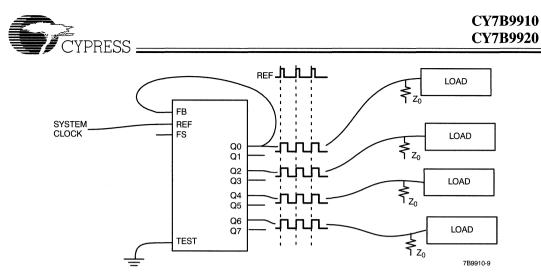

| CY7B9910/CY7B9920 | Low Skew Clock Buffer                 |

# Quality

**Dual Ports**

# Page Number

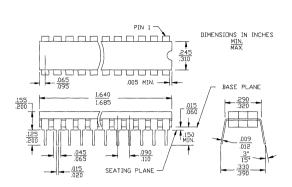

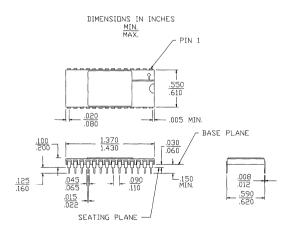

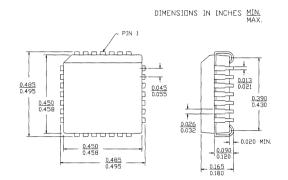

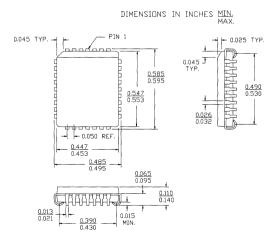

# **Package Diagrams**

# Page Number

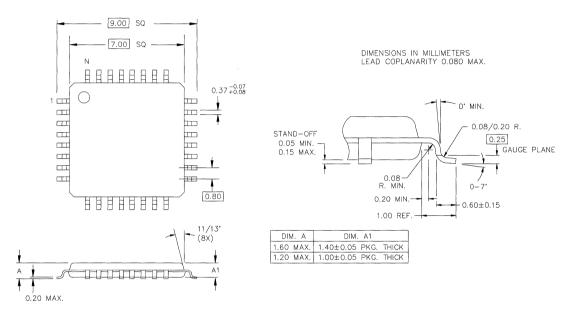

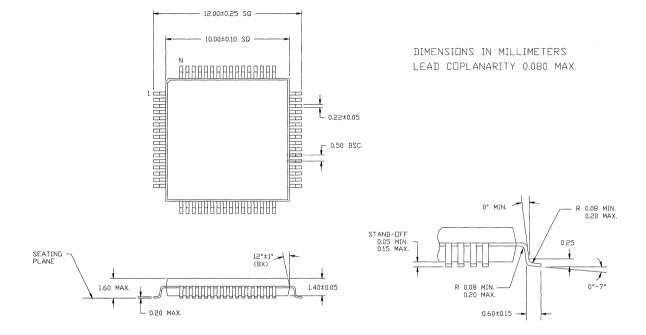

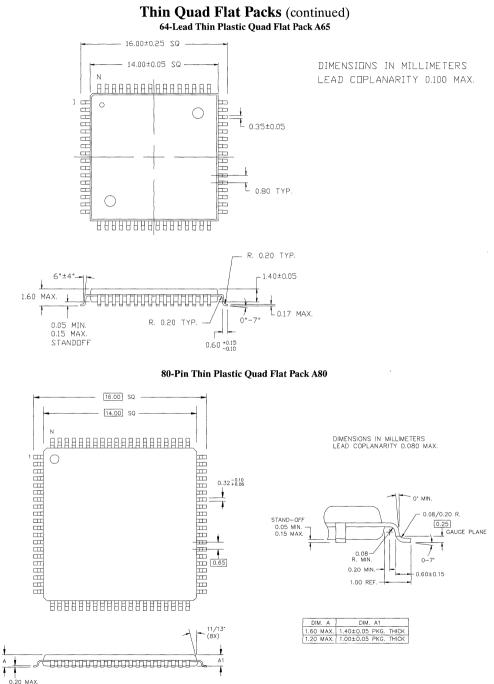

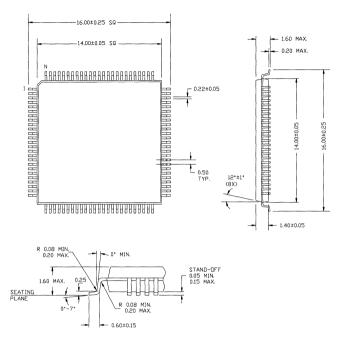

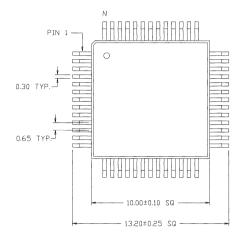

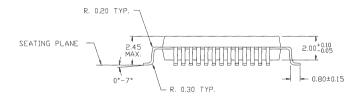

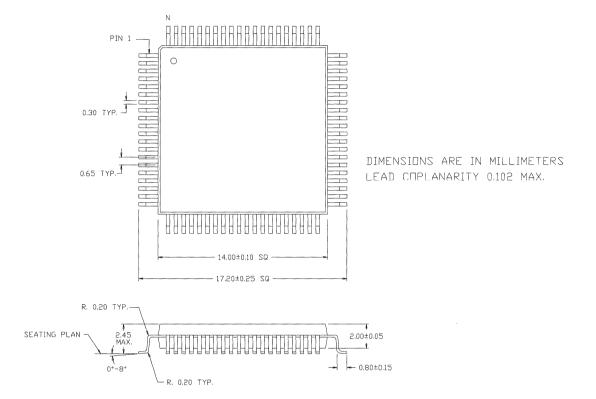

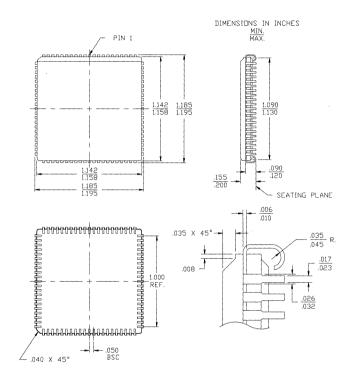

| Thin Quad Flat Packs9-32-Lead Plastic Thin Quad Flat Pack (TQFP) A329-64-Pin Thin Quad Flat Pack A649-64-Lead Thin Plastic Quad Flat Pack A659-80-Pin Thin Plastic Quad Flat Pack A809-100-Pin Plastic Thin Quad Flat Pack (TQFP) A1009- | -1<br>-2<br>-3<br>-3 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Ceramic Dual-In-Line Packages                                                                                                                                                                                                            | - 5                  |

| 5                                                                                                                                                                                                                                        |                      |

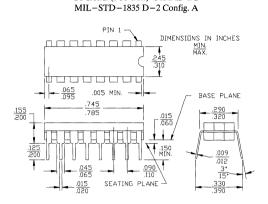

| 16-Lead (300-Mil) CerDIP D2 MIL-STD-1835 D-2 Config. A                                                                                                                                                                                   |                      |

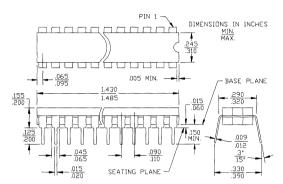

| 28-Lead (600-Mil) CerDIP D16 MIL-STD-1835 D-10 Config. A                                                                                                                                                                                 | -5                   |

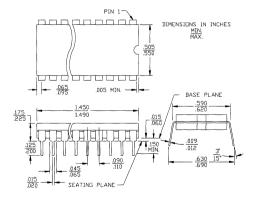

| 28-Lead (300-Mil) CerDIP D22 MIL-STD-1835 D-15 Config. A                                                                                                                                                                                 | -5                   |

| 32-Lead (300-Mil) CerDIP D32                                                                                                                                                                                                             | -6                   |

| 28-Lead (600-Mil) Sidebraze DIP D43                                                                                                                                                                                                      |                      |

|                                                                                                                                                                                                                                          |                      |

| Plastic Leaded Chip Carriers                                                                                                                                                                                                             | -7                   |

| 28-Lead Plastic Leaded Chip Carrier J64                                                                                                                                                                                                  |                      |

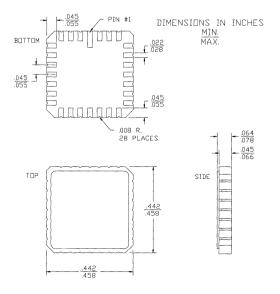

| 32-Lead Plastic Leaded Chip Carrier J65                                                                                                                                                                                                  | -7                   |

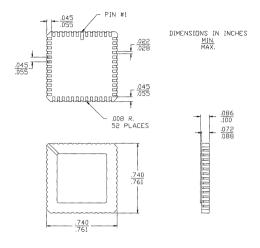

| 52-Lead Plastic Leaded Chip Carrier J69                                                                                                                                                                                                  | -8                   |

| 68-Lead Plastic Leaded Chip Carrier J81                                                                                                                                                                                                  | -8                   |

| 84-Lead Plastic Leaded Chip Carrier J83                                                                                                                                                                                                  | -8                   |

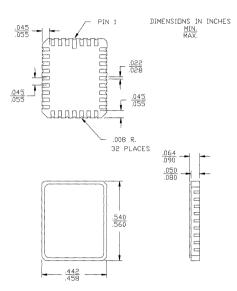

| Ceramic Leadless Chip Carriers                                                                                                                                                                                                           | -9                   |

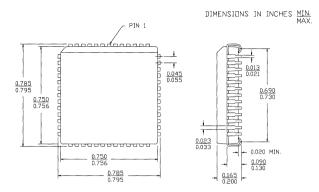

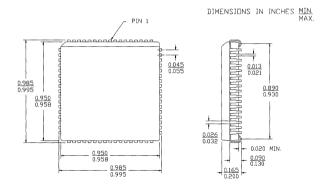

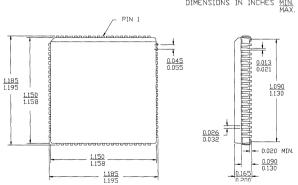

| 32-Pin Rectangular Leadless Chip Carrier L55 MIL-STD-1835 C-12                                                                                                                                                                           | -9                   |

| 28-Square Leadless Chip Carrier L64 MIL–STD–1835 C–4                                                                                                                                                                                     |                      |

| 20-5quare Leaviess Chip Carrier Lot Will=51D=1055 C=4                                                                                                                                                                                    | -9                   |

# Page Number

\_

| Package Diagrams (continued)<br>52-Square Leadless Chip Carrier L69                                                                                                |                                       | . 9–9                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|

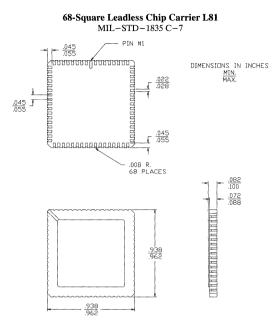

| 68-Square Leadless Chip Carrier L81 MIL–STD–1835 C–7<br>Plastic Quad Flatpacks<br>52-Lead Plastic Quad Flatpack N52<br>80-Lead Plastic Quad Flatpack N80           |                                       | <b>9–11</b><br>9–11         |

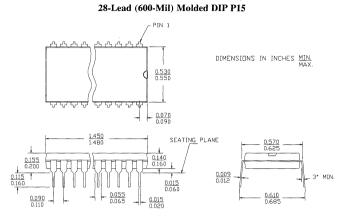

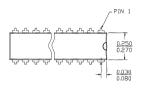

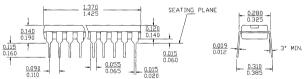

| Plastic Dual-In-Line Packages         28-Lead (600-Mil) Molded DIP P15         28-Lead (300-Mil) Molded DIP P21         48-Lead (600-Mil) Molded DIP P25           | · · · · · · · · · · · · · · · · · · · | <b>9-13</b><br>9-13<br>9-13 |

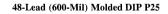

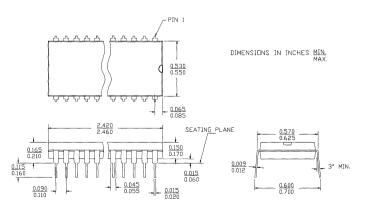

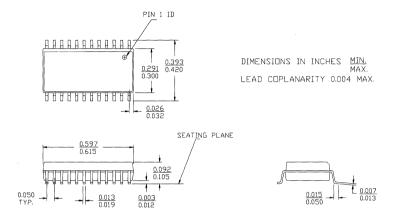

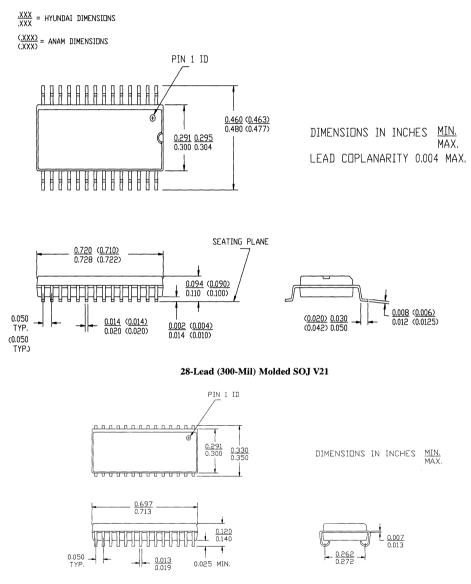

| Plastic Small Outline ICs         24-Lead (300-Mil) Molded SOIC S13         28-Lead 450-Mil (300-Mil Body Width) SOIC S22         28-Lead (300-Mil) Molded SOJ V21 | • • • • • • • • • • • • •             | 9–14<br>9–15                |

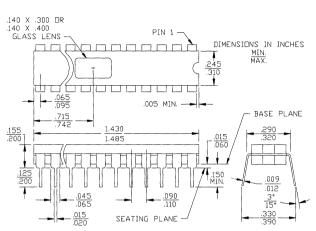

| Ceramic Windowed Dual-In-Line Packages                                                                                                                             |                                       |                             |

| Ceramic J-Leaded Chip Carriers                                                                                                                                     |                                       |                             |

# General Information 1

| General Information                                            | Page Number |

|----------------------------------------------------------------|-------------|

| Cypress Semiconductor Background                               | 1–1         |

| DataCom Background                                             | 1-4         |

| Ordering Information                                           | 1–5         |

| Product Selector Guide                                         | 1-6         |

| Cypress Semiconductor Bulletin Board System (BBS) Announcement | 1–13        |

# **Cypress Semiconductor Background**

Cypress Semiconductor was founded in April 1983 with the stated goal of serving the high-performance semiconductor market. This market is served by producing the highest-performance integrated circuits using state-of-the-art processes and circuit design. Cypress is a complete semiconductor manufacturer, performing its own process development, circuit design, wafer fabrication, assembly, and test. The company went public in May 1986 and has been listed on the New York Stock Exchange since October 1988.

The initial semiconductor process, a CMOS process employing 1.2-micron geometries, was introduced in March 1984. This process is used in the manufacturing of Static RAMs and Logic circuits. In the third quarter of 1984, a 1.2-micron CMOS EPROM process was introduced for the production of programmable products. At the time of introduction, these processes were the most advanced production processes in the industry. Following the 1.2-micron processes, a 0.8-micron CMOS SRAM process was implemented in the first quarter of 1986, and a 0.8-micron EPROM process in the third quarter of 1987.

In keeping with the strategy of serving the high-performance markets with state-of-the-art integrated circuits, Cypress introduced two new processes in 1989. These were a bipolar submicron process, targeted for ECL circuits, and a BiCMOS process to be used for most types of TTL and ECL circuits.

The circuit design technology used by Cypress is also state of the art. This design technology, along with advanced process technology, allows Cypress to introduce the fastest, highest-performance circuits in the industry. Cypress's offers products in four divisions: the Static Memory Division, the Programmable Products Division, the Computation Products Division, and the Data Communications Division.

### **Static Memories Division**

Cypress is a market-leading supplier of SRAMs, providing a wide range of SRAM memories for leading companies worldwide. SRAMs are used in high-performance personal computers, workstations, telecommunications systems, industrial systems, instrumentation devices, and networking products. Cypress's lower production cost structure allows the company to compete effectively in the high-volume personal computer and workstation market for SRAMs, including providing cache RAMs to support today's high-performance microprocessors, such as Pentium<sup>™</sup>, and PowerPC<sup>™</sup>. This business, combined with upcoming low-voltage products for the cellular communications, portable instrument, and laptop/notebook PC markets, positions Cypress for future success in this key product area.

Multichip modules is a fast-growing market segment that consists of multiple semiconductor chips mounted in packages that can be inserted in a computer circuit board. Cache modules for personal computers are the mainstay of this product line, and Cypress has announced major design wins for these products in IBM's PS/ValuePoint <sup>™</sup> line of PCs, and in Apple Computer's highest performing Power Macintosh <sup>™</sup> products.

### **Programmable Products Division**

With increasing pressure on system designers to bring products to market more quickly, programmable logic devices (PLDs) are becoming extremely popular. PLDs are logic control devices that can be easily programmed by engineers in the field, and later erased and reprogrammed. This allows the designers to make key changes to their systems very late in the development cycle to ensure competitive advantage. Used extensively in a wide range of applications, PLDs constitute a large and growing market. Cypress's UltraLogic <sup>™</sup> product line addresses the high-density programmable logic market. UltraLogic includes the Ultra38000 <sup>™</sup> and pASIC380 <sup>™</sup> families of field-programmable gate arrays (FPGAs), the industry's fastest. It also includes high performance complex PLDs, the FLASH370 <sup>™</sup> family. Both of these product families are supported by Cypress's VHDL (Very high-speed integrated circuit Hardware Description Language) based *Warp* software design tools. Cypress pioneered the use of VHDL for PLD programming, and *Warp* software is a key factor in the company's overall success in the PLD market.

Cypress is a leading provider of the industry-standard 22V10 PLD with a wide range of products. Cypress is committed to competing in all ranges of the PLD market, with small devices, including the industry standard 16V8, the MAX340 EPLD line, and the UltraLogic products. To support these products, Cypress offers one of the industry's broadest range of programming tools and software for the programming of its PLDs.

Cypress provides one of the industry's broadest ranges of CMOS EPROMs and PROMs. Cypress owns a large share of the highspeed CMOS PROM market, and with its new cost structure, is effectively penetrating the mainstream EPROM market with a popular 256 Kbit EPROM, and the introduction of the world's fastest 512K and 1 Megabit EPROMs at 25 ns.

FCT Logic products are used in bus interface and data buffering applications in almost all digital systems. With the addition of the FCT logic product line, Cypress now offers over 46 standard logic and bus interface functions. The products are offered in the second generation FCT-T format, which is pin-compatible with the older FCT devices, but adds TTL (transistor-to-transistor logic) outputs for significantly lower ground bounce and improved system noise immunity. Cypress also offers the most popular devices with on-chip 25-ohm termination resistors (FCT2-T) to further lower ground bounce with no speed loss. Included in the new product family is the CYBUS3384, a bus switch that enables bidirectional data transfer between multiple bus systems or between 5 volt and 3.3 volt devices. Cypress also offers 16-bit versions of popular FCT products. This broad product offering is produced on Cypress's high-volume, CMOS manufacturing lines.

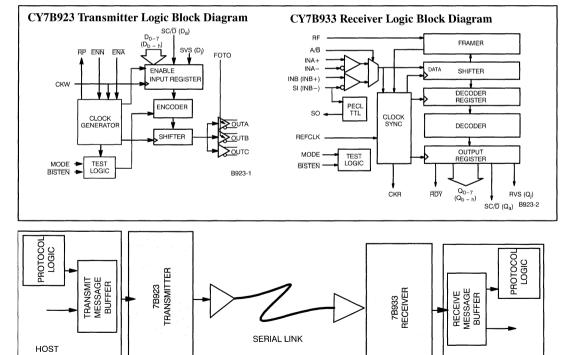

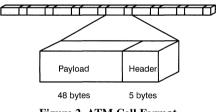

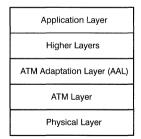

### **Data Communications Division**

This is an especially significant area for Cypress since it represents a more market-driven orientation for the company in a fast-growing market segment. As part of the new company strategy, Cypress has dedicated this product line to serve the highspeed data communications market with a range of products from the physical connection layer to system-level solutions. HOTLink<sup>™</sup>, high-speed, point-to-point serial communications chips have been well received. HOTLink, along with the SO-NET/SDS Serial Transceiver (SST<sup>™</sup>), address the fast-growing market segments of Asynchronous Transfer Mode (ATM) and Fibre Channel communications. The company has also entered the Ethernet market with the 100BaseT-4 CY7C971 Fast Ethernet Transceiver and the CY7B8392 Coax Ethernet Transceiver. The data communications division encompasses related products including RoboClock, a programmable skew clock buffer that adjusts complex timing control signals for a broad range of systems. The division also offers a broad range of First-In, First-Out (FIFO) memories, used to communicate data between systems operating at different frequencies, and Dual-Port Memories, used to distribute data to two different systems simultaneously.

### **Computation Products Division**

This division focuses on the high-volume, high-growth market surrounding the desktop computer. It is the second of Cypress's market-oriented divisions. The division includes timing technology products offered through Cypress's IC Designs Subsidiary in Kirkland, Washington. IC Designs products are used widely in personal computers and disk drives, and the product line provides Cypress with major inroads into these markets, helping move the company towards a more market-driven orientation. IC Designs clock oscillators control the intricate timing of all aspects of a computer system, including signals for the computer's central processing unit (CPU), keyboard, disk drives, system bus, serial port, and real-time clock. They replace all of the metal can oscillators used in the system. IC Designs recently announced a new product, QuiXTAL<sup>™</sup>, which is a programmable metal can oscillator, and replaces individual oscillators used to control timing signals in virtually every type of electronics equipment. QuiXTAL can be programmed to any frequency, providing users the ability to make last-minute frequency adjustments, speeding time to market. QuiXTAL takes frequency synthesis beyond the PC market, and addresses the broad market segments of electronic instrumentation, telecommunications equipment, and medical systems.

Also offered by this division are chipsets for personal computers. Cypress entered this market with the 1994 acquisition of Contaq Microsystems, and recently announced the hyperCache <sup>TM</sup> Chipset for Pentium <sup>TM</sup>-class PCs. The hyperCache Chipset is the industry's most highly integrated. In addition to integrating keyboard and mouse control, real-time clock, and local-bus IDE control, it is the only chipset which offers integrated second-level cache.

# **Cypress Facilities**

Cypress operates wafer fabrication facilities in California's Silicon Valley (San Jose), Round Rock (Austin), Texas, and Bloomington, Minnesota. The company's fourth wafer fab, located adjacent to the Bloomington, Minnesota facility, went on-line in July 1995. There are additional Cypress Design Centers in Starkville, Mississippi, Colorado Springs, Colorado, and the United Kingdom, and a PLD software design group in Beaverton, Oregon. The facilities are designed to the most demanding technical and environmental specifications in the industry. At the Texas and Minnesota facilities, the entire wafer fabrication area is specified to be a Class 1 environment. This means that the ambient air has less than 1 particle of greater than 0.2 microns in diameter per cubic foot of air. Other environmental considerations are carefully insured: temperature is controlled to a  $\pm 0.1$ degree Fahrenheit tolerance; filtered air is completely exchanged more than 10 times each minute throughout the fab; and critical equipment is situated on isolated slabs to minimize vibration.

The company has also received ISO9000 registration, a standard model of quality assurance that is awarded to companies with exacting standards of quality management, production, and inspections.

Attention to assembly is equally critical. Cypress manufactures 100 percent of its wafers in the United States, at the front-end fabrication sites in California (San Jose), Minnesota (Blooming-ton), and Texas (Round Rock). Cypress Texas, the company's largest fab, and Cypress Minnesota's fabs, are all Class 1 facilities.

To improve global competitiveness, Cypress chose to move most back-end assembly, test, and mark operations to a facility in Thailand. Be assured that Cypress's total quality commitment extends to the new site—Cypress Bangkok.

The move to Bangkok consummated an intense search by Cypress for a world-class, environmentally sophisticated facility that we could bring on line quickly. The Cypress search team scrutinized fifteen manufacturing facilities in five countries and chose a site managed by Alphatec Electronics Co., Ltd., a privately owned, entrepreneurial company promoted by the Thailand Board of Investment. Cypress Bangkok occupies almost 25,000 square feet—a significant portion of the manufacturing floor space available within the facility. The full facility at Bangkok occupies more than 85,000 square feet on a site that encompasses 25 acres—sufficient room for expansion to a number of buildings in a campus-like setting. In order to meet growing demand for its products, Cypress has broken ground on a new assembly and test facility in the Philippines, which is scheduled for completion in 1996.

Cypress San Jose maintains complete management control of all assembly, test, mark, and ship operations worldwide, thus assuring complete continuity of back-end operations and quality.

Cypress has added Tape Automated Bonding (TAB) to its package offering. TAB, a surface-mount packaging technology, provides the densest lead and package footprint available for fully tested die.

From Cypress's facility in Minnesota, a VME Bus Interface Products group has been in operation since the acquisition of VTC's fab in 1990. Cypress manufactures VIC and VAC VME devices on the 0.8 micron CMOS process.

The Cypress motto has always been "only the best—the best facilities, the best equipment, the best employees ... all striving to make the best products."

# **Cypress Process Technology**

In the last decade, there has been a tremendous need for highperformance semiconductor products manufactured with a balance of SPEED, RELIABILITY, and POWER. Cypress Semiconductor overcame the classically held perceptions that CMOS was a moderate-performance technology.

Cypress initially introduced a 1.2-micron "N" well technology with double-layer poly and a single-layer metal. The process employed lightly doped extensions of the heavily doped source and drain regions for both "N" and "P" channel transistors for significant improvement in gate delays. Further improvements in performance, through the use of substrate bias techniques, have added the benefit of eliminating the input and output latch-up characteristics associated with older CMOS technologies.

Cypress pushed process development to new limits in the areas of PROMs (Programmable Read Only Memory) and EPLDs (Erasable Programmable Logic Devices). Both PROMs and EPLDs have existed since the early 1970s in a bipolar process that employed various fuse technologies and was the only viable high-speed nonvolatile process available. Cypress PROMs and EPLDs use EPROM technology, which has been in use in MOS (Metal Oxide Silicon) since the early 1970s. EPROM technology has traditionally emphasized density while forsaking performance. Through improved technology, Cypress produced the first high-performance CMOS PROMs and EPLDs, replacing their bipolar counterparts.

To maintain our leadership position in CMOS technology, Cypress introduced a sub-micron technology in 1987. This 0.8 micron breakthrough made Cypress's CMOS one of the most advanced production processes in the world. The drive to maintain

leadership in process technology has not stopped with the 0.8-micron devices. Cypress introduced a 0.65-micron process in 1991. A 0.5-micron process is currently in production.

Although not a requirement in the high-performance arena, CMOS technology substantially reduces the power consumption for any device. This improves reliability by allowing the device to operate at a lower die temperature. Now higher levels of integration are possible without trading performance for power. For instance, devices may now be delivered in plastic packages without any impact on reliability.

While addressing the performance issues of CMOS technology, Cypress has not ignored the quality and reliability aspects of technology development. Rather, the traditional failure mechanisms of electrostatic discharge (ESD) and latch-up have been addressed and solved through process and design technology innovation.

ESD-induced failure has been a generic problem for many highperformance MOS and bipolar products. Although in its earliest years, MOS technology experienced oxide reliability failures, this problem has largely been eliminated through improved oxide growth techniques and a better understanding of the ESD problem. The effort to adequately protect against ESD failures is perturbed by circuit delays associated with ESD protection circuits. Focusing on these constraints, Cypress has developed ESD protection circuitry specific to 1.2-, 0.8-, 0.65-, and 0.5-micron CMOS process technology. Cypress products are designed to withstand voltage and energy levels in excess of 2001 volts and 0.4 milli-joules.

Latch-up, a traditional problem with CMOS technologies, has been eliminated through the use of substrate bias generation techniques, the elimination of the "P" MOS pull-ups in the output drivers, the use of guardring structures and care in the physical layout of the products.

Cypress has also developed additional process innovations and enhancements: multilayer metal interconnections, advanced metal deposition techniques, silicides, exclusive use of plasma for etching, and 100-percent stepper technology with the world's most advanced equipment.

Cypress technologies have been carefully designed, creating products that are "only the best" in high-speed, excellent reliability, and low power.

UltraLogic, Ultra3800, FLASH370, *Warp3*, HOTLink, SST, and hyperCache are trademarks of Cypress Semiconductor Corporation. pASIC is a trademark of QuickLogic.

Pentium is a trademark of Intel Corporation.

Power PC and PS/Value Point are trademarks of International Business Machines Corporation.

Power Macintosh is a trademark of Apple.

MAX is a trademark of Altera.

# **DataCom Background**

Cypress Semiconductor was founded in April 1983 with the stated goal of serving the high-performance semiconductor market. We have continued to serve this market using state-of-theart process and circuit technology combined with architectural excellence. Our initial product thrusts included high-performance SRAMs, PLDs, FIFOs, Dual Port RAMs, and EPROMs.

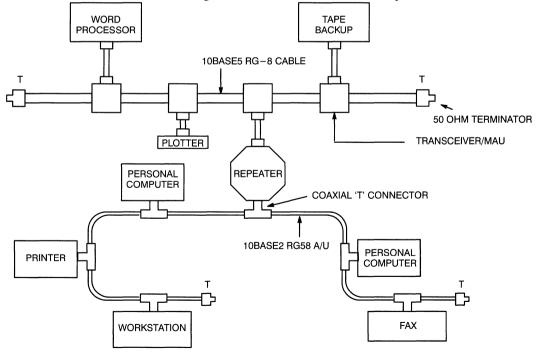

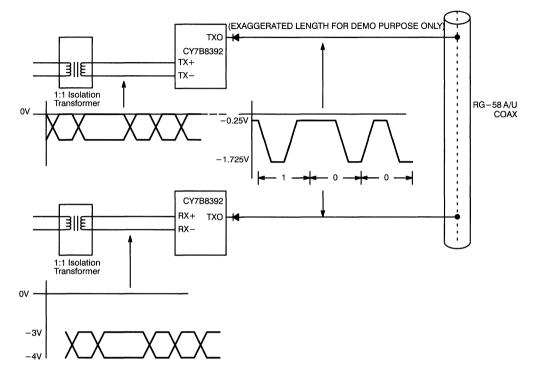

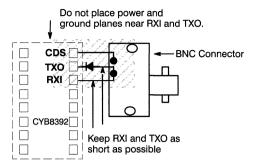

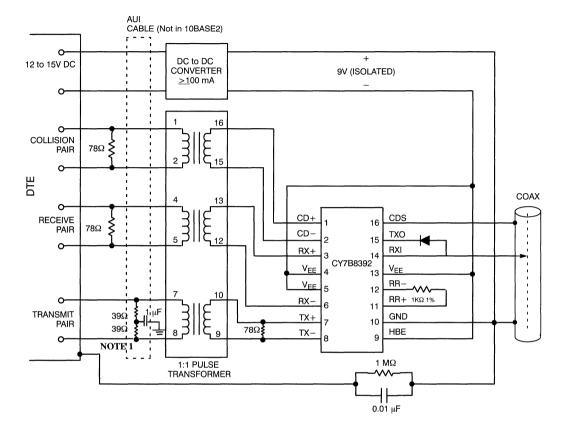

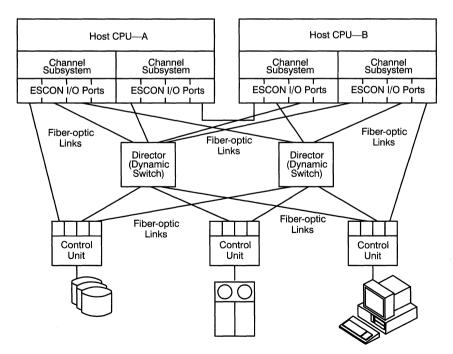

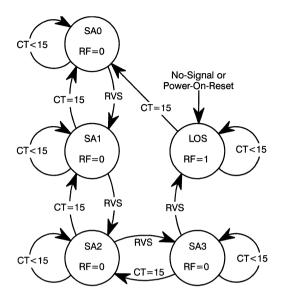

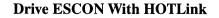

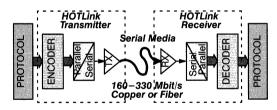

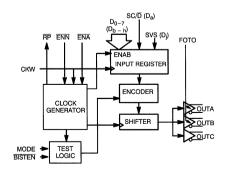

In 1991, Cypress created a Data Communications division, with a focus on Physical Layer (PHY) devices to serve the ATM, SO-NET, Ethernet, ESCON, and Fibre Channel markets. Cypress's DataCom division has delivered a family of these PHY devices including the SST (SONET Serial Transceiver) Clock Recovery Device, the HOTLink 330 MHz point-to-point transmitter/receiver chip set, the CY7C971 10/100 Base-T4 Fast Ethernet Transceiver and the industry standard CY7B8392 10Base-2 Ethernet Coax Transceiver. In 1996 and 1997, Cypress will continue to deliver high performance solutions for the Physical Layer Datacom market covering 10 Base-FL, 100 Base-TX, and 155 MHz (OC-3) ATM/SONET Integration.

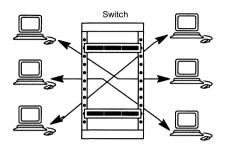

Our goal is to continue to provide PHY solutions for all segments of the DataCom market including Network Adapter Cards, Routers, Switches, Repeaters, Mass Storage, and Disk Farms. Our product evolution will continue through complete solutions for these growth markets.

In addition to PHY devices, the DataCom division includes a multitude of Specialty Memories including FIFOs (First-In-First-Out) and Dual Port RAMs which are frequently used in communications systems. Our current product count includes 44 Asynchronous and Synchronous FIFOs ranging from 64 x 9/18 through 32K x 9 at 100 MHz as well as 18 Dual Ports from 1K x 8 through 8K x 18 with 15 ns access times. We are confident that our wide variety of Specialty Memory products will suit many of your buffering requirements.

In addition to this DataCom Data Book, Cypress also offers technical documentation including a new Applications Handbook, HOTLink User's Guide, and a VME User's Guide.

We look forward to serving you. Please call with any requests for design, application, or additional product information.

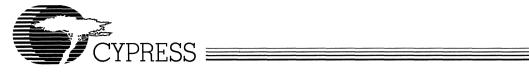

# **Ordering Information**

In general, the valid ordering codes for all products (except modules and VMEbus products) follow the format below; e.g., CY7C128-45DMB, PALC16R8L-35PC

Cypress FSCM #65786

# **Product Selector Guide**

# **Dual-Port RAMs**

| Size | Organization                         | Pins   | Part Number | Speed (ns)                           | I <sub>CC</sub><br>(mA@ns) | Packages |

|------|--------------------------------------|--------|-------------|--------------------------------------|----------------------------|----------|

| 8K   | 1Kx8—Dual-Port Master                | 48     | CY7C130     | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170@25                     | D,P      |

| 8K   | 1Kx8—Dual-PortSlave                  | 48     | CY7C140     | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170@25                     | D,P      |

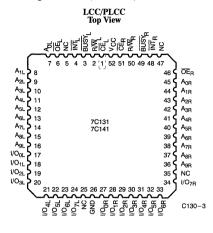

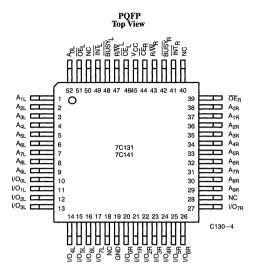

| 8K   | 1Kx8-Dual-Port Master                | 52     | CY7C131     | $t_{AA} = 25, 30, 35, 45, 55$        | 170@25                     | J, L, N  |

| 8K   | 1Kx8—Dual-PortSlave                  | 52     | CY7C141     | $t_{AA} = 25, 30, 35, 45, 55$        | 170@25                     | J, L, N  |

| 16K  | 2Kx8—Dual Port Master                | 48     | CY7C132     | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170@25                     | D,P      |

| 16K  | 2Kx8—Dual-PortSlave                  | 48     | CY7C142     | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170@25                     | D,P      |

| 16K  | 2Kx8-Dual-Port Master                | 52     | CY7C136     | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170@25                     | J, L, N  |

| 16K  | 2Kx8-Dual-PortSlave                  | 52     | CY7C146     | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170@25                     | J, L, N  |

| 32K  | 4Kx8-Dual-Port, No Arbitration       | 48     | CY7B134     | $t_{AA} = 20, 25, 35, 55$            | 240@20                     | D, L, P  |

| 32K  | 4Kx8-Dual-Port, w/Semaph             | 52     | CY7B1342    | $t_{AA} = 20, 25, 35, 55$            | 240@20                     | J        |

| 32K  | 2Kx16-Dual-PortSlave                 | 68     | CY7C143     | t <sub>AA</sub> = 15, 25, 35, 55     | 170@25                     | J,A      |

| 32K  | 2Kx16—Dual-Port Master               | 68     | CY7C133     | t <sub>AA</sub> = 15, 25, 35, 55     | 170@25                     | J,A      |

| 32K  | 4Kx8-Dual-Port, w/Semaph, Busy, Int  | 64,68  | CY7B138     | t <sub>AA</sub> = 15, 25, 35, 55     | 260@15                     | J,L,A    |

| 32K  | 4Kx8—Dual-Port, No Arbitration       | 52     | CY7B135     | t <sub>AA</sub> = 20, 25, 35, 55     | 240@20                     | J,L      |

| 32K  | 4Kx9-Dual-Port, w/Semaph, Busy, Int  | 68,80  | CY7B139     | t <sub>AA</sub> = 15, 25, 35, 55     | 260@15                     | J,L,A    |

| 64K  | 8Kx8Dual-Port, w/Semaph, Busy, Int   | 64,68  | CY7B144     | t <sub>AA</sub> = 15, 25, 35, 55     | 260@15                     | J,L,A    |

| 64K  | 8Kx9-Dual-Port, w/Semaph, Busy, Int  | 68,80  | CY7B145     | t <sub>AA</sub> = 15, 25, 35, 55     | 260@15                     | J,L,A    |

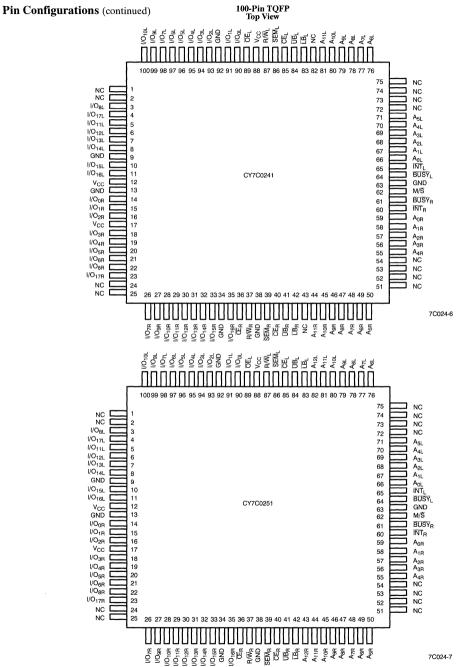

| 64K  | 4Kx16-Dual-Port,w/Semaph,Busy,Int    | 84,100 | CY7C024     | t <sub>AA</sub> = 15, 25, 35, 55     | 280@15                     | J,A      |

| 64K  | 4Kx18-Dual-Port, w/Semaph, Busy, Int | 84,100 | CY7C0241    | t <sub>AA</sub> = 15, 25, 35, 55     | 280@15                     | J,A      |

| 128K | 8Kx16—Dual-Portw/Semaph, Busy, Int   | 84,100 | CY7C025     | t <sub>AA</sub> =15, 25, 35, 55      | 280@15                     | J,A      |

| 128K | 8Kx18-Dual-Portw/Semaph, Busy, Int   | 84,100 | CY7C0251    | t <sub>AA</sub> =15,25,35,55         | 280@15                     | J,A      |

| 128K | 16Kx8—Dual-Portw/Semaph, Busy, Int   | 64,68  | CY7C006     | t <sub>AA</sub> =15, 25, 35, 55      | 260@15                     | J,A      |

| 128K | 16Kx9—Dual-Portw/Semaph, Busy, Int   | 68,80  | CY7C016     | t <sub>AA</sub> =15,25,35,55         | 260@15                     | J,A      |

# **Communication Products**

| Description                          | Pins       | Part Number | Speed (MHz) | I <sub>CC</sub> (mA) | Packages |

|--------------------------------------|------------|-------------|-------------|----------------------|----------|

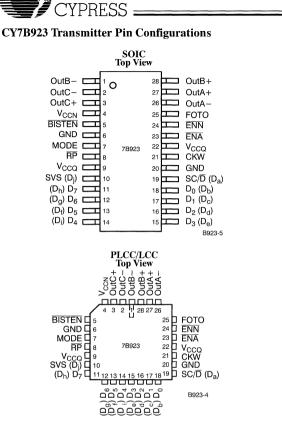

| HOTLink Transmitter                  | 28         | CY7B923     | 160-330     | 65                   | J,L,S    |

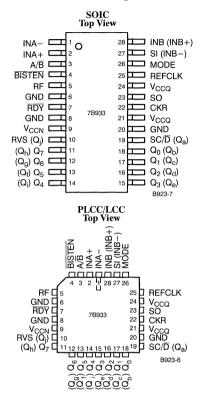

| HOTLink Receiver                     | 28         | CY7B933     | 160-330     | 120                  | J, L, S  |

| SONET/SDH Serial Transceiver         | 24         | CY7B951     | 51 & 155    | 50                   | S        |

| ATM SONET/SDH Transceiver            |            | CY7B955     |             |                      | ļ        |

| 10BASE 2/5 Ethernet Coax Transceiver | 16, 20, 28 | CY7B8392    | 10          | 25                   | J,P      |

| Fast Ethernet 100BASE-T4 Transceiver | 80         | CY7C971     | 10 & 100    | 300                  | N        |

| Fast Ethernet 100BASE-TX Transceiver | 44         | CY7C973     | 100         | 200                  | J        |

| HOTLink Evaluation Card              | N/A        | CY9266      | 160-330     | —N/A                 | C, F*, T |

# **FIFOs**

# Asynchronous

| Organization              | Pins   | Part Number | Speed (ns)                 | I <sub>CC</sub><br>(mA@ns) | Packages         |

|---------------------------|--------|-------------|----------------------------|----------------------------|------------------|

| 64x4                      | 16     | CY3341      | 1.2, 2 MHz                 | 45                         | D,P              |

| 64x4                      | 16     | CY7C401     | 5, 10, 15, 25 MHz          | 75                         | D, L, P          |

| 64x4—w/OE                 | 16     | CY7C403     | 10, 15, 25 MHz             | 75                         | D, L, P          |

| 64x5                      | 18     | CY7C402     | 5, 10, 15, 25 MHz          | 75                         | D, L, P          |

| 64x5w/OE                  | 18     | CY7C404     | 10, 15, 25 MHz             | 75                         | D, L, P          |

| 64x8w/OE and Almost Flags | 285    | CY7C408A    | 15, 25, 35 MHz             | 115@15                     | D, L, P, V       |

| 64x9—w/Almost Flags       | 28S    | CY7C409A    | 15, 25, 35 MHz             | 115@15                     | D, L, P, V       |

| 256 x 9—w/Half Full Flag  | 285,32 | CY7C419     | 10, 15, 20, 25, 30, 40, 65 | 35@20                      | A, D, L, P, V    |

| 512x9—w/HalfFullFlag      | 28     | CY7C420     | 20, 25, 30, 40, 65         | 35@20                      | D,P              |

| 512x9w/HalfFullFlag       | 285,32 | CY7C421     | 10, 15, 20, 25, 30, 40, 65 | 35@20                      | A, D, J, L, P, V |

| 1Kx9—w/HalfFullFlag       | 28     | CY7C424     | 20, 25, 30, 40, 65         | 35@20                      | D,P              |

| 1Kx9—w/HalfFullFlag       | 285,32 | CY7C425     | 10, 15, 20, 25, 30, 40, 65 | 35@20                      | A, D, J, L, P, V |

| 2Kx9w/HalfFullFlag        | 28     | CY7C428     | 20, 25, 30, 40, 65         | 35@20                      | D,P              |

| 2Kx9—w/HalfFullFlag       | 285,32 | CY7C429     | 10, 15, 20, 25, 30, 40, 65 | 35@20                      | A, D, J, L, P, V |

| 4Kx9-w/HalfFullFlag       | 28     | CY7C432     | 25, 30, 40, 65             | 35@20                      | D,P              |

| 4Kx9—w/HalfFullFlag       | 285,32 | CY7C433     | 10, 15, 20, 25, 30, 40, 65 | 35@20                      | A,D,J,L,P,V      |

| 8K x 9-w/HalfFullFlag     | 28     | CY7C460     | 15, 25, 40, 65             | 105@15                     | D, J, L, P       |

| 8K x 9—w/Prog. Flags      | 28     | CY7C470     | 15, 25, 40, 65             | 105@15                     | D, J, L, P       |

| 16K x 9w/Half Full Flag   | 28     | CY7C462     | 15, 25, 40, 65             | 105@15                     | D, J, L, P       |

| 16K x 9—w/Prog. Flags     | 28     | CY7C472     | 15, 25, 40, 65             | 105@15                     | D, J, L, P       |

| 32K x 9—w/Half Full Flag  | 28     | CY7C464     | 15, 25, 40, 65             | 105@15                     | D, J, L, P       |

| 32K x 9w/Prog. Flags      | 28     | CY7C474     | 15, 25, 40, 65             | 105@15                     | D, J, L, P       |

| 2Kx9—Bidirectional        | 28S    | CY7C439     | 25, 30, 40, 65             | 147@25                     | D, J, L, P       |

# Clocked

| Organization                   | Pins   | Part Number | Speed (ns) | I <sub>CC</sub><br>(mA@MHz) | Packages      |

|--------------------------------|--------|-------------|------------|-----------------------------|---------------|

| 512 x 9—Clocked                | 285,32 | CY7C441     | 14,20,30*  | 70@20                       | D, J, L, P, V |

| 512 x 9—Clocked w/ Prog. Flags | 32     | CY7C451     | 14,20,30*  | 70@20                       | D, J, L       |

| 2K x 9—Clocked                 | 285,32 | CY7C443     | 14,20,30*  | 70@20                       | D, J, L, P, V |

| 2K x 9—Clocked w/Prog. Flags   | 32     | CY7C453     | 14,20,30*  | 70@20                       | D, J, L       |

| 512 x 18—Clocked w/Prog. Flags | 52     | CY7C455     | 14,20,30*  | 90@20                       | J, L, N       |

| 1Kx18-Clocked w/Prog. Flags    | 52     | CY7C456     | 14,20,30*  | 90@20                       | J, L, N       |

| 2Kx18—Clockedw/Prog.Flags      | 52     | CY7C457     | 14,20,30*  | 90@20                       | J, L, N       |

# Synchronous

| Organization      | Pins | Part Number | Speed (ns)      | I <sub>CC</sub><br>(mA@MHz) | Packages |

|-------------------|------|-------------|-----------------|-----------------------------|----------|

| 64x9—Synchronous  | 32   | CY7C4421    | 10, 15, 25, 35* | 50@20                       | A,J      |

| 256x9—Synchronous | 32   | CY7C4201    | 10, 15, 25, 35* | 50@20                       | A,J      |

| 512x9—Synchronous | 32   | CY7C4211    | 10,15,25,35*    | 50@20                       | A,J      |

| 1Kx9—Synchronous  | 32   | CY7C4221    | 10, 15, 25, 35* | 50@20                       | A,J      |

| 2Kx9—Synchronous  | 32   | CY7C4231    | 10, 15, 25, 35* | 50@20                       | A,J      |

Note: Please contact a Cypress Representative for product availability.

# FIFOs (continued)

| Organization        | Pins  | Part Number | Speed (ns)      | I <sub>CC</sub><br>(mA@MHz) | Packages |

|---------------------|-------|-------------|-----------------|-----------------------------|----------|

| 4Kx9—Synchronous    | 32    | CY7C4241    | 10, 15, 25, 35* | 50@20                       | A,J      |

| 8Kx9—Synchronous    | 32    | CY7C4251    | 10, 15, 25, 35* | 50@20                       | A,J      |

| 16Kx9—Synchronous   | 32    | CY7C4261    | 10, 15, 25, 35* | 50@20                       | A,J      |

| 32Kx9—Synchronous   | 32    | CY7C4271    | 10, 15, 15, 35* | 50@20                       | A,J      |

| 64 x 18—Synchronous | 64,68 | CY7C4425    | 10, 15, 25, 35* | 100@20                      | A, J     |

| 256x18—Synchronous  | 64,68 | CY7C4205    | 10, 15, 25, 35* | 100@20                      | A,J      |

| 512x18—Synchronous  | 64,68 | CY7C4215    | 10, 15, 25, 35* | 100@20                      | A,J      |

| 1Kx18—Synchronous   | 64,68 | CY7C4225    | 10, 15, 25, 35* | 100@20                      | A,J      |

| 2Kx18—Synchronous   | 64,68 | CY7C4235    | 10, 15, 25, 35* | 100@20                      | A, J     |

| 4Kx18—Synchronous   | 64,68 | CY7C4245    | 10, 15, 25, 35* | 100@20                      | A,J      |

| 8Kx18—Synchronous   | 64,68 | CY7C4255    | 10, 15, 25, 35* | 100@20                      | A, J     |

| 16Kx18—Synchronous  | 64,68 | CY7C4265    | 10, 15, 25, 35* | 100@20                      | A,J      |

\* Cycle Times

# **Timing Technology Products**

| Application                                                                     | Part#    | # of<br>PLLs | # of<br>Outputs | Features                                                                                                              | Package            |

|---------------------------------------------------------------------------------|----------|--------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|--------------------|

| Industry Standard Motherboard<br>Frequency Synthesizers                         | CY2250   | 1            | 14              | Pentium/Pentium Pro servers: 12 skew controlled CPU clocks (250 ps pin-to-pin), 2 buffered reference clocks, 3.3V     | 28 SOIC            |

|                                                                                 | CY2252   | 2            | 14              | Pentium portables: 5 CPU/6 PCI clocks (2 "early" PCI for docking stations), 24 MHz, 2 buffered reference clocks, 3.3V | 28 SSOP            |

|                                                                                 | CY2254   | 2            | 14              | Intel Triton chipset compatible: 4 CPU/6 PCI clocks, 12<br>MHz, 24 MHz, 2 buffered reference clocks, 3.3V             | 28 SOIC            |

|                                                                                 | CY2255   | 1            | 14              | OPTi Viper chipset compatible: 6 CPU (1 "early")/6 PCI<br>clocks, 2 buffered reference clocks, 3.3V                   | 28 SOIC            |

|                                                                                 | CY2257   | 1            | 14              | Ali Aladdin chipset compatible: 6 CPU/6 PCI clocks, 2 buff-<br>ered reference clocks, 3.3V                            | 28 SOIC            |

|                                                                                 | CY2260   | 2            | 14              | Intel Natoma/Triton II chipset compatible: 4 CPU/6 PCI clocks, 48 MHz USB clock, 3 buffered reference clocks, 3.3V    | 28 SOIC<br>28 SSOP |

| General Purpose Programmable<br>Products (486 Pentium/Pentium                   | CY2071   | 1            | 3               | Factory EPROM programmable single PLL, 0.5–100 MHz, 5V/3.3V                                                           | 8 SOIC             |

| Promotherboards, peripherals,<br>cable TV, video games, MPEG<br>decoders, etc.) | CY2081   | 3            | 3               | Factory EPROM programmable triple PLL, $0.5 - 100$ MHz, $5V/3.3V$                                                     | 8 SOIC             |

|                                                                                 | CY2291   | 3            | 8               | Factory EPROM programmable triple PLL, 0.2–100 MHz, 5V/3.3V                                                           | 20 SOIC            |

|                                                                                 | CY2292   | 3            | 6               | Factory EPROM programmable triple PLL, 0.2–100 MHz, 5V/3.3V                                                           | 16 SOIC            |

|                                                                                 | ICD2051  | 2            | 5               | User-programmable dual PLL, 0.3-120 MHz, 5V                                                                           | 16SOIC             |

|                                                                                 | ICD2053B | 1            | 1               | User-programmable single PLL, 0.4-100 MHz, 5V                                                                         | 8 SOIC             |

| PC Graphics Frequency<br>Synthesizers                                           | ICD2061A | 2            | 2               | User-programmable PC video/memory clocks, 0.4–120<br>MHz, 5V                                                          | 16 SOIC            |

|                                                                                 | ICD2062B | 2            | 6               | User-programmable PECL video clock for workstations,<br>0.5-165 MHz, 5V                                               | 20 SOIC            |

|                                                                                 | ICD2063  | 2            | 2               | User-programmable PC video/memory clocks, 0.3-135<br>MHz, 5V/3.3V                                                     | 16SOIC             |

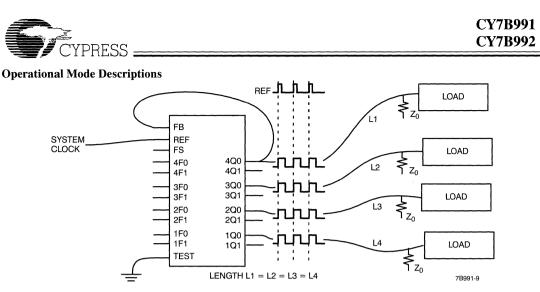

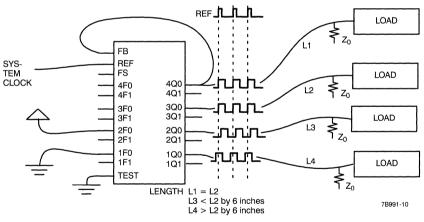

| Programmable Skew Clock Buffer<br>(TTL Output)                                  | CY7B991  | 1            | 8               | 3–80 MHz, Programmable Skew (700 ps increments)<br>250 ps pin-to-pin skew                                             | J,L                |

| Programmable Skew Clock Buffer<br>(CMOS Output)                                 | CY7B992  | 1            | 8               | 3–80 MHz, Programmable Skew (700 ps increments)<br>250 ps pin-to-pin skew                                             | J,L                |

Note: Please contact a Cypress Representative for product availability.

# **Product Selector Guide**

# Timing Technology Products (continued)

| Application                            | Part #   | # of<br>PLLs | # of<br>Outputs | Features                                                      | Package |

|----------------------------------------|----------|--------------|-----------------|---------------------------------------------------------------|---------|

| Low Skew Clock Buffer<br>(TTL Output)  | CY7B9910 | 1            | 8               | $15-80$ MHz, $t_{PD} = 500$ ps<br>250 ps pin-to-pin skew      | S       |

| Low Skew Clock Buffer<br>(CMOS Output) | CY7B9920 | 1            | 8               | 15-80 MHz, t <sub>PD</sub> = 500 ps<br>250 ps pin-to-pin skew | S       |

Note: Please contact a Cypress Representative for product availability.

# **HOTLink Cross Reference**

| Cypress TriQuin |                | TriQuint    |                | AMCC               |              | Raytheon |                |

|-----------------|----------------|-------------|----------------|--------------------|--------------|----------|----------------|

| Device          | Speed<br>Range | Device      | Speed<br>Range | Device Speed Range |              | Device   | Speed<br>Range |

| CY7B923/33      | 160-330        | GA9101/2/3* | 200/265        | S2032/33*          | 265/531/1062 | RCC700*  | 200/265        |

# **SST Cross Reference**

| Cypress | Cypress                           |         | ces                               | AMCC   |                                   |

|---------|-----------------------------------|---------|-----------------------------------|--------|-----------------------------------|

| Device  | Requires<br>155-MHz<br>Oscillator | Device  | Requires<br>155-MHz<br>Oscillator | Device | Requires<br>155-MHz<br>Oscillator |

| CY7B951 | No                                | AD 802* | Yes                               | S3014* | Yes                               |

\* Not pin compatible; see product profile for Cypress advantages.

# CY7C971 Fast Ethernet Transceiver (100BASE-T4) Cross Reference

| Cypress | · · · · · · · · · · · · · · · · · · · | Broadcom |                                  | Seeq    |                                  | AT&T   |                                  |

|---------|---------------------------------------|----------|----------------------------------|---------|----------------------------------|--------|----------------------------------|

| Device  | Integrated<br>Transmit<br>Filter      | Device   | Integrated<br>Transmit<br>Filter | Device  | Integrated<br>Transmit<br>Filter | Device | Integrated<br>Transmit<br>Filter |

| CY7C971 | Yes                                   | BCM5000* | No                               | 80C240* | Yes                              | *      | No                               |

\* Not pin compatible; see product profile for Cypress advantages.

# CY7B8392 10BASE-2 Ethernet Coax Transceiver Cross Reference

| Cypress  |                 |             |          | National |                 |             |          | Seeq   |                 |             |          |

|----------|-----------------|-------------|----------|----------|-----------------|-------------|----------|--------|-----------------|-------------|----------|

| Device   | I <sub>CC</sub> | Auto<br>AUI | Distance | Device   | I <sub>CC</sub> | Auto<br>AUI | Distance | Device | I <sub>CC</sub> | Auto<br>AUI | Distance |

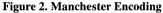

| CY7B8392 | 35 mA           | Yes         | 300M     | 8392     | 130 mA          | No          | 185M     | 83C92  | 70 mA           | No          | 185M     |

# CY7B8392 10BASE-2 Ethernet Coax Transceiver Cross Reference

| Phillips/Sig |       |             |          | SSI     |                 |             |          |

|--------------|-------|-------------|----------|---------|-----------------|-------------|----------|

| Device       | ICC   | Auto<br>AUI | Distance | Device  | I <sub>CC</sub> | Auto<br>AUI | Distance |

| NE83Q92      | 35 mA | Yes         | 185M     | 78Q8392 | 130 mA          | No          | 185M     |

\* Not pin compatible; see product profile for Cypress advantages.

# **Product Cross Reference**

# **FIFO Cross Reference**

| Cypress, prefix CY |               | IDT, prefix IDT |               |                |               | Quality,       | prefix QS     | TI, prefi      |               | Sharp, prefix LH |               |

|--------------------|---------------|-----------------|---------------|----------------|---------------|----------------|---------------|----------------|---------------|------------------|---------------|

| Device             | Speed<br>(ns) | Device          | Speed<br>(ns) | Device         | Speed<br>(ns) | Device         | Speed<br>(ns) | Device         | Speed<br>(ns) | Device           | Speed<br>(ns) |

| 7C401              | 5-25**        | 72401           | 10-45**       | 67C401         | 10-35*        |                |               | ALS236         | 10-45**       |                  |               |

| 7C402              | 5-25**        | 72402           | 10-45**       | 67C402         | 10-35*        | <u> </u>       |               |                |               |                  |               |

| 7C403              | 5-25**        | 72403           | 10-45**       | 67C403         | 10-35*        |                |               | ALS234         | 10-45**       |                  |               |

| 7C404              | 5-25**        | 72404           | 10-45**       | 67C404         | 10-35*        |                |               |                |               |                  |               |

| 7C408/9            | 15-35**       |                 |               |                |               |                |               | 1              |               | 5481/91*         | 15-50         |

| 7C419              | 10-65         | 7200            | 15-65         | 7200           | 25-120        |                |               | ACT7200        | 15-50         | 5495             | 15-80         |

| 7C420/1            | 10-65         | 7201            | 15-65         | 7201           | 25-120        | 7201           | 12-120        | ACT7201        | 15-50         | 5496             | 15-80         |

| 7C424/5            | 10-65         | 7202            | 15-65         | 7202           | 15-80         | 7202           | 12-120        | ACT7202        | 15-50         | 5497             | 15-80         |

| 7C428/9            | 10-65         | 7203            | 15-65         | 7203A          | 15-80         | 7203           | 10-120        | ACT7203        | 20-50         | 5498             | 15-80         |

| 7C432/3            | 10-65         | 7204            | 15-65         | 7204A          | 15-80         | 7204           | 10-120        | ACT7204        | 20-50         | 5499             | 20-50         |

| 7C441/451          | 14-30         | 72211*          | 15-50         |                |               |                |               |                |               |                  |               |

| 7C443/453          | 14-30         | 72231*          | 15-50         |                |               |                |               |                |               | 5492*            | 25-50         |

| 7C455              | 14-30         | 72215*          | 15-50         |                |               |                |               |                |               | 540215*          | 20-50         |

| 7C457              | 14-30         | 72235*          | 15-50         |                |               |                |               |                |               |                  |               |

| 7C460              | 15-40         | 7205            | 20-50         | 7205           | 15-50         | <u> </u>       |               |                |               |                  |               |

| 7C462              | 15-40         | 7206            | 20-50         |                |               |                |               |                |               |                  |               |

| 7C462              | 15-40         | 7207            | 15-50         |                |               |                |               |                |               |                  |               |

| 7C4421             | 10-35         | 72421           | 15-50         |                |               |                |               |                |               | +                |               |

| 7C4201             | 10-35         | 72201           | 15-50         |                |               |                | <u> </u>      |                |               | +                |               |

| 7C4211             | 10-35         | 72211           | 15-50         |                |               | 72211          |               | ACT72211       | 15-50         |                  |               |

| 7C4221             | 10-35         | 72221           | 15-50         |                |               | 72221          |               | ACT72221       | 15-50         |                  |               |

| 7C4231             | 10-35         | 72231           | 15-50         |                |               | 72231          | <u> </u>      | ACT72231       | 15-50         |                  |               |

| 7C4241             | 10-35         | 72241           | 15-50         |                |               | 72241          |               | ACT72241       | 15-50         |                  |               |

| 7C4251             | 10-35         |                 |               |                | <u> </u>      |                |               |                | 10 00         |                  |               |

| 7C4261             | 10-35         |                 |               |                |               |                |               |                |               |                  |               |

| 7C4271             | 10-35         |                 |               |                |               |                |               |                |               | +                |               |

| 7C4425             | 10-35         | _               |               |                |               |                |               |                |               |                  |               |

| 7C4205             | 10-35         | 72205           | 10-50         |                |               |                |               |                |               | +                |               |

| 7C4215             | 10-35         | 72215           | 10-50         |                |               | 72215          |               |                |               |                  |               |

| 7C4225             | 10-35         | 72225           | 10-50         | ·····          |               | 72215          |               |                |               |                  |               |

| 7C4235             | 10-35         | 72235           | 10-50         |                |               |                |               |                |               | 1                |               |

| 7C4245             | 10-35         | 72245           | 10-50         |                |               | -              |               |                |               |                  |               |

| 7C4255             | 10-35         | 72213           | 10 50         |                |               |                |               |                |               |                  |               |

| 7C4265             | 10-35         |                 |               |                |               |                |               |                |               | +                |               |

| Package            | Code          | Package         | Code          | Package        | Code          | Package        | Code          | Package        | Code          | Package          | Code          |

| PLCC               | J             | PLCC            | J             | PLCC           | J             | PLCC           | JR            | PLCC           | RJ            | PLCC             | U             |

| T/PQFP             | N             | T/POFP          | PF            |                |               | +              |               | T/PQFP         | PN/PH         | +                |               |

| PDIP               | P             | PDIP            | TP            | PDIP           | R/P           | PDIP           | P/P6          | PDIP           | NP/NT         | PDIP             | D/Blank       |

| CDIP               | D             | CDIP            | D             | CDIP           | X             | CDIP           | D/D6          | CDIP           | NR/           | +                |               |

| Temp.<br>Range     | Code          | Temp.<br>Range  | Code          | Temp.<br>Range | Code          | Temp.<br>Range | Code          | Temp.<br>Range | Code          | Temp.<br>Range   | Code          |

| Com'l              | Coue          | Com'l           | Blank         | Com'l          | Coue          | Com'l          | N/A           | Com'l          | SN            | Com'l            | Coue          |

| Industrial         | I             | Industrial      |               | Industrial     | <u> </u>      | Industrial     | 11/2          | Industrial     | 514           | Industrial       |               |

| mausulai           | MB            | incustrial      | В             | mousuidi       | 1             | Imaustrial     | 1             | muustilai      |               | Incustilal       | 1             |

\* Not pin compatible; see product profile for Cypress advantages. \*\* Speed in MHz.

# **Product Cross Reference**

# **Dual Port Cross Reference**

| Cypress, p       | orefix CY     | IDT, prefix IDT |               |  |  |

|------------------|---------------|-----------------|---------------|--|--|

| Device           | Speed<br>(ns) | Device          | Speed<br>(ns) |  |  |

| 7C130/1<br>7B131 | 15-55         | 7130            | 20-100        |  |  |

| 7C132            | 25-55         | 7132            | 20-100        |  |  |

| 7C133            | 15-55         | 7133            | 25-90         |  |  |

| 7C136<br>7B136   | 15-55         | 71321           | 25-55         |  |  |

| 7C140/1<br>7B141 | 15-55         | 7140            | 20-100        |  |  |

| 7C142            | 25-55         | 7142            | 20-100        |  |  |

| 7C143            | 15-55         | 7143            | 25-90         |  |  |

| 7C146<br>7B146   | 15-55         | 71421           | 25-55         |  |  |

| 7B134 /5         | 15-35         | 7134            | 25-70         |  |  |

| 7B1342           | 15-35         | 71342           | 25-70         |  |  |

| 7B144            | 15-35         | 7005            | 25-70         |  |  |

| 7C024            | 15-55         | 7024            | 20-70         |  |  |

| 7C025            | 15-55         | 7025            | 20-70         |  |  |

| 7C006            | 15-55         | 7006            | 25-70         |  |  |

| 7C016            | 15-55         | 7016            | 15-70         |  |  |

| 7C0241           | 15-55         |                 |               |  |  |

| 7C0251           | 15-55         |                 |               |  |  |

| 7B145            | 15-55         | 7015            | 20-70         |  |  |

| Package          | Code          | Package         | Code          |  |  |

| PLCC             | J             | PLCC            | J             |  |  |

| PDIP             | Р             | PDIP            | Р             |  |  |

| CDIP             | D             | CDIP            | D             |  |  |

| Temp.<br>Range   | Code          | Temp.<br>Range  | Code          |  |  |

| Com'l            | С             | Com'l           | Blank         |  |  |

| Industrial       | I             | Industrial      |               |  |  |

| Military         | MB            | Military        | В             |  |  |

\* Not pin compatible; see product profile for Cypress advantages. \*\* Speed in MHz.

# Cypress Semiconductor Bulletin Board System (BBS) Announcement

Cypress Semiconductor supports a 24-hour electronic Bulletin Board System (BBS) that allows Cypress Applications to better serve our customers by allowing them to transfer files to and from the BBS.

The BBS is set up to serve in multiple ways. One of its purposes is to allow customers to receive the most recent versions of Cypress programming software. Another is to allow the customers to send PLD programming files that they are having trouble with to the BBS. Cypress Applications can then find the errors in the files, correct them, and place them back on the BBS for the customer to download. The customer may also ask questions in our open forum message area. The sysop (system operator) will forward these questions to the appropriate applications engineer for an answer. The answers then get posted back into the forum.

# **Communications Set-Up**

The BBS uses USRobotics HST Dual Standard modems capable of 14.4-Kbaud rates without compression and rates upwards of 19.2-Kbaud with compression. It is compatible with CCITT V.32 bis, V.32, V.22 (2400-baud), Bell 212A (1200-baud), CCITT V.42, and CCITT V.42 bis. It also handles MNP levels 2, 3, 4, and 5.

To call the BBS, set your communication package parameters as follows:

Baud Rate:

Rate: 1200 baud to 19.2 Kbaud. Max. is determined by your modem. Data Bits: 8 Parity: None (N) Stop Bits: 1

In the U.S. the phone number for the BBS is (408) 943–2954. In Japan the BBS number is 81-423-69-8220. In Europe the BBS number is 49-810-62-2675. These numbers are for transmitting data only.

If the line is busy, please retry at a later time. When you access the BBS, an initial screen with the following statement will appear:

Rybbs Bulletin Board

After you choose the graphics format you want to use, the system will ask for your first and last name. If you are a first-time user, you will be asked a few questions for the purposes of registration. Otherwise you will be asked for your password, and then you will be logged onto the BBS, which is completely menu driven.

# **Downloading Application Notes and Datasheets**

A complete listing of files that may be downloaded is included on the BBS. Application notes are available for downloading in two formats, PCL and Postscript  $^{\mathbb{M}}$ . An "hp" in front of the file name indicates it is a PCL file and can be downloaded to Hewlett-Packard LaserJets  $^{\mathbb{M}}$  and compatible printers. Files without the hp preceding them are in Postscript and can be downloaded to any Postscript printer.

If you have any problems or questions regarding the BBS, please contact Cypress Applications at (408) 943-2821 (voice).

Postscript is a trademark of Adobe Corporation. LaserJet is a trademark of Hewlett Packard Corporation.

# Ethernet

# Page Number

| Device Number     | Description                                            |

|-------------------|--------------------------------------------------------|

| CY7C971           | 100BASE-T4/10BASE-T Fast Ethernet Transceiver (CAT 3)  |

| CY7B8392          | Ethernet Coax Transceiver Interface                    |

| CY7B4663          | Integrated 10BASE-FL Ethernet Transceiver 2-31         |

| Application Notes |                                                        |

| CY7B8392          | Low Power Ethernet Coaxial Transceiver Application     |

| CY7C971           | 100BASE-T4/10BASE-T Ethernet Transceiver Application   |

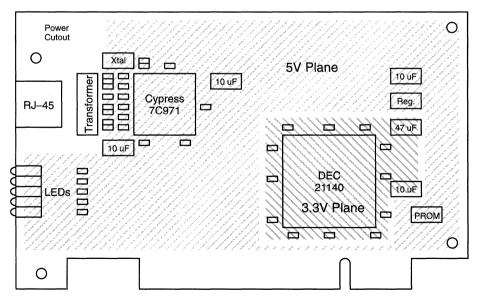

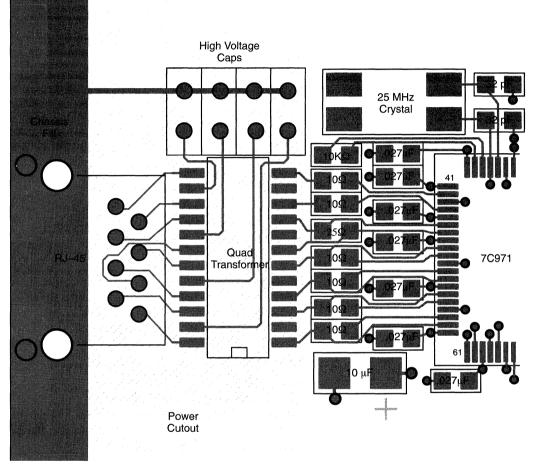

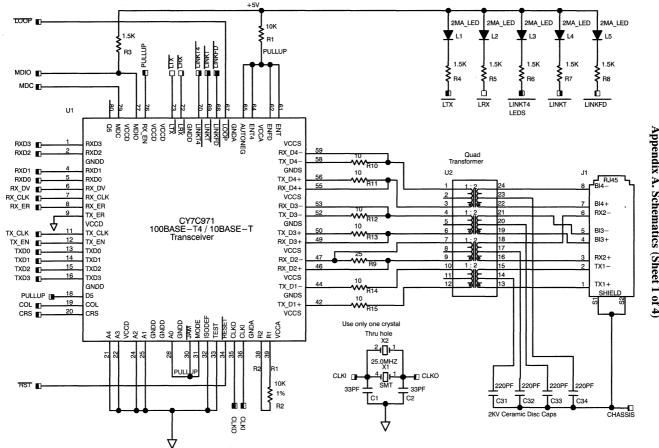

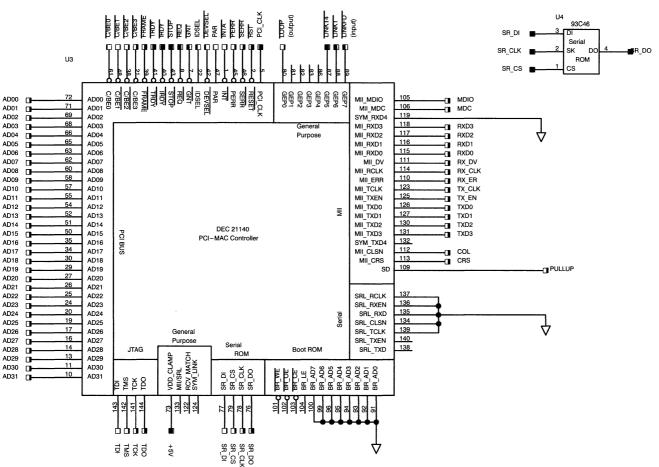

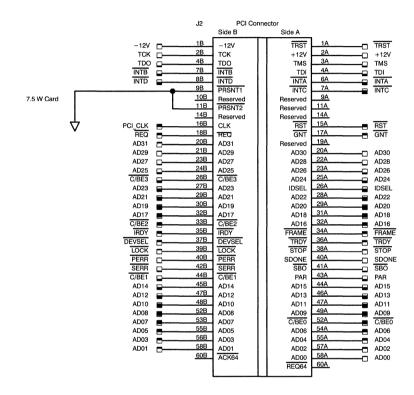

| CY7C971           | 100BASE-T4 /10BASE-T Ethernet PCI Network Adapter 2-55 |

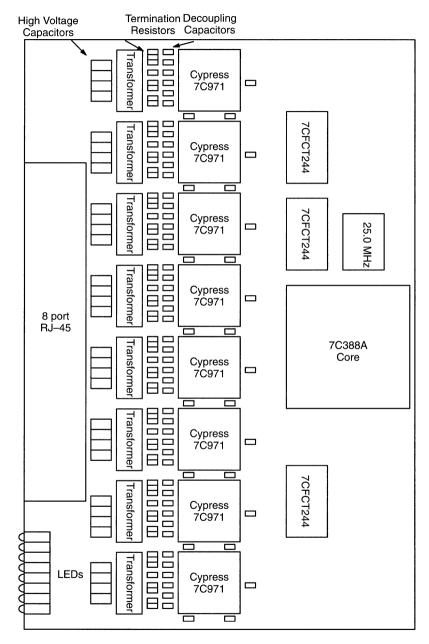

| CY7C971/CY7C388P  | 100BASE-T4 Ethernet Repeater                           |

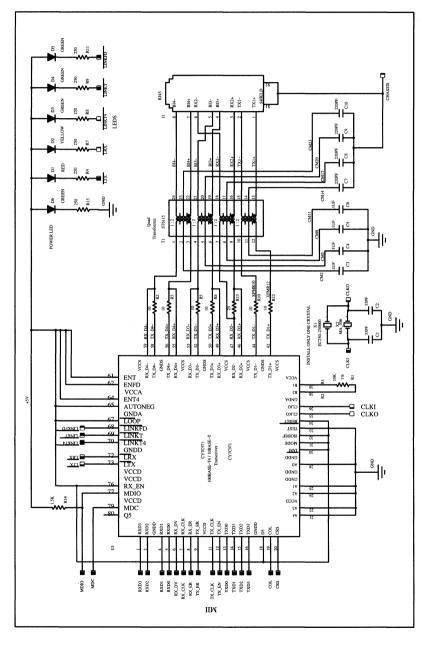

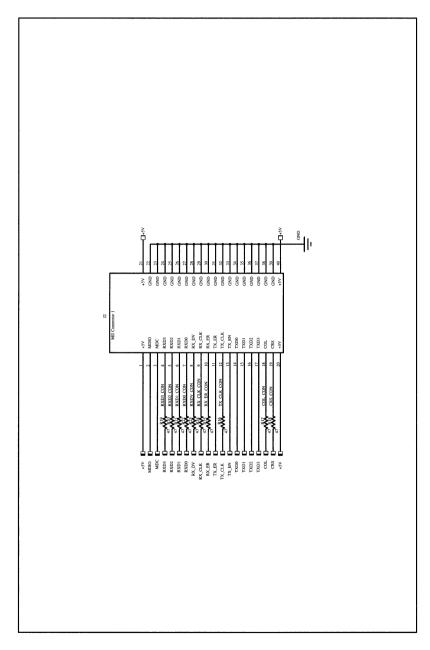

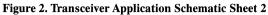

PRELIMINARY CY7C971

# 100BASE-T4/10BASE-T Fast Ethernet Transceiver (CAT 3)

# Features

- Complies with IEEE 802.3u draft standard

- Three operating modes:

- 10BASE-T Full Duplex

- 10BASE-T

- Media Independent Interface (MII)

- Three-state receive port

- Serial management port

- Auto-Negotiation

- On-chip transmit wave shaper

- Receive filter and adaptive equalization

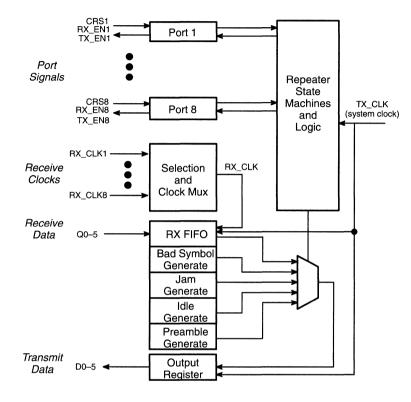

- PMA Interface for repeater applications

- Jam function for hub applications

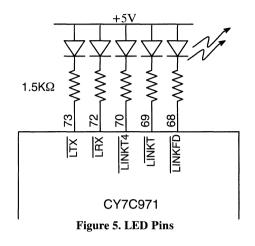

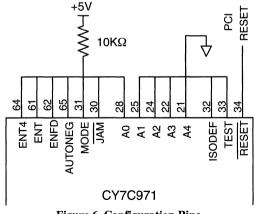

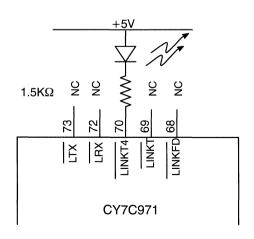

- LED status indicators: TX, RX, Link

- Loopback mode for PHY integrity testing

- Auto-polarity correction

- Low-power CMOS

- 80-pin PQFP

# **Functional Description**

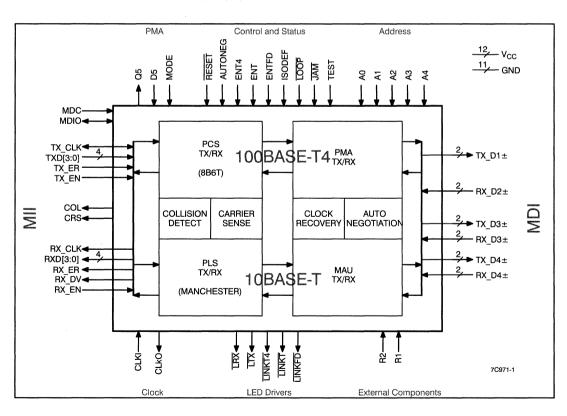

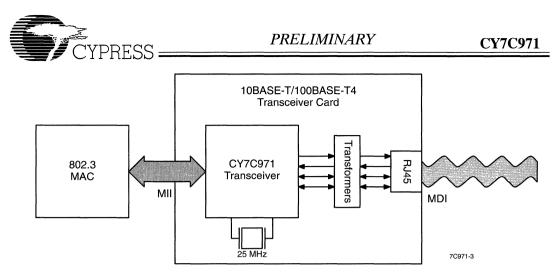

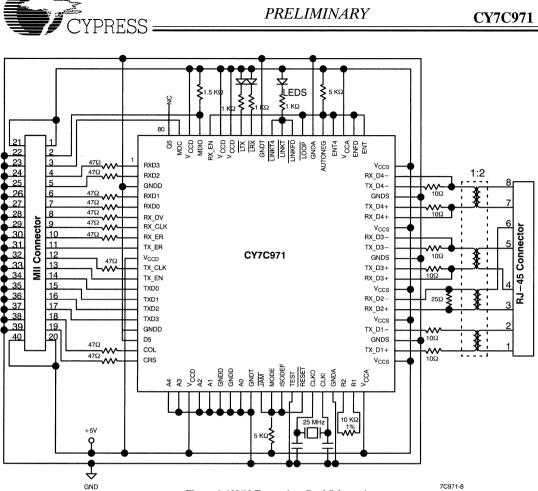

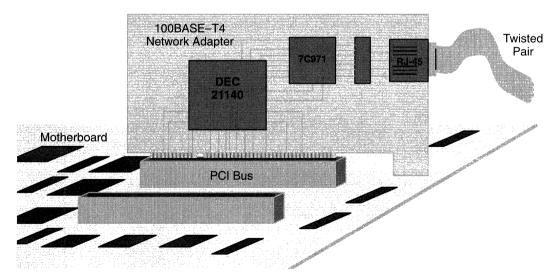

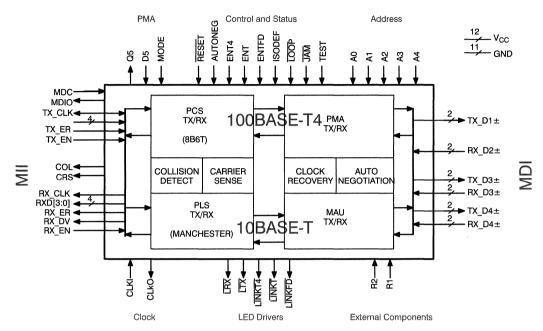

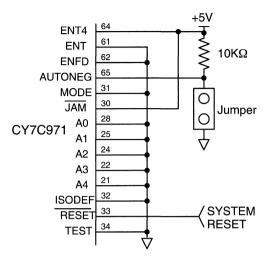

The CY7C971 is a full featured physical layer transceiver (PHY) device supporting both 100BASE-T4 (Fast Ethernet) and 10BASE-T Local Area Network (LAN) standards. The CY7C971 complies with IEEE 802.3 100BASE-T4, 10BASE-T, MII, and Auto-Negotiation standards for twisted pair interfaces.

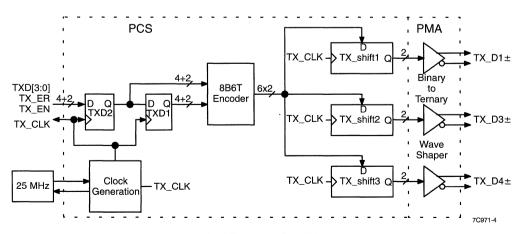

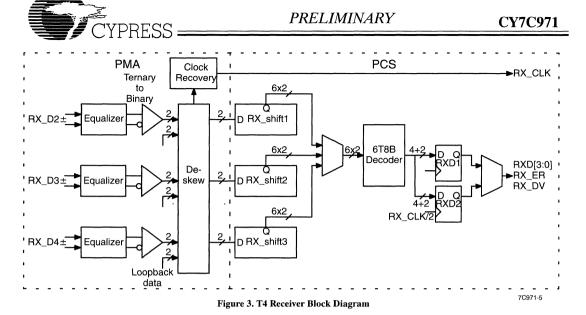

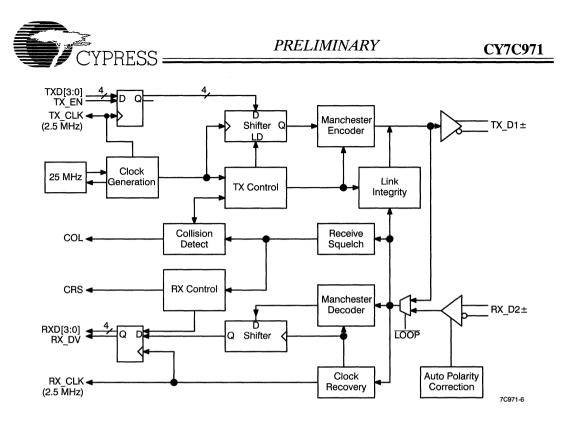

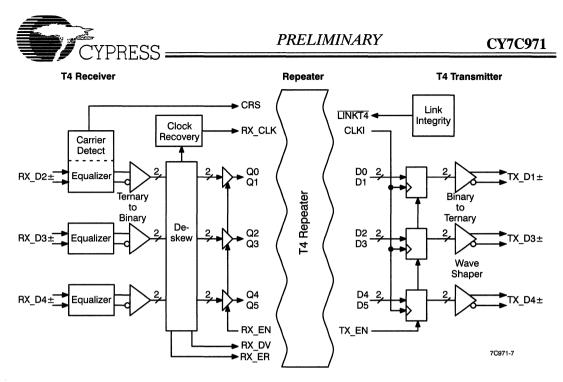

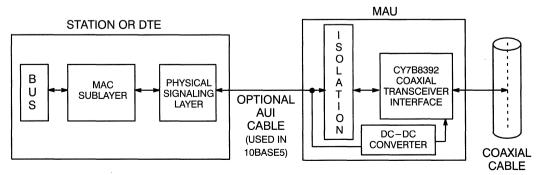

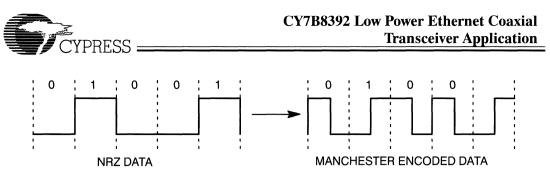

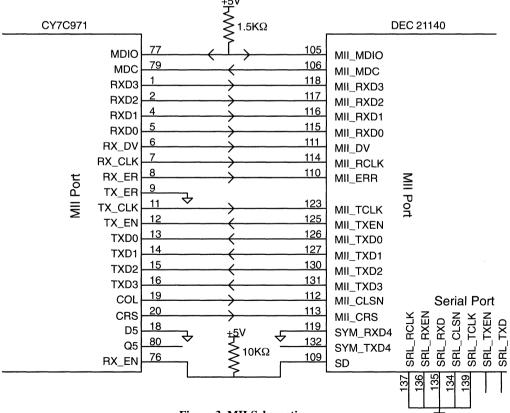

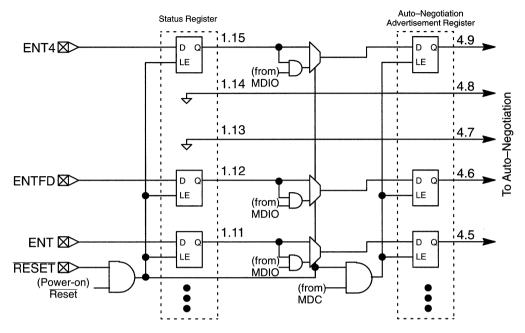

The CY7C971 interfaces to category 3, 4, or 5 unshielded twisted-pair cable through its Media Dependent Interface (MDI). The Media Independent Interface (MII) attaches directly to Media Access Control (MAC) layer devices. The CY7C971 performs the Physical Coding Sublayer (PCS), Physical Layer Signalling (PLS), Physical Media Attachment (PMÀ), and Media Attachment Unit (MAU) functions defined in the 802.3 standard. Ethernet frames are transferred from the MAC to the CY7C971 over the MII interface. The data is encoded in the PCS or PLS encoder (8B6T for 100BASE-T4 or Manchester for 10BASE-T) and then passed to the PMA or MAU where the encoded data is shifted bitwise on to the twisted-pair media. Collision and Carrier Sense signals are generated by the CY7C971 and passed to the MAC over the MII.

The CY7C971 PHY uses 802.3 standard Auto Negotiation to configure the link. The PHY includes a direct interface to the PMA layer for repeater applications.

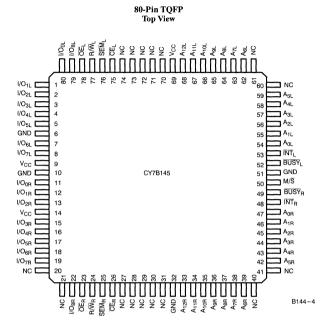

CY7C971

**Pin Configuration**

# **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature $\dots -65^{\circ}C$ to $+150^{\circ}C$ |

|-------------------------------------------------------------|

| Ambient Temperature with<br>Power Applied                   |

| Supply Voltage to Ground Potential $\dots -0.5V$ to $+7.0V$ |

| DC Voltage Applied to Outputs                               |

| in High Z State $-0.5V$ to $+7.0V$                          |

| DC Input Voltage                                            |

| Static Discharge Voltage       | >2001V  |

|--------------------------------|---------|

| (per MIL-STD-883, Method 3015) |         |

| Latch-Up Current               | >200 mA |

# **Operating Range**

| Range      | Ambient<br>Temperature           | V <sub>CC</sub> |  |

|------------|----------------------------------|-----------------|--|

| Commercial | $0^{\circ}$ C to $+70^{\circ}$ C | $5V \pm 10\%$   |  |

# CY7C971

Pin Descriptions Media Independent Interface (MII)

| Name                 | I/O                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXD[3:0]<br>(D[3:0]) | Input<br>(TTL)                         | Transmit Data. TXD[3:0] are the data signals that carry the Ethernet transmit frame data from the MAC to the PHY on a nibble basis. TXD[3:0] are sampled on the rising edge of TX_CLK when TX_EN is asserted HIGH. In PMA mode, these pins become the D[3:0] pins used for passing binary encoded 8B6T symbols to the PMA sublayer.                                                                                                                                                                    |