# PARALLEL NETWORK PROCESSOR

## Proposal

for

## PARALLEL NETWORK PROCESSOR

Negotiation No. J0417

14 August 1964

Prepared

for

UNIVERSITY OF CALIFORNIA Lawrence Radiation Laboratory Livermore, California

by

WESTINGHOUSE DEFENSE AND SPACE CENTER

Aerospace Division

Baltimore, Maryland

COMPANY

PROPRIETARY INFORMATION

## TABLE OF CONTENTS

|                                       | Page |

|---------------------------------------|------|

| 1. INTRODUCTION AND SUMMARY           | 1-1  |

| 2. TECHNICAL SECTION                  | 2-1  |

| 2.1 General Description of SOLOMON II | 2-1  |

| 2.2 System Design Refinements         | 2-3  |

| 2.2.1 PE-Memory Interface             | 2-3  |

| 2.2.2 PE Design                       | 2-4  |

| 2. 2. 3 Network Control Unit Design   | 2-29 |

| 2.2.4 Network Sequencing Unit         | 2-33 |

| 2.2.5 PE Network Design               | 2-34 |

| 2.2.6 Console                         | 2-36 |

| 2.3 Memory System                     | 2-39 |

| 2.3.1 1-Microsecond Memory Breadboard | 2-39 |

| 2.3.2 Molecular Sense Amplifiers      | 2-40 |

| 2.4 Power System                      | 2-41 |

| 2.5 Packaging                         | 2-43 |

| 2.6 Reliability                       | 2-46 |

| 2.7 Software                          | 2-50 |

| 2.7.1 Scope of Work                   | 2-50 |

| 2.7.2 Diagnostic Programs             | 2-50 |

| 2.7.3 Functional Assembly System      | 2-51 |

| 2.7.4 Simulation Program              | 2-51 |

| 2.7.5 Documentation                   | 2-52 |

| 2.8 Growth Potential                  | 2-52 |

|                                               | Page |

|-----------------------------------------------|------|

| 3. MANAGEMENT                                 | 3-1  |

| 3.1 SOLOMON Experience                        | 3-1  |

| 3.1.1 SOLOMON Program Contracts               | 3-1  |

| 3. 1. 2 Internally Sponsored SOLOMON Studies  | 3-4  |

| 3.2 Project Organization and Personnel        | 3-6  |

| 3.3 Schedule                                  | 3-29 |

| 3.3.1 Hardware Milestones                     | 3-29 |

| 3.3.2 Programming Milestones                  | 3-31 |

| 3.4 Related Experience and Facilities         | 3-33 |

| 3.4.1 Computer Experience                     | 3-33 |

| 3.4.2 Facilities                              | 3-39 |

| 3.5 Reliability and Quality Assurance Control | 3-44 |

| 3.5.1 Parts Selection and Control             | 3-45 |

| 3.5.2 Design                                  | 3-46 |

| 3.5.3 Quality Assurance Program               | 3-46 |

| 3.5.4 Reliability Analysis                    | 3-48 |

| 3.6 Subcontractor Selection                   | 3-48 |

| 3.6.1 RFP Preparation                         | 3-48 |

| 3. 6. 2 Selection of Bidders                  | 3-49 |

| 3.6.3 Evaluation of Proposals                 | 3-52 |

| 3. 6. 4 Selection of Subcontract Type         | 3-52 |

| 3.6.5 Negotiation                             | 3-53 |

| 3. 6. 6. Subcontract Control                  | 3-53 |

## LIST OF ILLUSTRATIONS

| Figure |                                                                             | Page |

|--------|-----------------------------------------------------------------------------|------|

| 2-1    | PE-PEM Interface for Previous 256-PE Module                                 | 2-4  |

| 2-2    | PE-PEM Interface for Present 32-PE Module                                   | 2-5  |

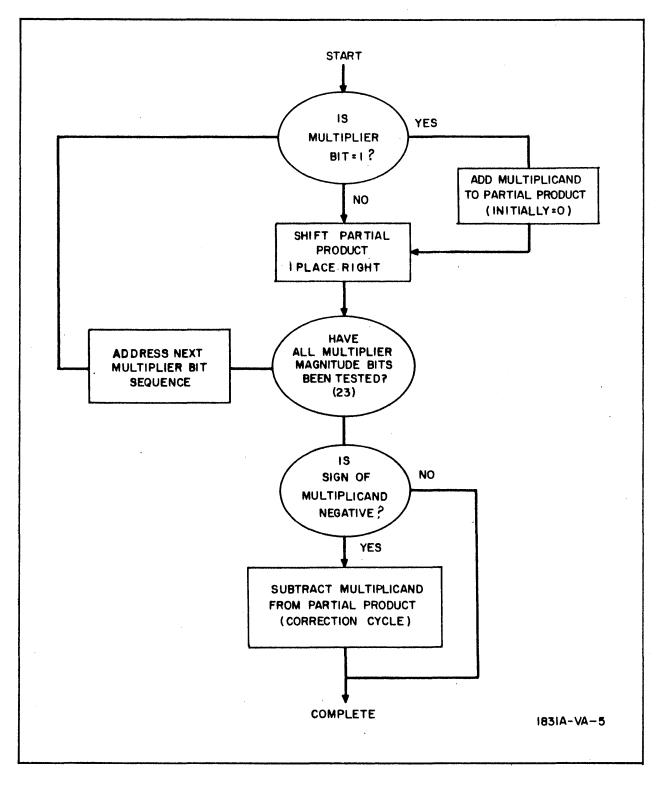

| 2-3    | Basic Multiply Algorithm                                                    | 2-14 |

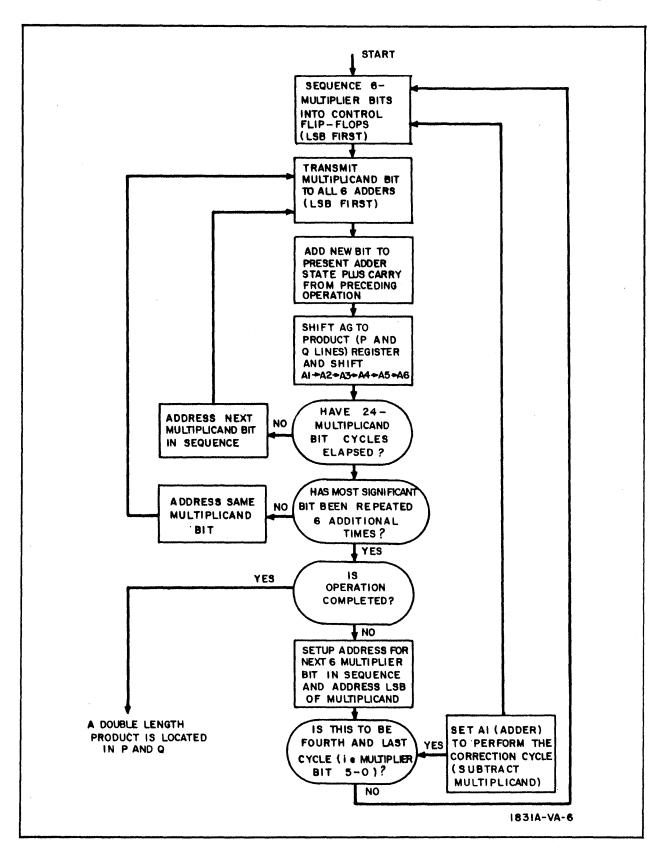

| 2-4    | Logical Sequence of SOLOMON II Premultiply Scheme                           | 2-15 |

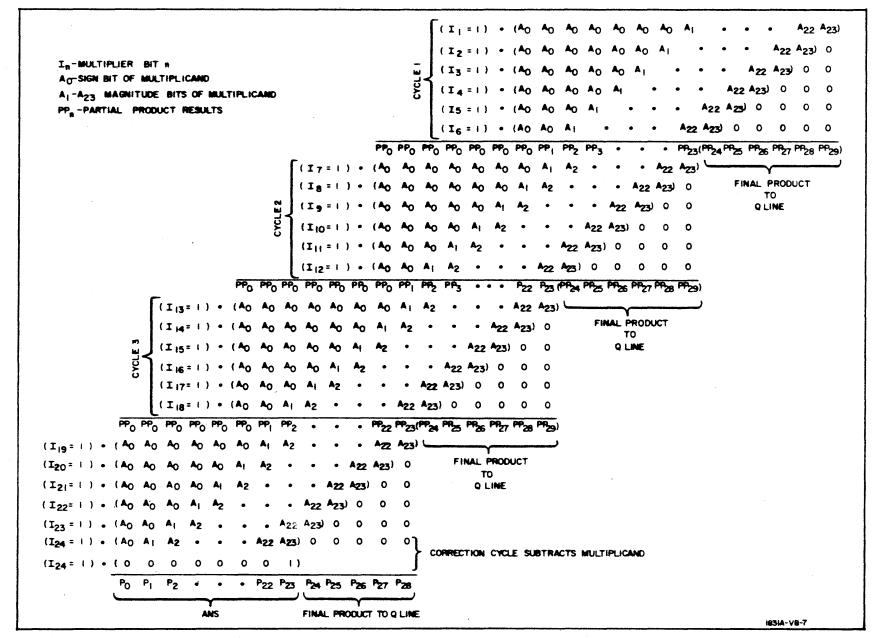

| 2-5    | SOLOMON PE Logical Representation of Multiply Sequence                      | 2-16 |

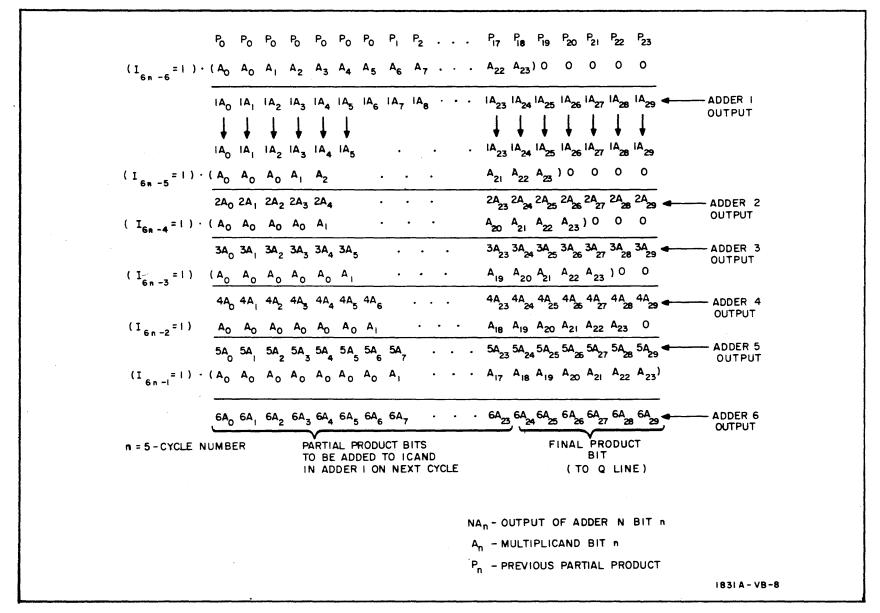

| 2-6    | SOLOMON PE Multiply Sequence, 1 Cycle                                       | 2-17 |

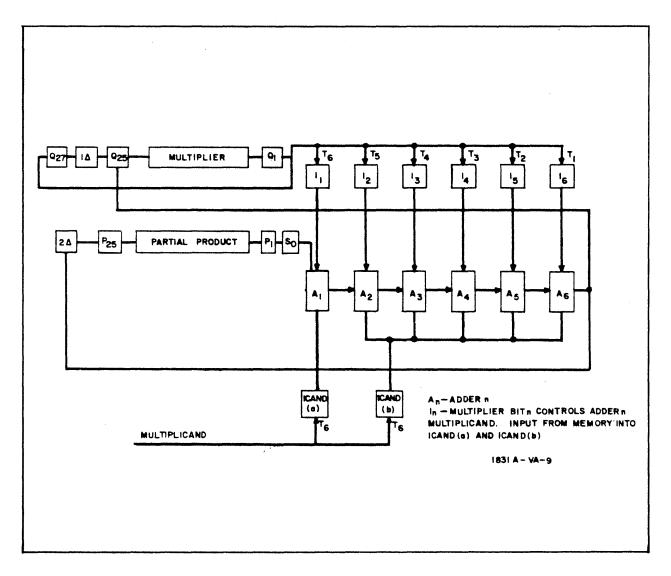

| 2-7    | SOLOMON II PE Multiply Hardware (Block Diagram)                             | 2-18 |

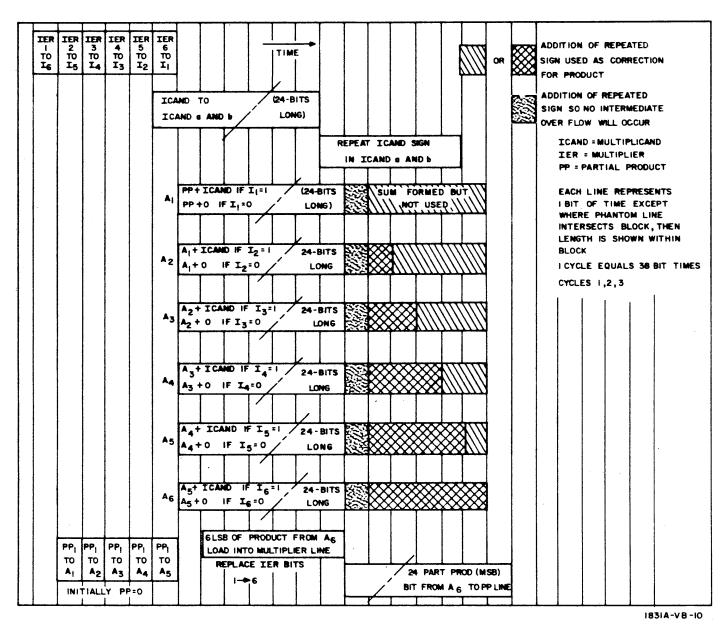

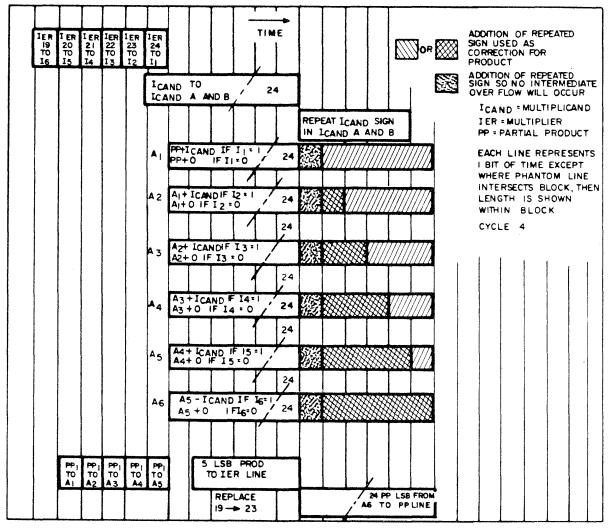

| 2-8    | Multiply Instruction Timing                                                 | 2-19 |

| 2-9    | Multiply Instruction Timing                                                 | 2-20 |

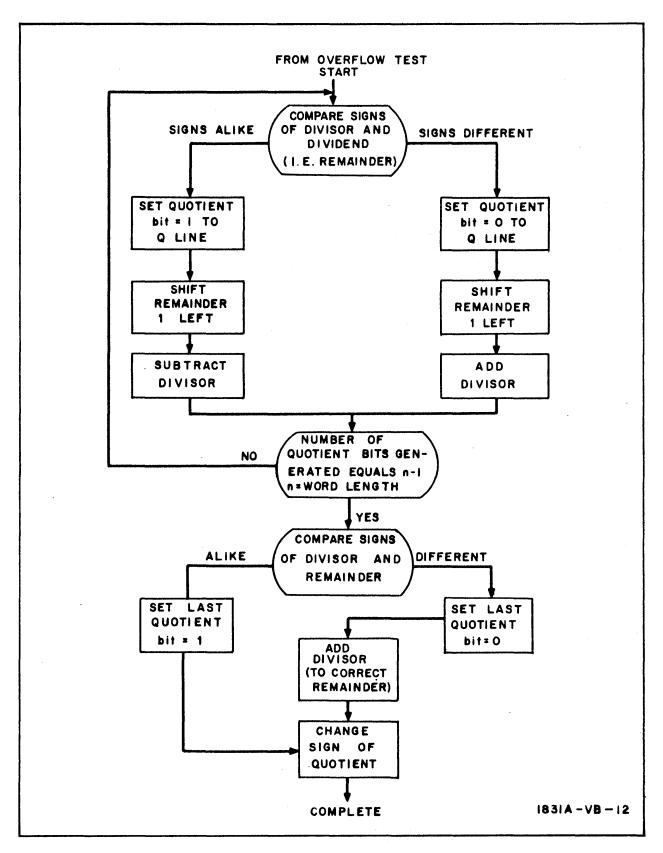

| 2-10   | Divide Alogrithm                                                            | 2-23 |

| 2-11   | PE Divide Hardware (Block Diagram)                                          | 2-24 |

| 2-12   | Divide Overflow Test                                                        | 2-27 |

| 2-13   | PE Network Signal Distribution                                              | 2-35 |

| 2-13A  | Main Power Bus End View                                                     | 2-44 |

| 2-14   | Packaging Arrangement                                                       | 2-45 |

| 2-15   | Cabinet Arrangement                                                         | 2-46 |

| 2-16   | System Layout                                                               | 2-47 |

| 2-17   | Routing Paths                                                               | 2-48 |

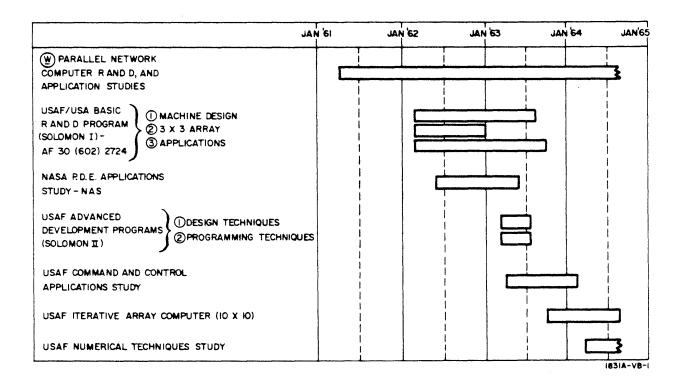

| 3-1    | Westinghouse - SOLOMON Chronology                                           | 3-2  |

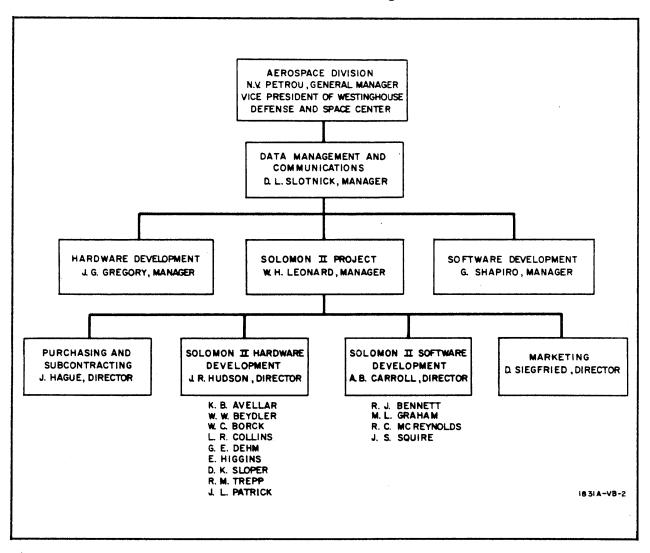

| 3-2    | SOLOMON II Project Organization                                             | 3-7  |

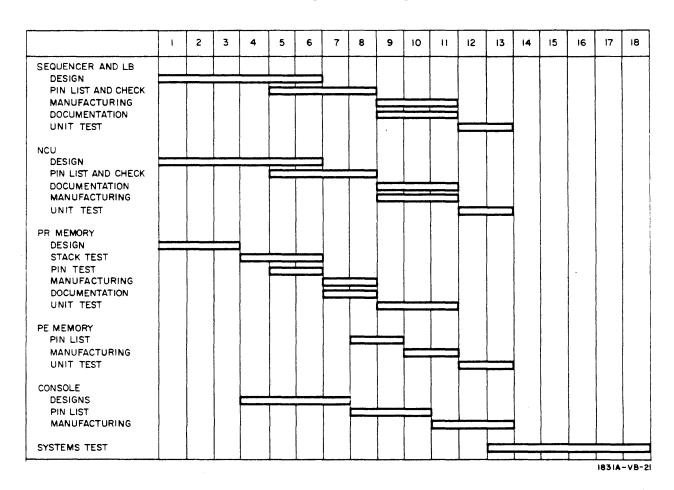

| 3-3    | SOLOMON II Hardware Schedule                                                | 3-29 |

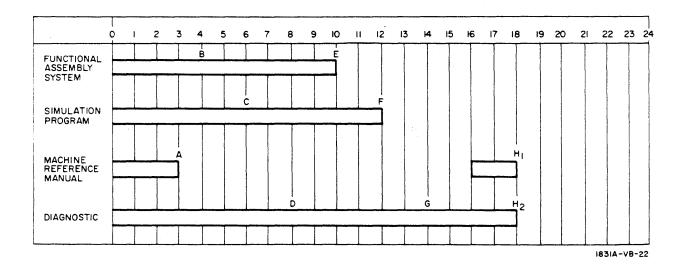

| 3-4    | SOLOMON II Software Schedule                                                | 3-30 |

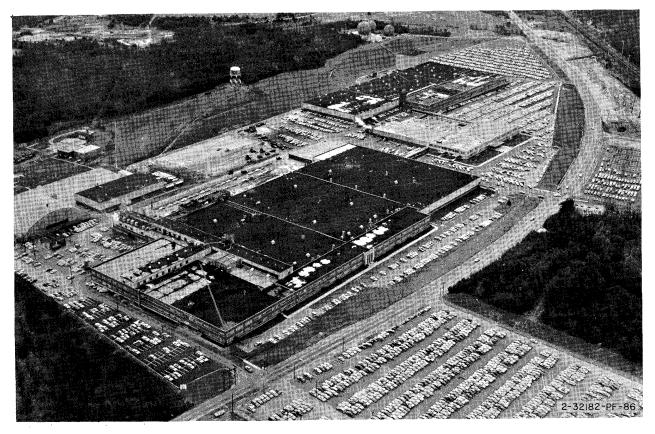

| 3-5    | Westinghouse Defense and Space Center, Aerospace Division in the Foreground | 3-40 |

#### 1. INTRODUCTION AND SUMMARY

In response to the stated requirement of the Lawrence Radiation Laboratory for a Parallel Network Processor, Westinghouse Electric Corporation is pleased to submit a proposed program which it is believed will result in filling this requirement in minimum time and with highest performance/cost ratio. This program consists of two phases: a development phase during which all remaining design questions are resolved and each system element fabricated and tested and a production phase which produces sufficient additional, identical units to build the phase 1 system up to operational size.

The basic design of the parallel network computing system known as SOLOMON II was developed by the Westinghouse Electric Corporation under USAF contract AF30(602)3417, Multiple Processing Techniques. Since the completion of this contractual effort Westinghouse has continued the design and development of the Parallel Network Processor (SOLOMON II) System, under corporate sponsorship, resulting in a substantial number of design refinements. As a result the Parallel Network Processor System described in this proposal is a more complete, better defined, and functionally improved machine design than that previously reported in the referenced AF report.

A number of developmental areas still remain in the machine design, but these are well defined, and several reasonable solutions for each are available for final cost-effectiveness determination during phase 1 of the program. Examples of some of the more important design areas that have not yet been resolved are: external interfaces with the SOLOMON II system, diagnostics, maintenance, power distribution and packaging.

Section 2, the technical portion of this proposal concentrates on the design refinements that have been made since the above-cited AF report was prepared. Following a brief basic functional description of the overall system, each major system element is described in detail.

Section 3, Management, presents relevant background and details the proposed Westinghouse phase 1 program.

#### 2. TECHNICAL SECTION

#### 2.1 GENERAL DESCRIPTION OF SOLOMON II

The parallel network of processing elements (PE network) making up the majority of the computation capability of the SOLOMON II system consists of a set of bit-serial arithmetic units controlled by a common source referred to as the network sequence unit (NSU). Each processing element has a unique block of core memory containing 32768 bits referred to as the processing element memory (PEM). The PEM provides bit-serial access in the form of 24-bit words to all PEs simultaneously.

The PEs are arranged in a matrix with a serial data path connecting each PE with the four neighboring PEs. This arrangment provides each PE with access to its own block of memory (referred to as internal memory) and the memories of its four nearest neighbors. The steering of data between PEs and PEM is referred to as data routing. Routing applies only to the reading of data, the PE can write only into its internal memory.

The data paths and the execution of instruction in the PE network are under the control of the NSU and the multimodal status capability of the PE. The NSU supplies the memory address and the control signals for executing all network instructions. The PE mode control determines if the PE is to execute the instruction by comparing the mode value (MV) stored in the PE with program mode control bits from the NSU. The PE mode value capability is provided by a 2-bit (4 state) register in each PE that can be unconditionally set by the NSU, conditionally set on the results of an instruction, stored in PEM, or loaded from PEM. Another condition may also be used to determine if the PE is to execute an instruction. This control is referred to as the "geometric control." Associated with each column and row of the PE network is a control line that must be high for the PEs of that column or row to

execute an instruction. These control lines are referred to as geometric column control and geometric row control, and are connected to two registers (GCR and GRR) which can be modified under a program control. One, both, or neither of these registers can be used to control the PE network on any given instruction. For a PE to execute an instruction GCR, GRR and mode values for that PE must correspond to the selected states in the instruction being executed. When these conditions are satisfied the PE is said to be active and will perform the current instruction. In addition to the data paths between PEs and the PEM mentioned, each PE has a data path to a register that is common to all PEs, a data path that is common to all PEs is a row, and a path that is common to all PEs in a column. These registers are referred to as the "broadcast register" (BR), "L buffer column (LC), and "L buffer row" (LR). BR, LC and LR are two-way data paths controlled by the NSU. The broadcast register functionally is the OR of all the PE accumulators if output is specified, and the source of a common operand for all PEs if input is specified. Transfers between BR and PE are conditional on the PE being active. The LC path is the OR of all PE accumulators of a column of PEs on a one column at a time basis if output is specified, and the source of an operand common to the column if input is specified. The same rules apply for LR transfers in the row direction of the network. Both L buffer transfers are conditional on the PE being active.

The L buffer is a set of registers 24 bits in length that can be loaded bitserial or word (24 bits) parallel. The number of registers in the L buffer corresponds to one dimension of the PE network. This unit allows data from a parallel memory to be transferred to serial memory.

The word parallel memory in the system is referred to as the program memory (PRM), and is used to store instructions and additional data. The LB-PRM combination allows data to be organized by a conventional sequential processor and transferred to the network. It also allows conventional input-output (I-O) devices to be attached to the system. Only data is transferred between the PRM and the network via the LB. Between the NSU and the PRM is a conventional

sequential control unit referred to as the network control unit (NCU). The NCU is used to process instructions before transferring them to the NSU for execution. The NCU performs functions such as indexing (program modification), input-output control, predecoding of instructions, and loading, storing, and sampling NSU registers.

The set of NSU registers and indicators accessible by the NCU are: BR, GCR, GRR, and the indicator register (IDR). The indicator register is used to test network status; overflow, none, one, or more than one PE active on an instruction and busy conditions in the NSU and PE network.

#### 2.2 SYSTEM DESIGN REFINEMENTS

This paragraph presents refinements in the proposed configuration from that reported in the final report submitted under USAF/RADC Contract AF30(602)3417.

#### 2.2.1 PE-Memory Interface

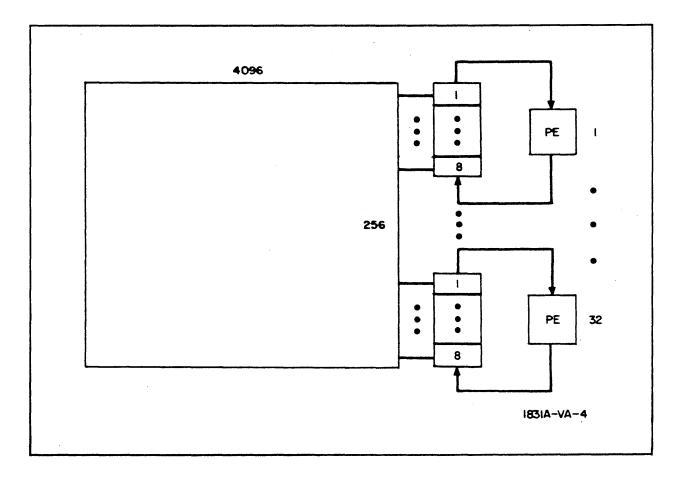

The PEM system described in the AF report has been reorganized to allow greater flexibility in network size. This alteration has also significantly reduced the electrical problems of transmitting data between the network and the memory. The earlier PEM system required 8 memories for each module of 256 PEs. Each PE was connected to one bit position of eight 256 x 4096 bit memory banks via a collection gate illustrated in figure 2-1.

In the current memory interface design one 256 x 4096 bit memory is connected to 32 PEs via a shift register. The contents of the 256-bit memory read/write register is gated in parallel to a 256-bit shift register. Each PE is assigned an 8-bit segment of the shift register which allows a 1-microsecond memory to supply 32 PEs with data at an 8-mc rate (figure 2-2). This implementation allows a system to be built up of blocks of 32 PEs rather than 256. It also allows the memories to be placed much nearer the PE network which significantly reduces length of the communication path.

The implementation of the L buffer, geometric control registers, and NSU signal driver to the network has been modified to allow these items to be expanded as blocks of 32 PEs are added to a system.

Figure 2-1. PE-PEM Interface for Previous 256-PE Module

#### 2.2.2 PE Design

Since the majority of the components, cost, and complexity in the SOLOMON system is in the PE network, much effort has gone into optimizing and minimizing the PEs themselves. A basic change has been made in the PE design to permit operation with 24-bit words in lieu of 20-bit words as was specified in the AF report. To maintain compatibility with this basic change and to provide a safety factor in circuit requirements and NSU signal distribution tolerances, an 8-mc logic system rate has been chosen. The PE logic design itself has undergone some beneficial evolution due primarily to the ability to modularize the PE network on the basis of 32 rather than 256, and the concurrent PEM design improvements outlined in the preceding paragraph. The algorithms and actual manipulations involved in performing instructions have been slightly modified in several cases to take advantage of the aforementioned

Figure 2-2. PE-PEM Interface for Present 32-PE Module

improvements in the basic PE network structure. Table 2-1 indicates complete instruction operating times (including fetch or storage of operands) for the current SOLOMON II system. In cases where major alogrithm or functional changes have occurred the present system is described in detail for each instruction in the following paragraphs.

#### 2.2.2.1 PE Instructions

Due to the large number of multiply operations in mesh calculations and similar problems, intensive efforts have been made to arrive at an efficient multiply capability. Design studies have shown that a number of adders connected in series is the best way to gain speed in this operation in a basic serial structure. All applicable and promising techniques were analyzed to determine the best cost versus performance ratios.

TABLE 2-1

PE OPERATION TIMES

| Command Description                                 | Time (µsec) |

|-----------------------------------------------------|-------------|

| Multiply                                            | 19.1        |

| Any compare                                         | 3.8         |

| Any command that writes into memory                 | 3. 8        |

| Divide                                              | 84.6        |

| Shifts:                                             |             |

| l. single length left circular $\geq 12$            | 12.8        |

| 2. single length left circular < 12                 | 6.4         |

| 3. single length left algebraic ≥ 12                | 6.5         |

| 4. single length left algebraic < 12                | 3.3         |

| <ol> <li>single length left logical ≥ 12</li> </ol> | 6.5         |

| 6. single length left logical < 12                  | 3.3         |

| 7. single length right algebraic $\geq 12$          | 6. 2        |

| 8. single length right algebraic < 12               | 9.4         |

| 9. single length right logical $\geq 12$            | 6.2         |

| 10. single length right logical < 12                | 9.4         |

| 11. double length left algebraic $\geq$ 12          | 13.5        |

| 12. double length left algebraic < 12               | 6.8         |

| 13. double length left logical $\geq$ 12            | 13.3        |

| 14. double length left logical < 12                 | 6.6         |

| 15. double length right algebraic ≥ 12              | 9.8         |

| 16. double length right algebraic < 12              | 16.4        |

| 17. double length right logical $\geq$ 12           | 16. 1       |

| 18. double length right logical < 12                | 9.6         |

| All other commands                                  | 3.4         |

Two multiply techniques were selected and evaluated in detail and their cost and speed charted. Scheme A was that scheme used in the 10-mc PE described in the AF report, and Scheme B is described later in this section.

Also, a two-bit multiply scheme for each adder was costed and the speed charted. Table 2-2 shows this cost breakdown with the speeds in the adjacent column. It was finally decided that Scheme B with 6 adders would be used in SOLOMON II. Furthermore, a cost decrease for the system was realized in that the multiplicand could come from memory through four separate accesses and thereby save one of the delay lines in the PE.

TABLE 2-2

SUMMARY CHART-PE MULTIPLY COST/EFFECTIVENESS

| Mul<br>Time<br>(µsec) | LOGIC COST FACTOR | Scheme                                                 |

|-----------------------|-------------------|--------------------------------------------------------|

| 31.0                  | 430               | 3 x 1 B                                                |

| 28.6                  | 480               | 3 x 1 A                                                |

| 25.0                  | 560               | 4 x 1 B                                                |

| 22.5                  | 640               | 4 x 1 A                                                |

| 19.1                  | 800               | 6 x 1 B                                                |

| 17.0                  | 920               | 6 x 1 A                                                |

| 16.0                  | 1070              | 8 x 1 B                                                |

| 14.0                  | 1200              | 4 x 2 A                                                |

| 13.0                  | 1550              | 6 x 2 B                                                |

| 11.8                  | 1800              | 6 x 2 A                                                |

| (for 24 bit<br>words) | (per PE)          | (No. of ad-<br>ders times<br>No. of bits<br>at a time) |

<sup>\*</sup> Additional Logic cost for the rest of the PE in all schemes is approximately \$1200 (cost for PE multiply with 5 adders as in 10 mc AF report system is approximately \$680).

After the multiply scheme was decided upon and designed, the basic gates for the add, Boolean mode control, etc, instructions were added. Divide was then designed and finally the shift instruction was added. Here again as in multiply considerable investigation was done to determine how shift would be

implemented. Using scheme l as a basis for hardware count, 6 schemes were costed and the corresponding shift times calculated. After careful analysis (summarized in table 2-3) it was decided that scheme l would be the most satisfactory solution. Scheme l is discussed in more detail below.

TABLE 2-3

SHIFT INSTRUCTION ANALYSIS

| Shift Scheme                                                                                                                            | Extra PE Hardware                                |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 1. L shift < 13 3.3 μsec<br>L shift ≥ 13 6.6 μsec<br>R shift < 13 9.8 μsec<br>R shift ≥ 13 6.6 μsec                                     | No hardware                                      |

| 2. L shift < 13 3.3 μsec<br>L shift ≥ 13 3.3 μsec<br>R shift < 13 6.6 μsec<br>R shift ≥ 13 6.6 μsec                                     | 2-5 bit delays<br>1-2 bit delays<br>2-diode cans |

| 3. L shift < 13 3.3 μsec R shift < 13 4.9 μsec Two commands for shift ≥ 13 μsec                                                         | 3-5 bit delays<br>1-2 bit delays<br>2-diode cans |

| 4. L shift < 13 8.0 μsec L shift ≥ 13 8.0 μsec R shift < 13 8.0 μsec R shift ≥ 13 8.0 μsec                                              | Save: 2 diode cans<br>1-2 bit delay              |

| Uses 2 fixed memory location                                                                                                            |                                                  |

| 5. L shift < 13 3.3 µsec R shift < 13 3.3 + SL Destroy all Q's not in right mode or store all Q's in memory Two commands for shift ≥ 13 | No hardware                                      |

| 6. L shift < 13 3.3 µsec R shift < 13 7.3 + µsec Two command for shift ≥ 13 uses l fixed memory location                                | No hardware                                      |

#### 2. 2. 2. 2 Add, Subtract, and Boolean Instructions

The processing element receives all its data in the R register. The control signals from the NSU determine which input will be recognized. These include memory inputs from North, South, East, and West neighboring PEs, internal memory, BR, and L-buffer inputs either via row or column.

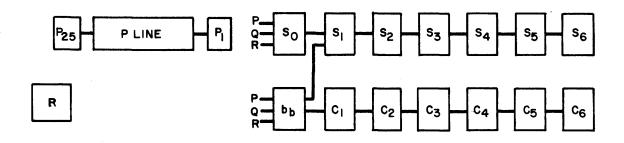

From the R register data it is then directed to different flip-flops in the PE depending upon the instruction. A load instruction will send data to  $S_0$ . The word then goes through  $S_1$  then to  $P_{25}$  where it is circulated. The total time for this instruction is 27 bit times or 3.3 microseconds.

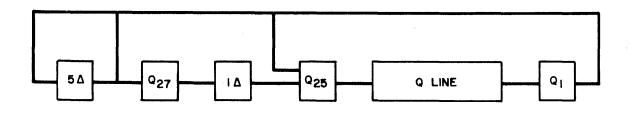

A load Q instruction will send this data to  $\mathbf{Q}_{27}$  then to  $\mathbf{Q}_{25}$  and circulation in the Q line.

If the instruction is add, R may be chosen as operand 1 in which case it is gated to  $b_0$  or operand 2 may be chosen, in which case it is gated into  $S_0$ . At this point it is gated into the adder  $S_1$  where an addition occurs with the other operand. The operand may be the contents of either P or Q. The 24-bit addition occurs in 27 bit times. The reason for this time is that: (1) 24 bit times must be used for data storage itself ( $P_1$  and delay line) and (2) one bit time is used to select the proper operand ( $S_0$  and  $b_0$ ). This selection not only includes the selection of R,  $P_1$ , and  $Q_1$ , but also their complements. This permits subtraction, and in addition, the capability exists to do absolute value instruction of P at this level, (3) one bit time to perform the actual addition, or logical operation whichever the case might be ( $S_1$ ), and (4) one bit time for selection of where the answer will be written. This may be either in P ( $P_{25}$ ) or Q ( $Q_{25}$ ). All additions and Booleans are merely single modifications of the above-mentioned operations. The additions and Booleans differ in the PE only in control signals necessary for  $S_1$  and  $C_1$ .

It seems appropriate to mention mode control at this point in that it effects these commands as it effects all commands. If the proper mode of the instruction is specified the PE will perform the specified operation and the resultant bits will be circulated in the proper delay line and be ready for another operation at the end of 3.4 microseconds. If, however, the PE is not in the proper mode the EXC flip-flop will not be set. In this state the PE must not alter any of the data within itself. Therefore the result of the computation

must be rejected at  $(P_{25})$  or  $(Q_{25})$  and the old information restored in the delay lines. The information also must stay aligned in time with that data in other PEs which have been modified.

The path for this delay is

$$P_1 \rightarrow C_5 \rightarrow C_6 \rightarrow P_{25}$$

(27-bit path)

$Q_1 \rightarrow Q_{27} \rightarrow 1\Delta \rightarrow Q_{25}$  (27-bit path)

If an add instruction does not use a memory cell for the address of one operand, it may in fact store one operand (P or Q) in a specified memory cell. Due to the peculiar nature of the memory and its association with the PE it is necessary to increase the time for this class of instructions to 3.8 microseconds. The flip-flop used to write information is b and will select either P or Q but not the result of the operation.

The paths for this operation are

$$\begin{array}{c} {\rm P_{EXC}} \\ {\rm P_1 \rightarrow S_0 \rightarrow S_1 \rightarrow S_3 \rightarrow S_4 \rightarrow S_5 \rightarrow S_6 \rightarrow P_{25} \ {\rm or} \ \Omega_{25} \\ {\rm P_{EXC}} \\ {\rm P_1 \rightarrow R \rightarrow C_2 \rightarrow C_3 \rightarrow C_4 \rightarrow C_5 \rightarrow C_6 \rightarrow P_{25} \\ \Omega_{EXC} \ {\rm and} \ \overline{\rm EXC} \\ \Omega_1 \rightarrow 5 \ \Delta \rightarrow \Omega_{27} \rightarrow \Omega_{26} \end{array}$$

Within the logic for the above-mentioned instructions exists the capability to detect overflow. Overflow is detected on all add and subtract instructions. The OF flip-flop is set when overflow occurs and then enacts the program options for handling overflow. They may

- a. set the mode flip-flop to the desired states

- b. set the mode flip-flops and jump

- c. jump

- d. do nothing

Another class of instructions is the compare commands. These instructions are similar to the add command except the result of the operation is used to set the PE modes accordingly. This setting of the modes requires extra time since first the set must go to the OF flip-flop so it can control the mode states.

It becomes convenient to choose the same time for this instruction as for a write instruction since the compare commands always require information to be rewritten in the P and Q lines. The data paths are:

$$\begin{array}{c} \mathbf{P_{\overline{EXC}}} \text{ and } \mathbf{EXC} \\ \mathbf{P_1} \rightarrow \mathbf{b_b} \rightarrow \mathbf{C_2} \rightarrow \mathbf{C_3} \rightarrow \mathbf{C_4} \rightarrow \mathbf{C_5} \rightarrow \mathbf{C_6} \rightarrow \mathbf{P_{25}} \\ \mathbf{Q_{EXC}} \text{ and } \overline{\mathbf{EXC}} \\ \mathbf{Q_1} \rightarrow \mathbf{5\Delta} \rightarrow \mathbf{Q_{27}} \rightarrow \mathbf{Q_{25}} \end{array}$$

ьb

bo - OPERAND

So-OPERAND

Sn - ADDERn

Cn - CARRYn

Q27 ,Q25 - Q INPUT SELECT

P25-P INPUT SELECT

bb - OUTPUT SELECT

R - ROUTING SELECT

#### 2.2.2.3 Multiply Instruction

There is essentially only one multiply instruction. This instruction causes R to be multiplied by Q with a double length product to be stored in P and Q (i.e.,  $R \times Q \rightarrow P$ , Q). A multiplication of -1 x -1 (an allowable number) produces an incorrect product of -1.

The basic multiply algorithm is shown in figure 2-3. Examples 1, 2, and 3 illustrate the multiplication of two numbers by use of this algorithm.

Figure 2-4 illustrates the logical sequence of the multiply operation with respect to the 6 adders. Basically six multiplier bits at a time are stored in multiply control flip-flops ( $I_1 - I_6$ ) which perform the function of controlling the corresponding 6 adders. When the multiply control flip-flops are set, the multiplicand bits are transmitted serially to the 6 adders - least significant bit first. On the basis of the corresponding control flip-flop, the adder either adds or does not add the multiplicand to the partial product. Figure 2-5 illustrates the actual sequence for the 4 cycles and figure 2-6 illustrates the operation of each adder and how those bits feed the next successive adder. For example, on the first 6-bit cycle (this refers to 6 multiplier bits) product bits  $P_{47} - P_{42}$  are generated (i.e.,  $P_{47} = A_{33}$ ,  $P_{45} = A_{21} + A_{22} + A_{23}$ , etc). Of course, if the corresponding multiplier bit is zero, then the multiplicand is not added (i.e., if  $M_{21}$  is zero and  $M_{22}$  and  $M_{23}$  are 1, then  $P_{45} = 0 + A_{22} + A_{23}$ ) each additional 6-bit cycle will generate 6 product bits and on the fourth cycle the remaining 29 bits are produced.

Figure 2-7 is a block diagram of the system which performs the multiplication. Figures 2-8 and 2-9 refer to the timing necessary to implement the multiply. If the processing element is not in the proper mode, the multiply must not be undertaken and no change should occur on the data within it.

By virtue of the EXC and EXC signals, the mode distinction is made in the PEs.

Figure 2-3. Basic Multiply Algorithm

Figure 2-4. Logical Sequence of SOLOMON II Premultiply Scheme

2-16

Figure 2-5. SOLOMON PE Logical Representation of Multiply Sequence

Figure 2-6. SOLOMON PE Multiply Sequence, 1 Cycle

Figure 2-7. SOLOMON II PE Multiply Hardware (Block Diagram)

The nonexecute paths for multiply are:

## FOR P

$$P_1 \rightarrow P_{25}$$

(25-bit path) 3 cycles = 75 bit times

$P_1 \rightarrow b_b \rightarrow P_{25}$  (26-bit path) 3 cycles = 78 bit times

FOR Q

$Q_1 \rightarrow Q_{25}$  (25-bit path)

$Q_1 \rightarrow Q_{27} \rightarrow Q_{25}$  (26-bit path)

Each block in figures 2-8 and 2-9 refers to an operation performed by the element shown in figure 2-7, and the size of the blocks are identical to the

Figure 2-8. Multiply Instruction Timing

Figure 2-9. Multiply Instruction Timing

1831A -VB -11

length of the operation except where phantom lines cut the blocks. In this case, the number of bit times are specified inside the block. (Note that each vertical line refers to a bit time.) The entire operation requires 153 bit times for completion.

#### Multiply Examples

### Example 1

| Multiplican<br>Multiplier | d =<br>= |   |   |   |   |   |   |   |   |   |   |   | = +9/32<br>= +13/32 |

|---------------------------|----------|---|---|---|---|---|---|---|---|---|---|---|---------------------|

| _                         |          | ō | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | ,                   |

|                           |          | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |   |                     |

|                           |          | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |   |   |                     |

|                           |          | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |   |   |   |                     |

|                           |          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |   |                     |

|                           |          | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |   |   |                     |

| Product                   | = Sign   | 0 | 0 | 0 | 0 | I | 1 | 1 | 0 | 1 | 0 | 1 | = +117/1024         |

#### Example 2

| Multiplicand = Multiplier = |    |   |   |    |   |   |   |   |               |              |   | = +9/32<br>= -19/32  |

|-----------------------------|----|---|---|----|---|---|---|---|---------------|--------------|---|----------------------|

| Wuitipiiei –                | 0  | 0 | 0 | _  | ^ |   | 0 | 1 | $\frac{1}{0}$ | <del>-</del> |   | · /                  |

|                             | U  | U | U | U  | U | U | U | Ŧ | U             | U            | 1 | Correct cycle, if    |

|                             | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0 | 0             | 0            |   | sign of multiplier   |

|                             | 0  | 0 | 0 | 0  | 0 | 1 | 0 | 0 | 1             |              |   | is negative subtract |

|                             | 0  | 0 | 0 | 0  | 1 | 0 | 0 | 1 |               |              |   | multiplicand (i.e.,  |

|                             | 0  | 0 | 0 | 0  | 0 | 0 | 0 |   |               |              |   | 2's complement and   |

|                             | 1_ | 1 | 0 | _1 | 1 | 1 |   |   |               |              |   | add)                 |

| Product =                   | 1  | 1 | 1 | 0  | 1 | 0 | 1 | 0 | 1             | 0            | 1 | = -171/1024          |

#### Example 3

Note that sign bit of negative multiplicands is propagated to form final product.

#### 2.2.2.4 Division

Divide within the PE can be performed on either single or double length dividends. The divisor is located in PE memory and its address is specified by R. If a single length divide is specified, the dividend is located in the P register (i.e., the most significant of a double length product). If double length, divide is specified the least significant half of the double length dividend and is contained in the Q register. A single length quotient will be formed in either case with the quotient stored in the P register and the remainder stored in the Q register.

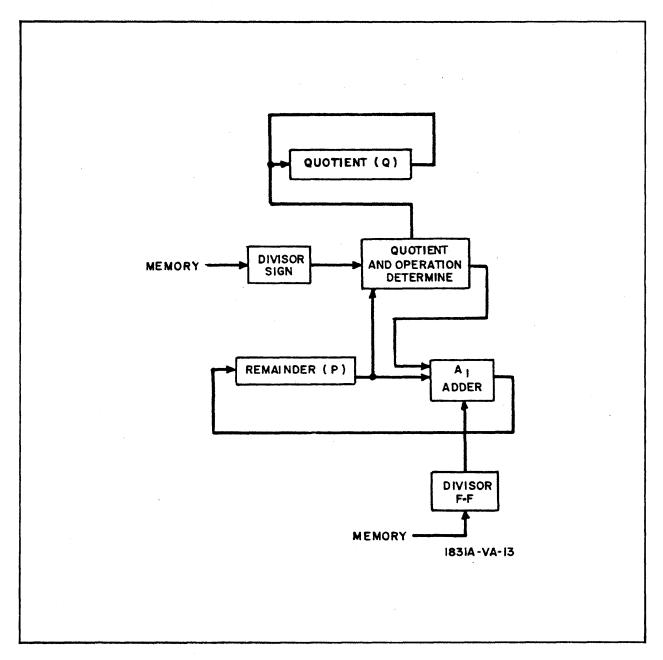

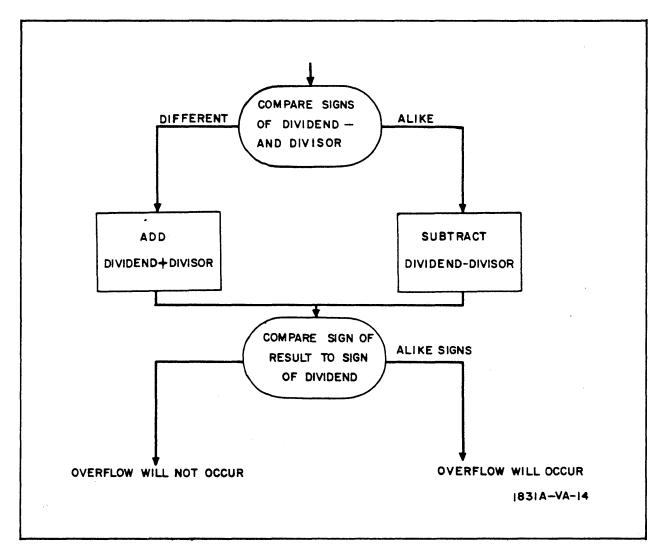

To illustrate in detail the divide operation, the actual divide algorithm is given in figure 2-10 and a block diagram for accomplishing this in the PE is shown in figure 2-11. Figure 2-12 illustrates the overflow tests performed on the operands. By observation of figure 2-10 and the divide examples 1, 2, and 3, one can readily see exactly how division is accomplished in the PEs. Note that in example 2, 5/16 is the dividend and -8/16 is the divisor which yields a quotient of -11/16, while in example 3 with the same absolute values the dividend is negative and the divisor is positive the quotient is -10/16. Obviously then the exact quotient is not obtained in all cases since -10/16 is exact and -11/16 is 1/16 in error. Due to the rather simple nature of the PE, the correction cycles to ensure an exact divide are not implemented. However, in all cases the correct quotient can be obtained by considering the remainder with the quotient. Table 2-4 outlines the possibilities that can exist.

The total time for the divide instruction is 84.6 microseconds. After the initial over flow test the sign of the divisor and the dividend (remainder after first cycle) are compared as shown in example I and stored in P sign. This then controls whether the divisor is added or subtracted from the remainder. The P sign value is gated into the Q line in  $Q_{25}$  at the appropriate time. This is repeated for the 24 bits with the cycle repeating every 26-bit times. Note that the path is 27 bits (figure 2-11) but that a shift must be affected each time and this is accomplished by using 26-bit times for the repeat time.

Figure 2-10. Divide Alogrithm

Figure 2-11. PE Divide Hardware (Block Diagram)

The nonexecute paths to keep the operands aligned are:

P

$$\overline{EXC}$$

Q  $\overline{EXC}$

$P_1 \rightarrow C_5 \rightarrow C_b \rightarrow P_{25}$  (1 time)  $Q_1 \rightarrow Q_{27} \rightarrow \Delta \rightarrow Q_{25}$  (1 time)  $Q_1 \rightarrow Q_{27} \rightarrow Q_{25}$  (25 times)  $Q_1 \rightarrow Q_{27} \rightarrow Q_{25}$  (25 times)

# Divide Examples

# Example 1

| Dividend | = | 11111110              | =    | -1/64                        |           |          |               |

|----------|---|-----------------------|------|------------------------------|-----------|----------|---------------|

| Divisor  | = | 01000000              | =    | +1/2                         |           |          |               |

|          |   |                       |      | Operation                    |           | s Status | Quotient Bits |

|          |   | 11111100              |      | Shift                        | -         | Differ   | 0             |

|          |   | 01000000              |      | $\operatorname{Add} olimits$ |           |          |               |

|          |   | 00111100              |      |                              |           | Alike    | 1             |

|          |   | 01111000              |      | Shift                        |           |          |               |

|          |   | 11000000              |      | Subt                         |           |          |               |

|          |   | 00111000              |      |                              |           | Alike    | 1             |

|          |   | 01110000              |      | Shift                        |           |          |               |

|          |   | 11000000              |      | Subt                         |           |          |               |

|          |   | 00110000              |      |                              |           | Alike    | 1             |

|          |   | 01100000              |      | Shift                        |           |          |               |

|          |   | 11000000              |      | Subt                         |           |          |               |

|          |   | 00100000              |      |                              | _         | Alike    | 1             |

|          |   | 01000000              |      | Shift                        |           |          |               |

|          |   | 11000000              |      | Subt                         |           |          |               |

|          |   | 00000000              |      |                              | _         | Alike    | 1             |

|          |   | 00000000              |      | Shift                        |           |          |               |

|          |   | 11000000              |      | Subt                         |           |          |               |

|          |   | 11000000              |      |                              | ]         | Differ   | 0             |

|          |   | 10000000              |      | Shift                        |           |          |               |

|          |   | 01000000              |      | Add                          |           |          |               |

|          |   | 11000000              |      | ,                            | ]         | Differ   | 0             |

|          |   | 01000000              |      | Add                          |           |          |               |

|          |   | 0000000               | Fina | 1 Remainder                  |           |          |               |

|          |   |                       |      |                              |           |          |               |

|          |   | 01111100              | Inco | rrect Quotien                | ıt        |          |               |

|          |   | 1                     | Cor  | rection Cycle                | (Change S | Sign)    |               |

|          |   | $\overline{11111100}$ | Fina | l Quotient                   | _         |          |               |

## Example 2

|                                             | -5/16 - Dividend<br>+8/16 - Divisor                                  |

|---------------------------------------------|----------------------------------------------------------------------|

| $\frac{10110}{01000}$ $\frac{11110}$        | 0                                                                    |

| $\frac{11100}{01000}$ $\frac{01000}{00100}$ | 0                                                                    |

| 01000                                       | 1                                                                    |

| $\frac{11000}{00000}$                       | 1                                                                    |

| $00000 \\ \frac{11000}{11000}$              | 0                                                                    |

| 11000<br>01000                              | Correction Cycle                                                     |

| 00000                                       | Corrected Remainder                                                  |

| 1.0110                                      | Uncorrected Quotient Corrected Quotient = -10/16 with 0/16 Remainder |

## Example 3

1.0101 = -11/16 with -8/16 Remainder

Figure 2-12. Divide Overflow Test

TABLE 2-4

TABULATION OF POSSIBLE DIVISION RESULTS

| Divisor<br>Sign | Dividend<br>Sign | Quotient<br>Nature | Quotient                                 | Remainder                       |

|-----------------|------------------|--------------------|------------------------------------------|---------------------------------|

| -               | ±                | Exact              | Exact answer -2-23                       | Sign and magnitude of = divisor |

| +               | ±                | Exact              | Exact answer                             | = zero                          |

| -               | ±                | Nonexact           | Unrounded<br>(magnitude is too<br>large) | = negative                      |

| +               | ±                | Nonexact           | Unrounded<br>(magnitude is too<br>small) | = positive                      |

#### 2.2.2.5 Shift Instructions

In SOLOMON where some PEs may be operating and some may remain unchanged, all instructions must be of such a length as to have the first bits in all PEs aligned at the conclusion of the instruction. As a result the way chosen to effect a shift is to enter delays into the delay-line loop. The basic time for a left shift is approximately 1-word time and a delay equal to the shift length is added to the delay loop. For a right shift the basic time for the instruction becomes twice the word time and the delay which is added equals 25 minus the shift length. Since the object in designing in the shift was to use as much existing hardware as possible, it was found that only 14 delays could be found without adding extra flip-flops and delay elements. As a result, in order to do a left shift of greater than 13, two passes through the shift paths had to be effected. Similarly, in order to do a right shift of less than 12 two passes had to be made.

These delays are completely dependent on shift length. For shifts that require greater than 13 delays the first pass always is one with 13 delays and the second pass adds the required additional delays.

SOLOMON PEs also have the capability to perform double length shifts both algebraic and logical with P being the most significant and Q the least significant portion of the word.

### 2.2.3 Network Control Unit Design

The network control unit (NCU) is functionally the same unit described in the AF report. This section will be restricted to supplying more detail concerning the interface and how the NCU functions as a system component.

The NCU and the network are designed to operate concurrently. This feature allows housekeeping required for the network program to be overlapped with execution in the network.

The NSU buffers two instructions to allow the network to operate at maximum rate. Lookahead is required because of the dynamic register in the PEs. At the completion of an instruction, the NSU must have the signal lines for the next instruction high before the end of the switching blank in the PE delay-line registers. If this condition is not met, a complete network cycle is lost, which could approach a 50 percent reduction in performance.

Because of the concurrency between the NCU and NSU and the two instruction buffers in the NSU, all data transferred over the NCU-to-NSU interface must be interlocked to assure that the sequence of the program is not changed. The following description will define the interface.

The network instruction set contains options that allow overflow, the existence of an active PE, and the existence of more than one active PE in the network to be detected. The NCU instruction set contains conditional branch instructions that use these indicators to determine if the branch is to be executed. For the NCU to execute one of these branch instructions, the NSU busy signal must not be present. The broadcast register, geometric row register, and the geometric column register are programmable registers that are loaded from PRM or stored into PRM by the NCU. For the NCU to execute these transfers, the NSU busy signal must not be present.

The transfer of data between the LB and the PRM is controlled by the NCU. The transfer between the LB and the network is controlled by the NSU. To maintain the program sequence, the NCU must know if the NSU is executing or has buffered an LB transfer instruction. The NCU contains a two-stage up-and-down counter which is stepped up each time an LB-network

instruction is sent to the NSU and stepped down each time the NSU completes an LB-network transfer. The NCU will execute an LB-PRM transfer only if the count is zero.

# 2.2.3.1 Program Memory Interface

In the system configuration proposed, the contents of the PRM are accessed by the NCU and LB only. The NCU instruction word is 48 bits and the data word is 24 bits, corresponding to the NSU 48-bit instruction word and the network 24-bit data word. The path between the NCU and the PRM is 48 bits. The path between the LB and the PRM is 96 bits. The number of bits accessed per memory cycle is 192. The 48-bit instruction formats were selected to allow the PRM to be expanded if desired and the data word from PRM to be a multiple of the 24-bit network data word. The 96-bit path between the LB and the PRM allows data to be transferred between the network and PRM at nearly maximum rate that data can be transferred over the edge of a 32 x 32 PE network. In approximately 3 microseconds, 32 24-bit data words can be transferred between the LB and network. Between the LB and PRM, eight 24-bit words (192 bits) are transferred per memory cycle. Four 1-microsecond memory cycles will transfer 32 data words. A 96-bit path was selected for this communication rather than a 48-bit path to reduce the electrical design problem of the interface. In principle, sufficient time is available to load or read the memory register during the clear or restore portion of memory cycle, but the detailed design of the interface indicates that this implementation is not practical.

The PRM and the PEM are electrically and mechanically the same except for the interface. Both memories use identical electronics and packaging. The only difference is that the PRM accesses 192 bits per cycle and PEM accesses 256 bits. Four PEM's are packaged in the same enclosure for 128 PEs. The PE network is designed to be modular in blocks of 32, which requires the PEM enclosure to be modular. Physically, this memory arrangement allows the PRM to be expanded in increments of 16,000 (48-bit words) to 64,000, within the same physical unit.

The electrical design of the memory allows an additional degree of freedom in expanding the PRM. Additional memory banks can be added to the same interface electronics, or the memories can be independent units that are accessed concurrently. If memory banks are added to make a larger single memory, the hardware required for the digit direction of the memories is shared. Functionally, the memories are tied together at their preamplifiers. If additional memories are to operate independently, a duplicate unit is added including the interface. A brief explanation of the details of the PRM interface will indicate how this is implemented.

Each unit connected to the PRM uses a driver at its interface that is capable of driving as many terminated transmission lines as there are independent memories. The unit decodes the high-order two bits of an address to specify which memory bank is being requested. At each memory bank a memory priority circuit selects the unit to be serviced and gates the address to the memory access circuitry and returns an acknowledgement to the unit. low-order two bits of the address are decoded at the memory to select the proper 48-bit word. The design that is proposed allows four memories to be connected in this manner to two units. This selection was made to correspond to the estimate of the requirements of an expanded system in the near future. Electrically the interface can be expanded to eight with the same set of drivers. This is the same driver developed for distributing the NSU signals to the network. The number of gates that are practical to package in the interface and the cost of these gates are the limiting factors. The detailed layout of the interface cards has not been attempted, therefore the freedom in expanding the interface, by leaving space for additional cards, beyond the present design cannot be stated.

# 2.2.3.2 Priority Interrupt

The design of the priority interrupt system has been developed to minimize the complexity of the hardware in the NCU and to allow maximum program control. The current design allows interrupts from four sources to be serviced. Associated with each interrupt source are two memory cells that will be referred to as mail boxes (MB). One MB is used by the programmer

to store a jump instruction to enter the desired service routine, or a No-Op instruction to ignore the interrupt. The other MB, if required, is used by the interrupt source to store information to define the interrupt, if more than one condition can generate the interrupt. Each interrupt source connected to the NCU is assigned a priority determined by the position to which it is wired on the interface. A simple sample and hold network is used to strobe the interrupt lines and select the highest order interrupt. When interrupt is detected, the NCU generates an execute instruction with an address field corresponding to the programmed MB. The sampling network is stopped when an interrupt is recognized and an acknowledgement is returned to the source that is going to be serviced.

If the execute instruction receives No-Op instruction from the MB, the sampling network is released to scan the interrupt lines. If a jump instruction is obtained from the MB, the interrupt lines are not scanned until an unlock interrupt instruction is executed. A lock interrupt instruction that stops the scan of the interrupt lines is available to the programmer. The status of interrupt lines can be sampled under program control by reading the indicator register (IDR) of the NCU, but an acknowledgement to the interrupt source cannot be generated directly by the program. The interrupt unit will be packaged so that it can be expanded by adding additional interface and sample and hold stages.

## 2.2.3.3 General Purpose Computer or I-O Controller Interface

An input-output system to control peripheral devices is not included in the present SOLOMON II design, but a generalized interface has been designed into the NCU to allow an input-output system or a general purpose computer to be added. The selection of the interface that will be described is a result of an I-O controller designed earlier in the SOLOMON project and the desire to provide a flexible I-O interface for the current system without adding a large amount of hardware to the NCU.

The function of the I-O interface can be illustrated by considering an I-O controller having an independent interface with the PRM that receives

commands that define the function to be executed and the area of memory to be used. Associated with the I-O controller is an MB in the PRM that is used to transfer commands to the I-O controller. The programmer loads the MB with the command (the name command will be used only to refer to the contents of the I-O controller MB) and issues an alert instruction. The alert instruction will result in a signal line being raised to the I-O controller. The I-O controller obtains the MB, and returns a signal to release the NCU. Command completion signals are returned via the priority interrupt system. The second MB associated with the priority system would be used to identify the command completed in a multichannel I-O controller. Afield of the alert instruction is coded to identify the alert line if more than one independent unit is connected to the PRM.

Connecting a commercially available general purpose computer directly to the PRM in this manner cannot be similarly generalized because of the variety of machines that could possibly be used and the lack of specification of a particular machine and detailed information concerning the memory interfaces, interrupt systems, and circuits.

### 2.2.4 Network Sequencing Unit

The function of the NSU in the proposed system is identical to that previously described. The purpose of the NSU has been outlined in the general description of SOLOMON II in paragraph 2.1 of this proposal.

### 2.2.4.1 Network Control

The PE network is made up of a matrix of bit-serial arithmetic units with a minimum of control within the PE (detailed description of PE in paragraph 2.2.2). The only control that is unique to the PE is the execute control. If the execute control is not present, the PE ignores the current instruction. The execute control is set by comparing the decoded value of two mode value bits in the PE with four-mode control signals from the NSU. If any bit position agrees within the PE, execute control is set and the PE is said to be active. The mode value (MV) in the active PE, can be unconditional set or conditional

set by the NSU. Overflow options and compare instructions are used to conditional set the MV. The execute control of the PE is also conditional on the state of two other NSU controls, geometric row and geometric column controls, which were previously described. Both of these signals must be high for the PE to be active.

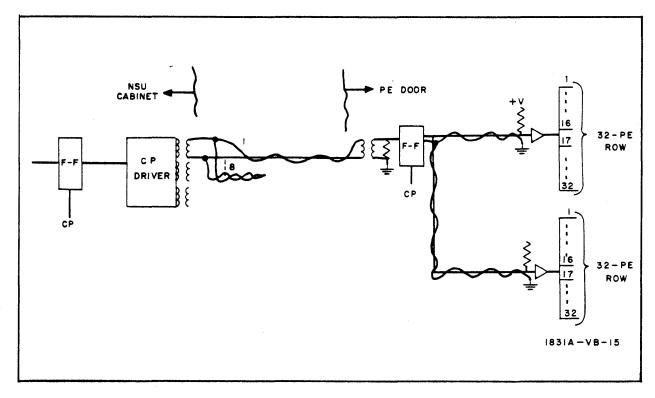

## 2.2.4.2 Signal Distribution

The signal drive between the NSU and the network has been designed to allow the network to be expanded from 32 PEs to 1024 PEs. The packaging is designed to expand the network in increments of 64 PEs to 1024 PEs (paragraph 2.5). A PE consists of four unique cards. In the PE door, 64 PEs are laid out in eight rows. Within a row, the PE card types are identical, which allows the NSU signals specifically required for a given row to be contained in that row. Each NSU signal required in a row has a driver located at the center of the row that is capable of driving 32 loads. The distance from the driver to any PE is less than 18 inches. The input to the row drivers is supplied by a set of flip-flops at the bottom of the PE door. A clocked flipflop is used at this point in the NSU drive pyramid to retime the signals and to allow transformer coupling between the NSU and the PE door. In the NSU the signals are input to a clock driver that has an adjustable time delay. The output of the clock driver is three transformers that are capable of driving 8 terminated lines each. One terminated line supplies a control signal for a door of 64 PEs (figure 2-13). As additional doors of PEs are added, the signal drive lines are connected to the output transformers in the NSU.

### 2.2.5 PE Network Design

The design improvements and refinements in the PEs themselves have been previously described in paragraph 2.2 of this proposal. The arrangement of these PEs into a simultaneously operating network and the interfaces of the PEs to the rest of the system present some unique control requirements. These requirements, where differences exist from the basic earlier SOLOMON II design, are presented in the following paragraphs.

Figure 2-13. PE Network Signal Distribution

## 2.2.5.1 PE Data Interfaces

Data are transferred bit serial as 24-bit words between the two PE delayline registers and the PEM, the LB, or the broadcast register. All data path connections are controlled by the NSU and are the same for all PEs.

The PEM is physically made up of linear select core banks that contain  $10^6$  bits and can access 256 bits per memory cycle. Each bank is connected to a 32-PE module via an eight-bit shift register (figure 2-2). The shift register allows a 1-microsecond memory to transfer data continuously at an 8-mc bit-serial rate.

Data is transferred between the LB and the network by rows or columns. When writing into the network all active PEs in the same row or column receive the same operand. When reading from the network, the output of all active PEs in a selected row or column are sent to the LB.

The broadcast register is a data source or sink that is common to all active PEs. To write into the network the BR is gated to each of the LB-row

lines. To read, the LB-row lines are all "ORed" at the input of the broad-cast register.

#### 2.2.5.2 Indicators

The status of the network can be sampled by testing for overflow or active. Overflow check on arithmetic (paragraph 2.2.2.2) instructions is a programming option that can be used to set an indicator if any active PE overflows. The test for active (paragraph 2.2.4.1) sets one indicator if more than one PE is active and another indicator if only one PE is active.

To test overflow, the overflow flip-flop in each PE is gated to the line used to collect data by rows and the OR gates for loading the broadcast register from the network are opened. If a one is detected, an indicator is set.

To test the active status of the network, the execute flip-flop of the PE's are gated to the lines that collect data by rows and the lines that collect data by columns. The collection lines are gated to a shift register that is used to detect the presence of one or more than one bit set. If more than one bit is detected in either register, only the more than one indicator is set. If only one is detected in either of the registers, the one indicator is set.

A programming option is also available that allows the Execute FF's to be loaded into the Geometric Row and Geometric Col.Register. The same set of lines are used that are necessary to collect the Execute FF's. Both of the Geometric Control registers are programmable.

## 2.2.6 Console

The console that is proposed is a combination operator's and maintenance console. The ability to load NCU registers, read-write the PRM, to read PEM, and to read PE registers are aids designed to reduce time required to isolate failures. The console typewriter and the PE Mode Value display make up the major portion of the console hardware associated with normal operation.

## 2.2.6.1 Console Typewriter

The console typewriter is connected to the NCU by a six-bit data path.

Input from the typewriter is controlled by the operator. The starting

location is set on the console switch and ENTER TYPEWRITER pushbutton is depressed to initiate a transfer. The characters typed are assembled into 48-bit words by the NCU and are loaded into contiguous memory locations until END OF TRANSFER is depressed by the operator. End of transfer will cause the last group of characters assembled to be loaded into the next memory location. Output to the typewriter is under program control. One 48-bit word is output each time the output instruction is executed.

The PRM can also be loaded from the console by setting the location and the value on a set of console switches and depressing the LOAD MEMORY switch.

## 2.2.6.2 Single-Step Control

The single-step control is designed to allow the program to be stepped one instruction at a time or one minor cycle of the instruction at a time.

### 2.2.6.3 Halt Control

A set of halt conditions that can be selected at the console has been provided as a maintenance aid. The NCU can be stopped by the following conditions:

- a. Stop if a bit of the NCU's IDR matches its corresponding console switch.

- b. Stop when the IC equals the value set in the console switches.

The stop conditions can also be used to generate a branch to a location specified by a set of console switches. This feature allows the operator to cycle on a selected segment of a program when isolating failures.

#### 2.2.6.4 Start Controls

Two basic controls from the console are used to start a program. If the machine has been cleared, initiate is used to set the NCU IC from console switches. If the machine was stopped by a halt instruction or from the console, start is used to initiate the program.

Depressing MASTER CLEAR switch at the console clears all NCU and NSU register and controls. MASTER CLEAR is interlocked with halt, such that it has no effect if the machine is operating.

## 2.2.6.5 Displays

A complete list of the control to be displayed has not been finalized. The following description will outline the major displays.

The following NCU registers will be displayed:

- a. Memory data register (48 bits)

- b. Memory address register

- c. Instruction register

- d. Instruction counter

- e. Indicator register

- f. Arithmetic registers

- g. Selected flip-flops in timing control

The following NSU registers will be displayed:

- a. Instruction buffer

- b. Broadcast register

- c. Geometric control registers

- d. Memory address register

- e. Selected flip-flops in timing control

Two 32-position rotary switches will be provided to allow one-bit position of the geometric row and the geometric column controls to be selected from the console for displaying the contents of the PE register or the contents of a PRM word or the contents of an LB location. The rotary switches are interlocked with halt. To display a network register, the operator depresses the control corresponding to the register desired and the NSU initiates a timing cycle that gates the contents of the register through the network-broadcast register path to a display register in the NSU. If a word of PRM is desired, the address is set on console switches and the procedure for reading a register is followed. The state of the network is not changed by generating the displays mentioned.

The mode value flip-flops in the PE will be connected directly to console lamps for display. This display will physically be laid out in the same matrix notation manner that the network is labeled.

## 2.3 MEMORY SYSTEM

The memory system selected for SOLOMON II serves the purpose of both the PEM and PRM as previously defined. Since the AF report was published, certain test programs have verified the selection of the memory system.

These tests and their results are briefly described in the following paragraphs.

## 2.3.1 1-Microsecond Memory Breadboard

Four planes of 30-18 mil cores built by Lockheed Electronics Co. were obtained for test. Each plane consisted of a  $32 \times 10$  section of cores fully wired with loose cores on each line to increase the size to  $128 \times 64$ . A 4-wire system was used for each plane. The planes were interconnected so that the read-write lines were 256 cores long. Thus 2 planes formed 32 words of 256 bits each.

#### 2.3.1.1 Test Circuits

The drive system consisted of 12-current drivers; a 12-input LSM transformer, a drive-line selection transformer, and a transistor switch. The switch had a 68-ohm terminating resistor in its collector.

The sense amplifier consisted of 2-differential pairs in series, transformer coupled to a rectifying and output stage.

The digit driver consisted of a voltage switch transformer coupled from a driving stroke gate.

### 2.3.1.2 Test Results

A 400-milliampere pulse 250-nanoseconds wide was used to interrogate the word lines. Rise and fall times of the pulse was 75-100 nanoseconds. With a full-write pulse so that all 256 cores switched the back-voltage developed by the cores was about 13 volts.

A 180-milliampere one-half write pulse, 400-nanoseconds wide, in conjunction with a 100-milliampere 325-nanoseconds wide digit pulse caused the core to switch to a "1" state.

The digit lines on one of the extra planes were interconnected so that a digit line of  $32 \times 64$  cores or 2048 cores was formed. A sense line parallel to the digit line was also interconnected but in a manner so as to cancel

digit noise. The digit and sense lines thus consisted of 2048 cores plus one plane of 64 cores or a total of 2112 cores.

The noise cancellation achieved was very good. The signal-to-noise ratio was also good.

#### 2.3.1.3 Conclusion

The conclusion from the tests was that all circuits functioned well and that no additional information could be obtained without the use of a full-size stack, since all tests with the small stack were favorable and no problems were encountered in the system design.

It is of interest to note that the existing coincident current memory for the Westinghouse 2402 computer uses access circuitry along one axis similar to that required in the 1-microsecond linear select system. In fact, the only difference other than amplitude of currents, was that the 2402 system requires 128-drive line outputs while the 1-microsecond linear select system requires only 64 outputs. The checkout of the 2402 access circuitry has been completed and its performance is quite satisfactory. The drive system is capable of providing a 350-milliampere current pulse into a core line of 3300 cores terminated in 100 ohms in 40 nanoseconds.

# 2.3.2 Molecular Sense Amplifiers

The basic package of the molecular sense amplifier consists of 3, 14-lead flat packs built by Texas Instruments to Westinghouse specifications. The molecular sense amplifiers have met or exceeded all specifications. The bandpass of the devices is 5.5-6 mc normally limited in circuit by a transformer. The delay through the molecular sense amplifier is 60 nanoseconds. Common mode rejection appeared to be very good - no detectable offset using Tektronix 545 scope with a 2.0-volt common mode input.

### 2.4 POWER SYSTEM

In view of the high currents being required at low voltages, all practical power distribution systems involve distributing an ac voltage, either 60 cycles, 400 cycles, or higher frequency, to power supplies located in the various major computing modules.

The choice of primary power to be distributed to the modules depends largely upon the use to which the computer installation is to be directed, and the quality of the primary power that is available at the computer location.

The use to which a computer is directed determines to a large extent how many computer interruptions can be economically or practically tolerated, resulting from power line disturbances. The quality of the power refers to how closely it is regulated, maximum fluctuations, and the duration of the fluctuations. Fluctuations expected range from minor disturbances resulting from switching loads, more serious line variations resulting from heavy load changes on a poorly regulated line to complete line outages lasting from several milliseconds to several hours.

A wide variety of requirements can be met by variations on a basic system where the incoming power is preregulated or improved in quality to a point where the regulators installed in the various computing modules can be quite economically fabricated. In the process of preregulating the power it is advantageous to change the frequency to higher than 60 cycles so that the components in the module power supplies can be smaller, lighter, more efficient, and more economical. In this type system the design of the power supplies in the individual computing modules remains fixed while the preregulator is modified to fit varying requirements.

In the design of past proposed SOLOMON systems, several divisions of Westinghouse, the Lima Division and the Buffalo Division, have participated in the design of power systems to meet the requirements for several different SOLOMON applications. Several outside vendors have also been contacted.

In general the more adverse the requirements, the more complex the system becomes. Systems considered include the following types of regulating systems.

- a. No preregulator module power supply uses raw 60 cycles

- b. Brushless rotating frequency changer with and without flywheel storage preregulator followed by 400 cycle or 2000 cycle input modular power supplies.

- c. Constant-voltage transformer-rectifier battery charger and battery with:

- (1) dc-to-dc module converters

- (2) dc-to-400 or 2000 cycle frequency changers with module regulated power supplies

- d. Same as c above with standby diesel engine generator sets. All systems except c(1) and (a) use the same regulator module in the computer module. The regulator of (a) is of similar nature but must operate over a wider range of input voltages and the components are larger in the rectifier section due to the use of 60 cycles. When the input voltage quality is not good and the system is large, the supply described in (b) becomes the more practical. Systems (c) and (d) are for use where line interruptions are expected but operation interruption is not allowable.

The physical size of a type (b) final regulator used to supply the following power to one door containing 64 PE elements is:

- +6 v at 114 amps

- +9 at 32 amps

- -1.5 at 3 amps

Since the regulation of the high-frequency ac power is good, the power supplies contained in the memory and any auxiliary equipment can be correspondingly small and efficient.

Due to the large number of components and dense packaging the distribution of power has received serious attention. Initial designs indicate that 114 amperes of 6-volts dc power per PE door will be required. With currents

of this magnitude, it requires a conductor of 0.216 square-inch to carry the current with a voltage drop of 10 millivolts per foot.

Since this is a reasonable sized cross section of copper, it is not practical to transmit this over a considerable distance from central power sources.

This size conductor yields a 1 percent dc drop for each 6-feet of length.

To maintain the noise on the dc voltage buses within a tolerable level, 3 percent, it is necessary that the characteristic impedance of the bus lines be kept low. Since the characteristic impedance, Z, of a cable is given by:

$$Z = \sqrt{L/C}$$

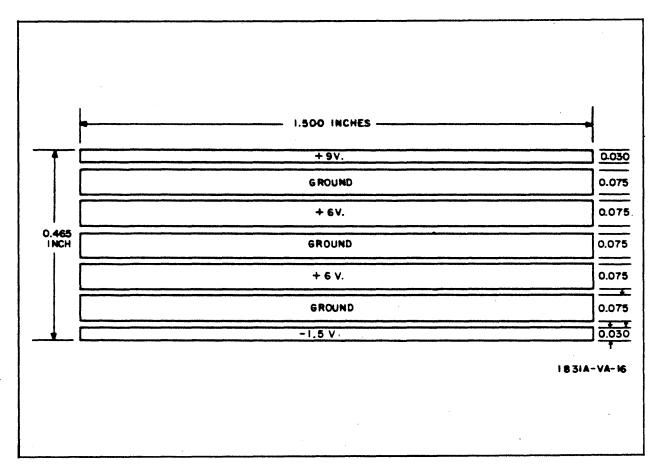

it is desirable to reduce L. This is obtained by keeping the conductor close to the ground return bus, in this application there is to be 5 mils separation. To further reduce the inductance, the 6 volt bus is laminated; i.e., two strips are paralleled and sandwiched between a ground plane on the main bus inside the cabinet. On the main bus inside the cabinet, capacitors are distributed along the bus to get the impedance sufficiently low, the amount required being approximately 180-microfarad per foot for a bus of the configuration of figure 2-13A.

The most serious problem occurs with the +6 volts, since it is required to have the lowest impedance. The +9 volts requires but 0.92-microfarad per foot and will be an outside conductor having a ground only on one side.

The -1.5 volts bus will be identical to the +9 volts.

Figure 2-13A indicates the cross sectional view of the main bus in the door. Similar designs will be used for the branch bus; however, only one conductor will be used for the +6 volts and the dimensions will be smaller.

## 2.5 PACKAGING

The detailed design of the cabinets has not been completed. An analysis of the signal distribution problem and card count has established the geometry and space requirement. All analysis was made assuming a 1024 network was to be packaged in modules of 64 PEs. The system is modular in increments as small as 32 PEs but the analysis of the packaging indicates that it is more practical to package in modules of 64 PEs.

Figure 2-13A. Main Power Bus End View

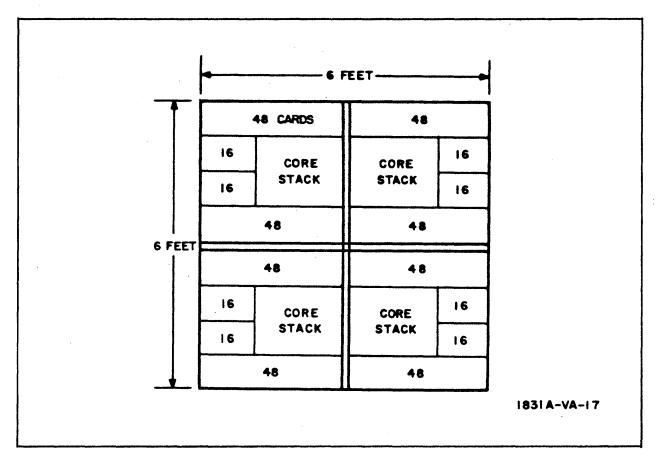

The distance between the PEM and PEs has the most influence on the gross geometry of a system larger than 256 PEs. Within a 256 network the physical size of the memories dictate the geometry of the enclosures. Four 256 x 4096 memories can be packaged in a 6-foot x 6-foot x 15-inch enclosure (figure 2-14). Because each memory services 32 PEs, the block of 128 PEs associated with the memory enclosure has been packaged in two doors that hinge at opposite ends of the memory enclosure (figure 2-15). Assuming four cards per PE and eight addition card spaces per 32 PE cards and 0.7-inch card centers, 64 PEs can be packaged in 8 rows, 28 inches long. The door will be larger than this to allow for cabling and cabinet structure. A practical dimension for the door appears to be 3 foot x 5 foot x 8 inches. The dimensions of the memory enclosure will be longer than 6 feet to allow for power supplies and

Figure 2-14. Packaging Arrangement

cabling. The power supplies that supply power for the PE doors will be mounted at the edge of the memory enclosure to minimize bus length between the supplies and the load.

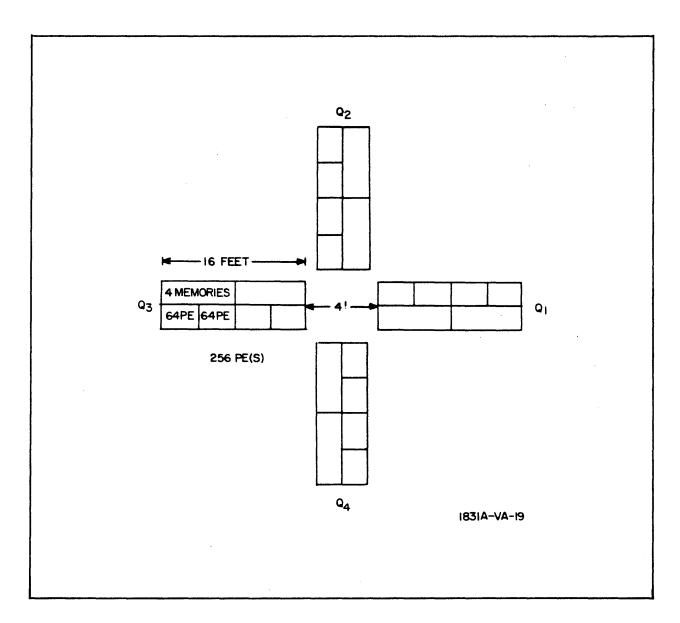

A 256-PE network consist of two 128-PE enclosures in line to form a wing approximately 16-feet long. A 1024-PE network consist of four wings positioned as a cross with a 4-foot open center section (figure 2-16).

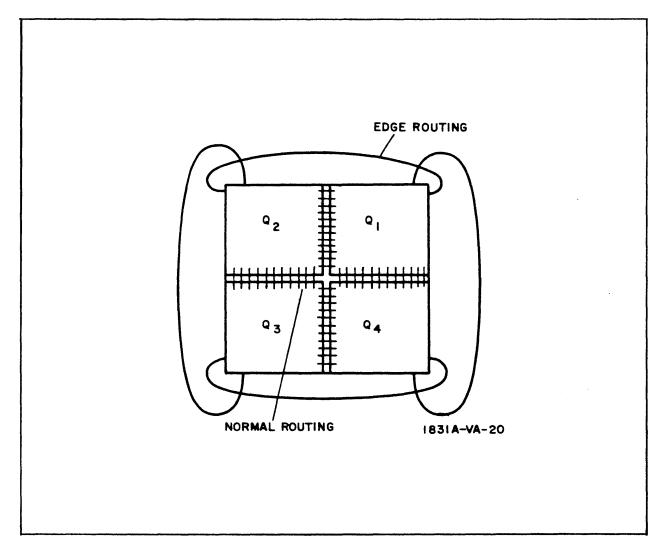

The cross configuration was selected to assure that no routing line in the sytem would exceed 40 feet and that all cabinets were easily accessible for maintenance. In figure 2-17 the wings have been labeled  $Q_1$  through  $Q_4$  and the routing paths illustrated. All lines between adjacent wings will run diagonally under the floor. Note that there are no routing lines between  $Q_1$  and  $Q_3$  or  $Q_2$  and  $Q_4$ . The maximum line length is between the ends of adjacent wings.

Figure 2-15. Cabinet Arrangement

### 2.6 RELIABILITY

The SOLOMON II computer system reliability is ensured through the use of silicon integrated circuits at low power levels for logic gates, flip-flops, and memory sense amplifiers, and through the extensive derating of components in the discrete component circuits used as memory drivers and in peripheral and auxiliary electronics. The expected level of reliability for SOLOMON II is shown in tables 2-5 and 2-6, which are mean time between failure (MTBF) figures for 32 PE and for 256 PE SOLOMON II computers respectively. The usual assumption of Poisson distribution of failures is made, i.e.,

$$R = e^{-\lambda(t-t_0)}$$

where

R = reliability = probability, given that the system is operating at time t, that the system is operating at time t.

$\lambda$  = system failure rate in failures/unit time.

e = base of natural logarithms.

Since failures are assumed independent of time, as a result they are assumed independent of each other. Thus the formula equates any single failure to

1831A

Figure 2-16. System Layout

Figure 2-17. Routing Paths

system failure. It should be noted that, due to the SOLOMON II organization, this definition of system failure results in a conservative reliability estimate.

TABLE 2-5

32 PE SOLOMON II RELIABILITY

| Component                        | Quantity | Failure Rate<br>%/1000 hr              | Aggregate Failure Rate %/1000 hr |  |

|----------------------------------|----------|----------------------------------------|----------------------------------|--|

| Integrated Circuit<br>(TO-5 can) | 25,445   | 0.001                                  | 25.45                            |  |

| Transistor                       | 3,374    | 0.001                                  | 3.37                             |  |

| Diode                            | 26,047   | 0.0004                                 | 10.43                            |  |

| Resistor                         | 5,947    | 0.0004                                 | 2.38                             |  |

| Capacitor                        | 3, 163   | 0.001                                  | 3.16                             |  |

| Transformer                      | 1,252    | 0.001                                  | 1.25                             |  |

| Solder Connection                | 540,000  | 0.0001                                 | 54.00                            |  |

| System Failure Rate              | e        | $100.04 \approx 100\%/1000 \text{ hr}$ |                                  |  |

TABLE 2-6

256 PE SOLOMON II RELIABILITY

$1000 \; hr$

394 hr

| Component                        | Quantity  | Failure Rate<br>%/1000 hr              | Aggregate Failure Rate<br>%/1000 hrs |  |  |  |

|----------------------------------|-----------|----------------------------------------|--------------------------------------|--|--|--|

| Integrated Circuit<br>(TO-5 can) | 72,399    | 0.001                                  | 72.40                                |  |  |  |

| Transistor                       | 11,404    | 0.001                                  | 11.40                                |  |  |  |

| Diode .                          | 103,017   | 0.0004                                 | 41.20                                |  |  |  |

| Resistor                         | 15,369    | 0.0004                                 | 6.15                                 |  |  |  |

| Capacitor                        | 12,624    | 0.001                                  | 12.62                                |  |  |  |

| Transformer                      | 5,634     | 0.001                                  | 5.63                                 |  |  |  |

| Solder Connection                | 1,043,000 | 0.0001                                 | 104.30                               |  |  |  |