# **INTRODUCTION AND INSTALLATION**

| Introduction | 1-1 |

|--------------|-----|

| Installation | 1-1 |

Page

# **INTRODUCTION AND INSTALLATION**

# **INTRODUCTION**

This document describes the TEK6100 Series family of computing systems. This first section provides an introduction along with installation procedures (to be provided). Each following section discusses individual major subassemblies, for example Section 2 discusses the computer board and Section 3 discusses the expansion memory board.

# **INSTALLATION**

This information will be provided at a later date.

# **COMPUTER BOARD**

|                                           | rage |

|-------------------------------------------|------|

| Introduction                              | 2-1  |

| Computer Board Overview                   | 2-1  |

| Board Configuration                       | 2-1  |

| On-Board RAM Configuration Jumpers        | 2-1  |

| Expansion RAM Jumpers                     |      |

| ROM Configuration Links                   | 2-2  |

| Kernel Configuration.                     |      |

| LAN Interface Jumpers                     |      |

| Special Registers                         |      |

| Functional Block Description              |      |

|                                           |      |

| System Bus Structures                     |      |

| Kernel Bus                                | 2-3  |

| Internal Address Bus                      | 2-3  |

| Internal Address/Data Bus<br>External Bus | 2-3  |

| External Bus                              | 2-3  |

| Kernel (1)                                |      |

| Kernel Bus                                |      |

| Kernel Timing and Control Bus             | 2-4  |

| Central Processing Unit                   |      |

| Slave Processor Bus Cycles                | 2-7  |

| Memory Management Unit                    | 2-7  |

| Memory Management                         | 2-7  |

| Floating Point Unit                       |      |

| Timing Control Unit                       |      |

| Kernel ROM (2)                            |      |

| Non-Volatile Memory (8)                   |      |

| Main Memory (14)                          |      |

| Memory Access and Refresh Timing (13)     | 2-9  |

| Memory Addressing (14)                    | 2-9  |

| Parity Generation and Checking (14)       |      |

| System Control Block (9)                  |      |

| Floppy Disk Interface (4, 10)             | 2-10 |

|                                           |      |

| Erroneous ALE Detection Logic             |      |

| Hard Disk Interface (3)                   |      |

| Disk Data Cache                           |      |

| Buffer Control PAL                        |      |

| Dual RS-232-C Interface (5)               | 2-12 |

| GPIB Interface (6)                        | 2-12 |

| Local Area Network Interface (12)         | 2-13 |

| Interrupt Control                         | 2-13 |

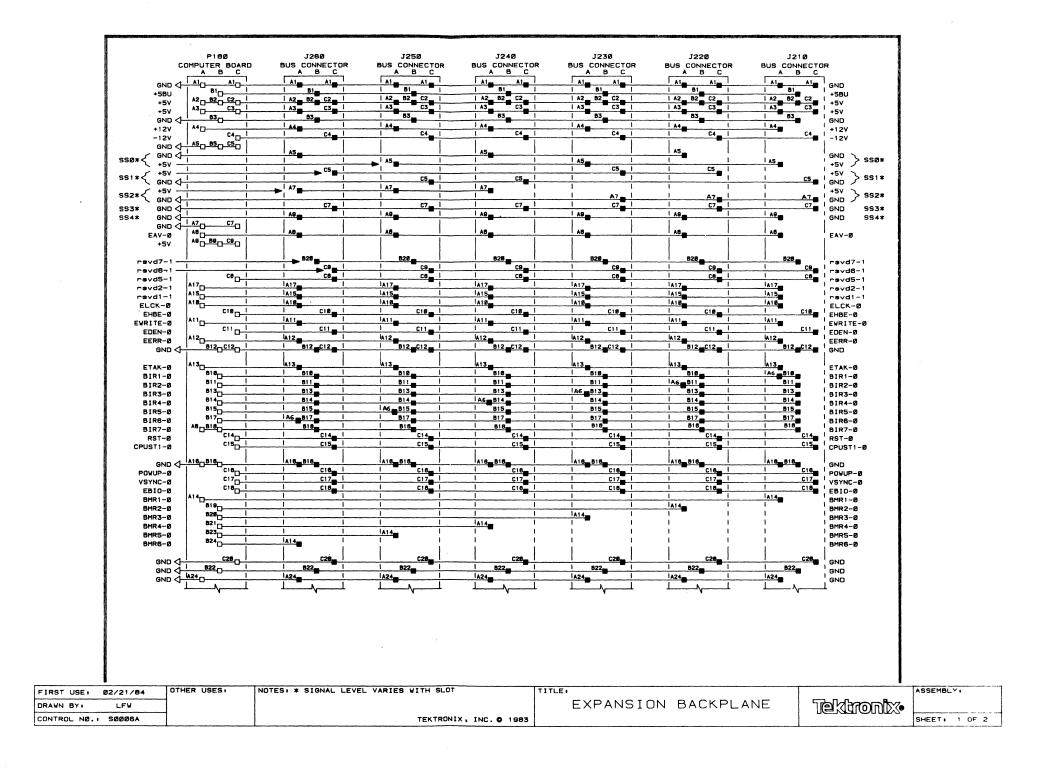

| External Bus Interface                    | 2-13 |

| Bus Timeout                               | 2-13 |

| DMA Arbitration (2)                       | 2-14 |

| DMA Arbitration PAL                       |      |

| Clock Generation (7)                      |      |

| Reset Pulse Stretcher                     |      |

| Time-of-Day Clock (9)                     |      |

|                                           |      |

#### TABLES

D - ---

| Table<br>No. |                           | Page |

|--------------|---------------------------|------|

| 2-1          | RAM Configuration Jumpers | 9-1  |

1 ł .

# **COMPUTER BOARD**

# INTRODUCTION

This section describes the use and operation of the TEK6100 Series computer board. This document does not discuss software interface topics relevent to the computer board. Refer to the TEK6100 Series OEM Manual for this information. The contents of this section are organized as follows:

- Computer Board Overview

- Board Configuration

- Functional Block Description

# **COMPUTER BOARD OVERVIEW**

The TEK6100 Series computer board, is a 16032-based processor that provides the computer resources and base I/O interfaces for the TEK6100 Series family of workstations. The board is a large circuit board located at the top of the system cabinet and contains up to 1 megabyte of main memory, with an additional 2 megabytes (maximum) available on an expansion board.

# **BOARD CONFIGURATION**

The board has a number of jumpers and links that must be configured at the factory if the board is to be installed properly. Jumpers are zero ohm resistors that are machine insertable. Links are small shorting connectors that are installed on .025-inch diameter pins.

# **ON-BOARD RAM CONFIGURATION JUMPERS**

There are six jumpers that select the density of the RAM memory chip used on the board. These jumpers are configured for the applicable memory chip as indicated in the following table:

#### Table 2-1

|               | W2141   | W2143   | W 2130  | W2131   | W2140   | W2142   |

|---------------|---------|---------|---------|---------|---------|---------|

| 64-kbit chip  | remove  | install | remove  | install | remove  | install |

| 256-kbit chip | install | remove  | install | remove  | install | remove  |

#### **RAM CONFIGURATION JUMPERS**

### **EXPANSION RAM JUMPERS**

A jumper pair is used to select whether or not an expansion memory board is used in the system. If expansion memory is used, jumper W0151 is installed and jumper is removed. If expansion is not used, jumper W0151 is removed and jumper W0152 is installed.

### **ROM CONFIGURATION LINKS**

There are two links that establish the density of the ROM chips used, either 64k/128k bit or 256-kbit. If the system uses 64 or 128-kbit ROM parts, install links between pins 2 and 3 only of jumpers J5290 and J5291. If the system uses 256-kparts, install links between pins 1 and 2 only of jumpers J5290 and J5291.

## **KERNEL CONFIGURATION.**

There are four links that are used to establish whether the MMU is used in the system and one link that establishes if the FPU is in the system. If the MMU is resident, no links are installed in jumpers J2040-J2042, and J0243. If the MMU is not resident, install a link between pins 1 and 2 of jumpers J2040-J2042, and J0243.

If the FPU is resident in the system, no link is installed in jumper J0250. If the FPU is resident, install a link between pins 1 and 2 of jumper J0250.

## LAN INTERFACE JUMPERS

Three jumpers select which serial interface chip is used for the LAN interface. If the Intel 82501 Serial Interface chip is used, jumpers W8050 and W8051 are installed, and jumper W8052 is removed. If the SEEQ 8002 Serial Interface chip is used, jumpers W8350 and W8351 are removed and jumper W8352 is installed.

# SPECIAL REGISTERS

Refer to the OEM Manual for topics such as software interface, memory maps, system and I/O control and status registers, etc.

# FUNCTIONAL BLOCK DESCRIPTION

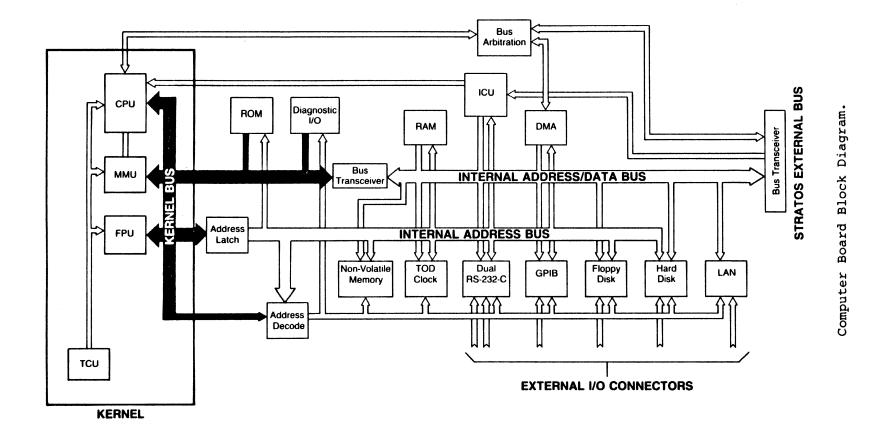

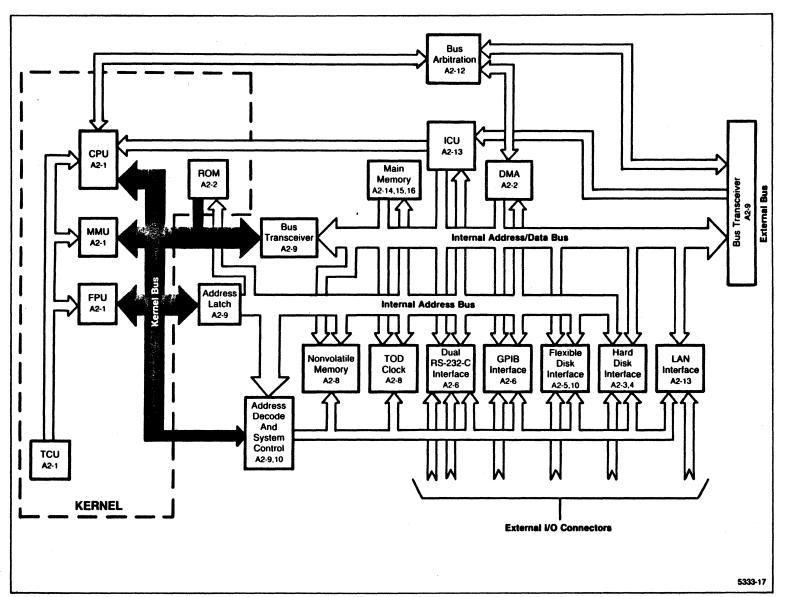

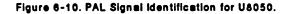

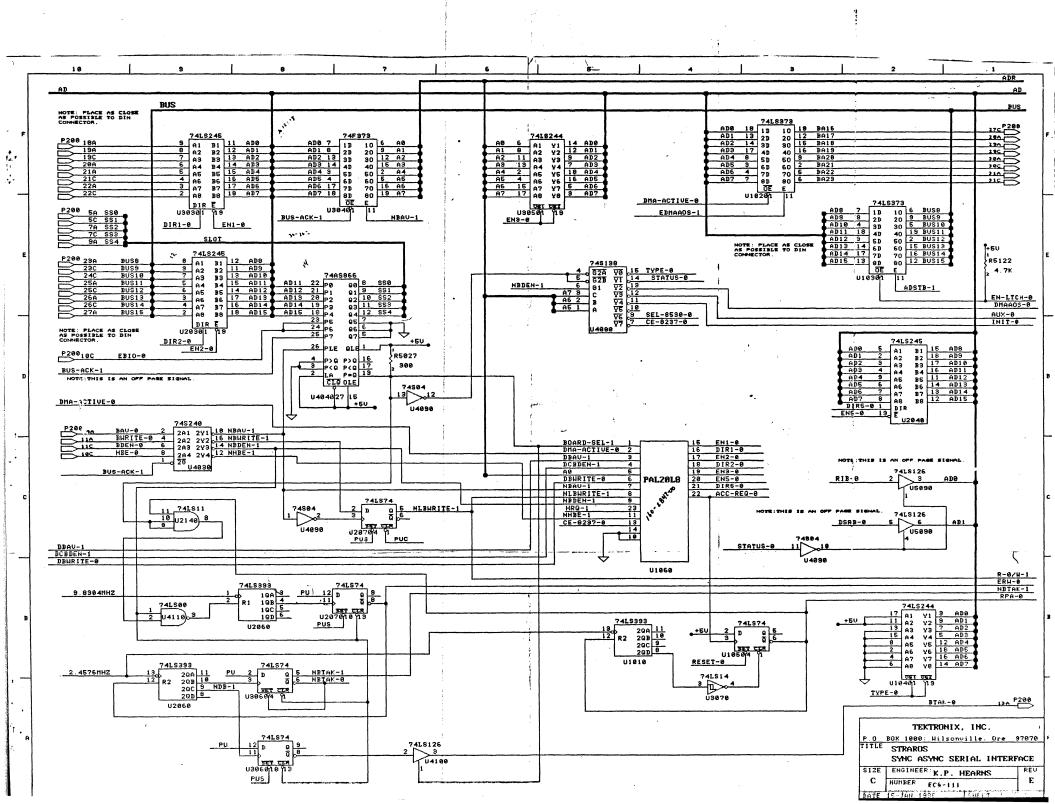

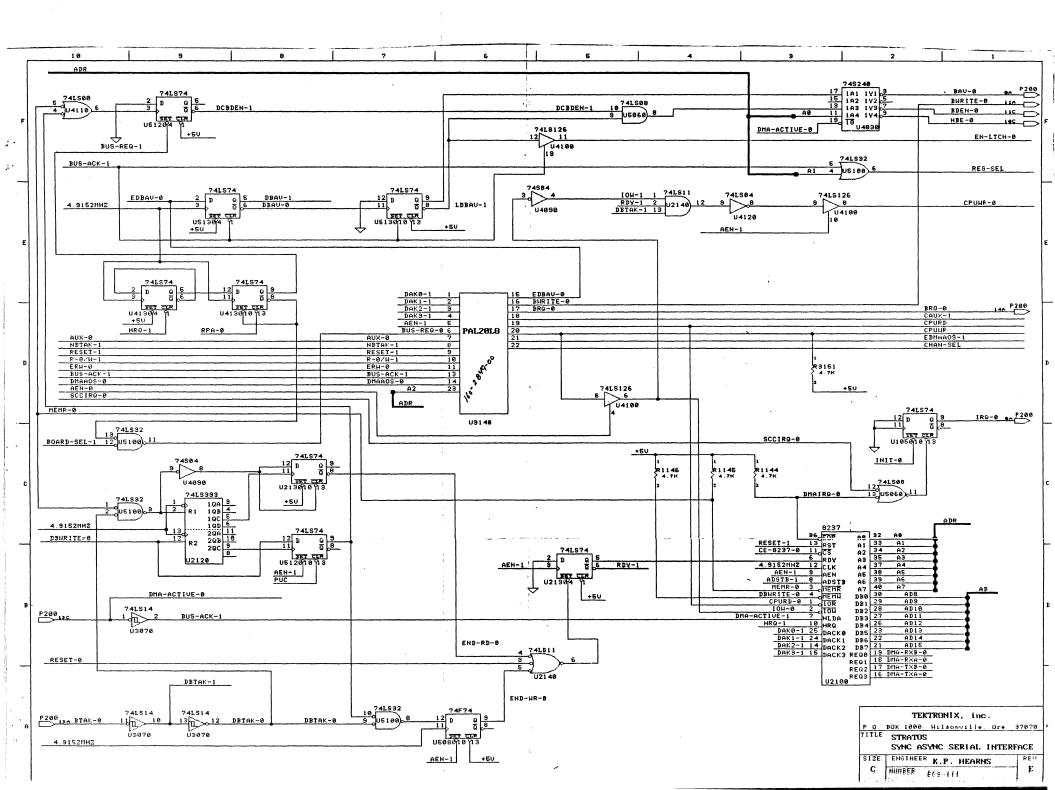

The computer board is divided into several major functional circuit areas or blocks, with each block performing a general function. This section identifies and discusses the operation of each functional block. The bus structures that tie the major functional blocks together are discussed first. The number immediately following the various section titles identifies the schematic page on which that fuctional block of circuitry can be found.

Figure 1-1 is a block diagram showing each of the blocks discussed.

### SYSTEM BUS STRUCTURES

There are four major buffered bus structures that support data transfer between each functional block and throughout the computer board:

#### Kernel Bus

This bus supports data transfer within the kernel and is buffered from the remainder of the system. The kernel is further defined later in this section.

#### Internal Address Bus

The Internal Address Bus (IA Bus) is the latched address portion of the multiplexed Kernel Bus (see page 9 of te schematic diagrams). This bus provides 24-bit addressing for Kernel ROM and main memory as well as the system I/O control decoders. Latching is performed by three 74F373 octal latches.

#### Internal Address/Data Bus

The Internal Address/Data Bus (IA/D Bus) provides the address and data interface between the kernel and the various system I/O devices on the compute engine. Interface between the External Bus and the kernel is also provided by the IA/D Bus. The structure of the I/AD Bus is basically the same as the Kernel Bus: a 24-bit multiplexed address/data bus with the 16-bit data bus sharing the lower 16 lines of the 24-bit address bus (see page 9 of the schematic diagrams). The IA/D Bus is buffered from the Kernel Bus by three 74ALS245 octal bus transceivers.

#### **External Bus**

The External Bus provides the interface between the compute engine and system options. Bus connectors located on the options backplane provide electrical interface. The External Bus primarily an extension of the IA/D Bus. Bidirectional interface for the address/data bus itself is provided by six 74AS373 octal D-type latches and associated bus interface control logic. Interface for the bus-control and protocol signals is provided by two 74F244 octal buffer/line drivers (see page 11 of the schematic diagrams.

#### **KERNEL (1)**

The kernel controls, either directly or indirectly, the major functions for the entire compute engine. As stated above, the kernel is comprised of five major components: the Central Processing Unit (CPU), the Memory Management Unit (MMU), the Floating Point Unit (FPU), and the Timing Control Unit (TCU), and kernel ROM. The FPU is an optional device. Within the kernel, these devices are supported by additional logic. System addressing and memory management/protection is a task that is shared between the CPU and the MMU, while floating point operations are supported by the FPU.

Data transfer within the kernel and with the remainder of the system is via the Kernel Bus, which consists of the multiplexed address and data bus. Another bus apart from the Kernel Bus is the Kernel Timing and Control Bus, which provides the necessary timing, status, and control signals between the primary components.

#### Kernel Bus

The Kernel Bus provides the means of data transfer within the kernel and between the kernel and the rest of the compute engine. All signals on the Kernel Bus are high-active. The Kernel Bus may be sampled at the CPU pinout. Refer to "Central Processing Unit" for CPU pin assignments or page 1 of the schematic diagrams.

Address Bits 16-23. These lines are high-active outputs and are the most significant eight bits of the Kernel Bus address bus. During clock period T1, the bus contains the virtual address output by the CPU. During clock period TMMU, this bus contains the translated, physical address output by the MMU.

Address/Data Bits 00-15. These are the multiplexed, bi-directional address and data lines for the Kernel Bus. All lines are high-active. Bit 00 is the least-significant bit. During clock period TMMU, this bus contains the virtual address output by the CPU. During TMMU this bus contains the physical address output by the MMU. During clock periods T2 through T4, this bus contains data output by the CPU, MMU, memory, etc.

#### Kernel Timing and Control Bus

This bus is local to the kernel and is used to provide control, timing, and coordination of kernel-level operations, including memory management, and the execution of floating point operations. These signals may be sampled at the CPU pinout, which is provided in the following section. Bus signals are defined below:

**Phase 1, Phase 2.** These pins provide two non-overlapping phases of a single frequency, 10megahertz clock, although this clock may be slowed to 5 megahertz for big build. These inputs are taken from the Timing Control Unit. The execution of microinstructions within the CPU or steps in a data transfer over the Kernel Bus is synchronized and controlled with respect to the number of Timing states or T states required to complete the execution. A T state is defined as the wavelength of the Phase 1 clock input. T states are numbered progressively from the beginning of a bus cycle to it's completion.

**Ready-1**. This is a high-active signal that is asserted by the Timing Control Unit at the end of the bus cycle to signal the CPU that the operation is complete. The CPU then terminates the cycle. An external device that requires additional time to finish the bus cycle can request an extension to the TCU. The TCU will then insert a given number of wait states, allowing the device to finish the cycle before asserting Ready-1.

Hold Request-0. This low-active input is asserted by another device (MMU) that is requesting the use of the Kernel Bus. If the CPU complies, the CPU asserts Hold Acknowledge-0 to the MMU, thereby granting the bus to the MMU. Hold Request-0 is asserted for the entire time the MMU has the bus and Hold Acknowledge-0 remains asserted by the CPU until the bus is regained by the CPU. This handshake sequence allows the MMU to acquire the bus and place the translated address on the bus. See the following definition.

Hold Request Acknowledge. This low-active output is asserted by the CPU to grant the bus to another device on the Kernel Bus (MMU). This signal is asserted after the MMU has asserted Hold Request-0. Both signals remain asserted for the duration of the bus cycle, after which the MMU deasserts Hold Request-0 and the CPU regains control of the bus by deasserting Hold Request Acknowledge-0. See the previous definition. **High Byte Enable-0**. This low-active output is asserted by the by the CPU to enable the high byte of the addressed location to be placed on the bus. Memory is organized as two eight-bit banks, with each bank receiving the 24-bit address in parallel. The low bank (bits D00-D07) responds to even byte addresses, that is when the least-significant address bit (A00) is low. The high memory bank (bits D08-D15) is enabled when High Byte Enable-0 is asserted. This feature permits the addressing of individual bytes even though the data bus is 16-bits wide.

**Data Strobe-0/Float-0**. This is a dual-function pin, the function of which is determined by whether or not the MMU is performing address translation or the CPU is addressing the Kernel Bus directly. For bus cycles that are not address-translated, this pin functions as a Data Strobe-0 output from the CPU. Data Strobe-0 is asserted after the multiplexed address/data bus has switched from address presentation to accepting or presenting data. The assertion of Data Strobe-0 validates the data on bus lines AD00-AD15. Since address translation is always performed for every bus cycle initiated by the CPU, Data Strobe-0 is never asserted.

For bus cycles that are address-translated, this pin functions as the Float-0 input to the CPU. The assertion of Float-0 by the MMU causes the CPU to wait longer than the normally allotted TMMU T state for the MMU to perform address translation. This function is employed by the MMU in order for it to update its internal translation cache from page tables in memory, or to update status bits contained within the tables. Timing states are not numbered during a float condition, and the entire bus cycle is placed on a temporary hold. After Float-0 is deasserted, the bus cycle continues from where it was suspended. The Kernel has been implemented such that address translation is always performed by the MMU, although the translated physical address may be the same as the virtual address.

**Reset-0/Abort-0**. This is a low-active, dual-function input. If this signal is asserted during TMMU or TFloat (an address-translated cycle) and held low for one clock cycle, this pin causes an Abort of the bus cycle and the instruction that executed it. The rest of the system remains unaware of the aborted cycle, since the MMU Physical Address Valid-0 address strobe, which triggers the physical cycle, was not yet asserted.

If this pin is held low for at least 64 clock cycles a Reset is initiated.

Address Translation-0/Slave Processor Control-0. AT-0/SPC-0 is a bidirectional, dual function signal. The AT-0 portion of this signal enables address translation by the MMU. The SPC-0 function enables slave processor communications (ie, with the FPU).

The CPU is able to operate with or without address translation. The mode of operation is determined by the presence of the MMU. The MMU asserts Address Translation-0 during reset and at power up. The CPU samples AT-0 on the rising edge of the reset pulse. If the AT-0 is high (no MMU present), bus cycles are performed without address translation. If during reset AT-0 is low, the bus cycle includes an extra clock cycle (TMMU). At this point, the DS-0/FLT-0 signal becomes a Float-0 command input to the CPU (see previous definition of DS-0/FLT-0).

AT-0/SPC-0 is also used as the data strobe in slave processor data transfers. During slave processor data transfers, data is transferred on bus lines AD00- AD15, but no bus control lines other than DDIN-0 (controlled by the CPU) are asserted. For example, ADS-0, HBE-0, ect, are not used. During a slave processor bus cycle, the slave processor samples the CPU status lines ST0 and ST1 on the leading edge of SPC-0. During a data read, SPC-0 remains asserted until data has been read from the slave processor. During a data write, the slave processor latches the status bits on the leading edge of SPC-0 and latches data on the trailing edge of SPC-0. In all slave processor bus cycles, SPC-0 is asserted by the CPU. Refer to Slave Processor Bus Cycles. **User-1/Supervisor-0**. This output is taken from the U bit in the Processor Status Register, which is an internal status register. Asserted high, this signal indicates that the CPU is running in the user mode. Asserted low indicates the supervisor. This signal is sampled by the MMU for mapping and protection purposes.

Address Strobe-0. Address Strobe-0 (ADS-0) is asserted by the CPU when it places an address on the Kernel address bus. Without the MMU, this signal would be used to validate and latch the address. However, with address translation by the MMU, this signal is sent to the MMU only, where it latches the virtual address. The MMU outputs the Physical Address Valid-0 strobe to validate the translated, physical address.

**Physical Address Valid-0**. This MMU output is generated during TMMU and is used as the address strobe to latch the physical address into external memory devices. This signal is also used during a float condition to access the external page tables.

**Data Direction In-0**. Data Direction In-0 (DDIN-0) is output by the CPU or the MMU to specify a read operation (low) or a write operation (high). During normal bus cycle with address translation, this signal is output by the CPU to indicate data direction. During a float condition, the CPU tristates DDIN-0, allowing the MMU to assert DDIN-0 low, thus allowing the MMU to update its page tables from memory. The MMU also controls DDIN-0 when it has control of the Kernel Bus.

**Program Flow Status-0**. This low-active pulse is asserted by the CPU to indicate the beginning of an instruction cycle.

**Status ST0-ST3**. This is a four-bit bus cycle status code that provides status information. The pins are interpreted as a four-bit value, with ST0 as the least-significant bit. Only two bits, ST0 and ST1, are sampled by the FPU during slave processor bus cycles. Refer to the CPU data manual for a definition of each of the codes.

Interlocked Operation-0. This is a low-active output that is asserted during a Set Bit, Interlocked or Clear Bit, Interlocked instruction. This signal is used to reserve the bus in a multiprocessor system that shares resources, in this case, common RAM that the compute engine shares with the display engine.

Non-Maskable Interrupt-0. The Non-Maskable Interrupt-0 (NMI-0) is a low-active input to the CPU.

#### **Central Processing Unit**

The NS16032 CPU (U1280) is the heart of the kernel. This device is configured in a 48-pin, dual-in-line package. The CPU provides a 16-megabyte uniform address space. The CPU's internal architecture features 32-bit data paths, although the data path at the pin-out is 16-bits wide. Refer to page 1 of the schematic diagrams.

The CPU provides 16 registers, eight of which are dedicated control/status registers, and eight general purpose registers. The general-purpose registers are 32-bits in length and are used for general storage requirements, such as storing temporary variables and addresses. The CPU clock frequency is 10 megahertz. As stated previously, data transfer within the computer board is afforded by the Kernel Bus and other bus structures. Within the Kernel however, dedicated data transfer that is transparent to the rest of the system is accomplished via the slave processor bus cycle. Slave Processor Bus Cycles. The slave processor bus cycle permits communication between the CPU and the slave processors (the MMU and the FPU) without executing the Kernel Bus protocol. This type of transfer utilizes the data bus portion (AD00-AD15) but none of the bus control/signals (excluding DDIN-0).

Slave processor bus cycles require only 2 clock cycles or T states (labeled T1 and T4) to finish. At the start of a data read cycle (T1), the CPU places the appropriate status code on lines ST3-ST0 and the appropriate processor identification byte on data line AD00-AD07 of the Kernel Bus. The CPU then asserts SPC-0. Both the FPU and the MMU decode the ID byte and latch the status from the CPU on the leading edge of SPC-0. The appropriate slave processor responds by placing data on lines AD00-AD15 at T4. The CPU reads the data and terminates the cycle by deasserting SPC-0.

During a data write (at T1), the CPU places the appropriate status code and processor ID on data lines AD00-AD07, as before. The CPU then asserts SPC-0 and the appropriate processor responds by latching the status and ID byte. The CPU then removes the ID byte from the Kernel Bus and places data on the bus. The data is latched by the slave processor on the trailing edge of SPC-0 as it is deasserted (T4). At the end of a data write, the slave processor signals a successful transfer by pulsing SPC-0 low.

Since ADS-0 is not asserted by the CPU, none of the other associated bus protocol signals are asserted. The CPU, however asserts DDIN-0 as appropriate. In both of the above cases, the status code is set up by the CPU during the previous clock cycle.

#### Memory Management Unit

The NS16082 Memory Management Unit (MMU) (U1300) provides support for demand-paged virtual-memory management. The chip, in concert with the CPU, permits rapid address translation and protection on individual 512-byte memory pages. The chip uses a associative cache that stores the 32 most frequently used memory page table entries. The MMU is packaged in a 48-pin, dual-in-line configuration. Refer to page 1 of the schematic diagrams.

Memory Management. For addressing purposes, memory is divided into several 512-byte pages. Associated with each page of memory are page tables that the MMU and the operating system maintain in physical memory. The page tables contain information pertinent to each memory page, such as the page access permission codes, whether the page has been accessed, and if it has been written to. Also contained in the page tables are values that are used to arrive at the physical address. The MMU executes a translation algorithm that determines the validity of the access and provides the physical address. Of the virtual address provided by the CPU, the least-significant 9-bits are not modified. These 9 bits provide discrimination to the byte level within the 512-byte page.

By modifying the page tables as required, the operating system controls the mapping of virtual addresses to physical memory. Additionally, the operating system can control the degree of access (read or read and write) permitted to specific pages in the supervisor and user modes by generating translation error aborts if access permission codes are violated.

The most frequently referenced or accessed page tables are stored by the MMU in an internal cache memory, thus saving the MMU from having to retrieve the page table from memory for the majority of accesses. The cache contains 32 page table entries. If during a bus cycle, the given access is not a "hit", the MMU asserts the Float-0 signal to the CPU, which temporarily suspends the bus cycle while the MMU retrieves the page table from physical memory via the Kernel Bus. Once the page table entry has been retrieved, the least-used entry is removed from the cache and the newest entry is placed in the cache. The Float condition is terminated and the bus cycle continues from where it was suspended.

All bus cycles initiated by the CPU are address-translated, however in some cases the translated, physical address may equal the virtual address placed on the Kernel Bus by the CPU.

#### **Floating Point Unit**

The NS16081 Floating Point Unit (FPU) (U1260) operates as a slave processor and performs both single precision (32-bit) and double precision (64-bit) arithmetic. This device is packaged in a 24-pin configuration. Data transfer between the CPU and the FPU is not accomplished using the normal Kernel Bus protocol, but the slave communications protocol described previously. The FPU contains 9 32-bit registers, eight of which are general-purpose. The ninth register is a status register. Refer to the FPU data sheet for additional information and page 1 of the schematic diagrams.

#### **Timing Control Unit**

The NS16201 Timing Control Unit (TCU) (U0320) is a 24-pin DIP that provides the twophase 10 megahertz clock output based on the 20 megahertz crystal frequency, as well as several signals that support Kernel Bus logic, timing and control functions. The TCU also provides for a variety of bus cycle extensions to compensate for slower devices (compute engine or peripheral devices). Refer to the TCU data sheet for additional information and page 1 of the schematic diagrams.

#### Kernel ROM (2)

Up to 128 kbytes of Kernel ROM are provided by four 256-kbit (32k x 8) EPROM chips (U3280, 3300, 4280, and 4300). Kernel ROM is organized as two, 64-kword banks. Lesser total capacities are 64 kbytes and 32 kbytes, depending on chip density. Addressing is provided via the Internal Address Bus, which is the latched address portion (AD00-AD15) of the Kernel Bus, while ROM data is placed directly on the Kernel Bus data bus. Refer to page 2 of the schematic diagrams. Kernel ROM is discussed further in Section Five of the TEK6100 Series OEM Manual.

#### **NON-VOLATILE MEMORY (8)**

This block consists of two 256-bit, non-volatile, sequential-access EEPROMs (U143, U144) and a Non-volatile-Memory Control Register (U108). Each memory chip is organized as 16 registers containing 16 bits each. Each register is read from serially.

#### MAIN MEMORY (14)

Main memory provided on the computer board consists of up to 1 megabyte of dynamic RAM using 256-kbit parts, or 256 kbytes using 64-kbit parts. The board contains a maximum of 36 RAM chips, each of which is organized in a 256 k by 1-bit or 64 k by 1-bit format. On the board, memory is organized as two rows, each containing a maximum of 18 chips. Each memory row is two-bytes wide plus one parity bit per byte. Jumpers that select the chip density and board capacity, as well as whether or not the sytem is equipped with an expansion memory board, are discussed in the a previous section of this document, titled Board Configuration.

The computer board contains logic that provides support functions for the RAM. These functions are: memory access and refresh timing, memory addressing, and parity generation and error detection.

#### Memory Access and Refresh Timing (13)

This logic coordinates the memory refresh cycle, which is performed every 12.5 microseconds, and normal memory accesses. The Refresh Clock operates a 80 KHz and initiates a memory refresh cycle on the rising edge of the clock pulse, at which time various status lines that indicate an impending data transfer are sampled. If the status lines are asserted, the refresh is postponed until the data transfer is completed. When refresh is in process, memory access are locked out until the refresh is completed.

This logic employs a 200-nanosecond delay line to establish memory-access and refresh-cycle timing. The data read cycle from memory requires approximately 400 nanoseconds, whereas a data write cycle from memory can be extended beyond 400 nanoseconds.

This logic supports a distributed refresh method whereby only one memory row is refreshed per refresh cycle. The next refresh cycle increments the refresh address counter by one in preparation for that cycle. The counter is incremented on the trailing edge of the Refresh Clock. After the new row address has been placed on the Memory Address Bus (MA Bus), the Row Address Strobe (RAS-0) is pulsed, refreshing the 512 memory-bit locations in that row. With 256 k-byte parts, 512 refresh cycles are required for a full memory refresh.

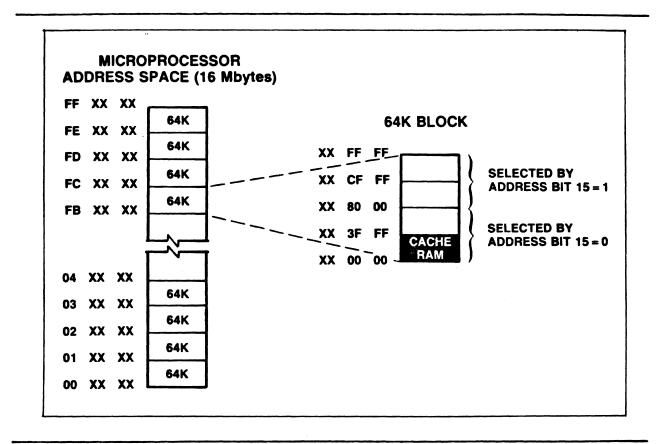

#### Memory Addressing (14)

This block samples the IA/D lines 18-23 to determine if the bus cycle is a memory access, in which case the impending refresh cycle is may be postponed until the end of the data transfer. This block also provides the multiplexing required to place the 16-bit address word (IA/D01 - IA/D16) on the 9-bit Memory Address Bus (MA0 - MA8), as well as the Row Address Strobe-0 (RAS-0) and Column Address Strobe-0 (CAS-0) synchronization required to latch the address into memory.

#### Parity Generation and Checking (14)

This block utilizes two parity generators/checkers and associated logic to generate and store an odd parity bit for each byte during a memory write operation, and to check the stored parity bit during a memory read. If an error is detected during a read, a Parity Error signal is generated, as well as a bit defining whether the error applies to the high or low byte. A Parity Error Register, which is continually loaded with the current memory address, is used to provide the address of the faulty memory location. A brief description of the operation of the parity generation and checking logic for the high byte is given below:

During a memory write, the high data byte from the IA/D Bus is input to the U25 parity generator/checker. At this time, the octal D-type latch U140 is disabled by status signals that are set as a function of the type of data transfer, read or write. Nand gate U139 outputs a high at pin six, and the parity generator U25 generates even parity for the data byte plus the additional high bit input at pin 4. This parity bit is equivalent to odd parity for the data byte, and the parity bit is stored with the byte in memory.

During a memory read, the octal latch U140 is enabled and the stored parity bit is inverted by nand gate U139 and input at pin four of parity generator U25. U25 generates parity for the data byte plus the inverted parity bit. If the stored bit or the data byte is in error by one bit, the parity checker generates an even-low parity bit, thus signaling a parity error.

## SYSTEM CONTROL BLOCK (9)

The system control block provides the system I/O enables and control signals required to enable DMA transfers via the various I/O devices, as well as the enables for the System Control Register and the System Status Register. These enables are arranged as memory-mapped I/O locations in the kernel's external memory space. This logic consists primarily of two 74F138 3-to-8-bit decoders.

This block also contains the System Control Register (octal D-type flipflop U18) and the System Status Register (octal D-type flipflop U19), along with the enables required to drive these registers (as given above).

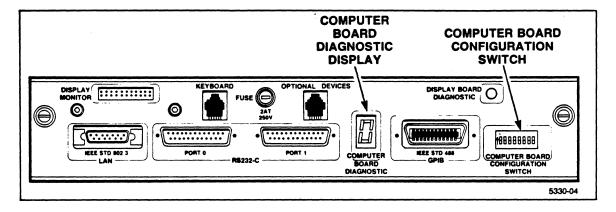

The system control block also provides a mechanism for low-level debugging of the board. This consists of a diagnostics switch register and a diagnostics display register. The switch register is a 8-switch DIP that corresponds to lines AD00-AD07. The setting of the switch is read by enabling 74F244 octal buffer U16 (address FFF008). Diagnostic information is displayed by a write to the same address. An 74LS273 octal D-type flipflop performs as the display register. The D outputs (AD00-AD06) correspond to segments A-G of a seven-segment display. Bit AD07 drives the decimal point.

## **FLOPPY DISK INTERFACE (4, 10)**

The floppy disk interface is composed of two major LSI components: the WD1770 Floppy Disk Controller (U7020) and the AM9516 DMA Controller (U8290), along with supporting logic. The WD1770 is a floppy disk controller and formatter and also contains digital data separation logic and write precompensation circuitry. The WD1770 is a 28-pin DIP. There are six registers within the floppy disk controller that allow the Am9516 DMA controller to execute data transfer between the disk controller and the DMA controller. These registers contain command and status information, various head positioning information, and 8-bit data. Interface between the two controllers is via an 8-bit bidirectional data bus and various control signals.

The DMA controller (page 10 of the schematic diagrams) is equipped to handle two separate channels although only one DMA channel (channel B) is used. DMA operations are initiated by the kernel by loading DMA control parameters into a control block known as the Channel Control Table. The Channel Control Table is maintained by the kernel in main memory. The kernel then places the starting address of the Channel Control Table in the Chain Address Register (internal to the DMA controller) and issues a "Start Chain" command to the controller. The DMA controller responds by updating its various internal control registers with the control parameters located in the Channel Control Table. The Channel Control Table contains such information as what specific registers are to be updated or reloaded, the source data address, the destination data address, ect.

"Chaining", allows the several DMA transfers to be performed asynchronously. This method places the address of the next Channel Control Table in the within the previous table, so that when a given DMA operation is completed, the DMA controller reads the new address of the control table, updates internal control registers with the table, and executes the new command.

The DMA controller also performs byte/word alignment between the 8-bit disk data bus and the 16-bit IA/D Bus. As mentioned before, the System Control Block provides the address decoding required to access the floppy disk interface.

#### Erroneous ALE Detection Logic

Logic associated with the AM9516 DMA Controller includes erroneous ALE detection logic. This consists of the D-type flipflops U6041, U6130 and associated logic. This logic was implimented in order to detect and void or cancel the erroneous assertion of Address Latch Enable-1 by the controller. This logic differentiates between chain operations and single data transfers. Note that this interface allows only single data transfers per bus-request/busrelease cycle. This logic operates as follows:

The Normal/System-0 output from the DMA Controller is programmed to be asserted high when data is being transferred between the controller and the host. During a data transfer, ALE is asserted by the controller to the Kernal Bus as Kernal Physical Addrss Valid-0 (KPAV-0). When data is placed on the bus, Normal is asserted by the DMA Controller, which is clocked through U6041 as NOALE-0. NOALE-0 disables AND gate U3140 and Quit ALE-1 (QALE-) deasserts KPAV-0 to the Kernel Bus.

During chaining operations, System-0 is asserted by the DMA Controller, which is clocked though U60410 and U6130 as Hold Bus-0 (HLDBUS-0). In this case, Bus Request has been released and there is no data strobe. Disk Data Strobe-0 is asserted as Memory Data Strobe-1 (MDS-1) in order to complete the bus cycle. Since the DMA Controller is executing reads from memory during chaining operations, memory data is not affected.

# HARD DISK INTERFACE (3)

The hard disk interface is composed primarily of the WD1010 Winchester Disk Controller (U7100), an external 4-kbyte cache, a DP8460 data separator and a Hard Disk Control Register.

The controller performs the normal functions of a hard disk drive controller/formatter, although it does not feature write precompensation and this logic (consisting of quad D-type flipflop U47, delay line U51, and data multiplexer U52) is implimented externally.

On the drive side of the controller, the data separator receives MFM encoded data from the disk drive and separates this data into synchronized data (SDATA) and a Read Clock (RCLK) signal. The disk controller decodes this serial data from RCLK into 8-bit parallel data. During a write to the disk, data is MFM-encoded by the controller.

#### Disk Data Cache

On the host side of the controller, the 4-kbyte cache is a serial, disk-data transfer buffer that is accessible by the disk controller or the kernel. The buffer appears to the kernel as a 2kword (16-bits) sequential-access buffer. The buffer itself consists of two 2048 x 8-bit static RAM chips, U156 and U157. This buffer and octal bus transceiver U159 also serve as a data assembler/disassembler in that data is transferred between the kernel and the buffer in 16-bit words, whereas data transfer between the buffer and the disk controller occurs in 8-bit bytes.

Buffer addressing is performed by two dual, four-bit binary counters, U155 and U99. Only half of U99 is used. During a data write to the disk, the kernel clears the buffer by setting the Manual Clear bit in the Hard Disk Control Register (octal D-type flipflop U158). This generates the Counter Clear (CCLR) output of the Buffer Control Programmable Array Logic (PAL) chip U44, which clears the counter. As each 16-bit word is loaded into the buffer, the counter is incremented by the Counter Clock (CCLK) output of PAL U44, which develops the clock from the Data Strobe-0 input. When the kernel has loaded the buffer, the kernel writes a Manual Ready-1 signal to the controller via the PAL (input to the controller as Hard Disk Buffer Ready-0 (HDBRDY-0)). The controller then clears the buffer counter and transfers the contents of the buffer to disk, incrementing the buffer address counter as each 16-bit word is read. Since the buffer is organized as two 2k x 8-bit chips, each byte can be read individually by the controller. This is permitted by the bus transceiver U159, which multiplexes both the high and the low bytes of the buffer onto Hard Disk Data lines 0-7 (HDD0-HDD7).

During a data read from the disk, the controller clears the buffer address counter and begins loading the buffer. This time the bus transceiver operates in reverse fashion, demultiplexing the 8-bit data from the controller into the high and low bytes prior to loading into the buffer. CCLK is generated by Buffer Chip Select-0 output from the controller, via the PAL. When the controller-to-buffer transfer to completed, the controller signal the kernel by asserting Hard Disk Interrupt-1. The kernel proceeds to read the contents of the buffer, by first resetting the buffer address counter and then incrementing the counter with each word read.

Two 74LS245 bus transceivers (U45 and U46) serve to buffer or isolate the IA/D bus from disk/cache data. As given previously, the System Control Block provides the address decoding required to enable data transfer via the hard disk interface.

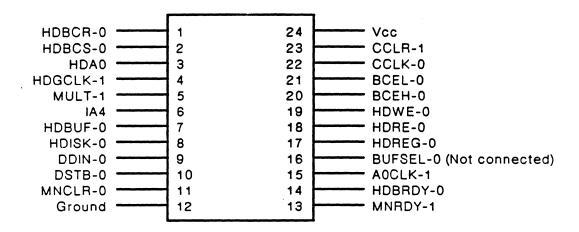

#### **Buffer Control PAL**

The Buffer Control PAL (U8050) controls the operation the disk data buffer and the data buffer address counter. Inputs to the PAL are from the disk controller and the system control logic (address decode). Outputs drive the buffer chip enables, address counter, and Controller Ready-0 line.

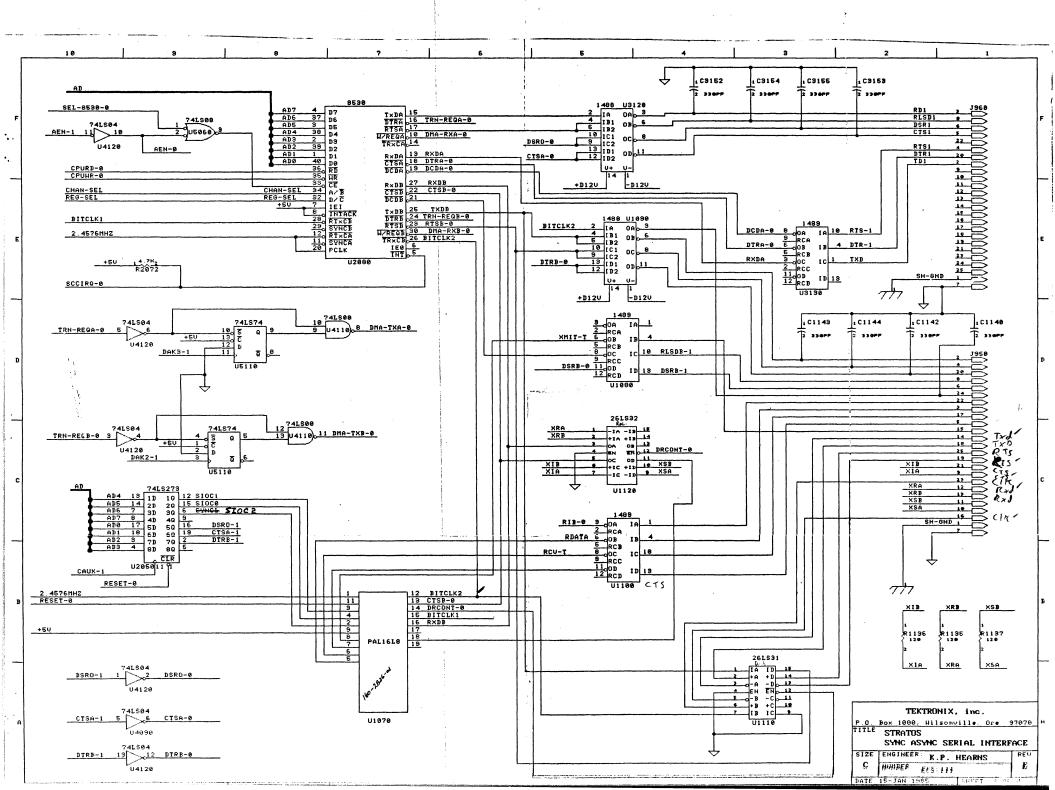

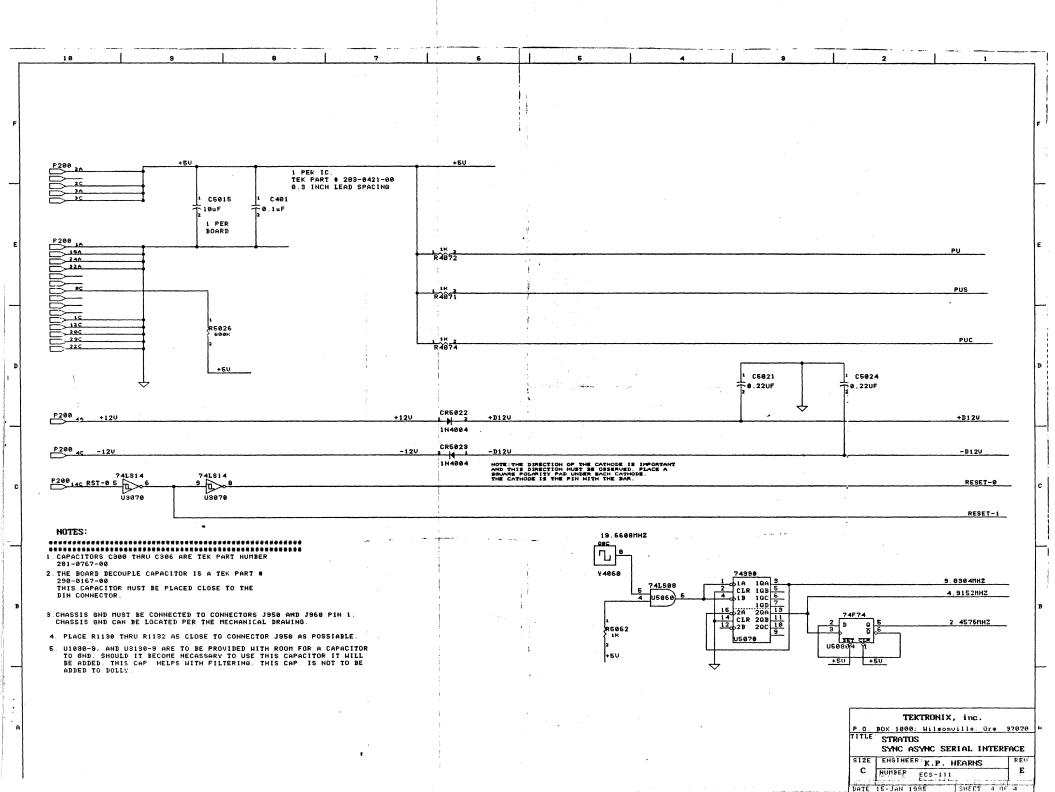

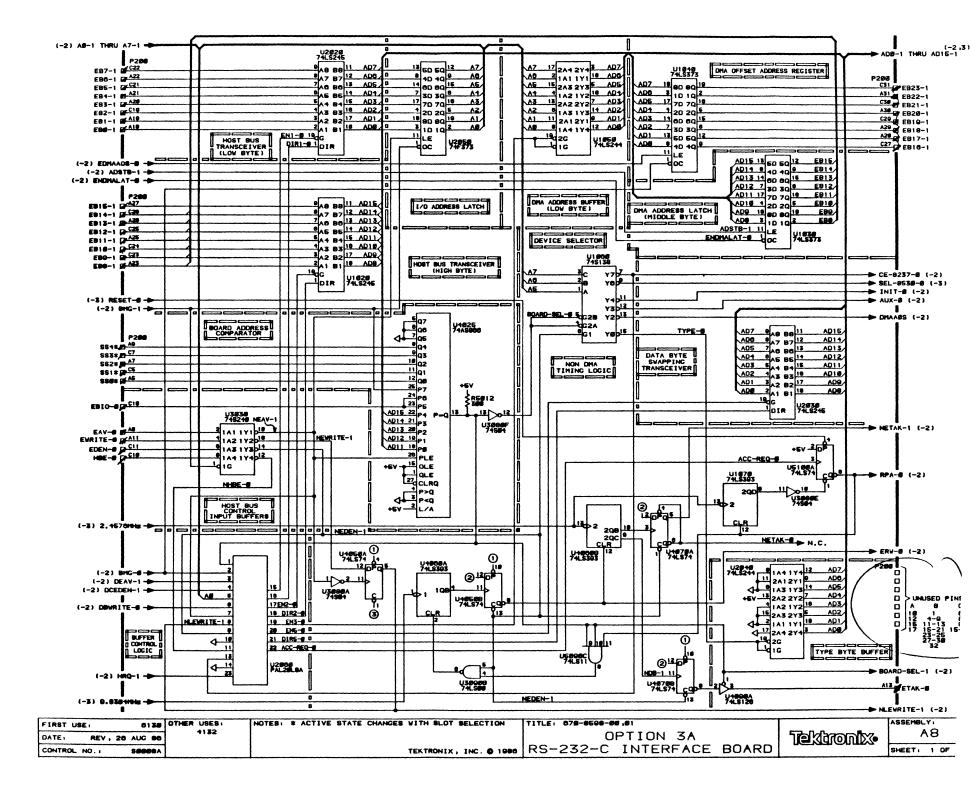

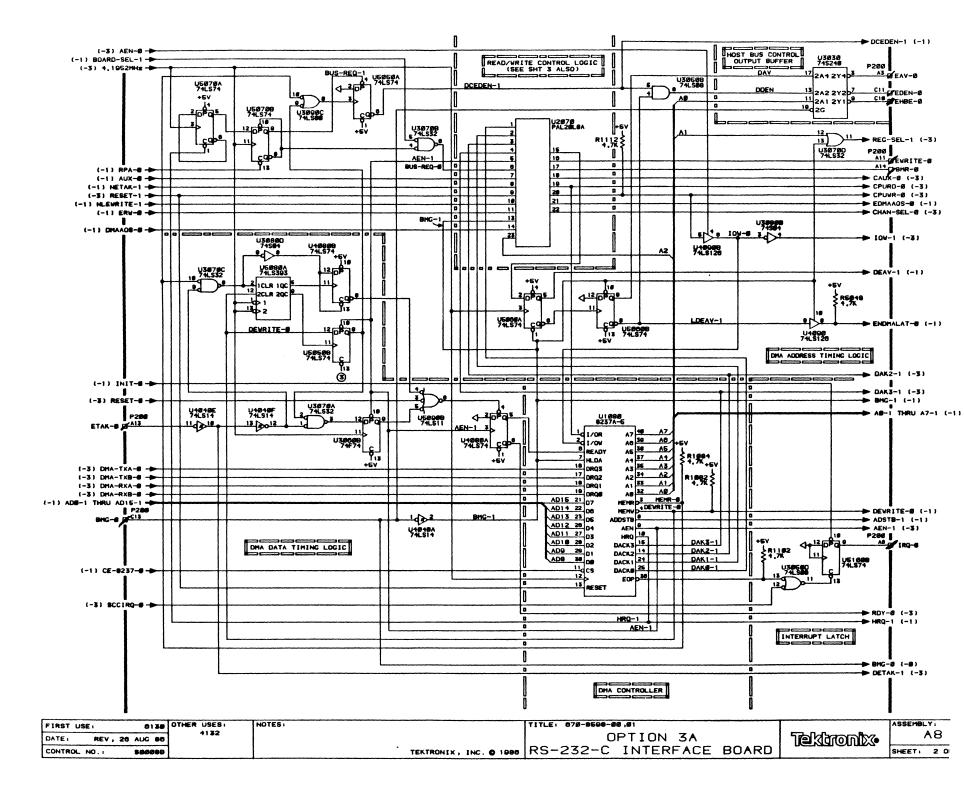

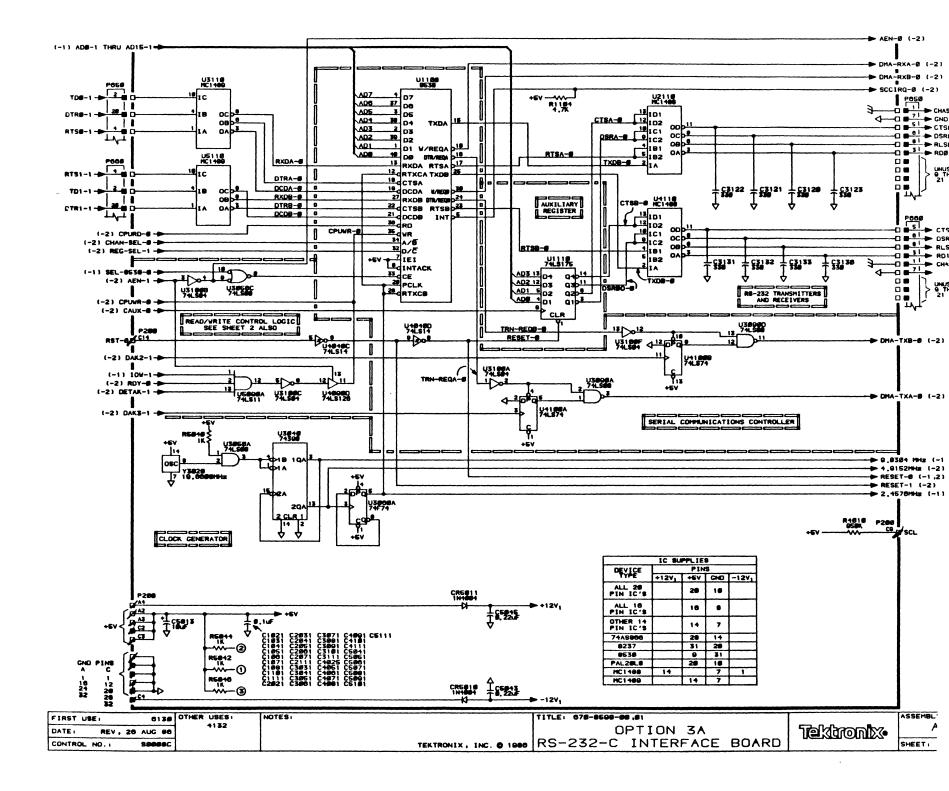

## **DUAL RS-232-C INTERFACE (5)**

The RS-232-C interface is a dual-channel, serial asynchronous DCE port that utilizes the AM8530 Serial Communications Controller (U6340). The output driver for each port is a DS1488 transmission line driver. The receiver for each port is DS1489 transmission line receiver. All configuration, control, status, and data registers are internal to the controller. Serial port enables are address-decoded by the System Control block. A 4 MHz clock developed by the clock generator is supplies to the controller.

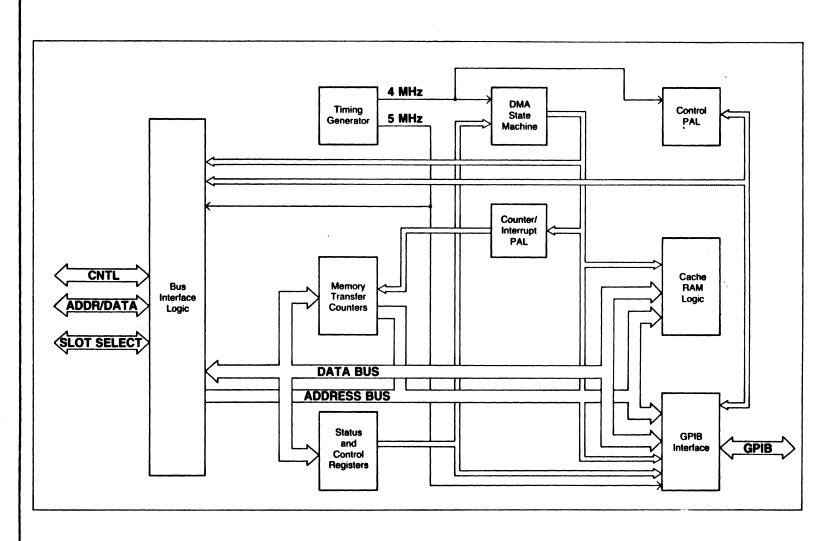

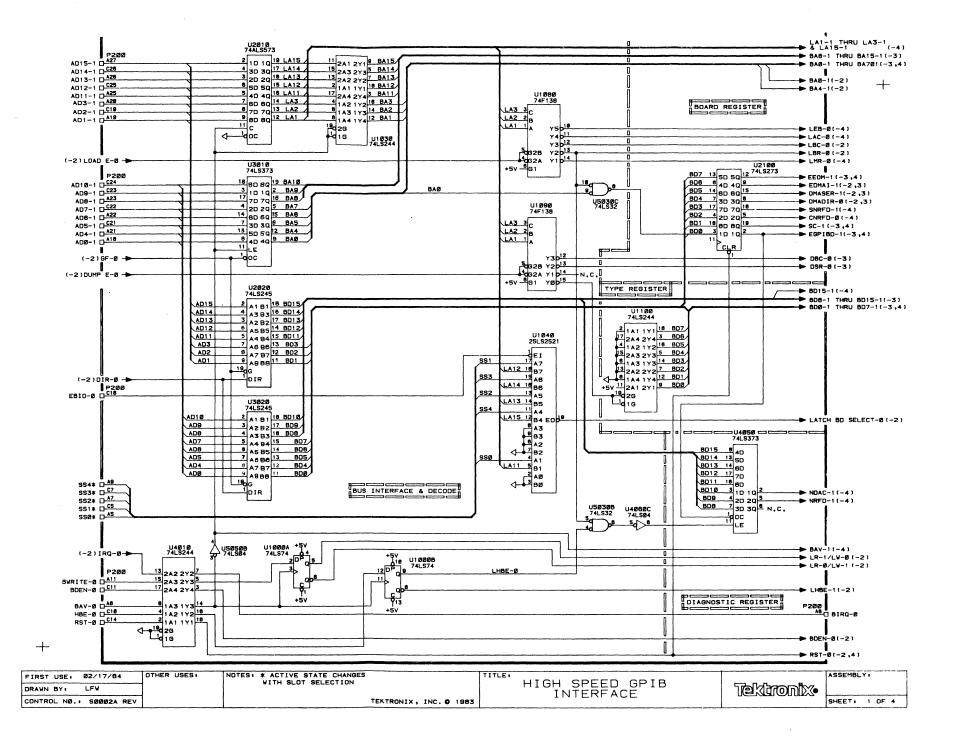

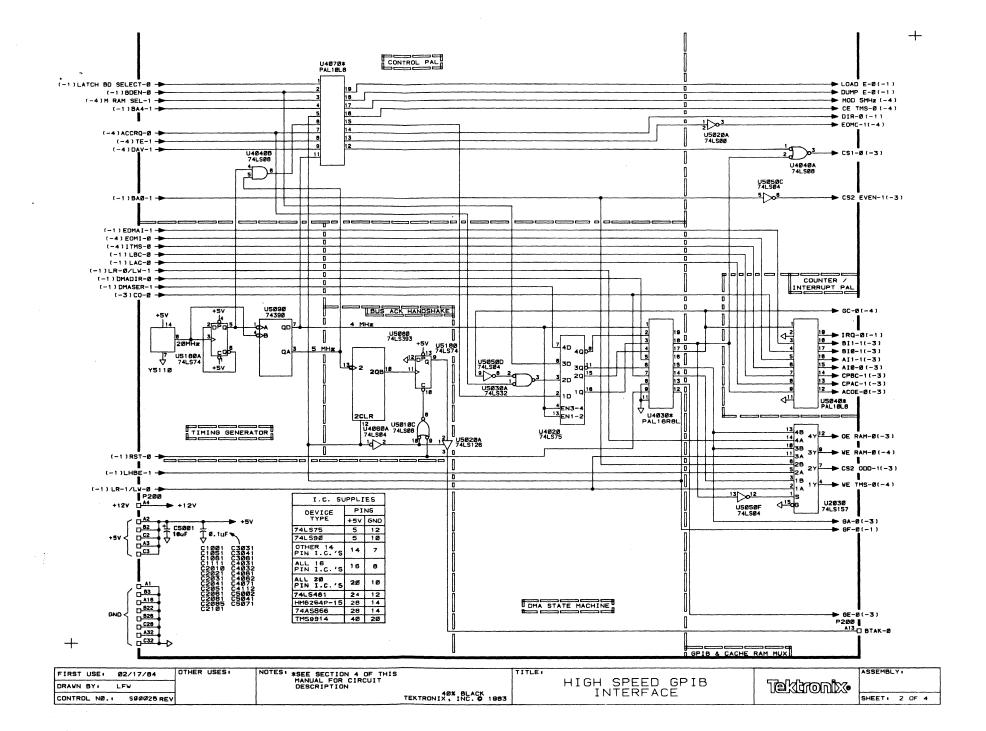

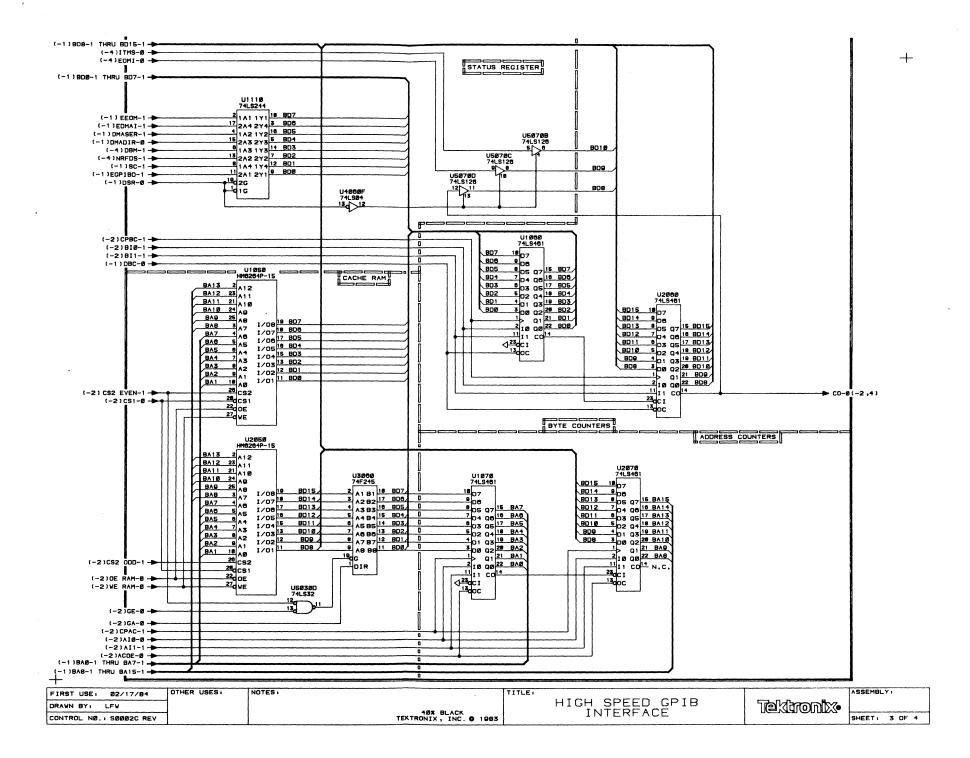

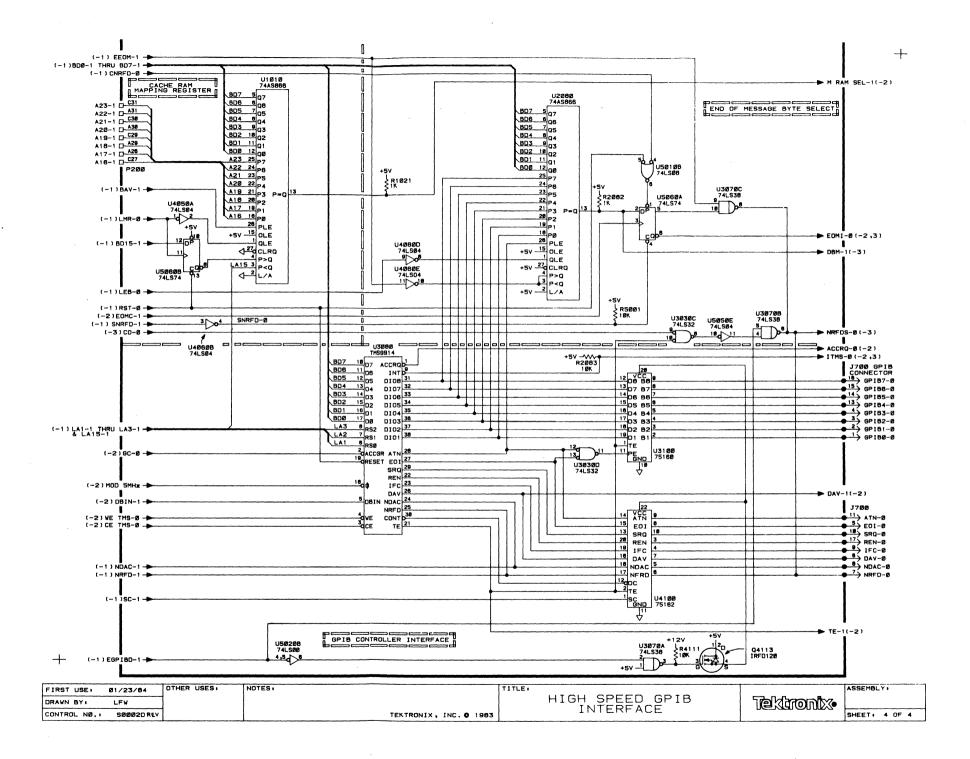

## **GPIB INTERFACE (6)**

The GPIB interface utilizes the TMS 9914 GPIB Controller and the SN75160 and SN75162 bus transceivers. This interface supports talker, listener, and controller functions. This design does not incorporate DMA support and the transfer rate is limited by the speed of the programmed data transfer. System control of the bus is provided via a GPIB Control Register (U36), which is a 74LS174 hex D-type flipflop. The System Control Block provides the address decoding required to enable GPIB I/O operations.

Communication between the controller and the kernel is performed via 13 memory-mapped registers that contain status and control information, data. These registers are contained within the controller. Three Register Select lines (RS0-RS2) address one of eight possible locations, each of which contain one read and/or one write register. Register selection within the addressed location is a function of the operation: read or write.

On the host side of the controller, data interface is 8-bits wide over lines IA/D0-IA/D7. As stated previously, there is no DMA support for this port.

The 75162 octal bus transceiver U35 drives and receives the GPIB control bus lines, while a 751600 octal bus transceiver U34 drives and receives the 8-bit port data.

The GPIB Control Register contains a GPIB Enable bit (bit IA/D0) that disables the GPIB bus transceivers and also enables the bus buffer gate U98. U98 permits the kernel to test the GPIB protocol sequence of the TMS9914 controller by writing test bits to the control register.

# LOCAL AREA NETWORK INTERFACE (12)

The Local Area Network (LAN) interface consists primarily of the 82586 LAN Controller (8310) and the 82501 Serial Interface Chip (U9370). The primary function of this port is to provide an interface between system memory and the LAN link. The host initiates a transfer over the LAN by the writing the transfer parameters to a control block residing in system memory. Once the control block is configured, the host toggles the Channel Attention line to the LAN controller by writing the appropriate address to the system control decoders. This causes the LAN controller to copy the contents of the control block into internal memory and execute the command. The controller is a bus master of the IA/D Bus and most of the DMA transfers are executed with the LAN directly accessing system memory. For this purpose, 256 kbytes of system memory are reserved for the LAN. The LAN interface is tested via the System Control Register. Refer to page 12 of the schematic diagrams.

The 82501 Serial Interface chip provides the 10 MHz transmit clock for the 82586 controller, performs the encoding/decoding of the transmitted/received frames, and provides the electrical interface for the Ethernet transceiver cable.

# **INTERRUPT CONTROL**

The Interrupt Control Unit (ICU) and associated logic provide interrupt management for the CPU. This logic handles up to 15 prioritized interrupt sources from the various intelligent I/O devices within the system. Six interrupt lines handle computer board I/O devices, two lines handle the MMU and FPU, and seven interrupt lines are reserved for optional devices operating on the External Bus. The ICU resolves interrupt priorities and issues a byte-wide interrupt vector to the CPU. This device is configured in a 40-pin DIP configuration. Refer to page 12 of the schematic diagrams.

# **EXTERNAL BUS INTERFACE**

This block provides the interface between the Interal Address/Data Bus and the External Bus. The block consists of primarily of a Bus Interface Control PAL (U6290), six octal D-type latches used as bus buffers, Bus Timeout Logic, and associated logic. The Bus Interface Control PAL monitors various system status and control signals and controls the direction and enable signals required to control the bus buffers.

#### Bus Timeout

This block also handles bus timeout control. The bus timeout counter is started by the assertion of System Address Strobe-1 (SAS-1) and is clocked by a 400 KHz clock. The counter is cleared by the normal execution of the bus protocol within the time required. The counter is also cleared by a reset. The bus-timeout period is approximately 10 microseconds. The complete bus-timeout cycle takes about 20 microseconds; 10 microseconds are alloted for the faulty DMA device to release the bus after the associated Bus Grant signal has been deasserted by the host.

#### **DMA ARBITRATION (2)**

This block performs DMA arbitration for the six available External Bus options slots, and the computer-board based LAN port and floppy disk drive interface. Each bus-request line is weighted at a particular priority level. Simultaneous External Bus bus requests are arbitrated according to the priority level assigned to each request line and a bus-grant signal is issued to the arbitrated requester. This block also generates a 4-bit code (via the 74LS140 8-to-3 line encoder U70) that is loaded into the System Status Register and indicates the most recently used DMA channel. This code is used after a bus timeout to identify the faulty DMA device.

#### **DMA** Arbitration PAL

DMA arbitration is performed by a 24-pin DMA Arbitration PAL (U1230) and associated logic. The PAL monitors the various prioritized bus-request signals from the External Bus option boards, the floppy disk DMA controller, and the LAN interface, and issues a bus grant to the highest-priority requester.

#### **CLOCK GENERATION (7)**

The clock generation logic develops most of the clock pulses required by the system. The primary clock source is a 20 MHz clock taken from a crystal oscillator. Three 74LS390 4-bit counters divide this pulse into a 10 MHz clock, a 1 MHz clock, an 80 KHz refresh clock, and a 200 Hz ICU clock. A secondary crystal oscillator operating at 16 MHz is used to develop an 8 MHz clock and a 4 MHz clock.

#### **Reset Pulse Stretcher**

Resets are generated by any device on the External Bus, the power supply, and the Interrupt Control Unit. All resets pulses are expanded by 2 milliseconds by the pulse-stretching logic shown on page 7. This logic consists binary counter U6301, quad nand gate U6270 (shown in four locations), and inverter U6320. U6301 is employed as a flipflop that is set when Received Reset-0 (RRSET-0) is first asserted. Two milliseconds later the counter U6301 resets the flipflop, which desasserts External Reset-0. Reset signals from the ICU (Insane-0) and power supply (PSINIT-0) are placed on the External Reset-0 path. This allows them to be input to the clock generator block as Received Reset-0, and the Reset Pulse Stretcher operates in the same fasion as described above.

#### TIME-OF-DAY CLOCK (9)

This block consists of a MM58167 microprocessor-compatible real-time clock and a 32.768 KHz reference crystal oscillator. The clock contains a real-time counter, 56-bits of RAM, two interrupts, and a comparator. The RAM is used during power-down storage and as the alarm latch for comparison to the counter. Address interface with the CPU is via the five low-order bits (IA0-IA5) of the latched Internal Address Bus. Data interface with the CPU is via the low byte of the Internal Address/Data Bus. Battery back-up is provided for the clock by a 3 volt, 1200 milliampere/hour lithium battery and associated power-fail logic.

# **EXPANSION MEMORY BOARD**

#### Page

| Introduction                      | 3-1 |

|-----------------------------------|-----|

| Expansion Memory Board Overview   |     |

| Board Configuration               |     |

| Functional Block Description      | 3-1 |

| External Bus Interface Logic      |     |

| Memory Address Decode Logic       |     |

| Control and Status Register       |     |

| Memory Access and Refresh Timing  |     |

| Refresh Logic                     |     |

| Parity Generation and Check Logic |     |

| Memory Address                    |     |

| Memory Data Buffer                |     |

| Memory                            |     |

| •                                 |     |

## **ILLUSTRATIONS**

| No.        |                                                                                                     | Page |

|------------|-----------------------------------------------------------------------------------------------------|------|

| 3-1<br>3-2 | The Control and Status Register During CSR Write<br>The Control and Status Register During CSR Read |      |

Fig.

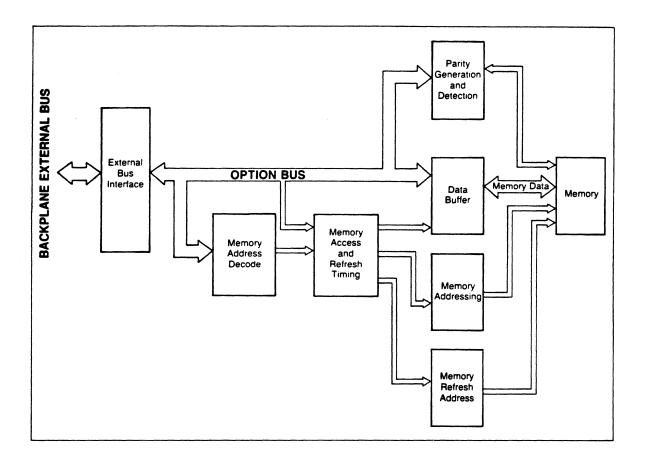

Expansion Memory Board Block Diagram.

# **EXPANSION MEMORY BOARD**

# **INTRODUCTION**

This section discusses the use and operation of te Expansion Memory Board for Big Build. This discussion does not necessarily apply to the final production product. This contents of this section are organized as follows:

- Expansion Memory Board Overview"

- Board Configuration

- Functional Block Description

# **EXPANSION MEMORY BOARD OVERVIEW**

The Expansion Memory board is a double-width option board that provides additional main memory for the TEK6100 workstation. The amount of memory provided by the board is dependent on the density of the memory chip used. Using 64K X 1-bit memory chips provides 256K bytes of memory in a fully populated board. Using 256K x 1-bit chips provides 2 megabytes on a fully populated board. (The Big Build version of this board uses 64-kbit chips only)

# **BOARD CONFIGURATION**

The Big Build version of this board will use 64-kbit chips only. If necessary, refer to the schematic diagrams for jumper information. Additional configuration information will be provided at a later date.

# FUNCTIONAL BLOCK DESCRIPTION

The Expansion Memory board is comprised of eight major functional blocks that are listed below and discussed in the following paragraphs:

- External Bus Interface Logic

- Memory Address Decode Logic

- Memory Access and Refresh Timing

- Refresh Logic

- Parity Generation and Check Logic

- Memory Address Logic

- Memory Data Buffer

- Memory

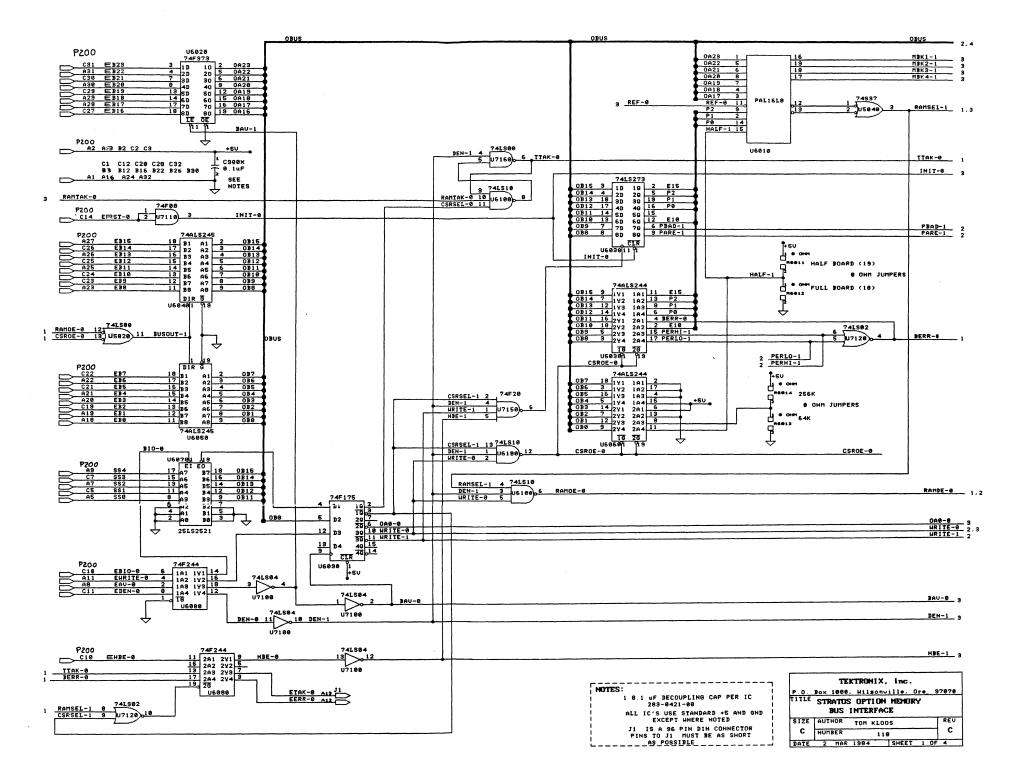

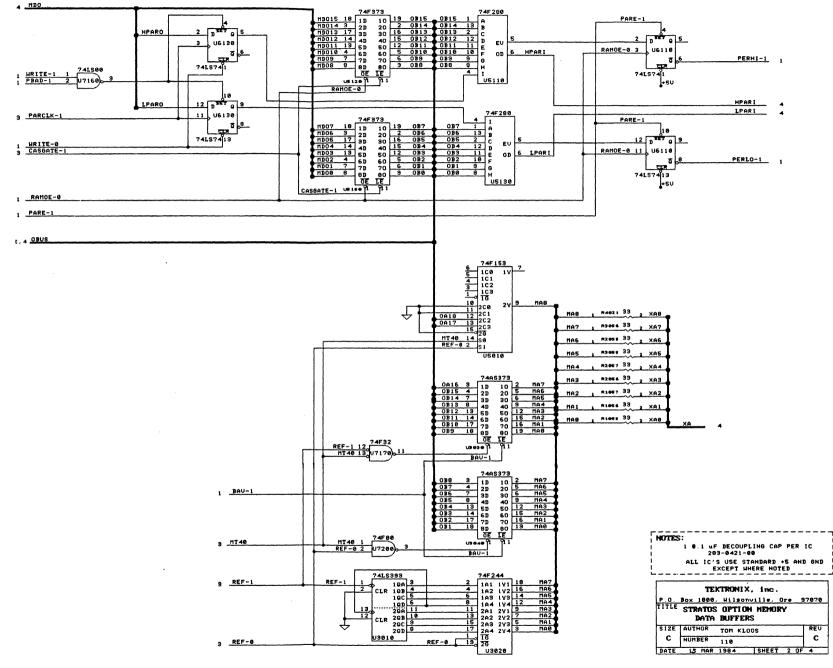

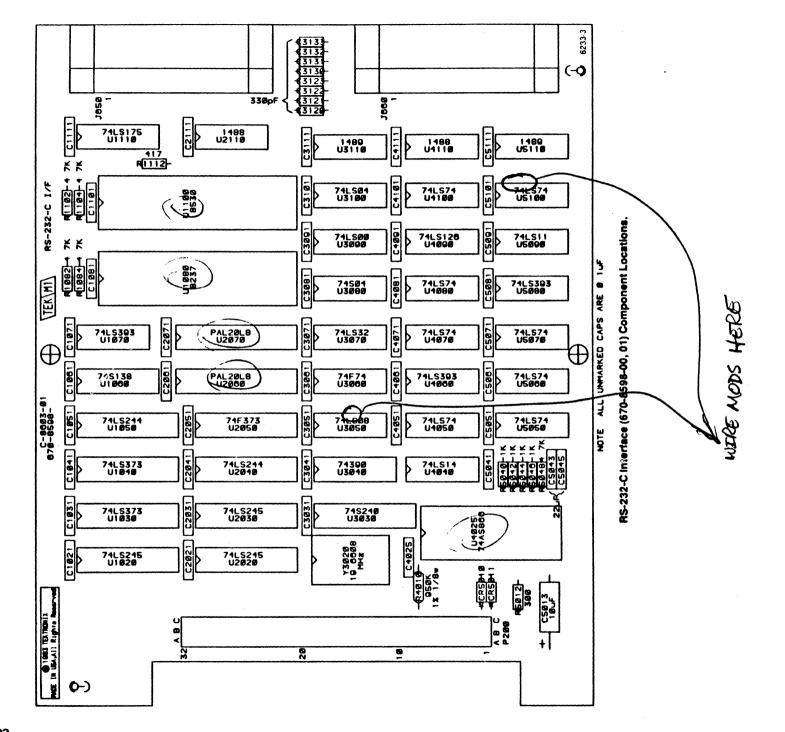

### **EXTERNAL BUS INTERFACE LOGIC**

This block provides the electrical interface between the External Bus and the Option Bus located on the Expansion Memory board. This function is performed by a 74F373 octal D-type flipflop (U102) and two 74ALS245 octal bus transceivers (U9103 and U9104) along with associated logic. U102 latches bits 16-23 of the address word, while U9103 and U9104 provide bidirectional interface for bits AD00 - AD15 of the External Bus.

## **MEMORY ADDRESS DECODE LOGIC**

Address decoding for the memory board is provided by a 25LS251 equal-to comparator (U9105, which decodes the memory board CSR address) and the U9113 programmable array logic (PAL) chip.

The comparator decodes the CSR address by comparing the predetermined Status Select Lines SS0-SS4 with bits 11-15 of the Option Bus. A match selects the memory board CSR. Data is latched into the CSR on the trailing edge of Data Enable (DEN-1). DEN-1 is the inverted equivalent of External Data Enable (EDEN-0).

The PAL U9113 decodes bits 17-23 of the address word and outputs the appropriate bank select signal to memory, as well as an additional memory-access control signal. The P0-P2 signals input to the PAL define a 3-bit program code that is loaded into the CSR by the host. This code is used to map the memory into the desired address space. The U9113 PAL is also used during memory refresh in the generation of the row address strobes.

#### Control and Status Register

The passing of status and control information between the host and the memory board is permitted by the Control and Status Register (CSR). The CSR is a 16-bit read/write register that consists of a 74LS273 octal D-type flipflop U9120, and two 74ALS244 octal bus transceivers (U9121 and U9122).

The contents of the CSR is dependent whether the host is writing to the CSR or reading from it. During a CSR write, the host loads the CSR with memory mapping program bits (P0-P2) and parity logic control bits. During a read from the CSR, bus transceivers U9121 and U9122 permit the host to read the mapping program bits, parity status information, and a code that defines the option type.

The contents of the CSR during a CSR write is defined below:

| )15  | D14-D12 | D11  | D10  | D09    | D08    | D07-D00 |

|------|---------|------|------|--------|--------|---------|

| N.U. | P2-P0   | N.U. | N.U. | PBAD-1 | PARE-1 | N.U.    |

| N.U. | P2-P0   | N.U. | N.U. | PBAD-1 | PARE-1 | N.U     |

Figure 3-1. The Control and Status Register During CSR Write.

**Program Bits P2-P0**. This is a 3-bit code that is used by the host to map the memory board into the desired location within address range of the host. There are eight possible mapping locations.

**PBAD-1**. PBAD-1 (Parity Bad-1) is a parity logic test bit that is set by the host to force the generation of bad parity during a memory write. The host then reads from the same location and generates valid parity, and then compares the stored parity value against the valid bit.

**PARE-1**. PARE-1 (Parity Enable-1) is set by the host to enable the parity logic. Writing a zero to this location disables parity.

The CSR contains the following information during a CSR read operation.

| D15  | D14-D12 | D11   | D10  | D09     | D08     | D07-D00  |

|------|---------|-------|------|---------|---------|----------|

| N.U. | P2-P0   | IRQ-0 | N.U. | PERHI-1 | PERLO-1 | DEV TYPE |

|      |         | I     |      |         |         |          |

| Figure | 3-2. | The | Control | and | Status | Register | During | CSR | Read . |

|--------|------|-----|---------|-----|--------|----------|--------|-----|--------|

|        |      |     |         |     |        |          |        |     |        |

**P2-P0**. This is the mapping code that is defined above. This feature allows host to read back this value.

**IRQ-0**. IRQ-0 (Interrupt Request-0) is asserted by the memory board after a parity error is detected.

**PERHI-1**. PERHI-1 (Parity Error High-1) is set by the memory board when a parity error is detected on the high byte (bits 08-15).

**PERLO-1**. PERLO-1 (Parity Error Low-1) is set by the memory board when a parity error is detected on the low byte (bits 00-07).

**DEV TYPE.** DEV TYPE (Device Type) bits 00-07 of the CSR register contain an 8-bit code that is used to identify the option device type that is located at a given option slot. The hexadecimal value that is assigned to the double-width expansion memory board is 18 through 1F. Bit 01 of the code defines whether the board is equipped with 64K (0) or 256K chips (1). Bit 00 defined whether the board is half-populated (1) or fully-populated (0).

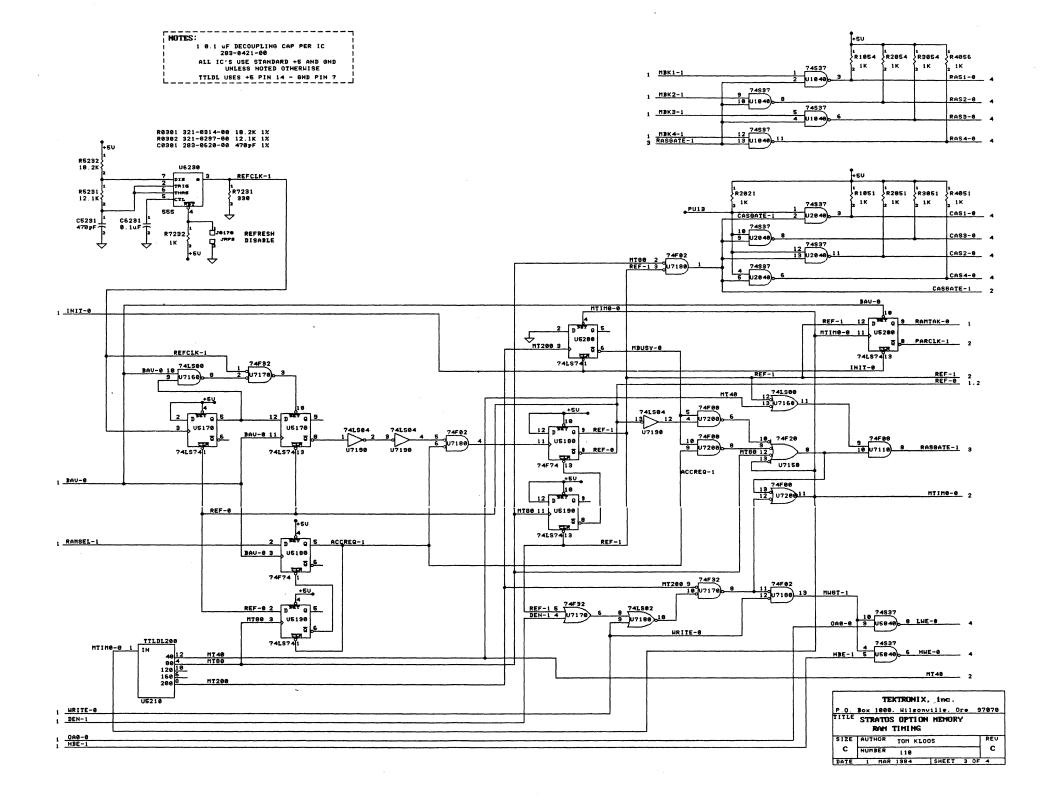

## **MEMORY ACCESS AND REFRESH TIMING**

This block coordinates the memory refresh cycle, which is performed approximately every 14.5 microseconds, and normal memory accesses. The refresh clock (REFCLK-1) operates at approximately 69.5 KHz and initiates a refresh cycle on the rising edge of the clock pulse. This block then samples RAM Select (RAMSEL-1) to insure that a memory access is not imminent. IF RAMSEL-1 is asserted, the refresh cycle is aborted until the memory access is completed (this function is performed by U9304 at pin 4). After a refresh is in process, memory accesses are locked out until the refresh is completed (this function is performed by U9302 at pin 10). Refer to page 3 of the schematic diagrams.

This block employs a 200 nanosecond delay line to establish memory access and refresh cycle timing. The data-read cycle from memory requires approximately 400 nanoseconds, whereas the data-write cycle can be extended beyond 400 nanoseconds.

### **REFRESH LOGIC**

Once a refresh cycle has been initiated by the memory access and refresh timing block, the memory refresh logic executes the memory refresh. This block supports a distributed refresh method whereby only one memory row is refreshed per refresh cycle. The next refresh cycle increments a refresh row address counter by one in preparation for that cycle. The counter is incremented on the trailing edge of the REFCLK-1. After the new row address has been placed on the Memory Address Bus, all four row address strobes RAS1-0 through RAS4-0) are pulsed to refresh the memory bit locations in that row.

## PARITY GENERATION AND CHECK LOGIC

This block generates odd parity for both the high and the low byte during memory writes and checks parity for both bytes during memory reads. The block uses a 74F280 parity generator/checker for both the high and low bytes. If, during a memory read a parity error is detected, the parity error signal is generated that also indicates whether the error applies to the high byte or the low byte.

## **MEMORY ADDRESS**

Memory addressing is performed by two 74F373 octal D-type flipflops (see page 2 of the schematic diagrams), which are used to demultiplex the 16-bit Option Bus address onto 8-bit Memory Address Bus, along with associated Row Address Strobe (RAS) and Column Address Strobe (CAS) logic. RAS and CAS signals are used to latch the memory address into memory. See page 3 of the schematic diagrams.

#### **MEMORY DATA BUFFER**

Two 74F373 octal D-type flipflops (U9202 and U9203) act as buffers between the 16-bit Memory Data Bus and the multiplexed Option Bus. See page 2 of the schematic diagrams.

#### MEMORY

The memory board is organized electronically as four banks of 18 chips each. Each bank is organized as two 8-bit bytes with parity. The board can be configured either fully populated or half populated. The use of 64K x 1-bit memory chips provides 256k bytes of memory on a fully populated board, whereas a fully populated board using 256K x 1-bit chips provides 2 megabytes of memory. Board population and chip density are selected by jumper configuration.

# HARD COPY INTERFACE BOARD

|                                                 | Page |

|-------------------------------------------------|------|

| Introduction                                    | 4-1  |

| Option Overview                                 | 4-1  |

| Option Board Configuration                      | 4-1  |

| Device ID Jumpers                               | 4-1  |

| Signal Termination Jumpers                      |      |

| Option Base Address Configuration               | 4-1  |

| Hard Copy Port Hardware Interface               | 4-2  |

| Special Registers                               |      |

| Device ID Register                              | 4-2  |

| DMA Controller Pointer Register                 | 4-2  |

| DMA Controller Access Register                  | 4-2  |

| Port 1 Data Register                            |      |

| Port 1 Configuration Register                   | 4-3  |

| Port 2 Data Register                            |      |

| Port 2 Configuration Register                   |      |

| Interface Status Register                       |      |

| Functional Block Description                    |      |

| External Bus Interface and Address Decode Logic |      |

| Register Address Decode                         |      |

| DMA Control Block                               |      |

| Interface Status and Configuration Registers    |      |

| Port 1 Data/Protoco! Interface                  |      |

| Port 2 Data/Protocol Interface                  |      |

| Interrupt Control Block                         |      |

#### ILLUSTRATIONS

#### Fig. No.

### Page

| 4-1 | Port 1 Configuration Register        | 4-3         |

|-----|--------------------------------------|-------------|

|     | Port 2 Configuration Register        |             |

|     | Hard Copy Interface Status Register  |             |

| 4-4 | Hard Copy Option Board Block Diagram | <b>4-</b> 8 |

#### TABLES

| Table<br>No. | P                                   | sce |

|--------------|-------------------------------------|-----|

| 4-1          | Hard Copy Interface Device ID Codes | 4-2 |

# HARD COPY INTERFACE BOARD

# INTRODUCTION

This section describes the installation, use, and operation of the Hard Copy Interface Board. The contents of this section are organized as follows:

- Option Overview

- Option Board Configuration

- Special Registers

- Block Level Hardware Description

# **OPTION OVERVIEW**

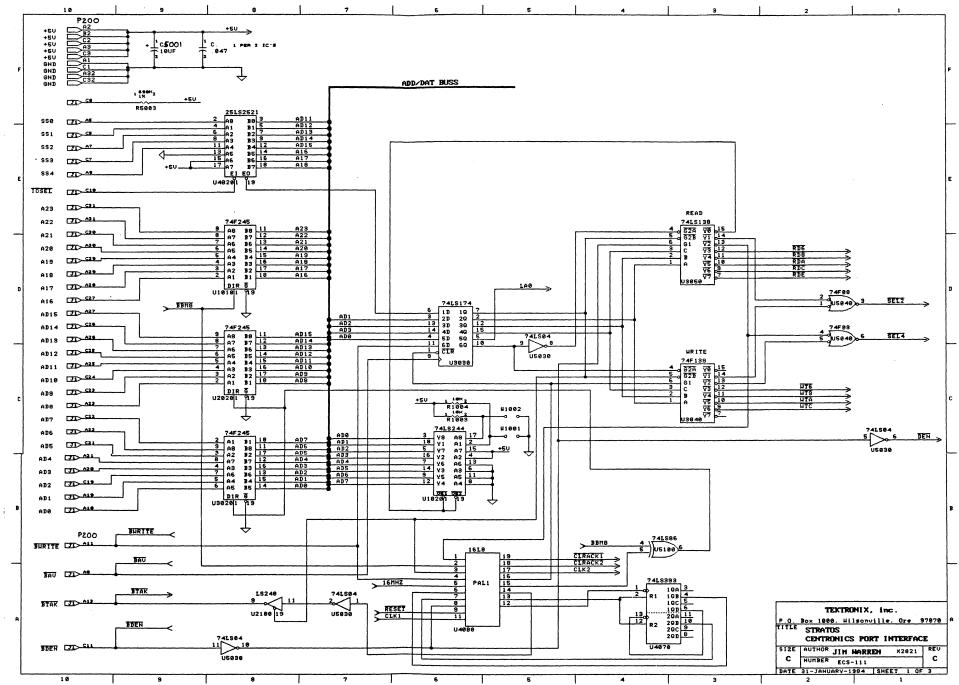

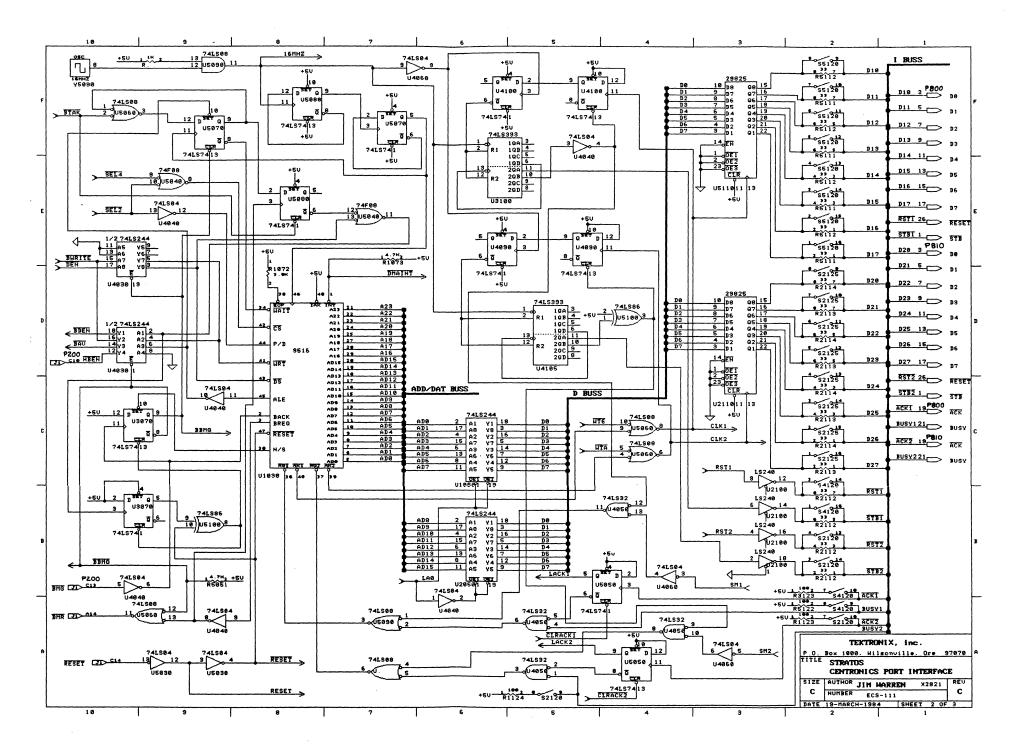

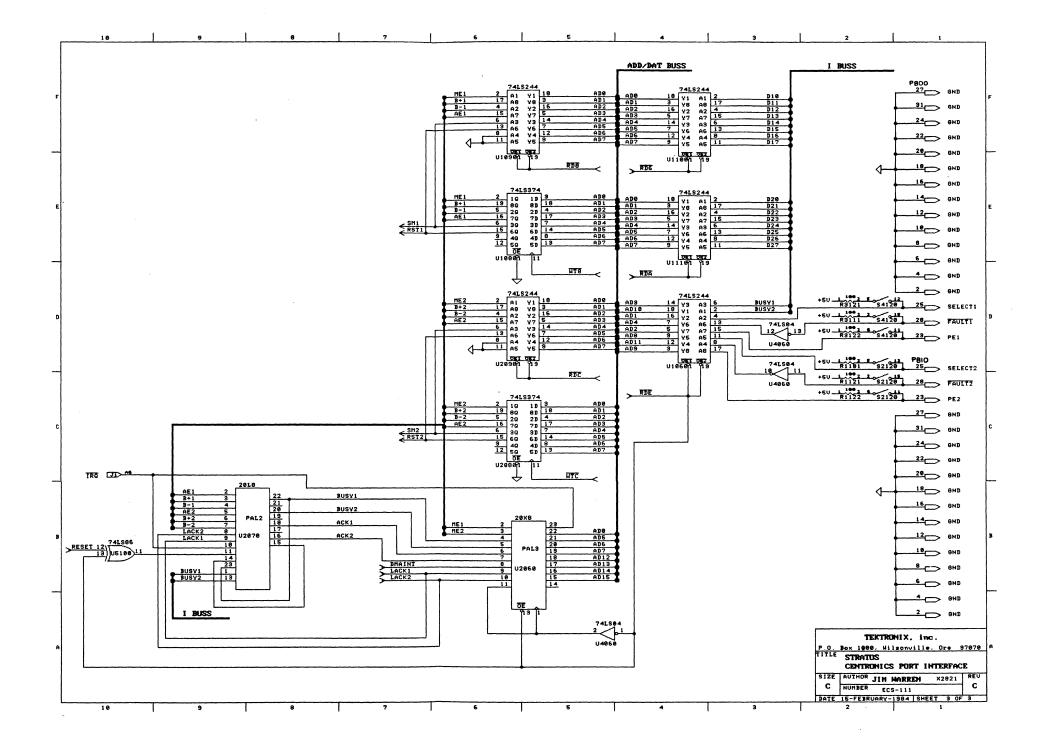

The Hard Copy Interface board is a single-width option board that provides two independent Centronix-type parallel interface ports for the TEK 6100 family of workstations. Each port provides communication with, and control of, peripheral devices via a parallel data bus and associated control signals.

# **OPTION BOARD CONFIGURATION**

This section describes the jumpers that are used to configure the option board and also describes the peripheral interface connectors.

# **DEVICE ID JUMPERS**

The device 1D jumpers are configured at the factory during manufacturing and are not configurable by the user.

## SIGNAL TERMINATION JUMPERS

There are four 8-bit DIP switches that, when installed (or closed), connect all inputs from the peripherals to 100 ohm pull-up resistors and removes the 33 ohm series termination resistors on all outputs. These DIP switches are removed (or opened) when driving a standard Centronix peripheral, and installed when driving modified instruments that have input terminations, such as the Tektronix 4691 and 4692 copiers.

# **OPTION BASE ADDRESS CONFIGURATION**

The base address for the option board is determined by which slot the board occupies. Refer to the Installation section at the front of this document for more information.

# HARD COPY PORT HARDWARE INTERFACE

Electrical interface for each hard copy port is provided by an AMP connector, part number 102893-3. The connectors are attached to the rear of the board and are accessable at the rear of the box when the board is installed.

# SPECIAL REGISTERS

The Hard Copy Option Board contains eight registers, two of which are DMA Control registers and six of which are option configuration, status, and data registers. Each register is defined below. All register addresses are given relative to the base address of the board. The base address of the board is dependent on the option slot in which it is installed. Refer to the Installation section at front of this document for option board installation information.

# **DEVICE ID REGISTER**

This is 8-bit (D0-D7) read-only register is located at relative address 0. This register defines one of three possible option configurations, as indicated below:

#### Table 4-1

#### HARD COPY INTERFACE DEVICE ID CODES

| ID Code (Hex) | Board Configuration                                                                                           |

|---------------|---------------------------------------------------------------------------------------------------------------|

| D             | Single Port board, no DMA support<br>Single Port board, with DMA support<br>Dual Port board, with DMA support |

| E             | Single Port board, with DMA support                                                                           |

| F             | Dual Port hoard, with DMA support                                                                             |

# DMA CONTROLLER POINTER REGISTER

This 6-bit read/write register (D0-D5) is located at relative address 02. This register contains the address of the internal register to be accessed by the host. Valid addresses for this register are provided in the AMD 9516 DMA Controller data manual

# DMA CONTROLLER ACCESS REGISTER

This 16-bit read/write register (D0-D15) is located at relative address 04. The register provides access to all of the DMA controller registers. The contents written to this register by the host are transferred to the DMA control register specified by the address located in the pointer register. The format of the data placed in this register is dependent on the register that is being accessed. Refer to the DMA controller data manual for more information. When this register is read, the cycle is delayed by approximately 2 microseconds to allow for slow registers.

# PORT 1 DATA REGISTER

This 8-bit read/write register (D0-D7) is located at relative address 08. It is the interface between the option address/data bus and the port 1 data path. All data transferred from the option bus to the peripheral bus are aligned on the low byte (D0-D7) of the option bus. The host can read the last byte sent to the peripheral by reading the contents of this register.

# **PORT 1 CONFIGURATION REGISTER**

This 6-bit (D0-D5) read/write register is located at relative address 08. This register is used to establish the configuration of the port 1 interface.

The contents of the Port 1 Configuration register are defined below:

| 05            | 04    | 03     | 02     | 01     | 00    |

|---------------|-------|--------|--------|--------|-------|

| <b>RST1-1</b> | SM1-1 | AIE1-1 | BTEI-1 | BLEI-1 | ME1-1 |

Figure 4-1. Port 1 Configuration Register.

#### RST1-1, Bit 05

RST1-1 (Reset 1-1), when set, issues a hardware rest to the peripheral. Reset remains asserted until it is cleared by the host.

#### SM1-1, Bit 04

SM1-1 (Stream Mode 1-1), when set, places port 1 in the streaming mode of operation. This mode can be used by some peripherals to increase data transmission rates. In the streaming mode, if DMA is being performed, the next transfer is initiated immediately after the current byte is transferred, without waiting for the peripheral to assert Acknowledge-1. The streaming mode has no affect on non-DMA transfers. When this bit is cleared, the port returns to the normal mode of operation.

#### AIE1-1, Bit 03

AIE1-1 (Acknowledge Interrupt Enable 1-1) is set by the host to enable the generation of an interrupt on the assertion of Acknowledge-1 by the port 1 peripheral. Clearing AIE1-1 causes the interrupt control logic to ignore the Acknowledge signal.

#### BTEI-1, Bit 02

Setting this bit (Busy Trailing Edge Interrupt-1) enables an interrupt to be generated to the host whenever the port 1 Busy-1 line is deasserted by the peripheral. This interrupt is generated by the trailing edge of Busy-1. Clearing this bit causes the interrupt logic to ignore the trailing edge of Busy, and no interrupt is generated.

#### BLEI-1, Bit 01

Setting this bit (Busy Leading Edge Interrupt-1) enables an interrupt to be generated to the host whenever the port 1 Busy-1 line is asserted by the peripheral. This interrupt is generated by the leading edge of Busy-1. Clearing this bit causes the interrupt logic to ignore the leading edge of Busy, and no interrupt is generated.

#### ME1-1, Bit 00

ME1-1 (Master Enable 1-1) is set by the host to enable interrupts to be generated by the port. Clearing this bit still allows the Interface Status register to store status information, but keeps the port status lines from generating an interrupt to the host.

# PORT 2 DATA REGISTER

This 8-bit (D7-D0) read/write register is located at relative address 0A. It is the interface between the option address/data bus and the port 2 data path. All data transferred from the option bus to the peripheral bus are aligned on the low byte (D0-D7) of the option bus. The host can read the last byte sent to the peripheral by reading the contents of this register.

# **PORT 2 CONFIGURATION REGISTER**

This 6-bit (D0-D5) read/write is register located at relative address 0C (Hex). This register is used to establish the configuration of the port 2 interface. Each bit is defined below:

| 05     | 04    | 03     | 02     | 01     | 00    |

|--------|-------|--------|--------|--------|-------|

| RST2-1 | SM2-1 | AIE2-1 | BTEI-1 | BLEI-1 | ME2-1 |

Figure 4-2. Port 2 Configuration Register.

#### RST2-1, Bit 05

RST2-1 (Reset 2-1), when set, issues a hardware reset to the peripheral. Reset remains asserted until cleared.

#### SM2-1, Bit 04

SM2-1 (Stream Mode 2-1) when set, places port 2 in the streaming mode of operation. This mode can be used by some peripherals to increase data transmissions rates. In the streaming mode, if DMA is being performed, the next transfer is initiated immediately after the current byte is transferred, without waiting for the peripheral to assert Acknowledge-1. The streaming mode has no effect on non-DMA transfers. When this bit is cleared, the port returns to the normal mode of operation.

#### AJE2-1, Bit 03

AIE2-1 (Acknowledge Interrupt Enable 2-1) is set by the host to enable the generation of an interrupt on the assertion of Acknowledge-1 by the port 2 peripheral. Clearing AIE2-1 causes the interrupt control logic to ignore the Acknowledge signal.

#### BTEI-1, Bit 02

Setting this bit (Busy Trailing Edge Interrupt-1) enables an interrupt to be generated to the host whenever the port 2 Busy-1 line is deasserted by the peripheral. This interrupt is generated by the trailing edge of Busy-1. Clearing this bit causes the interrupt logic to ignore the trailing edge of Busy, and no interrupt is generated.

#### BLEI-1, Bit 01

Setting this bit (Busy Leading Edge Interrupt-1) enables an interrupt to be generated to the host whenever the port 2 Busy-1 line is asserted by the peripheral. This interrupt is generated by the leading edge of Busy-1. Clearing this bit causes the interrupt logic to ignore the leading edge of Busy, and no interrupt is generated.

#### ME1-1, Bit 00

ME1-1 (Master Enable 1-1) is set by the host to enable interrupts to be generated by the port. Clearing this bit still allows the Interface Status register to store status information, but keeps the port status lines from generating an interrupt to the host.

## **INTERFACE STATUS REGISTER**

This 16-bit read-only register is located at relative address OE and contains all of the status information for both ports. This register is usually read by the host after an interrupt has been generated to determine the cause of the interrupt. When this register is read, all bits capable of generating an interrupt are cleared, except bit 0. Bit 15 (Master Interrupt Pending) is also cleared. The contents of this register are defined below:

| 15    | 14     | 13       | 12     | 11     | 10     | 09    | 08     |

|-------|--------|----------|--------|--------|--------|-------|--------|

| MIP-1 | BIP2-1 | ACKIP2-1 | ACK2-1 | FLT2-1 | BSY2-1 | PE2-1 | SEL2-1 |

Interface Status Register High Byte

| 07    | 06       | 05     | 04     | 03     | 02    | 01     | <b>0</b> 0 |

|-------|----------|--------|--------|--------|-------|--------|------------|

| BIP1- | ACKIP1-1 | ACK1-1 | FLT1-1 | BSY1-1 | PE1-1 | SEL1-1 | DIP1-1     |

Interface Status Register Low Byte

Figure 4-3. Hard Copy Interface Status Register.

#### MIP-1, Bit 15

This bit (Master Interrupt Pending-1), when set, indicates that the DMA Controller has an interrupt pending. This occurs when any of bits 0, 6, 7, 13, or 14 of the Interface Status Register are set.

Bits 14-8 of the Interface Status register apply to port 2.

#### BIP2-1, Bit 14

This bit (Busy Interrupt Pending 2-1), when set, indicates that a Busy Interrupt from the port 2 peripheral is pending. The conditions that will enable the generation of this interrupt are selected by bits 1 and 2 of the Port 2 Configuration Register.

## ACKIP2-1, Bit 13

This bit (Acknowledge Interrupt Pending 2-1), when set, indicates that an Acknowledge Interrupt is pending from the port 1 peripheral.

## ACK2-1, Bit 12

This bit (Acknowledge 2-1), when set, indicates that Acknowledge been asserted by the port 2 peripheral since that the last reading of this register.

### FLT2-1, Bit 11

This bit (Fault 2-1), when set, indicates that the port peripheral is off-line (deselected) and/or is out of paper.

### BSY2-1, Bit 10

This bit (Busy 2-1), when set, indicates that the peripheral on port 2 has been deselected, is out of paper, or the data buffer is full.

#### PE2-1, Bit 09

This bit (Paper Empty 2-1), when set, indicates that the peripheral on port 2 is out of paper.

#### SEL2-1, Bit 08

This bit (Select 2-1), when set, indicates that the peripheral on port 2 is in the selected state.

#### BIP1-1, Bit 07

This bit (Busy Interrupt Pending 1-1), when set, indicates that a Busy Interrupt from the port 1 peripheral is pending. The conditions that will enable the generation of this interrupt are selected by bits 1 and 2 of the Port 1 Configuration Register.

#### ACKIP1-1, Bit 05

This bit (Acknowledge Interrupt Pending 1-1), when set, indicates that an Acknowledge Interrupt from the port 1 peripheral is pending.

#### ACK1-1, Elt 05

This bit (Acknowledge 1-1), when set, indicates that the Acknowledge signal has been asserted by the port 1 peripheral since the last time the register was read.

#### FLT1-1, Bit 04

This bit (Fault 1-1), when set, indicates that the port peripheral is off line (deselected) and/or is out of paper.

#### BSY1-1, Bit 03

This bit (Busy 1-1), when set, indicates that the peripheral on port 1 has been deselected, is out of paper, or the data buffer is full.

#### PE1-1, Bit 02

This bit (Paper Empty 1-1), when set, indicates that the peripheral on port 1 is out of paper.

#### SEL1-1, Bit 01

This bit (Select 1-1), when set, indicates that the port 1 peripheral is in the selected state.

#### DIP1-1, Bit 00

This bit (DMA Interrupt Pending 1-1), when set, indicates that the DMA Controller has an interrupt pending.

# FUNCTIONAL BLOCK DESCRIPTION

The Hard Copy Interface board comprises of six major functional blocks that are listed below.

- External Bus Interface and Address Decode Logic

- DMA Control Block

- Interface Status and Configuration Registers

- Port 1 Data/Protocol Interface

- Port 2 Data/Protocol Interface

- Interrupt Control Block

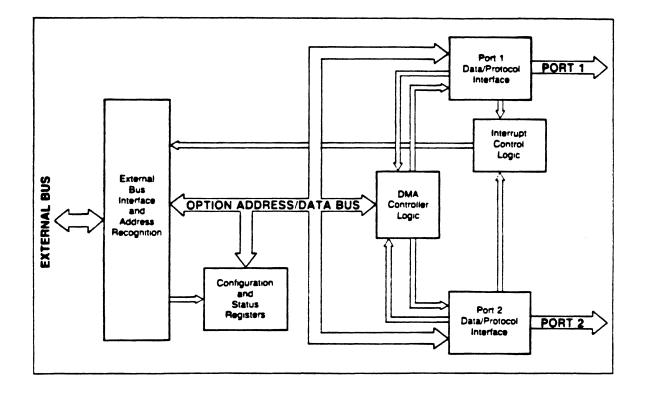

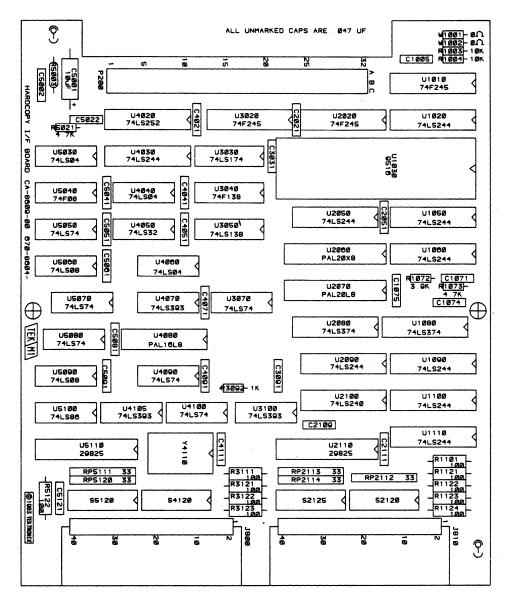

Each of the functional blocks are discussed in the following paragraphs. Refer to the block diagram of the board shown in figure 1-1 and the schematic diagram.

## **EXTERNAL BUS INTERFACE AND ADDRESS DECODE LOGIC**

This block provides the electrical interface between the External Bus and the multiplexed address/data bus on the option board, as well as address recognition for the hard copy interface option board. External Bus electrical interface is provided by three 74LS245 octal bus transceivers.

Address recognition is performed by a 25LS2521 Equal-to comparator that compares address lines AD11-AD18 of the on-board address bus against the predefined slot select lines SS0-SS4. A match indicates that the board has been addressed and lets the host access the option board status, control, and data registers.

Associated with the address recognition logic is the Device Register. This 8-bit, read-only register contains the jumper-selected, 8-bit ID word assigned to the Hard Copy Interface Board. The register consists of a 74LS244 bus transceiver (U1020) that is output-enabled by the address recognition logic. The contents of this register are read by the host at power-up and system reset.

Figure 4-4. Hard Copy Option Board Block Diagram.

#### Register Address Decode

This option board contains 6 registers that are mapped into the address space of the host. These registers are accessed for read or write operations by two 74LS138 3-to-8 decoders and enabled by the address recognition logic described above. All board-level registers other than DMA Control Registers are discussed in a previous section of this document titled "Special Registers".

# DMA CONTROL BLOCK

The DMA Control Block comprises a AMD 9516 DMA Controller and associated support logic. This block executes the protocols necessary for data transfer from the the External Bus (host side) to the peripherals. Each port is completely independent of the other. DMA transfers are initiated by the host by loading DMA control parameters into a control block known as the Chain Control Table. The Chain Control Table is maintained in main memory by the host. The host also programs two registers internal to the controller known as the Master Mode Register, which controls chip-level interface parameters, and the Chain Address Register, which contains the address of the Chain Control Table. The host then issues a Start command to the controller, which proceeds to copy the contents of the Chain Control Table into its own internal registers and execute the transfer. Only fly-by transfers are supported by this interface.

The DMA Control Block includes the logic necessary to support the External Bus bus protocol, such as the Bus Request/Bus Grant flip-flop U3070, the bus protocol signal driver U4030, the Wait State Generator (flip-flop U5070, pin 8), and associated logic. During a DMA cycle, the Wait State Generator asserts a WAIT to the DMA controller on the assertion of Address Latch Enable by the controller. The DMA controller samples WAIT at T2 and maintains data on the bus until BTACK-O (Bus Transfer Acknowledge) is asserted by the host. At that time, WAIT is cleared and the bus cycle finishes. The DMA Control Block will be discussed more thoroughly in later documenation.

## INTERFACE STATUS AND CONFIGURATION REGISTERS