## M6805 HMOS M146805 CMOS Family

Microcomputer/Microprocessor User's Manual

# M6805 HMOS M146805 CMOS FAMILY MICROCOMPUTER/MICROPROCESSOR USER'S MANUAL

SECOND EDITION

Library of Congress Catalog Number: 83-60771

0-13-541375-3

0-13-541383-4 (special ed.)

Editorial/production supervision: Barbara A. Cassel Manufacturing buyer: Gordon Osbourne

© 1983, 1980 by Motorola Inc.

All rights reserved. No part of this book may be reproduced in any form or by any means without permission in writing from the publisher.

Motorola reserves the right to make changes to any products herein to improve functioning or design. Although the information in this document has been carefully reviewed and is believed to be reliable, Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

ISBN 0-13-541375-3 ISBN 0-13-541383-4 (SPECIAL ED.)

Prentice-Hall International Inc., London

Prentice-Hall of Australia Pty. Limited, Sydney

Prentice-Hall do Brasil, Ltda., Rio de Janiero

Prentice-Hall Canada Inc., Toronto

Prentice-Hall of India Private Limited, New Delhi

Prentice-Hall of Japan, Inc., Tokyo

Prentice-Hall of Southeast Asia Pte. Ltd., Singapore

Whitehall Books Limited, Wellington, New Zealand

#### M6805 HMOS/M146805 CMOS FAMILY USERS MANUAL TABLE OF CONTENTS

| Paragraph<br>Number                                                                                        | Title                                                                                                                                                                                                                 | Page<br>Number          |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                                                                                                            | CHAPTER 1 GENERAL DESCRIPTION                                                                                                                                                                                         |                         |

| 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.3<br>1.3.1<br>1.3.2<br>1.4                                               | Introduction to The M6805 HMOS/M146805 CMOS Family Optimized for Controller Applications Instruction Set Addressing Modes Choice of Technologies HMOS Features CMOS Features Hardware Hardware Common to All Devices  | 2 3 4 4 5               |

| 1.4.2                                                                                                      | Family Options                                                                                                                                                                                                        |                         |

|                                                                                                            | CHAPTER 2<br>SOFTWARE DESCRIPTION                                                                                                                                                                                     |                         |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.5.1<br>2.2.5.2<br>2.2.5.3<br>2.2.5.5<br>2.3 | Introduction Register Set Accumulator (A). Index Register (X) Program Counter (PC) Stack Pointer (SP) Condition Code Register (CC) Carry (C) Zero (Z) Negative (N) Half-Carry (H) Interrupt Mask (I) Addressing Modes | 10 11 12 12 14 14 15 15 |

| 2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.5.1                                                       | Inherent Addressing Mode Immediate Addressing Mode Extended Addressing Mode Direct Addressing Mode Indexed Addressing Mode Indexed—No Offset                                                                          | 17<br>18<br>20<br>21    |

## TABLE OF CONTENTS (Continued)

| Paragraph<br>Number | Title                               | Page<br>Number |

|---------------------|-------------------------------------|----------------|

| 2.3.5.2             | Indexed—8-Bit Offset                |                |

| 2.3.5.3             | Indexed—16-Bit Offset               | . 24           |

| 2.3.5.4             | Indexing Compatibility              |                |

| 2.3.6               | Relative Addressing Mode            | . 25           |

| 2.3.7               | Bit Manipulation                    |                |

| 2.3.7.1             | Bit Set/Clear Addressing Mode       |                |

| 2.3.7.2             | Bit Test and Branch Addressing Mode |                |

| 2.4                 | Instruction Set Overview            |                |

| 2.4.1               | Introduction                        | . 31           |

| 2.4.2               | Register/Memory Instructions        | . 31           |

| 2.4.3               | Read/Modify/Write Instructions      | . 32           |

| 2.4.4               | Control Instructions                |                |

| 2.4.5               | Bit Manipulation Instructions       | . 33           |

| 2.4.6               | Branch Instructions                 |                |

|                     | CHAPTER 3                           |                |

|                     | SOFTWARE APPLICATIONS               |                |

| 3.1                 | Introduction                        |                |

| 3.2                 | Serial I/O Routines                 |                |

| 3.2.1               | MC145000 Serial I/O Software        |                |

| 3.2.2               | Serial I/O Software for RS-232      |                |

| 3.2.3               | Software Serial Loop                |                |

| 3.3                 | Block Move                          |                |

| 3.4                 | Stack Emulation                     |                |

| 3.5                 | Keypad Scan Routine                 |                |

| 3.6                 | DAA (Decimal Adjust Accumulator)    |                |

| 3.7                 | Multiply                            |                |

| 3.8                 | Divide                              | . 49           |

| 3.9                 | ASSIST05 Debug Monitor              |                |

| 3.9.1               | ASSIST05 Command Description        | . 52           |

| 3.9.2               | Detailed Command Description        | . 54           |

| 3.9.3               | ASSIST05 Routines                   | . 56           |

|                     | CHAPTER 4                           |                |

|                     | HARDWARE FEATURES                   |                |

| 4.1                 | Introduction                        |                |

| 4.2                 | Processing Technology               |                |

| 4.3                 | Temporary Storage (RAM)             | . 76           |

| 4.4                 | Permanent Storage (ROM Or EPROM)    |                |

| 4.5                 | Oscillator                          |                |

| 4.6                 | Resets                              | . 78           |

## TABLE OF CONTENTS (Continued)

| Paragraph<br>Number | Title                                                    | Page<br>Number |

|---------------------|----------------------------------------------------------|----------------|

| 4.7                 | Interrupts                                               | 79             |

| 4.7.1               | General                                                  | 79             |

| 4.7.2               | Timer Interrupt                                          | 80             |

| 4.7.3               | External Interrupts                                      | 80             |

| 4.7.4               | Software Interrupt (SWI)                                 | 81             |

| 4.8                 | I/O Ports                                                |                |

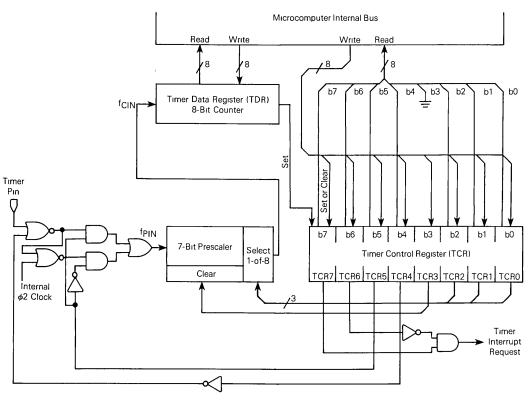

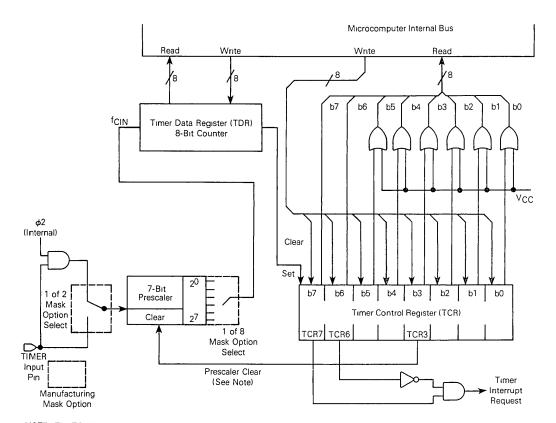

| 4.9                 | Timer Description                                        |                |

| 4.9.1               | General                                                  |                |

| 4.9.2               | M146805 CMOS Family                                      |                |

| 4.9.2.1             | General                                                  | 84             |

| 4.9.2.2             | Timer Input Mode 1                                       |                |

| 4.9.2.3             | Timer Input Mode 2                                       |                |

| 4.9.2.4             | Timer Input Mode 3                                       | 85             |

| 4.9.2.5             | Timer Input Mode 4                                       |                |

| 4.9.2.6             | Timer Control Register (TCR)                             | 86             |

| 4.9.3               | M6805 HMOS Family Timer                                  |                |

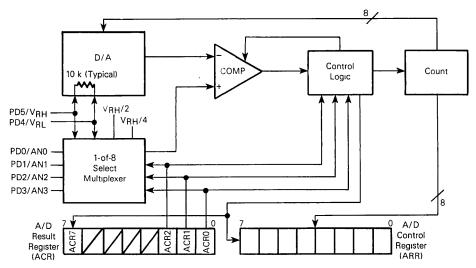

| 4.10                | Analog-To-Digital (A/D) Converter                        |                |

| 4.11                | Phase-Lock Loop (PLL)                                    | 89             |

| 4.11.1              | General                                                  | 89             |

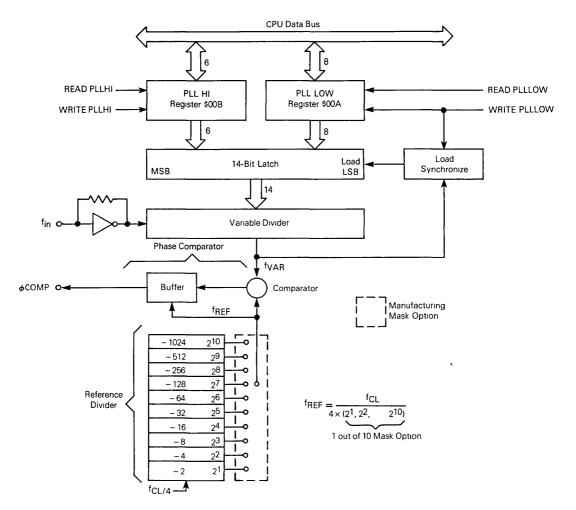

| 4.11.2              | Reference Divider                                        |                |

| 4.11.3              | Variable Divider                                         | 91             |

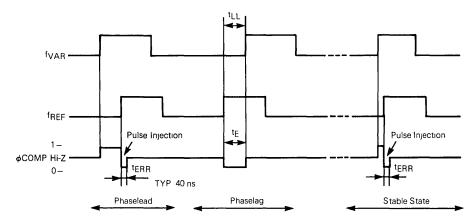

| 4.11.4              | Phase Comparator                                         |                |

| 4.12                | MC146805E2 Microprocessor (MPU) External Bus Description |                |

|                     | CHAPTER 5                                                |                |

|                     | HARDWARE APPLICATIONS                                    |                |

| 5.1                 | Introduction                                             | 95             |

| 5.2                 | I/O Expansion                                            |                |

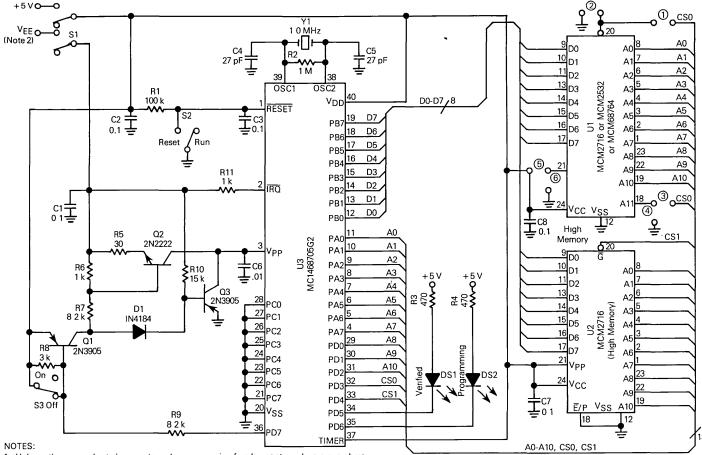

| 5.2.1               | MC146805E2 Microprocessor Unit (MPU)                     | 95             |

| 5.2.1.1             | Interfacing Multiplexed Bus Memory with Peripherals      | 96             |

| 5.2.1.2             | Interfacing Non-Multiplexed Bus Memory with Peripherals  | 96             |

| 5.2.1.3             | Interfacing with Slow Memory and Peripheral Devices      | 99             |

| 5.2.1.4             | Emulating the MC146805G2 MCU                             |                |

| 5.2.2               | Single-Chip Microcomputers (MCUs)                        | 99             |

| 5.3                 | Periodic Wake-up from WAIT Mode                          | 101            |

| 5.4                 | Interrupts                                               | 101            |

| 5.4.1               | Exiting from STOP Mode                                   | 102            |

| 5.4.2               | 60 Hz Interrupt for Time of Day Clock                    | 102            |

| 5.5                 | CMOS Design Considerations                               | 103            |

| 5.5.1               | Power Consumption                                        | 104            |

| 5.5.2               | CMOS Latch-up                                            | 105            |

| 5.6                 | 32 kHz Oscillator                                        | 105            |

## TABLE OF CONTENTS (Concluded)

| Paragraph<br>Number                                                                                              | Title                                                                                                                                                                                                                                                                                                                                                                                             | Page<br>Number                                              |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 5.7<br>5.8<br>5.9<br>5.9.1<br>5.9.2<br>5.9.3<br>5.9.3.1<br>5.9.3.2<br>5.10<br>5.10.1<br>5.10.2<br>5.10.3<br>5.11 | Stand-Alone Analog-to-Digital Converter (AN-869) Frequency Synthesizer Using The MC6805T2L1 (AN-871) Keyless Entry System Using The MC146805F2()1 (AN-863) Introduction Initialization Operation Opening The Digital Lock Changing The Coded Sequence Bicycle Computer Using The MC146805G2()1 (AN-858) Introduction Hardware Configuration Bicycle Computer Function Available Application Notes | 116<br>119<br>119<br>120<br>120<br>120<br>120<br>122<br>123 |

|                                                                                                                  | CHAPTER 6 EPROM PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                       |                                                             |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.2<br>6.2.1<br>6.2.1.1<br>6.2.1.2<br>6.2.1.3<br>6.2.2                         | Introduction General. M6805 HMOS Family Bootstrap M146805 CMOS Family Bootstrap Programming. M6805 HMOS Family M6805 HMOS Family MC68705P3 Programming MC68704R3/MC68705U3 Programming Printed Circuit Board MC1468705G2 Programming                                                                                                                                                              | 129<br>132<br>133                                           |

|                                                                                                                  | CHAPTER 7<br>SELF-CHECK                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5                                                          | Introduction Self-Check Description RAM Self-Check ROM Self-Check Timer Self-Check A/D Self-Check Flowchart Example                                                                                                                                                                                                                                                                               | 139<br>140<br>140<br>140<br>140<br>140<br>141               |

#### **APPENDICES**

| A. | M6805 HMOS/M146805 CMOS Family Compatibility With MC6800 | 143 |

|----|----------------------------------------------------------|-----|

| B. | RASM05 Macro Assembler Syntax and Directives             | 147 |

| C. | Instruction Set Detailed Definition                      | 153 |

| D. | Instruction Set Alphabetical Listing                     | 221 |

| E. | Instruction Set Functional Listing                       | 223 |

| F. | Instruction Set Numerical Listing                        | 227 |

| G. | Instruction Set Cycle-By-Cycle Operation Summary         | 233 |

| H. | ASCII Hexadecimal Code Conversion Chart                  | 245 |

| 1. | Instruction Set Opcode Map                               | 247 |

#### LIST OF ILLUSTRATIONS

| Figure<br>Number | Title                                                                 | Page<br>Number |

|------------------|-----------------------------------------------------------------------|----------------|

| 1-1              | M6805 HMOS/M146805 CMOS Family Basic Microcomputer                    |                |

|                  | Block Diagram                                                         | 6              |

| 1-2              | M6805 HMOS/M146805 CMOS Family Nomenclature Example                   | 7              |

| 2-1              | M6805 HMOS/M146805 CMOS Family Register Architecture                  | 10             |

| 2-2              | Stacking Order                                                        | 13             |

| 2-3              | Inherent Addressing Mode Example                                      |                |

| 2-4              | Immediate Addressing Mode Example                                     |                |

| 2-5              | Extended Addressing Mode Example                                      |                |

| 2-6              | Direct Addressing Mode Example                                        |                |

| 2-7              | Indexed Addressing Mode, No Offset Example                            |                |

| 2-8              | Indexed Addressing Mode, 8-Bit Offset Example                         |                |

| 2-9              | Indexed Addressing Mode, 16-Bit Offset Example                        | 24             |

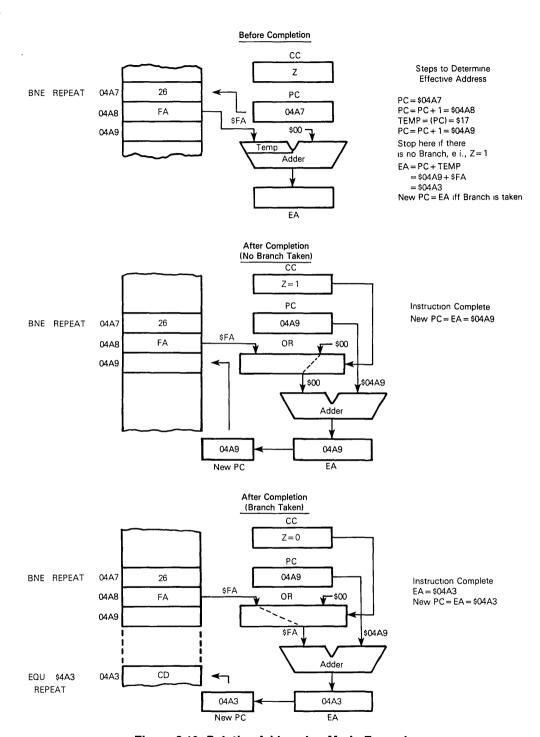

| 2-10             | Relative Addressing Mode Example                                      |                |

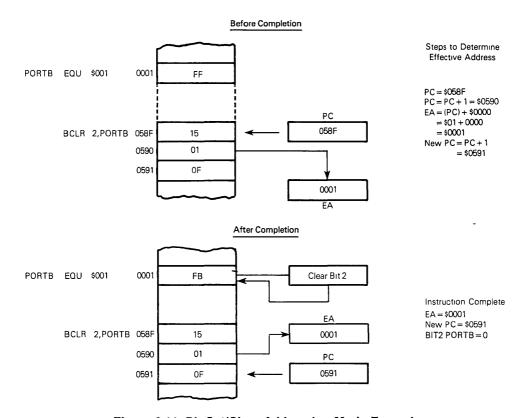

| 2-11             | Bit Set/Clear Addressing Mode Example                                 |                |

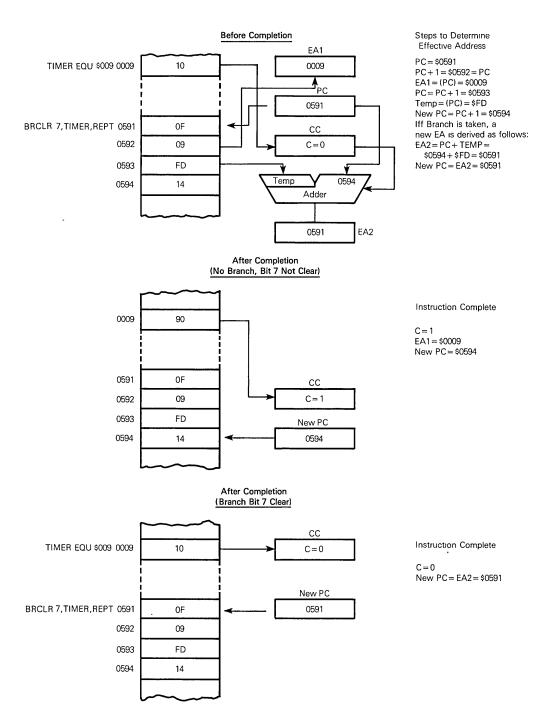

| 2-12             | Bit Test and Branch Addressing Mode Example                           | 30             |

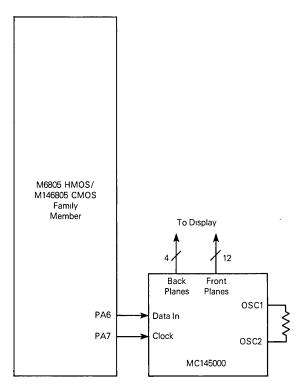

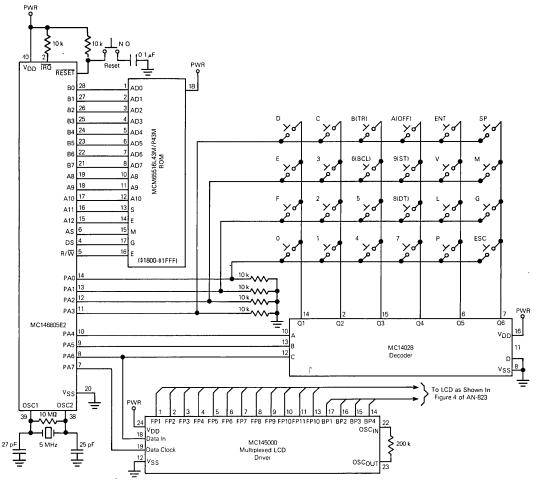

| 3-1              | MC145000 LCD Driver Interface Schematic Diagram                       | 36             |

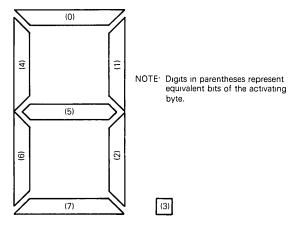

| 3-2              | 7-Segment Display Format                                              |                |

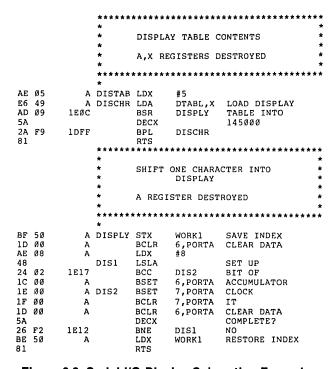

| 3-3              | Serial I/O Display Subroutine Examples                                |                |

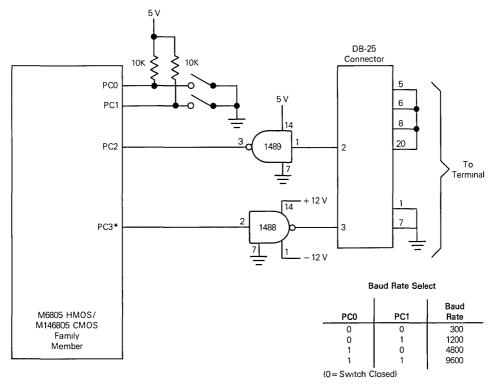

| 3-4              | RS-232 Interface for Serial I/O via I/O Port Lines Schematic Diagram. | 38             |

| 3-5              | Serial I/O Software Subroutine Example                                | 39             |

| 3-6              | Software Serial Loop Hardware Connections Schematic Diagram           | 41             |

| 3-7              | Block Move Routine                                                    | 42             |

| 3-8              | Stack Emultation Routine                                              |                |

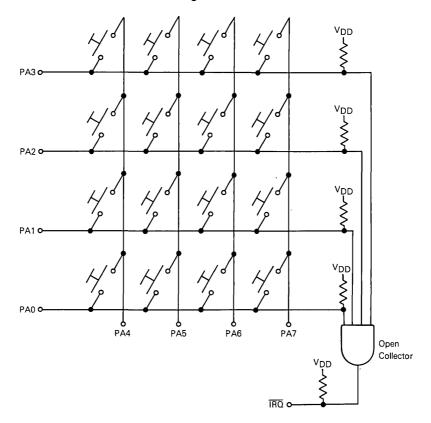

| 3-9              | 4 × 4 Keypad and Closure Detection Circuit Schematic Diagram          | 44             |

| 3-10             | KEYSCN Routine Example                                                | 45             |

| 3-11             | DAA Subroutine Example                                                | 46             |

| 3-12             | 16 Bit × 16 Bit Multiplication Subroutine Example                     |                |

| 3-13             | 8-bit × 8-bit Multiplication Subroutine Example                       | 48             |

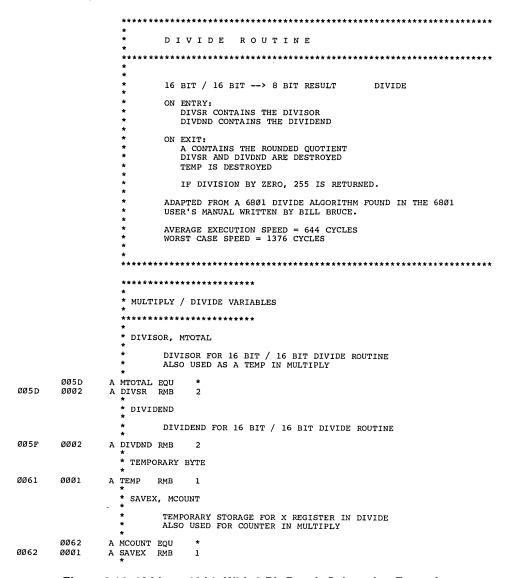

| 3-14             | 16-bit — 16-bit With 8-Bit Result Subroutine Example                  |                |

| 3-15             | 16-bit — 16-bit With 16-Bit Result Subroutine Example                 |                |

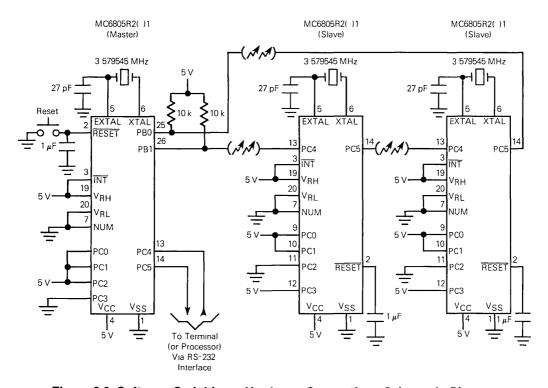

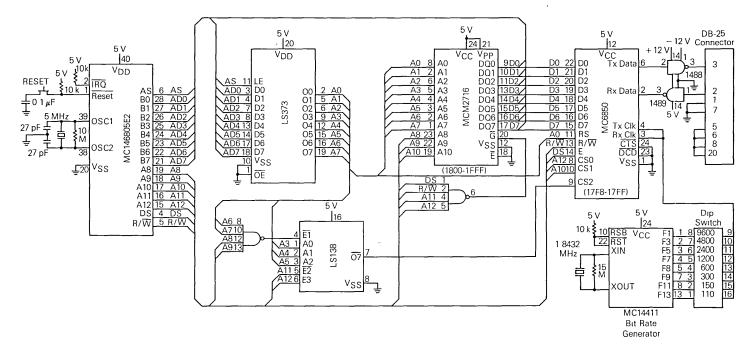

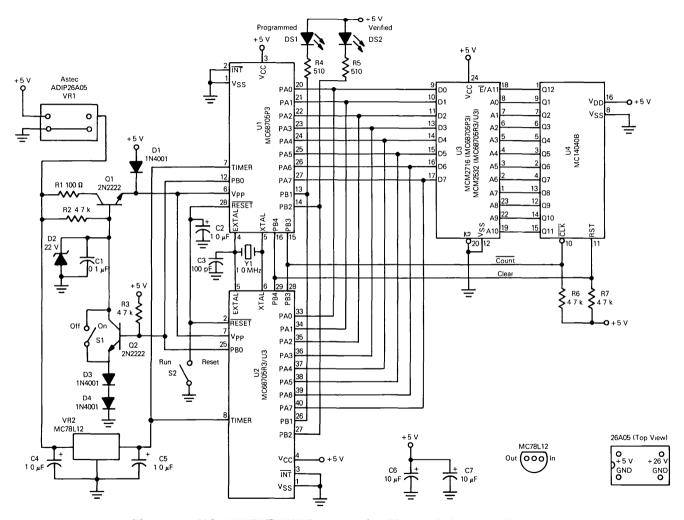

| 3-16             | ASSIST05 Interface Schematic Diagram                                  |                |

| 3-17             | ASSIST05 Program Listing                                              | 57             |

| 4-1              | M6805 HMOS/M146805 CMOS Family Block Diagram                          |                |

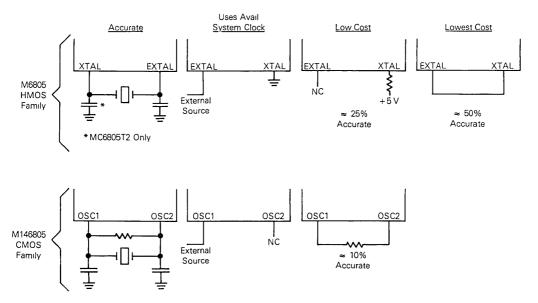

| 4-2              | M6805 HMOS/M146804 CMOS Family Oscillator Modes                       |                |

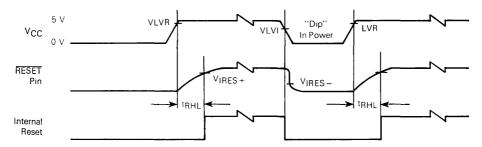

| 4-3              | Power and Reset Timing                                                |                |

| 4-4              | Power up Reset Delay Circuit                                          | 78             |

## LIST OF ILLUSTRATIONS (Continued)

| Figure<br>Number       | Title                                                     | Page<br>Number |

|------------------------|-----------------------------------------------------------|----------------|

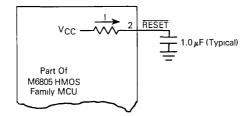

| 4-5                    | External Interrupt                                        |                |

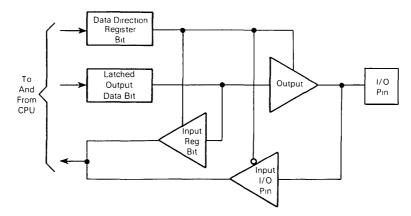

| 4-6                    | Typical Port I/O Circuitry                                |                |

| 4-7                    | M146805 CMOS Family Timer Block Diagram                   |                |

| 4-8                    | M6805 HMOS Family Timer Block Diagram                     |                |

| 4-9                    | A/D Block Diagram                                         |                |

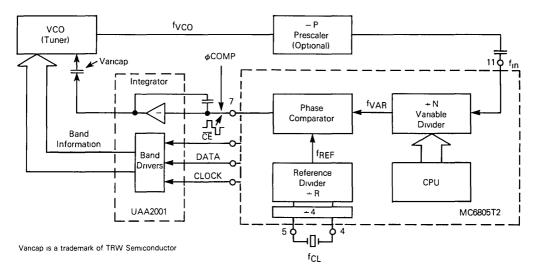

| 4-10                   | Phase-Lock-Loop in an rf Synthesizer                      |                |

| 4-11                   | MC6805T2 PLL Block Diagram                                | 90             |

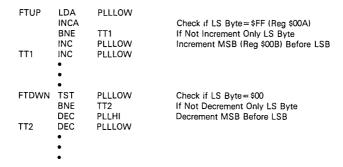

| 4-12                   | Typical Fine Tune Software Example                        | 91             |

| 4-13                   | Phase Comparator Output Waveform                          | 92             |

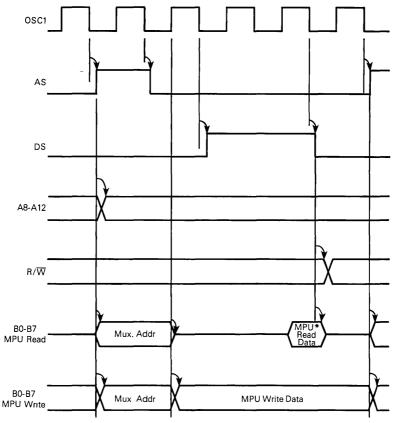

| 4-14                   | OSC1 to Bus Transitions                                   | 93             |

| 5-1                    | CBUG05 Debug Monitor Minimum CMOS Only Systems,           | 07             |

| <b>5</b> 0             | Schematic Diagram                                         | 97             |

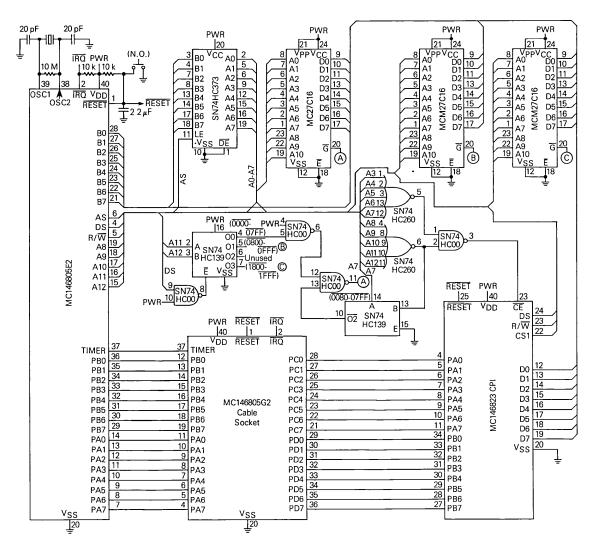

| 5-2<br>5-2             | MC146805G2 Emulator Schematic Diagram                     |                |

| 5-3<br>5-4             | MCU Interface With Multiplexed Bus Peripheral             | 100<br>100     |

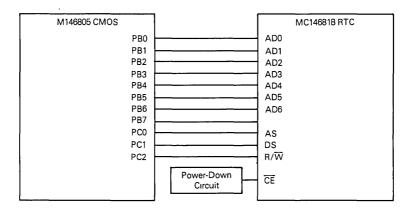

| 5- <del>4</del><br>5-5 | MCU to MC146818 Interface Software                        | 100            |

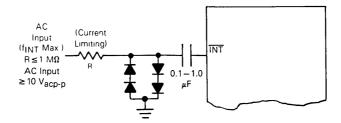

| 5-6                    | Typical Zero Crossing Interrupt Circuit Schematic Diagram | 101            |

| 5-0<br>5-7             | Time of Day Clock Software Listing                        | 102            |

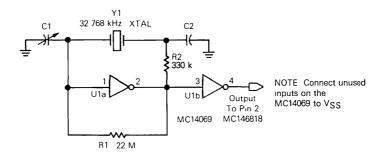

| 5-7<br>5-8             | 32.768 kHz Square Wave Oscillator Schematic Diagram       |                |

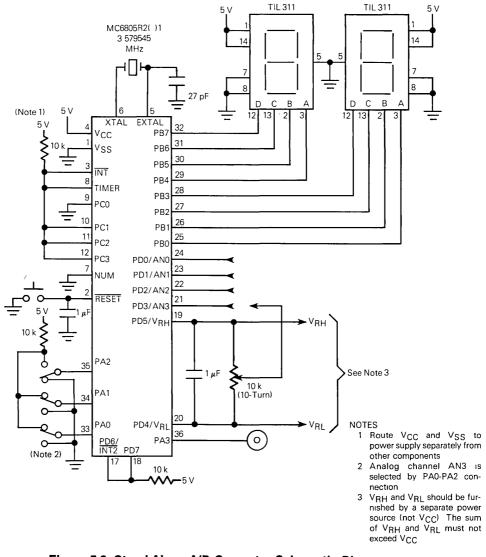

| 5-9                    | Stand-Alone A/D Converter Schematic Diagram               |                |

| 5-10                   | A/D Conversion Routine Software                           |                |

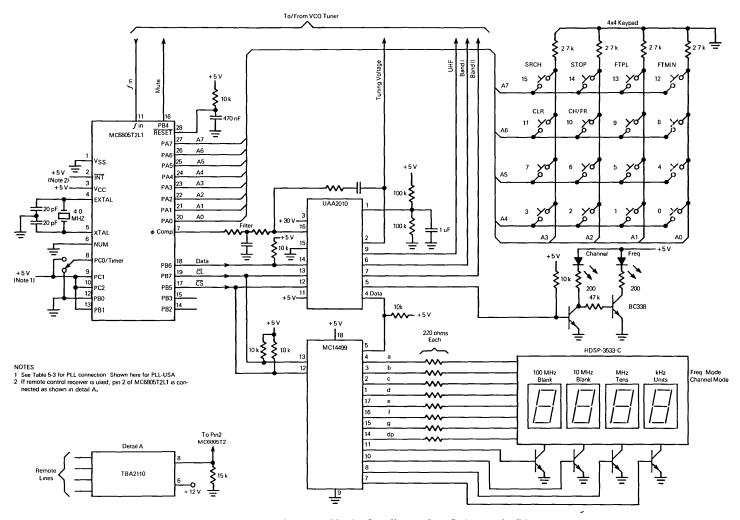

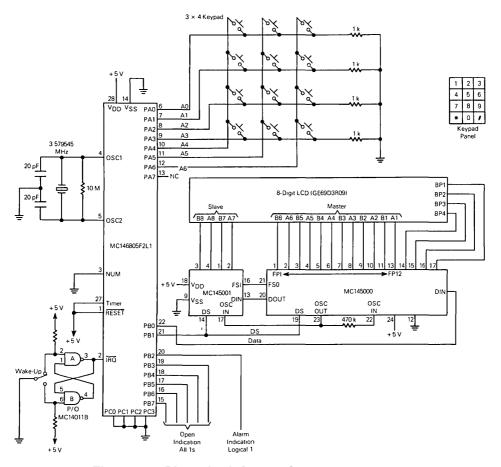

| 5-11                   | Synthesizer Mode Configuration Schematic Diagram          |                |

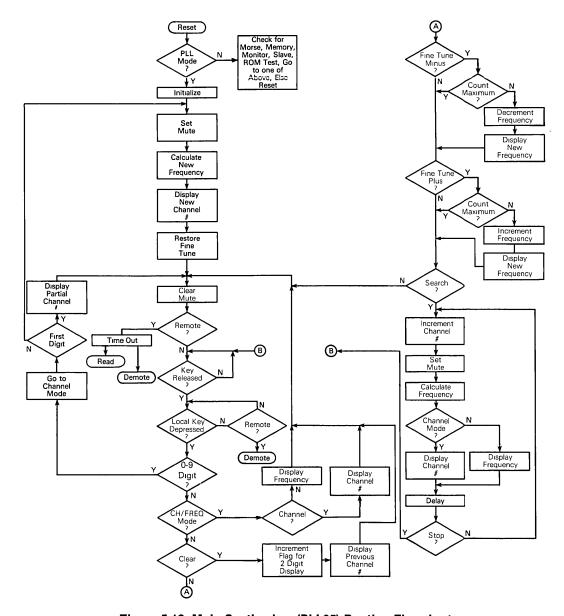

| 5-12                   | Main Synthesizer (PLL05) Routine Flowchart                | 117            |

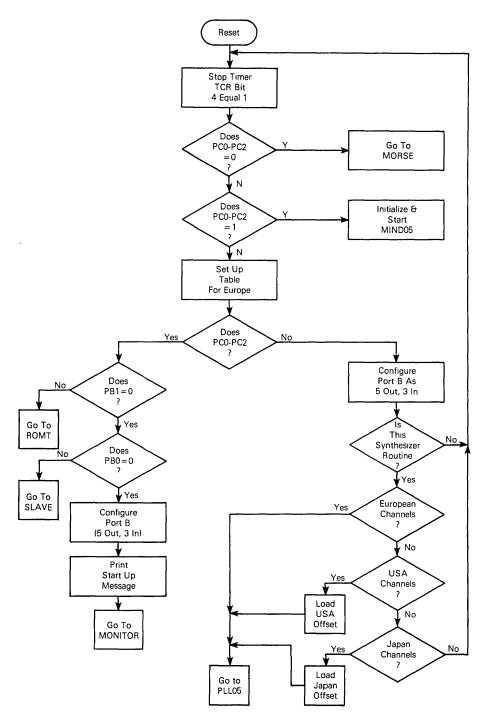

| 5-13                   | Reset Routine Flowchart                                   |                |

| 5-14                   | Digital Lock System Schematic Diagram                     |                |

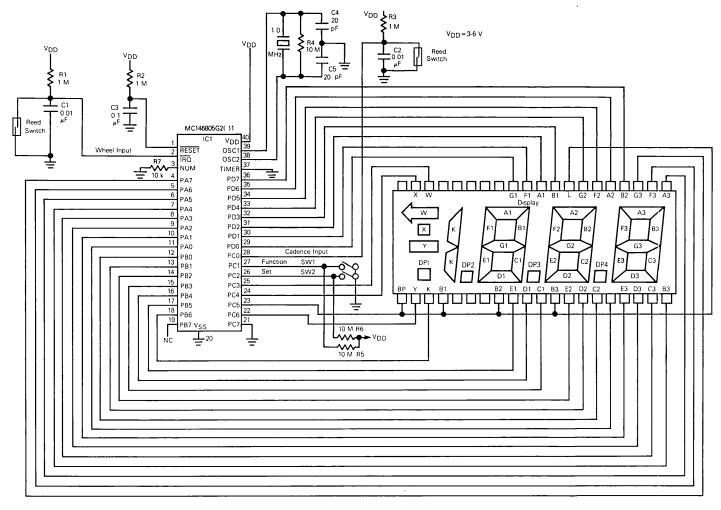

| 5-15                   | Bicycle Computer Schematic Diagram                        |                |

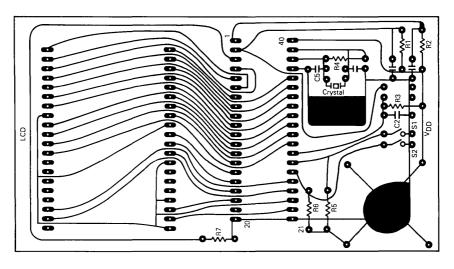

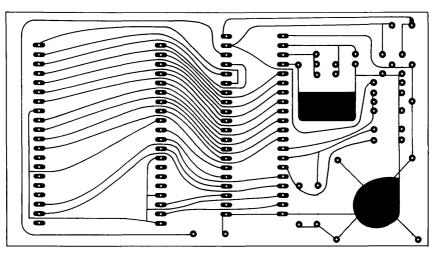

| 5-16                   | Bicycle Computer Circuit Board                            |                |

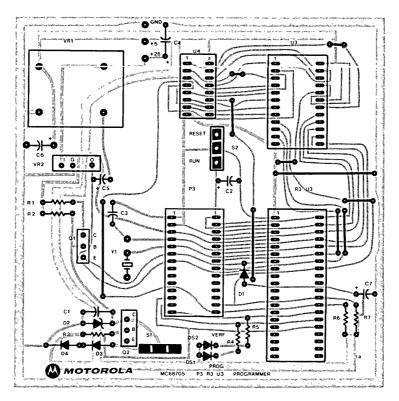

| 6-1                    | MC68705P3/R3/U3 Programming Module Schematic Diagram      | 128            |

| 6-2                    | MC1468705G2 Programming Circuit Schematic Diagram         |                |

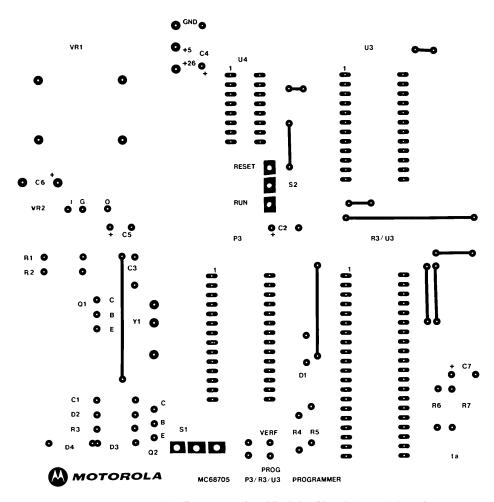

| 6-3                    | MC68705P3/R3/U3 Programming Module Parts Layout           |                |

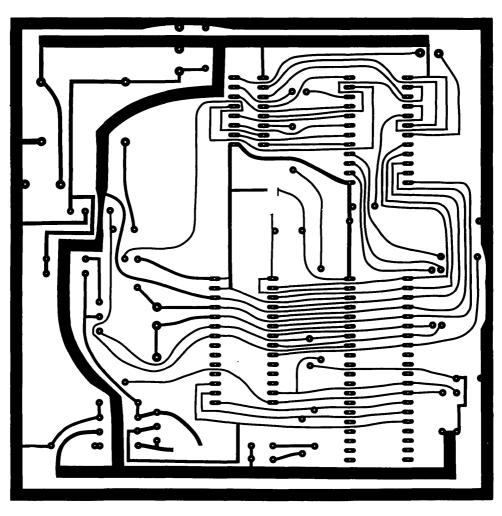

| 6-4                    | MC68705P3/R3/U3 Programming Module Circuit Board Art      |                |

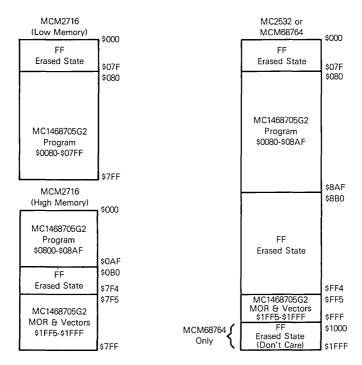

| 6-5                    | MC1468705G2 Programming Memory Location in MC2716,        | 10-1           |

| J <b>J</b>             | MCM2532, or MCM68764                                      | 137            |

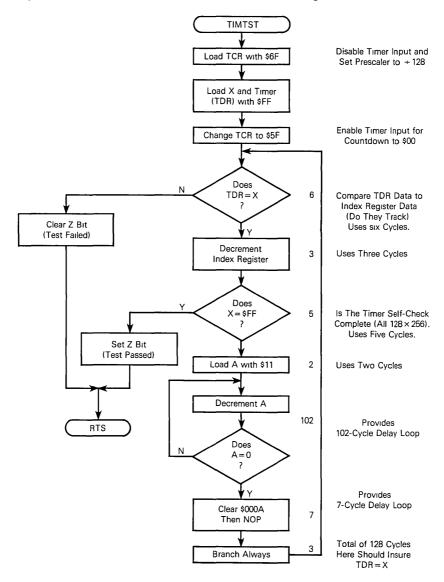

| 7-1                    | MC146805G2-MPU Timer Test (TIMTST) Flowchart              | 141            |

#### LIST OF TABLES

| Table<br>Number                               | Title                                                                                                                                                                                                                                                                                        | Page<br>Number                  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 1-1                                           | M6805 HMOS/M146805 CMOS Family List of Features                                                                                                                                                                                                                                              | 8                               |

| 3-1<br>3-2                                    | Display Format Conversions                                                                                                                                                                                                                                                                   | 36<br>52                        |

| 4-1<br>4-2<br>4-3                             | Comparison of Features Between HMOS and CMOS                                                                                                                                                                                                                                                 | 82                              |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7 | Comparison of Processing Techniques  A/D Control Inputs for Selecting AN0-AN3 and Calibration Channels PLL Country/Land Selection Configuration  Channel Characteristics for Europe  Channel Characteristics for USA  Channel Characteristics for Japan  List of Available Application Notes | 107<br>108<br>111<br>113<br>115 |

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6        | M6805 HMOS Family Mask Option Register M1468705G2 Mask Option Register M6805 HMOS EPROM LED Results MC1468705G2 EPROM LED Results MC68705P3/R3/U3 Programing Module Parts List MC1468705G2 MCU EPROM Programming Circuits Parts List                                                         | 127<br>127<br>129<br>131        |

| 7-1                                           | Subroutine Enter/Exit Addresses                                                                                                                                                                                                                                                              | 139                             |

This manual provides users with concise up-to-date information on Motorola's M6805 HMOS/M146805 CMOS family. This versatile family of microcomputers and a microprocessor offers many versions for diverse applications with the latest features including EPROM for easy prototype system design, low power versions, low cost, and powerful architecture.

Thorough descriptions and instructions are given throughout the manual — beginning with a general description and introduction of the M6805 HMOS/M146805 CMOS family and including the explanation of optimization for controller applications, choice of HMOS and CMOS technology, and hardware options. Detailed information on software (descriptions and applications) and hardware (features and applications) is provided in the main chapters. Also included are chapters on the EPROM programmer and on the self-test, the on-chip firmware test capability. Appendices are included to provide designers with the latest M6805 HMOS/M146805 CMOS family programming information.

| · |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

### CHAPTER 1 GENERAL DESCRIPTION

#### 1.1 INTRODUCTION TO THE M6805 HMOS/M146805 CMOS FAMILY

The continuing technological evolution in microprocessors and microcomputers has resulted in larger, more complex, and more powerful devices which contain characteristics of both mini and mainframe computers. The technological evolution of the MC6800 to the M6809 Family and the 16-bit MC68000 is a clear example of devices which evolved upward from the mini and mainframe computer architecture. The experience gained during this upward evaluation has greatly enhanced the expertise needed to design more powerful low- and mid-range devices. By using the architectural characteristics of the mini and mainframe computers, the microprocessor/microcomputer hardware and software becomes regular and versatile, yet simple.

The demanding requirements of the mid-range control-oriented microprocessor market (low cost) can be met with the M6805 HMOS/M146805 CMOS Families of microcomputer (MCU) and microprocessor (MPU). The M6805 HMOS/M146805 CMOS Families are the first to provide the software and hardware capabilities of more advanced computers to the controller market. Previously, designers and manufacturers were required to choose between "no processor at all" or a processor that functioned more like a calculator than a computer.

Control-oriented microprocessors have evolved from two different bases: calculator based and computer based. The calculator-based design was at first considered as a natural building block for controllers since, most often, a controller was required to be a complete self-contained unit. However, calculator based control-oriented microprocessors use a split memory architecture containing separate data paths between the CPU and peripherals (memory or I/O or registers). In addition, calculator-based I/O, display, and keypad were separated from program and data storage memory. Because of this, separate address maps were required which forced the inclusion of many special purpose instructions and resulted in an irregular architecture. As a result, these calculator based devices required that hardware and software designers remember and consider many special cases in order to perform any task. Thus, the software and hardware became very random, irregular, and difficult to update.

The computer-based design led to another group of processors, like the MC6800, which contained many features of large computers. These devices contain a single data bus which allows access to a single address map, eliminating the need for split memory architecture. In this one-address map design, all I/O, program, and data may be accessed with the same instruction; therefore, there are fewer instructions to remember. The

actual number of unique instructions is increased by a variety of addressing modes which define how an instruction accesses any data required for the operation. For example, depending upon which addressing mode is used, the accumulator may be loaded (LDA instruction) with data in six different ways. This effectively provides the programmer with more tools to work with but fewer things to remember. Thus, because of regularity of the architecture, the hardware is regular and can be implemented more efficiently.

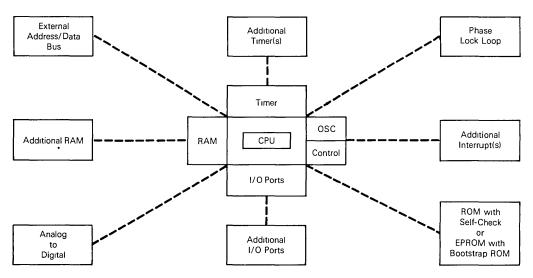

All members of the M6805 HMOS/M146805 CMOS Family of MCUs and MPUs are designed around a common core which consists of CPU, timer, oscillator, ROM (EPROM, masked, or none), control section (for interrupts and reset), and varying amounts of bidirectional I/O lines. In addition to this common core, additional items can be added such as: additional memory, A/D converter, phase-lock-loop, and additional I/O lines. As of the printing of this manual in late 1982, this versatile common core design has already provided 11 different M6805 HMOS Family devices and four different M146805 CMOS Family devices. These 15 different family members allow the user to choose the device best suited for his particular application. The increased number of devices could preclude paying for a supplied feature that is not needed or paying extra to externally add a needed feature that is not included.

Information describing I/O options and general operation of the M6805 HMOS/M146805 CMOS Family members is included in this chapter. Detailed information concerning device operation is included in the following chapters as well as appendices. Chapters discussing hardware and software applications are also included to illustrate some of the family features and provide a useful tool for the user.

The M6805 HMOS/M146805 CMOS Family architecture and instruction set are very similar to that of Motorola's MC6800. Any programmer who has worked with the MC6800 can attain equivalent proficiency with the M6805 HMOS/M146805 CMOS Family in a relatively short time. In some respects the M6805 HMOS/M146805 CMOS Family is more powerful than the MC6800 (depending upon the application) as a result of architecture optimization. Appendix A summarizes the architectural and instruction set differences between the M6805 HMOS/M146805 CMOS and M6800 Families.

#### 1.2 OPTIMIZED FOR CONTROLLER APPLICATIONS

The M6805 HMOS/M146805 CMOS Family architecture has been optimized for controller applications, rather than general purpose data processing operations. Several features contribute to this optimization.

#### 1.2.1 Instruction Set

The instruction set, used with the M6805 HMOS/M146805 CMOS Family, is specifically designed for byte-efficient program storage. Byte efficiency permits a maximum amount of program function to be implemented within a finite amount of on-chip ROM. Improved ROM efficiency allows the M6805 HMOS/M146805 CMOS Family to be used in applications where other processors might not perform the task in the available ROM space.

More features may be included in applications where ROM space is more than adequate. In some cases the user might wish to include programs for more than one application. In such cases the appropriate program could be selected by the power-up initialization program. The ability to nest subroutines, the addition of true bit test and bit manipulation instructions, the multi-function instructions, and the versatile addressing modes all contribute to byte efficiency.

Superficial comparisons of the number of bytes per instruction for the M6805 HMOS/M146805 CMOS Family, when compared to other machines in this class, can be very misleading. A single M6805 HMOS/M146805 Family instruction occupying 2 or 3 bytes accomplishes as much real programming work as several single byte instructions, or a subroutine, would accomplish in many other processors.

The bit test and bit manipulation instructions permit the program to:

branch on bit set branch on bit clear set bit clear bit.

These instructions operate on any individual bit in the first 256 address spaces (page zero). As such, the bit manipulations access I/O pins, RAM bits, and ROM bits.

In the M6805 HMOS/M146805 CMOS Family, a page consists of 256 consecutive memory locations. Page zero includes the lowest-numbered 256 memory addresses (\$00 through \$FF), page one the next 256 memory addresses (\$100 through \$1FF), etc. The first 128 bytes of page zero memory locations (\$00 through \$7F) are used primarily for I/O function registers, timer, PLL, RAM, and the stack. The next 128 bytes of page zero (\$80 through \$FF) contain ROM which is available for the user program. An efficient use of pages zero and one would be for storage of tables since these two pages are easily accessed by the indexed addressing mode.

#### 1.2.2 Addressing Modes

One of the chief measures of the effectiveness of a computer architecture is its ability to access data. The M6805 HMOS/M146805 CMOS Family has several major memory addressing modes. They include immediate, direct, and extended, plus three distinct indexed modes. The programmer is thus given the opportunity to optimize the code to the task. The indexed addressing modes permit conversion tables, jump tables, and data tables to be located anywhere in the address space. The use of tables is an important tool in controller type applications.

Efficient addressing methods are coupled with instructions which manipulate memory without disturbing the program registers. Thus, RAM may be used for the same functions that other processors use general purpose registers (increment, decrement, clear, complement, test, etc.). The M6805 HMOS/M146805 CMOS Family members have a very versatile, efficient, and easy-to-use I/O structure. All microcomputer I/O function registers are memory mapped into the first 16 processor addresses. Advantage is thus taken of the efficient addressing modes, the many memory reference instructions, and the use of

RAM (or I/O registers) as general purpose registers. As an example, there are 64 unique instructions which permit the programmer to modify an I/O port. The programmer's problem is not so much how to accomplish a given I/O task, but rather to choose the most effective method from the many methods available. In addition, as with other M6800 Family I/O devices, most M6805 HMOS/M146805 CMOS Family I/O pins are individually programmed as inputs or outputs under software control.

#### 1.3 CHOICE OF TECHNOLOGIES

The first option to be selected by the system designer is the choice between HMOS or CMOS as a processor technology.

#### 1.3.1 HMOS Features

The NMOS (N-Channel Metal Oxide on Silicon) technology has been the mainstay of the M6800 Family. The current state of the continual shrinking of NMOS is called HMOS (High-Density NMOS).

The prime consideration in choosing an M6805 HMOS Family microcomputer is its lower price. Motorola's highly-efficient fabrication process results in a greater yield than other processes. The decreased production costs ultimately result in lower selling prices. The economics of large scale production also contribute to a low selling price.

The high speed of Motorola's HMOS, when compared to PMOS or other NMOS processors, produces a very high performance/price ratio.

A low voltage inhibit (LVI) feature may be selected on HMOS versions. The LVI option forces a reset when the supply voltage drops below a threshold which guarantees correct operation. The CMOS Family members offer wide operating voltage and clock speed ranges, which preclude establishing an LVI threshold.

#### 1.3.2 CMOS Features

An emerging microcomputer technology is CMOS (Complementary MOS, both P- and N-Channel devices). The unique properties of CMOS are increasingly attractive. Some applications are simply not feasible with PMOS, NMOS, or HMOS microcomputers.

Maximum power consumption of CMOS parts ranges from 1/15 to 1/200 of that of an equivalent HMOS part. Low power consumption is important in several classes of applications; thus, CMOS microcomputers are desirable.

- (a) Portable Equipment Hand-held and other portable units operated from self-contained batteries. Battery drain is frequently important in such applications.

- (b) Battery Back-Up CMOS is appropriate in ac powered applications when some or all system functions must continue during a power outage. A small, rechargeable battery keeps a CMOS MCU operable.

- (c) Storage Batteries Automotive and telephone equipment operate from larger batteries. Automobile battery drain must be low when the engine is not running. Telephones must operate independently of ac power.

- (d) Heat Dissipation Packaging constraints sometimes preclude dissipating electronics-generated heat, or the heat is costly to dissipate. In addition, dissipation of heat directly effects device reliability.

- (e) Power Costs The cost of electricity to power the equipment becomes a significant factor in calculating the total life cycle cost of equipment which operates continuously.

The CMOS technology inherently operates over a wide range of supply voltages. Thus, CMOS is used where the supply voltage fluctuates, such as in battery powered equipment; or if line power is available, a lower-cost, loosely regulated supply may be used.

An additional advantage of CMOS is that circuitry is fully static. CMOS microcomputers may be operated at any clock rate less than the guaranteed maximum. This feature may be used to conserve power, since power consumption increases with higher clock frequencies. Static operation may also be advantageous during product developments.

#### 1.4 HARDWARE

Every M6805 HMOS/M146805 CMOS Family microcomputer or microprocessor contains hardware common to all versions, plus a combination of options unique to a particular version. There are also several differences among family members of which potential users should be aware.

#### 1.4.1 Hardware Common To All Devices

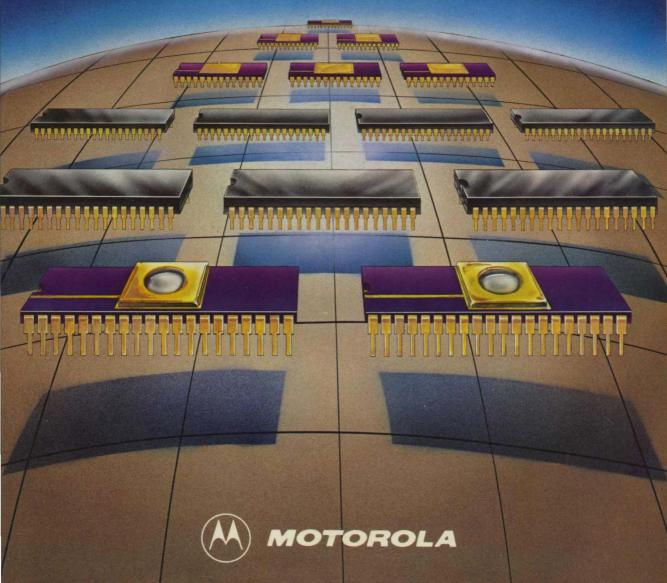

Figure 1-1 details the hardware functional blocks common to all M6805 HMOS/M146805 CMOS Family devices.

The central processor unit (CPU) contains the 8-bit arithmetic logic unit, accumulator, program counter, index register, stack pointer, condition code register, instruction decoder, and timing and control logic. These elements resemble the M6800 Family of microprocessors which reflect the M6805 HMOS/M146805 CMOS Family heritage.

The M6805 HMOS/M146805 CMOS Family has on-chip RAM, permitting the microcomputer versions to operate without external memory. The addressing modes and register-like memory operations use this RAM to the fullest extent possible.

Parallel I/O capability, with pins programmable as input or output, is built into every unit.

The external interrupt input, and the capability for multiple nesting of subroutine and interrupts, are features usually found on much more powerful architectures. They permit an M6805 HMOS/M146805 CMOS Family MCU to be used in projects usually considered too complex for microcomputers.

Figure 1-1. M6805 HMOS/M146805 CMOS Family Basic Microcomputer Block Diagram

A feature which greatly simplifies software development and extends the capability of a microcomputer is an on-chip timer/counter. This 8-bit counter and its prescaler can be programmed for innumerable functions. It can generate an interrupt at software selected intervals. It can also be used as an event counter to generate an interrupt after some software selected number of external events. The timer/counter can also be used for timekeeping, measuring and generating pulses, and counting external events. In the case of the M146805 CMOS Family devices, the timer can be set to "wake-up" the processor from the power-saving WAIT mode.

The external interrupt and timer/counter interrupt are vectored to different service routine addresses. This greatly simplifies interrupt programming. It also speeds execution of interrupt routines, by eliminating software interrupt polling, for determining the source of the interrupt.

The first 16 processor addresses are reserved for memory mapped I/O registers. The programmer of the M6805 HMOS/M146805 CMOS Family may take full advantage of the versatile addressing modes and the register-like RAM operations of the Family.

#### 1.4.2 Family Options

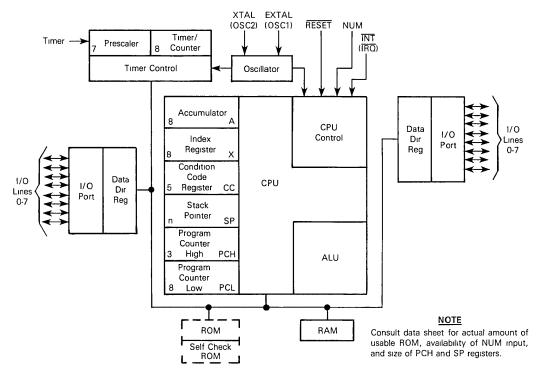

In addition to the common hardware described previously, users can make selections from among devices having a combination of hardware options. Potential users should consult their local Motorola sales representative or the most recent data brochures to determine which versions have reached production. Table 1-1 provides a listing of the features included in each family member. Figure 1-2 illustrates the part number nomenclature of three different members of the M6805 HMOS/M146805 CMOS Family.

Figure 1-2. M6805 HMOS/M146805 CMOS Family Nomenclature Example

The first option to be selected by the system designer is the choice of technology. In general, the HMOS units would be selected unless the application specifically requires one of the unique characteristics of CMOS.

User ROM sizes range from none, for the microprocessor, to 4K and larger. Future versions will have additional ROM sizes. When self-check ROM is a part of the device, the ROM area used in the self-check operation is not included in the published ROM sizes. The entire ROM space is available to the user for his program.

A portion of the ROM is located in page zero (the direct page) to facilitate more efficient access to look up tables using all available addressing modes. This ROM can, of course, be used for program storage as well as look-up tables.

The initial M6805 HMOS/M146805 CMOS Family devices contain either 64 or 112 bytes of on-chip RAM which is located in page zero. Future devices may accommodate additional or differing amounts of RAM.

Package size options permit as many as four, full 8-bit bidirectional I/O ports. Each pin is defined under software control as an input or output by loading a data direction register.

Table 1-1. M6805 HMOS/M146805 CMOS Family List of Features

#### M6805 HMOS Family MCUs

| Features                    | MC6805P2  | MC6805P4  | MC6805P6  | MC6805R2   | MC6805R3   | MC6805T2   | MC6805U2  | MC6805U3  |

|-----------------------------|-----------|-----------|-----------|------------|------------|------------|-----------|-----------|

| Technology                  | HMOS      | HMOS      | HMOS      | HMOS       | HMOS       | HMOS       | HMOS      | HMOS      |

| Number of Pins              | 28        | 28        | 28        | 40         | 40         | 28         | 40        | 40        |

| On-Chip RAM (Bytes)         | 64        | 112*      | 64        | 64         | 112        | 64         | 64        | 112       |

| On-Chip User<br>ROM (Bytes) | 1.1K      | 1.1K      | 1 8K      | 2K         | 3 8K       | 2 5K       | 2K        | 3 8K      |

| External Bus                | None      | None      | None      | None       | None       | None       | None      | None      |

| Bidirectional I/O Lines     | 20        | 20        | 20        | 24         | 24         | 19         | 24        | 24        |

| Unidirectional I/O<br>Lines | None      | None      | None      | 6 Inputs   | 6 Inputs   | None       | 8 Inputs  | 8 Inputs  |

| Other I/O Features          | Timer .   | Timer     | Timer     | Timer, A/D | Timer, A/D | Timer, PLL | Timer     | Timer     |

| External Interrupt Inputs   | 1         | 1         | , 1       | 2          | 2          | 2          | 2         | 2         |

| EPROM Version               | MC68705P3 | MC68705P3 | MC68705P3 | MC68705R3  | MC68705R3  | None       | MC68705U3 | MC68705U3 |

| STOP and WAIT               | No        | No        | No        | No         | No         | No         | No        | No        |

<sup>\*</sup>Indicates standby RAM.

#### M6805 HMOS/M146805 CMOS Family EPROM MCUs

| Features                     | MC68705P3  | MC68705R3  | MC68705U3  | MC1468705G2 |

|------------------------------|------------|------------|------------|-------------|

| Technology                   | HMOS       | HMOS       | HMOS       | CMOS        |

| Number of Pins               | 28         | 40         | 40         | 40          |

| On-Chip RAM (Bytes)          | 112        | 112        | 112        | 112         |

| On-Chip User<br>ROM (Bytes)  | 1 8K EPROM | 3 8K EPROM | 3.8K EPROM | 2K EPROM    |

| External Bus                 | None       | None       | None       | None        |

| Bidirectional I/O Lines      | 20         | 24         | 24         | 32          |

| Unidirectional I/O<br>Lines  | None       | 6 Inputs   | 8 Inputs   | None        |

| Other I/O Features           | Timer      | Timer, A/D | Timer      | Timer       |

| External Interrupt<br>Inputs | 1          | 2          | 2          | 1           |

| EPROM Version                | _          | _          | _          |             |

| STOP and WAIT                | No         | No         | No         | Yes         |

#### M146805 CMOS Family MPU/MCUs

| Features                     | MC146805E2 | MC146805F2 | MC146805G2  |

|------------------------------|------------|------------|-------------|

| Technology                   | CMOS       | CMOS       | CMOS        |

| Number of Pins               | 40         | 28         | 40          |

| On-Chip RAM (Bytes)          | 112        | 64         | 112         |

| On-Chip User ROM<br>(Bytes)  | None       | 1K         | 2K          |

| External Bus                 | Yes        | None       | None        |

| Bidirectional I/O Lines      | 16         | 16         | 32          |

| Unidirectional I/O<br>Lines  | None       | 4 Inputs   | None        |

| Other I/O Features           | Timer      | Timer      | Timer       |

| External Interrupt<br>Inputs | 1          | 1          | 1           |

| EPROM Version                | None       | None       | MC1468705G2 |

| STOP and WAIT                | Yes        | Yes        | Yes         |

## CHAPTER 2 SOFTWARE DESCRIPTION

#### 2.1 INTRODUCTION

During the early 1970's, microprocessors (MPU) and microcomputers (MCU) helped ease the shortage of hardware designers by providing the hardware with more intelligence. However, because the power of any MPU or MCU is the result of the software programs, a shortage of software engineers was created. Thus, as MPUs and MCUs reduced hardware costs, software development costs rose. As a result, the system designer of today must carefully weigh the software and support costs of his system. Processors such as those of the M6805 HMOS/M146805 CMOS Family, which are designed to include the programming features inherited from minicomputers, require less effort from the programmer and make system design much more efficient. The importance of "userfriendly" software in mini and mainframe computers is a widely accepted fact. Easy-to-use software is the key to writing and maintaining efficient programs.

The M6805 HMOS/M146805 CMOS Family architecture is based upon the Von Neumann model which places all data, program, and I/O spaces into a single address map. Thus, since only a single address map must be supported, very few special purpose instructions are necessary in the M6805 HMOS/M146805 CMOS Family instruction set. The overall result of this is a small, very regular, and easy-to-remember instruction set.

A regular instruction set is symmetrical in that, for most instructions, there is a complement instruction. Some of these instructions (plus complements) are listed below.

LDA — STA Load and Store

INC - DEC Increment and Decrement

BEQ — BNE Branch If Equal and Branch If Not Equal

ADD - SUB Add and Subtract

AND — ORA Logic AND and Logic OR

BCLR — BSET Bit Clear and Bit Set

ROR — ROL Rotate Right and Rotate Left

JSR — RTS Jump-To-Subroutine and Return-From-Subroutine

The symmetry provided by the M6805 HMOS/M146805 CMOS Family instruction set means that the programmer need only remember about 30 to 40 separate instructions to know the entire instruction set. The M6805 HMOS Family has 59 instructions in its instruction set; whereas, the M146805 CMOS Family has 61. The two additional instructions for the M146805 CMOS Family are the STOP and WAIT instructions which enable one of the CMOS low-power standby modes.

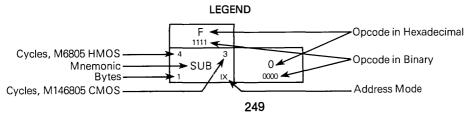

The instruction set is expanded by the use of a variety of versatile addressing modes. The addressing modes, which are part of the minicomputer heritage of M6805 HMOS/M146805 CMOS Family, expand the instruction set by allowing the programmer to specify how the data for a particular instruction is to be fetched. As illustrated in the Opcode Map of Appendix I, The 59/61 separate instructions, enhanced by the seven addressing modes, expand into 207/209 opcodes; however, the programmer need only remember 66/68 items (59/61 instructions plus seven addressing modes) instead of 207/209.

#### 2.2 REGISTER SET

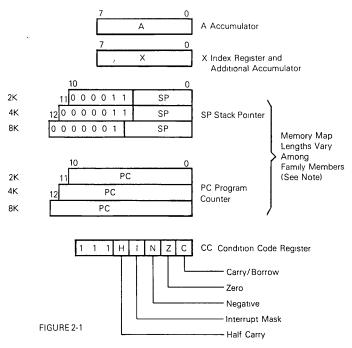

Each M6805 HMOS/M146805 CMOS Family member contains five registers as shown in Figure 2-1. The accumulator (A) and index register (X) are used as working program registers. The condition code register (CC) is used to indicate the current status of the processor program. The program counter (PC) contains the memory address of the next instruction that the processor is to execute. The stack pointer (SP) register contains the address of the next free stack location. For more information concerning each register, see the section below describing that register.

NOTE. The stack pointer and program counter size is determined by the memory size that the family member device can access, e.g., an 8K memory map requires a 13-bit stack pointer and program counter

Figure 2-1. M6805 HMOS/M146805 CMOS Family Register Architecture

#### 2.2.1 Accumulator (A)

The A register is a general purpose 8-bit register that is used by the program for arithmetic calculations and data manipulations. The full set of read/modify/write instructions operates on the A register. The accumulator is used in the register/memory instructions for data manipulation and arithmetic calculation. Refer to the Instruction Set Summary discussion later in this chapter for information about the read/modify/write and register/memory instruction. An example using the accumulator to add the contents of two memory locations is shown below.

| B6 | 50 | LDA | \$50 | Load accumulator with contents of memory location \$50.      |

|----|----|-----|------|--------------------------------------------------------------|

| BB | 87 | ADD | \$87 | Add the contents of memory location \$87 to the accumulator. |

| B7 | 3C | STA | \$3C | Store the accumulator contents in memory location \$3C.      |

#### 2.2.2 Index Register (X)

The index register is used in the indexed modes of addressing or used as an auxiliary accumulator. It is an 8-bit register and can be loaded either directly or from memory, have its contents stored in memory, or its contents can be compared to memory.

In indexed instructions, the X register provides an 8-bit value, that is added to an instruction-provided value, to create an effective address. The indexed addressing mode is further described in the Addressing Modes paragraph of this chapter.

The X register is also used in the M6805 HMOS/M146805 CMOS Family for limited calculations and data manipulation. The full set of read/modify/write instructions operates on the X register as well as the accumulator. Instruction sequences which do not use the X register for indexed addressing may use X as a temporary storage cell, or accumulator.

The following example shows a typical use of the index register in one of the indexed addressing modes. The example performs a block move that is BCNT in length.

|        | LDX  | #BCNT    | GET LENGTH      |

|--------|------|----------|-----------------|

| REPEAT | LDA  | SOURCE,X | GET DATA        |

|        | STA  | DESTIN,X | STORE IT        |

|        | DECX | , ,      | NEXT            |

|        | BNE  | REPEAT   | REPEAT IF MORE. |

The X register is also useful in counting events since it can be incremented or decremented. The INCX or DECX instructions can be used to control the count. By either decrementing or incrementing the X register, starting at a known value, and then comparing the X register contents to the contents of a memory location (or a specific number) a loop can be ended or a branch taken after a certain number of events.

The following routine uses the index register as a counter for a keypad debounce routine of CNT X 6, CMOS (or CNT X 8, HMOS).

| ΑE | FF | DBNCE | LDX #CNT  | CNT = 255 in this example |

|----|----|-------|-----------|---------------------------|

| 5A |    | AGAIN | DECX      |                           |

| 26 | FD |       | BNE AGAIN |                           |

#### 2.2.3 Program Counter (PC)

The PC contains the memory address of the next instruction that is to be fetched and executed. Normally, the PC points to the next sequential instruction; however, the PC may be altered by interrupts or certain instructions. During a valid interrupt, the PC is loaded with the appropriate interrupt vector. The jump and branch instructions modify the PC so that the next instruction to be executed is not necessarily the next instruction in physical memory. The actual size of the PC depends upon the size of the address space of the individual family members and currently ranges from 11 to 13 bits.

#### 2.2.4 Stack Pointer (SP) ·

The stack array (stack) is an area of memory in RAM used for the temporary storage of important information. It is a sequence of registers (memory locations) used in a last-infirst-out (LIFO) fashion. A stack pointer is used to specify where the last-in entry is located or where the next-in entry will go. Since the stack must be written to, as well as read, it must be located in RAM.

Interrupts and subroutines make use of the stack to temporarily save important data. The SP is used to automatically store the return address (two bytes of the PC) on subroutine calls and to automatically store all registers (five bytes; A, X, PC and CC) during interrupts. The saved registers may be interleaved on the stack (nested), thus allowing for: (1) nesting of subroutines and interrupts, (2) subroutines to be interrupted, and (3) interrupts to call subroutines. The nesting of subroutines and interrupts can only occur to some maximum amount, which is described below.

Since the M6805 HMOS/M146805 CMOS is a family of devices, the actual size of the stack pointer may vary with memory size of the particular family member (see appropriate data sheets). But from the programmer's perspective, the stack pointers all appear similar on the different members. Both the hardware RESET pin and the reset stack pointer (RSP) instruction reset the stack pointer to its maximum value (\$7F on all current members). The stack pointer on the M6805 HMOS/M146805 CMOS Family always points to the next free location on the stack. Each "push" decrements the SP while each "pull" increments it ("push" and "pull" are not available as user instructions in the M6805 HMOS/M146805 CMOS Family).

Nested subroutine calls and interrupts must not underflow the SP. The usable stack length will vary between devices as well as between the M6805 HMOS and M146805 CMOS Families. In the M6805 HMOS Family, the usable stack length is  $2^n-1$  (where n= the number of bits in the stack pointer); however, in the M146805 CMOS Family the

usable stack length is  $2^n$  (where n = number of bits in the stack pointer). When the allowable stack length is exceeded, the SP will wrap around to the top of stack. This condition of stack underflow should be avoided since the previously stacked data will be lost. An example of calculating the usable stack length for an M6805 HMOS Family device with a 5-bit stack pointer is:  $2^5 - 1$  or 31 bytes maximum. However, for an M146805 CMOS Family device, with a 6-bit stack pointer, the calculation is:  $2^6$  or 64 bytes maximum.

A 5-bit M6805 HMOS Family device SP accommodates up to 15 nested subroutine calls (30 bytes), six interrupts (30 bytes), or a mixture of both. The programmer must exercise care when approaching the underflow threshold. When the SP underflows it will wrap around, and the contents more than likely are lost. The stack limit in the 5-bit M6805 HMOS Family example above is thus stated to be 31, not 32, bytes. The stack limit is well beyond the needs required by most programs. A maximum subroutine nesting of five levels (10 bytes) coupled with one interrupt level (five bytes) occupies only 15 bytes of stack space. The allowed stack length is typically traded off against the needed data RAM space.

In the M6805 HMOS/M146805 CMOS Family, the stack builds in the direction of decreasing address; therefore, the SP always points to the next empty location on the stack. The SP is decremented each time a data byte is pushed onto the stack and it is incremented each time a data type is pulled from the stack. The SP is only changed during certain operations and, except for the RSP instruction, it is not under direct software control. During external or power-on reset, and during a reset pointer (RSP) instruction, the SP is set to its upper limit (\$7F).

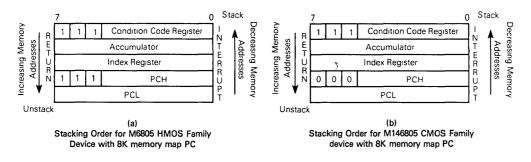

The order in which bytes are stored onto and retrieved from the stack is shown in Figure 2-2. Note that the PC has a number of fixed and variable bits. The number of variable bits depends upon the size of the memory available in a particular family member (see Figure 2-1 for this relationship).

#### NOTES.

- Since, in all family devices, the stack pointer decrements during pushes, the PCL is stacked first, followed by the PCH, etc. Pulling from the stack is in the reverse order.

- Fixed bits in the M6805 HMOS Family PC are always set, whereas, the M146805 CMOS Family PC fixed bits are always clear.

Figure 2-2. Stacking Order

#### 2.2.5 Condition Code Register (CC)

The M6805 HMOS/M146805 CMOS Family uses five condition code flag bits, labeled H, I, N, Z, and C, which reside in the CC register. The three MSBs of the CC register are all ones which fill the register to eight bits.

The function of the condition codes is to retain information concerning the results of the last executed data reference instruction. The effect of an instruction on each condition code is shown, together with the instruction, in Appendix D. Any bit or a combination of bits, except the I bit, are testable using the conditional branch instructions. See the Addressing Modes paragraph for more information.

2.2.5.1 CARRY (C). The C bit is set if a carry or borrow out of the 8-bit ALU occurred during the last arithmetic operation. It is also set during shift, rotate, and bit test instructions.

The C bit is mainly set in one of six ways.

- 1. It is set during an add instruction if the result of the additions produces a carry out of the 8-bit ALU (arithmetic logic unit).

- For subtraction and comparison instructions, it is set when the absolute value of the subtrahend is larger than the absolute value of the minuend. This generally implies a borrow.

- 3. It is changed during shift and rotate instructions. For these instructions the bit shifted out of the accumulator becomes the C bit.

- 4. It is set when an SEC instruction is executed.

- 5. It is set when a COM instruction is executed.

- 6. It is set if a bit test and branch bit is set.

Two instructions, add with carry (ADC) and subtract with carry (SBC), use the carry bit as part of the instruction. This simplifies the addition or subtraction of numbers that are longer than eight bits. The carry bit may be tested with various conditional branch instructions.

**2.2.5.2 ZERO (Z).** The Z bit is set if the result of the last data manipulation, arithmetic, or logical operation was zero. The Z bit is set only if all eight bits of the result are zero; otherwise, it is cleared.

The Z bit can be used to cause a branch with the BHI, BLS, BNE, or BEQ instructions. When the BHI instruction is used, both the C bit and Z bit are used for the branch.

The Z bit can be used to initiate a branch after the A or X contents equal the contents of a memory location. For example, the accumulator can be compared to the contents of a memory location and when the eight resultant bits are all zeros (Z bit set), a branch would result with the BEQ instruction. Conversely, if the same comparison were made and a BNE instruction were used, a branch would result after each compare until the eight resultant bits were all zeros (Z bit set).

**2.2.5.3 NEGATIVE (N).** The N bit is set when bit seven of the result of the last data manipulation, arithmetic, or logical operation is set. This indicates that the result of the operation was negative. The N bit is cleared by the CLR and LSR instructions. In all other instructions affecting the N bit, its condition is determined by bit 7 of the result.

The N bit can be used to cause a branch if it is set by using the BMI instruction. Likewise, the N bit can be used for a branch if it cleared by using the BPL instruction. In one case it is tested for a negative result and in the other it is tested for a positive result.

The N bit can be used to initiate a branch after a comparison of two numbers. For example, the contents of the X register could be compared to the contents of memory location M and a branch taken if N = 1. In using the CPX instruction, the N bit would remain clear and no branch is taken, as long as the X register contents were greater than or equal to the contents of M; however, if the X register contents become less than the contents of M, the N bit becomes 1 and a branch could be initiated (using BMI instruction).

2.2.5.4 HALF CARRY (H). The H bit is set when a carry occurs between bits 3 and 4 during an ADD or ADC instruction. The half-carry flag may be used in BCD addition subroutines since each binary-coded-decimal digit is contained either in the 0-3 (least significant) or 4-7 bits. Thus, when the sum of the two least significant BCDs results in a carry out of bit position 3 into bit position 4, the H bit is set. Chapter 3 describes a routine which uses the H bit to emulate the MC6800 DAA (decimal adjust) instruction.

2.2.5.5 INTERRUPT MASK (I). When the I bit is set, the external interrupt and timer interrupt are masked (disabled). Clearing the I bit allows interrupts to be enabled. If an interrupt occurs while the I bit is set, the interrupt is latched internally and held until the I bit is cleared. The interrupt vector is then serviced normally.

Except for when an external interrupt (INT or IRQ) is applied, the I bit is controlled by program instructions. Some program instructions change the I bit only as a result of the instruction, whereas, others cause it to change as a part of the instruction. For example, CLI clears the I bit and SEI sets the I bit; however, SWI automatically sets the I bit as part of the interrupt instruction. The STOP and WAIT instructions in M146805 CMOS Family parts also automatically set the I bit as part of instruction. See the Interrupts section of Chapter 4 for more information.

#### NOTE

The SWI instruction and RESET are the only non-maskable interrupts in the M6805 HMOS/M146805 CMOS Families.

#### 2.3 ADDRESSING MODES

The power of any computer lies in its ability to access memory. The addressing modes of the processor provide that capability. The M6805 HMOS/M146805 CMOS Family has a set of addressing modes that meets these criteria extremely well.

The addressing modes define the manner in which an instruction is to obtain the data required for its execution. An instruction, because of different addressing modes, may access its operand in one of up-to-five different addressing modes. In this manner, the

addressing modes expand the basic 59 M6805 HMOS Family instructions (61 for M146805 CMOS Family) into 207 separate operations (209 for M146805 CMOS Family). Some addressing modes require that the 8-bit opcode be accompanied by one or two additional bytes. These bytes either contain the data for the operations, the address for the data, or both.

In the addressing mode descriptions which follow, the term effective address (EA) is used. The EA is the address in memory from which the argument for an instruction is fetched or stored. In two-operand instructions, such as add to accumulator (ADD), one of the effective operands (the accumulator) is inherent and not considered an addressing mode per se.

Descriptions and examples of the various modes of addressing the M6805 HMOS/M146805 CMOS Family are provided in the paragraphs which follow. Several program assembly examples are shown for each mode, and one of the examples is described in detail (ORG, EQU, and FCB are assembler directives and not part of the instruction set). Parentheses are used in these descriptions/examples of the various addressing modes to indicate "the contents of" the location or register referred to; e.g., (PC) indicates the contents of the location pointed to by the PC. The colon symbol (:) indicates a concatenation of bytes. In the following examples, the program counter (PC) is initially assumed to be pointing to the location of the first opcode byte. The first PC + 1 is the first incremental result and shows that the PC is pointing to the location immediately following the first opcode byte.

The information provided in the program assembly examples uses several symbols to identify the various types of numbers that occur in a program. These symbols include:

- 1. A blank or no symbol indicates a decimal number.

- 2. A \$ immediately preceding a number indicates it is a hexadecimal number; e.g., \$24 is 24 in hexadecimal or the equivalent of 36 in decimal.

- 3. A # indicates immediate operand and the number is found in the location following the opcode.

There are seven different addressing modes used in the M6805 HMOS/M146805 CMOS Family, namely: inherent, immediate, direct, extended, indexed, relative, and bit manipulation. The indexed and bit manipulation addressing modes contain additional subdivisions to increase their flexibility; i.e., three additional for the indexed mode and two for bit manipulation. Each of these programming modes is discussed in the paragraphs which follow. The cycle-by-cycle description of each instruction in all possible addressing modes is included in Appendix G. This allows the processor bus activity and instruction operation relationship to be studied.

#### 2.3.1 Inherent Addressing Mode

In this addressing mode there is no EA (effective address). Inherent address instructions are used when all information required for the instruction is already within the CPU, and no external operands, from memory or the program, are needed. Since all the information necessary to carry out the instruction is contained in the opcode, and no external

operands are needed, inherent instructions only require one byte. These one-byte instructions are shown in Appendix E as part of control and read/modify/write instruction tables.

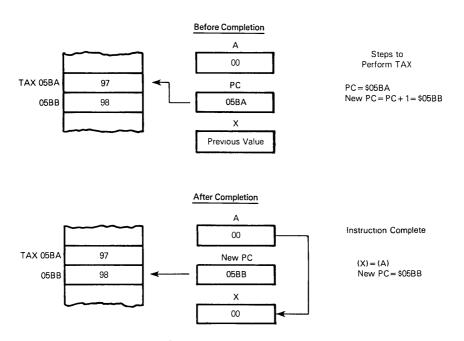

The following is an example of a subroutine that clears all registers (accumulator and index) plus the C bit and then returns. Figure 2-3 shows an example of the steps required to perform the TAX instruction in the subroutine.

| 05B9 4F | CLEAR | CLRA | Clear Accumulator          |

|---------|-------|------|----------------------------|

| 05BA 97 |       | TAX  | Transfer Accumulator       |

|         |       |      | Contents to Index Register |

| 05BB 98 |       | CLC  | Clear the Carry Bit        |

| 05BC 81 |       | RTS  | Return from Subroutine     |

Figure 2-3. Inherent Addressing Mode Example

#### 2.3.2 Immediate Addressing Mode

The EA of an immediate mode instruction is the location following the opcode. This mode is used to hold a value or constant which is known at the time the program is written, and which is not changed during program execution. These are two-byte instructions, one for the opcode and one for the immediate data byte. Immediate addressing may be used by any register/memory instructions as shown in Appendix E.

$$PC + 1 \rightarrow PC$$

$EA = PC$

$PC + 1 \rightarrow PC$

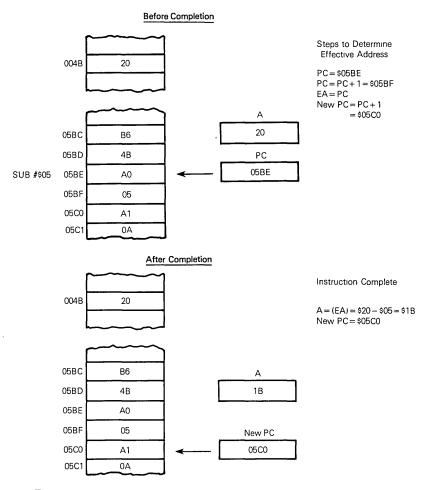

The following is an example which subtracts 5 from the contents of the accumulator and compares the results to 10. Figure 2-4 shows an example of the steps required to perform the SUB instruction.

| 05BC | B6 | 4B | LDA | \$4B | Load Accumulator from RAM   |

|------|----|----|-----|------|-----------------------------|

| 05BE | Α0 | 05 | SUB | #5   | Subtract 5 from Accumulator |

| 05C0 | A1 | 0A | CMP | #10  | Compare Accumulator to 10   |

Figure 2-4. Immediate Addressing Mode Example

#### 2.3.3 Extended Addressing Mode

The EA of an extended mode instruction is contained in the two bytes following the opcode. Extended addressing references any location in the M6805 HMOS/M146805 CMOS Family memory space, I/O, RAM, and ROM. The extended addressing mode allows an instruction to access all of memory. Also, since the two bytes following the opcode contain 16 bits, the addressing range of the M6805 HMOS/M146805 CMOS Family may be

extended in the future without affecting the instruction set or addressing modes. Extended addressing mode instructions are three bytes long, the one-byte opcode plus a two-byte address. All register/memory instructions, as shown in Appendix E, can use extended addressing.

$$PC + 1 \rightarrow PC$$

$EA = (PC)$ : (PC + 1)

$PC + 2 \rightarrow PC$

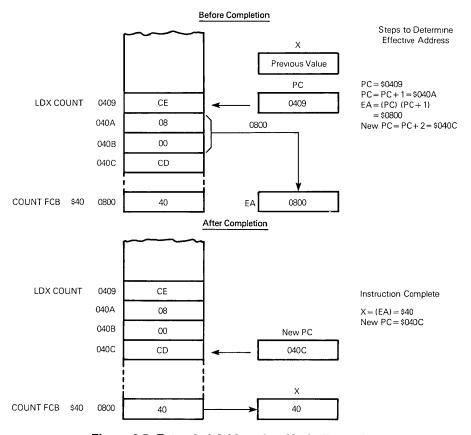

The following example loads the contents of a memory location (labeled COUNT) into the index register and then jumps to a subroutine to provide a delay. Figure 2-5 shows an example of the steps required to determine the EA from which to load the index register.

|      |    | 0800<br>1200 | COUNT<br>DELAY | EQU<br>EQU | \$800<br>\$1200 |                                                           |

|------|----|--------------|----------------|------------|-----------------|-----------------------------------------------------------|

| 0409 | CE | 0800         |                | LDX        | COUNT           | Load Index Register with<br>Contents of Location<br>\$800 |

| 040C | CD | 1200         |                | JSR        | DELAY           | Jump to Subroutine<br>Located at \$1200                   |

Figure 2-5. Extended Addressing Mode Example

#### 2.3.4 Direct Addressing Mode

The direct addressing mode is similar to the extended addressing mode except only one byte is used to form the EA. Direct addressing allows an instruction to only access any location in page 0 (locations \$00-\$FF) with a two-byte instruction; therefore, the upper address bits are set to \$00. Direct addressing may be used with any read-modify-write, or register/memory and bit manipulation instruction.

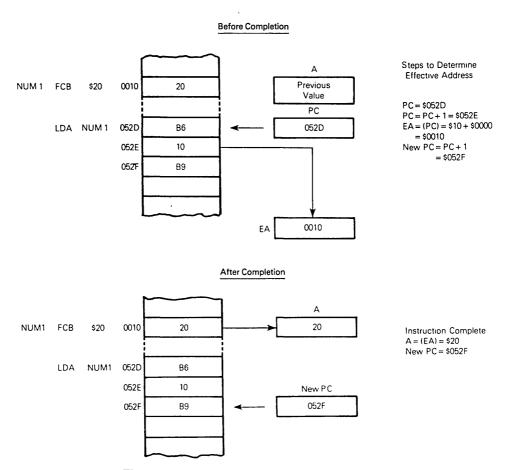

The following example adds two 16-bit numbers. The result is then placed in the location of the first number; however, if the result exceeds 16-bits the C bit will be set. Figure 2-6 illustrates the steps required to determine the EA from which to load the accumulator with the contents of NUM1 (first number).

Figure 2-6. Direct Addressing Mode Example

|      |    |    |      | ORG | \$10     |                                                   |

|------|----|----|------|-----|----------|---------------------------------------------------|

|      |    |    | NUM1 | RMB | 2        |                                                   |

|      |    |    | NUM2 | RMB | 2        |                                                   |

| 0527 | B6 | 11 |      | LDA | NUM1 + 1 | Load Accumulator with Contents of Location \$0011 |

| 0529 | ВВ | 13 |      | ADD | NUM2 + 1 | Add Contents of Location \$0013 to Accumulator    |

| 052B | B7 | 11 | •    | STA | NUM1 + 1 | Save Result in Location \$0011                    |

| 052D | B6 | 10 |      | LDA | NUM1     | Load Accumulator with Con-                        |

|      |    |    |      |     |          | tents of Location \$0010                          |

| 052F | B9 | 12 |      | ADC | NUM2     | Add Contents of Location                          |

|      |    |    |      |     |          | \$0012 and C Bit to<br>Accumulator                |

| 0531 | B7 | 10 |      | STA | NUM1     | Save Result in Location \$0010                    |

|      |    |    |      |     |          |                                                   |

#### 2.3.5 Indexed Addressing Mode

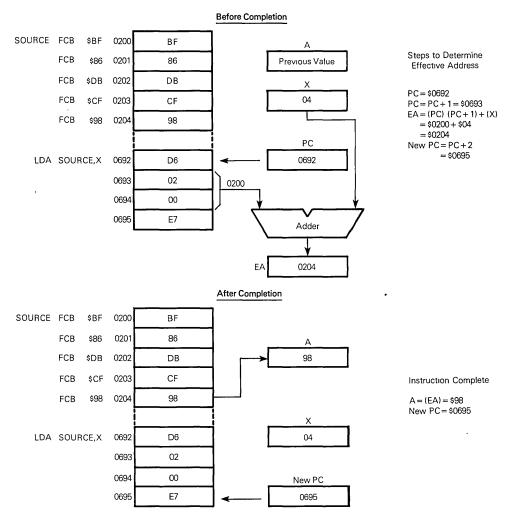

In the indexed addressing mode, the EA is variable and depends upon two factors: (1) the current contents of the index (X) register and (2) the offset contained in the byte(s) following the opcode. Three types of indexed addressing exist in the M6805 HMOS/M146805 CMOS Family: no offset, 8-bit offset, and 16-bit offset. A good assembler should use the indexed addressing mode which requires the least offset. Either the no-offset or 8-bit offset indexed addressing mode may be used with any read-modify-write or register/memory instruction. The 16-bit offset indexed addressing is used only with register/memory instructions.

2.3.5.1 INDEXED — NO OFFSET. In this mode the contents of the X register is the EA; therefore, it is a one-byte instruction. This mode is used to create an EA which is pointing to data in the lowest 256 bytes of the address space, including: I/O, RAM, and part of ROM. It may be used to move a pointer through a table, point to a frequently referenced location (e.g., an I/O location), or hold the address of a piece of data that is calculated by a program. Indexed, no-offset instructions use only one byte: the opcode.

$$EA = X + $0000$$

PC + 1 -> PC

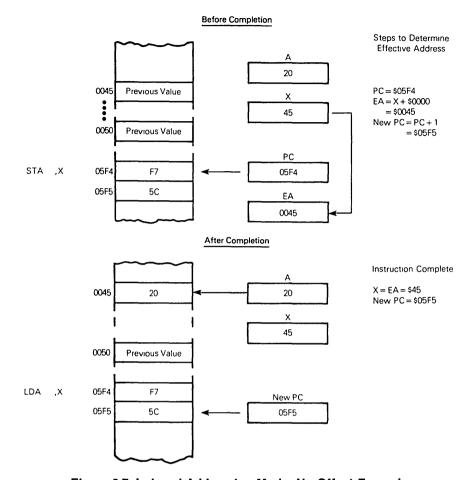

In the following example, locations \$45 to \$50 are to be initialized with blanks (ASCII \$20). Figure 2-7 illustrates the steps necessary to determine the EA from which to store the accumulator contents into a memory location pointed to by the index register.

| 05F0 | ΑE | 45         |        | LDX  | #\$45       | Initialize Index Register with \$45 |