File No. S360-01 Form A22-6908-0

# Systems Reference Library

## IBM System/360 Model 50

## **Operating Procedures**

This manual describes operator procedures for an IBM 2050 Processing Unit, operating with or without an associated IBM 1052 Printer-Keyboard. The manual describes machine functions, machine procedures, program-oriented procedures, and operator-intervention procedures. In addition, an appendix of reference material and an index are included.

The reader is assumed to have a knowledge of the following SRL publications:

IBM System/360 Principles of Operation, Form A22-6821 IBM System/360 Model 50 Functional Characteristics,

Form A22-6898

- IBM System/360 Basic Programming Support Operating Guide for Basic Assembler and Utilities, Form C28-6557

- IBM System/360 Basic Programming Support Operating Guide, Form C24-3391

- IBM System/360 Basic Operating System Operating Guide, Form C24-3450

IBM System/360 Operating System Operator's Guide, Form C28-6540 For information pertaining to the operation of units attachable to the System/360 Model 50, refer to the appropriate SRL publication. SRL publications that pertain to IBM System/360 and attachable units are abstracted and referenced by form number in IBM System/360 Bibliography, Form A22-6822.

#### FIRST EDITION

Significant changes or additions to the specifications contained in this publication will be reported in subsequent revisions or Technical Newsletters.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form is provided at the back of this publication for reader's comments. If the form has been removed, comments may be addressed to IBM Corporation, Customer Manuals, Dept. B98, PO Box 390, Poughkeepsie, N.Y. 12602.

<sup>©</sup> International Business Machines Corporation 1966

## Contents

| System Control Panel Machine Functions                | 5  |

|-------------------------------------------------------|----|

| Control Panel Functions                               | 5  |

| Operator Control                                      | 5  |

| Operator Intervention                                 | 6  |

| Master Check                                          | 10 |

| Customer Engineering (CE) Control                     | 10 |

| Status Indicators (Rollers)                           | 10 |

| 1052 Printer-Keyboard                                 | 10 |

| Peripheral Equipment                                  | 11 |

| Language Conventions Used in this Manual              | 11 |

| Machine Procedures                                    | 13 |

| Operator's Machine Responsibility                     | 13 |

| Emergency Pull Switch                                 | 13 |

| Turning On the System                                 |    |

| Turning Off the System                                | 13 |

| Program Loading                                       | 13 |

| Manual IPL                                            | 13 |

| Setting the Storage Protect Key                       | 14 |

| Clear Storage Procedure                               | 14 |

| Instruction Stepping                                  | 14 |

| PSW Procedures                                        | 14 |

| Display Current PSW (First Half)                      | 15 |

| Alter Current PSW (First Half)                        | 15 |

| Display First Byte of Second Word of Current PSW      | 15 |

| Display Remainder of Second Word of Current PSW       | 15 |

| Display the Instruction Address (Instruction Counter) | 15 |

| Alter the Instruction Counter in the Current PSW      | 15 |

| Storage Procedures                                    | 15 |

| Display Main Storage                                  | 15 |

| Store into Main Storage                               | 15 |

| CAW Display                                           | 15 |

| Local Storage Procedures                              | 15 |

| Display Local Storage or Registers                    | 15 |

| Store into Local Storage or Registers                 | 16 |

| Program-Oriented Procedures                           | 17 |

| I/O Unit Addressing                                   | 17 |

| SYSGEN Time                                           | 17 |

| System-Operator Communications                        |    |

| Making an Entry: Printer-Keyboard                     |    |

| Messages: System Operator (1052)<br>Making an Entry: Operator's Console<br>Messages: System Operator (System/360 BPS and BOS) | 18<br>18  |

|-------------------------------------------------------------------------------------------------------------------------------|-----------|

| Operator's Console                                                                                                            | 18        |

| Messages: System Operator (System/360 BAP)                                                                                    |           |

| Operator's Console                                                                                                            | 19        |

| Operator-Console Considerations (except under                                                                                 |           |

| System/360 OS)                                                                                                                | 19        |

| Using the 1410/7010 Emulator                                                                                                  | 19        |

| Using the 7070/7074 Emulator                                                                                                  | 21        |

| Operator Intervention Procedures                                                                                              | 23        |

| End of Job Procedure.                                                                                                         |           |

| Checkpoint/Restart Procedure                                                                                                  | 23<br>23  |

| Process a Section of a Program                                                                                                | 23        |

| Start at a Specific Instruction                                                                                               | 23        |

| Compare-Stop Procedures                                                                                                       | 24        |

| Stop on Address Compare (IAR)                                                                                                 | $24^{-1}$ |

| Stop on Address Compare (SAR)                                                                                                 |           |

| CPU Against Main Storage Location                                                                                             | 24        |

| Stop on Address Compare (SAR)                                                                                                 |           |

| I/O Against Main Storage Location                                                                                             | 24        |

| Storage Dump Procedure                                                                                                        | 24        |

| Error Log-out Procedures                                                                                                      | 24        |

| Continuous Loop During Assembly with 1052 (BPS Only)                                                                          | 25        |

| Continuous Loop During Assembly,                                                                                              |           |

| without a 1052 (BPS Only)                                                                                                     | 25        |

| Continuous Looping                                                                                                            | 25        |

| Analyzing an Unexpected Wait State Condition                                                                                  |           |

| (System/360 BAP)                                                                                                              | 25        |

| Analyzing Input/Output Commands                                                                                               | 26        |

| Appendix                                                                                                                      |           |

| A: Symbolic Addresses (System/360 BPS and BOS)                                                                                | 27        |

| B: Reference Tables For the System/360 Units                                                                                  |           |

| C: System/360 BAP System-Operator Codes                                                                                       |           |

| D: Job Control Cards (System/360 BPS)                                                                                         |           |

| E: Bit Meanings of Displays                                                                                                   |           |

| F: Input/Output Operation                                                                                                     |           |

| · · Input/ Sulput Operation.                                                                                                  | 74        |

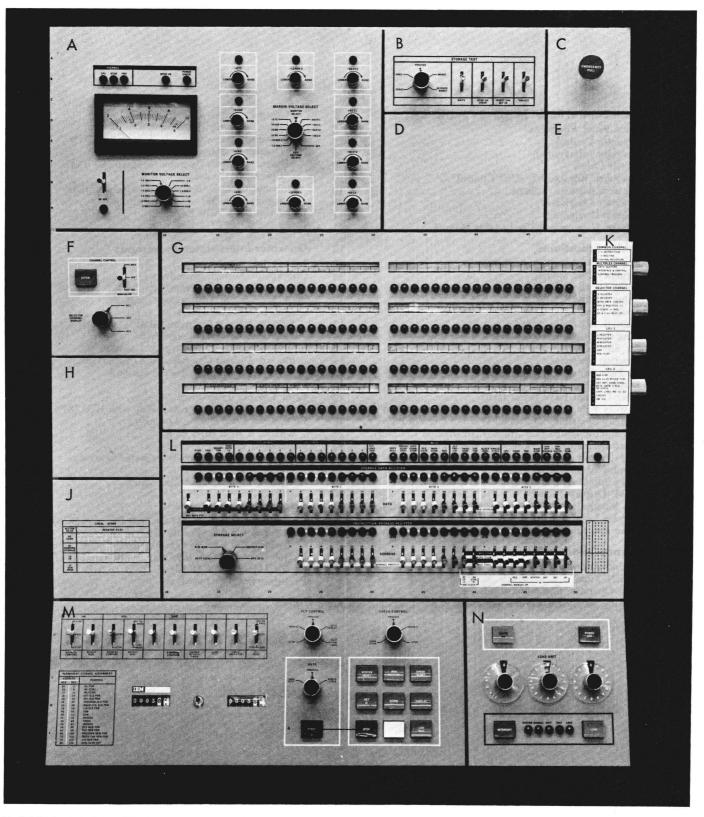

Model 50 System Control Panel

Operational control of IBM System/360 Model 50 is centralized in the system control panel (frontispiece). The control panel contains indicators, switches, keys, and register displays for the operator's use. Mounted on the 2050 Processing Unit, the system control panel, in conjunction with the reading board (also mounted on the 2050), comprises the operator's console. The operator may monitor system operation on both the control panel and with the associated printout on the optional 1052 Printer-Keyboard from the operator's console.

The control panel is used to:

- 1. Turn system control on and off.

- 2. Reset the system.

- 3. Load initial program information.

4. Store, display, and alter information in storage, registers, and program status word (Psw).

- 5. Provide operator-to-machine communication.

- 6. Permit operator intervention.

- 7. Perform customer engineering (CE) maintenance.

### **Control Panel Functions**

The control panel performs three general functions: operator control, operator intervention, and customer engineering control. The controls described in this section are additionally referenced in a later section, "Machine Procedures," and again, where applicable, in the section, "Program-Oriented Procedures."

#### **Operator Control**

The main functions provided by the operator controls are the control and indication of power, the indication of system status, operator-to-machine communication, and initial program loading.

Operator controls and indicators are:

| NAME           | PANEL | TYPE          |

|----------------|-------|---------------|

| Emergency Pull | С     | Pull switch   |

| Power On       | N     | Key           |

| Power Off      | Ν     | Key           |

| Prefix Select  | N     | Key switch    |

| Load Unit      | Ν     | Rotary switch |

| Load           | Ν     | Key           |

| Interrupt      | N     | Key           |

| System         | N     | Light         |

| Manual         | Ν     | Light         |

| Wait           | Ν     | Light         |

| Test           | N     | Light         |

| Load           | N     | Light         |

NOTE: Operator intervention controls are described later in this section.

#### **Keys and Switches**

*Emergency Pull:* Pulling this switch turns off all power beyond the power-entry terminal on every unit that is part of the system or that can be switched onto the system. The switch latches in the out position and can be restored to its normal position by maintenance personnel only. When the emergency pull switch is in the out position, the power-on key is ineffective.

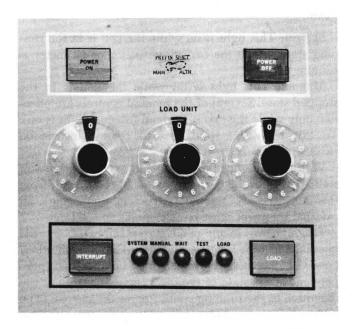

Power On: Pressing this key (Figure 1) initiates the power-on sequence of the system. As part of the power-on sequence, a system reset is performed in such a way that the system performs no instructions or 1/0 operations until explicitly directed. The contents of main storage are preserved.

The power-on key is backlighted to indicate when the power-on sequence is completed. The key is effective only when the emergency pull switch is in the normal in position.

*Power Off:* Pressing this key initiates the power-off sequence of the system. The contents of main storage (but not the keys in storage associated with the protection feature) are preserved, provided that the CPU is in the stopped state. The key is effective while power is on the system.

*Prefix Select:* This switch is used only when shared storage option is utilized (multisystem feature). The

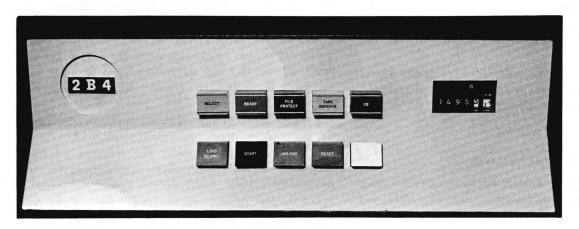

Figure 1. Section N Panel

System Control Panel Machine Functions 5

switch provides the choice between main and alternate prefix during manually initiated initial program load (IPL). The setting of the switch determines the state of the prefix circuit following the system reset after the load key is pressed. The alternate-prefix light (in top row of lights, Panel L) is on when the prefix select switch is in the ALTN position.

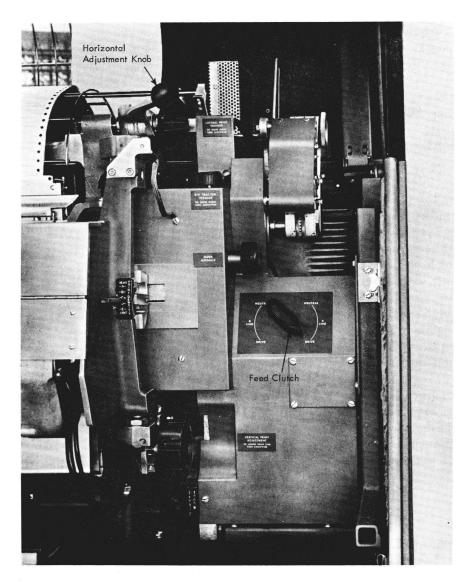

Load Unit: Three rotary switches provide the 11 rightmost 1/0 address bits used for IPL.

The leftmost rotary switch has eight positions labeled 0-7 that are used for the channel address. The middle 16-position rotary switch is labeled with the hexadecimal characters 0-9, A-F for the control unit address. The third switch has 16 positions, and is used for the unit address. (Actual IPL does not commence until the load key is pressed.) These switches may be set without disturbing CPU operation.

Load: Pressing this key starts IPL. The key is effective while power is on the system. The loading is from the I/o unit specified in the three load unit switches. Pressing the load key causes execution of the system reset internal diagnostic sequence, then loads the first 24 bytes of information from the load unit into the first 24 bytes of main storage. (This key is normally used while the CPU is in the stopped state.)

Interrupt: Pressing this key requests an external interruption. The interruption is taken when not masked, and when the CPU is not stopped. Otherwise, the interruption request remains pending. Bit 25 in the interruption-code portion of the current PSW is made 1 to indicate that the interrupt key is the source of the external interruption. The key is effective while power is on the system.

#### Lights

System: This light is on while the CPU is in the running state (while the CPU usage meter or CE meter is running).

Manual: This light is on while the CPU is in the stopped state. Several of the manual controls are effective only while the CPU is stopped (manual light is on). To exit from this state (i.e., to resume instruction processing), press the start key.

Wait: This light is on while the CPU is in the wait state. (Bit 14 of the current PSW equals 1.) To exit from this state (i.e., to resume instruction processing), an external interrupt must be provided.

*Programming Note:* The states indicated by the manual and wait lights are independent of each other; however, the state of the system light is not independent of the state of these two lights because of the definition of the running condition for the meters. (The system light is the meter light.) The possible conditions when power is on are:

| SYSTEM | MANUAL | WAIT  | CPU           | 1/0          |

|--------|--------|-------|---------------|--------------|

| LIGHT  | LIGHT  | LIGHT | STATE         | STATE        |

| off    | off    | off   | *             | *            |

| off    | off    | on    | Wait          | Not Working  |

| off    | on     | off   | Stopped       | Not Working  |

| off    | on     | on    | Stopped, wait | Not Working  |

| on     | off    | off   | Running       | Undetermined |

| on     | off    | on    | Wait          | Working      |

| on     | on     | off   | Stopped       | Working      |

| on     | on     | on    | Stopped, wait | Working      |

| * 41   | -<br>  |       |               |              |

\* Abnormal condition.

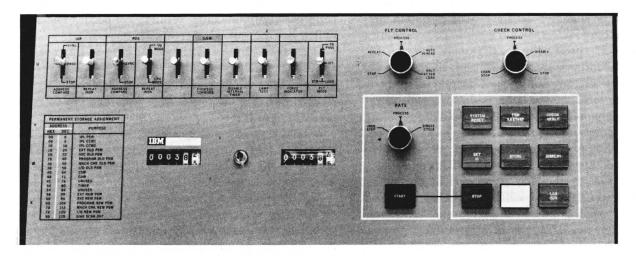

Test: This light is on when a manual control is not in its normal position or when a maintenance function is being performed for CPU, channels, or storage. The normal position for rotary switches is straight up, and for key switches is straight out.

The test switches described are shown in Figures 2, 3, and 4. These switches cause the test lights to be on if any are not in their normal position:

| SWITCHES                                             | PANEL        |

|------------------------------------------------------|--------------|

| Rate switch not to PROCESS                           | М            |

| Check Control switch not to PROCESS                  | М            |

| FLT CONTROL switch not to PROCESS                    | М            |

| FLT Mode key switch not to OFF                       | М            |

| Lamp Test switch not straight out                    | М            |

| Disable Interval Timer key switch not straight out   | М            |

| Address Compare (SAR) key switch to STOP             | Μ            |

| Repeat Insn (ÎAR or ROS) key switch not straight out | М            |

| Address Compare (IAR) key switch not to PROCESS      | М            |

| Address Compare (ROS) key switch not to SYNC         | Μ            |

| Rev Data Pty key switch not straight out             | L            |

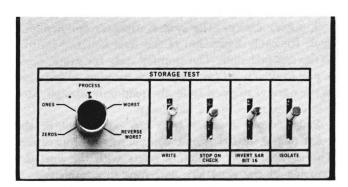

| Storage Test switch not to PROCESS                   | В            |

| Invert SAR Bit 16 key switch not straight out        | В            |

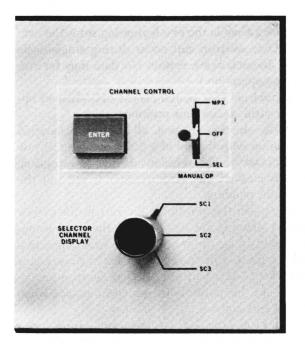

| Manual Op key switch not straight out                | $\mathbf{F}$ |

| Meter switch in CE position                          | М            |

Load: This light is on during IPL; it is turned on when the load key is pressed, and is turned off after the IPL operation and the loading of the new PSW are completed successfully.

#### **Operator Intervention**

Sections L and M of the system control panel contain the controls required for the operator to intervene in normal programmed operation. Operator intervention controls provide the system reset and the store and display functions.

Intervention controls and indicators are (keys have momentary pushbutton action):

| NAME                  | PANEL | TYPE          |

|-----------------------|-------|---------------|

| System Reset          | М     | Key           |

| PSW Restart           | М     | Key           |

| Check Reset           | М     | Key           |

| Set IC                | М     | Key           |

| Store                 | М     | Key           |

| Display               | М     | Key           |

| Stop                  | М     | Key           |

| Start                 | М     | Key           |

| Log-Out               | М     | Key           |

| Rate                  | М     | Rotary switch |

| Check Control         | М     | Rotary switch |

| Address Compare (IAR) | М     | Key switch    |

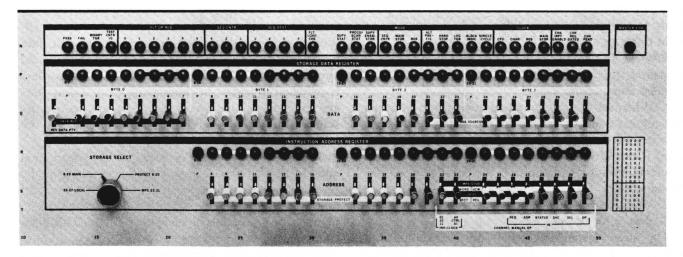

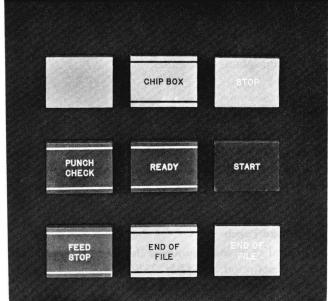

Figure 2. Section M Panel

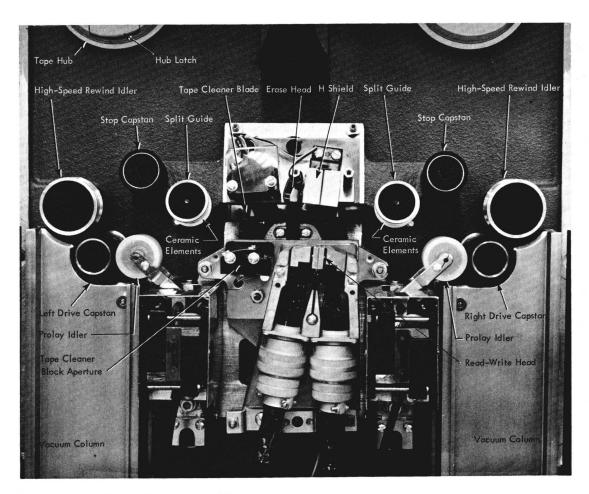

Figure 3. Section B Panel

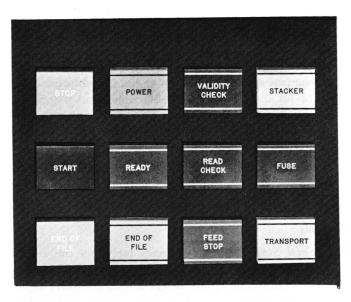

Figure 4. Section F Panel

| NAME                  | PANEL        | TYPE          |

|-----------------------|--------------|---------------|

| Address Compare (SAR) | М            | Key switch    |

| Storage Select        | L            | Rotary switch |

| Address               | $\mathbf{L}$ | Key switches  |

| Data                  | L            | Key switches  |

NOTE: Operator controls are listed in a previous table.

System Reset: This key resets the channels and control units, and places the CPU in the stopped state; all pending interruptions are eliminated, and all error indicators are reset. The instruction address register is set to zero. The key is effective while power is on the system. (The reset function does not affect any off-line or shared device.) It is recommended to press the stop key before pressing system reset key.

*PSW Restart:* This key causes a system reset, after which a PSW is loaded from the double word starting at storage location 0 and the CPU is changed from stopped to operating state.

*Check Reset:* This key resets all CPU and channel check indicators (including some master checks) to the no-error state. Check reset is forced by CPU reset or system reset. It is active in all modes. Check lights remaining on after check reset must be cleared at the check source by use of appropriate manual controls.

Set IC: This key takes the address set in the address switches and enters it into the instruction counter portion of the active PSW. The key is effective only while the CPU is in the stopped state.

Store: This key is pressed to store information in the location specified by the storage select and address switches. Correct parity is automatically generated. Storage protection is ignored. The key is effective only while the CPU is in the stopped state. The contents of the data key switches are placed in specified locations in main storage, general registers, or floating-point registers. If the storage select switch is set to MAIN, the entire contents of the data switches are stored in main storage. If the storage select switch is set to LOGAL, address switches 24-27 specify the local storage location address, while address switches 22 and 23 specify the local storage sector. Sector specification determines whether the local storage area addressed will be the multiplexor channel, working storage, general registers, or floating-point registers. When the location designated by the address switches and storage select switch is not available, data are not stored.

Display: The display key is pressed to display information in the location specified by the storage select switch and address switches. When the designated location is not available, the displayed information is unpredictable. The key is effective only while the CPU is in the stopped state, and while power is on the system.

If the storage select switch is set to MAIN, the data in main storage at the location specified are displayed in the storage data register. If set to LOCAL, the data in the local storage are displayed in the L register. If the storage select switch is set to MPX, the data specified are displayed in the SDR. If set to PROTECT, the data specified are displayed in the F register.

Stop: The stop key causes the CPU to enter the stopped state and turns on the manual light. The CPU completes the instruction being executed at the time the stop signal is recognized. All pending interruptions that are not masked are taken and any 1/0 operation in progress is completed.

Pressing the stop key has no effect when a continuous string of interruptions is performed or when the CPU is unable to complete an instruction because of machine malfunction.

Start: The start key is pressed to start instruction execution as specified by the rate switch. The key is effective only while the CPU is in the stopped state.

Pressing the start key after a normal stop causes instruction processing to continue as if no stop had occurred, provided that the rate switch is set to PROC-ESS OF INSN STEP. If the start key is pressed after the system reset without first introducing a new instruction address, the results are unpredictable.

Log-Out: This key provides a means of logging the machine status into storage. Pressing the key causes the CPU and channel status to be stored in fixed locations in main storage. The log-out area occupies 44 words (176 bytes) of main storage, starting at byte 128. The log-out action is the same as that performed by programming when an error is detected. This key is operative only while the CPU is in the stopped state.

Rate: This three-position rotary switch is used to indicate the manner in which instructions are to be performed. The position of the switch should be

changed only while the CPU is in the stopped state. Otherwise, unpredictable results may occur. The rate switch has the following settings:

1. PROCESS—In this position, the system starts operating at normal speed when the start key is pressed. The test light is on when the rate switch is not set to PROCESS. Moving the rate switch from PROCESS to INSN STEP stops the CPU.

2. INSN STEP—In this position, the system executes one instruction for each depression of the start key and returns to the stopped state. The timer is not updated when the switch is in this position.

Any instruction can be executed with the rate switch set to INSN STEP. Input/output operations are completed to the interruption point. While the CPU is in the wait state, no instruction is performed, but pending interruptions, not masked, are taken before the CPU returns to the stopped state. Initial program loading is completed with the loading of the new PSW before any instruction is performed.

3. SINCLE CYCLE—The system executes one machine cycle for each depression of the start key and returns to the stopped state. The stopped state for single cycle is one in which no CPU clocks are running. Otherwise, in the normal stopped state, the read only storage (ROS) is running, executing a halt loop.

Single cycle operates with I/O equipment to the point of the initiation of the asynchronous operation. The asynchronous operation starts with the next depression of the start key and runs to completion. If start is pressed during this time, the next cycle is taken. If an interruption results, the interruption sequence is not automatically executed but must be single cycled. Moving the rate switch from PROCESS to SINGLE CYCLE while the CPU is running stops the CPU.

NOTE: Data overrun can occur during single-cycle operation. In such cases, certain 1/0 data may be lost. (This is a ce operation.)

*Check Control:* This switch checks cru/channel operation for error. It has four positions:

1. PROCESS—In this position, all errors are handled by the monitor with the aid of a general log-out, if PSW bit 13 is unmasked. This is followed by an interruption. If bit 13 is masked, the error register is set, but the error remains pending.

2. DISABLE—In this position, all errors in the CPU or multiplexor channel are ignored and the system continues, disregarding the error. The program operation can still be affected by the error. Errors in the selector channel (except data parity) cause 1/0 interruption.

3. stop—In this position, the processing stops when an error is encountered.

4. CHAN STOP—In this position, processing stops when an error other than incorrect length indication (ILI) is encountered. NOTE: Under normal circumstances, the system is run with the check control switch in the process position. At any other setting, this switch causes the test light to go on.

Address Compare (IAR): This switch provides a means of stopping the CPU on a successful instruction address comparison.

1. When set to STOP, an equal comparison between the address switches and the TAR causes the CPU to stop. The stop occurs at completion of the addressed instruction. (Comparison includes only the part of the instruction address that addresses the physical word size of storage.)

2. When set to process, no comparison occurs.

3. SYNC is for CE use.

The address compare switch can be manipulated without disrupting CPU operation other than causing the address-comparison stop. When this switch is set to any position except normal (straight out) the test light is on.

Address Compare (SAR): The storage address register compare switch provides a means of stopping the CPU on a successful data (not IAR) address comparison.

1. When set to stop, an equal comparison between data switches 8-31 (low-order 24 positions) and a storage address may be used either to locate data or as a successful status-switching address. Either comparison causes the CPU to stop at the completion of the instruction containing the address. Data switches 0 and 1 (byte 0) may be set to effect the stop when the storage reference is made by either the CPU, the channels, or by both.

2. When set to SYNC, no stop occurs.

3. The address compare (SAR) switch can be manipulated without disrupting CPU operation other than causing the address-comparison stop. When this switch is set to STOP, the test light goes on.

The address compare (SAR) switch is normally left set to SYNC.

The following operator intervention controls are located on Panel L in Figure 5.

Storage Select: This four-position rotary switch is used to select the main storage area addressed by the address switches. The storage select switch is active only in the stopped state. The switch can be changed without disrupting CPU operations. The storage select switch has the following settings:

1. MAIN—Selects a main storage location specified by the address switches. The data are then displayed in the storage address register.

2. LOCAL—Selects a local storage location specified by the address switches. The data are then displayed in the L register.

3. PROTECT—Unconditionally selects the storage protect key register (used by the CE).

4. MPX—To select multiplexor (used by the CE).

When addressing general or floating-point registers, working storage, and the multiplexor, the sector addresses must be computed in conjunction with data posted on Panel J. (Addresses given in this manual already include this computation.) When storage select is switched to LOCAL, in conjunction with "Local Storage Procedures," the sector addresses are specifically stated. The storage select switch may be left on at any setting.

Address: The address switches on the instruction address register panel provide a means of manually selecting an addressable location in storage when used in conjunction with the storage select switch, or to identify the address to be compared when an addresscomparison stop is desired. Correct parity is automatically generated. The switches can be manipulated without disrupting CPU operation. The 24 switches are arranged in hexadecimal groups, numbered like the data switches above them.

For main storage select, the address switches are used to manually address a main storage location when the storage select switch is set to MAIN. For an addresscomparison stop, the address switches provide the stop address. When addressing main storage, the 24 switches represent a 24-bit binary address. The rightmost switch is the units position or low-order position. Because data in main storage is stored or displayed a word at a time, the two low-order position address switches (switch positions 30 and 31) are not involved in determining the address.

When an address switch is in the down position, it represents a 1 bit. Color coding is provided to identify the hexadecimal digit groupings. If the address switches are manipulated while address compare (IAR) is set to STOP, a machine check can occur.

The lights directly above the switches indicate the address selected. Three lights have a P below, indicating parity of the associated byte. Bytes identified are bits 8-15, 16-23, and 24-31.

Data: The 32 data switches on the storage data register panel are arranged in hexadecimal groups. The switches specify the data to be stored in the location indicated by the storage select switch and address switches. Correct data parity is automatically generated. Changing the switches does not affect CPU operation.

The data switches can be used to represent a full physical storage word of information. A data switch in the down position represents a 1 bit and in the center (restored) position, a 0 bit. The lights directly above the switches indicate the information being displayed or stored. Certain lights have a P below, indicating parity of the associated byte. Bytes identified are bits 0-7, 8-15, 16-23, and 24-31.

Figure 5. Section L Panel

#### **Master Check**

This indicator light turns on to indicate that a machine error has been detected. Press the check reset key to turn the indicator light off. (The error is not corrected by the check reset key.)

#### **Customer Engineering (CE) Control**

All other keys, switches, and controls not described in this manual are principally for customer engineering use. The usage meter and CE meter are on Panel M. A key switch controls the meter to be run when the machine is in process. When power is on and the key switch is in the customer operation position, the usage meter accumulates time (while the system light is on). If the key switch is in the customer engineer position, the test light is on, and the CE meter accumulates time while the system light is on.

#### **Status Indicators (Rollers)**

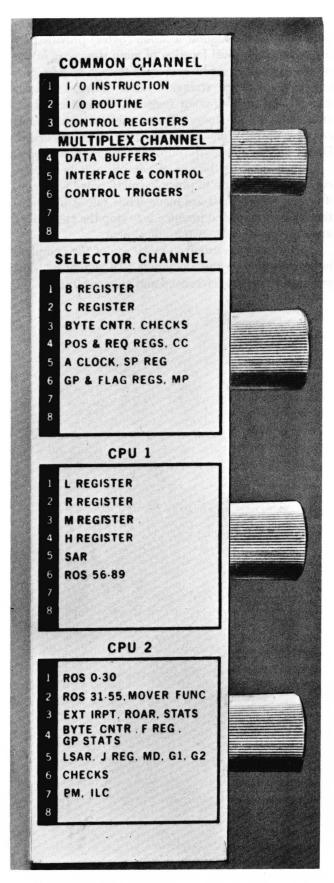

The status indicators on Panel G (Frontispiece) provide a display of CPU and channel status. The 144 indicators are arranged in four rows, 36 to a row. Each row is separated in the center, with 18 lights in the left half and 18 in the right half.

Eight different status words can be displayed in each row of indicators. The desired word is selected with an eight-position roller select switch (Panel K). The switch also positions a roller format to identify the information displayed. The significance of each switch position is identified by the label on the face of the panel by the related roller positioning switch (Figure 6).

Roller select switches display (detailed description of bit meanings in these displays is given in Appendix E):

#### ROLLER SWITCH POSITION

| IIC.             | II FOSTION |                                                                                         |

|------------------|------------|-----------------------------------------------------------------------------------------|

| 1                | 1          | Common channel: I/O instruction                                                         |

| 1                | 2          | Common channel: I/O routine                                                             |

| 1                | 3          | Common channel: control registers, buffers                                              |

| 1                | 4          | Multiplexor channel: data buffers                                                       |

| 1                | 5          | Multiplexor channel: interface and control                                              |

| 1                | 6          | Multiplexor channel: control triggers                                                   |

| 2<br>2           | 1          | Selector channel: B register                                                            |

| 2                | 2<br>3     | Selector channel: C register                                                            |

| 2                | 3          | Selector channel: byte counter, miscellaneous registers, and channel checks             |

| 2                | 4          | Selector channel: position, control, and request registers                              |

| 2                | 5          | Selector channel: A clock and control registers                                         |

| 2                | 6          | Selector channel: general purpose and flag<br>registers, and MP latches                 |

| 3                | 1          | CPU: L register (local storage, first half of current PSW)                              |

| 3                | 2          | CPU: R register                                                                         |

| 3                | 3          | CPU: M register                                                                         |

| 3<br>3<br>3<br>3 | 4          | CPU: H register                                                                         |

| 3                | 5          | CPU: SAR, byte stats, and byte store stats                                              |

| 3                | 6          | CPU: ROS (group #3, 56-89)                                                              |

| 4                | 1          | CPU: ROS (group #1, 0-30)                                                               |

| 4                | 2<br>3     | CPU: ROS (group #2, 31-55)                                                              |

| 4                | 3          | CPU: ROAR, external interrupt register, and stats (first byte of second word in current |

|                  |            | PSW)                                                                                    |

| 4                | 4          | CPU: byte counters, F register, edit and GP stats, and storage ring (storage protection |

|                  |            | key)                                                                                    |

| 4                | 5          | CPU: LSAR, J register, MD, G1, and G2                                                   |

| 4                | 6          | CPU: error register                                                                     |

| 4                | 7          | CPU: current ROS address                                                                |

8 CPU: previous ROS address

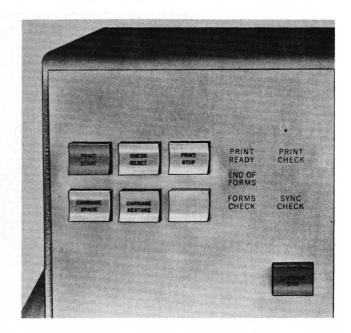

## 1052 Printer-Keyboard

4

In conjunction with the operator's console, the operator exercises control of the 1052 Printer-Keyboard. For detailed description of the 1052, see *IBM 1052 Printer-Keyboard Model 7*, Form A22-6877. The 1052

Figure 6. Section K Panel

is powered by the operator's console. Operation of the 1052 involves:

*Ready:* Pressing this key causes the 1052 to become ready. If the 1052 is in the not ready condition, this key overrides the condition and makes the 1052 ready if these conditions allow: not out of forms, not busy, and not in initial select sequence (from channel). The 1052 must be in the ready condition to perform read and write operations.

*Request:* This key is pressed (after the ready key) to initiate operator communication via the 1052. This key prohibits read/write operations until the system accepts the request.

Attn: This light, when on, indicates that the request is pending (the system hasn't accepted it yet).

*Procd:* The system has accepted the operator's request and the keyboard is unlocked.

Intvin Reqd: The 1052 is not ready; operator intervention is required. (Example: lack of sufficient paper causes this light to go on when the keyboard is addressed by the system.)

## **Peripheral Equipment**

The Model 50 has peripheral equipment (at least I/o devices) that may be under the operator's control. A customer's manual that describes the operation of each unit of peripheral equipment used in the system is available. Execution of the operator-information discussed in the pertinent manual is the operator's responsibility. Titles of the manuals and their form numbers may be found in *IBM System/360 Bibliography*, Form A22-6822. A partial list of peripheral I/o devices, with brief descriptions, is given in Appendix F.

## Language Conventions Used in this Manual

1. When a letter or digit is used in the text, without modifier, conventional (plain English) alphameric value is implied; for example, addresses must end in 0, 4, or 8 for proper boundary byte locations. Up to this point in the manual this has been the only meaning for any letter or number in the text. (Exception: When 0 or 1 is used, it is the same in all number systems.)

2. When a digital value is followed by "hex" in parentheses, the decimal number has been converted to its hexadecimal equivalent, and is presented in the text, requiring only coding into bits for use by the machine; for example, caw location is 48 (hex). In this example, decimal location 72 has already been translated to 48 (hex) for use in the text. To enter location 48 (hex) into the address switches, the last (low-order) switches will code: 0100 1000. (See hexadecimal to decimal conversion table in "Appendix B.")

3. Low-order refers to "right-hand" end of the word, or byte.

4. To read hexadecimal (language used by the operator's console) picture the 8-bit byte

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | <br> | <u> </u> |     | ~    |  |

|-----------------------------------------|------|----------|-----|------|--|

| Zone                                    |      |          | Num | eric |  |

divided into first half (zone portion) and second half (numeric portion). In all practical operator applications the zone portion will be all l's (F, in hex), representing the sign "positive," because the numerical values in operator communication are all positive. The numeric portion can be pictured in two parts, each part comprising a hex digit. Thus: 1111 0001 = (effective decimal) 1. Similarly, 1111 0011 = (effective decimal) 3.

5. Main storage refers to contiguous storage locations 0000 to the highest location (bytes) provided by the system. (Physical location of main storage is in the processor cabinet; additional main storage may be provided by auxiliary storage.) Local storage includes general and floating-point registers, channel registers, and "scratch pad" storage. Terms such as *memory* and *core* are obsolete insofar as this manual is concerned. Direct access replaces the obsolete term random access.

6. In describing the use of console switches, reference has been made to possible interference with CPU, if switch adjustments are made while CPU is in operation. A recommended practice is to stop the CPU before making any console switch adjustment.

7. The reader is urged to make use of the complete index provided in this document. All significant subjects and terms are referenced and cross-referenced. This section describes specific machine procedures performed by the operator. (Operator procedures involving programs or the operating system are described in the next section.)

## **Operator's Machine Responsibility**

The operator is responsible for turning on the system (if the power has been off), initializing the system (manual IPL procedures in conjunction with the appropriate operating system), entering into the system programs prepared by programmers, maintaining a running log of jobs, communicating with the system (through console indicators and printer-keyboard), making operator adjustments as required (to console and peripheral equipment), certain operator troublecorrection procedures, and turning off the system, as required. The operator notifies the CE when equipment trouble occurs in the system. See Appendix F for I/o operation, where typical I/o devices are briefly described.

## **Emergency Pull Switch**

This switch (described previously under "Keys and Switches") is to be pulled out by the operator in *true emergency* only. For this purpose, a true emergency is defined as a system fire, or in any extreme case where real danger threatens personnel. Once pulled out, the switch locks, and can be reset only by the CE; therefore, notify him immediately. (Thermal overloads may also drop system power. If system power cannot be maintained, notify the CE.)

## **Turning On the System**

1. Before turning on the system, check all peripheral units externally. Check that doors are properly closed, feeds not impeded, paper/card supply is sufficient. If any I/O units have been removed from powering sequence, it may be necessary to jumper their plugs. CAUTION:

Do not operate any switches unless necessary.

2. Press power on key. This initiates a power-on sequence automatically. At the completion of the sequence, the backlighted power on key lights up. (Should this fail to occur, check emergency pull switch to make certain it is all the way in.) Check sequence power plugs for 1/0 units. If these checks and operator check of the primary power source fail to disclose difficulty, call the CE. (The system light and other state lights may go on, depending on the state of the system at previous power turn off.) If the test light is on, check the position of the test switches as described under "Test." Restore the switches as required to turn the test light off. If the master check light is on, press the check reset key. The master check light should go off.

3. Turn on the power for shared/peripheral equipment not directly connected in the power-on sequence.

## **Turning Off the System**

If manual light is not on, press the stop key. Manual light goes on.

1. Check all tape drives. Put them in an unload state; press reset, load rewind, and then the unload keys on each tape drive.

2. Check all disk drives. Put them in unload state by pressing start/stop key if they are running.

3. Press power off key. Power is removed automatically in an ordered sequence. The power on light goes out.

4. Continue power-off procedures for shared/peripheral equipment not connected to the powering sequence.

## **Program Loading**

Programs can be initially loaded into the system by the manual IPL procedure or by loader programs. Manual IPL is an automatic technique of loading, performed by the operator and the system microprogram; it can load any program into main storage. Because manual IPL is a prime prerequisite for loading any program (loader, control, or problem) into storage, it is described in detail.

## Manual IPL

The procedure to be followed after a power-on sequence following a shutoff of electrical power, after malfunctions that necessitate reloading the resident portion of the operating system into main storage, or for initial loading of any program is: 1. Place the appropriate program on the desired 1/0 device.

2. Make the 1/0 device ready.

3. Select the desired 1/0 device with the three load unit switches.

4. Press load key. The manual/wait light goes off, the load light turns on and system reset occurs. The first 24 bytes of information are loaded from the selected device into locations 0-23 of main storage. Depending on data content the exact procedure from this point varies. A typical illustration follows:

The IPL PSW is in locations 0-7, with two ccw's following in locations 8-23. Control of the system is passed to the channel, which obtains the first ccw (location 8) and uses it to continue reading from the input unit, placing the data in storage. When the input operation is completed, the IPL PSW is loaded into the CPU registers. When this PSW is successfully loaded, the load light turns off. If either the reading operation or the PSW loading is unsuccessful, the CPU idles, and the load light remains on. Under certain conditions, the IPL PSW may specify a wait state, in which case the load light turns off and the wait light goes on. (In this case, the operator provides the setup change required, and returns the system to running state by pressing the interrupt key.) When the current PSW specifies a running state, the loaded program is executed, beginning at the location specified at the current PSW (which may be the IPL PSW if it originally specified running state).

Note: If, at the beginning of a job, any individual device cannot be readied, press the system reset key. This resets all unusual conditions; however, if a job is already being run, information already on the channels or interface units will be lost. (Because this manual IPL procedure executes the same internal diagnostic sequence and reset functions that the system reset key performs, that key need not be pressed before manual IPL.)

## Setting the Storage Protect Key

To change the protection information associated with a given block of storage (in blocks of 2,048 bytes):

- 1. Press stop key. Manual light goes on.

- 2. Set storage select switch to PROTECT.

- 3. Press display key.

4. Rotate roller 4 to position 4. The F register displays the old storage protect key.

5. Set address switches 12-19 for change of key.

6. Set new storage protect key data in data switches 24-27.

7. Press store key. The storage protect key has now been reset. The F register now displays the new storage protect key. 8. To resume processing, press start key. Manual light goes off.

## **Clear Storage Procedure**

Under normal operating-system type operation, it is unnecessary to clear storage, because the operating system provides the function as required. For certain testing operations, however, it may be desirable to clear storage. The following procedure clears all main storage, but does not alter the contents of general purpose or floating-point registers:

1. Press system reset key. Manual light goes on.

2. Set rate switch to SINGLE CYCLE. Test light goes on.

3. Set IC to zero (by setting address switches to zero, then pressing set IC key).

4. Set data switches to 0200. (Data switch 22 down, all others remain straight out.)

5. Set repeat insn (Ros) switch in down position.

6. Press start key.

7. Restore repeat insn (Ros) switch to straight out position.

8. Restore data switches straight out.

9. Set rate switch to PROCESS. Test light goes out.

10. Press start key. All main storage (except registers) is now cleared.

11. Press system reset key. Manual light goes on.

12. Press store key.

## **Instruction Stepping**

One method that is used to debug a program is to process one instruction at a time, service all interrupts, and stop:

1. Press stop key. Manual light goes on.

2. Set rate switch to INSN STEP. Test light goes on.

3. Press start key. The next instruction is processed; I/o operations are completed, and all pending interruptions are serviced. The program is run basically in the same way as during normal processing, except that the system returns to the stopped state at the completion of execution of that instruction. The address of the next instruction to be processed is displayed in the IAR.

4. Repeat Step 3 for each instruction step.

When the instruction-step processing is completed, reset the rate switch to PROCESS.

## **PSW Procedures**

The current PSW governs control of the system. Because the PSW is a double word, it is necessary to display it in parts. All the parts are accessible, as described. (See PSW format in Appendix B.)

#### Display Current PSW (First Half)

- 1. Press stop key. Manual light goes on.

- 2. Set address switches to 170.

- 3. Set storage select switch to LOCAL.

- 4. Press display key.

5. Rotate roller 3 (CPU 1) to position 1, revealing the L register.

The first half of the current PSW is now displayed in the L register.

#### Alter Current PSW (First Half)

1. Perform the five steps to display PSW (shown above).

2. Set new information desired in the data switches.

3. Press store key. The PSW is now altered.

4. Press display key to display new PSW data in the L register.

#### **Display First Byte of Second Word of Current PSW**

1. Rotate roller 4 to position 3.

2. The first byte of second word of current PSW is now displayed in PSW portion of roller display labeled PSW (last 8 bits).

#### **Display Remainder of Second Word of Current PSW**

This is the three-byte instruction address. See the following procedure.

#### **Display the Instruction Address (Instruction Counter)**

The instruction counter is always on display in the instruction address register. To read the lights in that register, press stop key. Manual light goes on. To resume processing, press start key. Manual light goes off.

#### Alter the Instruction Counter in the Current PSW

- 1. Press stop key. Manual light goes on.

- 2. Set address switches to desired instruction address.

3. Press set IC key. The desired IC address is now in the current psw. When the program resumes, the instruction at the desired 1C address is executed, and the next IC address is displayed in the instruction address register. (If the instruction executed was a branch, and the branch was taken, the new address displayed in the IAR is the address of the branch instruction.)

4. To resume processing, press start key. Manual light goes off.

## Storage Procedures

Data can be stored in main storage, general and floating-point registers, and in special local storage. Certain channel registers are also addressable.

#### **Display Main Storage**

- 1. Press stop key. Manual light goes on.

- 2. Set address switches to the desired storage address.

- 3. Set storage select switch to MAIN.

4. Press display key. The contents of main storage addressed is now displayed in the storage data register.

#### Store into Main Storage

- 1. Perform Steps 1-3 under "Display Main Storage."

- 2. Set data switches to data desired.

3. Press store key. Desired data are now stored at desired address. (Check for accuracy by displaying contents of stored location.) Note that main storage addresses must end in 0, 4, 8, or C for proper boundary byte locations.

## **CAW** Display

1. This is a special case of display main storage. Follow that procedure.

2. The location (address switches setting) is 48 (hex).

3. When display key is pressed, the CAW is displayed in the storage data register. (See CAW format in Appendix B.)

## Local Storage Procedures

Separate from main storage, the local storage contains 16 full word general registers (CR0-CR15), four double word floating-point registers (FP0, FP2, FP4, FP6), multiplexor channel registers, and working storage for scratch pad use. Each of these functions are specified as sectors. The four sectors are addressed by address switches 22 and 23. These switches address the local storage sectors as follows:

00 Multiplexor Channel

- 01 Working Storage

- 10 Floating-Point Registers 11 General Purpose Registers

The data in these registers are displayed one full word at a time. Generally this is all that is required. Floatingpoint registers, however, display only the single word of the double word capability. To display the second word, increment the address by 4 (bytes). When the display key is again pressed, the second word is displayed.

## **Display Local Storage or Registers**

1. Press stop key. Manual light goes on.

2. Set sector to be displayed in address switches 22 and 23. Set location to be displayed in address switches 24-27.

3. Set storage select switch to LOCAL.

- 4. Press display key.

- 5. Rotate roller 3 (CPU 1) to position 1 (L register).

The contents of the specified location in local storage is now displayed in the L register.

6. To resume processing, press start key. Manual light goes off.

#### Store into Local Storage or Registers

- 1. Press stop key. Manual light goes on.

- 2. Set sector to be displayed in address switches 22

and 23. Set location of local storage or registers desired in address switches 24-27.

- 3. Set storage select switch to LOCAL.

- 4. Set data switches to data desired.

5. Press store key. Desired data is now stored in local storage or registers.

6. To resume processing, press start key. Manual light goes off.

The System/360 Model 50 may use any of four IBMsupplied operating systems, listed in order of increasing complexity:

- 1. Basic Assembly Program (System/360 BAP)

- 2. Basic Programming System (System/360 BPS)

- 3. Basic Operating System (System/360 BOS)

- 4. Operating System (System/360 os)

Where no distinction is made for any operating procedure, it is understood that the procedure is common to all. Differences, even in single steps of a detailed procedure, are distinguished and noted in every case. For more detailed information on each of these operating systems, the operator is referred (in order) to: *IBM System/360 Basic Programming Support, Operating Guide for Basic Assembler and Utilities,* Form C28-6557; *IBM System/360 Basic Programming Support, Operating Guide,* Form C24-3391; *IBM System/360 Basic Operating System, Operating Guide,* Form C24-3450; and *IBM System/360 Operating System, Operator's Guide,* Form C28-6540.

## **/O Unit Addressing**

Implicit in any information processing system are the various 1/0 units, identified in this system by a unique three-digit address for each device. (This 1/0 device address is not to be confused with a storage location address.) In practical usage, the three-digit address is described: first digit for channel, and next two digits for subchannel (or device, with control unit implicitly contained). Example: 1/0 address 00A may be interpreted as being on multiplexor channel (0), with control-unit device 0A (i.e., Card Read Punch). Similarly, address 187 may be on selector channel 1, controlunit drive 87 (i.e., tape unit).

A typical 1/0 unit address table example is:

| DEVICE                     | ADDRESS                   |

|----------------------------|---------------------------|

| Tapes (2402), Selector     | 180, 181: 7-track,        |

| Channel 1                  | 182, 183: 9-track,        |

|                            | 184-187: assigned locally |

| Tapes (2402), Selector     | 280, 281: 7-track         |

| Channel 2                  | 282, 283: 9-track         |

|                            | 284-287: assigned locally |

| Card Read Punch<br>(1442)  | 00A                       |

| Printer (1443)             | 00B                       |

| Card Reader (2540)         | 00C                       |

| Card Punch (2540)          | 00D                       |

| Printer (1403)             | 00E                       |

| Printer-Keyboard<br>(1052) | 009                       |

| Disk Storage (2311)        | 190                       |

If this installation uses System/360 BPS or BOS, then symbolic addresses may be used. Some of the most popular symbolic addresses have been standardized, and are listed in Appendix A.

## **SYSGEN** Time

Given the particular machine and I/O configuration of this Model 50 installation, the programmer or operator places a complement of IBM-supplied operating system programs in residence in main storage (or disk drive), generating a specific operating system for this installation. This system generation procedure is abbreviated syscen, and the time of its generation is referred to as syscen TIME. Once generated, the control lasts (possibly through many problem programs) until a change in operating system is required. Specific syscen procedures are given in the related publications for the operating system desired.

## System-Operator Communications

If the current operating system has provision for communication with the operator, and if the current control cards specifying this provision have been incorporated in the SYSCEN assembly, system-operator communication is used, with a 1052 Printer-Keyboard, if available; otherwise, the communication is by operator console. The 1052 is assigned to SYSLOC (BFS/BOS) or an appropriate address. Detailed system-operator communication, with appropriate tables for all allowable codes, is included in the Operating Guides referenced at the beginning of this section.

#### Making an Entry: Printer-Keyboard

To originate an operator-request, start at Step 1. When the operator responds to a system request, omit Steps 1 and 2.

1. Press the ready key on the keyboard. The 1052 is now ready.

2. Press the request key. The attn light may go on, indicating that the request has been initiated, but not accepted yet by the system. If the request is accepted, an I/O interruption to the CPU occurs (unless the PSW is masked against it). After the procd light comes on, the operator may proceed. The read light is on when the system reads the operator's request and the subsequent message. Now the operator may type his message. (The procd light goes off and on in between each typed character, but this is generally too rapid to be noticed by the operator. During the time the procd light is off, the keyboard is locked.) Most replies are a single character. Note that an operator response of 0 or 1 (even if transmitted inadvertently) terminates (aborts) the job in process if operating under System/360 BPS or BOS.

3. Position the carriage as desired. Normally the previous operation has done this automatically.

4. Make the desired entry by pressing the desired key(s). (A print-out occurs for each character entry.) Continue until entire entry is made.

Note: To cancel an entry, perform Steps 5 and 6; otherwise, omit these steps.

5. To cancel, press the altn code key and simultaneously press the cancel (numerical 0) key. This cancels all entries made during this typing. The procd light turns off momentarily, but comes back on again.

6. Re-enter the entire message. It is not necessary to press the request key again if the procd light is on. (Even if message is not re-entered, continue with following steps to terminate.)

7. Simultaneously press altn code and EOB (numerical 5) key to terminate. (If the program cannot wait, it may terminate by program operation.) In any case, termination locks the keyboard, turns off the procd and read lights, and returns the carriage to starting position. (Under System/360 os control is turned over to the system.)

8. Under System/360 BPS or BOS an additional step is required; press interrupt key to turn control over to the system. (If the system has terminated the communication and has started processing, this step may be omitted.)

Note: If the system has entered the wait state (wait light is on), operator intervention is positively required. (This is a practical, rather than a theoretical consideration: Wait state frequently occurs in all-machine programming; at machine speed the wait state would hardly register on the operator's mind. If the system waits long enough for the wait light to remain on, and nothing is running, look for messages or some sign of operator intervention.) If under System/360 BPS or BOS a keyboard entry is not feasible, operator must restore control to the system by pressing start, then interrupt keys on the operator's console.

#### Messages: System Operator (1052)

Information messages in telegraphic plain English may appear on the 1052 as check reports. These may be for information only. When a message appears on the 1052 and the system goes into a wait state, operator intervention is indicated. Most system messages (BPS and BOS) are single 4- or 5-character coded words (possibly followed by comments in plain English). The meaning and action required for the code are defined in the appropriate operating guides. (In System/360 os the code is not necessarily the message.) If a 3-character code (System/360 BPS) or a 4-character code (System/ 360 BOS) is printed on the first line, with a 4- or 5-character code below it, the first line code is the address of the unit, and the second line code contains the error and action involved.

If System/360 BAP is in use, the system, on entering the wait state, prints a 3-character code on the 1052, identifying the reason for the program wait. In some cases a brief descriptive message in plain English follows. Code meaning and action required are defined in the appropriate operating guides for that system. In certain cases the code is not typed out on the 1052; it is then necessary to check the operator's console, which always displays the reason for the program wait in the last three bytes of the instruction address. (On the console, the 3-byte code is displayed in hexadecimal, appearing as six characters.)

#### Making an Entry: Operator's Console

To initiate communication, or to respond to a system request (the wait light will be on) start at Step 1.

1. Press stop key. Manual light goes on.

2. If any operating system except System/360 BAP or os is in use, display main storage address 000. Locations 0-4 are displayed in the SDR. Read the hexadecimal characters, translate them to alphameric, and find the meaning in the appropriate operating guide for that system. If location 4 contains an alphameric A (1100 0001) then action/reply is required. After taking the required action, store into main storage address 005 (in hexadecimal) the single-character reply required. (Go to Step 4.) Note that an operator response of 0 or 1 (even if transmitted inadvertently) terminates (aborts) the job in process.

3. If System/360 BAP is in use, display three lowestorder bytes of the instruction counter. Code meaning and action required are defined in the appropriate operating guides for that system. (No provision is made for operator reply to the console. Go to Step 4.)

4. After appropriate operator action (and reply, if available) it is necessary to take the system out of the wait state. Press start key. Manual light goes off.

5. Press interrupt key. The system resumes processing.

#### Messages: System Operator (System/360 BPS and BOS) Operator's Console

Because of the limitation of the number of bytes of information provided by the console for system-operator communication, plain English statements are not included. The bytes will be code and hexadecimal characters. In certain cases, the system will issue two coded messages—one for the device involved, and the second for the error and action desired. The following operator action is necessary between the two messages:

If the system is in the wait state (wait light is on) and the operator has pressed the stop key (manual light is on), he next displays main storage address 000. If location 4 in the SDR (locations 3 and 4 under System/360 BPs) is all zeros, the message must be recorded (because it indicates the device-portion of a two-part message). He then presses the start key and the interrupt key. This passes control back to the system, which can then send the second part of the message. (System reply is almost instantaneous; therefore, it may seem to the operator that the interruption has not worked properly, because the system may go into the wait state immediately.) Now press the stop key to prevent interruption. When the contents of storage address 000 is displayed, note that the sor has the second part of the message. After appropriate action, release the system with the same procedure, pressing the start key, then the interrupt key. (The operator must release the system in any event.)

#### Messages: System Operator (System/360 BAP) Operator's Console

If the 1052 is not available under this operating system, the sole communication between the system and the operator is via the operator's console. (The sDR is not used for this purpose.) The three lowest-order bytes of the instruction counter now contain a code that shows the reason for any system wait. Definition and procedures for the code are found in *IBM System/360 Basic Programming Support Operating Guide for Basic Assembler and Utilities*, Form C28-6557. Communication is provided only one-way (from system to operator). The only possible communication provided between operator and system is by pressing the start and interrupt keys, which returns control to the system. (See also "Analyzing an Unexpected Wait State Condition.")

# Operator-Console Considerations (except under System/360 OS)

When the system goes into the wait state, providing the operator with a code message on the operator's console, press the stop key; this places the system in a manual stop. (This holds potential interruptions pending while displaying and reading the appropriate code.) The only way to return the system to control after a manual stop is to manually press the start key. Press the interrupt key to return to the program.

If the stop key is not pressed to read the console code, then control can be returned to the system by pressing the interrupt key alone. (It is not necessary to press the start key to return control unless a manual stop has been executed.)

## Using the 1410/7010 Emulator

Detailed information on this feature can be found in *IBM System/360 Model 50 Emulation of the IBM 1410/7010 Data Processing Systems*, Form C28-6568. The emulator program, provided on cards, may use card format in actual programming. If it is desired to convert the card program to tape, the following procedures are recommended.

#### **Object Generation of Emulator Program**

This is a pre-sysgen (1410/7010) procedure used to establish the required I/O configuration for this installation.

1. Prepare the control cards for use with card-totape utility program 360P-UT-051 used to establish the tape drive as the output address. Integrate the control cards with the card-to-tape utility program, forming the card-to-tape deck. (See Appendix D for job control cards for utility programs. See detailed procedure, *System/360 BPS Specifications*, Form C24-3363 for card-to-tape [see only the sections on utility-modifier cards and field-select cards]. See *System/306 BPS Programmer's Guide*, Form C24-3354 for format [see section on job control cards for utility programs]. See *System/360 BPS Operating Guide*, Form C24-3392 for card sequence [see section on card-to-tape utility program].)

2. Prepare the necessary REP cards for storage size, channel identification, and device addressing required for the emulator program. (See detailed procedure in referenced manual, Form C28-6568.)

3. Take the IBM-supplied combined absolute-loader and emulator program in card form, together with the cards and utility program of the preceding steps and combine them as: card-to-tape utility program, absolute-loader, and emulator, with REP cards. Place the combined deck on the card reader. Make the device ready.

4. Mount a clean tape on another tape drive for the configurated emulator object program. Make the device ready.

5. Set disable interval timer switch to DSAB INTVL TIMER.

6. Select the desired card reader with the three load unit switches.

7. Press load key. Load light goes on.

8. Because device addresses have been patched in (REP cards), the entire updated combined-emulator object program is now written onto the output tape. (If the required device patch addresses are not constant enough to be a part of the combined emulator tape, at least enter REP cards with the 1052 address and card reader address. In this way the tape can still be used, picking up the REP patch data as required via

the 1052, during the wait state which occurs at the end of the emulator tape.) In any case, communication between emulated system and the operator during emulation is via the 1052. At the completion of object generation, the configurated emulator object program processed on tape has been tailored to this installation's I/O configuration. Remove the reels and decks. Reset disable interval timer switch to normal position (straight out).

#### Operating the 1052 in Emulator Mode

To make entries in the emulator program (when operator intervention is provided between the emulator program and the problem program):

1. Press the request key.

2. Press the single-character function key. (For example, press the numerical 3 key for a device assignment. See referenced manual, Form C28-6568 for detailed coding.)

3. Press the space bar. (The carriage returns.)

4. Enter the information desired. (Observe format described in the referenced manual, Form C28-6568.)

5. To correct typing errors—any line may be canceled by simultaneously pressing the altn code key and the numerical 0 key. (The system then returns the carriage. The last line has been canceled. It is necessary to retype it.) To delete the entire function—start a new line (perform the cancel function if necessary), then simultaneously press the altn code key and the numerical 5 (EOB) key.

6. To release data, at the end of the information line or message, simultaneously press the altn code key and the numerical 5 (EOB) key. (This function is similar to the release of the 1415 console.)

#### **Operating the 1052 in Problem Mode**

To make entries required by the problem program:

1. Press the request key. The read and procd lights go on.

2. Press the I key.

3. Press the space bar. (Carriage returns.)

4. The read and procd lights go out and the system responds by typing an I. (If the system does not respond by typing an I, press the numerical 2 key, then press the space bar. The lights go out and the system then responds by typing an I.)

5. Enter the information desired.

6. To correct typing errors—simultaneously press the altn code key and the numerical 0 key. Any cancellation in problem mode requires return to Step 1, as the entire communication has been canceled.

7. To release—simultaneously press the altn code key and the numerical 5 (EOB) key.

# Using the Configurated Emulator Program (Load-and-Go)

This is a single-phase operation where emulator, control cards, and problem program are set into appropriate initialized I/0 units; manual IPL starts load-and-go.

1. Prepare the CTL and LOAD control cards (described in detail in the referenced manual, Form C28-6568). If the problem program is on cards, insert the control cards in front of the problem program deck and place the combined deck on the card reader. Otherwise, place the control cards on the card reader and the problem program on an appropriate device. Make the device(s) ready.

2. Mount the configurated emulator program tape on the tape drive. Make the tape drive ready.

3. Select the tape drive with the three load unit switches.

4. Press load key. Load light goes on. The combinedemulator program is IPL-loaded. Control is passed to the emulated IBM 1410/7010 System, which immediately takes up the control cards from the card reader, and continues with execution of the problem program from its I/o device.

#### Using the Configurated Emulator Program (Operator Intervention between Emulator Mode and Problem Mode)

This is a two-phase operation. First the emulator program is loaded, causing the system to emulate a 1410/7010 system; the card reader is deliberately not made ready. Accordingly, the emulated system, when loaded, goes into a wait state, awaiting operator intervention.

1. Mount the configurated emulator program tape on a tape drive. Make the tape drive ready.

2. Select the tape drive with the three load unit switches.

3. Press load key. Load light goes on. The configurated emulator program is IPL-loaded. The emulated system goes into a wait state.

During the wait state the operator intervenes, as required (see "Operating the 1052 in Emulator Mode"). When the operator is ready to start the problem program:

1. Prepare the CTL and LOAD problem-program control cards (described in detail in the referenced manual, Form C28-6568). If the problem program is on cards, insert the control cards in front of the problem program deck and place the combined deck in the card reader. Otherwise, place the control cards in the card reader and the problem program on an appropriate device. Make the device(s) ready. (If the card reader is not available, the control functions can be entered via 1052; see "Operating the 1052 in Emulator Mode," using "a" as the single-character function key.) 2. Press request key.

3. Press numerical 8 key. The system now executes the problem program.

#### **Operator Considerations**

During emulation procedures, the system operates with minimum burden to the operator. When the operator is involved, however, certain minimal differences involved in emulator operation must be recognized:

1. Certain dissimilar graphics occur in the print-out during emulation, because of typeface difference in systems. These differences are shown in comparison tables in the emulation publication referenced. Normal alphabetic and numerical values are identical to those conventionally used.

2. Device assignment addresses (1410/7010) are in different format from the 3-digit group normally used in System/360 addressing. The emulator manual describes the technique for relating addresses between systems, and techniques for causing a print-out of the device assignment table in use by the emulator.

3. Operator communication code format (specifically set in any system) is similarly described in the referenced emulator manual.

4. The 1052 keyboard, in addition to providing system-operator communication, is used by the operator as an emulated 1415 Console Printer. These console functions are described in Table 1.

Table 1. Correlations of 1415 Functions with 1052 Functions

| FUNCTIONS OF    | CORRESPONDING 1052                                 | 1052 printout     |

|-----------------|----------------------------------------------------|-------------------|

| тне 1415        | <b>KEY/FUNCTION</b>                                | IDENTIFICATION    |

| Programmed Halt |                                                    | S                 |

| Error Halt      |                                                    | E                 |

| Reply           |                                                    | R                 |

| Table Display   | 6                                                  | 6                 |

| Alter           | Α                                                  | Α                 |

| Restart         | 8                                                  | 8                 |

| Address Set     | В                                                  | В                 |