MIDWAY REPORT ANTACCS PROJECT July 1964

INFORMATICS INC.

.

# MIDWAY REPORT

ANTACCS PROJECT TECHNOLOGY, METHODOLOGY AND INTEGRATION COVERING PERIOD January 1964 to July 1964

Prepared Under Contract

to

The Office Of Naval Research (Nonr-4388(00))

by

INFORMATICS INC. 15300 Ventura Boulevard Sherman Oaks, California

July 15, 1964

# ERRATUM

Discontinuities in the numbering system omit page numbers:

.

2-166 to 2-177 2-245 to 2-265 4-28 to 4-33

No material is missing.

.

,

# TABLE OF CONTENTS

| TABLE OF CONTENTS     |                                                                      |       |  |

|-----------------------|----------------------------------------------------------------------|-------|--|

| LIST OF ILLUSTRATIONS |                                                                      |       |  |

| SUMMARY               |                                                                      |       |  |

|                       |                                                                      |       |  |

| SECTION I             | INTRODUCTIONS                                                        |       |  |

| 1-1                   | General                                                              | 1 – 1 |  |

| 1-2                   | Study Objectives and Approach                                        | 1-4   |  |

| 1-3                   | Report Organization                                                  | 1-5   |  |

| SECTION 2             | TECHNOLOGY                                                           |       |  |

| 2-1                   | General and Introductory                                             | 2-1   |  |

| 2-2                   | Display Technology                                                   | 2-2   |  |

| 2-3                   | Displays – User Technology and Software                              | 2-23  |  |

| 2-4                   | Input/Output Technology                                              | 2-77  |  |

| 2-5                   | Memories                                                             | 2-131 |  |

| 2-6                   | Components and Packaging                                             | 2-189 |  |

| 2-7                   | Advanced Usage Techniques                                            | 2-217 |  |

| 2-8                   | Computer System Organization                                         | 2-221 |  |

| 2-9                   | Programming                                                          | 2-268 |  |

| SECTION 3             | METHODOLOGY                                                          |       |  |

| 3-1                   | Introduction                                                         | 3-1   |  |

| 3-2                   | General Methodology                                                  | 3-2   |  |

| 3-3                   | Implementation Methodology                                           | 3-82  |  |

| 3-4                   | Specific Methodology                                                 | 3-113 |  |

| SECTION 4             | STUDY INTEGRATION TASK                                               |       |  |

| 4-1                   | Scope and Objectives of Study Integration Task                       | 4-1   |  |

| 4-2                   | Comparison of Implications of Alternate System<br>Operating Concepts | 4-6   |  |

# Page No.

| SECTION 4 (C | ont'd.)                                                           |      |

|--------------|-------------------------------------------------------------------|------|

| 4-3          | Demonstration of the Synthesis and<br>Evaluation of a System Node | 4-21 |

| 4-4          | Discussion of System Planning Items                               | 4-34 |

| SECTION 5    | BIBLIOGRAPHY                                                      |      |

| 5-1          | Introduction                                                      | 5-1  |

| 5-2          | Technology                                                        | 5-2  |

| 5-3          | Methodology                                                       | 5-47 |

# LIST OF ILLUSTRATIONS

| FIG. NO. | TITLE                                              | PAGE NO.      |

|----------|----------------------------------------------------|---------------|

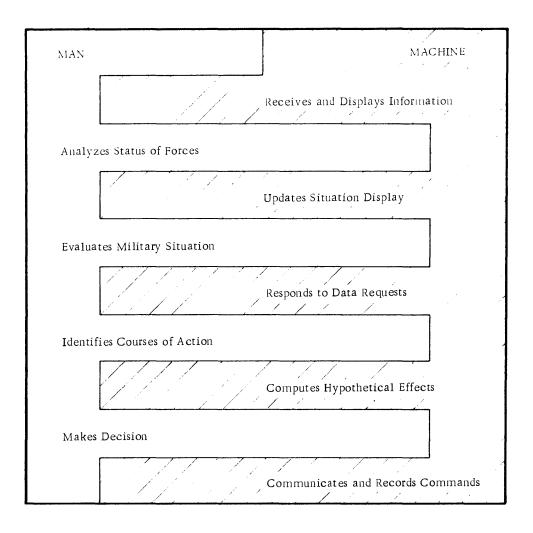

| 2-1      | Man/Machine Coordination                           | 2-31          |

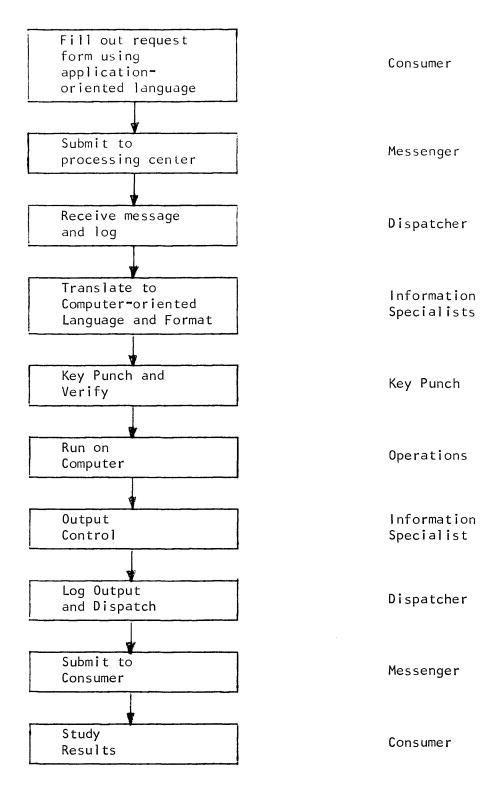

| 2-2      | Over-all Command Function                          | 2-33          |

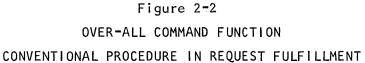

| 2-3      | List Display of Military Installations             | 2-35          |

| 2-4      | List Display Modifying Military Installations      | 2-35          |

| 2-5      | List Display Modifying Bomber Air Bases            | 2-35          |

| 2-6      | List Display Modifying Fuel Storage                | 2 <b>-</b> 35 |

| 2-7      | List Display Political Limits                      | 2 <b>-</b> 36 |

| 2-8      | Format Display Current Totals                      | 2-36          |

| 2-9      | Schematic of Commander's D. P. System              | 2-40          |

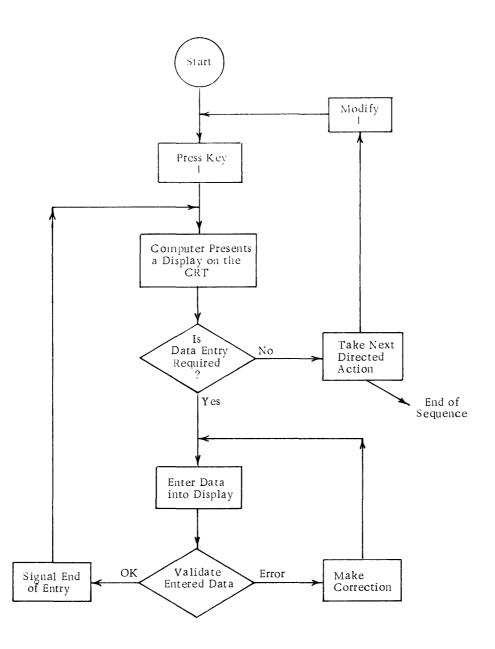

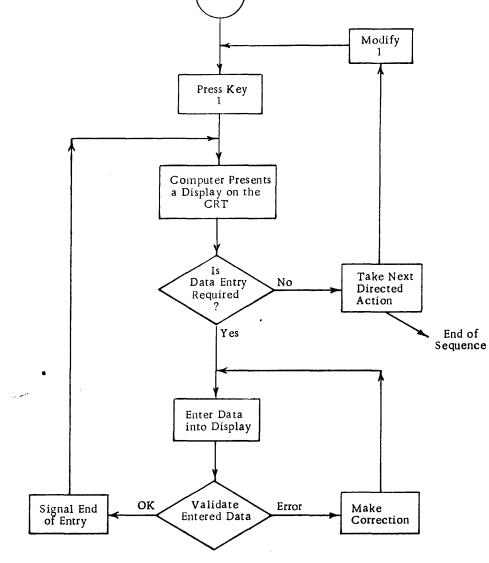

| 2-10     | Typical Operator Steps in Use of Function Keys     | 2-44          |

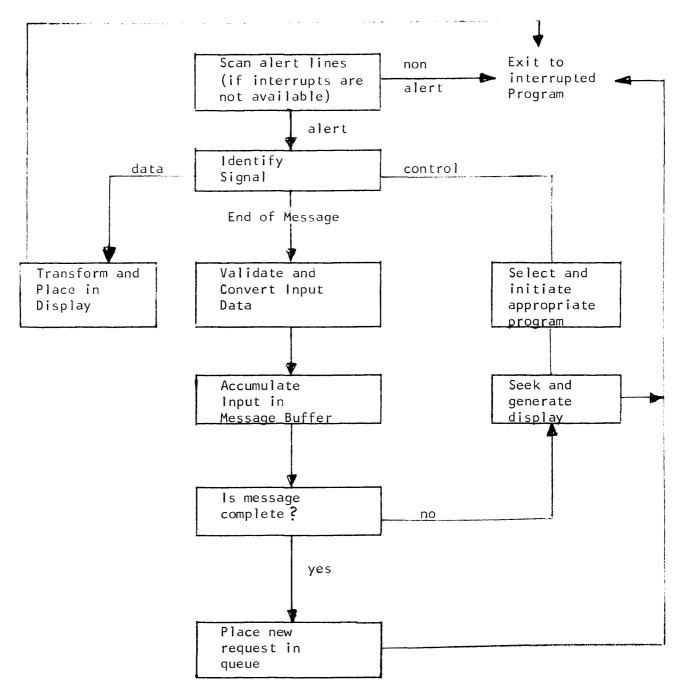

| 2-11     | Computer Steps in Conjunction with Function Keys   | 2-45          |

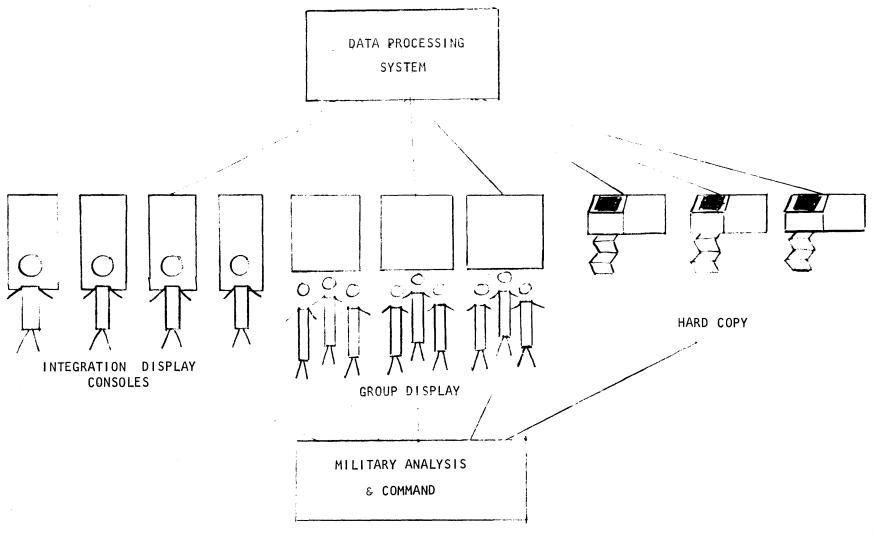

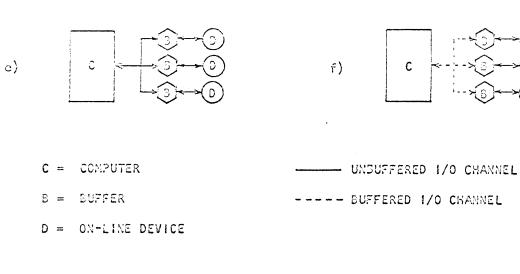

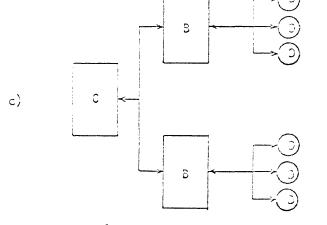

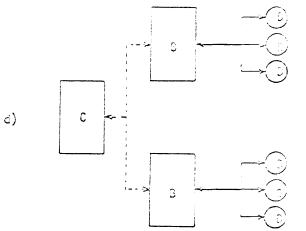

| 2-12     | Computer/On-line Device Configurations             | 2-46          |

| 2-13     | Example of Format Display                          | 2-50          |

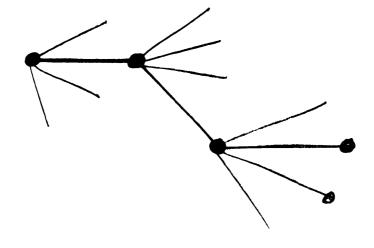

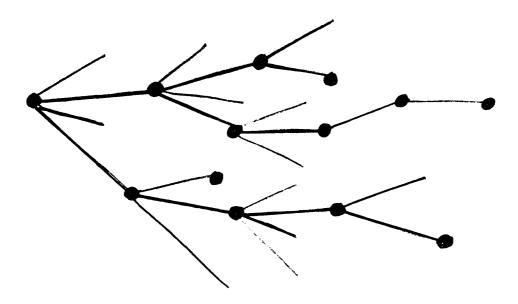

| 2-14     | Selection "Trees"                                  | 2-51          |

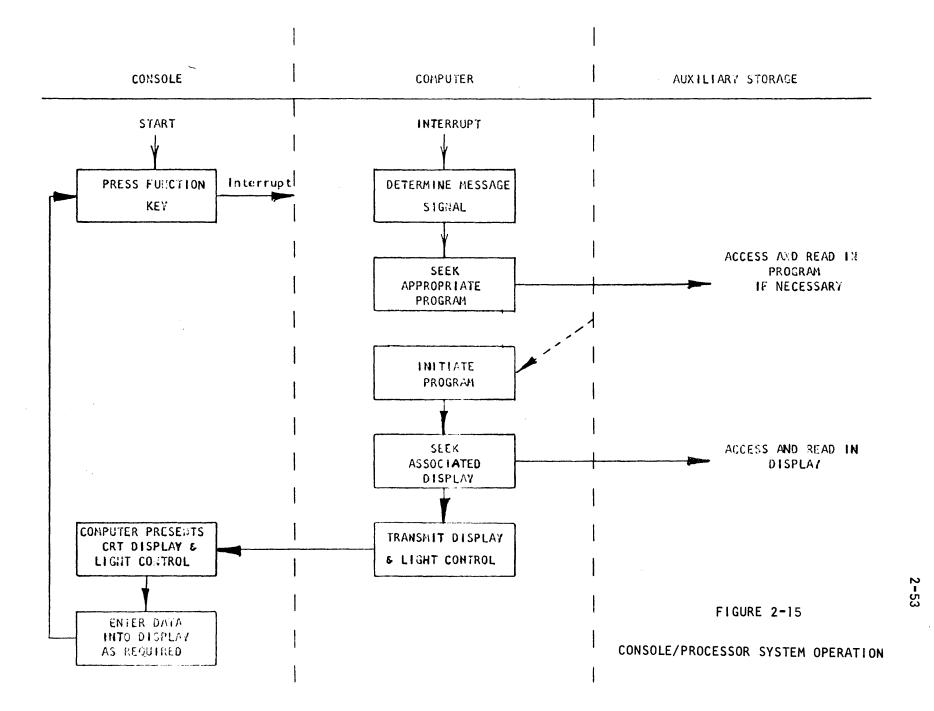

| 2-15     | Console/Processor System Operation                 | 2-53          |

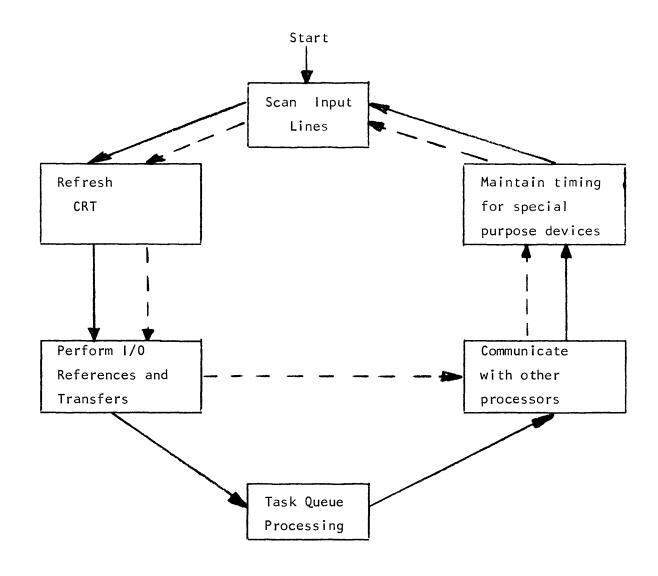

| 2-16     | Basic Executive Control Loop                       | 2-61          |

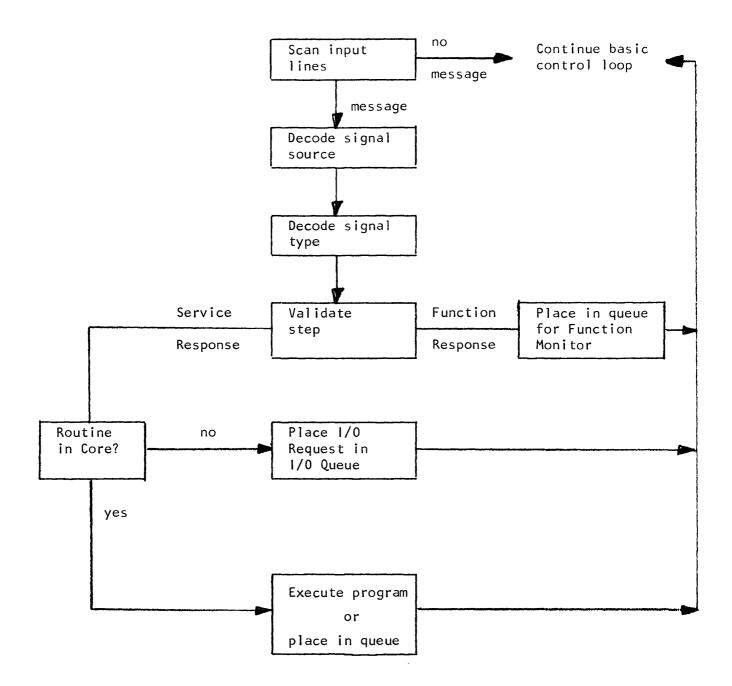

| 2-17     | Tasks Associated with Scanning Input Message Lines | 2-62          |

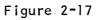

| 2-18     | Processing Servicing Requirements                  | 2-64          |

| 2-19     | Programs for a Display Console                     | 2-73          |

| 2-20     | Probability of Console Service                     | 2-75          |

| 2-21     | Relations of Man and Machine                       | 2-78          |

| 2-22     | Typical Display Overlay                            | 2-93          |

| 2-23     | Typical Series of Operator Steps                   | 2-95          |

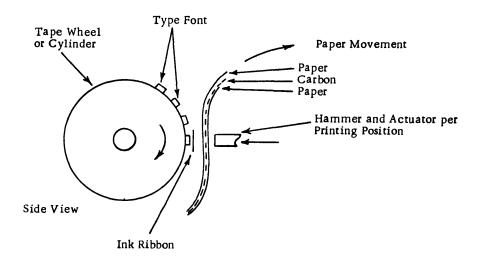

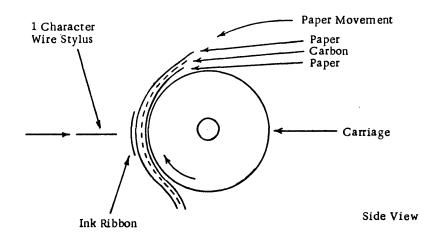

| 2-24     | Rotating Drum Printer                              | 2-98          |

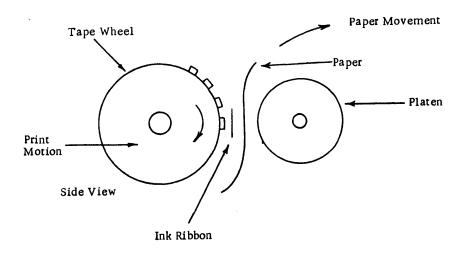

| 2-25     | Impact Wheel Printer                               | 2-99          |

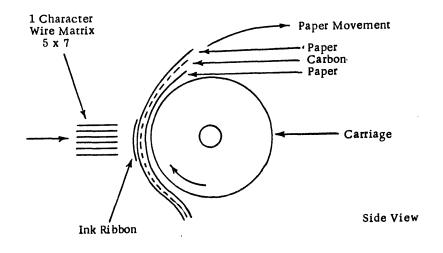

| 2-26     | Matrix Printer                                     | 2-100         |

| 2-27     | Stylus Printer                                     | 2-101         |

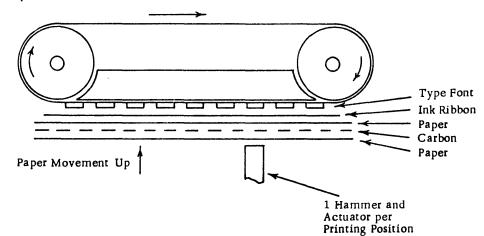

| 2-28     | Chain Printer                                      | 2-102         |

| 2-29     | Stick-Type Printer Bars                            | 2-103a        |

1

|   | FIG. NO. |                                                         | PAGE NO. |

|---|----------|---------------------------------------------------------|----------|

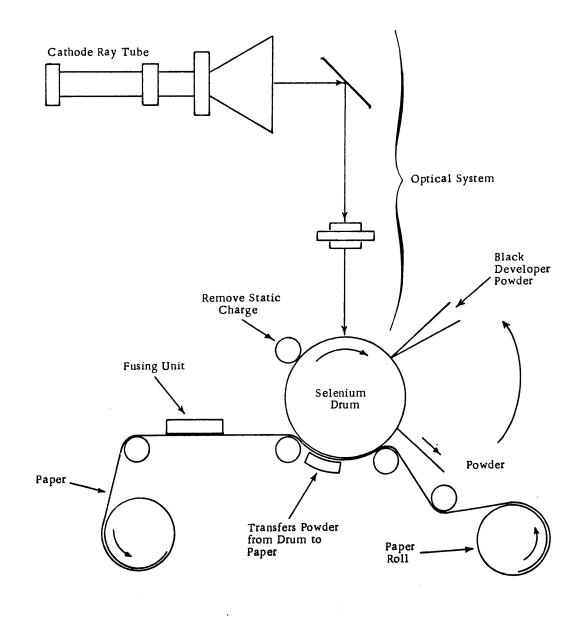

|   | 2-30     | Electro-Optical Printer                                 | 2-108    |

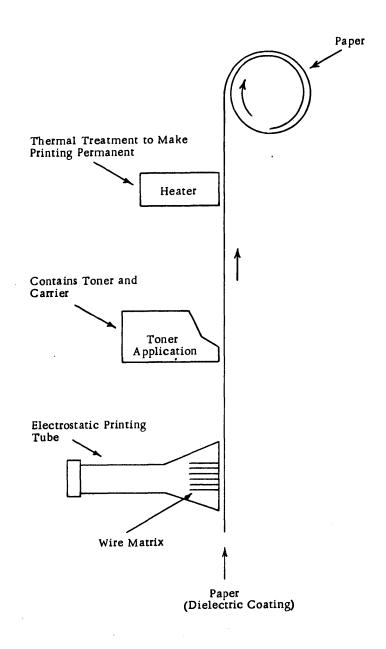

|   | 2-31     | Electrographic Printer                                  | 2-110    |

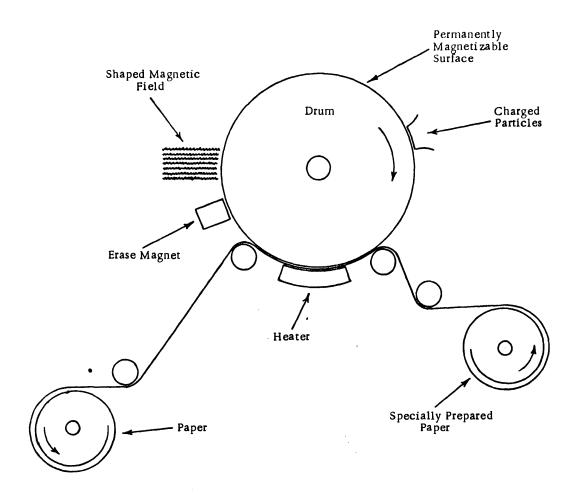

|   | 2-32     | Magnetic Printer                                        | 2-113    |

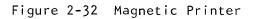

|   | 2-33     | Drum Printer                                            | 2-116    |

|   | 2-34     | Typical Interface Functions                             | 2-122    |

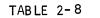

|   | 2-35     | Storage Capacity and Cycle Time of Memories             | 2-182    |

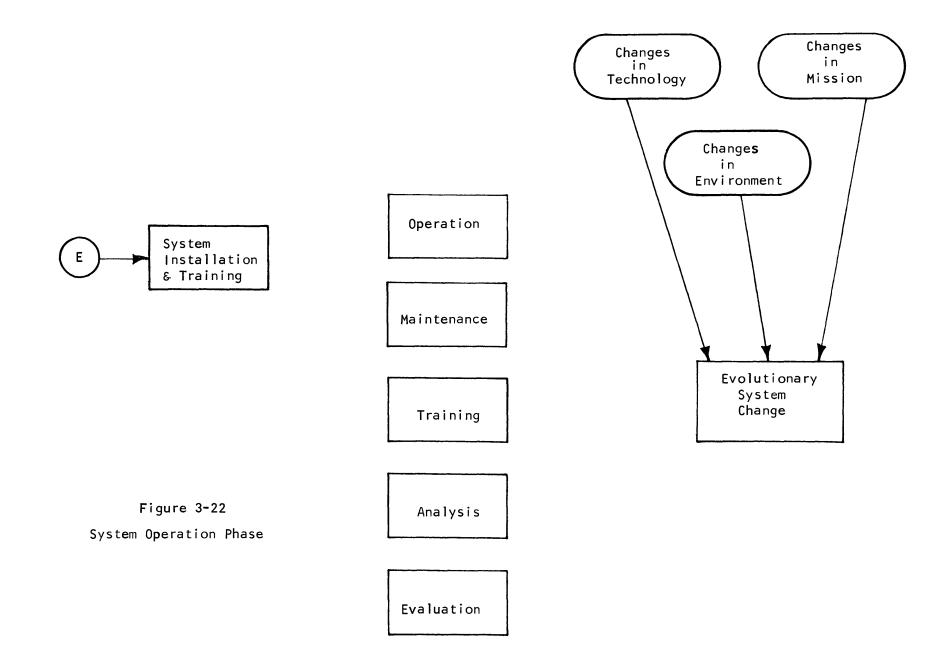

|   | 3-1      | Command and Control Environment                         | 3-15     |

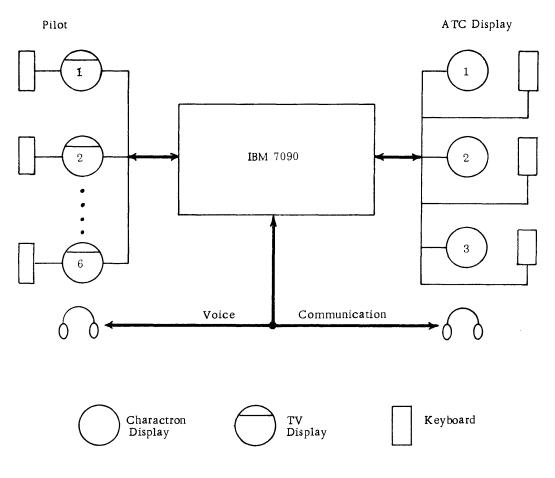

|   | 3-2      | Functional Diagram of Air Traffic Control<br>Simulation | 3-16     |

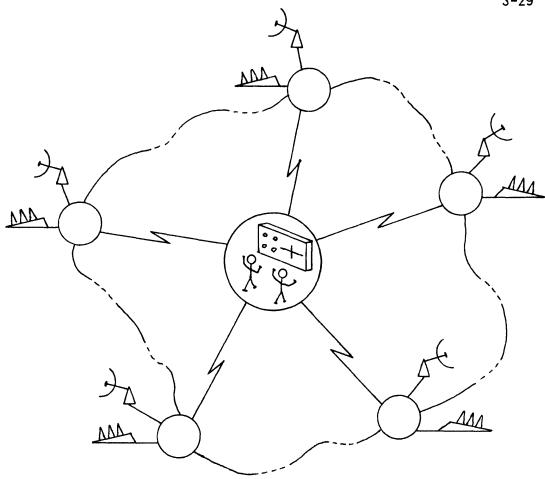

|   | 3-3      | Hypothetical System Design                              | 3-29     |

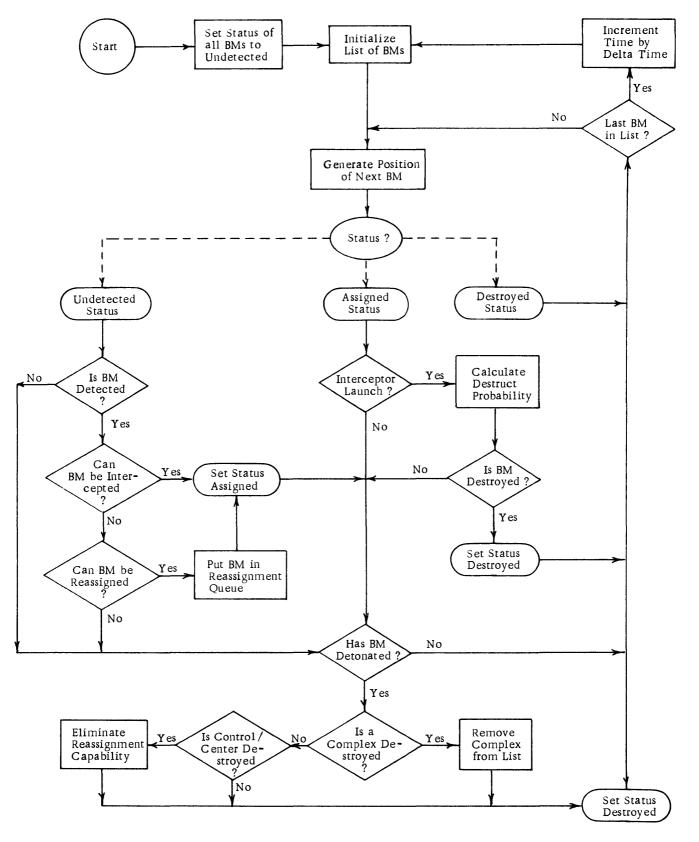

|   | 3-4      | Missile Interceptor Model                               | 3-32     |

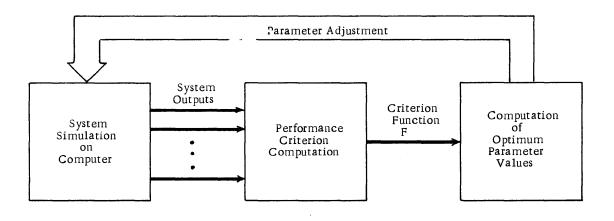

|   | 3-5      | Design Optimization Problem                             | 3-46     |

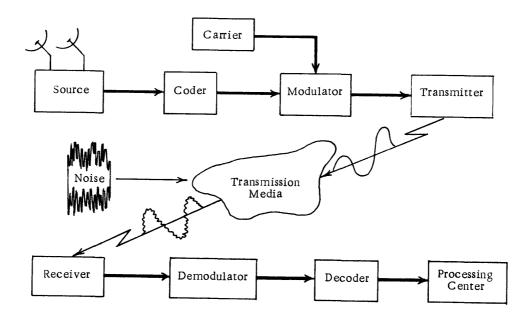

|   | 3-6      | Carrier Transmission System                             | 3-47     |

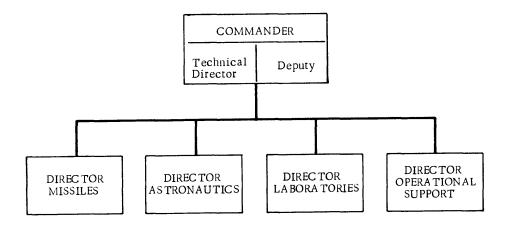

|   | 3-7      | Technical Branches PMR                                  | 3-54     |

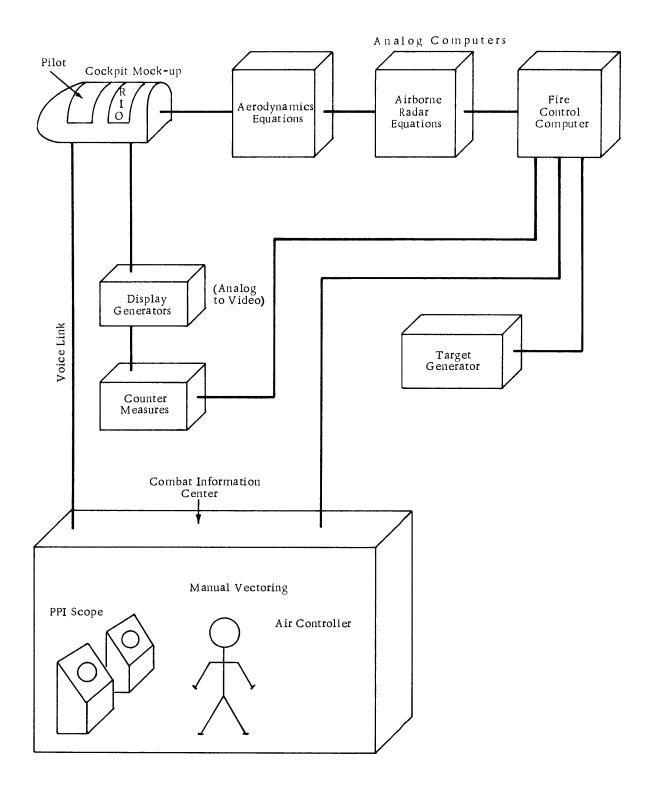

|   | 3-8      | Manual Vectoring Schematic                              | 3-62     |

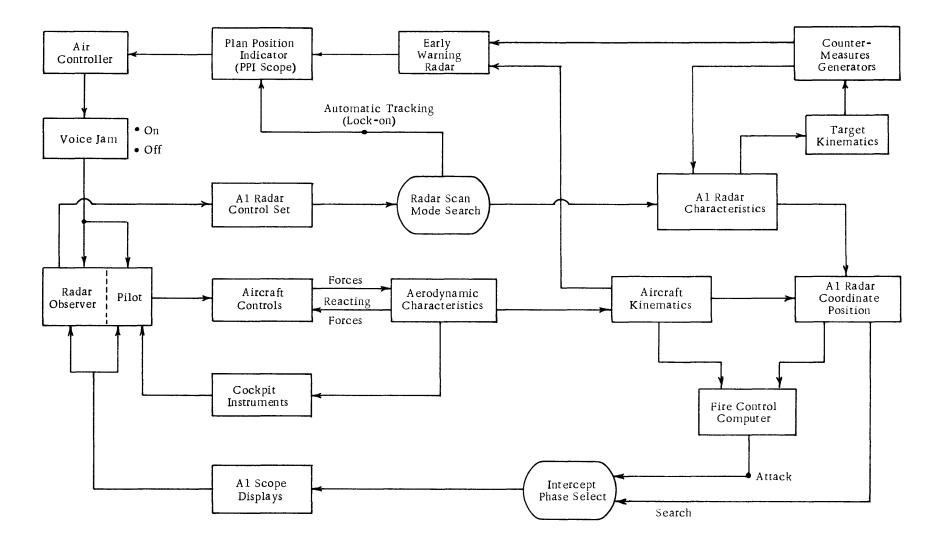

|   | 3-9      | F-4B Intercept Simulator                                | 3-67     |

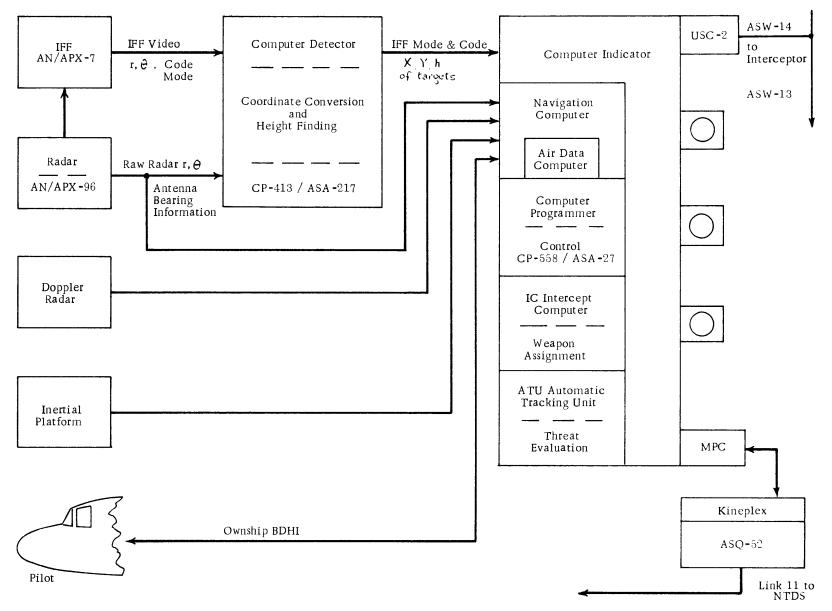

|   | 3-10     | ATDS Prime Avionics Equipment Configuration             | 3-71     |

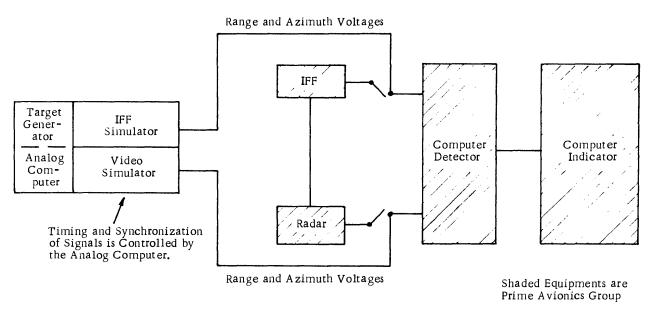

|   | 3-11     | Radar Data Input Simulation                             | 3-78     |

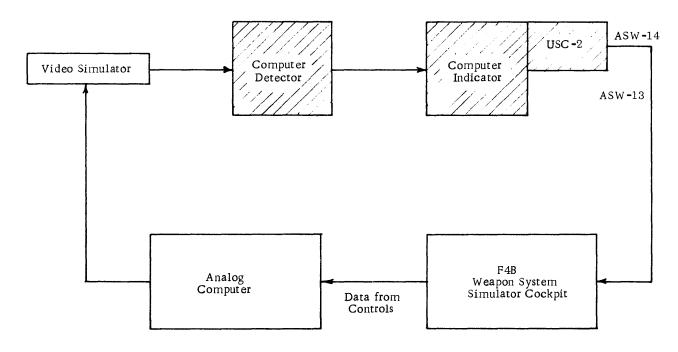

|   | 3-12     | Using the Cockpit Simulator                             | 3-78     |

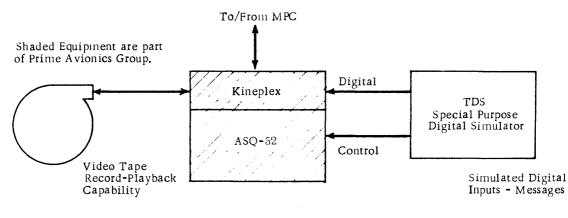

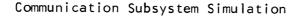

|   | 3-13     | Communication Subsystem Simulation                      | 3-81     |

|   | 3-14     | Communications                                          | 3-81     |

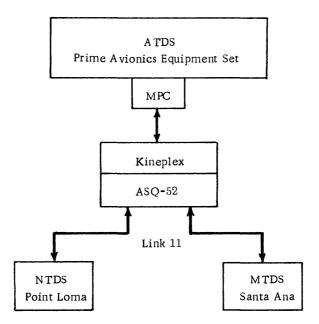

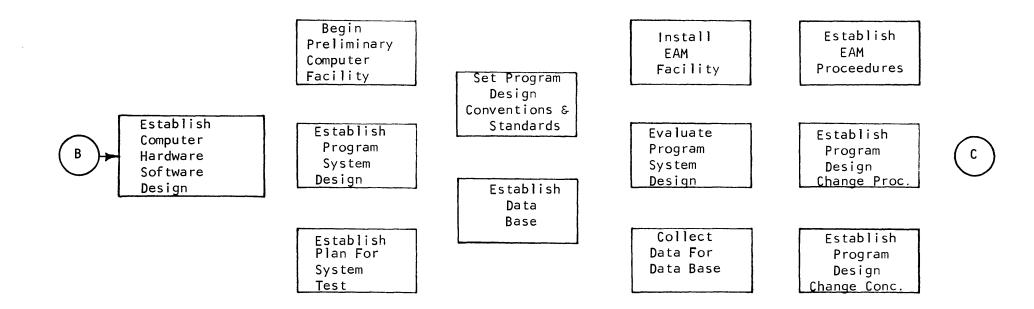

|   | 3-15     | System Definition Phase                                 | 3-94     |

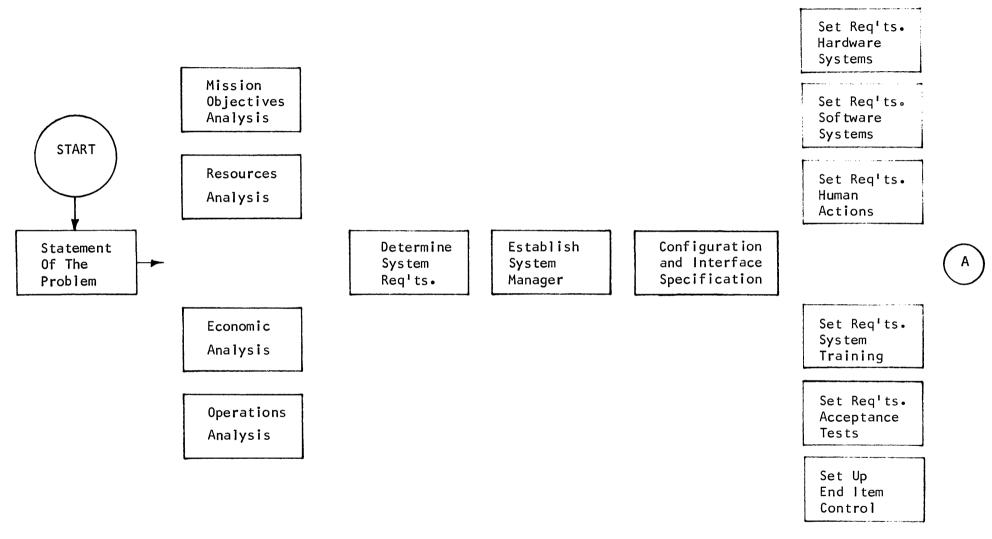

|   | 3-16     | System Design Phase                                     | 3-95     |

|   | 3-17     | Program Design Phase (1)                                | 3-96     |

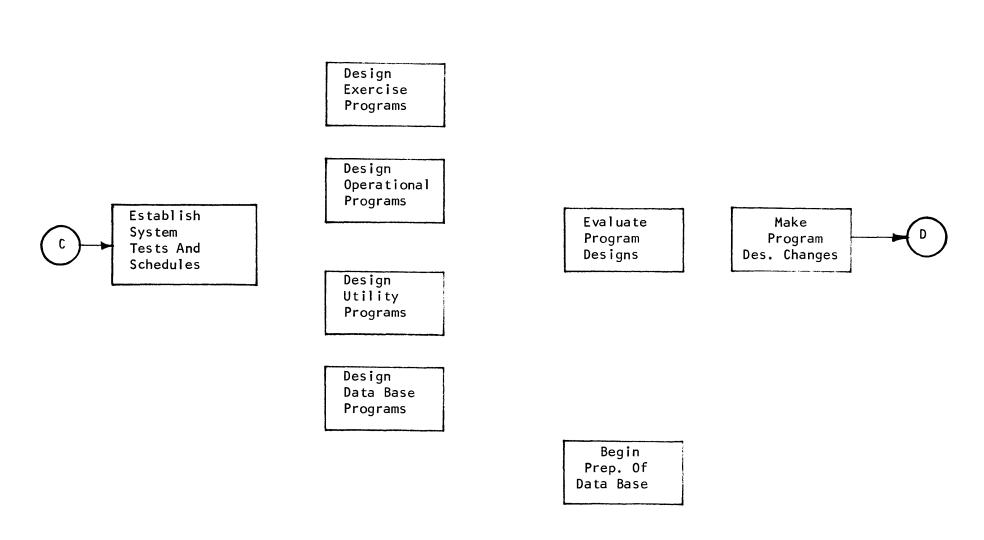

|   | 3-18     | Program Design Phase (II)                               | 3-97     |

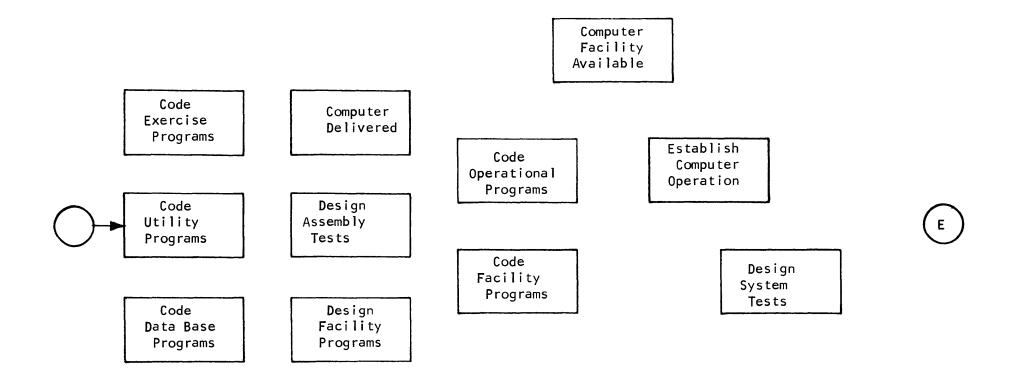

|   | 3-19     | Program Production Phase                                | 3-100    |

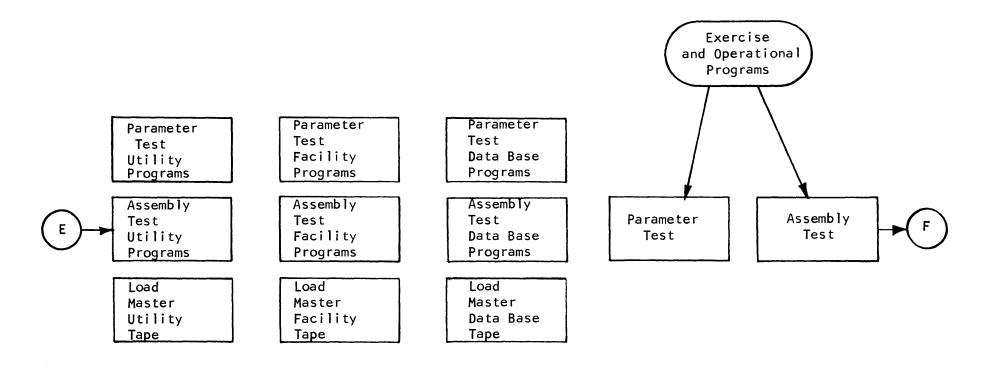

|   | 3-20     | Program Test Phase                                      | 3-101    |

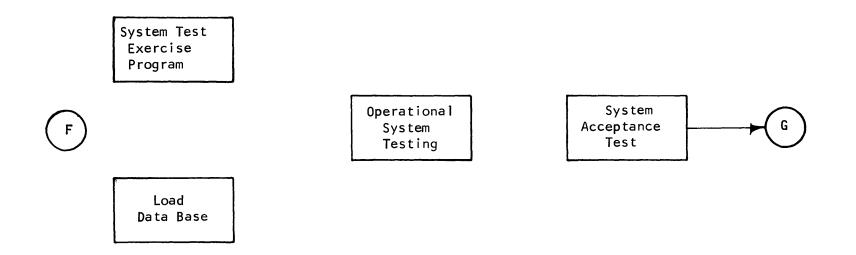

| ` | 3-21     | System Test Phase                                       | 3-102    |

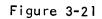

|   | 3-22     | System Operation Phase                                  | 3-103    |

|   |          |                                                         |          |

iv

#### ANTACCS MIDWAY REPORT

### SUMMARY

This is a report of the technology, methodology, and integration aspects of the ANTACCS study project sponsored by the Office of Naval Research, in conjunction with various Naval organizations including BuShips, BuWeps, Chief of Naval Operations, and Commandant Marine Corps. It is the preliminary report of work performed by Informatics Inc. under Contract Nonr-4388(00). It is a Midway Report representing that portion of the work accomplished during the first half of the 12 month project.

The project members of Informatics Inc. are indebted to Mr. R. Tuttle, the ONR Scientific Officer who is guiding this effort. They are also indebted to the Study Monitor Group, a group consisting of knowledgable and experienced persons from BuShips, BuWeps, Chief of Naval Operations, NAVCOSSACT and Marine Corps Headquarters for their advice in this effort. The knowledge of the Scientific Officer and the Study Monitor Group in Naval requirements and environment as well as their experience with present Naval efforts has been of valuable assistance in the assurance of a more useful product.

The technical staff of Informatics has been supplemented in certain technical areas by subcontracting efforts of Hobbs Associates. Hobbs Associates has provided many of the sections on hardware techniques, especially those in the circuits and packaging areas. Hobbs Associates has also contributed in the area of memories and display devices. The purpose of this project is to develop and present information concerning technology, methodology and integration which will be of assistance to planners in the design and implementation of command control systems. The project scope and emphasis is restricted to the application of its techniques and data to the solution of problems concerning the Advanced Naval Tactical Command Control System. This system is identified by an SOR as being visualized for the 1970-1980 time period, and for which a TDP is to be developed in 1966.

The three areas of the project are: Technology, Methodology, and Integration. <u>Technology</u> deals with scientific and technical material of potential use to Naval command control systems. This material includes both hardware and software subjects. <u>Methodology</u> is concerned with technical and managerial techniques used in the planning and implementation of Naval systems. <u>Integration</u> covers the unification of technology, methodology, and requirements into candidate approaches to the design of Naval systems and their parts.

This Midway Report represents work in progress. An attempt has been made to organize the report in such a way that all areas are included, at least structurally, as they will appear in the final report. Since this is a preliminary report, many sections are incomplete. In many cases only a foundation of information for the technical area has been collected and organized. Still to be accomplished in most of the areas is the translation of that basic information to opinions and conclusions concerning the usefulness or future application of this particular information. For instance, in the display area the techniques have been identified, classified and analyzed. Remaining is a discussion

vi

of the relative merits of the various approaches, especially related to operational requirements in ANTACCS.

It is the express desire of the Informatics project personnel that this report be examined with a critical eye by the Scientific Officer, the Study Monitor Group and others who may also be qualified to criticize it. It is hoped that the critical viewpoint is taken within the framework of the fact that this is a preliminary report representing work in progress. The major useful contribution of the contract effort will be developed and reported during the last half of the project effort. We believe that sufficient information is presented in this present report to indicate the general direction in which the project is proceeding. It should provide the basis to allow the ONR Scientific Officer and the Study Monitor Group to redirect the efforts as appropriate.

### 1. INTRODUCTION

#### 1.1 GENERAL

Perhaps the fastest growing technology within the military at the present time is that of command and control systems for strategic and tactical uses. This technology deals with the application of modern electronic computer techniques to modern military operational requirements. The subject matter of this report is techniques for design and implementation of tactical command and control systems. Although the work deals principally with the techniques, equipments, technology and methodology involved in the implementation of Advanced Naval Tactical Command and Control Systems (ANTACCS) for the 1970-1980 time period; the information is of interest in other military command and control systems.

The technology stemming from and involved with the modern stored program electronic computer is only 14 or 15 years old. It has not benefited from the many years of experience and discipline of such important Naval technologies as naval architecture or armament design. The technology is very new and rapidly growing; methodology in the sense of unified, universally-used techniques is virtually nonexistent. The object of the ANTACCS study project is to provide information on information processing technology and information systems design methodology to serve as a resource document for the use of planners of future Naval tactical data systems.

Military command and control systems provide a greater challenge to electronic data processing than any other application. Some of the characteristics of command and control systems which account for this challenge are:

Considerable emphasis on man/machine interactions and requirements; the command and control system is, in the final analysis, designed to facilitate the decision processes of the commander and his staff.

- 2) The computer is imbedded in an on-line or real-time environment involving a large amount of instrumentation and peripheral equipment with which it must interact.

- 3) In most command and control applications there are large-scale file management tasks involving the receipt, collation, and retrieval of facts.

- 4) Most command and control system are very large information handling systems involving a multiplicity of input and output information channels. These systems are further complicated by the requirement to interact logically with many command levels and with much remote instrumentation.

- 5) There are especially challenging operational and environmental problems; reliability requirements are exceedingly high, and physical and logical environmental constraints are very often especially restricting.

Together these create a special challenge for the designer, from the component level to the system integration level.

Naval tactical command and control systems supply even greater challenges than command and control systems in general. There are additional physical factors which become important; space limitations and the movement of a ship or vehicle are simple examples. There are additional logical and operational factors: missions change for a given vehicle or platform, the entities with which the system communicates may change depending on the mission or operation, and there are extraordinary problems of logistics in installing, maintaining and operating equipment on a fighting ship.

To assure a meaningful product and remain responsive to the requirements of ANTACCS, the project will illustrate the techniques developed by applying them to the requirements developed and discussed by Booz Allen Applied Research, Inc. in a companion report. Accordingly, this volume discusses

1-2

technical material useful to system designers in defining, designing, and implementing systems such as ANTACCS. This is done from the standpoint of the electronic equipments involved, and with special regard for the people who will use them. It deals with the technology of future command and control systems, that is, the hardware and software techniques available for or necessary to system implementation. It also deals with the methodology of system implementation, that is, the techniques of system engineering management and the application of these techniques to satisfy requirements and to thereby produce an operational system. Although this work is related to the requirements which have been developed in a companion project by Booz Allen Applied Research, Inc., to a very great extent, it can stand on its own as a document for future use of planners of Naval command and control systems.

The scope of the present work is of extraordinary magnitude. The subject matter of technology ranges from integrated circuitry of a computer to computer systems organization. Methodology subjects range from simulation languages to techniques for planning and implementing ANTACCS.

# 1.2 STUDY OBJECTIVES AND APPROACH

There are three aspects of the study treated in this report: Technology, Methodology and Integration. Technology deals with the techniques and embodiments - both hardware and software--for implementing data processing functions. Methodology deals with the techniques for the design, evaluation, and synthesis of equipments of all levels within the system as well as the management techniques for accomplishment of an operational system.

The principal objective of the integration subtask is to illustrate technology and methodology by developing certain approaches to the design of various portions of ANTACCS, as prescribed by the requirements developed by BAARINC. It is visualized that this subtask will analyze and evaluate synthesized system components at various levels, thus illustrating how the various aspects of technology and methodology are unified and integrated into usable concepts.

The objectives of the ANTACCS project are visualized to the the following:

- To identify, analyze and evaluate hardware and software techniques of potential use in ANTACCS.

- To develop resource information and to provide reference documentation representing information of use to future Naval command and control system planners.

- To supply a unifying force to integrate the concepts developed or available in technology and methodology.

- To develop approaches to a number of candidate systems which illustrate, in a practical way, techniques of technology and methodology in ANTACCS.

The information developed in this project can be used in a number of ways:

- 1) As reference documentation.

- 2) To identify research and development needs for future system implementation.

- 3) As a specific guide to planners of future systems.

# 1.3 REPORT ORGANIZATION

The principal organization of this report is a division of the presentation into the three main efforts: technology, methodology and integration. Section 2 covers technology. The following items are covered: displays, input/output devices, memories, components and packaging, packaging techniques, advanced usage techniques and machine system organization.

In each portion of the technology there is first a classification of the techniques. Next, the sources of information are discussed and presented. This refers to the people, companies, and the literature from which information was obtained. The characteristics appropriate for ANTACCS are discussed, the application of the technology in the Naval environment is further presented, as well as a review of the current status of the equipments and techniques. Following this, the availability of technology in the 1975 era, the limitations of the present and planned technology and the recommended developments for the future are presented. Each portion is concluded with a discussion of evaluation criteria, conclusions and recommendations. Although the specific sections may deviate from this order in certain instances, in general in each section there is an attempt to cover all of these points.

Section 3 deals with methodology. For the purposes of project organization, methodology has been split into three major areas: general methodology, implementation procedures, and specific methodology. General methodology deals with:

- Tools and techniques which the system designer has at his disposal.

- A methodology generally or universally applicable and not necessarily restricted to systems of a special purpose nature or a special class.

- A methodology which is generally available, exists as a tool, and can be readily applied.

Implementation procedure deals with the understanding of tasks - both technical and managerial - which must be accomplished in the implementation of modern command and control systems. Specific methodology relates to the special requirements of selected equipment configurations and design problems which might arise in ANTACCS.

In general, the elements discussed above under technology with regard to classification, sources, requirements, status, limitations, evaluations, developments, conclusions and recommendations are covered in each methodology section. Under general methodology simulation languages and techniques of simulation are covered in some detail. Under implementation procedures, system design, implementation and evolutionary aspects of systems have been described. In specific methodology some quantitative design tools are presented.

In the section on integration the scope and objectives of integration are first discussed. Following this there is a comparison of implications of alternate system operating concepts. This concerns the various operational philosophies which the Navy might adopt relating to the structure and organization of the various tasks to be performed and involving such aspects as platforms, missions and command structures. Following this there is a discussion of the synthesis and evaluation of a system node. This illustrates how the information developed under requirements with regard to system technical functions can be translated into data processing functions. A matrix technique is described which relates platforms together with their missions and command levels, to operational tasks and data processing tasks.

Included in each section is an extensive bibliography. Generally, in the text reference is made at appropriate points to items in the bibliography. Also, at the close there is a general bibliography for the entire project effort.

1-6

(In the future final report there will be certain additions and modifications to the organization described above. For instance, in the final report there will be an extensive list of opinions, conclusions and recommendations for the entire project effort and for the various tasks. There will also be a cross reference index to assist the reader in finding his way through the technical information. Another item to be added in the final version is an extensive glossary of terms.)

#### 2. TECHNOLOGY

### 2.1 GENERAL AND INTRODUCTORY

`

The purpose of this study of present and advanced technology is to identify, analyze, evaluate and document those areas of technology which will have significant impact on future Navy tactical data systems. This study will probably not uncover any new areas of technology or disclose any new areas of application to the experienced system designer. It will, however, provide analyses which will place the new technologies in proper perspective and provide criteria and examples to aid in evaluating and selecting future equipment.

As the first phase of this study is necessarily devoted to the collection of information and the analysis of that information, rather than its evaluation and documentation, it follows that little completed work is available to include in this report.

It is, therefore, intended that this section should indicate those areas in which progress has been made and show the type of work being done, rather than present some small sample of the finished product.

2-1

### 2.2 DISPLAY TECHNOLOGY

# 2.2.1 Classification of Display Types

Display types can be classified in a number of different ways that are not mutually exclusive. Associated groupings of display technology will vary with the method of classification. Among the ways in which displays can be classified are:

| 1) | Functional                        | Console                                                                                                                                                                                              |

|----|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                   | Large-Screen                                                                                                                                                                                         |

| 2) | Nature of Data to<br>be presented | Status Displays<br>Real-time or Dynamic Displays                                                                                                                                                     |

| 3) | Type of Data                      | Alphanumeric<br>Symbols<br>Graphical                                                                                                                                                                 |

| 4) | Type of Mechanization             | Cathode ray tube<br>Electroluminescent<br>Character lights<br>Photographic Projection<br>Light-valve<br>Mechanical Inscriber<br>Photochromic<br>Ferro-electric<br>Opto-Magnetic<br>Laser-luminescent |

In this report, displays will be classified by the type of mechanization. In the discussion of each type of display that has been investigated to date, the functional use and the nature and type of data to which it is adaptable will be considered. Any factors that make a particular type of display unsuitable for a certain function or for certain kinds of data will also be noted. For example, the fact that a cathode ray tube is not suitable for a large-screen display, or the fact that a photographic projection type, large-screen, display cannot present real-time dynamic information, will be discussed as limitations of these techniques that make them unsuitable for certain functional uses and for certain types of data.

# 2.2.2 Sources of Information

# 2.2.2.1 People and Organizations

The following lists the companies and governmental agencies with whom displays have been discussed during this study, and the type of displays discussed with each.

| 1) | Bunker-Ramo Corporation<br>Canoga Park, California            | Light-valve displays<br>Continuous-strip photographic<br>projection displays<br>CRT displays                                 |

|----|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 2) | General Dynamics/Electronics<br>San Diego, California         | Charactron CRT displays<br>Light-valve displays                                                                              |

| 3) | General Telephone Laboratories<br>Bayside, Long Island, N. Y. | Continuous-sheet electroluminescent<br>displays with XY matrix addressing<br>Acoustic/electroluminescent<br>displays         |

| 4) | RCA Laboratories<br>Princeton, New Jersey                     | Ferroelectric displays                                                                                                       |

| 5) | Laboratory for Electronics<br>Boston, Mass.                   | Magnetic thin-film displays                                                                                                  |

| 6) | NCR<br>El Segundo, California                                 | Electro-mechanical photochromic<br>displays<br>CRT-Photochromic projection<br>displays                                       |

| 7) | Sylvania<br>Waltham, Mass.                                    | Discrete alphanumeric character<br>displays<br>Continuous-sheet electro-<br>luminescent displays with XY<br>matrix selection |

| 8) | Stanford Research Institute<br>Menlo Park, California         | Magnetic thin-film displays<br>Modulated crystal filter<br>displays                                                          |

| 9)  | Rome Air Development Center<br>Rome, New York | Light-valve displays                               |  |

|-----|-----------------------------------------------|----------------------------------------------------|--|

|     |                                               | Modulated crystal interference-<br>filter displays |  |

|     |                                               | Thermo-plastic displays                            |  |

|     |                                               | Laser displays                                     |  |

|     |                                               |                                                    |  |

| 10) | USAER&DL<br>Fort Monmouth, New Jersey         | Photochromic displays                              |  |

|     |                                               | Laser-luminescent displays                         |  |

|     |                                               | Fiber-optic CRT displays                           |  |

|     |                                               | Photographic projection displays                   |  |

|     |                                               | Display memories                                   |  |

| 11) | U.S. Navy Bureau of Ships<br>Washington, D.C. | Photographic projection displays<br>CRT displays   |  |

Much of the information presented in subsequent portions of this section are based on discussions with display experts in the organizations listed above. Their descriptions of specific display techniques and their opinions of the advantages, disadvantages, and limitations of display techniques were relied upon heavily in the preparation of this report.

# 2.2.2.2 Literature

An extensive list of references pertinent to the study of display technology are given in the Bibliography. To date, only a few of these have been studied in detail. Some of the material in this section has been extracted from these references. The more important and pertinent of these references will be studied in detail during the remainder of this study and new references will be added to the Bibliography to reflect material published or discovered subsequent to the preparation of this report.

### 2.2.3 Display Characteristics for ANTACCS

The display characteristics required for ANTACCS cannot be fully identified at this time since the results of the requirements analysis have not been available. However, it is anticipated that both console and large-screen displays will be required; that alphanumeric, graphical, and dynamic real-time data must be presented; and that multi-color displays (particularly for large-screen applications) will be required. It is further believed that electro-mechanical display systems and photographic projection systems will not be acceptable for a 1970 system.

The analysis of display technology and the information presented in the final report will permit the selection of display technologies with the appropriate characteristics for any functional use in an NTDS or MTDS system. This analysis will include all the more important and feasible types of displays that might be applicable to such systems in 1970.

# 2.2.4 Applications of Displays in the Naval Environment

It is anticipated that applications of displays for shipboard and ground-based military environments in the 1970 era will include console and large-screen presentation of both status information and real-time dynamic information such as target track data. The applicability of specific types of displays to different applications will be considered in further detail in the remainder of this study.

## 2.2.5 Current Status Review

The investigation of new display technology has not progressed as far at this point in the study as that of some other areas, such as, for example, memory technology. The information collected to date is summarized here, but comparisons and evaluations of different types of displays are not yet available. Detailed comparisons of specific existing display devices were presented and discussed in the initial proposal for this study. Although these are available, they are not included in this report since they are representative of past technology rather than that to be anticipated for the 1970 era. Since a number of satisfactory techniques for console type displays are now available, there will be no problem with respect to the availability of console type displays for a 1970 system. Existing cathode ray tube technology and anticipated improvements in this technology should meet all requirements for small-screen console type displays, even if none of the new technologies prove to be superior. However, with respect to

\* References are listed at the end of each subsection.

large-screen displays the situation is much less favorable. In an RADC Technical Documentary Report<sup>3</sup> published in 1962, the state-of-the-art and development efforts for large screen displays were described as follows:

"Display developments are being undertaken in three major technological areas. These areas may be differentiated in terms of the basic processes being applied and on the basis of development time required to provide fully operational subsystems.

The first of these processes is based on projection and employs a stable light modulator, such as film or selenium plate, to provide the display. Operational subsystems of this sort are considered to be achievable within months.

The second process, the light valve, in theory should provide adequate performance for systems applications, and it has the dual advantages of operation at electronic speeds and of the elimination of expensive film. However, the performance potentials have not been realized in practice, and major technological improvements must be made before the light valve can be useful for most systems applications. The presently available models exhibit major weaknesses in their capability to provide high resolution and brightness.

This low brightness makes it impossible to use the light valve in the high-ambient lighting conditions of most of the systems. The interactions of the oil film and the lens systems are such that it is not possible to increase the display brightness level without major improvements in the characteristics of the modulation surface. Improvement, very likely, is contingent on the development of suitable thermoplastic materials. Light valve techniques show considerable promise, and with suitable development may eventually supersede film systems. However, it should be clearly recognized that full realization of the light valve's potential may require years of additional research.

The third process, electroluminescence, does not require projection since the display surface itself acts both as light source and modulator. Only small laboratory devices for demonstration and experimentation are available at the present time. Electroluminescence is appealing in its apparent simplicity, its capability to eliminate projection, and its characteristic of non-catastrophic failure. In addition, there is a potential for full color operation at high brightness levels, and the large surface reduces the problems of obtaining high resolution. Unfortunately, there is an impressive number of technical obstacles that must be overcome before electroluminescent devices can meet the requirements of the systems. The most immediate problem is that of modulating the display surface, and a number of promising efforts are underway in this area at the present time. This effort is concurrent with others that are aimed at the development and application of new phosphors to obtain high brightness levels and multiple colors. However, even allowing for impressive technological improvements, years will be required to advance the capability of electroluminescent displays to the point where they can serve as dynamic large scale displays for system applications.

Desirable as these advanced displays are, most immediate requirements of Command and Control Systems can only be met by projection techniques using film or xerographic techniques for light modulation."

Unfortunately, developments during the past two years have not significantly altered the views quoted above, except that improved technologies are of course somewhat closer to realization now than they were in 1962.

Photographic projection techniques are still the only feasible means of meeting operational requirements for large-screen displays in Command and Control Systems. Significant progress has been made in light-valve type displays during the last two years, but the reliability and life of these devices does not permit their use at this time in an operational system in which minimum down time is an important requirement. However, new and improved light-valve type devices offer great promise for a system to be operational in 1970.

Display techniques that have been developed or that appear promising for the future include individual character lights, cathode ray tubes, mechanical inscriber systems, film or photographic projection systems, light-valves, photochromic systems, electroluminescent devices, ferroelectric devices, opto-magnetic devices, and laser systems. Of the above techniques, it is believed that mechanical inscriber systems and film and photographic projection systems will be obsolete by 1970. Improved light-valves, electroluminescent panels, photochromic displays and, possibly, laserluminescent displays appear very promising for that time period. The display technologies that have been investigated to date are discussed briefly in the following parts of this section.

# 2.2.5.1 Mechanical Inscribing Machine

A mechanical inscribing system permits the large-screen display of real-time dynamic information at a relatively slow rate<sup>4</sup>. In this type of display, a glass slide coated with an opaque material is inserted into a projection system. Another glass plate with a stylus mounted in its center is positioned parallel to the first slide so that tipping the glass plate causes the stylus to penetrate the opaque material. When the stylus is moved in the X and Y directions by a servo-mechanism under the control of external signals, a trace is inscribed in the opaque material on the face of the slide. The light from a lamp is projected through this trace on the glass slide and focused on a projection screen. Thus, the trace will appear on the screen and can be drawn in real-time.

The use of color filters in the light path permits color traces to be generated. A composite multi-input or multi-color display can be generated by superimposing the images from several projection systems. Additional projectors can be used to superimpose static information, such as maps, on the dynamic information. Since the inscribed trace remains on the glass slide, no external memory is required for this type of display.

With a trace width of 0.001 inches on the slide, the projected trace will be about 0.1% of the screen size. Recent systems require approximately 50 milliseconds to inscribe a trace across the full width of the screen. Alphanumeric characters can be inscribed at a rate of approximately 20 characters per second.

# 2.2.5.2 Charactron Shaped-Beam Cathode Ray Tube

The Charactron is basically a cathode ray tube which includes a character generating mask and the necessary electrodes for shaping the beam inside the tube<sup>5</sup>. The electron beam is deflected to the proper position in the character mask corresponding to the character to be generated. As the beam passes through the mask, it is extruded into the shape of the character. The shaped beam is then returned to the axis of the tube by deflection electrodes and deflected to the desired position on the face of the tube.

Random display rates of 50,000 characters per second are possible with this technique. The limiting factor is the time required to position the character on the face of the tube rather than the time required to shape the beam. The Charactron tube is not limited to the generation of alphanumeric characters but can also generate any symbol fabricated in the mask. A typical mask has 64 different characters or symbols, but 144 symbol masks have been used, and several hundred are considered possible.

The Charactron is claimed to have three major advantages over the stroke or dot matrix method of symbol generation:

- 1) Reliability

- 2) Legibility or definition

- 3) System complexity

Since the charactron is basically a cathode ray tube, it can be operated as a conventional cathode ray tube to generate graphical data and target traces in real time. Any shape and size of symbol can be chosen since this is a function of the fabrication of the mask. Charactron tubes are useful for image generation in photographic projection systems for large-screen displays as well as for direct viewing in console displays. Recent development permits the simultaneous generation of alphanumeric and real-time video information by the use of two electron guns in the tube. Another recent development provides a rear window in the tube so that a photographic image can be projected through the window and superimposed on the face of the tube with the electronically generated picture. Fiber-optic face plates have been used to avoid parallax by bringing the image from the inner surface to the outer surface of the tube. Large-screen display systems based on projection of photographic images have been used in a number of existing Command and Control Systems and several specific systems have been described in the literature<sup>6,7,8</sup>. In essence, these systems involve:

- A symbol generator for converting the digital information to a shaped symbol or character on the face of the CRT

- 2) An image generator for positioning the symbols and generating graphical data on the face of the CRT

- Processing equipment for exposing film to the image on the CRT, for developing the film, and, if necessary, for making prints

- 4) Slide or film storage and selection equipment for storing the film images and making them available upon call

- 5) A projector and screen for projecting and displaying the selected image.

Usually, a multiple projection system is used to permit the simultaneous projection and superimposing of multiple images to generate multi-color displays or to superimpose multiple overlays over a map background. Systems that superimpose three or four independently selected images encounter difficult registration problems in the final projected display. Other systems that contain the multiple images on a single film chip overcome the registration problem, but the image size is reduced and flexibility in selecting the combination of images to be displayed simultaneously is lost. A more recent development proposes the use of a lenticular type film in which three separate color images are contained on the same film image. A number of the photographic projection systems in current use employ discrete slides as described above, but a few use a continuous film strip to provide more rapid updating of the display and to permit a simpler mechanical system than one in which individual slides are selected independently. The flexibility offered by random slide selection is sacrificed. The continuous film strip type projection system is more suitable to rapid updating of pseudo-real-time displays where the same type of information is displayed continuously but updated rapidly. The individual slide approach is more suitable to situation displays where a large number of different kinds of situations or pictorial combinations are available, any of which may be required at a given time and in any sequence.

The photographic projection type systems are currently the most practical solution to a large-screen display where continuous operation is required. However, because of the relatively slow response time, the inability to display dynamic information, and the mechanical equipment involved, this is not a desirable long range solution. It is believed that this type of system will be obsolete before the 1970 period and should not be considered for a 1970 system.

## 2.2.5.4 Photochromic Display Systems

The use of photochromic materials offers considerable promise for future display systems<sup>9</sup>. Photochromic materials are organic dyes which become opaque when exposed to ultraviolet light, and return to the transparent state when exposed to heat or infrared light. By coating a transparent film with a thin layer of photochromic material, a "photographic" type media can be produced in which the chemical process is reversible. An image can be exposed with ultraviolet light and erased with infrared light.

2-11

The exposed image will decay at room temperature at rates depending upon the particular chemical compound. Typical persistency times for photochromic materials used in display systems range from approximately 2 seconds to 15 minutes. Faster decay times can be obtained but this is usually not desirable for display purposes. Achieving longer persistence times would probably require cooling the image since the photochromic decay is inhibited by cold temperatures.

Photochromic materials exhibit a fatique characteristic at present, after a few hundred cycles of a particular spot. Red, blue, or green colors can be obtained with a resolving power capability in excess of 1,000 lines per millimeter. The sensitivity varies with the photochromic material but is about 1/3-watt-second per square centimeter. The persistency of the image can be controlled by varying the temperature, the material, or the method of applying the material to the base. The earlier photochromic display systems generated a dynamic display by focusing an ultraviolet light through a lens system onto a photochromic film; the ultraviolet light being mechanically positioned by a servo-mechanism. Since the photochromic material becomes opaque at the point at which the ultraviolet strikes, projection type displays can be generated by inserting the photochromic material between the lamp and the lens of a projection system. Moving the lens through which the ultraviolet light is focused causes the opaque spot on the photochromic film to move, generating a dynamic display on the screen. Shining an ultraviolet light beam through a character-matrix mask permits the generation of alphanumeric characters on the display screen. Special symbols can be generated in a similar manner. This type of display is interesting for tracking a limited number of targets or for generating displays that change relatively slowly. However, the speed of the photochromic material and the mechanical motions involved in deflecting the ultraviolet light limit the speed of this type of device.

2-12

In a newer development, a cathode ray tube is combined with the photochromic film to permit the electronic generation of an image. In this development, a fiber-optic face plate cathode ray tube is used to generate an image on the outer surface of the face of the cathode ray tube by conventional techniques. The ultraviolet light from the phosphor on the inner surface of the face of the cathode ray tube is transmitted through the fiber-optic face plate to generate an opaque image on the photochromic film. A dichroic mirror that transmits ultraviolet light and reflects visual light is sandwiched between the fiberoptic face plate and a photochromic film. Visual light from an external source is projected through the photochromic film onto the dichroic mirror which reflects it back to a viewing screen. The opaque image on the photochromic film prevents the light from the projector from striking the dichroic mirror. Hence, this image is reflected onto the screen.

At the present time, the speed of photochromic materials limits the character generation rate to approximately 10 characters per second in this type of display. If work on faster photochromic materials is successful, this approach could provide an attractive all-electro-optical dynamic large-screen display with no mechanically moving parts. Photochromic display systems combining electronic, photochromic, and projection techniques are very promising for use in a 1970 system.

### 2.2.5.5 Light-Valve Systems

The term light-value in a generic sense refers to any system in which light passing through the system is modulated. However, the term is usually used in a narrower sense to refer to a cathode ray tube projection display system using a Schlieren optical system.

In a typical system of this type, a metallic mirror-like surface covered with a thin film of oil is placed inside an evacuated cathode ray tube type device. An electron beam is used to generate an image on the oil film. This is similar to the operation of a normal cathode ray tube except that the image is generated on the oil film rather than on a phosphor face. The electrons impinging on the oil film create electro-static forces that cause a temporary deformation of the oil film. When a high intensity light source is focused on the oil film, the light is reflected at a different angle for those areas that have been deformed by the electron beam than for the remainder of the oil film. Passing the reflected image through a ladder-like grating permits selective passing of the light, depending upon whether it was reflected from a deformed area or a non-deformed area of the oil film. Hence, the desired image is displayed on the viewing screen.

Light-valves are promising for future display systems and will probably be in widespread use in 1970. At present, they suffer from the severe disadvantage of short cathode life (20 to 200 hours MTBF). Since it is necessary to have an oil film inside the vacuum, it is difficult to maintain a good vacuum. As a result, there is a tendency for the cathode to be poisoned by evaporated oil. Light-valve systems of this type are in common use in large-screen theatre-television systems. However, these systems are operated for short periods of time for special events, and considerable time can be allotted prior to the event for bringing the system up to proper operation. Unfortunately, in the military command and control environment, the system is required to be in almost continuous operation. Another disadvantage is that multi-color displays require multiple projection units with a consequent registration problem.

Considerable development efforts are being expended toward improving the performance, reliability, and life of light-valve systems. The Rome Air Development Center, in particular, is sponsoring extensive efforts toward improving light-valve systems. It is their belief that light-valve projection systems will constitute the next generation of large-screen display systems. It is likely that projection lightvalve systems will constitute the next generation of large-screen display systems, but this is an interim solution. Such systems will probably be surpassed by other techniques for a system designed for 1970.

2-14

# 2.2.5.6 Electroluminescent Displays

The major applications of electroluminescent materials in display equipment so far have been in the form of individual character or symbol indicators<sup>11</sup>. In these devices, each character position in an alphanumeric display is represented by an electroluminescent panel which can be caused to display any one of a predetermined set of characters depending upon the electrical signals applied to the device. However, extensive research and development efforts have been devoted to the use of electroluminescent materials to fabricate a complete display screen capable of displaying graphical data as well as alphanumeric characters.

Electroluminescent displays offer the advantages of an all-solidstate display without moving parts or projection optics, a flat display requiring very little depth, and sufficient brightness for viewing under normal ambient room lighting conditions. An electroluminescent element consists of a thin layer of phosphor powder that is embedded in a dielectric medium and sandwiched between two parallel plate electrodes, one of which is transparent. The application of an alternating voltage to the electrodes causes the phosphor to emit light.

Aside from the discrete character display, the electroluminescent display which has been developed further than others to date has been the electroluminescent crossed grid display<sup>12</sup>. This display uses a continuous electroluminescent sheet with the electrodes on one surface subdivided into parallel strips in the X direction and with the electrodes on the other surface subdivided into parallel strips in the Y direction. Applying excitation to an X and a Y strip will cause the electroluminescent material to emit light at the intersection. In this XY selection, each wire carries approximately one-half the

voltage necessary to excite the electroluminescent material so that full excitation voltage occurs only at the intersection. A continuous sheet of non-linear resistor material is coated on the electroluminescent material between two sets of electrodes to avoid partial excitation and partial light at points along the selected X and Y strips other than the point of intersection.

This approach is useful for a large-screen or console type display. Real-time dynamic displays, such as target tracks, can be generated by properly sequencing the selection of X and Y grids. Alphanumeric characters and symbols can be drawn on the same display. However, it is necessary to regenerate each spot on the display periodically since it has no storage characteristic. As a result, this type of display requires either an external storage or computer controlled regeneration. To avoid noticeable flicker, the picture must be regenerated at least 30 times per second. The frame rate of 30 per second, and the fact that 1 - 5 microseconds are required to energize each spot on the display, limit the total number of positions that can be activated. Periodic action is required for active spots that remain static as well as for those that are changing.

One display of this type provides a 256 x 256 matrix in a 16 x 16 inch display panel. This display panel is  $3\frac{1}{2}$  inches thick. The spot size is approximately 1/10 of an inch. It is expected that spot sizes of 1/40 to 1/50 of an inch are realizable in the near future, and that 1/100 of an inch is feasible.

In another type of electroluminescent display, a continuous sheet of electroluminescent material is deposited over a sheet of piezo-electric ceramic<sup>13</sup>. With the proper voltage applied to the electroluminescent material, a mechanical shock wave travelling through the piezo-electric ceramic can generate sufficient voltage to energize the electroluminescent material in the vicinity of the shock wave. Introducing

2-16

a shock wave to one edge of the ceramic causes a light signal to propagate across the electroluminescent material as the shock wave propagates across the ceramic beneath it. A reduced shock wave on one edge, combined with a shock wave on a perpendicular edge, can cause a point of light corresponding to the intersection of the two wave motions to propagate across the display. A non-linear resistor material is again used to suppress partial excitation. Controlling the time of the two shock waves provides the ability to position the spot of light as it moves.

A third approach to electroluminescent displays can provide a dynamic large-screen display that does not require periodic regeneration. In this approach, the display screen is fabricated with a matrix of discrete electroluminescent elements, each having an associated storage element. An XY selection matrix is used to energize a specific electroluminescent element. The associated storage element then maintains the electroluminescent element in that state until it is cut off by another XY selection operation. At present, the addressing rate is limited to a switch-on time of approximately 10 microseconds per element. The switch-off time is approximately 30 microseconds, but it is not necessary to maintain the electrical signal for this length of time. It is anticipated that the switch-on time can be reduced to 5 microseconds in the near future. Resolving powers of 10 lines per inch can be realized now with 6 - 20 lines per inch considered feasible in 1970.

This approach provides a true dynamic large-screen display with exact registration and positioning without mechanically moving parts and without an optical projection system. Since the individual storage elements eliminate the necessity for periodically regenerating the picture, only those elements that change must be activated and energized or de-energized.

A multi-color display would be difficult but is conceivable by segmenting each element of the display into three elements corresponding to a three color system. This type of display would be quite expensive due to the electronic selection of individual elements and the electronic storage associated with each element. However, it is a practical display in that a dynamic large-screen display of this type can be built in a relatively short time with a high assurance of success. Future developments in integrated circuit techniques may lower the cost of the electronic elements sufficiently to make this approach attractive for a 1970 system.

### 2.2.5.7 Opto-Magnetic Displays

A different approach to solid-state displays is based on the magnetic properties of certain thin-film materials that affect their reflection of light. If a thin-film of magnetic material of this type is deposited on a substrate, areas that have been magnetized will reflect light in a different way than other areas of the film. An XY matrix selection can be used to generate a magnetic image on the surface. If a high intensity light is projected on the magnetic film, a visual image will appear as the result of the effect of the magnetic image on the reflection of the light.

Contrast ratios of 75 to 1 have been obtained, providing a good display under normal ambient light conditions. Only a few percent of the incident light is reflected. Resolutions in the order of 5 mils have been obtained in the laboratory. The intensity varies with the viewing angle but there is very little variation within angles of approximately  $90^{\circ}$ .

This is an interesting approach to a dynamic large-screen display, but it is too early in the development stage to determine with confidence whether it will be available and feasible for a 1970 system.

# 2.2.5.8 Crystal Light Modulators

A projection display device using a birefringent KDP crystal element has been proposed <sup>14</sup>. An electron beam in a cathode ray tube is used to control the passage of light through a KDP crystal in the face of the tube. This permits a system in which a polarized light is projected through a rear window in a cathode ray tube and then through

the crystal modulating element in the face of the tube and onto a screen. The electron gun in the cathode ray tube generates an image on the crystal modulator, the polarized light passing through the modulator then projects this image onto the screen. This approach is being followed with interest, but there is no indication at this time as to whether it will be feasible for a 1970 system.

## 2.2.5.9 Laser Luminescent Display Systems

Conceptually, a large-screen display can be generated by writing on a luminescent screen with a laser beam. This would be somewhat equivalent to an "outdoor" cathode ray tube in which the laser beam replaces the electron beam and the luminescent screen replaces the phosphor coating and the face plate of the tube. This approach would offer an advantage over a cathode ray tube in that a vacuum is not required and a large-screen image can be generated directly. The difficulty lies in the deflection of the laser beam. However, a number of development efforts have been aimed at this problem with some laboratory success<sup>15</sup>. An operational system of this type may not be developed by 1970, but it offers long range promise. Continuing efforts in the development of improved lasers and advances in the ability to deflect laser beams will contribute directly to the ultimate success of this type of display.

# 2.2.6 Display Availability in the 1970-80 Period

The investigation of display systems has not progressed far enough at this point of the study to permit a complete determination of the availability of different types of display systems in 1970. From the investigations to date, it is believed that film-based photographic projection systems and mechanical inscribers will be obsolete. Lightvalve projection systems will be in widespread use but may be phasing out by 1970. Cathode ray tubes will continue to be a dominant factor in the generation of displays and in console viewing screens. Electroluminescent and photochromic systems offer promise for 1970-80 systems. Ferroelectric and opto-magnetic displays offer possibilities depending upon the success of current development efforts. Laser display systems appear to offer great promise but significant research and development efforts are required.

#### 2.2.7 Limitations of Present and Planned Displays

Most of the present large-screen displays are limited by the use of electro-mechanical film based projection systems. Photochromic and electroluminescent displays are currently limited by the rate at which individual positions can be altered. Light-valve systems are limited by short cathode life. It is not possible at this point of the investigation to discuss the limitations of future display systems.

#### 2.2.8 Recommended Developments to Meet ANTACCS Needs

Development efforts sponsored by the Navy to meet ANTACCS needs for the 1970-80 period should be concentrated on solid-state techniques that are adaptable to both fabrication methods. Electroluminescent, opto-magnetic and laser displays appear to be the most fruitful areas for development efforts pointed toward the 1970-80 period.

## 2.2.9 The Evaluation Criteria Recommended

Characteristics and parameters to be considered in evaluating display systems should include the following:

Display technique Display media Console or large-screen Static or dynamic Hard copy Legibility Color Brightness Screen Size Resolution Frame generation rate Response time Character generation rate Character generation technique Image storage capability Image storage method Storage and regeneration requirement Capacity

Character repertoire Character size Symbol shapes Accuracy of position Registration Stability Color capability Contrast Image quality Optical quality Processing requirements (if any) Image handling requirements Accessability Background illumination permissible Viewing distance Physical space requirements Weight Power Requirements

It will not be necessary to make detailed comparisons and evaluations of each of these characteristics since many of them are common to most display types. Such characteristics would be used to rule out a limited number of displays that do not posses the characteristic. Other characteristics might be common for most displays but a unique property of a specific display technique could enhance this characteristic to offer a strong advantage to that technique. Those characteristics that vary significantly from display to display, but within acceptable limits, will be compared to permit evaluation of the characteristics of acceptable display technologies.

## 2.2.10 Conclusions and Recommendations

Only brief preliminary conclusions and recommendations can be made at this time. Emphasis should be placed on the development and use of solid-state displays that do not require periodic regeneration and on batch-fabrication of display screens and arrays.

#### References: Displays, Section 2.2

- 1 "Physical Principles of Displays Classification," H. G. Talmadge, Jr., <u>Electronic Information Display Systems</u>, Spartan Books, Washington, DC, 1963, pp. 69-86

- 2 "Cathode-Ray Tubes," F. R. Darne, <u>Electronic Information Display</u> Systems, Spartan Books, Washington, DC, 1963, pp 87-109

- 3 "Criteria for Group Display Chains for the 1962-65 Time Period," Technical Documentary Report No. RADC-TDR-62-315, Rome Air Development Center, July 1962, pp 1-2

- 4 "A Synopsis of the State of the Art of Dynamic Plotting Projection Displays," R. Anderson, Second National Symposium of the Society for Information Display, New York, October 1963

- 5 "Advanced Display Techniques Through the Charactron Shaped Beam Tube," J. H. Redman, Society for Information Display Symposium, March 1963

- 6 "Colordata Display" Hughes Aircraft Co. Brochure, Fullerton, California, 1963

- 7 "Artoc Displays," R. T. Loewe, <u>Electronic Information Display</u> <u>Systems</u>, Spartan Books, Washington, DC., 1963, pp 231-246

- 8 "DODDAC An Integrated System for Data Processing Interrogation and Display," W. F. Bauer and W. L. Frank, Proceedings EJCC, Washington DC, December 1961

- 9 "Photochromic Dynamic Display," E. J. Haley, <u>Electronic Information</u> Display System, Spartan Books, Washington, D.C., 1963, pp 110-120

- 10 "Epic Display", H. L. Bjelland, Proceedings 3rd National Symposium on Information Display, San Diego, Calif., February 1964, pp 286 - 299

- 11 "Display Applications of Electroluminescence," M. S. Wasserman, Electronic Information Display Systems, Spartan Books, Washington DC, 1963, pp 121-125

- 12 "Non Linear Resistors Enhance Display Panel Contract," H. G. Blank, J. A. O'Connell, and M. S. Wasserman, <u>Electronics</u>, August 3, 1963

- 13 "Solid State Display Device," Stephen Yardo, Proceedings of the IRE, December 1962

- 14 "Solid Crystal Modulates Light Beams," E. Lindberg, <u>Electronics</u>, Vol 36, No. 51, December 20, 1963, pp 58-51

- 15 "A Fast, Digital-Indexed Light Deflector," W. Kulcke, T. Harris, K. Kosanke, and E. Max, <u>IBM Journal</u>, of R & D, Vol 8, No. 1, Jan 1964, pp 64-67

## 2.3 DISPLAYS--USER TECHNOLOGY AND SOFTWARE

# 2.3.1 Introduction

## 2.3.1.1 Objective

Real time data processing systems have become an important point of interest. The development of digital transmission systems and the availability of bulk data storage devices have stimulated the use of on-line systems in which information is entered into the data processor <u>as it is generated</u>, and outputs are requested from the computer <u>as they are required</u>, and in fact limited to that information needed at the moment. The on-line concept established a requirement for an intimate relationship between man and computer--one in which not only the characteristics of the computer are important, but where equal concern must be given the communication devices by which man interacts with the system. This study is concerned withthe application of on-line displays to military command and control.

# 2.3.1.2 Historical Review and Perspective

Perhaps one of the first display devices associated with a computer system was the simple cathode ray tube (CRT) display. For example, such a device was available in 1953 on the ILLIAC (University of Illinois) computer where two tubes were driven in parallel. One CRT was mounted for visual observation whereas the second was associated with a camera capable of photographing the computer generated display. The computer controlled the film advance. While the primary use of this device was the rapid generation of graphic information, another use was the on-line monitoring of the progress of a calculation by the programmer. By appropriate displays, he was able to detect programming errors or, during production runs, make better initial guesses during iterative procedures or parameter studies. This was perhaps one of the first on-line display devices. It is important to define what constitutes an on-line display device. From many points of view, all of the following can be considered as display devices:

> Typewriter Plotter Printer Closed circuit TV Document viewers CRT consoles

For purposes of this investigation, however, we limit considerations to essentially two types of devices, the single operator console and the group display. These must satisfy the following criteria:

- 1) Directly tieable to data processing system.

- 2) Ability to initiate messages or control signals from a data entry keyboard or switches for transmission to the computer.

- 3) Ability to receive messages or control signals from the computer and display them to the operator or viewer.

"Off-line" devices are included if they receive information which is computer generated. Conventional printing and plotting equipment, however, are excluded. So are document viewing devices associated with the information retrieval problem. These devices generally operate on reference libraries and not on digitized data.

Based on the above, the typewriter station, the keyboard with CRT console and the large screen viewing system are the basic items applicable to this study.

2.3.1.3 Typical Systems and Operating Modes

# SAGE

Perhaps the first, or at least most well-known display system was that associated with the SAGE System. The operating principle in SAGE Direction Centers is the interplay of man and computers via display consoles for the purposes of making a composite number of simple decisions concerning the air threat at any instant in time. To do this, geographic information is presented by the computer to the console operator on a volatile CRT screen, and the human responds to the machine by operating a light gun and button keyboard. Alarms

,'

and alerts, in both audible and visual form, are available. In a typical center, there are close to one hundred consoles. Depending upon the function, the console features differ from one another, there being over a dozen "special purpose" configurations. Operating characteristics have been cited where the computer reads up to 5000 console switch actions every 2.5 seconds. During this period, 200 different displays may be generated consisting of 20,000 characters, 18,000 points and 5000 lines.

Typically, a console has a 19 inch Charactron tube and a 9 inch Digitron tube manufactured by General Dynamics/Electronics and Hughes respectively. The larger scope is used as a situation display capable of showing alphanumeric characters and lines, whereas the small CRT is a data summary display capable of only alphanumeric information. Whereas the former leads to considerable flicker to the casual observer, it is maintained that operational personnel who are subject to a special environment of blue light find no problem in working with the displayed information.

In the SAGE System, on-line devices first came to be used on a large scale. The significant application principle here is the use of the console in the area of computer assistance where human judgment can be applied.

## NORAD

Another area of interest in the application of display techniques and devices is NORAD.

The current NORAD Complex at Colorado Springs (apart from the plans of 425L) include two major installations, the Space Detection and Tracking System (SPADATS) and the Combat Operation Center (COC). The display devices and techniques used here are:

- b) Tote board presenting tabular information of all space vehicles currently in orbit. Manual updating of perigee, apogee, period, etc. is performed daily.

- c) Closed circuit Wollensak TV for transmitting parts of the display on the tote board to other operation rooms.

- COC a) Large screen of the North American continent capable of showing tracks. This system uses the Iconorama projection system which automatically updates film chips from tele-type messages.

- b) Smaller screen devoted to showing the BMEW's system on a map background of the Arctic region.

- c) Weapon Status Board registers which display the status of forces.

Of considerable interest here is the Iconorama system which is perhaps the first on-line, multi-color, group display system to be installed. The NORAD System generates information which can be displayed in the following additional sites:

Joint War Room, Pentagon Air Force Command Post, Pentagon SAC Command Post, Offutt Field Canadian Joint Chiefs of Staff National Resource Evaluation Center

## Air Force Command Post

The display activity to data at the Air Force Command Post has been limited to several rear projection screens capable of showing slides and films. Perhaps the most dynamic display is the Iconorama System which is fed by NORAD. In addition, there are status boards exhibiting the defense conditions (DEFCON). Also there is a Bomb Alarm display which consists of a map of the United States consisting of colored regional blocks. Upon an indicator going off, an appropriate light goes on behind the map and lights up the endangered area. During the spring of 1962, this system was augmented by the first stage of the 473L program called the Operational and Training Capability (OTC) phase. This was implemented by IBM Federal Systems Division by the Introduction of the IBM 1401/1405 (disc) systems together with the DC400B/DIB display and interrogation system of Thompson Ramo Wooldridge.

The latter system consisted of two RW consoles having single 10-inch CRT displays together with a sophisticated keyboard. Of these, one console was a remnant of earlier equipment while the second console was a newly manufactured copy. Both consoles were interfaced with the 1401 by use of a Display Interface Buffer which is a core storage device. These consoles were to be used in the Command post by placing them at the disposal of the various area desks as an on-line tool for information retrieval and analysis. The following functions were selected for this initial application:

> Emergency Actions Defcon Actions Plan Abstracts Flight Following Status of Forces Airfield Facilities Aircraft and Missile Characteristics

The purpose of the OTC was twofold: to achieve some automated capability rapidly; and to experiment with equipment and techniques in anticipation of the next phase of 473L development. The latter point motivated the interest in on-line display devices so that experience would be obtained for design of the Interim Operational Capability.

4) Defense Communication Agency: Defense National Communication Control Center

The Defense National Communications Control Center (DNCCC) is the focal point for the controlling and supervising function of the Defense Communication Agency over the Defense Communication System. The latter encompasses all of the telecommunication requirements for the Department of Defense. The basic function of the DNCCC is the maintenance of world-wide communication traffic status. In this capacity three basic on-line displays are generated to show operational conditions; traffic status, system status and read-out panel. These displays are computer driven, wall-lined panels. The first two are static in composition, that is, they are fixed format displays on which status is demonstrable by the manipulation of colored lights as generated by the Philco 2000 computer system.

The System Status panel is an 8 ft. x 15 ft. map of the world on which are etched major trunk lines and system relay stations for which the back lighting can be red, green or yellow.

Another panel is the Traffic Status Board which is an 8 ft. square display. It consists of four bays of nine columns each, showing station backlog status by use of coded illuminators opposite each identified station.

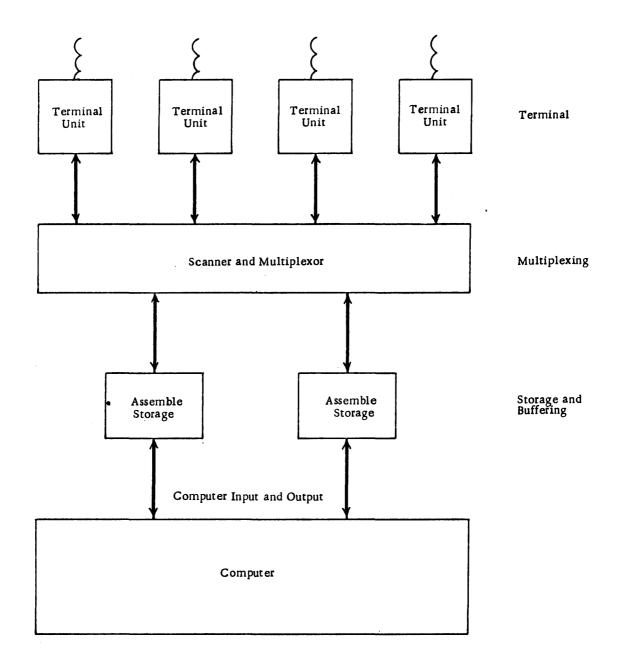

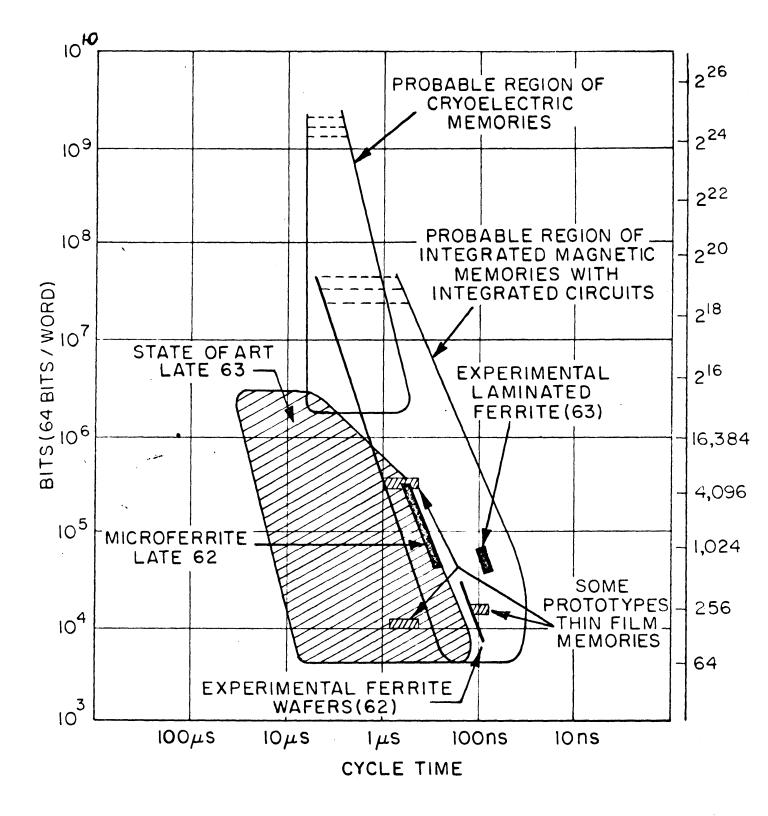

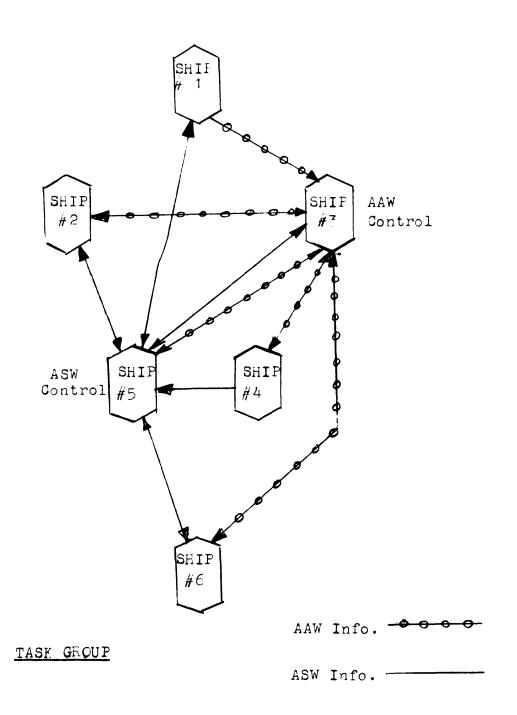

Finally there is a readout panel which is a 7 ft. square rear projection display. This display can present tabular and textual information generated by the computer as a result of an inquiry. The process incorporates a modified Anelex High Speed Printer which generates text on special material from which a film transparency is generated by non-chemical means. This film is sequentially added to and is, therefore, spool fed and wound with 70 characters per line at 100 lines per minute. The letter image is 1 inch high, and is large enough to be read at 25 ft. distance in a room with ambient lighting of 25 ft. lamberts.