# Quality Software Design

## SOFTWARE DESIGN GUIDES

- **OVERVIEW** This guide describes the design of high quality software for embedded systems. The intent is to promote well-founded, justified designs and confidence in their operation. It provides guides, checklists and templates.

- BENEFITS Improve the quality of source code: its maintainability, testability, etc. Prevent potential defects Smoother, shorter design / release cycles Better software products

- TEMPLATES Design documentation templates Design review checklists Bug reporting template Coding Style guides for C and Java Bug defect type classification Code review checklists Code quality rubric

Copyright © 2003-2018 Blackwood Designs, LLC. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Blackwood Designs.

**FILE**: G:\My Documents\BD4 SW Design Documents\guide-quality software\BD4 Quality Software Guide - 2018-7-8.doc

**RANDALL MAAS** has spent decades in Washington and Minnesota. He consults in embedded systems development, especially medical devices. Before that he did a lot of other things... like everyone else in the software industry. He is also interested in geophysical models, formal semantics, model theory and compilers.

You can contact him at randym@randym.name.

LinkedIn: http://www.linkedin.com/pub/randall-maas/9/838/8b1

| <u>PRE</u>        | PREFACE1                                                                                                                    |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.                | ORGANIZATION OF THIS DOCUMENT1                                                                                              |  |  |

| <u>SPE</u>        | CIFICATIONS                                                                                                                 |  |  |

|                   |                                                                                                                             |  |  |

| <u>0V</u>         | ERVIEW OF SOFTWARE DESIGN QUALITY7                                                                                          |  |  |

| 2.                | Overview                                                                                                                    |  |  |

| 3.                | SOFTWARE QUALITY OVERVIEW                                                                                                   |  |  |

| 4.                | A TIP ON STAFFING                                                                                                           |  |  |

| 5.                | REFERENCES AND RESOURCES                                                                                                    |  |  |

| PRO               | DCESS                                                                                                                       |  |  |

| <u></u>           |                                                                                                                             |  |  |

| 6.                | Process                                                                                                                     |  |  |

| 7.                | THE ROLE OF CERTIFYING STANDARDS                                                                                            |  |  |

| 8.                | SOFTWARE DEVELOPMENT PLAN                                                                                                   |  |  |

| 9.                | RISK ANALYSIS                                                                                                               |  |  |

| 10.               | TERMS RELATED TO TESTING, VERIFICATION, AND VALIDATION20                                                                    |  |  |

| 11.               | REFERENCES AND RESOURCES                                                                                                    |  |  |

|                   |                                                                                                                             |  |  |

| REC               | QUIREMENTS CHECKLISTS23                                                                                                     |  |  |

|                   |                                                                                                                             |  |  |

| 12.               | OVERVIEW OF WELL WRITTEN REQUIREMENTS                                                                                       |  |  |

| 13.               | REQUIREMENTS REVIEW CHECKLIST                                                                                               |  |  |

| SOL               | TWARE RISK ANALYSIS                                                                                                         |  |  |

| 301               | - I WARE NISK ANAL I SIS                                                                                                    |  |  |

| 14.               | Software Requirements Risk Analysis                                                                                         |  |  |

| 15.               | REFERENCE DOCUMENTS                                                                                                         |  |  |

|                   |                                                                                                                             |  |  |

| SOF               | TWARE DESIGN & DOCUMENTATION                                                                                                |  |  |

|                   |                                                                                                                             |  |  |

| DES               | SIGN OVERVIEW & WRITING TIPS                                                                                                |  |  |

|                   | <b>-</b>                                                                                                                    |  |  |

| 16.               | THE ROLE AND CHARACTERISTICS OF DESIGN DOCUMENTATION                                                                        |  |  |

| <b>17.</b><br>17. | Documentation organization         36           1.1         Tips for getting the definitions for standards terms         38 |  |  |

| 17.               |                                                                                                                             |  |  |

| 17.2              |                                                                                                                             |  |  |

|                   |                                                                                                                             |  |  |

| 17.2.       | 3 FILES                                        |

|-------------|------------------------------------------------|

| 18.         | REFERENCES AND RESOURCES                       |

|             |                                                |

| HIGH        | I-LEVEL DESIGN TEMPLATE41                      |

| <u></u>     |                                                |

| 19.         | BASIC OUTLINE                                  |

| 20.         | Division into modules                          |

| 21.         | REFERENCES AND RESOURCES                       |

|             |                                                |

| COLT        | WARE ARCHITECTURE RISK ANALYSIS                |

| <u>30F1</u> | WARE ARCHITECTORE RISK ANALTSIS                |

|             |                                                |

| 22.         | Software Architecture Risk Analysis            |

|             |                                                |

| DETA        | NILED DESIGN                                   |

|             |                                                |

| 23.         | DIAGRAMS AND DESIGN DECOMPOSITION INTO MODULES |

| 24.         | REFERENCES AND RESOURCES                       |

|             |                                                |

| сом         | MUNICATION PROTOCOL TEMPLATE                   |

|             |                                                |

| 25.         | COMMUNICATION PROTOCOL OUTLINE                 |

| 25.<br>26.  | INTERACTIONS                                   |

| 20.<br>27.  | THE DIFFERENT TRANSPORT MECHANISMS             |

| 28.         | TIMING CONFIGURATION AND CONNECTION PARAMETERS |

| 29.         | Message formats                                |

|             | 1 COMMAND                                      |

| 29.1.       |                                                |

| 30.         | REFERENCES AND RESOURCES                       |

|             |                                                |

| SOFT        | WARE MODULE DOCUMENTATION TEMPLATE62           |

| <u></u>     |                                                |

| 31.         | DETAILED DESIGN OUTLINE62                      |

| 31.<br>32.  | THE OVERVIEW SECTION                           |

| 52.<br>33.  | THE OVERVIEW SECTION                           |

|             | THE SOFTWARE INTERFACE DOCUMENTATION           |

| <b>34.</b>  | THE DETAILED DESIGN SECTION                    |

| 35.         | CONFIGURATION INTERFACE                        |

| 36.         | THE TEST SECTION                               |

| 37.         | REFERENCES AND RESOURCES                       |

|             |                                                |

| COLT        | WARE DESIGN GUIDANCE                           |

| 3011        | <u>ware Design Guidance</u>                    |

|             |                                                |

| 38.         | CODE REUSE                                     |

| 39.         | DESIGN TO BE DEBUGGABLE71                      |

| 40. F                         | AULT DETECTION: DETECTING AN ERROR CONDITION               | 72        |

|-------------------------------|------------------------------------------------------------|-----------|

| 40.7.1                        | THE THEORY OF OPERATION                                    | 76        |

| 40.7.2                        | THE DETAILED IMPLEMENTATION                                | 76        |

| 40.7.3                        | COMMENTARY ON DESIGN ALTERNATIVES                          | 78        |

| 41. SY                        | STEM AND MICROCONTROLLER SPECIFIC DETAILED DESIGN ELEMENTS | 79        |

| 41.1.1                        | Атомісіту                                                  | 79        |

| 41.1.2                        | A NOTE ON ARM CORTEX-MO PROCESSORS                         | 79        |

| 41.1.3                        | SOFTWARE BREAKPOINTS                                       | 79        |

| 41.1.4                        | HARDWARE EXCEPTIONS                                        | 79        |

| 41.1.5                        | MEMORY BARRIERS                                            | 79        |

| 41.1.6                        | DIGITAL INPUTS AND OUTPUTS                                 | 80        |

| 41.1.7                        | BITBAND                                                    | 80        |

| 41.1.8                        | PROCEDURE BLIP                                             | 80        |

| 41.1.9                        | FIND-FIRST SET BIT                                         | 81        |

| 41.1.10                       | INTERRUPT PRIORITIZATION                                   | 81        |

| 42. T                         | ESTS                                                       | 82        |

| 43. R                         | EFERENCES AND RESOURCES                                    | 90        |

|                               |                                                            |           |

| DESIGN                        | I REVIEW CHECKLISTS                                        | 91        |

|                               |                                                            |           |

| 44. D                         | ESIGN REVIEW                                               | 01        |

|                               |                                                            |           |

| 45. D                         | ETAILED DESIGN REVIEW CHECKLISTS                           | 92        |

|                               |                                                            |           |

| <u>SOFTW</u>                  | ARE DETAILED DESIGN RISK ANALYSIS                          | <u>98</u> |

|                               |                                                            |           |

| 46. S                         | OFTWARE DETAILED DESIGN RISK ANALYSIS                      | 98        |

|                               |                                                            |           |

| SOURC                         |                                                            | 01        |

| SUURC                         | E CODE CRAFTSMANSHIP1                                      | UI        |

|                               |                                                            |           |

| OVERV                         | IEW OF SOURCE CODE WORKMANSHIP1                            | <u>03</u> |

|                               |                                                            |           |

| 47. S                         | DURCE CODE WORKMANSHIP1                                    | 03        |

|                               |                                                            |           |

|                               | NG STYLE1                                                  | ΛE        |

|                               | NG 51 TLE                                                  | 05        |

|                               |                                                            |           |

|                               | ODING STYLE OVERVIEW1                                      |           |

|                               | DURCE CODE FILES                                           |           |

| 49.4.1                        | GUARDS                                                     |           |

| 49.4.2                        | EXTERN DECLARATION / PROCEDURE PROTOTYPES                  |           |

| 49.4.3                        | DOCUMENTED CODE 1                                          |           |

| 50. P                         | REFERRED TYPES1                                            | 09        |

| 50.3.1                        | INTEGER NUMBERS                                            | 10        |

| 50.3.2                        | FLOATING POINT NUMBERS                                     | 10        |

| 50.5.1                        | THE CONST QUALIFIER 1                                      |           |

| 50.5.2 The volatile qualifier |                                                            |           |

| 50.6.                                                 | 1 CANARY METHOD (AKA RED ZONES)                                                                                                                                                                        | 112                                                  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 51.                                                   | MACROS                                                                                                                                                                                                 | 112                                                  |

| 51.1.                                                 | 1 EXAMPLES OF EFFECTS                                                                                                                                                                                  | 113                                                  |

| 51.2.                                                 | 1 EXAMPLES OF EFFECTS                                                                                                                                                                                  | 113                                                  |

| 51.2.                                                 | 2 How to fix these problems                                                                                                                                                                            | 114                                                  |

| 51.2.                                                 | 3 OTHER COMMENTS                                                                                                                                                                                       | 115                                                  |

| 52.                                                   | OPERATORS & MATH                                                                                                                                                                                       | 115                                                  |

| 52.4.                                                 | 1 USE OF RATIONAL NUMBER FORMS                                                                                                                                                                         | 117                                                  |

| 53.                                                   | CONTROL FLOW, AVOIDING COMPLEXITY                                                                                                                                                                      | 118                                                  |

| 53.4.                                                 | 1 LOOP CONDITIONS                                                                                                                                                                                      | 119                                                  |

| 54.                                                   | PROCEDURE STRUCTURE                                                                                                                                                                                    | 119                                                  |

| 55.                                                   | NAMING CONVENTIONS                                                                                                                                                                                     | 121                                                  |

| 56.                                                   | MATH, STRINGS, AND ASSEMBLY                                                                                                                                                                            | 122                                                  |

| 57.                                                   | MICROCONTROLLER SPECIFIC GUIDELINES                                                                                                                                                                    |                                                      |

| 57.1.                                                 | 1 DO NOT USE FLOATS ON CORTEX-MO AND CORTEX-M3                                                                                                                                                         | 123                                                  |

| 57.2.                                                 | 1 USING THE "SLEEP" INSTRUCTION                                                                                                                                                                        | 123                                                  |

| 57.2.                                                 | 2 USE OF MULTIPLICATION AND DIVISION                                                                                                                                                                   | 123                                                  |

| 57.2.                                                 | 3 INTERRUPT TIME AND NORMAL TIME                                                                                                                                                                       | 123                                                  |

| 57.2.                                                 | 4 Use of Arrays instead of Switches or Pure Functions                                                                                                                                                  | 124                                                  |

| 58.                                                   | REFERENCES AND RESOURCES                                                                                                                                                                               | 124                                                  |

|                                                       |                                                                                                                                                                                                        |                                                      |

| 17/7                                                  | CODING STYLE GUIDE                                                                                                                                                                                     | 126                                                  |

| JAVA                                                  |                                                                                                                                                                                                        | 120                                                  |

|                                                       |                                                                                                                                                                                                        |                                                      |

| 59.                                                   | BASICS                                                                                                                                                                                                 |                                                      |

| 60.                                                   | LOCKS AND SYNCHRONIZATION                                                                                                                                                                              |                                                      |

| 61.                                                   | TYPE CONVERSION                                                                                                                                                                                        |                                                      |

| 62.                                                   | GUI RELATED CODE                                                                                                                                                                                       | 130                                                  |

|                                                       |                                                                                                                                                                                                        |                                                      |

| CODE                                                  | E INSPECTIONS AND REVIEWS                                                                                                                                                                              | 134                                                  |

|                                                       |                                                                                                                                                                                                        |                                                      |

| 63.                                                   | WHEN TO REVIEW                                                                                                                                                                                         | 174                                                  |

| 63.<br>64.                                            | -                                                                                                                                                                                                      |                                                      |

|                                                       |                                                                                                                                                                                                        | -                                                    |

| • · ·                                                 | WHO SHOULD REVIEW                                                                                                                                                                                      | 134                                                  |

| 65.                                                   | HOW TO INSPECT AND REVIEW CODE                                                                                                                                                                         | 134<br>135                                           |

| 65.<br>66.                                            | How to inspect and review code<br>The outcomes of a code review                                                                                                                                        | 134<br>135<br>136                                    |

| 65.                                                   | HOW TO INSPECT AND REVIEW CODE                                                                                                                                                                         | 134<br>135<br>136                                    |

| 65.<br>66.<br>67.                                     | HOW TO INSPECT AND REVIEW CODE<br>THE OUTCOMES OF A CODE REVIEW<br>REFERENCES AND RESOURCES                                                                                                            | 134<br>135<br>136<br>137                             |

| 65.<br>66.<br>67.                                     | How to inspect and review code<br>The outcomes of a code review                                                                                                                                        | 134<br>135<br>136<br>137                             |

| 65.<br>66.<br>67.                                     | HOW TO INSPECT AND REVIEW CODE<br>THE OUTCOMES OF A CODE REVIEW<br>REFERENCES AND RESOURCES                                                                                                            | 134<br>135<br>136<br>137                             |

| 65.<br>66.<br>67.<br><u>CODE</u>                      | HOW TO INSPECT AND REVIEW CODE<br>THE OUTCOMES OF A CODE REVIEW<br>REFERENCES AND RESOURCES<br>E INSPECTION & REVIEWS CHECKLISTS                                                                       | 134<br>135<br>136<br>137<br>138                      |

| 65.<br>66.<br>67.<br><u>CODE</u><br>68.               | How to inspect and review code<br>The outcomes of a code review<br>References and resources<br>E INSPECTION & REVIEWS CHECKLISTS                                                                       | 134<br>135<br>136<br>137<br>138                      |

| 65.<br>66.<br>67.<br><u>CODE</u><br>68.<br>69.        | HOW TO INSPECT AND REVIEW CODE<br>THE OUTCOMES OF A CODE REVIEW<br>REFERENCES AND RESOURCES<br>E INSPECTION & REVIEWS CHECKLISTS                                                                       | 134<br>135<br>136<br>137<br>138<br>138<br>138        |

| 65.<br>66.<br>67.<br><u>CODE</u><br>68.<br>69.        | How to inspect and review code<br>The outcomes of a code review<br>References and resources<br>E INSPECTION & REVIEWS CHECKLISTS<br>Reviews<br>Basic review checklist                                  | 134<br>135<br>136<br>137<br>138<br>138<br>138        |

| 65.<br>66.<br>67.<br><u>CODE</u><br>68.<br>69.<br>70. | How to inspect and review code<br>The outcomes of a code review<br>References and resources<br>E INSPECTION & REVIEWS CHECKLISTS<br>Reviews<br>Basic review checklist<br>Specialized review Checklists | 134<br>135<br>136<br>137<br>138<br>138<br>138<br>141 |

| 65.<br>66.<br>67.<br><u>CODE</u><br>68.<br>69.<br>70. | How to inspect and review code<br>The outcomes of a code review<br>References and resources<br>E INSPECTION & REVIEWS CHECKLISTS<br>Reviews<br>Basic review checklist                                  | 134<br>135<br>136<br>137<br>138<br>138<br>138<br>141 |

| 65.<br>66.<br>67.<br><u>CODE</u><br>68.<br>69.<br>70. | How to inspect and review code<br>The outcomes of a code review<br>References and resources<br>E INSPECTION & REVIEWS CHECKLISTS<br>Reviews<br>Basic review checklist<br>Specialized review Checklists | 134<br>135<br>136<br>137<br>138<br>138<br>138<br>141 |

| <u>PRO</u>   | PRODUCT STANDARDS155                          |  |  |

|--------------|-----------------------------------------------|--|--|

| 71.          | STANDARDS                                     |  |  |

| 72.          | PRODUCT STANDARDS                             |  |  |

| 73.          | REFERENCES AND RESOURCES                      |  |  |

| <u>BUG</u>   | REPORT TEMPLATE158                            |  |  |

| 74.          | OUTLINE OF A PROPER BUG REPORT                |  |  |

| 75.          | BUG HEADER INFORMATION                        |  |  |

| 76.          | BUG TITLE AND DESCRIPTION                     |  |  |

| 77.          | Additional Information Requirements (General) |  |  |

| 78.          | CONTACT INFORMATION                           |  |  |

| 79.          | PRODUCT-SPECIFIC ADDITIONAL INFORMATION       |  |  |

| <u>TYPE</u>  | S OF DEFECTS                                  |  |  |

| 80.          | Overview                                      |  |  |

| 81.          | CLASSIFYING THE TYPE OF DEFECT                |  |  |

| 011          |                                               |  |  |

| COD          | E-COMPLETE REQUIREMENTS REVIEW CHECKLISTS     |  |  |

|              | · · · ·                                       |  |  |

| 82.          | CHECKLIST: REQUIREMENTS                       |  |  |

| <u>COD</u>   | E-COMPLETE DESIGN REVIEW CHECKLISTS173        |  |  |

| 83.          | CHECKLIST: ARCHITECTURE                       |  |  |

| 84.          | CHECKLIST: MAJOR CONSTRUCTION PRACTICES       |  |  |

| 85.          | CHECKLIST: DESIGN IN CONSTRUCTION             |  |  |

| 86.          | CHECKLIST: CLASS QUALITY                      |  |  |

| 87.          | CHECKLIST: THE PSEUDOCODE PROGRAMMING PROCESS |  |  |

| 88.          | CHECKLIST: A QUALITY-ASSURANCE PLAN           |  |  |

| 89.          | CHECKLIST: EFFECTIVE PAIR PROGRAMMING         |  |  |

| 90.          | CHECKLIST: TEST CASES                         |  |  |

| 91.          | CHECKLIST: DEBUGGING REMINDERS                |  |  |

| 92.          | CHECKLIST: CODE-TUNING STRATEGY               |  |  |

| 93.          | CHECKLIST: CONFIGURATION MANAGEMENT           |  |  |

| 94.          | CHECKLIST: INTEGRATION                        |  |  |

| 95.          | CHECKLIST: PROGRAMMING TOOLS                  |  |  |

| <u>DES</u> I | GN REVIEW RUBRIC                              |  |  |

|              |                                               |  |  |

| 96.          | DOCUMENTATION                                 |  |  |

| 97.          | DESIGN                                        |  |  |

| 57.          |                                               |  |  |

| FLOATING-POINT PRECISION |                                                       |  |

|--------------------------|-------------------------------------------------------|--|

| COD                      | E-COMPLETE CODE REVIEW CHECKLISTS                     |  |

|                          |                                                       |  |

| 98.                      | CHECKLIST: EFFECTIVE INSPECTIONS                      |  |

| 99.                      | CHECKLIST: HIGH-QUALITY ROUTINES                      |  |

| 100.                     | CHECKLIST: DEFENSIVE PROGRAMMING189                   |  |

| 101.                     | CHECKLIST: GENERAL CONSIDERATIONS IN USING DATA190    |  |

| 102.                     | CHECKLIST: NAMING VARIABLES191                        |  |

| 103.                     | CHECKLIST: FUNDAMENTAL DATA                           |  |

| 104.                     | CHECKLIST: CONSIDERATIONS IN USING UNUSUAL DATA TYPES |  |

| 105.                     | CHECKLIST: ORGANIZING STRAIGHT LINE CODE194           |  |

| 106.                     | CHECKLIST: CONDITIONALS                               |  |

| 107.                     | CHECKLIST: LOOPS                                      |  |

| 108.                     | CHECKLIST: UNUSUAL CONTROL STRUCTURES                 |  |

| 109.                     | CHECKLIST: TABLE DRIVEN METHODS                       |  |

| 110.                     | CHECKLIST: CONTROL STRUCTURE ISSUES                   |  |

| 111.                     | REFACTORING                                           |  |

| 112.                     | CHECKLIST: CODE-TUNING TECHNIQUES                     |  |

| 113.                     | CHECKLIST: LAYOUT                                     |  |

| 114.                     | CHECKLIST: GOOD COMMENTING TECHNIQUE                  |  |

| 115.                     | CHECKLIST: SELF-DOCUMENTING CODE                      |  |

|                          |                                                       |  |

| COD                      | E REVIEW RUBRIC                                       |  |

|                          |                                                       |  |

| 116.                     | SOFTWARE READABILITY RUBRIC                           |  |

| 117.                     | SOFTWARE COMMENTS & DOCUMENTATION206                  |  |

| 118.                     | IMPLEMENTATION                                        |  |

| 119.                     | ERROR HANDLING                                        |  |

| 120.                     | BEHAVIOUR                                             |  |

| <u>REFE</u>              | RENCES & RESOURCES                                    |  |

|                          |                                                       |  |

| 121.                     | REFERENCE DOCUMENTATION AND RESOURCES                 |  |

| FIGURE 1: THE HIERARCHY OF SYSTEMS & SUBSYSTEMS                            |    |

|----------------------------------------------------------------------------|----|

| FIGURE 2: LEVELS OF ABSTRACTION IN DEVELOPMENT PROCESS                     |    |

| FIGURE 3: LEVELS OF ABSTRACTION IN DEVELOPMENT PROCESS                     |    |

| FIGURE 4: WHERE KEY FUNCTIONS & REQUIREMENTS ARE IDENTIFIED IN THE PROCESS |    |

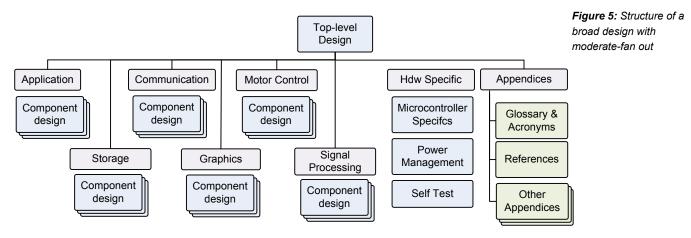

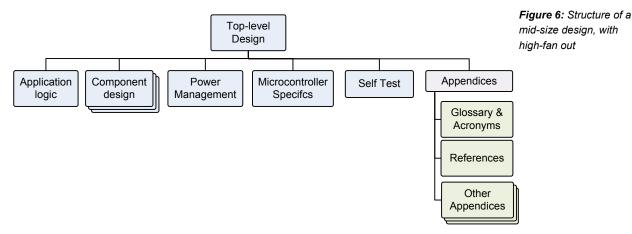

| FIGURE 5: STRUCTURE OF A BROAD DESIGN WITH MODERATE-FAN OUT                |    |

| FIGURE 6: STRUCTURE OF A MID-SIZE DESIGN, WITH HIGH-FAN OUT                |    |

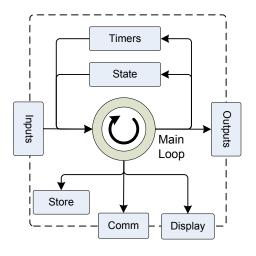

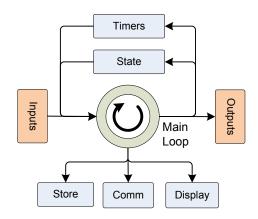

| FIGURE 7: BASIC FLOW STRUCTURE OF THE SOFTWARE                             |    |

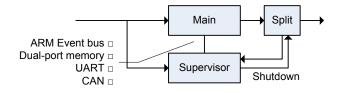

| FIGURE 8: PROCESSOR WITH A SUPERVISOR PROCESSOR                            |    |

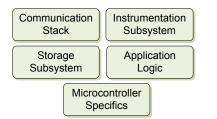

| FIGURE 9: MAJOR FUNCTIONALITY GROUPS                                       |    |

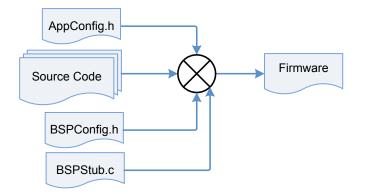

| FIGURE 10: THE CONFIGURATION OF THE PRODUCTION FIRMWARE                    |    |

| FIGURE 11: BASIC FLOW STRUCTURE OF THE SOFTWARE                            |    |

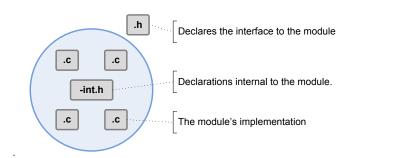

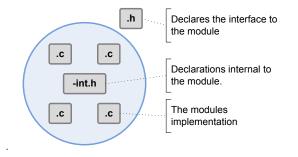

| FIGURE 12: HOW .H AND .C FILES RELATED TO A MODULE                         | 53 |

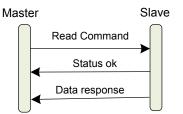

| FIGURE 13: SEQUENCE FOR READING PORTION OF THE XYZ DATA                    |    |

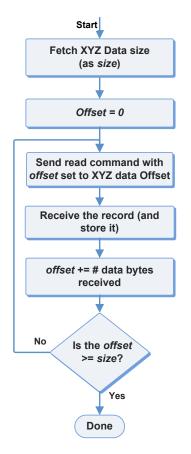

| FIGURE 14: THE XYZ DATA RETRIEVAL ALGORITHM                                |    |

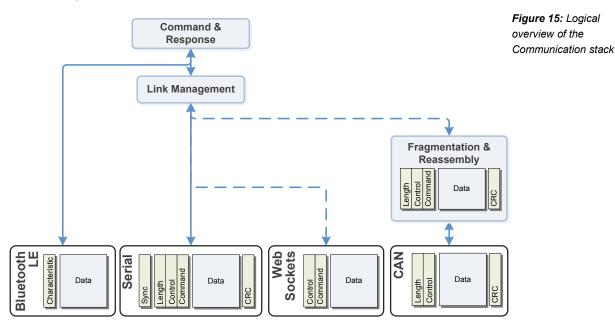

| FIGURE 15: LOGICAL OVERVIEW OF THE COMMUNICATION STACK OVERVIEW            |    |

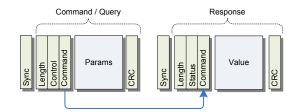

| FIGURE 16: THE FORMAT OF THE COMMAND/QUERY AND RESPONSE MESSAGES           |    |

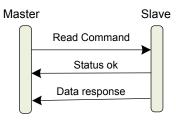

| FIGURE 17: READ COMMAND SEQUENCE ON SUCCESS                                |    |

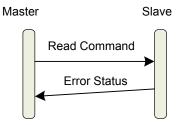

| FIGURE 18: READ COMMAND WITH ERROR RESPONSE                                | 61 |

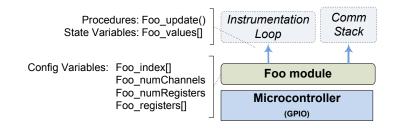

| FIGURE 19: OVERVIEW OF THE FOO MODULE                                      |    |

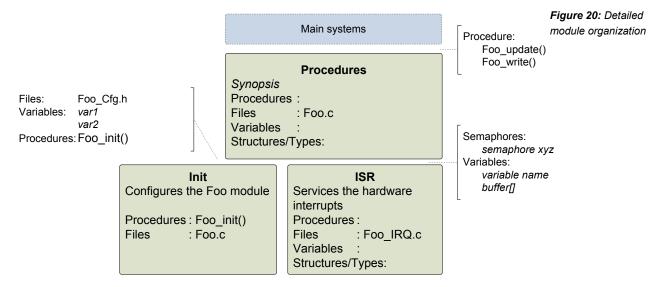

| FIGURE 20: DETAILED MODULE ORGANIZATION                                    |    |

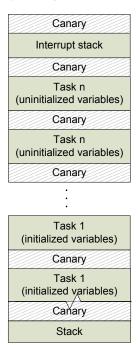

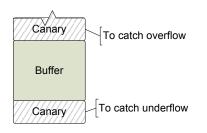

| FIGURE 21: SEGMENTATION OF MEMORY WITH CANARIES                            | 74 |

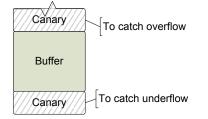

| FIGURE 22: OVERVIEW OF BUFFERS WITH CANARIES                               |    |

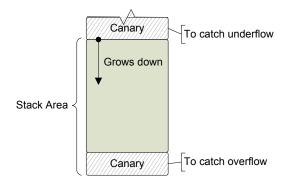

| FIGURE 23: OVERVIEW OF THE STACK STRUCTURE WITH CANARIES                   |    |

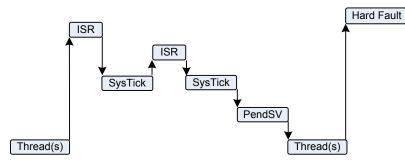

| FIGURE 24: PRIORITIZED INTERRUPTS AND EXCEPTIONS                           |    |

| FIGURE 25: HOW .H AND .C FILES RELATED TO A MODULE                         |    |

| FIGURE 26: TYPICAL PROCEDURE TEMPLATE                                      |    |

| FIGURE 27: OVERVIEW OF BUFFERS WITH CANARIES                               |    |

| Table 1: ISO/IEC 25010 MODEL OF SOFTWARE QUALITY                                              | 8 |

|-----------------------------------------------------------------------------------------------|---|

| TABLE 2: MCCALL MODEL OF SOFTWARE QUALITY.                                                    | 8 |

| Table 3: Inputs for each kind of risk analysis         1                                      | 9 |

| Table 4: Value Accuracy risks                                                                 | 8 |

| Table 5: Hazard probability levels based on Mil-Std 882         2                             | 8 |

| <b>TABLE 6:</b> AN EXAMPLE RISK ACCEPTABILITY MATRIX DETERMINING RISK ACCEPTABILITY         2 | 8 |

| Table 7: Message capacity risks         2                                                     | 9 |

| Table 8: Timing capacity risks         2                                                      | 9 |

| Table 9: Software function risks         3                                                    | 0 |

| TABLE 10: SOFTWARE ROBUSTNESS RISKS                                                           | 0 |

| TABLE 11: SOFTWARE CRITICAL SECTIONS RISKS         3                                          | 1 |

| TABLE 12: UNAUTHORIZED USE RISKS    3                                                         | 1 |

| <b>TABLE 13:</b> THE SOFTWARE DESIGN ELEMENTS         4                                       | 3 |

| <b>TABLE 14:</b> THE EXTERNAL ELEMENTS         4                                              | 3 |

| TABLE 15: THE FUNCTIONALITY GROUPS         4                                                  | 4 |

| <b>TABLE 16:</b> SUMMARY OF MODULE PREFIXES         4                                         | 5 |

| Table 17: Timing capacity risks         4                                                     | 8 |

| Table 18: Software function risks         4                                                   | 9 |

| TABLE 19: THE SOFTWARE DESIGN ELEMENTS         5                                              | 2 |

| Table 20:         Summary of the Read Data command         6                                  | 0 |

| Table 21: Parameters for Read Command                                                         | 0 |

| Table 22: Parameters for Read Response         6                                              | 0 |

| TABLE 23: FOO STRUCTURES         6                                                            | 4 |

| TABLE 24: FOO_T STRUCTURE                                                                     | 5 |

| TABLE 25: FOO VARIABLES                                                                       | 5 |

| TABLE 26: FOO INTERFACE PROCEDURES         6                                                  | 5 |

| TABLE 27: MODULE FILES                                                                        | 8 |

| Table 28: Configuration of the Foo module         6                                           | 9 |

| Table 29: Rewriting                                                                           | 6 |

| Table 30: Software function risks         9                                                   | 9 |

| TABLE 31: THE PREFERRED C INTEGER TYPE FOR A GIVEN SIZE       11                              | 0 |

| Table 32: Common Acronyms and Abbreviations         14                                        | 9 |

| TABLE 33: GLOSSARY OF COMMON TERMS AND PHRASES         15                                     | 0 |

| Table 34: Safety standards and where they adapt from                                          | 7 |

| Table 35: Readability rubric                                                                  | 3 |

| Table 36: Documentation organization and clarity rubric         18                            | 4 |

| Table 37: Implementation rubric                                                               | 5 |

| Table 38:         Float range                                                                 | 7 |

| TABLE 39: ACCURACY OF INTEGER VALUES REPRESENTED AS A FLOAT         18                        | 7 |

| Table 40:   Readability rubric                                                                | 5 |

| Table 41: Comments and documentation rubric         20                                        | 6 |

| Table 42: Implementation rubric                                                               | 7 |

| Table 43: Error handling rubric   21                                                          | 0 |

| Table 44: Behaviour rubric                                                                    | 0 |

## Preface

This guide aims to provide relevant tools to support creating quality software. It tries to do so in a manner that the reader may apply to their projects. Why create such a thing? As a consultant who has seen many client development organizations, I've found that few have the material that I present here. None has any guidelines on good software designs, design reviews and hazard analysis of software. Many lack coding style guide, code review guidance, and bug reporting standards. If they do have code guidelines, it is sparse, and could do so much more to improve quality.

This is a guide will only cover the quality of software design and the workmanship of source code. It does not cover:

- Writing software requirements

- Testing of the software

- Debugging the software

- Project and development management

- Planning, scheduling or budgeting

#### 1. ORGANIZATION OF THIS DOCUMENT

This guide is written in 3 parts, with the broadest up front, and the most specific or esoteric toward the rear.

• CHAPTER 1: PREFACE. This chapter describes the other chapters.

PART I: SPECIFICATIONS.

- CHAPTER 2: OVERVIEW OF SOFTWARE DESIGN QUALITY. Introduces what is meant by quality.

- CHAPTER 3: PROCESS.

- CHAPTER 4: REQUIREMENTS CHECKLISTS. This chapter provides checklists for reviewing requirements.

- CHAPTER 5: SOFTWARE RISK ANALYSIS.

PART II: SOFTWARE DESIGN & DOCUMENTATION. This part provides guides for software design and its documentation

- CHAPTER 6: DESIGN OVERVIEW & WRITING TIPS.

- CHAPTER 7: GUIDELINES FOR HIGH-LEVEL DESIGNS. Provides guidelines for high-level designs (e.g. architectures).

- CHAPTER 8: SOFTWARE ARCHITECTURE RISK ANALYSIS.

- CHAPTER 9: GUIDELINES FOR DETAILED DESIGNS. Provides guidelines for detailed designs (e.g. major subsystems or "stacks").

- CHAPTER 10: PROTOCOL DOCUMENTATION TEMPLATE. Provides a guide for protocol documentation.

- CHAPTER 11: SOFTWARE MODULE DOCUMENTATION TEMPLATE. Provides a guide for detailed design documentation of a module.

- CHAPTER 12: GUIDELINES FOR MODULE DESIGNS. Provides guidelines for low-level module designs.

- CHAPTER 13: DESIGN REVIEWS CHECKLISTS. Provides checklists for reviewing a design.

- CHAPTER 14: SOFTWARE DETAILED DESIGN RISK ANALYSIS. Describes reviewing software for hazard analysis.

PART III: SOURCE CODE CRAFTSMANSHIP. This part provides source code workmanship guides

- CHAPTER 15: OVERVIEW OF SOURCE CODE WORKMANSHIP. Provides TBD.

- CHAPTER 16: C CODING STYLE. This chapter outlines the style used for C source code.

- CHAPTER 17: JAVA CODING STYLE. This chapter outlines the style used for Java source code.

- CHAPTER 18: CODE INSPECTION & REVIEWS. Describes code reviews.

- CHAPTER 19: CODE INSPECTION & REVIEWS CHECKLISTS. Provides checklists for reviewing source code.

APPENDICES: The appendices provides extra material

- APPENDIX A: ABBREVIATIONS, ACRONYMS, & GLOSSARY. This appendix provides a gloss of terms, abbreviations, and acronyms.

- APPENDIX B: PRODUCT STANDARDS. This appendix provides supplemental information on standards and how product standards are organized

- APPENDIX C: BUG REPORTING TEMPLATE. This appendix provides a template (and guidelines) for reporting bugs

- APPENDIX D: TYPES OF DEFECTS. This appendix provides a classification of different kinds of software defects that are typically encountered.

- APPENDIX E: CODE COMPLETE REQUIREMENTS REVIEW CHECKLISTS. This appendix reproduces checklists from *Code Complete, 2nd Ed* that are relevant to requirements reviews.

- APPENDIX F: CODE COMPLETE DESIGN REVIEW CHECKLISTS. This appendix reproduces checklists from *Code Complete, 2nd Ed* that are relevant to design reviews.

- APPENDIX G: DESIGN REVIEW RUBRIC. This appendix provides rubrics relevant in assessing the design and its documentation.

- APPENDIX H: FLOATING POINT PRECISION. This appendix recaps the limits of floating point precision.

- APPENDIX I: CODE COMPLETE CODE REVIEW CHECKLISTS. This appendix reproduces checklists from *Code Complete, 2nd Ed* that are relevant to code reviews.

- APPENDIX J: SOFTWARE REVIEW RUBRIC. This appendix provides rubrics relevant in assessing software workmanship.

REFERENCES AND RESOURCES. This provides further reading and referenced documents.

<sup>&</sup>quot;The project development people seemed to be a special breed of programmers whose incomprehensibility was matched only by their desire to document in a level of detail that baffled the minds of ordinary folk." – NSA Cryptolog, 1979 June

[This page is intentionally left blank for purposes of double-sided printing]

### PART I

# Specifications

This first part provides guides for software design and its documentation

- OVERVIEW OF SOFTWARE DESIGN QUALITY. Introduces what is meant by quality.

- PROCESS

- REQUIREMENTS CHECKLISTS. This chapter provides checklists for reviewing requirements.

- SOFTWARE RISK ANALYSIS.

[This page is intentionally left blank for purposes of double-sided printing]

# CHAPTER 2 Overview of Software Design Quality

This chapter promotes good software quality:

- Software quality overview

- Where do bugs come from?

- How quality software can be achieved

- A tip on staffing

#### 2. OVERVIEW

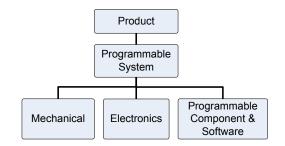

Software lives as part of a system within a product. Typical embedded software can be described as fit into a hierarchy of systems and subsystems:

*Figure 1:* The hierarchy of systems & subsystems

There is the "final" *product* itself, with a portion – sometimes a large portion, sometimes a small portion – that is the *programmable system*. This system has mechanical and electronic subsystems, as well as the *programmable component* (usually a microcontroller) that is executing the software that will be discussing through this guidebook.

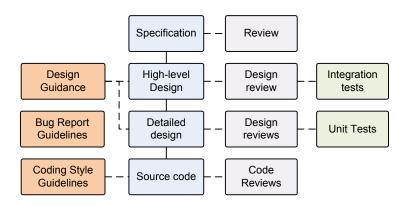

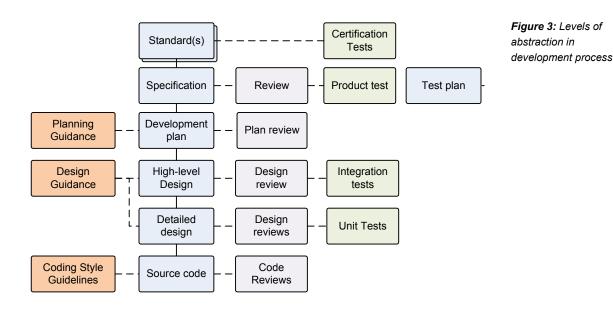

The diagram below synopsizes the levels of abstraction in the normative software development process. Guidance documents help the work to be performed be done quickly, and with appropriate craftsmanship. The tests and reviews help catch errors and improve the construction of the software.

*Figure 2:* Levels of abstraction in development process

Review checklists & rubrics should be a dual (twin) to the coding style. Everything in one should be in the other.

#### 3. SOFTWARE QUALITY OVERVIEW

It may be helpful to provide a brief overview of what "software quality" is. ISO/IEC 25010 model of software quality is one useful way to organize the areas of quality:

| Quality factor              | Quality Criteria                                                                                              | <b>Table 1:</b> ISO/IEC 25010 model of |

|-----------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Functionality               | Completeness, Correctness, Appropriateness                                                                    | software quality                       |

| Performance &<br>Efficiency | Time behavior, Resource utilization, Capacity                                                                 |                                        |

| Compatibility               | Interoperability                                                                                              |                                        |

| Usability                   | Appropriateness, Recognisability, Learnability, Operability, User error protection, Aesthetics, Accessibility |                                        |

| Reliability                 | Maturity, Availability, Fault tolerance, Recoverability                                                       |                                        |

| Security                    | Confidentiality, Integrity, Non-repudiation, Accountability, Authenticity                                     |                                        |

| Maintainability             | Analyzability, Modifiability, Modularity, Reusability, Testability                                            |                                        |

| Portability                 | Adaptability, Installability, Replaceability                                                                  |                                        |

McCall's model is another way to organize the areas of quality. It maps each top-level area of quality to a more specific quality.

| Quality factor  | Quality Criteria                                              | Table 2: McCall model<br>of software quality |

|-----------------|---------------------------------------------------------------|----------------------------------------------|

| Correctness     | Traceability, Completeness, Consistency                       |                                              |

| Reliability     | Consistency, Accuracy, Error tolerance                        |                                              |

| Efficiency      | Execution efficiency, Storage efficiency                      |                                              |

| Integrity       | Access control, Access audit                                  |                                              |

| Usability       | Operability, Training, Communicativeness                      |                                              |

| Maintainability | Simplicity, Conciseness, Self-descriptiveness, Modularity     |                                              |

| Testability     | Simplicity, Instrumentation, Self-descriptiveness, Modularity |                                              |

| Flexibility     | Simplicity, Expandability, Generality, Modularity             |                                              |

| Portability      | Simplicity, Software system independence, Machine independence                            |

|------------------|-------------------------------------------------------------------------------------------|

| Reusability      | Simplicity, Generality, Modularity, Software system independence,<br>Machine independence |

| Interoperability | Modularity, Communications commonality, Data commonality                                  |

These same metrics apply to the programmable system, and perhaps the product overall.

#### 3.1. WHERE DO BUGS & DEFECTS COME FROM?

Where do the bugs & defects come from?

- The wrong requirements that the product and programmable system was designed to the wrong set of rules.

- Operation action and input inconsistent settings, out of range entries, and so forth. These errors indicate insufficient requirements about the constraints on the user interface.

- Poor design a design is unsound, an algorithm has too high of computational complexity, bottlenecks & contention for resources, prioritization issues, etc.

- Edge case circumstances, such as race conditions and overloading of processing resources.

- Programmer mistakes, such as language mistakes, or incorrect of use of hardware use of disabled peripherals, bad parameters, index out of range, hardware exceptions, divide by zero, and the like. These are often in the form of "exceptions" and "assert" failures.

- Hardware components may have shifted values; connections break.

- Environmental conditions such as a component being used out of its operating range, a low battery, and so forth.

It is important to note: the software can perform with high quality, and the programmable system low quality. This can come from the wrong requirements, at any level.

#### 3.2. HOW QUALITY SOFTWARE CAN BE ACHIEVED

Steps to quality software include recognizing that

- It is an acquired, disciplined art.

- It requires practice, diligence and assessment

- Organizations must teach how to write quality code.

- The organization must value quality software in order for the individual to value it

- The development organization has a culture of accountability and commitment

- There is encouragement for respectful, frank, rational conversations about failures

- Information, activities and agreements are explicitly communicated (rather than tacit and assumed)

#### 3.3. TESTING

Testing

- Has an important role in quality

- Most often removes the "easy" and frequent bugs

- Won't find subtle timing bugs and edge cases. It can help regression test to ensure that specific occurrences do not recur

- Doesn't improve workmanship

#### 4. A TIP ON STAFFING

This guidebook generally does not address development process – plans, schedules, sequencing, staffing, and so on. However, here are some opinionated tips:

- 1. Assign leadership to those who care about the quality. In any organization, there is a leader somewhere who capitates the quality even if there is a leaders who drives a minimum quality standard. It doesn't matter if the quality is something aesthetic (like being stylish & usable), or a process quality (like being maintainable and traceable), or other quality.

- 2. Work with people who value the development artifacts they are creating and the processes they work in. For instance, my experience has been that people who dislike writing or reading documentation will create poor documentation and the hate shines thru.

- 3. Encourage *gracious professionalism*<sup>1</sup> where the staff is fiercely driven, seeks mutual gain, are intensely respectful and kind

- 4. Reduce stress. Faux urgency and cranking up the time pressure is a common managerial technique in too many places. Meeting regular shipment schedules or quality goals is a long marathon.

In short, *care* and *drive* (or *passion, internal motivation, pride*).

#### 5. REFERENCES AND RESOURCES

ISO/IED FDIS 25010:2011, "Systems and software engineering - Systems and software Quality Requirements and Evaluation (SQuaRE) - System and software quality models" 2011 IEEE Std 730-2014, IEEE Standard for Software Quality Assurance Processes, 2014 IEEE Std 1061-1998, IEEE Standard for a Software Quality Metrics Methodology

<sup>&</sup>lt;sup>1</sup> Coined by Dr Woodie Flowers, registered trademark of FIRST

### CHAPTER 3

## Process

This chapter describes the software development process:

- Process, specifications, and requirements

- The role of standards & certification

- System engineering

- Development plan

- Risk analysis

- Testing, Verification, Validation, and Testing

#### 6. PROCESS

A process is how – implicitly or explicitly – an organization achieves a goal. Explicit processes decompose the steps of what an organization may do (or must do or should do), spelling out the activities and artifacts (more importantly information to be captured in the artifacts). Rigorous processes attempt to assure that

- the project will succeed,

- that the schedule will be reasonably met,

- the cost of development is acceptable,

- the product is acceptable & performs as intended

- the product does not pose an unacceptable risk of harm

- the product is well made

- the product can be kept in use / operation for a time period, including revising and maintaining the product.

project assurance

A design should be thoughtfully worked out, drilling down from the high-level specifications to the more specialized specifications, and designs.<sup>2</sup> Ideally – and depending on the rigor – each should be assessed or reviewed for appropriateness, and matching the products intent and requirements. Once a module's detailed design has been approved, the creation of its source code may begin in earnest.<sup>3</sup>

The process should call out (and provide) workmanship guidelines, style guides, standards, and evaluation rubrics used to craft the source code; this is often done in the development plan. One goal of the guides is to provide direction to producing clear code, with a low barrier to understanding and evaluation. The following chapters provide reference guides.

The source code should be reviewed (and otherwise inspected) against those guides, designs, and against workmanship evaluation guides. The purpose of reviewing the work is to examine quality of construction – it is not an evaluation of the engineers, and it is more identifying defects.

#### 6.1. THE DIFFERENT TYPES OF SPECIFICATION DOCUMENTS

The documents - or portions of documents - discussed here include:

A *high-level specification* is a finite set of requirements specification, e.g. system specification, customer inputs, marketing inputs, etc.

A *requirements specification* is a set of requirements, and clear text explaining or justifying the requirements. A justification may base the requirement in other documents, such as research, standards, regulations or other laws.

high-level specification

requirements specification

<sup>&</sup>lt;sup>2</sup> Designing of a "lower" layer can begin (and often does) based on the anticipated top-level design, and norms for the lower layer. Its completion is dependent the top-level design being settled.

<sup>&</sup>lt;sup>3</sup> Not all reviews or designs must be complete before implementations begin, except in the most stringent of processes. Modules built in an investigatory (or as a short-term shim) fashion are useful but should be considered in an "as-is" or draft state, until they have been revised to match the design, workmanship rules, and so in.

| • A <i>requirement</i> defines what an item must do, and often is presented as text in a special form.                                                                                                                                                                                                                                                                                                            | requirement          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| • A <i>customer requirement</i> is a requirement in any of the top-level documents, but especially in the customer (or user) requirements specification.                                                                                                                                                                                                                                                          | customer requirement |

| • A <i>comment</i> is text, usually to provide context, clarify or explain the requirement(s).                                                                                                                                                                                                                                                                                                                    | comment              |

| • An <i>identifier</i> can refer to product, specific version of the product, a document, requirement, test, external document, or comment. In practice this is so important that each item is given a label.                                                                                                                                                                                                     | identifier           |

| A <i>design document</i> explains the design of a product, with a justification how it addresses safety and other concerns.                                                                                                                                                                                                                                                                                       | design document      |

| <i>Test specifications</i> describe a set of tests intended to check that the product meets it requirements. The test specifications define:                                                                                                                                                                                                                                                                      | test specification   |

| • A set of <i>test requirements</i> that define what tests a product must pass.                                                                                                                                                                                                                                                                                                                                   | test requirements    |

| • A set of <i>test procedures</i> that carry out the test requirement and test the product                                                                                                                                                                                                                                                                                                                        | test procedure       |

| • A mapping of a test requirement to a set of requirements that it tests. {note: this may be covered in the trace below.}                                                                                                                                                                                                                                                                                         |                      |

| A <i>test report</i> is a set of outcomes: <i><test id,="" product="" result=""></test></i> describing how a product performed under test. (The performance may vary with versions of the product)                                                                                                                                                                                                                | test report          |

| A <i>trace matrix</i> is used to identify requirements in a higher level specification that are not carried thru to lower requirements specifications and designs; and (in stringent cases) identify features of the design without requirements, and requirements in lower documents that are not drive by requirements at a higher level. Logically it defines two functions, forming a directed acyclic graph: | trace matrix         |

| <ul> <li>It maps a requirement to the set of requirements that it directly descends (or dervices) from</li> </ul>                                                                                                                                                                                                                                                                                                 |                      |

• It maps a requirement to a set of requirements that directly or indirectly descends from it.

#### 6.2. CRITICAL THINKING

Quality oriented – and especially safety oriented – processes apply analysis and reasoning to further improve the product being developed. All processes try to the address what/why/where/when/how questions, by identifying where the information is or comes from:

What are we making?

1. The high level specification

How do we know that we have the right (product) specification(s)?

- 1. Standards

- 2. Stakeholder reviews

- 3. Customer feedback (e.g. voice of customer)

- 4. Hazard analysis

- 5. Usability studies

- 6. Field tests

#### How do we know that the product meets the specification(s)?

- 1. Verification activities of the system and subsystem

- 2. Validation activities of the product

Why are we confident that product is well made and safe?

- 1. Reviews of specifications and design

- 2. Analysis of the specification for key qualities, esp. safety

- 3. Verification & validation, testing

How do we know if a part of a higher-level specification was missed when making a lowerlevel (more specific) specification?

- 1. Tracing

- 2. Validation & validation, testing

*How do we know what to do?*

- 1. Specifications

- 2. Development plans

- 3. Guidelines, e.g. coding style guides, design guides

- 4. Development protocols & work instructions

Why the product was designed and made this way?

- 1. Specifications

- 2. Guidelines, e.g. coding style guides, design guides

- 3. Design documentation

- 4. Design reviews

and so on

#### 7. THE ROLE OF CERTIFYING STANDARDS

Product certification – specifically the standards being certified against – may drive software quality. Standards approach software quality as necessary to achieve product quality, especially safety and security. To simplify (and over generalize), such standards have specifications that address the following areas of software quality:

- Risk management, including analysis, assessment and control of the risks

- The process and artifacts, and how they will be stored and updated. These include a software development lifecycle (SDLC) and quality management systems (QMS)

- Techniques to be applied in the software design and implementation

- *Tests* and characterizations to be applied.

Some important examples of the safety-facing standards are:

- IEC 61508: *Functional safety of electrical/electronic/programmable electronic safetyrelated systems* (Part 3 deals with software and Part 7 with specific techniques)

- IEC 60730: Automatic Electrical Controls. (Annex H deals with software)

- ANSI/IEC 62304:2006 Medical Device Software Software Lifecycle Processes

- DO-178C, Software Considerations in Airborne Systems and Equipment Certification

- IEEC Std 7-4.3.2 2010 IEEE Standard Criteria for Digital Computers in Safety Systems of Nuclear Power Generating Stations

#### 7.1. IEC 61508 AND DERIVATIVE STANDARDS (E.G. IEC 60730)

IEC 61508's has many process facing areas, over a complete safety life cycle. It mandated a IEC 61508 A specific safety management approach, parallel to the development of primary . functionality. This produces a set of software safety requirements. A specific risk management approach, including a risk assessment and analysis approach that is far more strenuous than the art in many fields. (And was when it was introduced). A software development lifecycle<sup>4</sup>, with several activities to be performed, and several artifacts to be produced. A mandate and guidance to apply very specific & detailed software design and implementation techniques, depending on the classification of software. Most of the techniques had been documented at least two decades prior to the first version of the version (1998-2000); all were documented at least decade prior. Most, however, were not in common use outside of niche applications. Several IEC standards adapt IEC 61508 for an industry segment, a kind of product, or specific see Appendix B applications. These IEC standards are organized into a main standard (with dash 1 suffix). These normatively reference the IEC 61508 standard (that is, mandate its use), or choose to incorporate the relevant portions into the narrower standard, with some modifications. Then there are a set of specific standards targeting requirements of specific categories of products or applications. (These have the same major number as the standard, followed by dash 2 with another suffix). These specific standards often modify the "dash 1" standard, reducing the stringency in some areas. IEC 60730-1 incorporates much of IEC 61508's software requirements (but not the risk IEC 60730 assessment system) for home appliances. This includes the production of software safety requirements. The IEC 60730-2-xyz standards specify requirements for various types of appliances. IEC 60730 divides functionality (including software function) into three categories of safety: . Class A are the functions that are not relied upon for safety see Appendix B for other classifications

- Class B are the functions that directly (or indirectly) prevent unsafe operation

- Class C are the functions that directly (or indirectly) prevent special hazards (such as explosion).

IEC 60335 follows the same pattern: 60335-1 incorporates most (but not all) of IEC 60730 *IEC 60335* software requirements. The IEC 60335-2-xyz standards specify requirements for various types of appliances.

This guidebook has been structured in such a manner to directly support software development under these standards. This includes not just software design & implementation, but the artifacts: requirements, design, and documentation.

<sup>&</sup>lt;sup>4</sup> Modern software development lifecycle can be found in IEEE Std 12207 (ISO/IEC 12207).

#### 7.2. ANSI/IEC 62304

ANSI/IEC 62304 is a software development lifecycle document, and it is organized in the classic "v-model" fashion. It mandates a variety of artifacts and activities in the software development. It works intimately with a separate risk management process, and quality management system.

ANSI/IEC 62304

Like IEC 60730, it divides software into three categories of safety:

- Class A are the functions that pose no risk of injury

- Class B are the functions that pose a "non-serious" risk of injury

- Class C are the functions that could result in death or serious injury

It mandates a formal development processes, including checkpoints with formal reviews and signoffs by key personnel, assuring successful completion of all criteria.

This guidebook has been structured in such a manner to directly support software development under these standards. This includes not just software design & implementation, but the artifacts: requirements, design, and documentation.

Note: ANSI/IEC 62304 is meant to work with a risk management approach, but – unlike IEC 61508 – it is expected to be provided separately. It also expects to work with a separated defined quality management system.

#### 7.3. A SIDE NOTE ON THE ECONOMIC BENEFIT TO DEVELOPMENT

Vendors have developed support for these software functions, as these functions are employed in a many product markets. Their support is in the form of certified microcontroller self test libraries, and application notes giving guidance on how to meet these standards (especially using their libraries).

This standardization also provides a means of identifying the skills and experience needed, and thus able to find expert workers.

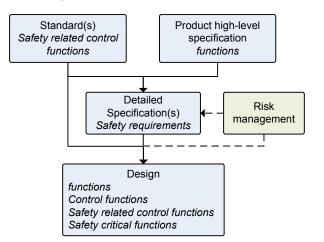

#### 7.4. THE SAFETY ELEMENTS

The standards atomize – with respect to behaviour and element of electronics and software – the product functions & requirements into:

**Figure 4:** Where key functions & requirements are identified in the process

safety-critical function

The high-level specification of the product defines the intended, primary *function* of the *function* product. The function is its role or purpose, and the operations that it is intended to perform.

The standards identify *control functions*<sup>5</sup> that are to be provided by the product and its design. *control function* The standards categorize functions along three axes:

- Whether or not it is a control function relevant to safety (earlier this was rated as type A, B, or C);

- 2. Whether or not the function is critical to the operation of a control function used in safety

- 3. Whether or not software is responsible (at least in part) for the function

#### This becomes:

Safety-related control functions are a type of control function that prevents unsafe conditionssafety-related controland/or allows the operator to use the equipment in the intended, safe manner. In IEC 60730functionType B control functions prevent unsafe state; Type C prevents special harms. The productfunctionspecifications and design often expand the number of control functions, and elaborate theirspecific operation.

The *safety critical functions* are those functions that, should they fail, present a hazardous situation. This may be because they impair the ability for safety-related control function to fulfill its specification. The standards impose a variety of software functions to "self-check" that the microcontroller (or other programmable element) is functioning sufficiently to carry out the other functions. A safety-related control function is often (but may not be) a safety critical function, but not all safety critical functions are safety-related control functions.

When software is used to realize (i.e. implement) a safety-related control function, or a safety critical function, the standards impose a many requirements on the design and behaviour of

<sup>&</sup>lt;sup>5</sup> Function(s) can have types (or roles) such as control, filter, protection, monitoring, test, conversion, limiting, distribution, isolation, protection, and so on.

the software (and supporting electronics). This is a very good thing for quality, and this guidebook is intended to help address these.

The product and subsystem specifications are to provide a detailed set of *safety requirements*, which specify in detail the functional behaviour of the product, and each of those safety-related control functions and safety-critical functions. This is true for the functions implemented by software. The *software safety requirements* are to provide added requirements that address: