DE0 Nano SoC Kullanma Kılavuzu So C_KK C KK

User Manual: DE0-Nano-SoC_KK

Open the PDF directly: View PDF ![]() .

.

Page Count: 71

Çeviren: Mustafa UZUN Düzenleyen: Erkan ÇİL

2

DE0-Nano-SoC Kullanıcı Kılavuzu

İçindekiler :

Bölüm 1 : DE0-Nano-SoC Geliştirme Kartı

1.1 Paket İçeriği ............................................................................................................................................................... 6

DE0-Nano-SoC Paketinin içeriği: ..................................................................................................................................... 6

1.2 DE0-Nano-SoC Sistem CD .......................................................................................................................................... 7

1.3 Erişim Yardım ............................................................................................................................................................ 7

Bölüm 2 : DE0-Nano-SoC Kartı İle İlgili Bilgiler

2.1 Yerleşim ve Bileşenler ............................................................................................................................................... 8

FPGA ................................................................................................................................................................................ 9

HPS (Hard Processor Sistem) .......................................................................................................................................... 9

2.2 DE0-Nano-SoC Kartın Blok Şeması ............................................................................................................................ 9

FPGA Cihazı ................................................................................................................................................................... 10

Yapılandırma ve Hata Ayıklama(Debug) ....................................................................................................................... 10

Hafıza Birimi .................................................................................................................................................................. 10

İletişim ........................................................................................................................................................................... 11

Bağlantı Elemanları ....................................................................................................................................................... 11

ADC................................................................................................................................................................................ 11

Anahtarlar, Butonlar ve Göstergeler ............................................................................................................................. 11

Sensorler ....................................................................................................................................................................... 11

Güç ................................................................................................................................................................................ 11

Bölüm 3 : DE0-Nano-SoC Kartının Kullanımı

3.1 FPGA Yapılandırma Modu’nun Ayarları ................................................................................................................. 12

3.2 DE0-Nano-SoC üzerinde Cyclone V SoC FPGA Yapılandırma .................................................................................. 13

DE0-Nano-SoC Kartı üzerinde JTAG Zinciri ................................................................................................................ 13

FPGA Yapılandırma JTAG Modunda .......................................................................................................................... 14

FPGA Yapılandırma AS Modunda .............................................................................................................................. 17

3.3 Kart Gösterge Elemanları ........................................................................................................................................ 17

3.4 Kart Reset Elemanları .............................................................................................................................................. 18

3.5 Zaman Döngüsü ...................................................................................................................................................... 19

DE0-Nano-SoC Kullanıcı Kılavuzu

3

3.6 FPGA’ye Bağı Çevresel Birimler ............................................................................................................................... 20

3.6.1 Kullanıcı Buton’ları, Anahtar’leri ve LED’leri ........................................................................................................ 20

3.6.2 2x20 GPIO Genişleme Başlığı ............................................................................................................................... 23

3.6.3 Arduino Uno R3 Genişleme Başlığı ...................................................................................................................... 26

3.6.4 A/D Çevirici ve Analog Giriş ................................................................................................................................. 28

3.7 Hard Processor Sistem (HPS)’e bağlı Çevresel Birimler .......................................................................................... 30

3.7.1 Kullanıcı Buton’ları ve LED’leri ............................................................................................................................. 30

3.7.2 Gigabit Ethernet ................................................................................................................................................... 30

3.7.3 UART .................................................................................................................................................................... 31

3.7.4 DDR3 Hafıza ......................................................................................................................................................... 32

3.7.5 Micro SD Kart Soketi ............................................................................................................................................ 35

3.7.6 USB 2.0 OTG PHY.................................................................................................................................................. 35

3.7.7 G-Sensor ............................................................................................................................................................... 36

3.7.8 LTC bağlantısı ....................................................................................................................................................... 37

Bölüm 4 : DE0-Nano-SoC Sistem Builder

4.1 Girizgah ................................................................................................................................................................... 39

4.2 Tasarım Akışı ........................................................................................................................................................... 39

4.3 DE0-Nano-SoC Sistem Üreticisinin Kullanımı .......................................................................................................... 40

DE0-Nano-SoC Sistem Üreticisinin Kurulumu ve Çalıştırılması ................................................................................. 40

Proje İsmi Girme ....................................................................................................................................................... 41

Sistem Yapılandırma ................................................................................................................................................. 42

GPIO Genişleme ........................................................................................................................................................ 42

Proje Ayar Yönetimi .................................................................................................................................................. 43

Proje Üretimi ............................................................................................................................................................. 44

Gösterilerin Kurulumu .............................................................................................................................................. 45

Bölüm 5 : FPGA için Örnekler

5.1 DE0-Nano-SoC Fabrika Yapılandırma ...................................................................................................................... 45

Demonstration Setup, Dosyaların Konumu, ve Yönergeler ...................................................................................... 45

5.2 ADC Okuma ............................................................................................................................................................. 46

Sistem Gereksinimleri ............................................................................................................................................... 47

Gösterim Dosya Konumları ....................................................................................................................................... 47

Gösterim Kurulum ve Yönergeleri............................................................................................................................. 47

Gösterimlerin Kurulması ........................................................................................................................................... 49

4

DE0-Nano-SoC Kullanıcı Kılavuzu

Bölüm 6 : HPS SoC için Örnekler

6.1 Hello Program ......................................................................................................................................................... 49

Program Dosyası ....................................................................................................................................................... 49

Makefile .................................................................................................................................................................... 49

Derleme..................................................................................................................................................................... 50

Gösterim Kaynak Kodu .............................................................................................................................................. 50

Gösterim Kurulumu ................................................................................................................................................... 50

6.2 Kullanıcıların LED ve Butonları ................................................................................................................................ 51

Fonksiyon Blok Şeması .............................................................................................................................................. 51

GPIO Arayüzünün Blok Şeması .................................................................................................................................. 51

GPIO Kayıt Bloğu ....................................................................................................................................................... 52

Yazılım API ................................................................................................................................................................. 53

LED ve KEY Kontrolü .................................................................................................................................................. 54

Gösterim Kaynak Kodu .............................................................................................................................................. 55

Gösterim Kurulumu ................................................................................................................................................... 55

6.3 G-Sensor I2C Arabirimi ............................................................................................................................................ 56

Fonksiyon Blok Şeması .............................................................................................................................................. 56

I2C Sürücüsü ............................................................................................................................................................. 56

G-Sensor Kontrol ....................................................................................................................................................... 57

Gösterim Kaynak Kodu .............................................................................................................................................. 57

Gösterim Kurulumu ................................................................................................................................................... 58

Bölüm 7 : HPS SoC ve FGPA’in Birlikte Kullanımına Örnekler

7.1 HPS Kontrol FPGA LED ............................................................................................................................................. 59

FPGA yönetici üzerine kısa bir gözatma .................................................................................................................... 59

Fonsiyon Blok Şeması ................................................................................................................................................ 59

LED Kontrol Yazılım Tasarımı..................................................................................................................................... 60

Gösterim Kaynak Kodu .............................................................................................................................................. 61

Gösterim Kurulumu ................................................................................................................................................... 61

Bölüm 8 : EPCS Cihazını Programlama

8.1 Programlamaya Başlamadan Önce ......................................................................................................................... 63

8.2 SOF Dosyasını .JIC Dosyasına Çevirme .................................................................................................................... 63

8.3 EPCS Cihazı içine JIC Dosyası Yazma ........................................................................................................................ 68

8.4 EPCS Cihazını Temizlemek ....................................................................................................................................... 69

DE0-Nano-SoC Kullanıcı Kılavuzu

5

8.5 Nios-2-Flash-Programmer İle EPCS Cihazını Programlama ..................................................................................... 70

8.6 Nios II Boot from EPCS Aygıt in Quartus II v13.1veya later .................................................................................... 70

Bölüm 9 : EK: A

9.1 DE0-Nano-SoC kiti ile Atlas-SoC kiti arasında ne fark var? ..................................................................................... 71

6

DE0-Nano-SoC Kullanıcı Kılavuzu

Bölüm 1

DE0-Nano-SoC Geliştirme Kartı

DE0-Nano-SoC Geliştirme Kartı olağanüstü tasarım esnekliği için son teknoloji çift çekirdekli Cortex-A9 gömülü

işlemcileriyle endüstri temelli programlanabilir mantığı birleştiren Altera Sistem-on-Chip (SoC) FPGA ile sağlam bir

yazılım tasarım platformu inşa etme imkânı sunar. Şimdi kullanıcılar yüksek bir performanslı az enerjili bir sistem ile

gücün muazzaam yeniden yapılandırılabilir çiftini güçlendirebilir. Altera’s SoC bir ARM-temelli hard processor

system (HPS) işlemciden meydana gelmektedir, çevresel birimler ve hafıza arabirimleri ile sorunsuz bağlı bir FPGA

yüksek bant genişlikli ara bağlantı kuran bir omurga içerir. DE0-Nano-SoC geliştirme kartları yüksek hızlı DDR3

hafıza, analog ve digital işlevler, ethernet bağlantısı ve daha birçok ilgi çekici uygulamalar ile donatılmıştır.

DE0-Nano-SoC Geliştirme Kartı Microsoft Windows XP ya da daha ileri modellerle çalışan bilgisayarlarla

çalışmak için gerekli olan bütün araçları içerir.

Bütün bunlara ek olarak, DE0-Nano-SoC Kit Altera’nın Rockboard.org isimli Linux topluluğunda

(http://www.rocketboards.org/atlas-soc) Atlas-SoC Kit olarak bilinir.DE0-Nano-SoC Kit ve Atlas-SoC Kit tam olarak

aynı şeylerdir fakat bu topluluk DE0-Nano-SoC Kit’inden farklı geliştirme kaynakları sağlar. Bu kitin içeriği Appendix

Bölümü’nde bulunabilir.

1.1 Paket İçeriği

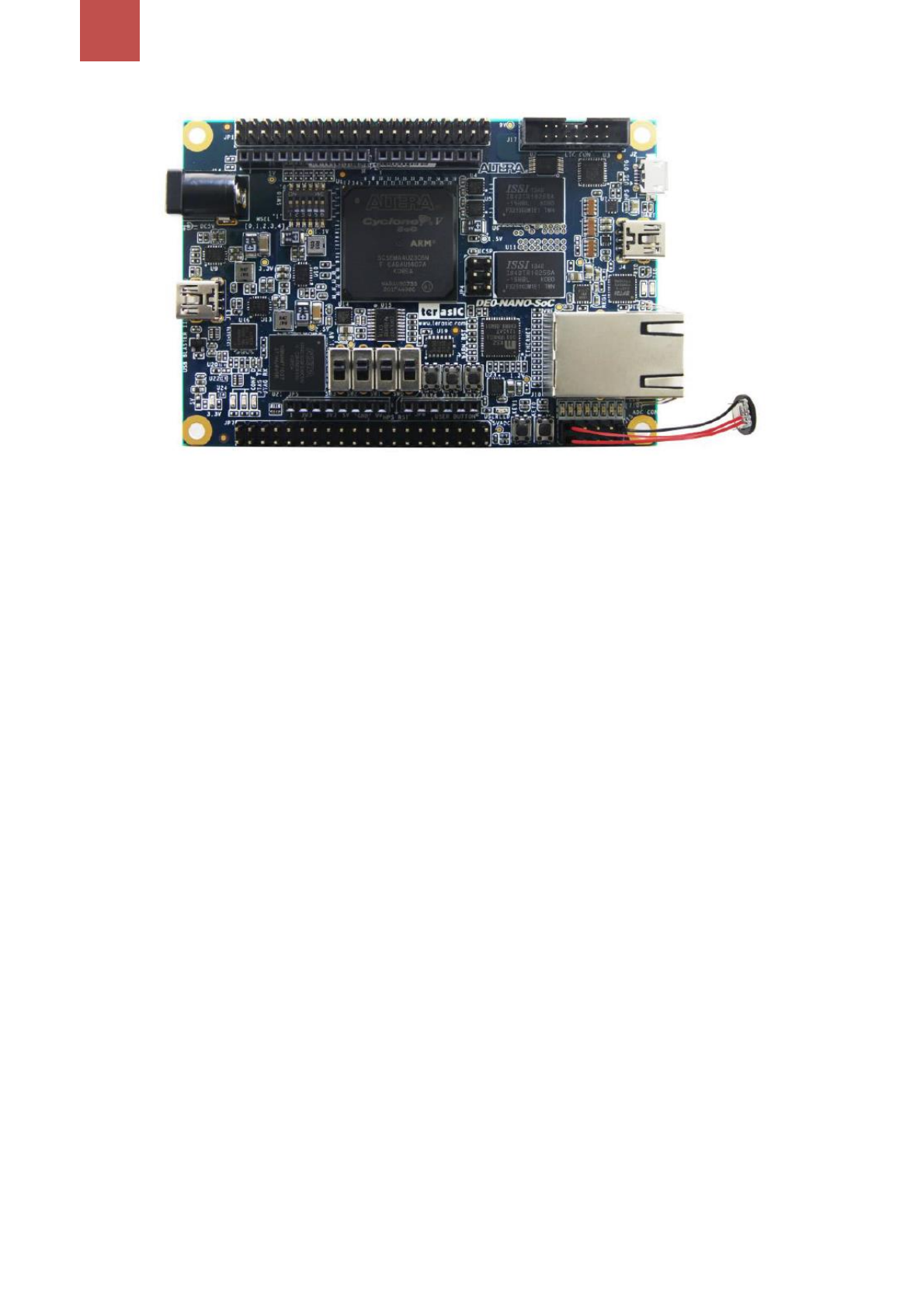

Resim 1-1 DE0-Nano-SoC Paketinin bir fotoğrafını gösteriyor.

Resim 1-1 DE0-Nano-SoC Paket İçeriği

DE0-Nano-SoC Paketinin içeriği:

DE0-Nano-SoC yazılım kartı

DE0-Nano-SoC Kolay Kullanım Kılavuzu

USB kablosu Type A to Mini-B, UART kontrol veya FPGA programlama için

USB kablosu Type A to Micro-B for USB OTG bağlamak için PC’ye

5V/2A DC güç adaptörü

4GB microSD Card (Yüklenmiş)

DE0-Nano-SoC Kullanıcı Kılavuzu

7

1.2 DE0-Nano-SoC Sistem CD

DE0-Nano-SoC Sistem CD, DE0-Nano-SoC ile ilgili kullanıcı kılavuzu, kurulum dosyaları, referans tasarımlar ve

cihaz veri sayfaları dâhil bütün belge ve yardımcı materyalleri içerir.

Kullanıcılar için Sistem CD linki: http://cd-de0-nano-soc.terasic.com.

1.3 Erişim Yardım

Herhangi bir problem ile karşılaşırsanız bu adresten bize ulaşabilirsiniz:

Altera Corporation

101 Innovation Drive San Jose, CalEğerornia, 95134 USA

Email: university@altera.com

Terasic Technologies

9F. , No.176, Sec.2, Gongdao 5th Rd, East Dist, Hsinchu City, 30070. Taiwan

Email: support@terasic.com

Tel. : +886-3-575-0880

Website: de0-nano-soc.terasic.com

8

DE0-Nano-SoC Kullanıcı Kılavuzu

Bölüm 2

DE0-Nano-SoC Kartı İle İlgili Bilgiler

Bu bölüm kartın dış özellikleri ve tasarım özellikleri ile alakalı bilgileri içerir.

2.1 Yerleşim ve Bileşenler

Resim 2-1 ve Resim 2-2 kartın üstten ve alttan bir fotoğrafını gösteriyor. Burada kilit bileşenler ve bağlantıların

kart üzerindeki yerleşimi gösteriliyor.

Resim 2-1 DE0-Nano-SoC Geliştirme Kartı (üstten)

Resim 2-2 DE0-Nano-SoC Geliştirme Kartı (alttan)

DE0-Nano-SoC Kullanıcı Kılavuzu

9

DE0-Nano-SoC Kartı kullancıya basit bir döngü yaratmaktan çeşitli multimedia projeleri oluşturmaya varan birçok

şey yapmasına imkân sağlayan birçok özelliğe sahiptir.

Takip eden yazılım kart üzerinde çalışmaktadır:

FPGA

Altera Cyclone® V SE 5CSEMA4U23C6N aygıtı

Seri yapılandırma aygıtı – EPCS128

USB-Blaster II kart üzeri programlama için; JTAG Modunda

2 buton

4 sürgülü anahtar

8 yeşil kullanıcı LED’i

Üç 50MHz saat sinyali üretecin saat sinyali kaynağı

tane

İki 40-pin genişletme başlığı

Ardunio kabuğuna bağlanabilen bir Arduino genişletme başlığı (Uno R3 compatibility),

Bir 10-pin Analog Giriş genişletme başlığı. (Arduino Analog input ile paylaşımlı)

A/D çevirici, 4-wire SPI arayüzü with FPGA

HPS (Hard Processor Sistem-Kalıcı İşlemci Sistemi)

925MHz Dual-core ARM Cortex-A9 işlemci

1GB DDR3 SDRAM (32-bit veri verialtı)

1 Gigabit Ethernet PHY with RJ45 bağlantısı

port USB OTG, USB Micro-AB bağlantısı

Micro SD card soketi

İvmeölçer (I2C arayüzü + interrupt)

UART to USB, USB Mini-B bağlantısı

Sıcak ve soğuk reset butonu

Bir kullanıcı buton ve bir kullanıcı LED’i

LTC 2x7 genişletme başlığı

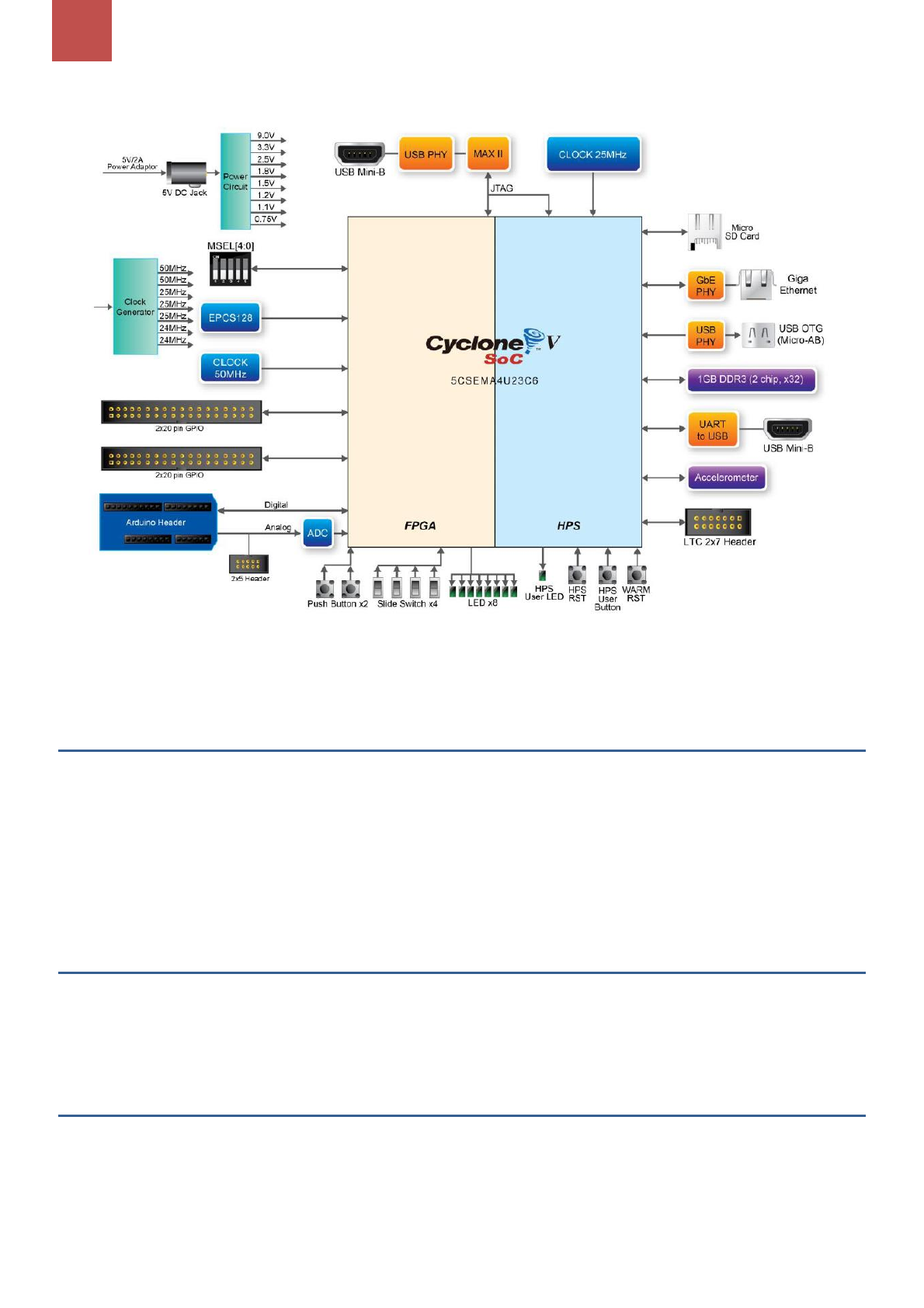

2.2 DE0-Nano-SoC Kartın Blok Şeması

Resim 2-3 kartın blok şemasını gösterir. Cyclone V SoC FPGA cihazdaki bütün bağlantılar kullanıcılara

maksimum esnekliği sağlamak için geliştirildi. Kullanıcılar hiçbir sistem yapılandırmasına gereksinim duymadan

FPGA’yı kullanabilir.

10

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 2-3 DE0-Nano-SoC’un Blok Şeması

Resim 2-3 ile alakalı detaylı bilgi aşağıda listelenmiştir.

FPGA Cihazı

Cyclone V SoC 5CSEMA4U23C6N Aygıt

Çift çekirdekli ARM Cortex-A9 (HPS)

40K programlanabilir lojik element

2,460 Kbits gömülü hafıza

5 kesirli PLLs

2 katı hafıza denetleyicisi

Yapılandırma ve Hata Ayıklama(Debug)

Seri yapılandırma aygıtı – EPCS128 on FPGA

Onboard USB-Blaster II (Mini-B USB bağlantısı)

Hafıza Birimi

1GB (2x256Mx16) DDR3 SDRAM (HPS üzerinde)

Micro SD kart soketi (HPS üzerinde)

DE0-Nano-SoC Kullanıcı Kılavuzu

11

İletişim

1 adet USB 2.0 OTG (ULPI arayüzü ile USB Micro-AB bağlacı)

UART to USB (USB Mini-B bağlaç)

10/100/1000 Ethernet

Bağlantı Elemanları

2 adet 40-pin genişletme başlığı

Arduino genişletme başlığı

Bir 10-pin ADC giriş başlığı

Bir LTC bağlantısı (bir Serial Peripheral Interface(Seri Çevrebirim Arayüzü) (SPI) Master ,bir I2C ve

bir GPIO arayüzü)

ADC

12-Bit Çözünürlük, 500Ksps Örnekleme Oranı. SPI Arayüzü.

8-Kanallı Analog Giriş. Giriş Aralığı : 0V ~ 4.096V.

Anahtarlar, Butonlar ve Göstergeler

3 kullanıcı anahtarı (FPGA x2, HPS x1)

4 kullanıcı anahtarı (FPGA x4)

9 kullanıcı LED’i (FPGA x8, HPS x 1)

2 HPS reset butonu (HPS_RESET_n ve HPS_WARM_RST_n)

Sensorler

HPS üzerinde G-Sensor

Güç

5V DC giriş

12

DE0-Nano-SoC Kullanıcı Kılavuzu

Bölüm 3

DE0-Nano-SoC Kartının Kullanımı

Bu bölümde kartın kullanımı anlatmakta ve çevresel birimler tanımlanmaktadır.

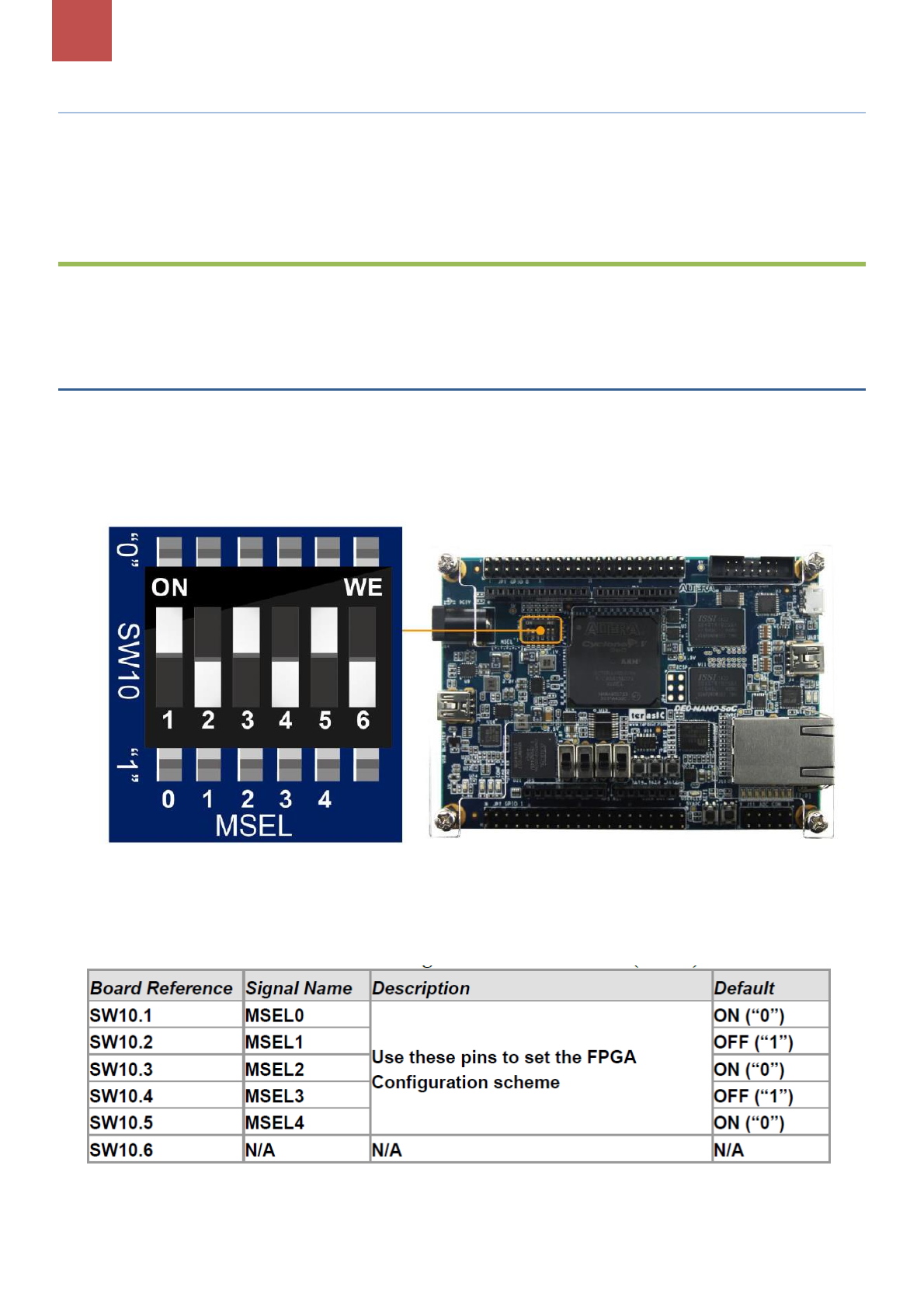

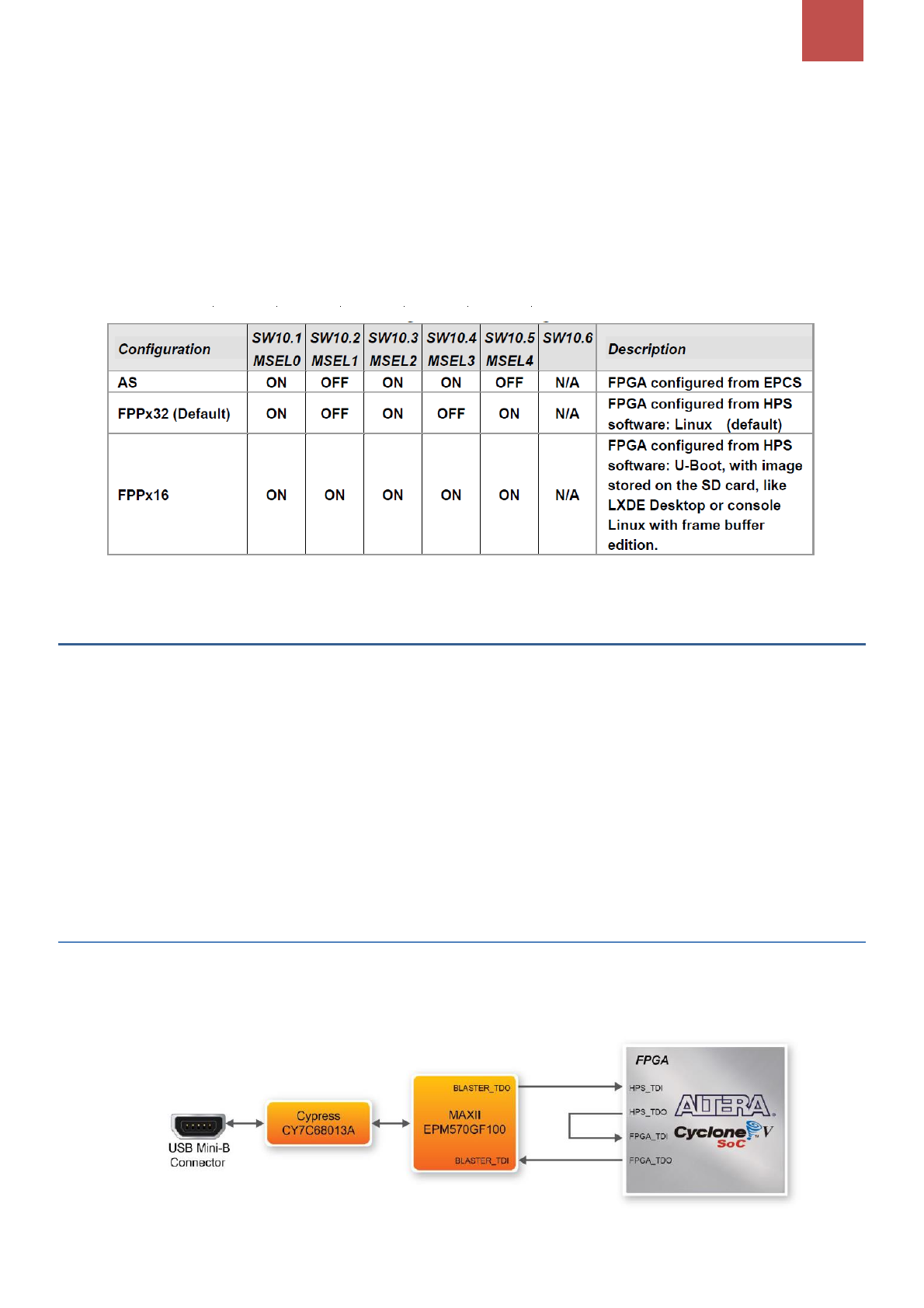

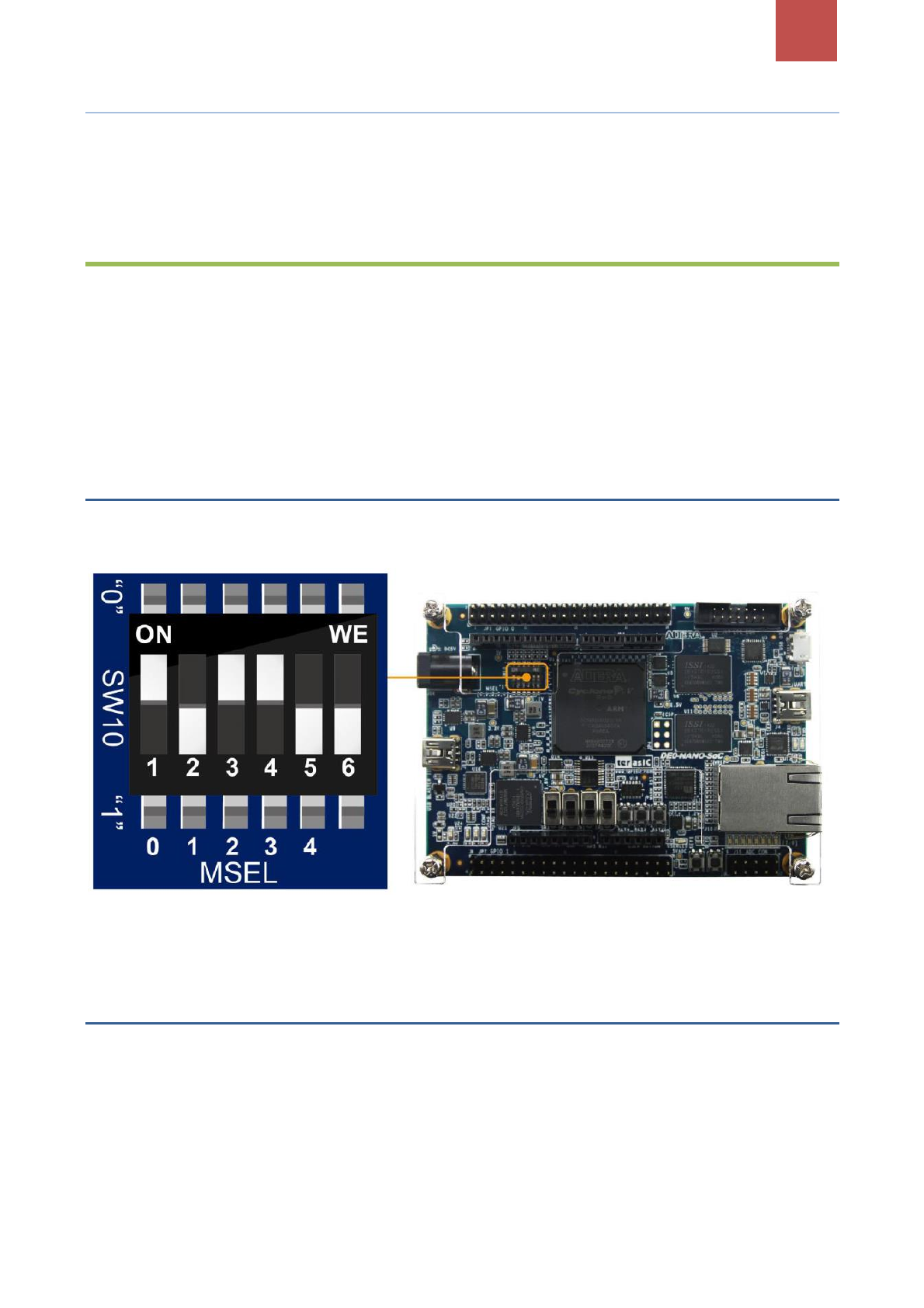

3.1 FPGA Yapılandırma Modu’nun Ayarları

DE0-Nano-SoC kartı açıldığında, FPGA EPCS veya HPS üzerinden yapılandırılır.

The MSEL[4:0] pinleri yapılandırma taslağı seçmek için kullanılır. DE0-Nano-Soc kart üzerine 6-pin DIP switch

(SW10) olarak konulmuştur(Resim 3-1).

Resim 3-1 FPP x32 Modunda’un DIP switch (SW10) ayarı

Tablo 3-1 MSEL[4:0] ve DIP switch (SW10).

Tablo 3-1 FPGA Yapılandırma Modunda Switch (SW10)

DE0-Nano-SoC Kullanıcı Kılavuzu

13

Tablo 3-2 FPGA yapılandırma için MSEL[4:0] ayarını gösterir, DE0-Nano-SoC üzerindeki FPPx32 modun

varsayılan ayarıdır.

Karta güç geldiği ve MSEL[4:0] “10010” ayarına geldiği zaman, EPCS üzerinden FPGA yapılandırma yapar,

varsayılan kod ile yarı programlıdır. Eğer geliştiriciler FPGA’yi Linux üzerinden çalışan bir aplikasyon yazılımı

aracığıyla yapılandırmak isterlerse, programlama süreci başlamadan önce MSEL[4:0] “01010” ayarına getirilmelidir.

Eğer geliştiriciler "Çerçeve Arabellek ile Linux konsolu" yada "Linux LXDE Masaüstü" SD Card imajı kullanacaksa,

karta güç gelmeden önce MSEL[4:0] “00000” olarak ayarlanmalıdır.

Tablo 3-2 MSEL Pin Settings for FPGA Yapılandırma of DE0-Nano-SoC

3.2 DE0-Nano-SoC üzerinde Cyclone V SoC FPGA Yapılandırma

DE0-Nano-SoC tarafından desteklenen iki programlama metodu vardır:

1. JTAG Metodu: İsmini IEEE standarts Joint Test Action Group’tan alır.

Yapılandırma bit akıntısı direk olarak Cyclone V SoC FPGA içine indirilir. Karta güç geldiği müddetçe FPGA içinde

saklanır; güç kesildiğinde ise konfgürasyon bilgisi kaybolur.

2. AS Metodu: Diğer bir program metodu ise Active Seri Configuration (AS) Metodudur.

Yapılandırma bit akıntısı Seri yapılandırma aygıtı (EPCS128)’in içine indirilir ki bit akışı için kalıcı depolama

sağlar. DE0-Nano-SoC kart kapalı olsa bile bilgi EPCS128 içinde tutulur. Karta güç geldiğinde, EPCS128 cihazının

içindeki yapılandırma verisi otomatik olarak Cyclone V SoC FPGA’in içine yüklenir.

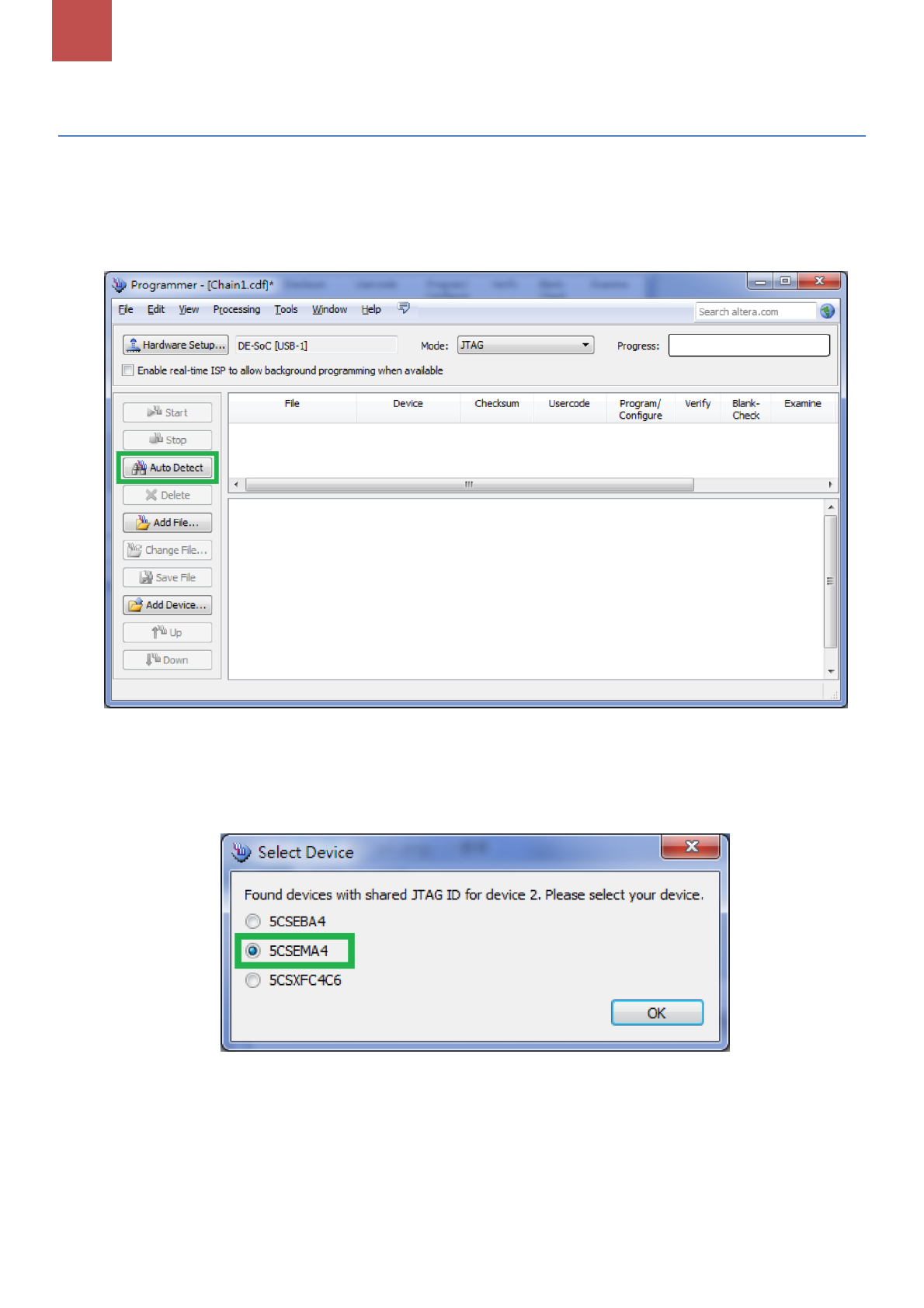

DE0-Nano-SoC Kartı üzerinde JTAG Zinciri

FPGA aygıtı DE0-Nano-SoC kartındaki JTAG arayüzü aracılığıyla yapılandırılabilir, fakat JTAG zinciri kapalı döngü

formunda olmak zorundadır ki Quartus II programlayıcı’ya FPGA cihazını saptama imkanı verir. Resim 3-2 DE0-

Nano-SoC kart üzerinde JTAG zincirine bir örnektir.

Resim 3-2 JTAG Zincirinin Şeması

14

DE0-Nano-SoC Kullanıcı Kılavuzu

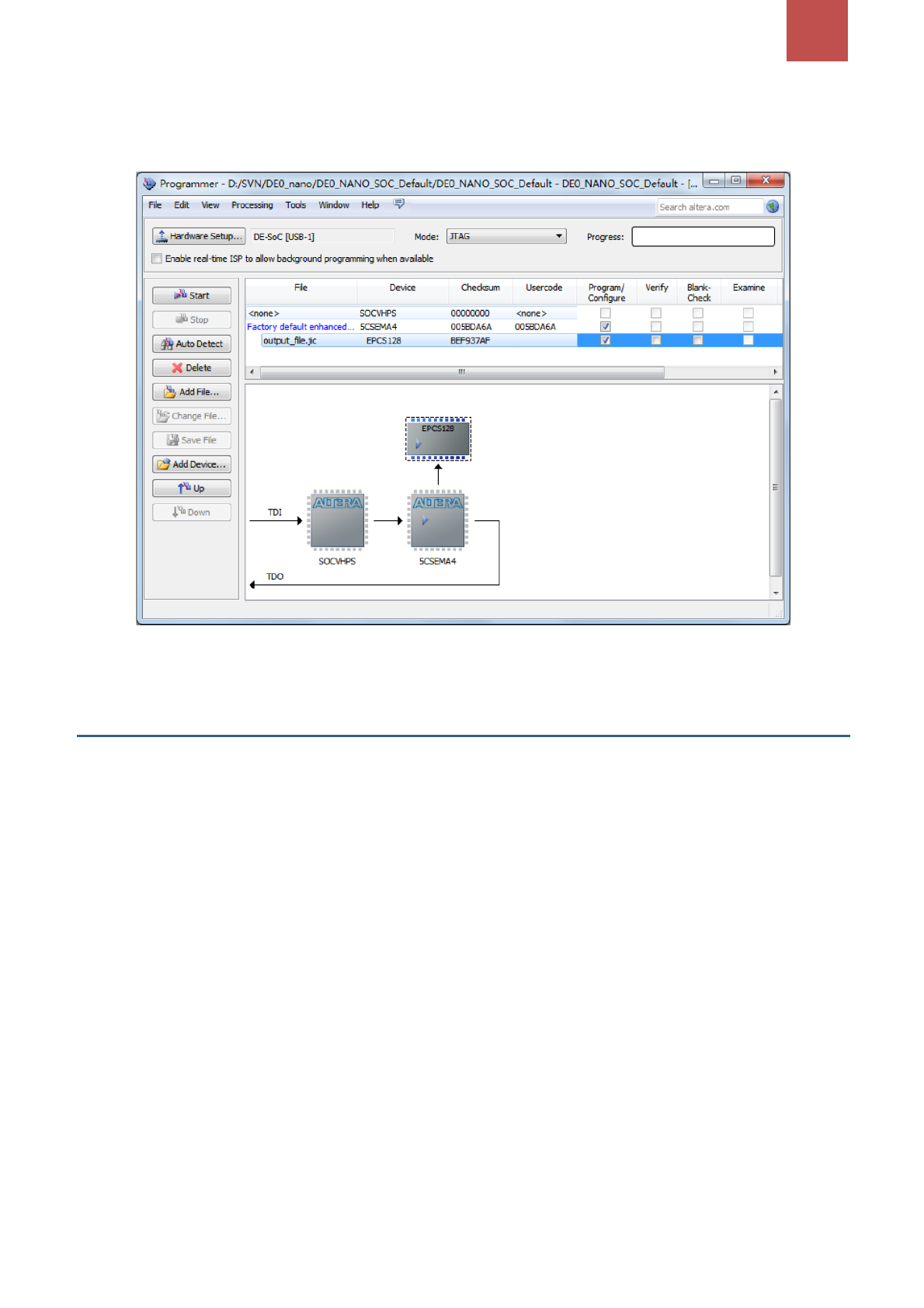

JTAG Modunda FPGA Yapılandırma

JTAG zinciri üzerinde iki tane cihaz (FPGA ve HPS) vardır. Takip eden görseller FPGA JTAG Modda nasıl

programlanır adım adım göstermektedir.

Quartus II programmer’ı aç ve “Auto Detect” seçeneğini tıkla (Resim 3-3).

Resim 3-3 JTAG modunda FPGA cihazı saptamak

Kart ile birlikte atanmış cihazı seç, (Resim 3-4).

Resim 3-4 5CSEMA4 cihazını seç

DE0-Nano-SoC Kullanıcı Kılavuzu

15

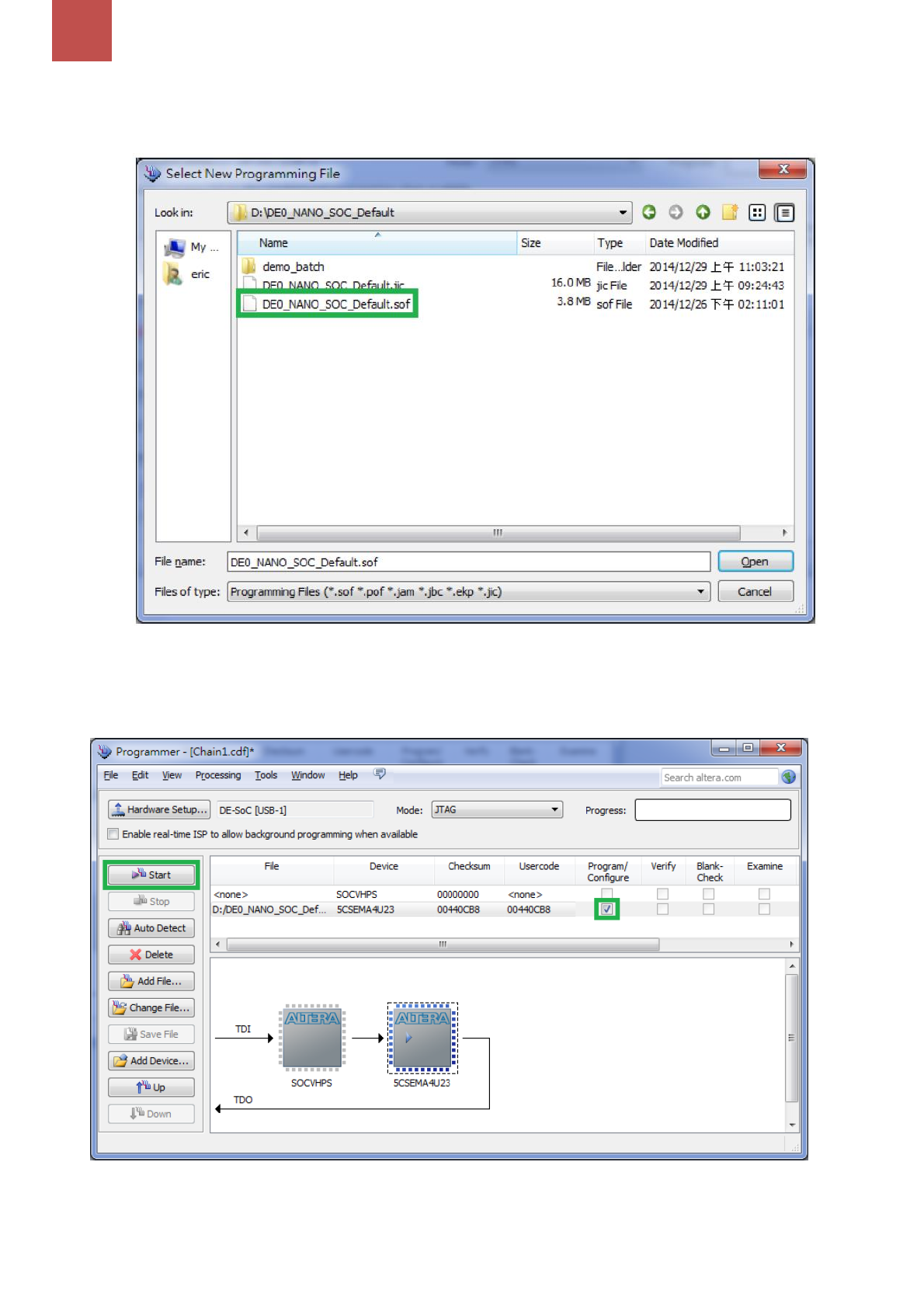

FPGA ve HPS birlikte saptanmıştır (Resim 3-5).

Resim 3-5 Quartus programmer’da FPGA ve HPS saptanmış

FPGA cihazına sağ tıklayın ve programlamak için .sof uzantılı dosyayı açın (Resim 3-6).

Resim 3-6 FPGA cihazı içine programlamak için .sof uzantılı dosyayı açın

16

DE0-Nano-SoC Kullanıcı Kılavuzu

Programlamak için .sof uzantılı dosyayı seçin (Resim 3-7).

Resim 3-7 FPGA cihazının içine programlamak için .sof uzantılı dosyayı seçin.

“Program/Yapılandırma” işaret kutusuna tıklayın sonra .sof uzantılı dosyayı FPGA cihazının içine indirmek

için “Start” butonuna tıklayın (Resim 3-8).

Resim 3-8 .sof dosyasını FPGA cihazının içine programlamak

DE0-Nano-SoC Kullanıcı Kılavuzu

17

AS Modunda FPGA Yapılandırma

DE0-Nano-SoC kartı Cyclone V SoC FPGA’ya yapılandırma verisi sunmak amacıyla bir Seri yapılandırma cihazı

(EPCS128) kullanır. Bu yapılandırma verisı karta güç geldiği anda FPGA içindeki Seri yapılandırma cihaz çipinden

otomatik olarak yüklenir.

Kullanıcılar Seri yapılandırma cihazını JTAG arayüzü yoluyla programlamak için Serial Flash Loader (SFL)

kullanmaya ihtiyaç duyarlar. FPGA-temelli-SFL, FPGA dâhilinde JTAG ve Flash arayüzleri arasında köprü vazifesi

gören bir yazılımsal fikri mülkiyet (IP) çekirdeğidir. SFL Megafonksiyonu Quartus II içinde mümkündür. Resim 3-9

SFL çözümü adapteli programlama metodunu gösteriyor.

Lütfen Bölüm 8’e bakınız: Seri Yapılandırma Cihazının Programlama Komutları için Programlama Adımları

Resim 3-9 SFL Çözümü ile bir Seri yapılandırma cihazı programlamak

3.3 Kart Gösterge Elemanları

FPGA/HPS cihazının kontrol edebildiği 9 LED’e ek olarak, kart durumunu gösterebilen 6 gösterge bulunmaktadır

(Resim 3-10), detaylı bilgi için Tablo 3-3’e bakınız.

Resim 3-10 DE0-Nano-SoC üzerinde LED Göstergeler

Tablo 3-3 LED Göstergeler

18

DE0-Nano-SoC Kullanıcı Kılavuzu

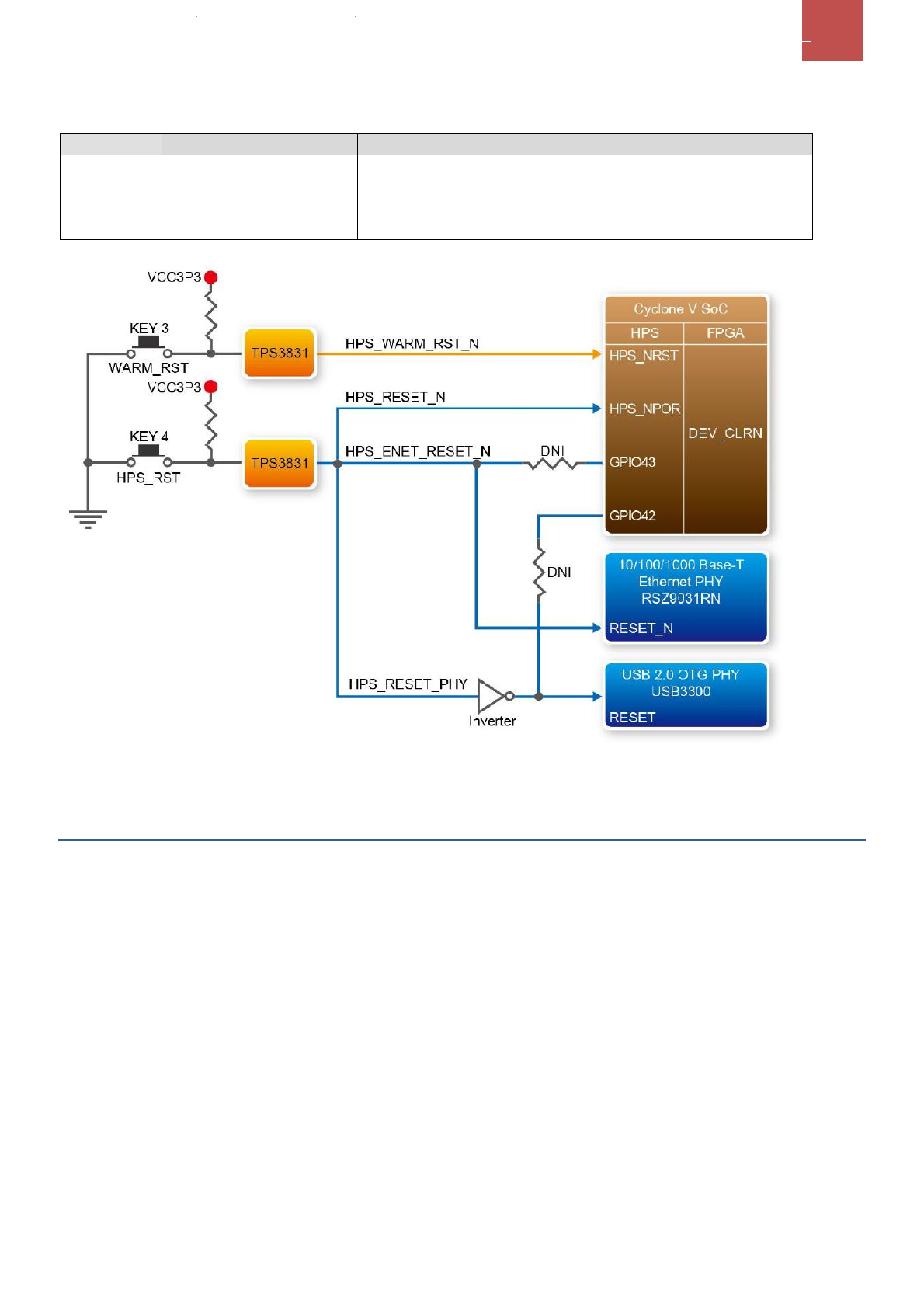

3.4 Kart Reset Elemanları

DE0-Nano-SoC üzerinde iki tane HPS reset butonu vardır, HPS (soğuk) reset ve HPS sıcak reset (Resim 3-11‘de

bu iki HPS reset butonunun görevleri tanımlanıyor. Resim 3-12’de DE0-Nano-SoC’un reset ağacı gösteriliyor.

Resim 3-11 DE0-Nano-SoC üzerindeki sıcak ve soğuk HPS reset butonları

DE0-Nano-SoC Kullanıcı Kılavuzu

19

Tablo 3-4 DE0-Nano-SoC üzerindeki 2 HPS Reset Butonunun Tanımları

Kart Referansı

Sinyal İsmi

Tanım

KEY4

HPS_RESET_N

Soğuk reset HPS, Ethernet PHY ve USB host aygıt içindir.

Aktif lojik giriş, resetlenebilen her HPS lojik sistemini resetler.

KEY3

HPS_WARM_RST_N

Sıcak reset HPS Blok içindir . Aktif düşük giriş, düzeltme

amacıyla sistemin yenileme alanını etkiler

Resim 3-12 DE0-Nano-SoC Kartı üzerinde HPS yenileme ağacı

3.5 Zaman Döngüsü

Resim 3-13 Cyclone V SoC FPGA için tüm harici saat darbelerinin varsayılan sıklıklarını gösterir . Bir saat darbesi

üreteci düşük bir sapma payı ile saat darbelerini dağıtır. FPGA’ya bağlı 50MHz’lik 2 saat darbesi kullancı mantığı için

zaman kaynağı olarak kullanılır. 3 tane 25MHz’lik saat darbesinin 2 tanesi HPS saat darbesi girişine diğeri ise Gigabit

Ethernet Transceiver’ın saat darbesi girişine bağlıdır. Bir 24MHz’lik saat darbesi FPGA ve USB Blaster II devre için

USB bağlantısına bağlıdır. Başka bir 24 MHz’lik saat darbesi ise USB OTG PHY’nin saat darbesi girişine bağlıdır. Saat

darbeleri için atanmış pin atamaları Tablo 3-5’de listelenmiştir.

20

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 3-13 DE0-Nano-SoC üzerindeki zaman dağılımının blok şeması

Tablo 3-5 Saat Darbeleri için Pin Atamaları

Sinyal İsmi

FPGA Pin No.

Tanım

I/O

Standart

FPGA_CLK1_50

PIN_V11

50 MHz saatDarbesi girişi

3.3V

FPGA_CLK2_50

PIN_Y13

50 MHz saatDarbesi girişi

3.3V

FPGA_CLK3_50

PIN_E11

50 MHz saatDarbesi girişi (share with FPGA_CLK1_50)

3.3V

HPS_CLK1_25

PIN_E20

25 MHz saatDarbesi girişi

3.3V

HPS_CLK2_25

PIN_D20

25 MHz saatDarbesi girişi

3.3V

3.6 FPGA’ye Bağı Çevresel Birimler

Bu bölümde FPGA’ye bağlı arabirimler tanımlanır. Kullanıcılar farklı arabirimleri FPGA’den kontrol edebilir ya da

görüntüleyebilirler.

3.6.1 Kullanıcı Buton’ları, Anahtar’leri ve LED’leri

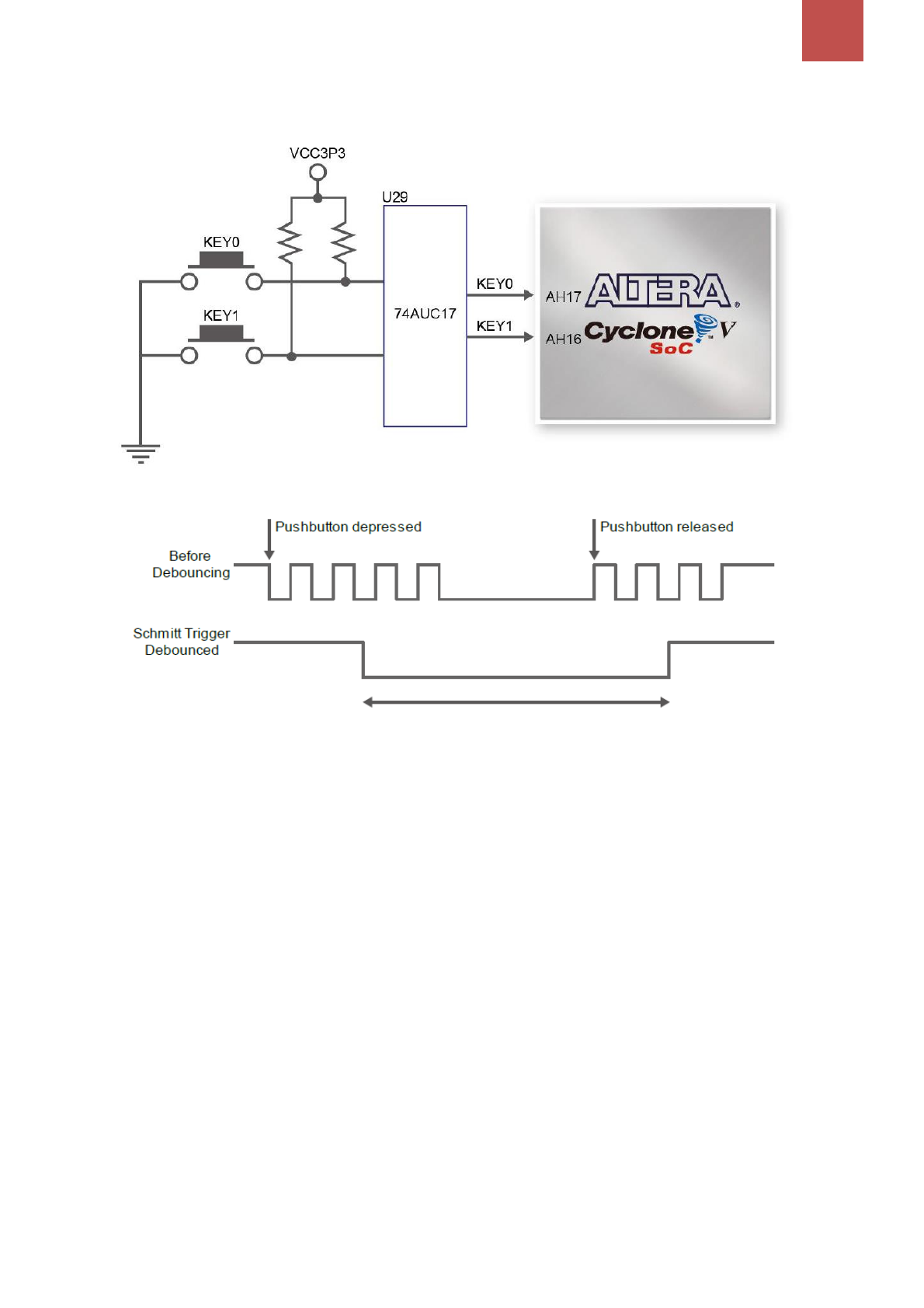

Bu kart FPGA’ye bağlı iki buton’a sahiptir (Resim 3-14’de görülüyor). Buton’lar ve Cyclone V SoC FPGA arasında

bağlantı vardır. Resim 3-15’de bağlı butonlar için Schmitt tetikleyici devresi uygulanmıştır dalga anahtarı gibi

davranmaktadır. KEY0 ve KEY1 olarak isimlendirilen bu iki buton direk olarak Cyclone V SoC FPGA’ye bağlı Schmitt

tetikleyici devresinden önce çıkmaktadır. Bu buton sıkışık ya da değilken sırasıyla yüksek ya da düşük lojik level akım

oluşturur. Butonlar filtrelendiği zaman, bir devre için zaman ya da reset girişinde olarak kullanılabilir.

DE0-Nano-SoC Kullanıcı Kılavuzu

21

Resim 3-14 Buton’lar ve the Cyclone V SoC FPGA arasındaki bağlantılar

Resim 3-15 Switch sıçrama önleyici

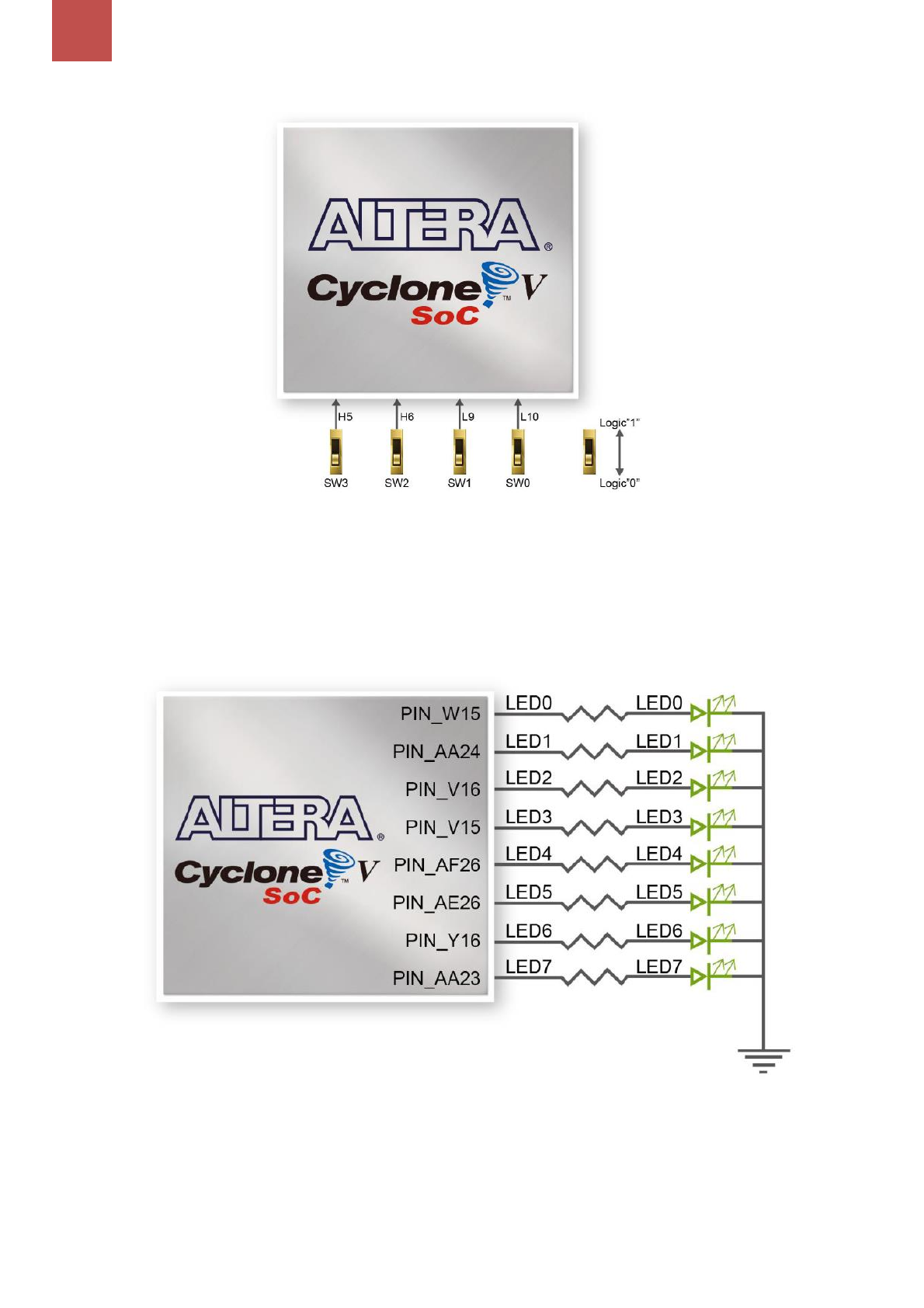

FPGA’ye bağlı 4 tane slide switch vardır (Resim 3-16). Bu anahtarlar filtrelenmemiştir ve herhangi bir devre için

hassas seviyeli veri girişi için kullanılır. Her bir switch direk ve bireysel olarak FPGA’ye bağlıdır. Switch DOWN

pozisyonuna ayarlandığı zaman (kartın ayrıtına doğru), FPGA için düşük lojik seviye oluşturur. Switch UP

pozisyonuna ayarlandığı zaman, FPGA için yüksek lojik seviye oluşturur.

22

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 3-16 Slide Anahtarı ve Cyclone V SoC FPGA arasındaki bağlantılar

Ayrıca FPGA’ye bağlı kullanıcı kontrollü 8 LED vardır. Her bir LED Cyclone V SoC FPGA tarafından direk ve

birbirinden bağımsız çalıştırılmaktadır; LED’leri yakmak veya söndürmek için atanmış pinlerini sırasıyla yüksek ya da

alçak lojik seviyeye getirmektedir. Resim 3-17 LED’ler ve Cyclone V SoC FPGA arasındaki bağlantıları

göstermektedir. Tablo 3-6, Tablo 3-7 ve Tablo 3-8 kullanıcıların buton, anahtar, ve LED’lerinin pin atamalarını

listelemektedir.

Resim 3-17 LED’ler ve Cyclone V SoC FPGA arasındaki bağlantılar

DE0-Nano-SoC Kullanıcı Kılavuzu

23

Tablo 3-6 Slide Anahtar’ler için Pin Atamaları

Sinyal İsmi

FPGA Pin No.

Tanım

I/O Standart

SW[0]

PIN_L10

Slide Switch[0]

3.3V

SW[1]

PIN_L9

Slide Switch[1]

3.3V

SW[2]

PIN_H6

Slide Switch[2]

3.3V

SW[3]

PIN_H5

Slide Switch[3]

3.3V

Tablo 3-7 Buton’lar için Pin Atamaları

Sinyal İsmi

FPGA Pin No.

Tanım

I/O Standart

KEY[0]

PIN_AH17

Buton[0]

3.3V

KEY[1]

PIN_AH16

Buton[1]

3.3V

Tablo 3-8 LED’ler için Pin Atamaları

Sinyal İsmi

FPGA Pin No.

Tanım

I/O Standart

LED[0]

PIN_W15

LED [0]

3.3V

LED[1]

PIN_AA24

LED [1]

3.3V

LED[2]

PIN_V16

LED [2]

3.3V

LED[3]

PIN_V15

LED [3]

3.3V

LED[4]

PIN_AF26

LED [4]

3.3V

LED[5]

PIN_AE26

LED [5]

3.3V

LED[6]

PIN_Y16

LED [6]

3.3V

LED[7]

PIN_AA23

LED [7]

3.3V

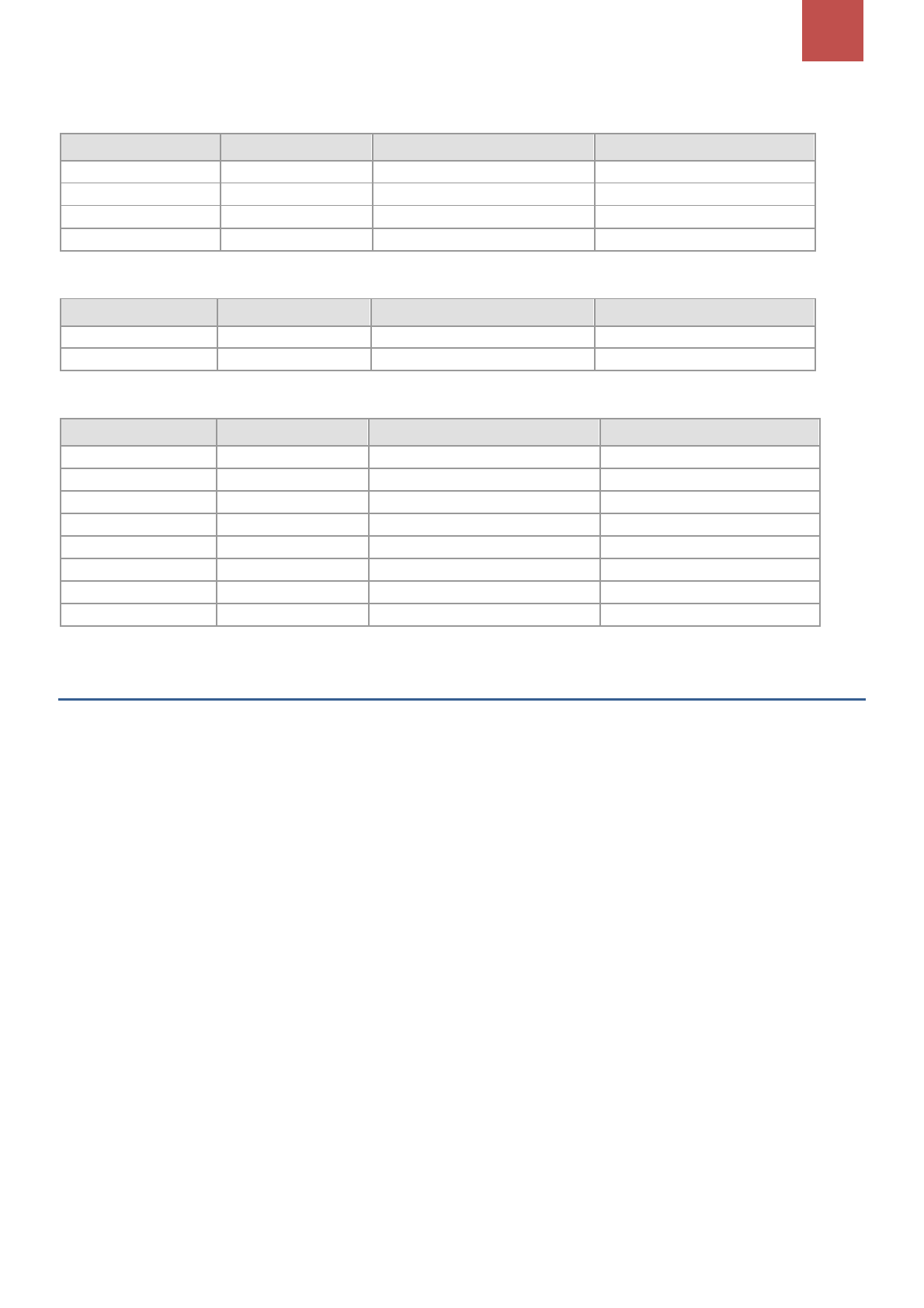

3.6.2 2x20 GPIO Genişleme Başlığı

Bu kart iki tane 40-pin genişleme başlığına sahiptir. Her bir başlık Cyclone V SoC FPGA’ya direk olarak bağlanan

36 kullanıcı pinine sahiptir. O ayrıca DC +5V (VCC5), DC +3.3V (VCC3P3) ve 2 GND pini ile geliyor. Resim 3-18 GPIO

bağlacının I/O dağıtıcısını gösteriyor. Maksimum güç tüketimi 1 ya da 2 GPIO kartına bağlanabilen bir yavru karta

izin veriyor.Tablo 3-9 ve Tablo 3-10 GPIO bağlacının bütün pin atamalarını gösteriyor.

24

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 3-18 GPIO Pin Arrangement

DE0-Nano-SoC Kullanıcı Kılavuzu

25

Tablo 3-9 Voltaj ve Genişleme başlığının belirli max. limiti(s)

Kaynak Voltaj

Belirli max. limit

5V

1A (depend on the power adapter specEğerication.)

3.3V

1.5A

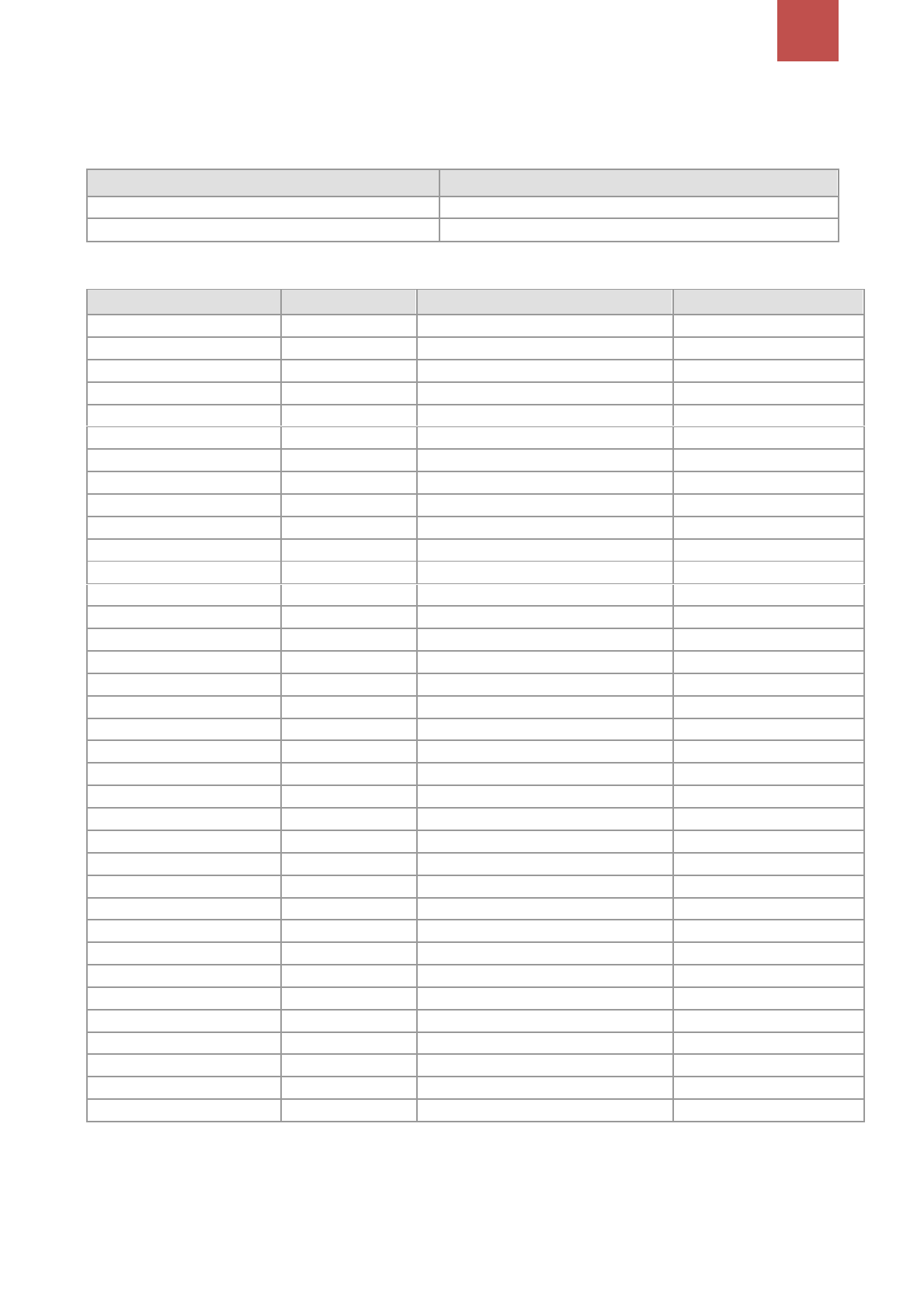

Tablo 3-10 Genişleme Başlığının Pin Atamaları

Sinyal İsmi

FPGA Pin No.

Tanım

I/O Standart

GPIO_0[0]

PIN_V12

GPIO bağlantısı 0[0]

3.3V

GPIO_0[1]

PIN_AF7

GPIO bağlantısı 0[1]

3.3V

GPIO_0[2]

PIN_W12

GPIO bağlantısı 0[2]

3.3V

GPIO_0[3]

PIN_AF8

GPIO bağlantısı 0[3]

3.3V

GPIO_0[4]

PIN_Y8

GPIO bağlantısı 0[4]

3.3V

GPIO_0[5]

PIN_AB4

GPIO bağlantısı 0[5]

3.3V

GPIO_0[6]

PIN_W8

GPIO bağlantısı 0[6]

3.3V

GPIO_0[7]

PIN_Y4

GPIO bağlantısı 0[7]

3.3V

GPIO_0[8]

PIN_Y5

GPIO bağlantısı 0[8]

3.3V

GPIO_0[9]

PIN_U11

GPIO bağlantısı 0[9]

3.3V

GPIO_0[10]

PIN_T8

GPIO bağlantısı 0[10]

3.3V

GPIO_0[11]

PIN_T12

GPIO bağlantısı 0[11]

3.3V

GPIO_0[12]

PIN_AH5

GPIO bağlantısı 0[12]

3.3V

GPIO_0[13]

PIN_AH6

GPIO bağlantısı 0[13]

3.3V

GPIO_0[14]

PIN_AH4

GPIO bağlantısı 0[14]

3.3V

GPIO_0[15]

PIN_AG5

GPIO bağlantısı 0[15]

3.3V

GPIO_0[16]

PIN_AH3

GPIO bağlantısı 0[16]

3.3V

GPIO_0[17]

PIN_AH2

GPIO bağlantısı 0[17]

3.3V

GPIO_0[18]

PIN_AF4

GPIO bağlantısı 0[18]

3.3V

GPIO_0[19]

PIN_AG6

GPIO bağlantısı 0[19]

3.3V

GPIO_0[20]

PIN_AF5

GPIO bağlantısı 0[20]

3.3V

GPIO_0[21]

PIN_AE4

GPIO bağlantısı 0[21]

3.3V

GPIO_0[22]

PIN_T13

GPIO bağlantısı 0[22]

3.3V

GPIO_0[23]

PIN_T11

GPIO bağlantısı 0[23]

3.3V

GPIO_0[24]

PIN_AE7

GPIO bağlantısı 0[24]

3.3V

GPIO_0[25]

PIN_AF6

GPIO bağlantısı 0[25]

3.3V

GPIO_0[26]

PIN_AF9

GPIO bağlantısı 0[26]

3.3V

GPIO_0[27]

PIN_AE8

GPIO bağlantısı 0[27]

3.3V

GPIO_0[28]

PIN_AD10

GPIO bağlantısı 0[28]

3.3V

GPIO_0[29]

PIN_AE9

GPIO bağlantısı 0[29]

3.3V

GPIO_0[30]

PIN_AD11

GPIO bağlantısı 0[30]

3.3V

GPIO_0[31]

PIN_AF10

GPIO bağlantısı 0[31]

3.3V

GPIO_0[32]

PIN_AD12

GPIO bağlantısı 0[32]

3.3V

GPIO_0[33]

PIN_AE11

GPIO bağlantısı 0[33]

3.3V

GPIO_0[34]

PIN_AF11

GPIO bağlantısı 0[34]

3.3V

GPIO_0[35]

PIN_AE12

GPIO bağlantısı 0[35]

3.3V

26

DE0-Nano-SoC Kullanıcı Kılavuzu

GPIO_1[0]

PIN_Y15

GPIO bağlantısı 1[0]

3.3V

GPIO_1[1]

PIN_AG28

GPIO bağlantısı 1[1]

3.3V

GPIO_1[2]

PIN_AA15

GPIO bağlantısı 1[2]

3.3V

GPIO_1[3]

PIN_AH27

GPIO bağlantısı 1[3]

3.3V

GPIO_1[4]

PIN_AG26

GPIO bağlantısı 1[4]

3.3V

GPIO_1[5]

PIN_AH24

GPIO bağlantısı 1[5]

3.3V

GPIO_1[6]

PIN_AF23

GPIO bağlantısı 1[6]

3.3V

GPIO_1[7]

PIN_AE22

GPIO bağlantısı 1[7]

3.3V

GPIO_1[8]

PIN_AF21

GPIO bağlantısı 1[8]

3.3V

GPIO_1[9]

PIN_AG20

GPIO bağlantısı 1[9]

3.3V

GPIO_1[10]

PIN_AG19

GPIO bağlantısı 1[10]

3.3V

GPIO_1[11]

PIN_AF20

GPIO bağlantısı 1[11]

3.3V

GPIO_1[12]

PIN_AC23

GPIO bağlantısı 1[12]

3.3V

GPIO_1[13]

PIN_AG18

GPIO bağlantısı 1[13]

3.3V

GPIO_1[14]

PIN_AH26

GPIO bağlantısı 1[14]

3.3V

GPIO_1[15]

PIN_AA19

GPIO bağlantısı 1[15]

3.3V

GPIO_1[16]

PIN_AG24

GPIO bağlantısı 1[16]

3.3V

GPIO_1[17]

PIN_AF25

GPIO bağlantısı 1[17]

3.3V

GPIO_1[18]

PIN_AH23

GPIO bağlantısı 1[18]

3.3V

GPIO_1[19]

PIN_AG23

GPIO bağlantısı 1[19]

3.3V

GPIO_1[20]

PIN_AE19

GPIO bağlantısı 1[20]

3.3V

GPIO_1[21]

PIN_AF18

GPIO bağlantısı 1[21]

3.3V

GPIO_1[22]

PIN_AD19

GPIO bağlantısı 1[22]

3.3V

GPIO_1[23]

PIN_AE20

GPIO bağlantısı 1[23]

3.3V

GPIO_1[24]

PIN_AE24

GPIO bağlantısı 1[24]

3.3V

GPIO_1[25]

PIN_AD20

GPIO bağlantısı 1[25]

3.3V

GPIO_1[26]

PIN_AF22

GPIO bağlantısı 1[26]

3.3V

GPIO_1[27]

PIN_AH22

GPIO bağlantısı 1[27]

3.3V

GPIO_1[28]

PIN_AH19

GPIO bağlantısı 1[28]

3.3V

GPIO_1[29]

PIN_AH21

GPIO bağlantısı 1[29]

3.3V

GPIO_1[30]

PIN_AG21

GPIO bağlantısı 1[30]

3.3V

GPIO_1[31]

PIN_AH18

GPIO bağlantısı 1[31]

3.3V

GPIO_1[32]

PIN_AD23

GPIO bağlantısı 1[32]

3.3V

GPIO_1[33]

PIN_AE23

GPIO bağlantısı 1[33]

3.3V

GPIO_1[34]

PIN_AA18

GPIO bağlantısı 1[34]

3.3V

GPIO_1[35]

PIN_AC22

GPIO bağlantısı 1[35]

3.3V

3.6.3 Arduino Uno R3 Genişleme Başlığı

Bu kart 4 bağımsız başlıkla birlikte gelen Arduino Uno revision 3 uygunluklu genişleme bağlığı sağlar.

Genişleme başlığı direk olarak Cyclone V SoC FPGA’ya bağlı 17 kullanıcı pinine (16 pin GPIO ve 1pin Reset)

sahiptir. 6 pinli analog giriş ADC’ye bağlanır ayrıca DC +9V (VCC9), DC +5V (VCC5), DC +3.3V (VCC3P3 ve

IOREF) ve 3 GND pini sağlar.

Detaylı pin çıkış bilgisi için Resim 3-19’a bakınız. Mavi font Arduino Uno R3 kartının pin çıkış

tanımlarını belirtir.

DE0-Nano-SoC Kullanıcı Kılavuzu

27

Resim 3-19 Arduino Uno bağlacının sinyal isimlerini ve pin çıkışlarını gösteriyor. Mavi font Arduino pin

çıkış tanımlaını gösteriyor.

Bu 16 GPIO pini dijital I/O için Ardunio başlığa sağlanıyor. Tablo 3-11 Arduino Uno bağlacı (dijital) ve

Cyclone V SoC FPGA ile alakalı sinyal isimlerini listeliyor.

28

DE0-Nano-SoC Kullanıcı Kılavuzu

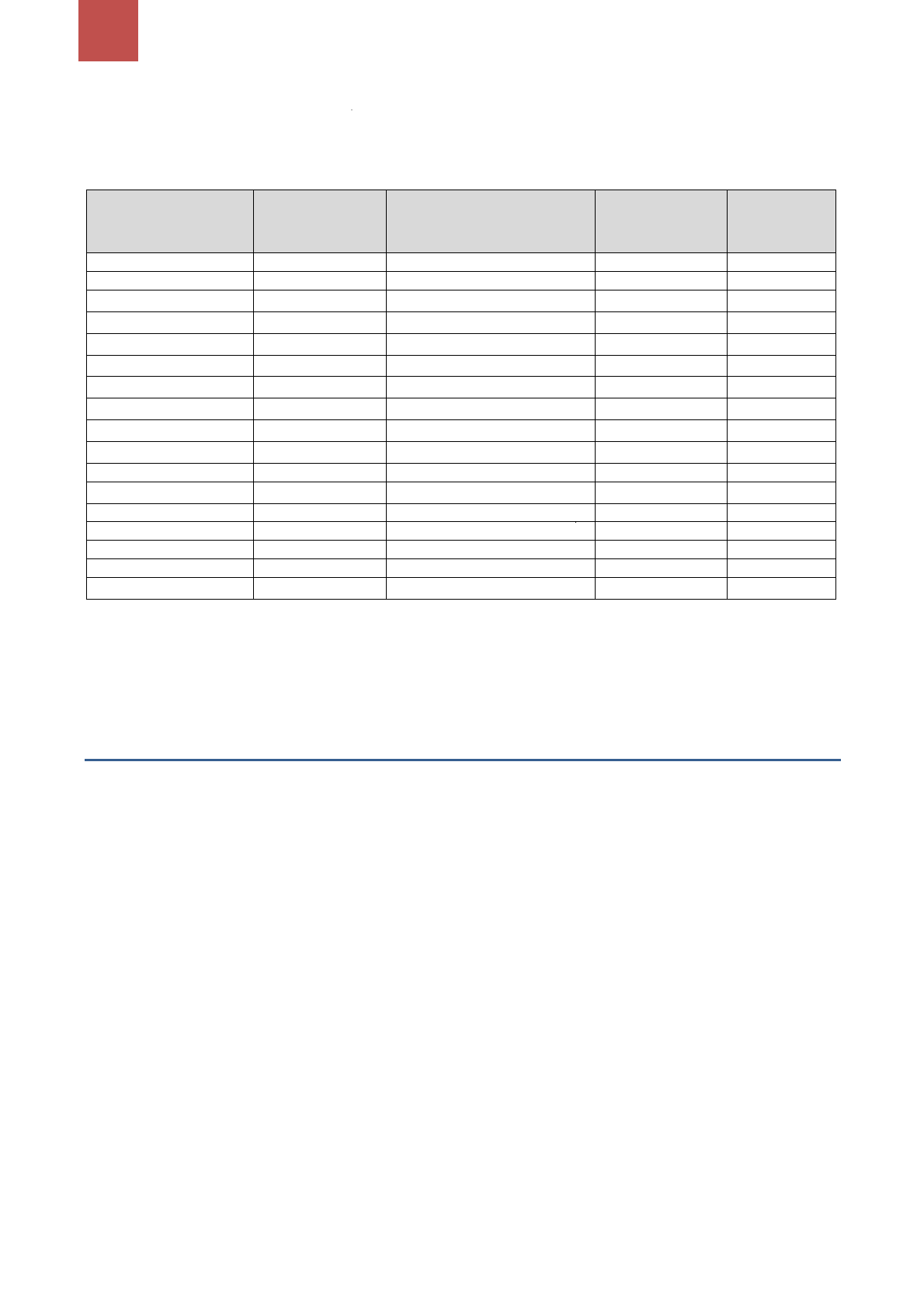

Tablo 3-11 Arduino Uno Genişleme Başlığının Pin Atamaları

Şematik Sinyal İsmi

FPGA Pin No.

Tanım

Arduino için

SpesEğerik

Özellikler

I/O Standart

Arduino_IO0

PIN_AG13

Arduino IO0

RXD

3.3-V

Arduino_IO1

PIN_AF13

Arduino IO1

TXD

3.3-V

Arduino_IO2

PIN_AG10

Arduino IO2

3.3-V

Arduino_IO3

PIN_AG9

Arduino IO3

3.3-V

Arduino_IO4

PIN_U14

Arduino IO4

3.3-V

Arduino_IO5

PIN_U13

Arduino IO5

3.3-V

Arduino_IO6

PIN_AG8

Arduino IO6

3.3-V

Arduino_IO7

PIN_AH8

Arduino IO7

3.3-V

Arduino_IO8

PIN_AF17

Arduino IO8

3.3-V

Arduino_IO9

PIN_AE15

Arduino IO9

3.3-V

Arduino_IO10

PIN_AF15

Arduino IO10

SS

3.3-V

Arduino_IO11

PIN_AG16

Arduino IO11

MOSI

3.3-V

Arduino_IO12

PIN_AH11

Arduino IO12

MISO

3.3-V

Arduino_IO13

PIN_AH12

Arduino IO13

SCK

3.3-V

Arduino_IO14

PIN_AH9

Arduino IO14

SDA

3.3-V

Arduino_IO15

PIN_AG11

Arduino IO15

SCL

3.3-V

Arduino_Reset_n

PIN_AH7

Reset signal, low active.

3.3-V

Dijital GPIO için olan 16 pinin yanısıra, Arduino Uno R3 Genişleme Başlığı üzerinde 6 analog giriş vardır

(ADC_IN0 ~ ADC_IN5). Sonuç olarak, biz gelecekteki muhtemel analogtan dijitale uygulamalar için kart

üzerindeki çizgisel teknolojiden ADC LTC2308 kullanıyoruz.Sıradaki bölümde tanışacağız.

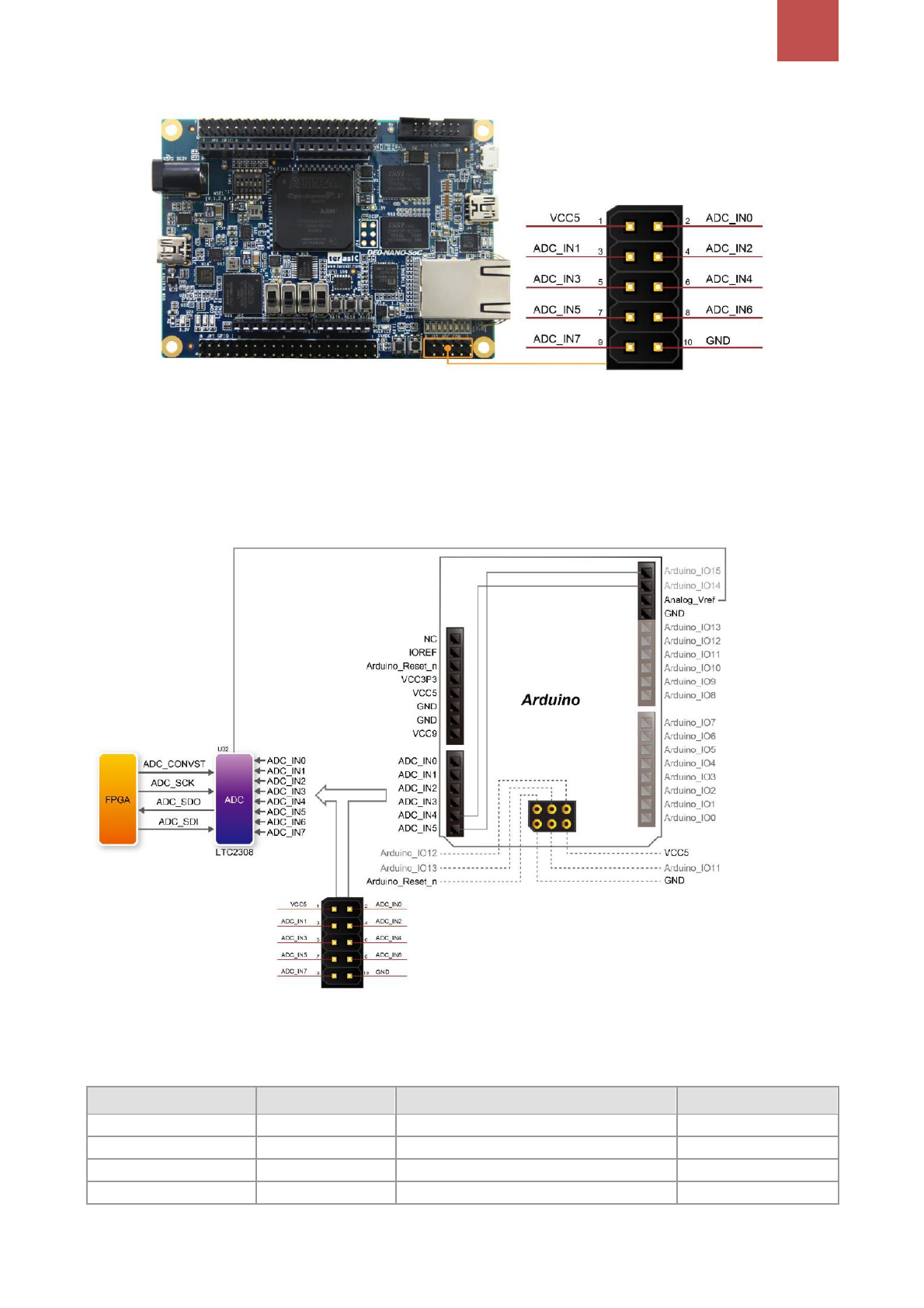

3.6.4 A/D Çevirici ve Analog Giriş

DE0-Nano-SoC bir analog-dijital dönüştürücüye sahiptir (LTC2308).

LTC2308 düşük sesli, 500ksps, 8-kanal,bir SPI/MICROWIRE ile 12-bit ADC’li uyumlu Seri bir arayüzdür.

ADC olağan mod gürültüsünü engellemek için dahili bir referans ve tamamiyle farklı örnekle-tut döngüsü

içerir. Dahili dönüşüm zamanı 40MHz üzerindeki her frekansta çalışmak için harici Seri çıkış veri zamanına

(SCK)’a izin verir.

ADC_IN0’den ADC_IN7’ye kadar 8 giriş işaretini kabul etmek için yapılandırma yapabilir. Bu 8 giriş

işareti 2x5 başlığa bağlıdır(Resim 3-20).

DE0-Nano-SoC Kullanıcı Kılavuzu

29

Resim 3-20 2x5 başlığın işaretleri

Bu analog girişler Arduino’nun analog giriş pini (ADC_IN0 ~ ADC_IN5) ile paylaşılır), Resim 3-21 FPGA,

2x5 başlığı, Arduino analog giriş ve A/D çevirici arasındaki bağlantıları gösterir.

A/D dönüştürücü çip ile ilgili daha fazla bilgi onun veri sayfasında mevcuttur. İmalatçı firmanın web

sitesinde ya da direk olarak “\Verisheet\ADC of DE0-Nano-SoC Sistem CD”

Resim 3-21 FPGA, 2x5 başlığı ve the A/D çevirici arasındaki bağlantılar

Tablo 3-12 ADC için Pin Atamaları

Sinyal İsmi

FPGA Pin No.

Tanım

I/O Standart

ADC_CONVST

PIN_U9

Dönüşüm Başlangıcı

3.3V

ADC_SCK

PIN_V10

Seri Veri Zamanı

3.3V

ADC_SDI

PIN_AC4

Seri Veri girişi (FPGA to ADC)

3.3V

ADC_SDO

PIN_AD4

Seri Veri çıkışı (ADC to FPGA)

3.3V

30

DE0-Nano-SoC Kullanıcı Kılavuzu

3.7 Hard Processor Sistem (HPS)’e bağlı Çevresel Birimler

Bu bölüm Cyclone V SoC FPGA’in HPS bölümüne bağlı arayüzler hakkında bilgi vermektedir.Kullanıcılar

bu arayüzler aracılııyla HPS işlemcisine erişebilir.

3.7.1 Kullanıcı Buton’ları ve LED’leri

FPGA’ye benzer olarak, HPS münhasıran bağlı kendi anahtarlarının, butonlarının, LED’lerinin ve diğer

arayüzlerin ayarlarına sahiptir. Kullanıcılar bu arayüzleri HPS’nin durumunu görüntülemek için kumanda

edebilir.

Tablo 3-13 tüm LED’lerin, Anahtar’lerin, ve buton’ların pin atamalarını verir.

Tablo 3-13 LED’lerin, Anahtar’lerin ve Buton’ların Pin Atamaları

Sinyal İsmi

FPGA Pin No.

HPS GPIO

Register/bit

Fonksiyon

HPS_KEY

PIN_J18

GPIO54

GPIO1[25]

I/O

HPS_LED

PIN_A20

GPIO53

GPIO1[24]

I/O

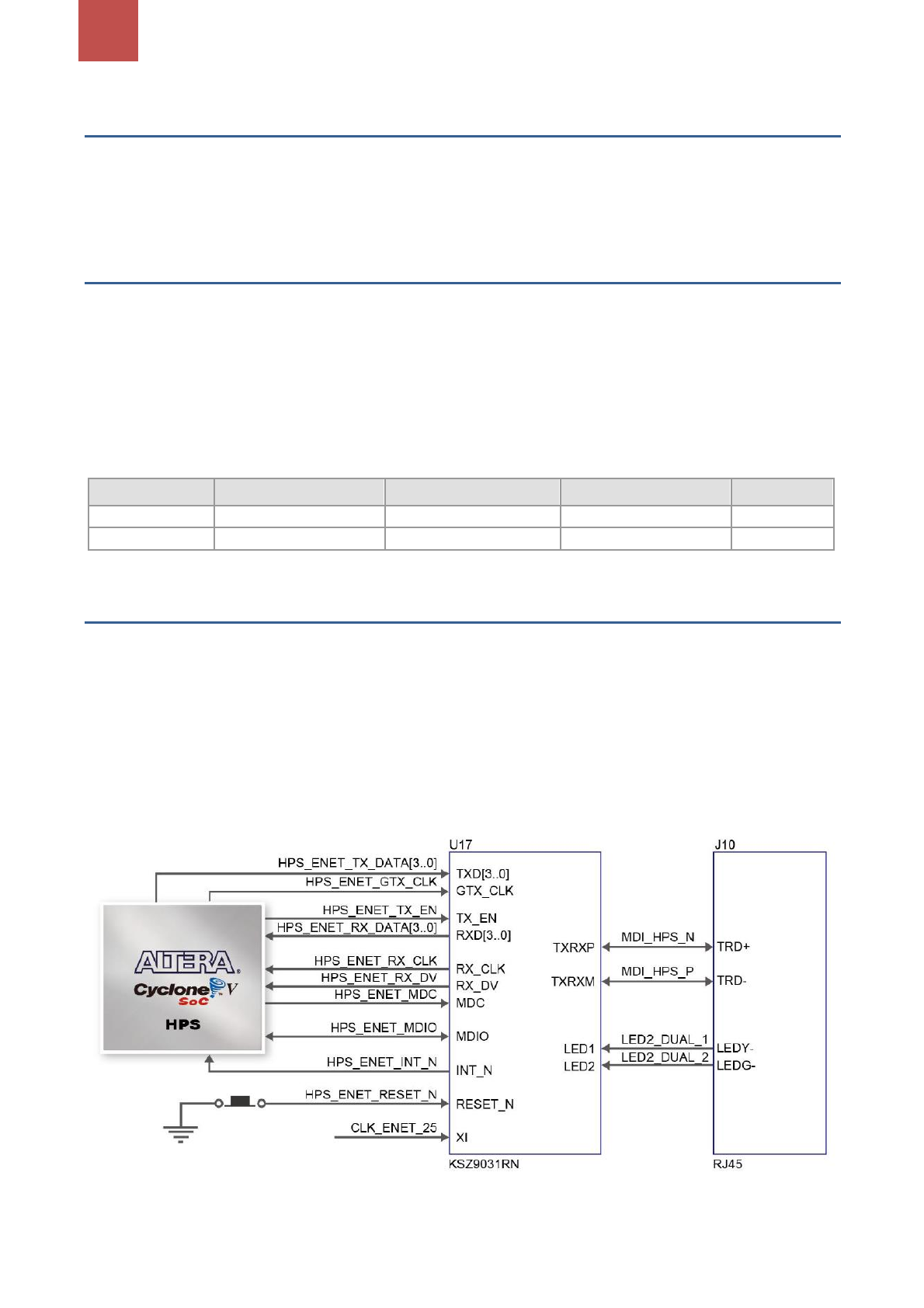

3.7.2 Gigabit Ethernet

Bu kart harici Micrel KSZ9031RN PHY çipi ve HPS Ethernet MAC fonksyonu tarafından sağlanan Gigabit

Ethernet transferini destekler. The KSZ9031RN çip ile entegre 10/100/1000 Mbps Gigabit Ethernet alıcıverici

RGMII MAC arayüzü destekler. Resim 3-22 HPS, Gigabit Ethernet PHY, ve RJ-45 bağlacı arasındaki

bağlantıları gösterir.

Gigabit Ethernet arayüzü için atanmış pin atamaları Tablo 3-14’de listelenmiştir. KSZ9031RN PHY çip ve

veri sayfası ile ilgili daha fazla üretici firmanın web sayfasında mevcuttur.

Resim 3-22 HPS ve Gigabit Ethernet arasındaki bağlantılar

DE0-Nano-SoC Kullanıcı Kılavuzu

31

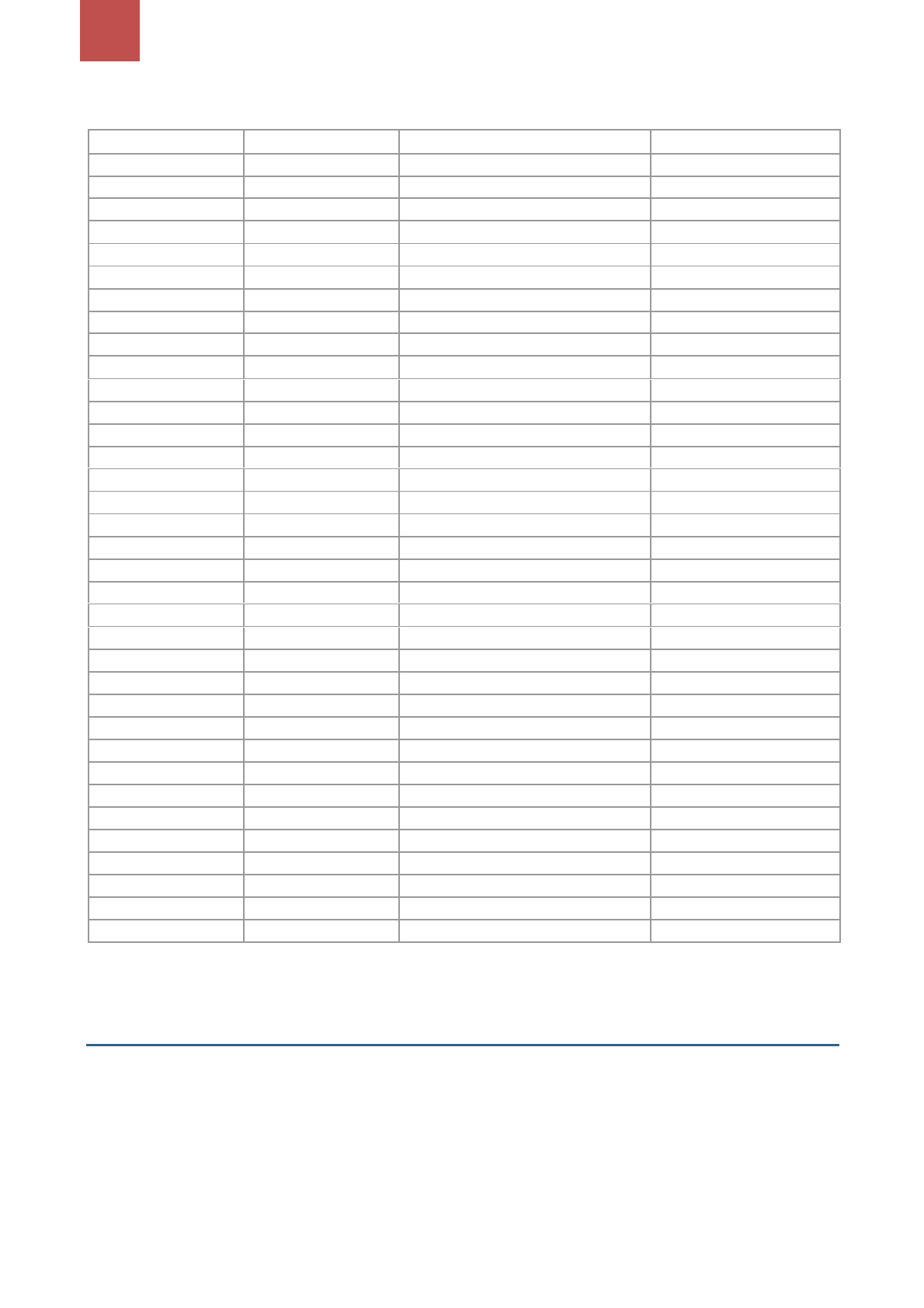

Tablo 3-14 Gigabit Ethernet PHY’nin Pin Atamaları

Sinyal İsmi

FPGA Pin No.

Tanım

I/O

Standart

HPS_ENET_TX_EN

PIN_A12

GMII ve MII transmit enable

3.3V

HPS_ENET_TX_VERİ[0]

PIN_A16

MII transmit veri[0]

3.3V

HPS_ENET_TX_VERİ[1]

PIN_J14

MII transmit veri[1]

3.3V

HPS_ENET_TX_VERİ[2]

PIN_A15

MII transmit veri[2]

3.3V

HPS_ENET_TX_VERİ[3]

PIN_D17

MII transmit veri[3]

3.3V

HPS_ENET_RX_DV

PIN_J13

GMII ve MII receive veri valid

3.3V

HPS_ENET_RX_VERİ[0]

PIN_A14

GMII ve MII receive veri[0]

3.3V

HPS_ENET_RX_VERİ[1]

PIN_A11

GMII ve MII receive veri[1]

3.3V

HPS_ENET_RX_VERİ[2]

PIN_C15

GMII ve MII receive veri[2]

3.3V

HPS_ENET_RX_VERİ[3]

PIN_A9

GMII ve MII receive veri[3]

3.3V

HPS_ENET_RX_CLK

PIN_J12

GMII ve MII receive clock

3.3V

HPS_ENET_RESET_N

PIN_B14

Donanım Reset Signal

3.3V

HPS_ENET_MDIO

PIN_E16

Management Veri

3.3V

HPS_ENET_MDC

PIN_A13

Management Veri Clock Reference

3.3V

HPS_ENET_INT_N

PIN_B14

Interrupt Open Drain Output

3.3V

HPS_ENET_GTX_CLK

PIN_J15

GMII Transmit Clock

3.3V

Ethernet PHY (KSZ9031RN)’nin statüsünü gösteren iki tane LED vardır: yeşil LED (LEDG) ve sarı LED

(LEDY). Bu LED kontrol işaretleri RJ45 bağlacı üzerindeki LED’lere bağlıdır. LEDG ve LEDY’nin durum ve

tanımları Tablo 3-15’te listelenmiştir. Örneğin, karttan Gigabit Ethernet’e olan bağlantı LEDG yandığında

kurulmuş oluyor.

Tablo 3-15 LED Modu Pinlerin Durum ve Tanımları

LED (State)

LED (Definition)

Link /Activity

LEDG

LEDY

LEDG

LEDY

H

H

OFF

OFF

Link off

L

H

ON

OFF

1000

Link / No Activity

Toggle

H

Blinking

OFF

1000

Link / Activity (RX, TX)

H

L

OFF

ON

100

Link / No Activity

H

Toggle

OFF

Blinking

100

Link / Activity (RX, TX)

L

L

ON

ON

1

10

Link/ No Activity

Toggle

Toggle

Blinking

Blinking

0

10

Link / Activity (RX, TX)

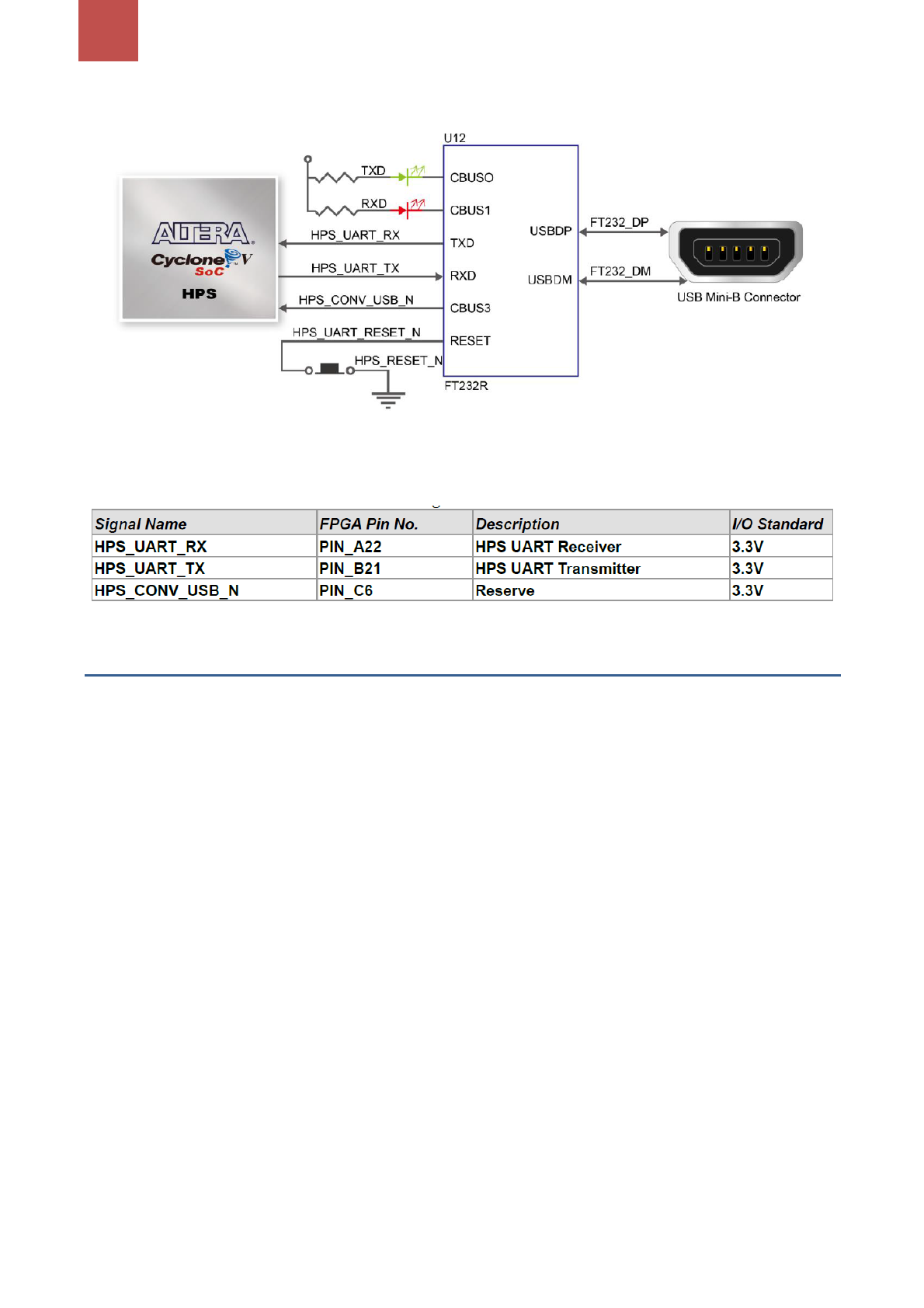

3.7.3 UART

Kart HPS ile iletişim için bağlı bir tane UART arayüze sahiptir.Bu arayüz HW akım kotrol sinallerini

desteklemiyor.Fiziksel arayüz FT232R çipinden UART-USB yerleşik köprüsü tarafından ana sistem ve bir USB

Mini-B bağlacı için yerine getiriliyor.Çip ile alakalı daha fazla bilgi için üretici firmanın websitesine bakın ya

da direk olarak “\Verisheets\UART_TO_USB of DE0-Nano-SoC Sistem CD”. Resim 3-23 HPS, FT232R çipi ve

USB Mini-B bağlacı arasındaki bağlantıları gösteriyor. Tablo 3-16 HPS’ye UART arayüzünün pin atamalarını

listeliyor.

32

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 3-23 HPS ve FT232R Çip arasındaki bağlantılar

Tablo 3-16 UART Arayüzü için Pin Atamaları

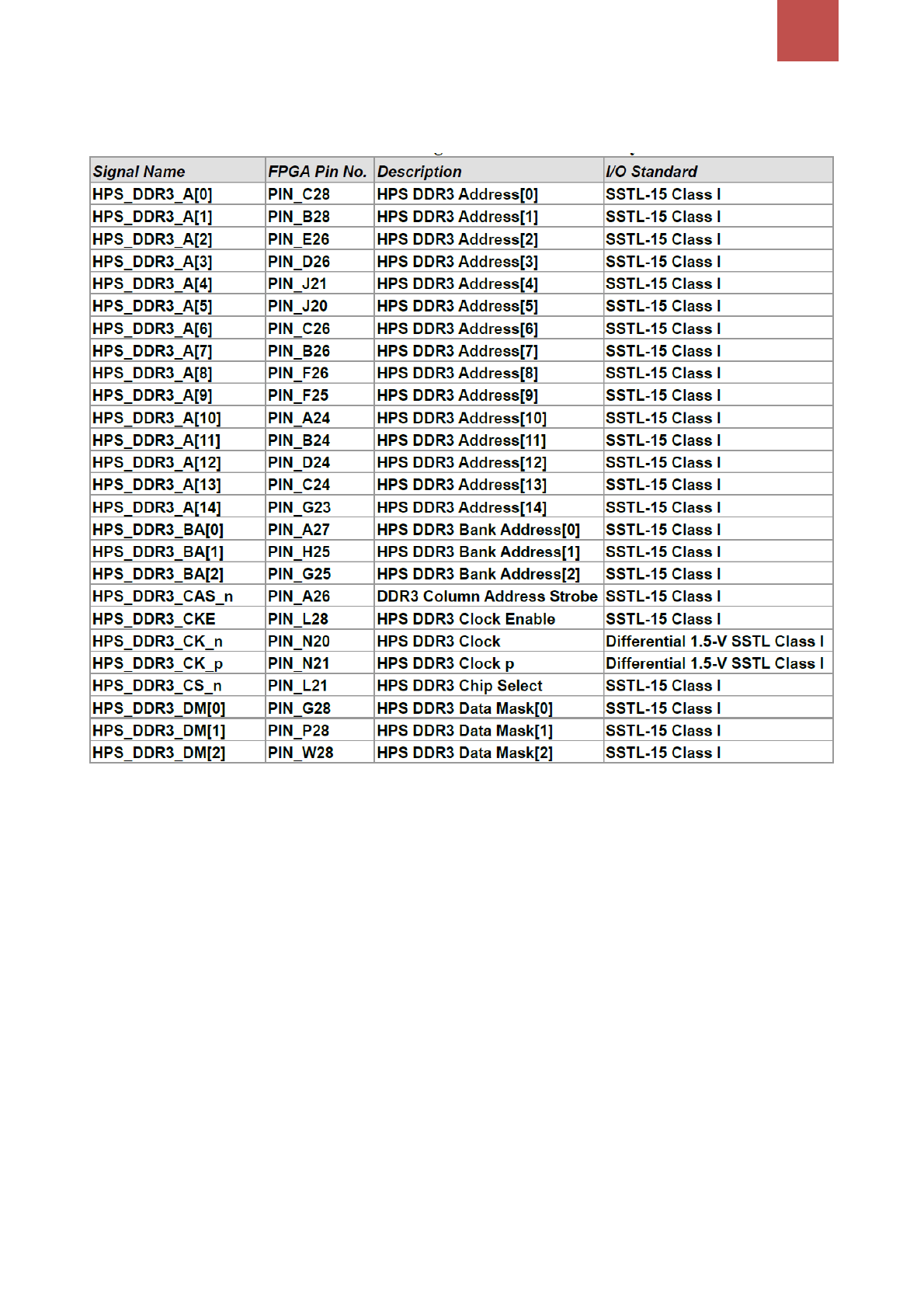

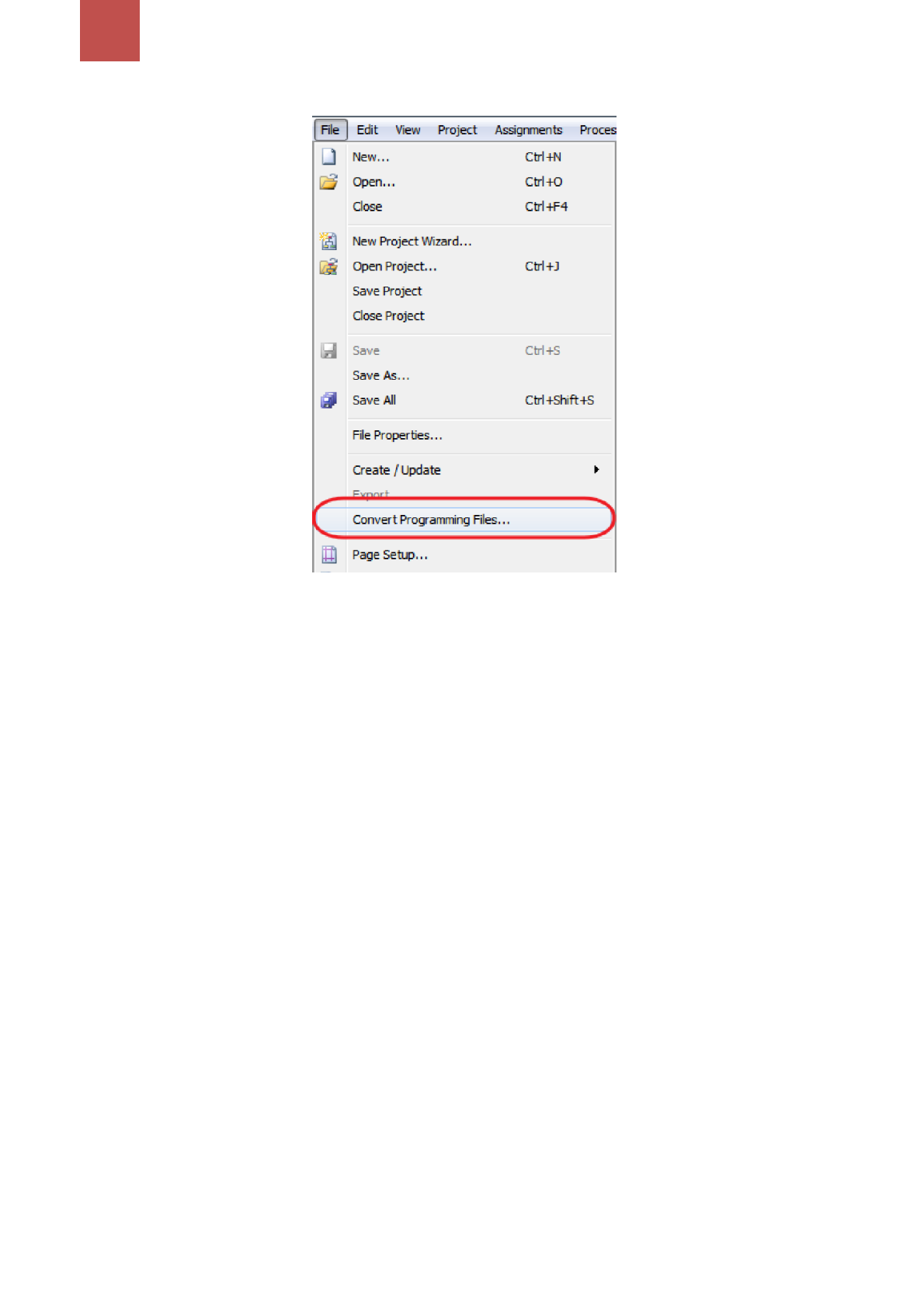

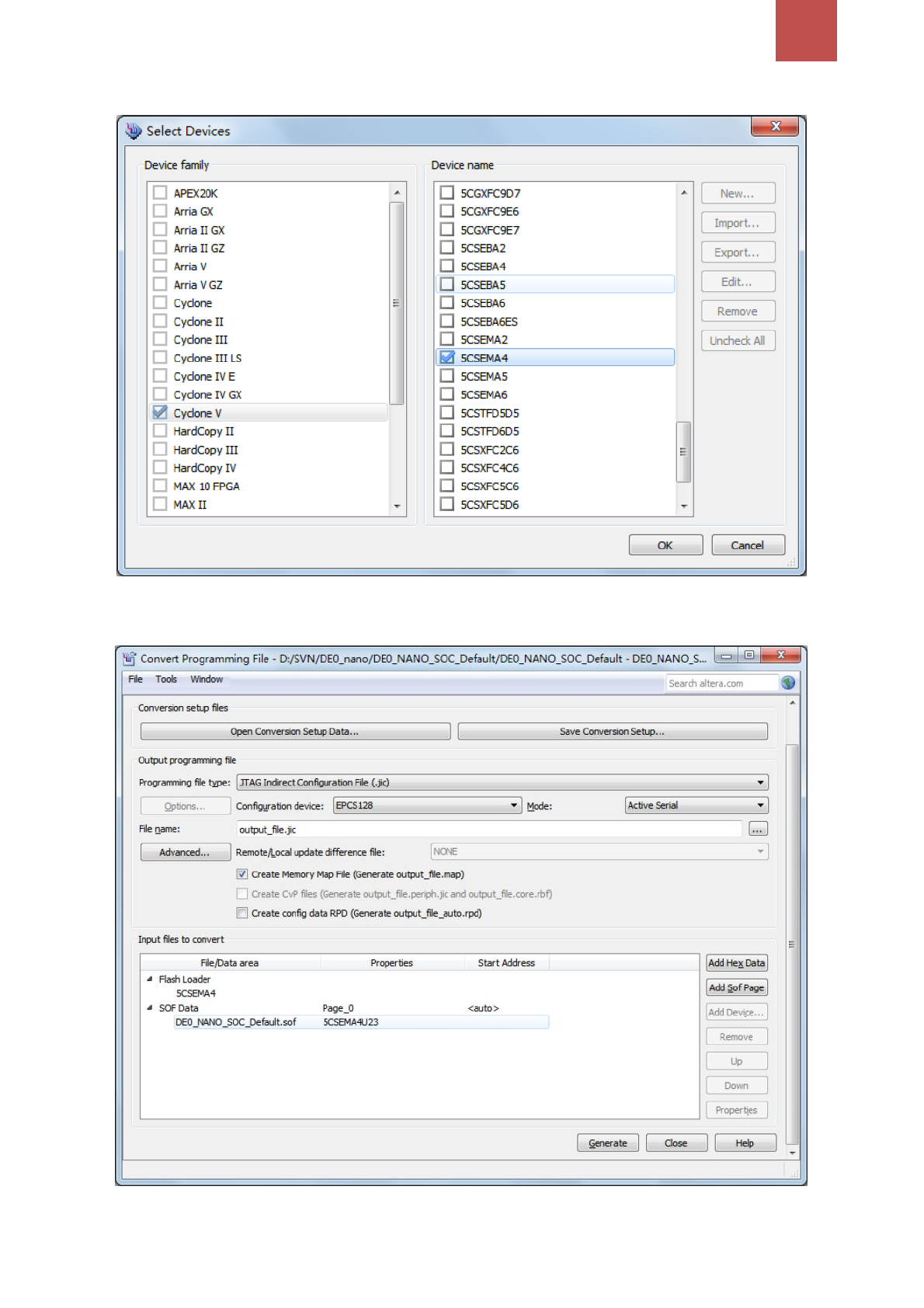

3.7.4 DDR3 Hafıza

HPS’ye bağlı DDR3 hafıza birimleri FPGA’ye bağlananlarla aynı modeldir. 1GB kapasiteli ve 32-bit’lik veri

bant genişlikli, tek adresli/komuta verialtı sürücülü 2 x16 cihaza denktir. İşaretler HPS I/O bankları için

ayrılmış Hard Memory Kontroller’a bağlıdır ve hedef hız 400 MHz’dir. Tablo 3-17 DDR3 ve onun I/O standart

tanımları için pin atamalarını göstermektedir.

DE0-Nano-SoC Kullanıcı Kılavuzu

33

Tablo 3-17 DDR3 Hafıza için Pin Atamaları

34

DE0-Nano-SoC Kullanıcı Kılavuzu

DE0-Nano-SoC Kullanıcı Kılavuzu

35

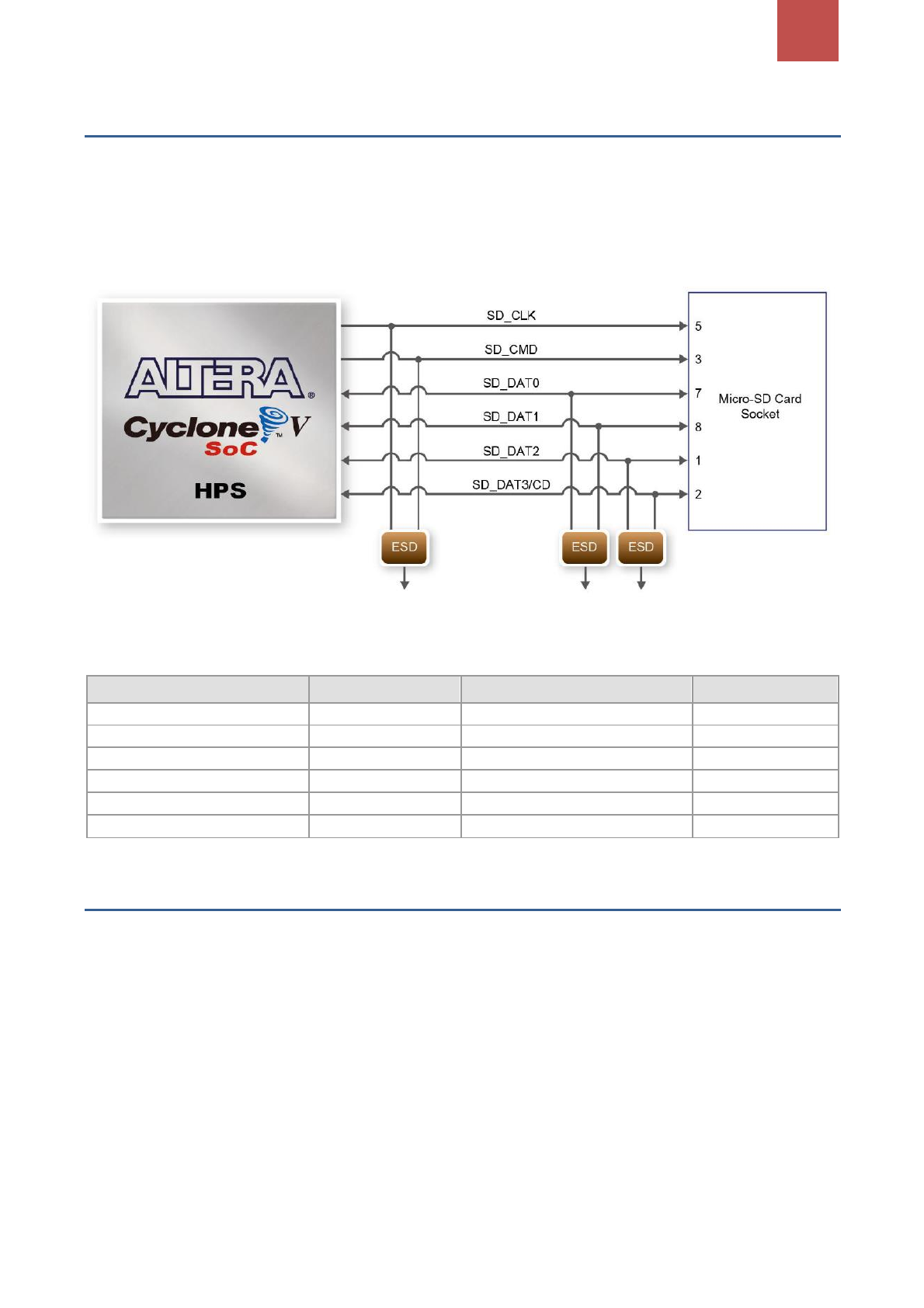

3.7.5 Micro SD Kart Soketi

Micro SD kart arayüzü ile x4 veri çizgisini desteklemektedir. HPS için harici depolama hizmetinin yanısıra

DE0-Nano-SoC kart için alternatif boot seçeneği sağlar. Resim 3-24 HPS ve Micro SD kart soketi arasındaki

sinyalleri gösterir.

Tablo 3-18 HPS için Micro SD kart soketinin pin atamalarını gösterir.

Resim 3-24 FPGA ve SD kart soketi arasındaki bağlantılar

Tablo 3-18 Micro SD Kard Soketi Pin Atamaları

Sinyal İsmi

FPGA Pin No.

Tanım

I/O Standart

HPS_SD_CLK

PIN_B8

HPS SD Clock

3.3V

HPS_SD_CMD

PIN_D14

HPS SD KomutaLine

3.3V

HPS_SD_VERİ[0]

PIN_C13

HPS SD Veri[0]

3.3V

HPS_SD_VERİ[1]

PIN_B6

HPS SD Veri[1]

3.3V

HPS_SD_VERİ[2]

PIN_B11

HPS SD Veri[2]

3.3V

HPS_SD_VERİ[3]

PIN_B9

HPS SD Veri[3]

3.3V

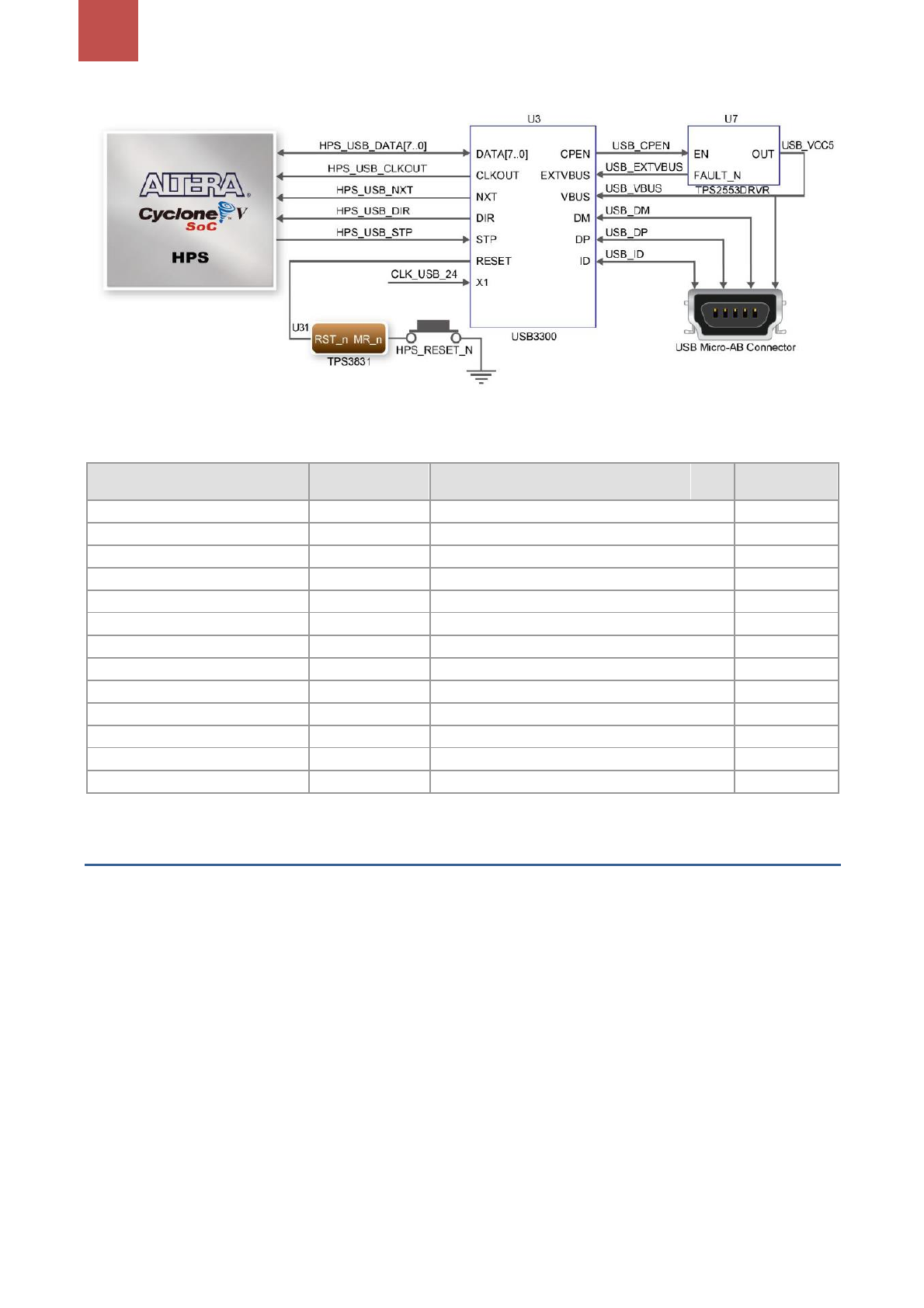

3.7.6 USB 2.0 OTG PHY

Kart SMSC USB3300 kontroller kullanımı için USB arayüz sağlar. 32-pin QFN paket cihazı içindeki SMSC

USB3300 cihazı tek tipli AB Micro-USB bağlacı için arayüz kullanır.Bu cihaz HPS’deki USB 2.0 kontroller ile

iletişime geçmek için UTMI+ Düşük Pin Arayüzü(ULPI)’nü destekler. OTG Modu tarafından tanımlanan PHY

ana sistem ya da cihaz modlarında çalışabilir. Ana sistem modunda çalışırken, arayüz cihaz için Micro-USB

arayüzü yoluyla güç sağlar. Resim 3-25 USB PTG PHY’nin HPS’ye olan bağlantılarını gösterir. Tablo 3-19 USB

OTG PHY’nin HPS için pin atamalarını listeler.

36

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 3-25 HPS ve USB OTG PHY arasındaki bağlantılar

Tablo 3-19 USB OTG PHY’nin Pin Atamaları

Sinyal İsmi

FPGA Pin

No.

Tanım

I/O

Standart

HPS_USB_CLKOUT

PIN_G4

60MHz Reference Clock Output

3.3V

HPS_USB_VERİ[0]

PIN_C10

HPS USB_VERİ[0]

3.3V

HPS_USB_VERİ[1]

PIN_F5

HPS USB_VERİ[1]

3.3V

HPS_USB_VERİ[2]

PIN_C9

HPS USB_VERİ[2]

3.3V

HPS_USB_VERİ[3]

PIN_C4

HPS USB_VERİ[3]

3.3V

HPS_USB_VERİ[4]

PIN_C8

HPS USB_VERİ[4]

3.3V

HPS_USB_VERİ[5]

PIN_D4

HPS USB_VERİ[5]

3.3V

HPS_USB_VERİ[6]

PIN_C7

HPS USB_VERİ[6]

3.3V

HPS_USB_VERİ[7]

PIN_F4

HPS USB_VERİ[7]

3.3V

HPS_USB_DIR

PIN_E5

Direction of the Data Verialtı

3.3V

HPS_USB_NXT

PIN_D5

Throttle the Data

3.3V

HPS_USB_RESET

PIN_H12

HPS USB PHY Reset

3.3V

HPS_USB_STP

PIN_C5

Stop data stream on the Verialtı

3.3V

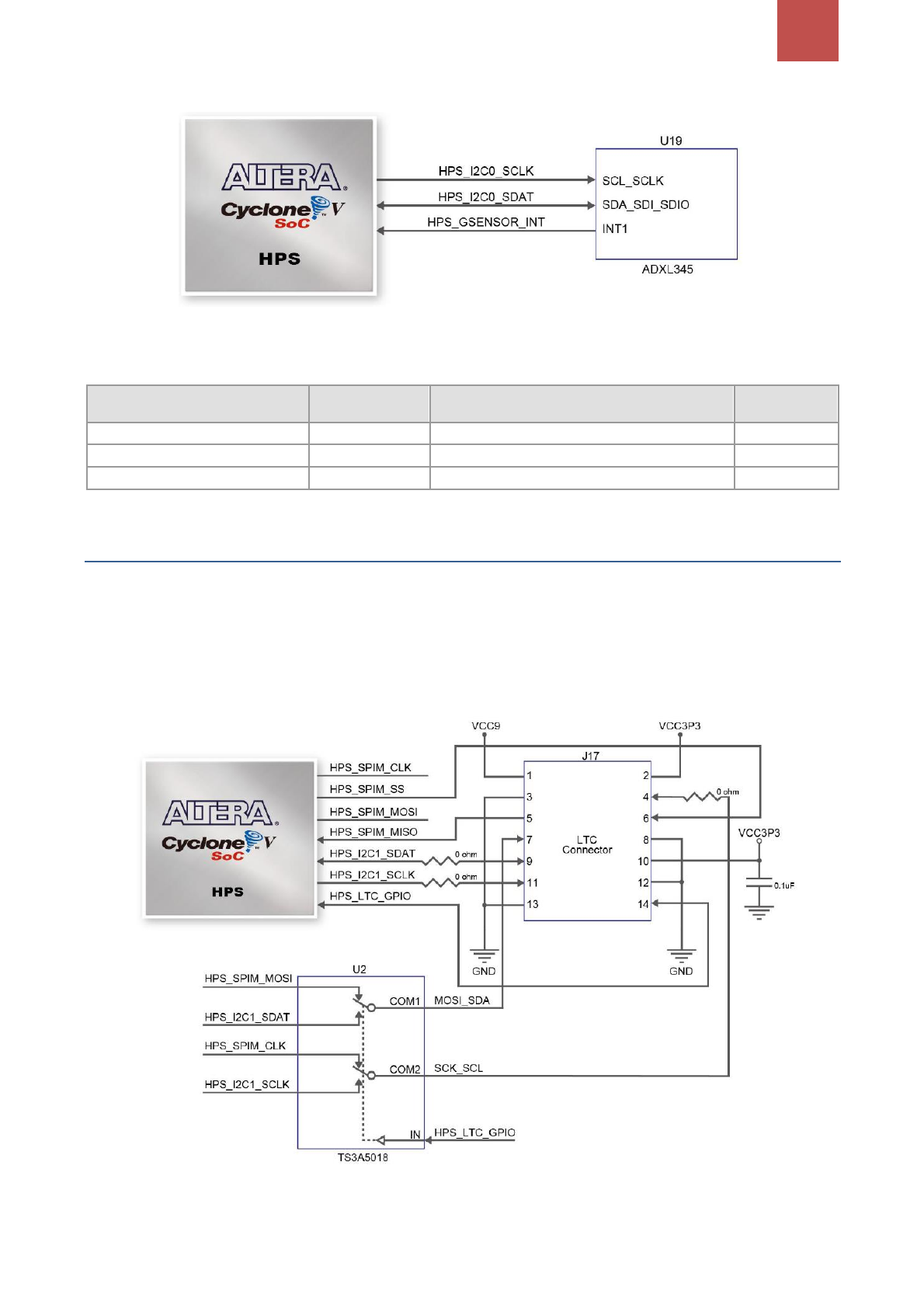

3.7.7 G-Sensor

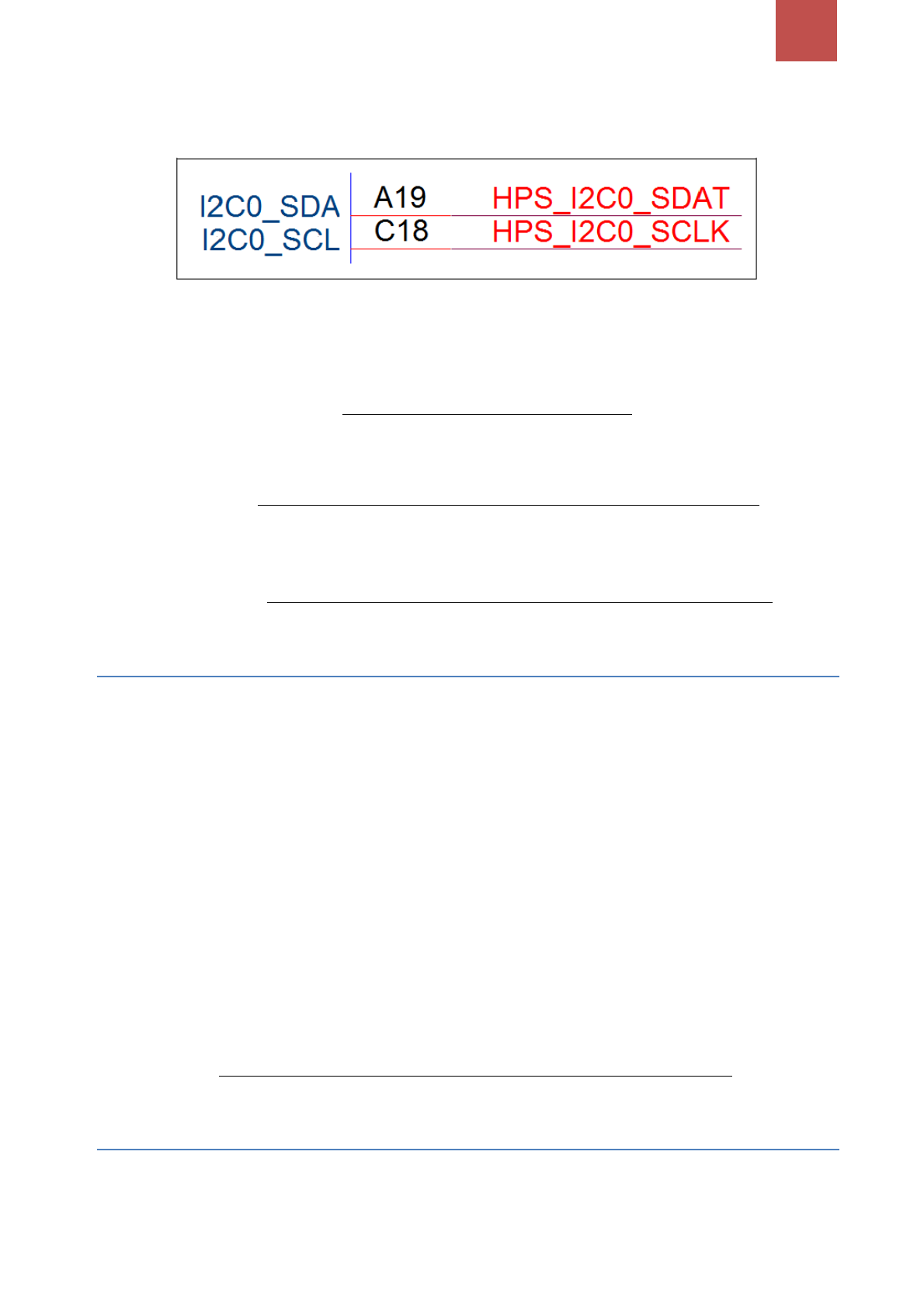

Kart genellikle G-Sensor olarak bilinen bir dijital ivmeölçer sensor modülü(ADXL345) ile geliyor. Bu G-

Sensor yüksek-çözünürlüklü ölçümü ile küçük, ince ultra düşük güç tüketimli 3-eksenli bir ivme ölçerdir.

Dijital çıkış ikisinin 16 bit tamamlayıcı olarak biçimlendirilir ve I2C arayüzü üzerinden erişilebilir. G-Sensor’ün

I2C adresi 0xA6/0xA7.Bu çip hakkında daha fazla bilgi için üretici firmanın web sitesine bakın ya da direk

olarak “\Verisheet\G-Sensor folder of DE0-Nano-SoC Sistem CD”. Resim 3-26 HPS ve G-Sensor arasındaki

bağlantıları gösteriyor. Tablo 3-20 HPS için G-Sensor pin atamaları listeleniyor.

DE0-Nano-SoC Kullanıcı Kılavuzu

37

Resim 3-26 Cyclone V SoC FPGA ve G-Sensor arasındaki bağlantılar

Tablo 3-20 G-Sensor’ün Pin Atamaları

Sinyal İsmi

FPGA Pin

No.

Tanım

I/O

Standart

HPS_GSENSOR_INT

PIN_A17

HPS GSENSOR Interrupt Output

3.3V

HPS_I2C0_SCLK

PIN_C18

HPS I2C0 Clock

3.3V

HPS_I2C0_SDAT

PIN_A19

HPS I2C0 Veri

3.3V

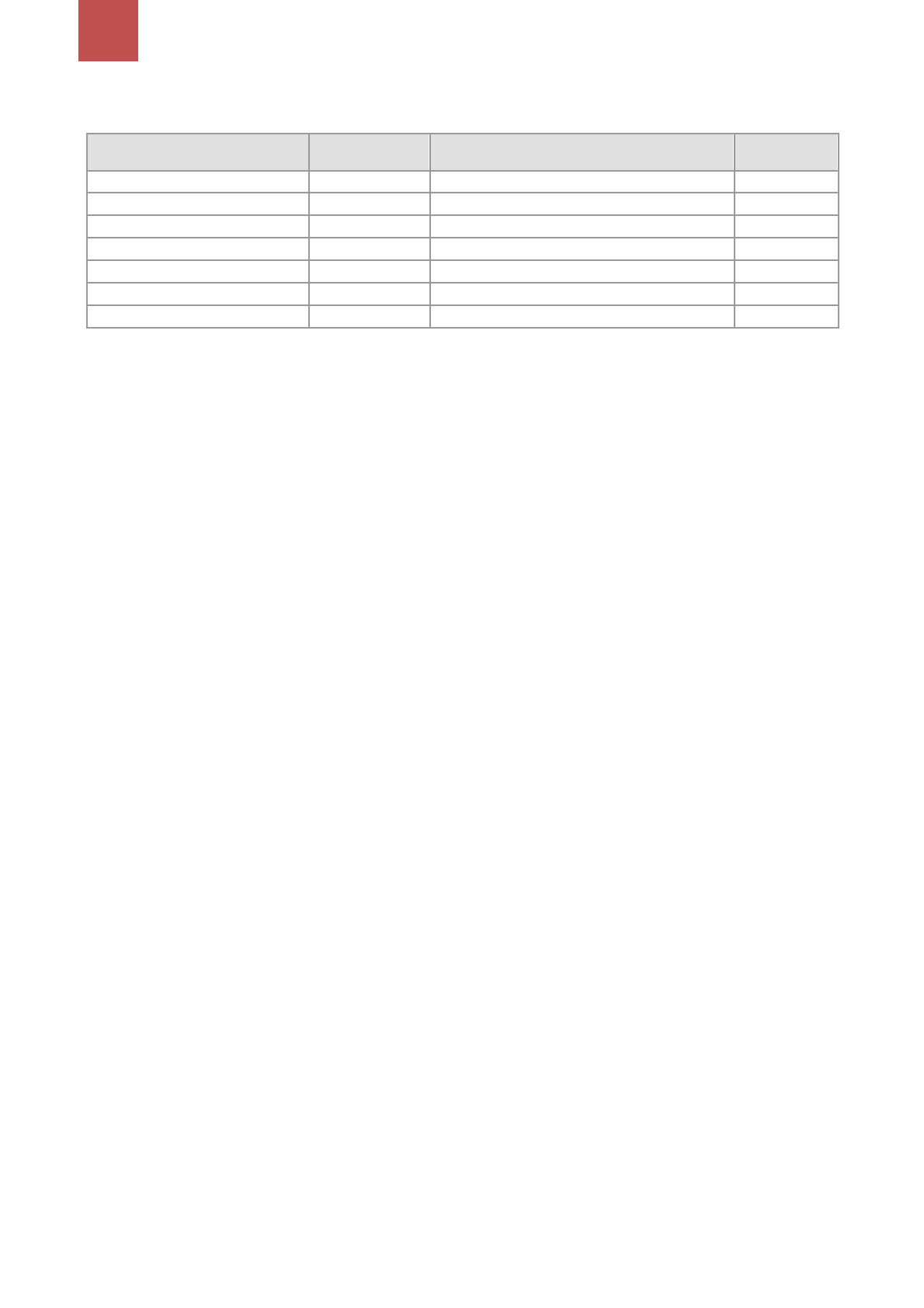

3.7.8 LTC bağlantısı

Kart esas olarak Linear Teknolojiden çeşitli yardımcı kartlarla iletişim için kullanılan 14-pinli başlığına

sahiptir. SPI Master ve HPS’nin I2C portlarına bağlıdır. Bu iki protokolle olan iletişim çift yönlüdür. Bu 14-

pinli başlık ayrıca HPS ile GPIO, SPI,veya I2C temelli iletişim için kullanılır. HPS ve LTC bağlantısı

arasındaki bağlantı Resim 3-27’de gösterilmiştir ve Tablo 3-21’de LTC bağlantısı için pin atamaları

listelenmiştir.

Resim 3-27 HPS ve LTC bağlantısı arasındaki bağlantılar

38

DE0-Nano-SoC Kullanıcı Kılavuzu

Tablo 3-21 LTC bağlantısı için Pin Atamaları

Sinyal İsmi

FPGA Pin

No.

Tanım

I/O

Standart

HPS_LTC_GPIO

PIN_H13

HPS LTC GPIO

3.3V

HPS_I2C1_SCLK

PIN_B21

HPS I2C1 Clock

3.3V

HPS_I2C1_SDAT

PIN_A21

HPS I2C1 Veri

3.3V

HPS_SPIM_CLK

PIN_C19

SPI Clock

3.3V

HPS_SPIM_MISO

PIN_B19

SPI Master giriş/Slave Output

3.3V

HPS_SPIM_MOSI

PIN_B16

SPI Master Output /Slave giriş

3.3V

HPS_SPIM_SS

PIN_C16

SPI Slave Select

3.3V

DE0-Nano-SoC Kullanıcı Kılavuzu

39

Bölüm 4

DE0-Nano-SoC Sistem Builder

Bu bölüm kullanıcıların nasıl DE0-Nano-SoC Sistem Builder ile kendi özel tasarım projelerini

oluşturacaklarını anlatıyor.

4.1 Girizgah

DE0-Nano-SoC Sistem Builder Windows temelli bir yardımcı programdır.Kullanıcıların DE0-Nano-S0C için

bir Quartus II projesi yapmalarına yardım için tasarlanmıştır.veyataya çıkan Quartus II proje dosyalarının

içeriği:

Quartus II proje dosyası (.qpf)

Quartus II ayar dosyası (.qsf)

Top tasarım dosyası (.v)

Synopsis tasarım limitleri dosyası (.sdc)

Pin atama evrakları (.htm)

DE0-Nano-SoC Sistem Üreticisi tarafından oluşturulan yukarıdaki dosyalar kullanıcıların üst düzey tasarım

dosyalarını ya da pin atamalarını elle derledikleri zaman oluşan hatalarınveyataya çıkmasını engelleyebilir.

• Yanlış bank voltaj ayarı veya hatalı pin atamasına dayalı kart zararı

• Yanlış cihaz seçimi, pin atamaları ve yönünün yanlış beyanı ya da unutulmasına dayalı kart zararı

• Uygunsuz pin atamasından kaynaklı performans düşüşü.

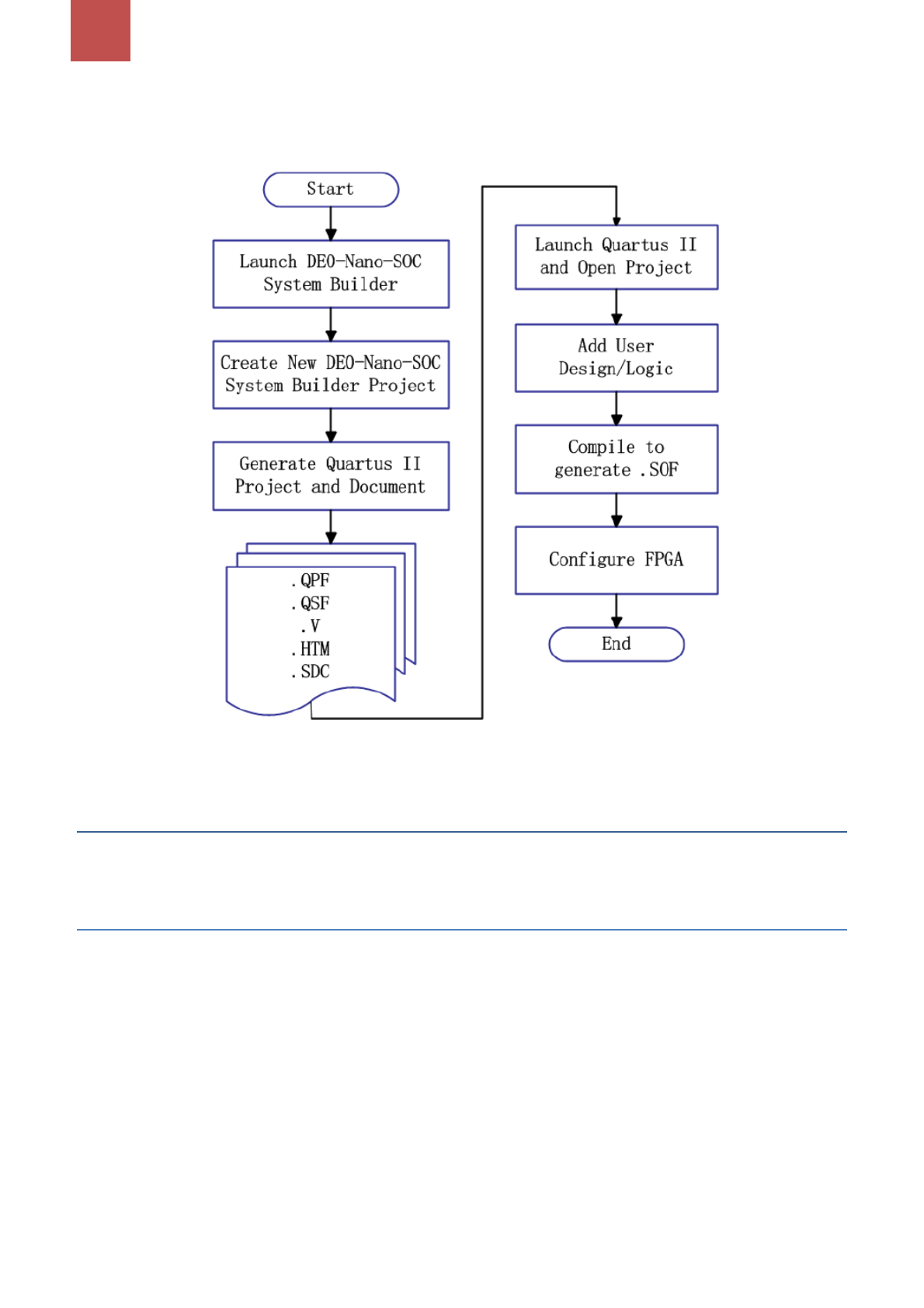

4.2 Tasarım Akışı

Bu bölümde DE0-Nano-SoC Sistem Oluşturucu altında DE0-Nano-SoC için Quartus II projesinin yapım

tasarım akışına bir giriş yapılır. Tasarım akışı Resim 4-1’de gösterilmştir.

DE0-Nano-SoC Sistem Oluşturucu kullanıcıların kendi tasarım gereksinimlerine göre yeni bir proje

oluşturması için iki büyük dosya oluşturur: üst düzey bir tasarım dosyası (.v) ve Quartus II ayar dosyası (.qsf)

Üst düzey tasarım dosyası kullanıcıların kendi tasarım/mantığını eklemek için bir üst düzey Verilog HDL

sarıcı içerir. Quartus II ayar dosyası her kullanıcı tanımlı I/O pin için FPGA cihaz türü, üst düzey pin ataması I/O

standart gibi bilgleri içerir.

40

DE0-Nano-SoC Kullanıcı Kılavuzu

Son olarak, Quartus II programlayıcı geliştirme kartı için JTAG arayüzü aracılığıyla .sof uzantılı dosyayı

indirir.

Resim 4-1 Bir proje yapmak için baştan sonra tasarım şeması

4.3 DE0-Nano-SoC Sistem Üreticisinin Kullanımı

Bu bölüm DE0-Nano-SoC Sistem Üreticisinin nasıl kullanıldığıyla ilgili detayların yönergelerini anlatır.

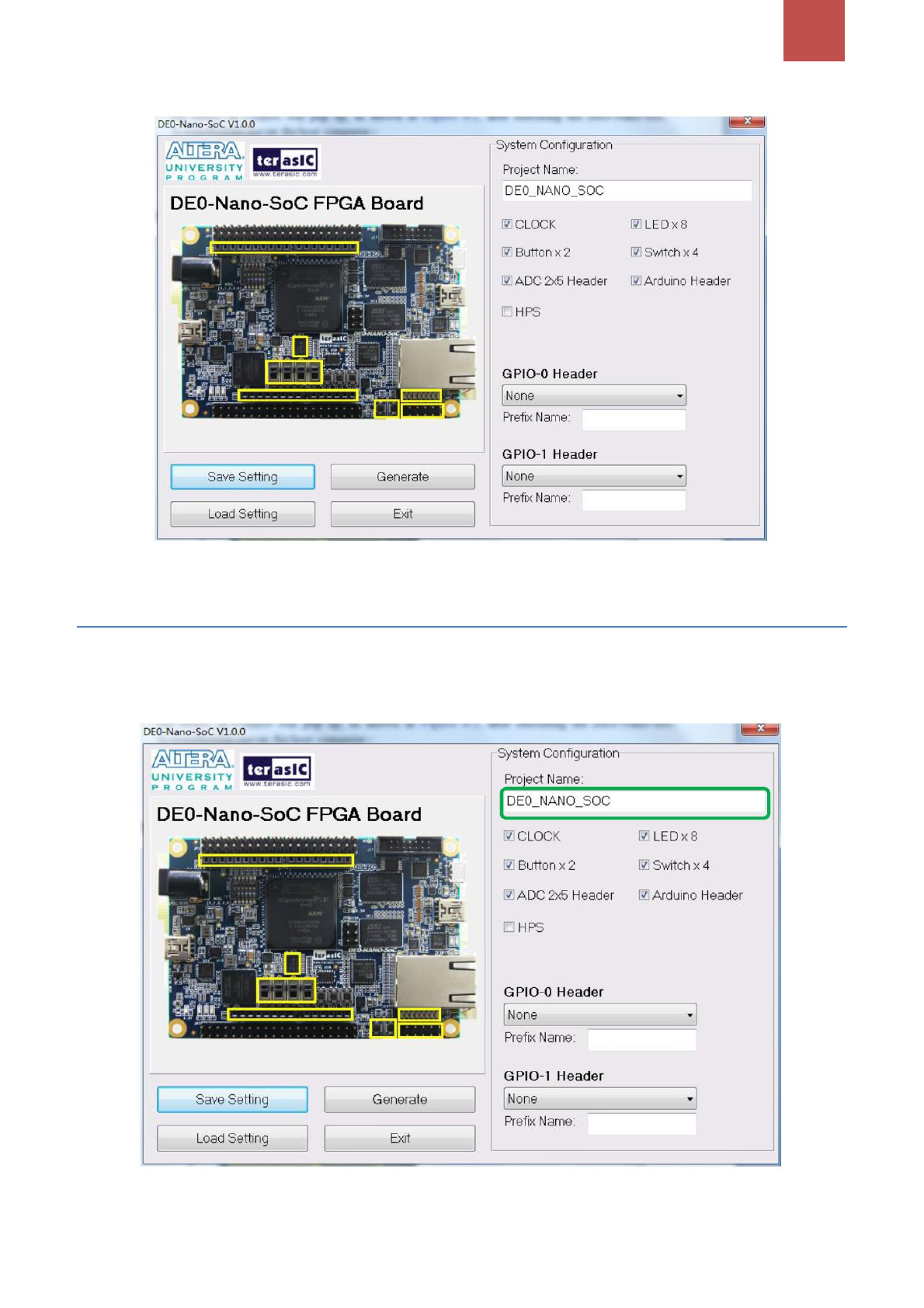

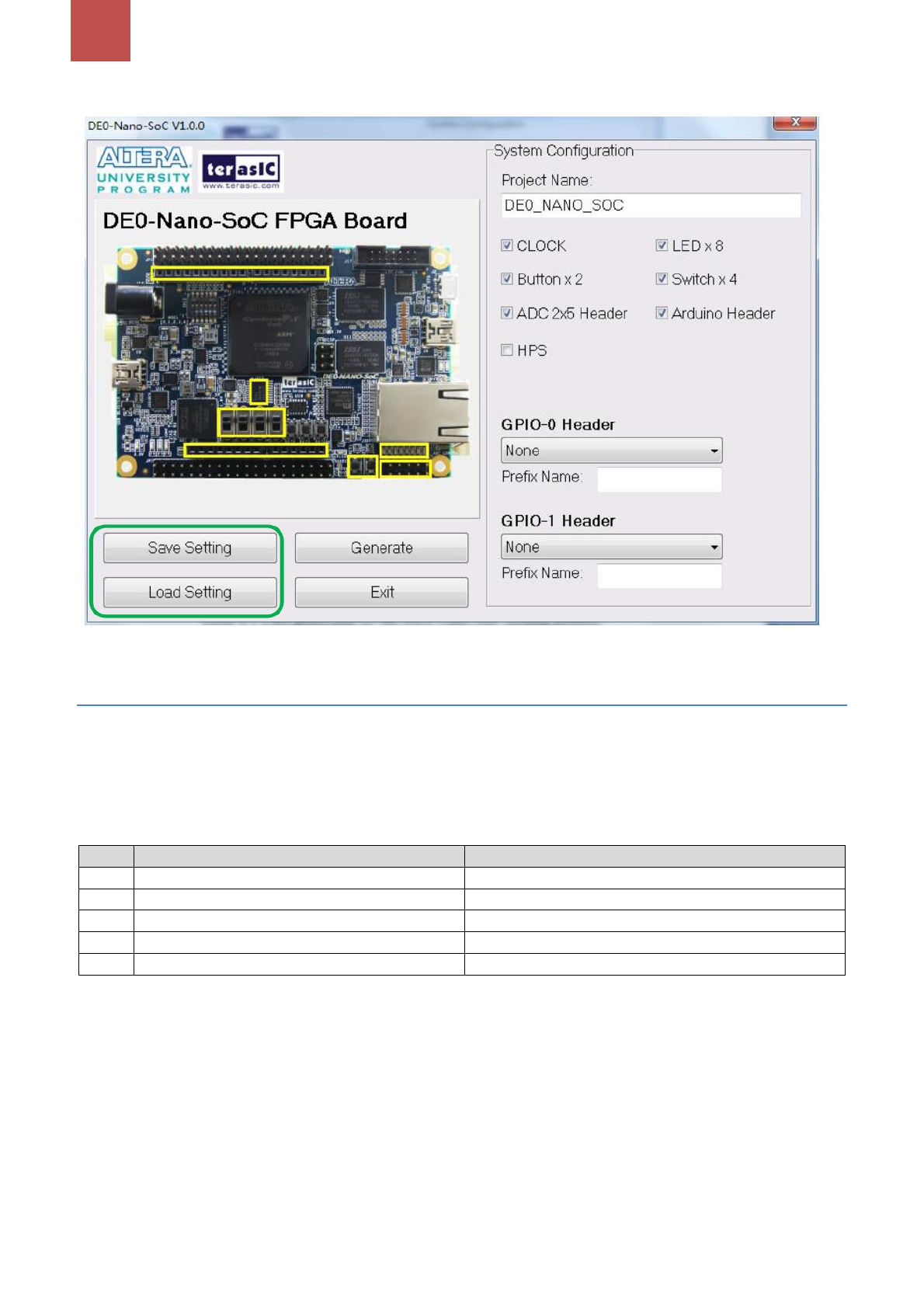

DE0-Nano-SoC Sistem Üreticisinin Kurulumu ve Çalıştırılması

DE0-Nano-SoC Sistem Üreticisi DE0-Nano-SoC Sistem CD’si içinde “Tools/SistemBuilder” konumunda

bulunmaktadır.Kullanıcılar programı kurmadan çalıştırmak için tüm dosyayı kendi bilgisayarlarına

kopyalayabilirler. Kullanıcılar bilgisayarlarında “DE0-Nano-SoC SystemBuilder.exe” yi çalıştırdıklarından sonra

karşılarına Resim 4-2’deki gibi bir pencere çıkacaktır.

DE0-Nano-SoC Kullanıcı Kılavuzu

41

Resim 4-2 DE0-Nano-SoC Sistem Builder Arayüzü

Proje İsmi Girme

Resim 4-3’deki gösterilen kutucuğa proje ismi girilir.

Yazdığınız proje adı otomatik olarak yaptığınız üst düzey tasarım varlığının adı olarak atanacaktır.

Resim 4-3 Proje İsmi Girme

42

DE0-Nano-SoC Kullanıcı Kılavuzu

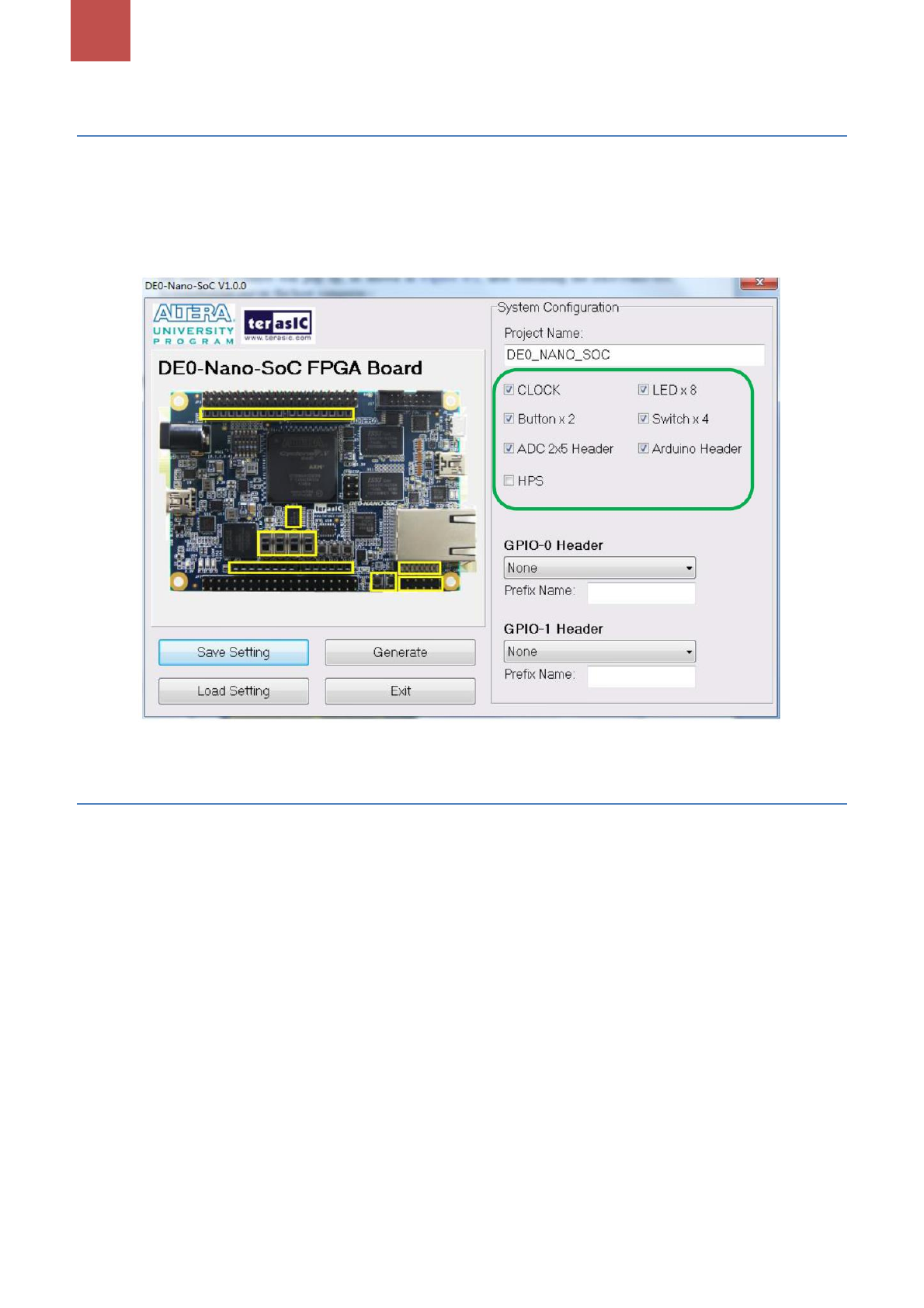

Sistem Yapılandırma

Kullanıcılara sistem Yapılandırmanda proje içine kendi seçtikleri değişkenleri dahil edebilmeleri için

esneklik tanınmıştır(Resim 4-4).Her bir yerleşik bileşen listelenmiştir ve ve kullanıcılar onlardan bir ya da daha

fazlasını Aktif ya da pasEğer hale getirebilir. Eğer bir bileşen aktifse, DE0-Nano-SoC Sistem Üreticisi otomatik

olarak pin adı, konumu, yönergesini ve I/O standartı ile beraber pin atamasını oluşturur.

Resim 4-4 Sistem yapılandırma grubu

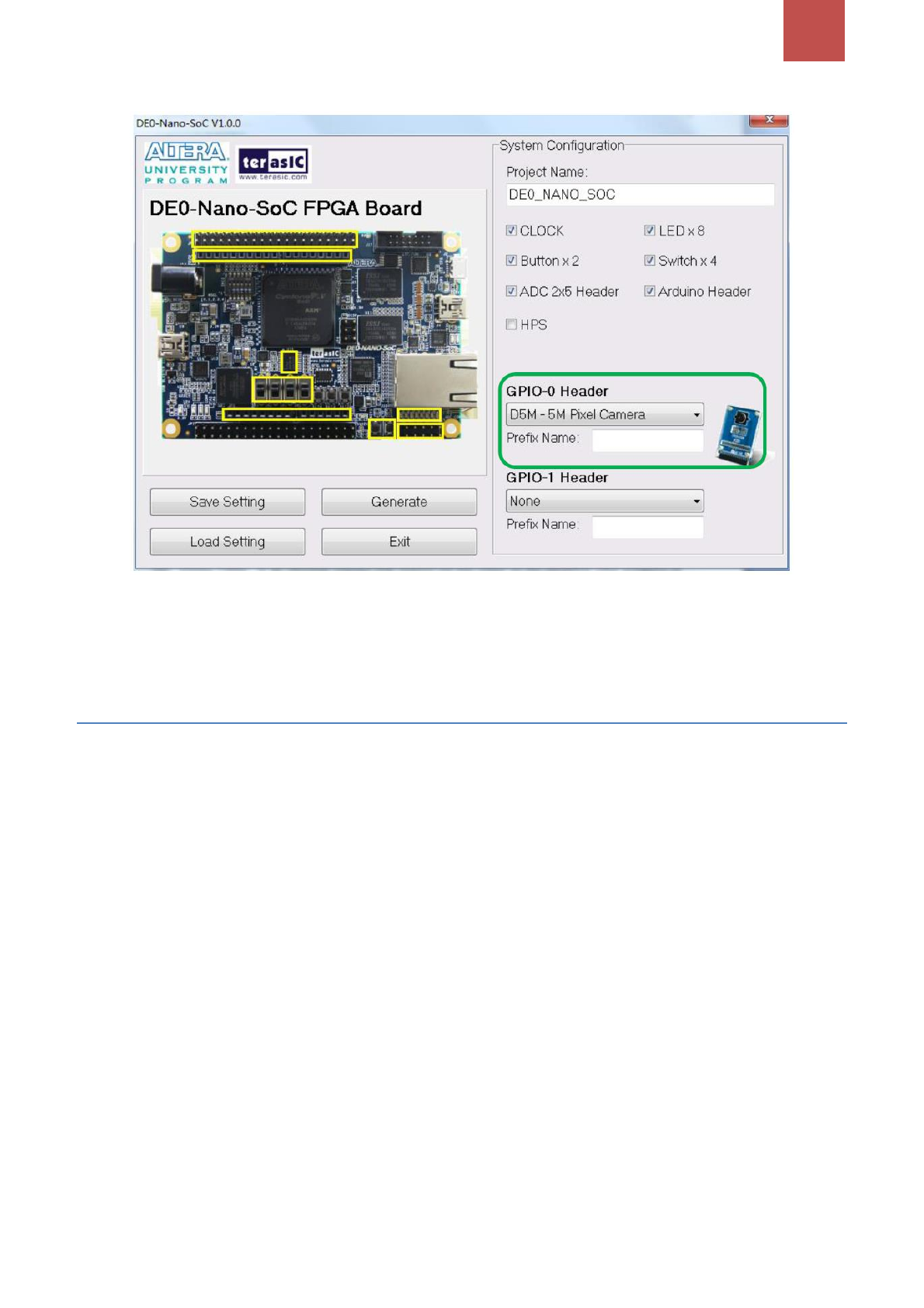

GPIO Genişleme

Eğer kullanıcılar De0-Nano-SoC üzerindeki GPIO bağlacı için herhangi bir GPIO-temelli Terasic yardımcı

kart takarsa, DE0-Nano-SoC Sistem Üreticisi ilgili modülü içeren bir proje üretebilir(Resim 4-5). Ayrıca, DE0-

Nano-SoC Sistem Üreticisi otomatik olarak pin adı, konumu, yönergesini ve I/O standartı ile beraber pin

atamasını oluşturur.

DE0-Nano-SoC Kullanıcı Kılavuzu

43

Resim 4-5 GPIO genişleme grubu

Tasarımınız içine atanan kartın pin adını göstermek kullanıcıya bağlı bir özelliktir. Kullanıcılar alanı boş

bırakabilir.

Proje Ayar Yönetimi

Ayrıca DE0-Nano-SoC Sistem Builder kullanıcılara .cfg dosyasından bir ayar çağırma ya da belirli kart

yapılandırmalarını içine kaydetme seçeneği verir(Resim 4-6).

44

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 4-6 Proje Ayarları

Proje Üretimi

Kullanıcılar “Oluştur” seçeneğine bastığında, DE0-Nano-SoC Sistem Tablo 4-1’de listelenen dosya ve

dökümanları oluşturur.

Tablo 4-1 DE0-Nano-SoC Sistem Üreticisi tarafından oluşturulan dosyalar

No:

Dosya Adı

Tanım

1

<Project name>.v

Quartus II için Üst Düzey Verilog HDL Dosyası

2

<Project name>.qpf

Quartus II Poje Dosyası

3

<Project name>.qsf

Quartus II Ayar Dosyası

4

<Project name>.sdc

Synopsis Design Constraints file for Quartus II

5

<Project name>.htm

Pin Atamaları Dökümanı

Kullanıcılar SRAM Nesne Dosyası (.sof) oluşturmak için Quartus II’de projeye özel mantık ekleyebilir ve

projeyi derleyebilir.

DE0-Nano-SoC Kullanıcı Kılavuzu

45

Bölüm 5

FPGA için Örnekler

Bu bölümde DE0-Nano-SoC kartı üzerinde RTL veya Qsys tarafından oluşturulan gelişmiş tasarım

örnekleri gösterilir. Bu referans tasarımları A/D Çevirici gibi FPGA’ye bağlı çevresel birimlerin özelliklerini

kapsar.Konuyla ilgili tüm dosyalar “\Demonstrations\FPGA of DE0-Nano-SoC Sistem CD” içinde bulunabilir.

Gösterilerin Kurulumu

Gösterileri bilgsayarınıza kurun:

Gösterimler klasörünü seçtiğiniz yerel bir dizine kopyalayın. Yerel dizinin hiç boş alan içerp

içermediğinden emn olmanız önemlidir. Aksi takdirde Nios II hataya yol açabilir.

Tüm gösterimler için Quartus II v14.0 veya daha sonraki sürümlerin Cyclone V SoC aygıtı desteklemesi

gereklidir.

5.1 DE0-Nano-SoC Fabrika Yapılandırma

DE0-Nano-SoC kartı kart üzerindeki temel özellikleri gösteren önceden programlanmış bir geçerli

yapılandırma veri akışına sahiptir. Bu gösterim için kurulum gereklidir ve dosyalarının konumu altta

gösterilir.

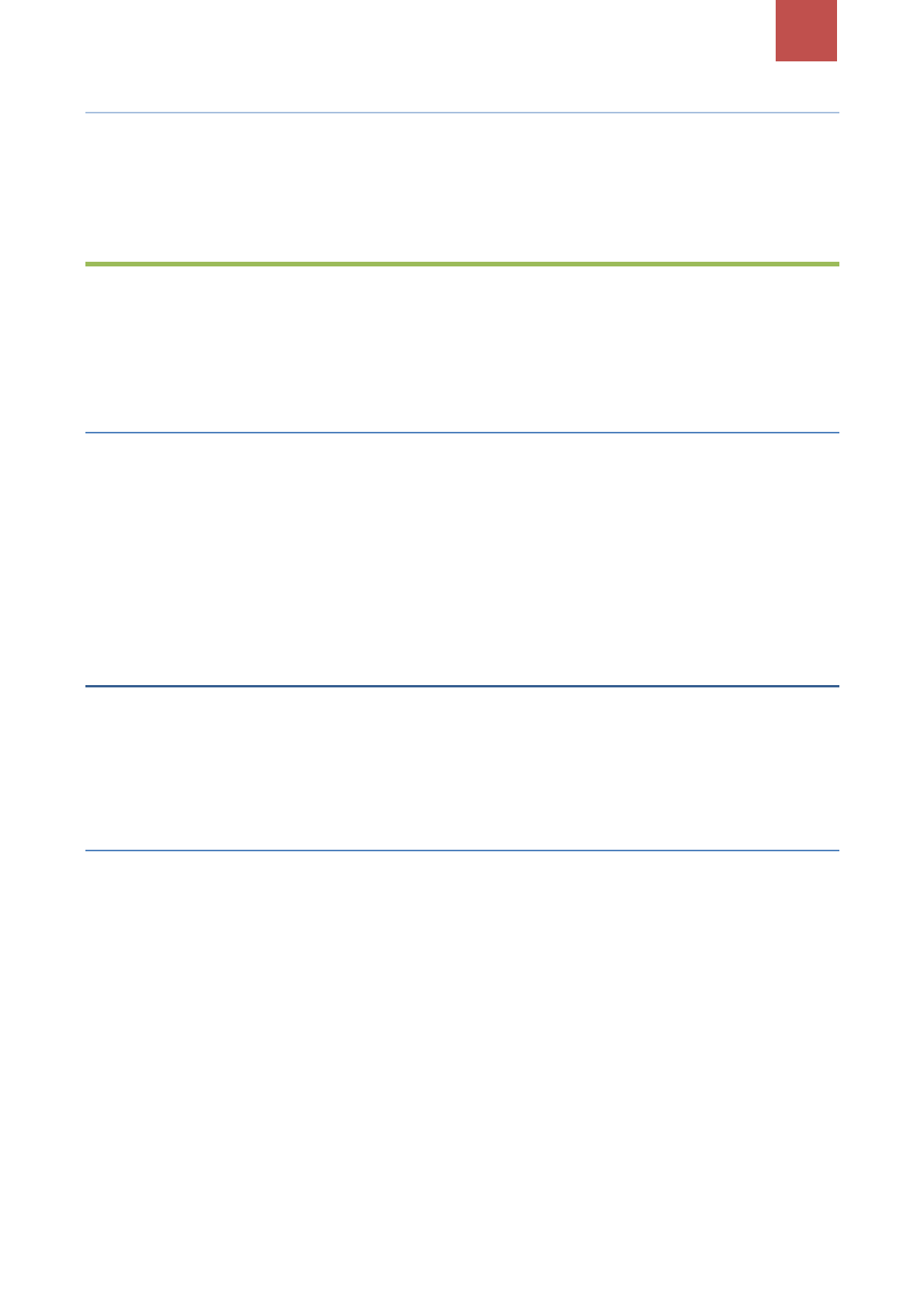

Demonstration Setup, Dosyaların Konumu, ve Yönergeler

Proje dizini: DE0_NANO_SOC_Default

Kullanılan Veri Akışı: DE0_NANO_SOC_Default.sof veya DE0_NANO_SOC_Default.jic

DE0-Nano-SoC kartı üzerindeki güç USB kablosu ile US-Blaster II porta bağlıdır.Gerekirse (Varsayılan

fabrika yapılandırması şu anda EPCS cihazda saklanan değilse) JTAG arayüzü üzerinden bit akışı

indirilmelidir.

Artık LED’leri ışıldarken gözlemleyebilirsiniz.

Uygulama kolaylığı için, proje içinde bir demo_batch klasörü sağlanır. Bu yalnızca komut satırı içinde

FPGA’ye veri akışı indirmeye yaramaz, ayrıca testi test.bat dosyasını uygularken (Resim 5-1) EPCS

cihazı için.jic dosyası programlamaya ya da silmeye yarar.

Eğer kullanıcılar EPCS içinde yeni bir tasarım programlamayı istiyorlarsa en kolay metod yeni “.sof”

dosyasını demo_batch klasörü içine kopyalamak ve test.bat dosyasını çalıştırmak.İkinci seçenek “.sof”

dosyasını “.jic” dosyasına çevirmek ve üçüncü seçenek ise “.jic” dosyasını EPCS cihazı içinde

programlamaktır.

46

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 5-1 FPGA ve EPCS cihazını programlamak için batch dosyasının komut satırı

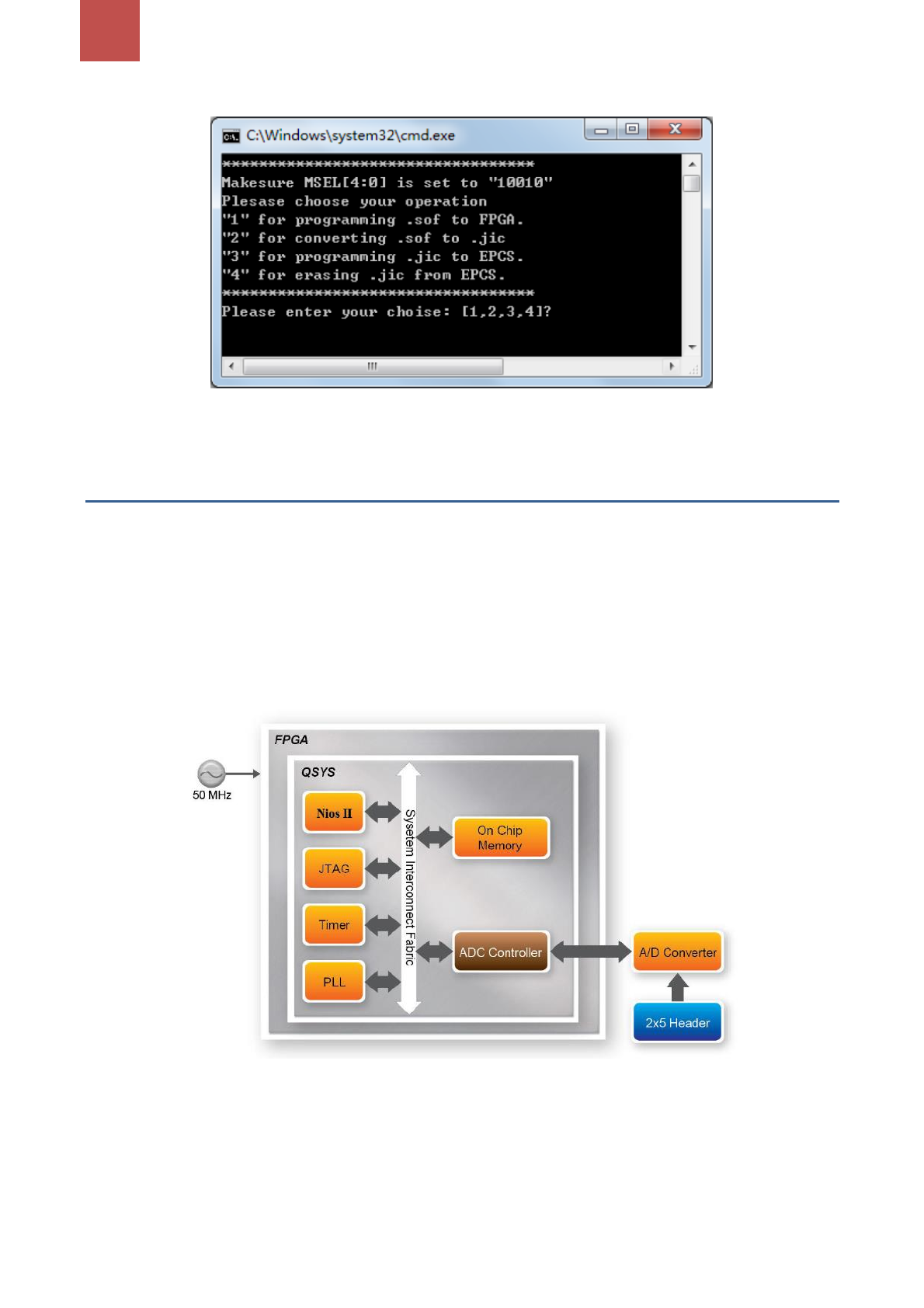

5.2 ADC Okuma

Bu gösterim 8-kanallı 12-bit A/D çevirici LTC2308’in performansının hesaplanmasını adım adım

gösterir.2x5 başlık üzerindeki 5.0V DC düzenleyici potansiyometre tarafından analog sinyalleri sürmek için

kullanılır. Voltaj 0 ve 4.096V arasındaki bir değere ayarlanabilir. 12-bitlik voltaj ölçümü NIOS II konsolu

üzerinde görüntülenebilir. Resim 5-2 bu gösterimin blok Şemasını gösterir.

Eğer giriş voltajı -2.0V ile 2.0V arasında ise önceden ölçekli bir devre giriş voltajını 0 ile 4V arasında

ayarlayabilir.

Resim 5-2 ADC Okumanın Blok Şeması

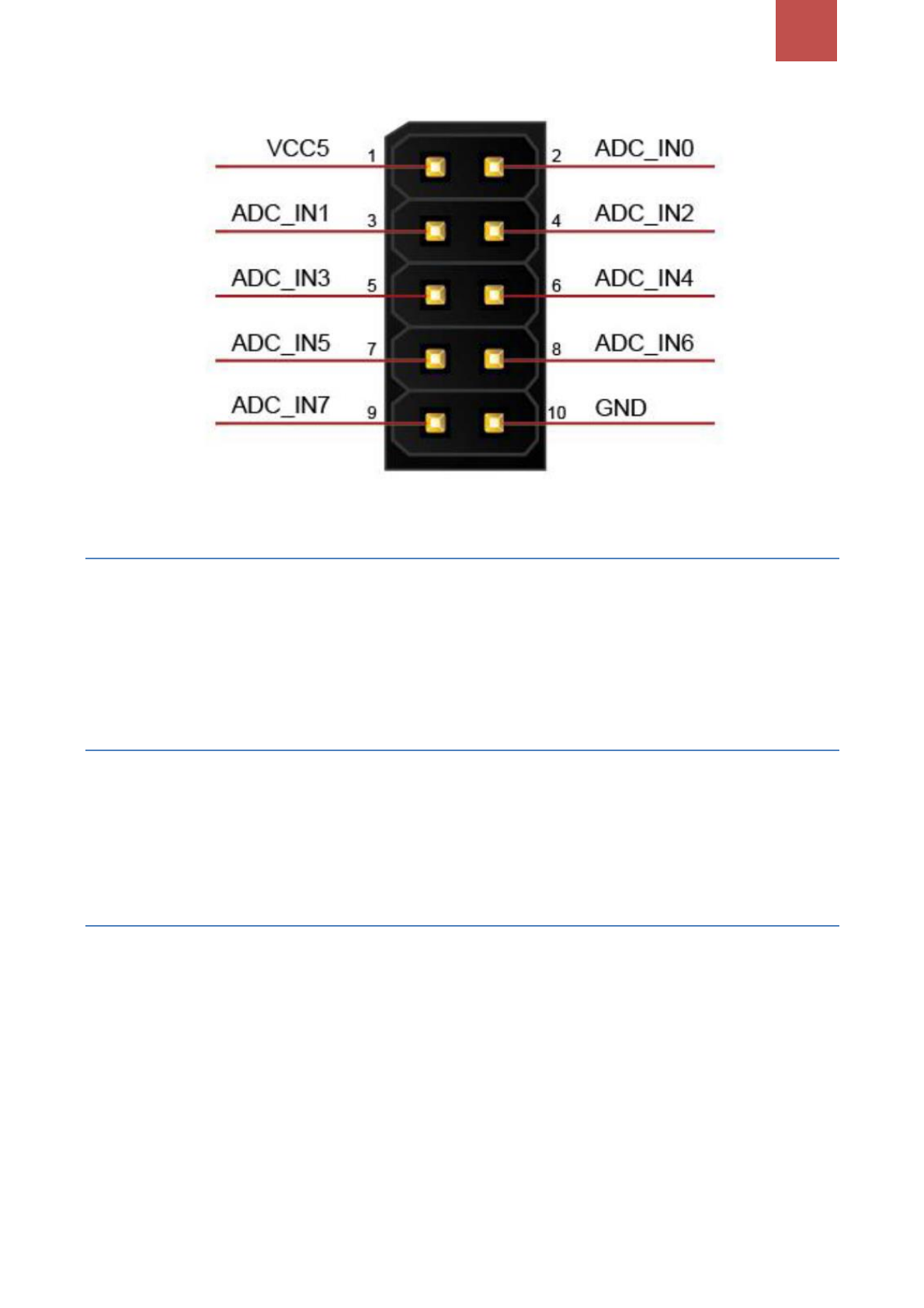

Resim 5-3 2x5 başlığın pin atamalarını gösteriyor. Bu gösterimde bu başlık ADC dönüştürücünün giriş

kaynağıdır. Kulanıcılar ADC dönüştürücüye voltaj sağlamak için bir düzenleyiciye bağlanarak ADC kanalını

(ADC_IN0 ~ ADC_IN7) belirtebilir. FPGA voltaj değerini Nios II konsolda göstermek için dönüştürücü içindeki

ilgili kayıtı Seri arayüz aracılığıyla okur ve dönüştürür.

DE0-Nano-SoC Kullanıcı Kılavuzu

47

Resim 5-3 ADC için 2x5 Başlığın Pin Dağıtımı

Sistem Gereksinimleri

Bu gösterim için aşağıdaki listelenen malzemeler gereklidir:

DE0-Nano-SoC kartı x1

Düzenleyici Potansiyometre x1

Tel Lerit x3

Gösterim Dosya Konumları

Donanım Proje Yönergesi: DE0_NANO_SOC_ADC

Kullanılan Veri Akışı: DE0_NANO_SOC_ADC.sof

Yazılım Proje Yönergesi : DE0_NANO_SOC_ADC\software

Batch Dosyasının Demosu : DE0_NANO_SOC_ADC\demo_batch\DE0_NANO_SOC_ADC.bat

Gösterim Kurulum ve Yönergeleri

2x5 başlık üzerindeki ADC channel’a karşılık gelen tetikleyiciye (Resim 5-4), +5V ve GND sinyallerinin

yanısıra. Yukarıda gösterilen kurulum ADC channel 0’a bağlıdır.

Veri akışını ve yazılım uygulama dosyasını FPGA’ye indirmek için DE0_NANO_SOC_ADC.bat demo

dosyasını çalıştırın.

Nios II konsolu belirtilen kanal voltaj sonuç bilgilerinin voltajını gösterir.

48

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 5-4 ADC okuma gösterimi için yazılım kurulumu

DE0-Nano-SoC Kullanıcı Kılavuzu

49

Bölüm 6

HPS SoC için Örnekler

Bu bölüm Yocto Projesi tarafından yapılan Altera SoC Linux temelli bazı C kodları sağlar.Bu örnekler

DE0-Nano-SoC üzerinde HPS arayüzüne bağlı olan kullanıcı LED/LEY’leri ya da I2C arayüzlü G-Sensorü gibi

çevresel birimlerin önemli özelliklerini gösterir. Konu ile alakalı bütün dosyalar “Demonstrations/SOC of

DE0-Nano-SoC Sistem CD” çinde bulunabilir. DE0-Nano-SoC kartı üzerinde Linux çalıştırmak için DE0-Nano-

SoC_Erişim_Started_Guide.pdf içinden Bölüm 5 "Running Linux on DE0-Nano-SoC board" e bakabilirsiniz.

Gösterimlerin Kurulması

Ana bilgisayarda gösterimleri kurmak için:

Demonstrations klasörünü istediğiniz herhangi bir yerel birim içine kopyalayın.Kullanıcıların C kodlu

projeyi derlemesi için Altera SoC EDS v14.0 gereklidir.

6.1 Hello Program

Bu gösterim Altera SoC EDS aleti ile nasıl ilk HPS projenizi geliştireceğinizi gösterir.Daha fazla

bilgiye erişmek için lütfen Sistem CS’sinden My_First_HPS.pdf dosyasına başvurun.

HPS projesi yapıp geliştirmenin önemli aşamaları:

Ana blgisayara Altera SoC EDS’yi kurun.

Jenerik metin editörü ile program .c/.h dosyaları oluşturun.

Jenerik metin editörü ile Create “Makefile” oluşturun.

Altera SoC EDS altında proje yapın.

Program Dosyası

Hello World gösterisi için ana program:

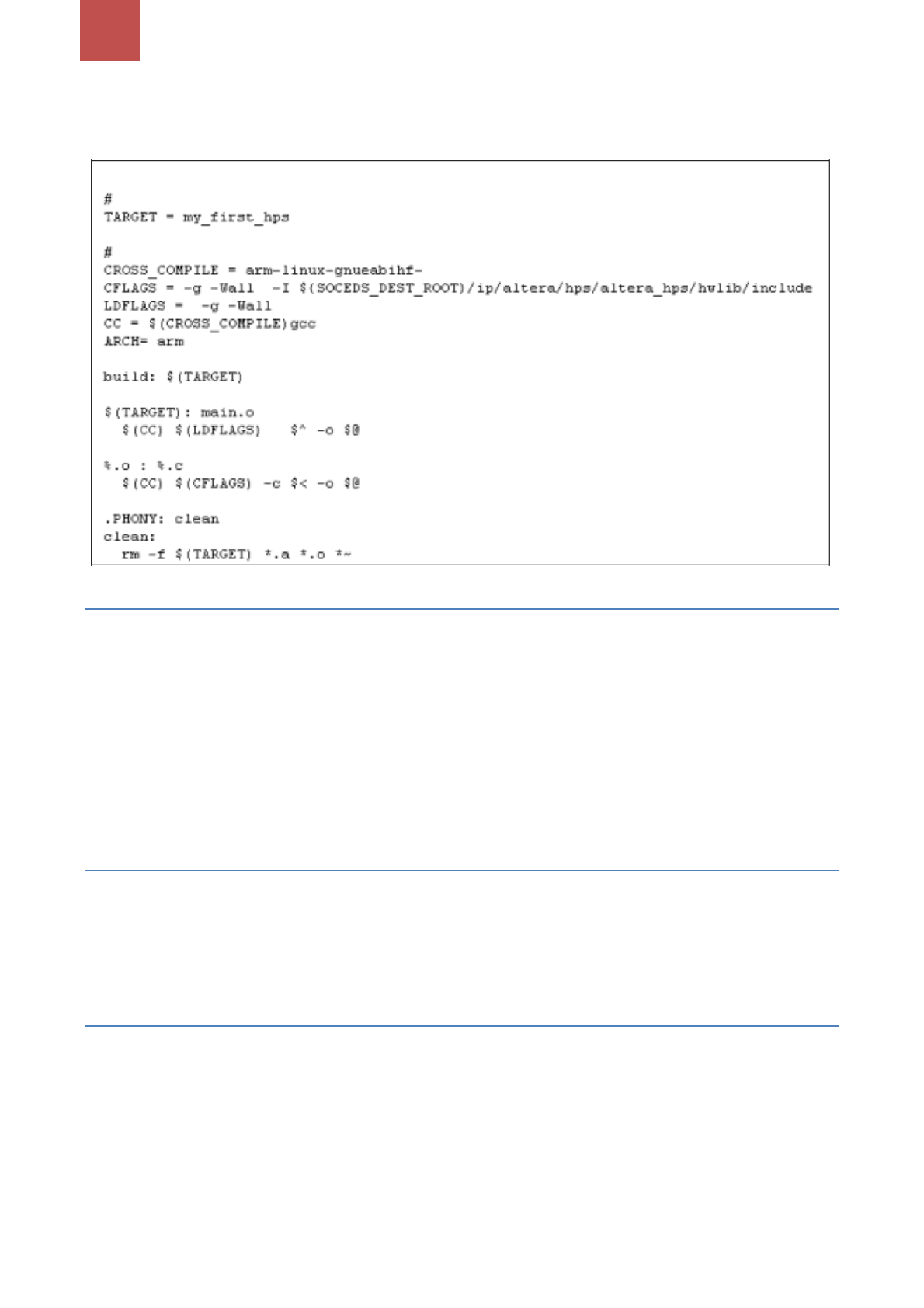

Makefile

50

DE0-Nano-SoC Kullanıcı Kılavuzu

Proje derlemek için bir Makefile gereklidir. Bu demo için kullanılan Makefile:

Derleme

Bir projeyi uygulayarak derlemek için lütfen Altera SoC EDS Shell komutunu çalıştırın.

C:\altera\14.0\embedded\Embedded_Command_Shell.bat

"cd" komutu Hello World projesinin yer aldığı geçerli dizini değiştirebilir.

“make” komutu projeyi yapar. Derleme süreci başarılı olduktan sonra yürütülebilir "my_first_hps"

dosyası oluşturulur. “clean all” komutu bütün tüm geçici dosyaları götürür.

Gösterim Kaynak Kodu

Tasarım Aracı: Altera SoC EDS v14.0

Proje Klasörü: \Demonstration\SoC\my_first_hps

Makine Kodu Dosyası: my_first_hps

Yapı Komutu: make ("make clean" to remove all temporary files)

Yürütme Komutu: ./my_first_hps

Gösterim Kurulumu

DE0-Nano-SoC kartı üzerindeki USB-to-UART bağlacı (J4) ve ana bilgisayarı bir USB kablosuyla

bağlayın

"my_first_hps" demo dosyasını Linux’ta "/home/root" klasörünün altında bir micro SD karta

kopyalayın.

DE0-Nano-SoC kartın içine microSD önyükleme kartını takın.

DE0-Nano-SoC kata güç verin.

PuTTY’i çalıştırın ve PuTTY’nin UART portu ile bağlantı kurun. Altera Yocto Linux’a giriş için “root”

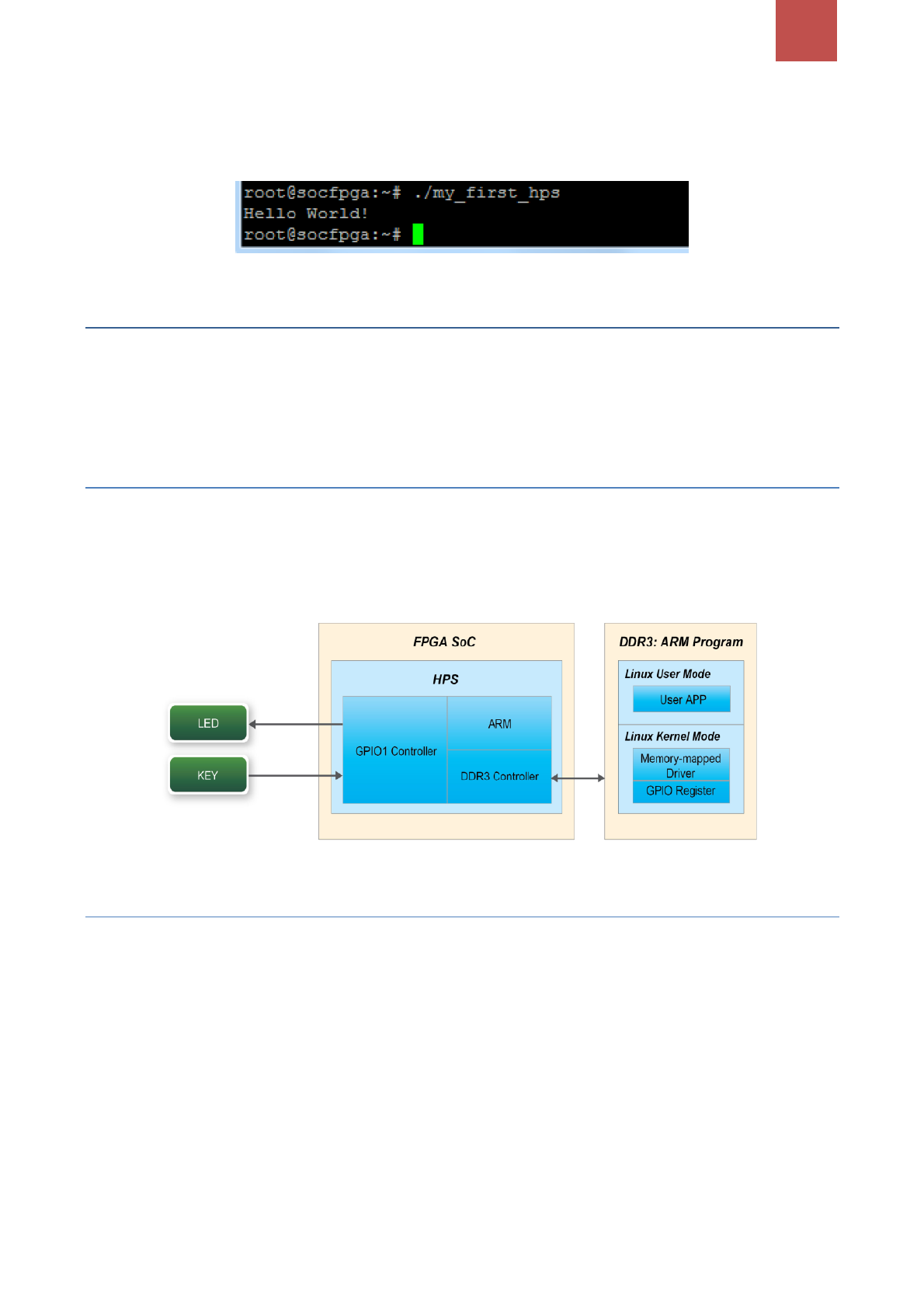

yazın.

DE0-Nano-SoC Kullanıcı Kılavuzu

51

Programı başlatmak için PuTTY’nin UART terminalinde "./my_first_hps" yazın ve "Hello World!"

mesajı terminalde görülecektir.

6.2 Kullanıcıların LED ve Butonları

Bu gösterim kullanıcıların bellek eşlemeli aygıt sürücüsü aracılığıyla GPIO denetleyici kaydına

erişerek kullanıcı LED ve Butonlarını kontrol ettiğini gösterir. Bellek eşlemeli aygıt sürücüsü

kullanıcıların sistem fizksel hafızasına eşirmesine izin verir.

Fonksiyon Blok Şeması

Resim 6-1 bu gösterimin fonksiyon blok Şemasını gösterir. Kullanıcı LED ve Butonları HPS içindeki GPIO1

denetleyicisine bağlıdır. GPIO denetleyicisinin davranımı GPIO denetleyicisindeki kayıtlar tarafından kontrol

edilir. Aplikasyon yazılımı Altera SoC Linux içine inşa edilmiş bellek eşlemeli aygıt sürücüsü aracılığıyla

kayıtlara erişebilir.

Resim 6-1 GPIO gösteriminin Blok Şeması

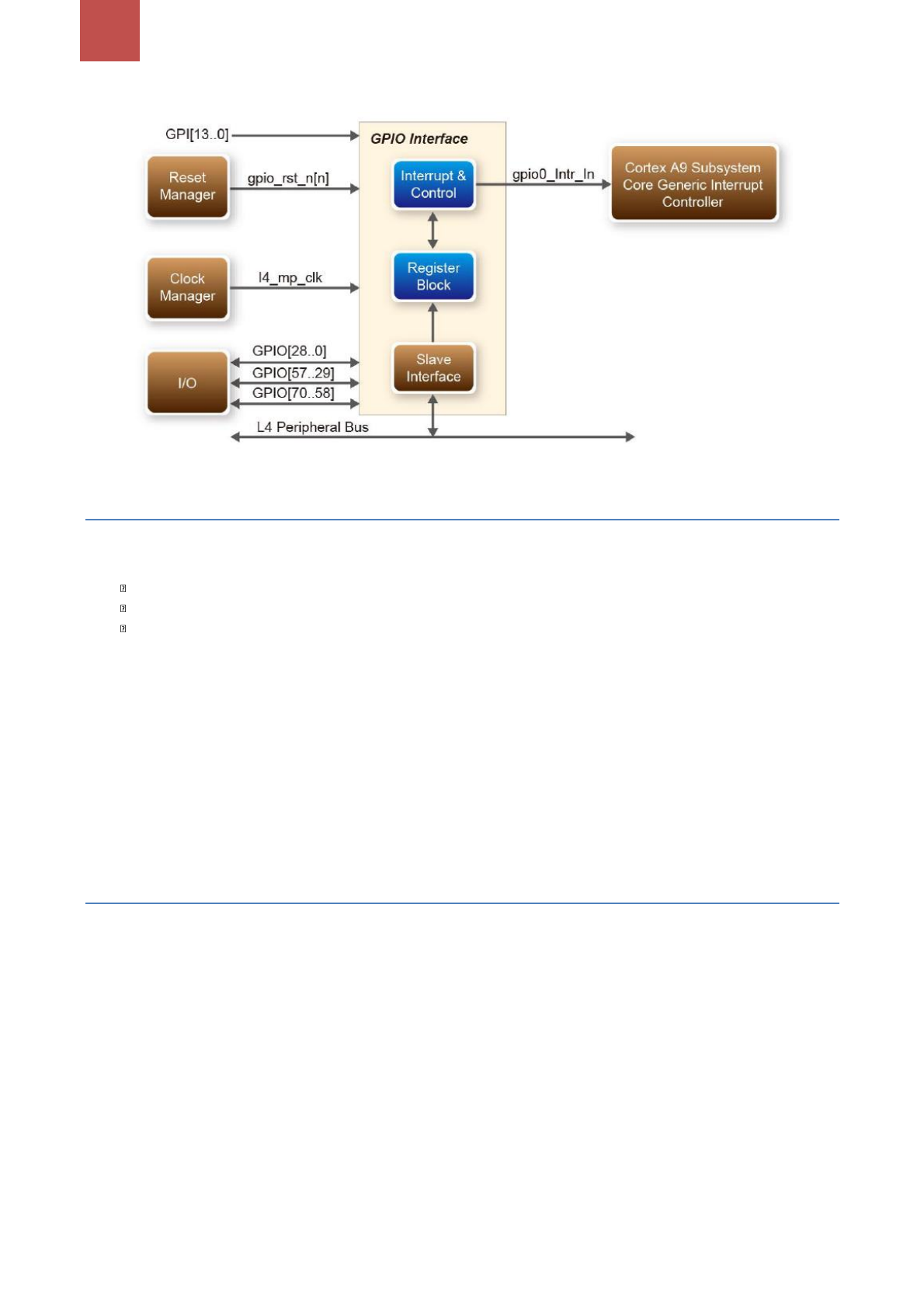

GPIO Arayüzünün Blok Şeması

HPS üç tane genel amaçlı I/O (GPIO) arayüz modülü sağlar. Resim 6-2 GPIO arayüzünün blok şemasını

gösterir. GPIO[28..0], GPIO0 denetleyicisi tarafından ve GPIO[57..29] ise GPIO1 denetleyicisi tarafından

kontrol edilir. GPIO[70..58] ve sadece girişli GPI[13..0] GPIO2 denetleyicisi tarafından kontrol edilir.

52

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 6-2 GPIO Arayüzünün Blok Şeması

GPIO Kayıt Bloğu

I/O pin davranışı kayıt bloğundaki kayıtlar tarafından kontrol edilir. GPIO denetleyicisindeki 3 tane 32-

bit kayıt vardır.Bu kayıtlar:

gpio_swporta_dr: I/O pininin çıkışı için çıkış veri kayıtlarını yazar

gpio_swporta_ddr: I/O pininin yönergelerini ayarlar

gpio_ext_porta: I/O giriş pininin giriş verilerini okur

gpio_swporta_ddr LED’leri çıkış pini olarak ayarlar ve LED’lere gpio_swporta_dr kaydı için yazılan

verilere göre yüksek ya da alçak gerilim verilir. gpio_swporta_dr kaydının ilk biti alakalı GPIO

denetleyicisindeki ilk I/O pinin çıkış değerini kontrol eder, ikinci bit ikinci denetleyicininkini eder ve böylece

gider. Register bit değeri "0" I / O yönü girişi gösterir iken kayıt bit değeri "1", I / O yönü çıkış olduğunu

gösterir.

Butonun durumu gpio_ext_porta kaydının okunan değeri tarafından sorgulanır. İlk bit GPIO

denetleyicisi atamalarındaki ilk I/O pinin giriş durumunu sunar, ikinci ikincininkini sunaar ve böylece devam

eder. Kayıt içinde “1” değeri giriş voltajını yüksek, “0” değeri giriş voltajını düşük olarak belirtir.

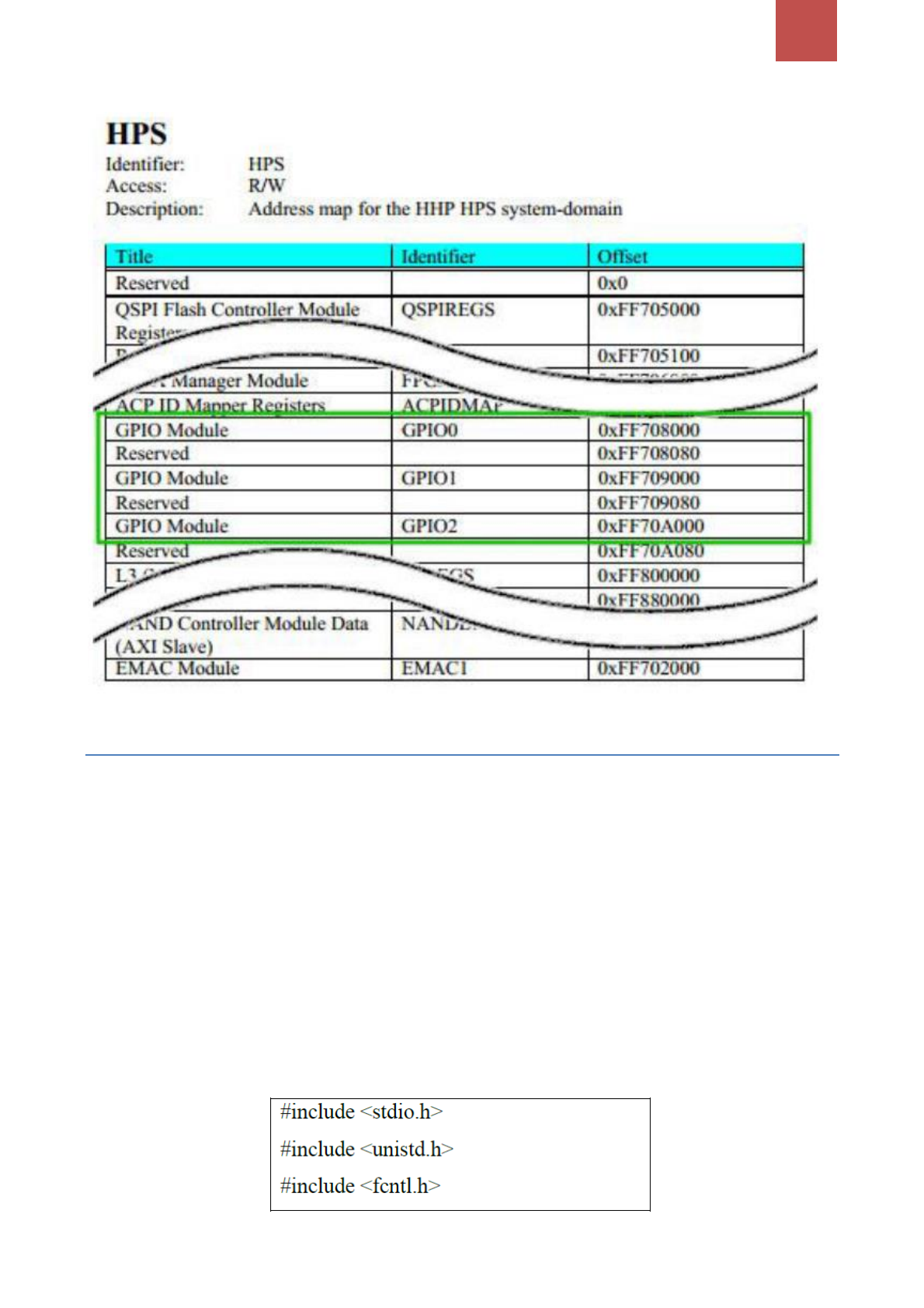

GPIO Kayıt Adres Eşleştirme

HPS çevre birimlerinin kayıtları 64KB boyutlu HPS taban adres alanı 0xFC000000 ile eşleştirilir, GPIO1

denetleyicisi kayıtları 4KB boyutlu taban adresi 0xFF708000 ile eşlenir ve GPIO2 denetleyicisi kayıtları 4KB

boyutlu taban adresi 0xFF70A000 ile eşleştirilir (Resim 6-3).

DE0-Nano-SoC Kullanıcı Kılavuzu

53

Resim 6-3 GPIO Adres Haritası

Yazılım API

Geliştiriciler, GPIO denetleyicisinin kayıtlarına erişmek için aşağıdaki yazılım API’yı kullanabilirler:

open: bellek haritalı cihaz sürücüsünü açar

mmap: kullanıcı alanı için fiziksel bellek haritası

alt_read_word: belirtilen bir kayıttan bir değer okur

alt_write_word: belirtilen bir kayıt içine bir değer yazar

munmap: bellek haritasını temizler

close: chaz sürücüsünü kapar

Geliştiriciler kayıtlara ulaşmak için aşağıdaki MACRO’yu da kullanabilirler:

alt_setbits_word: belirli bir kayıt için belirli bir bit değerini “1” e ayarlar.

alt_clrbits_word: belirli bir kayıt için belirli bir bit değerini “0” a ayarlar.

Pogram GPIO denetleyicisinin kayıtlarına erişmek maksadıyla API üzerinde kullanmak için

aşağıdaki başlıklı dosyaları içermek zorundadır.

54

DE0-Nano-SoC Kullanıcı Kılavuzu

LED ve Buton Kontrolü

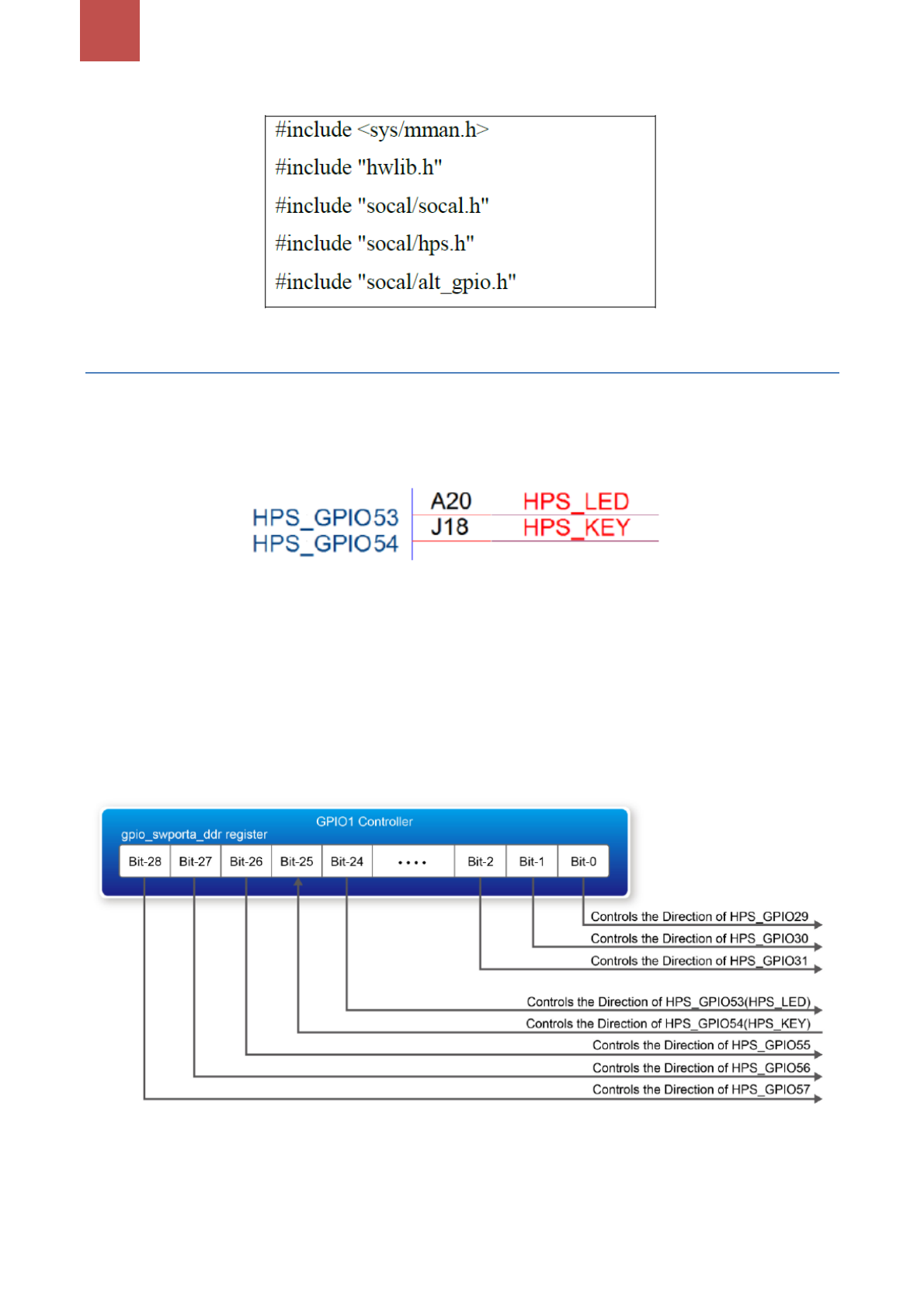

Resim 6-4 HPS kullanıcıları için DE0-Nano-SoC kartı üzerindeki LED ve Butonların pin atamalarını

göstermektedir. LED, HPS_GPIO53’ya ve KEY HPS_GPIO54’ya bağlıdır. Bunlar GPIO1 denetleyicisi tarafından

kontrol edilmektedir, bu denetleyici HPS_GPIO29 ~ HPS_GPIO57’ları kontrol eder.

Resim 6-4 LED ve Butonların Pin Atamaları

Resim 6-5 GPIO1 denetleyicisinin gpio_swporta_ddr kayıtlarını gösterir. bit-0, HPS_GPIO29’nun pin

yönergesini kontrol eder. bit-24, HPS_GPIO53’nun pin yönergesini kontrol eder, ki HPS_GPIO53 HPS_LED’e

bağlanır, bit-25, HPS_GPIO54’nun pin yönergesini kontrol eder, ki HPS_GPIO54 HPS_KEY’e bağlanır ve

böylece devam eder. HPS_LED ve HPS_Butonun pin yönergeleri GPIO1 denetleyicisinin gpio_swporta_ddr

kaydındaki ,sırasıyla, bit-24 ve bit-25 tarafından kontrol edilir. Benzer şekilde, HPS_LED’in çıkış durumu

GPIO1 denetleyicisindeki gpio_swporta_dr kaydındaki bit-24 tarafından kontrol edilir. Butonun durumu

GPIO1 denetleyicisinin gpio_ext_porta kaydındaki bit-24 değeri okunarak sorgulanabilir.

Resim 6-5 GPIO1 denetleyicisindeki gpio_swporta_ddr kaydı

DE0-Nano-SoC Kullanıcı Kılavuzu

55

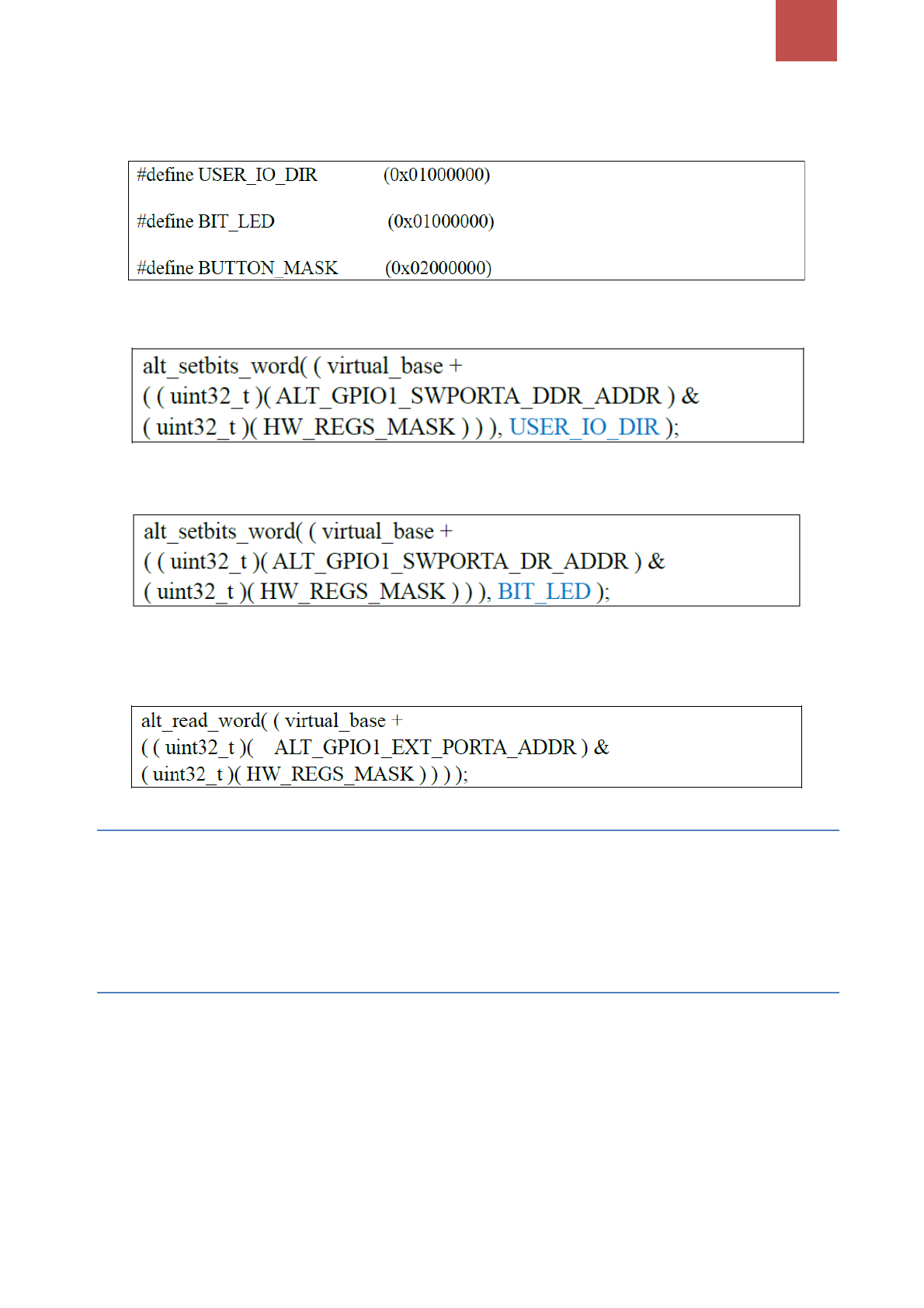

Aşağıdaki örtü LED ve Buton yönergeleri ile LED’in çıkış değerini kontrol etmek için oluşturulan demo

kodu içinde tanımlanmıştır.

Aşağıdaki komut LED’le ilişkili pinleri çıkış pini olarak ayarlamak için kullanılır.

Aşağıdaki komut LED’i yakmak için kullanılır.

Aşağıdaki komut gpio_ext_porta kaydının içeriğini okumak için kullanılır. Bit örtüsü Butonların

durumunu kontrol etmek için kullanılır.

Gösterim Kaynak Kodu

Tasarım Aracı: Altera SoC EDS V14.0

Proje Klasörü: \Demonstration\SoC\hps_gpio

Makine Kodu Dosyası: hps_gpio

Yapı Komutu: make ('make clean' to remove all temporal files)

Yürütme Komutu: ./hps_gpio

Gösterim Kurulumu

DE0-Nano-SoC kartı üzerindeki USB-to-UART bağlacı (J4) ve ana bilgisayarı bir USB kablosuyla

bağlayın

"my_first_hps" demo dosyasını Linux’ta "/home/root" klasörünün altında bir micro SD

karta kopyalayın.

DE0-Nano-SoC kartın içine microSD önyükleme kartını takın.

DE0-Nano-SoC kata güç verin.

PuTTY’i çalıştırın ve PuTTY’nin UART portu ile bağlantı kurun. Altera Yocto Linux’a giriş için

“root” yazın.

Programı başlatmak için PuTTY’nin UART terminalinde "./my_first_hps" yazın.

56

DE0-Nano-SoC Kullanıcı Kılavuzu

HPS_LED iki kere yanıp söner ve kullanıcılar kullanıcı LED’ini buton ile kontrol edebilirler.

HPS_LED’i yakmak için HPS KEY’e basın.

Programı sonlandırmak için "CTRL + C" ye basın.

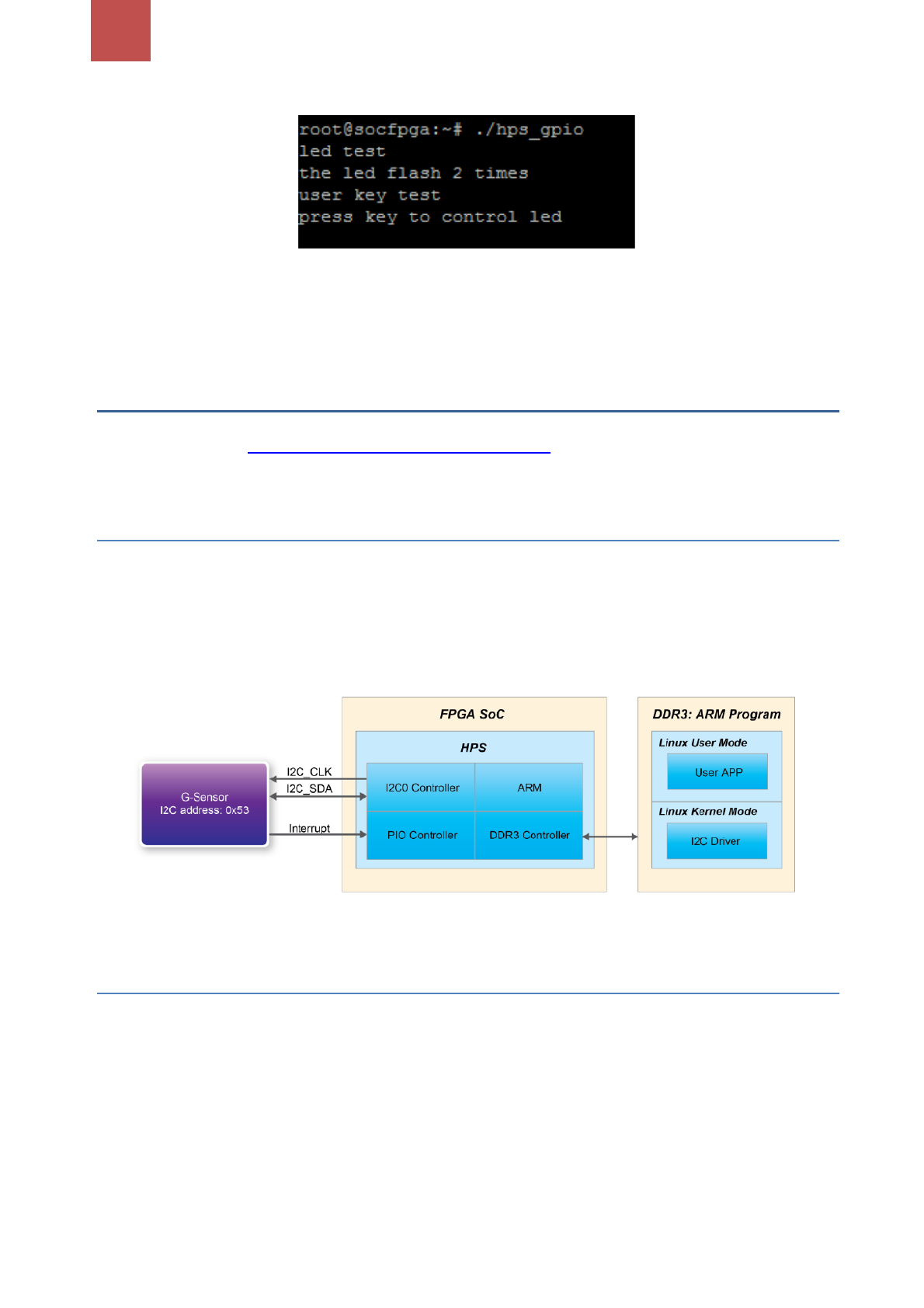

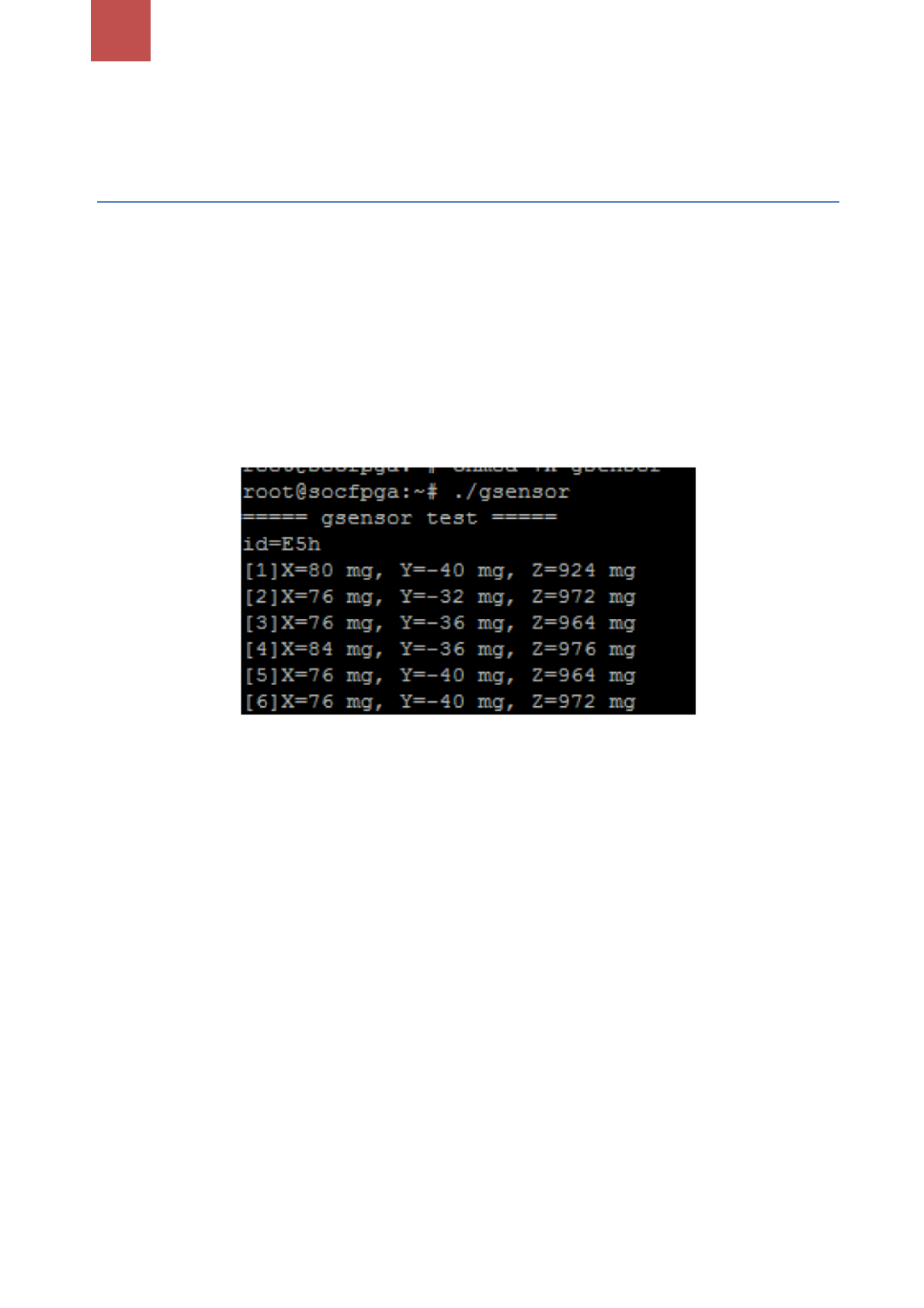

6.3 G-Sensor I2C Arabirimi

Burada G-Sensor Altera Soc Yocto Powered Embedded Linux içinde yerleşik I2C çekirdek sürücüsü

aracılığıyla kayıtlara erişerek nasıl kontrol edilir gösterilmektedir.

Fonksiyon Blok Şeması

Resim 6-6 bu gösterimin foksiyon blok şemasını gösterir. DE0-Nano-SoC kartı üzerindeki G-Sensor HPS

içindeki I2C0 denetleyicisine bağlıdır. G-Sensor’ün I2C 7-bit cihaz adresi 0x53’tür. Sistem I2C verialtı

sürücüsü G-Sensor’deki kayıt dosyalarına erişmek için kullanılır. G-Sensor kesme sinyali PIO denetleyicisine

bağlıdır. Bu gösterim kayıt verilerini okumak için yoklama metodu kullanır.

Resim 6-6 G-Sensor Gösteriminin Blok Şeması

I2C Sürücüsü

Sistemde var olan I2C verialtı sürücüsü tarafından G-Sensor kayıt dosyalarından kayıt değer okumak

için gereken aşamalar:

1. I2C verialtı sürücüsünü açın "/dev/i2c-0": file = open("/dev/i2c-0", O_RDWR);

2. SpecEğery G-Sensor'ün I2C adresini belirtin 0x53: ioctl(file, I2C_SLAVE, 0x53);

3. G-Sensor’de istenen kayıt endeksini belirtin: write(file, &Addr8, sizeof(unsigned char));

4. Bir bitlik kayıt değerini okuyun: read(file, &Data8, sizeof(unsigned char));

DE0-Nano-SoC Kullanıcı Kılavuzu

57

G-Sensor I2C verialtı I2C0 denetleyicisine bağlıdır (Resim 6-7). Verilen sürücü ismi: '/dev/i2c-0'.

Resim 6-7 HPS I2C sinyallerinin bağlantıları

The step 4 above can be changed to the following to write a value into a register.

write(file, &Data8, sizeof(unsigned char));

The step 4 above can also be changed to the following to read multiple byte values.

read(file, &szData8, sizeof(szData8)); // where szVeri is an array of bytes

The step 4 above can be changed to the following to write multiple byte values.

write(file, &szData8, sizeof(szData8)); // where szVeri is an array of bytes

G-Sensor Kontrol

ADI ADXL345 I2C ve SPI arayüzlerini sağlar. I2C arayüzü CS pini DE0-Nano-SoC kart üzerinde HIGH

ayarlayarak seçilir.

The ADI ADXL345 G-Sensor 13-bit kullanıcı tarafından seçilebilir 13-bit ± 16g üzerinde çözünürlük

sağlar. Bu çözünürlük DATA_FORAMT(0x31) kaydı tarafından ayarlanabilir. Bu gösterimdeki verinin

formatı:

Full Resolution Modunda

± 16g range Modunda

Left-justified Modunda

olarak ayarlanabilir.

X/Y/Z veri değerleri VERİX0(0x32), VERİX1(0x33), VERİY0(0x34), VERİY1(0x35), VERİZ0(0x36), ve

VERİX1(0x37) kayıtlarından elde edilebilir. The VERİX0 en az önemli baytı VERİX1 ise en önemli baytı temsil

eder.Veri ile ardışık kayıtları okuma arasındaki değişimi engellemek için tüm kayıtların çoklu-bayt

okumasını gerçekleştirmek gereklidir. Aşağıdaki komut X, Y ve Z değerlerinin 6 baytını okur.

read(file, szData8, sizeof(szData8)); // where szVeri is an array of six-bytes

Gösterim Kaynak Kodu

Tasarım Aracı: Altera SoC EDS v14.0

Proje Klasörü: \Demonstration\SoC\hps_gsensor

Makine Kodu Dosyası: gsensor

58

DE0-Nano-SoC Kullanıcı Kılavuzu

Yapı Komutu: make ('make clean' to remove all temporal files)

Yürütme Komutu: ./gsensor [loop count]

Gösterim Kurulumu

DE0-Nano-SoC kartı üzerindeki USB-to-UART bağlacı (J4) ve ana bilgisayarı bir USB kablosuyla

bağlayın

"my_first_hps" demo dosyasını Linux’ta "/home/root" klasörünün altında bir micro SD

karta kopyalayın.

DE0-Nano-SoC kartın içine microSD önyükleme kartını takın.

DE0-Nano-SoC kata güç verin.

PuTTY’i çalıştırın ve PuTTY’nin UART portu ile bağlantı kurun. Altera Yocto Linux’a giriş için “root”

yazın.

Demo programı PuTTY içinde X,Y ve Z değerlerini gösterecektir.

Resim 6-8’de görüldüğü gibi G-Sensor sorgulamasını başlatmak için PuTTY’nin UART terminalinde

“./gsensor” ü çalıştırın.

Resim 6-8 G-Sensor gösteriminin terminal çıkışı

Programı sonlandırmak için "CTRL + C" ye basın.

DE0-Nano-SoC Kullanıcı Kılavuzu

59

Bölüm 7

HPS SoC ve FGPA’in Birlikte

Kullanımına Örnekler

HPS ve FPGA bağımsız olarak çalışmalarına rağmen, yüksek performanslı ARM AMBA® AXITM verialtı

köprüleri yüksek bant genişlikli sistem arabağlantısı aracılığıyla sıkıca bağlanmışlardır. FPGA sistemi ve HPS

bu arabağlantı köprüleri aracılığıyla birbirlerine erişebilirler. Bu bölümdeayrı bir FPGA ve ayrık işlemci

içeren çözümleri karşılaştırırken bu bağlantı köprüleri ile üstün performans ve düşük gecikmeveyaanına

ulaşmanın yolu gösteriliyor.

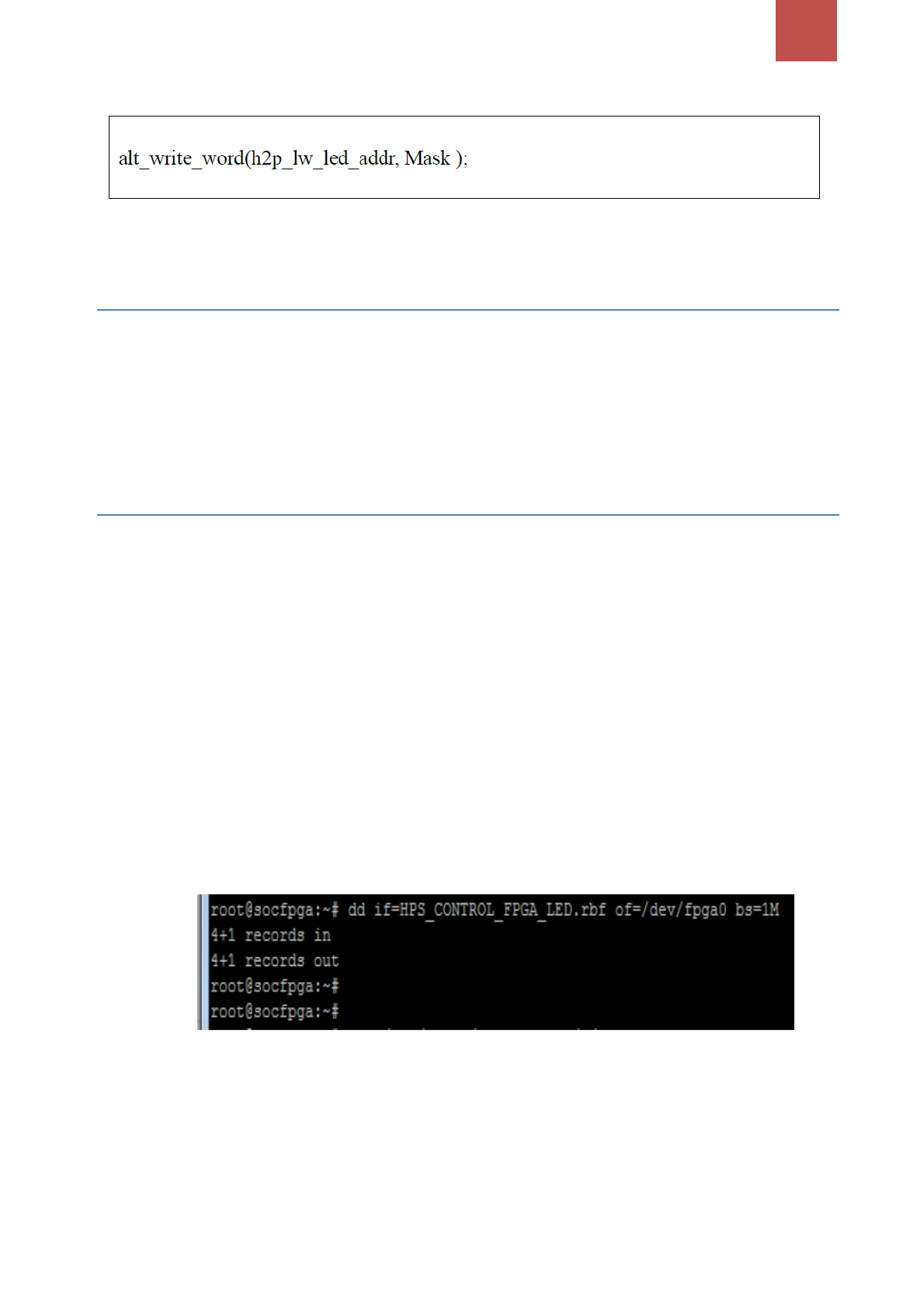

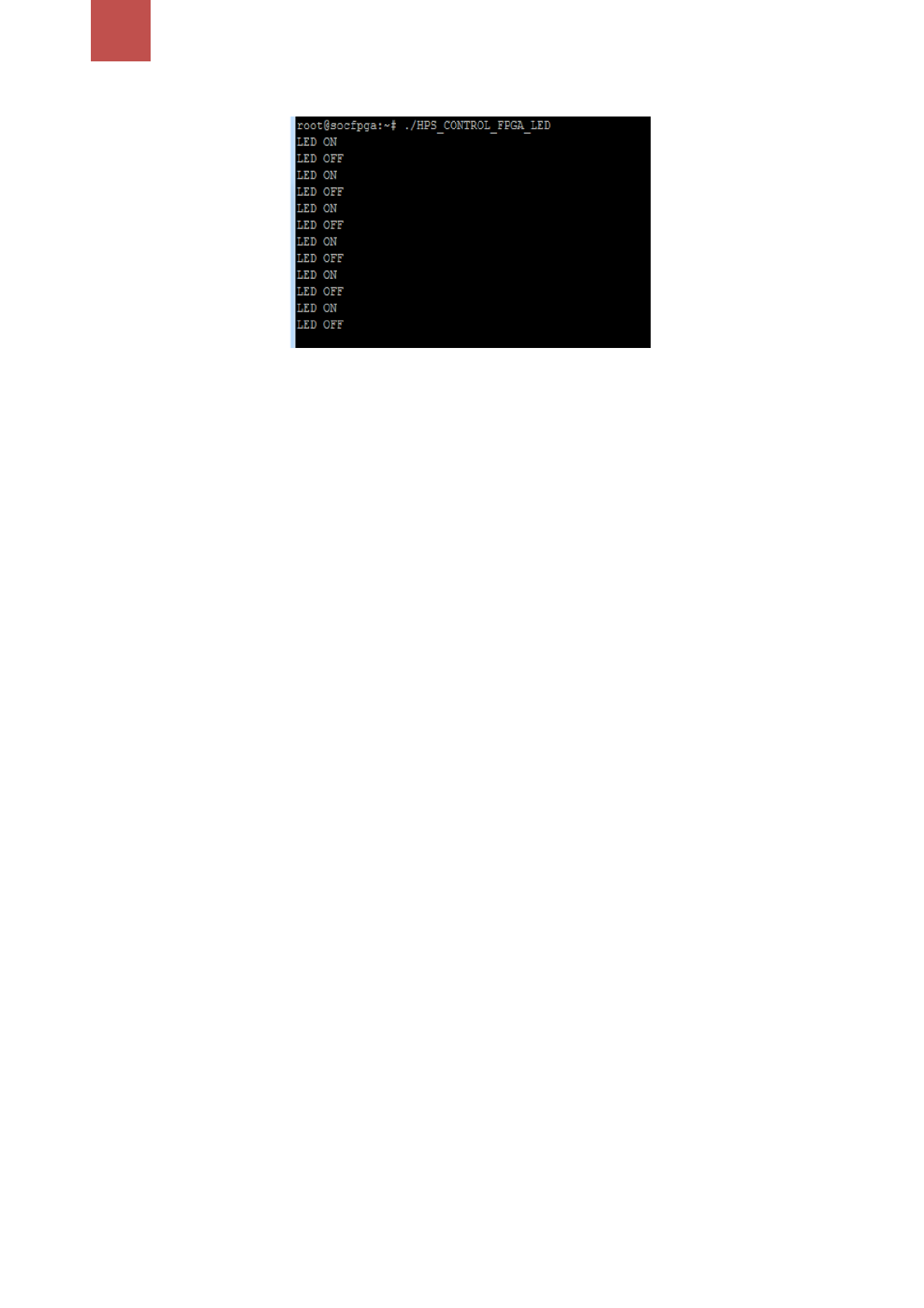

7.1 HPS Kontrol FPGA LED

Bu bölüm HPS Lightweigth HPS-to-FPGA köprüsü aracılığıyla FPGA LED’i nasıl kontrol eder onu

göstermektedir. Bu FPGA, HPS tarafından HPS’de yer alan FPGA yöneticisi aracılığıyla yapılandırılır.

FPGA yönetici üzerine kısa bir gözatma

HPS’deki FPGA yöneticisi HPS’deki FPGA sistemi tarafından ayarlanır. Ayrıca FPGA’in ve sürücülerin

ya da örnek sinyallerin FPGA sistemi için izler. Bu komut FPGA’in FPGA sistemi tarafından kontrol

edilmesini sağlar. FPGA yapılandırma verisi .rf uzantılı dosya içinde saklanır.Komutu HPs üzerinde

çalıştırmadan önce MSEL[4:0] 00000 olarak ayarlanmalıdır.

Fonsiyon Blok Şeması

Resim 7-1 bu gösterimin blok şemasını göstermektedir. HPS FPGA ile iletişim için Lightweight HPS-to-

FPGA AXI köprüsü kullanmaktadır. FPGA kısmındaki yazılım Qsys içine yapılır. The veri transferred through

Lightweight HPS-to-FPGA Köprüsü tarafından aktarılan veri Avalon-MM ana kayıt arayüzü içine

döndürülür.

PIO Denetleyicisi sistem içerisinde Avalon-MM’e bağımlı olarak çalışır.Onlar LED’lerin durumunu

değiştirmek için atanmış pinleri kontrol ederler. LED’leri kontrol için Nios II işlemcisi kullanan bir sistemle

benzerdir.

60

DE0-Nano-SoC Kullanıcı Kılavuzu

Resim 7-1 HPs tarafından kontrol edilen FPGA LED

LED Kontrol Yazılım Tasarımı

The Lightweight HPS-to-FPGA Köprüsü bir HPS çevresel birimidir. Linux üzerinde çalışan yazılım bu HPS

çevresel biriminin fiziksel adresine erişemez. Çevresel birim ulaşılabilir olmadan önce fiziksel adres

kullanıcı alanı le eşleştirilmelidir. Alternatif olarak, özelleştirilmiş bir aygıt sürücüsü modülü çekirdeğe

eklenebilir. HPS’nin tüm CSR erim aralığı bu aralık içindeki çeşitli kayıtlara erişmek eşleştirilir. Eğer diğer