# GM1200E Mobile Radio

## **Detailed Service Manual**

68P64115B15

## **CAUTION**

#### **ELECTROSTATIC SENSITIVE DEVICES**

PRECAUTIONS SHOULD BE TAKEN TO MINIMIZE THE RISK OF DAMAGE BY ELECTROSTATIC DISCHARGE TO ELECTROSTATIC SENSITIVE DEVICES (ESDs).

ANY DEVICES EMPLOYING METAL OXIDE SILICON (MOS) TECHNOLOGY ARE PARTICULARLY SUSCEPTIBLE.

CIRCUIT DIAGRAMS MARKED WITH THE ABOVE SYMBOL INDICATE ELECTRONIC CIRCUITS (PECs) FOR WHICH ESD HANDLING PRECAUTIONS ARE NECESSARY.

THE USER SHOULD REFER TO BS5783, 1984: HANDLING OF ELECTROSTATIC SENSITIVE DEVICES. THIS BRITISH STANDARD SUPERSEDES DEF STAN 59-98, ISSUE 2.

| Cautions and Warnings |  |  |

|-----------------------|--|--|

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

## WARNING

#### **SAFETY WARNINGS**

THE ELECTRICAL POWER USED IN THIS EQUIPMENT IS AT A VOLTAGE HIGH ENOUGH TO ENDANGER LIFE.

BEFORE CARRYING OUT MAINTENANCE OR REPAIR, PERSONS CONCERNED MUST ENSURE THAT THIS EQUIPMENT IS ISOLATED FROM THE ELECTRICAL SUPPLY AND TESTS ARE MADE TO ENSURE THAT ISOLATION IS COMPLETE.

WHEN THE SUPPLY CANNOT BE ISOLATED, MAINTENANCE AND REPAIR MUST BE UNDERTAKEN BY PERSONS WHO ARE FULLY AWARE OF THE DANGERS INVOLVED AND WHO HAVE TAKEN ADEQUATE PRECAUTIONS TO PROTECT THEMSELVES.

COMPONENTS CONTAINING BERYLLIUM OXIDE ARE USED IN THIS EQUIPMENT. DUST FROM THIS MATERIAL IS A HEALTH HAZARD IF INHALED OR ALLOWED TO COME INTO CONTACT WITH THE SKIN.

GREAT CARE MUST BE TAKEN WHEN HANDLING THESE COMPONENTS WHICH MUST NOT BE BROKEN OR SUBJECTED TO EXCESSIVE HEATING. DEFECTIVE COMPONENTS MUST BE DISPOSED OF IN ACCORDANCE WITH CURRENT INSTRUCTIONS.

LEAD ACID BATTERIES MAY BE FITTED AS THE STANDBY BATTERY. CARE MUST BE TAKEN WHEN REMOVING OR INSTALLING THESE BATTERIES TO:

- 1. ENSURE THAT THE TERMINALS ARE NOT SHORTED TOGETHER.

- 2. PREVENT SPILLAGE OF THE CORROSIVE ELECTROLYTE.

| Cautions and Warnings |  |  |

|-----------------------|--|--|

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

## **Detailed Service Manual**

#### Contents

### Chapter

#### 1.0 Introduction

Gives a brief introduction into the manual and the service policy.

#### 2.0 Control Head - Level 3 Information

Provides level 3 service information on the Display/Keypad Control Head (K6) detailed in the following chapters:

- 2.1 Introduction/Theory of Operation

- 2.2 PCB/Schematic Diagrams and Parts Lists

#### 3.0 UHF/VHF Radio - Level 3 Information

Provides level 3 service information on the UHF/VHF radio detailed in the following chapters:

- 3.1 Introduction/Theory of Operation

- 3.2 PCB/Schematic Diagrams and Parts Lists

Detailed Service Manual vii

| $\sim$ |    |     |    |

|--------|----|-----|----|

|        | nt |     |    |

| u      |    | CII | Lo |

viii Detailed Service Manual

# Chapter 1

## Introduction

## **Table of Contents**

| Paragra | aph                          | Page |

|---------|------------------------------|------|

| 1.0     | Introduction                 | 1    |

| 2.0     | Scope of Manual              | 1    |

| 3.0     | How to Use This Manual       | 1    |

| 4.0     | Warranty and Service Support | 1    |

| 4.1     | Warranty Period              | 1    |

| 4.2     | After Warranty Period        | 2    |

| 4.3     | Piece Parts                  | 2    |

| 4.4     | Technical Support            | 2    |

| 4.5     | Associated Documentation     | 2    |

Introduction 1-i

#### **Table of Contents**

1-ii Introduction

#### 1.0 Introduction

This chapter outlines the scope and use of the detailed service manual and provides an overview of the warranty and service support.

#### 2.0 Scope of Manual

This manual is intended for use by experienced technicians familiar with similar types of equipment. It contains level 3 service information required for the equipment described and is current as of the printing date. Changes which occur after the printing date maybe incorporated by a complete Detailed Service Manual revision or alternatively as additions, for example, to Band Specific information.

#### 3.0 How to Use This Manual

The detailed service manual contain an introductory chapter giving information on warranty and support. Chapter 2 contains level 3 service information for the control head. Chapter 3 details level 3 service information for the radios in band specific sub-chapters each containing theory of operation and schematics/parts lists. Refer to the Table of Contents for a general overview of the manual.

#### 4.0 Warranty and Service Support

Motorola offers long term support for its products. This support includes full exchange and/or repair of the product during the warranty period, and service/ repair or spare parts support out of warranty. Any "return-for-exchange" or "return-for-repair" by an authorised Motorola Dealer must be accompanied by a Warranty Claim Form. Warranty Claim Forms are obtained by contacting an Authorised Motorola Dealer.

#### 4.1 Warranty Period

The terms and conditions of warranty are defined fully in the Motorola Dealer or Distributor or Reseller contract. These conditions may change from time to time and the following notes are for guidance purposes only.

In instances where the product is covered under a "return for replacement" or "return for repair" warranty, a check of the product should be performed prior to shipping the unit back to Motorola. To ensure the product has been correctly programmed or has not been subjected to damage outside the terms of the warranty.

Prior to shipping any radios back to the appropriate Motorola warranty depot, please contact Customer Services. All returns must be accompanied by a Warranty Claim Form, available from your Customer Services representative. Products should be shipped back in the original packaging, or correctly packaged to ensure no damage occurs in transit.

Introduction 1-1

#### 4.2 After Warranty Period

After Warranty period, Motorola continues to support products in two ways.

Firstly, Motorola's Radio Parts and Service Group (RPSG) offer a repair service to both end users and dealers at competitive prices.

Secondly, RPSG supplies individual parts and modules that can be purchased by dealers who are technically capable of performing fault analysis and repair.

#### 4.3 Piece Parts

Some replacement parts, spare parts, and/or product information can be ordered directly. If a complete Motorola part number is assigned to the part, it is available from Motorola Radio Parts and Service Group (RPSG). If a generic part is listed or only a part description is listed, the part is not normally available from Motorola. If a parts list is not included, this generally means that no user-serviceable parts are available for that kit or assembly.

All orders for parts/information should include the complete Motorola identification number. All part orders should be directed to your local RPSG office.

#### **Head Office**

Motorola G.m.b.H. European Parts Department 65232 Taunusstein Germany

#### 4.4 Technical Support

Motorola Product Services is available to assist the dealer/distributors in resolving any malfunctions which may be encountered. Initial contact should be by telephone whenever possible. When contacting Motorola Technical Support, be prepared with the product model number and the unit's serial number.

#### 4.5 Associated Documentation

| Publication Number                  | Description                                                                                                        |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| ENLN4051A<br>ENLN4052A<br>ENLN4053A | GM1200E Product Manual (with Level 1/2 repair information)<br>GM1200E Produkthandbuch<br>Manuel de Produit GM1200E |

| 68P64117B01                         | Shared Mobile Radio Systems (SMR) using MPT1327<br>A System Integrators Cookbook                                   |

| 68P02900X57-A                       | Data Application Notes for 1200 Series Radios                                                                      |

1-2 Introduction

# Chapter 2

## Control Head - Level 3 Information

## **Table of Contents**

## Chapter

- 2.1 Introduction/Theory of Operation

- 2.2 PCB/Schematic Diagram and Parts List

# Chapter 2.1

## Introduction/Theory of Operation

| Paragra | aph                                | Page |

|---------|------------------------------------|------|

| 1.0     | Overview                           | 1    |

| 2.0     | Exploded View Diagram              | 2    |

| 3.0     | Theory of Operation                | 2    |

| 3.1     | General                            | 2    |

| 3.2     | Power Supplies                     | 3    |

| 3.3     | Voltage Regulator Circuit          | 3    |

| 3.4     | Power On / Off                     | 3    |

| 3.5     | Microprocessor Circuit             | 4    |

| 3.6     | Serial Peripheral Interface (SPI)  |      |

| 3.7     | Keypad Keys                        | 5    |

| 3.8     | Status LED and Back Light Circuit  |      |

| 3.9     | Liquid Crystal Display (LCD)       | 5    |

| 3.10    | Microphone Connector               | 6    |

| 3 11    | Flectrostatic Transient Protection | 6    |

#### 1.0 Overview

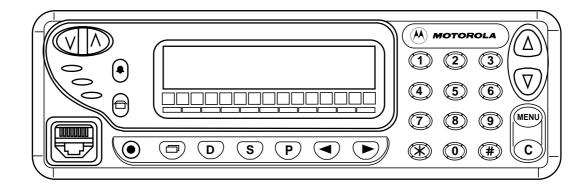

#### 128 Channel, Keypad/Display Radio Control Head (Model K6)

The features of the radio control head are as follows:

- □ On/Off Button

□ Rocker type Volume Up/Down Control

□ Volume Level Indicators (RSSI)

□ Backlit Liquid Crystal Display (LCD) with display icons to show call progress and status

□ Up/Down scrolling keys for the display

□ Left/Right scrolling keys for the display

- 3 x 4 CCITT Keypad Microphone Socket  $\Box$ Clear/Edit Button  $\Box$ Menu Button Status Button Personality Button **Data Button** Call In Absence Button

- □ Base Call Button □ External Alarm Button

- ☐ 3 LED's (Red, Yellow and Green)

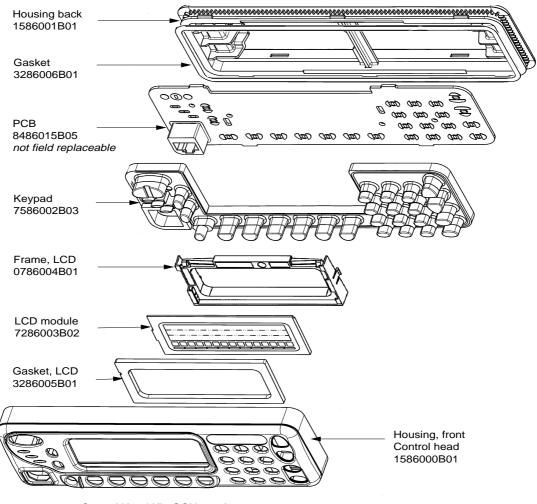

#### 2.0 Exploded View Diagram

Control Head Kit GCN6110A

LAPD0008-2

### 3.0 Theory of Operation

#### 3.1 General

The control head contains the microphone connector, several buttons to operate the radio, several indicator Light Emitting Diodes (LED) to inform the user about the radio status and a Liquid Crystal Display (LCD) with 19 pre - defined symbols, 11 bars and a 24x120 dot matrix for graphical or alpha - numerical information e.g. channel number, select code, call address name. To control the LEDs and the LCD, and to communicate with the host radio, the control head uses the Motorola 68HC11E9 or 68HC11E20 (dependent on the used character set) microprocessor.

#### 3.2 Power Supplies

The power supply to the control head is taken from the host radio FLT A+ voltage via connector J0901 pin 2. The voltage FLT A+ is at battery level and is used for the LEDs, the back light, to power up the radio via On / Off button and to supply the voltage regulator circuit. The regulator circuit provides the stabilized +5 volt which is used for the microprocessor circuit, the display, the display driver and the keypad buttons. The voltage +5V USW also provided by the regulator circuit is used to buffer the internal RAM of the microprocessor (U0901). The regulated +5V taken from the host radio via connector J0901 pin 10 (line +5V SOURCE) is only used to switch on or off the voltage regulator in the control head.

#### 3.3 Voltage Regulator Circuit

Voltage regulator U0891 provides 5V for the control head. The supply voltage FLT A+ for the voltage regulator is fed via parallel resistors R0893/4 and dual diode D0891 to pin 8 of U0891. The +5 volt output is switched on and off by the host radio's 5 volt source via line +5V SOURCE and control transistor Q0891. When the host radio is switched off the voltage on line +5V SOURCE is at ground level and switches off transistor Q0891. Pull up resistor R0892 pulls input SHUTDOWN (pin 3) of the voltage regulator U0891 to FLT A+ level and switches off the output of U0891 (pin 1). When the host radio is switched on the voltage on line +5V SOURCE of about +5 volts switches on transistor Q0891 which in turn pulls input SHUTDOWN (pin 3) to ground and switches on the output of U0891. Input and output capacitors (C0892 / C0893 and C0895 - C0896) are used to reduce high frequency noise and provide proper operation during battery transients. Diode D0891 prevents discharge of C0893 by negative spikes on the FLT A+ voltage. This regulator provides a reset output (pin 5) that goes to 0 volts if the regulator output goes out of regulation. This is used to reset the microprocessor (U0901) and the display driver (U0902) to prevent improper operation.

The voltage +5V USW derived from voltage FLT A+ is stabilized using resistor R0896 and diode VR0891 This voltage is used to buffer the microprocessor's internal RAM. C0898 allows the battery voltage to be disconnected for a couple of seconds without losing RAM parameters. Diode D0892 prevents radio circuitry from discharging this capacitor. The +5V at the second anode of D0892 speeds up charging of C0898 when the host radio is turned on by a high level at the ignition input while the supply voltage is applied to the radio. This prevents the microprocessor from accidently entering bootstrap mode.

#### 3.4 Power On / Off

The On/Off button when pressed switches the radio's voltage regulators on by pulling ON OFF CONTROL to high via D0931 and connects the base of Q0932 to FLT A+. This transistor pulls the line ANALOG 3 low to inform the  $\mu P$  that the On/Off button is pressed. If the radio is switched off, the  $\mu P$  will switch it on and vice versa. If the On/Off button is pressed and held while the radio is on, the software detects a low state on line ANALOG 3 and switches the radio off. If the radio is switched on either manually or automatically its +5V source switches on the control head voltage regulator U0891 via line +5 SOURCE and transistor Q0891 and the control head microprocessor starts execution.

#### 3.5 Microprocessor Circuit

The control head uses the Motorola 68HC11E9 or 68HC11E20 (dependent on the used character set) microprocessor ( $\mu$ P) (U0901) to control the LEDs, the LCD and to communicate with the host radio. RAM and ROM are contained within the microprocessor itself.

The clock generator for the microprocessor can use two different configurations:

- 1. The oscillator inside the microprocessor (U0901) along with a 4 MHz ceramic resonator (Y0922) and R0920 generate the clock.

- 2. The oscillator inside the microprocessor (U0901) along with some external components (C0922-C0924, L0921, R0922, Y0921) generate the 7.9488 MHz clock. Q0921 is used to alter the clock frequency slightly under software control if there is a possibility of harmonics of this clock source interfering with the desired radio receive frequency.

The microprocessor E9/E20 (U0101) contains internal 12 (E9) or 20 (E20) Kbytes ROM, 512 (E9) or 768 (E20) bytes SRAM and 512 bytes EEPROM.

The microprocessor's RAM is always powered to maintain parameters such as the last operating mode. This is achieved by maintaining 5V at U0901-25. Under normal conditions, when the radio is off +5V USW is formed by FLT A+ via D0892. C0898 allows the battery voltage to be disconnected for a couple of seconds without losing RAM parameters. Diode D0892 prevents radio circuitry from discharging this capacitor.

There are 8 analogue to digital converter ports (A/D) on U0901. They are labelled within the device block as PE0-PE7. These lines sense the voltage level ranging from 0 to 5V of the input line and convert that level to a number ranging from 0 to 255 which can be read by the software to take appropriate action.

U0901-22 is the high reference voltage for the A/D ports on the  $\mu$ P. Resistor R0927 and capacitor C0925 filter the +5V reference. If this voltage is lower than +5V the A/D readings will be incorrect. Likewise U0901-21 is the low reference for the A/D ports. This line is normally tied to ground. If this line is not connected to ground, the A/D readings will be incorrect.

The MODB (U0901-25) input of the  $\mu$ P must be at a logic '1' for it to start executing correctly. The XIRQ (U0901-45) and the IRQ (U0901-46) pins should also be at a logic '1'.

The microprocessor can determine the keypad type used, by reading the voltages at pins 63 and 64. Connections JU0911 and JU0912 are provided by the individual keypads.

Capacitors C0927 and C0928 serve to filter out any AC noise on +5V line at U0901.

#### 3.6 Serial Peripheral Interface (SPI)

The host radio (master) communicates to the control head  $\mu P$  (slave) through its SPI port (BUS). This port consists of SPI TRANSMIT DATA (SPI MOSI) (U0901-52), SPI RECEIVE DATA (SPI MISO) (U0901-51), SPI CLK (SPI CLCK BUF) (U0901-53) and a control head select line (CNTL HD CE) (U0901-54). This BUS is a synchronous bus, in that the timing clock signal SPI CLCK is sent while SPI data (SPI TRANSMIT DATA or SPI RECEIVE DATA) is sent. Therefore, whenever there is activity on either SPI TRANSMIT DATA or SPI RECEIVE DATA there should be a uniform signal on SPI CLK. The SPI TRANSMIT DATA is used to send serial from the host radio to the control head  $\mu P$ , and SPI RECEIVE DATA is used to send data from the control head  $\mu P$  to the host radio.

When the host radio needs to communicate to the control head  $\mu P$  it brings the control head select line (CNTL HD CE) to a logic '0' and then sends the proper data and clock signals. After the data has been sent the control head select line is returned to a logic '1'. When the control head  $\mu P$  wants to communicate to the host radio the  $\mu P$  brings request line CNTL HD REQ to a logic '0' by switching on transistor Q0931 via  $\mu P$  pin 11. The host radio then starts communication by activating the control head select line (CNTL HD CE), sending the clock signal and sending data via SPI MOSI or receiving data via SPI MISO and buffer U0931-1.

#### 3.7 Keypad Keys

The control head keypad is a 26 - key keypad. All keys are configured as 6 analogue lines (AN 0 - 5) to the control head  $\mu$ P. Lines AN 0 - 3 each control four keys, lines AN 4, 5 each control five keys. The voltage on the analogue lines varies between 0V and +5V depending on which key has been pressed. If a button is pressed, it will connect one of the 6 lines AN 0 - 5 to a resistive voltage divider R0807 - R0811 connected to +5V. The voltages of the lines are A/D converted inside the  $\mu$ P (ports PE 0 - 5) and specify the pressed button.

#### 3.8 Status LED and Back Light Circuit

All the indicator LEDs (D0881 - D0884) are driven by current sources Q0881 - Q0883. To change the LED status the host radio sends a data message via SERIAL PERIPHERAL INTERFACE (SPI) to the control head  $\mu P$ . The control head  $\mu P$  determines the LED status from the received message and switches the LEDs on or off via pins 5, 6, 7. The LED status is stored in the  $\mu P$ 's memory. The LED current is determined by the resistor at the emitter of the respective current source transistor.

The backlight for the LCD and the keypad is controlled by the host radio the same way as the indicator LEDs using μP pins 8, 9, 10. The keypad backlight current is drawn from the FLT A+ source and controlled by transistor Q0851. The current flowing through the LEDs cause a proportional voltage drop across the parallel resistors R0861, R0862. This voltage drop is amplified by the opamp U0831-2. U0831-2 and Q0852 form a differential amplifier. The voltage difference between the base of Q0852 and the output of U0831-2 determines the current from the base of the LED control transistor Q0851 and in turn the brightness of the LEDs. The µP can switch the LEDs on and off by a logic high or low level at the port connected to the base of Q0852. If the base of Q0852 is at ground level, Q0852 is switched off and no current flows through Q0851 and the LEDs. If the µP port changes to +5V a current flows through Q0852 and in turn through Q0851 causing the LEDs to turn on and a rising voltage drop across R0861, R0862. The rising voltage causes the output of the opamp to rise and to reduce the base to emitter voltage of Q0852. This decreases the current of Q0852 until the loop has settled. The backlight for the LCD uses a similar circuit. By using two µP ports (pin 8, 9) and different weighting resistors R0837 and R0838 the base of Q0832 can be set to four different voltage levels. This allows to switch the LEDs off or to select among three levels of brightness.

#### 3.9 Liquid Crystal Display (LCD)

The LCD module U0902 consists of the display and the display driver. The display is a single layer super twist nematic (STN) LCD display. It has a dot matrix of 24 x120 dots for displaying graphics and alpha - numerical information, a line with 19 pre - defined icons below the dot matrix and line with 11 bars below the icon line. Six of the bars can be used to display the status of the keys located below.

The display driver is fixed on the flex which connects the display to the PC board. The driver contains a data interface to the  $\mu$ P, an LCD segment driver, an LCD power circuit, an oscillator, data RAM and control logic. At power up the driver's control logic is reset by a logic '0' at input RES (U0902-9). Resistor R0946 sets the driver's internal oscillator to about 18 kHz. By connecting U0902 pin 12 to +5V the driver's  $\mu$ P interface is configured to accept 8 bit parallel data input (U0902-D0-D7) from the control head  $\mu$ P (U0901 port PC0-PC7). Pin 15 connected to +5V sets the 6800  $\mu$ P control mode.

To write data to the driver's RAM the  $\mu P$  sets chip select (U0902-14) to logic '1' via U0901-59 and R/W (U0902-17) to logic '0' via U0901-56. With input A0 (U0902-16) set to logic '0' via U0901-58 the  $\mu P$  writes control data to the driver. Clock signal E at pin 18 generated by  $\mu P$  pin 57, shifts 8 bit parallel data into the driver. Control data includes the RAM start address for the following display data. With input A0 set to logic '1' the  $\mu P$  then writes the display data to the display RAM. When data transfer is complete the  $\mu P$  terminates the chip select and the clock activities.

The voltage supply for the display is provided by the display driver power circuit. This circuit consists of a voltage multiplier, voltage regulator and a voltage follower. To use an external voltage supply the built-in power circuit can be turned off by a control command. The settings of the inputs T1 (U0902-36) and T2 (U0902-35) select among the various functions of the power circuit. With both inputs set to ground level by resistors R0955 and R0956 the voltage multiplier, the voltage regulator and the voltage follower are activated and no external voltage supply is required for the LCD. The external capacitors C0951 - C0953 configure the multiplier to triple the supply voltage. If R0957 is used instead of C0952 the multiplier doubles the supply voltage. In this configuration the multiplier output VOUT (U0902-42) supplies a voltage of -5V (2\* -5V below VDD). The multiplied voltage VOUT is sent to the internal voltage regulator. To set the voltage level of the regulator output V5 (U0902-43) this voltage is divided by the resistors R0958 and R0959 and feed back to the reference input VR (U0902-44). In addition the regulator output voltage V5 can be controlled electronically by a control command sent to the driver. With the used configuration the voltage V5 is about -3V. The voltage V5 is resistively divided by the driver's voltage follower to provide the voltages V1 - V4. These voltages are needed for driving the liquid crystals. The driver circuit can be configured to use externally generated voltages for VOUT and V1 - V5. In this case the +5V supply voltage is multiplied by the μP (U0901-62) along with the multiplier circuit D0911, C0912, R0911 and R0913. The μP provides a square wave signal at pin 62 to drive the multiplier circuit. The voltages V1-V4 are generated from VOUT or V5 by the resistive divider R0941 - R0945 and supplied to the driver ports V1 - V5. Dependent on the configuration the level of VOUT or V5 can be measured by one of the μP's analogue to digital converters (U0901-20) via resistive divider R0914, R0915. To stabilize the display brightness over a large temperature range the µP measures the temperature via analogue to digital converter (U0901-18) using thermistor R0918 and resistor R0917. Dependent on the measured temperature the µP adjusts the driver output voltage V5, and in turn the display brightness, via parallel interface.

#### 3.10 Microphone Connector

Signals BUS+, PTT, HOOK, MIC HI, HANDSET AUDIO and FLT A+ available at the microphone connector J0903, are connected to the radio's controller section via connector J0901.

#### 3.11 Electrostatic Transient Protection

Electrostatic transient protection is provided for the sensitive components in the control head by diodes VR0901 - VR0905, VR0931 - VR0935. The diodes limit any transient voltages to tolerable levels. The associated capacitors provide Radio Frequency Interference (RFI) protection.

# Chapter 2.2

## PCB/Schematic Diagram and Parts List

| Description                                                       | Page |

|-------------------------------------------------------------------|------|

| Display/Keypad Radio Control Head (K6) - Diagrams and Parts Lists |      |

| PCB Layout Top Side                                               | 1    |

| PCB Layout Bottom Side                                            | 1    |

| Schematic Diagram 1 of 2                                          | 2    |

| Schematic Diagram 2 of 2                                          | 3    |

| Parts List                                                        | 4    |

# Chapter 3

## UHF/VHF Radio - Level 3 Information

## **Table of Contents**

## Chapter

- 3.1 Introduction/Theory of Operation

- 3.2 PCB/Schematic Diagrams and Parts Lists

# Chapter 3.1

## Introduction/Theory of Operation

| Paragra | ph Page                                                            |

|---------|--------------------------------------------------------------------|

| 1.0     | Introduction 1                                                     |

| 2.0     | Open Controller1                                                   |

| 2.1     | General1                                                           |

| 2.2     | Voltage Regulators 1                                               |

| 2.3     | Electronic On/Off                                                  |

| 2.4     | Emergency2                                                         |

| 2.5     | Mechanical On/Off                                                  |

| 2.6     | Ignition                                                           |

| 2.7     | Hook RSS3                                                          |

| 2.8     | Microprocessor Clock Synthesizer 4                                 |

| 2.9     | Serial Peripheral Interface (SPI)4                                 |

| 2.10    | SPEB Serial Interface5                                             |

| 2.11    | General Purpose Input/Output6                                      |

| 2.12    | Normal Microprocessor Operation6                                   |

| 2.13    | FLASH Electronically Erasable Programmable Memory (FLASH EEPROM) 8 |

| 2.14    | Electrically Erasable Programmable Memory (EEPROM) 8               |

| 2.15    | Static Random Access Memory (SRAM)9                                |

|         | Controller Audio and Signalling Circuits                           |

| 3.0     | General 9                                                          |

| 3.1     | Audio Signalling Filter IC (ASFIC)9                                |

| 3.2     | Audio Ground9                                                      |

| 4.0     | Transmit Audio Circuits                                            |

| 4.1     | Mic Input Path                                                     |

| 4.2     | External Mic Path11                                                |

| 4.3     | PTT Sensing and TX Audio Processing 11                             |

| 4.4     | TX Secure Audio (optional)11                                       |

|         |                                                                    |

| Paragra | ph Pa                                                 | ige  |

|---------|-------------------------------------------------------|------|

| 5.0     | Transmit Signalling Circuits                          |      |

| 5.1     | Sub-audible Data (PL/DPL)                             |      |

| 5.2     | High Speed Data                                       |      |

| 5.3     | Dual Tone Multiple Frequency (DTMF) Data              | 13   |

| 6.0     | Receive Audio Circuits                                | . 14 |

| 6.1     | Squelch Detect                                        | . 14 |

| 6.2     | Audio Processing and Digital Volume Control           | . 15 |

| 6.3     | Audio Amplification Speaker (+) Speaker (-)           | . 15 |

| 6.4     | Handset Audio                                         | . 16 |

| 6.5     | Filtered Audio                                        |      |

| 6.6     | RX Secure Audio (optional)                            | . 16 |

| 7.0     | Receive Signalling Circuits                           | . 17 |

| 7.1     | Sub-audible Data (PL/DPL) and High Speed Data Decoder | . 17 |

| 7.2     | Alert Tone Circuits                                   |      |

|         | UHF (403-470MHz) SPECIFIC CIRCUIT DESCRIPTION         |      |

| 8.0     | Receiver Front-End                                    | . 18 |

| 8.1     | Front-End Band-Pass Filter & Pre-Amplifier            | . 18 |

| 8.2     | Mixer and Intermediate Frequency (IF) Section         |      |

| 8.3     | IF IC (U5201)                                         |      |

| 9.0     | Transmitter Power Amplifier (PA) 5-25W                | . 19 |

| 9.1     | Power Controlled Stage                                | . 19 |

| 9.2     | PA Stages                                             | 20   |

| 9.3     | Directional Coupler                                   | 20   |

| 9.4     | Antenna Switch                                        | 21   |

| 9.5     | Harmonic Filter                                       | . 21 |

| 9.6     | Power Control                                         | . 21 |

| 10.0    | Frequency Synthesis                                   | 23   |

| 10.1    | Reference Oscillator                                  | . 23 |

| 10.2    | Fractional-N Synthesizer (U5701)                      | 23   |

| 10.3    | Voltage Controlled Oscillator (VCO)                   | 24   |

| 10.4    | Synthesizer Operation                                 | 24   |

#### Paragraph Page VHF (136-174MHz) SPECIFIC CIRCUIT DESCRIPTION 11.0 11.1 11.2 11.3 12.0 12.1 12.2 12.3 12.4 12.5 12.6 13.0 13.1 13.2 13.3 13.4

#### 1.0 Introduction

This section provides a detailed theory of operation for the radio and its components. The main radio is a single board design, consisting of the transmitter, receiver, and controller circuits.

The main board is designed to accept one additional option board. This may provide functions such as secure voice/data or DTMF decoder. The control head is mounted directly on the front of the radio or connected via an extension cable in remote mount operation. The control head contains LED indicators, a microphone connector, buttons/keypad and a display. These provide the user with interface control over the various features of the radio.

In addition to the power cable and antenna cable, an accessory cable can be attached to a connector on the rear of the radio. The accessory cable provides the necessary connections for items such as external speaker, emergency switch, foot operated PTT, ignition sensing, etc.

#### 2.0 Open Controller

#### 2.1 General

| The r | adio controller consists of 4 main subsections |

|-------|------------------------------------------------|

|       | Digital Control                                |

|       | Audio Processing                               |

|       | Power Control                                  |

|       | Voltage Regulation                             |

The digital control section of the radio board is based upon an open architecture controller configuration. It consists of a microprocessor, support memory, support logic, signal MUX ICs, the On/Off circuit, and general purpose Input/Output circuitry.

The controller uses the Motorola 68HC11K1 microprocessor (U0101). In addition to the microprocessor, the controller has 3 external memory devices. The 3 memory devices consist of a 32kbyte SRAM (U0103), a 512kbyte FLASH EEPROM (U0102), and a 16kbyte EEPROM (U0104).

Note: From this point on the 68HC11K1 microprocessor will be referred to as  $\mu P$  or K1 $\mu P$ . References to the control head will be to the Display/Keypad radio model (K6).

#### 2.2 Voltage Regulators

Voltage regulation for the controller is provided by 3 separate devices; U0631 (LP2951CM) +5V, U0601 (LM2941T) +9.3V, and UNSW 5V (a combination of R0621 and VR0621). An additional regulator is located in the RF section.

Voltage regulation providing 5V for the digital circuitry is done by U0631. Input and output capacitors (C0631/C0632 and C0633-C0635) are used to reduce high frequency noise and provide proper operation during battery transients. This regulator provides a reset output (pin 5) that goes to 0 volts if the regulator output goes out of regulation. This is used to reset the controller to prevent improper operation. Diode D0631 prevents discharge of C0632 by negative spikes on the 9V3 voltage.

Regulator U0601 is used to generate the 9.3 volts required by some audio circuits, the RF circuitry and power control circuitry. Input and output capacitors (C0601-C0603 and C0604/C0605) are used to reduce high frequency noise. R0602/R0603 set the output voltage of the regulator. If the voltage at pin 1 is greater than 1.3 volts the regulator output decreases and if the voltage is less than 1.3 volts the regulator output increases. This regulator output is electronically enabled by a 0 volt signal on pin 2. Q0601 and associated circuitry (R0601/R0604/R0605) are used to disable the regulator when the radio is turned off.

UNSW 5V is only used in a few areas which draw low current and require 5 V while the radio is off.

UNSW 5V CL is used to buffer the internal RAM. C0622 allows the battery voltage to be disconnected for a couple of seconds without losing RAM parameters. Diode D0621 prevents radio circuitry from discharging this capacitor.

The voltage 9V3 SUPP is only used in the VHF radio (T1) to supply the drain current for the RF MOS FET in the PA. The voltage SW B+ is monitored by the  $\mu$ P through the voltage divider R0641/R0642 and line BATTERY VOLTAGE. Diode VR0641 limits the divided voltage to 5.1V to protect the  $\mu$ P.

Diode D5601 (UHF) / D3601 (VHF) / D2601 (MB) located on the PA section acts as protection against transients and wrong polarity of the supply voltage.

#### 2.3 Electronic On/Off

The radio has circuitry which allows radio software and/or external triggers to turn the radio on or off without direct user action. For example, automatic turn on when ignition is sensed and off when ignition is off.

Q0611 is used to provide SW B+ to the various radio circuits. Q0611 contains a pnp and an npn transistor and acts as an electronic on/off switch. The switch is on when the collector of the npn transistor (Q0611-1) is low. When the radio is off the pnp transistor is cutoff and the voltage at pin 1 is at A+. This effectively prevents current flow through the pnp transistor from emitter (pin 3) to collector (pin 2).

When the radio is turned on the voltage at the Q0611 pin 4 is high (about 4.4V) and the npn transistor switches on (saturation) and pulls down the voltage at the base of the pnp transistor. With Transistor Q0611 now "enabled" current flows through the device from pin 3 to pin 2. This path has a very low impedance (less than 1 ohm) from emitter to collector. This effectively provides the same voltage level at SWB+ as at A+.

The electronic on/off circuitry can be enabled by the microprocessor (through ASFIC port GCB2, line B+ CONTROL), the emergency switch (line EMERGENCY CONTROL), the mechanical On/Off button on the control head (line ON OFF CONTROL), or the ignition sense circuitry (line IGNITION CONTROL). If any of the 4 paths cause a low at Q0611 pin 1, the electronic ON is engaged.

#### 2.4 Emergency

The emergency switch (J0400-9), when engaged, grounds the base of Q0441 and pulls the line EMERGENCY CONTROL to low via D0441. EMER IGN SENSE is pulled high by R0441. When the emergency switch is released the base of Q0441 is pulled high by R0442. This causes the collector of transistor Q0441 to go low (0.2V), thereby setting the EMER IGN SENSE line to low.

While EMERGENCY CONTROL is low, SW B+ is on, the microprocessor starts execution, reads that the emergency input is active through the voltage level of EMER IGN SENSE, and sets the B+ CONTROL output of the ASFIC pin B4 to a logic high. This high will keep Q0611 switched on. This operation allows a momentary press of the emergency switch to power up the radio. When the microprocessor has finished processing the emergency press, it sets the B+ CONTROL line to a logic 0. This turns off Q0611 and the radio turns off. Notice that the microprocessor is alerted to the emergency condition via line EMER IGN SENSE. If the radio was already on when emergency was triggered then B+ CONTROL would already be high.

#### 2.5 Mechanical On/Off

This refers to the typical on/off button, located on the control head, and which turns the radio on and off. If the radio is turned off and the on/off button is pressed, line ON OFF CONTROL goes high and switches the radio on as long as the button is pressed. The microprocessor is alerted through line ANALOG 3 which is pulled to low by Q0925 (Display/Keypad Control Head) while the on/off button is pressed. If the software detects a low state it asserts B+ CONTROL via ASFIC pin B4 high which keeps Q0611, and in turn the radio switched on.

If the on/off button is pressed and held while the radio is on, the software detects the line ANALOG 3 changing to low and switches the radio off by setting B+ CONTROL to low.

#### 2.6 Ignition

Ignition sense is used to prevent the radio from draining the vehicle's battery because the engine is not running.

When the IGNITION input (J0400-10) goes above 6 volts Q0611 is turned on via line IGNITION CONTROL. Q0611 turns on SW B+ and the microprocessor starts execution. A high IGNITION input reduces the voltage of line EMER IGN SENSE by turning on Q0450. The software reads the line EMER IGN SENSE, determines from the level (Emergency has a different level) that the IGNITION input is active and sets the B+ CONTROL output of the ASFIC pin B4 to high to latch on SW B+.

When the IGNITION input goes below 6 volts, Q0450 switches off and R0449, R0450 pull line EMER IGN SENSE high. The software is alerted by line EMER IGN SENSE to switch off the radio by setting B+ CONTROL to low. The next time the IGNITION input goes above 6 volts the above process will be repeated.

#### 2.7 Hook RSS

The HOOK RSS input is used to inform the  $\mu P$  when the Microphone's hang-up switch is engaged. Dependent on the radio model the  $\mu P$  may take actions like turning the audio PA on or off. The signal is routed from J0101-3 and J0400-14 through transistor Q0101 to the K1 $\mu P$  U0101-23. The voltage range of HOOK RSS in normal operating mode is 0-5V.

To start SBEP communication this voltage must be above 6V. This condition generates a  $\mu$ P interrupt via VR0102, Q0105, Q0104, Q0106 and enables the BUS+ line for communication via Q0122, Q0121.

#### 2.8 Microprocessor Clock Synthesizer

The clock source for the microprocessor system is generated by the ASFIC (U0201). Upon power-up the synthesizer U5701 (UHF) / U3701 (VHF) / U2701 (MB) generates a 2.1 MHz waveform that is routed from the RF section (via C0202) to the ASFIC (on U0201-E1) For the main board controller the ASFIC uses 2.1MHz as a reference input clock signal for its internal synthesizer. The ASFIC, in addition to audio circuitry, has a programmable synthesizer which can generate a synthesized signal ranging from 1200Hz to 32.769MHz in 1200 Hz steps.

When power is first applied, the ASFIC will generate its default 3.6864 MHz CMOS square wave  $\mu P$  CLK (on U0201-D1) and this is routed to the microprocessor (U0101-73). After the microprocessor starts operation, it reprograms the ASFIC clock synthesizer to a higher  $\mu P$  CLK frequency (usually 7.9488 MHz) and continues operation.

The ASFIC may be reprogrammed to change the clock synthesizer frequencies at various times depending on the software features that are executing. In addition, the clock frequency of the synthesizer is changed in small amounts if there is a possibility of harmonics of this clock source interfering with the desired radio receive frequency.

The ASFIC synthesizer loop uses C0228, C0229 and R0222 to set the switching time and jitter of the clock output. If the synthesizer cannot generate the required clock frequency it will switch back to its default 3.6864MHz output.

Because the ASFIC synthesizer and the  $\mu P$  system will not operate without the 2.1MHz reference clock, it (and the voltage regulators) should be checked first when debugging the system.

#### 2.9 Serial Peripheral Interface (SPI)

The  $\mu P$  communicates to many of the ICs through its SPI port. This port consists of SPI TRANSMIT DATA (MOSI) (U0101-1), SPI RECEIVE DATA (MISO) (U0101-80), SPI CLK (U0101-2) and chip select lines going to the various ICs, connected on the SPI PORT (BUS). This BUS is a synchronous bus, in that the timing clock signal CLK is sent while SPI data (SPI TRANSMIT DATA or SPI RECEIVE DATA) is sent. Therefore, whenever there is activity on either SPI TRANSMIT DATA or SPI RECEIVE DATA there should be a uniform signal on CLK. The SPI TRANSMIT DATA is used to send serial from a  $\mu P$  to a device, and SPI RECEIVE DATA is used to send data from a device to a  $\mu P$ . The only device from which data can be received via SPI RECEIVE DATA is the EEPROM (U0104 or U0107) and a control head with graphical display (Display/Keypad Radio Model K6).

On the controller there are three ICs on the SPI BUS, ASFIC (U0201-F2), EEPROM (U0104-1 or U0107-1) and D/A (U0731-6). In the RF sections there is one IC on the SPI BUS which is the FRAC-N Synthesizer. The SPI TRANSMIT DATA and CLK lines going to the RF section are filtered by L0131/L0132 to minimize noise. The chip select lines for the IC's are decoded by the address decoder U0105.

The SPI BUS is also used for the control head. U0106-2,3 buffer the SPI TRANSMIT DATA and CLK lines to the control head. U0106-1 switch off the CLK signal for the LCD display if it is not selected via LCD CE and Q0141.

When the  $\mu P$  needs to program any of these IC's it brings the chip select line for that IC to a logic 0 and then sends the proper data and clock signals. The amount of data sent to the various IC's are different, for example the FRAC-N can receive up to 21 bytes (168 bits) while the DAC can receive up to 3 bytes (24 bits). After the data has been sent the chip select line is returned to a logic 1.

When the control head with graphical display wants to communicate to the  $\mu P$  it brings request line ANALOG 2 (J0101-11) to a logic "0". The  $\mu P$  reads this line via one of the analogue to digital converters (U0101-48) and then starts communication by activating the control head select line (LED CHT CE) via U0105-9 and J0101-12, sending the clock signal via U0106-3 and J0101-5 and sending data via U0106-2 and J0101-6 or receiving data via J0101-10 and gate U0171. During data transfer gate U0171 is switched on by line LED CHT CE via transistor Q0171 and gate U0172-1. Gate U0172-1 is enabled by the  $\mu P$  via ASFIC output GCB4 (U0201-A2).

The Option board interfaces are different in that the  $\mu P$  can also read data back from devices connected. The timing and operation of this interface is specific to the option connected, but generally follows the pattern:

- 1. an option board device generates an interrupt via J0103-8, Q0124, Q0125 and  $\mu P$  pin 61 (IRQ). The  $\mu P$  determines the interrupt source by reading a high at the collector of Q0124 via  $\mu P$  pin 7 and R0129.

- 2. the main board asserts a chip select for that option board device via U0105-10, J0102-5,

- 3. the main board  $\mu P$  generates the CLK (J0102-6),

- 4. the main board μP writes serial data via J0102-4 and reads serial data via J0102-2 and,

- 5. when data transfer is complete the main board terminates the chip select and CLK activity.

#### 2.10 SPEB Serial Interface

The SBEP serial interface allows the radio to communicate with the Dealer Programming Software (DPS) via the Radio Interface Box (RIB). This interface connects to the Microphone connector (J0903/J0803) via Control Head connector (J0101-15) or to the accessory connector J0400-6 and comprises BUS+ (J0101-15). The line is bi-directional, meaning that either the radio or the DPS can drive the line.

When the RIB (Radio Interface Box) is connected to the radio, a voltage on the HOOK RSS line above 6 volts switches on Q0105. The low state at collector of Q0105 switches Q0104 off and in turn, Q0106 on. A high to low transition at the collector of Q0106 generates an interrupt via  $\mu P$  pin 61. The  $\mu P$  determines the interrupt source by reading a high at the collector of Q0104 via  $\mu P$  pin 6 and R0125. The switched on Q0105 also switches off Q0122 enabling the  $\mu P$  to read BUS+ via pin 78 and to write BUS+ via pin 79 and transistors Q0123, Q0121. While the radio is sending serial data at pin 79 via Q0123 and Q0121 it receives an "echo" of the same data at pin 78.

When the voltage on the HOOK RSS line is below 6 volts (RIB is not connected), the high collector of Q0105 turns on Q0122. The low collector of Q0122 prevents the  $\mu P$  from writing data to BUS+ via Q0123. In this mode line BUS+ is used for signal SCI RX of the Serial Communication Interface (SCI). The  $\mu P$  reads the SCI via signal SCI RX (pin 78) and writes via signal SCI TX (pin 79). Both signals are available on the accessory connector J0400 (SCI DATA OUT, SCI DATA IN).

#### 2.11 General Purpose Input/Output

The Controller provides one general purpose line (GP I/O) available on the accessory connector J0400-12 to interface to external options. The software and the hardware configuration of the radio model defines the function of the port. The port uses an output transistor (Q0432) controlled by  $\mu P$  via ASFIC port GCB3 (pin B3).

An external alarm output, available on J0400 pin 4 is generated by the  $\mu P$  via ASFIC port GCB1 (pin A3) and transistor Q0411. Input EXTERNAL PTT on J0400 pin 3 is read by the  $\mu P$  via line REAR PTT and  $\mu P$  pin 8.

Pin 13 of the accessory connector J0400 provides a voltage at battery level while the radio is switched on. The output is capable to drive a dc current up to 20mA. When the radio is switched on, the voltage 9V3 turns on transistor Q0482. Transistor Q0482 switches on Q0481 and enables a current flow from emitter to collector of Q0481. This path has a very low impedance and effectively provides the same voltage level at SW FLT A+ as at FLT A+. If the radio is switched off the voltage 9V3 is at ground level which switches off Q0482 and in turn cuts off the current from emitter to collector of Q0481.

#### 2.12 Normal Microprocessor Operation

For this radio, the  $\mu P$  is configured to operate in one of two modes, expanded and bootstrap. In expanded mode the  $\mu P$  uses external memory devices to operate, whereas in bootstrap operation the  $\mu P$  uses only its internal memory. In normal operation of the radio the  $\mu P$  is operating in expanded mode as described below.

In expanded mode on this radio, the  $\mu P$  (U0101) has access to three external memory devices; U0102 (FLASH EEPROM), U0103 (SRAM), U0104 or U0107 (optional EEPROM). Also, within the  $\mu P$  there are 768 bytes of internal RAM and 640 bytes of internal EEPROM, as well as logic to select external memory devices.

The (optional) external EEPROM (U0104 or U0107) as well as the  $\mu P$ 's own internal EEPROM space contain the information in the radio which is customer specific, referred to as the codeplug. This information consists of items such as: 1) what band the radio operates in, 2) what frequencies are assigned to what channel, and 3) tuning information. In general tuning information and other more frequently accessed items are stored in the internal EEPROM (space within the 68HC11K1), while the remaining data is stored in the external EEPROM. (See the particular device subsection for more details.)

The external SRAM (U0103) as well as the  $\mu$ P's own internal RAM space are used for temporary calculations required by the software during execution. All of the data stored in both of these locations is lost when the radio powers off (See the particular device subsection for more details).

The FLASH EEPROM contains the actual Radio Operating Software. This software is common to all open architecture radios within a given model type. For example Securenet radios may have a different version of software in the FLASH EEPROM than a non-secure radio (See the particular device subsection for more details).

The K1 $\mu$ P provides an address bus of 16 address lines (A0-A15), and a data bus of 8 data lines (D0-D7). There are also three control lines; CSPROG (U0101-29) to chip select U0102-30 (FLASH EEPROM), CSGP2 (U0101-28) to chip select U0103-20 (SRAM) and PG7\_R\_W to select whether to read or to write. All other chips (ASFIC/PENDULLUM/DAC/FRACN/LCD/LED/optional EEPROM/OPTION BOARD) are selected by 3 lines of the  $\mu$ P using address decoder U0105. When the  $\mu$ P is functioning normally, the address and data lines should be toggling at CMOS logic levels.

Specifically, the logic high levels should be between 4.8 and 5.0 V, and the logic low levels should be between 0 and 0.2 V. No other intermediate levels should be observed, and the rise and fall times should be <30 ns.

The low-order address lines (A0-A7) and the data lines (D0-D7) should be toggling at a high rate, i.e., you should set your oscilloscope sweep to 1 us/div. or faster to observe individual pulses. High speed CMOS transitions should also be observed on the  $\mu P$  control lines.

On the  $\mu P$  the lines XIRQ (U0101-30), MODA LIR (U0101-77), MODB VSTPY (U0101-76) and RESET (U0101-75) should be high at all times during normal operation. Whenever a data or address line becomes open or shorted to an adjacent line, a common symptom is that the RESET line goes low periodically, with the period being in the order of 20 msecs. In the case of shorted lines you may also detect the line periodically at an intermediate level, i.e. around 2.5 V when 2 shorted lines attempt to drive to opposite rails.

The MODA LIR (U0101-77) and MODB VSTPY (U0101-76) inputs to the  $\mu P$  must be at a logic 1 for it to start executing correctly. After the  $\mu P$  starts execution it will periodically pulse these lines to determine the desired operating mode. While the Central Processing Unit (CPU) is running, MODA LIR is an open-drain CMOS output which goes low whenever the  $\mu P$  begins a new instruction (an instruction typically requires 2-4 external bus cycles, or memory fetches).

However, since it is an open-drain output, the waveform rise assumes an exponential shape similar to an RC circuit.

There are eight analogue to digital converter ports (A/D) on U0101. They are labelled within the device block as PE0-PE7. These lines sense the voltage level ranging from 0 to 5 V of the input line and convert that level to a number ranging from 0 to 255 which can be read by the software to take appropriate action.

For example, U0101-46 is the battery voltage detect line. R0641 and R0642 form a resistor divider on SWB+. With 30K and 10K and a voltage range of 11 V to 17 V, that A/D port would see 2.74 V to 4.24 V which would then be converted to ~140 to 217 respectively.

U0101-51 is the high reference voltage for the A/D ports on the  $\mu$ P. Resistor R0106 and capacitor C0106 filter the +5 V reference. If this voltage is lower than +5 V the A/D readings will be incorrect. Likewise U0101-50 is the low reference for the A/D ports. This line is normally tied to ground. If this line is not connected to ground, the A/D readings will be incorrect.

Capacitors C0104, C0105, C0113, C0114 serve to filter out any AC noise which may ride on +5V at U0101.

Input IRQ (U101-61) generates an interrupt, if either HOOK RSS (J0101-3) is higher than 6V (SBEP communication) and turns Q0106 on via Q0105, Q0104, or a low at the option interrupt pin (J0103-8) turns Q0124 off and Q0125 on. The  $\mu$ P determines the interrupt source by reading the collector of Q0104 via U0101-6 and the collector Q0124 via U0101-7.

## 2.13 FLASH Electronically Erasable Programmable Memory (FLASH EEPROM)

The 512 KByte FLASH EEPROM (U0102) contains the radio operating software. This software is common to all open architecture radios within a given model type. This is, as opposed to the codeplug information stored in EEPROM (U0104) which could be different from one user to another in the same company.

In normal operating mode, this memory is only read, not written to. The memory access signals (CE, OE and WE) are generated by the  $\mu$ P.

To upgrade/reprogram the FLASH software, the  $\mu P$  must be set in bootstrap operating mode, and the FLASH device pin (U0102-9)  $V_{pp}$  must be between 11.4 and 12.6 V. This voltage switches Q0102 on and in turn Q0103 off. The low state at collector of Q0102 pulls MODA LIR (U0101-77) and MODB VSTBY (U0101-76) via diode D0101 to low which enables the bootstrap operating mode after power up. The high state at collector of Q0103 enables the  $\mu P$  to control the FLASH EN OE (U0102-32) input via U0106-4. Chip select (U102-30) and read or write operation (U102-7) are controlled by  $\mu P$  pins 29 and 33. In normal operating mode  $V_{PP}$  is below 5V which switches Q0102 off and Q0103 on.

The FLASH device may be reprogrammed 1,000 times without issue. It is not recommended to reprogram the FLASH device at a temperature below 0°C.

Capacitor C0131 serves to filter out any AC noise which may ride on +5V at U0101, and C0132 filters out any AC noise on  $V_{pp}$ .

## 2.14 Electrically Erasable Programmable Memory (EEPROM)

The optional EEPROM (U0104 or U0107) contains additional radio operating parameters such as operating frequency and signalling features, commonly known as the codeplug. It is also used to store radio operating state parameters such as current mode and volume. U0104 can have up to 8kbyte and U0107 up to 16 kbyte. This memory can be written to in excess of 100,000 times and will retain the data when power is removed from the radio. The memory access signals (SI, SO and SCK) are generated by the  $\mu P$  and chip select (CS) is generated by address decoder U0105-4.

Additional EEPROM is contained in the  $\mu P$  (U0101). This EEPROM is used to store radio tuning and alignment data. Like the external EEPROM this memory can be programmed multiple times and will retain the data when power is removed from the radio.

**Note:** The external EEPROM plus the 640 bytes of internal EEPROM in the 68HC11K1 comprise the complete codeplug.

## 2.15 Static Random Access Memory (SRAM)

The SRAM (U0103) contains temporary radio calculations or parameters that can change very frequently, and which are generated and stored by the software during its normal operation. The information is lost when the radio is turned off. The device allows an unlimited number of write cycles. SRAM accesses are indicated by the CS signal U103-20 (which comes from U101-CSGP2) going low. U0103 is commonly referred to as the external RAM as opposed to the internal RAM which is the 768 bytes of RAM which is part of the 68HC11K1. Both RAM spaces serve the purpose. However, the internal RAM is used for the calculated values which are accessed most often. Capacitor C0133 serves to filter out any ac noise which may ride on +5V at U0103.

#### CONTROLLER BOARD AUDIO AND SIGNALLING CIRCUITS

#### 3.0 General

#### 3.1 Audio Signalling Filter IC (ASFIC)

The ASFIC (U0201) used in the controller has 4 functions;

| RX/TX audio shaping, i.e. filtering, amplification, attenuation                                  |

|--------------------------------------------------------------------------------------------------|

| RX/TX signalling, PL/DPL/HST/MDC/MPT                                                             |

| Squelch detection                                                                                |

| Microprocessor clock signal generation (see Microprocessor Clock Synthesizer Description Block). |

The ASFIC is programmable through the SPI BUS (U0201-E3/F1/F2), normally receiving 21 bytes. This programming sets up various paths within the ASFIC to route audio and/or signalling signals through the appropriate filtering, gain and attenuator blocks. The ASFIC also has 6 General Control Bits GCB0-5 which are CMOS level outputs and used for AUDIO PA ENABLE (GCB0) to switch the audio PA on and off, EXTERNAL ALARM (GCB1) and B+ CONTROL (GCB2) to switch the voltage regulators (and the radio) on and off. GCB3 controls output GPI/O (accessory connector J0400-12), HIGH LOW BAND (GCB4) can be used to switch between band splits and GCB5 is available on the option board connector J0102-3. Output GCB4 controls gate U0171 via U0172-1 which enables the  $\mu P$  to receive data from the control head. The supply voltage for the ASFIC has additional filtering provided by Q0200, D0200, R0200, L0200 and C0200. Diode D0200 increases the voltage at the base of Q0200 about 0.6 volts above the 5 volt supply voltage to compensate the base - emiter voltage drop of Q0200.

#### 3.2 Audio Ground

VAG is the dc bias used as an audio ground for the op-amps that are external to the Audio Signalling Filter IC (ASFIC). U0251-1 form this bias by dividing 9.3V with resistors R0251, R0252 and buffering the 4.65V result with a voltage follower. VAG emerges at pin 1 of U0251-1. C0253 is a bypass capacitor for VAG. The ASFIC generates its own 2.5V bias for its internal circuitry. C0221 is the bypass for the ASFIC's audio ground dc bias. Note that while there are ASFIC VAG, and BOARD VAG (U0201-1) each of these are separate; they do not connect together.

#### 4.0 Transmit Audio Circuits

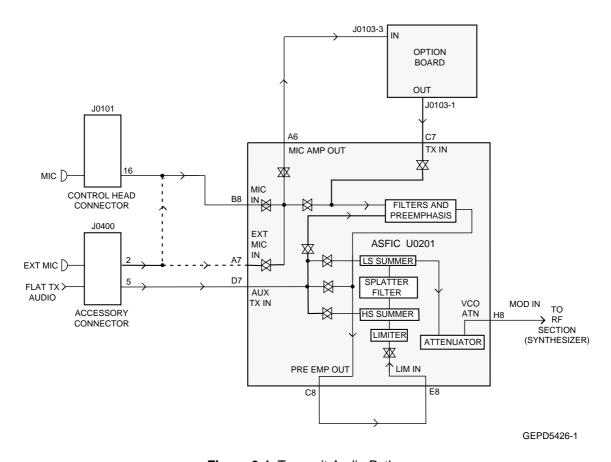

Refer to Figure 3-1 for reference for the following sections.

## 4.1 Mic Input Path

The radio supports two distinct microphone paths known as internal (from Control Head) and external mic (from accessory connector J0400-2) and an auxiliary path (FLAT TX AUDIO). The microphones used for the radio require a DC biasing voltage provided by a resistive network.

These two microphone audio inputs are connected together through R0413; resistors R0414 and R0415 are not placed. Following the internal mic path; the microphone is plugged into the radio control head and is connected to the controller board via J101-16.

From here the signal is routed to R0206. R0204 and R0205 provide the 9.3VDC bias and R0206 provides input protection for the CMOS amplifier input. R0205 and C0209 provide a  $1k\Omega$  AC path to ground that sets the input impedance for the microphone and determines the gain based on the emitter resistor in the microphone's amplifier circuit.

Figure 3-1 Transmit Audio Paths

Filter capacitor C0210 provides low-pass filtering to eliminate frequency components above 3 kHz, and C0211 serves as a DC blocking capacitor. The audio signal at U0201-B8 should be approximately 80mV for 1.5kHz or 3kHz of deviation with 12.5kHz or 25 kHz channel spacing. The FLAT TX AUDIO signal from accessory connector J0400-5 is buffered by op-amp U0202-1 and fed to the ASFIC U0201-D7 through C0205.

#### 4.2 External Mic Path

The external microphone signal enters the radio on accessory connector J0400 pin 2 and connects to the standard microphone input through R0413. Components R0414 - R0416, C0413, C0414, C0417 are not used.

## 4.3 PTT Sensing and TX Audio Processing

Mic PTT coming from the Control Head via connector J101-4 is sensed by the  $\mu P$  U0101 pin 22. An external PTT can be generated by grounding pin 3 on the accessory connector. When microphone PTT or externalPTT is sensed, the  $\mu P$  will always configure the ASFIC for the "internal" mic audio path.

Inside the ASFIC, the MIC audio is filtered to eliminate frequency components outside the 300-3000Hz voice band, pre-emphasized if pre-emphasis is enabled. The capacitor between ASFIC pre-emphasis out U0201-C8 and ASFIC limiter in U0201-E8 AC couples the signal between ASFIC blocks and prevents the DC bias at the ASFIC output U0201-H8 from shifting when the ASFIC transmit circuits are powered up. The signal is then limited to prevent the transmitter from over deviating. The limited MIC audio is then routed through a summer which, is used to add in signalling data, and then to a splatter filter to eliminate high frequency spectral components that could be generated by the limiter. The audio is then routed to two attenuators, which are tuned in the factory or the field to set the proper amount of FM deviation. The TX audio emerges from the ASFIC at U0201-H8 MOD IN, at which point it is routed to the RF section.

## 4.4 TX Secure Audio (optional)

The audio follows the normal transmit audio processing until it emerges from the ASFIC MIC AMP OUT pin (U0201-A6), which is fed to the Secure board residing at option connector J0103-3. The Secure board contains circuitry to amplify, encrypt, and filter the audio. The encrypted signal is then fed back from J0103-1 to the ASFIC TX IN input (U0201-C7). The signal level at this pin should be about 80mVrms. The signal is then routed through the TX path in the ASFIC and emerges at VCO ATN pin H8.

## 5.0 Transmit Signalling Circuits

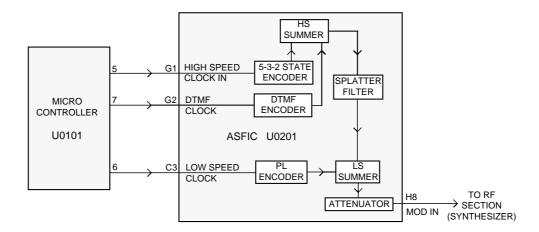

Refer to Figure 3-2 for reference for the following sections. From a hardware point of view, there are three types of signalling:

- 1. Sub-audible data (PL/DPL/Connect Tone) that gets summed with transmit voice or signalling,

- 2. DTMF data for telephone communication in trunked and conventional systems, and

- 3. Audible signalling including Select 5, MPT-1327, MDC, High speed Trunking.

**NOTE:** All three types are supported by the hardware while the radio software determines which signalling type is available.

GEPD5433

Figure 3-2 Transmit Signalling Paths

## 5.1 Sub-audible Data (PL/DPL)

Sub-audible data implies signalling whose bandwidth is below 300Hz. PL and DPL waveforms are used for conventional operation and connect tones for trunked voice channel operation. The trunking connect tone is simply a PL tone at a higher deviation level than PL in a conventional system. Although it is referred to as "sub-audible data," the actual frequency spectrum of these waveforms may be as high as 250 Hz, which is audible to the human ear. However, the radio receiver filters out any audio below 300Hz, so these tones are never heard in the actual system.

Only one type of sub-audible data can be generated by U0201 (ASFIC) at any one time. The process is as follows, using the SPI BUS, the  $\mu P$  programs the ASFIC to set up the proper low-speed data deviation and select the PL or DPL filters. The  $\mu P$  then generates a square wave which strobes the ASFIC PL / DPL encode input PL CLK U0201-C3 at twelve times the desired data rate. For example, for a PL frequency of 103Hz, the frequency of the square wave would be 1236Hz.

This drives a tone generator inside U0201 which generates a staircase approximation to a PL sine wave or DPL data pattern. This internal waveform is then low-pass filtered and summed with voice or data. The resulting summed waveform then appears on U0201-H8 (MOD IN), where it is sent to the RF board as previously described for transmit audio. A trunking connect tone would be generated in the same manner as a PL tone.

## 5.2 High Speed Data

High speed data refers to the 3600 baud data waveforms, known as Inbound Signalling Words (ISWs) used in a trunking system for high speed communication between the central controller and the radio. To generate an ISW, the  $\mu P$  first programs the ASFIC (U0201) to the proper filter and gain settings. It then begins strobing U0201-G1 (TRK CLK IN) with a pulse when the data is supposed to change states. U0201's 5-3-2 State Encoder (which is in a 2-state mode) is then fed to the post-limiter summer block and then the splatter filter.

From that point it is routed through the modulation attenuators and then out of the ASFIC to the RF board. MPT 1327 and MDC are generated in much the same way as Trunking ISW. However, in some cases these signals may also pass through a data pre-emphasis block in the ASFIC. Also these signalling schemes are based on sending a combination of 1200 Hz and 1800 Hz tones only. Microphone audio is muted during High Speed Data signalling.

## 5.3 Dual Tone Multiple Frequency (DTMF) Data

DTMF data is a dual tone waveform used during phone interconnect operation. It is the same type of tones which are heard when using a "Touch Tone" telephone.

There are seven frequencies, with four in the low group (697, 770, 852, 941Hz) and three in the high group (1209, 1336, 1477Hz).

The high-group tone is generated by the  $\mu P$  (U0101-5) strobing U0201-G1 at six times the tone frequency for tones less than 1440Hz or twice the frequency for tones greater than 1440Hz. The low group tone is generated by the  $\mu P$  (U0101-7) strobing U0201-G2 (DTMF CLCK) at six times the tone frequency. Inside U0201 the low-group and high-group tones are summed (with the amplitude of the high group tone being approximately 2 dB greater than that of the low group tone) and then preemphasized before being routed to the summer and splatter filter. The DTMF waveform then follows the same path as was described for high-speed data.

## 6.0 Receive Audio Circuits

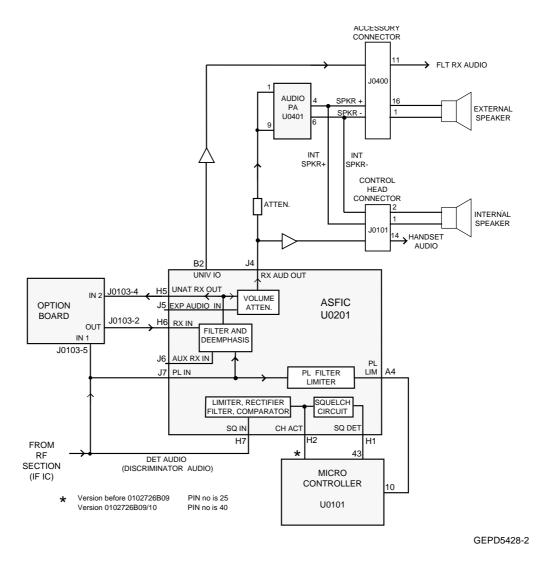

Refer to Figure 3-3 for reference for the following sections.

Figure 3-3 Receive Audio Paths.

## 6.1 Squelch Detect

The radio's RF circuits are constantly producing an output at the discriminator U5201-28 (UHF) / U5201-28 (VHF) / U2201-28 (MB). This signal (DET AUDIO) is routed to the ASFIC's squelch detect circuitry input SQ IN (U0201-H7). All of the squelch detect circuitry is contained within the ASFIC. Therefore from a user's point of view, DET AUDIO enters the ASFIC, and the ASFIC produces two CMOS logic outputs based on the result. They are CH ACT (U0201-H2) and SQ DET (U0201-H1).

The squelch signal entering the ASFIC is amplified, filtered, attenuated, and rectified. It is then sent to a comparator to produce an active high signal on CH ACT. A squelch tail circuit is used to produce SQ DET (U0201-H1) from CH ACT. The state of CH ACT and SQ DET is high (logic 1) when carrier is detected, otherwise low (logic 0).

CH ACT is routed to the  $\mu P$  pin 40 while SQ DET adds up with LOCK DET, weighted by resistors R0113, R0114, and is routed to one of the  $\mu P$ 's ADC inputs U0101-43. From the voltage weighted by the resistors the  $\mu P$  determines whether SQ DET, LOCK DET or both are active.

SQ DET is used to determine all audio mute/unmute decisions except for Conventional Scan. In this case CH ACT is a pre-indicator as it occurs slightly faster than SQ DET.

## 6.2 Audio Processing and Digital Volume Control

The receiver audio signal enters the controller section from the IF IC U5201-28 (UHF) / U5201-28 (VHF) / U2201-28 (MB) on DET AUDIO and passes through RC filter, R0203 and C0208 which filters out IF noise. The signal is AC coupled by C0207 and enters the ASFIC via the PL IN pin U0201-J7.

Inside the ASFIC, the signal goes through 2 paths in parallel, the audio path and the PL/DPL path.

The audio path has a programmable amplifier, whose setting is based on the channel bandwidth being received, then a LPF filter to remove any frequency components above 3000Hz and then an HPF to strip off any sub-audible data below 300Hz. Next, the recovered audio passes through a deemphasis filter if it is enabled (to compensate for Pre-emphasis which is used to reduce the effects of FM noise). The IC then passes the audio through the 8-bit programmable attenuator whose level is set depending on the value of the volume control. Finally the filtered audio signal passes through an output buffer within the ASFIC. The audio signal exits the ASFIC at RX AUDIO (U0201-J4).

The  $\mu P$  programs the attenuator, using the SPI BUS, based on the volume setting. The minimum / maximum settings of the attenuator are set by codeplug parameters.

Since sub-audible signalling is summed with voice information on transmit, it must be separated from the voice information before processing. Any sub-audible signalling enters the ASFIC from the IF IC at PL IN U0201-J7. Once inside it goes through the PL/DPL path.

The signal first passes through one of 2 low pass filters, either PL low pass filter or DPL/LST low pass filter. Either signal is then filtered and goes through a limiter and exits the ASFIC at PL LIM (U0201-A4). At this point the signal will appear as a square wave version of the sub-audible signal which the radio received. The microprocessor (U0101-10) will decode the signal directly to determine if it is the tone/code which is currently active on that mode.

## 6.3 Audio Amplification Speaker (+) Speaker (-)

The output of the ASFIC's digital volume pot, U0201-J4 is routed through a voltage divider formed by R0401 and R0402 to set the correct input level to the audio PA (U0401). This is necessary because the gain of the audio PA is 46 dB, and the ASFIC output is capable of overdriving the PA unless the maximum volume is limited.

The audio then passes through C0401 which provides AC coupling and low frequency roll-off. C0402 provides high frequency roll-off as the audio signal is routed to pins 1 and 9 of the audio power amplifier U0401.

The audio power amplifier has one inverted and one non-inverted output that produces the differential audio output SPK+ / SPK- (U0401-4/6). The inputs for each of these amplifiers are pins 1 and 9 respectively; these inputs are both tied to the received audio. The audio PA's DC biases are not activated until the audio PA is enabled at pin 8.

The audio PA is enabled via AUDIO PA ENABLE signal from the ASFIC (U0201-B5). When the base of Q0401 is low, the transistor is off and U0401-8 is high, using pull up resistor R0406, and the Audio PA is ON. The voltage at U0401-8 must be above 8.5VDC to properly enable the device. If the voltage is between 3.3 and 6.4V, the device will be active but has its input (U0401-1/9) off. This is a mute condition which is not employed in this radio design. R0404 ensures that the base of Q0401 is high on power up. Otherwise there may be an audio pop due to R0406 pulling U0401-8 high before the software can switch on Q0401.

The SPK+ and SPK- outputs of the audio PA have a DC bias which varies proportionately with FLT A+ (U0401-7). FLT A+ of 11V yields a DC offset of 5V, and FLT A+ of 17V yields a DC offset of 8.5V. If either of these lines is shorted to ground, it is possible that the audio PA will be damaged. SPK+ and SPK- are routed to the accessory connector (J400-16 and 1) and to the control head (connector J0101-1 and 2).

#### 6.4 Handset Audio

Certain hand held accessories have a speaker within them which require a different voltage level than that provided by U0401. For those devices HANDSET AUDIO is available at J0101-14.

The received audio from the output of the ASFIC's digital volume attenuator is also routed to U0202-4 pin 9 where it is amplified 15 dB; this is set by the 10k/68k combination of R0233 and R0232. This signal is routed from the output of the op amp U202-4 pin 8 to J0101-14. The control head sends this signal directly out to the microphone jack. The maximum value of this output is 6.6Vp-p.

#### 6.5 Filtered Audio

The ASFIC has an audio whose output at U0201-B2 has been filtered and de-emphasized, but has not gone through the digital volume attenuator. From ASFIC U0201-B2 the signal is AC coupled to U0202-2 by capacitor C0230. R0224 and R0225 determine the gain of op-amp U0202-2. The output of U0202-2 is the routed to J0400-11. Note that any volume adjustment of the signal on this path must be done by the accessory.

#### 6.6 RX Secure Audio (optional)

Discriminator audio, which is now encrypted audio, enters the Secure board at connector J0103-5. On the Secure board, the encrypted signal is converted back to normal audio format, and then fed back through (J0103-2) to RX IN of the ASFIC (U0201-H6). From then on it follows a path identical to conventional receive audio, where it is filtered (0.3 - 3kHz) and de-emphasized. The signal UNAT RX OUT from the ASFIC (U0201-H5), also routed to option connector J0103-4, is not used for the Secure board but for other option boards.

## 7.0 Receive Signalling Circuits

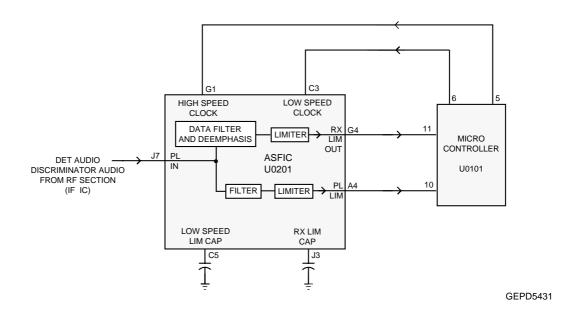

Refer to Figure 3-4 for reference for the following sections.

Figure 3-4 Receive Signalling Path.

## 7.1 Sub-audible Data (PL/DPL) and High Speed Data Decoder

The ASFIC (U0201) is used to filter and limit all received data. The data enters the ASFIC at U0201-J7. Inside U0201 the data is filtered according to data type (HS or LS), then it is limited to a 0-5V digital level. The MDC and trunking high speed data appear at U0201-G4, where it connects to the  $\mu P$  U0101-11

The low speed limited data output (PL, DPL, and trunking LS) appears at U0201-A4, where it connects to the  $\mu P$  U0101-10. While receiving low speed data, the  $\mu P$  may output a sampling waveform, depending on the sampling technique, to U0201-C3 between 1 and 2 kHz.

The low speed data is read by the  $\mu P$  at twice the frequency of the sampling waveform; a latch configuration in the ASFIC stores one bit every clock cycle. The external capacitors C0226, C0225, and C0223 set the low frequency pole for a zero crossings detector in the limiters for PL and HS data. The hysteresis of these limiters is programmed based on the type of received data. Note that during HS data the  $\mu P$  may generate a sampling waveform seen at U0201-G1.

#### 7.2 Alert Tone Circuits

When the software determines that it needs to give the operator an audible feedback (for a good key press, or for a bad key press), or radio status (trunked system busy, phone call, circuit failures), it sends an alert tone to the speaker.

It does so by sending SPI BUS data to U0201 which sets up the audio path to the speaker for alert tones. The alert tone itself can be generated in one of two ways: internally by the ASFIC, or externally using the  $\mu P$  and the ASFIC.

#### **Receiver Front-End**

The allowable internal alert tones are 304, 608, 911, and 1823Hz. In this case a code contained within the SPI BUS load to the ASFIC sets up the path and determines the tone frequency, and at what volume level to generate the tone. (It does not have to be related to the voice volume setting).