Computer Exercise 1

ISRAEL INSTITUTE OF TECHNOLOGY - TECHNION ANDREW AND ERNA VITERBI FACULTY OF ELECTRICAL ENGINEERING

# Introduction to VLSI Computer Exercise 1

Circuit simulations - Custom Design

Last update: November 7, 2018

Submission in pairs only until 11/12/2018

If you have questions please contact Nicolás Wainstein - nicolasw@campus.technion.ac.il

# Contents

| 1                    | Introduction         1.1       Submission                                                                                                                                            | <b>3</b><br>3<br>3<br>4                                                                |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 2                    | Schematic of an XOR2         2.1 Create symbol         2.2 Create Test Circuit                                                                                                       | <b>5</b><br>7<br>8                                                                     |

| 3                    | Schematic Simulation         3.1       Plot the output                                                                                                                               | <b>8</b><br>10<br>11<br>12<br>12<br>13<br>14<br>14<br>14<br>15<br>15<br>15<br>16<br>16 |

| <b>4</b><br><b>5</b> | Layout         4.1       Placement         4.2       DRC         4.3       Routing         4.4       Layout vs Sechamtic (LVS)         Hierarchical Design         5.1       Routing | <b>17</b><br>19<br>19<br>20<br>21<br><b>21</b><br>22                                   |

|                      | 5.2       RC Extraction         5.3       Extracted Layout Simulation                                                                                                                | $\frac{22}{23}$                                                                        |

# 1 Introduction

This is the first of two design labs. The labs are intended to teach you the practicalities of chip design using industry-standard CAD tools from Cadence.

This lab teaches you the basics of how to use the computer-aided design (CAD) tool to design, simulate, and verify schematics and layout of logic gates. It also serves as a stand-along tutorial to quickly get up to speed with the Cadence tools. The first step is to draw a schematic indicating the connection of transistors to build cells such as NAND gates, NOR gates, and NOT gates.

These cells are simulated by applying digital inputs and checking that the outputs match expectation, while varying some parameters and working conditions. You will also estimate time delays and power dissipation. A symbol for the cell is also created. Then, you will draw a layout indicating how the transistors and wires are physically arranged on the chip. The layout is checked to ensure it satisfies the design rules and that the transistors match the schematic. Finally, you will perform a hierarchical design, both in the schematic level and in the layout level. The design will be simulated and characterized.

#### 1.1 Submission

You are intended to submit electronically (Moodle) a report that includes all the figures/simulations/questions that are asked under the title **Submission** (it may be convenient that you take a look at this subsection before you start to work). There's no need to extend in your answers, be **precise** and **concise**. Try to include waveforms (graphs) that clearly explain the issue, for example zoom-in to the relevant section.

Please, in the first page write down your names, IDs, your lab account and the amount of hours you invested in this work

#### 1.2 An Overview of VLSI CAD Tools

VLSI designers have a wide variety of CAD tools to choose from, each with their own strengths and weaknesses. The leading Electronic Design Automation (EDA) companies include Cadence and Synopsys. Exist some open-source CAD tools such as Electric.

There are two general strategies for chip design. Custom design involves specifying how every transistor is connected and physically arranged on the chip. Synthesized design involves describing the function of a digital chip in a hardware description language such as Verilog or VHDL, then using a computer-aided design tool to automatically generate a set of gates that perform this function, place the gates on the chip, and route the wires to connect the gates. The majority of commercial designs are synthesized today because synthesis takes less engineering time. However, custom design gives more insight into how chips are built and into what to do when things go wrong. Custom design also offers higher performance, lower power, and smaller chip size. The first lab emphasize the fundamentals of custom design, while the next two use logic synthesis and automatic placement to save time.

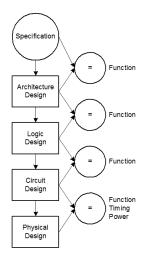

#### 1.3 Design Flow

Cells are commonly described at three levels of abstraction. The register-transfer level (<u>RTL</u>) description is a Verilog or VHDL file specifying the behaviour of the cell in terms of registers and combinational logic. It often serves as the specification of what the chip should do. The <u>schematic</u> illustrates how the cell is composed from transistors or other cells. The <u>layout</u> shows how the transistors or cells are physically arranged.

the outputs match expectation. Typically, logic verification is done first on the RTL to check that the specification is correct. A test-bench written in Verilog or VHDL automates the process of applying and checking all of the vectors. The same test vectors are then applied to the schematic to check that the schematic matches the RTL. Later, we will use a layout-versus schematic (LVS) tool to check that the layout matches the schematic (and, by inference, the RTL).

Figure 1: VLSI Design Flow

#### 1.4 Getting Started with Cadence Virtuoso

To initiate Cadence Virtuoso follow these steps:

- 1. Login to a lab machine (instructions posted separately)

- 2. In the console type:

- (a) cd cadence

- (b) source KIT.cshrc

- (c) cdsprj lab

- (d) virtuoso & (The ampersand isn't necessary but it makes the terminal window available for further use. Otherwise it is fully dedicated to the process and cannot be used or closed.)

- 3. The main window will open at the bottom of the screen. Select 'Tools  $\rightarrow$  Library Manager'. The library manager window will open.<sup>1</sup>

- 4. Create (don't use the existing one) a library by invoking  $File \rightarrow New \rightarrow Library...$  in the Library Manager. Name the library *lab1\_xxxx*, where xxxx is your group lab account. Click OK'.

- 5. In the window that opens, select 'Attach to an existing techfile', click 'OK' and then select ts018-prim as the Technology Library. Click 'OK' and you should see your new library appear in the library manager.

- 6. SUGGESTION: save your work periodically.

046237

<sup>&</sup>lt;sup>1</sup>Don't try to move libraries around or rename them directly in Linux; there is some unexpected behavior and you are likely to break them.

# 2 Schematic of an XOR2

In this part you will design and simulate an XOR2 gate in the schematic level. The first sections explain how to design your schematic and Section 3 will teach you how to simulate your circuit. We will work with TowerJazz 0.18  $\mu$ m process with  $\lambda = 90 \text{ nm}^2$ . Note: To ease the design, consider  $\bar{a}$  and  $\bar{b}$ , a and b complements, respectively, as different inputs. Remember to take this into account in your simulations. This means your gate will have 4 inputs.

Each gate or larger component is called a cell. Cells have multiple views, called '*cellviews*'. A *cellview* is an aspect of the cell, such as its schematic, its layout, its simulation model, etc. Common *cellviews* include:

- Schematic: A circuit schematic consisting of 'symbol' views of other cells.

- Layout: The physical layout of a particular schematic cellview, with objects in the layout typically linked to their schematic counterparts. Layout consists of various layers such as: polysilicon, M1, M2, Nwell,  $N^+$ ,  $P^+$ , etc.

- Symbol: A visual representation of the cell, which is used for inserting the cell into other schematics.

- Various Spectre/HSpice simulation models, usually only for discrete components like passives or transistors (we won't use this tool).

- Simulation states (see Section 3).

- Power and timing data.

For example, your library will, eventually, contain several cells (at least one XOR2 schematics and one for its layout).

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>D</u> esign Mana                                                  | ager <u>H</u> elp                                                                                                         |                             | cādence           |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|

| □ Show Categories □ Si<br><mark>Library</mark>                                                              | now Files                                                                                                                 | View                        |                   |

| ahdlLib                                                                                                     | nor_gate                                                                                                                  | symbol                      |                   |

| ahdiLib<br>analogLib<br>avTech<br>basic<br>cdsDefTechLib<br>cds_generic<br>connectLib<br>functional<br>lab1 | multiplexer<br>multiplier<br>n_jfet<br>natural_log<br>noise_src<br>nor_gate<br>not_gate<br>np_bjt<br>offset_meas<br>opamp | View A Lock symbol veriloga | Size<br>21k<br>2k |

| rfExamples<br>rfLib<br>sbaLib<br>sheetBorder<br>ts018_prim                                                  | open_ckt_fault<br>or_gate<br>p_controller<br>parallel_reg_8<br>pcm_demodulator<br>pcm_modulator<br>pd_controller          |                             |                   |

| Messages                                                                                                    | 16                                                                                                                        |                             |                   |

|                                                                                                             |                                                                                                                           | Lib: ahdlLib                | Free: 201.29G     |

Figure 2: Library Manager

<sup>&</sup>lt;sup>2</sup>Remember  $\lambda$  is half of the channel's width

In the library manager, select your library. Go to 'File  $\rightarrow New \rightarrow Cell View$ '. In the window that opens give the cellview the name xor2. Make sure that the View Name is set to 'schematic' and that the Library Name is set to your library. Click 'OK' and a new schematic window will open.

To add a component, e.g., an NMOS transistor, with the schematic window selected, go to 'Create  $\rightarrow$  Instance' on the menu bar (or click 'i' on the keyboard) and an 'Add Instance' window will open. Click 'Browse' and a window similar to the library manager will open. Navigate to the Tower library, 'ts018\_prim', find the 'nmos\_18' cell, click it and click the 'symbol' view. Then click inside the schematic window to place it. For now, disregard the values that got filled in the 'Add Instance' window. Press 'ESC' on the keyboard to stop placement.

| 😣 😐 Edit Object Pro              | perties                       |         |  |  |  |

|----------------------------------|-------------------------------|---------|--|--|--|

| Apply To only current instance 💌 |                               |         |  |  |  |

| Show 📃 system                    | 🛚 🗹 user 🗹 CDF                |         |  |  |  |

| Browse                           | Reset Instance Labels Display |         |  |  |  |

| Property                         | Value                         | Display |  |  |  |

| Library Name                     | ts018_prim                    | off 🔽   |  |  |  |

| Cell Name                        | nmos_18                       | value 🔽 |  |  |  |

| View Name                        | symbol                        | off     |  |  |  |

| Instance Name                    | M1                            | off 🔽   |  |  |  |

| (                                | Add Delete Modify             |         |  |  |  |

| CDF Parameter                    | Value                         | Display |  |  |  |

| Model name                       | n18                           | off 🔽   |  |  |  |

| Total Gate Width                 | 0,27                          | off 🔽   |  |  |  |

| Finger Width                     | 0,27                          | off 🔽   |  |  |  |

| Gate Length (1)                  | 0,18                          | off 🔽   |  |  |  |

| Fingers                          | 1                             | off 🔽   |  |  |  |

| Number of fingers (nf)           | 1                             | off 🔽   |  |  |  |

| Apply Threshold                  |                               | off 🔽   |  |  |  |

| Multiplier                       | 1                             | off 🔽   |  |  |  |

| Connect gates                    | 🖲 No 🔾 Top 🔾 Bottom 🔾 Both    | off 🔽   |  |  |  |

| Drain Contact Coverage           | 100                           | off 🔽   |  |  |  |

| Source Contact Coverage          | 100                           | off 🔽   |  |  |  |

| Switch S/D                       | 🖲 No 🔾 Yes                    | off 🔽   |  |  |  |

| Show External Tap Prope          | 🖲 No 🔾 Yes                    | off 🔽   |  |  |  |

|                                  |                               |         |  |  |  |

Figure 3: Edit properties

Click on the NMOS and type 'q'. This will open the properties window (Fig. 3). Note 'Finger Width', 'Gate Length' and 'Fingers'. Width and length should be obvious. 'Fingers' refers to the practice of using multiple parallel transistors instead of a single wide one. Let's make  $W_N$  and  $W_P$  (NMOS and PMOS width respectively) parametric. For NMOS, in Finger Width write pPar("WN") and for PMOS pPar("WP"). This will allow us to change parameters in higher hierarchies of the design. Leave the length at its default (and smallest)  $0.18\mu$ m value. Click 'OK'. Remember - everything in Linux is case sensitive, so note how you wrote everything. Note that sizes are in microns, rather than meters or  $\lambda$  units.

Place all the transistors needed for an static CMOS XOR2 gate (components can be copied by pressing 'c', clicking, dragging and clicking; for moving components, simply drag them) and connect them using wires by going to 'Create  $\rightarrow$  Wire' or clicking 'w' in the keyboard. Note that components

can also be connected by placing their red box terminals together. Then, place  $V_{DD}$  and ground, they are both in the *analogLib* library ('vdd' and 'gnd' respectively). You can use 'Ctrl+r' to rotate the instances. Take care in connecting the bulk of each transistor to either gnd or vdd.

Next, create input and output pins (name them, e.g., a and b for inputs and y for output), go to 'Create  $\rightarrow Pin$ ' or click 'p', and then connect them with wires to the gates or output node. Make sure the direction is properly set for inputs and outputs. Save and check your schematic, choose 'File  $\rightarrow Check$  and Save' or press 'Shift+x'.<sup>3</sup>

You can zoom in and out with the scroll-wheel and fit the whole schematic by pressing 'f' in the keyboard. Also you can zoom in to a desired place by selecting the area with the right click pressed.

#### Submit:

1. Print screen of the XOR2 schematic and test circuit (FO1).

#### 2.1 Create symbol

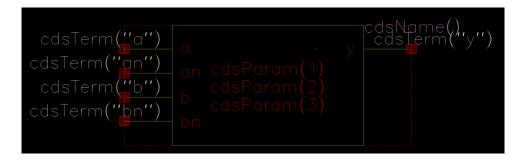

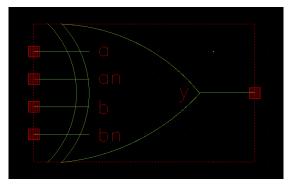

Each schematic can have a corresponding symbol to represent the cell in a higher-level schematic. You will need to create a symbol for your XOR2 gate. When creating your symbol, it is a good idea to keep everything aligned to the grid, this will make connecting symbols simpler and cleaner when you need it for another cell. While looking at your XOR2 schematic, choose  $Create \rightarrow Cellview \rightarrow$ *From Cellview....* In the window that opens, make sure Cell name is *xor2*, '*From View Name*' is *schematic*, and '*To View Name*' is *symbol*, and click *OK*. Cadence will create a generic symbol based on your pin names. Check that everything is as expected in the Symbol Generation Options window which opens up, and click *OK*. The Symbol L Editing window that opens up may look like Fig. 4.

Figure 4: Symbol

A schematic is easier to read when familiar symbols are used instead of generic boxes. Modify the symbol to look like a standard XOR2. Pay attention to the dimensions of the symbol; the overall design will look more readable if symbols are of consistent sizes. Experiment with the arc drawing tool. Finally, choose  $Create \rightarrow Selection Box...$  and choose 'Automatic'. This creates a red box around the symbol that will define where to click to select the symbol when it appears in another schematic. Our art work is shown in Fig. 5.

<sup>&</sup>lt;sup>3</sup>If you see an error message in the parameter display of the transistors, do not worry, it is just because the tool does not know how to calculate W (yet).

Figure 5: XOR2 Symbol example

#### 2.2 Create Test Circuit

Now let's create a test circuit to simulate the XOR2. Create a new schematic and name it test\_xor2. Place the XOR2 symbol you created in the last step (it should be on your library lab1\_xxxx; use 'i' or  $Create \rightarrow instance$ ), and change its properties (click on it and type 'q'). They should appear as 'Wn' and 'Wp'). Select 'Wn' to be minimum (the technology spec says the minimum width is 0.22  $\mu$ m) and 'Wp' to be 'r\*0.22'. With this last definition we will define the width of the PMOS as a multiple (r) of the minimum width of 0.22  $\mu$ m. At the output of this XOR2 gate connect one of the inputs of a second same gate as a load. This results in Fan Out of 1 (FO1).

Add <u>four</u> voltage sources (use *vpulse* from *analogLib*) to control the inputs of the first XOR2 gate. Think of how you could generate the 4 input possibilities. **Remember that there are two complementary pairs.** All possibilities should occur in one 20  $ns^4$  lapse. Set properties of the voltage sources (by pressing 'q') as follows: voltages 1 and 2 to be 0 V and 1.8 V, respectively, or *vice versa*. Rise and fall times to be 100 *ps*. Play with period, pulse width and delay to generate the input sequence. You may also use other types of voltage sources.

Now add a voltage source as the main power supply (vdc in analogLib) and set the voltage to 1.8 V. Connect the ground and connect a small floating wire to the positive voltage node ('PLUS'). Go to  $Create \rightarrow Wire Name...$  (or press 'L'), name it vdd! (including the exclamation mark, meaning that this is a constant global net rather than a parameter) and select the wire. This action will match vddterminal in our XOR2 with this voltage source. Complete the schematic by selecting a proper voltage for the undriven inputs.

### Submit:

- 2. Explain how you implemented the input sources and include the output waveform that shows the 4 cases.

- 3. What's the worst case scenario you should simulate for  $t_{prd}$  and  $t_{pfd}$  (propagation fall and rise delay respectively)?

# **3** Schematic Simulation

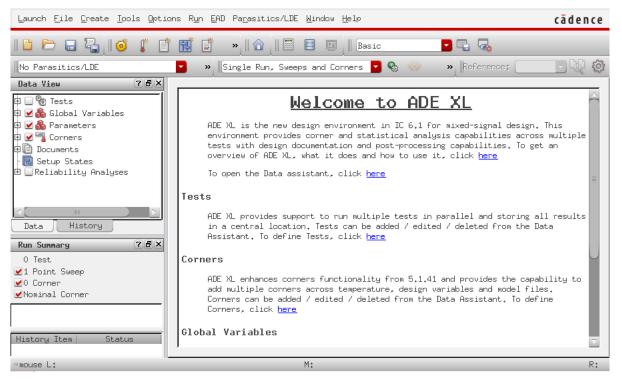

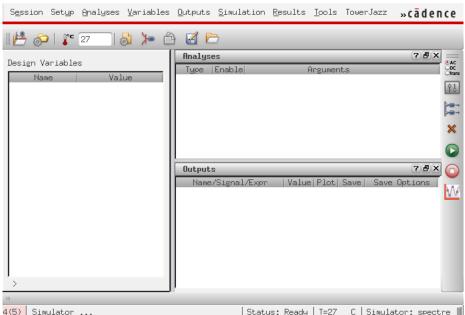

In this section you will simulate the XOR2 schematic. In the *test\_xor2* Schematic Cellview go to  $Launch \rightarrow ADE \ GXL$  and select *Create New View*. This will open the Virtuoso Analog Design Environment window (from now on, *'simulation window'*). A window like Fig. 6 will pop-up. In this window you will manage design variables and parameters, select simulations that will run and

<sup>&</sup>lt;sup>4</sup>The tool understands  $\mathbf{m}$  as mili,  $\mathbf{u}$  as micro,  $\mathbf{n}$  as nano,  $\mathbf{p}$  as pico, etc.

setup outputs to be plotted automatically. When properly set up this is a very powerful tool and this exercise will try to show you how to automate things as much as possible.

The left side shows the useful Data View bar. To create a new test, expand the 'Tests' item and select '*Click to add test*'. A new window will open (Fig. 7) and a small pop-up window will ask you to select the *cellview* you want to simulate. Choose the *test\_xor2* schematic.

Figure 6: ADE XL Main Window

A brief description of the window in Fig. 7:

- Left side: Design Variables lists all defined parameters and variables. This is now empty but we can quickly import them from the schematic.

- Upper right sub-window: Analyses lists the defined simulations, some of their parameters and whether they are active or not.

- Lower right sub-window: Outputs shows the outputs you define for automatic calculation. These can display values, like DC bias points and results of formulas. It can also list output plots that are automatically plotted after each simulation run.

Status: Ready | T=27 C | Simulator: spectre |

Figure 7: ADE XL Test Editor

Let's go ahead and save the simulation state now, even though it's currently empty. Go to Session  $\rightarrow$  Save State... Under Save State Option select Cellview. This will save this simulation state and all its settings and results as another cellview in your cell. You may change the name in 'State' to something meaningful, like 'trise' or 'tfall' which is what we'll first do in the exercise itself. Click 'OK' to save. From now on, it will appear in the library manager as a cellview, and you may even open it without going through the schematic. Make sure to save your simulation state regularly and you won't have to redefine variables and outputs from session to session.

On the right there's a column of buttons. Click the topmost, 'Choose Analyses'. The Analyses window opens. It shows all possible simulations you can run. Let's start with a transient ('tran') simulation. Select it, set 'Stop Time' to 20 ns and make sure to check the 'Enabled' button at the bottom. It's here that you can later turn it off, although this is a fast simulation that doesn't take much time. Click 'OK' and you will see it appear in the Analyses List.

Click on the second button from the top, 'Edit Variables'. In the window that opens click 'Copy From' near 'Cellview Variables' and watch all the parametric values you wrote in the schematic magically appear in the list (in our case, only r appears). Choose 1 for now (we will perform a Parametric Sweep later). After writing each value click 'Change' to save it, or it won't be saved!

Go back to the ADE GXL window. The new test should appear beneath the *Tests* tag on the Data View bar. To run the simulation go to  $Run \rightarrow Single Run, Sweeps and Corners...$  or click the Green-Play button. If you have errors at this point, carefully repeat this part to make sure you got all the setup right, and if there are still any errors seek help from the course or lab staff. Remember to save your state periodically.

#### 3.1Plot the output

After the simulation finishes successfully, we need to define an output to display the curve. There are different ways to do this. We'll explore two.

In both cases below, we explain selecting the output node of the first XOR2 gate. To compute propagation delay, you will also need to add waveforms of the two inputs of that gate.

#### 3.1.1 Using the calculator

Click the 'Setup Outputs' button (third from the top) in the simulation window. Name the output 'out'. Click 'Open' next to 'Calculator'. This is the very powerful and very complicated calculator tool. Fig. 8 shows its window. The second bar from the top allows you to select different types of signals (e.g. vt and it for transient voltage and current respectively, etc.). Select 'vt'. The schematic window pops up so that you can select the voltage signal of your preference. Select the output of the first XOR2 gate. You are taken back to the calculator window and it should show VT("/netX") (or another net name) in the buffer.

Go to  $Tools \rightarrow Plot$  to plot the *buffered* signal (alternatively, click the calculator-wave symbol in the third bar from the top). You should immediately see the voltage waveform. Observe that you can change where the other signals are plotted by changing the option next to the calculator-wave symbol in the calculator window (options include 'New subwindow', 'Append' and 'New window').

The calculator allow us to perform different calculations with the results. It is extremely helpful in more complicated simulations. **Hint:** Explore functions *delay*, *riseTime*, *fallTime*, they can be useful in the following simulations. Using function *delay* you can define  $t_{pdr}$ ,  $t_{pdf}$ , and then  $t_d = \frac{t_{pdr} + t_{pdf}}{2}$ .

| Eile Iools View Options Constants Help C                                                                                       | ādence                   |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| In Context Results DB:                                                                                                         | • 🖻                      |

|                                                                                                                                |                          |

| 📗 Off 🔾 Family 🔾 Wave   🗹 Clip   🍌 🐗 New Subwindow 🔽 Rectangular 🔽 🥸   📑                                                       |                          |

| Ke     Ø×       7     8       7     8       4     5       1     2       0     ±       +     →       1     1                    |                          |

| Stack                                                                                                                          | đ×                       |

|                                                                                                                                |                          |

|                                                                                                                                |                          |

|                                                                                                                                |                          |

|                                                                                                                                |                          |

|                                                                                                                                |                          |

| Function Panel                                                                                                                 | 5×                       |

|                                                                                                                                |                          |

|                                                                                                                                |                          |

| 10**x acos average compressionVRI d2a dft exp freq gainBwProd gp ha                                                            | umx<br>armonic           |

| Rn asin bandwidth convolve dB20 dnl eyeDiagram frequency getAsciiWave gpc_gain h:                                              | armonicFre<br>istogram2D |

| a2d asinh clip cos dBm dutyCycle fallTime ga gmax groupDelay if<br>abs atan compare cosh delay evmQAM flip gac_freq gmin gt if |                          |

|                                                                                                                                | ×                        |

| Function Panel Expression Editor                                                                                               |                          |

| status area                                                                                                                    |                          |

| 17                                                                                                                             |                          |

Figure 8: ADE XL Calculator

#### 3.1.2 Using the Output Editor

In this case, instead of opening the calculator, in the ADEXL window, either go to  $Outputs \rightarrow Setup...$  or click the Setup Output buttons (3rd from above on the right bar). Name the output as you wish, click the button '*From schematic*'. The schematic pops up. Select the signal of your preference. By selecting wires in the schematic, voltages will be plotted; by selecting pins, currents will be plotted. Observe the '*Type*' field of each output to make sure it's what you intend.

#### 3.2 Parametric sweep

Now that we've experimented with the simulations, let's perform a parametric sweep. This powerful tool allows us to observe how the signals change by changing one or more parameters. In our case we observe the effect of PMOS width on propagation delay. You are required to simulate the worst case scenario from the logic point of view. For this part you may use DC (constant) voltage sources for some inputs and reduce the simulation time.

In the Data View bar of ADEXL, expand the 'Global Variable' tag. Your design variables should appear. Next to the variable name, click in the value field. A button with ... will appear. Click it, and in the new window (where the initial value 1 is shown) write your desired list of values such as  $\{1, 1.5, 2, 2.5, 3, 3.5, 4\}$  and click 'OK'. Run the simulation as above (e.g., use the green Play button).

The plots are observable in the ADEXL window, Results tab. Click the chart button to see the waveforms. Zoom in (right click and drag) to one of the transitions. Observe how  $t_{pdf}$  and  $t_{pdr}$  (propagation fall delay and propagation rise delay respectively)<sup>5</sup> are affected by r, namely by PMOS width. Add horizontal and vertical markers to help you find the relevant points by pressing 'h' and 'v' respectively on the 'Visualization & Analysis' window. Double clicking a marker helps select exact level. Select 50% levels and read out times. Another method is to use the *delay* function as mentioned before.

Look for the r value that yields a symmetric gate, namely where  $t_{pdf}$  and  $t_{pdr}$  are roughly equal and for the r value that yields to minimum delay. You will need to use those r values in subsequent sections.

#### Submit:

- 4. Simulation waveforms of the parametric sweep of r (submit at least 3 cases).

- 5. Make a table showing  $t_{pdf}$  and  $t_{pdr}$  for every r.

- 6. Based on the simulations, what is  $W_{P_{opt}}$  ( $W_P$  that results in an optimal/minimum delay)?

- 7. Based on the simulations, what is  $W_{P_{sym}}$  ( $W_P$  that results in a symmetric gate *i.e.*, equal  $t_{pdf}$  and  $t_{pdr}$ )?

- 8. How are  $t_{pdf}$  and  $t_{pdr}$  changed/influenced by the input-order-of-arrival *i.e.*, when the inputs do not arrive simultaneously?

- 9. Calculate, theoretically and using the technology parameters,<sup>6</sup>  $W_{P_{opt}}$  for minimum propagation delay.

#### 3.3 Corner simulations

You will now perform simulations to observe how environmental changes affect circuit performance. The desired environmental corners for the 0.18  $\mu m$  process are summarized in Table 1.

| Corner | Voltage | Temperature |

|--------|---------|-------------|

| F      | 1.98    | 0 °C        |

| Т      | 1.8     | 70 °C       |

| S      | 1.62    | 125 °C      |

| 5 | 1.02 | 125 C |

|---|------|-------|

|   |      |       |

|   |      |       |

Table 1: Environmental Corners

<sup>&</sup>lt;sup>5</sup>Remember: propagation delay accounts for maximum time from the input crossing 50% to the output crossing 50% <sup>6</sup>You may use:  $\mu_n = 291 \text{ cm}^2/Vs$ ,  $\mu_p = 71 \text{ cm}^2/Vs$ ,  $V_{tn} = 0.5 V$ ,  $V_{tp} = -0.42 V$ ,  $t_{ox} = 50$ Å,  $\varepsilon_{ox} = 3.85$ ,  $C_{ja} = 1.1 \times 10^{-3} pF/\mu m^2$

We create a new test to study corners. We will vary only supply voltage and temperature, but leave transistor models in the 'typical' mode (if needed, designers can try slow and fast transistors as well, to investigate On Chip Variation, OCV). Under the Tests item on the Data View bar in ADEXL, select Click to add test, select same  $test\_xor2$  schematic, Copy from Cellview and choose the symmetric r value found above.

In the schematic window, go to  $Window \rightarrow Assistants \rightarrow Variables and Parameters^7$ . The Variables and Parameters bar should be open on the left. Select the voltage source vdd and select the 'Parameter' tab in the aforementioned bar. On the filter menu select 'CDF Parameters'. A list with all the vdc parameters appears. Right click on 'DC voltage' and select 'Create Parameter'. Go back to the ADE XL window and observe that this parameter appears under 'Parameters' tag.

Now we will create a new corner. In 'Data View' expand 'Corners' tag and click to add a new corner. A window like Fig 9 will open. First we will import the *model files*. Click on '*Click to add*' below the 'Model Files' title. In the window that pops up click the button '*Import from Tests*', a list of models will appear in the window and press OK.

| Corners            | 🗹 Nominal | <b>V</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CO                   |

|--------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Temperature        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 125                  |

| Design Variables   |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 120                  |

| Click to add       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| Parameters         |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| /schematic/V2/vdc  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.6                  |

| Click to add       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| Model Files        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| global.scs         |           | <ul> <li>Image: A set of the set of the</li></ul> | BSIM                 |

| global_5V.scs      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | section>             |

| fet.scs            |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NOM                  |

| fethv.scs          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | section>             |

| nat.scs            |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | section>             |

| bjt.scs            |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | section>             |

| accap.scs          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | section>             |

| mimcap.scs         |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | section><br>section> |

| mfc.scs<br>res.scs |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | section><br>section> |

| diode.scs          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | section>             |

| Click to add       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | section>             |

| Model Group(s)     |           | <modelg< td=""><td>roun&gt;</td></modelg<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | roun>                |

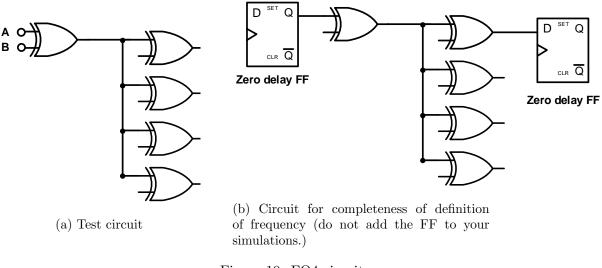

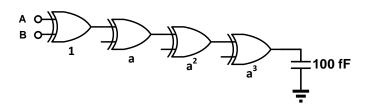

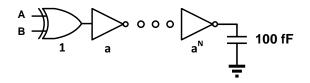

| Click to add       |           | sinoaoig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | roupe                |