# Model Sim.

# SE/EE

Tutorial

Version 5.4

The world's most popular HDL simulator

Model *Sim* /VHDL, Model *Sim* /VLOG, Model *Sim* /LNL, and Model *Sim* /PLUS are produced by Model Technology Incorporated. Unauthorized copying, duplication, or other reproduction is prohibited without the written consent of Model Technology.

The information in this manual is subject to change without notice and does not represent a commitment on the part of Model Technology. The program described in this manual is furnished under a license agreement and may not be used or copied except in accordance with the terms of the agreement. The online documentation provided with this product may be printed by the end-user. The number or copies that may be printed is limited to the number of licenses purchased.

Model *Sim* is a registered trademark of Model Technology Incorporated. PostScript is a registered trademark of Adobe Systems Incorporated. UNIX is a registered trademark of AT&T in the USA and other countries. FLEXIm is a trademark of Globetrotter Software, Inc. IBM, AT, and PC are registered trademarks, AIX and RISC System/6000 are trademarks of International Business Machines Corporation. Windows, Microsoft, and MS-DOS are registered trademarks of Microsoft Corporation. OSF/Motif is a trademark of the Open Software Foundation, Inc. in the USA and other countries. SPARC is a registered trademark and SPARCstation is a trademark of SPARC International, Inc. Sun Microsystems is a registered trademark, and Sun, SunOS and OpenWindows are trademarks of Sun Microsystems, Inc. All other trademarks and registered trademarks are the properties of their respective holders.

Copyright (c) 1990 - 2000, Model Technology Incorporated. All rights reserved. Confidential. Online documentation may be printed by licensed customers of Model Technology Incorporated for internal business purposes only.

Published: March 2000

Model Technology Incorporated 10450 SW Nimbus Avenue / Bldg. R-B Portland OR 97223-4347 USA

phone: 503-641-1340 fax: 503-526-5410 e-mail: <u>support@model.com</u>, <u>sales@model.com</u> home page: <u>http://www.model.com</u>

#### SE/EE Tutorial - Part # M16540

# **Table of Contents**

| Introduction                                    |

|-------------------------------------------------|

| Before you begin                                |

| Lesson 1 - Creating a Project                   |

| Lesson 2 - Basic VHDL simulation                |

| Lesson 3 - Debugging a VHDL design              |

| Lesson 4 - Running a batch-mode simulation      |

| Lesson 5 - Executing commands at startup        |

| Lesson 6 - Tcl/Tk and ModelSim6-47              |

| Lesson 7 - Basic Verilog simulation             |

| Lesson 8 - Mixed VHDL/Verilog simulation        |

| Lesson 9 - Simulating with Performance Analyzer |

| Lesson 10 - Simulating with Code Coverage       |

| Lesson 11 - Finding names and values            |

| Lesson 12 - Using the Wave window               |

| Technical Support, Updates, and Licensing       |

| Software License Agreement 135                  |

| Index                                           |

# Introduction

# Chapter contents

| Software version | ns.    |       | •    |      |    | • | • | • | • |  | • | • |  | 6 |

|------------------|--------|-------|------|------|----|---|---|---|---|--|---|---|--|---|

| ModelSim's gra   | phic i | inter | face | e.   |    |   | • |   |   |  |   |   |  | 6 |

| Standards suppo  | rted   |       |      |      |    |   | • |   |   |  |   |   |  | 6 |

| Assumptions .    | •      |       | •    |      |    | • | • | • | • |  |   |   |  | 7 |

| Where to find ou | ır doo | cum   | enta | tion | ι. |   |   |   |   |  |   |   |  | 8 |

### Software versions

This documentation was written to support ModelSim SE/EE 5.4 for UNIX, Microsoft Windows NT 4.0, and Windows 95/98/2000. If the Model*Sim* software you are using is a later release, check the README file that accompanied the software. Any supplemental information will be there.

Although this document covers both VHDL and Verilog simulation, you will find it a useful reference even if your design work is limited to a single HDL.

# ModelSim's graphic interface

While your operating system interface provides the window-management frame, Model*Sim* controls all internal-window features including menus, buttons, and scroll bars. The resulting simulator interface remains consistent within these operating systems:

- SPARCstation with OpenWindows, OSF/Motif, or CDE

- IBM RISC System/6000 with OSF/Motif

- Hewlett-Packard HP 9000 Series 700 with HP VUE, OSF/Motif, or CDE

- Linux (Red Hat v. 6.0 or later) with KDE or GNOME

- Microsoft Windows NT and Windows 95/98/2000

Because Model*Sim*'s graphic interface is based on Tcl/TK, you also have the tools to build your own simulation environment. Easily accessible preference variables and configuration commands simulator preference variables, and graphic interface commands give you control over the use and placement of windows, menus, menu options and buttons.

# **Standards supported**

Model*Sim* VHDL supports the IEEE 1076-1987, 1076-1993 VHDL, 1164-1993 *Standard Multivalue Logic System for VHDL Interoperability* and the 1076.2-1996 *Standard VHDL Mathematical Packages* standards. Any design developed with Model*Sim* will be compatible with any other VHDL system that is compliant with either IEEE Standard 1076-1987 or 1076-1993.

ModelSim Verilog is based on the IEEE Std 1364-1995 Standard Hardware Description Language Based on the Verilog Hardware Description Language. (ModelSim 5.2e does not currently support VPI routines for PLI 2.0.) The Open Verilog International Verilog LRM version 2.0 is also applicable to a large extent. Both PLI (Programming Language Interface) and VCD (Value Change Dump) are supported for ModelSim PE and EE users. In addition, all products support SDF 1.0 through 3.0, VITAL 2.2b, and VITAL'95 - IEEE 1076.4-1995.

### Assumptions

We assume that you are familiar with the use of your operating system. You should be familiar with the window management functions of your graphic interface: either OpenWindows, OSF/Motif, or Microsoft Windows NT/95/98/2000.

We also assume that you have a working knowledge of VHDL and Verilog. Although Model*Sim* is an excellent tool to use while learning HDL concepts and practices, this document is not written to support that goal.

### Comments

Comments and questions about this manual and Model*Sim* software are welcome. Call, write, or fax or email:

Model Technology Incorporated 10450 SW Nimbus Avenue, Bldg. R-B Portland, OR 97223-4347 USA

phone: 503-641-1340 fax: 503-526-5410 email: <u>manuals@model.com</u> home page: <u>http://www.model.com</u>

# Where to find our documentation

Model*Sim* documentation is available from our web site at <u>model.com/resources/</u><u>index.html</u> or in the following formats and locations:

| Document                                              | Format     | How to get it                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Start Here for ModelSim                               | paper      | shipped with ModelSim                                                                                                                                                                                                                                                                                   |

| <i>SE/EE</i><br>(installation & support<br>reference) | PDF online | from the Model <i>Sim</i> <b>Help</b> menu (select <b>SE/EE</b><br><b>Documentation</b> > <b>Licensing and Support</b> ), or find<br><i>se_start.pdf</i> in the \ <i>modeltech</i> \ <i>docs</i> directory; also<br>available from the Support page of our web site:<br><u>www.model.com</u>            |

| ModelSim SE/EEQuick Guide                             | paper      | shipped with ModelSim                                                                                                                                                                                                                                                                                   |

| (command and feature quick-<br>reference)             | PDF online | from the Model <i>Sim</i> <b>Help</b> menu (select <b>SE/EE</b><br><b>Documentation</b> > <b>SE/EEQuick Guide</b> ), or find<br><i>se_guide.pdf</i> in the \ <i>modeltech</i> \ <i>docs</i> directory; also<br>available from the Support page of our web site:_<br><u>www.model.com</u>                |

| ModelSim SE/EE Tutorial                               | PDF online | from the Model <i>Sim</i> <b>Help</b> menu in the <b>SE/EE</b><br><b>Documentation</b> group, or find <i>se_tutor.pdf</i> in the /<br><i>modeltech/docs</i> directory on the CD-ROM, or hard drive<br>after installation, also available from the Support page of<br>our web site: <u>www.model.com</u> |

| ModelSim SE/EEUser's<br>Manual                        | PDF online | from the Model <i>Sim</i> <b>Help</b> menu in the <b>SE/EE</b><br><b>Documentation</b> group, or find <i>se_man.pdf</i> in the /<br><i>modeltech/docs</i> directory on the CD-ROM, or hard drive<br>after installation                                                                                  |

| <i>ModelSim</i> SE/EECommand<br><i>Reference</i>      | PDF online | from the Model <i>Sim</i> <b>Help</b> menu in the <b>SE/EE</b><br><b>Documentation</b> group, or find <i>se_cmds.pdf</i> in the /<br><i>modeltech/docs</i> directory on the CD-ROM, or hard drive<br>after installation                                                                                 |

| Tcl man pages (Tcl manual)                            | HTML       | use the Main window menu selection: <b>Help &gt; Tcl Man</b><br><b>Pages</b> , or find <i>contents.html</i> in \modeltech\docs\html                                                                                                                                                                     |

| tech notes                                            | ASCII      | from the Model <i>Sim</i> Help menu, or located in the<br>\modeltech\docs\technotes directory after installation                                                                                                                                                                                        |

# Before you begin

Preparation for some of the lessons leaves certain details up to you. You will decide the best way to create directories, copy files and execute programs within your operating system. (When you are operating the simulator within Model*Sim*'s GUI, the interface is consistent for all platforms.)

Additional details for VHDL, Verilog, and mixed VHDL/Verilog simulation can be found in the *ModelSim User's Manual* and *Command Reference*. (See "Where to find our documentation" (8).)

Examples show Windows path separators - use separators appropriate for your operating system when trying the examples.

#### Command, button, and menu equivalents

Many of the lesson steps are accomplished by a button or menu selection. When appropriate, VSIM command line (PROMPT:) or menu (MENU:) equivalents for these selections are shown in parentheses within the step. This example shows three options to the **run -all** command, a button, prompt command, and a menu selection.

(PROMPT: run -all) (MENU: Run > Run -All)

#### Drag and drop

Drag and drop allows you to copy and move signals among windows. If drag and drop applies to a lesson step, it is noted in a fashion similar to MENUS and PROMPTS with: DRAG&DROP.

#### **Command history**

As you work on the lessons, keep an eye on the Main transcript window. The commands invoked by buttons and menu selections are echoed there. You can scroll through the command history with the up and down arrow keys, or the command history may be reviewed with several shortcuts at the Model*Sim*/VSIM prompt.

| Shortcut        | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| click on prompt | left-click once on a previous ModelSim or VSIM prompt in<br>the transcript to copy the command typed at that prompt to<br>the active cursor |

| his or history  | shows the last few commands (up to 50 are kept)                                                                                             |

#### **Reusing commands from the Main transcript**

ModelSim's Main transcript may be saved, and the resulting file used as a DO (macro) file to replay the transcribed commands. You can save the transcript at any time before or during simulation. You have the option of clearing the transcript (File > Clear Transcript) if you don't want to save the entire command history.

To save the contents of the transcript select **File > Save Main As** from the Main menu.

Replay the saved transcript with the **do** command:

do <do file name>

For example, if you saved a series of compiler commands as *mycompile.do* (the .do extension is optional), you could recompile with one command:

do mycompile.do

**Note:** Neither the prompt nor the Return that ends a command line are shown in the examples.

# Lesson 1 - Creating a Project

# The goals for this lesson are:

- Explore the Welcome to ModelSim dialog box features

- Create a project (.mpf file)

# The Welcome to ModelSim dialog box

Upon opening Model*Sim* for the first time, you will see a Welcome to Model*Sim* dialog box. (If this screen is not available, you can enable it by selecting **Help > Enable Welcome** from the Main window. It will then display the next time you start ModelSim.)

| Welcome to Mod   | lelSim                                                |            |

|------------------|-------------------------------------------------------|------------|

| Quick Start      | New users start here (5 Minutes)                      |            |

| Licensing        | Run ModelSim licensing diagnostics                    |            |

| Create a Project | Wizard for creating a new project                     | H CONTRACT |

| Open Project     | E:/MTI53alpha4/win32//examples/projects/mixer         | Tool EUR   |

| Done             | Continue to ModelSim                                  |            |

| C Alwa           | ays open last project (do not show this dialog again) |            |

| Alwa             | ays show this dialog                                  |            |

|                  |                                                       |            |

From this dialog box, you can:

- View the Quick Start menus, which contain answers to commonly asked questions.

- Run ModelSim licensing diagnostics.

- Use the project creation wizard to create a new project from scratch or to copy an existing project.

- Open an existing project.

- Click Done to continue to the ModelSim Main window.

### **Creating a Project**

A project is a collection entity for an HDL design under specification or test. At a minimum, it has a root directory, a work library, and a session state that is stored in a .mpf file located in the project's root directory. A project may also consist of:

- HDL source files

- subdirectories

- Local libraries

- References to global libraries

For more information about using project files, see the ModelSim User's Manual.

Note: Beginning with the 5.3 release, ModelSim incorporates the file extension .mpf to denote project files. In past releases the modelsim.ini file (the system initialization file) was used as the project file.

**1** Start Model*Sim* with one of the following:

for UNIX at the shell prompt:

vsim

for Windows - your option - from a Windows shortcut icon, from the Start menu, or from a DOS prompt:

modelsim.exe

| Welcome to Mod            | lelSim                                                |   |         |

|---------------------------|-------------------------------------------------------|---|---------|

| Quick Start               | New users start here (5 Minutes)                      |   |         |

| Licensing                 | Run ModelSim licensing diagnostics                    |   |         |

| Create a Project          | Wizard for creating a new project                     |   |         |

| Open Project              | E:/Tutorials/PE_Tutorial                              | Ŧ | The EUR |

| Done                      | Continue to ModelSim                                  |   |         |

| C Alwa                    | ays open last project (do not show this dialog again) |   |         |

| <ul> <li>Alway</li> </ul> | ays show this dialog                                  |   |         |

|                           |                                                       |   |         |

2 Select the **Create a Project** button from the Welcome to ModelSim dialog box.

Note: If the Welcome to ModelSim screen is not available, you can enable it by selecting Help > Enable Welcome from the Main window. It will then display the next time you start ModelSim. You can also access the Create a New Project dialog box by selecting File > New > New Project from the ModelSim Main window.

Clicking the **Create a Project** button opens the Create a New Project dialog box and a project creation wizard. The wizard helps you through each step of creating a new project. It provides the option of entering Verilog or VHDL source file descriptions, then helps you load the project.

3 In the Create a New Project dialog box, you can elect to create a new project from scratch or copy an existing project. The easiest way to start any project is to copy a similar project. Let's begin by selecting "copy an existing project."

| 🙀 Create a New Project |                                                                      |          | _ 🗆 ×  |

|------------------------|----------------------------------------------------------------------|----------|--------|

|                        | Create<br>C a new project from scratch<br>C copy an existing project |          |        |

| New Project's Home:    |                                                                      |          | Browse |

| New Project's Name:    |                                                                      |          |        |

| Existing Project:      |                                                                      | <u>+</u> | Browse |

|                        | OK                                                                   |          |        |

- 4 Specify the "New Project's Home," which is the directory under which the project's directory tree will reside. This directory must already exist completion of this dialog box will not create it.

- **5** Specify the "New Project's Name," which will act both as the project's directory name and the name for the .mpf file. Use a unique name for each project.

**6** Specify an "Existing Project" name, which is the full path to an existing project's .mpf file. For this lesson, browse to *modeltech/examples/projects/vhdl/vhdl.mpf* and select this file.

| 🙀 Create a New Project                                               | _ 🗆 ×  |

|----------------------------------------------------------------------|--------|

| Create<br>C a new project from scratch<br>C copy an existing project |        |

| New Project's Home: C:/Project Files                                 | Browse |

| New Project's Name: Lesson1                                          |        |

| Existing Project: E:/modeltech/examples/projects/vhdl/vhdl.mpf       | Browse |

| OK Cancel                                                            |        |

- 7 Once you have specified enough information to copy an existing project, the OK button is selectable. Selecting OK causes the project directory to be created with a default working library. You will then be asked if you want to make this project your current project. Click Yes.

- **8** In the dialog box that asks if you want to create a new HDL source file for your project, click No. Then click Done in the Welcome to ModelSim dialog box.

Now you can begin compiling your project.

9 Select **Options > Edit Project**. This opens the Edit Project dialog box.

| Edit Project "Les | son1"                  |                |

|-------------------|------------------------|----------------|

| Source List Proje | ct Build               |                |

| Source File:      |                        | E Browse       |

| Ν                 | lew Import Edit        | Delete         |

| Project Library:  | rork                   | <u>±</u>       |

| Com               | pile Compiler Settings | Add to Library |

|                   | Done                   |                |

Click the down arrow next to the Source File entry field and select the source *counter.vhd*.

With the source file selected, the Compile button becomes available.

| \$MODELSIM_PROJECT/counter.vhd |  |

|--------------------------------|--|

| \$MODELSIM_PROJECT/counter.vhd |  |

|                                |  |

|                                |  |

**10** Click the **Compile** button in the Edit Project dialog box. With a source file compiled, the Add to Library button becomes available.

11 Click Add to Library, then Done, in the Edit Project dialog box.

Note: The combination of Compile and Add to Library creates a script (DO file) that will recompile the entire project. You must Add to Library after each Compile to create a proper script. To recompile a project use the Main > Design > Compile Project menu selection.

**12** Start the simulator by selecting the **Load Design** button from the toolbar:

(PROMPT: vsim counter)

The Load Design dialog box comes up, as shown below (you won't see this dialog box if you invoke **vsim** with *counter* from the command line).

| 🙀 Load Design                   |             | _ 🗆 ×  |

|---------------------------------|-------------|--------|

| Design VHDL Verilog SDF         |             | 1      |

| Simulator Resolution: default 💻 |             |        |

| Library: work                   | <u>±</u>    | Browse |

| Simulate:                       |             | Add    |

| Design Unit                     | Description |        |

| 😐 counter                       | Entity      |        |

|                                 |             |        |

|                                 |             |        |

The Load Design dialog box allows you to select the library and the top-level design unit to simulate. Select "counter" under Design Unit and then select the **Load** button.

This completes the process of creating a project by copying an existing project. The newly created project will be open for use in the Main window.

You can now elect to leave Model*Sim* or edit this project's HDL components until the project is completely specified and all files compile into libraries local to the project. If you leave this Model*Sim* session, you can reopen the project by clicking **Open Project** in the Welcome to Model*Sim* screen.

# **Lesson 2 - Basic VHDL simulation**

# The goals for this lesson are:

- Create a library

- Compile a VHDL file

- Start the simulator

- Learn about the basic VSIM windows, mouse, and menu conventions

- Run VSIM using the **run** command

- List some signals

- Use the waveform display

- Force the value of a signal

- Single-step through a simulation run

- Set a breakpoint

# Preparing the simulation

Prior to running a simulation, you compile your HDL code and load the top-level design unit.

Start by creating a new directory for this exercise (in case other users will be working with these lessons). Create the directory, then copy all of the VHDL (.vhd) files from \<install\_dir>\modeltech\examples to the new directory.

Make sure the new directory is the current directory. Do this by invoking Model*Sim* from the new directory or by selecting the **File > Change Directory** command from the Model*Sim* Main window.

2 Start Model*Sim* with one of the following:

for UNIX at the shell prompt:

vsim -gui

for Windows - your option - from a Windows shortcut icon, from the Start menu, or from a DOS prompt:

modelsim.exe

- **Note:** If you didn't add Model*Sim* to your search path during installation, you will have to include the full path when you type this command at a DOS prompt.

- 3 Before you compile any HDL code, you'll need a design library to hold the compilation results. To create a new design library, make this menu selection in the Main window: Design > Create a New Library.

In the Create a New Library dialog box select **Create: a new library and a logical mapping to it**. Make sure **Library:** indicates **work**, then select **OK**.

This creates a subdirectory named *work* - your design library - within the current directory. ModelSim saves a special file named *\_info* in the subdirectory.

(PROMPT: vlib work vmap work work)

| MC | reate a New Library                       |

|----|-------------------------------------------|

|    | Create                                    |

|    | a new library and a logical mapping to it |

|    | 🔘 a new library only (no mapping)         |

|    | O a map to an existing library            |

|    | ary: work to: work Browse                 |

|    | OK Cancel                                 |

Note: Do not create a Library directory using UNIX or Windows commands, because the \_info file will not be created. Always use the Library menu or the vlib command from either the ModelSim or UNIX/DOS prompt.)

**4** Compile the file *counter.vhd* into the new library by selecting the **Compile** button on the toolbar:

(PROMPT: vcom counter.vhd)

This opens the Compile HDL Source Files dialog box. (You won't see this dialog box if you invoke vcom from the command line.)

| Compile HDL                                              | Source Files                                                                                                                        |                                                         | ? × |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|

| Library:                                                 | work                                                                                                                                | -                                                       |     |

| Look jn:                                                 | 🔁 examples                                                                                                                          | 💽 🖻 🔳                                                   |     |

| foreign<br>mixedHDL<br>tcl_tutorial<br>work<br>adder.vhd | <ul> <li>counter.v</li> <li>counter.vhd</li> <li>gates.vhd</li> <li>io_utils.vhd</li> <li>jedec.vhd</li> <li>pal16r8.vhd</li> </ul> | ian stimulus.∨hd<br>ian toounter.∨<br>ian testadder.vhd |     |

| File <u>n</u> ame:                                       | counter. vhd                                                                                                                        | Comp                                                    | ile |

| Files of <u>type</u> :                                   | HDL Files (*.vhdl;*.vhd;*.v)                                                                                                        | Don                                                     | e   |

|                                                          | Default Options                                                                                                                     | Edit Source                                             |     |

Complete the compilation by selecting *counter.vhd* from the file list and clicking **Compile**. Select **Done** when you are finished.

You can compile multiple files in one session from the file list. Individually select and Compile the files in the order required by your design.

5 Now let's load the design unit. Select the Load Design button from the toolbar:

(PROMPT: vsim counter)

The Load Design dialog box comes up, as shown below (you won't see this dialog box if you invoke **vsim** with *counter* from the command line).

| 🙀 Load Design                                                 |                        |        |

|---------------------------------------------------------------|------------------------|--------|

| Design VHDL Verilog SDF                                       | 1                      |        |

| Simulator Resolution: default =<br>Library: work<br>Simulate: |                        | Browse |

| Design Unit                                                   | Description            |        |

| Counter                                                       | Entity                 |        |

| Load                                                          | kit Save Settings Cano | cel    |

The Load Design dialog box lets you select the library and top-level design unit to simulate. You can also select the resolution limit for this simulation. By default, the following will appear for this simulation run:

- Simulator Resolution: default (the default is 1 ns)

- Library: work

- Design Unit: counter

- Description: entity

If the Design Unit is an entity (like **counter** in this design), you can click on the plus-box prefix to view any associated architectures.

| Design Unit | Description  |

|-------------|--------------|

| counter     | Entity       |

| only        | Architecture |

- 6 Select the entity counter and choose Load to accept these settings.

- 7 Next, select View > All from the Main window menu to open all VSIM windows.

(PROMPT: view \*)

For descriptions of the windows, consult the ModelSim User's Manual.

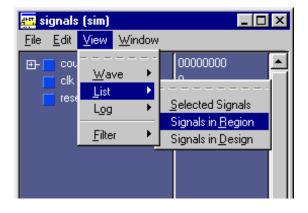

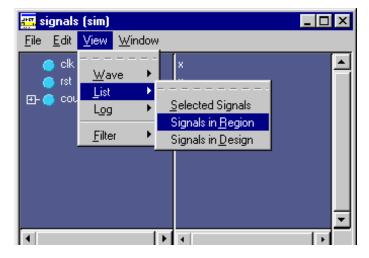

8 From the Signals window menu, select **View > List > Signals in Region**. This command displays the top-level signals in the List window.

(PROMPT: add list /counter/\*)

9 Next add top-level signals to the Wave window by selecting View > Wave > Signals in Region from the Signals window menu.

(PROMPT: add wave /counter/\*)

### **Running the simulation**

We will start the simulation by applying stimulus to the clock input.

1 Click in the Main window and enter the following command at the VSIM prompt:

force clk 1 50, 0 100 -repeat 100

VSIM interprets this force command as follows:

- force clk to the value 1 at 50 ns after the current time

- then to 0 at 100 ns after the current time

- repeat this cycle every 100 ns

| ModelSim                                                                                                                                                                                                                           |                                                |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|

| <u>File Edit D</u> esign <u>V</u> iew <u>R</u> un <u>M</u> ac                                                                                                                                                                      | ro <u>O</u> ptions <u>W</u> indow <u>H</u> elp |  |

| 🕸 🚘   🖻 🛍   📑 📃 1 🥲                                                                                                                                                                                                                | 🗧 🗊 🗊 📑 就 🛛 🔂 🗘                                |  |

| <pre># Loading work.counter(only) view * # .structure .signals .variables .process .source .wave .list .dataflow add list sim:/counter/* # 3 add wave sim:/counter/* VSIM 4&gt; force clk 1 50, 0 100 -repeat 100 VSIM 5&gt;</pre> |                                                |  |

| Now: 0 ns Delta: 0                                                                                                                                                                                                                 | sim:/counter                                   |  |

Note how the Run Length selector on the toolbar now indicates 100 (ns is the current default resolution). You will see the effects of this **force** command as soon as you tell the simulator to run.

2 Now you will exercise two different **Run** functions from the toolbar buttons on either the Main or Wave window. (The **Run** functions are identical in the Main and Wave windows.) Select the **Run** button first. When the run is complete, select **Run All**.

**Run**. This causes the simulation to run and then stop after 100 ns. (PROMPT: run 100) (MENU: Run > Run 100ns)

**Run -All**. This causes the simulator to run forever. To stop the run, go on to the next step. (PROMPT: run -all) (MENU: Run > Run -All)

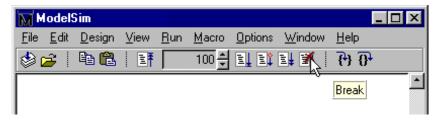

3 Select the Break button on either the Main or Wave toolbar to end the run.

(KEYBOARD: control+c)

The arrow in the Source window points to the next HDL statement to be executed. (If the simulator is not evaluating a process at the time the Break occurs, no arrow will be displayed in the Source window.)

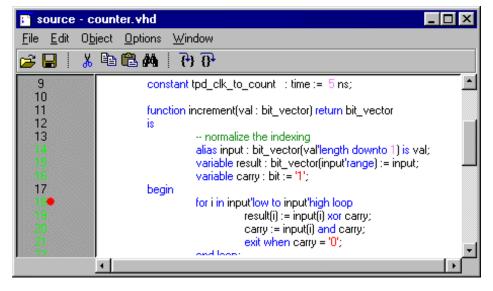

Next, you will set a breakpoint in the function on line 18.

4 Move the pointer to the VSIM Source window. Scroll the window vertically until line 18 is visible. Click on or near line number 18 to set the breakpoint. You should see a red dot next to the line number where the breakpoint is set. The breakpoint can be toggled between enabled and disabled by clicking it. When a breakpoint is disabled, the circle appears open. To delete the breakpoint, click the line number with your right mouse button and select delete.

(PROMPT: bp counter.vhd 18)

• **Note:** Breakpoints can be set only on executable lines — denoted by green line numbers.

**5** Select the **Continue Run** button to resume the run that you interrupted. VSIM will hit the breakpoint, as shown by an arrow in the VSIM Source window and by a Break message in the Main window.

(PROMPT: run -continue) (MENU: Run > Continue)

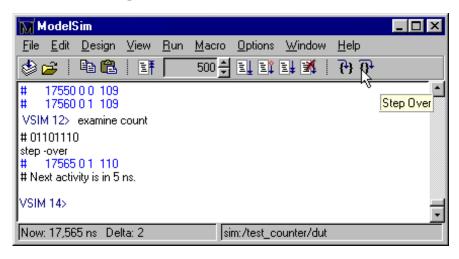

6 Click the **Step** button to single-step through the simulation. Notice that the values change in the VSIM Variables window. You can keep clicking **Step** if you wish.

(PROMPT: run -step) (PROMPT: step)

7 When you're done, quit the simulator by entering the command:

quit -force

This command exits VSIM without saving data. Your window positions will be saved in the *modelsim.ini* file and the windows will close. (Refer to the *ModelSim User's Manual* for additional information on the *modelsim.ini* file.)

# Lesson 3 - Debugging a VHDL design

### The goals for this lesson are:

- Show an example of a VHDL testbench a VHDL architecture that instantiates the VHDL design units to be tested, provides simulation stimuli, and checks the results

- Map a logical library name to an actual library

- Change the default run length

- Recognize assertion messages in the command window

- Change the assertion break level

- Restart the simulation run using the **restart** command

- Examine composite types displayed in the VSIM Variables window

- Change the value of a variable

- Use a strobe to trigger lines in the VSIM List window

- Change the radix of signals displayed in the VSIM List window

### Preparing the simulation

- 1 Create a new directory for this exercise and copy the following VHDL (.vhd) files from \<*install\_dir*>\modeltech\examples to the new directory.

- gates.vhd

- adder.vhd

- testadder.vhd

Make sure the new directory is the current directory. Do this by invoking Model*Sim* from the new directory or by using the **File > Change Directory** command from the Model*Sim* Main window.

**2** Start Model*Sim* with one of the following:

for UNIX at the shell prompt:

vsim -gui

for Windows - your option - from a Windows shortcut icon, from the Start menu, or from a DOS prompt:

modelsim.exe

**3** Enter the following command at the Model*Sim* prompt to create a new library:

vlib library\_2

**4** Compile the source files into the new library by entering this command at the system prompt:

vcom -work library\_2 gates.vhd adder.vhd testadder.vhd

5 Now let's map the new library to the work library. To create a mapping you can edit the [Library] section of the *modelsim.ini* file, or you can create a logical library name with the **vmap** command:

vmap work library\_2

ModelSim modifies the modelsim.ini file for you.

6 Start the simulator by selecting **Design > Load New Design** from the Main window, or by clicking the Load Design icon. The Load Design dialog box is displayed, as shown below.

**7** Perform the following steps in this dialog box:

| Load Design                   |                         |        |

|-------------------------------|-------------------------|--------|

| Design VHDL Verilog SD        | F                       |        |

| Simulator Resolution: default | _                       |        |

| Library: work                 | <u>±</u>                | Browse |

| Simulate:                     |                         | Add    |

| Design Unit                   | Description             |        |

| 🗉 adder                       | Entity                  |        |

| 🗷 addern                      | Entity                  |        |

| ⊞ andg                        | Entity                  |        |

|                               | Entity                  |        |

| test_adder_behavioral         | Config                  |        |

| test_adder_structural         | Config                  |        |

| testbench                     | Entity                  |        |

| ■ xorg                        | Entity                  |        |

|                               |                         |        |

|                               |                         |        |

|                               |                         |        |

| Load                          | Exit Save Settings Cano | el     |

|                               |                         |        |

|                               |                         |        |

- Make sure that the simulator resolution is **default**. (The default resolution is **ns**.)

- Look in the Design Unit scroll box and select the configuration named **test\_adder\_structural**.

- Click Load to accept the settings.

(PROMPT: vsim -t ns work.test\_adder\_structural)

**8** To open all of the VSIM windows, enter the following command in the Main window at the VSIM prompt:

```

view *

```

(Main MENU: View > All)

Model*Sim* will open all the windows in the positions you left them at the end of the last exercise, if no one has run the simulator since then.

**9** Drag and drop the top-level signals to the List window in the following manner: make sure the hierarchy is not expanded (no minus boxes), select all signals in the Signals window with Edit > Select All, then drag the selected signals to the List window.

```

(Signals MENU: View > List > Signals in Region) (PROMPT: add list *)

```

**10** To add top-level signals to the Wave window, enter the command:

```

add wave *

```

(Signals MENU: View > Wave > Signals in Region) (DRAG&DROP)

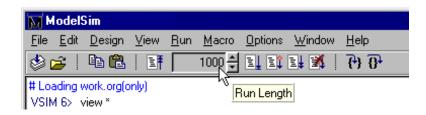

**11** Now change the default simulation run length to 1000 (ns) with the run length selector on the Main toolbar. Click on the field to edit the number to 1000 (notice how the arrows allow you to change the run length in increments).

(Main MENU: Options > Simulation > Defaults)

# Running and debugging the simulation

1 Now you will run the simulator. Select the **Run** button on the Main window toolbar.

(PROMPT: run)

A message in the Main window will notify you that there was an assertion error.

| I | run<br># ** Error: Sum is 00000111. Expected 00001000<br># Time: 600 ns Iteration: 0 Instance: /testbench<br># ** Note: There were ERRORS in the test.<br># Time: 1 us Iteration: 0 Instance: /testbench<br>VSIM 10> |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Now: 1 us Delta: 1 sim:/testbench                                                                                                                                                                                    |

Let's find out what's wrong. Perform the following steps to track down the assertion message.

2 First, change the simulation assertion options. Select **Options > Simulation** from the Main window menu.

| Simulation Options  |                         |  |  |

|---------------------|-------------------------|--|--|

| Defaults Assertions |                         |  |  |

|                     |                         |  |  |

| Break on Assertion  | -Ignore Assertions For: |  |  |

| C Fatal             | 🗖 Failure               |  |  |

| C Failure           | Error                   |  |  |

| Error               | 🗖 Warning               |  |  |

| C Warning           | Note                    |  |  |

| C Note              |                         |  |  |

|                     |                         |  |  |

- **3** Select the **Assertions** page. Change the selection for **Break on Assertion** to **Error** and click **OK**. This will cause the simulator to stop at the HDL statement *after* the assertion is displayed.

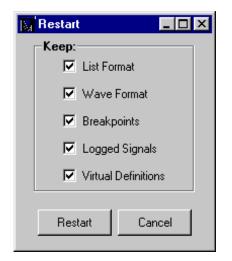

- 4 To restart the simulation select the **Restart** button on the Main toolbar.

(Main MENU: File > Restart) (PROMPT: restart)

Make sure all items in the Restart dialog box are selected, then click Restart.

| М | Restart 📃 🗖 🛛       | 1 |

|---|---------------------|---|

|   | Кеер:               |   |

|   | 🔽 List Format       |   |

|   | 🔽 Wave Format       |   |

|   | 🔽 Breakpoints       |   |

|   | Logged Signals      |   |

|   | Virtual Definitions |   |

|   |                     |   |

|   | Restart Cancel      |   |

|   |                     |   |

**5** From the Main window toolbar select the **Run** button.

(Main MENU: Run > Run 1000 ns) (PROMPT: run)

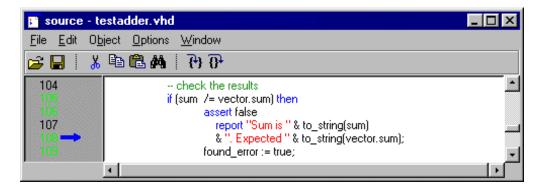

Notice that the arrow in the Source window is pointing to the statement after the assertion.

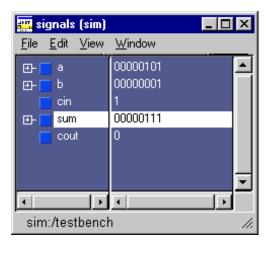

**6** If you look at the Variables window now, you can see that i = 6. This indicates that the simulation stopped in the sixth iteration of the test pattern's loop.

| 📅 variables                                   |                                             |

|-----------------------------------------------|---------------------------------------------|

| <u>F</u> ile <u>E</u> dit ⊻iew <u>W</u> indow |                                             |

| adder8                                        | L                                           |

| n                                             | 8                                           |

| 🖅 📄 test_patterns                             | {{{0000000} {0000001} {0} {00000            |

| ⊡- 🛑 to_char                                  | UX01ZWLH-                                   |

| test                                          | {{00000000} {0000000} {0} {0000000}<br>true |

|                                               | •                                           |

| test                                          | li.                                         |

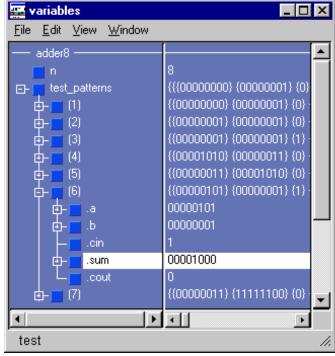

7 Expand the variable named **test\_patterns** by clicking the [+]. (You may need to resize the window for a better view.)

**8** Also expand the sixth record in the array **test\_patterns(6)**, by clicking the [+]. The Variables window should be similar to the one below.

The assertion shows that the Signal **sum** does not equal the **sum** field in the Variables window. Note that the sum of the inputs **a**, **b**, and **cin** should be equal to the output **sum**. But there is an error in the test vectors. To correct this error, you need to restart the simulation and modify the initial value of the test vectors.

**9** In the Main window, type:

restart -f

The -f option causes VSIM to restart without popping up the confirmation dialog.

**10** Add variables to the Variables window by selecting the **test /testbench** process in the Process window.

11 In the Variables window, expand test\_patterns and test\_pattern(6) again. Then highlight the .sum record by clicking on the variable name (not the box before the name) and then use the Edit > Change menu selection.

| M change                                            |

|-----------------------------------------------------|

| Variable Name: /testbench/test/test_patterns(6).sum |

| Value: 00000111                                     |

| C <u>h</u> ange <u>C</u> ancel                      |

- 12 Select the last four bits (1000) in the value field by dragging the pointer across them. Then replace them with 0111, and click **Change**. (Note that this is a temporary edit, you must use your text editor to permanently change the source code.)

- **13** Select the **Run** button from the Main window toolbar.

(Main MENU: Run > Run 1 us) (PROMPT: run)

At this point, the simulation will run without errors.

| run<br># ** Note: 1<br># Time: 1<br>VSIM 14> | est completer<br>us Iteration: I | d with no errors.<br>0 Instance: /testbench |

|----------------------------------------------|----------------------------------|---------------------------------------------|

| Now: 1 us                                    | Delta: 1                         | Env: /testbench                             |

# Changing new-line triggering

By default, a new line is displayed in the List window for each transition of a listed signal. The following steps will change the triggering so the values are listed every 100 ns.

| Modify Display Proper                        | rties (list)                                    |

|----------------------------------------------|-------------------------------------------------|

| Window Properties                            | ggers                                           |

| Deltas:<br>Expand Deltas                     | C Collapse Deltas C No Deltas                   |

| <b>⊤Trigger On:</b><br>□ Signals<br>☑ Strobe | Strobe Period: 100 ns<br>First Strobe at: 70 ns |

| Trigger Gating:                              | Use Expression Builder                          |

| Expression:                                  |                                                 |

| On Duration:                                 | 0 ns                                            |

|                                              | OK Cancel Apply                                 |

1 In the List window, select **Prop > Display Props**.

- **2** Perform these steps on the **Triggers** page:

- Deselect Trigger On: Signals to disable triggering on signals.

- Select **Trigger On: Strobe** to enable the strobe.

- Enter 100 in the Strobe Period field.

- Enter 70 in the First Strobe at field.

- Click **OK** to accept the settings.

- **3** Your last action will be to change the radix to decimal for signals a, b, and sum.

Select **Prop > Signal Props**. This opens the Modify Signal Properties (list) dialog box.

| Modify Signal Propertie                                                                            | s (list)                                           |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Signal:<br>Label: //testbe                                                                         | nch/a                                              |

| Radix:<br>O Symbolic<br>O Binary<br>O Octal                                                        | Width: वि Characters                               |

| <ul> <li>Decimal</li> <li>Unsigned</li> <li>Hexadecimal</li> <li>ASCII</li> <li>Default</li> </ul> | Trigger:<br>Triggers line<br>Does not trigger line |

| ОК                                                                                                 | Apply Cancel                                       |

- 4 In the List window select the signal you want to change, then make the property changes in the dialog box. Make the following property changes:

- Select signal **a**, then click **Decimal**, then click **Apply**.

- Select signal **b**, then click **Decimal**, then **Apply**.

- Select signal sum, then click Decimal, then OK.

This brings you to the end of this lesson, but feel free to experiment further with the menu system. When you are ready to end the simulation session, quit VSIM without saving data by entering the following command at the VSIM prompt:

quit -force

# Lesson 4 - Running a batch-mode simulation

# The goals for this lesson are:

- Run a batch-mode VHDL simulation

- Execute a macro (DO) file

- View a saved simulation

Batch-mode allows you to execute several commands that are written in a text file. You create a text file with the list of commands you wish to run, and then specify that file when you start Model*Sim*. This is particularly useful when you need to run a simulation or a set of commands repeatedly.

Important: Batch-mode simulations must be run from a DOS or UNIX prompt. In Windows 95/98/NT, you get a DOS prompt by selecting Start > Programs > Command Prompt. Unless directed otherwise, enter all commands in this lesson at a DOS or UNIX prompt.

**1** To set up for this lesson you'll need to create a new directory and make it the current directory. Copy this file into your new directory:

$\verb|<install_dir>\verb|modeltech|examples|counter.vhd|$

- 2 Create a new design library (Remember, enter these commands at a DOS or UNIX prompt): vlib work

- **3** Map the library:

vmap work work

**4** Then compile the source file:

vcom counter.vhd

**5** You will use a macro file that provides stimulus for the counter. For your convenience, a macro file has been provided with Model*Sim*. You need to copy this macro file from the installation directory to the current directory:

<install\_dir>\modeltech\examples\stim.do

**6** Create a batch file using an editor; name it *yourfile*. With the editor, put the following on separate lines in the file:

```

add list -decimal *

do stim.do

write format list counter.lst

```

and save to the current directory.

7 To run the batch-mode simulation, enter the following at the command prompt:

```

vsim -wav saved.wav counter < yourfile</pre>

```

This is what you just did in Step 7:

- invoked the VSIM simulator on a design unit called "counter"

- the **-wav** switch instructed the simulator to save the simulation results in a log file named *saved.wav*

- used the contents of *yourfile* to specify that values are to be listed in decimal, to execute a stimulus file called *stim.do*, and to write the results to a file named *counter.lst*, the default for a design named counter

- 8 Since you saved the simulation results in *saved.wav*, you can view the simulation results by starting up VSIM with its **-view** switch:

vsim -view saved.wav

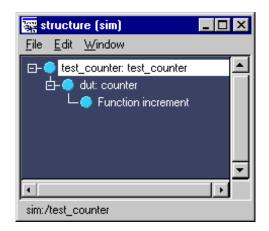

**9** Open these windows with the VIEW menu in the Main window, or the equivalent command at the ModelSim prompt:

view structure signals list wave

- **Note:** If you open the Process or Variables windows they will be empty. You are looking at a saved simulation, not examining one interactively; the logfile saved in *saved.wav* was used to reconstruct the current windows.

- **10** Now that you have the windows open, put the signals in them:

- add wave \* add list \*

- **11** Use the available VSIM windows to experiment with the saved simulation results and quit when you are ready:

quit -f

For additional information on the batch and command line modes, please refer to the *ModelSim User's Manual*.

# Lesson 5 - Executing commands at startup

# The goals for this lesson are:

- Specify the design unit to be simulated on the command line

- Edit the modelsim.ini file

- Execute commands at startup with a DO file

**Important:** Start this lesson from either the UNIX or DOS prompt.

1 For this lesson, you will use a macro (DO) file that provides startup information. For convenience, a startup file has been provided with the Model*Sim* program. You need to copy this DO file from the installation directory to your current directory:

```

\<install_dir>\modeltech\examples\startup.do

```

2 Next, you will edit the system initialization file in the \modeltech directory to specify a command that is to be executed after the design is loaded. To do this, open <install\_dir>\modeltech\ modelsim.ini using a text editor and uncomment the following line (by deleting the leading ;) in the [vsim] section of the file:

Startup = do startup.do

Then save modelsim.ini.

- ▶ Note: The *modelsim.ini* file must be write-enabled for this change to take place. Using MS Explorer, right-click on \<*install\_dir*>\*modeltech*\*modelsim.ini*, then click Properties. In the dialog box, uncheck the Read-only box and click OK.

- **3** Take a look at the DO file. It uses the predefined variable **\$entity** to do different things at startup for different designs.

- **4** Start the simulator and specify the top-level design unit to be simulated by entering the following command at the UNIX/DOS prompt:

vsim counter

Notice that the simulator loads the design unit without displaying the Load Design dialog box. This is handy if you are simulating the same design unit over and over. Also notice that all the windows are open. This is because the **view** \* command is included in the startup macro.

**5** If you plan to continue with the following practice sessions, keep Model*Sim* running. If you would like to quit the simulator, enter the following command at the VSIM prompt:

quit -f

**6** You won't need the *startup.do* file for any other examples, so use your text editor to comment out the "Startup" line in *modelsim.ini*.

# Lesson 6 - Tcl/Tk and ModelSim

## The goals for this lesson are:

- Create a "hello world" button widget

- Execute a procedure using a push button

- Simulate an intersection with traffic lights

- Draw a state machine that represents the simulation

This lesson is divided into several Tcl examples intended to give you a sense of Tcl/Tk's function within Model*Sim*. The examples include a custom simulation interface created with Tcl/Tk (the code is already written).

• **Note:** You must be using Model*Sim* SE/EE-VHDL or Model*Sim* SE/MIXED to complete these exercises.

### More information on Tcl/Tk

Sources of information about Tcl include *Tcl and the Tk Toolkit* by John K. Ousterhout, published by Addison-Wesley Publishing Company, Inc., and *Practical Programming in Tcl and Tk by* Brent Welch published by Prentice Hall.

Also, the following lists several of th many online Tcl references:

- When using ModelSim make this VSIM Main menu selection: Help > Tcl Man Pages.

- Tcl man pages are also available at: www.elf.org/tcltk-man-html/contents.htm

- Tcl/Tk general information is available from the Tcl/Tk Consortium: www.tclconsortium.org

- The Scriptics Corporation, John Ousterhout's company (the original Tcl developer): www.scriptics.com.

### How Tcl/Tk works with ModelSim

Model*Sim* incorporates Tcl as an embedded library package. The Tcl library consists of a parser for the Tcl language, routines to implement the Tcl built-in commands, and procedures that allow Tcl to be extended with additional commands specific to Model*Sim*.

Model*Sim* generates Tcl commands and passes them to the Tcl parser for execution. Commands may be generated by reading characters from an input source, or by associating command strings with Model*Sim*'s user interface features, such as menu entries, buttons, or keystrokes.

When the Tcl library receives commands it parses them into component fields and executes built-in commands directly. For commands implemented by Model*Sim*, Tcl calls back to the application to execute the commands. In many cases commands will invoke recursive invocations of the Tcl interpreter by passing in additional strings to execute (procedures, looping commands, and conditional commands all work in this way).

Model*Sim* gains a programming advantage by using Tcl for its command language. Model*Sim* can focus on simulation-specific commands, while Tcl provides many utility commands, graphic interface features, and a general programming interface for building up complex command procedures.

By using Tcl, Model*Sim* need not re-implement these features, a benefit that allows it's graphic interface to remain consistent on all platforms. (The only vestige of the host platform's graphic interface is the window frame manager.)

# The custom traffic-light interface

The subject of our main Tcl/Tk lesson is a simple traffic-light controller. The system is comprised of three primary components: a state machine, a pair of traffic lights, and a pair of traffic sensors. The components are described in three VHDL files: traffic.vhd (the state machine), queue.vhd (the traffic arrival queue) and tb\_traffic.vhd (the testbench).

You could, of course, simulate this system with Model*Sim*'s familiar interface, but Tcl/Tk provides us the option to try something different. Since we're simulating something most of us have seen and experienced before, we can create an intuitive interface unique to the simulation.

### Assumptions

The example assumes that source files were previously compiled. Here's how it works:

| Ë                                          | Ë                                                                                                 | Ë                                                                              |

|--------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| VHDL source files describe the system      | Tcl procedures create and<br>connect the interface, plus the<br>source files, to Model <i>Sim</i> | ModelSim commands are run via the new interface using the Tcl procedures       |

|                                            | draw_intersection                                                                                 |                                                                                |

| traffic.vhd<br>queue.vhd<br>tb_traffic.vhd | connect_lights                                                                                    | vsim -lib vhdl/work tb_traffic<br>examine -value <light_timing></light_timing> |

|                                            | draw_queues                                                                                       |                                                                                |

|                                            | draw_controls                                                                                     | force -freeze \$var \$val ns                                                   |

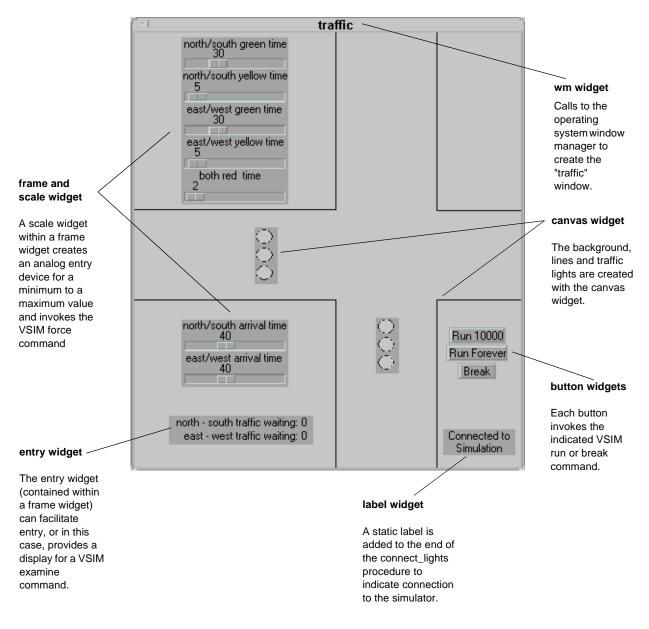

The result is a traffic intersection interface similar to this illustration:

### Tk widgets

The intersection illustration points out several Tcl/Tk "widgets." A widget is simply a user interface element, like a menu or scrolled list. Tk widgets are referenced within Tcl procedures to create graphic interface objects. The Tk tool box comes with several widgets, additional widgets can be created using these as a base.

### Controlling the simulation

The components of the intersection interface have the following effect within ModelSim:

| Intersection control<br>used | Effect in ModelSim                                                                                        |

|------------------------------|-----------------------------------------------------------------------------------------------------------|

| Run 1000 button              | invokes the run command for 1000 ns                                                                       |

| Run Forever button           | invokes the run -all command                                                                              |

| Break button                 | invokes the break command                                                                                 |

| light timing control         | invokes the force command with the arguments for the indicated signal and time                            |

| arrival time control         | invokes the force command with the arguments for the indicated direction and time                         |

| waiting queue                | any time you change a control the examine command is<br>invoked to display the value of the waiting queue |

### Saving time

Since several intersection controls invoke a VSIM command and arguments with a single action (such as the movement of a slider), this custom interface saves time compared to invoking the commands from the command line or Model*Sim* menus.

### Copies of the original example files

Additional copies of the Tcl example files from these exercises are located in the .../*examples*/*tcl\_tutorial*/*originals* directory.

#### Solutions to the examples

Throughout the traffic intersection examples you will be modifying Tcl files to complete the final intersection. You will find a completed set of intersection examples ready-to-run in the *tcl\_tutorial*\solutions directory. Invoke these commands from the ModelSim prompt to run the intersection:

```

cd solutions

do traffic.do

```

### **Viewing files**

If you would like to view the source for any of the Tcl files in our examples, use the **notepad** command at either the Model*Sim* or VSIM prompt.

```

notepad <filename>

```

Most files are opened in read-only mode by default; you can edit the file by deselecting **read only** from the notepad **Edit** menu.

#### The Tcl source command

The Tcl **source** command reads the Tcl file into the Tcl interpreter, which parses the procedures for use within the current environment. Once sourced, a Tcl procedure can be called from the Model*Sim* prompt as shown in the syntax below. VSIM executes the instructions within the procedure.

#### Syntax

```

source <tcl filename>

<tcl procedure name>

```

#### Arguments

```

<tcl filename>

```

The Tcl file read into the VSIM Tcl interpreter with the source command.

#### <tcl procedure name>

The Tcl procedure defined within <tcl filename>, called from the Model*Sim* prompt, and executed by VSIM.

The *traffic.do* file is a good example of the **source** command syntax (the file is a macro that runs the traffic light simulation). Check it out with the notepad:

notepad traffic.do

### Shortcuts

To save some typing, copy the commands from the PDF version of these instructions and paste them at the Model*Sim* prompt. Paste with the right (2 button mouse), or middle (3 button mouse). You can also select a Model*Sim* or VSIM prompt from the Main transcript to paste a previous command to the current command line.

#### Make a transcript DO file

You can rerun the commands executed during the current session with a Do file created from the Main transcript. Make the DO file by saving the transcript with the **File > Save Main As** menu selection at any time during the exercises. Run the DO file to repeat the commands (do <do filename>).

### **Initial setup**

**Important:** These steps must be completed before running the Tcl examples.

1 Create, and change to a new working directory for the Tcl/Tk exercises. Copy the lesson files in the following directory (include all subdirectories and files) to your new directory:

```

<install_dir>\modeltech\examples\tcl_tutorial

```

2 Make the new directory the current directory, then invoke ModelSim:

for UNIX

vsim -gui

for Windows (from a shortcut or Start > Run, etc.)

modelsim.exe

**3** At the ModelSim prompt, create a **work** library in the */vhdl* directory:

vlib vhdl/work

4 Map the work library.

vmap work vhdl/work

**5** Compile the VHDL example files with these commands (or the Compile dialog box):

vcom vhdl/traffic.vhd vcom vhdl/queue.vhd vcom vhdl/tb\_traffic.vhd

# Example 1 - Create a "hello world" button widget

Before you begin the examples make sure you have completed "Initial setup" (6-54). In this example you will study a "hello world" button that prints a message when pressed.

**1** Source the Tcl file from the Model*Sim* prompt:

source hello.tcl

then run the procedure defined within *hello.tcl*:

hello\_example

The file *hello.tcl* was read into the VSIM Tcl interpreter. The instructions in *hello\_example* procedure were then executed by VSIM, and "Hello World" was printed to the Main transcript. Selecting the button will print the message again.

You've just created your first top-level widget!

2 Invoke the *hello\_example* procedure again and notice how the new button replaces the original button. The procedure destroyed the first button and created the new one. Get a closer look at the source Tcl file with the **notepad**:

notepad hello.tcl

Close the hello\_example window when you're done.

## Example 2 - Execute a procedure using a push button

Before you begin this example make sure you have completed "Initial setup" (6-54).

This example will display all of the gif images in the images directory. Each button has a binding attached to it for "enter" events, and a binding for a mouse button press. When the mouse enters the button graphic, the image file name is printed to the Main window. When the mouse button is pushed, its "widget" name will be printed to the Main window.

1 Build an image viewer by invoking this command, and calling this procedure:

```

source images.tcl

image_example

```

2 Drag the mouse across the buttons and notice what happens in the Main transcript.

Push one of the buttons; you will see an error dialog box. You can solve this problem by modifying the *images.tcl* file.

**3** To view the source file press the **See Source Code** button at the bottom of the image display or invoke **notepad** at the Model*Sim* prompt:

notepad images.tcl

You'll find that the *pushme* procedure is missing; it's commented out in *images.tcl*.

4 Search for "proc push" using the **Edit** > **Find** menu selection in the notepad.

Remove the comments (the "#" symbols) to return the function to your source, then close the image window with the **Destroy** button.

**5** Once the *pushme* procedure is in place it will print its one parameter, the object name, to the transcript.

After you have added the *pushme* procedure to your source, you need to resource and rerun the Tcl procedure with these commands (use the up arrow to scroll through the commands or do !source):

```

source images.tcl

image_example

```

Press all the buttons and notice the object names in the Main transcript. Close the image example window when you're done.

### **Example 3 - Simulate an intersection with traffic lights**

In this example you'll simulate an intersection with traffic lights. The simulation interface you create allows you to run "what if" scenarios efficiently.

### Introduction of the traffic intersection widget

This portion of our example introduces the traffic intersection widget. You'll add other widgets to the intersection to create a custom traffic simulation environment.

Once again, make sure you have completed "Initial setup" (6-54) before working this example.

1 Draw the intersection by invoking this command and procedure at the ModelSim prompt:

```

source intersection.tcl

draw_intersection

```

2 From the Model*Sim* prompt, use the procedure set\_light\_state to change the color of the lights:

```

set_light_state green .traffic.i.ns_light

set_light_state green .traffic.i.ew_light

```

You can use the Copy and Paste buttons on the Main toolbar to help build instructions from previous commands.

**3** View the source code with this command at the Model*Sim* prompt:

notepad intersection.tcl

You can locate the *set\_light\_state* procedure with **Edit** > **Find** from the Main menu (it's located toward the middle of the file).

#### Connect traffic lights to the simulation

Using the intersection widget, you will add *when* statements to connect the lights to the real simulation. Once the connection is made, you will simulate the traffic light controller and watch the lights change.

We'll use VSIM *when* statements to condition the simulation to call our Tcl program when a desired simulation condition happens.

For our example, the desired condition is the state of the lights. Whenever the state of the light in the simulation changes, we want to change the color of the light on the screen.

**4** Load the VHDL libraries you compiled in preparation for these examples using this command at the Model*Sim* prompt:

```

vsim tb_traffic

```

Be sure you invoke this command before the start of the connect\_lights procedure, if you don't load the libraries, you won't have a design to simulate.

**5** Connect the lights to the simulation with this command and procedure:

```

source lights.tcl

connect_lights

```

Try running the simulation now; select either run button on the intersection. Select **Break** if you used the **Run Forever** button. Notice how the Source window opens and indicates the next line to be executed. (If the simulator is not evaluating an executable process when the break occurs, the Source window will not open.) Only the East/West lights are working. You can make both lights work by editing the *lights.tcl* file.

6 Edit *lights.tcl* with the **notepad** to add a *when* statement for the North/South light.

notepad lights.tcl

You need to add this because the current statement is for the East/West light only. You'll find the solution commented. (Remember to change the read-only status of the file so you can edit it.)

You'll find the code commented-out toward the end of the file (try Edit >Find again).

7 After you have made the changes, reload and run the simulation again.

```

source lights.tcl

connect_lights

```

Both lights are now working.

**Note:** Remember, if you need to return to the original Tcl files (maybe you've edited the file and it doesn't work right) you'll find the files in the *tcl\_tutorial/originals* directory.

### Add widgets to display simulation information

Running the lights may be interesting, but not very useful - let's add some displays that will tell us what's happening to the cars at the intersection.

Now you will add queue widgets to display the sum of the length of each pair of queues as we simulate.

8 The East/West widget for displaying the total East/West queue length is already provided. Let's edit the source to add a display for the North/South direction. Use the **notepad**:

```

notepad queues.tcl

```

The solution is commented out in queues.tcl.

The Queue Display widget consists of an enclosing frame with two label widgets. The first label is a simple text string. The second label is the value of the queue length. The text in the second label will be updated whenever the queue lengths change.

**9** After you have added your North/South widget, run your program by invoking this command:

```

source queues.tcl

draw_queues

```

According to the traffic indicators, the cars are leaving the intersection at the same rate. That seems fair, but if you are designing an intersection that responds to the traffic flow into the intersection you might want to change the light cycles. Perhaps one of the directions has more incoming traffic than the other.

Adding controls, in the form of scale widgets, allows you to quickly change the assumptions about traffic flow into the intersection.

#### Add "scale" widgets to control the simulation

Next you will add Tk "scale" widgets that will control the arrival rates and the length of the lights.

**10** The East/West widget for controlling the East/West queue inter-arrival time is provided. You'll edit the source code to add controls for the North/South direction. Use this command:

notepad controls.tcl

You can remove the comments in the code to make this change.

Similarly, add the North/South widget for controlling the length of the lights. The East/ West widget for light control is provided. (You can remove the comments in the code to make this change as well.)

These control widgets are implemented using the Tk "scale" widgets, enclosed in a frame.

When the value of the scale widget changes, it calls the command specified with the **-command** option on each scale.

**11** After you have added your North/South widgets, run your program with this command:

```

source controls.tcl

draw_controls

```

Now you have a complete intersection interface. Try the run buttons and the slider scales. You can also view the simulation with Model*Sim*'s GUI. Check the Source window to view the VHDL files, and add signals to a Wave window

(**add wave** \*). You can also change the run length in the Main window. Try using the Run buttons in the Main window and the intersection window.

Keep the intersection simulation running to complete the next example. If you want to recreate the final intersection environment quickly, invoke these commands from the ModelSim prompt (after "Initial setup" (6-54)):

```

cd solutions

vmap work work

do traffic.do

```

# Example 4 - Draw a state machine that represents the simulation

In this final example you will draw a state machine representing the simulation, and connect it to the state signal inside the traffic light controller. Each transition that the controller makes is displayed as it happens.

The intersection environment from the previous example needs to be running for this example. To get it running quickly, invoke these commands from the Model*Sim* prompt (after "Initial setup" (6-54)).

```

cd solutions

do traffic.do

```

**1** Run the state machine with these commands:

```

source state-machine.tcl

draw_state_machine

```

Let's make some changes to the light colors and transition arrows.

**2** Open the source file with this command:

notepad state-machine.tcl

Note the "ModelSim EXAMPLE part 1" comments in the file. You can change "both\_red" state coordinates from x = 125 and y = 50 to any coordinates. (You may need to uncheck the **read only** selection in the Edit menu before making changes.)

**3** Note the "ModelSim EXAMPLE part 2" comments in the file. You can change the transition arrow coordinates to correspond with the new "both\_red" state coordinates.

- 4 Note the "ModelSim EXAMPLE part 3" comments in the file. Change the active color from "black" to "purple".

- **5** Reuse the original commands when you're ready to run the state machine (remember, to copy a previous command to the current command line, select the previous Model*Sim* prompt):

```

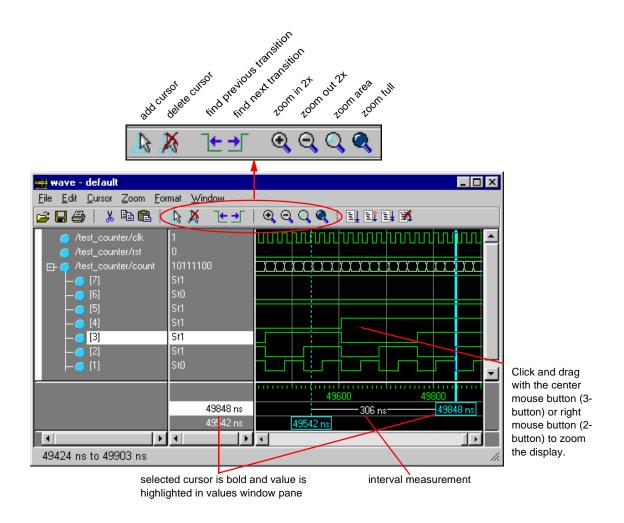

source state-machine.tcl