**User Manual**

# DSP6000A Digital Studio-Transmitter Link

Doc. 602-11157-01 R: A

Released August 1997

111 Castilian Drive Santa Barbara, CA 93117-3093 U.S.A. Phone: 805-968-9621 Fax: 805-685-9638 http://www.moseleysb.com

#### **FCC Notice**

Note: This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

Any external data or audio connection to this equipment must use shielded cables.

#### DSP6000A User Manual Document #602-11157-01 R: A Revision Configuration:

| SECTION           | DWG           | REV | ECO     | REVISED/<br>RELEASED |

|-------------------|---------------|-----|---------|----------------------|

| Table of Contents | 602-11157-TOC | A   | DCO1049 | August 1997          |

| 1                 | 602-11157-11  | A   | DCO1049 | August 1997          |

| 2                 | 602-11157-21  | A   | DCO1049 | August 1997          |

| 3                 | 602-11157-31  | А   | DCO1049 | August 1997          |

| 4                 | 602-11157-41  | A   | DCO1049 | August 1997          |

| 5                 | 602-11157-51  | A   | DCO1049 | August 1997          |

| 6                 | 602-11157-61  | A   | DCO1049 | August 1997          |

| 7                 | 602-11157-71  | A   | DCO1049 | August 1997          |

| Appendix          | 602-11157-AA1 | A   | DCO1049 | August 1997          |

# **Table of Contents**

| Section      | Contents                                              | Page        |

|--------------|-------------------------------------------------------|-------------|

|              | Table of Contents                                     | i           |

|              | List of Figures                                       | v           |

|              | List of Tables                                        | vii         |

|              | Glossary                                              | x           |

|              | About this Manual                                     | xii         |

| 1            | System Characteristics                                |             |

| 1.1          | Introduction                                          | 1-2         |

| 1.2          | System Features                                       | 1-3         |

| 1.2          | DSP6000A System                                       | 1-4         |

| 1.3.1        | DSP6000A System Specifications                        | 1-4         |

| 1.3.2        | DSP6000E Encoder Specifications                       | 1-5         |

| 1.3.3        | DSP6000D Decoder Specifications                       | 1-6         |

| 1.4          | System Description                                    | 1-7         |

| 1.4.1        | DSP6000E Encoder Description                          | 1-7         |

| 1.4.2        | DSP6000D Decoder Description                          | 1-11        |

| 2            | Installation                                          |             |

| 2.1          | Unpacking                                             | 2-2         |

| 2.2          | Power                                                 | 2-2         |

| 2.2.1        | AC Line Voltage Selection                             | 2-2         |

| 2.2.2        | DC Option Fuses                                       | 2-4         |

| 2.3          | Pre-Installation Checkout                             | 2-5         |

| 2.3.1        | Checkout of Encoder/Decoder Only                      | 2-5         |

| 2.3.2        | Checkout of System — Encoder/STL/Decoder              | 2-7         |

| 2.4          | Rack Installation                                     | 2-9<br>2-10 |

| 2.5          | STL Installation                                      | 2-10        |

| 2.5.1        | Encoder                                               | 2-10        |

| 2.5.2        | Decoder                                               | 2-12        |

| 2.5.3        | Air-Chain Processing                                  | 2-14        |

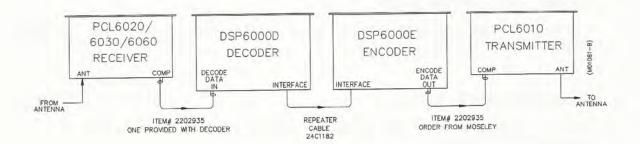

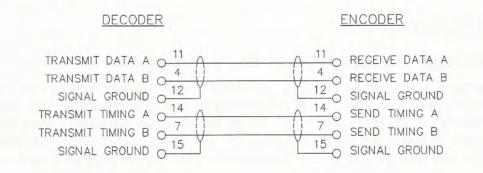

| 2.5.4        | Repeater                                              | 2-18        |

| 2.6          | Fractional T1 (FT1) Installation                      | 2-22        |

| 2.7<br>2.7.1 | Data Communications<br>Data Rate and Format Selection | 2-22        |

| Section | Contents                                | Page |

|---------|-----------------------------------------|------|

| 2.7.2   | Remote Control Communication            | 2-23 |

| 2.7.2.1 | Subcarrier Communications               | 2-23 |

| 2.7.2.2 | FSK Communications                      | 2-23 |

| 2.7.2.3 | RS-232 Communications                   | 2-23 |

| 2.8     | Retrofit STL Installation               | 2-31 |

| 2.8.1   | PCL6010 Transmitter                     | 2-31 |

| 2.8.2   | PCL6020/6030/6060 Receiver              | 2-32 |

| 2.8.3   | PCL606 Transmitter, Mono                | 2-36 |

| 2.8.4   | PCL606 Receiver, Mono                   | 2-38 |

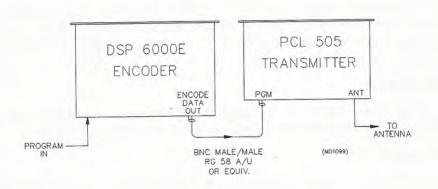

| 2.8.5   | PCL606/C Transmitter, Composite         | 2-40 |

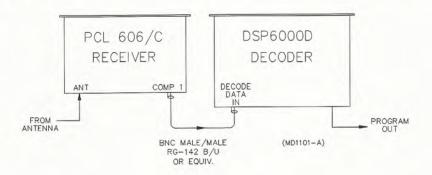

| 2.8.6   | PCL606/C Receiver, Composite            | 2-41 |

| 2.8.7   | PCL505 Transmitter, Composite           | 2-43 |

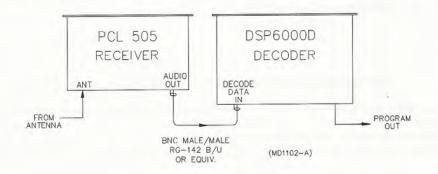

| 2.8.8   | PCL505 Receiver, Composite              | 2-44 |

| 2.8.9   | Other Radios                            | 2-45 |

| 2.8.10  | Retrofit Repeater Installation with STL | 2-46 |

| 3       | Operation                               |      |

| 3.1     | Encoder Front Panel                     | 3-2  |

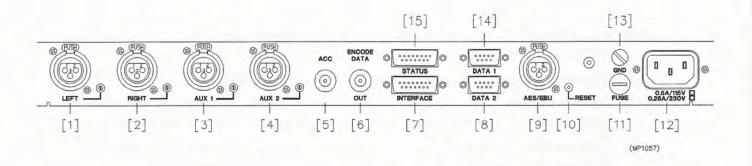

| 3.2     | Encoder Back Panel                      | 3-3  |

| 3.3     | Encoder Pin Assignments                 | 3-4  |

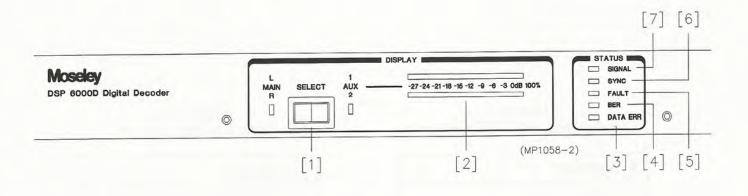

| 3.4     | Decoder Front Panel                     | 3-6  |

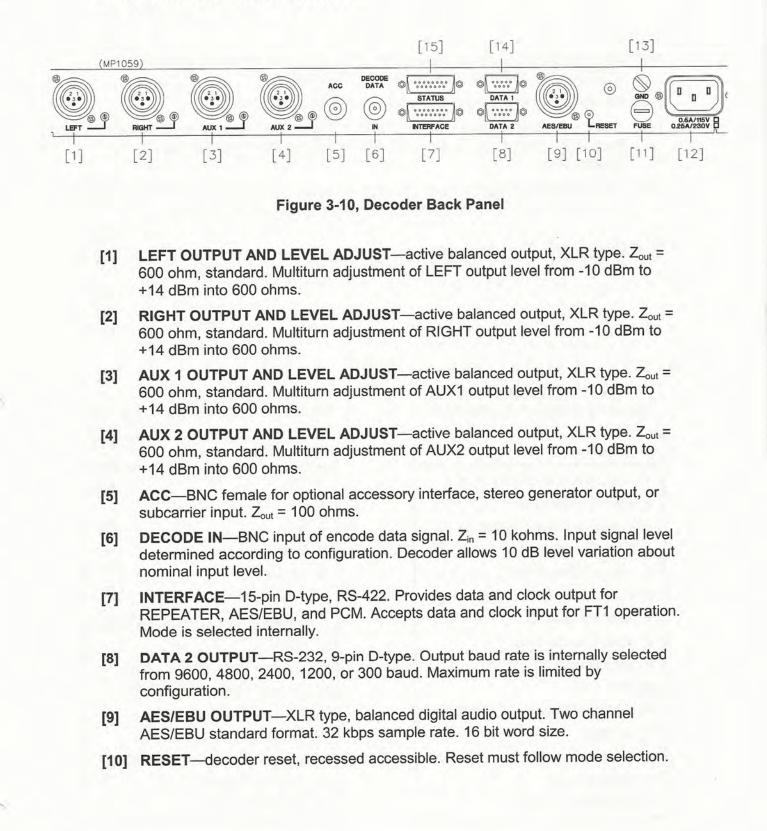

| 3.5     | Decoder Back Panel                      | 3-7  |

| 3.6     | Decoder Pin Assignments                 | 3-8  |

| 4       | Customer Service Information            |      |

| 4.1     | Introduction                            | 4-2  |

| 4.2     | Technical Consultation                  | 4-2  |

| 4.3     | Factory Service                         | 4-3  |

| 1.4     | Field Repair                            | 4-4  |

| 5       | Configuration                           |      |

| 5.1     | Introduction                            | 5-2  |

| 5.2     | Encoder Channel Configuration           | 5-3  |

| 5.3     | Encoder Alignment                       | 5-5  |

| 5.4     | Encoder Interface Configuration         | 5-9  |

| 5.4.1   | Interface Mode 0 — PROGRAM, FT1 SEND    | 5-10 |

| .4.2    | Interface Mode 1 — REPEATER             | 5-11 |

| Section            | Contents                                                       | Page         |

|--------------------|----------------------------------------------------------------|--------------|

| 5.4.3              | Interface Mode 2 — AES/EBU, FT1 SEND                           | 5-12         |

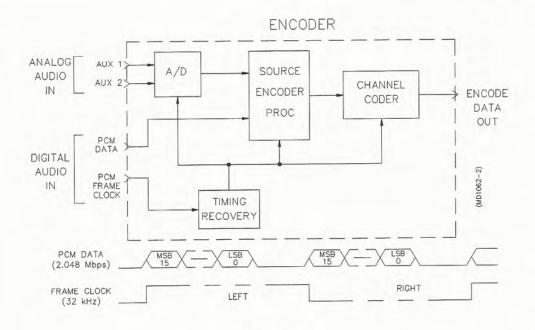

| 5.4.4              | Interface Mode 3 — PCM                                         | 5-13         |

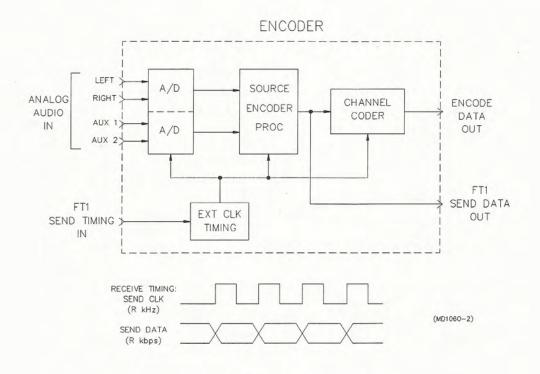

| 5.4.5              | Interface Mode 4 — PROGRAM, FT1 RECEIVE                        | 5-14         |

| 5.4.6              | Interface Mode 5 — AES/EBU, FT1 RECEIVE                        | 5-15         |

| 5.5                | Decoder Channel Configuration                                  | 5-16         |

| 5.6                | Decoder Alignment                                              | 5-18         |

| 5.6.1              | Decoder Alignment — Standard Efficiency                        | 5-21         |

| 5.6.2              | Decoder Alignment — High Efficiency with Pilot                 | 5-23         |

| 5.6.3              | Decoder Alignment — Standard Efficiency with Pilot             | 5-25         |

| 5.6.4              | Decoder Alignment — FT1                                        | 5-27<br>5-27 |

| 5.7                | Decoder Interface Configuration                                | 5-27         |

| 5.7.1              | Interface Mode 0 — PROGRAM                                     | 5-29         |

| 5.7.2              | Interface Mode 1 — REPEATER                                    | 5-30         |

| 5.7.3              | Interface Mode 2 — AES/EBU                                     | 5-31         |

| 5.7.4              | Interface Mode 3 — PCM                                         | 5-32         |

| 5.7.5              | STL Interface Mode                                             | 5-32         |

| 5.7.6              | FT1 Interface Mode                                             | 5-33         |

| 5.8                | Changing Transmission Efficiency<br>Data Channel Configuration | 5-33         |

| 5.9<br>5.9.1       | DATA 1 (RS-232)                                                | 5-35         |

| 5.9.1              | DATA 2 (RS-232)                                                | 5-37         |

| 5.10               | BER Threshold Selection                                        | 5-38         |

| 5.10               | Automatic Audio Mute                                           | 5-39         |

| 5.12               | Scrambler Disable                                              | 5-39         |

| 5.13               | Configuration Programming Summary Tables                       | 5-40         |

| 6                  | Troubleshooting and Testing                                    |              |

| 6.1                | Audio Measurements                                             | 6-2          |

| 6.1.1              | Signal-to-Noise Ratio                                          | 6-2          |

| 6.1.2              | Distortion/SINAD                                               | 6-4          |

| 6.2                | Troubleshooting                                                | 6-4          |

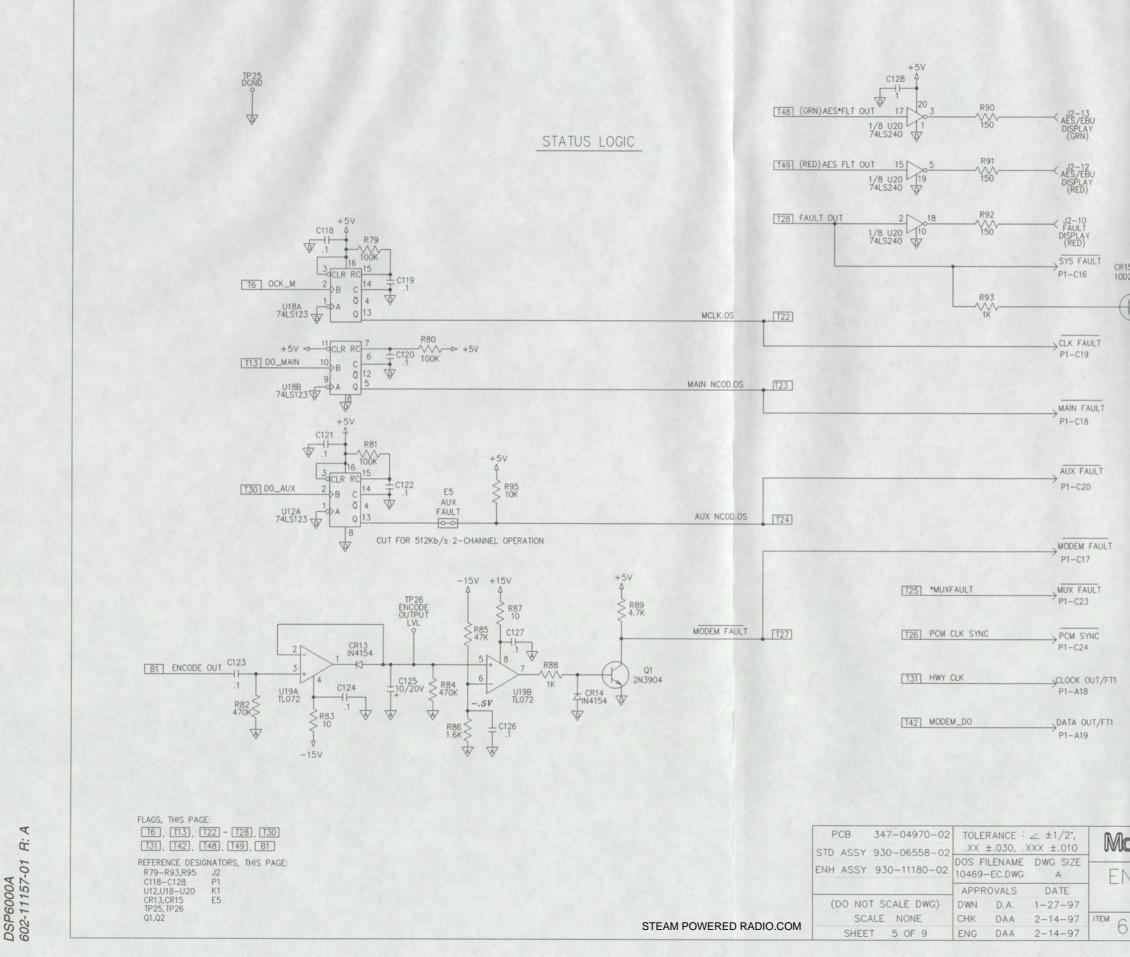

| 6.2.1              | Encoder STATUS Output                                          | 6-5          |

| 6.2.2              | Decoder STATUS Output                                          | 6-7<br>6-9   |

| 6.3                | Board Alignment Information                                    | 6-9          |

| 6.3.1              | Encoder                                                        | 6-9          |

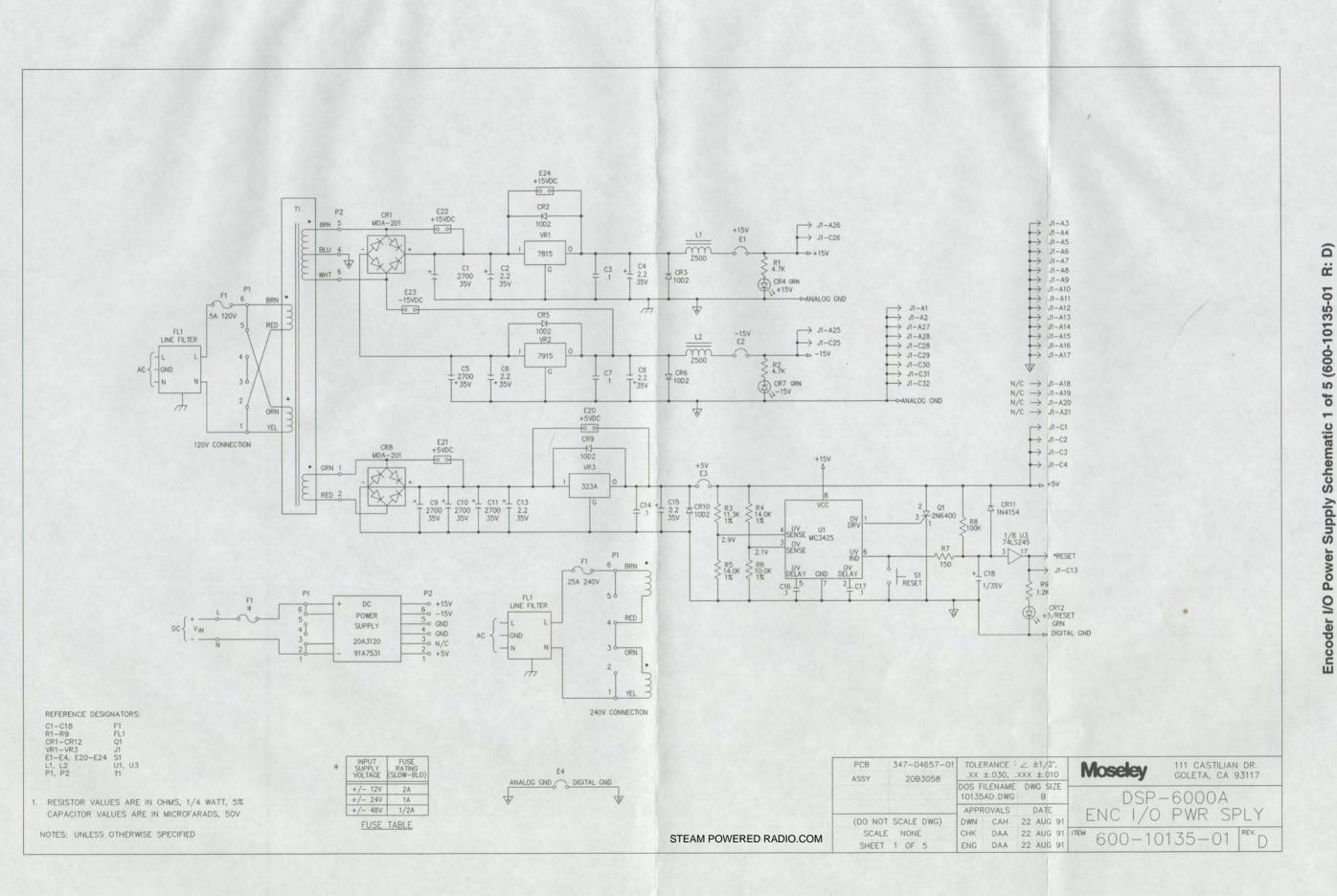

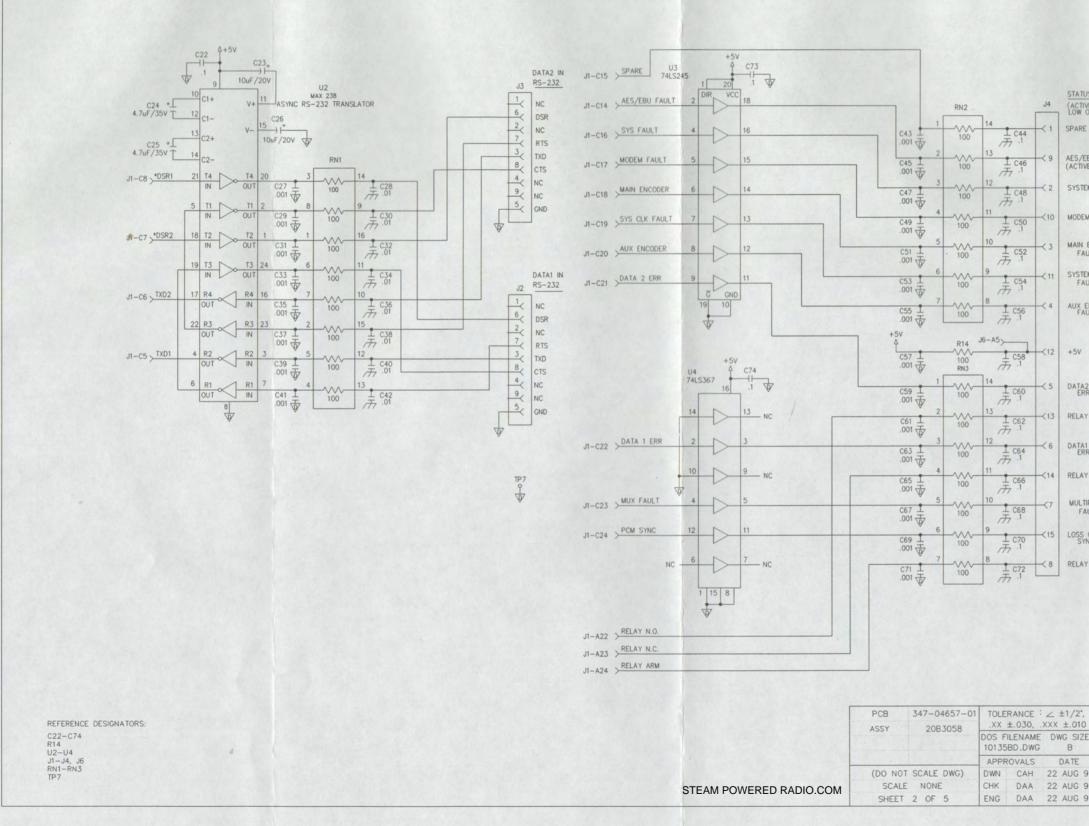

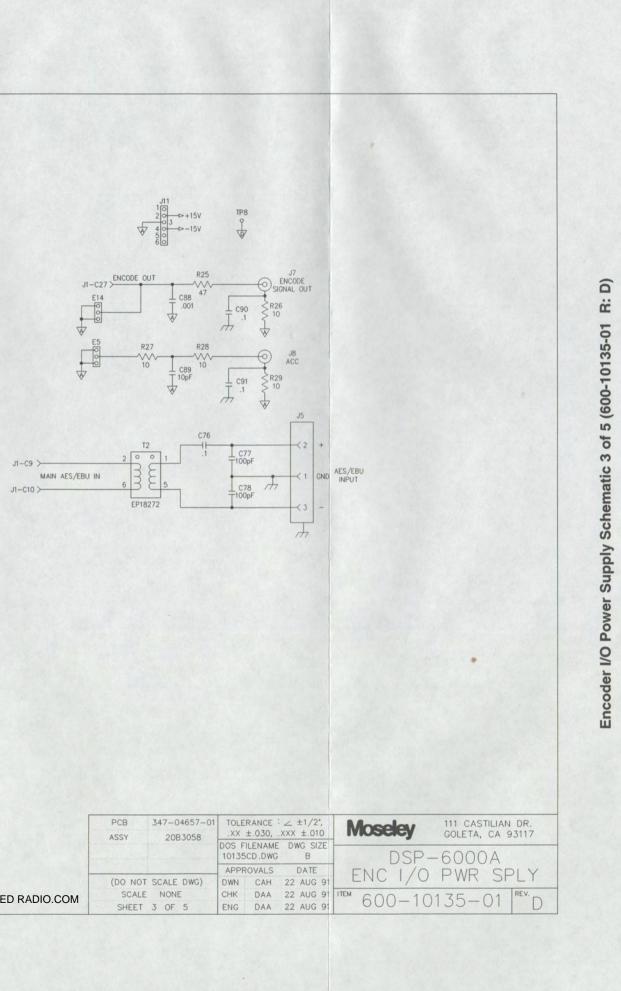

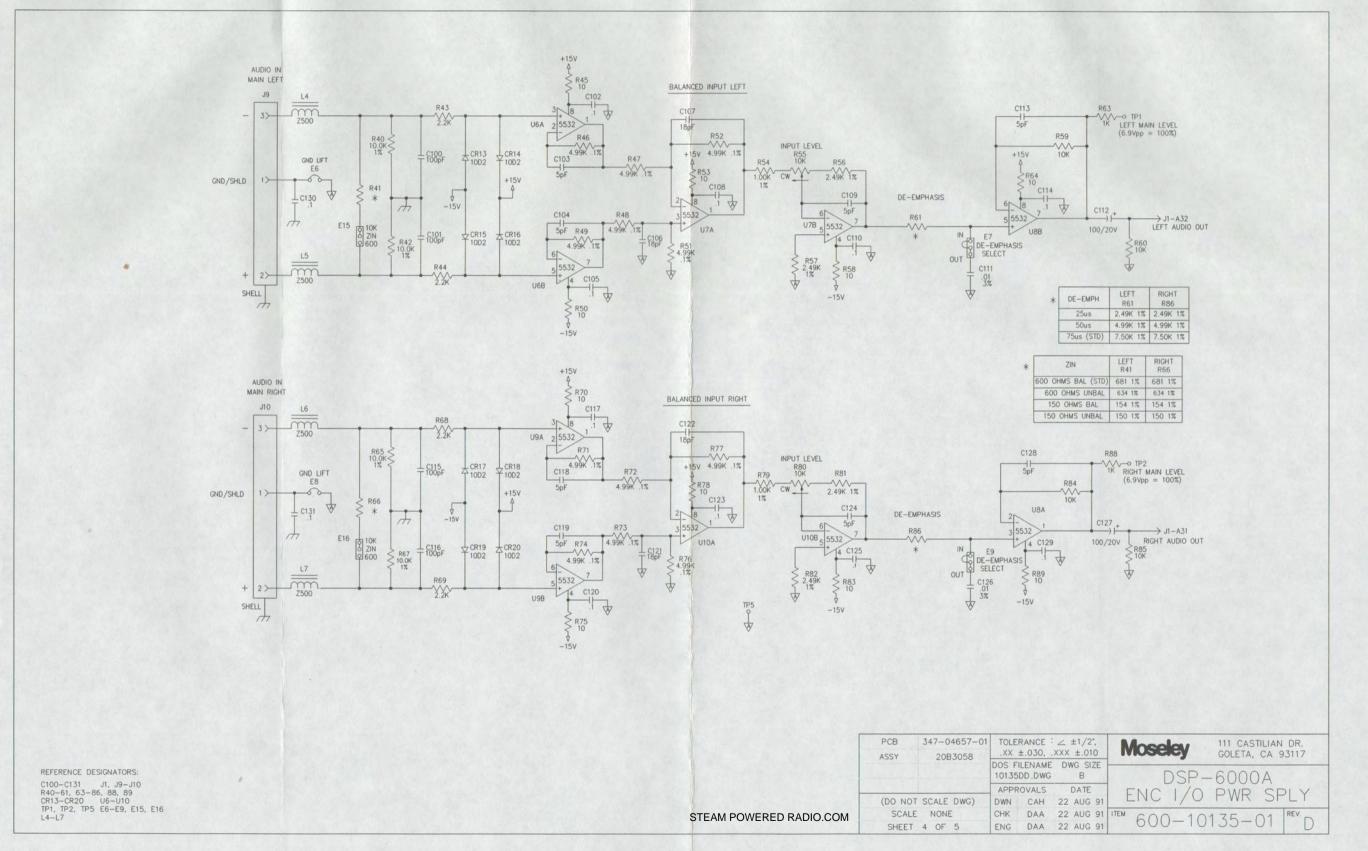

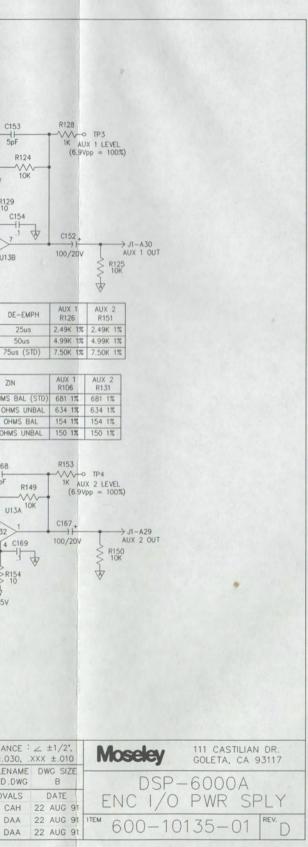

| 6.3.1.1            | Encoder I/O Power Supply Board                                 | 6-12         |

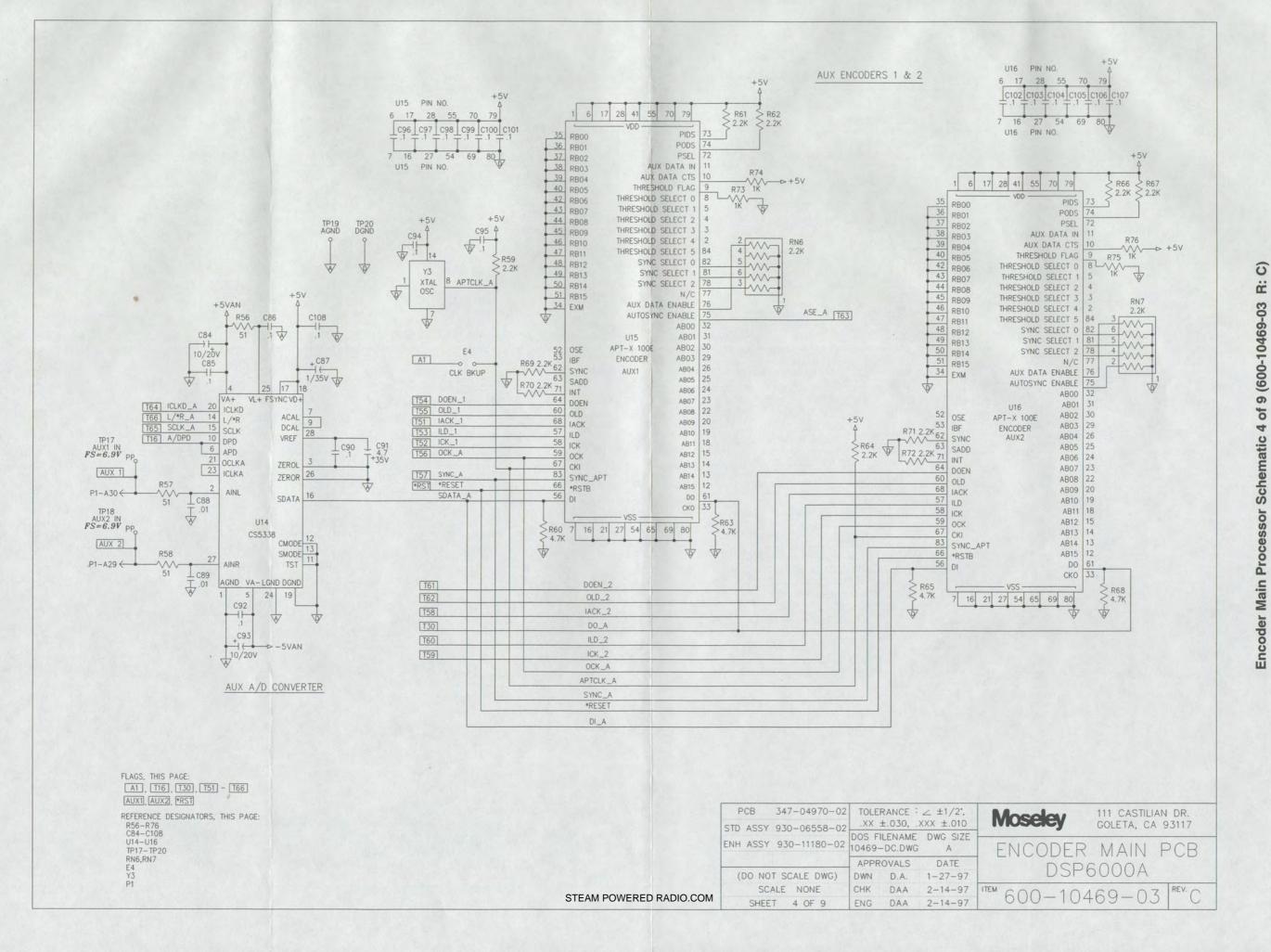

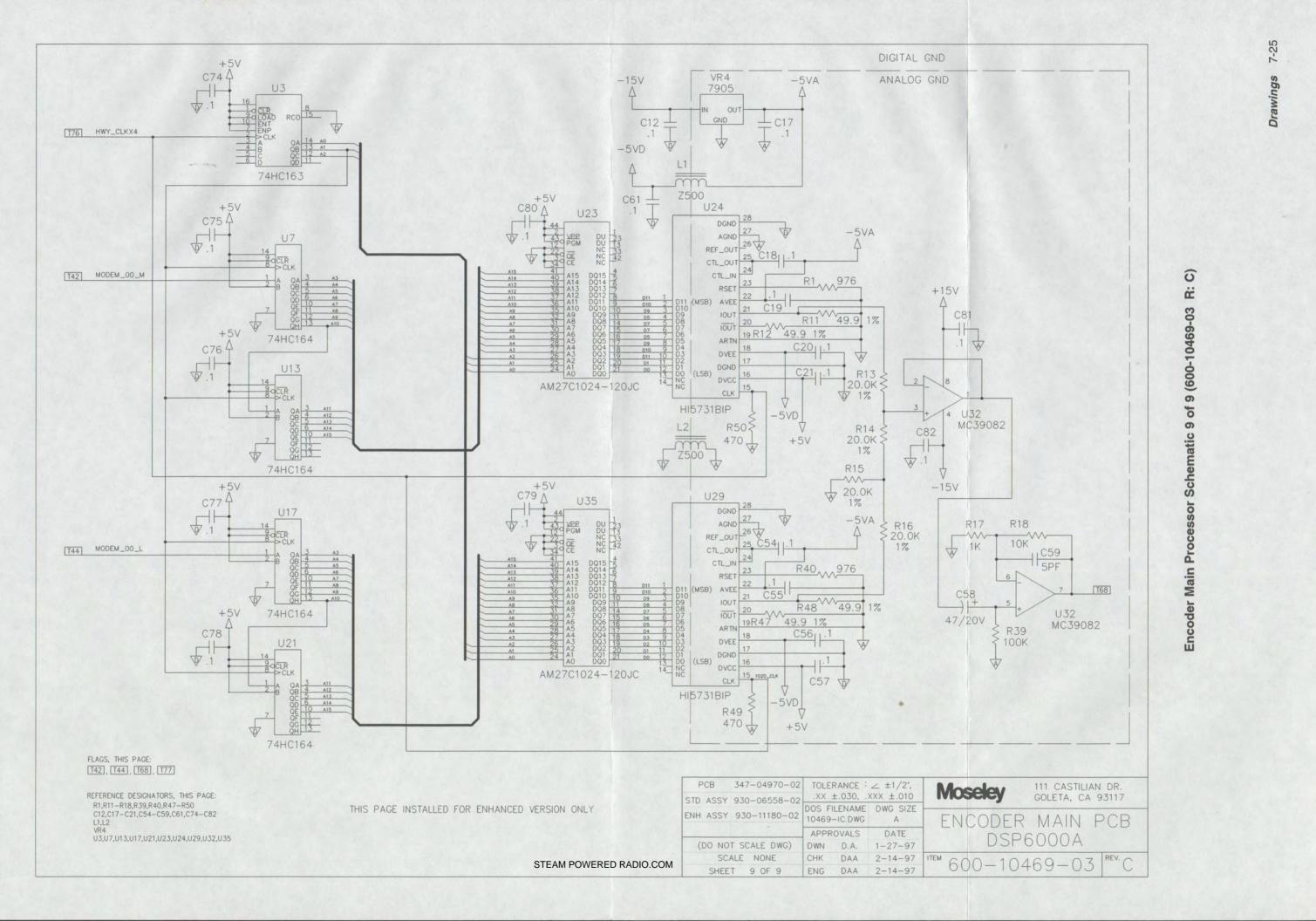

| 6.3.1.2            | Encoder Main Processor Board                                   | 6-15         |

| 6.3.1.3            | Encoder Display Board                                          | 6-16         |

| 6.3.2              | Decoder<br>Decoder I/O Power Supply Board                      | 6-16         |

| 6.3.2.1<br>6.3.2.2 | Decoder I/O Power Supply Board<br>Decoder Main Processor       | 6-19         |

| Section | Contents                                 | Page |

|---------|------------------------------------------|------|

| 6.3.2.3 | Decoder Display Board                    | 6-24 |

| 6.4     | Test Equipment                           | 6-26 |

| 6.5     | Test Fixture Diagrams                    | 6-27 |

| 7       | Schematic and Assembly Drawings Appendix |      |

| A.1     | Path Evaluation Information              | A-2  |

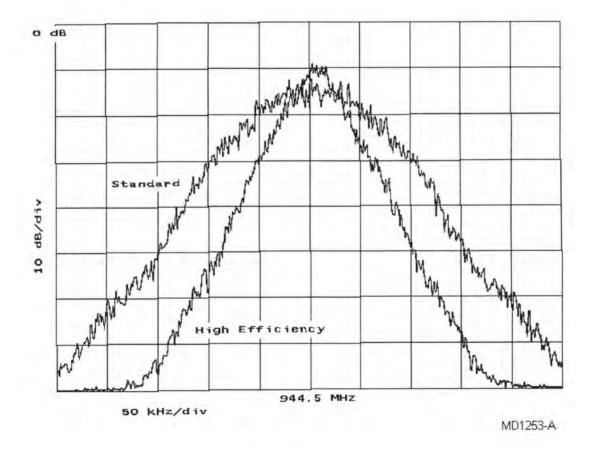

| A.2     | Spectral Efficiency                      | A-2  |

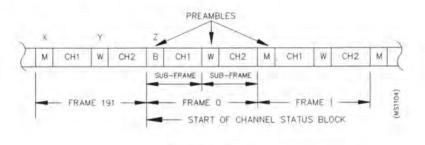

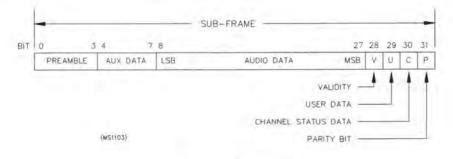

| A.3     | AES/EBU Digital Audio Data Format        | A-5  |

| A.3.1   | AES/EBU Standard                         | A-5  |

| A.3.2   | DSP6000A AES/EBU Output                  | A-7  |

# List of Figures

| Figure         | Title                                                        | Page        |

|----------------|--------------------------------------------------------------|-------------|

| 1-1            | DSP6000A Digital Studio-Transmitter Link (DSTL) System       | 1-2         |

| 1-2            | DSP6000A Encoder Block and Level Diagram (92A1336 R: A)      | 1-10a       |

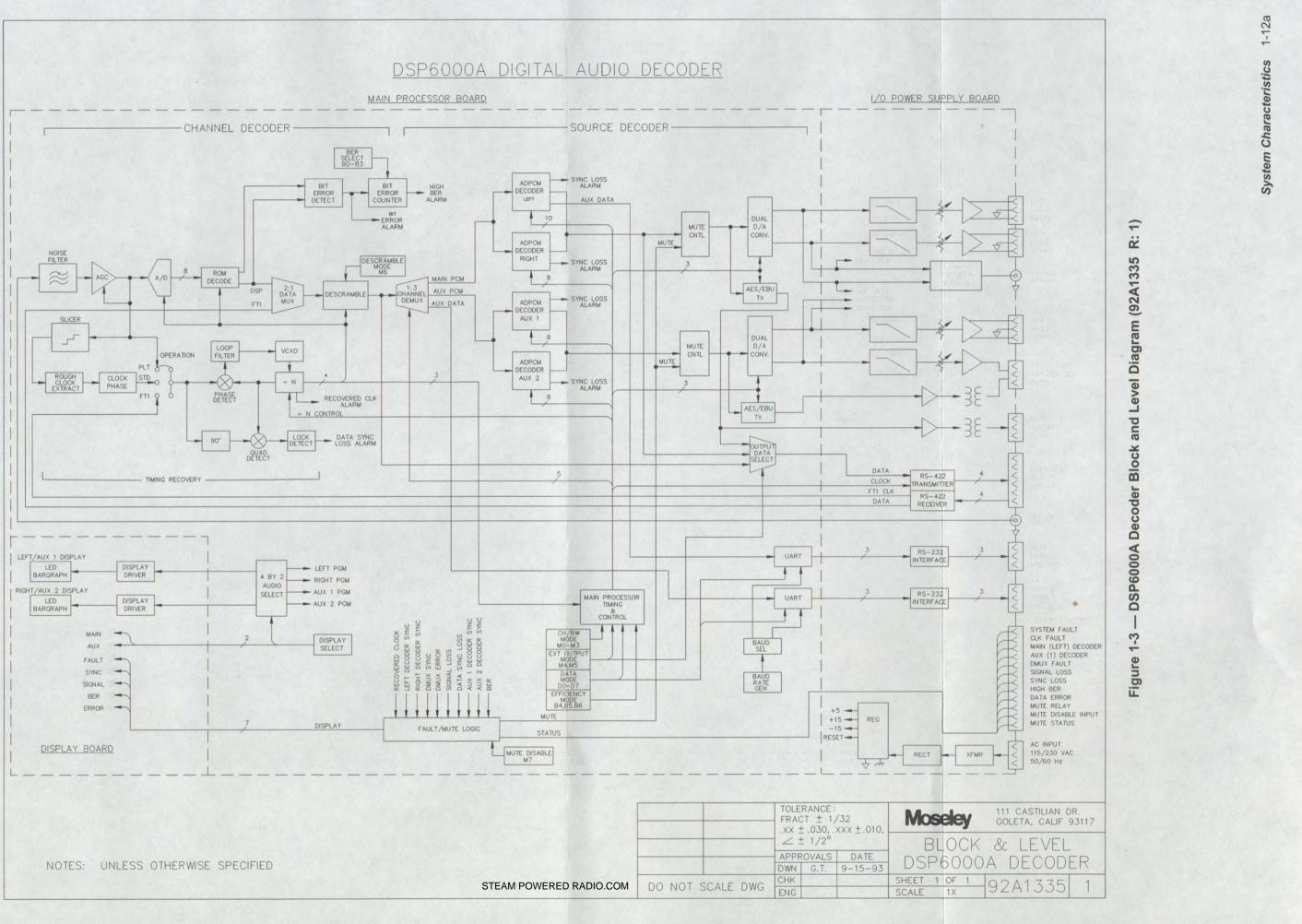

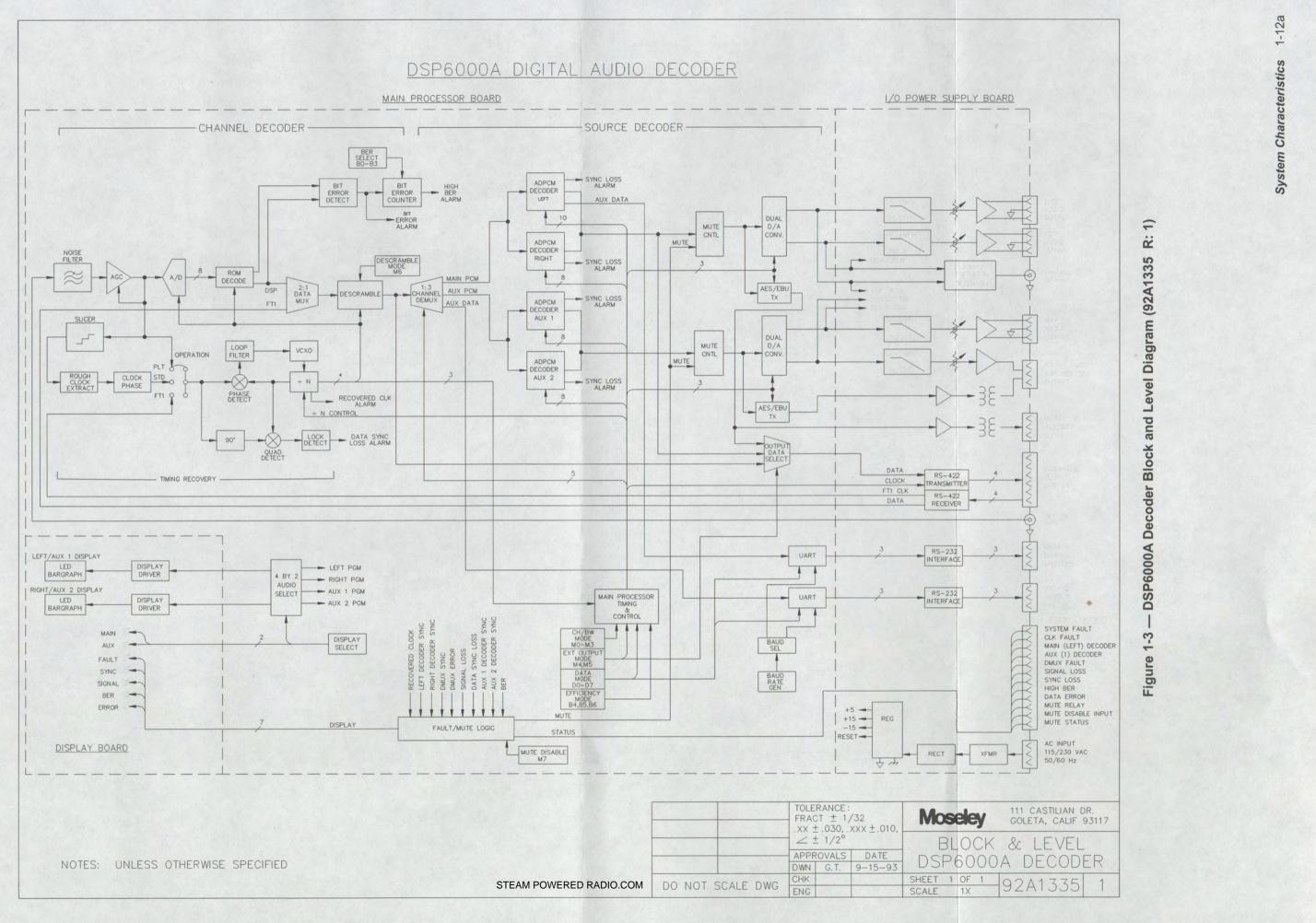

| 1-3            | DSP6000A Decoder Block and Level Diagram (92A1335 R: 1)      | 1-12a       |

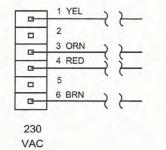

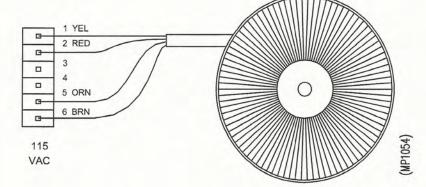

| 2-1            | Transformer AC Wiring detail                                 | 2-3         |

| 2-2            | Bench Test Setup for Encoder/Decoder Only                    | 2-4         |

| 2-3            | Bench Test Setup For Digital STL System                      | 2-6<br>2-10 |

| 2-4            | Encoder-to-STL Transmitter Interconnect                      | 2-10        |

| 2-5            | Decoder-to-STL Receiver Interconnect                         | 2-12        |

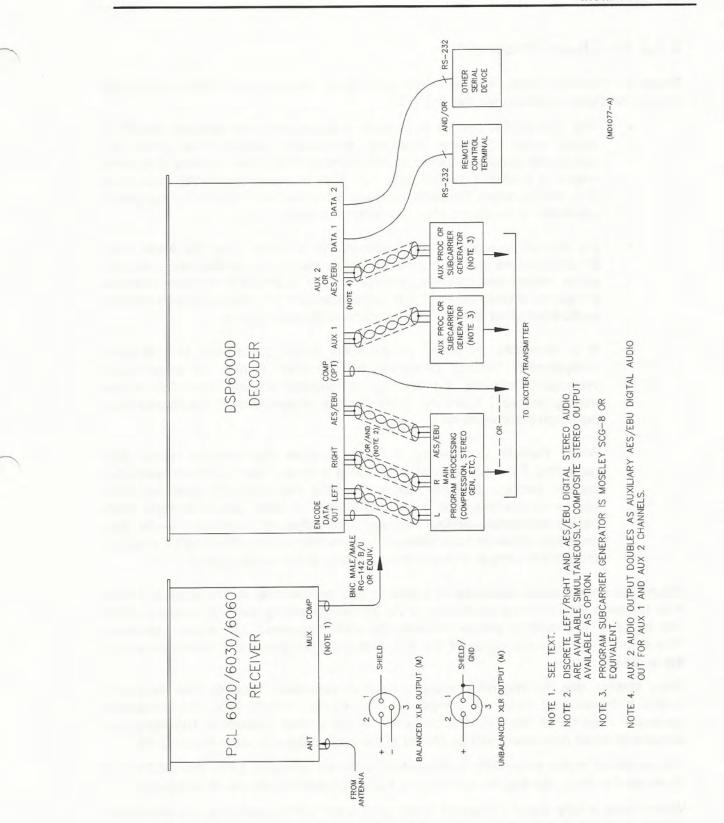

| 2-6            | Air-Chain Processing with the Digital STL                    | 2-15        |

| 2-7            | Digital Repeater Interconnection                             | 2-16        |

| 2-8            | Repeater Cable Detail<br>Fractional T1 Network               | 2-19        |

| 2-9<br>2-10a   | DSP6000A to CSU (RS-449) Interconnection Cable               | 2-20        |

| 2-10a<br>2-10b | DSP6000A to CSU (EIA-530) Interconnection Cable              | 2-20        |

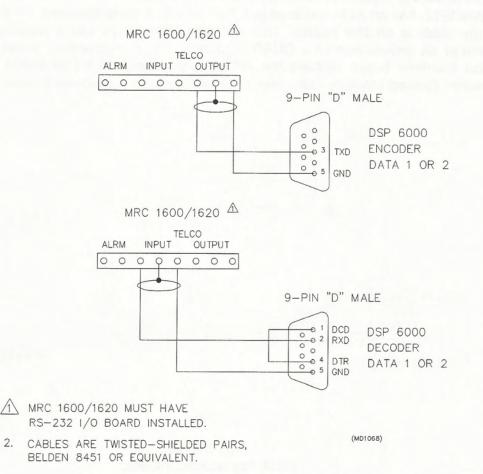

| 2-100          | DSP6000A to MRC1600/1620 Data Connections                    | 2-25        |

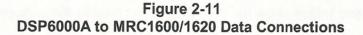

| 2-12           | ACIA Replacement Cable                                       | 2-26        |

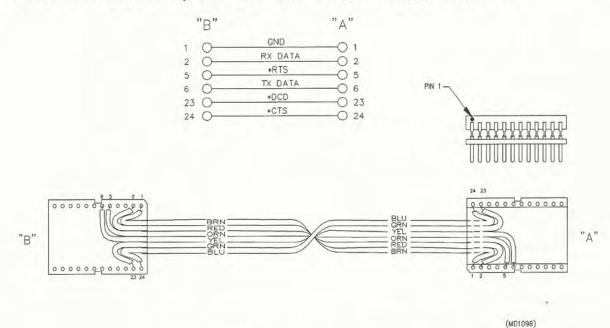

| 2-12           | DSP6000A to MRC-1/2/2S Data Connections                      | 2-27        |

| 2-14           | DSP6000A to MultiTech MT202TD Data Connections               | 2-28        |

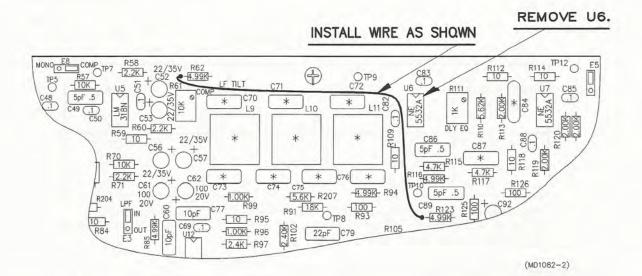

| 2-15           | Modification of Older PCL6020/6030 Audio/PS for Digital STL  |             |

|                | Operation                                                    | 2-33        |

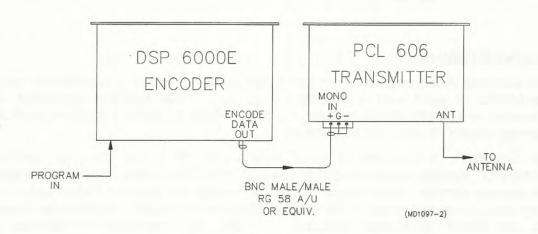

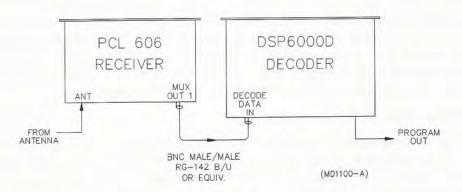

| 2-16           | Encoder-to-PCL606 Interconnection                            | 2-35        |

| 2-17           | Decoder-to-PCL606 Mono Receiver Interconnection              | 2-37        |

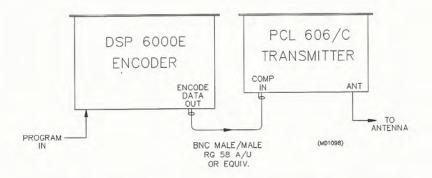

| 2-18           | Encoder-to-PCL606/C Interconnection                          | 2-39        |

| 2-19           | Decoder-to-PCL606 Receiver Composite Interconnection         | 2-40        |

| 2-20           | Encoder-to-PCL505 Composite Interconnection                  | 2-42        |

| 2-21           | Decoder-to-PCL505 Receiver Composite Interconnection         | 2-43        |

| 3-1            | Encoder Front Panel                                          | 3-2         |

| 3-2            | Encoder Back Panel                                           | 3-3         |

| 3-3            | STATUS Output (TTL), DB-15 F                                 | 3-4         |

| 3-4            | INTERFACE I/O (RS-422A), DB-15 F                             | 3-5         |

| 3-5            | XLR Sockets, IEC 268-14, Female                              | 3-5         |

| 3-6            | BNC Sockets, Female                                          | 3-5         |

| 3-7            | DATA1 Input (RS-232), DB-9 F<br>DATA2 Input (RS-232), DB-9 F | 3-5         |

| 3-8            | Decoder Front Panel                                          | 3-6         |

| 3-9<br>3-10    | Decoder Back Panel                                           | 3-7         |

| 3-10           | STATUS Output (TTL), DB-15 F                                 | 3-8         |

| 3-12           | INTERFACE I/O (RS-422A), DB-15 F                             | 3-8         |

| Figure | Title                                                            | Page |

|--------|------------------------------------------------------------------|------|

| 3-13   | XLR Plugs, IEC 268-14, Male                                      | 3-9  |

| 3-14   | BNC Sockets, Female                                              | 3-9  |

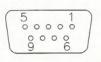

| 3-15   | DATA1 Output (RS-232), DB-9 F                                    | 3-9  |

| 3-16   | DATA2 Output (RS-232), DB-9 F                                    | 3-9  |

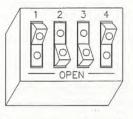

| 5-1    | DIP Switch Setting Definitions                                   | 5-2  |

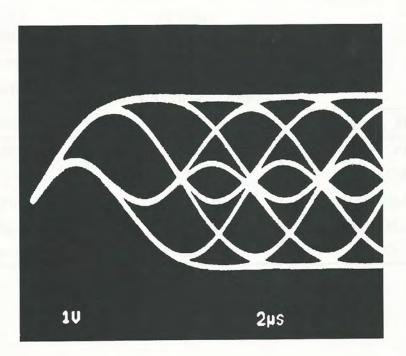

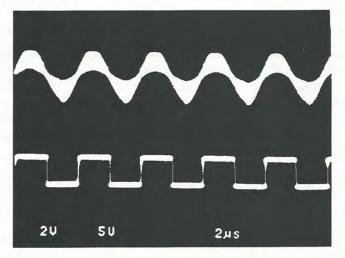

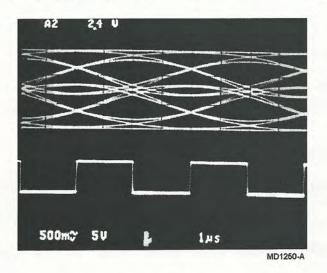

| 5-2    | Encoder Output Waveform ("Eye Pattern")                          | 5-7  |

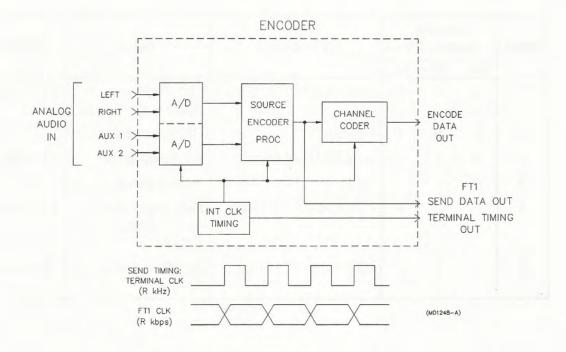

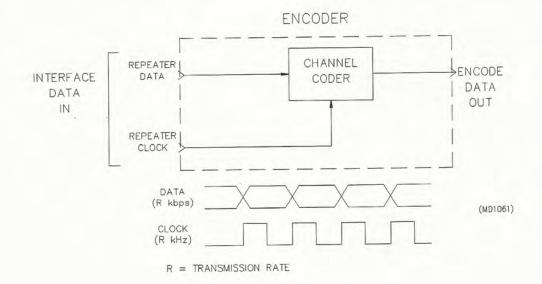

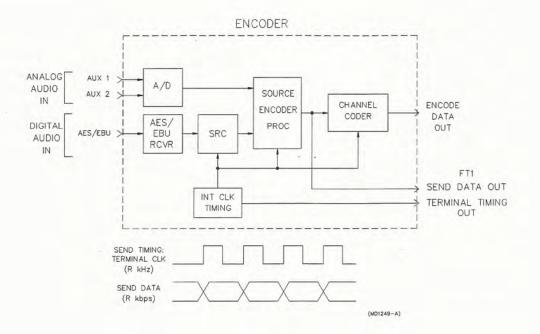

| 5-3    | PROGRAM Input Operation Interface Mode 0                         | 5-10 |

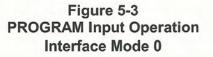

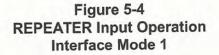

| 5-4    | REPEATER Input Operation Interface Mode 1                        | 5-11 |

| 5-5    | AES/EBU Input Operation Interface Mode 2                         | 5-12 |

| 5-6    | PCM Input Operation Interface Mode 3                             | 5-13 |

| 5-7    | PROGRAM Input Operation with External Timing                     |      |

| 5-8    | Interface Mode 4<br>AES/EBU Input Operation with External Timing | 5-14 |

|        | Interface Mode 5                                                 | 5-15 |

| 5-9    | Test Setup for Decoder Alignment (STL Applications)              | 5-20 |

| 5-10   | Clock Recovery Waveforms at TP10 and TP11                        | 5-22 |

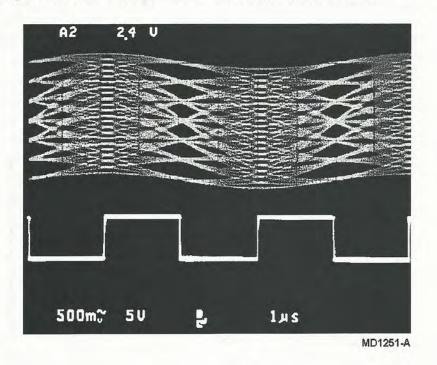

| 5-11   | A/D CLOCK Alignment TP6 with A/D Input TP4,                      |      |

|        | Standard Efficiency                                              | 5-22 |

| 5-12   | A/D CLOCK Alignment TP6 with A/D Input TP4,                      |      |

|        | High Efficiency with Pilot                                       | 5-24 |

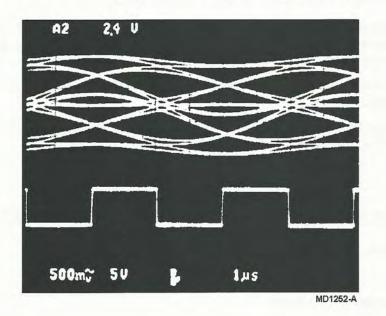

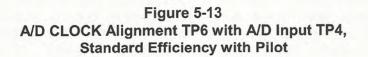

| 5-13   | A/D CLOCK Alignment TP6 with A/D Input TP4,                      |      |

|        | Standard Efficiency with Pilot                                   | 5-26 |

| 5-14   | PROGRAM Output Operation Interface Mode 0                        | 5-28 |

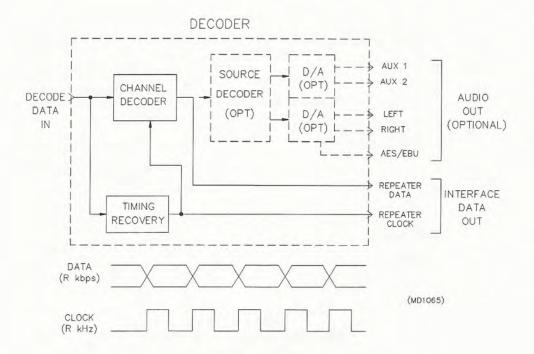

| 5-15   | REPEATER Output Operation Interface Mode 1                       | 5-29 |

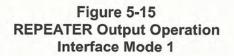

| 5-16   | AES/EBU Output Operation Interface Mode 2                        | 5-30 |

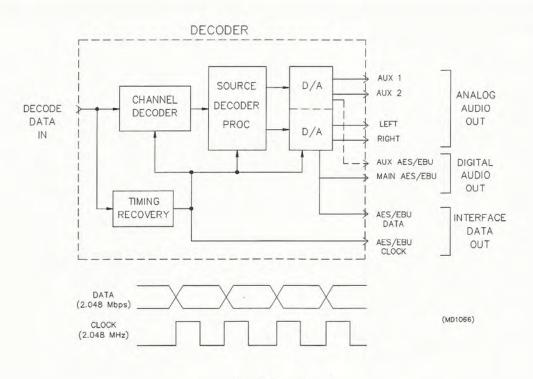

| 5-17   | PCM Output Operation Interface Mode 3                            | 5-31 |

| 5-18   | FT1 Decoder Operation                                            | 5-32 |

| 6-1    | Signal-to-Noise Ratio Equipment Set-up                           | 6-3  |

| 6-2    | Status Test Fixtures                                             | 6-27 |

| 6-3    | RS-232 Test Fixtures                                             | 6-27 |

|        | See Table of Contents for Section 7 Figures                      |      |

| A-1    | DSP6000A Occupied Spectrum                                       | A-4  |

| 4-2    | AES/EBU Standard Frame                                           | A-5  |

| 4-3    | AES/EBU Standard Subframe                                        | A-5  |

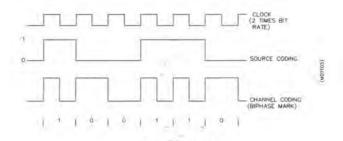

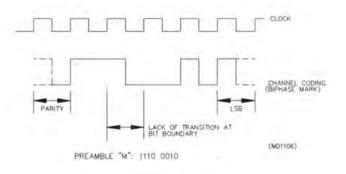

| 4-4    | AES/EBU Standard Coding                                          | A-6  |

| 4-5    | AES/EBU Standard Sync Preamble                                   | A-6  |

# List of Tables

| Table | Title                                                          | Page |

|-------|----------------------------------------------------------------|------|

| 2-1   | Encoder and Decoder AC Fuse Values                             | 2-3  |

| 2-2   | Encoder and Decoder DC Fuse Values                             | 2-4  |

| 2-3   | Channel Programming                                            | 2-17 |

| 2-4   | Setting Encoder Timing                                         | 2-18 |

| 2-4   | Setting Decoder Timing                                         | 2-18 |

| 2-6   | CSU Timing Programming                                         | 2-19 |

| 2-0   | DATA 1 Format                                                  | 2-21 |

| 2-8   | DATA 2 Format                                                  | 2-22 |

| 2-9   | RS-232 Communications for MRC Systems                          | 2-23 |

| 2-10  | Remote Terminal (RT) MRC1600/1620 RS-232 Input                 | 2-24 |

| 2-10  | Control Terminal (CT) MRC1600/1620 RS-232 Output               | 2-24 |

| 2-11  | MRC-1/2/2S (Remote Terminal) RS-232 Input, TELCO               |      |

| 2-12  | (Subcarrier) Output                                            | 2-26 |

| 2-13  | MRC-1/2/2S (Control Terminal) RS-232 Output, TELCO             |      |

| 2-15  | (Subcarrier) Input                                             | 2-27 |

| 2-14  | MT202TD Settings                                               | 2-29 |

| 2-14  | PCL6010 Audio/PS Settings                                      | 2-30 |

| 2-15  | PCL6020/6030 Audio/PS Settings                                 | 2-31 |

| 2-10  | MUX Channel Usage with DSP6000A Standard Efficiency            |      |

| 2-17  | Operation                                                      | 2-32 |

| 2-18  | MUX Channel Usage with DSP6000A High Efficiency Operation      |      |

| 2-10  | MOX Charmer Usage with Der Geografigh Enterently approximation | 2-32 |

| 2-19  | IF Filter Configuration                                        | 2-34 |

| 2-19  | Mono Audio Processor Configuration                             | 2-35 |

| 2-20  | Mono Baseband Processor Configuration                          | 2-37 |

| 2-21  | Double Converter Configuration                                 | 2-40 |

| 2-22  | FM Radio Specifications for DSP6000A Compatibility             | 2-44 |

| 2-23  | Fin Radio Specifications for Der Geoor Company                 |      |

| 5-1   | Encoder Channel Configuration                                  | 5-3  |

| 5-2   | Encoder Channel Components                                     | 5-4  |

| 5-3   | Setting Encoder Transmission Efficiency                        | 5-5  |

| 5-4   | Encoder HDR1 Selection                                         | 5-6  |

| 5-5   | Encoder Output Level to PCL6010 and Transmitter Deviation      | 5-7  |

| 5-6   | Encoder Output Level Conversion for other Transmitters         | 5-8  |

| 5-7   | Encoder Interface Modes                                        | 5-9  |

| 5-8   | Decoder Channel Configuration                                  | 5-16 |

| 5-9   | Decoder Channel Components                                     | 5-17 |

| 5-9   | Setting Decoder Transmission Efficiency                        | 5-18 |

| 5-10  | Decoder HDR1 Selection                                         | 5-19 |

| 5-12  | Decoder HDR2 Selection                                         | 5-19 |

| 5-12  |                                                                |      |

| 5-13  | Decoder Input Level — Standard Efficiency                      | 5-21 |

| Table | Title                                              | Page |

|-------|----------------------------------------------------|------|

| 5-14  | Decoder Input Level — High Efficiency              | 5-23 |

| 5-15  | Decoder Interface Modes                            | 5-27 |

| 5-16  | Data Channel Baud Rate                             | 5-34 |

| 5-17  | Data Channel Configuration                         | 5-34 |

| 5-18  | Data Channel Test Modes                            | 5-35 |

| 5-19  | Data Channel 1 Baud Selection                      | 5-36 |

| 5-20  | Data 1 Format Selection                            | 5-36 |

| 5-21  | Data Channel 2 Baud Selection                      | 5-37 |

| 5-22  | Data 2 Format Selection                            | 5-37 |

| 5-23  | Decoder BER Configuration                          | 5-38 |

| 5-24  | Setting Decoder Automatic Audio Mute               | 5-39 |

| 5-25  | Scrambler Mode Selection                           | 5-39 |

| 5-26  | DSP6000E Encoder DIP Switch Configuration Settings | 5-40 |

| 5-27  | DSP6000D Decoder DIP Switch Configuration Settings | 5-41 |

| 6-1   | Encoder STATUS Pin Descriptions                    | 6-5  |

| 6-2   | Encoder STATUS Output Validity                     | 6-6  |

| 6-3   | Decoder STATUS Pin Descriptions                    | 6-7  |

| 6-4   | Decoder STATUS Output Validity                     | 6-8  |

| 6-5   | Power Supply Section                               | 6-9  |

| 6-6   | Main Audio Section                                 | 6-10 |

| 6-7   | Aux Audio Section                                  | 6-11 |

| 6-8   | External Sync Section                              | 6-12 |

| 6-9   | Channel Encoder Section                            | 6-13 |

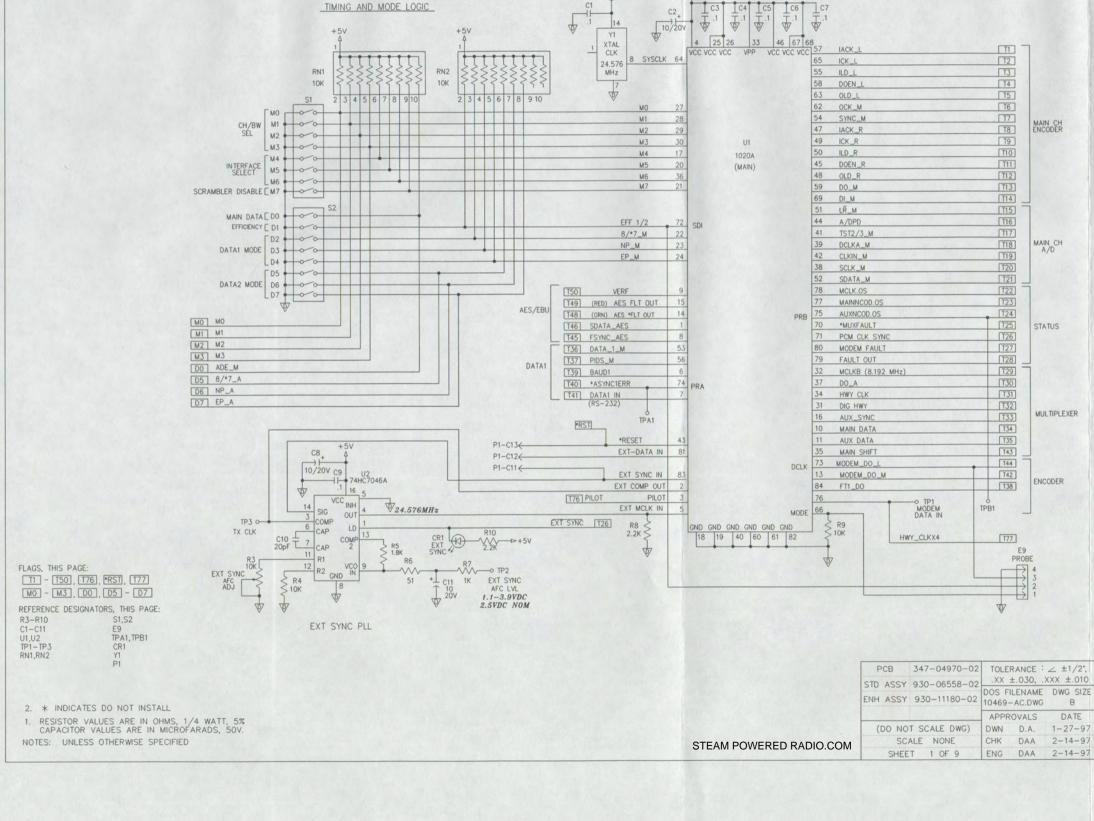

| 6-10  | Timing and Mode Control                            | 6-13 |

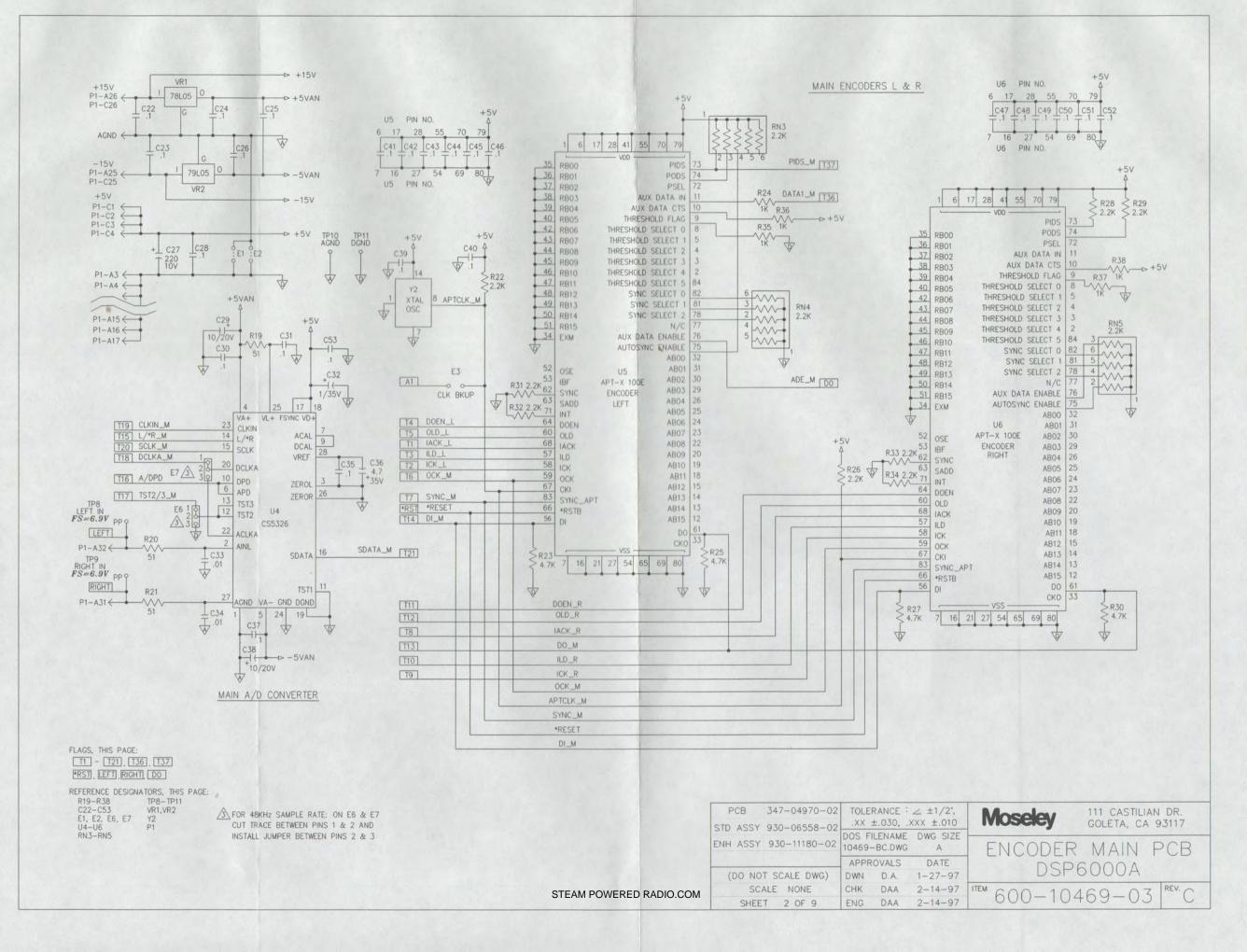

| 6-11  | Main Encoder Section                               | 6-13 |

| 6-12  | Aux Encoder Section                                | 6-14 |

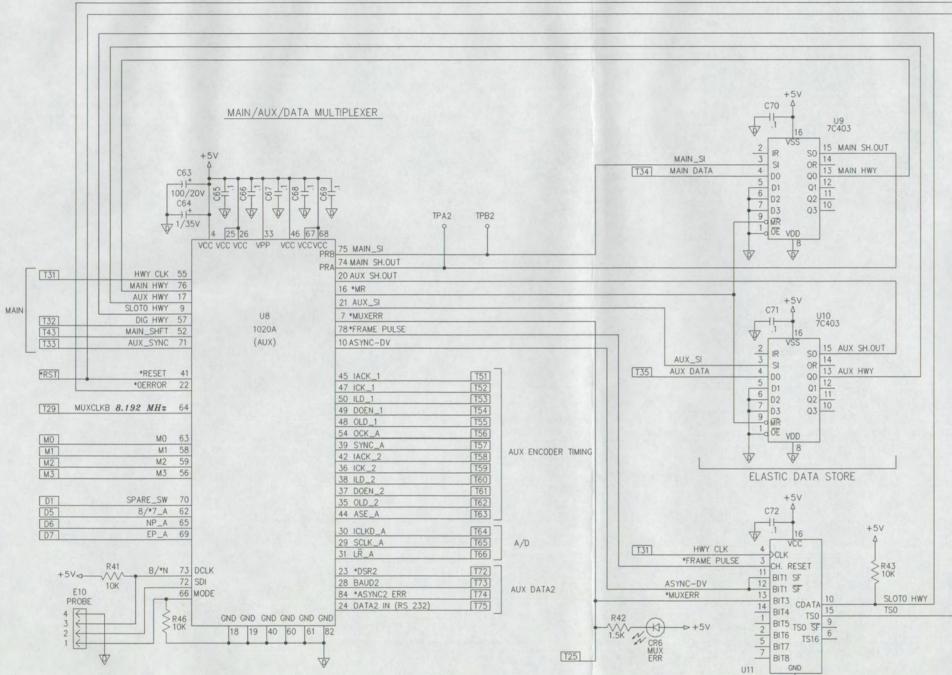

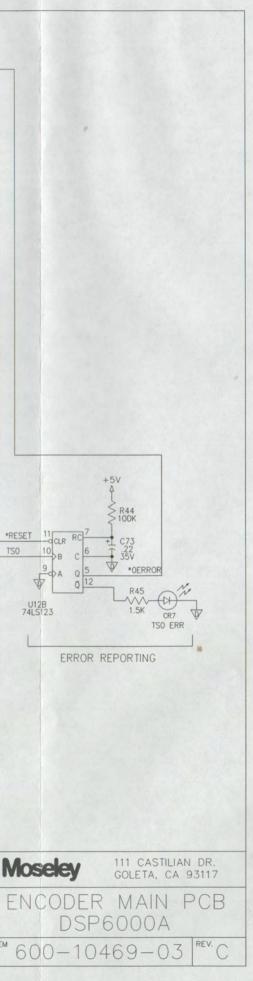

| 6-13  | Main/Aux/Data Multiplexer                          | 6-14 |

| 6-14  | Asynchronous Data                                  | 6-14 |

| 6-15  | Encoder Display                                    | 6-15 |

| 6-16  | Power Supply Section                               | 6-16 |

| 6-17  | Main Audio Section                                 | 6-17 |

| 6-18  | Aux Audio Section                                  | 6-18 |

| 6-19  | AGC Section                                        | 6-19 |

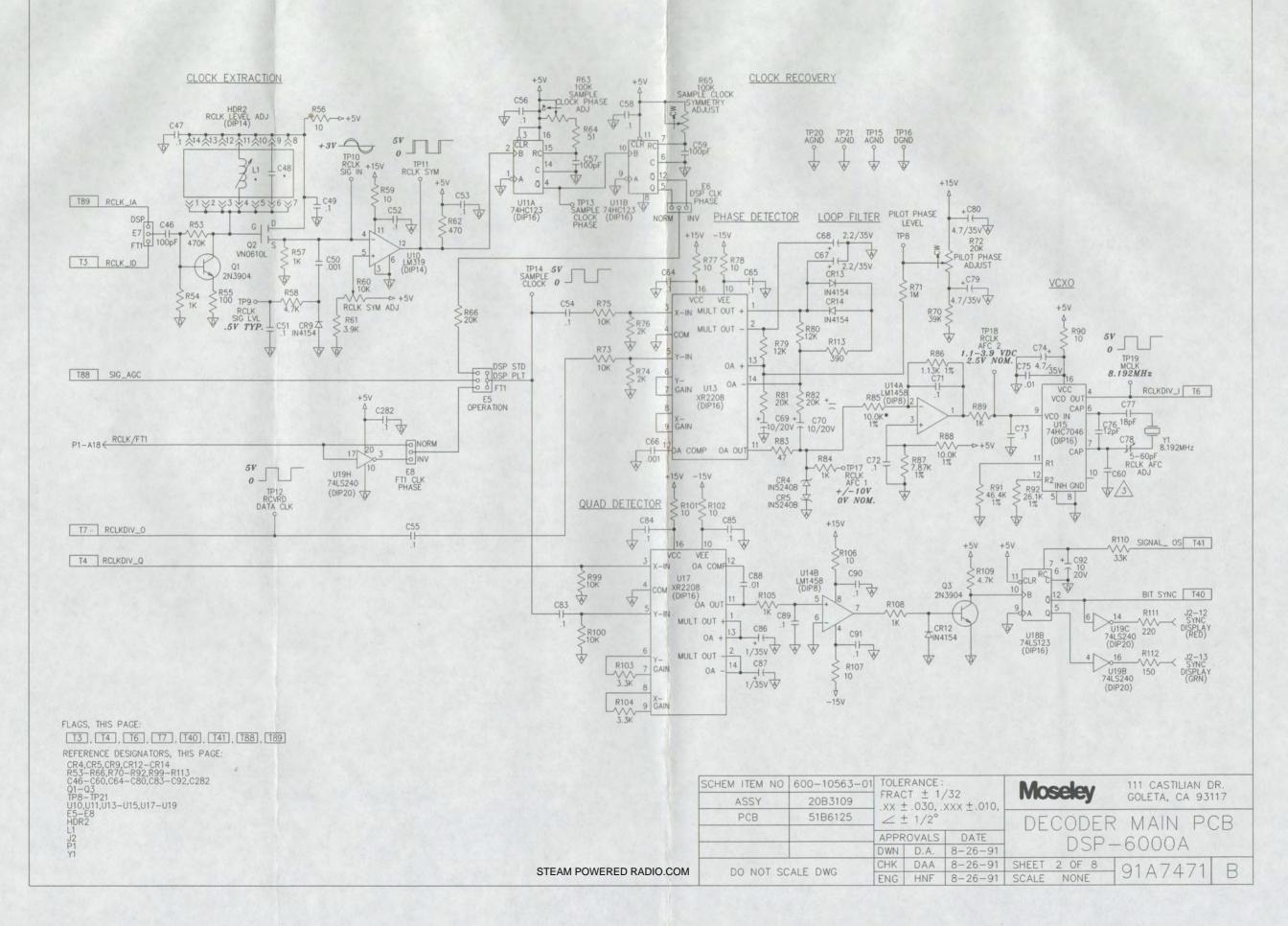

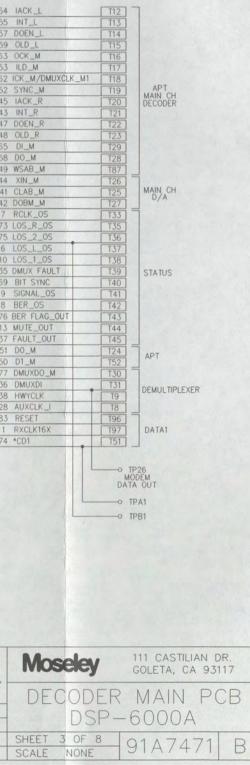

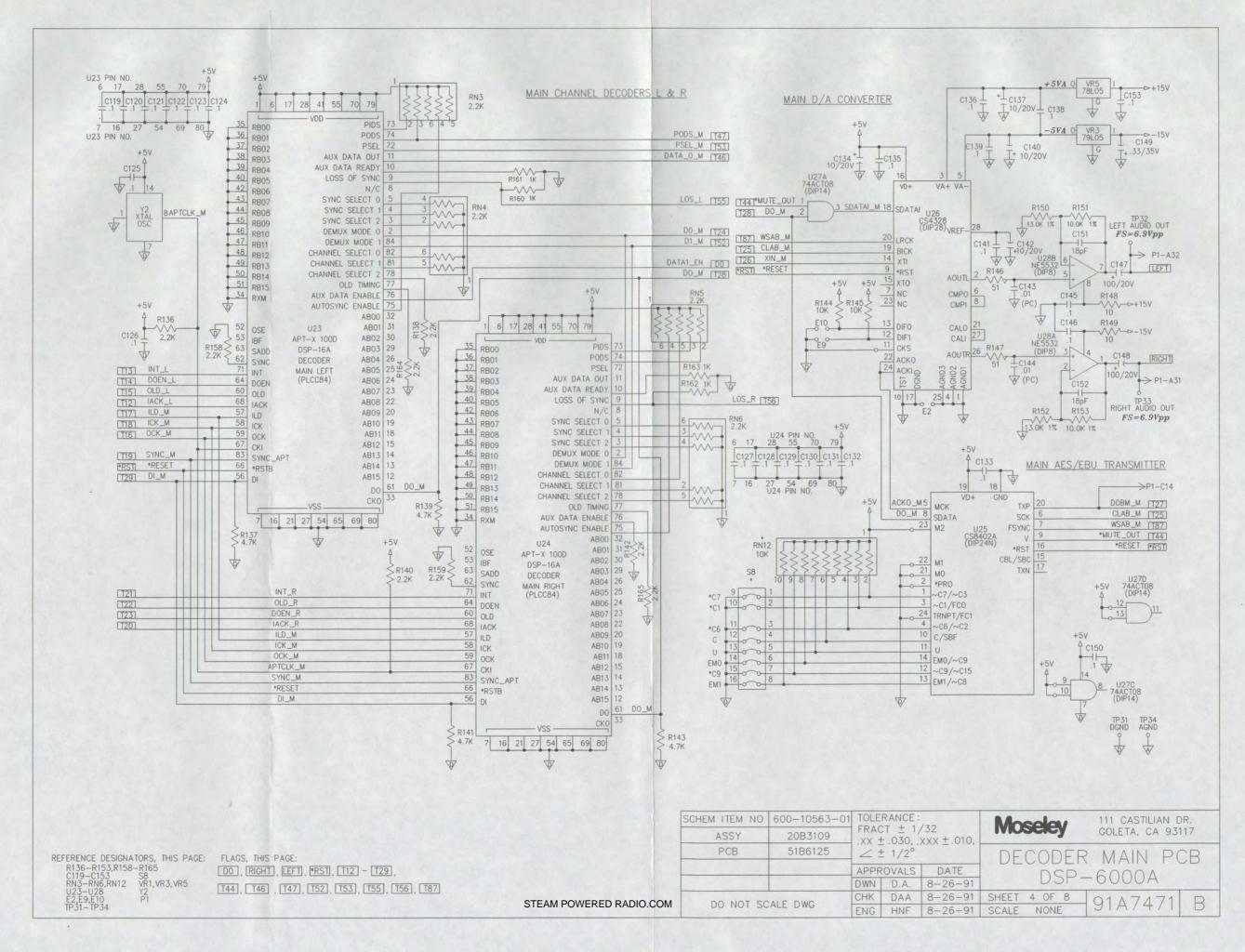

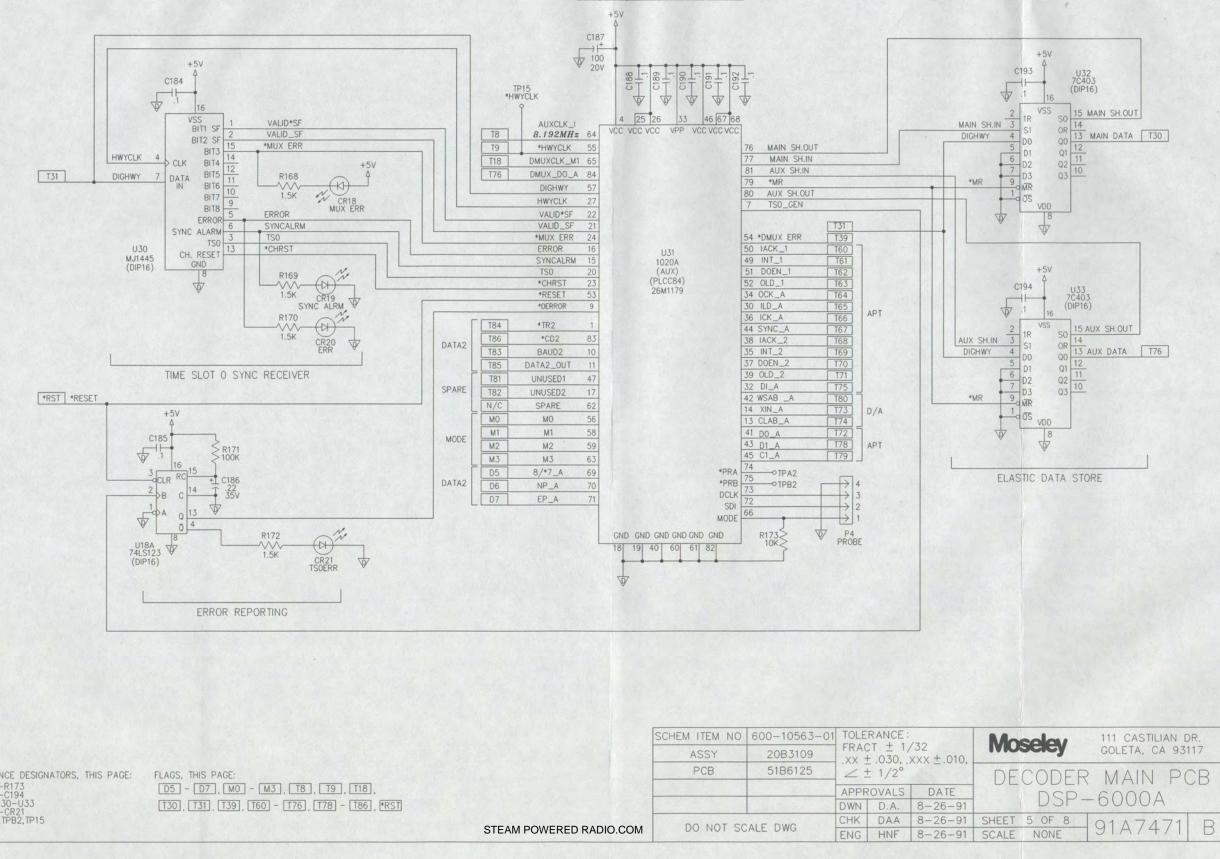

| 6-20  | Clock Recovery Section                             | 6-20 |

| 6-21  | Timing and Mode Control Section                    | 6-21 |

| 6-22  | Channel Decoder Section                            | 6-21 |

| 6-23  | Main Decoder Section                               | 6-21 |

| 6-24  | Aux Decoder Section                                | 6-22 |

| 6-25  | Main/Aux/Data Multiplexer                          | 6-22 |

| 6-26  | Asynchronous Data                                  | 6-23 |

| 6-27  | Spares                                             | 6-23 |

| 6-28  | Decoder Display Board                              | 6-24 |

| 6-29  | Recommended Test Equipment                         | 6-25 |

| A-1   | DSP6000A Threshold Versus Transmission Rate        | A-2  |

| 4-2   | Spectral Efficiency Modes                          | A-3  |

| Table | Title                                          | Page |

|-------|------------------------------------------------|------|

| A-3   | Spectral Occupancy                             | A-3  |

| A-4   | AES/EBU Standard Sync Preamble                 | A-6  |

| A-5   | DSP6000A AES/EBU Subframe Composition          | A-7  |

| A-6   | DSP6000A AES/EBU Channel Status Bit Assignment | A-8  |

# GLOSSARY

| A/D     | Analog-to-Digital                           |

|---------|---------------------------------------------|

| ADPCM   | Adaptive Differential Pulse Code Modulation |

| AES/EBU |                                             |

| AGC     | Auto Gain Control                           |

| BER     | Bit Error Rate                              |

| DTE     | Data Terminal Equipment                     |

| CMRR    | Common Mode Rejection Ratio                 |

| Codec   | Coder-Decoder                               |

| CPFSK   | Continuous-Phase Frequency Shift Keying     |

| CSU     | Channel Service Unit                        |

| DCE     | Data Circuit-Terminating Equipment          |

| DSTL    | Digital Studio-Transmitter Link             |

| DTE     | Data Terminal Equipment                     |

| D/A     | Digital-to-Analog                           |

| dB      | Decibel                                     |

| dBm     | Decibel relative to 1 mW                    |

| dBu     | Decibel relative to .775 Vrms               |

| DSP     | Digital Signal Processing                   |

| DSTL    | Digital Studio-Transmitter Link             |

| DVM     | Digital Voltmeter                           |

| EMI     | Electromagnetic Interference                |

| FMO     | Frequency Modulation Oscillator             |

| FPGA    | Field Programmable Gate Array               |

| FSK     | Frequency Shift Keying                      |

| FT1     | Fractional T1                               |

| IEC     | International Electrotechnical Commission   |

| IF      | Intermediate Frequency                      |

| IMD     | Intermodulation Distortion                  |

| kbps    | Kilobits per second                         |

| kHz     | Kilohertz                                   |

| LED     | Light Emitting Diode                        |

| LSB     | Least significant bit                       |

| Mbps    | Megabits per second                         |

| Modem   | Modulator-demodulator                       |

| ms      | Millisecond                                 |

| MSB     | Most significant bit                        |

| μS      | Microsecond                                 |

| μV    | Microvolt                               |

|-------|-----------------------------------------|

| MUX   | Multiplex                               |

| PCB   | Printed Circuit Board                   |

| PCM   | Pulse Code Modulation                   |

| PGM   | Program                                 |

| PLL   | Phase-Locked Loop                       |

| R     | Transmission Rate                       |

| RF    | Radio Frequency                         |

| RPTR  | Repeater                                |

| SCA   | Subsidiary Communications Authorization |

| SINAD | Signal to Noise and Distortion          |

| SNR   | Signal-to-Noise Ratio                   |

| STL   | Studio-Transmitter Link                 |

| TDM   | Time Division Multiplexing              |

| THD   | Total Harmonic Distortion               |

| TP    | Test Point                              |

| Vp    | Volts peak                              |

| Vp-p  | Volts peak-to-peak                      |

| Vrms  | Volts root mean square                  |

| ZIN   | Input Impedance                         |

| ZOUT  | Output Impedance                        |

|       |                                         |

## About This Manual

This manual is a comprehensive operation guide to the DSP6000A Digital Studio-Transmitter Link with information for new installations, retrofit installations, configuration, alignment, and general troubleshooting in the field.

If you are unfamiliar with the basic use of the DSP6000A, read Sections 1 through 3 before installing any equipment. Sections 4 through the appendix will aid those in need of more detailed information on the operation of this system.

Section 1, System Characteristics, is a brief overview of the DSP6000A. It includes encoder and decoder specifications, features, and system descriptions.

Section 2, Installation, covers unpacking, installation, and checkout procedures. It also describes retrofit modifications for STL's and remote controls.

Section 3, Operation, discusses the controls, adjustments, and I/O operations for the DSP6000A system that the user will encounter in normal operation and initial setup.

Section 4, Customer Service, tells how to get technical assistance or return equipment for factory service, and provides some field repair basics.

Section 5, Configuration, presents programming information for the various configurations of the system. Alignment information is also included.

Section 6, Troubleshooting and Testing, covers audio performance checks, troubleshooting aids, and user adjustments that are used to service and maintain the DSP6000A. This section also includes recommended test equipment and test fixtures.

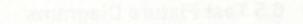

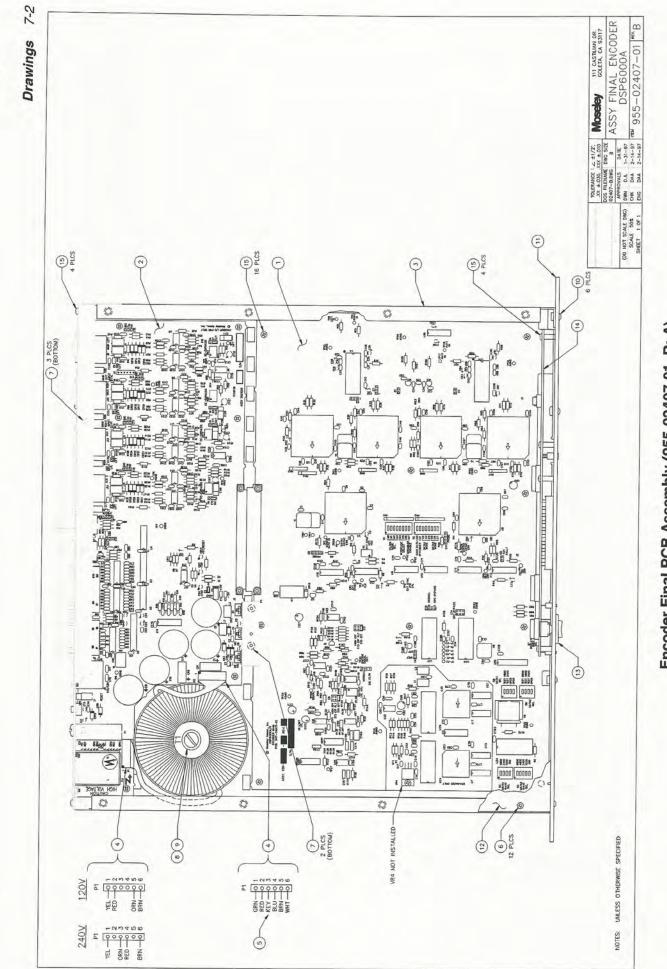

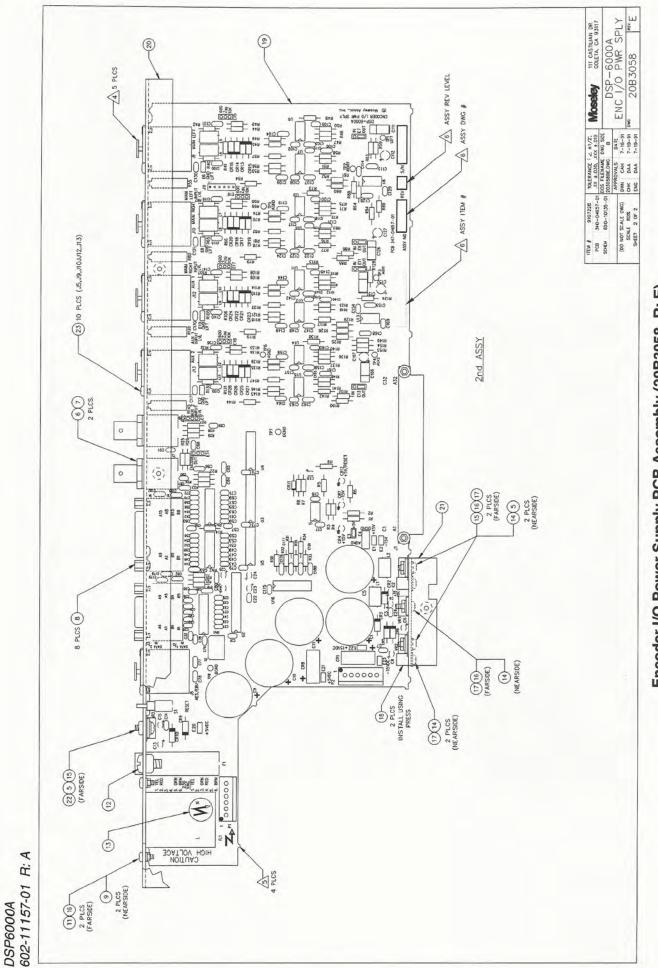

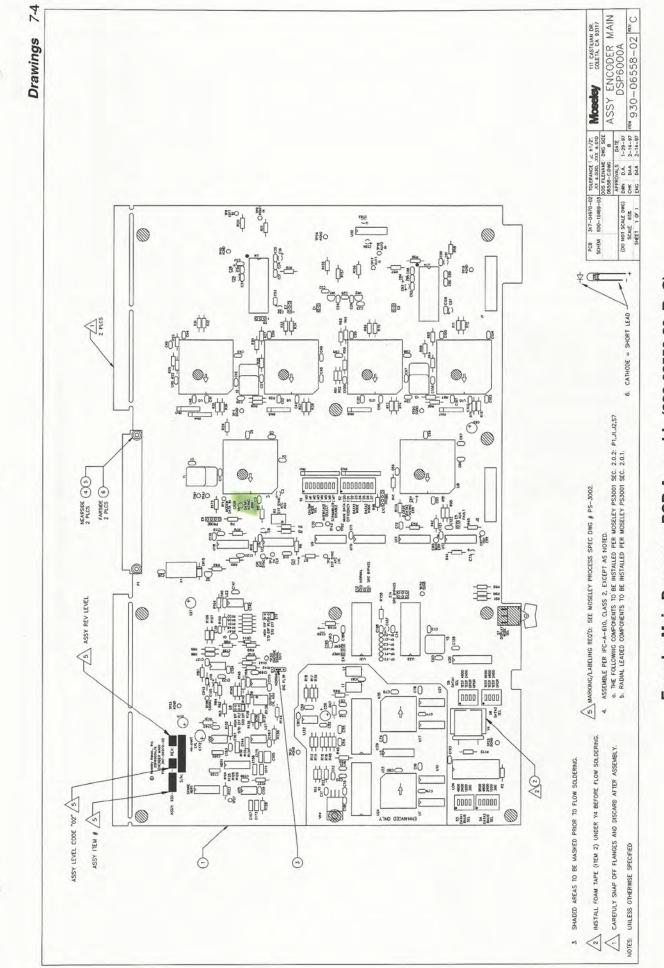

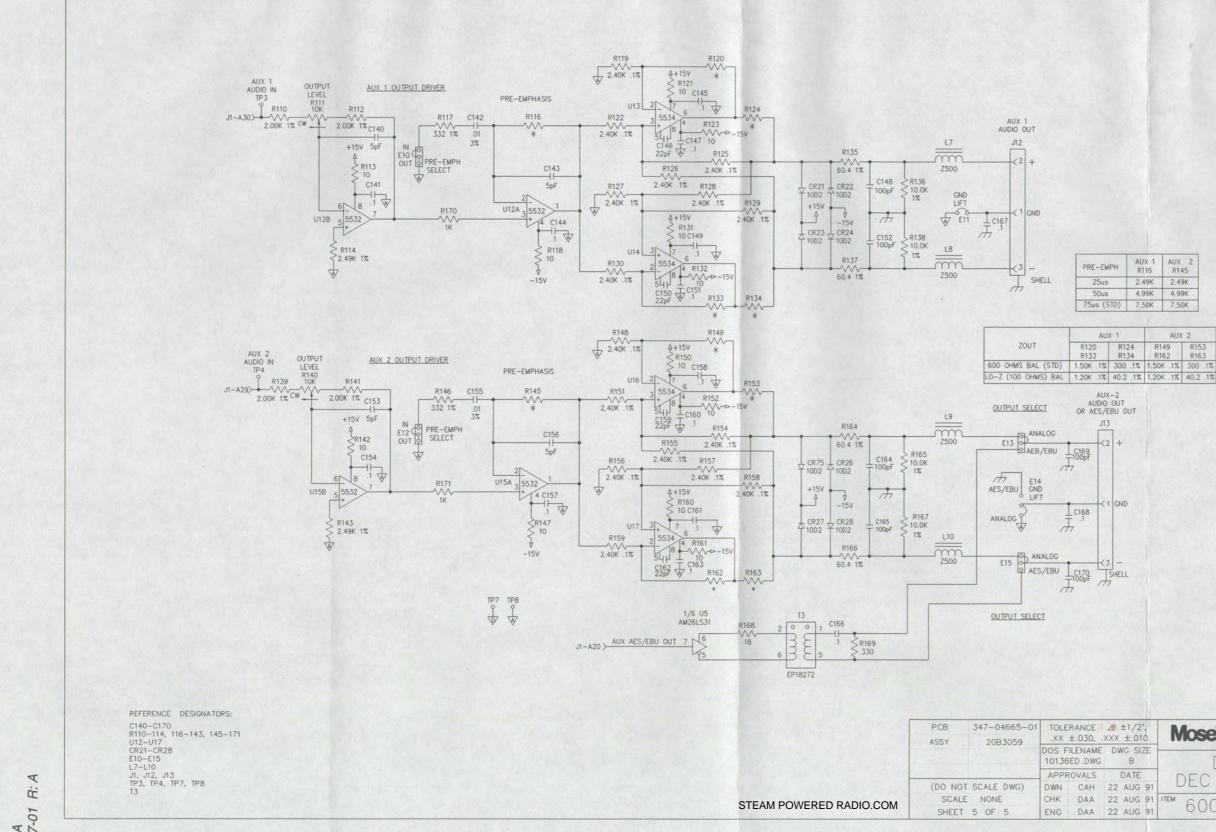

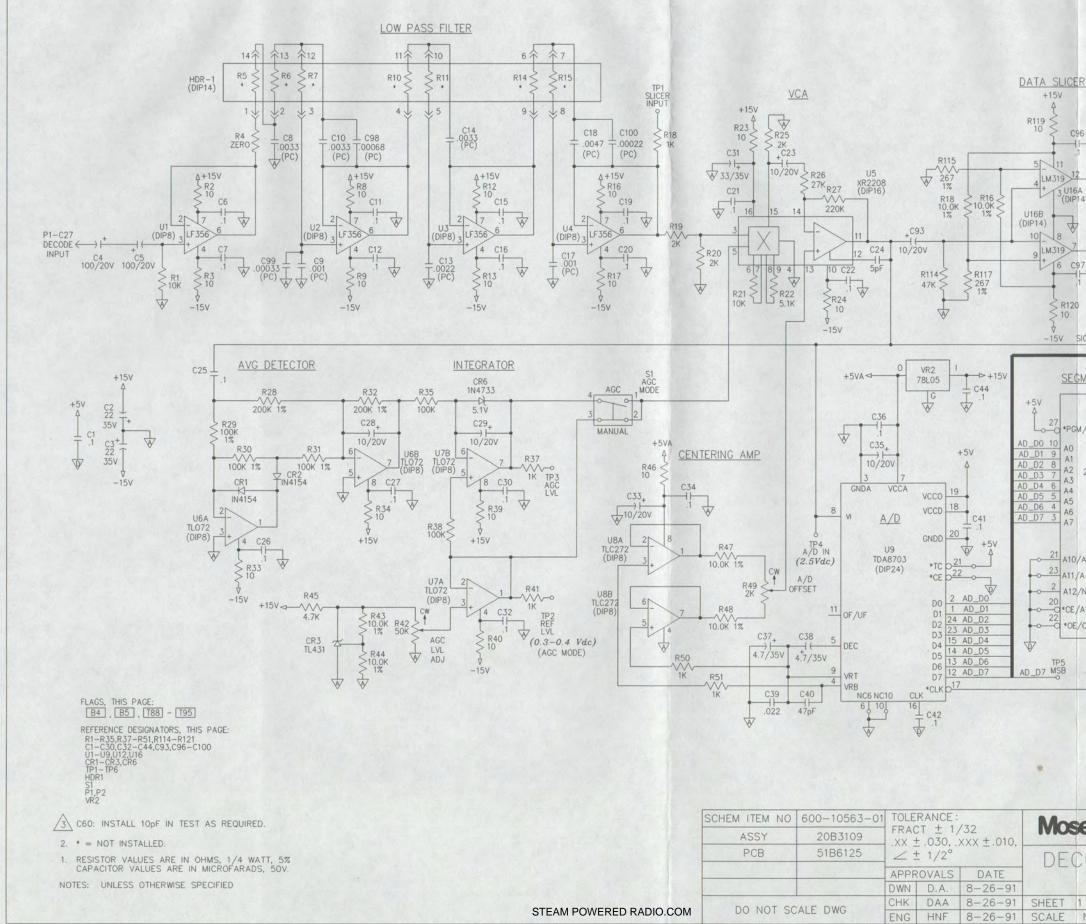

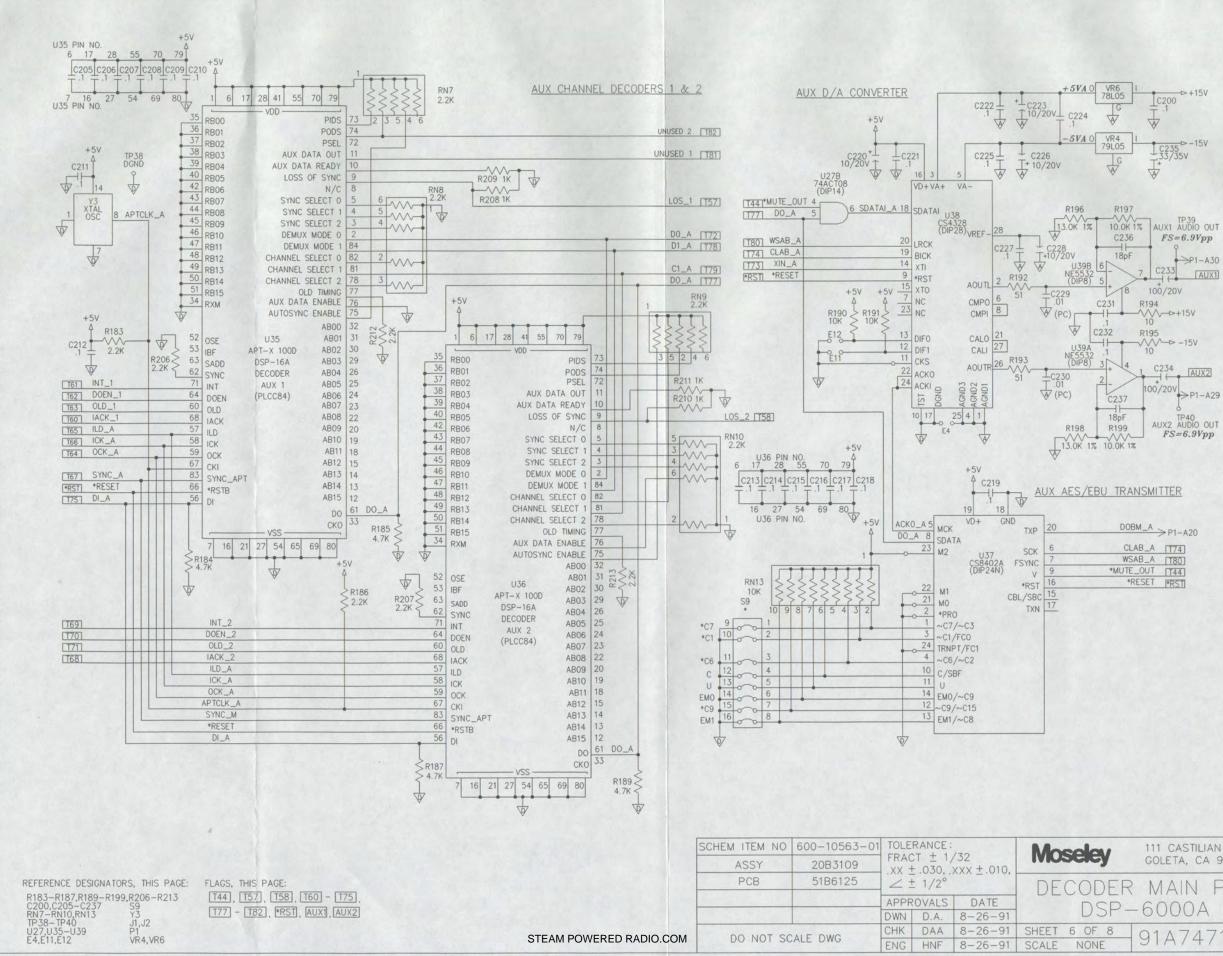

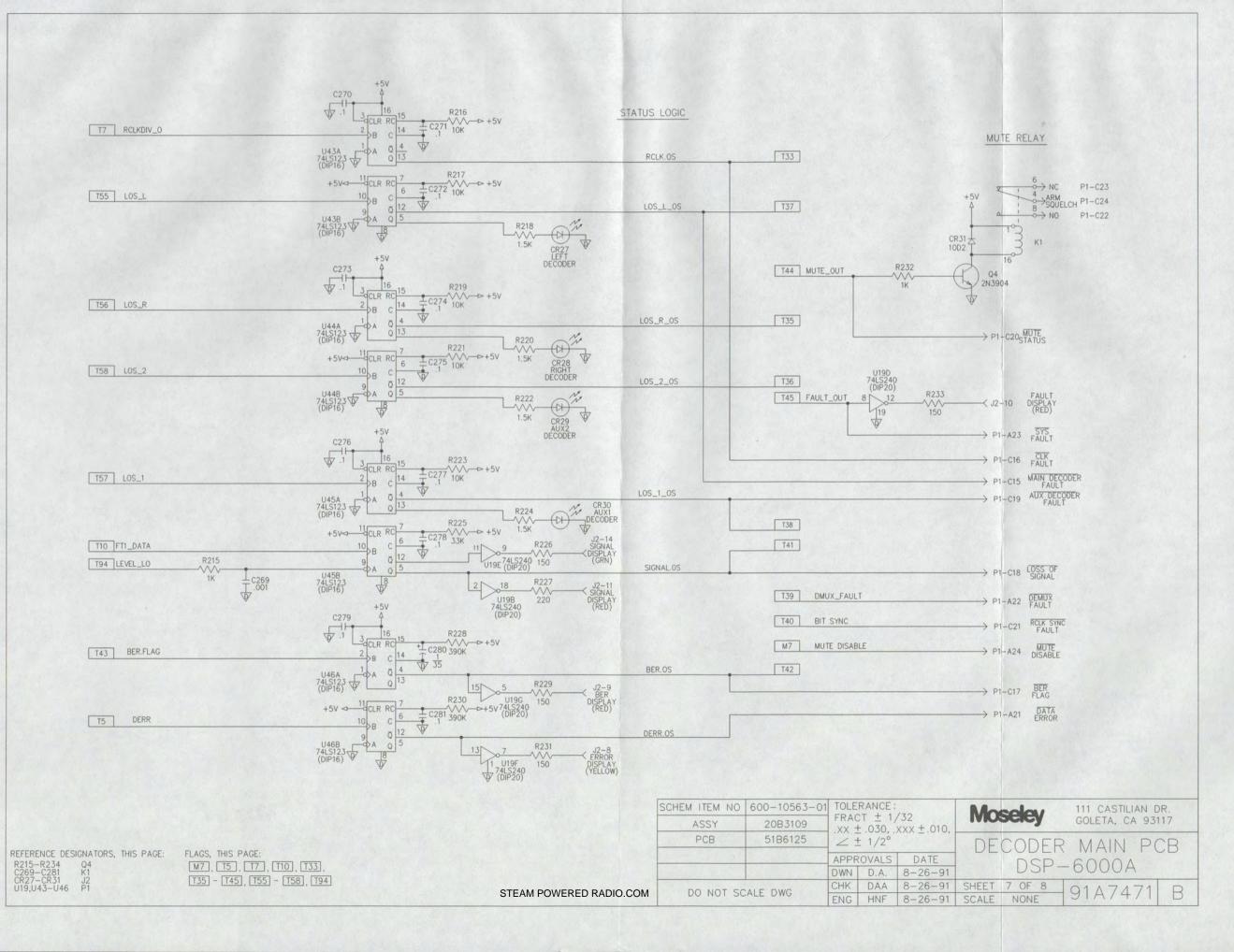

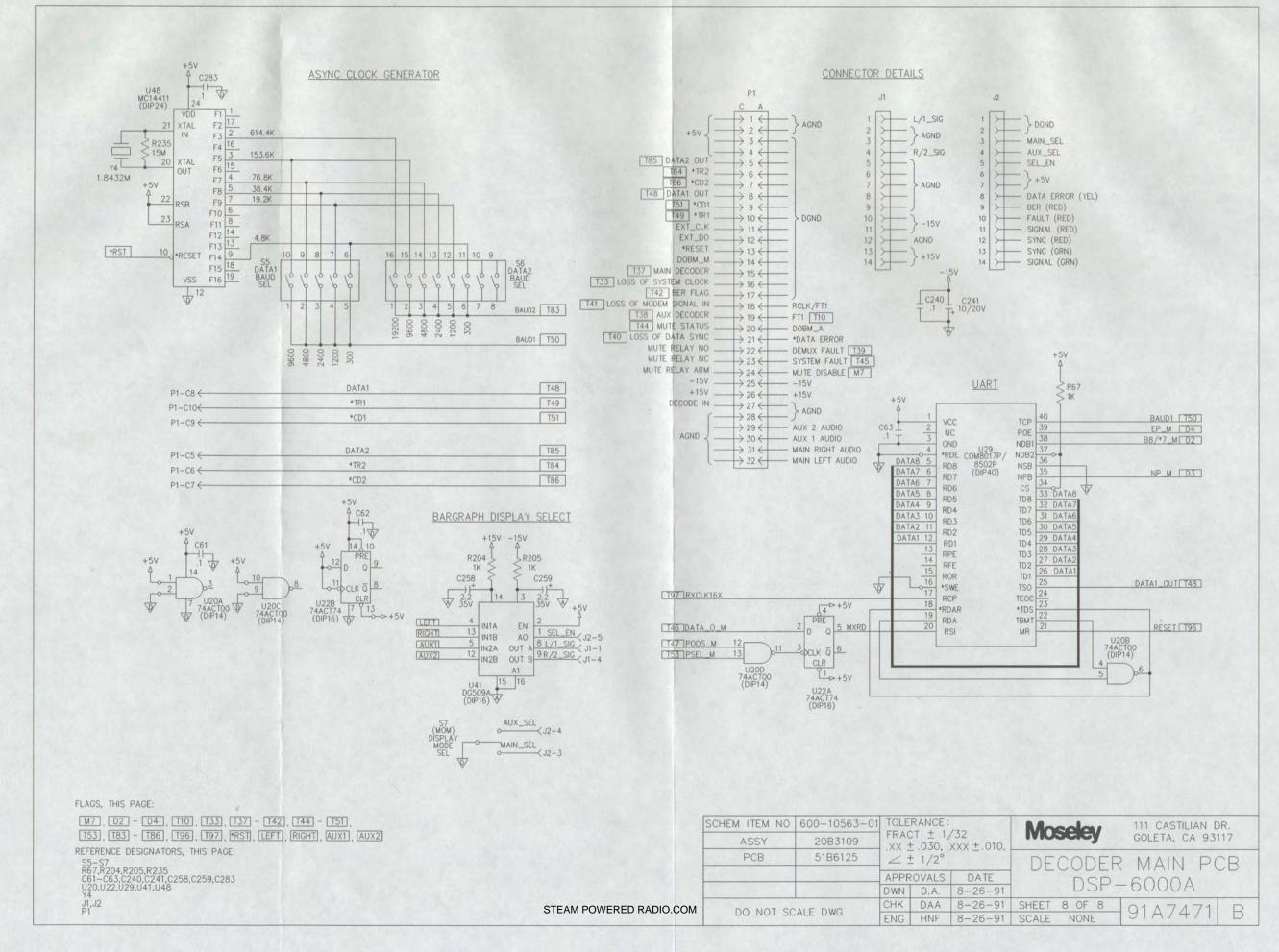

Section 7, Schematic and Assembly Drawings, contains system schematics and board diagrams to aid in troubleshooting and field repair.

The Appendix contains addendum information to the 950 MHz Microwave path evaluation, spectral occupancy information, and AES/EBU digital audio data format overview.

STEAM POWERED RADIO.COM

1

# Section 1

# System Characteristics

| Section | Contents                        | Page |

|---------|---------------------------------|------|

| 1.1     | Introduction                    | 1-2  |

| 1.2     | System Features                 | 1-3  |

| 1.3     | DSP6000A System                 | 1-4  |

| 1.3.1   | DSP6000A System Specifications  | 1-4  |

| 1.3.2   | DSP6000E Encoder Specifications | 1-5  |

| 1.3.3   | DSP6000D Decoder Specifications | 1-6  |

| 1.4     | System Description              | 1-7  |

| 1.4.1   | DSP6000E Encoder Description    | 1-7  |

| 1.4.2   | DSP6000D Decoder Description    | 1-11 |

## **1.1 Introduction**

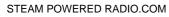

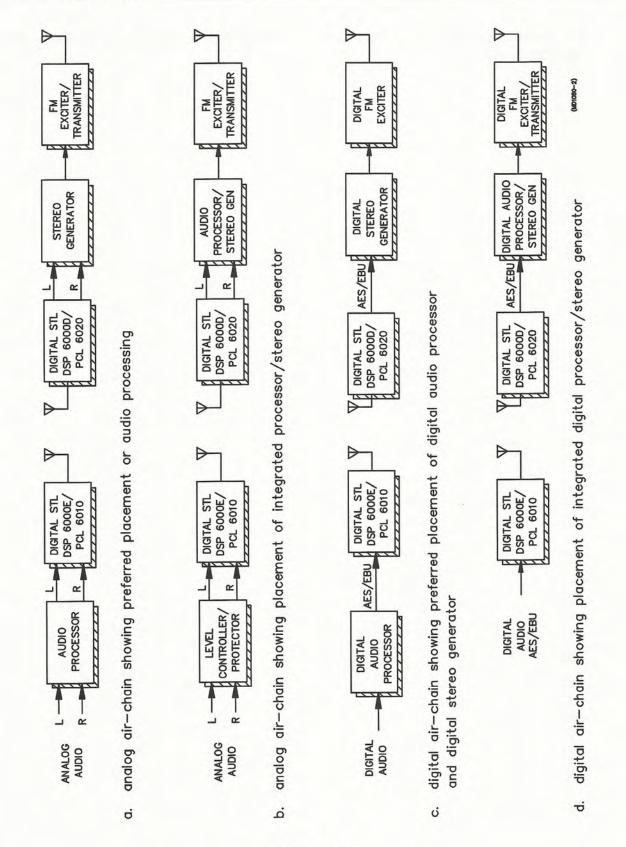

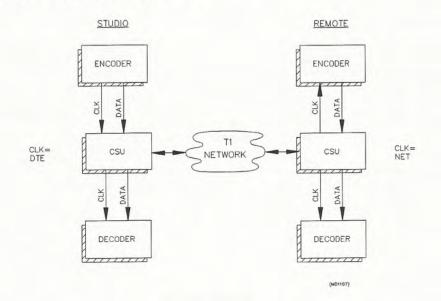

The DSP6000A Digital Studio-Transmitter Link (DSTL) system conveys high quality program material over FM radio or fractional T1 (FT1) networks to a remote site. Typically, program material is transmitted from a studio site to a remote transmitter site or to a repeater site.

The DSP6000E and DSP6000D comprise a digital audio codec (coder/decoder) which converts high-quality audio material into a bandwidth-reduced digital signal compatible with transmission over conventional FM radio links. This operation is shown in Figure 1-1. When used in conjunction with the PCL6000 or PCL606 studio-transmitter links (STL), the overall system constitutes a digital STL radio spectrally compatible with existing FCC Part 74 frequency allocations.

The DSP6000E encoder accepts four discrete audio program inputs, or one digital stereo program input with two discrete audio program inputs. The encoder generates a bandwidth-efficient digital baseband data stream that is accepted at the composite input of the STL transmitter. This results in an efficient continuous-phase frequency shift keying (CPFSK) modulation from the transmitter.

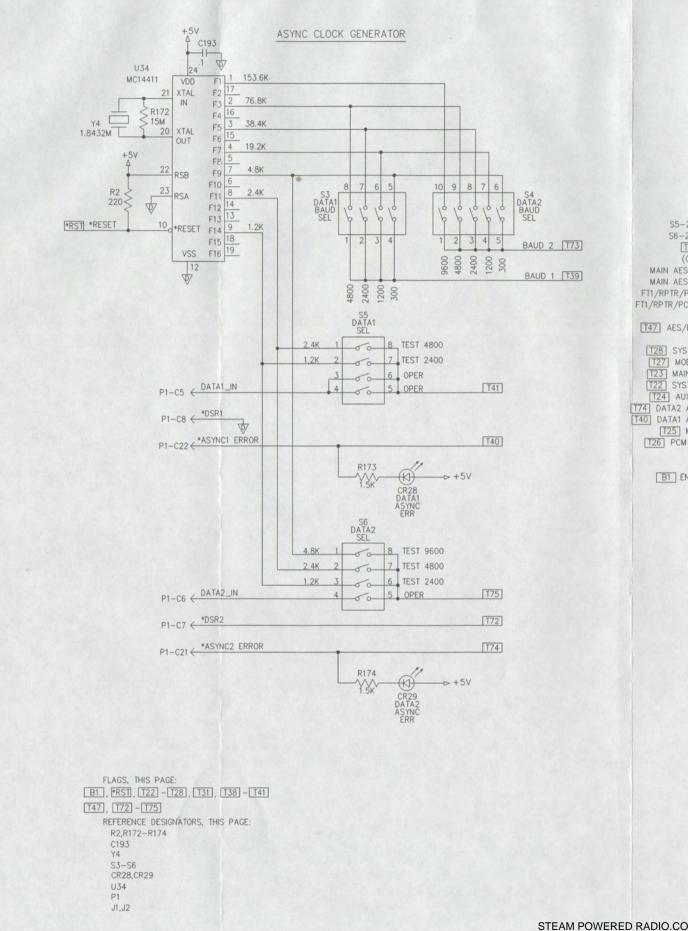

The DSP6000D decoder receives the recovered digital baseband from the STL receiver and translates this signal back to high quality program audio or digital stereo for output. The system also has provisions for two low-speed (up to 9600 baud) asynchronous data channels for supervisory or other auxiliary applications.

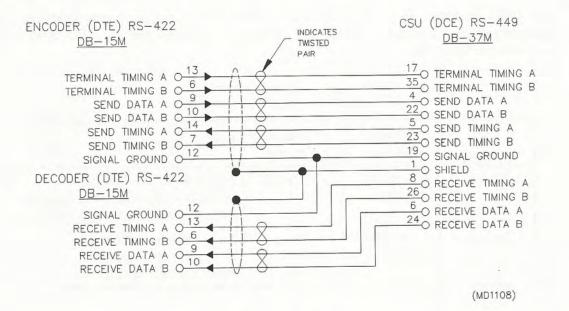

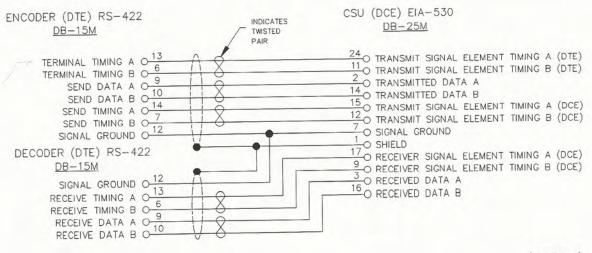

The DSP6000A codec is also compatible with transmission over fractional T1 networks. The 4:1 data rate reduction provided by the codec facilitates the transmission of four full-bandwidth program channels over a fraction of one T1 service. The fractional use of the T1 line typically provides a corresponding economy in monthly line costs.

Figure 1-1 DSP6000A Digital Studio-Transmitter Link (DSTL) System

## **1.2 System Features**

In addition to establishing a new industry standard for studio-transmitter link performance, the DSP6000A incorporates many new and innovative features to aid in application, operation, installation, and maintenance of the system. These features include:

- CD quality audio performance.

- Operation through existing analog FM STL gear.

- Operation through fractional T1 networks.

- Higher system gain, 26 dB more than composite STL.

- Degradation-free multiple hops.

- Linear-phase audio channels.

- Configurable for up to 4 audio program channels per STL system.

- No crosstalk between channels.

- No background chatter from co-channel or adjacent-channel interference.

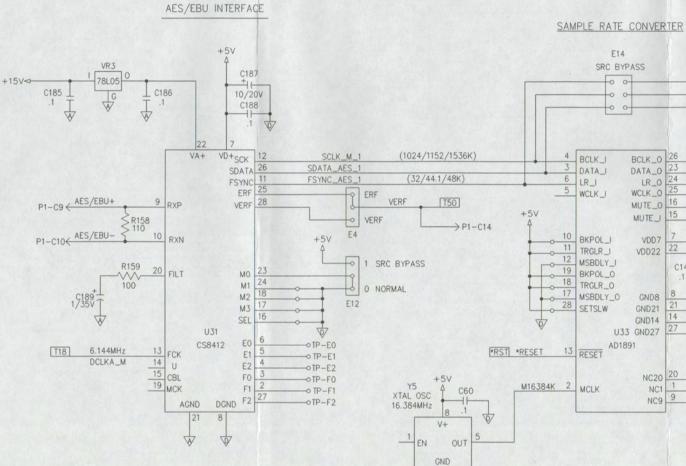

- Built-in AES/EBU digital audio interface.

- Built-in data channels eliminate need for data sub-carrier.

- Extensive status monitoring.

- Peak-reading LED bargraph display for all audio channels.

- Adjustable bit error rate threshold indication for monitoring transmission quality.

- Use of field programmable gate arrays (FPGA's) greatly reduce circuit density, enhance reliability, and facilitate rapid field upgrades and enhancements.

- Integrated construction eliminates harnessing to enhance reliability.

- Selectable RF spectral efficiency.

- Encoder input sample rate converter (SRC) for digital audio operation from 30 to 50 kHz.

NOTE

$\triangle$

Study this manual at least through Section 3 before attempting to install your system.

## 1.3 DSP6000A System

# 1.3.1 DSP6000A System Specifications

| Frequency Response     | Wide:<br>Narrow:                                                                                                                                                          | 20 Hz to 15 kHz ±0.2 dB<br>20 Hz to 7.5 kHz ±0.2 dB       |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|

| Distortion             | < .01%, sut                                                                                                                                                               | < .01%, subjective                                        |  |  |

| Dynamic Range          | > 86 dB (90                                                                                                                                                               | > 86 dB (90 dB typical) static                            |  |  |

| Crosstalk              | < -80 dB                                                                                                                                                                  | < -80 dB                                                  |  |  |

| Level Stability        | < 0.2 dB                                                                                                                                                                  |                                                           |  |  |

| Data Coding Method     | Sub-band A                                                                                                                                                                | Sub-band ADPCM                                            |  |  |

| Sample Rate            | 32 kHz (inte                                                                                                                                                              | 32 kHz (internal), 30–50 kHz at AES/EBU input             |  |  |

| Time Delay             | < 3.8 ms                                                                                                                                                                  | < 3.8 ms                                                  |  |  |

| Bit Error Immunity     | <b>Bit Error Immunity</b> > 10 <sup>-4</sup> for no subjective loss in audio quality                                                                                      |                                                           |  |  |

| RF Spectral Efficiency |                                                                                                                                                                           | acy: 0.7 bps/Hz 50 dB down<br>ancy: 1.4 bps/Hz 50 dB down |  |  |

| Sensitivity            | 5 $\mu$ V (-93 dBm) at 10 <sup>-4</sup> BER for PCL6000 for two channel configuration (standard efficiency)                                                               |                                                           |  |  |

| Data Channels          | Channels DATA 1:<br>RS-232; selectable baud rates from 4800, 2400, 1200,<br>300 baud<br>DATA 2:<br>RS-232; selectable baud rates from 9600, 4800, 2400,<br>1200, 300 baud |                                                           |  |  |

| Program Channels       | 1-4 channels; programmable as 15 or 7.5 kHz;<br>transmission rate changes as function of number of<br>channels and bandwidths                                             |                                                           |  |  |

| Transmission Rates     | selectable from 64, 128, 205, 256, 341, 410, and 512 kbps, depending on channel configuration                                                                             |                                                           |  |  |

# 1.3.2 DSP6000E Encoder Specifications

| Audio Input         | Electronically balanced input, XLR type, female; CMRR > 60 dB.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Audio Level         | Each channel adjustable from -10 dBu to +18 dBu, multi-turn, rear panel accessible                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Digital Audio Input | AES/EBU standard (16 bit word length), RS-422A<br>transformer balanced XLR type, 110 ohms input<br>impedance; Sample rate input range: 30–50 kHz                                                                                                                                                                                                                                                                                                                                                                   |  |

| Data Inputs         | DATA 1:RS-232, 9-pin D-type, femaleDATA 2:RS-232, 9-pin D-type, female                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

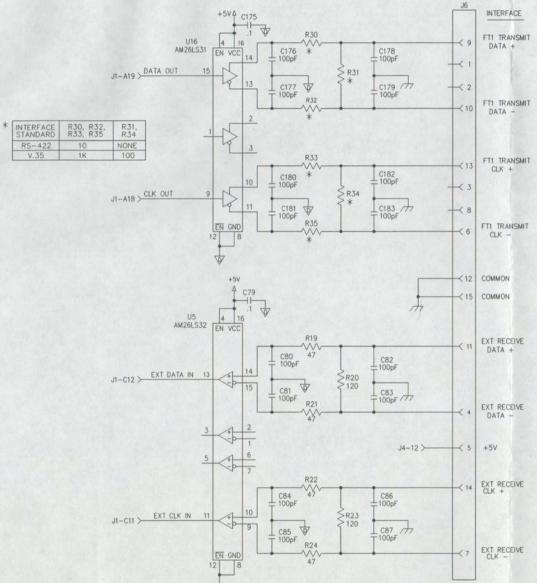

| Interface I/O       | RS-422, 15-pin D-type, female;<br>Input for regenerated data and clock from decoder<br>in RPTR MODE;<br>Input for unformatted linear 16-bit PCM data and frame<br>sync in PCM MODE;<br>Output for program data and input/output for clock in<br>FT1 MODE                                                                                                                                                                                                                                                           |  |

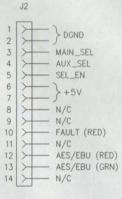

| Status Output       | 15-pin D-type female provides active-low indication of<br>system fault, clock fault, modem fault, processor fault,<br>mux fault, system-power fault relay contact, AES/EBU<br>fault, and DATA channel faults                                                                                                                                                                                                                                                                                                       |  |

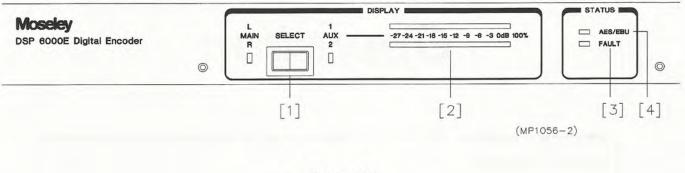

| Indicators          | <ul> <li>Bargraph Display: dual ten-LED display indicates peak program level relative to 100% full scale (0 dB) A/D input overload level for audio program channels; display switchable from MAIN program to AUXILIARY program channels</li> <li>MAIN: indicates bargraph is displaying main Left/Right program levels</li> <li>AUX: indicates bargraph is displaying auxiliary</li> <li>Aux 1/Aux 2 program levels</li> <li>AES/EBU: indicates status of digital audio input FAULT: system fault alarm</li> </ul> |  |

| Power, AC           | 115/230 VAC, 50/60 Hz, 30 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Power, DC Options   | 12 VDC:         9-18 VDC, 30 W, isolated ground           24 VDC:         18-36 VDC, 30 W, isolated ground           48 VDC:         36-72 VDC, 30 W, isolated ground                                                                                                                                                                                                                                                                                                                                              |  |

# 1.3.3 DSP6000D Decoder Specifications

| Audio Output         | Electronically balanced output, XLR type, male                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Audio Level          | Each channel adjustable from -10 dBm to +14 dBm into 600 ohms, 10-turn rear panel accessible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Digital Audio Output | AES/EBU standard, RS-422A transformer balanced XLR male, 110 ohms output impedance. Sample rate 32 kbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Data Outputs         | DATA 1:RS-232, 9-pin D-type, femaleDATA 2:RS-232, 9-pin D-type, female                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Interface I/O        | RS-422, 15-pin D-type female;<br>Output for regenerated data and clock (to encoder) in<br>RPTR MODE;<br>Output for unformatted linear 16-bit PCM data and<br>frame sync in PCM MODE;<br>Output for AES/EBU digital audio data is AES/EBU<br>MODE;<br>Input for program data and clock in FT1 MODE                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Status Output        | 15-pin D-type female provides active-low indication of<br>system fault, loss-of-data-sync, loss-of-incoming signal,<br>clock fault, modem fault, processor fault, BER fault, data<br>error, demux fault, mute status, mute relay contacts, and<br>mute disable input                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Indicators           | <ul> <li>Bargraph Display: dual ten-LED display indicates peak program level relative to 100% full scale (0 dB) D/A output level for audio program channels; display switchable from MAIN program to AUXILIARY program channels</li> <li>MAIN: indicates bargraph is displaying main Left/Right program levels</li> <li>AUX: indicates bargraph is displaying auxiliary Aux 1/Aux 2 program levels</li> <li>FAULT: system fault alarm</li> <li>SYNC: bicolor indication for data synchronization</li> <li>SIGNAL: bicolor indicates received data error</li> <li>BER: indicates alarm condition when received bit error rate surpasses preset level (selectable from 10<sup>-1</sup> to 10<sup>-6</sup>)</li> </ul> |  |  |

| Power, AC            | 115/230 VAC, 50/60 Hz, 30 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Power, DC Options    | 12 VDC:9-18 VDC, 30 W, isolated ground24 VDC:18-36 VDC, 30 W, isolated ground48 VDC:36-72 VDC, 30 W, isolated ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

## 1.4 System Description

## 1.4.1 DSP6000E Encoder Description

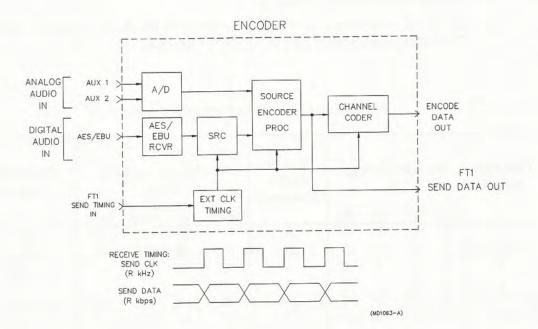

The DSP6000E is a digital audio encoder designed to work with existing STL transmission equipment or fractional T1 telco lines. The system accepts four discrete audio inputs, a digital audio input, and two low-rate data inputs for encoding. The audio channels are converted to digital binary form. Digital signal processing then reduces each channel data rate by a factor of four. Channel data is multiplexed together with the data channels. This composite signal is available for output to a T1 CSU for fractional T1 transmission. Otherwise, the composite digital signal is processed by an efficient channel coding scheme. This signal is then output to frequency modulate any FM-type STL transmitter.

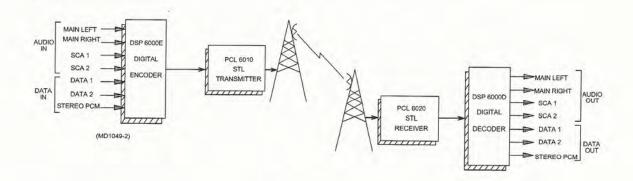

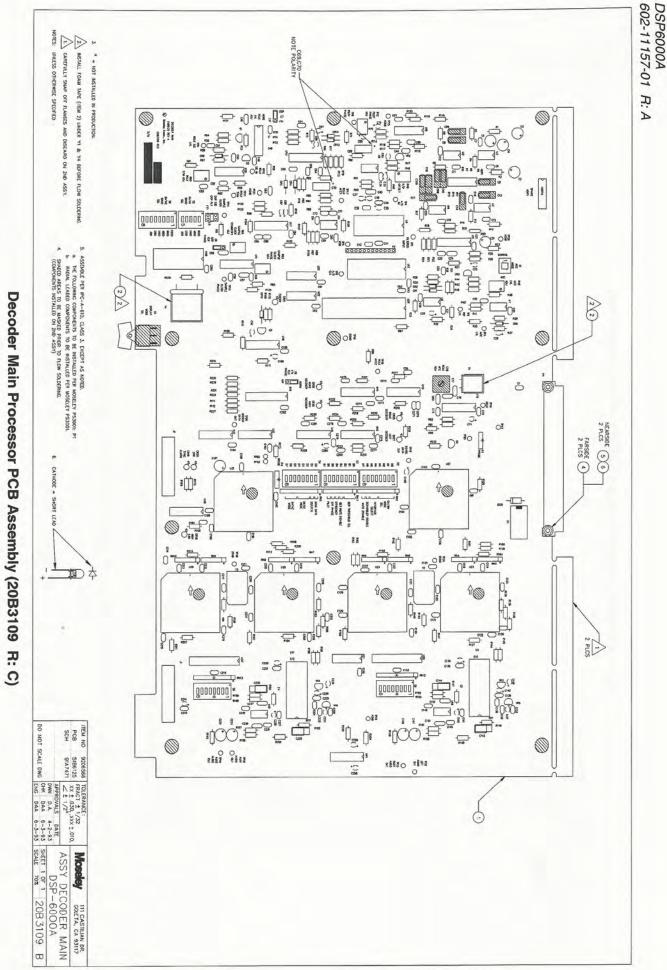

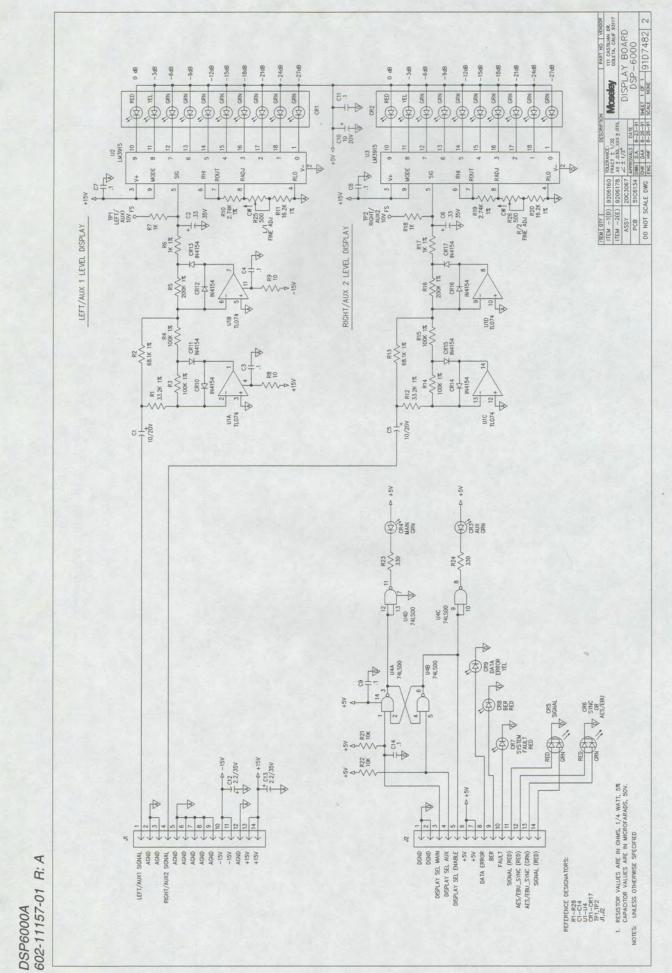

The encoder is physically partitioned into three printed circuit assemblies—the I/O board, the main processor board, and the display board. Functionally, the encoder is partitioned into six groups which are described below. Refer to Figure 1-2, Encoder Block and Level Diagram, for reference to this section.

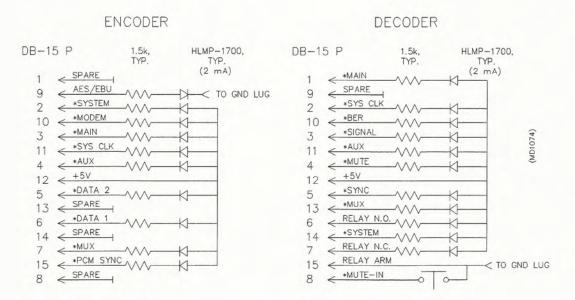

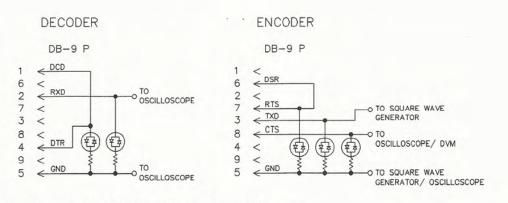

#### Audio-Digital I/O Interface (I/O Board)

The audio-digital I/O interface consists of four active balanced program audio inputs (LEFT, RIGHT, AUX 1, and AUX 2) with input level adjustments and selectable active preemphasis, AES/EBU digital stereo input (MAIN only), RS-232 data inputs, RS-422 INTERFACE input, and buffered STATUS output. This board provides the appropriate signal conditioning, I/O buffering, and electromagnetic interference (EMI) protection between the outside world and the main processor portion of the encoder.

#### Source Encoder (Main Processor Board)

The source encoder converts the audio information into digital binary 1's and 0's serial format. The source encoder consists of the analog-to-digital (A/D) converters, the adaptive-differential pulse code modulation (ADPCM) encoders, and the data multiplexer. The A/D converters receive discrete audio inputs from the I/O board which are converted to 16-bit linear PCM serial data. The ADPCM encoders, in turn, convert these signals to 4-bit serial data, yielding a 4:1 data reduction. Alternatively, the main channel analog audio inputs (LEFT and RIGHT) may be replaced by one digital stereo audio input in AES/EBU format. In this case the main A/D converter is bypassed and the digital audio is input directly into the ADPCM encoder for data reduction.

The serial outputs from the ADPCM encoders (one from each channel), along with two low-rate asynchronous data channels, are then time division multiplexed together into one composite serial data stream. This data is available for output for T1 transmission or sent to the channel encoder for processing prior to channel transmission. System and data timing are derived internally from a crystal clock reference for STL operation, or are derived either internally or externally for fractional T1 synchronization.

#### Channel Encoder (Main Processor Board)

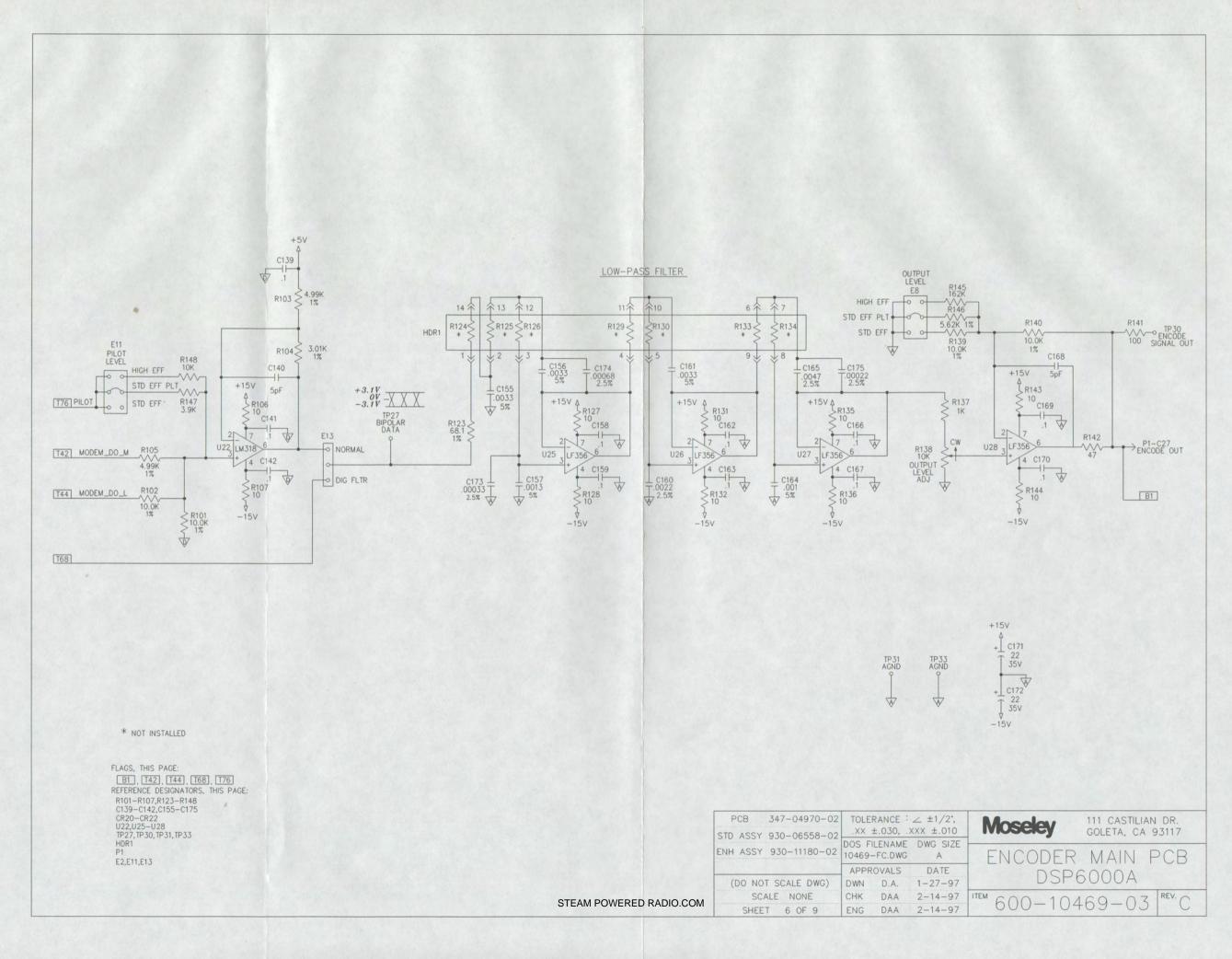

The channel encoder processes the serial binary data from the source encoder into a multilevel, spectrally shaped signal prior to channel transmission. The channel encoder consists of the scrambler, precoder, and shaping filter. The scrambler eliminates discrete spectral information. The precoder eliminates error propogation. The shaping filter produces either a 3-level or 7-level shaped data signal that corresponds to "standard" or "high" spectral efficiency transmission modes, respectively.

The channel encoder also accepts data from the external INTERFACE input, bypassing the internal source encoder, to facilitate repeater operation or the use of alternate source coding equipment. For FT1 operation the channel encoder is bypassed and only the source encoder is used.

#### Timing and Control (Main Processor Board)

The channel configuration (1 to 4 audio channels with 1 or 2 data channels), the channel bandwidths (15 kHz or 7.5 kHz), and resulting data transmission rate (64 kbps to 512 kbps) are determined through the mode selection DIP switches M0 to M3. The interface mode DIP switches M4, M5, and M6 select I/O source data from the following: 1) internal program channels with internal synchronization for standard STL/FT1 operation, 2) internal program channels with external synchronization for FT1 operation, 3) external program data for repeater operation or outboard source coding, 4) AES/EBU digital audio input, or 5) unformatted linear PCM input. RF spectral efficiency is selected between "standard" (3-level) and "high" (7-level) with DIP switch D1.

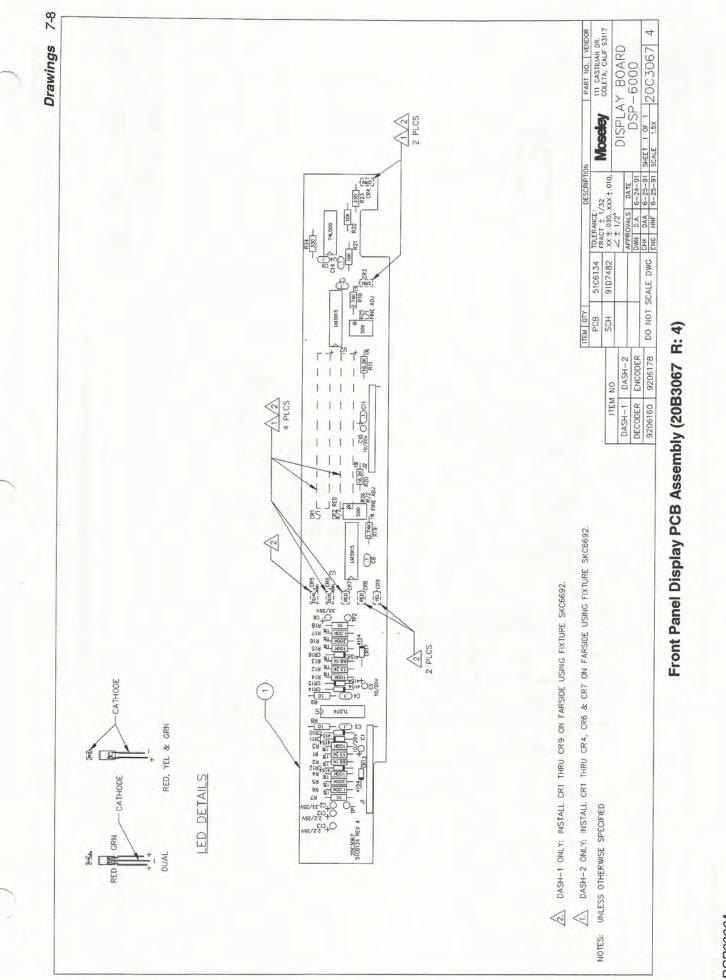

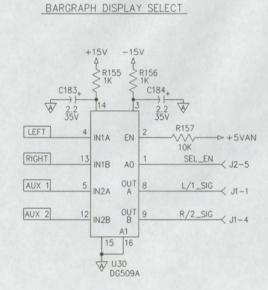

#### Status and Metering (Display Board)

This board contains the front panel indicator LED's. The peak program level of the discrete audio channels is displayed in MAIN or AUX channel pairs on the dual LED bargraphs. A tricolor LED displays the status and condition of the AES/EBU digital audio input. A red LED gives indication of system failure.

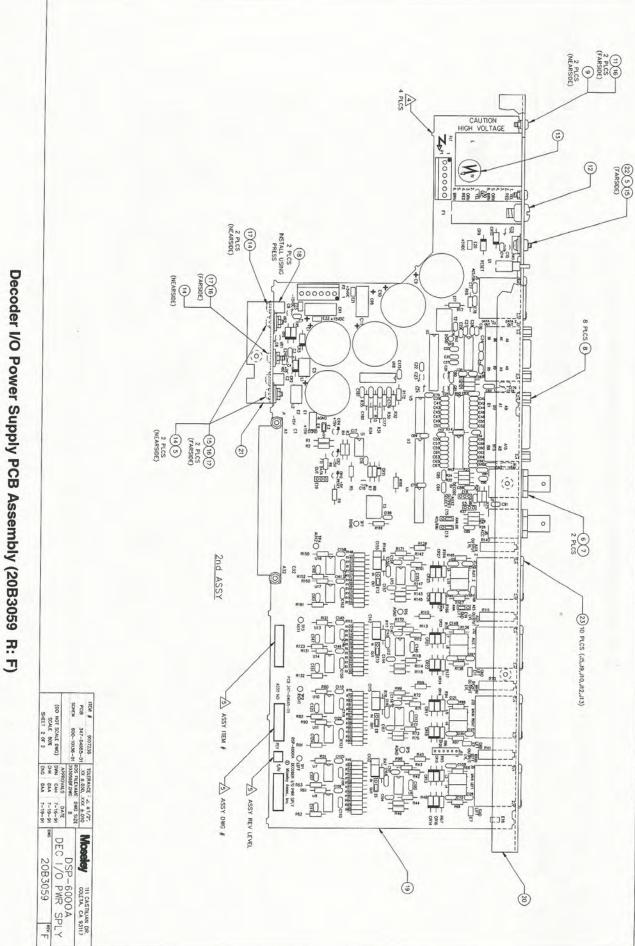

#### Power Supply (I/O Board)

The power supply converts AC line source (115 VAC or 230 VAC, internally wired) to three regulated voltages: +5 VDC, +15 VDC, and -15 VDC. Supervisory functions provide system reset for power-up and low voltage conditions (for example, power drop out or brown out) and crowbar/pull-down on the +5 VDC line during overvoltage conditions (for example, from a faulty regulator) to protect vital processing components.

#### Note

Once the crowbar is tripped the system may require a new fuse or manually removing and reapplying AC power to bring the system up.

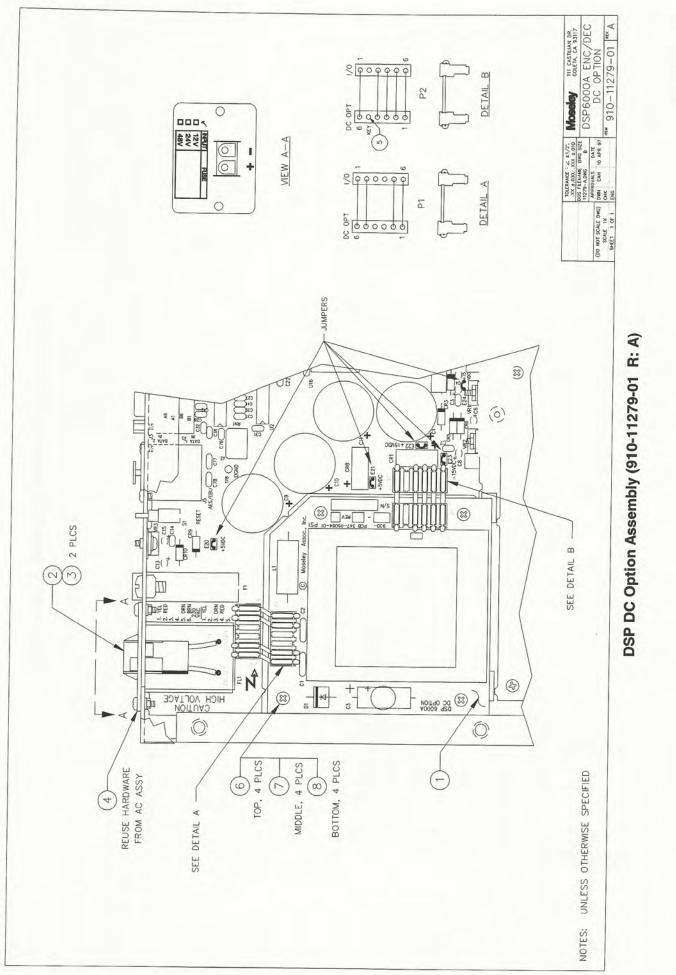

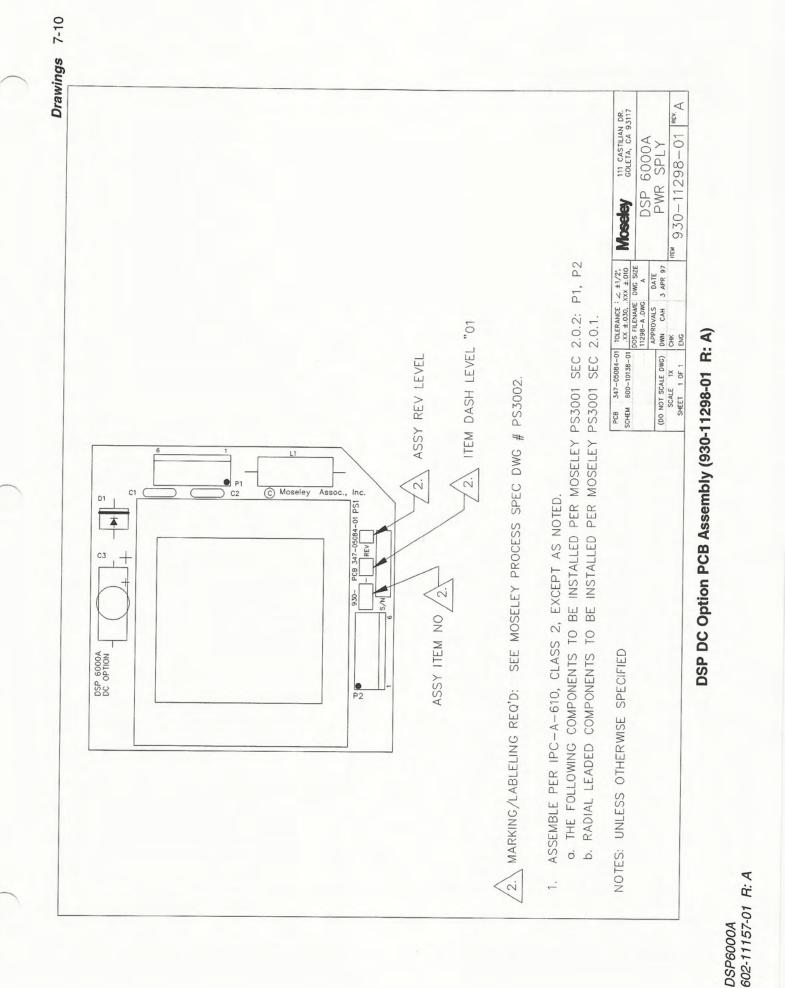

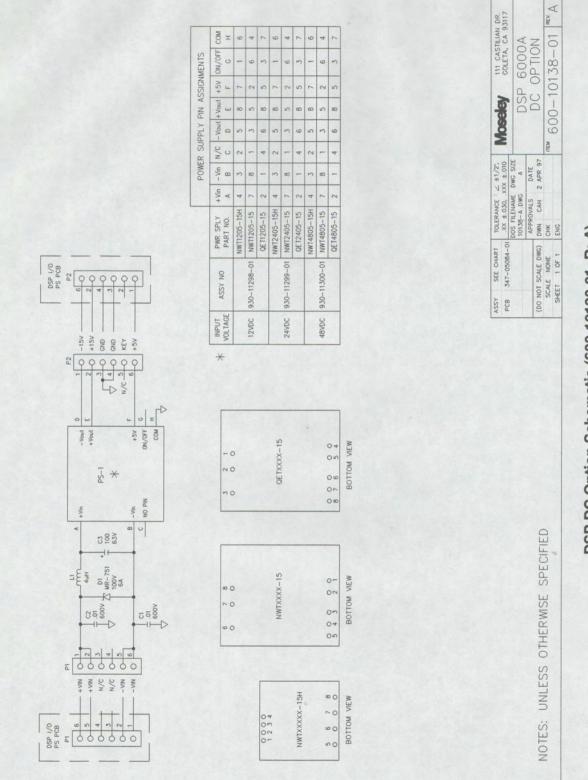

#### **DC Option**

The DC option uses a triple output DC-DC converter with a 12, 24, or 48V input. The linear regulators are bypassed on the I/O card. The inputs are isolated, allowing for positive or negative ground operation.

This page is intentionally blank.

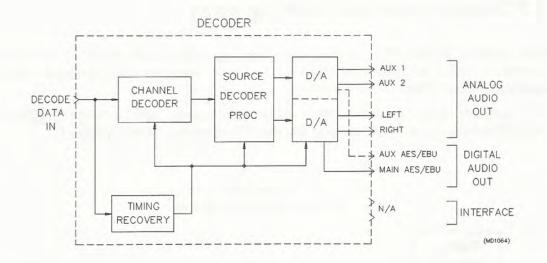

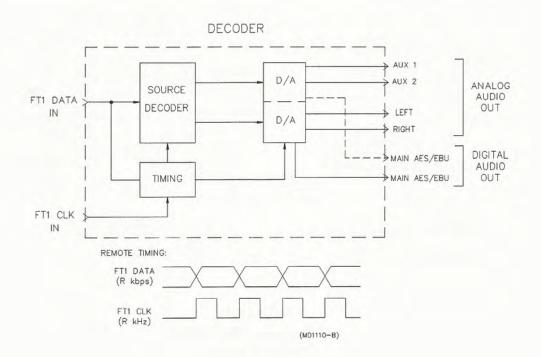

#### 1.4.2 DSP6000D Decoder Description

The DSP6000D is a digital audio decoder designed to work through existing STL receiving equipment or fractional T1 telco lines. The decoder accepts the recovered baseband signal at the STL receiver demodulator output which had originally been generated by the companion DSP6000E encoder and STL transmitter. From the STL baseband signal the decoder recovers the encoded data and associated data timing. For FT1 operation where an STL is not required the decoder accepts RS-422 data and timing directly. The data is demultiplexed into the original data subgroups, which are in turn converted back into discrete audio, formatted digital audio, and data channels.

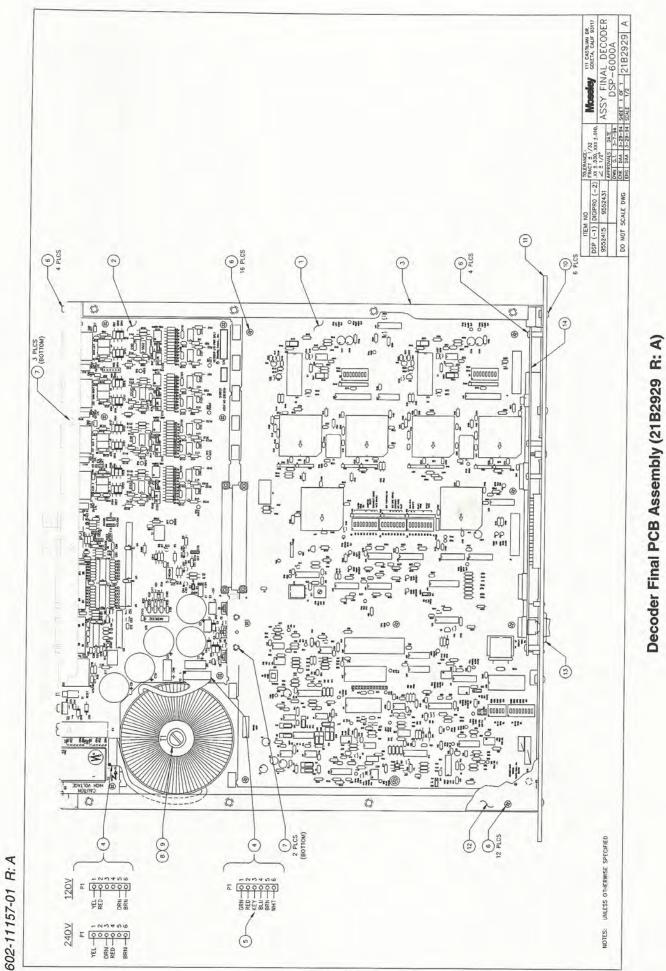

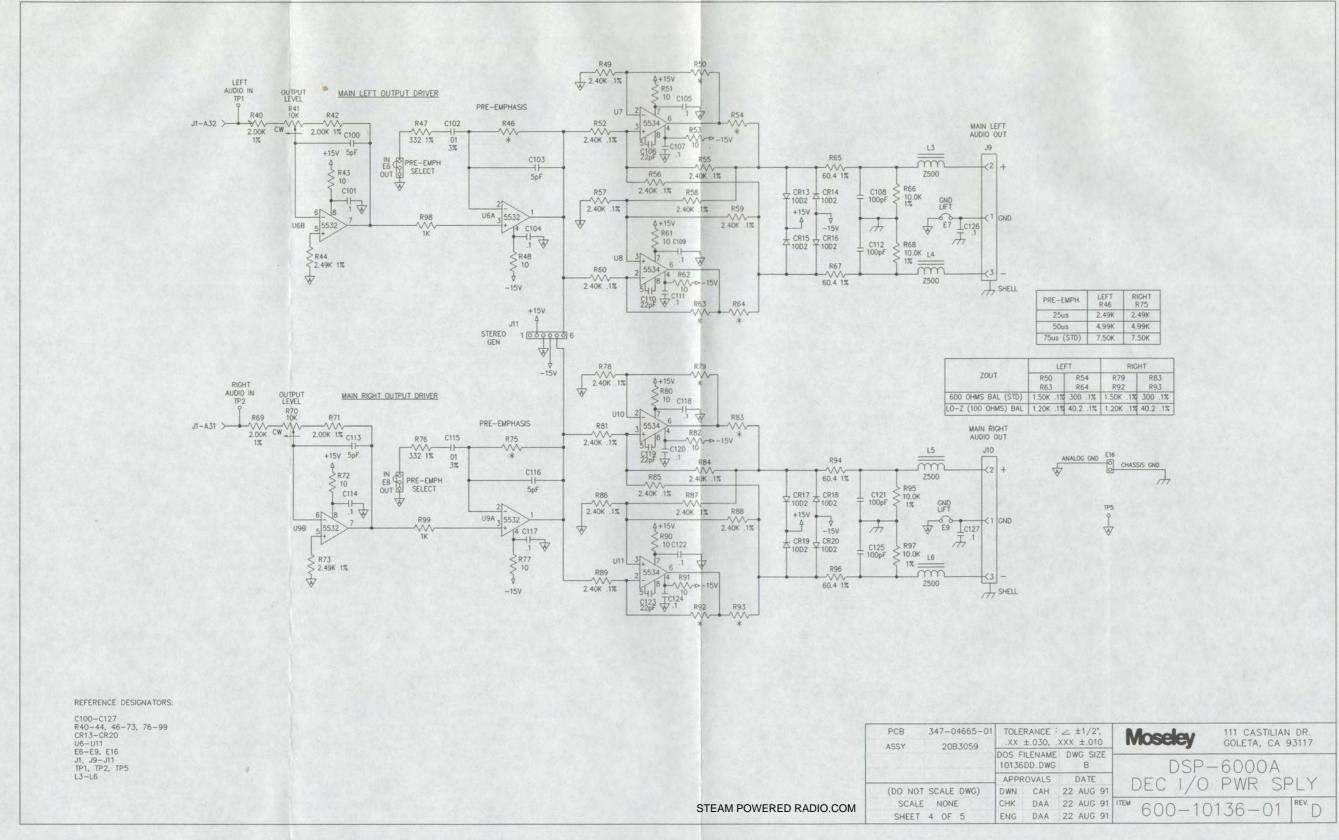

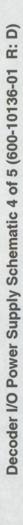

The decoder is physically partitioned into three printed circuit boards—the I/O board, the main processor board, and the display board. Functionally, the decoder is partitioned into six groups which are described below. Refer to Figure 1-3, Decoder Block and Level Diagram, for reference to this section.

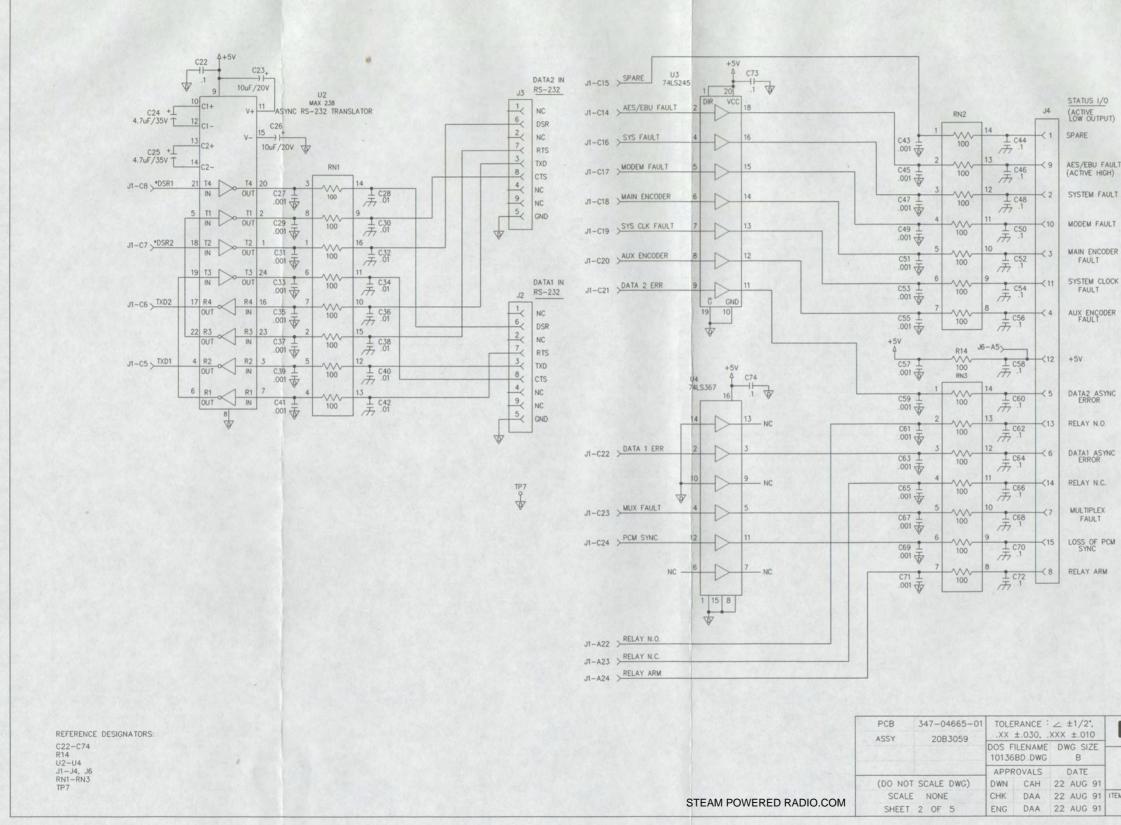

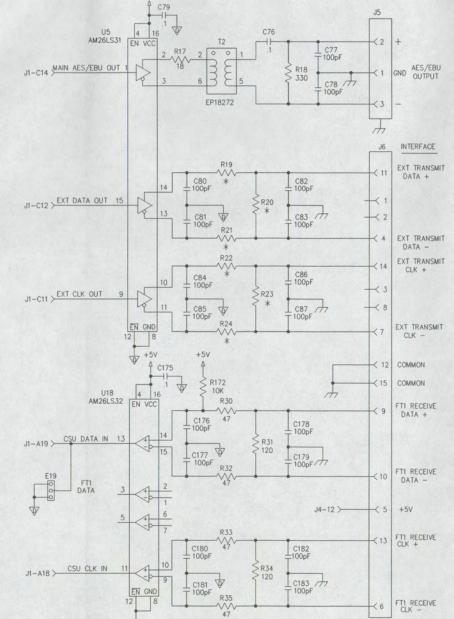

#### Audio-Digital I/O Interface (I/O Board)

The audio-digital I/O interface consists of four program audio active balanced outputs (LEFT, RIGHT, AUX 1, and AUX 2) with output level adjustments and selectable active de-emphasis, AES/EBU digital stereo outputs (both MAIN and AUX), RS-232 data outputs, RS-422 INTERFACE output, and buffered STATUS output. This board provides the appropriate signal conditioning, I/O buffering, and electromagnetic interference (EMI) protection between outside world and the main processor portion of the decoder.

#### Channel Decoder (Main Processor Board)

The channel decoder converts the encoded multilevel baseband signal from the STL receiver demodulator into the binary data stream that was originally generated at the input of the channel encoder portion of the DSP6000E encoder. The channel decoder consists of an active low-pass Bessel noise filter, automatic gain control, analog-to-digital convertor, ROM decoder, timing recovery phase-locked loop, data descrambler, data error detection, and BER (bit error rate) flag. The regenerated data stream is routed to the source decoder and to the external INTERFACE output port. The external output facilitates repeater operation or the use of alternate source decoding equipment. The channel decoder is bypassed for FT1 operation.

#### Source Decoder (Main Processor Board)

The source decoder performs the inverse operation of the source encoder of the DSP6000E, converting the serial bit stream back into audio and data channels. The source decoder consists of the demultiplexer, the ADPCM decoders, and the digital-to-analog (D/A) converters. The data stream from the channel decoder is demultiplexed into the original channel data streams. The ADPCM decoders convert serial 4-bit words into linear 16-bit PCM data. The PCM data is converted to formatted AES/EBU digital audio data for digital output, or to discrete audio by the D/A converters for analog output.

#### Timing and Control (Main Processor Board)

The channel configuration (1 to 4 audio channels with 1 or 2 data channels), the channel bandwidths (15 kHz or 7.5 kHz), and the resulting data transmission rate (64 kbps to 512 kbps) are determined through mode selection DIP switches M0 to M3. These settings will typically match that of the encoder for correct operation. Interface mode DIP switches M4, M5, and D1 configure data I/O at the INTERFACE port from the following: 1) program data output with internal synchronization for repeater operation or outboard source decoding, 2) program data output with external synchronization for FT1 operation, 3) AES/EBU digital audio output, or 4) raw PCM data output. RF spectral efficiency is selected between "standard" and "high" with DIP switch B4.

#### Status and Metering (Display Board)

This board contains the front panel indicator LED's. The peak program output level of the discrete audio channels is displayed in MAIN or AUX channel pairs on the dual LED bargraphs. Two bicolor LED's display signal and data-sync status. Two red LED's give indication of system failure and BER threshold. A yellow LED indicates individual data errors.

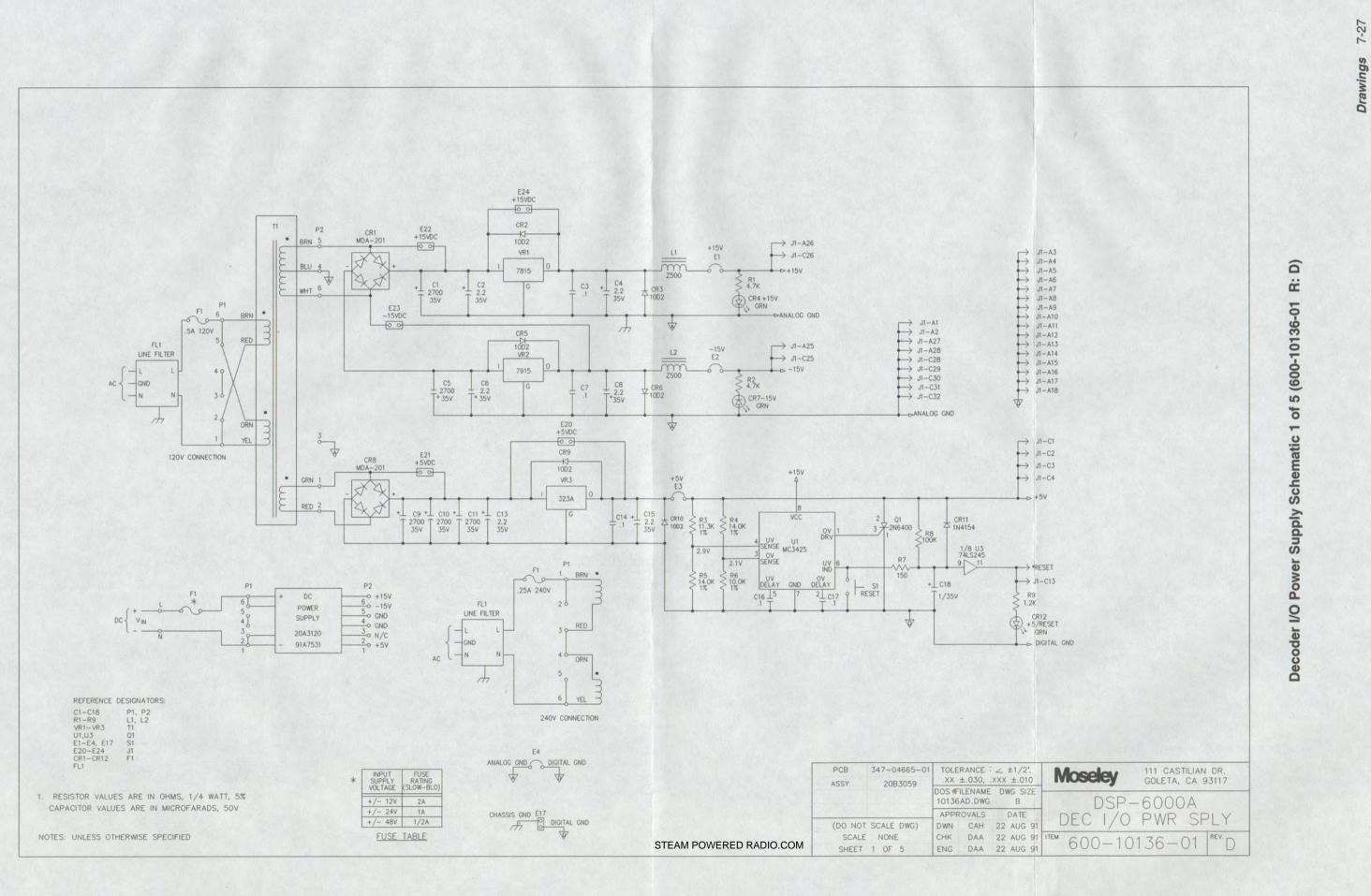

#### Power Supply (I/O Board)

The power supply converts AC line source (115 VAC or 230 VAC, internally wired) to three regulated voltages: +5 VDC, +15 VDC, and -15 VDC. Supervisory functions provide system reset for power-up and low voltage conditions (for example, power drop out or brown out) and crowbar/pull-down on the +5 VDC line during overvoltage conditions (for example, from a faulty regulator) to protect vital processing components.

#### Note

Once the crowbar is tripped the system may require a new fuse or manually removing and reapplying AC power to bring the system up.

#### **DC** Option

The DC option uses a triple output DC-DC converter with a 12, 24, or 48V input. The +5V and -15V linear regulators are bypassed on the I/O card; the +15V linear regulator is not bypassed, in order to maintain tighter regulation for critical decoder components. The inputs are isolated, allowing for positive or negative ground operation.

# Section 2

# Installation

| Section | Contents                                 | Page |

|---------|------------------------------------------|------|

| 2.1     | Unpacking                                | 2-2  |

| 2.2     | Power                                    | 2-2  |

| 2.2.1   | AC Line Voltage Selection                | 2-2  |

| 2.2.2   | DC Option Fuses                          | 2-4  |

| 2.3     | Pre-Installation Checkout                | 2-5  |

| 2.3.1   | Checkout of Encoder/Decoder Only         | 2-5  |

| 2.3.2   | Checkout of System — Encoder/STL/Decoder | 2-7  |

| 2.4     | Rack Installation                        | 2-9  |

| 2.5     | STL Installation                         | 2-10 |

| 2.5.1   | Encoder                                  | 2-10 |

| 2.5.2   | Decoder                                  | 2-12 |

| 2.5.3   | Air-Chain Processing                     | 2-14 |

| 2.5.4   | Repeater                                 | 2-16 |

| 2.6     | Fractional T1 (FT1) Installation         | 2-18 |

| 2.7     | Data Communications                      | 2-22 |

| 2.7.1   | Data Rate and Format Selection           | 2-22 |

| 2.7.2   | Remote Control Communication             | 2-23 |

| 2.7.2.1 | Subcarrier Communications                | 2-23 |

| 2.7.2.2 | FSK Communications                       | 2-23 |

| 2.7.2.3 | RS-232 Communications                    | 2-24 |

| 2.8     | Retrofit STL Installation                | 2-31 |

| 2.8.1   | PCL6010 Transmitter                      | 2-31 |

| 2.8.2   | PCL6020/6030/6060 Receiver               | 2-32 |

| 2.8.3   | PCL606 Transmitter, Mono                 | 2-36 |

| 2.8.4   | PCL606 Receiver, Mono                    | 2-38 |

| 2.8.5   | PCL606/C Transmitter, Composite          | 2-40 |

| 2.8.6   | PCL606/C Receiver, Composite             | 2-41 |

| 2.8.7   | PCL505 Transmitter, Composite            | 2-43 |

| 2.8.8   | PCL505 Receiver, Composite               | 2-44 |

| 2.8.9   | Other Radios                             | 2-45 |

| 2.8.10  | Retrofit Repeater Installation with STL  | 2-46 |

## 2.1 Unpacking

The DSP6000A Encoder and Decoder should be carefully unpacked and inspected for shipping damage. Should inspection reveal any shipping damage, visible or hidden, immediately file a claim with the carrier. Keep all packing materials at least until correct performance of the system is confirmed. If possible, save all packing materials in case the unit must be shipped in the future.

Units configured to order by the factory may be accompanied by additional components in the shipping container. These may not be required for the intended application, but should be retained for future reconfiguration.

We recommend removal of the top covers of both the encoder and decoder for a brief inspection of the internal components. Verify that assemblies and cables are mechanically secure. Check also for socketed components that may have been jarred loose or partially dismounted. This is a good time to familiarize yourself with the various assemblies, using the Block and Level diagrams (Figures 1-2 and 1-3) and the drawings of Section 7. After the internal inspection, replace the top covers or continue directly to Section 2.2.

### CAUTION

Do not make adjustments of any kind until the nature of each adjustment is understood.

Do not apply AC power to the encoder or decoder until the procedure in Section 2.2.1 is completed.

## 2.2 Power

The encoder and decoder are each capable of operating at one of the two nominal AC power source voltages of 115 or 230 VAC, 50–60 Hz. Optionally, one or both units may configured for 12, 24, or 48 VDC operation. Units are configured for 115 VAC operation when shipped, unless otherwise specified. See Section 2.2.1 for AC operation or Section 2.2.2 for DC operation.

### 2.2.1 AC Line Voltage Selection

The AC operating voltage is determined by the wiring of the power transformer inside the unit. To change the operating voltage configuration, rewire the transformer connector as shown in Figure 2-1. The electrical contacts can be extracted from the insulating connector shell by using a pointed tool to depress the detents, which are accessible through the side of the shell. Insert each contact into its new location until it is secured by the detent. Tug gently to verify the contact is correctly installed. If the operating voltage is changed, change the fuse also in accordance with the fuse ratings listed in Table 2-1 (also found on the rear panel of each unit).

# WARNING High voltage is present when the unit is plugged in. To prevent electrical shock, unplug the power cable before servicing. Unit should be serviced by qualified personnel only.

Figure 2-1 Transformer AC Wiring detail

| Table 2-1   |            |                    |  |  |

|-------------|------------|--------------------|--|--|

| Encoder and | Decoder AC | <b>Fuse Values</b> |  |  |

| Line Voltage | Encoder Fuse | Decoder Fuse |

|--------------|--------------|--------------|

| 115 VAC      | 1/2 Amp Slow | 1/2 Amp Slow |

| 230 VAC      | 1/4 Amp Slow | 1/4 Amp Slow |

## Section 2.2.2 DC Option Fuses

For DC operation, verify the correct fuse is installed in accordance with the fuse ratings listed in Table 2-2.

| Input Voltage | Encoder Fuse | Decoder Fuse |

|---------------|--------------|--------------|

| ±12 VDC       | 1 Amp Slow   | 1 Amp Slow   |

| ±24 VDC       | 1/2 Amp Slow | 1/2 Amp Slow |

| ±48 VDC       | 1/4 Amp Slow | 1/4 Amp Slow |

Table 2-2 Encoder and Decoder DC Fuse Values

## 2.3 Pre-Installation Checkout

While both encoder and decoder are at the same location, we suggest that a checkout of the system be performed before mounting the equipment in racks separated by many miles. This also allows for verification of fault conditions and mode selection, which will be discussed in subsequent sections.

#### 2.3.1 Checkout of Encoder/Decoder Only

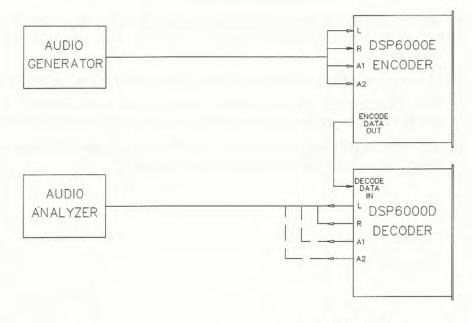

If the DSP6000A Encoder and Decoder were purchased to retrofit an existing system (that is, if the STL transmitter and receiver are currently installed at separate sites or are not readily available for back-to-back test) the encoder and decoder may be tested in back-to-back configuration, separate from the system. Figure 2-2 shows a typical bench test setup.

(MD1078-A)

Figure 2-2 Bench Test Setup for Encoder/Decoder Only

#### **Test Equipment**

Audio signal generator and analyzer (HP 339 or equivalent)

#### Procedure

1. Connect the system as shown in Figure 2-2 and apply AC power to the encoder and decoder. The presence of power is indicated by the green display mode LED's, MAIN or AUX, on both encoder and decoder.

On the encoder, the red FAULT LED and the bicolor AES/EBU LED should both be off.

On the decoder, the bicolor status LED's SIGNAL and SYNC should display green, while the red status LED's FAULT and BER, and the yellow status LED DATA ERROR should be all off within a few seconds after power-up.

2. Remove the signal from DECODE DATA IN on the decoder.

SIGNAL, SYNC, and FAULT should turn red and BER and DATA ERROR should turn on. Reconnect the signal to DECODE DATA IN.

Apply audio to the encoder audio input at +10 dBu. The display mode should be set to the appropriate channel, MAIN or AUX, for both encoder and decoder.

The encoder LED bar graph should be registering to the yellow (-3 dB) level.

The decoder LED bargraph should also register to the yellow (-3 dB) level, and the decoder output level should be approximately +10 dBm (600 ohms).

4. The input signal may be removed and the audio signal-to-noise ratio (SNR) measured using a 22 kHz measurement bandwidth.

# 2.3.2 Checkout of System — Encoder/STL/Decoder

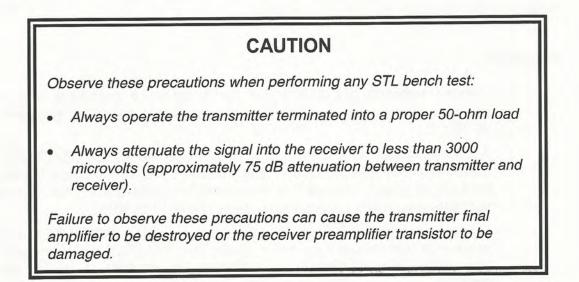

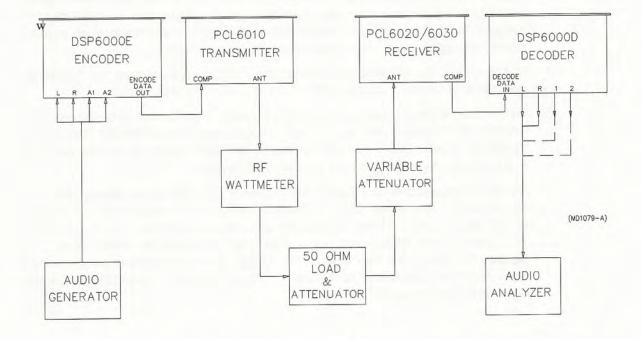

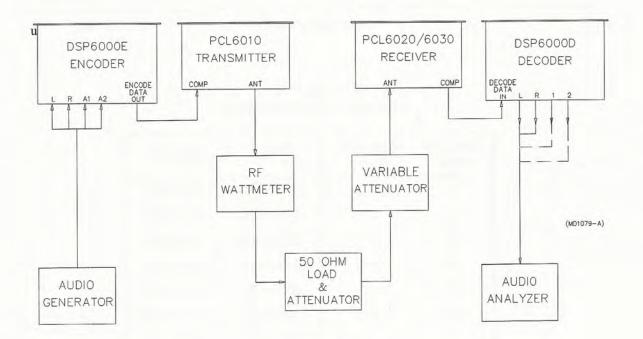

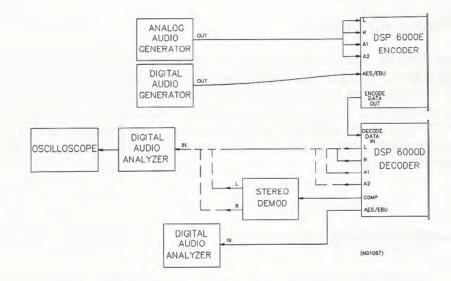

If the DSP6000A Encoder and Decoder were purchased as a system along with PCL6000 Studio-Transmitter Links, it is best to perform back-to-back tests of the entire system. Figure 2-3 shows a typical setup for bench test of a complete system. Refer also to the PCL6000 manual.

Figure 2-3 Bench Test Setup For Digital STL System

# **Test Equipment**

RF wattmeter with measurement range of 5–12 watts (Bird 43 or equivalent)

50 ohm, 10 watt dummy load for 950 MHz with 30 dB of attenuation output capability (Sierra 661A-30 or equivalent)

Variable attenuator, 0–100 dB at 950 MHz (Kay Model 432D or equivalent)

Audio distortion analyzer (HP 339 or equivalent)

## Procedure

- With the wattmeter and dummy load connected to the transmitter, apply AC power to the receiver. The SIGNAL LED will be red, indicating that there is no RF.

- 2. Apply AC power to the transmitter and place the OPERATE/STANDBY switch in the OPERATE position. The RADIATE and AFC LED's will change from red to green. Observe that the wattmeter indicates 5–8 watts and that the transmitter meter will provide readings of FWD POWER.

A brief period after the RADIATE LED turns green, the SIGNAL LED on the receiver should change from red to green. The RF LEVEL meter position on the receiver may be selected to determine the strength of the RF signal received.

- 3. Adjust the variable attenuator until an input signal strength of approximately 1000 microvolts is indicated. It should be noted that, in any bench test where the transmitter and receiver are in close proximity, there can be sufficient RF leakage from the cables to render impractical any computations of applied signal strength based upon power and attenuation data.

- 4. At this point, the encoder/decoder portion of the system may be tested as described in the prior section (that is, for encoder/decoder only).

- 5. This is also a good opportunity to verify threshold performance of the system. Increase the variable attenuation until the decoder DATA ERROR status LED begins to flicker. The STL receiver signal strength should be on the order of  $5 \mu$ V–10  $\mu$ V, depending on the system configuration.

As the attenuation is increased, the decoder BER (Bit Error Rate) red LED will eventually illuminate. This indicates an error rate in excess of 10<sup>-2</sup> (1 error in 100 bits of data). There will also be an audible click from the MUTE relay. This error rate is factory set but is internally selectable for other rates (see Section 5). Due to the nature of digital transmission, the system will transition from error-free operation to failure in only 2–4 dB of attenuation once the error threshold is reached.

This concludes the basic bench test of the units. The user may want to run further experiments to become familiar with the system. Before proceeding with higher level testing, consult Sections 1–3 for a thorough understanding of the DSP6000A system.

# 2.4 Rack Installation

#### NOTE

Always pre-test the system on the bench in its intended configuration prior to installation at a remote site.

The DSP6000A Encoder and Decoder are designed for mounting in standard rack cabinets, preferably between waist and shoulder height. The encoder and decoder have mounting holes for Chassis Trak C-300-5-1-14 chassis rack slides. If the rack will accept chassis rack slides, their use is recommended. When using rack slides, be sure to leave at least a 15-inch service loop in all cables to the equipment.

When mounted in a rack, the unit must have an unobstructed free flow of cooling air above and, if possible, below the unit. Continued operation in a confined environment can cause the ambient temperature to exceed specification, resulting in reduced life or system failure.

It is desirable to collocate the encoder with the STL transmitter to reduce the length of the interconnect cable. Similarly, the decoder should be located with the STL receiver. Due to strong electromagnetic interference (EMI) typical at a transmitter site, RF field conduction on long interconnect cables can adversely effect the system error performance and cause audio drop-outs.

NOTE

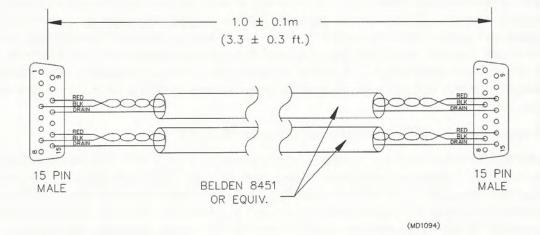

Avoid cable interconnection length in excess of 1 meter in strong RF environments.

We highly recommend installation of lightning protectors in the power lines to the encoder and decoder to prevent line surges from damaging expensive components.

In configurations of two STL transmitters with the DSP6000E Encoder, Moseley's TPT-2 transfer panel may be installed to provide automatic switchover upon detectable transmitter failure. The transmitters should not already incorporate automatic transfer. Mount the transfer panel between the transmitters, thereby allowing short cables and better ventilation.

For automatic switchover in systems using the DSP6000D Decoder with two STL receivers, install the MOSELEY TPR-2 transfer panel. The receivers should not already incorporate automatic transfer, and the TPR-2 should be mounted between them.

# 2.5 STL Installation

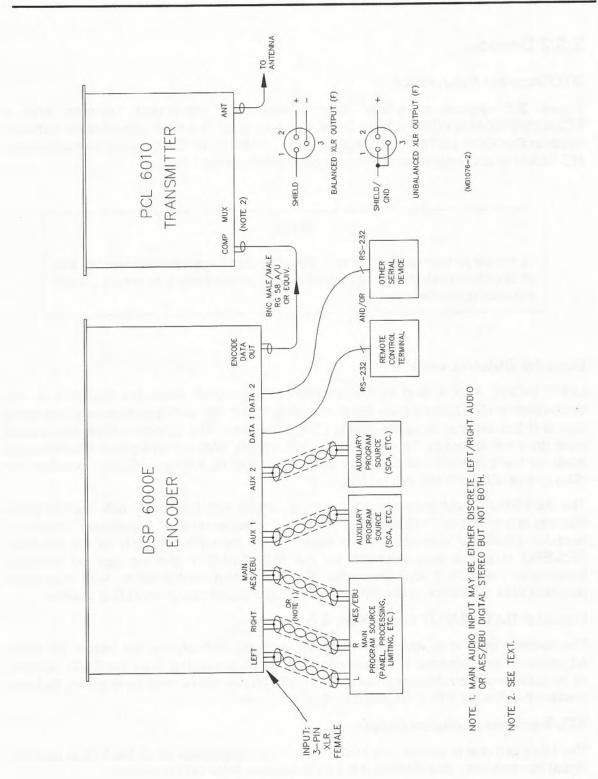

# 2.5.1 Encoder

# Encoder/STL Connection

Figure 2-4 depicts a typical interconnection of a DSP6000E Encoder with a PCL6010 STL transmitter for normal operation. The interconnect cable between encoder ENCODE DATA OUT and STL transmitter COMPOSITE IN should be coaxial type (RG-58A/U or equivalent) with BNC male connectors on each end.

## **Encoder Audio Input Levels**

LEFT, RIGHT, AUX 1, and AUX 2 discrete audio program levels are displayed on the peak-reading LED bargraph on the front panel. The 0 dB/100% point refers to full-scale input of the encoder analog-to-digital (A/D) converters. Audio inputs above this level are clipped, which causes distortion and sounds bad! Allow some headroom when setting the input levels. Apply audio program and set the input level for meter readings to the -3 dB (yellow) LED on the largest program peaks (the corresponding VU reading will be approximately 4-14 dB below the peak audio level displayed by the meter, depending on the program source material). Ideally, some form of peak limiting or leveling should precede the encoder audio inputs.

NOTE