# **BIOS User's Manual**

Version 1.2

Cypress Semiconductor 3901 North First Street San Jose, CA 95134 Tel.: (800) 858-1810 (toll-free in the U.S.) (408) 943-2600

www.cypress.com

### **Cypress Disclaimer Agreement**

The information in this document is subject to change without notice and should not be construed as a commitment by Cypress Semiconductor Corporation Incorporated. While reasonable precautions have been taken, Cypress Semiconductor Corporation assumes no responsibility for any errors that may appear in this document.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Cypress Semiconductor Corporation.

Cypress Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Cypress Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Cypress

Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Cypress Semiconductor and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Cypress Semiconductor was negligent regarding the design or manufacture of the product.

The acceptance of this document will be construed as an acceptance of the foregoing conditions.

BIOS User's Manual v1.2.

Copyright © 2003 Cypress Semiconductor Corporation.

All rights reserved.

## Chapter 1. BIOS Interface

| 1.1 Introduction                                         | 1-1  |

|----------------------------------------------------------|------|

| 1.1.1 Overview                                           | 1-1  |

| 1.1.2 General Notes                                      | 1-1  |

| 1.2 Development Utilities                                | 1-2  |

| 1.2.1 GNU Development Tools from RedHat                  |      |

| 1.3 BIOS Overview                                        | 1-2  |

| 1.3.1 CY16 Memory Map                                    |      |

| 1.3.2 BIOS Initialization Process                        |      |

| 1.3.3 Boot Control                                       | 1-8  |

| 1.3.3.1 SIE1 Host/Peripheral USB Initialization          | 1-8  |

| 1.3.3.2 Co-processor and Stand-alone Boot Control        | 1-8  |

| 1.4 Link Control Protocol (LCP)                          | 1-9  |

| 1.4.1 LCP Overview for Host Processor Interface (HPI)    | 1-9  |

| 1.4.1.1 Programming Overview                             | 1-10 |

| 1.4.2 LCP Overview for High Speed Serial (HSS)           | 1-10 |

| 1.4.3 LCP Overview for Serial Peripheral Interface (SPI) | 1-12 |

| 1.5 Hardware Interrupts                                  | 1-13 |

| 1.5.1 BIOS Hardware Interrupt Usage                      | 1-15 |

| 1.5.1.1 Interrupts Not Used by the BIOS                  | 1-15 |

| 1.5.1.2 Interrupts Used by the BIOS                      | 1-16 |

| 1.6 Debugging Tools support                              | 1-18 |

| 1.7 Software Interrupts                                  | 1-19 |

| 1.7.1 Interrupt 48-49: LCP Message Subroutines           | 1-21 |

| 1.7.2 Signature SCAN Support                             | 1-21 |

| 1.7.2.1 Interrupt 67: SCAN_INT                           |      |

| 1.7.2.1.1 Software Interface                             |      |

| 1.7.2.1.2 Example                                        |      |

| 1.7.2.2 Interrupt 79: SCAN_DECODE_INT                    |      |

| 1.7.2.2.1 Software Interface                             |      |

| 1.7.3 OTG Interrupt Functions                            |      |

| 1.7.3.1 Interrupt 50 (OTG_STATE)                         |      |

| 1.7.3.2 Interrupt 112 (OTG_STATE_INT)                    |      |

|                                                          |      |

| 1.7.3.3 Interrupt 88 (OTG Descriptor)                    |      |

| 1.7.3.4.1 Software Interface                             |      |

| 1.7.3.5 Interrupt 86 (REMOTE_WAKEUP_INT)                 |      |

| 1.7.3.5.1 Software Interface                             |      |

|                                                          |      |

| 1.7.4 USB Host Interrupt Functions                                    | 1-28 |

|-----------------------------------------------------------------------|------|

| 1.7.4.1 Interrupt 114/115: HUSB_SIE1_INIT_INT/ HUSB_SIE2_INIT_INT     | 1-29 |

| 1.7.4.1.1 Software Interface                                          | 1-29 |

| 1.7.4.1.2 Example:                                                    | 1-29 |

| 1.7.4.2 Interrupt 116: HUSB_RESET_INT                                 | 1-29 |

| 1.7.4.2.1 Software Interface                                          | 1-30 |

| 1.7.4.2.2 Example                                                     | 1-30 |

| 1.7.5 USB Peripheral Interrupt Functions                              | 1-30 |

| 1.7.5.1 Interrupt 113: SUSB_INIT_INT                                  | 1-31 |

| 1.7.5.1.1 Software Interface                                          | 1-31 |

| 1.7.5.1.2 Example                                                     | 1-31 |

| 1.7.5.2 Interrupt 90,106: SUSB1_DEVICE_DESCRIPTOR_VEC,                |      |

| SUSB2_DEVICE_DESCRIPTOR_VEC                                           |      |

| 1.7.5.2.1 Software Interface                                          |      |

| 1.7.5.2.2 Example                                                     | 1-33 |

| 1.7.5.3 Interrupt 91,107:SUSB1_CONFIGURATION_DESCRIPTOR_VEC,          |      |

| SUSB2_CONFIGURATION_DESCRIPTOR_VEC                                    |      |

| 1.7.5.3.1 Software Interface                                          |      |

| 1.7.5.3.2 Example                                                     | 1-36 |

| 1.7.5.4 Interrupt 92,108:SUSB1_STRING_DESCRIPTOR_VEC,                 |      |

| SUSB2_STRING_DESCRIPTOR_VEC                                           |      |

| 1.7.5.4.1 Software Interface                                          |      |

| 1.7.5.4.2 Example                                                     |      |

| 1.7.5.5 Interrupt 89,105:SUSB1_FINISH_INT, SUSB2_FINISH_INT           |      |

| 1.7.5.5.1 Software Interface                                          |      |

| 1.7.5.5.2 Example                                                     |      |

| 1.7.5.6 Interrupt 82,98: SUSB1_STALL_INT, SUSB2_STALL_INT             | 1-37 |

| 1.7.5.6.1 Software Interface                                          |      |

| 1.7.5.7 Interrupt 83,99: SUSB1_STANDARD_INT, SUSB2_STANDARD_INT       |      |

| 1.7.5.7.1 Software Interface                                          |      |

| 1.7.5.7.2 Example                                                     | 1-39 |

| 1.7.5.8 Interrupt 80, 96: SUSB1_SEND_INT, SUSB2_SEND_INT              |      |

| (Send data to USB SIE1,2 endpoint x respectively)                     |      |

| 1.7.5.8.1 Software Interface                                          |      |

| 1.7.5.8.2 Example                                                     | 1-41 |

| 1.7.5.9 Interrupt 81,97: SUSB1_RECEIVE_INT,                           |      |

| SUSB2_RECEIVE_INT (Receive data from USB endpoint x)                  |      |

| 1.7.5.9.1 Software Interface                                          |      |

| 1.7.5.9.2 Example                                                     |      |

| 1.7.5.10 Interrupt 85,101: SUSB1_VENDOR_INT, SUSB2_VENDOR_INT         |      |

| 1.7.5.10.1 Software Interface                                         |      |

| 1.7.5.10.2 Example                                                    |      |

| 1.7.5.11 Interrupt 87,103: SUSB1_CLASS_INT, SUSB2_CLASS_INT           |      |

| 1.7.5.11.1 Software Interface                                         |      |

| 1.7.5.11.2 Example                                                    |      |

| TO BE INDEPENDENCE OF THE SUSBELLUADER INTERIOR SUSBELLUADER INTERIOR | コーケン |

ii Table of Contents

| 1.7.5.12.1 Software Interface                                          | 1-52 |

|------------------------------------------------------------------------|------|

| 1.7.5.12.2 Example                                                     | 1-53 |

| 1.7.5.13 Interrupt 95,111:SUSB1_DELTA_CONFIG_INT,                      |      |

| SUSB2_DELTA_CONFIG_INT                                                 | 1-55 |

| 1.7.5.13.1 Software Interface                                          |      |

| 1.7.5.13.2 Example                                                     |      |

| 1.7.6 Interrupt 51-63 and 118-125                                      |      |

| 1.7.7 Memory Functions                                                 | 1-56 |

| 1.7.7.1 Interrupt 76: REDO_ARENA                                       | 1-56 |

| 1.7.7.2 Interrupt 69: Memory Data Pointer                              | 1-56 |

| 1.7.7.2.1 Software Interface                                           | 1-56 |

| 1.7.7.3 Interrupt 68: ALLOC_INT                                        |      |

| 1.7.7.3.1 Software Interface                                           |      |

| 1.7.7.3.2 Example                                                      | 1-57 |

| 1.7.7.4 Interrupt 75: FREE_INT                                         |      |

| 1.7.7.4.1 Software Interface                                           |      |

| 1.7.7.4.2 Example                                                      |      |

| 1.7.7.5 Interrupt 73: PUSHALL_INT                                      | 1-58 |

| 1.7.7.5.1 Software Interface                                           |      |

| 1.7.7.5.2 Example                                                      |      |

| 1.7.7.6 Interrupt 74: POPALL_INT                                       | 1-58 |

| 1.7.7.6.1 Software Interface                                           |      |

| 1.7.7.6.2 Example                                                      |      |

| 1.7.7.7 Interrupt 77: HW_SWAP_REG (Swap register bank)                 |      |

| 1.7.7.7.1 Software Interface                                           |      |

| 1.7.7.7.2 Example                                                      |      |

| 1.7.7.8 Interrupt 78: HW_REST_REG (Restore register bank)              | 1-60 |

| 1.7.7.8.1 Software Interface                                           | 1-60 |

| 1.7.7.8.2 Example                                                      |      |

| 1.7.8 BIOS Idle task functions                                         |      |

| 1.7.8.1 Interrupt 70: IDLE_INT                                         |      |

| 1.7.8.1.1 Software Interface                                           |      |

| 1.7.8.1.2 Example                                                      |      |

| 1.7.8.2 Interrupt 71: IDLER_INT                                        |      |

| 1.7.8.2.1 Example                                                      |      |

| 1.7.8.3 Interrupt 72: INSERT_IDLE_INT                                  | 1-63 |

| 1.7.8.3.1 Software Interface                                           |      |

| 1.7.8.3.2 Example                                                      |      |

| 1.7.9 Debugging Support functions                                      |      |

| 1.7.9.1 Interrupt 126-127 Reserved for Debugger                        |      |

| 1.7.10 Serial EEPROM support                                           |      |

| 1.7.10.1 Interrupt 64: 2-wire Serial EEPROM (from 256-byte to 2 KByte) |      |

| 1.7.10.1.1 Software Interface                                          |      |

| 1.7.10.2 Interrupt 65: 2-wire Serial EEPROM from (4 KByte to 64 KByte) | 1-68 |

| 1 7 11 LIAPT functions                                                 | 1-68 |

| 1.7.11.1 Interrupt 66: UART_INT                                    | 1-68 |

|--------------------------------------------------------------------|------|

| 1.7.11.1.1 Software Interface                                      |      |

| 1.7.11.1.2 Example                                                 | 1-70 |

| 1.7.11.2 Interrupt 123: KBHIT                                      |      |

| 1.7.11.2.1 Overview                                                | 1-70 |

| 1.7.11.2.2 Software Interface                                      |      |

| 1.7.11.2.3 Example                                                 | 1-70 |

| Chapter 2. Link Control Protocol Firmware                          |      |

| 2.1 Introduction                                                   | 2-1  |

| 2.1.1 Overview                                                     | 2-1  |

| 2.1.2 Scope                                                        | 2-1  |

| 2.2 Detailed Design                                                | 2-2  |

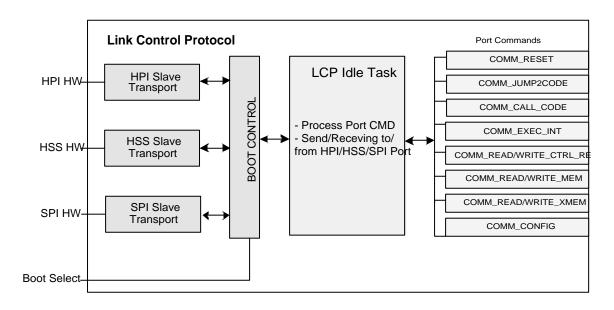

| 2.2.1 Architectural Outline                                        | 2-2  |

| 2.2.2 Transport Requirements                                       | 2-3  |

| 2.2.3 BIOS ROM Code (LCP)                                          | 2-3  |

| 2.2.3.1 Data Structures and Variables for Port Command Processing. | 2-3  |

| 2.2.3.2 Command Descriptions                                       | 2-4  |

| Chapter 3. USB Host BIOS Specifications                            |      |

| 3.1 Introduction                                                   |      |

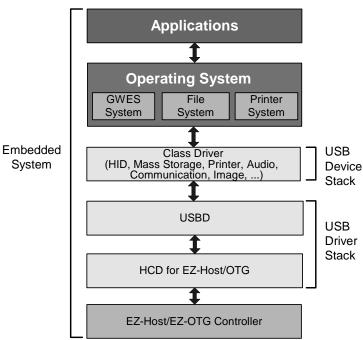

| 3.1.1 Co-processor Mode                                            | 3-1  |

| 3.1.2 Stand-alone Mode                                             | 3-2  |

| 3.2 Functional Requirements                                        | 3-2  |

| 3.3 USB Host BIOS Overview                                         | 3-2  |

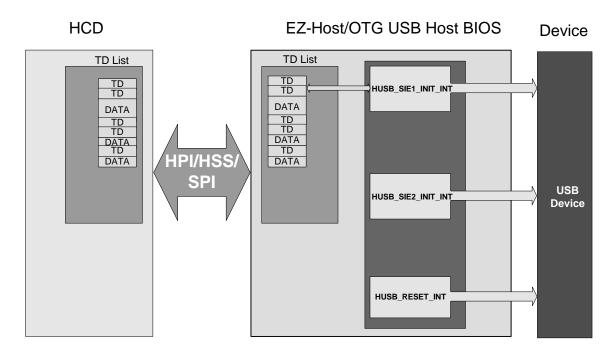

| 3.3.1 Block Diagram                                                | 3-2  |

| 3.3.1.1 HUSB_SIEx_INIT_INT                                         | 3-3  |

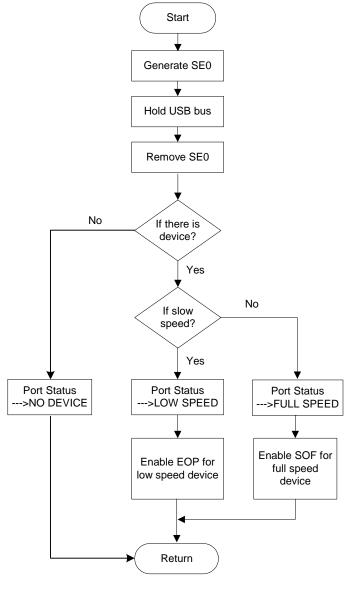

| 3.3.1.2 HUSB_RESET_INT                                             | 3-4  |

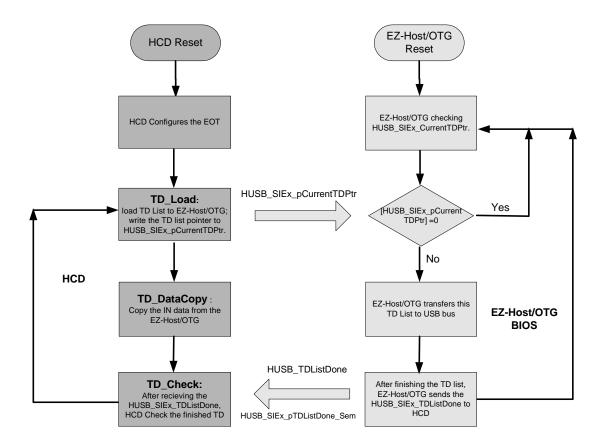

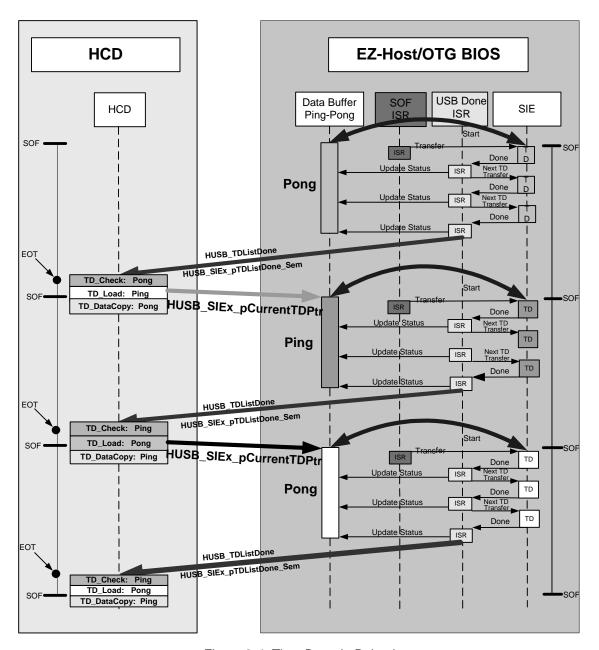

| 3.3.2 Flow Chart of USB Transfer                                   | 3-4  |

| 3.4 Software Interface Between HCD and BIOS                        | 3-6  |

| 3.4.1 TD Semaphore Address                                         | 3-7  |

| 3.4.1.1 HUSB_SIEx_pCurrentTDPtr                                    | 3-7  |

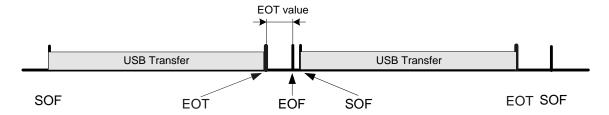

| 3.4.1.2 EOT and HUSB_pEOT                                          | 3-7  |

| 3.4.1.3 HUSB_SIEx_pTDListDone_Sem                                  | 3-8  |

| 3.4.2 TD SIE Mailbox Message                                       | 3-8  |

| 3.5 TD List Data Structure                                         | 3-9  |

| 3.5.1 BaseAddress (WORD: 0x00-01)                                  | 3-9  |

| 3.5.2 Port_Length (WORD: 0x02-03)                                  | 3-10 |

| 3.5.3 PID_EP (BYTE: 0x04)                                          |      |

| 3.5.4 DevAdd (BYTE: 0x05)                                          |      |

| 3.5.5 Control (BYTE: 0x06)                                         |      |

| 3.5.6 Status (BYTE: 0x07)                                          | 3-13 |

| 3.5.7 RetryCnt (BYTE: 0x08)                                        |      |

| 3.5.8 Residue (BYTE: 0x09)                                | 3-15 |

|-----------------------------------------------------------|------|

| 3.5.9 NextTDPointer (WORD: 0x0A-0B)                       | 3-15 |

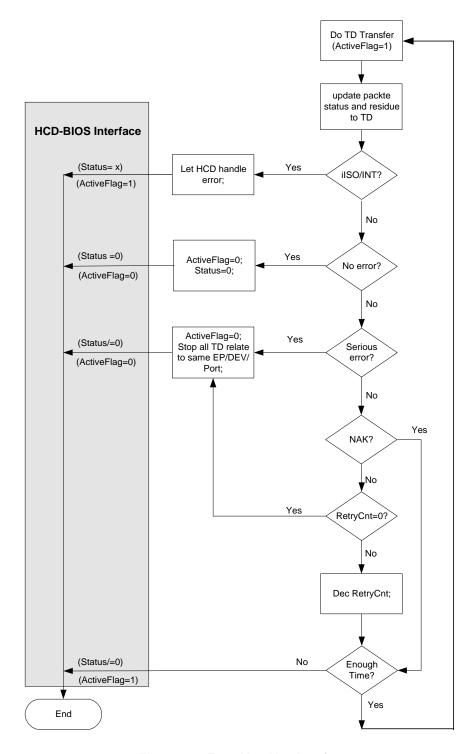

| 3.6 Error Handling                                        | 3-16 |

| 3.7 Schedule Bus Transaction Times                        |      |

| 3.8 Detail Design                                         |      |

| 3.8.1 HUSB_SIEx_INIT_INT                                  | 3-19 |

| 3.8.1.1 Software Interface                                | 3-19 |

| 3.8.1.2 Example:                                          | 3-19 |

| 3.8.2 HUSB_RESET_INT                                      | 3-19 |

| 3.8.2.1 Software Interface                                | 3-19 |

| 3.8.2.2 Example                                           | 3-20 |

| 3.8.2.3 Flow Chart                                        | 3-20 |

| Chapter 4. Slave Support Module Firmware                  |      |

| 4.1 Introduction                                          | 4-1  |

| 4.1.1 Overview                                            | 4-1  |

| 4.1.2 Scope                                               | 4-1  |

| 4.2 Functional Requirements                               | 4-1  |

| 4.3 Detailed Design                                       | 4-4  |

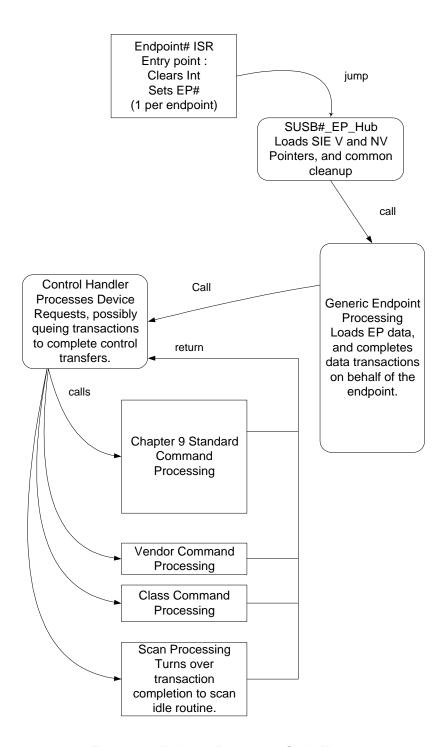

| 4.3.1 Endoint0 Processing Outline                         | 4-4  |

| 4.3.1.1 Behavior                                          | 4-4  |

| 4.3.1.2 Architecture                                      | 4-5  |

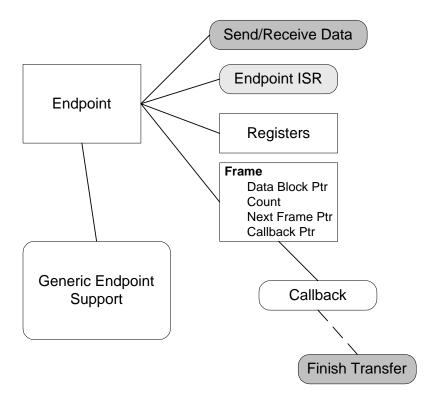

| 4.3.2 Generic Endpoint Support                            | 4-6  |

| 4.3.2.1 Behavior                                          | 4-6  |

| 4.3.2.2 Architecture                                      | 4-7  |

| 4.3.2.3 Data Structures                                   | 4-8  |

| 4.3.2.4 Code Structure                                    | 4-9  |

| 4.3.3 Reasons for Important Choices                       | 4-11 |

| Chapter 5. HPI Transport Module                           |      |

| 5.1 Introduction                                          | 5-1  |

| 5.1.1 Overview                                            | 5-1  |

| 5.1.2 Scope                                               | 5-1  |

| 5.2 Functional Requirements                               | 5-1  |

| 5.3 Detailed Design                                       | 5-1  |

| 5.3.1 HPI General Description                             | 5-1  |

| 5.3.2 HPI Signal Description                              |      |

| 5.3.3 Host DMA to/from EZ-Host/EZ-OTG Memory via HPI Port | 5-3  |

| 5.3.4 HPI INIT Routine                                    | 5-4  |

| 5.3.5 Host to EZ-Host/EZ-OTG MailBox Message              |      |

| 5.3.6 EZ-Host/EZ-OTG to Host MailBox Message              |      |

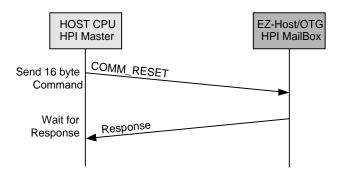

| 5.3.7 HPI TRANSFER DIAGRAMS FOR LCP                       | 5-5  |

| 5.3.7.1 COMM_RESET via HPI               | 5-5  |

|------------------------------------------|------|

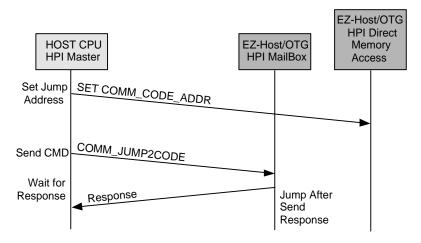

| 5.3.7.2 COMM_JUMP2CODE via HPI           | 5-5  |

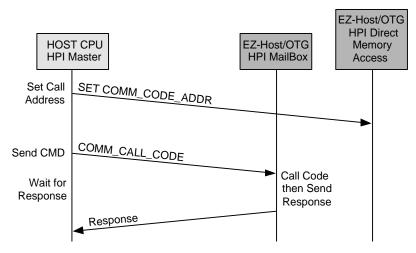

| 5.3.7.3 COMM_CALL_CODE via HPI           | 5-6  |

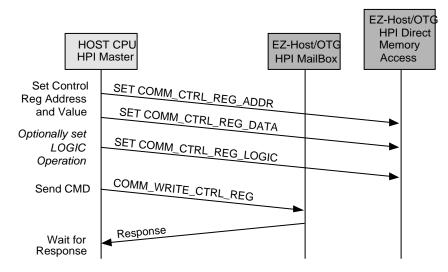

| 5.3.7.4 COMM_WRITE_CTRL_REG via HPI      | 5-7  |

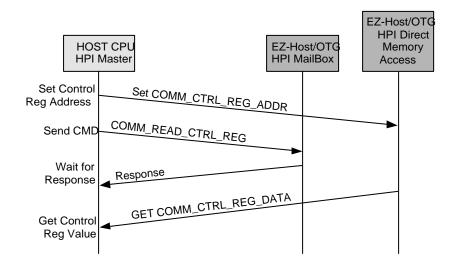

| 5.3.7.5 COMM_READ_CTRL_REG via HPI       | 5-8  |

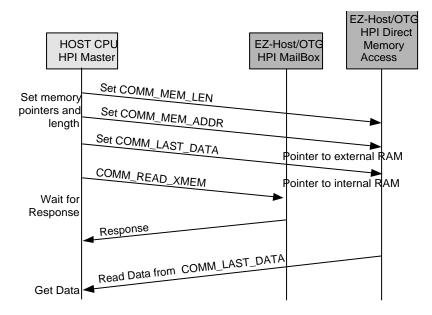

| 5.3.7.6 COMM_READ_XMEM via HPI           | 5-9  |

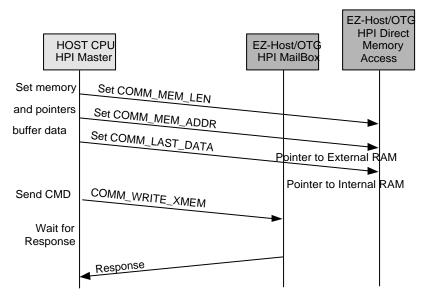

| 5.3.7.7 COMM_WRITE_XMEM via HPI          | 5-10 |

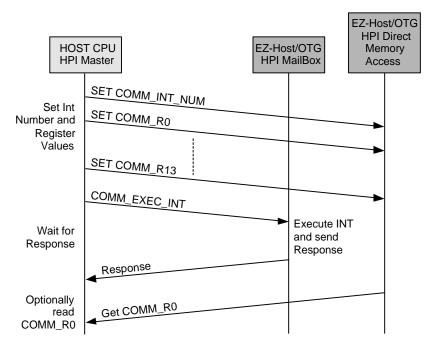

| 5.3.7.8 COMM_EXEC_INT via HPI            | 5-11 |

| Chapter 6. SPI Transport Module Firmware |      |

| 6.1 Introduction                         | 6-1  |

| 6.1.1 Overview                           | 6-1  |

| 6.1.2 Scope                              | 6-1  |

| 6.2 Functional Requirements              | 6-1  |

| 6.3 Detailed Design                      | 6-1  |

| 6.3.1 General Outline                    | 6-2  |

| 6.3.2 SPI INIT Routine                   | 6-2  |

| 6.3.3 SPI_RX_ISR                         | 6-2  |

| 6.3.4 SPI_Done_ISR                       | 6-2  |

| 6.3.5 SPI_Send_Blk Routine               | 6-3  |

| 6.3.6 SPI_Rec_Blk Routine                | 6-3  |

| 6.3.7 SPI polling the Status             |      |

| 6.3.8 SPI TRANSFER DIAGRAMS FOR LCP      | 6-4  |

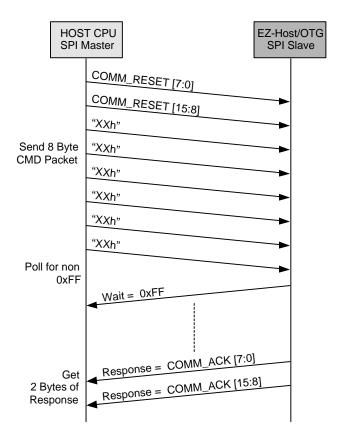

| 6.3.8.1 COMM_RESET via SPI               |      |

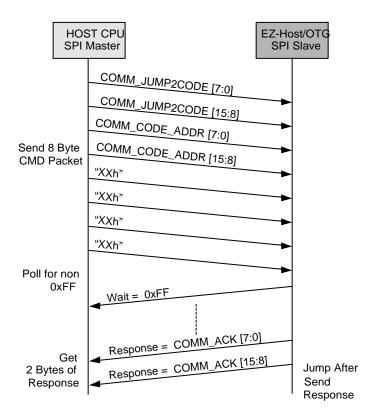

| 6.3.8.2 COMM_JUMP2CODE via SPI           |      |

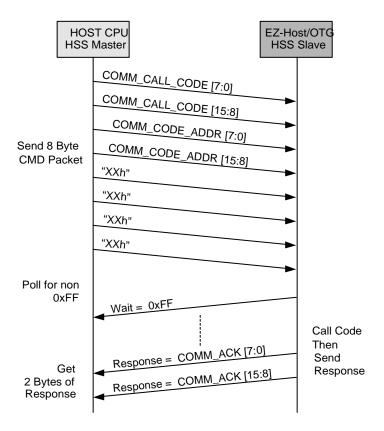

| 6.3.8.3 COMM_CALL_CODE via SPI           | 6-6  |

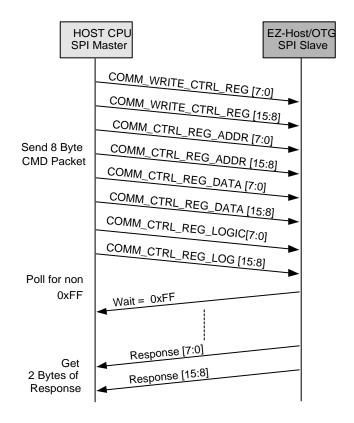

| 6.3.8.4 COMM_WRITE_CTRL_REG via SPI      |      |

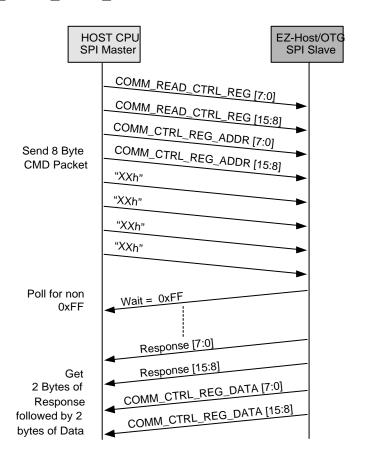

| 6.3.8.5 COMM_READ_CTRL_REG via SPI       |      |

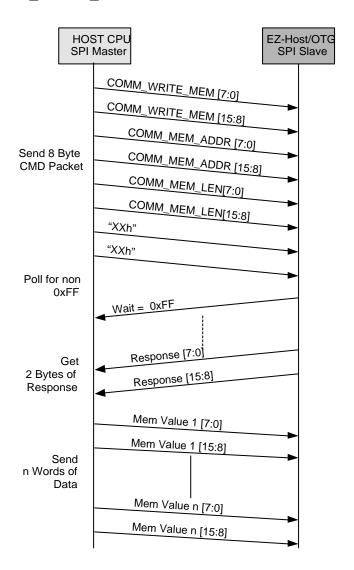

| 6.3.8.6 COMM_WRITE_MEM via SPI           |      |

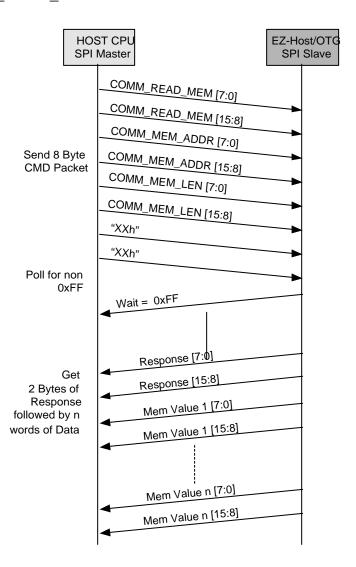

| 6.3.8.7 COMM_READ_MEM via SPI            |      |

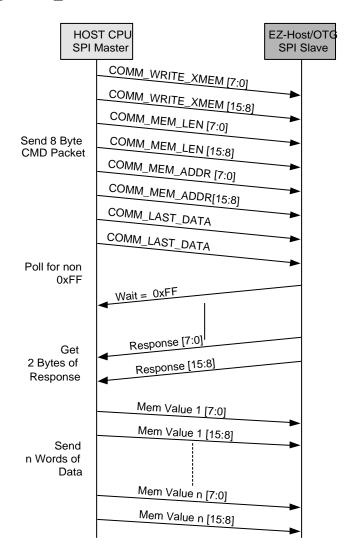

| 6.3.8.8 COMM_WRITE_XMEM via SPI          |      |

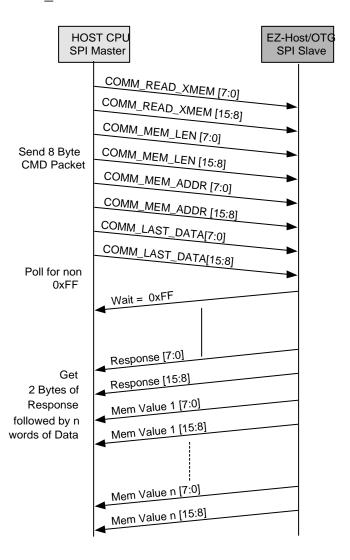

| 6.3.8.9 COMM_READ_XMEM via SPI           |      |

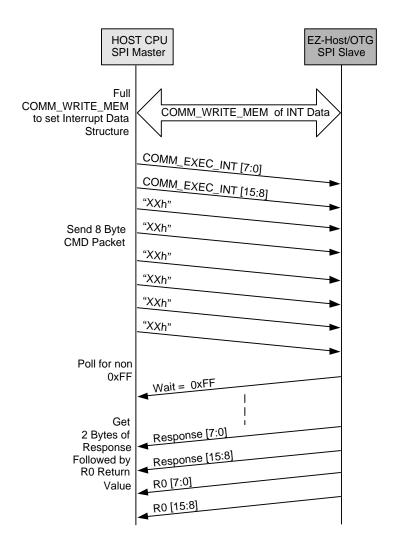

| 6.3.8.10 COMM_EXEC_INT via SPI           | 6-13 |

| Chapter 7. HSS Transport Module          |      |

| 7.1 Introduction                         |      |

| 7.1.1 Overview                           |      |

| 7.1.2 Scope                              |      |

| 7.2 Functional Requirements              |      |

| 7.3 Detailed Design                      | 7-1  |

| 7.3.1 General Outline                    |      |

| 7.3.2 HSS INIT Routine                   | 7-2  |

| 7.3.3 HSS RX ISR                         | 7-2  |

vi

| 7.3.4 HSS_DONE_ISR                  | 7-2          |

|-------------------------------------|--------------|

| 7.3.5 HSS_SEND_BLOCK Routine        |              |

| 7.3.6 HSS_RECEIVE_BLOCK Routine     | 7-3          |

| 7.3.7 HSS TRANSFER DIAGRAMS FOR LCP | 7-4          |

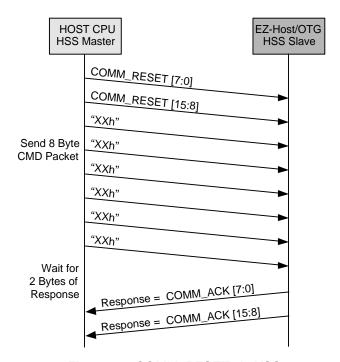

| 7.3.7.1 COMM_RESET via HSS          | 7-4          |

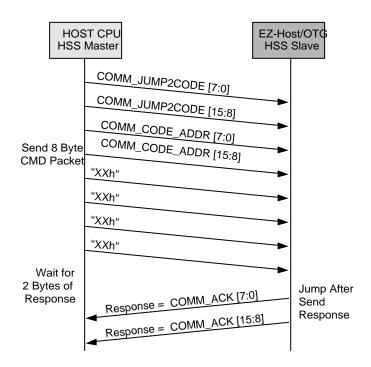

| 7.3.7.2 COMM_JUMP2CODE via HSS      | 7-5          |

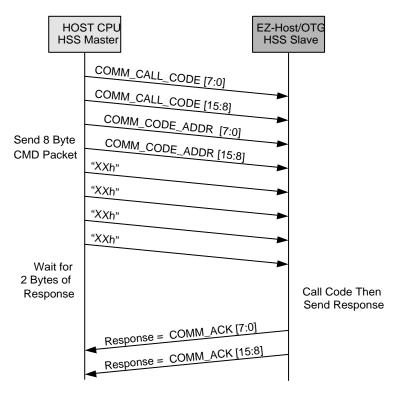

| 7.3.7.3 COMM_CALL_CODE via HSS      | 7-6          |

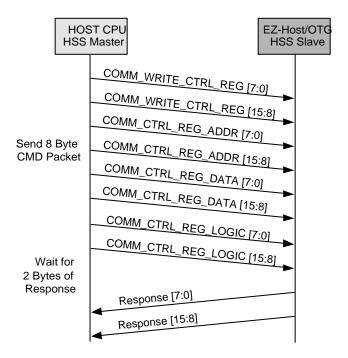

| 7.3.7.4 COMM_WRITE_CTRL_REG via HSS | 7-7          |

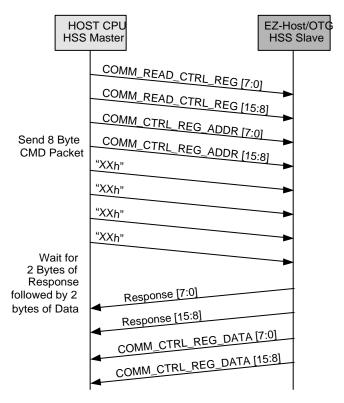

| 7.3.7.5 COMM_READ_CTRL_REG via HSS  | 7-8          |

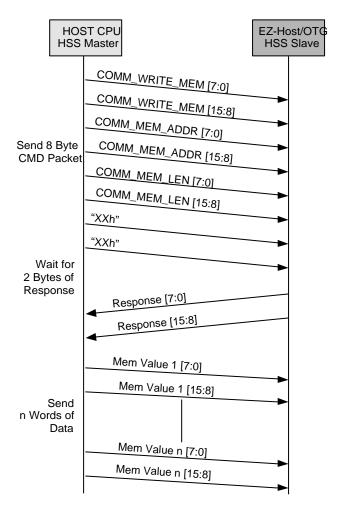

| 7.3.7.6 COMM_WRITE_MEM via HSS      | 7-9          |

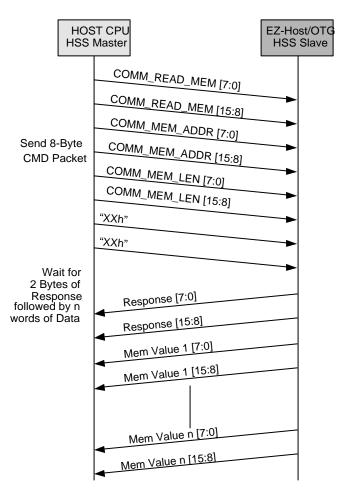

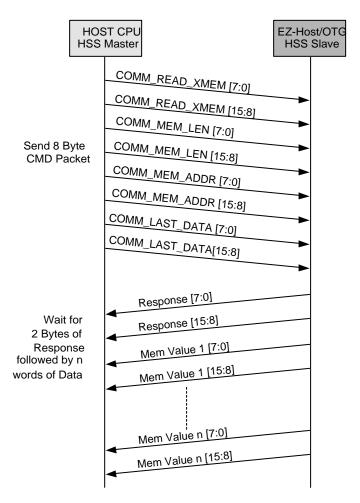

| 7.3.7.7 COMM_READ_MEM via HSS       | 7-10         |

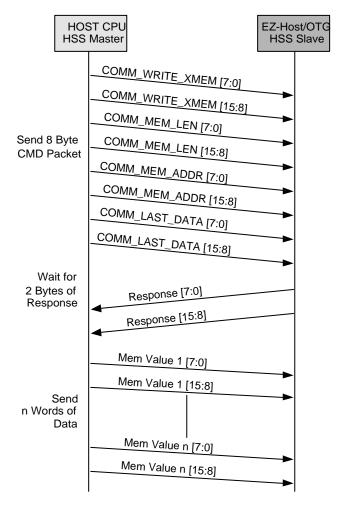

| 7.3.7.8 COMM_WRITE_XMEM via HSS     | 7-11         |

| 7.3.7.9 COMM_READ_XMEM via HSS      | 7-12         |

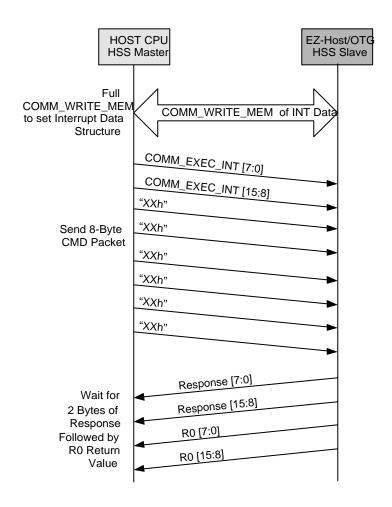

| 7.3.7.10 COMM_EXEC_INT via HSS      | 7-13         |

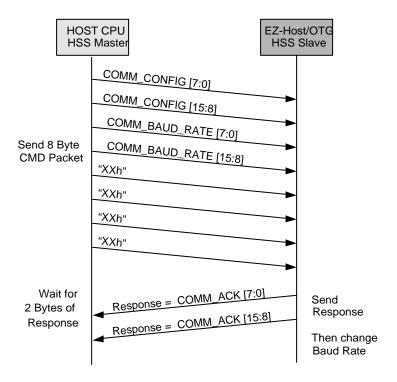

| 7.3.7.11 COMM_CONFIG via HSS        | 7-14         |

| Appendix A                          |              |

| Definitions                         | Appendix - 1 |

| Appendix B                          |              |

| References                          | Appendix - 3 |

| Appendix C                          |              |

| Revision History                    | Appendix - 5 |

| ,                                   | 1.1          |

Table of Contents Vii

viii Table of Contents

# List of Figures

| Figure 1-1. | Overview                                                  | 1-3  |

|-------------|-----------------------------------------------------------|------|

| Figure 1-2. | CY16 Memory Map                                           | 1-6  |

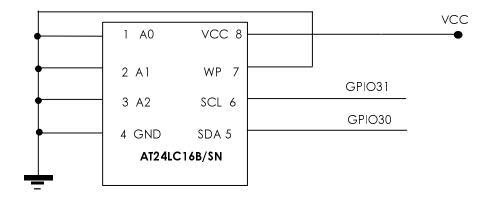

| Figure 1-3. | 2-wire Serial for up to 256 byte up to 2-KByte Connection | 1-66 |

| Figure 1-4. | 2-wire Serial from 4K up to 64-KByte Connection           | 1-66 |

| Figure 2-1. | Link Control Protocol                                     | 2-2  |

| Figure 3-1. | Co-processor Mode                                         | 3-1  |

| Figure 3-2. | Block Diagram of USB Host BIOS                            | 3-3  |

| Figure 3-3. | Flow Chart of USB Transfer                                | 3-5  |

| Figure 3-4. | Time Domain Behavior                                      | 3-6  |

| Figure 3-5. | End Of Transfer Point                                     | 3-8  |

| Figure 3-6. | Error Handling Interface                                  | 3-17 |

| Figure 3-7. | Flow chart of HUSB_RESET_INT                              | 3-20 |

| Figure 4-1. | Override-ability Dependency Stack                         | 4-3  |

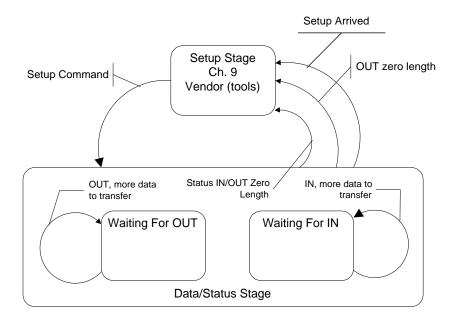

| Figure 4-2. | Control Transfer Handler State Diagram                    | 4-4  |

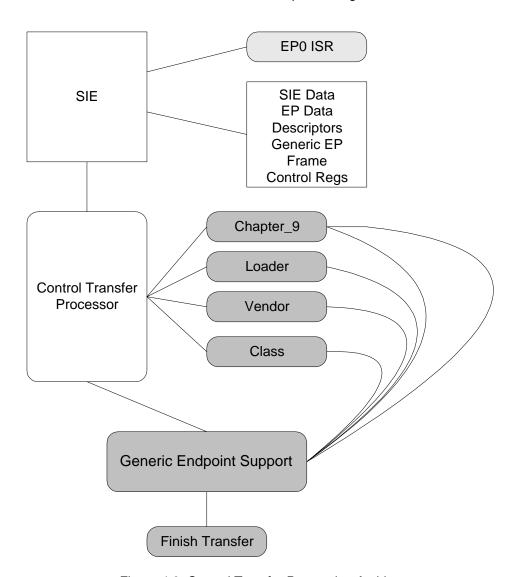

| Figure 4-3. | Control Transfer Processing Architecture                  | 4-5  |

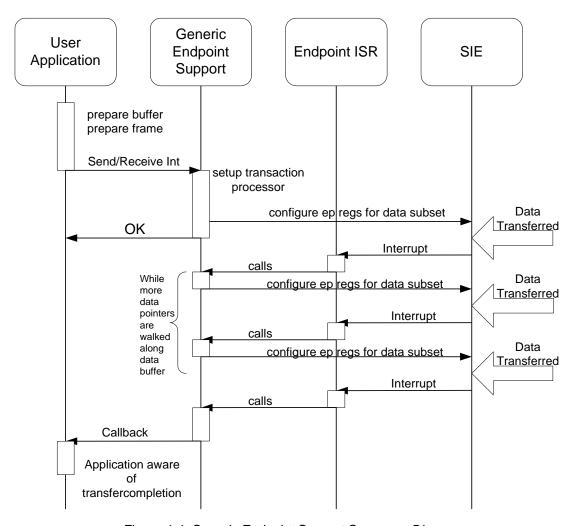

| Figure 4-4. | Generic Endpoint Support Sequence Diagram                 | 4-7  |

| Figure 4-5. | Generic Endpoint Support Architecture                     | 4-8  |

| Figure 4-6. | Endpoint Processing Code Flow                             | 4-10 |

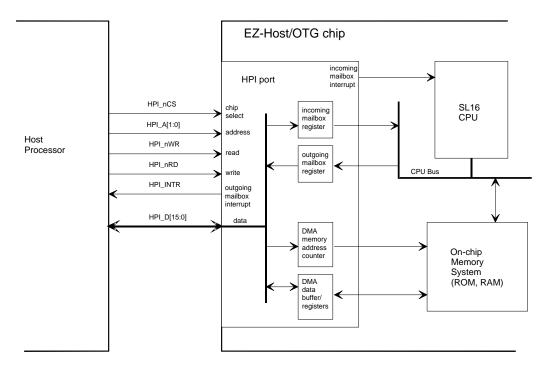

| Figure 5-1. | EZ-Host/EZ-OTG Chip                                       | 5-3  |

| Figure 5-2. | COMM_RESET via HPI                                        | 5-5  |

| Figure 5-3. | COMM_JUMP2CODE via HPI                                    | 5-5  |

| Figure 5-4. | COMM_CALL_CODE via HPI                                    | 5-6  |

| Figure 5-5. | COMM_WRITE_CTRL_REG via HPI                               | 5-7  |

| Figure 5-6. | COMM_READ_CTRL_REG via HPI                                | 5-8  |

| Figure 5-7. | COMM_READ_XMEM                                            | 5-9  |

| Figure 5-8. | COMM_WRITE_XMEM via HPI                                   | 5-10 |

| Figure 5-9. | COMM_EXEC_INT via HPI                                     | 5-11 |

| Figure 6-1. | COMM_RESET via SPI                                        | 6-4  |

| Figure 6-2. | COMM_JUMP2CODE via SPI                                    | 6-5  |

| Figure 6-3. | COMM_CALL_CODE via SPI                                    | 6-6  |

| Figure 6-4. | COMM_WRITE_CTRL_REG via SPI                               | 6-7  |

| Figure 6-5. | COMM_READ_CTRL_REG via SPI                                | 6-8  |

| Figure 6-6. | COMM_WRITE_MEM via SPI                                    | 6-9  |

| Figure 6-7. | COMM_READ_MEM via SPI                                     | 6-10 |

| Figure 6-8. | COMM_WRITE_XMEM via SPI                                   | 6-11 |

| Figure 6-9. | COMM_READ_XMEM via SPI                                    | 6-12 |

# (List of Figures)

| Figure 6-10. | COMM_EXEC_INT via SPI       | 6-13 |

|--------------|-----------------------------|------|

| Figure 7-1.  | COMM_RESET via HSS          |      |

| Figure 7-2.  | COMM_JUMP2CODE via HSS      | 7-5  |

| Figure 7-3.  | COMM_CALL_CODE via HSS      | 7-6  |

| Figure 7-4.  | COMM_WRITE_CTRL_REG via HSS | 7-7  |

| Figure 7-5.  | COMM_READ_CTRL_REG via HSS  | 7-8  |

| Figure 7-6.  | COMM_WRITE_MEM via HSS      | 7-9  |

| Figure 7-7.  | COMM_READ_MEM via HSS       | 7-10 |

| Figure 7-8.  | COMM_WRITE_XMEM via HSS     | 7-11 |

| Figure 7-9.  | COMM_READ_XMEM via HSS      | 7-12 |

| Figure 7-10. | COMM_EXEC_INT via HSS       | 7-13 |

| Figure 7-11. | COMM_CONFIG via HSS         | 7-14 |

List of Figures

# List of Tables

| Table 1-1. | Memory Map                                                                   | 1-5  |

|------------|------------------------------------------------------------------------------|------|

| Table 1-2. | Boot Control Pins                                                            | 1-8  |

| Table 1-3. | Commands Used for each Transport                                             | 1-9  |

| Table 1-4. | Hardware Interrupt Table                                                     | 1-13 |

| Table 1-5. | Interrupts not used by the BIOS                                              | 1-15 |

| Table 1-6. | Hardware Interrupt Table                                                     | 1-16 |

| Table 1-7. | Software Interrupt Table                                                     | 1-19 |

| Table 3-1. | TD List Data Structure                                                       | 3-9  |

| Table 3-2. | BaseAddress (WORD: 0x00-01)                                                  | 3-9  |

| Table 3-3. | Port_Length (WORD: 0x02-03)                                                  | 3-10 |

| Table 3-4. | PID_EP (BYTE: 0x04)                                                          | 3-11 |

| Table 3-5. | DevAdd (BYTE: 0x05)                                                          | 3-12 |

| Table 3-6. | Control (BYTE: 0x06)                                                         | 3-12 |

| Table 3-7. | Status (BYTE: 0x07)                                                          | 3-13 |

| Table 3-8. | RetryCnt (BYTE: 0x08)                                                        | 3-14 |

| Table 3-9. | NextTDPointer (WORD: 0x0A-0B)                                                | 3-15 |

| Table 4-1. | Standard Command (Chapter 9) Requirements                                    | 4-2  |

| Table 4-2. | Vendor Request Requirements                                                  | 4-2  |

| Table 4-3. | Generic Frame (1/ Send/Receive Request) Used by Generic Endpoint Processing. | 4-8  |

xii List of Tables

## Chapter 1 BIOS Interface

| 1 | .1  | 1 | otr | <b>0</b> | 1110 | tio  | n  |

|---|-----|---|-----|----------|------|------|----|

| • | _ / |   | ш   | UU       | IIC. | ,,,, | ,, |

#### 1.1.1 Overview

Cypress Semiconductor offers the industry's broadest portfolio of USB solutions. EZ-Host (CY7C67300) and EZ-OTG (CY7C67200) are two of Cypress's dual-role host/peripheral controllers. Although these devices are tailored toward different applications, they rely on many common core blocks. As a result they share the same microprocessor, the CY16 processor. Embedded within the internal ROM of these devices is a Basic Input Output System (BIOS) that is also common to both devices. This document describes the BIOS operation and software interrupts.

#### 1.1.2 General Notes

This specification assumes that you have some knowledge of the CY16 assembly language. You should read and understand the EZ-Host or EZ-OTG datasheet before attempting to read this document.

All numbers described in this document are marked as decimal numbers unless prefixed ("0x" for hexadecimal, "0b" for binary) and unless otherwise indicated, the contents of registers R0, R1, R2 and R8 may be lost.

Unless otherwise mentioned, if a register or memory location used as a pointer is zero, it is used as a NULL pointer, meaning that it does not point at anything.

If the specific USB controller that the BIOS is running on does not have the hardware associated with a particular software interrupt, the BIOS will return without effect.

## 1.2 Development Utilities

### 1.2.1 GNU Development Tools from RedHat

In order to support firmware development for the CY16 processor, Cypress provides a complete development system, including a GUI based Integrated Development Environment, Assembler, C Compiler, Linker, Debugger (GDB) and Binary Tools. For detailed information on the capabilities and use of this system, please refer to the documentation accompanying the tools. This development system may be used for creation of new application specific firmware, or to develop code that will replace or supplement functionality provided by the BIOS.

## 1.3 BIOS Overview

The BIOS consists mostly of interrupt service routines and a main/start-up routine. Other routines are typically not available to the user. Users should only use software vectors and not call arbitrary BIOS functions since these may move in newer versions of the BIOS.

Page 1-2 BIOS User's Manual v1.2

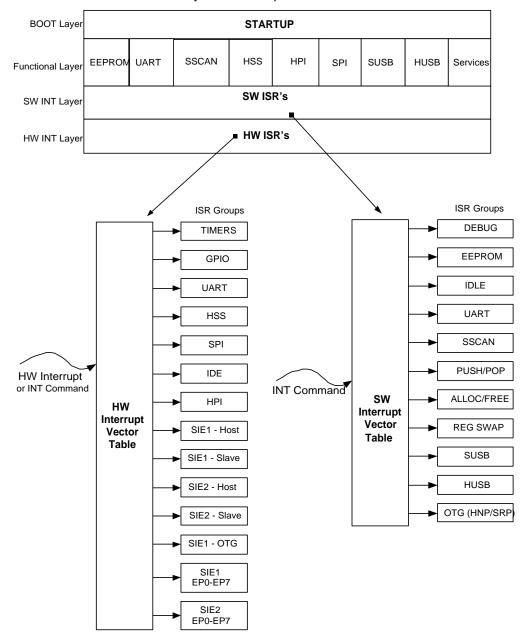

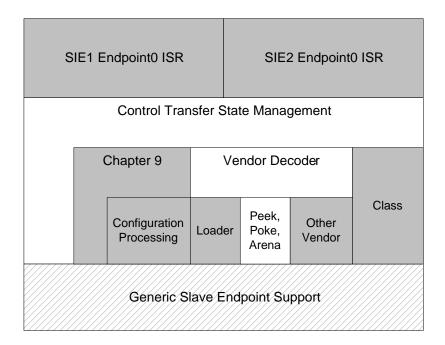

Figure 1-1 illustrates various BIOS layers and components.

Figure 1-1. Overview

### 1.3.1 CY16 Memory Map

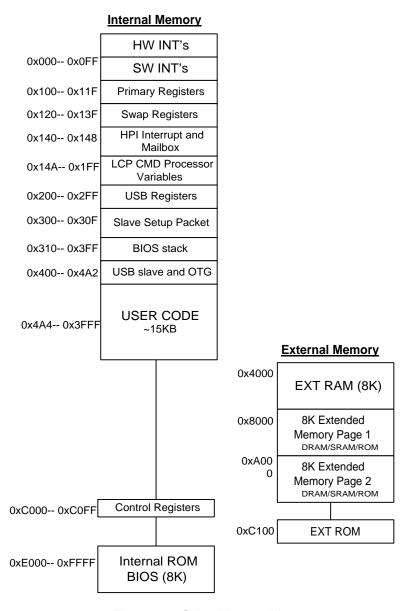

The total memory space directly addressable by the CY16 processor is 64 Kbytes. Program, data, and I/O space are contained within a 64 Kbyte address space. The program code or data can be stored in internal RAM, external RAM, or external ROM.

The EZ-Host device allows extended data or program code to be stored in external DRAM, SRAM, or ROM. The total size of extended memory can be up to 2 MByte. The CY16 processor can access extended memory via two address windows of 0x8000-0x9FFF and 0xA000-0xBFFF. The page-register 0xc018 is used to control the address window 0x8000-0x9FFF and the page register 0xC01A is used to control the address window of 0xA000-0xBFFF.

The HSS/HPI/SIE1/SIE2/SPI/IDE DMA engines ONLY transfer data between the support hardware to internal RAM (IRAM) and/or internal ROM (IROM). Setting up DMA to external memory space may result in internal RAM data corruption because the hardware does not check the address range. For example, setting up a DMA transfer to an external memory address like 0x8000 might result in a DMA transfer into address 0x0000.

The EZ-Host device provides a 16-bit memory interface that can support a wide variety of external DRAM, RAM, and ROM devices. At boot-up time, the BIOS attempts to detect 8-bit/16-bit external RAM and external ROM. For external RAM that is mapped to 0x4000-0x7FFF, BIOS attempts to check the size (8-bit/16-bit) via a write followed by a read verify. If there is SRAM connected to this BUS, it will allocate this RAM to become part of the BIOS memory space. If there is no SRAM connected to the bus, it will result in an 8-bit setting in the register 0xC03A.

If external ROM is mapped to the address 0xC100, which has a valid signatures scan (i.e. 0xC3B6 or 0xCB36), the BIOS will allow a boot-up from the external ROM code. BIOS can also auto detect booting up from an 8-bit external ROM or 16-bit external ROM using the special scan signatures at location 0xC100.

The BIOS will not setup the external memory space. The decision to connect either SRAM or ROM is left to the user.

The EZ-Host/EZ-OTG memory space is byte addressable. Table 1-1 shows how memory is divided (1k = 1024 bytes).

Page 1-4 BIOS User's Manual v1.2

Table 1-1. Memory Map

| Function                                                                                                                                                                                                                                                                   | Address                                                                                                                                                                                                                          | Memory size | Note    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|

| Internal RAM Hardware Interrupts Software Interrupts Primary Register Bank Swapped Register Bank HPI Interrupt and Mailbox LCP CMD Processor Variables USB Control Registers Slave Setup Packet BIOS Stack USB Slave and OTG Variables User Code/Data Space (Internal RAM) | 0x0000 - 0x3FFF<br>0x0000 - 0x007F<br>0x0080 - 0x00FF<br>0x0100 - 0x010F<br>0x0120 - 0x013F<br>0x0140 - 0x0148<br>0x014A - 0x01FF<br>0x0200 - 0x02FF<br>0x0300 - 0x030F<br>0x0310 - 0x03FF<br>0x0400 - 0x04A2<br>0x04A4 - 0x3FFF | 16 KBytes   |         |

| External RAM                                                                                                                                                                                                                                                               | 0x4000 – 0x7FFF                                                                                                                                                                                                                  | 16 KBytes   | 3       |

| Extended Page 1<br>DRAM/SRAM/ROM                                                                                                                                                                                                                                           | 0x8000 – 0x9FFF                                                                                                                                                                                                                  | 8 KBytes    | 1, 2, 3 |

| Extended Page 2<br>DRAM/SRAM/ROM                                                                                                                                                                                                                                           | 0xA000 – 0xBFFF                                                                                                                                                                                                                  | 8 KBytes    | 1, 2, 3 |

| Memory Mapped Registers                                                                                                                                                                                                                                                    | 0xC000 - 0xC0FF                                                                                                                                                                                                                  | 256 Bytes   |         |

| External ROM/External SRAM                                                                                                                                                                                                                                                 | 0xC100 - 0xDFFF                                                                                                                                                                                                                  | 7,936 Bytes | 3       |

| Internal ROM                                                                                                                                                                                                                                                               | 0xE000 – 0xFFFF                                                                                                                                                                                                                  | 8K Bytes    |         |

#### NOTES:

- If code is contained in the Extended Memory Pages, only 32K is usable because the CY16 RISC Core has 16-bit address generation.

- 2. If used for ROM space total ROM space is 16K+7936.

- 3. The external memory interfaces are only available on the EZ-Host and not on EZ-OTG

Figure 1-2 illustrates how memory is organized. Each external memory space can be 8- or 16-bits wide, and can be programmed to have up to seven wait states. On power-up, the BIOS sets all the default external memory wait state at 7-wait states (i.e. Register 0xC03A will be initialized to 0x27F7).

Note: Each memory wait state results in an extra 20.8ns added to the read/write cycle.

Figure 1-2. CY16 Memory Map

M

**Note:** The external memory interface is only available on the EZ-Host device.

Page 1-6 BIOS User's Manual v1.2

#### 1.3.2 BIOS Initialization Process

On reset, the BIOS performs the following:

- Hardware reset Sets the speed control register to divide by 16 ([0xC008] = 0x000F).

This provides the CY16 processor with a 3 MHz clock. Sets the program counter to 0xFF00.

- Jumps to 0xE000, the start of BIOS ROM code.

- Sets call stack pointer (r15) to 0x400.

- Sets the speed control register to zero ([0xC008] = 0x0) and disables global interrupt.

- The BIOS then sets the external memory control register for a 16-bit XROM and 16-bit XRAM five wait states ([0xC03A] = 0x2777).

- If an external ROM contains the pattern 0xCB36 in location 0xC100, the BIOS immediately jumps to location 0xC102.

- The BIOS then tests ROM at location 0xC100 for the pattern 0xC3B6 in 8-bit mode. If the

external ROM shows only the pattern 0xB6, then bit 7 of the external memory control register (0xC03A) is set to one for 8-bit operation. In the EZ-OTG device (i.e., the 48-pin

package) the BIOS sets up from 8-bit ROM mode to GPIO mode, if the BIOS does not

detect any valid scan signatures.

- Sets 0xC018 = 0 (page0: from 0x8000-0x9FFF) and 0xC01A = 1 (page1: from 0xA000-0xBFFF).

- Tests and enables RAM at location 0x6000 for 8- or 16-bit operation as appropriate.

- Sets the global interrupt enable register (0xC00E) to zero.

- Initializes hardware/software interrupt vectors.

- Initializes arena information (memory management).

- Initializes hardware for serial EEPROM and UART

- Initializes software for LCP idle task and USB idle task.

- Performs BOOT CONTROL (see Section 1.3.3, "Boot Control").

- Performs SCAN\_INT if data at ROM address 0xC100 = 0xC3B6.

- Enters execution idle tasks and waits for interrupts.

#### 1.3.3 Boot Control

Two pins (GPIO [30:31]) on the EZ-Host and EZ-OTG devices are used for boot control. The boot control is used to configure the device for Host or peripheral operation and to select a communication port for connection to an external processor.

### 1.3.3.1 SIE1 Host/Peripheral USB Initialization

GPIO 29 (OTG ID pin) is used to select either Host USB initialization or peripheral USB initialization.

#### 1.3.3.2 Co-processor and Stand-alone Boot Control

EZ-Host and EZ-OTG devices can be used in two basic configurations: stand-alone mode and coprocessor mode. In stand-alone mode the chip is not connected to an external CPU of any kind. Application specific firmware must be run on the internal processor. One option for loading this code is to use an external EEPROM, which is selected using the boot control pins.

In co-processor mode the chip is connected to an external master via one of three possible interfaces: Host Processor Interface (HPI), High Speed Serial (HSS), or Serial Peripheral Interface (SPI). The BIOS uses the boot control pins to determine the default port. This port is used to load code and data, and is monitored for Link Control Protocol (LCP) commands.

GPIO pins 30 and 31 are used as the boot control pins. The possible configurations are described below:

| GPIO 31 | GPIO 30 | Mode         | Boot Port and Baud           |

|---------|---------|--------------|------------------------------|

| 0       | 0       | co-processor | HPI                          |

| 0       | 1       | co-processor | HSS GPIO mode, Baud = 115.2K |

| 1       | 0       | co-processor | SPI GPIO mode                |

| 1       | 1       | stand-alone  | EEPROM                       |

Table 1-2. Boot Control Pins

#### Note:

- \* In co-processor mode all USB ports are disabled at power-up and must be turned on the external processor using LCP commands. For example, in peripheral mode the chip will not respond to any USB commands from the host until the ports have been enabled.

- \* In stand-alone mode, the USB-PortC always goes into full speed peripheral mode, which is dedicated for the debugger usage. The USB-PortA goes into peripheral mode if GPIO29 is high, and goes into host mode when GPIO29 is low.

- \* In stand-alone mode, users can use the serial EEPROM to over-ride the default mode for both USB-PortA and USB-PortC. In this mode, BIOS will use SCAN\_INT so user applications can be loaded into RAM from the EEPROM.

Page 1-8 BIOS User's Manual v1.2

## 1.4 Link Control Protocol (LCP)

The link control protocol allows an external processor to have full access and control over the EZ-Host/EZ-OTG devices. The boot control determines which interface (HPI/HSS/SPI) will be enabled for receiving LCP commands on power-up. The LCP commands are common for all interfaces but the communication protocol varies slightly between them due to capability differences of the interfaces. This section describes the methods used to access the EZ-Host/EZ-OTG devices via each of the three interfaces.

The BIOS does not support queuing of LCP commands. Only one LCP command may be executed at one time.

The following table shows which LCP commands are available and useful for each port.

Table 1-3. Commands Used for each Transport

| LCP Command         | HPI<br>Transport | HSS<br>Transport | SPI<br>Transport |

|---------------------|------------------|------------------|------------------|

| COMM_RESET          | Yes              | Yes              | Yes              |

| COMM_JUMP2CODE      | Yes              | Yes              | Yes              |

| COMM_CALL_CODE      | Yes              | Yes              | Yes              |

| COMM_EXEC_INT       | Yes              | Yes              | Yes              |

| COMM_READ_CTRL_REG  | Yes              | Yes              | Yes              |

| COMM_WRITE_CTRL_REG | Yes              | Yes              | Yes              |

| COMM_READ_MEM       | Yes*             | Yes              | Yes              |

| COMM_WRITE_MEM      | Yes*             | Yes              | Yes              |

| COMM_READ_XMEM      | Yes              | Yes              | Yes              |

| COMM_WRITE_XMEM     | Yes              | Yes              | Yes              |

| COMM_CONFIG         | Yes*             | Yes              | Yes*             |

Note: \*BIOS returns COMM\_ACK ONLY.

## 1.4.1 LCP Overview for Host Processor Interface (HPI)

Refer to Chapter 5, "HPI Transport Module" for a complete discussion on this topic.

HPI is a dual channel interface. By default, the BIOS uses the HPI direct memory access for memory read/write of data, and the mailbox for LCP commands and responses.

LCP commands are always sent in a 16-bit word, and a 16-bit response is expected. A sequence diagram of each LCP command is given in Chapter 5.

VI

Note: Unless specifically mentioned, all responses are either COMM\_ACK or COMM\_NAK.

#### 1.4.1.1 Programming Overview

HPI functionality is such that the following operations should happen for each LCP Command that is issued:

- Any data required for the LCP CMD is sent via HPI DMA (i.e., COMM\_CODE\_ADDR).

- The LCP command is then sent via HPI mailbox.

- The HPI status register is polled (or an ISR is used) to wait for mailbox response back from the BIOS.

- The response is then read from the mailbox.

- Any additional data from CMD execution is read using HPI DMA (i.e., COMM\_CTRL\_REG\_DATA).

## 1.4.2 LCP Overview for High Speed Serial (HSS)

Refer to Chapter 7, "HSS Transport Module" for complete details on this topic.

HSS is a full-duplex interface. By default, the BIOS sets up the HSS port as a simple 2-wire interface with no hardware or software handshaking.

LCP commands are always sent in an 8-byte packet. This packet contains the 16-bit LCP command and in some cases additional data for the command (like address and length of data to follow). When the Host sends down a command, the Host must be ready to receive the resultant data via an ISR.

A sequence diagram of each LCP command is given in Chapter 7.

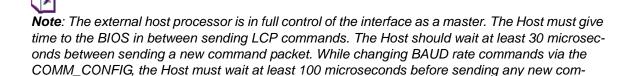

mands with the new baud rate.

Page 1-10 BIOS User's Manual v1.2

```

bool hss_xfer(char *cmd; int len; char *buf)

int i, stat;

bool data_wr=FALSE;

if (len>2048) return FALSE; // (*) hss HW support upto 1024-words

for (i=0; i<8; i++)

HSS_Write_byte(cmd[i]); // (8-byte commands) no delay here

// Read ACK/NAK status:

stat=HSS_Read_byte();

stat = (HSS_Read_byte() << 8) + stat;</pre>

i = (cmd[0] + (cmd[1] << 8));

switch (i)

case COMM WRITE XMEM:

case COMM WRITE MEM: data wr = TRUE;

if (len > 0)

if (data_wr) for (i=0; i<len; i++) HSS_Write_byte(buf[i]);</pre>

else for (i=0; i<len; i++) buf[i] = HSS Read byte();</pre>

if (i==COMM_CONFIG) Delay_100us() // requires for change baud rate

else Delay 30us(); // between LCP need this delay

return TRUE;

```

<sup>\*</sup> The HSS hardware transfer length only supports up to 2048 bytes, i.e., 1024 words.

## 1.4.3 LCP Overview for Serial Peripheral Interface (SPI)

Refer to Chapter 6, "SPI Transport Module Firmware" for complete details on this topic.

In SPI mode the EZ-Host or EZ-OTG device acts as an SPI Slave to the external host. The SPI connection requires a more detailed protocol because it is a master driver, synchronous, half-duplex interface. Hence the master must poll for the data after an LCP command is issued or it must use an additional hardware interrupt to notify the Host that data is ready. The BIOS supports both modes of communication. In the SPI mode, the GPIO24 line can be used as the interrupt line to the external processor, if the application avoids polling the COMM\_ACK status.

**Note:** The external host processor is in full control of the interface as a master. The Host must give time to the BIOS in between sending LCP commands and reading responses. The Host should wait at least 100 microseconds after sending a CMD packet before attempting to poll the response. Also, after receiving a response the host should wait 100 microseconds before issuing another CMD packet. For example:

```

bool spi_xfer(char *cmd; int len; char *buf)

int i, stat;

bool data wr=FALSE;

if (len>1024) return FALSE; // (*) spi HW support upto 512-words

for (i=0; i<8; i++)

SPI_Write_byte(cmd[i]); // (8-byte commands) no delay here

// Read ACK/NAK status:

οb

{

Delay 100us();

stat=SPI Read byte();

} while (stat == 0xff);

stat = (SPI Read byte() << 8) + stat;</pre>

i = (cmd[0] + (cmd[1] << 8));

switch (i)

case COMM WRITE XMEM:

case COMM_WRITE_MEM: data_wr = TRUE;

if (len > 0)

if (data wr) for (i=0; i<len; i++) SPI Write byte(buf[i]);

else for (i=0; i<len; i++) buf[i] = SPI Read byte();

Delay 100us(); // between LCP need this delay

return TRUE;

```

Page 1-12 BIOS User's Manual v1.2

<sup>\*</sup> The SPI hardware transfer length only support up to 1024-byte i.e. 512 word.

## 1.5 Hardware Interrupts

There are 48 hardware interrupt vectors for the EZ-Host/EZ-OTG devices. The only real difference between a hardware interrupt and a software interrupt is the fact that a hardware interrupt is triggered by an event in hardware. This may seem obvious, but it is important to understand that hardware interrupts can be called with the INT instruction the same way as software interrupts are, and any reserved or free hardware interrupts can be used as a software interrupt since there is no hardware stimulus associated with it. The EZ-Host/EZ-OTG hardware interrupt vectors are listed in Table 1-4.

Table 1-4. Hardware Interrupt Table

| Interrupt<br>Number | Vector<br>Address | Interrupt Type                            | Note |

|---------------------|-------------------|-------------------------------------------|------|

| 0                   | 0x00              | Timer0 (free for developer)               | 2    |

| 1                   | 0x02              | Timer1 (free for developer)               | 2    |

| 2                   | 0x04              | GP IRQ0 (free for developer)              | 2    |

| 3                   | 0x06              | GP IRQ1 (free for developer)              | 2    |

| 4                   | 0x08              | UART Tx (reserved for debugger)           | 1    |

| 5                   | 0x0A              | UART Rx (reserved for debugger)           | 1    |

| 6                   | 0x0C              | HSS DMA Done (reserved for LCP)           | 1    |

| 7                   | 0x0E              | HSS Rx Full (reserved for LCP)            | 1    |

| 8                   | 0x10              | IDE DMA Done (free for developer)         | 3    |

| 9                   | 0x12              | Reserved for future hardware              | 4    |

| 10                  | 0x14              | HPI Mailbox RX Empty (reserved for LCP)   | 1    |

| 11                  | 0x16              | HPI Mailbox TX Full (reserved for LCP)    | 1    |

| 12                  | 0x18              | SPI Tx (reserved for LCP)                 | 1    |

| 13                  | 0x1A              | SPI Rx (reserved for LCP)                 | 1    |

| 14                  | 0x1C              | SPI DMA Done (reserved for LCP)           | 1    |

| 15                  | 0x1E              | OTG ID / VBUS Valid (free for developer)  | 3    |

| 16                  | 0x20              | SIE1 Host Done (reserved for BIOS)        | 1    |

| 17                  | 0x22              | SIE1 Host SOF (reserved for BIOS)         | 1    |

| 18                  | 0x24              | SIE1 Host Ins/Remove (free for developer) | 3    |

| 19                  | 0x26              | Reserved for future hardware              | 4    |

| 20                  | 0x28              | SIE1 Peripheral Reset (reserved for BIOS) | 1    |

| 21                  | 0x2A              | SIE1 Peripheral SOF (reserved for BIOS)   | 1    |

| 22                  | 0x2C              | Reserved for future hardware              | 4    |

| 23                  | 0x2E              | Reserved for future hardware              | 4    |

| 24                  | 0x30              | SIE2 Host Done (reserved for BIOS)        | 1    |

| 25                  | 0x32              | SIE2 Host SOF (reserved for BIOS)         | 1    |

Table 1-4. Hardware Interrupt Table (Continued)

| Interrupt<br>Number | Vector<br>Address | Interrupt Type                                | Note |

|---------------------|-------------------|-----------------------------------------------|------|

| 26                  | 0x34              | SIE2 Host Ins/Remove (free for developer)     | 3    |

| 27                  | 0x36              | Reserved for future hardware                  | 4    |

| 28                  | 0x38              | SIE2 Peripheral Reset (reserved for BIOS)     | 1    |

| 29                  | 0x3A              | SIE2 Peripheral SOF (reserved for BIOS)       | 1    |

| 30                  | 0x3C              | Reserved for future hardware                  | 4    |

| 31                  | 0x3E              | Reserved for future hardware                  | 4    |

| 32                  | 0x40              | SIE1 Endpoint 0 Interrupt (reserved for BIOS) | 1    |

| 33                  | 0x42              | SIE1 Endpoint 1 Interrupt (reserved for BIOS) | 1    |

| 34                  | 0x44              | SIE1 Endpoint 2 Interrupt (reserved for BIOS) | 1    |

| 35                  | 0x46              | SIE1 Endpoint 3 Interrupt (reserved for BIOS) | 1    |

| 36                  | 0x48              | SIE1 Endpoint 4 Interrupt (reserved for BIOS) | 1    |

| 37                  | 0x4A              | SIE1 Endpoint 5 Interrupt (reserved for BIOS) | 1    |

| 38                  | 0x4C              | SIE1 Endpoint 6 Interrupt (reserved for BIOS) | 1    |

| 39                  | 0x4E              | SIE1 Endpoint 7 Interrupt (reserved for BIOS) | 1    |

| 40                  | 0x50              | SIE2 Endpoint 0 Interrupt (reserved for BIOS) | 1    |

| 41                  | 0x52              | SIE2 Endpoint 1 Interrupt (reserved for BIOS) | 1    |

| 42                  | 0x54              | SIE2 Endpoint 2 Interrupt (reserved for BIOS) | 1    |

| 43                  | 0x56              | SIE2 Endpoint 3 Interrupt (reserved for BIOS) | 1    |

| 44                  | 0x58              | SIE2 Endpoint 4 Interrupt (reserved for BIOS) | 1    |

| 45                  | 0x5A              | SIE2 Endpoint 5 Interrupt (reserved for BIOS) | 1    |

| 46                  | 0x5C              | SIE2 Endpoint 6 Interrupt (reserved for BIOS) | 1    |

| 47                  | 0x5E              | SIE2 Endpoint 7 Interrupt (reserved for BIOS) | 1    |

#### NOTES:

- These hardware interrupt vectors are reserved for internal BIOS usage. Users should not attempt to overwrite these functions.

- 2. These hardware interrupt vectors are not initialized.

- 3. These hardware interrupt vectors are initialized with empty ISR subroutine

- 4. These hardware interrupt vectors are reserved for future hardware expansion. Users should not use these vectors

All these vector interrupts are read/write accessible. Users can overwrite these default interrupt vectors by replacing their interrupt service subroutine. Example 1, "Modify Timer 1 Interrupt Vector" demonstrates how you can replace the hardware interrupt.

#### **Example 1: Modify Timer 1 Interrupt Vector.**

```

Initialize:

mov [0x0002],Timer1_isr ; New Timer1 ISR

or [0xc00e],2 ; enable timer1 interrupt

...

ret

```

Page 1-14 BIOS User's Manual v1.2

## 1.5.1 BIOS Hardware Interrupt Usage

Most hardware interrupts are used by the BIOS. The user can override these ISRs but care must be taken.

## 1.5.1.1 Interrupts Not Used by the BIOS

The following interrupts are not used by the BIOS and can be utilized by the developer.

Table 1-5. Interrupts not used by the BIOS

| Interrupt<br>Number | Interrupt Name          | Notes |

|---------------------|-------------------------|-------|

| 0                   | Timer0                  |       |

| 1                   | Timer1                  |       |

| 2-3                 | GPIO IRQ0 and GPIO IRQ1 |       |

| 8                   | IDE DMA Done            |       |

| 15                  | OTG ID / VBUS Valid     | 1     |

| 18                  | SIE1 Host Insert/Remove |       |

| 26                  | SIE2 Host Insert/Remove |       |

NOTE: Interrupt 15 is available to implement USB On-The-Go support

## 1.5.1.2 Interrupts Used by the BIOS

The following interrupts are used by the BIOS.

Table 1-6. Hardware Interrupt Table

| Interrupt<br>Number | Interrupt Name        | Notes                                                                                                                                                                                                                                                                  |

|---------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                   | UART Tx               | ISR: transmits characters from the software 16-byte FIFO Note: Overriding effects tool support over UART                                                                                                                                                               |

| 5                   | UART Rx               | ISR: receives characters and store into the software 16-byte FIFO.  Note: Overriding effects tool support over UART                                                                                                                                                    |

| 6                   | HSS DMA Done          | ISR: Used by HSS Transport to support LCP                                                                                                                                                                                                                              |

| 7                   | HSS Rx Full           | ISR: Used by HSS Transport to support LCP                                                                                                                                                                                                                              |

| 9                   | Reserved              | Reserved for future HW                                                                                                                                                                                                                                                 |

| 10                  | HPI Mailbox TX Empty  | ISR: Used by HPI Transport to support LCP                                                                                                                                                                                                                              |

| 11                  | HPI Mailbox RX Full   | Not used: Reserved for BIOS                                                                                                                                                                                                                                            |

| 12                  | SPI Tx                | Not used: Reserved for BIOS                                                                                                                                                                                                                                            |

| 13                  | SPI Rx                | ISR: Used by SPI Transport to support LCP                                                                                                                                                                                                                              |

| 14                  | SPI DMA Done          | ISR: Used by SPI Transport to support LCP                                                                                                                                                                                                                              |

| 16                  | SIE1 Host Done        | ISR: services a single packet via the Transfer Descriptor (TD). It will post the message to the HPI mailbox register 0x144 with 0x1000 after all the TD list items are serviced.                                                                                       |

| 17                  | SIE1 Host SOF         | ISR: services the TD list that supply from the application. As soon as the TD is not empty, it will start TD transaction.                                                                                                                                              |

| 20                  | SIE1 Peripheral Reset | ISR: enter this ISR after 5us of the falling edge of the USB_RESET. This interrupt will call the SUSB1_INIT_INT and will post the message to the HPI mailbox register 0x144 with value 0x100                                                                           |

| 21                  | SIE1 Peripheral SOF   | ISR: services for every 1ms SOF detect from USB Host. After second SOF detection, it will send a message to HPI mailbox register 0x144 with value 0x200. After detecting seven consecutive missing SOFs, it will set the value 0x800 to the HPI mailbox register 0x144 |

| 24                  | SIE2 Host Done        | ISR: services a single packet via the Transfer Descriptor (TD). It will post the message to the HPI mailbox register 0x148 with 0x1000 after all the TD list items are serviced.                                                                                       |

| 25                  | SIE2 Host SOF         | ISR: services the TD list that supply from the application. As soon as the TD is not empty, it will start TD transaction.                                                                                                                                              |

Page 1-16 BIOS User's Manual v1.2

Table 1-6. Hardware Interrupt Table (Continued)

| Interrupt<br>Number | Interrupt Name              | Notes                                                                                                                                                                                                                                                                                                                          |

|---------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28                  | SIE2 Peripheral Reset       | ISR: enter this ISR after 5us of the falling edge of the USB_RESET. This interrupt will call the SUSB2_INIT_INT and will post the message to the HPI mailbox register 0x148 with value 0x100                                                                                                                                   |

| 29                  | SIE2 Peripheral SOF         | ISR: services for every 1ms SOF detect from USB Host. After second SOF detection, it will send a message to HPI mailbox register 0x148 with value 0x200. After detecting seven consecutive missing SOFs, it will set the value 0x800 to the HPI mailbox register 0x148                                                         |

| 32                  | SIE1 Endpoint0              | ISR: services USB full/low speed enumeration in portA, which defined by the SUSB_INIT_INT. It handles retry when detect any ERROR in the USB bus. It also supports RedHat debugger/QTOOL and services the SUSB1_SEND_INT + SUSB1_RECEIVE_INT. It will set the bit0 of the HPI mailbox register 0x144 for every SUSB1_SEND_INT. |

| 32-39               | SIE1 Endpoint 1-7 Interrupt | ISR: This interrupt supports the SUSB1_SEND_INT and SUSB1_RECEIVE_INT. It handles retry when it detects an ERROR in the USB BUS. After the transfer of data that defines this interface is complete, it will set bits 1-7 in the HPI mailbox register 0x144.                                                                   |

| 40                  | SIE2 Endpoint0              | ISR: services USB full/low speed enumeration in portA, which defined by the SUSB_INIT_INT. It handles retry when detect any ERROR in the USB bus. It also supports the Red Hat debugger and services the SUSB2_SEND_INT + SUSB2_RECEIVE_INT. It will set the bit0 of the HPI mailbox register 0x148 for every SUSB2_SEND_INT.  |

| 41-47               | SIE2 Endpoint 1-7 Interrupt | ISR: This interrupt supports the SUSB2_SEND_INT and SUSB2_RECEIVE_INT. It handles retry when detect ERROR in the USB BUS. After the transfer of data that defines this interface is complete, it will set bits 1-7 in the HPI mailbox register 0x148.                                                                          |

## 1.6 Debugging Tools support

The BIOS supports the debugger via the following interfaces:

UART: Default baud rate = 28800, 8-bit, no-parity, 1 stop-bit, flow control: none The UART port will be used by the debugger

USB-portC will be used by the debugger.

HPI/HSS/SPI via LCP. The debugger software does not support debugging over these interfaces. Users will make use of these interfaces for their application development.

**Note**: USB-portA can also be used for the debugger, when it is configured as the peripheral. In coprocessor mode, both USB-portA and USB-portC will not be available to the debugger. Only the UART will be available in the EZ-Host chip because of design requirements.

**Note**: In co-processor mode, the debugger on the USB ports can be enabled by calling the SUSB\_INIT\_INT via the LCP interface in both EZ-Host and EZ-OTG devices.

**Note**: The UART and USB debugging ports are not available when the EZ-OTG chip is setup in the HPI mode (co-processor mode) because HPI pins are shared with the UART pins. However, the UART will be available when the EZ-OTG chip is setup in either HSS or SPI mode.

**Note**: The UART debugging port is available when the EZ-Host chip is setup in the HPI/HSS/SPI mode.

Page 1-18 BIOS User's Manual v1.2

## 1.7 Software Interrupts

The EZ-Host and EZ-OTG allocate address locations from 0x0060 to 0x00FE to software interrupts. The software interrupt vectors are listed in Table 1-7.

Table 1-7. Software Interrupt Table

| Interrupt<br>Number | Vector<br>Address | Interrupt Type                                                         | Notes |

|---------------------|-------------------|------------------------------------------------------------------------|-------|

| 48                  | 0x60              | Reserved for LCP status message                                        | 1     |

| 49                  | 0x62              | Reserved for LCP asynchronous message                                  | 1     |

| 50                  | 0x64              | Reserved for future BIOS on OTG Variable Data: Default = 0 = OTG State | 2     |

| 51-63               | 0x66-0x7F         | Free for developers                                                    | 3,4   |

| 64                  | 0x80              | Two-wire serial EEPROM (from 256-byte to 2K-byte)                      | 1     |

| 65                  | 0x82              | Two-wire serial EEPROM from (4k-byte to 16k byte)                      | 1     |

| 66                  | 0x84              | UART_INT                                                               | 1     |

| 67                  | 0x86              | SCAN_INT                                                               | 1     |

| 68                  | 0x88              | ALLOC_INT                                                              | 1     |

| 69                  | 0x8A              | Variable Data Pointer: start of free memory                            | 2     |

| 70                  | 0x8C              | IDLE_INT                                                               | 1     |

| 71                  | 0x8E              | IDLER_INT                                                              | 1     |

| 72                  | 0x90              | INSERT_IDLE_INT                                                        | 1     |

| 73                  | 0x92              | PUSHALL_INT                                                            | 1     |

| 74                  | 0x94              | POPALL_INT                                                             | 1     |

| 75                  | 0x96              | FREE_INT                                                               | 1     |

| 76                  | 0x98              | REDO_ARENA                                                             | 1     |

| 77                  | 0x9A              | HW_SWAP_REG                                                            | 1     |

| 78                  | 0x9C              | HW_REST_REG                                                            | 1     |

| 79                  | 0x9E              | SCAN_DECODE_INT                                                        | 1     |

| 80                  | 0xA0              | SUSB1_SEND_INT                                                         | 1     |

| 81                  | 0xA2              | SUSB1_RECEIVE_INT                                                      | 1     |

| 82                  | 0xA4              | SUSB1_STALL_INT                                                        | 1     |

| 83                  | 0xA6              | SUSB1_STANDARD_INT                                                     | 1     |

| 84                  | 0xA8              | OTG_SRP_INT                                                            | 1     |

| 85                  | 0xAA              | SUSB1_VENDOR_INT (default=SUSB1_STALL_INT)                             | 4     |

| 86                  | 0xAC              | REMOTE_WAKEUP_INT                                                      | 1     |

| 87                  | 0xAE              | SUSB1_CLASS_INT (default=SUSB1_STALL_INT)                              | 4     |

| 88                  | 0xB0              | Variable Data pointer: OTG descriptor                                  | 4     |

| 89                  | 0xB2              | SUSB1_FINISH_INT                                                       | 1     |

Table 1-7. Software Interrupt Table (Continued)

| Interrupt<br>Number | Vector<br>Address | Interrupt Type                                                                                           | Notes |

|---------------------|-------------------|----------------------------------------------------------------------------------------------------------|-------|

| 90                  | 0xB4              | <u>Variable Data pointer</u> : SUSB1 Device Descriptor. Default = Cypress Device Descriptor              | 2,4   |

| 91                  | 0xB6              | <u>Variable Data pointer</u> : SUSB1Configuration Descriptor. Default = Cypress Configuration Descriptor | 2,4   |

| 92                  | 0xB8              | <u>Variable Data pointer</u> : SUSB1 String Descriptor. Default = Cypress String Descriptor              | 2,4   |

| 93                  | 0xBA              | Reserved for future BIOS                                                                                 | 1     |

| 94                  | 0xBC              | SUSB1_LOADER_INT                                                                                         | 1     |

| 95                  | 0xBE              | SUSB1_DELTA_CONFIG_INT                                                                                   | 1     |

| 96                  | 0xC0              | SUSB2_SEND_INT                                                                                           | 1     |

| 97                  | 0xC2              | SUSB2_RECEIVE_INT                                                                                        | 1     |

| 98                  | 0xC4              | SUSB2_STALL_INT                                                                                          | 1     |

| 99                  | 0xC6              | SUSB2_STANDARD_INT                                                                                       | 1     |

| 100                 | 0xC8              | Reserved for future BIOS                                                                                 | 1     |

| 101                 | 0xCA              | SUSB2_VENDOR_INT (default: SUSB2_STALL_INT)                                                              | 4     |

| 102                 | 0xCC              | Reserved for future BIOS                                                                                 | 1     |

| 103                 | 0xCE              | SUSB2_CLASS_INT (default: SUSB2_STALL_INT)                                                               | 4     |

| 104                 | 0xD0              | Reserved for future BIOS                                                                                 | 1     |

| 105                 | 0xD2              | SUSB2_FINISH_INT                                                                                         | 1     |

| 106                 | 0xD4              | <u>Variable Data pointer</u> : SUSB2 Device Descriptor. Default = Cypress Device Descriptor              | 2,4   |

| 107                 | 0xD6              | <u>Variable Data pointer</u> : SUSB2Configuration Descriptor. Default = Cypress Configuration            | 2,4   |

| 108                 | 0xD8              | <u>Variable Data pointer</u> :SUSB2 String Descriptor. Default = Cypress String Descriptor               | 2,4   |

| 109                 | 0xDA              | Reserved for future BIOS                                                                                 | 1     |

| 110                 | 0xDC              | SUSB2_LOADER_INT                                                                                         | 1     |

| 111                 | 0xDE              | SUSB2_DELTA_CONFIG_INT                                                                                   | 1     |

| 112                 | 0xE0              | Reserved for future BIOS on OTG_STATE_INT                                                                | 1     |

| 113                 | 0xE2              | SUSB_INIT_NT                                                                                             | 1     |

| 114                 | 0xE4              | HUSB_SIE1_INIT_INT                                                                                       | 1     |

| 115                 | 0xE6              | HUSB_SIE2_INIT_INT                                                                                       | 1     |

| 116                 | 0xE8              | HUSB_RESET                                                                                               | 1     |

| 117                 | 0xEA              | KBHIT_INT                                                                                                | 1     |

| 118- 125            | 0xEC-0xFA         | Free for developers                                                                                      | 3,4   |

| 126- 127            | 0xFC-0xFE         | Reserved for debugger                                                                                    | 3     |

#### NOTES:

- These software vectors are used by the internal BIOS.

These vectors are used as the data pointers. Users should not execute code (i.e. JMP or INT) to these vectors.

- 3. These interrupt vectors are not initialized.