# Section 13. Parallel Master Port (PMP)

# **HIGHLIGHTS**

This section of the manual contains the following major topics:

| 13.1  | Introduction                              | 13-2  |

|-------|-------------------------------------------|-------|

| 13.2  | Control Registers                         | 13-3  |

| 13.3  | Master Modes of Operation                 | 13-12 |

| 13.4  | Slave Modes of Operation                  | 13-32 |

| 13.5  | Interrupts                                | 13-39 |

| 13.6  | Operation in Power-Saving and Debug Modes | 13-41 |

| 13.7  | Effects of Various Resets                 | 13-41 |

| 13.8  | Parallel Master Port Applications         | 13-42 |

| 13.9  | Parallel Slave Port Application           | 13-47 |

| 13.10 | Direct Memory Access Support              | 13-47 |

| 13.11 | I/O Pin Control                           | 13-48 |

| 13.12 | Design Tips                               | 13-50 |

|       | Related Application Notes                 |       |

| 13.14 | Revision History                          | 13-52 |

|       |                                           |       |

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all PIC32 devices.

Please consult the note at the beginning of the "Parallel Master Port (PMP)" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

# 13.1 INTRODUCTION

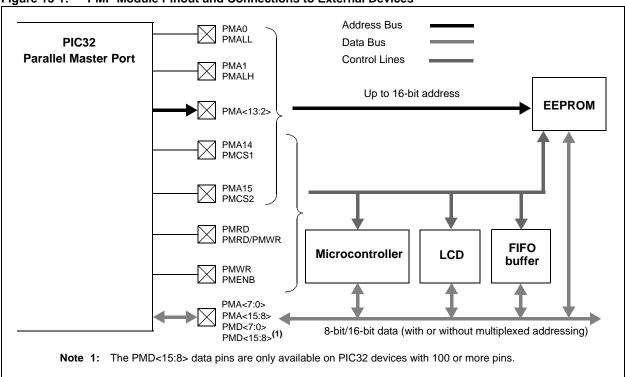

The Parallel Master Port (PMP) is a parallel 8-bit/16-bit I/O module specifically designed to communicate with a wide variety of parallel devices such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interfaces to parallel peripherals vary significantly, the PMP module is highly configurable.

Key features of the PMP module include:

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- Programmable polarity on control signals

- · Legacy parallel slave port support

- Enhanced parallel slave support

- Address support

- 4 bytes deep, auto-incrementing buffer

- · Schmitt Trigger or TTL input buffers

- Programmable Wait states

- · Freeze option for in-circuit debugging

Figure 13-1: PMP Module Pinout and Connections to External Devices

# 13.2 CONTROL REGISTERS

The PMP module uses these Special Function Registers (SFRs):

#### • PMCON: Parallel Port Control Register

This register contains the bits that control much of the module's basic functionality. A key bit is the ON control bit, which is used to Reset, enable or disable the module.

When the module is disabled, all of the associated I/O pins revert to their designated I/O function. In addition, any read or write operations active or pending are stopped, and the BUSY bit is cleared. The data within the module registers is retained, including the data in PMSTAT register. Therefore, the module could be disabled after a reception, and the last received data and status would still be available for processing.

When the module is enabled, all buffer control logic is reset, along with PMSTAT.

All other bits in PMCON control address multiplexing enable various port control signals, and select control signal polarity. These are discussed in detail in 13.3.1 "Parallel Master Port Configuration Options".

#### • PMMODE: Parallel Port Mode Register

This register contains bits that control the operational modes of the module. Master/Slave mode selection and configuration options for both modes, are set by this register. It also contains the universal status flag, BUSY, which is used in master modes to indicate that an operation by the module is in progress.

Details on the use of the PMMODE bits to configure PMP operation are provided in 13.3 "Master Modes of Operation" and 13.4 "Slave Modes of Operation".

#### • PMADDR: Parallel Port Address Register

This register functions as PMADDR in master modes. It contains the address to which outgoing data is to be written, as well as the Chip Select control bits for addressing parallel slave devices. The PMADDR register is not used in any of the Slave modes.

#### PMDOUT: Parallel Port Data Output Register

This register is used only in Slave mode for buffered output data.

#### PMDIN: Parallel Port Data Input Register

This register is used by the PMP module in both Master and Slave modes.

In Slave mode, this register is used to hold data that is asynchronously clocked in. Its operation is described in 13.4.2 "Buffered Parallel Slave Port Mode".

In Master mode, PMDIN is the holding register for both incoming and outgoing data. Its operation in Master mode is described in 13.3.3 "Read Operation" and 13.3.4 "Write Operation".

# • PMAEN: Parallel Port Pin Enable Register

This register controls the operation of address and Chip Select pins associated with the PMP module. Setting these bits allocates the corresponding microcontroller pins to the PMP module; clearing the bits allocates the pins to port I/O or other peripheral modules associated with the pin.

## • PMSTAT: Parallel Port Status Register (Slave modes only)

This register contains status bits associated with buffered operating modes when the port is functioning as a slave port. This includes overflow, underflow and full flag bit.

These flags are discussed in detail in 13.4.2 "Buffered Parallel Slave Port Mode".

# 13.2.1 PMP SFRs Summary

Table 13-1 provides a brief summary of all PMP-module-related registers. Corresponding registers appear after the summary with a detailed description of each bit.

Table 13-1: PMP SFRs Summary

| Name                      |       | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|---------------------------|-------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| PMCON <sup>(1,2,3)</sup>  | 31:24 |                            |                   | _                 | _                 |                   | _                 |                  |                  |  |  |  |

|                           | 23:16 | 1                          | 1                 | _                 | _                 | 1                 | _                 | Ι                | I                |  |  |  |

|                           | 15:8  | ON                         | 1                 | SIDL              | ADRMU             | JX<1:0>           | PMPTTL            | PTWREN           | PTRDEN           |  |  |  |

|                           | 7:0   | CSF                        | <1:0>             | ALP               | CS2P              | CS1P              | _                 | WRSP             | RDSP             |  |  |  |

| PMMODE <sup>(1,2,3)</sup> | 31:24 | 1                          | 1                 | _                 | _                 | 1                 | _                 | Ι                | I                |  |  |  |

|                           | 23:16 | 1                          | 1                 | _                 | _                 | 1                 | _                 | 1                | 1                |  |  |  |

|                           | 15:8  | BUSY                       | IRQM              | <1:0>             | INCM              | <1:0>             | MODE16            | MODE             | <1:0>            |  |  |  |

|                           | 7:0   | WAITE                      | 3<1:0>            | WAITM<3:0> WAITE  |                   |                   |                   |                  | <1:0>            |  |  |  |

| PMADDR <sup>(1,2,3)</sup> | 31:24 | _                          | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

|                           | 23:16 | _                          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|                           | 15:8  | CS2/A15 CS1/A14 ADDR<13:8> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|                           | 7:0   | ADDR<7:0>                  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| PMDOUT <sup>(1,2,3)</sup> | 31:24 | DATAOUT<31:24>             |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| I MIDOUT                  | 23:16 | DATAOUT<23:16>             |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|                           | 15:8  | DATAOUT<15:8>              |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|                           | 7:0   |                            |                   |                   | DATAOL            | JT<7:0>           |                   |                  |                  |  |  |  |

| PMDIN <sup>(1,2,3)</sup>  | 31:24 |                            |                   |                   | DATAIN            | <31:24>           |                   |                  |                  |  |  |  |

|                           | 23:16 |                            | DATAIN<23:16>     |                   |                   |                   |                   |                  |                  |  |  |  |

|                           | 15:8  |                            | DATAIN<15:8>      |                   |                   |                   |                   |                  |                  |  |  |  |

|                           | 7:0   |                            |                   |                   | DATAI             | N<7:0>            |                   |                  |                  |  |  |  |

| PMAEN <sup>(1,2,3)</sup>  | 31:24 | _                          | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

|                           | 23:16 | _                          | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

|                           | 15:8  |                            |                   |                   | PTEN-             | <15:8>            |                   |                  |                  |  |  |  |

|                           | 7:0   |                            |                   |                   | PTEN              | <7:0>             |                   |                  |                  |  |  |  |

| PMSTAT                    | 31:24 | _                          | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

|                           | 23:16 | _                          | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

|                           | 15:8  | IBF                        | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |  |  |  |

|                           | 7:0   | OBE                        | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |  |  |  |

**Legend:** — = unimplemented, read as '0'. Address offset values are shown in hexadecimal.

- Note 1: This register has an associated Clear register at an offset of 0x4 bytes. The Clear register has the same name with CLR appended to the register name (e.g., PMCONCLR). Writing a '1' to any bit position in the Clear register will clear valid bits in the associated register. Reads from the Clear register should be ignored.

- 2: This register has an associated Set register at an offset of 0x8 bytes. The Set register has the same name with SET appended to the register name (e.g., PMCONSET). Writing a '1' to any bit position in the Set register will set valid bits in the associated register. Reads from the Set register should be ignored.

- 3: This register has an associated Invert register at an offset of 0xC bytes. The Invert register has the same name with INV appended to the register name (e.g., PMCONINV). Writing a '1' to any bit position in the Invert register will invert valid bits in the associated register. Reads from the Invert register should be ignored.

Register 13-1: PMCON: Parallel Port Control Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4   | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|---------------------|---------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0                 | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                   |                    | _                   | _                   |                   | _                | _                |

| 23:16        | U-0               | U-0                 | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                   |                    | _                   | _                   |                   | _                | _                |

| 15:8         | R/W-0             | U-0                 | R/W-0              | R/W-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15.6         | ON <sup>(1)</sup> | _                   | SIDL               | ADRMU               | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7:0          | R/W-0             | R/W-0               | R/W-0              | R/W-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7.0          | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | CS2P <sup>(2)</sup> | CS1P <sup>(2)</sup> |                   | WRSP             | RDSP             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 **Unimplemented:** Write '0'; ignore read bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

ON: Parallel Master Port Enable bit<sup>(1)</sup>

1 = PMP enabled

0 = PMP disabled, no off-chip access performed

bit 14 Unimplemented: Write '0'; ignore read

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

11 = All 16 bits of address are multiplexed on PMD<15:0> pins

10 = All 16 bits of address are multiplexed on PMD<7:0> pins

01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper 8 bits are on PMA<15:8>

00 = Address and data appear on separate pins

bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

1 = PMP module uses TTL input buffers

0 = PMP module uses Schmitt Trigger input buffer

bit 9 PTWREN: Write Enable Strobe Port Enable bit

1 = PMWR/PMENB port enabled

0 = PMWR/PMENB port disabled

bit 8 PTRDEN: Read/Write Strobe Port Enable bit

1 = PMRD/PMWR port enabled

0 = PMRD/PMWR port disabled

bit 7-6 CSF<1:0>: Chip Select Function bits<sup>(2)</sup>

11 = Reserved

10 = PMCS2 and PMCS1 function as Chip Select

01 = PMCS2 functions as Chip Select, PMCS1 functions as address bit 14

00 = PMCS2 and PMCS1 function as address bits 15 and 14

bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

1 = Active-high (PMALL and PMALH)

$0 = Active-low (\overline{PMALL} \text{ and } \overline{PMALH})$

bit 4 CS2P: Chip Select 1 Polarity bit<sup>(2)</sup>

1 = Active-high (PMCS2)

$0 = Active-low (\overline{PMCS2})$

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

2: These bits have no effect when it's corresponding pin is used as an address line.

# **PIC32 Family Reference Manual**

# **PMCON: Parallel Port Control Register (Continued)** CS1P: Chip Select 0 Polarity bit<sup>(2)</sup> bit 3 1 = Active-high (PMCS1) $0 = Active-low (\overline{PMCS1})$ bit 2 Unimplemented: Write '0'; ignore read bit 1 WRSP: Write Strobe Polarity bit For Slave Modes and Master mode 2 (PMMODE<9:8> = 00,01,10): 1 = Write strobe active-high (PMWR) $0 = Write strobe active-low (\overline{PMWR})$ For Master mode 1 (PMMODE<9:8> = 11): 1 = Enable strobe active-high (PMENB) 0 = Enable strobe active-low (PMENB) bit 0 RDSP: Read Strobe Polarity bit For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10): 1 = Read strobe active-high (PMRD) $0 = \text{Read strobe active-low } (\overline{PMRD})$

- For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Read/write strobe active-high (PMRD/PMWR)

- $0 = \text{Read/write strobe active-low } (\overline{PMRD/PMWR})$

- Note 1: When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when it's corresponding pin is used as an address line.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4         | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0          |  |

|--------------|-------------------|----------------------|-------------------|---------------------------|-------------------|-------------------|------------------|---------------------------|--|

| 31:24        | U-0               | U-0                  | U-0               | U-0                       | U-0               | U-0               | U-0              | U-0                       |  |

| 31.24        | _                 | _                    |                   | _                         | _                 |                   | _                | _                         |  |

| 23:16        | U-0               | U-0                  | U-0               | U-0                       | U-0               | U-0               | U-0              | U-0                       |  |

| 23.10        | _                 | _                    | _                 | _                         |                   | -                 | _                |                           |  |

| 15:8         | R-0               | R/W-0                | R/W-0             | R/W-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0                     |  |

| 15.6         | BUSY              | IRQM<1:0>            |                   | INCM<1:0>                 |                   | MODE16            | MODE             | <1:0>                     |  |

| 7:0          | R/W-0             | R/W-0                | R/W-0             | R/W-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0                     |  |

| 7.0          | WAITB.            | <1:0> <sup>(1)</sup> |                   | WAITM<3:0> <sup>(1)</sup> |                   |                   |                  | WAITE<1:0> <sup>(1)</sup> |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 **Unimplemented:** Write '0'; ignore read

bit 15 **BUSY:** Busy bit (Master mode only)

1 = Port is busy0 = Port is not busy

bit 14-13 IRQM<1:0>: Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode), or on a read or write operation when PMA<1:0> = 11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

- bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (PMMODE<1:0> = 00 only)

- 10 = Decrement ADDR<15:0> by 1 every read/write cycle<sup>(2,4)</sup>

- 01 = Increment ADDR<15:0> by 1 every read/write cycle<sup>(2,4)</sup>

- 00 = No increment or decrement of address

- bit 10 MODE16: 8/16-bit Mode bit

- 1 = 16-bit mode: a read or write to the data register invokes a single 16-bit transfer

- 0 = 8-bit mode: a read or write to the data register invokes a single 8-bit transfer

- bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCSx, PMRD/PMWR, PMENB, PMA<x:0>, PMD<7:0> and PMD<8:15>(3))

- 10 = Master mode 2 (PMCSx, PMRD, PMWR, PMA<x:0>, PMD<7:0> and PMD<8:15>(3))

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS, PMD<7:0> and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS and PMD<7:0>)

- bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

- 10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

- 01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

- 00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

- Note 1: When WAITM<3:0> = 0000, the WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A15 and A14 are not subject to auto-increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

- 4: The PMPADDR register is always incremented/decremented by 1 regardless of the transfer data width.

# Register 13-2: PMMODE: Parallel Port Mode Register (Continued) bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup> 1111 = Wait of 16 TPB • 0001 = Wait of 2 TPB 0000 = Wait of 1 TPB (default) bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup> 11 = Wait of 4 TPB 10 = Wait of 3 TPB 01 = Wait of 2 TPB 00 = Wait of 1 TPB (default) For read operations: 11 = Wait of 3 TPB 10 = Wait of 3 TPB 10 = Wait of 2 TPB 01 = Wait of 3 TPB 10 = Wait of 1 TPB

- **Note 1:** When WAITM<3:0> = 0000, the WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A15 and A14 are not subject to auto-increment/decrement if configured as Chip Select CS2 and CS1.

- 3: These pins are active when MODE16 = 1 (16-bit mode).

00 = Wait of 0 TPB (default)

4: The PMPADDR register is always incremented/decremented by 1 regardless of the transfer data width.

# Register 13-3: PMADDR: Parallel Port Address Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                 | _                 | -                 | _                 |                   | -                 | _                | -                |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.6         | CS2               | CS1               |                   | ADDR<13:8>        |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          |                   |                   |                   | ADD               | R<7:0>            |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Write '0'; ignore read

bit 15 CS2: Chip Select 2 bit

1 = Chip Select 2 is active

0 = Chip Select 2 is inactive (pin functions as PMA<15>)

bit 14 CS1: Chip Select 1 bit

1 = Chip Select 1 is active

0 = Chip Select 1 is inactive (pin functions as PMA<14>)

bit 13-0 ADDR<13:0>: Destination Address bits

## Register 13-4: PMDOUT: Parallel Port Data Output Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | DATAOUT<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00:40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | DATAOUT<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 13.0         | DATAOUT<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | DATAC             | UT<7:0>           |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 DATAOUT<31:0>: Output Data Port bits for 8-bit write operations in Slave mode

Register 13-5: PMDIN: Parallel Port Data Input Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | DATAIN<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | DATAIN<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 13.0         | DATAIN<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          |                   |                   |                   | DATA              | IN<7:0>           |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 **DATAIN<31:0>:** Input/Output Data Port bits for 8-bit or 16-bit read/write operations in Master mode Input Data Port for 8-bit read operations in Slave mode.

Register 13-6: PMAEN: Parallel Port Pin Enable Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit 28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|----------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0            | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | _                 | _              | _                 | _                 | _                | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0            | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | _                 | _                 | _                 | _              |                   | _                 | _                | _                |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0          | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 13.6         | PTEN<             | 15:14>            | PTEN<13:8>        |                |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0          | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              |                   |                   |                   | PTEN           | <1:0>             |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Write '0'; ignore read

bit 15-14 PTEN<15:14>: PMCSx Strobe Enable bits

1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS2 and PMCS1(1)

0 = PMA15 and PMA14 function as port I/O

bit 13-2 PTEN<13:2>: PMP Address Port Enable bits

1 = PMA<13:2> function as PMP address lines

0 = PMA<13:2> function as port I/O

bit 1-0 PTEN<1:0>: PMALH/PMALL Strobe Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL(2)

- 0 = PMA1 and PMA0 pads function as port I/O

- Note 1: The use of these pins as PMA15/PMA14 or CS2/CS1 is selected by the CSF<1:0> bits (PMCON<7:6>).

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by the ADRMUX<1:0> bits in the PMCON register.

Register 13-7: PMSTAT: Parallel Port Status Register (Slave modes only)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 | _                 |                   | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | -                 | _                 |                   | -                 | _                | _                |

| 15:8         | R-0               | R/W-0             | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15.6         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7:0          | R-1               | R/W-0             | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7.0          | OBE               | OBUF              |                   | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Write '0'; ignore read

bit 15 IBF: Input Buffer Full Status bit

1 = All writable input buffer registers are full

0 = Some or all of the writable input buffer registers are empty

bit 14 IBOV: Input Buffer Overflow Status bit

1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

0 = No overflow occurred

This bit is set (= 1) in hardware; can only be cleared (= 0) in software.

bit 13-12 Unimplemented: Write '0'; ignore read

bit 11-8 IBnF: Input Buffer n Status Full bits

1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

0 = Input Buffer does not contain any unread data

bit 7 OBE: Output Buffer Empty Status bit

1 = All readable output buffer registers are empty

0 = Some or all of the readable output buffer registers are full

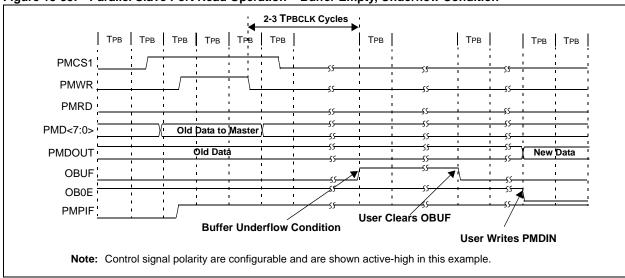

bit 6 **OBUF:** Output Buffer Underflow Status bit

1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

This bit is set (= 1) in hardware; can only be cleared (= 0) in software.

bit 5-4 Unimplemented: Write '0'; ignore read

bit 3-0 OBnE: Output Buffer n Status Empty bits

1 = Output buffer is empty (writing data to the buffer will clear this bit)

0 = Output buffer contains data that has not been transmitted

# 13.3 MASTER MODES OF OPERATION

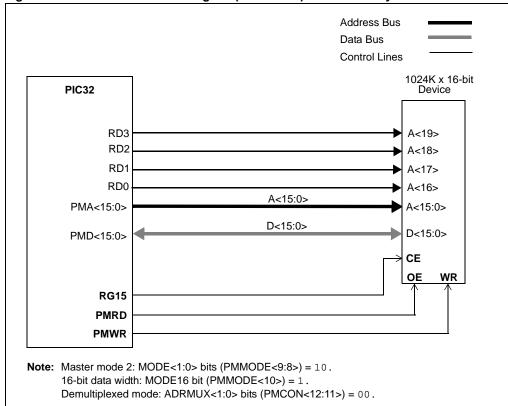

In its master modes, the PMP module can provide a 8-bit or 16-bit data bus, up to 16 bits of address, and all the necessary control signals to operate a variety of external parallel devices such as memory devices, peripherals and slave microcontrollers. The PMP master modes provide a simple interface for reading and writing data, but not executing program instructions from external devices, such as SRAM or Flash memories.

Because there are a number of parallel devices with a variety of control methods, the PMP module is designed for flexibility to accommodate a range of configurations. Some of these features include:

- · 8-bit and 16-bit data modes

- · Configurable address/data multiplexing

- · Up to two Chip Select lines

- Up to 16 selectable address lines

- Address auto-increment and auto-decrement

- · Selectable polarity on all control lines

- · Configurable Wait states at different stages of the read/write cycle

# 13.3.1 Parallel Master Port Configuration Options

#### 13.3.1.1 8-BIT AND 16-BIT DATA MODES

The PMP in Master mode supports data with widths of 8 and 16 bits. By default, the data width is 8 bits wide, MODE16 bit (PMMODE<10>) = 0. To select a data width of 16 bits, set MODE16 = 1. When configured in 8-bit Data mode, the upper 8 bits of the data bus, PMD<15:8>, are not controlled by the PMP module and are available as general purpose I/O pins.

**Note:** The PMD<15:0> data pins are available on PIC32 devices with 100 or more pins. For 64-pin device variants, only pins PMD<7:0> are available. For details, refer to the specific PIC32 device data sheet.

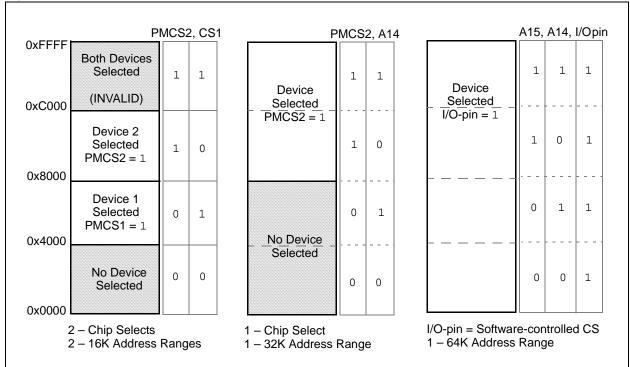

# 13.3.1.2 CHIP SELECT

Two Chip Select lines, PMCS1 and PMCS2, are available for master modes. These lines are multiplexed with the Most Significant bits (MSbs) of the address bus A14 and A15. When a pin is configured as a Chip Select, it is not included in any address auto-increment/decrement. It is possible to enable both PMCS2 and PMCS1 as Chip Selects, or enable only PMCS2 as a Chip Select, allowing PMCS1 to function strictly as address line A14. It is not possible to enable PMCS1 alone. The Chip Select signals are configured using the Chip Select Function bits CSF<1:0> (PMCON<7:6>).

Table 13-2: Chip Select Control

| CSF<1:0> | Function                     |

|----------|------------------------------|

| 10       | PMCS2, PMCS1 = Enabled       |

| 01       | PMCS2 = Enabled, PMCS1 = A14 |

| 00       | PMCS2 = A15, PMCS1 = A14     |

#### 13.3.1.3 PORT PIN CONTROL

There are several bits available to configure the presence or absence of control and address signals in the module. These bits are PTWREN (PMCON<9>), PTRDEN (PMCON<8>) and PTEN<15:0> (PMAEN<15:0>). They provide the ability to conserve pins for other functions and allow flexibility to control the external address. When any one of these bits is set, the associated function is present on its associated pin; when clear, the associated pin reverts to its defined I/O port function.

Setting a PTEN bit will enable the associated pin as an address pin and drive the corresponding data contained in the PMADDR register. Clearing any PTEN bit will force the pin to revert to its original I/O function.

# Section 13. Parallel Master Port (PMP)

For the pins configured as Chip Select (PMCS1 or PMCS2) with the corresponding PTEN bit set, Chip Select pins drive inactive data when a read or write operation is not being performed. The PTEN0 and PTEN1 bits also control the PMALL and PMALH signals. When multiplexing is used, the associated address latch signals should be enabled. For I/O pin configuration, see 13.11 "I/O Pin Control".

#### 13.3.1.4 READ/WRITE CONTROL

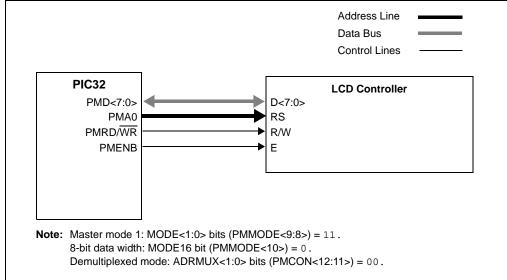

The PMP module supports two distinct read/write signaling methods. In Master mode 1, read and write strobe are combined into a single control line, PMRD/PMWR; a second control line, PMENB, determines when a read or write action is to be taken. In Master mode 2, read and write strobes (PMRD and PMWR) are supplied on separate pins.

#### 13.3.1.5 CONTROL LINE POLARITY

All control signals (PMRD, PMWR, PMENB, PMALL, PMALH, PMCS1 and PMCS2) can be individually configured for either positive or negative polarity. Configuration is controlled by separate bits in the PMCON register, as shown in Table 13-3.

Table 13-3: Pin Polarity Configuration

| Control<br>Pin | PMCON<br>Control Bit | Active-High<br>Select | Active-Low<br>Select |

|----------------|----------------------|-----------------------|----------------------|

| PMRD           | RDSP                 | 1                     | 0                    |

| PMWR           | WRSP                 | 1                     | 0                    |

| PMALL          | ALP                  | 1                     | 0                    |

| PMALH          | ALP                  | 1                     | 0                    |

| PMCS1          | CS1P                 | 1                     | 0                    |

| PMCS2          | CS2P                 | 1                     | 0                    |

**Note:** The polarity of control signals that share the same output pin (for example, PMWR and PMENB) are controlled by the same bit; the configuration depends on which Master Port mode is being used.

# 13.3.1.6 AUTO-INCREMENT/DECREMENT

While the PMP module is operating in one of the master modes, the INCM<1:0> bits (PMMODE<12:11>) control the behavior of the address value. The address in the PMADDR register can be made to automatically increment or decrement by 1, regardless of the transfer data width, after each read and write operation is completed, and the BUSY bit (PMMODE<15>) goes to '0'.

Table 13-4: Address INC/DEC Control

| INCM<1:0> | Function                    |

|-----------|-----------------------------|

| 10        | Decrement every R/W cycle   |

| 01        | Increment every R/W cycle   |

| 00        | No Increment – No Decrement |

If the Chip Select signals are disabled and configured as address bits, the bits will participate in the increment and decrement operations; otherwise, CS2 and CS1 bit values will be unaffected.

#### 13.3.1.7 WAIT STATES

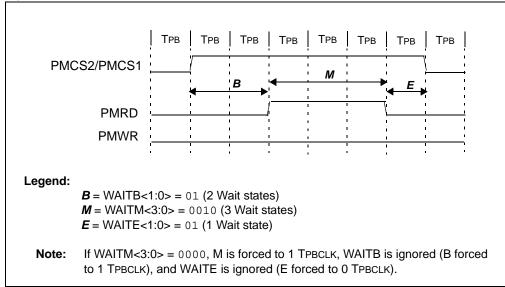

In Master mode, the user can control the duration of the read, write and address cycles by configuring the module Wait states. One Wait state period is equivalent to one peripheral bus clock cycle, TPBCLK. Figure 13-2 is an example of a Master mode 2 Read operation using Wait states.

Figure 13-2: Read Operation, Wait States Enabled

Wait states can be added to the beginning, middle and end of any read or write cycle using the corresponding WAITB, WAITM and WAITE bits in the PMMODE register.

The WAITB<1:0> bits (PMMODE<7:6>) define the number of wait cycles for the data setup prior to the PMRD/PMWR strobe in Mode 10, or prior to the PMENB strobe in Mode 11. When multiplexing the address and data bus, ADRMUX<1:0> bits (PMCON<12:11>) = 01, 10 or 11, WAITB defines the number of wait cycles for which the addressing period is extended.

The WAITM<3:0> bits (PMMODE<5:2>) define the number of wait cycles for the PMRD/PMWR strobe in Mode 10, or for the PMENB strobe in Mode 11. When this Wait state setting is '0000', WAITB and WAITE are ignored. The number of Wait states for the data setup time (WAITB) defaults to one, while the number of Wait states for data hold time (WAITE) defaults to one during a write operation and zero during a read operation.

The WAITE<1:0> bits (PMMODE<1:0>) define the number of wait cycles for the data hold time after the PMRD/PMWR strobe in Mode 10, or after the PMENB strobe in Mode 11.

# 13.3.1.8 ADDRESS MULTIPLEXING

Address multiplexing allows some or all address line signals to be generated from the data bus during the address cycle of a read/write operation. This can be a useful option for address lines PMA<15:0> needed as general purpose I/O pins. The user application can select to multiplex the lower 8 data bits, upper 8 data bits or full 16 data bits. These multiplexing modes are available in both Master mode 1 and 2. For Multiplexing mode timing diagrams, see 13.3.8 "Master Mode Timing".

Table 13-5: Address Multiplex Configurations

| ADRMUX<1:0> | Address/Data Multiplex Modes                           |

|-------------|--------------------------------------------------------|

| 11          | Fully multiplexed (16 data pins PMD<15:0>)             |

| 10          | Fully multiplexed (lower eight data pins PMD<7:0>)     |

| 01          | Partially multiplexed (lower eight data pins PMD<7:0>) |

| 00          | Demultiplexed                                          |

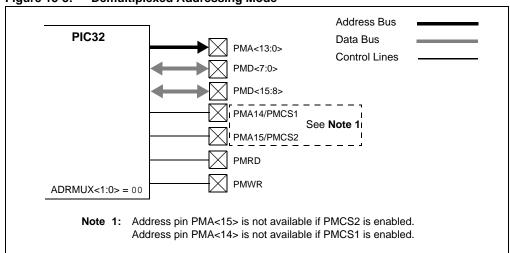

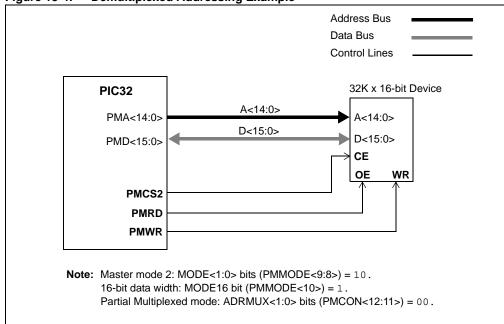

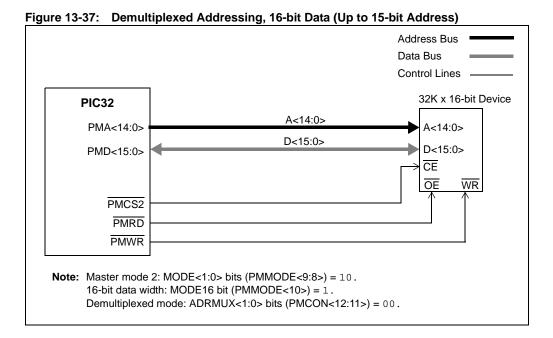

# 13.3.1.8.1 Demultiplexed Mode

Demultiplexed mode is selected by configuring the ADRMUX<1:0> bits (PMCON<12:11>) = 00. In this mode, address bits are presented on pins PMA<15:0>.

When PMCS2 is enabled, address pin PMA15 is not available. When PMCS1 is enabled, address pin PMA14 is not available.

In 16-bit Data mode, data bits are presented on pins PMD<15:0>. In 8-bit Data mode, data bits are presented on pins PMD<7:0>.

Figure 13-3: Demultiplexed Addressing Mode

Figure 13-4: Demultiplexed Addressing Example

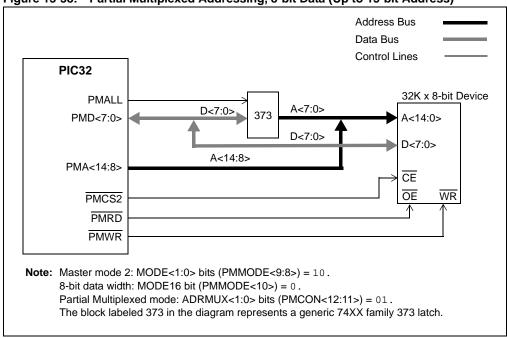

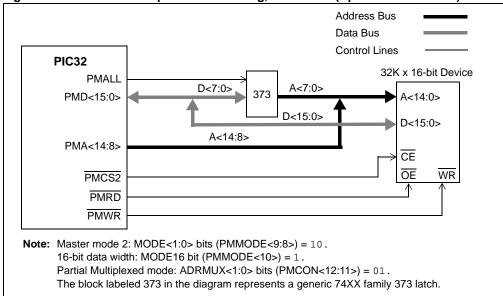

# 13.3.1.8.2 Partially Multiplexed Mode

Partially Multiplexed mode (8-bit data pins) is available in both 8-bit and 16-bit data bus configurations and is selected by setting the ADRMUX<1:0> bits (PMCON<12:11>) = 01. In this mode, the lower eight address bits are multiplexed with the lower eight data bus pins, PMD<7:0>. The upper eight address bits are unaffected and are presented on PMA<15:8>. In this mode, address pins PMA<7:1> are available as general purpose I/O pins.

Address pin PMA15 is not available when PMCS2 is enabled; address pin PMA14 is not available when PMCS1 is enabled.

Address pin PMA<0> is used as an address latch enable strobe, PMALL, during which the lower eight bits of the address are presented on the PMD<7:0> pins. Read and write sequences are extended by at least three peripheral bus clock cycles (TPBCLK).

If WAITM<3:0> (PMMODE<5:2>) is non-zero, the PMALL strobe will be extended by WAITB<1:0> (PMMODE<7:6>) Wait states.

Address Bus Multiplexed Address/Data Bus PIC32 PMA<13:8> Data Bus PMD<7:0> Control Lines PMD<15:8> PMA14/PMCS1 PMA15/PMCS2 PMA0/PMALL **PMRD PMWR** ADRMUX<1:0> = 01 Note 1: Address pin PMA<15> is not available if PMCS2 is enabled. Address pin PMA<14> is not available if PMCS1 is enabled.

**Partial Multiplexed Addressing Mode Figure 13-5:**

Figure 13-6: **Partial Multiplexed Addressing Example**

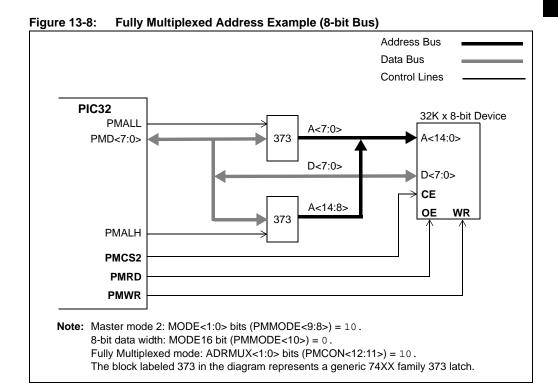

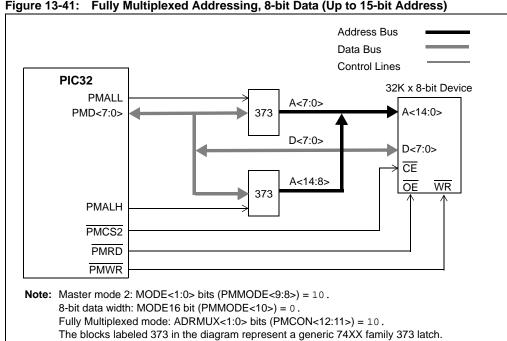

# 13.3.1.8.3 Fully Multiplexed Mode (8-bit Data Pins)

Fully Multiplexed mode (8-bit data pins) is available in both 8-bit and 16-bit data bus configurations and is selected by setting the ADRMUX<1:0> bits (PMCON<12:11>) = 10. In this mode, the entire 16 bits of the address are multiplexed with the lower eight data bus pins, PMD<7:0>. In this mode, PMA<13:2> pins are available as general purpose I/O pins.

If PMCS2/PMA15 or PMCS1/PMA14 are configured as Chip Select pins, the corresponding address bit, PMADDR<15> or PMADDR<14> is automatically forced to '0'.

Address pins PMA<0> and PMA<1> are used as an address latch enable strobes, PMALL and PMALH, respectively. During the first cycle, the lower eight address bits are presented on the PMD<7:0> pins with the PMALL strobe active. During the second cycle, the upper eight address bits are presented on the PMD<7:0> pins with the PMALH strobe active. The read and write sequences are extended by at least six peripheral bus clock cycles (TPBCLK).

If WAITM<3:0> (PMMODE<5:2>) is non-zero, both PMALL and PMALH strobes will be extended by WAITB<1:0> (PMMODE<7:6>) Wait states.

Fully Multiplexed Address/Data Bus

PMC32

PMC32

PMC31

See Note 1

PMA15/ PMCS2

PMA0/PMALL

PMA1/PMALH

PMRD

ADRMUX<1:0> = 10

PMWR

Figure 13-7: Fully Multiplexed Addressing Mode (8-bit Bus)

**Note 1:** Address bit PMADDR<15> is forced to '0' when PMCS2 is enabled. Address bit PMADDR<14> is forced to '0' when PMCS1 is enabled.

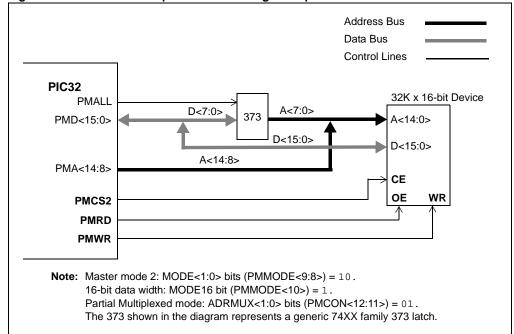

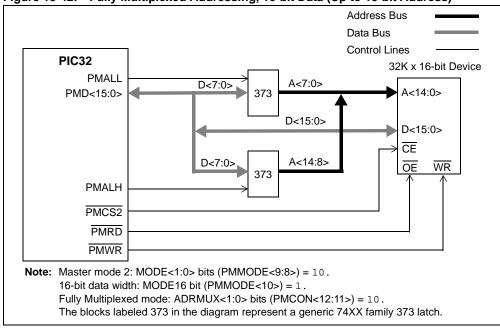

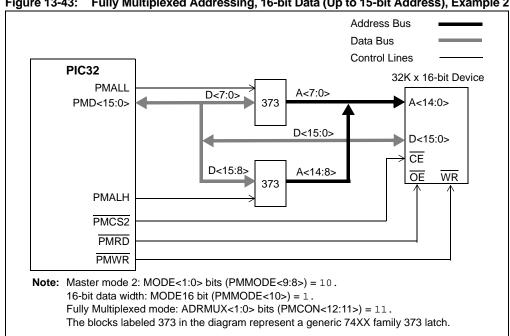

# 13.3.1.8.4 Fully Multiplexed Mode (16-bit Data Pins)

Fully Multiplexed mode (16-bit data pins) is only available in the 16-bit data bus configuration and is selected by configuring the ADRMUX<1:0> bits (PMCON<12:11>) = 11. In this mode, the entire 16 bits of the address are multiplexed with all 16 data bus pins, PMD<15:0>.

If PMCS2/PMA15 or PMCS1/PMA14 are configured as Chip Select pins, the corresponding address bit, PMADDR<15> or PMADDR<14> is automatically forced to '0'.

Address pins PMA<0> and PMA<1> are used as an address latch enable strobes, PMALL and PMALH, respectively, and at the same time. While the PMALL and PMALH strobes are active, the lower eight address bits are presented on the PMD<7:0> pins and the upper eight address bits are presented on the PMD<15:8> pins. The read and write sequences are extended by at least 3 peripheral bus clock cycles (TPBCLK).

If WAITM<3:0> (PMMODE<5:2>) is non-zero, both PMALL and PMALH strobes will be extended by WAITB<1:0> (PMMODE<7:6>) Wait states.

Figure 13-9: Fully Multiplexed Addressing Mode (16-bit Bus)

Fully Multiplexed Address/Data Bus

PMD<7:0> Control Lines

PMD<15:8>

PMD<15:8>

PMA14/ PMCS1

See Note 1

PMA0/PMALL

PMA0/PMALL

PMA0/PMALL

PMRD

PMRD

PMWR

Note 1: Address bit PMADDR<15> is forced to '0' when PMCS2 is enabled.

Address bit PMADDR<14> is forced to '0' when PMCS1 is enabled.

Figure 13-10: Fully Multiplexed Addressing Example (16-bit Bus) Address Bus Data Bus Control Lines PIC32 32K x 16-bit Device **PMALL** A<7:0> D<7:0> PMD<15:0> 373 A<14:0> D<15:0> D<15:0> CE D<15:8> A<14:8> OE WR 373 **PMALH** PMCS2 **PMRD PMWR** Note: Master mode 2: MODE<1:0> bits (PMMODE<9:8>) = 10. 16-bit data width: MODE16 bit (PMMODE<10>) = 1. Fully Multiplexed mode: ADRMUX<1:0> bits (PMCON<12:11>) = 11. The 373 shown in the diagram represents a generic 74XX family 373 latch.

# 13.3.2 Master Mode Configuration

The Master mode configuration is determined primarily by the interface requirements to the external device. Address multiplexing, control signal polarity, data width and Wait states typically dictate the specific configuration of the PMP.

To use the PMP as a master, the module must be enabled by setting the ON control bit (PMCON<15>) = 1, and the mode must be set to one of two possible master modes. Control bits MODE<1:0> (PMMODE<9:8>) = 10 for Master mode 2, or MODE<1:0> = 11 for Master mode 1.

The following Master mode initialization steps properly prepares the PMP port for communicating with an external device.

- If interrupts are used, disable the PMP interrupt by clearing the interrupt enable bit, PMPIE (IEC1<2>) = 0.

- 2. Stop and reset the PMP module by clearing the ON control bit (PMCON<15>) = 0.

- 3. Configure the desired settings in the PMCON, PMMODE and PMAEN control registers.

- 4. If interrupts are used:

- a) Clear the interrupt flag bit, PMPIF (IFS1<2>) = 0.

- b) Configure the PMP interrupt priority bits PMPIP<2:0> (IPC7<4:2>) and the interrupt subpriority bits PMPIS (IPC7<1:0>).

- c) Enable the PMP interrupt by setting the interrupt enable bit, PMPIE = 1.

- 5. Enable the PMP master port by setting the ON control bit = 1.

**Note:** It is recommended to wait for any pending read or write operation to be completed before reconfiguring the PMP module.

The following list illustrates an example setup for a typical Master mode 2 operation:

- 1. Select Master mode 2: MODE<1:0> bits (PMMODE<9:8>) = 10.

- 2. Select 16-bit Data mode: MODE16 bit (PMMODE<10>) = 0.

- 3. Select partially multiplexed addressing: ADRMUX<1:0> bits (PMCON<12:11>) = 01.

- 4. Select auto address increment: INCM<1:0> bits (PMMODE<12:11>) = 01.

- 5. Enable Interrupt Request mode: IRQM<1:0> bits (PMMODE<14:13>) = 01.

- 6. Enable PMRD strobe: PTRDEN bit (PMCON<8>) = 1.

- 7. Enable PMWR strobe: PTWREN bit (PMCON<9>) = 1.

- 8. Enable PMCS2 and PMCS1 Chip Selects: CSF<1:0> bits (PMCON<7:6>) = 10.

- 9. Select PMRD active-low pin polarity: RDSP bit (PMCON<0>) = 0.

- 10. Select PMWR active-low pin polarity: WRSP bit (PMCON<1>) = 0.

- 11. Select PMCS2, PMCS1 active-low pin polarity: CS2P bit (PMCON<4>) = 0 and CS1P bit (PMCON<3>) = 0.

- 12. Select 1 wait cycle for data setup: WAITB<1:0> bits (PMMODE<7:6>) = 00.

- 13. Select 2 wait cycles to extend PMRD/PMWR: WAITM<3:0> bits (PMMODE<5:2>) = 0001.

- 14. Select 1 wait cycle for data hold: WAITE<1:0> bits (PMMODE<1:0>) = 00.

- 15. Enable upper 8 PMA<15:8> address pins: PMAEN<15:8> = 1 (the lower 8 bits can be used as general purpose I/O).

See the code shown in Example 13-1.

#### Example 13-1: Initialization for Master Mode 2, Demultiplexed Address, 16-bit Data

```

Configuration Example: Master mode 2, 16-bit data, partially multiplexed

address/data, active-lo polarities. */

IEC1CLR = 0x0004

// Disable PMP interrupt

// Stop PMP module and clear control register

PMCON = 0 \times 0000;

PMCONSET = 0 \times 0 B80;

// Configure the addressing and polarities

PMMODE = 0x2A40;

// Configure the mode

PMAEN = 0xFF00;

// Enable all address and Chip Select lines

IPC7SET = 0x001C;

// Set priority level = 7 and

// Set subpriority level = 3

IPC7SET = 0x0003;

// Could have also done this in single

// operation by assigning IPC7SET = 0x001F

IEC1SET = 0 \times 0004;

// Enable PMP interrupts

PMCONSET = 0x8000;

// Enable the PMP module

```

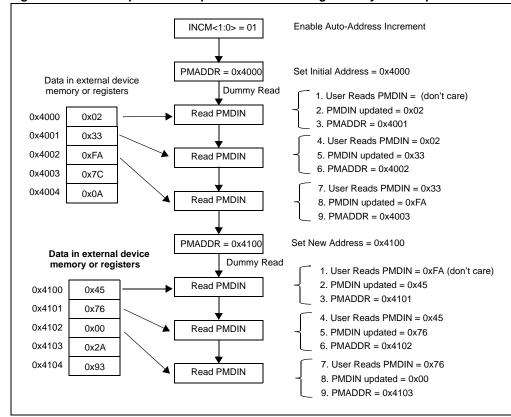

## 13.3.3 Read Operation

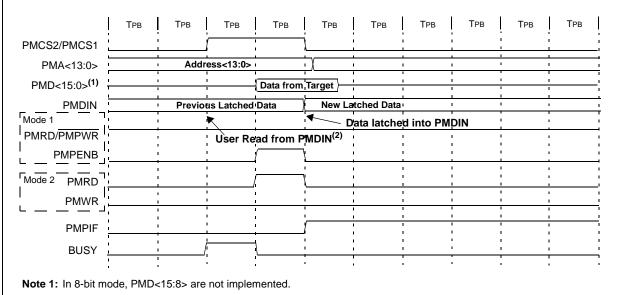

To perform a read on the parallel bus, the user application reads the PMDIN register. The effect of reading the PMDIN register retrieves the current value and causes the PMP to activate the Chip Select lines and the address bus. The read line PMRD is strobed in Master mode 2, PMRD/PMWR and PMENB lines in Master mode 1, and the new data is latched into the PMDIN register making it available the next time the PMDIN register is read.

Note that the read data obtained from the PMDIN register is actually the read value from the previous read operation. Therefore, the first user application read will be a dummy read to initiate the first bus read and fill the read register. See Figure 13-11, which illustrates this sequence. Also, the requested read value will not be ready until after the BUSY bit (PMMODE<15>) is observed low. Therefore, in a back-to-back read operation, the data read from the register will be the same for both reads. The next read of the register will yield the new value.

In 16-bit Data mode (MODE16 bit (PMMODE<10>) = 1), the read from the PMDIN register causes the data bus PMD<15:0> to be read into PMDIN<15:0>. In 8-bit mode, MODE16 bit (PMMODE<10>) = 0, the read from the PMDIN register causes the data bus PMD<7:0> to be read into PMDIN<7:0>. The upper 8 bits, PMD<15:8>, are ignored.

Figure 13-11: Example Read Sequence Demonstrating 'Dummy' Read Operation

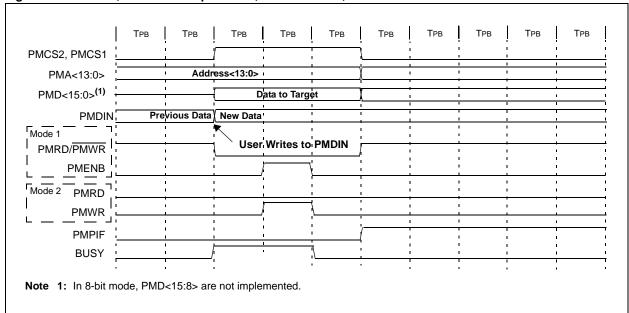

# 13.3.4 Write Operation

To perform a write on the parallel port, the user application writes to the PMDIN register (same register as a read operation). This causes the PMP module to first activate the Chip Select lines and the address bus. The write data from the PMDIN register is placed onto the PMD data bus and the write line PMPWR is strobed in Master mode 2, PMRD/PMWR and PMENB lines in Master Mode 1.

In 16-bit Data mode (MODE16 bit (PMMODE<10>) = 1), the write to the PMDIN register causes PMDIN<15:0> to appear on the data bus, (PMD<15:0>). In 8-bit mode, MODE16 bit (PMMODE<10>) = 0, the write to the PMDIN register causes PMDIN<7:0> to appear on the data bus, PMD<7:0>. The upper 8 bits, PMD<15:8>, are ignored.

# 13.3.5 Master Mode Interrupts

In PMP master modes, the PMPIF bit is set on every read or write strobe. An interrupt request is generated when the IRQM<1:0> bits (PMMODE<14:13>) are set = 01 and PMP interrupts are enabled, PMPIE (IEC1<2>) = 1.

#### 13.3.6 Parallel Master Port Status – The BUSY Bit

In addition to the PMP interrupt, the BUSY bit (PMMODE<15>) is provided to indicate the status of the module. This bit is only used in Master mode.

While any read or write operation is in progress, the BUSY bit is set for all but the very last peripheral bus cycle of the operation. This is helpful when Wait states are enabled or multiplexed address/data is selected. While the bit is set, any request by the user to initiate a new operation will be ignored (i.e., writing or reading the PMDIN register will not initiate a read or a write).

Since the system clock, SYSCLK, can operate faster than the peripheral bus clock in certain configurations, or if a large number of Wait states are used, it is possible for the PMP module to be in the process of completing a read or write operation when the next CPU instruction is reading or writing to the PMP module. For this reason, it is highly recommended that the BUSY bit be checked prior to any operation that accesses the PMDIN or PMADDR register. Example 13-2 shows a polling operation of the BUSY bit prior to accessing the PMP module.

In most applications, the PMP module's Chip Select pin(s) provide the Chip Select interface and is under the timing control of the PMP module. However, some applications may require the PMP Chip Select pin(s) to not be configured as a Chip Select, but as a high order address line, such as PMA<14> or PMA<15>. In this situation, the application's Chip Select function must be provided by an available I/O port pin under software control. In these cases, it is especially important that the user's software poll the BUSY bit to ensure any read or write operation is complete before deasserting the software controlled Chip Select.

#### Example 13-2: Example Code: Polling the BUSY Bit Flag

```

This example reads 256 16-bit words from an external device at address 0x4000 and copies

the data to a second external device at address 0x8000. The PMP port is operating in

Master mode 2. Note how the PMP's BUSY bit is polled prior to all operations to the

PMDOUT, PMDIN or PMADDR register, except where noted. */

unsigned short DataArray<256>;

// Provide the setup code here including large Wait

// states, auto increment.

CopyData();

// A call to the copy function is made.

void CopyData()

PMADDR = 0x4000;

// Initialize PMP address. First time, no need to poll BUSY bit

while(PMMODE & 0x8000);

// Poll - if busy, wait before reading.

// Read the PMDIN to clear previous data and latch new

PMDIN;

// data.

for(i=0; i<256; i++)

while(PMMODE & 0x8000);

// Poll - if busy, wait before reading.

DataArray<i> = PMDIN;

// Read the external device.

while(PMMODE & 0x8000);

// Poll - if busy, wait before changing PMADDR.

PMADDR = 0x8000;

// Address of second external device.

for(i=0; i<256; i++)

while(PMMODE & 0x8000); // Poll - if busy, wait before writing.

DataArray<i> = PMDIN;

// Read the external device.

return();

```

# 13.3.7 Addressing Considerations

The PMCS2 and PMCS1 Chip Select pins share functionality with address lines A15 and A14. It is possible to enable both PMCS2 and PMCS1 as Chip Selects, or enable only PMCS2 as a Chip Select; allowing PMCS1 to function strictly as address line A14. It is not possible to enable only PMCS1.

**Note:** Setting both A15 and A14 = 1 when PMCS2 and PMCS1 are enabled as Chip Selects will cause both PMCS2 and PMCS1 to be active during a read or write operation. This may enable two devices simultaneously and should be avoided.

When configured as Chip Selects, a '1' must be written into bit position 15 or 14 of the PMADDR register in order for PMCS2 or PMCS1 to become active during a read or write operation. Failing to write a '1' to PMCS2 or PMCS1 does not prevent address pins PMA<13:0> from being active as the specified address appears; however, no Chip Select signal will be active.

**Note:** When using Auto-Increment Address mode, PMCS2 and PMCS1 do not participate and must be controlled by the user's software by writing to '1' to PMADDR<15:14> explicitly.

In fully multiplexed modes, address bits PMADDR<15:0> are multiplexed with the data bus and in the event address bits PMA15 or PMA14 are configured as Chip Selects, the corresponding PMADDR<15:14> address bits are automatically forced to '0'. Disabling one or both PMCS2 and PMCS1 makes these bits available as address bits PMADDR<15:14>.

In any of the master mode multiplexing schemes, disabling both Chip Select pins PMCS2 and PMCS1 requires the user to provide Chip Select line control through some other I/O pin under software control, as shown in Figure 13-12.

Refer to 13.12 "Design Tips" for more information on memory banking.

Figure 13-12: PMP Chip Select Address Maps

# 13.3.8 Master Mode Timing

A PMP Master mode cycle time is defined as the number of PBCLK cycles required by the PMP to perform a read or write operation and is dependent on PBCLK clock speed, PMP Address/Data Multiplexing modes, and the number of PMP wait states, if any. Refer to the specific device data sheet for setup and hold timing characteristics.

A PMP Master mode read or write cycle is initiated by accessing (reading or writing) the PMDIN register. Table 13-6 provides a summary of read and write PMP cycle times for each multiplex configuration.

The actual data rate of the PMP (the rate at which the user's code can perform a sequence of read or write operations) will be highly dependent on several factors:

- · User's application code content

- · Code optimization level

- · Internal bus activity

- Other factors relating to the instruction execution speed

During any Master mode read or write operation, the busy flag will always de-assert 1 peripheral bus clock cycle (TPBCLK), before the end of the operation, including Wait states. The user's application must check the status of the busy flag to ensure it is equal to '0' before initiating the next PMP operation.

Table 13-6: PMP Read/Write Cycle Times<sup>(1)</sup>

| Address/Data Multiplex Configuration | ADRMUX Bit | PMP Cycle Time<br>(PBCLK Cycles) |       |

|--------------------------------------|------------|----------------------------------|-------|

|                                      | Settings   | Read                             | Write |

| Fully Multiplexed (16-bit data)      | 11         | 5                                | 6     |

| Fully Multiplexed (8-bit data)       | 10         | 8                                | 9     |

| Partial Multiplex                    | 01         | 5                                | 6     |

| Demultiplexed                        | 00         | 2                                | 3     |

Note 1: Wait states are not enabled.

The following timing examples represent the common master mode configuration options. These options vary from 8-bit to 16-bit data, non-multiplexed to fully multiplexed address, as well as with and without Wait states. For illustration purposes only, all control signal polarities are shown as "active-high".

#### 13.3.8.1 DEMULTIPLEXED ADDRESS AND DATA TIMING

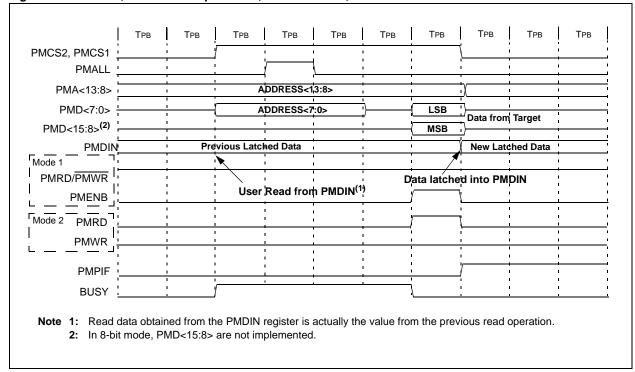

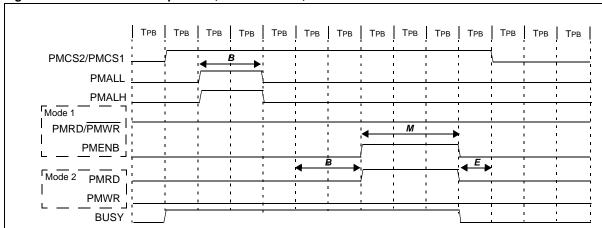

The timing diagram in Figure 13-13 illustrates the demultiplexed timing (separate address and data bus) for a read operation with no Wait states. A read operation requires 2 TPBCLK, peripheral bus clock cycles.

Figure 13-13: 8-bit, 16-bit Read Operations, ADRMUX = 00, No Wait States

2: Read data obtained from the PMDIN register is actually the value from the previous read operation.

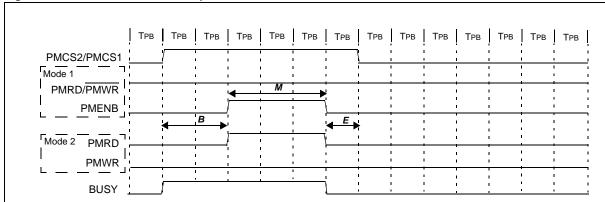

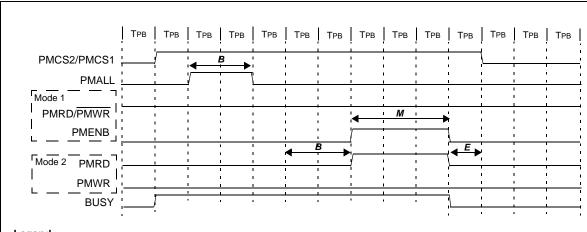

In this timing diagram with Wait states, shown in Figure 13-14, the read operation requires 6 TPBCLK, peripheral bus clock cycles.

Figure 13-14: 8-bit, 16-bit Read Operations, ADRMUX = 00, Wait States Enabled

Legend:

**B** = WAITB<1:0> = 01 (2 Wait states)

M = WAITM < 3:0 > = 0010 (3 Wait states)

**E** = WAITE<1:0> = 01 (1 Wait state)

Note: If WAITM<3:0> = 0000, M is forced to 1 TPBCLK, WAITB is ignored (B forced to 1 TPBCLK), and WAITE is ignored (E forced to 0 TPBCLK).

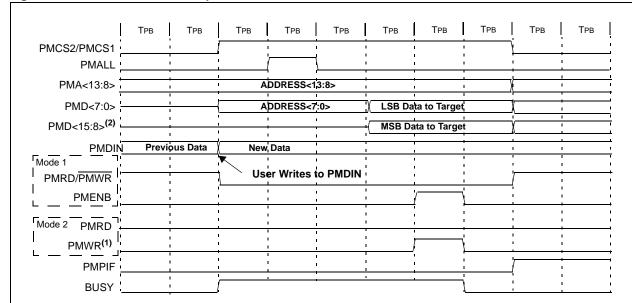

The timing diagram in Figure 13-15 illustrates demultiplexed timing (separate address and data bus) for a write operation with no Wait states. A write operation requires 3 TPBCLK, peripheral bus clock cycles.

Figure 13-15: 8-bit, 16-bit Write Operations, ADRMUX = 00, No Wait States

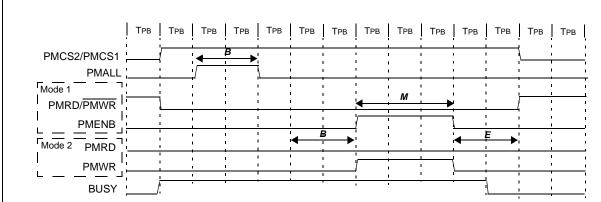

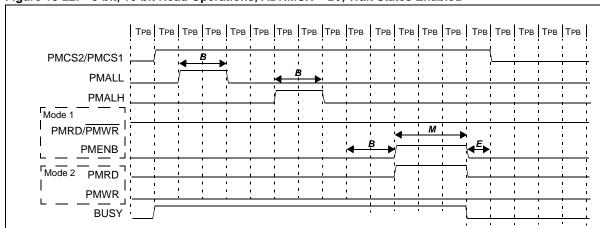

In this timing diagram with Wait states, shown in Figure 13-16, the write operation requires 7 TPBCLK, peripheral bus clock cycles.

Figure 13-16: 8-bit, 16-bit Write Operations, ADRMUX = 00, Wait States Enabled

## Legend:

**B** = WAITB<1:0> = 01 (2 Wait states)

**M** = WAITM<3:0> = 0010 (3 Wait states)

**E** = WAITE<1:0> = 01 (2 Wait states)

Note: If WAITM<3:0> = 0000, M is forced to 1 TPBCLK, WAITB is ignored (B forced to 1 TPBCLK), and WAITE is ignored (E forced to 1 TPBCLK).

#### 13.3.8.2 PARTIALLY MULTIPLEXED ADDRESS AND DATA TIMING

The timing diagram shown in Figure 13-17 illustrates partially multiplexed timing (address bits <7:0> multiplexed with data bus, PMD<7:0>) for a read operation with no Wait states. A read operation requires 5 TPBCLK, peripheral bus clock cycles.

Figure 13-17: 8-bit, 16-bit Read Operations, ADRMUX = 01, No Wait States

In this timing diagram with Wait states, shown in Figure 13-18, the read operation requires 10 TPBCLK, peripheral bus clock cycles.

Figure 13-18: 8-bit, 16-bit Read Operations, ADRMUX = 01, Wait States Enabled

Legend:

**B** = WAITB<1:0> = 01 (2 Wait states)

M = WAITM < 3:0 > = 0010 (3 Wait states)

**E** = WAITE<1:0> = 01 (1 Wait state)

Note: If WAITM<3:0> = 0000, M is forced to 1 TPBCLK, WAITB is ignored (B forced to 1 TPBCLK), and WAITE is ignored (E forced to 0 TPBCLK).

The timing diagram shown in Figure 13-19 illustrates partially multiplexed timing (address bits <7:0> multiplexed with data bus, PMD<7:0>) for a write operation with no Wait states. A write operation requires 6 TPBCLK, peripheral bus clock cycles.

Figure 13-19: 8-bit, 16-bit Write Operations, ADRMUX = 01, No Wait States

Note 1: During a write operation, there is one TPBCLK hold cycle following the PMWR signal.

2: In 8-bit mode, PMD<15:8> are not implemented.

In this timing diagram with Wait states, shown in Figure 13-20, the write operation requires 11 TPBCLK, peripheral bus clock cycles.

Figure 13-20: 8-bit, 16-bit Write Operations, ADRMUX = 01, Wait States Enabled

Legend:

$\mathbf{B} = \text{WAITB} < 1:0 > = 01 \text{ (2 Wait states)}$

M = WAITM < 3:0 > = 0010 (3 Wait states)

**E** = WAITE<1:0> = 01 (1 Wait state)

Note: If WAITM<3:0> = 0000, M is forced to 1 TPBCLK, WAITB is ignored (B forced to 1 TPBCLK), and WAITE is ignored (E forced to 1 TPBCLK).

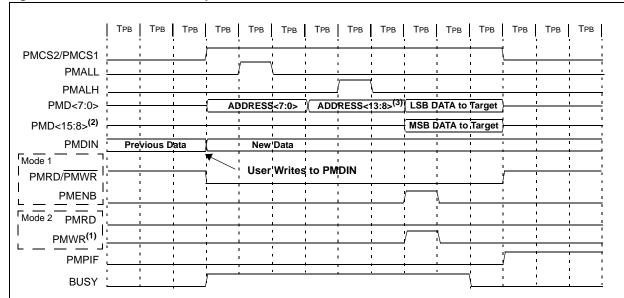

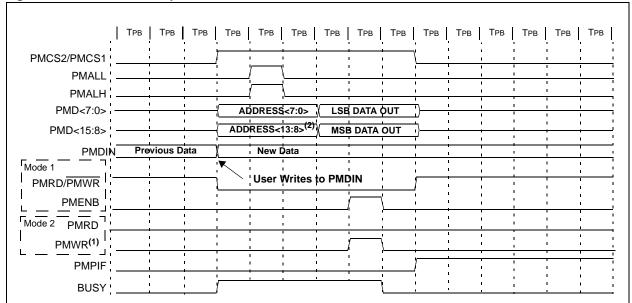

# 13.3.8.3 FULLY MULTIPLEXED (8-BIT BUS) ADDRESS AND DATA TIMING

The timing diagram in Figure 13-21 illustrates fully multiplexed timing (address bits <15:0> multiplexed with data bus, PMD<7:0>) for a read operation with no Wait states. A read operation requires 8 TPBCLK, peripheral bus clock cycles.

Трв Трв Трв Трв Трв Трв Трв Трв Трв PMCS2/PMCS1 **PMALL PMALH** PMD<7:0> ADDRESS<7:0> ADDRESS<13:8>(3) LSB **Data from Target** PMD<15:8>(2) MSB · **Previous Latched Data New Latched Data PMDIN** Mode 1 PMRD/PMWR User Read from PMDIN<sup>(1)</sup> **Data latched into PMDIN PMENB** Mode 2 **PMRD PMWR PMPIF BUSY**

Figure 13-21: 8-bit, 16-bit Read Operations, ADRMUX = 10, No Wait States

- Note 1: Read data obtained from the PMDIN register is actually the value from the previous read operation.

- 2: In 8-bit mode, PMD<15:8> are not implemented.

- 3: PMADDR address bit A15 and A14 are forced to '0' if PMCS2 and/or PMCS1 are enabled as Chip Selects.

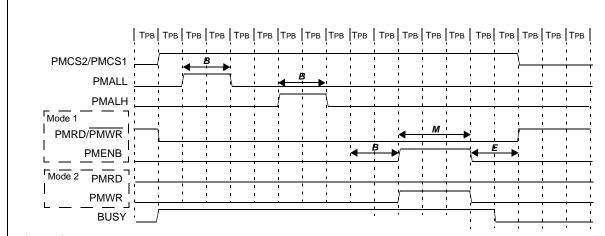

In this timing diagram with Wait states, shown in Figure 13-22, the read operation requires 14 TPBCLK, peripheral bus clock cycles.

Figure 13-22: 8-bit, 16-bit Read Operations, ADRMUX = 10, Wait States Enabled

# Legend:

**B** = WAITB<1:0> = 01 (2 Wait states)

M = WAITM < 3:0 > = 0010 (3 Wait states)

**E** = WAITE<1:0> = 01 (1 Wait state)

Note: If WAITM<3:0> = 0000, M is forced to 1 TPBCLK, WAITB is ignored (B forced to 1 TPBCLK), and WAITE is ignored (E forced to 0 TPBCLK).

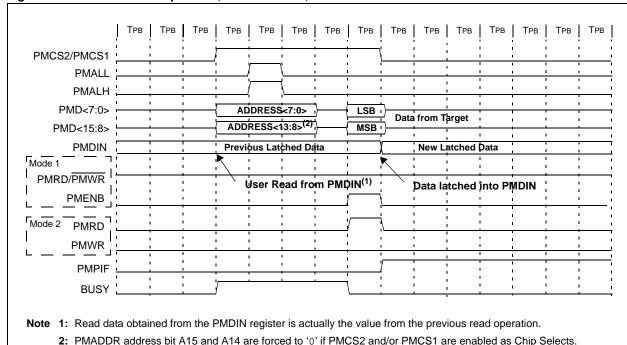

The timing diagram shown in Figure 13-23 illustrates fully multiplexed timing (address bits <15:0> multiplexed with data bus, PMD<7:0>) for a write operation with no Wait states. A write operation requires 9 TPBCLK, peripheral bus clock cycles.

Figure 13-23: 8-bit, 16-bit Write Operations, ADRMUX = 10, No Wait States

Note 1: During a write operation, there is one TPBCLK hold cycle following the PMWR signal.

2: In 8-bit mode, PMD<15:8> are not implemented.

3: PMADDR address bit A15 and A14 are forced to '0', if PMCS2 and/or PMCS1 are enabled as Chip Selects.

In this timing diagram with Wait states, shown in Figure 13-24, the write operation requires 15 TPBCLK, peripheral bus clock cycles.

Figure 13-24: 8-bit, 16-bit Write Operations, ADRMUX = 10, Wait States Enabled

Legend:

**B** = WAITB<1:0> = 01 (2 Wait states)

M = WAITM < 3:0 > = 0010 (3 Wait states)

**E** = WAITE<1:0> = 01 (2 Wait states)

Note: If WAITM<3:0> = 0000, M is forced to 1 TPBCLK, WAITB is ignored (B forced to 1 TPBCLK), and WAITE is ignored (E forced to 1 TPBCLK).

# 13.3.8.4 FULLY MULTIPLEXED (16-BIT BUS) ADDRESS AND DATA TIMING

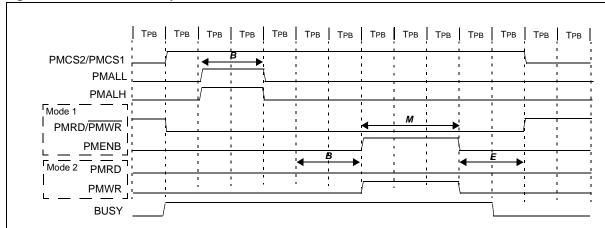

The timing diagram shown in Figure 13-25 illustrates fully multiplexed timing (address bits <15:0> multiplexed with data bus, PMD<15:0>) for a read operation with no Wait states. A read operation requires 5 TPBCLK, peripheral bus clock cycles.

Figure 13-25: 16-bit Read Operation, ADRMUX = 11, No Wait States

·

In this timing diagram with Wait states, shown in Figure 13-26, the read operation requires 10 TPBCLK, peripheral bus clock cycles.

Figure 13-26: 16-bit Read Operation, ADRMUX = 11, Wait States Enabled

Legend:

**B** = WAITB<1:0> = 01 (2 Wait states)

M = WAITM < 3:0 > = 0010 (3 Wait states)

**E** = WAITE<1:0> = 01 (1 Wait state)

Note: If WAITM<3:0> = 0000, M is forced to 1 TPBCLK, WAITB is ignored (B forced to 1 TPBCLK), and WAITE is ignored (E forced to 0 TPBCLK).

The timing diagram shown in Figure 13-27 illustrates fully multiplexed timing (address bits <15:0> multiplexed with data bus, PMD<15:0>) for a write operation with no Wait states. A read operation requires 6 TPBCLK, peripheral bus clock cycles.

Figure 13-27: 16-bit Write Operation, ADRMUX = 11, No Wait States

Note 1: During a write operation, there is one TPB hold cycle following the PMWR signal.

2: PMADDR address bit A15 and A14 are forced to '0' if PMCS2 and/or PMCS1 are enabled as Chip Selects.

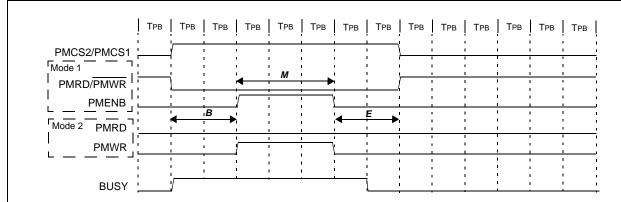

In this timing diagram with Wait states, shown in Figure 13-28, the write operation requires 11 TPBCLK, peripheral bus clock cycles.

Figure 13-28: 16-bit Write Operation, ADRMUX = 11, Wait States Enabled

#### Legend:

**B** = WAITB<1:0> = 01 (2 Wait states)

**M** = WAITM<3:0> = 0010 (3 Wait states)

**E** = WAITE<1:0> = 01 (2 Wait states)

Note: If WAITM<3:0> = 0000, M is forced to 1 ΤΡΒCLK, WAITB is ignored (B forced to 1 ΤΡΒCLK), and WAITE is ignored (E forced to 1 ΤΡΒCLK).

# 13.4 SLAVE MODES OF OPERATION

The PMP module provides 8-bit (byte) legacy Parallel Slave Port (PSP) functionality as well as new buffered and addressable slave modes.

Table 13-7: Slave Mode Selection

| Slave Mode  | PMMODE<9:8> bits<br>(MODE<1:0>) | PMMODE<12:11> bits<br>(INCM<1:0>) |

|-------------|---------------------------------|-----------------------------------|

| Addressable | 01                              | x = don't care                    |

| Legacy      | 00                              | x = don't care                    |

| Buffered    | 00                              | 11                                |

All slave modes support 8-bit data only and the module control pins are automatically dedicated when any of these modes are selected. The user application only needs to configure the polarity of the PMCS1, PMRD and PMWR signals.

Table 13-8: Slave Mode Pin Polarity Configuration

| CONTROL<br>PIN | PMCON<br>Control Bit | Active-High<br>Select | Active-Low<br>Select |

|----------------|----------------------|-----------------------|----------------------|

| PMRD           | RDSP                 | 1                     | 0                    |

| PMWR           | WRSP                 | 1                     | 0                    |

| PMCS1          | CS1P                 | 1                     | 0                    |

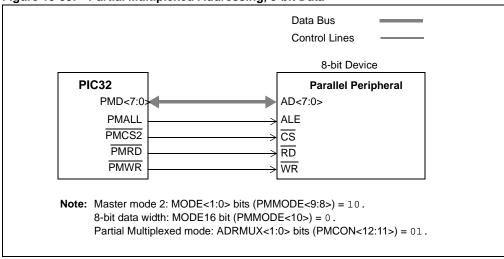

## 13.4.1 Legacy Slave Port Mode

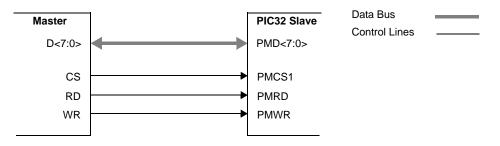

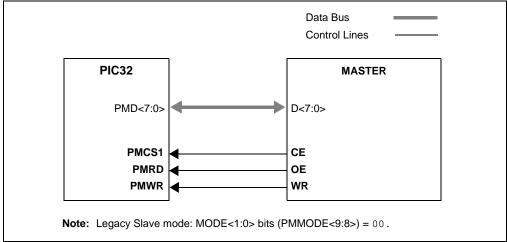

In 8-bit PMP Legacy Slave mode, the module is configured as a PSP using control bits MODE<1:0> (PMMODE<9:8>) = 00. In this mode, an external device such as another microcontroller or microprocessor can asynchronously read and write data using the 8-bit data bus PMD<7:0>, the read PMRD, write PMWR and Chip Select PMCS1 inputs.

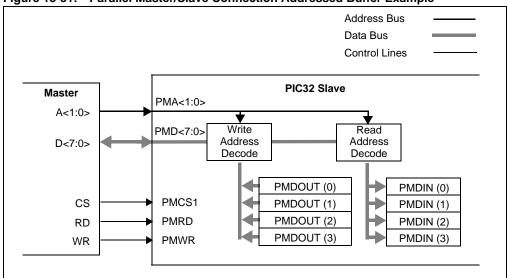

Figure 13-29: Parallel Master/Slave Connection Example

#### 13.4.1.1 INITIALIZATION STEPS

The following Slave mode initialization steps properly prepares the PMP port for communicating with an external device.

- 1. Clear the ON control bit (PMCON<15> = 0) to disable the PMP module.

- 2. Select Legacy mode with the MODE<1:0> bits (PMMODE<9:8>) = 00.

- 3. Select the polarity of the Chip Select pin, CS1P (PMCON<3>).

- 4. Select the polarity of the control pins, WRSP (PMCON<1>) and RDSP (PMCON<0>).

- 5. If interrupts are used:

- a) Clear the interrupt flag bit, PMPIF (IFS1<2>) = 0.

- b) Configure the PMP interrupt priority bits, PMPIP<2:0> (IPC7<4:2>) and the interrupt subpriority bits PMPIS (IPC7<1:0>).

- c) Enable the PMP interrupt by setting the interrupt enable bit, PMPIE (IEC1<2>) = 1.

- 6. Set the ON control bit to '1' to enable the PMP module.

# Example 13-3: Legacy Parallel Slave Port Initialization (Example Code)

#### 13.4.1.2 WRITE TO SLAVE PORT

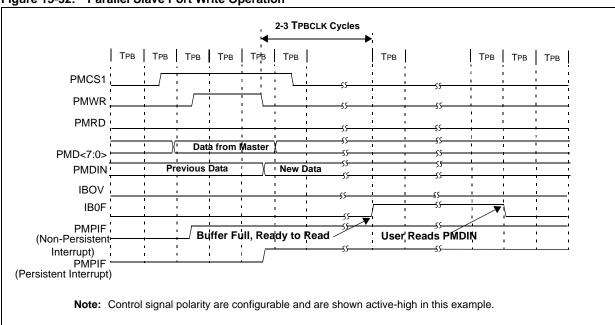

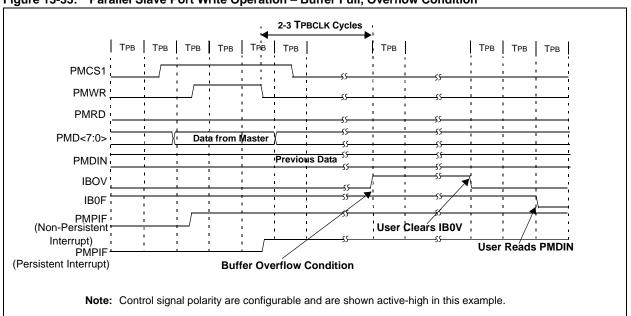

When Chip Select is active and a write strobe occurs, the data on the bus pins PMD<7:0> is captured into the lower 8 bits of the PMDIN register, PMDIN<7:0>. The PMPIF (interrupt flag bit) is set during the write strobe, however, IB0F (input buffer full flag) bit requires two to three peripheral bus clock cycles to synchronize before it is set and the PMDIN register can be read. The IB0F bit will remain set until the PMDIN register is read by the user application. If a write operation occurs while the IB0F = 1, the write data will be ignored and an overflow condition will be generated, IB0V = 1. See the timing diagrams in 13.4.4 "Slave Mode Read and Write Timing Diagrams".

# 13.4.1.3 READ FROM SLAVE PORT

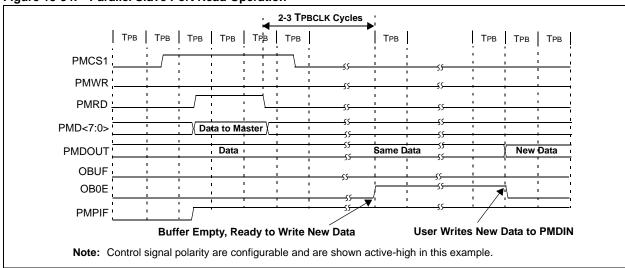

When Chip Select is active and a read strobe occurs, the data from the lower 8 bits of the PMDOUT register (PMDOUT<7:0>) is presented onto data bus pins PMD<7:0> and read by the master device. The PMPIF (interrupt flag bit) is set during the read strobe; however, the OB0E (output buffer empty flag) bit requires two to three peripheral bus clock cycles to synchronize before it is set. The OB0E bit will remain set until the PMDOUT register is written to by the user application. If a read operation occurs while the OB0E = 1, the read data will be the same as the previous read data and an underflow condition will be generated, OBUF = 1. See the timing diagrams in 13.4.4 "Slave Mode Read and Write Timing Diagrams".

#### 13.4.1.4 LEGACY MODE INTERRUPT OPERATION

In PMP Legacy Slave mode, the PMPIF bit is set every read or write strobe. If using interrupts, the user's application vectors to an Interrupt Service Routine (ISR) where the IBF and OBE status bits can be examined to determine if the buffer is full or empty. If not using interrupts, the user's application should wait for PMPIF to be set before polling the IBF and OBE Status bits to determine if the buffer is full or empty.

Note:

On persistent interrupt implementations of the PMP, the interrupt is generated on the falling edge of the WR signal with the WR signal configured to active-high polarity. On non-persistent interrupt implementations of the PMP, the interrupt is generated on the rising edge of the WR signal with the WR signal configured to active-high polarity. Firmware should poll the IBF or IBnF bit to ensure the data is valid before attempting to read the data from the PMP module.