# Field Engineering Theory of Operation

System/360 Model 40

**Comprehensive Introduction**

# Preface

This manual describes the basic data flow, machine instruction, and channel operations of the IBM 2040 Processing Unit. The basic numbering systems used within the IBM System/360 are explained in detail. A thorough understanding of this information is helpful in the study of the more complex units of the system.

Other manuals useful in understanding the Model 40 are:

- IBM System/360 Model 40, Functional Units, Order No. SY22-2843

- IBM System/360 Model 40, Theory of Operation, Order No. SY22-2844

- IBM System/360 Model 40, Power Supplies, Features, and Appendix, Order No. SY22-2845

- IBM System/360 Model 40, Maintenance Manual, Order No. SY22-2841

- IBM System/360 Model 40, Diagrams Manual, Order No. SY22-2842

- Solid Logic Technology Power Supplies, Order No. SY22-2799

- Solid Logic Technology, Packaging, Tools, and Wiring Change, Order No. SY22-2800

This manual is written to engineering change level 254814 for ALD's and CLD level 255263.

#### Sixth Edition (April, 1970)

This edition, Order No. SY22-2840-2, is a reprint of Form Y22-2840-1 incorporating changes released in FE Supplement Y22-6783, dated January 31, 1969. Changes are periodically made to the specifications herein; any such changes will be reported in subsequent revisions or FE Supplements.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. B96, P.O. Box 390, Poughkeepsie, N.Y. 12602. A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be sent to the above address.

© Copyright International Business Machines Corporation 1966, 1970

# Contents

| Introduction to IBM System/360 Model 40 | 5  |

|-----------------------------------------|----|

| System/360                              | 5  |

| The Processor Family                    | 5  |

| Flexibility and Compatibility           | 6  |

| System/360 Model 40                     | 6  |

| Computer Functional Units               | 6  |

| Functional Units – System/360 Model 40  | 9  |

| Data Formats                            | 10 |

| Data Coding                             | 10 |

| Binary Coding                           | 10 |

| Hexadecimal Coding                      | 13 |

| Decimal Coding                          | 13 |

| Data Codes for Input/Output             | 14 |

| Other Data Codes                        | 16 |

| Binary Fixed-Point Arithmetic           | 16 |

| Add and Subtract                        | 16 |

| Multiply                                | 17 |

| Divide                                  | 17 |

| Floating-Point Arithmetic               | 17 |

| Exponential Numbers                     | 18 |

| Floating-Point Notation                 | 18 |

| Decimal Arithmetic                      | 20 |

|                                         | 20 |

| System Controls                         | 22 |

| Instructions                            | 22 |

| Instruction Format                      | 22 |

| Address Generation                      | 23 |

| Instruction Types                       | 24 |

| Data-Handling Instructions              | 24 |

| Branch Instructions                     | 27 |

| Sequential Instruction Execution        | 28 |

| Program Status                          | 29 |

| Program Status Word (PSW)               | 29 |

| Status Switching Instructions           | 30 |

| Interrupt System                        | 30 |

| Types of Interrupts                     | 31 |

| Permanent Main Storage Locations        | 31 |

| Priority of Interrupts                  | 32 |

| Masking of Interrupts in PSW            | 32 |

| Interrupt Code in PSW                   | 33 |

| Instruction Length Code (ILC) in PSW    | 34 |

| CPU Status                              | 34 |

| I/O System                              | 35 |

| Sample System Configuration             | 35 |

| Sample System Soungaration              | 00 |

| Standard Interface                        | - 36 |

|-------------------------------------------|------|

| Input/Output Operations                   | - 36 |

| Channel Types                             | 37   |

| Channel Operation                         | 38   |

|                                           |      |

| Channel Program                           | 38   |

| Device Addressing                         | 39   |

| Channel Address Word (CAW)                | 40   |

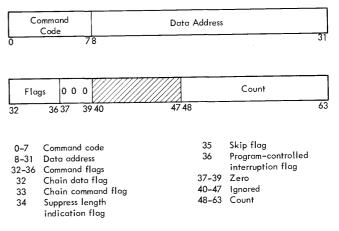

| Channel Command Word (CCW)                | 40   |

| Channel Control                           | 41   |

| Channel Status                            | 42   |

| I/O Instructions                          | 43   |

|                                           | 45   |

| Interrupts                                |      |

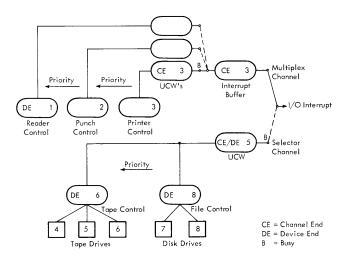

| Generation and Stacking of I/O Interrupts | 45   |

| Clearing of I/O Interrupts                | 46   |

| Sequencing Channel Interrupts             | 47   |

| I/O Interrupt Handling                    | 47   |

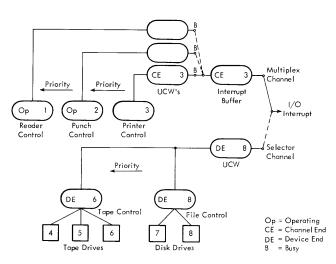

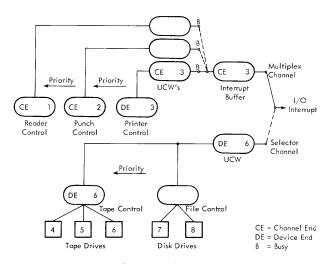

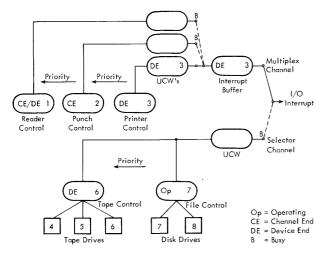

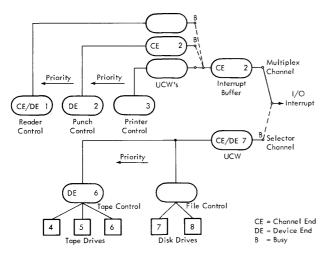

| Examples of Interrupt Sequencing          | 47   |

| Initial Program Load (IPL)                | 49   |

| Multiprogramming                          | 49   |

| System/360 Concept                        | 50   |

| Operating System Principles               | 51   |

| E a Data d'an and Har ll'an               |      |

| Error Detection and Handling              | 52   |

| Machine Malfunctions                      | 52   |

| Programming Errors                        | 52   |

|                                           | -    |

| Basic Data Paths                          | 53   |

| Main Registers and 16-Bit Data Flow       | -53  |

| ALU and 8-Bit Data Flow                   | 53   |

| Staticizer Latches (Stats)                | 53   |

| Local Storage and Addressing              | 53   |

| Main Storage (MS)                         | 55   |

|                                           | 56   |

| Data Transfers                            |      |

| Addressing                                | 56   |

| Extended Addressing                       | 56   |

| Special Area                              | 56   |

| Control                                   | 56   |

| Channels                                  | 57   |

| Multiplex                                 | 57   |

| Selector Channel                          | 57   |

| Selector Chamler                          | 51   |

| Basic System Timing                       | 59   |

| ODIL Timing                               | 59   |

| CPU Timing                                |      |

| CPU and MS Timing                         | 59   |

| Microprogramming Concepts                 | 61   |

|                                           |      |

| FIGURE TITLE                                        |      | PAGE |

|-----------------------------------------------------|------|------|

| Introduction to IBM System/360 Model 40             |      | _    |

| 1. System Configurations                            | <br> |      |

| 2. Functional Parts of a Computer                   | <br> |      |

| 3. Functional Parts of IBM 2040                     | <br> | . 8  |

| Data Formats                                        |      |      |

| 4. Data Formats                                     | <br> | . 11 |

| 5. Powers of Two                                    | <br> | . 12 |

| 6. Packed Decimal Format                            | <br> | . 13 |

| 7. EBCDIC and ASCII Tables                          | <br> | . 14 |

| 8. Extended Card Code                               |      |      |

| 9. Zoned Decimal Format                             |      |      |

| 10. Floating-Point Format                           |      |      |

| System Controls                                     |      |      |

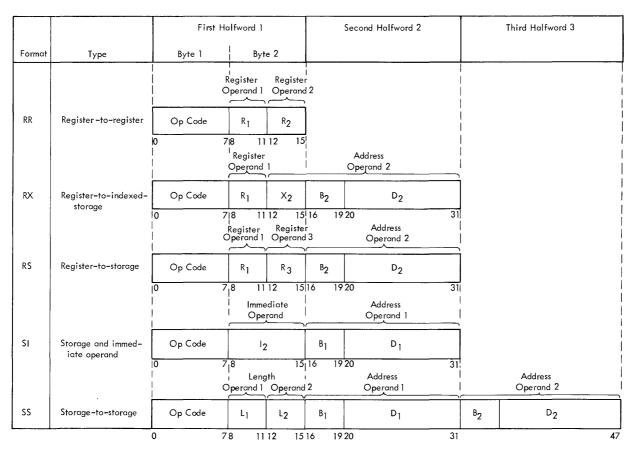

| 11. Five Basic Instruction Formats                  |      | 22   |

| 12. Alphabetic List of Instructions (Sheet 1 of 2)  |      |      |

| 12. Alphabetic List of Instructions (Sheet 2 of 2). |      |      |

| 12. Alphabetic East of Instructions (Sheet 2 of 2). | <br> | . 20 |

| 11. Five Basic Instruction Formats                                                                                                                        |    | 28. Main Storage and 16-Bit Buses Added      29. Read Only Storage Added |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------|----|

| <ol> <li>12. Alphabetic List of Instructions (Sheet 2 of 2)</li> <li>13. Program Status Word Format</li> <li>14. Permanent Storage Assignments</li> </ol> | 29 | Basic System Timing<br>30. Timing Relationships                          | 60 |

# List of Illustrations

| FIGU    | RE TITLE                                  | PAGE     |

|---------|-------------------------------------------|----------|

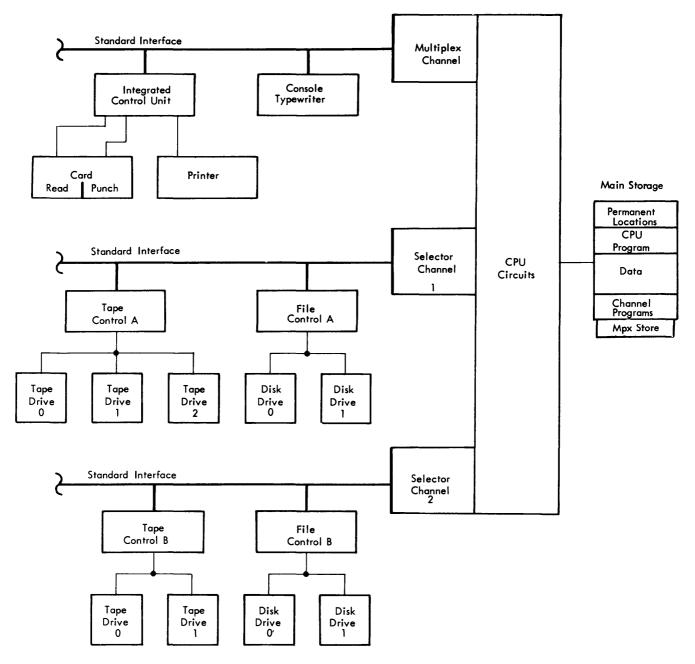

| 15.     | Sample System Configuration               | . 35     |

|         | Channel Command Word Format               |          |

| 17.     | Channel Status Word Format                | . 42     |

| 18.     | Initial System Status                     | . 48     |

|         | Situation After Steps 1 to 6              |          |

| 20.     | Situation After Steps 7 to 10             | . 48     |

|         | Situation After Steps 11 to 13            |          |

| 22.     | Situation After Steps 14 to 16            | . 49     |

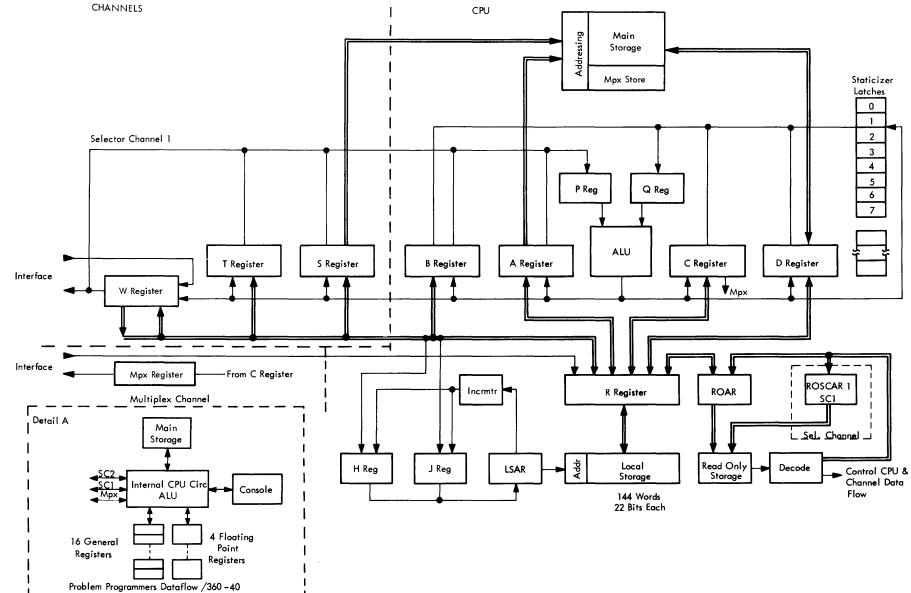

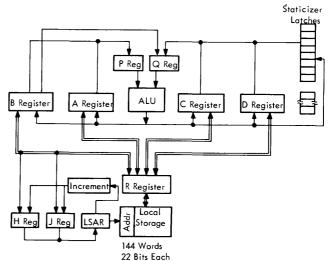

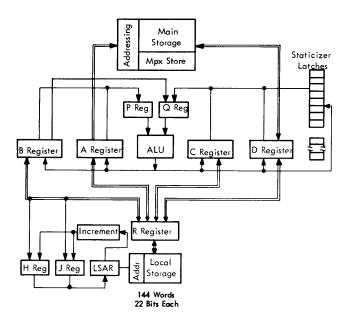

|         | 2040 Simplified Data Flow                 | . 54     |

|         | c Data Paths<br>2040 Simplified Data Flow | 5.       |

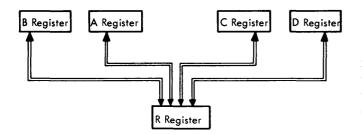

| 24.     | Main Registers and 16-Bit Data Flow       | . 53     |

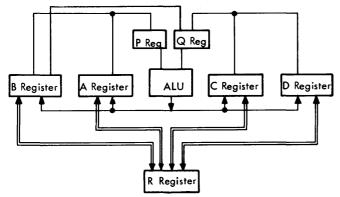

| 25.     | ALU and 8-Bit Data Flow Added             | . 53     |

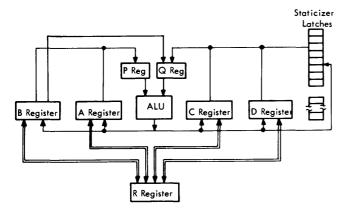

| 26.     | Staticizer Latches Added                  | . 53     |

| 07      | Local Storage Added                       | . 55     |

| 21.     |                                           | <u> </u> |

| 27. 28. | Main Storage and 16-Bit Buses Added       | . 50     |

# **Abbreviations**

| A0      | A Register byte 0                         | LS        | Local Storage     |

|---------|-------------------------------------------|-----------|-------------------|

| Al      | A Register byte 1                         | LSAR      | Local Storage A   |

| AX      | A Register Extension                      | LSD       | Least Significer  |

| ALU     | Arithmetic and Logic Unit                 |           |                   |

| AMWP    |                                           | MAP       | Maintenance A     |

|         | Bits 12-15 of the PSW                     | MC        | Machine Check     |

| A Reg   | A Register                                | MDM       | Maintenance D     |

| ASCII   | American Standard Code for Information    | MI        | Maskable Inter    |

|         | Interchange                               | MS        | Main Storage      |

| В       | Base Register                             | MSC       | Machine Status    |

| BCD     | Binary Coded Decimal                      | MSD       | Most Significan   |

| BCDIC   | Binary Coded Decimal Interchange Code     | MSS       | Manual Single     |

|         |                                           |           | 0                 |

| B Reg   | B Register                                | OS        | Operating Syste   |

| CAS     | Control Automation System                 | Р         | Parity (bit)      |

| CAW     | Channel Address Word                      | PC        | Parity Check      |

| CC      | Chain Command                             | PCI       | Program Contro    |

| CC      | Condition Code                            | PG        | Parity Generati   |

| ČČW     | Channel Command Word                      | PRI       | Program Interr    |

| CDA     | Chain Data Address                        | Prg Chk   | Program Check     |

| CE      |                                           |           |                   |

|         | Channel End                               | PSA       | Protected Stora   |

| CI      | Command Immediate                         | PSW       | Program Status    |

| CLD     | CAS Logic Diagram                         | Pty       | Parity            |

| CLFC    | Condensed Logic Flow Chart                | Rx        | Operand Regist    |

| COBOL   | Common Business Oriented Language         | ROAR      | Read Only Add     |

| CPU     | Central Processing Unit                   | ROBAR     | Read Only Bac     |

| C Reg   | C Register                                | ROS       | Read Only Stor    |

| CSW     | Channel Status Word                       |           |                   |

| CT      |                                           | ROSCAR    | ROS Channel A     |

|         | Count                                     | RR        | Register-to-regi  |

| CU      | Control Unit                              | R Reg     | R Register        |

| CX      | C Register Extension                      | RS        | Register-to-stor  |

| C0      | C Register byte 0                         | rtpt      | reinterpret       |

| C1      | C Register byte 1                         | RX        | Register-to-inde  |

| D       | Displacement Address                      | RX        | R Register Exte   |

| D Reg   |                                           | RO        | R Register byte   |

| Ų       | D Register                                | R1        |                   |

| D0      | D Register byte 0                         |           | R Register byte   |

| D1      | D Register byte 1                         | R/W       | Read/write        |

| DE      | Device End                                | SAB       | Storage Addres    |

| Decr    | Decrement                                 | SAT       | Storage Addres    |

| Del     | Delayed                                   | SC        | Selector Chann    |

| Des     | Destination                               | SI        | Storage-and-im    |

| DM      | Diagnostic Monitor                        | SIO       | Start I/O (Inpu   |

|         | -                                         | SILI      |                   |

| EBCDIC  | Extended Binary Coded Decimal Interchange | SLT       | Suppress Incom    |

|         | Code                                      |           | Solid Logic Tec   |

| EC      | Engineering Change                        | SMS       | Standard Modu     |

| ECAD    | Error Checking Analysis Diagram           | SP        | Storage Protect   |

| FNB     |                                           | SPLS      | Storage Protect   |

|         | Functional Branch                         | S Reg     | S Register        |

| FORTRAN | Formula Translating System                | SS        | Storage-to-stora  |

| FP      | Floating Point                            | SSK       | Set Storage Key   |

| GP      | General Purpose (Registers)               | STATS     | Staticizer Latch  |

|         |                                           | SVC       | Supervisor call   |

| HEX     | Hexaodecimal                              | SX        | S Register Exte   |

| HIO     | Halt I/O (Input/Output)                   | SO        | S Register Exte   |

| I       | Immediate Data (not in text)              |           | S Register byte   |

| IB      | Instruction Buffer                        | S1        | S Register byte   |

|         | Instruction Count                         | TCH       | Test Channel      |

| IC      |                                           | TIC       | Transfer in Cha   |

| ICC     | Interface Control Check                   | TIO       | Test I/O (Inpu    |

| ID      | Inhibit Dump                              | TROS      |                   |

| IDQ     | Invalid Decimal Digit (on Q bus)          | 1105      | Transformer Re    |

| ſF      | Interface                                 | UBA       | Use Bump Add      |

| ILC     | Instruction Length Code                   | UCW       | Unit Control W    |

| I/O     | Input/Output                              | Unobt     | Unobtainable      |

| IOCS    | Input/Output Control System               |           |                   |

| IPL     | Initial Program Load                      | WLR       | Wrong Length      |

| IR      | Interrupt Request                         |           | 0 0               |

| ISA     |                                           | Х         | Index Register    |

|         | Invalid Storage Address                   | YC        | Carry Latch       |

| ISK     | Insert Storage Key                        | YCH 1, 3  | Selector Channe   |

| IZT     | Integrated Zero Test                      | YCI       | Indirect Function |

| L       | Operand Length                            | YCD       | Direct function   |

| LDB     | Load Button                               | μP        | Microprogram      |

|         |                                           | <i>~~</i> |                   |

|         | · · · · · · · · · · · · · · · · · · ·     |           |                   |

ge ge Address Register icent Digit Analysis Procedure eck Diagram Manual terrupt tus Chart ant Digit gle Shot ystem ntrol Interrupt ration errupt  $\mathbf{eck}$ orage Address tus Word gister Address Register Back-up Address Register Storage el Address Register register operations torage operations ndexed-storage operations extensions yte 0 yte 1 ress Bus ress Test nnel -immediate-operand operation nput/Output) correct Length Indicator Technology dular System ect ect Local Storage orage operation Key atches all (op code) xtension yte 0 te 1 Channel nput/Output) Read Only Storage ddress l Word e th Record er nnel Stats 1, 3 ction Carry Stat ion Carry Stat

- Computers process large quantities of information at electronic speeds.

- Computers can process any information in appropriate form.

Modern methods of accounting, management and science generate large quantities of information that must be processed quickly and accurately.

The first steps in automation of office work took place a long time ago, when devices were introduced to relieve the staff from simple but repetitive jobs like writing a date or name (ink stamp). Later the desk calculator and the typewriter were added. Business data were stored and filed on sheets of paper; and many members of the office staff were busy keeping the files up to date.

Early scientists wasted years of their lives with relatively simple but highly repetitive calculations to find or prove laws of nature from the observation data they collected (planetary orbits for example). Calculating devices were among the first machines to handle scientific data.

Introduction of the punched card led to a new stage in information processing. The information itself was now in a form that could be read directly by machines. A great variety of machines were developed to automate various steps in data handling such as sorting, collating, reproducing, accumulating, calculating and printing. Intermediate results had still to be transferred manually from one machine to another and many business decisions and interventions were necessary to obtain the final result.

When electronic discoveries were applied, the speed for the single steps was vastly increased; but, more important, the single operations were interconnected so that transport of data and intermediate results was automated. This new machine, as we know it today, is the modern computer or data processing system.

Computers can process any type of information. The basic unit of information a system can handle may be only one decimal digit or alpha character at a time, but with groups and combinations of these elements any type of information can be described: numbers, values, words, messages, diagrams, photographs, etc.

Today's computers are used not only in the traditional fields of office automation and scientific calculations, but to automate such tasks as:

1. Control of automatic plants

2. Translation from one language to another

3. Medical diagnostics

4. Analysis of photographic equipment from weather satellites and other scientific equipment.

# System/360

Since the early electro-mechanical calculators such as the IBM 602A, the development of IBM computing devices has moved progressively from the use of thermionic tubes to solid-state circuits. Using tube circuits in the IBM 604 and 700 series, IBM progressed to solidstate standard modular system (SMS) circuitry in the 609, 1400 and 7000 series of machines.

The IBM System/360 makes use of IBM's latest technological advance – solid logic technology (SLT). This technology advances solid-state circuitry a stage further by repacking semiconductor circuits in sealed modules. This technique results in lower cost, greater reliability, faster switching speeds, and lower heat dissipation.

In order to achieve the compactness needed for high speeds (electronic transit delays increase with distance to be travelled) a condensed form of logic was needed.' sLT advances this compactness one stage further. A component density increase of about nine to one over SMS has been achieved. In addition, the circuit delays within circuit cards and components have been reduced. Operating at basic levels of 3, 6, and 12 volts, SLT circuits divide into three families of low, medium, and high-speed components having average delay-perstage rating of 700, 30, and 10 nanoseconds, respectively.

The over-all result is a range of processors of greatly reduced size and increased performance. These processors, together with an extremely wide range of equipment, constitute the IBM System/360.

# **The Processor Family**

The IBM System/360 is a family of processors and input/output equipment designed for applications including scientific and commercial data processing, process control, data acquisition, and teleprocessing. Each processor in the range, which covers from the medium-small (similar to the 1440) to the very large (similar to the 7094), can have several sizes of main storage. Storage sizes are indicated by suffixes from C (8K bytes of storage) to I(512K bytes). Typical examples would be 2030D and 2060H, which are a model 30 with 16K bytes and a model 60 with 256K bytes of storage, respectively.

# **Flexibility and Compatibility**

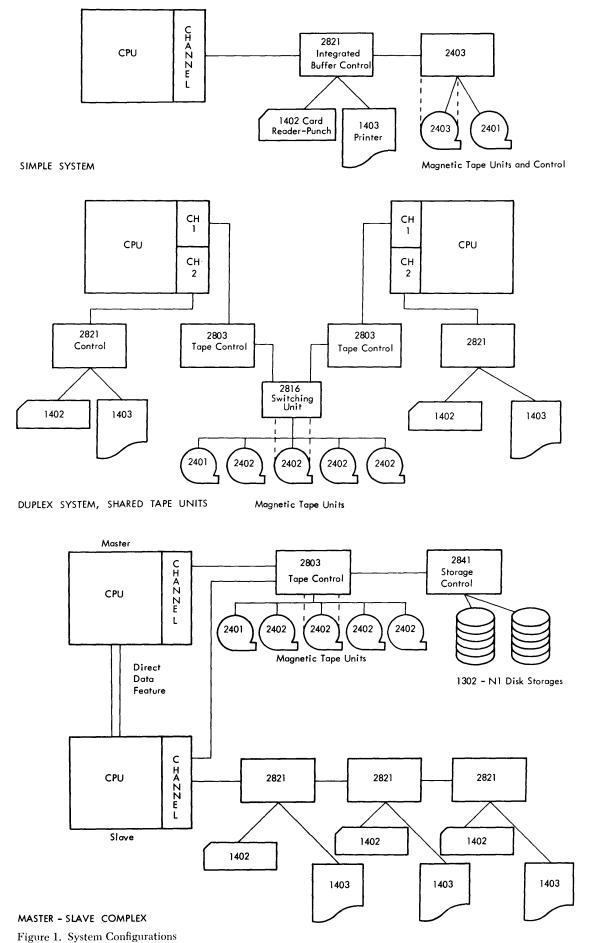

A wide range of input/output equipment is available for attachment to processors in the System/360. This equipment includes high and low-speed card readerpunches; printers; magnetic tape, disc, and drum units; paper-tape readers; inquiry and display terminals; transmission adapters; audio-response units; keyboard consoles; and optical and magnetic readers and printers. Figure 1 illustrates some typical system configurations.

The flexibility in processor and system configuration allows systems to be tailored to the individual user needs. In addition, a wide range of optional features extends the flexibility in system design.

The different models in the System/360 are compatible. This means that the instruction set is common and programs written for one system can run on any other, if the requirements for main storage, features, and input/output are fulfilled. This important factor reduces reprogramming to a minimum and provides for trouble-free system growth.

Most of the available types of System/360 input/ output may be attached to any model in the range. This is made possible by the standard interface, a standard set of control and data lines interconnecting the processor channels and the input/output control units. Thus, many combinations of processors and input/output are possible.

# System/360 Model 40

The Model 40 is a medium-small member of the IBM System/360. In physical size, its processor, the IBM 2040, is comparable with the IBM 1401 Processing Unit. Its computing power is, however, roughly three times that of an IBM 7070 Data Processing System for commercial work, and about twice that of an IBM 709 system for scientific work.

The range of input/output and data communications equipment that may be attached to the Model 40 allows the design of systems covering a wide range of applications and powers. A standard multiplex channel and two optional selector channels further enhance this model's input/output flexibility. Over all, the Model 40 fulfills IBM's objective of providing greater flexibility and increased computing power at reduced cost. The net result of applying these techniques is a compact processor requiring less electrical power, having a smaller heat dissipation, and achieving a reduction in size of approximately nine to one over an equivalent 7070 processor.

## **Computer Functional Units**

Five functional sections: Input Storage Arithmetic and Logical Circuits Control Output

- Data and instructions must be in the language of the system.

- Instructions to be performed must be broken down into steps the system can handle.

- A sequence of instruction steps is called a program.

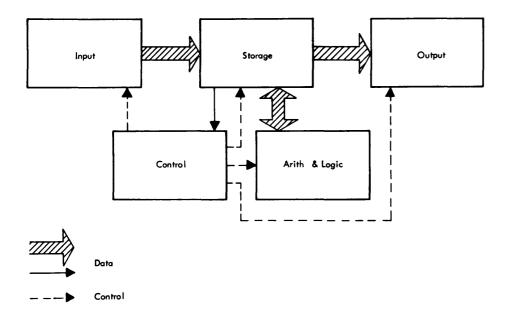

A modern computer (Figure 2) has five distinct functional sections: input, storage, arithmetic and logical circuits, control, and output.

All information to be used by the computer must pass through the input section. The input section interprets information and converts it into a form that the computer can handle. The input section may be one simple device or a big system of input consisting of card readers, magnetic tape units, disk storages, transmission lines, etc.

From the input, the information is directed to the storage section. The main purpose of the storage section is to hold the information necessary to instruct the system in what it has to do, and to serve as an information buffer between input and output sections.

The storage section of a computer consists mostly of a core storage unit with a capacity from a few thouands to many hundreds of thousands of characters, and an access time which is of the same order as the internal processing speed.

The control section directs the operation of the entire system. It receives directions from the storage portion where all instructions for a particular job are stored, prior to processing, in the sequence the machine is expected to execute them.

These instructions obviously must describe the single steps in a code that the control section can recognize and execute. The range of instructions that a computer can execute is relatively small; the instructions themselves are simple. For example, to calculate the square

Figure 2. Functional Parts of a Computer

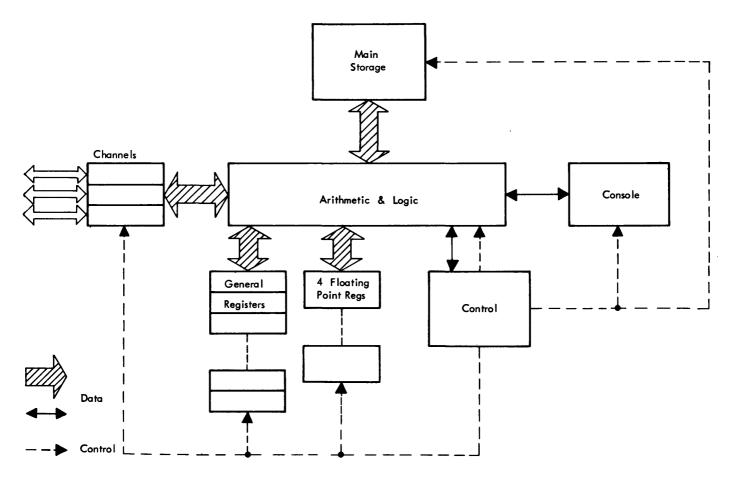

Figure 3. Functional Parts of IBM 2040

8 12-65 Model 40 Comprehensive Introduction

root of a number, the operation has to be broken down into a sequence of additions, multiplications, and divisions. A sequence of these steps is called a program.

The arithmetic and logical unit receives data from storage and performs the operations as directed by the control section. Intermediate or final results are put back into storage and then moved to the output section.

The output can be printed, punched into cards, written on magnetic tape or disks, or it can be directly used to control other systems.

### Functional Units—System/360 Model 40

- Input/output (1/0) units are physically separated from the central computer.

- The central computer is known as the IBM 2040.

- Three channels are provided to control 1/0 operations.

- In addition to main storage, high-speed data registers can store operands and intermediate results.

- A console contains the necessary operating controls.

Compared with the functional units of a general computer concept, as shown in Figure 2, a more specific breakdown is given in Figure 3. 1. The arithmetic and logic circuitry is the center of all information handling.

2. Main storage is connected as before to this circuitry.

3. I/O information does not flow directly to and from main storage, but passes through the common datahandling section and subsequently through the only main storage access path.

4. Up to three channels are provided to communicate with 1/0 devices. Channels can be regarded as independent computers to handle 1/0 operations concurrently with the CPU operations. Once instructed by the CPU they perform all functions necessary to complete an 1/0 operation on their own, selecting and controlling the 1/0 device, and perfroming the data transfer to or from main storage.

5. One channel can communicate with several 1/0 units. See Figure 1.

6. The time for one main storage cycle 2.5  $\mu$ sec (read/write) takes four internal process cycles (625 nanoseconds each); therefore, an intermediate storage for efficient data handling is introduced. 16 general, and 4 floating-point registers are provided.

7. For operator and customer engineer controls and interventions, a console panel provides access to all functional parts of the processor.

æ.

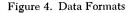

# **Data Formats**

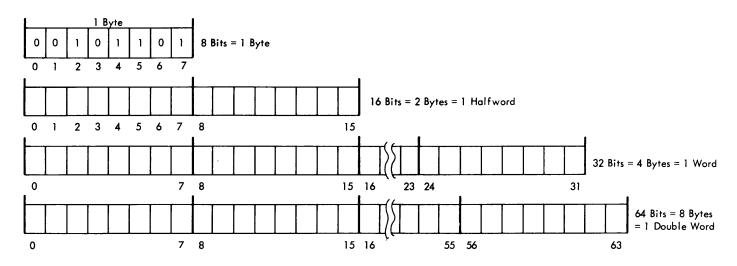

- The basic unit of information within the system is the binary bit.

- 8 bits are grouped together to form one byte.

- The byte is the basic unit of information that can be addressed and processed.

- Information can be either in a fixed-length or variable-length format.

- Fixed-length formats are:

- 1 Byte 2 Bytes = Halfword 4 Bytes = Word

- 8 Bytes = Double word

- Any operand in main storage is specified by the address of its leftmost byte.

- Fixed-length information must be held in main storage at the proper boundaries.

- Each general register (Figure 3) can store one word.

- Each floating-point register (Figure 3) can store one double word.

- Every byte contains a ninth bit for parity checking.

- Correct parity is always an odd bit count.

Common practice in computers is to refer to each of the individual units of information as a binary bit. Throughout the system all components are always in one of two possible states: a line is active or inactive, a latch is on or off, etc. Components that operate in this manner are said to be binary; the active or on state represents a binary 1, the inactive or off state a binary 0.

In order to represent decimal digits, letters, special characters, etc., a combination of several bits has to be used. In System/360, this unit of bit combinations is a group of 8 bits, called one byte. The byte is the basic information block that can be addressed and processed. The byte is also the unit in which the capacity of storage devices is expressed. Bytes may be handled individually or grouped together. A halfword is a group of 2 consecutive bytes. A word is a group of 8 consecutive bytes.

Every general register (Figure 3) can store 4 bytes (word). Every floating-point register can store 8 bytes. (double word).

The location of any field or group of bytes in main storage is specified by the address of its leftmost byte, except during read backward operations when the address specified is that of the rightmost byte.

The length of a field is either implied by the operation to be performed or stated explicitly as part of the instruction. When the length is implied, the information is said to have a fixed length which can be either 1, 2, 4 or 8 bytes.

Fixed-length information held in main storage must be located at the correct address boundaries. The address (leftmost byte) for any fixed-length information must specify one of the addresses that will be obtained if the complete storage, starting with address 0, would be consecutively filled with that information.

Consequently: Bytes can be stored at any address. Halfwords (2 bytes) must be stored at addresses that are multiples of 2. Words (4 bytes) must be stored at addresses that are multiples of 4. Double words (8 bytes) must be stored at addresses that are multiples of 8.

Within any fixed-length format, the bits making up the format are consecutively numbered from left to right, starting with the number 0 (Figure 4).

When the length of a field is stated explicitly, the information is said to have variable length. Variablelength fields can be from 1 to 256 bytes in increments of one byte; no boundaries have to be observed.

Every byte of information contains a ninth bit, the parity or check bit. Over-all parity per byte is always odd and is always checked when the byte is processed.

# **Data Coding**

Information is represented in binary coding. Certain bit configurations can represent other types of coding.

# **Binary Coding**

- The binary system is a place-value number system with the base 2.

- All numbers are expressed with the two symbols 0 and 1.

- Negative numbers are expressed in two's complement form.

- Binary numbers of various lengths are used within the system.

• Instructions translate numbers from the decimal to the binary system and vice versa.

The binary number system is a place-value system, as is the decimal system, differing from it in that its base is the number 2 (Figure 5). There are only two symbols, 0 and 1, with which all numbers are expressed. In the decimal system ten symbols are used: 1, 2, 3, 4, 5, 6, 7, 8, 9, and 0.

## Examples:

- 1. The decimal number 209 actually means:  $(2 \times 10^2) + (0 \times 10^1) + (9 \times 10^0)$ equally, in the binary system, the number 101 means:  $(\underline{1} \times 2^2) + (\underline{0} \times 2^1) + (\underline{1} \times 2^0)$ 5 (decimal)

- 2. The decimal number 6.35 actually means:  $(6 \times 10^{\circ}) + (3 \times 10^{-1}) + (5 \times 10^{-2})$   $(6 \times 10^{\circ}) \times \left(3 \times \frac{1}{10^{1}}\right) + \left(5 \times \frac{1}{10^{2}}\right)$ The binary number 11.01 means:  $(1 \times 2^{1}) + (1 \times 2^{0}) + (0 \times 2^{-1}) + (1 \times 2^{-2})$   $(2) + (1) + (1) + (0) + \left(1 \times \frac{1}{2^{2}}\right)$ 3.25 (decimal)

Negative numbers are expressed in complement form. The complement of any number is obtained by subtracting the number from the highest number in the system and adding a one to this intermediate result.

The complement calculated by this method is known as: the two's complement in the binary system and the ten's complement in the decimal system.

Examples:

subtract 15

add 1

| 1. | Decimal system – a  | number | system | of | four | positions | is |  |

|----|---------------------|--------|--------|----|------|-----------|----|--|

|    | assumed.            |        |        |    |      |           |    |  |

|    | ten's complement of |        |        | 15 |      |           |    |  |

|    | highest number      |        | 999    | 99 |      |           |    |  |

15

9984

9985

The highest digit position is used to indicate the sign: 0 for positive, 9 for negative. Not all possible numbers are valid in this system; the sign position can only be 0 or 9

| Possible numbers in this system ra | ange from:      |

|------------------------------------|-----------------|

| Most negative number               | 9000(-1000)     |

| Least negative number              | 9999(-1)        |

| Zero                               | 0000(0)         |

| Most positive number               | 0999 (999)      |

| 2. Binary system - four-position   | number system.  |

| two's complement of                | 101 (decimal 5) |

| highest number                     | 1111            |

| subtract 101                       | 101             |

|                                    | 1010            |

| add 1                              | 1011            |

The highest digit position is used to indicate the sign: 0 for positive, 1 for negative. All possible numbers in this system are valid.

| Numbers in this system range from: |                   |

|------------------------------------|-------------------|

| Most negative number               | 1000 (decimal –8) |

| Least negative number              | 1111 (decimal -1) |

| Zero                               | 0000              |

| Most positive number               | 0111 (decimal 7)  |

|                                    |                   |

The rule for complementing binary numbers is: invert every bit of the number and add 1.

#### Example: 0111 - invert: 1000 - add 1: 1001 +7 -7

Recomplementing a negative number follows the same rules discussed previously.

| Decimal: | 9985(-15) |

|----------|-----------|

|          | 9999      |

|          | -9985     |

|          | 0014      |

|          | + 1       |

|          | 15        |

|          |           |

| Binary:  | 1011(-5)  |

| Invert:  | 0100      |

|          | + 1       |

|          | 0101      |

|          | . ==      |

Binary numbers are used for all internal purposes; addressing is always binary (main storage, register,

| 2 <sup>n</sup>         | n          | 2 <sup>-n</sup> |     |     |     |     |     |             |     |     |     |     |    |

|------------------------|------------|-----------------|-----|-----|-----|-----|-----|-------------|-----|-----|-----|-----|----|

| 1                      | 0          | 1.0             |     |     |     |     |     |             |     |     |     |     |    |

| $\overline{2}$         | 1          | 0.5             |     |     |     |     |     |             |     |     |     |     |    |

| 4                      | 2          | 0.25            |     |     |     |     |     |             |     |     |     |     |    |

| 8                      | 3          | 0.125           |     |     |     |     |     |             |     |     |     |     |    |

| 16                     | 4          | 0.062           | 5   |     |     |     |     |             |     |     |     |     |    |

| 32                     | 5          | 0.002           |     |     |     |     |     |             |     |     |     |     |    |

| 64<br>64               | 6          | 0.001           |     |     |     |     |     |             |     |     |     |     |    |

| 128                    | 7          | 0.007           |     | 5   |     |     |     |             |     |     |     |     |    |

| 2-0                    | •          | 0.001           | 012 | v   |     |     |     |             |     |     |     |     |    |

| 256                    | 8          | 0.003           | 906 | 25  |     |     |     |             |     |     |     |     |    |

| 512                    | 9          | 0.001           | 953 | 125 |     |     |     |             |     |     |     |     |    |

| 1 024                  | 10         | 0.000           | 976 | 562 | 5   |     |     |             |     |     |     |     |    |

| 2 048                  | 11         | 0.000           | 488 | 281 | 25  |     |     |             |     |     |     |     |    |

| 4 096                  | 12         | 0.000           | 244 | 140 | 625 |     |     |             |     |     |     |     |    |

| 8 192                  | 13         | 0.000           |     |     |     | 5   |     |             |     |     |     |     |    |

| 16 384                 | 14         | 0.000           |     |     |     |     |     |             |     |     |     |     |    |

| 32 768                 | 15         | 0.000           |     |     |     |     |     |             |     |     |     |     |    |

| 52 100                 | 10         | 0.000           | 000 | 517 | 510 | 120 |     |             |     |     |     |     |    |

| 65 536                 | 16         | 0.000           | 015 | 258 | 789 | 062 | 5   |             |     |     |     |     |    |

| 131 072                | 17         | 0.000           | 007 | 629 | 394 | 531 | 25  |             |     |     |     |     |    |

| 262 144                | 18         | 0.000           | 003 | 814 | 697 | 265 | 625 |             |     |     |     |     |    |

| 524 288                | 19         | 0.000           | 001 | 907 | 348 | 632 | 812 | 5           |     |     |     |     |    |

| 1 040 576              | 90         | 0 000           | 000 | 052 | CTA | 210 | 406 | 05          |     |     |     |     |    |

| 1 048 576<br>2 097 152 | 20         | 0.000           |     |     |     |     |     |             |     |     |     |     |    |

| 4 194 304              | 21<br>22   | 0.000           |     |     |     |     |     |             | 5   |     |     |     |    |

| 8 388 608              | 23         | 0.000           |     | -   |     |     | -   |             |     |     |     |     |    |

| 0 000 000              | 20         | 0.000           | 000 | 113 | 209 | 205 | 330 | 101         | 23  |     |     |     |    |

| 16 777 216             | 24         | 0.000           | 000 | 059 | 604 | 644 | 775 | 390         | 625 |     |     |     |    |

| 33 554 432             | <b>2</b> 5 | 0.000           | 000 | 029 | 802 | 322 | 387 | <b>69</b> 5 | 312 | 5   |     |     |    |

| 67 108 864             | 26         | 0.000           | 000 | 014 | 901 | 161 | 193 | 847         | 656 | 25  |     |     |    |

| 134 217 728            | 27         | 0.000           | 000 | 007 | 450 | 580 | 596 | 923         | 828 | 125 |     |     |    |

| <b>26</b> 8 435 456    | 28         | 0.000           | იიი | 003 | 795 | 200 | 208 | 461         | 014 | 062 | 5   |     |    |

| 536 870 912            |            | 0.000           |     |     |     |     |     |             |     |     |     |     |    |

| 1 073 741 824          | 30         | 0.000           |     |     |     |     |     |             |     |     |     |     |    |

| <b>2</b> 147 483 648   | 31         | 0.000           |     |     |     |     |     |             |     |     |     |     |    |

| 8 TI 101 010           |            | 0.000           | 500 |     | 100 |     |     | 001         |     |     | 010 | •   |    |

| 4 294 967 296          |            | 0.000           |     |     |     |     |     |             |     |     |     |     |    |

| 8 589 934 592          | 33         | 0.000           |     |     |     |     |     |             |     |     |     |     |    |

| 17 179 869 184         | 34         | 0.000           |     |     |     |     |     |             |     |     |     |     |    |

| <b>34 359</b> 738 368  | 35         | 0.000           | 000 | 000 | 029 | 103 | 830 | 456         | 733 | 703 | 613 | 281 | 25 |

Figure 5. Powers of Two

I/O devices). With the basic instruction set only binary arithmetic is provided. Binary numbers within the system can have varying sizes:

Registers are addressed with 4-bit numbers – decimal 0 to 15.

Operation codes are eight-bit numbers – decimal 0 to 255.

Ms addresses are 24-bit numbers – decimal 0 to 16,777,215.

Halfword arithmetic uses 16-bit numbers – decimal -32,768 to +32,767.

General registers store fullword numbers – decimal -2,147,483,648 to +2,147,483,647.

Although binary numbers, in general, have more positions than their decimal counterparts (about 3.3 times as many), they are the most suitable numbers to be represented by binary devices (switches, latches, etc.).

Machine instructions are provided to translate decimal numbers into binary and vice versa. Assembly programs translate decimal values of the programmer to binary for internal use.

#### **Hexadecimal Coding**

- Hexadecimal is a place-value system with the base 16.

- Hexadecimal numbers are expressed with 16 different symbols.

- The hexadecimal number system is used in floatingpoint arithmetic.

- One hexadecimal digit represents four binary bits.

- Hexadecimal is a convenient shorthand for writing binary numbers.

Hexadecimal, usually abbreviated to "hex," is a placevalue number system with the base 16.

To express any number, 16 different symbols are necessary.

The symbols used by IBM are:

```

Decimal: 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

Hex: 0 1 2 3 4 5 6 7 8 9 A B C D E F

Example: The hex number 1C7 actually means:

(1 \times 16^2) + (C \times 16^1) + (7 \times 16^0)

```

```

(1 \times 256) + (12 \times 16) + (7 \times 1)

455 (decimal)

```

455 (decimal

The hexadecimal number system is used in floatingpoint arithmetic. Every hex digit represents a four-bit binary number.

| HEX | BINARY |

|-----|--------|

| 0   | 0000   |

| 1   | 0001   |

| 2   | 0010   |

| 3   | 0011   |

| 4   | 0100   |

| BINARY |

|--------|

| 0101   |

| 0110   |

| 0111   |

| 1000   |

| 1001   |

| 1010   |

| 1011   |

| 1100   |

| 1101   |

| 1110   |

| 1111   |

|        |

H

This property of hex digits provides a very useful and simple shorthand for writing large binary numbers. Examples:

| 1. A halfword | contains the | e value: |      |      |

|---------------|--------------|----------|------|------|

| Binary        | 0110         | 1110     | 0101 | 1010 |

| Hex           | 6            | Ε        | 5    | Α    |

2. The operation code D2 is actually stored as: 1101 0010

# **Decimal Coding**

- Two decimal numbers are packed into one byte (packed decimal format).

- Every decimal digit is represented by 4 bits.

- Only the combinations for the values 0 to 9 are valid.

- Packed decimal fields are variable in length.

- In a packed decimal field, the lowest-order 4 bits contain a sign code.

Decimal numbers are coded with four-bit binary numbers, two decimal digits per byte. This format is referred to as packed decimal (Figure 6).

| B     | Byte Byte |       |         | В | yte     | Byte  |         |  |  |

|-------|-----------|-------|---------|---|---------|-------|---------|--|--|

| Digit | Digit     | Digit | Digit   |   | Digit   | Digit | Sign    |  |  |

| 1000  | 0 1 0 1   | 1001  | 0 0 0 0 |   | 0 1 0 0 | 0011  | 1 1 0 1 |  |  |

| 8     | 5         | 9     | 0       |   | 4       | 3     | -       |  |  |

Figure 6. Packed Decimal Format

Only the binary numbers 0000 to 1001 (0-9 decimal) are valid digit codes.

Codes 1010 to 1111 are used to represent the sign. Interpretation is as follows:

| 1010 = +ASCII   | American Standard Code      |

|-----------------|-----------------------------|

| 1011 = -ASCII   | for Information Interchange |

| 1100 = + EBCDIC | Extended Binary Coded       |

| 1101 = -EBCDIC  | Decimal Interchange Code    |

| 1110 = +)       |                             |

| 1111 = +  (any  | v code)                     |

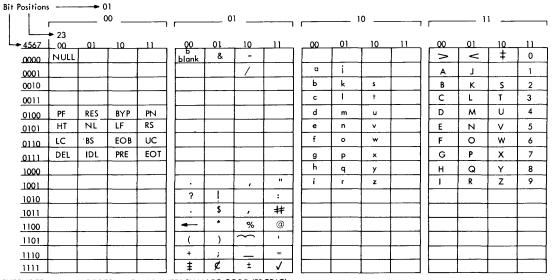

The sign code generated in decimal arithmetic depends on the character set (ASCII or EBCDIC) and is under program control (Figure 7).

Decimal numbers are treated as signed integers with a variable field-length format from 1 to 16 bytes long. Negative numbers are carried in true form. The sign is stored in the 4 least-significant bits.

# Data Codes for Input/Output

- 1/0 information is handled in units of one byte.

- Character-sensitive units use codes with one character per byte.

- Two character sets are standard, EBCDIC and ASCII.

- An extended card code provides punching of any character in one card column.

- Decimal numbers are coded in zoned decimal.

- The least-significant character includes the sign.

- Instructions are provided to convert zoned decimal into packed decimal and vice versa.

EXTENDED BINARY-CODED-DECIMAL INTERCHANGE CODE (EBCDIC)

| EBCDIC | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|--------|---|---|---|---|---|---|---|---|

| ASCII  | 7 | 6 | × | 5 | 4 | 3 | 2 | 1 |

BIT NUMBERING

| Bit Positions |      |                 | 5  |                |     |    |       |     |    |    |           |              |    |    |    |          |

|---------------|------|-----------------|----|----------------|-----|----|-------|-----|----|----|-----------|--------------|----|----|----|----------|

|               |      | 0               | )  | <br>. <b>.</b> | (   | 01 |       | ı — |    |    | 10        |              | ·  |    | 11 | 1        |

|               | ₩ X5 |                 |    |                |     |    |       |     |    |    |           |              | •  |    |    |          |

| ► <u>4321</u> | 00   | 01              | 10 |                | 01_ | 10 | _ 11_ | ۱   | 00 | 01 | <u>10</u> | <u> </u>     | 00 | 01 | 10 | <u> </u> |

| _0000         | NULL | DC <sub>0</sub> |    | blank          | 0   |    | ļ     |     |    |    | @         | P            |    |    |    | р        |

| _0001         | SOM  |                 |    | !              | 1   |    |       |     |    |    | A         | Q            |    |    | a  | ٩        |

| _0010         | EOA  | DC2             |    | н              | 2   |    |       |     |    |    | В         | R            |    |    | Ь  | r        |

| 0011          | EOM  |                 |    | #              | 3   |    |       | 1   |    |    | С         | S            |    | 1  | с  | s        |

| 0100          | EOT  | DC4<br>Stop     | ·  | \$             | 4   |    |       |     |    |    | D         | Т            |    |    | d  | t        |

| 0101          | WRU  | ERR             |    | <br>%          | 5   |    |       |     |    |    | E         | U            |    |    | e  | U        |

| 0110          | RU_  | SYNC            |    | &              | 6   |    |       |     |    |    | F         | V            |    |    | f  | v        |

| 0111          | BELL | LEM             |    | '              | 7   |    |       |     |    |    | G         | w            |    |    | g  | w        |

| 1000          | BKSP | S <sub>0</sub>  |    | (              | 8   |    |       |     |    |    | н         | Х            |    |    | h  | ×        |

| 1001          | нт   | S <sub>1</sub>  |    | )              | 9   |    |       |     |    |    | 1         | Y            |    |    | i  | У        |

| 1010          | LF   | <sup>5</sup> 2  |    | *              | :   |    |       |     |    |    | J         | Z            |    |    | i  | z        |

| 1011          | VT   | 53              |    | +              | ;   |    |       |     |    |    | к         | C            |    |    | k  |          |

| 1100          | FF   | S <sub>4</sub>  |    | ,              | <   |    |       |     |    |    | L         | $\mathbf{i}$ |    |    | 1  |          |

| 1101          | CR   | \$ <sub>5</sub> |    | -              | =   |    |       |     |    |    | м         | ]            |    |    | m  |          |

| 1110          | so   | <sup>S</sup> 6  |    |                | >   |    |       |     |    |    | N         | 1            |    |    | n  | ESC      |

| 1111          | SI   | \$ <sub>7</sub> |    | /              | ?   |    |       |     |    |    | 0         | -            |    |    | 0  | DEL      |

AMERICAN STANDARD CODE FOR INFORMATION INTERCHANGE (ASCII)

# Figure 7. EBCDIC and ASCII Tables

14 12-65 Model 40 Comprehensive Introduction

# • Any coding can be used on character-sensitive 1/0 units, since a translate instruction is provided which converts from any code into any other.

All information transfers to and from 1/0 devices are in units of one byte. Character-sensitive 1/0 units (printers, typewriters, card readers and punches) utilize a code in which one character (card column) is represented by one byte. The total number of characters possible is 256. Two standard sets for character coding are used: EBCDIC – Extended Binary Coded Decimal Interchange Code and ASCII – American Standard Code for Information Interchange (Figure 7). Bit numbering is different for the two codes. Corresponding bits are:

EBCDIC: 0 1 2 3 4 5 6 7 (the standard bit numbering within one byte)

ASCII: 7 6 X 5 4 3 2 1

Bits 0-3 are referred to as zone bits, (ASCII: 7-5)

Bits 4-7 are referred to as digit bits, (ASCII: 4-1)

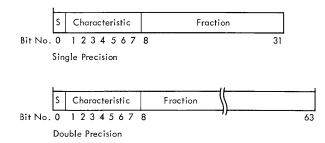

An extended card code provides punching of any byte value into one column (Figure 8).

| t Positions | <b></b>        | 0<br>0    |           | )          | ſ      |    | 0        | ı        | 1         | r        | 10       | o        |           | ו | <b></b>   |           | 11        |           |

|-------------|----------------|-----------|-----------|------------|--------|----|----------|----------|-----------|----------|----------|----------|-----------|---|-----------|-----------|-----------|-----------|

| ▲ 4567      | 23             | 01        | 10        | 11         | C      | 00 | 01       | 10       | 11        | 00       | 01       | 10       | 11        |   | 00        | 01        | 10        | 11        |

| 0000        | T09<br>18      | TE9<br>18 | E09<br>18 | TE09<br>18 |        |    | T        | E        | TEO       | T0<br>18 | TE<br>18 | E0<br>18 | TE0<br>18 |   | то        | EO        | 0<br>28   | 0         |

| 0001        | Т9<br>1        | E9<br>1   | 09<br>1   | 9<br>1     | T<br>1 | 09 | TE9<br>1 | 0        | TE09<br>1 | Т0<br>1  | TE       | E0<br>1  | TEO       |   | T<br>1    | E<br>1    | E09<br>1  | 1         |

| 0010        | T9<br>2        | E9<br>2   | 09<br>2   | 9<br>2     | T<br>2 | 09 | TE9<br>2 | E09<br>2 | TE09<br>2 | T0<br>2  | TE<br>2  | E0<br>2  | TE0<br>2  |   | T<br>2    | E<br>2    | 0<br>2    | 2         |

| 0011        | Т9<br>3        | E9<br>3   | 09<br>3   | 9<br>3     | Т<br>3 | 09 | TE9<br>3 | E09<br>3 | TE09<br>3 | T0<br>3  | TE<br>3  | E0<br>3  | TEO<br>3  |   | Т<br>3    | E<br>3    | 0<br>3    | 3         |

| 0100        | Т9<br>4        | E9<br>4   | 09<br>4   | 9<br>4     | T<br>4 | 09 | TE9<br>4 | E09<br>4 | TE09<br>4 | T0<br>4  | TE<br>4  | E0<br>4  | TEO<br>4  | ] | T<br>4    | E<br>4    | 0<br>4    | 4         |

| 0101        | Т9<br>5        | E9<br>5   | 09<br>5   | 9<br>5     | Т<br>5 | 09 | TE9<br>5 | E09<br>5 | TE09<br>5 | Т0<br>5  | TE<br>5  | E0<br>5  | TEO<br>5  |   | Т<br>5    | E<br>5    | 0<br>5    | 5         |

| 0110        | Т9<br>6        | E9<br>6   | 09<br>6   | 9<br>6     | T<br>6 | 09 | TE9<br>6 | E09<br>6 | TE09<br>6 | T0<br>6  | TE<br>6  | E0<br>6  | TE0<br>6  |   | Т<br>6    | E<br>6    | 0<br>6    | 6         |

| 0111        | <b>T9</b><br>7 | E9<br>7   | 09<br>7   | 9<br>7     | T<br>7 | 09 | TE9<br>7 | E09<br>7 | TE09<br>7 | T0<br>7  | TE<br>7  | E0<br>7  | TEO<br>7  |   | T<br>7    | E<br>7    | 0<br>7    | 7         |

| 1000        | T9<br>8        | E9<br>8   | 09<br>8   | 9<br>8     | Т<br>8 | 09 | TE9<br>8 | E09<br>8 | TE09<br>8 | Т0<br>8  | TE<br>8  | E0<br>8  | TEO<br>8  |   | Т<br>8    | E<br>8    | 0<br>8    | 8         |

| 1001        | T9<br>18       | E9<br>18  | 09<br>18  | 9<br>18    | T<br>1 | ,  | E<br>18  | 0<br>18  | 18        | то<br>9  | TE<br>9  | E0<br>9  | TEO<br>9  |   | Т<br>9    | E<br>9    | 0<br>9    | 9         |

| 1010        | T9<br>28       | E9<br>28  | 09<br>28  | 9<br>28    | T<br>2 | 1  | E<br>28  | TE       | 28        | T0<br>28 | TE<br>28 | E0<br>28 | TE0<br>28 |   | T09<br>28 | TE9<br>28 | E09<br>28 | TE0<br>28 |

| 1011        | T9<br>38       | E9<br>38  | 09<br>38  | 9<br>38    | Т<br>3 |    | E<br>38  | 0<br>38  | 38        | T0<br>38 | TE<br>38 | E0<br>38 | TE0<br>38 |   | T09<br>38 | TE9<br>38 | E09<br>38 | TEC<br>38 |

| 1100        | T9<br>48       | E9<br>48  | 09<br>48  | 9<br>48    | Т<br>4 |    | E<br>48  | 0<br>48  | 48        | T0<br>48 | TE<br>48 | E0<br>48 | TE0<br>48 |   | T09<br>48 | TE9<br>48 | E09<br>48 | TE0<br>48 |

| 1101        | T9<br>58       | E9<br>58  | 09<br>58  | 9<br>58    | Т<br>5 | 8  | E<br>58  | 0<br>58  | 58        | T0<br>58 | TE<br>58 | E0<br>58 | TE0<br>58 |   | T09<br>58 | TE9<br>58 | E09<br>58 | TEC<br>58 |

| 1110        | Т9<br>68       | E9<br>68  | 09<br>68  | 9<br>68    | Т<br>6 | 8  | E<br>68  | 0<br>68  | 68        | T0<br>68 | TE<br>68 | E0<br>68 | TE0<br>68 |   | T09<br>68 | TE9<br>68 | E09<br>68 | TEC<br>68 |

| 1111        | T9<br>78       | E9<br>78  | 09<br>78  | 9<br>78    | T      | 8  | E<br>78  | 0<br>78  | 78        | T0<br>78 | TE<br>78 | E0<br>78 | TE0<br>78 |   | T09<br>78 | TE9<br>78 | E09<br>78 | TEC<br>78 |

T = 12 Punch

E = 11 Punch

0 = Zero Punch

Figure 8. Extended Card Code

Decimal numbers coded in either EBCDIC or ASCII are referred to as zoned decimal format. Zoned decimal numbers are treated as signed integers with a variable field length. The sign is carried in the zone bits of the least-significant digit (Figure 9).

|        | Byte = 0 | Character | Byte = C | Character |    | Ву | te = 0 | haracter |

|--------|----------|-----------|----------|-----------|----|----|--------|----------|

|        | Zone     | Digit     | Zone     | Digit     |    | Si | gn     | Digit    |

| EBCD   | 1111     | 0100      | 1111     | 0 1 1 1   | ., | 11 | 01     | 0011     |

| ASCII  | 0 1 0 1  | 0 1 0 0   | 0 1 0 1  | 0 1 1 1   |    | 10 | 11     | 0011     |

|        | 4        | ţ         | 7        | 7         |    |    | l      | EBCD     |

|        |          |           |          |           |    |    | 9      | S ASCII  |

| Meanir | ng 4     | 1         | 7        | 7         |    |    | 3      | , -      |

Figure 9. Zoned Decimal Format

The zoned decimal format cannot be used for arithmetic operations. Instructions are provided for packing or unpacking decimal numbers so that they may be translated from the zoned to the packed format (which provides decimal arithmetic) and vice versa. Interpretation and generation of zone bits depends on the character set preferred and is program controlled (bit 12 of the psw).

I/o units that are not character-sensitive (magnetic tape units, disk files, etc.) can handle any coding format. On these devices, the information is stored in 8-bit bytes as in the CPU.

*Examples:* Magnetic tape units use a nine-track R/w head (8 bits plus parity), recording one byte in parallel. On disk files, the bits within the byte are recorded in series but there is no code change.

Any other character codes of character-sensitive I/O devices can be handled by means of a translate instruction. With this instruction, it is possible to convert variable-length fields from any code into any other.

# **Other Data Codes**

- Any information that is not in a format used for arithmetic operations is called logical information.

- Logical information can be in any code.

- Instructions are provided to handle logical information.

Information that is not in a format that can be handled with the normal arithmetic operations (binary fixedpoint or floating-point and packed decimal) is referred to as logical information.

Character-sensitive 1/0 codes or any other coding format are logical information. For the system, logical information is binary data without any special format. A full set of instructions is provided for handling logical information. Included are logical arithmetic instructions which do not recognize any special sign bits.

# **Binary Fixed-Point Arithmetic**

- Operands are signed binary integers, recorded in halfwords or words.

- Negative numbers are always in two's complement form.

- Operands are held in general registers or in main storage.

- Fixed-point arithmetic uses the add-to-accumulator principle.

- Halfword numbers loaded into general registers are expanded to a full word.

A fixed-point number is a signed value, recorded as a binary integer. It is called fixed-point, because the programmer determines the fixed position of the binary point.

Fixed-point numbers may be recorded in halfword (16 bit) or fullword (32 bit) length. In both lengths, the first bit position (bit 0) holds the sign of the number.

Negative numbers are always carried in two's complement form.

Fixed-point operands are held in general registers or in main storage. Results of arithmetic operations are always developed in general registers. For binary arithmetic the general registers can be assumed to be accumulators. This type of operation is known as addto-accumulator.

Halfword numbers loaded into general registers are expanded to a full word. The sign is propagated throughout the high-order 16 bit positions.

# **Add and Subtract**

- Rules for addition:

- 1. Zero plus zero equals zero.

- 2. Zero plus one equals one.

3. One plus one equals zero with a carry to the next higher order bit position.

- For subtract, the two's complement of the second operand is added.

- Carrys out of bit 0 are lost.

- Overflow has occurred if the carrys out of bit 0 and bit 1 are not equal.

Examples with eight-bit numbers (range from +127 to -128) follow.

|                    |   | COMMENTS                                                                                                                      |

|--------------------|---|-------------------------------------------------------------------------------------------------------------------------------|

| Bit number         |   | 0 1 2 3 4 5 6 7 Sign in position zero; significant digits in positions 1-7                                                    |

| + 22               | - | $0 \ 0 \ 0 \ 1 \ 0 \ 1 \ 0$                                                                                                   |

| +(+92)             | = | 0 1 0 1 1 1 0 0                                                                                                               |

| <u> </u>           |   | $0 \ \overline{0} \ 0 \ 1 \ 1 \ 1 \ 0 \ 0 - $ carrys                                                                          |

| +114               | = | $\overline{0\ 1\ 1\ 1\ 0\ 0\ 1\ 0}$ No overflow, carrys out of bit 0 and bit 1 are equal (both 0)                             |

| +114               | = |                                                                                                                               |

| -(+92)             | = | 1 0 1 0 0 1 0 0 two's complement of +92                                                                                       |

| <u>/</u>           |   | 1 1 0 0 0 0 - carrys                                                                                                          |

| + 22<br>- 22       | = | $\overline{0\ 0\ 0\ 1\ 0\ 1\ 1\ 0}$ No overflow, carrys out of bit 0 and bit 1 are equal (both 1, carry out of bit 0 is lost) |

| - 22               | = |                                                                                                                               |

| +(-92)             | = |                                                                                                                               |

|                    |   | $1 \overline{1 1 0 0 0 0 - carrys}$                                                                                           |

| -114               | = | 1 0 0 0 1 1 1 0 No overflow, carrys out of bit 0 and bit 1 are equal (both 1, carry out of bit 0 is lost)                     |

| $\frac{-114}{-22}$ | = |                                                                                                                               |

| -(-92)             | = | $0 \ 1 \ 0 \ 1 \ 1 \ 1 \ 0 \ 0$ two's complement of $-92 \ (=+92)$                                                            |

| ( 0-)              |   | $\frac{3}{1} \frac{1}{1} \frac{1}{1} \frac{1}{1} \frac{1}{1} \frac{1}{0} \frac{0}{0} \frac{0}{0} - \text{carrys}$             |

| + 70               | _ | 1 + 1 + 1 + 0 = 0 carry out of bit 0 and bit 1 are equal (both 1, carry out of bit 0 is lost)                                 |

| + 70               | = |                                                                                                                               |

| +114               | = | 0 1 1 1 0 0 1 0 Sign change                                                                                                   |

| +(+22)             | = | $\frac{0\ 0\ 0\ 1\ 0\ 1\ 1\ 0}{1\ 1\ 0}$                                                                                      |

|                    |   | 0 1 1 1 0 1 1 0 - carrys                                                                                                      |

| +136               | ¥ | 1 0 0 0 1 0 0 0 overflow, carrys out of bit 0 and bit 1 are unequal, result is not correct.                                   |

| -114               | = |                                                                                                                               |

| -(+22)             | = | 1 1 1 0 1 0 1 0 two's complement of $+22$                                                                                     |

|                    |   | $1 \overline{0 0 0 1 1 1 0} - carrys$                                                                                         |

| -136               | ≠ | 0 1 1 1 1 0 0 0 overflow, carrys out of bit 0 and bit 1 are unequal, result is not correct.                                   |

|                    |   |                                                                                                                               |

# **Multiply**

Multiplications of two fullword numbers results in a double word held in two consecutive general registers. The sign of the product is determined by the rules of algebra.

# Divide

The dividend is a double word number held in two consecutive general registers. The divisor is a fullword number; the resulting quotient is a fullword number. The sign of the quotient is determined by the rules of algebra; the remainder has the sign of the dividend.

# **Floating-Point Arithmetic**

- Needed for large numbers used in scientific fields.

- A floating-point number is expressed as a fraction multiplied by a power of 10.

- A floating-point number is normalized if the decimal point of the fraction is immediately to the left of the highest-order significant digit.

- Rules for Add and Subtract:

- 1. The number with the smaller exponent is shifted to the right until the exponents are equal.

- 2. The fractions are added (or subtracted); the exponent remains unchanged.

- 3. If necessary, the result is normalized.

- Rules for Multiply:

- 1. The fractions are multiplied.

- 2. The exponents are added.

- 3. If necessary, the result is normalized.

- Rules for Divide:

- 1. The fractions are divided.

- 2. The divisor exponent is subtracted from the dividend exponent.

- 3. If necessary the result is normalized.

Very large and very small numbers are often encountered in scientific calculations. The electron, for example, has a charge of 0.00000000048cgs (centimeter gram seconds): one light year (the distance that light travels in one year) is about 6,000,000,000,000 miles. It is conceivable that such numbers may be 50 digits in length.

The problem, when a computer is used to process such numbers unaltered, is that fixed-point registers should have 100 decimal digit positions (more than 300 bits) to allow for calculations involving large and small numbers. Such a computer would be expensive to build and its calculating speed would be slow. It should also be observed that most register positions would contain only zeros (spacer zeros) to define the magnitude of a few significant digits.

It is possible, however, to handle these numbers with the register size normally available. The programmer would have to process the significant digits, and, in a separate sequence, would have to establish the position of the decimal point which often (at the time of programming) is not easily predictable.

Thus, the need for a shorthand notation and a simplified arithmetic (floating-point) becomes apparent for those areas where the magnitude of numbers covers a wide range.

The key to floating-point data representation is the separation of the significant digits of a number from the size (magnitude) of the number. Thus, the number is expressed as a fraction multiplied by a power of 10.

# **Exponential Numbers**

1. In the decimal system, 0.0000000048 actually means:

$(0 \times 10^{\circ}) + (0 \times 10^{-1}) + \ldots + (4 \times 10^{-10}) + (8 \times 10^{-11})$

All terms except the last two are zero; the number can be written as:

$(4 \times 10^{-10}) + (8 \times 10^{-11})$

In order to simplify this expression, the second term is transformed into a number with the same power-of-ten factor as in the first.

$(4 \times 10^{-10})$  (.8 × 10<sup>-10</sup>)

$(4.8) \times 10^{-10}$  $4.8 \times 10^{-10}$

$.48 \times 10^{-9}$  (normalized)

2. In the decimal system, 6,000,000,000 actually means:

$(6 \times 10^{12}) + (0 \times 10^{11}) + \ldots + (0 \times 10^{0})$  $6 \times 10^{12}$  $.6 \times 10^{13}$

Whenever the decimal point is moved one position to the left, the power-of-ten (exponent) is increased by one.

Whenever the decimal point is moved one position to the right the exponent is decreased by one.

A floating-point number is normalized, if, in the fraction, no spacer zeros are carried. The decimal point is immediately to the left of the highest-order significant digit.

# **Rules for Add and Subtract**

- 1. The number with the smaller exponent is shifted to the right until the exponents are equal.

- 2. The fractions are added (or subtracted), the exponent remains unchanged.

- 3. If necessary the result is normalized.

Example:

$$21,700,000 + 800 = (.217 \times 10^8) + (.8 \times 10^3)$$

$= .217 \times 10^8$

$+ .000008 \times 10^8$

Shift right until exponents are equal.

#### **Rules for Multiply**

- 1. The fractions are multiplied.

- 18 12-65 Model 40 Comprehensive Introduction

- 2. The exponents are added.

- 3. If necessary the result is normalized. *Example:* 2500 × 0.000000033 =  $(.25 \times 10^{4}) \times (.33 \times 10^{-7})$ Multiply fractions:  $.25 \times .33 = .0825$ Add exponents: (+4) + (-7) = -3Result:  $.0825 \times 10^{-3}$ Normalized:  $.825 \times 10^{-4}$

# **Rules for Divide**

- 1. The fractions are divided.

- 2. The divisor exponent is subtracted from the dividend exponent.

- 3. If necessary the result is normalized.

Example:

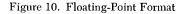

#### **Floating-Point Notation**

#### Format

- Floating-point numbers are recorded in the hexadecimal number system.

- The significant digits are recorded as hexadecimal fractions.

- The exponent (called the characteristic) is a sevenbit binary number to which the base 16 is raised.

- The characteristic can be a number from 0 to 127.

- Floating-point numbers are recorded in a fixedlength format: short precision in single words double precision in double words

- Bit 0 in either format denotes the sign of the fraction.

- Negative fractions are always carried in true form.

Floating-point numbers are recorded in the hexadecimal number system.

*Example:* The hexadecimal number 1C.A actually means:

$(1 \times 16^{1}) + (C \times 16^{0}) + (A \times 16^{-1})$

To express this number in the floating-point format, the exponents have to be equal and the significant digits are expressed as a fraction:

$(.1 \times 16^2) + (.0C \times 16^2) + (.00A \times 16^2)$ .1CA × 16<sup>2</sup>

In order to store such a number in the machine, two values have to be recorded:

- 1. The fraction (.1CA).

- 2. The power to which 16 has to be raised (+2).

The base is always 16; as this fact is implicit in the operations the number is not recorded.

The general format in which the two numbers are stored is a fixed-length format of either a single or a double word:

| Sign bit    | Seven-bit      | 24- or 56-bit |

|-------------|----------------|---------------|

| of fraction | characteristic | fraction      |

|             | _              |               |

Since each of the two numbers is signed, some method must be employed to express two signs. This is accomplished by making the fraction sign use the sign associated with the word (or double word) and expressing the exponent in excess -64 arithmetic. The signed number of the exponent is always increased by 64.

The exponent is expressed as a seven-bit binary number, giving a range for the exponent from 0 to 127. With excess -64 arithmetic, valid exponents are from -64 to +63. As this number is no longer a true exponent, it is referred to in common practice as a characteristic.

| Examples:      |         |            |              |

|----------------|---------|------------|--------------|

| Characteristic | 0000000 | stands for | $16^{-64}$   |

| Characteristic | 0111111 | stands for | 16-1         |

| Characteristic | 1000000 | stands for | $16^{\circ}$ |

| Characteristic | 1000001 | stands for | 16+1         |

| Characteristic | 1111111 | stands for | $16^{+63}$   |

The range of decimal numbers which can be expressed in floating-point notation is therefore  $16^{-64}$  to  $16^{+63}$ which is approximately  $10^{-78}$  to  $10^{+75}$ . The first is a very small number with 78 spacer zeros after the decimal point; the second is a very big number with 75 digits. This is the absolute value of the number, since the number itself can be positive or negative (indicated by the sign bit in position 0; zero indicates positive fraction, 1 indicates negative).

The fraction is always carried in true form (not complement). The two available formats (Figure 10) for floating-point numbers are called:

1. Single precision - the number is recorded in a single word, also referred to as short format.

2. Double precision - the number is recorded in a double word, also referred to as long format.

# Precision

The precision of any value can be expressed by the number of significant digits it contains.

The statement that the distance covered by light in one year is  $.6 \times 10^{13}$  miles is not very precise (only one significant digit). Exact measurements could possibly give this figure as  $.56322 \times 10^{13}$  miles or  $.6209 \times 10^{13}$  miles, or even a number with more significant digits.

The number of significant digits a computer can handle defines its precision.

*Example:* The ordinary slide rule can be regarded as a calculating device operating in a floating-point format. The significant digits are handled with the device; the exponents, however, have to be calculated by the user.

A 10-inch slide rule has an average precision of about 3 significant digits. This means that operands cannot have more than 3 significant digits and the results obtained are accurate only to about 3 significant digits:

.176 times .294 calculated with a slide rule is about .517  $\times$  10<sup>-1</sup>. The accurate result would be .51744  $\times$  10<sup>-1</sup>.

The floating-point format has a precision of either 24 or 56 binary bits (the bits available to store the fraction in either short or long form). These precisions are equal to 7 or 16 decimal significant digits, respectively.

The precision of short floating-point arithmetic can be compared with the precision of a hypothetical slide rule with a length of about 4 yards. Long floatingpoint arithmetic would require a slide rule with a length of about 2600 yards.

Conversion Example: To convert -149.375 into a short floating-point number:

1. Convert to hexadecimal; easiest way of doing this is by first converting to binary (use Figure 7).

|                                                      | 27 2° 25 24     | $2^{3} 2^{2} 2^{1} 2^{0} 2^{-1}$ | 2-2 2-3 2-4 |  |  |  |  |  |  |

|------------------------------------------------------|-----------------|----------------------------------|-------------|--|--|--|--|--|--|

| -149.375 dec                                         | $1 \ 0 \ 0 \ 1$ | 01010                            | 1 1 0       |  |  |  |  |  |  |

| in hex                                               | 9               | 5                                | 6           |  |  |  |  |  |  |

| 2. Express as fraction times a power of 16.          |                 |                                  |             |  |  |  |  |  |  |

| $.956 \times 16^{2}$                                 |                 |                                  |             |  |  |  |  |  |  |

| 3. Calculate characteria                             | stic and c      | onvert to bi                     | nary.       |  |  |  |  |  |  |

|                                                      | 2° 2            | $2^5 2^4 2^3 2^2 2^1 2$          | 0           |  |  |  |  |  |  |

| Exponent $+ 64 = 2 + 64 =$                           | $66 = 1 \ 0$    | 0 0 0 1 0                        |             |  |  |  |  |  |  |

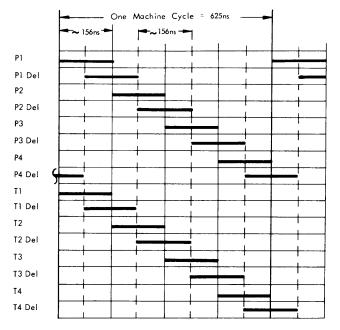

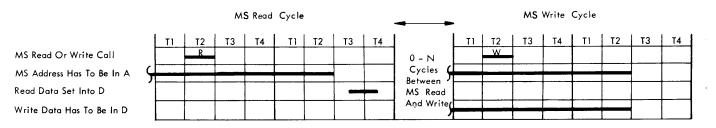

| 4. Arrange according to the format, insert the sign: |                 |                                  |             |  |  |  |  |  |  |