# System 3 Manual

#### Copyright

© 2000-2011 Tucker-Davis Technologies, Inc. (TDT). All rights reserved.

No part of this manual may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose without the express written permission of TDT.

Tucker-Davis Technologies 11930 Research Circle Alachua, FL 32615 USA

Phone: 386.462.9622 Fax: 386.462.5365

#### **Notices**

The information contained in this document is provided "as is," and is subject to being changed, without notice. TDT shall not be liable for errors or damages in connection with the furnishing, use, or performance of this document or of any information contained herein.

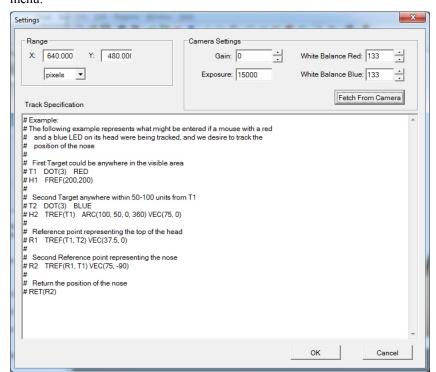

The latest versions of TDT documents are always online at <a href="www.tdt.com/support.htm">www.tdt.com/support.htm</a>.

A **CAUTION** informs users when failure to take or avoid a specified action could result in damage to the product or loss of data.

A **WARNING** calls attention to an operating procedure or practice that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

#### Licenses and Trademarks

ZIF-Clip<sup>®</sup> is a registered trademark of Tucker-Davis Technologies.

Updated: 11/18/2011 9:56 AM

#### Warranty

TDT System 3 hardware\* carries a five-year warranty on parts and labor.

Contact TDT to obtain an RMA (return merchandise authorization) number before returning any hardware. Repairs are usually completed within one week of receipt.

Package the hardware carefully and label the outside of the box with the RMA number.

Ship to:

TDT 11930 Research Circle Alachua, FL 32615

<sup>\*</sup> Custom hardware carries a one-year warranty on parts and labor. ES1 and EC1 carry a two year warranty.

## **Table of Contents**

| PART 1        | RZ Z-SERIES PROCESSORS               | 1-1  |

|---------------|--------------------------------------|------|

| RZ2 BioAmp    | Processor                            | 1-3  |

| RZ5 BioAmp    | Processor                            | 1-14 |

| RZ5D BioAm    | p Processor                          | 1-25 |

| RZ6 Multi I/0 | O Processor                          | 1-35 |

| RZ-UDP RZ     | Communications Interface             | 1-49 |

| PART 2        | DATA STREAMERS                       | 2-1  |

| RS4 Data Str  | eamer                                | 2-3  |

| PO8e Interfa  | ce for the RZ                        | 2-22 |

| PART 3        | RX PROCESSORS                        | 3-1  |

| RX5 Pentusa   | Base Station                         | 3-3  |

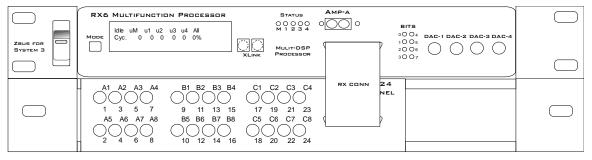

| RX6 Piranha   | Multifunction Processor              | 3-13 |

| RX7 Stimulat  | tor Base Station                     | 3-25 |

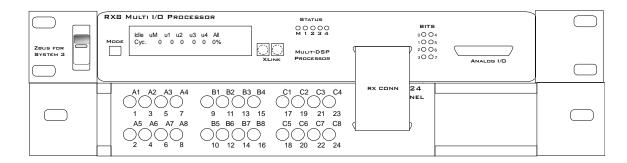

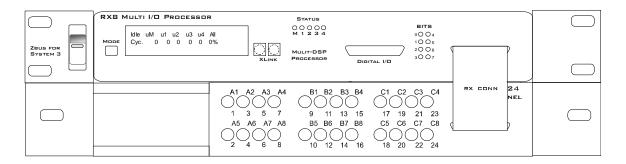

| RX8 Multi I/0 | 0                                    | 3-35 |

| PART 4        | RP PROCESSORS                        | 4-1  |

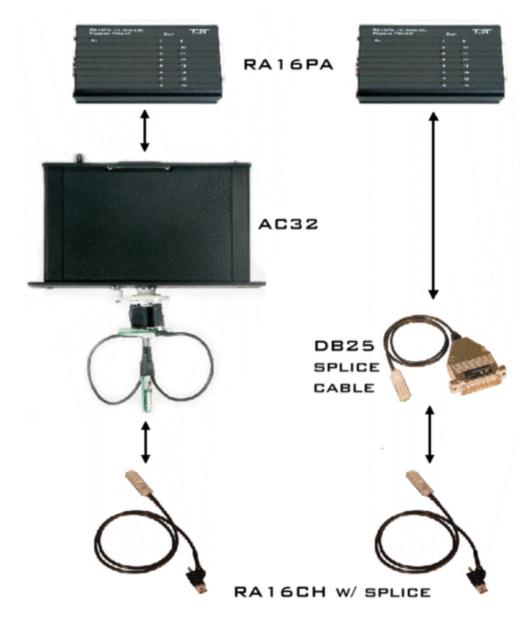

| RA16 Medus    | a Base Station                       | 4-3  |

| RP2.1 Real-T  | ime Processor                        | 4-7  |

| RV8 Barracu   | da                                   | 4-12 |

| PART 5        | RM MOBILE PROCESSORS                 | 5-1  |

| RM Mobile P   | Processors                           | 5-3  |

| PART 6        | PREAMPLIFIERS                        | 6-1  |

| PZ2 Preampl   | ifier                                | 6-3  |

| PZ3 Low Imp   | oedance Amplifier                    | 6-9  |

| PZ-RAT Exte   | ernal Battery Pack for PZ Amplifiers | 6-20 |

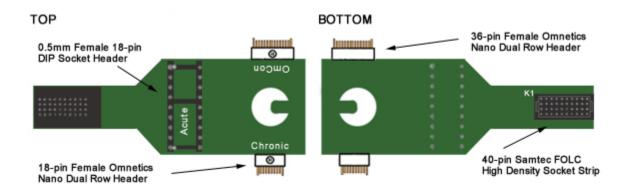

| PZ4 Digital Headstage Manifold                  | 6-21  |

|-------------------------------------------------|-------|

| Medusa Preamplifiers                            | 6-25  |

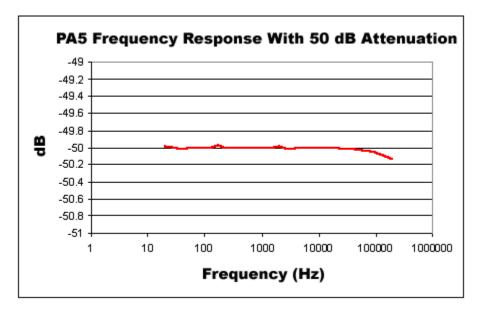

| Adjustable Gain Preamp                          | 6-30  |

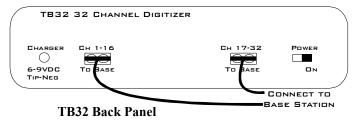

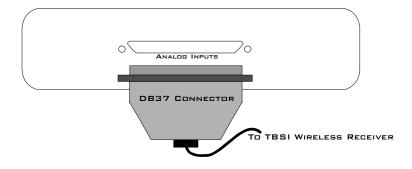

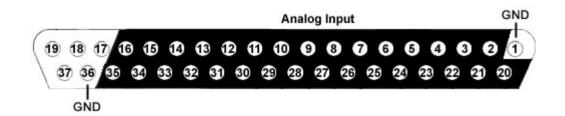

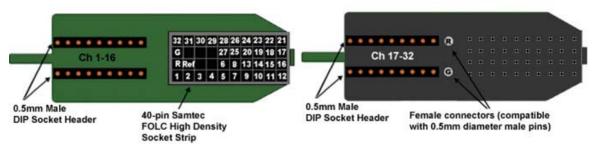

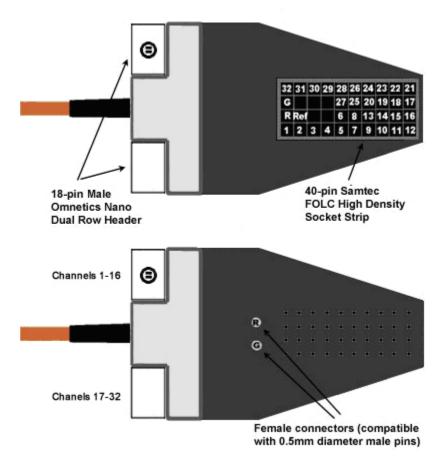

| TB32 32-Channel Digitizer                       | 6-34  |

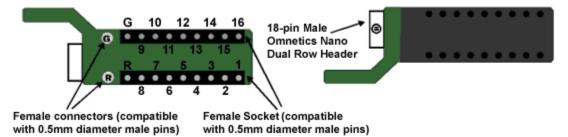

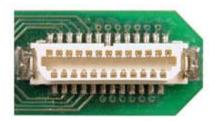

| Headstage Connection Guide                      | 6-38  |

| PART 7 STIMULUS ISOLATOR                        | 7-1   |

| MS4/MS16 Stimulus Isolator                      | . 7-3 |

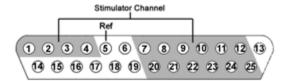

| IZ2 Stimulator                                  | 7-23  |

| PART 8 VIDEO PROCESSORS                         | 8-1   |

| RV2 Video Processor                             | . 8-3 |

| RVMap Software                                  | 8-18  |

| PART 9 MICROELECTRODE ARRAY INTERFACE           | 9-1   |

| MZ60 - MicroElectrode Array Interface           | . 9-3 |

| HC10 - Temperature Controller                   | 9-10  |

| PART 10 HIGH IMPEDANCE HEADSTAGES1              | 0-1   |

| ZIF-Clip® Headstages                            | 10-3  |

| RA16AC - 16 Channel Acute Headstage             | 0-15  |

| NN64AC - 64 Channel Acute Headstage             | 0-17  |

| NN32AC - 32 Channel Acute Headstage             | 0-19  |

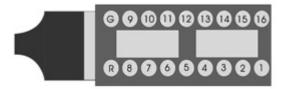

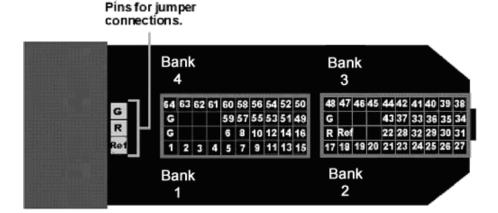

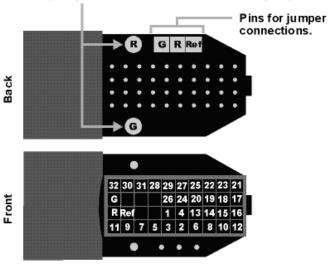

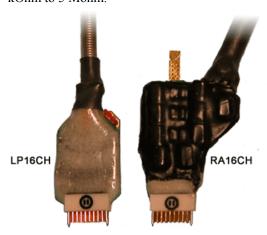

| RA16CH/LP16CH - 16 Channel Chronic Headstage1   | 0-22  |

| RA4AC - Four Channel Headstage                  | 0-24  |

| SH16 - 16 Channel Switchable Acute Headstage    | 0-26  |

|                                                 |       |

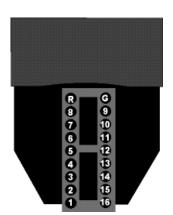

| SH16-Z - 16 Channel Switchable Acute Headstage1 | 0-35  |

| SH16-Z - 16 Channel Switchable Acute Headstage  |       |

|                                                 | 1-1   |

| RA16LI-D - 16   | 6 Channel Headstage with Differential | 11-7  |

|-----------------|---------------------------------------|-------|

| PART 12         | ADAPTERS AND CONNECTORS               | 12-1  |

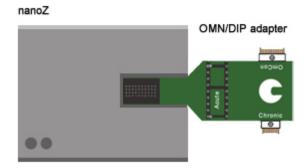

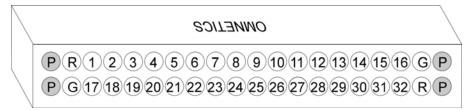

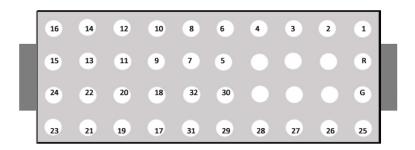

| Probe Adapter   | 'S                                    | 12-3  |

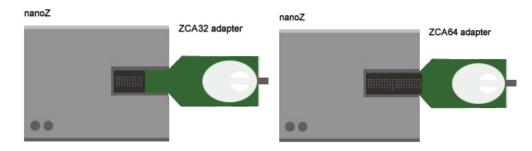

| ZIF-Clip® Hea   | dstage Adapters                       | 12-9  |

| Preamplifier A  | dapters                               | 12-17 |

| Connectors      |                                       | 12-20 |

| Splitters       |                                       | 12-21 |

| PART 13         | MICROWIRE ARRAYS                      | 13-1  |

| ZIF-Clip® Bas   | ed Microwire Arrays                   | 13-3  |

| Omnetics Base   | ed Microwire Arrays                   | 13-6  |

| Suggestions for | r Microwire Insertion                 | 13-8  |

| PART 14         | ATTENUATOR                            | 14-1  |

| PA5 Programi    | nable Attenuator                      | 14-3  |

| PART 15         | COMMUTATORS                           | 15-1  |

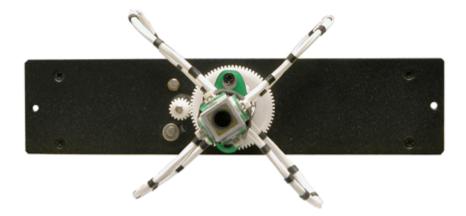

| ACx Motorize    | d Commutators                         | 15-3  |

| PART 16         | TRANSDUCERS AND AMPLIFIERS            | 16-1  |

| MF1 Multi-Fie   | eld Magnetic Speakers                 | 16-3  |

| CF1/FF1 Mag     | netic Speakers                        | 16-7  |

| EC1/ES1 Elect   | rostatic Speaker                      | 16-11 |

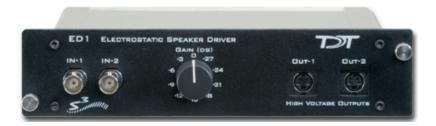

| ED1 Electrosta  | atic Speaker Driver                   | 16-16 |

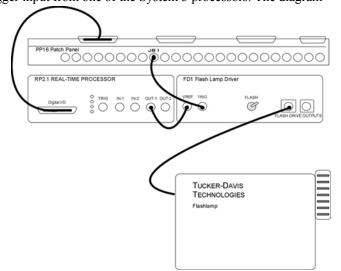

| FLYSYS Flash    | ıLamp System                          | 16-18 |

| HB7 Headpho     | ne Buffer                             | 16-21 |

| MA3: Microph    | none Amplifier                        | 16-24 |

| MS2 Monitor     | Speaker                               | 16-27 |

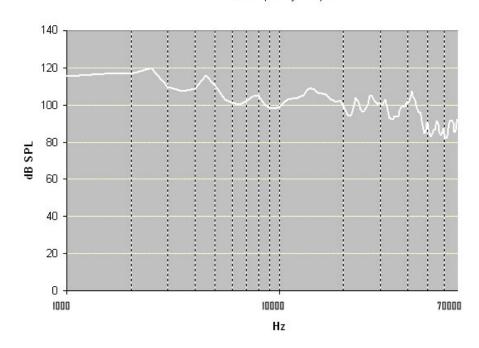

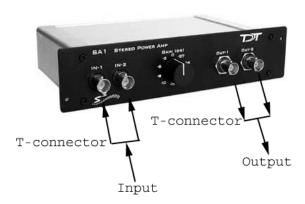

| SA1 Stereo An   | nplifier                              | 16-28 |

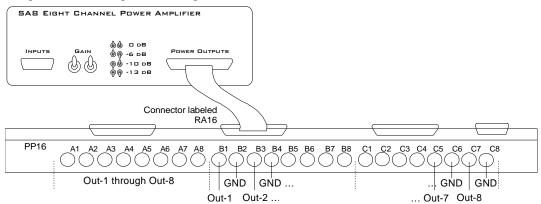

| SA8 Eight Cha   | nnel Power Amplifier                  | 16-30 |

| PART 17         | SUBJECT INTERFACES              | 17-1  |

|-----------------|---------------------------------|-------|

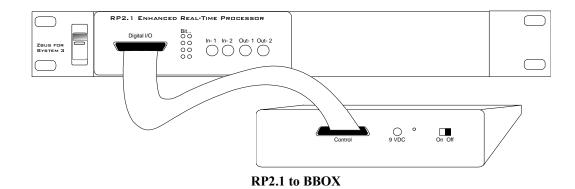

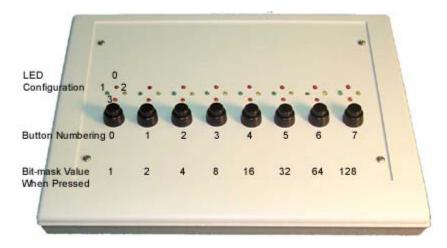

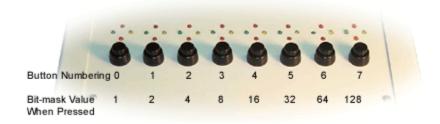

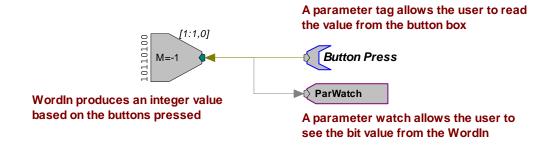

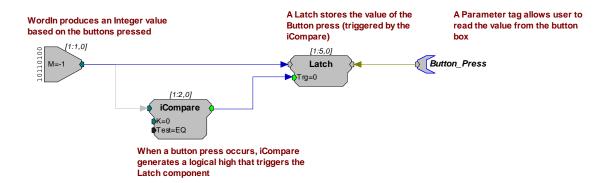

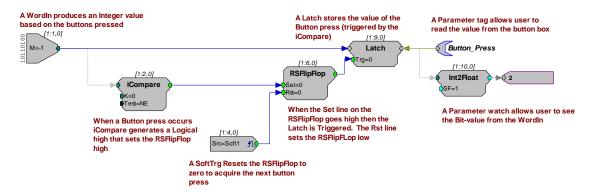

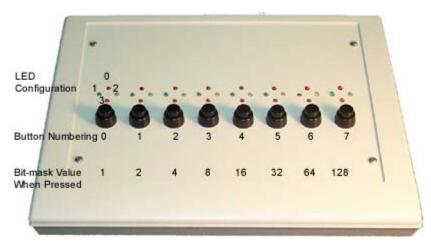

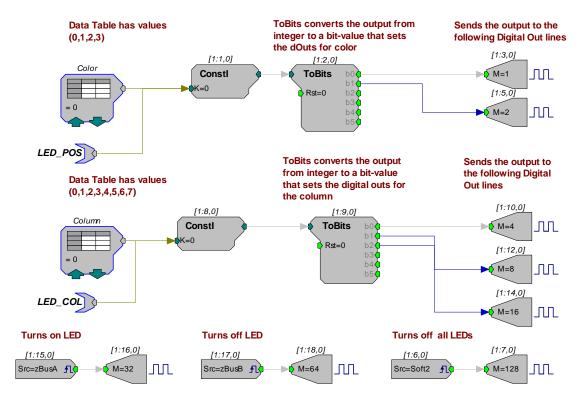

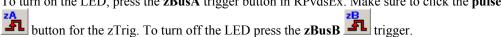

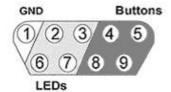

| BBOX Button     | Box                             | 17-3  |

| RBOX Respon     | nse Box                         | 17-12 |

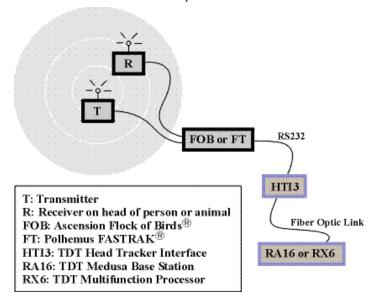

| HTI3 Head Tr    | acker Interface                 | 17-17 |

| PART 18         | SIGNAL HANDLING                 | 18-1  |

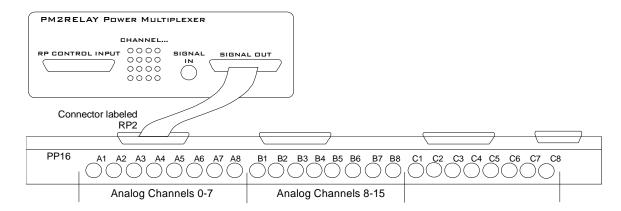

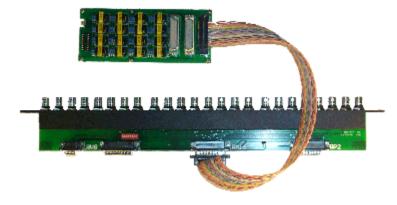

| PM2Relay        |                                 |       |

| SM5 Signal M    | ixer                            |       |

| PP16 Patch Pa   | nnel                            |       |

| PP24 Patch Pa   | nnel                            | 18-17 |

| ETM1 Experi     | ment Test Module                | 18-22 |

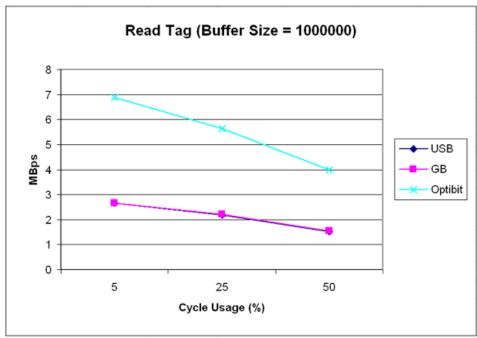

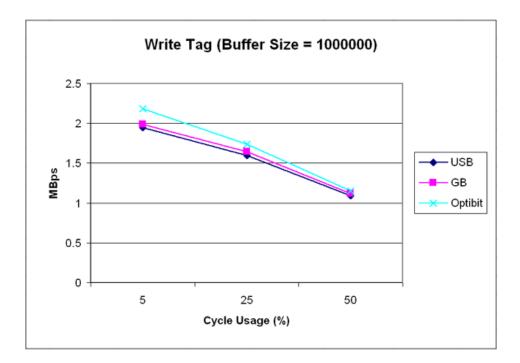

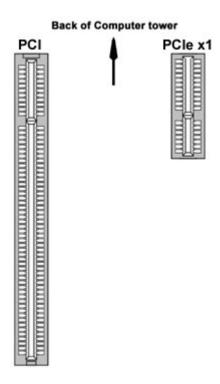

| PART 19         | PC INTERFACES                   | 19-1  |

| Interface Tran  | nsfer Rates                     | 19-3  |

| Optibit Interfa | ace                             | 19-5  |

| Gigabit Interf  | ace                             | 19-7  |

| UZ2 USB 2.0 I   | Interface                       | 19-9  |

| ExpressCard t   | to zBus Interface               | 19-11 |

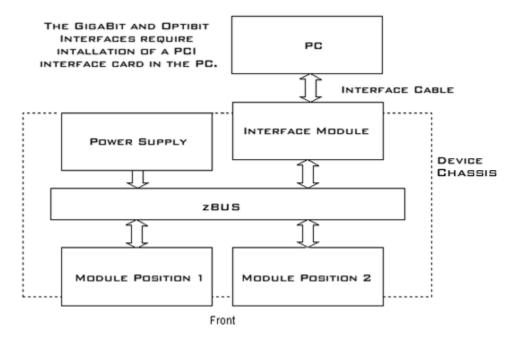

| PART 20         | THE ZBUS AND POWER SUPPLY       | 20-1  |

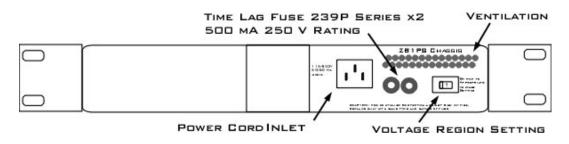

| ZB1PS Chassi    | s - Powered zBUS Device Chassis | 20-3  |

| ZB1 Device Ca   | addie and PS25F Power Supply    | 20-8  |

| PART 21         | SYSTEM 3 UTILITIES              | 21-1  |

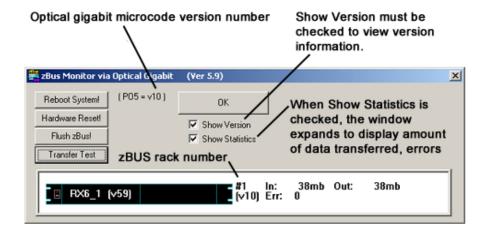

| zBUSmon – Bu    | us/Interface Test Utility       | 21-3  |

| RPProg - Mici   | rocode Undate Utility           | 21-5  |

# Part 1 RZ Z-Series Processors

1-2 RZ Z-Series Processors

~

## **RZ2 BioAmp Processor**

## Overview

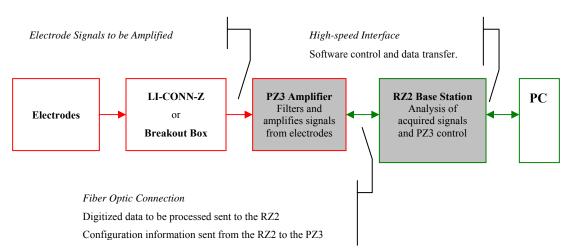

The RZ2 BioAmp Processor has been designed for high channel count neurophysiological recording and signal processing. The RZ2 features two (RZ2-2), four (RZ2-4), or eight (RZ2-8) Sharc digital signal processors networked on a multiprocessor architecture that features efficient onboard communication and memory access. The highly optimized multi-bus architecture realizes a device with up to nearly 20 gigaflops of processing power and four dedicated data buses to eliminate data flow bottlenecks—all transparent to the user. This architecture yields an extremely powerful system capable of sophisticated real-time processing and simultaneous acquisition on all 256 channels at sampling rates up to ~25 kHz and 128 channels at sampling rates up to ~50 kHz.

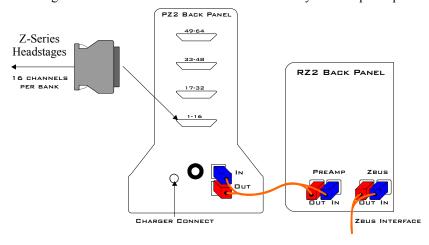

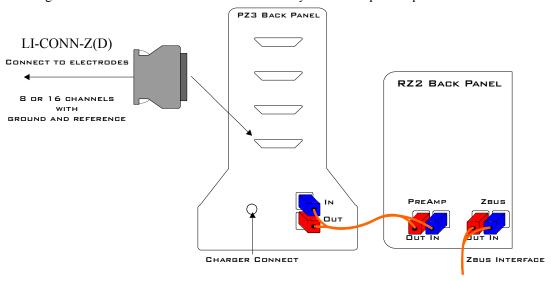

The RZ2 is typically used with a Z-Series Amplifier (such as the PZ2 or PZ3). High bandwidth data is streamed from the amplifier to the RZ2 over a lossless fast fiber optic connection.

The RZ2 also features 16 channels of analog I/O, 24 bits of digital I/O, two Legacy optical inputs for Medusa PreAmps, and an onboard LCD for system status display.

#### **Power and Communication**

The RZ2's Optibit optical interface ensures fast and reliable data transfer from the RZ2 to the PC and is integrated into the device. Connectors are provided on the back panel and are color coded for correct wiring. The RZ2's power supply is also integrated into the device and is shipped from the factory configured for the desired voltage setting (110 V or 220V). If you need to change the voltage setting, please contact TDT support at 386.462.9622 or email support@tdt.com.

The RZ2 is UL compliant, see the RZ2 Operations Manual for power and safety information.

#### Software Control

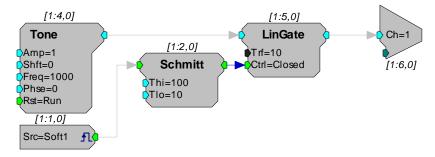

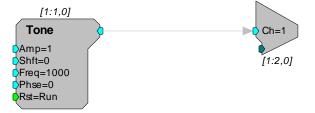

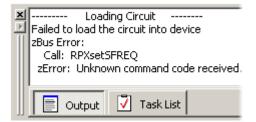

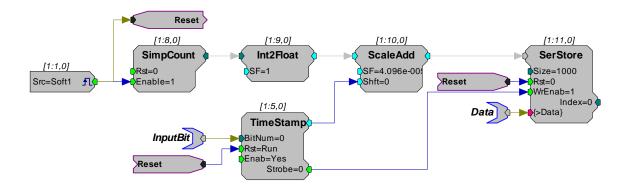

Software control is implemented with circuit files developed using TDT's RP Visual Design Studio (RPvdsEx). Circuits are loaded to the processor through TDT run-time applications or custom applications. This manual includes device specific information needed during circuit design. For circuit design techniques and a complete reference of the RPvdsEx circuit components, see *MultiProcessor Circuit Design* and *Multi-Channel Circuit Design* in the *RPvdsEx Manual*.

1-4 RZ Z-Series Processors

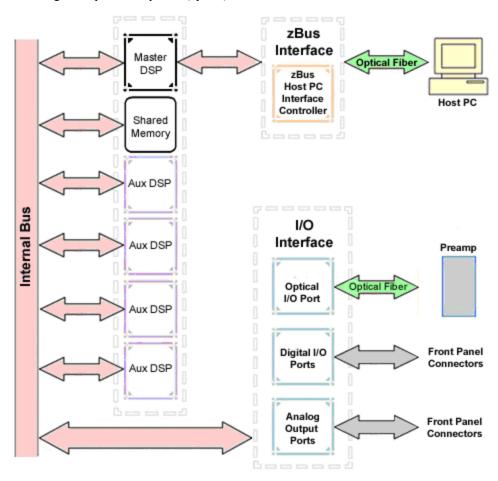

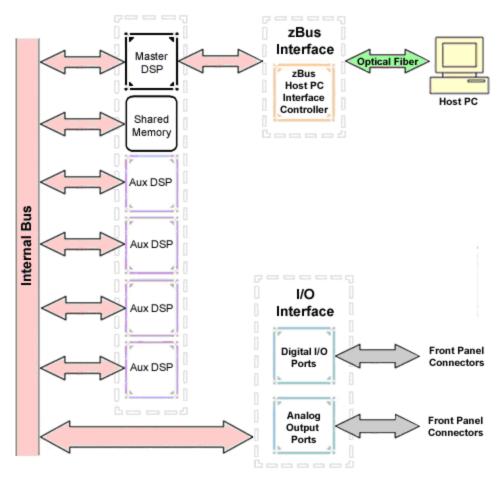

## **RZ2** Architecture

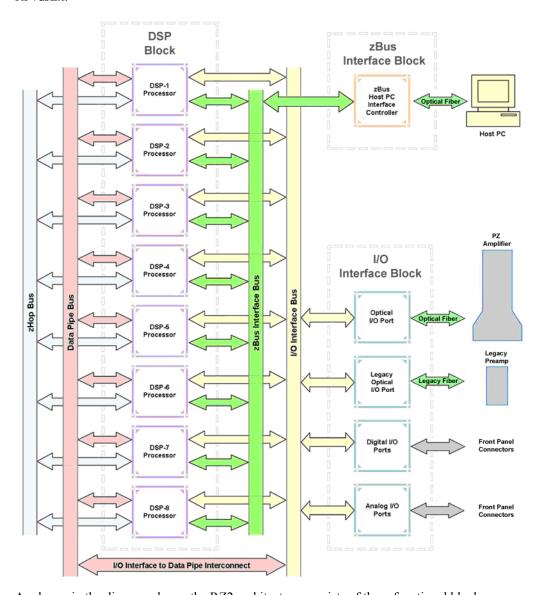

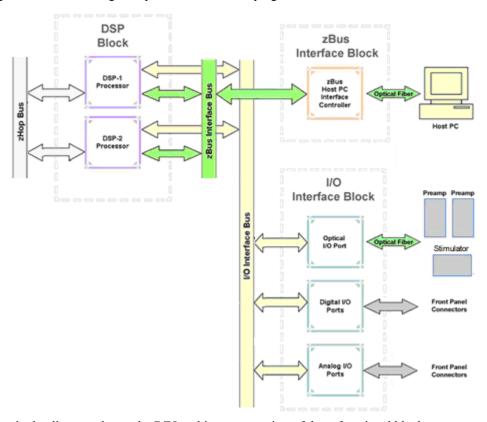

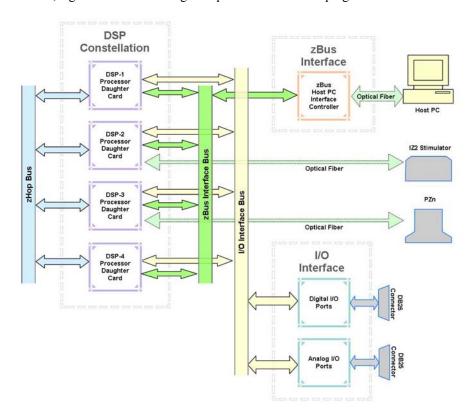

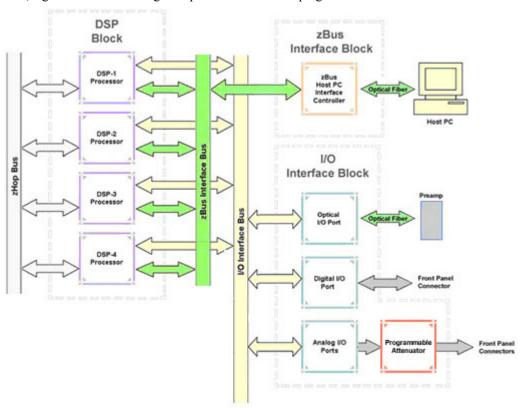

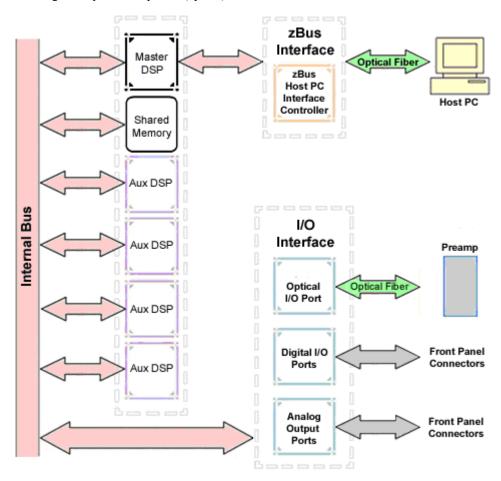

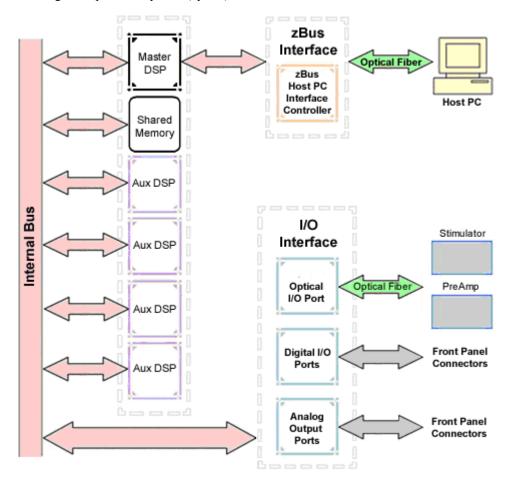

The RZ2 processor utilizes a highly optimized multi-bus architecture and offers four dedicated, data buses for fast, efficient data handling. While the operation of the system architecture is largely transparent to the user, a general understanding is important when developing circuits in RPvdsEx.

As shown in the diagram above, the RZ2 architecture consists of three functional blocks:

#### The DSPs

Each DSP in the DSP Block is connected to 64 MB SDRAM and a local interface to the four data buses: two buses that connect each DSP to the other functional blocks and two that handle data transfer between the DSPs (as described further in Distributing Data Across DSPs below). This architecture facilitates fast DSP-to-off-chip data handling.

Because each DSP has its own associated memory, access is very fast and efficient. However, large and complex circuits should be designed to balance memory needs (such as data buffers and filter coefficients)

across processors. Memory use can be monitored on the RZ2 front panel display.

When designing circuits also note that the maximum number of components for each RZ2 DSP is 768.

The zBus Interface

The zBus Interface provides a connection to the PC. Data and host PC control commands are transferred to and from the DSP Block through the **zBus Interface Bus**, allowing for large high-speed data reads and writes without interfering with other system processing.

The I/O Interface

The I/O Interface serves as a connection to outside signal sources or output devices. It is used primarily to input data from a PZ amplifier via the high speed optical port, but also serves the Legacy amplifier inputs and digital and analog channels. The I/O Interface Bus provides a direct connection to each DSP and the Data Pipe Bus.

### **Distributing Data Across DSPs**

To reap the benefits of added power made possible by multi-DSP modules, processing tasks must be efficiently distributed across the available DSPs. That means transferring data across DSPs. The RZ2 architecture provides two data buses for this type of data handling.

#### The Data Pipe Bus

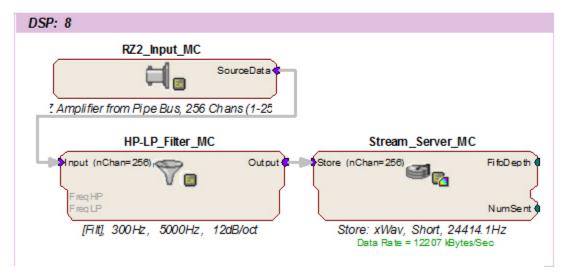

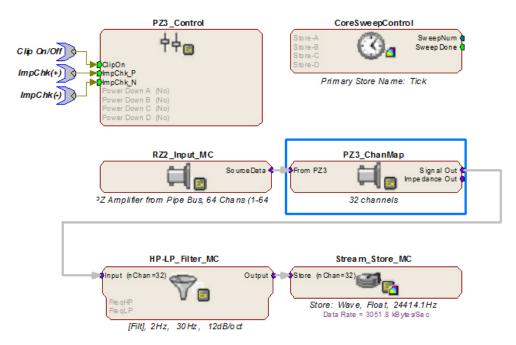

The Data Pipe Bus is optimized for handling high count multi-channel data streams and efficiently transfers up to 256 channels of data between DSPs. The Data Pipe Bus also interconnects to the I/O Interface Bus allowing direct access to data from the PZ amplifiers.

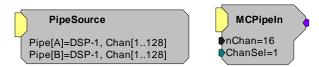

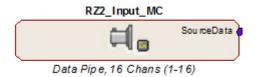

In RPvdsEx data can be transferred across the Data Pipe Bus using DataPipe components.

PipeSource and MCPipeIn components are used to select a data source (another DSP or the PZ amplifier) and feed data to a DSP circuit.

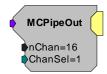

MCPipeOut feeds data off the DSP to the DataPipe Bus.

PZ Am plifier from Pipe Bus, 64 Chans (1-64

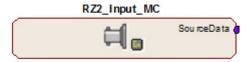

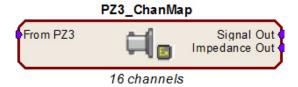

The RZ2 Input MC macro also transfers inputs from the I/O interface to the PipeBus and DSPs.

1-6 RZ Z-Series Processors

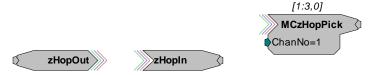

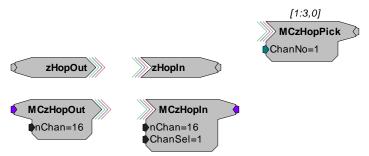

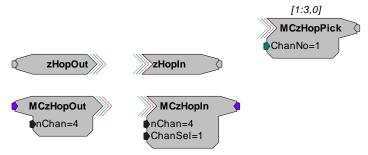

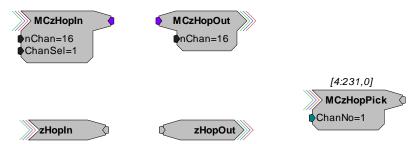

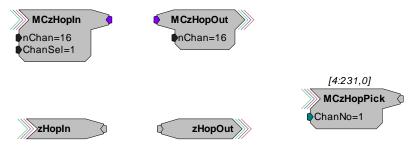

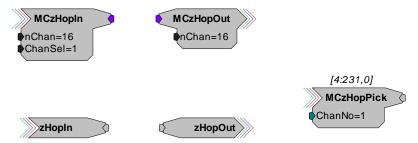

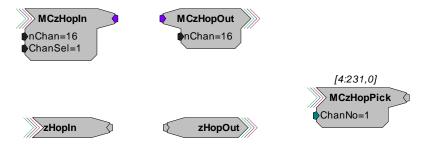

#### The zHop Bus

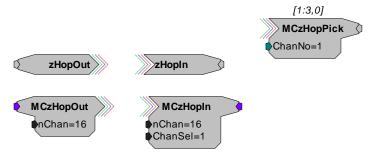

The zHop Bus is useful for transferring single or low channel count signals, such as timing and control signals.

In RPvdsEx data is transferred across the zHop Bus using paired zHop Components, including zHopIn, zHopOut, MCzHopIn, MCzHopOut, and MCzHopPick. Up to 126 pairs can be used in a single RPvdsEx circuit.

The zHopBus is less efficient than the Data Pipe Bus, so it is not recommended for multi-channel signals.

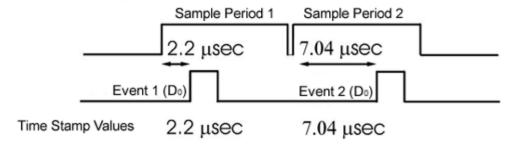

#### **Bus Related Delays**

Standard delays are associated with the zHop and Data Pipe Bus. The zHop Bus introduces a single sample delay and the Data Pipe Bus adds a two sample delay. However, these delays are taken care of for the user in OpenEx when Timing and Data Saving macros are used.

#### 50 kHz Sampling Rate Acquisition with the PZ Amplifier

The RZ2 and PZ amplifier support sample rates from ~6 kHz to ~50 kHz. When sampling at a rate of ~50 kHz, there are several important considerations:

Only the first 128 PZ amplifier channels will be available.

All DataPipes will have a max of 128 channels instead of 256.

Both halves (A and B) of the PipeSource component must be selecting the desired source. For example, when acquiring data from a PZ amplifier, Pipe[A] and Pipe[B] both need to be set to Amp. Chan[1..128].

#### **Data Transfer Rate**

As with other devices, your expected sustained RZ-to-Host PC data rate should not exceed 1/2 to 2/3 of the rated data transfer speed. For the RZ2 device this is 160 Mbits/second (Mbps) so your designs should have a sustained data rate of no more than ~100 Mbps. When the RZ2 is processing, the current data transfer rate (Mbps) is displayed in the top right corner of the LCD Screen. This maximum rate may be further limited by your PC's ability to store the data to disk.

This equates to streaming a maximum of 160 channels at a sampling rate of ~25 kHz or 90 channels at a sampling rate of ~50 kHz. See *Calculating Data Transfer Rates* in the *OpenEx Manual* for more information.

## RZ2 Features

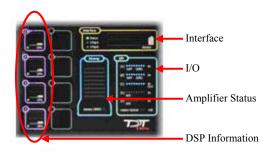

#### **LCD Screen**

The LCD screen shows information about each DSP, the optical PC interface, the PZ preamplifier and system I/O. A selection knob allows the user to highlight a section of the screen to display more detailed information. Rotate the selection knob to select a system component. Once the selection has been made, push the knob and expand the information view.

| Selection | Available Information                                                                                                                                          |                                                                                                                                                                                   |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DSPs      | Component usage, memory usage and pipe source statistics for that processor  A stacked histogram shows cycle usage for each DSP with the bottom section (blue) |                                                                                                                                                                                   |  |

|           | ge taken up by circuit operation and the top section (pink) ge required for data transfer                                                                      |                                                                                                                                                                                   |  |

|           | If the cycle usage surpasses 100%, a bar is drawn above the 100% line in the cycle usage and will persist until the RZ2 is rebooted                            |                                                                                                                                                                                   |  |

| Interface | Firmware version, ME                                                                                                                                           | 3 data received/sent and transfer errors                                                                                                                                          |  |

| Amp       | Amp model, number of channels and firmware version of connected PZ series amplifier                                                                            |                                                                                                                                                                                   |  |

| I/O       | Virtual indicator lights                                                                                                                                       |                                                                                                                                                                                   |  |

|           | [A], [B], and [C]:                                                                                                                                             | Digital I/O                                                                                                                                                                       |  |

|           |                                                                                                                                                                | LED will light for an input bit or it will show the logic level for an output bit                                                                                                 |  |

|           | [D] and [E]:                                                                                                                                                   | Analog I/O                                                                                                                                                                        |  |

|           |                                                                                                                                                                | 16 lights will indicate the signal level, green when a signal is present and red to warn that the signal is approaching the maximum voltage (at which point clipping would occur) |  |

|           | Legacy Optical:                                                                                                                                                | Amp Light For The Legacy Preamplifier Sync                                                                                                                                        |  |

|           |                                                                                                                                                                | Flash when no amp is connected and will be light light blue when the amplifier is correctly connected                                                                             |  |

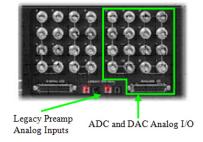

## **Amplifier and Onboard Analog I/O**

The RZ2 is equipped with both optical port amplifier input and onboard analog I/O capabilities. The high speed fiber optic ports (located on the RZ2 back panel) and Legacy fiber optic ports (shown left) allow a direct connection to Z-Series or Medusa Preamplifiers. Physiological signals are digitized on the preamplifier and transferred across noiseless fiber optics.

The RZ2 also includes onboard D/A for stimulus generation and experiment control, and A/D for input of signals from a variety of other analog sources.

1-8 RZ Z-Series Processors

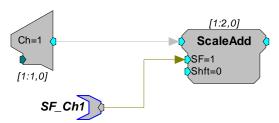

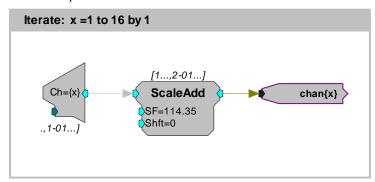

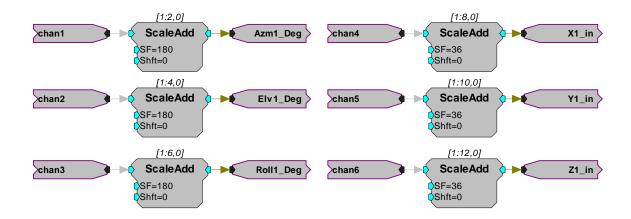

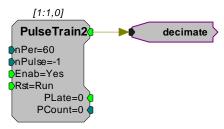

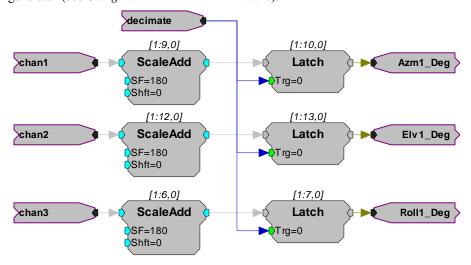

The RZ2\_Input\_MC macro provides a universal solution for analog input via the RZ2, automatically selecting the correct components, applying any scale factors or channel offsets, and performing data type conversion needed based on information the user provides about the input source.

The table below provides a quick overview of these I/O features and how they must be accessed during circuit design. When the RZ2\_Input\_MC macro is not used, reference the table and be sure to use the appropriate component, channel offset, scale factor and so forth. Further detail can be found below the table. Also, see the *RPvdsEx Manual* for more information.

| Analog<br>I/O                        | Description                                               | Components                  | Channels | Notes                                                                                           |

|--------------------------------------|-----------------------------------------------------------|-----------------------------|----------|-------------------------------------------------------------------------------------------------|

| Port D                               | Analog Input                                              | AdcIn                       | 1-8      | Standard Configuration (may vary)<br>Accessed through Port D BNCs or<br>Analog I/O labeled DB25 |

| Port E                               | Analog Output                                             | DacOut                      | 9-16     | Standard Configuration (may vary) Accessed through Port E BNCs or Analog I/O labeled DB25       |

| High<br>Speed<br>Fiber<br>Optic Port | Z-Series<br>BioAmp Input<br>(located on RZ<br>back panel) | MCPipeIn PipeIn recommended | 1-256    | When the RZ2_Input_MC is NOT USED, use MCInt2Float or Int2Float with a scale factor of 1e-9     |

|                                      |                                                           | MCAdcIn                     | 1-256    | No scale required.                                                                              |

| Legacy<br>Amp-A                      | Medusa<br>PreAmp Input                                    | AdcIn                       | 17-32    | When the RZ2_Input_MC is NOT USED, apply a scale factor of .000833                              |

| Legacy<br>Amp-B                      | Medusa<br>PreAmp Input                                    | AdcIn                       | 33-48    | When the RZ2_Input_MC is NOT USED, apply a scale factor of .000833                              |

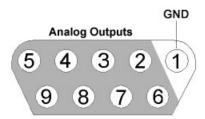

#### Onboard Analog I/O

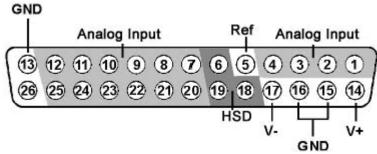

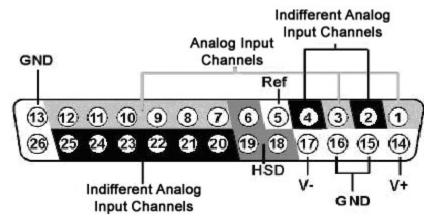

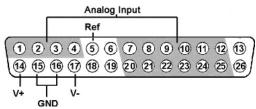

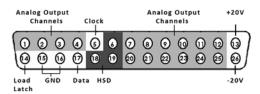

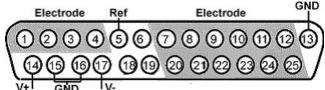

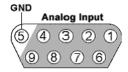

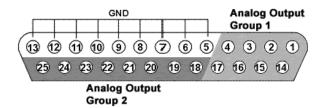

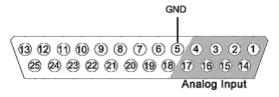

The RZ2 is equipped with eight channels of 16-bit PCM D/A and eight channels of 16-bit PCM A/D. All 16 channels can be accessed via front panel BNCs marked Port D and Port E or via a 25-pin analog I/O connector. See RZ2 Technical Specifications, page 1-11, for the DB25 pinout.

#### PZ Amplifier Fiber Optic Port

The RZ2's primary amplifier input, a high-speed fiber optic port is located on the back panel. The connectors on the fiber optic pair used for PZ amplifier communication are color coded for correct wiring. When designing circuits in RPvdsEx, the PZ Amplifier input channels are accessed using the Pipe components. When the DataPipe is used to feed signals from the Amplifier a MCInt2Float or Int2Float must be used with a scale factor of 1e-9. The Amplifier inputs can also be accessed using the RPvdsEx MCAdcIn component starting at channel 1; however, this access method is less efficient and not recommended for high channel count applications. Unlike the

Legacy Port, this high speed port can input up to 256 channels at a maximum sampling rate of 25 kHz or 128 channels at a maximum sampling rate of 50 kHz.

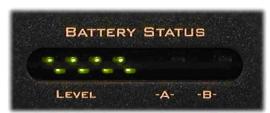

#### **Legacy Fiber Optic Ports**

The base station can also acquire digitized signals from the Medusa preamplifier, RA8GA, or other legacy enabled device over a fiber optic cable using the Legacy ports. Two Legacy fiber optic ports labeled -A- and -B- are provided to support simultaneous acquisition from up to two Medusa preamplifiers. Each port can input up to 16 channels at a maximum sampling rate of 25 kHz. The Legacy fiber optic ports can be used with any of the Medusa preamplifiers including, the RA16PA and the RA4PA, or the RA8GA. The channel numbers for each port begin at a fixed offset regardless of the number of channels available on the connected device.

#### Digital I/O

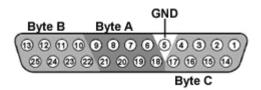

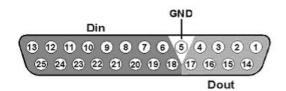

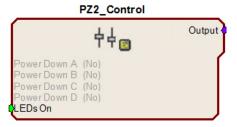

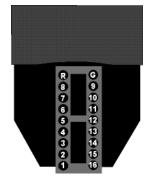

The digital I/O ports include 24 bits of programmable I/O. The digital I/O is divided into three ports (A, B, and C) as described in the chart below. All digital I/O lines are accessed via the 25-pin connector on the front of the RZ2 and ports A and C are available through BNC connectors on the front panel.

See RZ2 Technical Specifications, page 1-11, for the DB25 pinout and BNC channel mapping. See the Digital I/O Circuit Design section of the RPvdsEx Manual for more information on programming the digital I/O.

| Digital<br>I/O | Description | DB25 | BNCs | Notes               | Configuration                                                                                   |

|----------------|-------------|------|------|---------------------|-------------------------------------------------------------------------------------------------|

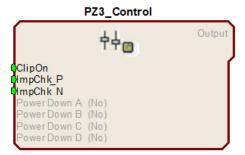

| Port A         | bits 0 - 7  | Yes  | Yes  | byte<br>addressable | RZ2_Control                                                                                     |

| Port B         | bits 0 - 7  | Yes  | No   | byte<br>addressable | Port-A Dir (Input)                                                                              |

| Port C         | bits 0 - 7  | Yes  | Yes  | bit<br>addressable  | Port-B Dir ( Input )<br>Port-C Dir ( 00000 000 )                                                |

|                |             |      |      |                     | <b>Note:</b> For more information on addressing and Digital I/O see the <i>RPvdsEx Manual</i> . |

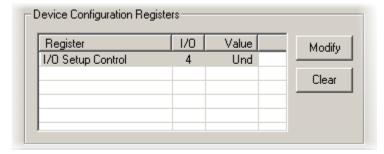

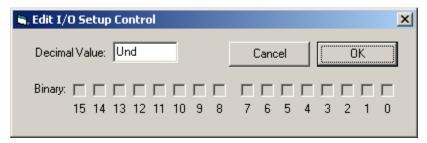

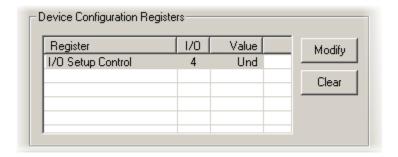

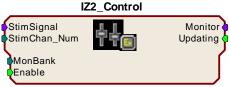

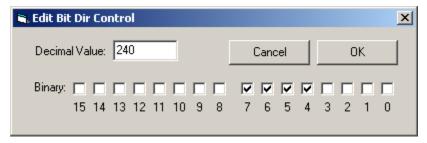

The data direction for the Digital I/O is configured using the RZ2\_Control macro in RPvdsEx. Double-click the macro to access the settings on the Digital I/O tab. The RZ2\_Control macro also offers a Direction Control Mode parameter that enables the macro inputs and allows the user to control data direction dynamically. For more information on using the RZ2\_Control macro see the help provided in the macro's properties dialog box.

The RZ digital I/O ports have different voltage outputs and logic thresholds depending on the type. Below is a table depicting the different voltage outputs and thresholds for both types.

1-10 RZ Z-Series Processors

| Digital I/O      | Voltage Output |           | Voltage Input |            |

|------------------|----------------|-----------|---------------|------------|

| Туре             | logic high     | logic low | logic high    | logic low  |

| byte addressable | 5 V            | 0 V       | ≥ 2.5 V       | 0 - 2.45 V |

| bit addressable  | 3.3 V          | 0 V       | ≥ 1.5 V       | 0 - 1.4 V  |

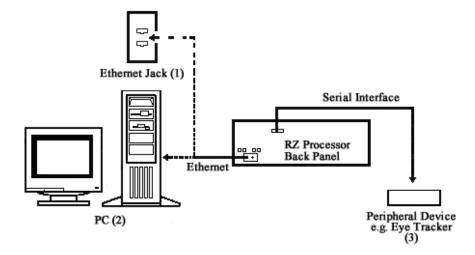

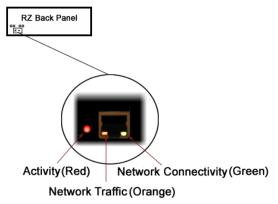

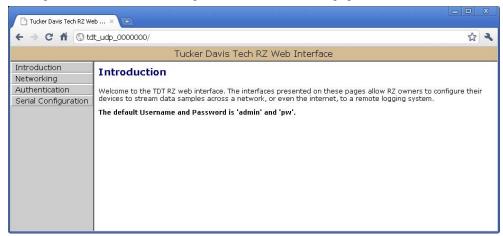

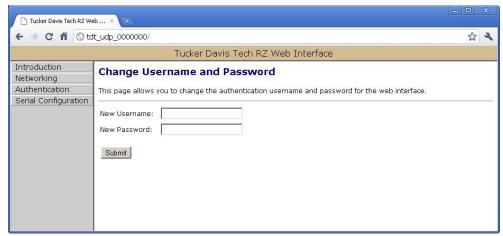

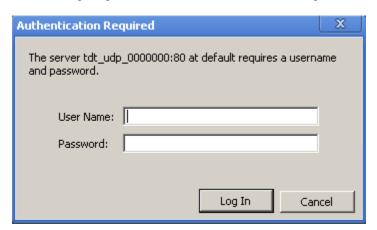

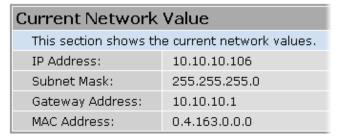

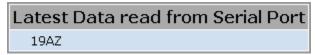

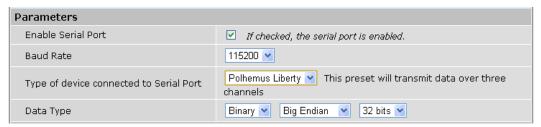

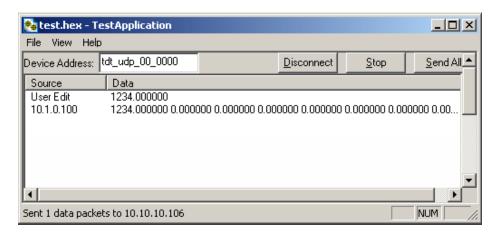

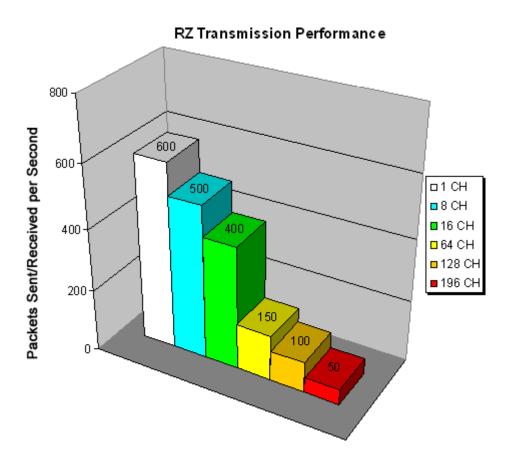

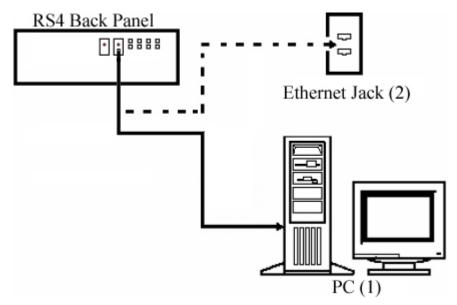

### **UDP Ethernet Interface (Optional)**

The RZ UDP Ethernet interface is designed to transfer data to or from a PC. RZ devices equipped with a UDP interface contain an additional port located on the back panel. See *UDP User Interface*, page 1-49, for more information.

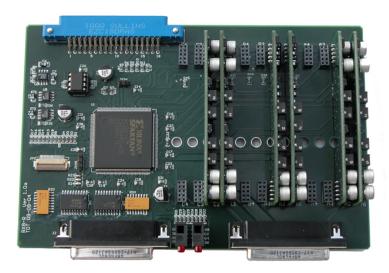

#### **Specialized DSP/Optical Interface Boards (Optional)**

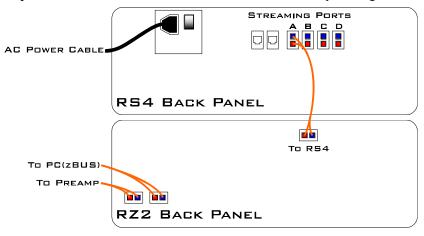

The RZ Standard DSP Boards can be replaced with specialized DSP Boards which include an optical interface for communication and control of RZ compatible devices, such as the IZ2 Stimulator and RS2 Data Streamer. RZ devices equipped with one or more specialized DSP boards include an optical port for each card. The ports are located on the back panel and labeled for easy identification.

#### **RZDSP-I**

This board supports the IZ2 Stimulator, allowing the RZ device to function as a controller or base station. See the IZ2 Stimulator section, page 7-23, for more information on using and designing circuits for the stimulator.

#### **RZDSP-S**

This board supports the RS2 Data Streamer, allowing the RZ device to stream data directly to the RS2's storage arrays. See the RS2 Data Streamer section, page 2-1, for more information on using and designing circuits for the streamer.

#### **RZDSP-U**

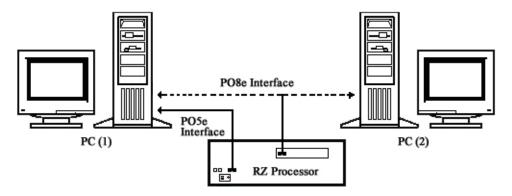

This board supports the PO8e interface card, allowing the RZ device to stream data directly to storage arrays on a PC or other device. See the PO8e documentation for more information.

#### **RZDSP-P**

This board supports PZ amplifier input, providing an alternate method for acquiring data from a PZ amplifier. It can be used to expand the number of channels that can be acquired on any RZ processor. Access to this input can be enabled in the PZ control macro.

#### **RZDSP-V**

This board supports the RV2 Video Tracking System, allowing the RZ device to function as a controller or base station. See the RV2 Video Processor section, page 8-1, for more information on using and designing circuits for the RV2.

## **Technical Specifications**

Specifications for the RZ2 Z-Series Base Station.

**Note**: Technical Specifications for amplifier A/D converters are found under the preamplifier's technical specifications.

| DSP                                           | 400 MHz DSPs, 2.4 GFLOPS peak per DSP<br>Two, Four, or Eight |  |  |

|-----------------------------------------------|--------------------------------------------------------------|--|--|

| Memory                                        | 64 MB SDRAM per DSP                                          |  |  |

| D/A                                           | 8 channels, 16-bit PCM                                       |  |  |

| Sample Rate                                   | Up to 48828.125 Hz                                           |  |  |

| Frequency Response                            | DC-Nyquist (~1/2 sample rate)                                |  |  |

| Voltage Out                                   | +/- 10.0 Volts                                               |  |  |

| S/N (typical) 82 dB (20 Hz - 20 kHz at 9.9 V) |                                                              |  |  |

| A/D                                           | 8 channels, 16-bit PCM                                       |  |  |

| Sample Rate                                   | Up to 48828.125 Hz                                           |  |  |

| Frequency Response                            | DC - 7.5 kHz (3 dB corner, 2nd order, 12 dB per octave)      |  |  |

| Voltage In                                    | +/- 10.0 Volts                                               |  |  |

| S/N (typical)                                 | 82 dB (20 Hz - 20 kHz at 9.9 V)                              |  |  |

| Fiber Optic Ports                             |                                                              |  |  |

| Z-Series                                      | One 256-channel input*                                       |  |  |

| Legacy (Medusa)                               | Two 16-channel inputs                                        |  |  |

| Digital I/O                                   | 24 bits programmable                                         |  |  |

<sup>\*</sup> The maximum sample rate is 48828.125 Hz when recording up to 128 channels or 24414.0625 Hz when recording 129 - 256 channels).

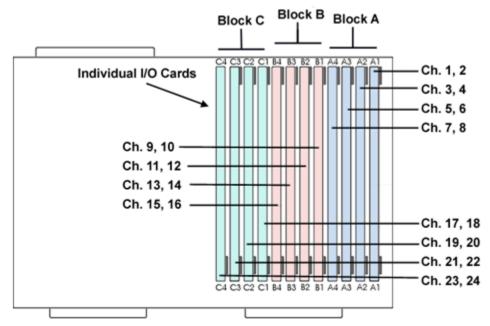

## **BNC Channel Mapping**

Please note channel numbering begins at the top right block of BNCs for each port and is printed on the face of the device to minimize miswiring. The figure below represents the standard configuration and may vary depending on customer request.

1-12 RZ Z-Series Processors

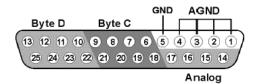

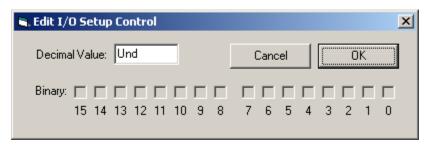

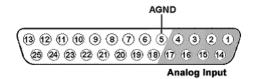

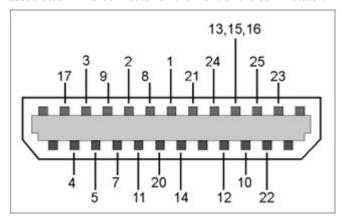

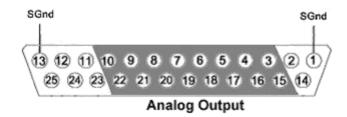

## **DB25 Analog I/O Pinout**

| Pin | Name | Description                       |

|-----|------|-----------------------------------|

| 1   | NA   | Not Used                          |

| 2   |      |                                   |

| 3   |      |                                   |

| 4   |      |                                   |

| 5   | AGND | Analog Ground                     |

| 6   | A2   | ADC                               |

| 7   | A4   | Analog Input<br>Channels (Port D) |

| 8   | A6   |                                   |

| 9   | A8   |                                   |

| 10  | A10  | DAC                               |

| 11  | A12  | Analog Output                     |

| 12  | A14  | Channels (Port E)                 |

| 13  | A16  |                                   |

| Pin | Name | Description                        |

|-----|------|------------------------------------|

| 14  | NA   | Not Used                           |

| 15  |      |                                    |

| 16  |      |                                    |

| 17  |      |                                    |

| 18  | A1   | ADC                                |

| 19  | A3   | Analog Input<br>Channels (Port D)  |

| 20  | A5   |                                    |

| 21  | A7   |                                    |

| 22  | A9   | DAC                                |

| 23  | A11  | Analog Output<br>Channels (Port E) |

| 24  | A13  |                                    |

| 25  | A15  |                                    |

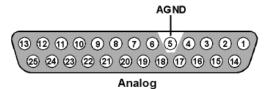

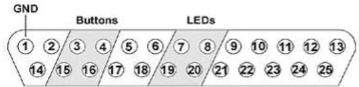

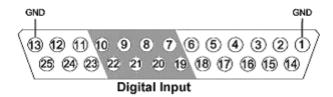

## **DB25 Digital I/O Pinout**

| Pin | Name | Description                     |

|-----|------|---------------------------------|

| 1   | C0   | Port C                          |

| 2   | C2   | Bit Addressable<br>digital I/O  |

| 3   | C4   | Bits 0, 2, 4, and 6             |

| 4   | C6   |                                 |

| 5   | GND  | Digital I/O Ground              |

| 6   | A1   | Port A                          |

| 7   | A3   | Word addressable<br>digital I/O |

| 8   | A5   | Bits 1, 3, 5, and 7             |

| 9   | A7   |                                 |

| 10  | B1   | Port B                          |

| 11  | В3   | Word addressable                |

| 12  | В5   | digital I/O                     |

| 13  | В7   | Bits 1, 3, 5, and 7             |

| Pin | Name | Description                     |

|-----|------|---------------------------------|

| 14  | C1   | Port C                          |

| 15  | СЗ   | Bit Addressable<br>digital I/O  |

| 16  | C5   | Bits 1, 3, 5, and 7             |

| 17  | С7   |                                 |

| 18  | A0   | Port A                          |

| 19  | A2   | Word addressable<br>digital I/O |

| 20  | A4   | Bits 0, 2, 4, and 6             |

| 21  | A6   |                                 |

| 22  | В0   | Port B                          |

| 23  | B2   | Word addressable<br>digital I/O |

| 24  | B4   | Bits 0, 2, 4, and 6             |

| 25  | В6   |                                 |

1-14 RZ Z-Series Processors

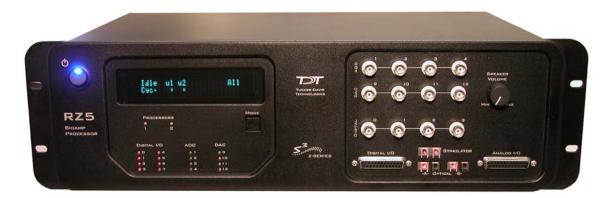

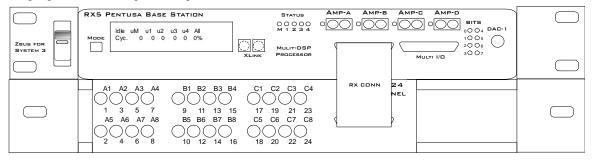

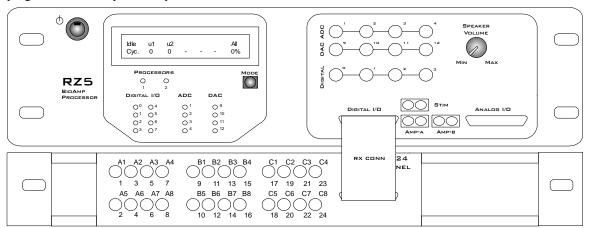

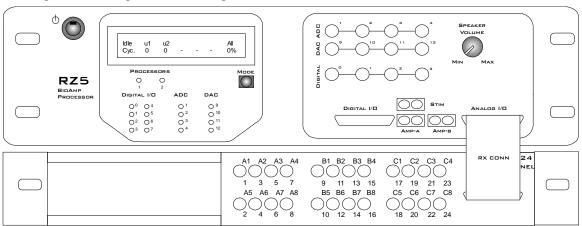

## **RZ5 BioAmp Processor**

## **Overview**

The RZ5 BioAmp Processor is available with either one or two 400 MHz Sharc digital signal processors networked on a multiprocessor architecture that features efficient onboard communication and memory access. The optimized multi-DSP architecture provides nearly five gigaflops of processing power, making the RZ5 a versatile solution for real-time processing and simultaneous acquisition.

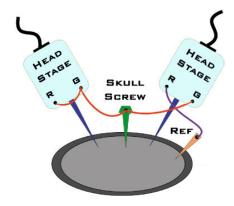

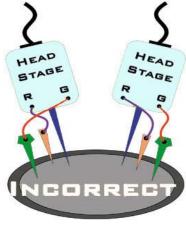

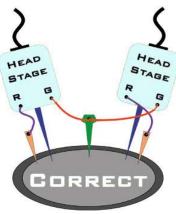

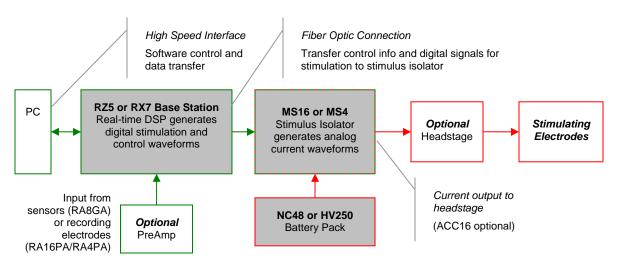

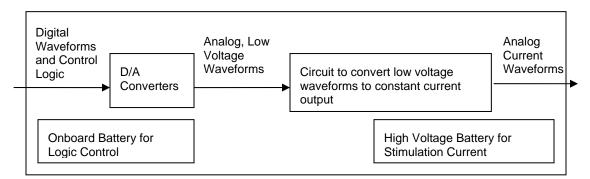

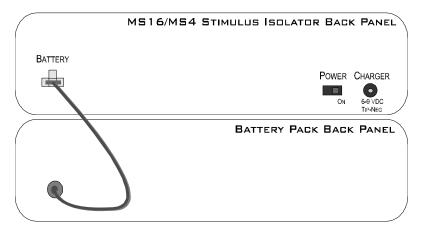

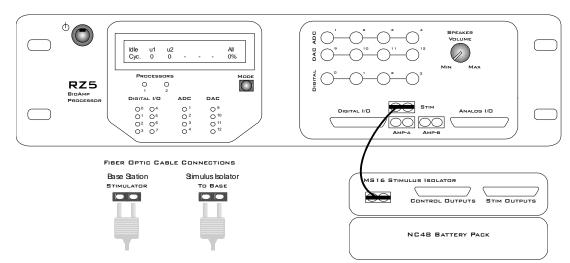

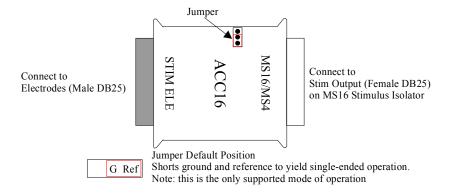

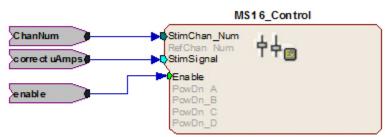

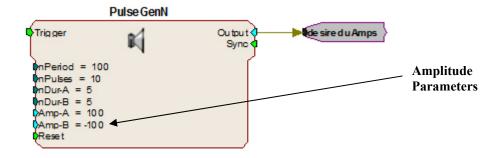

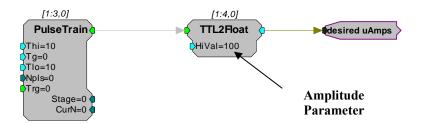

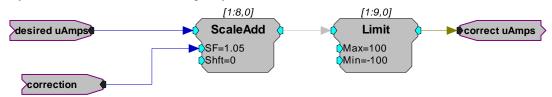

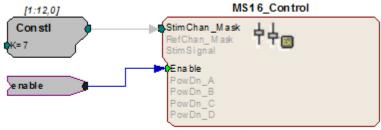

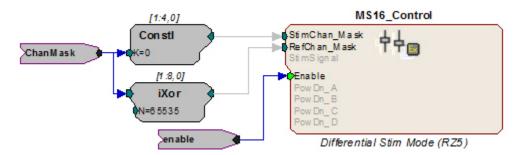

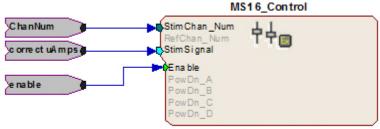

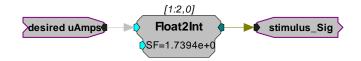

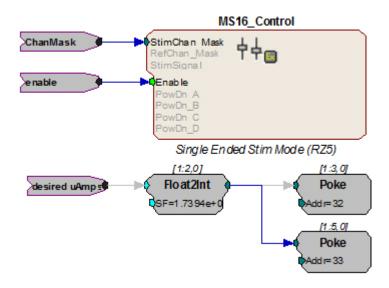

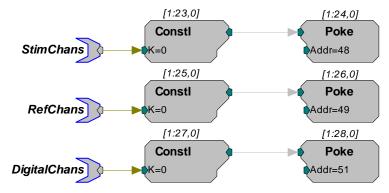

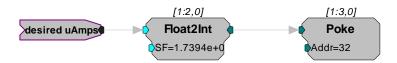

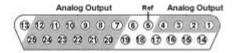

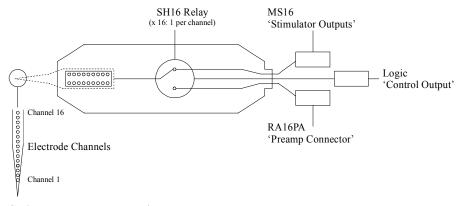

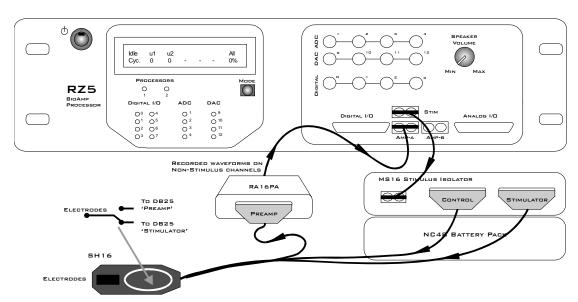

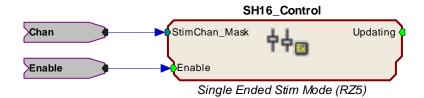

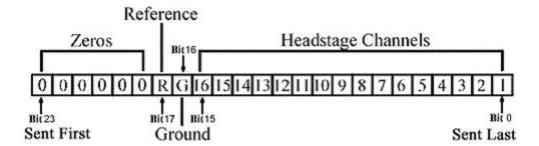

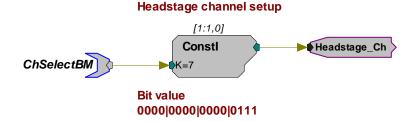

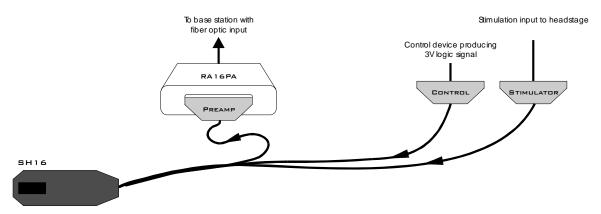

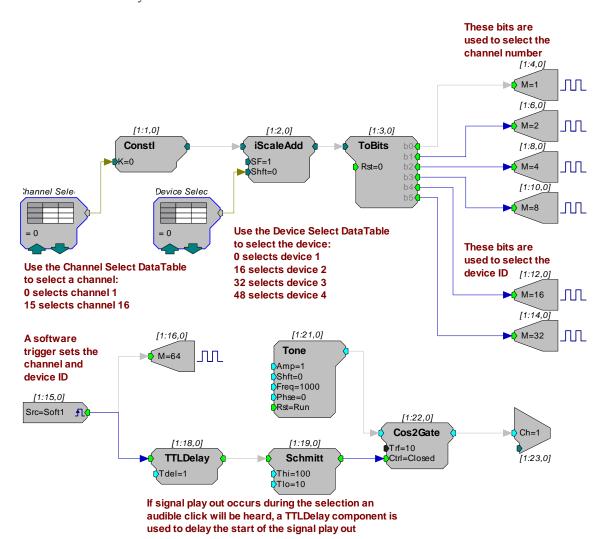

The RZ5 acquires and processes up to 32 channels of neurophysiological signals in real-time. Data can be input from two Medusa preamplifiers at a sampling rate of ~25 kHz. The RZ5 also supports microstimulation applications. The RZ5 can be used with one of TDT's stimulus isolators (MS16 or MS4) and switching headstage (SH16) to comprise a complete microstimulation system. For more information see *MS4/MS16 Stimulus Isolator*, page 7-3.

The RZ5 also features eight channels of analog I/O, 24 bits of digital I/O and an onboard monitor speaker with volume control.

#### **Power and Communication**

The RZ5's Optibit optical interface ensures fast and reliable data transfer from the RZ5 to the PC and is integrated into the device. Connectors are provided on the back panel and are color coded for correct wiring. The RZ5's power supply is also integrated into the device and is shipped from the factory configured for the desired voltage setting (110 V or 220V). If you need to change the voltage setting, please contact TDT support at 386.462.9622 or email support@tdt.com.

#### **Software Control**

Software control is implemented with circuit files developed using TDT's RP Visual Design Studio (RPvdsEx). Circuits are loaded to the processor through TDT run-time applications or custom applications. This manual includes device specific information needed during circuit design. For circuit design techniques and a complete reference of the RPvdsEx circuit components, see *MultiProcessor Circuit Design* and *Multi-Channel Circuit Design* in the *RPvdsEx Manual*.

## **RZ5 Architecture**

The RZ5 processor utilizes a multi-bus architecture and offers three dedicated, data buses for fast, efficient data handling. While the operation of the system architecture is largely transparent to the user, a general understanding is important when developing circuits in RPvdsEx.

As shown in the diagram above, the RZ5 architecture consists of three functional blocks:

The DSPs

Each DSP in the DSP Block is connected to 64 MB SDRAM and a local interface to the three data buses: two buses that connect each DSP to the other functional blocks and one that handles data transfer between the DSPs (as described further in Distributing Data Across DSPs below). This architecture facilitates fast DSP-to-off-chip data handling.

Because each DSP has its own associated memory, access is very fast and efficient. However, large and complex circuits should be designed to balance memory needs (such as data buffers and filter coefficients) across processors.

When designing circuits also note that the maximum number of components for each RZ5 DSP is 768.

The zBus Interface

The zBus Interface provides a connection to the PC. Data and host PC control commands are transferred to and from the DSP Block through the **zBus Interface Bus**, allowing for large high-speed data reads and writes without interfering with other system processing.

The I/O Interface

The I/O Interface serves as a connection to outside signal sources or output devices. It is used to input data from the preamplifier inputs and digital and analog channels. The I/O Interface Bus provides a direct connection to each DSP.

1-16 RZ Z-Series Processors

### **Distributing Data Across DSPs**

To reap the benefits of added power made possible by multi-DSP modules, processing tasks must be efficiently distributed across the available DSPs. That means transferring data across DSPs. The RZ5 architecture provides the zHop Bus for this type of data handling.

#### The zHop Bus

The zHop Bus allows the transfer of single or multi-channel signals between each DSP in the RZ5.

In RPvdsEx data is transferred across the zHop Bus using paired zHop Components, including zHopIn, zHopOut, MCzHopIn, MCzHopOut, and MCzHopPick. Up to 126 pairs can be used in a single RPvdsEx circuit.

#### **Bus Related Delays**

The zHop Bus introduces a single sample delay. However, this delay is taken care of for the user in OpenEx when Timing and Data Saving macros are used.

## **RZ5 Features**

### **DSP Status Displays**

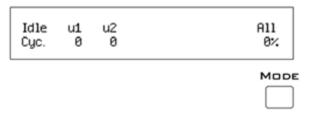

The RZ5 include status lights and a VFD (Vacuum Fluorescent Display) screen to report the status of the individual processors.

#### **Status Lights**

Two LEDs report the status of the multiprocessor's individual DSPs and will be lit solid green when the corresponding DSP is installed and running. The corresponding LED will be lit dim green if the cycle usage on a DSP is 0%. If the demands on a DSP exceed 99% of its capacity on any given cycle, the corresponding LED will flash red (~1 time per second).

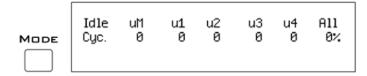

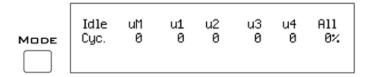

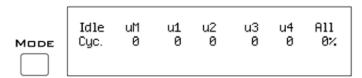

#### Front Panel VFD Screen

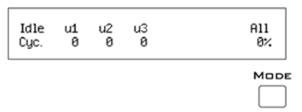

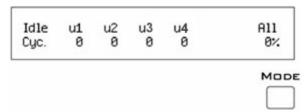

The front panel VFD screen reports detailed information about the status of the system. The display includes two lines. The top line reports the system mode, Run!, Idle, or Reset, and displays heading labels for the second line. The second line reports the user's choice of status indicators for each DSP followed by an aggregate value.

The user can cycle through the various status indicators using the Mode button to the bottom right of the display. Push and release the button to change the display or push and hold the button for one second then release to automatically cycle through each of the display options. The VFD screen may also report system status such as booting status (Reset).

**Note:** When burning new microcode or if the firmware on the RZ5 is blank, the VFD screen will report a cycle usage of 99% and the processor status lights will flash red.

#### **Status Indicators**

Cyc: cycle usage

**Bus%:** percentage of internal device's bus capacity used

I/O%: percentage of data transfer capacity used

**Opt:** Connection (sync) status of amplifiers A and B

**Important Note!:** The status lights flash when a DSP goes over the cycle usage limit, even if only for a particular cycle. This helps identify periodic overages caused by components in time slices.

### Amplifier and Onboard Analog I/O

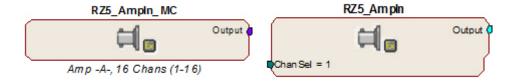

The RZ5 is equipped with both amplifier input and onboard analog I/O capabilities. The fiber optic ports allow a direct connection to Medusa Preamplifiers. Physiological signals are digitized on the preamplifier and transferred across noiseless fiber optics. The RZ5\_AmpIn\_MC and RZ5\_AmpIn macros automatically apply the necessary scale factors and channel offsets for configuring the preamplifier fiber optic ports.

The following table provides a quick overview of the amplifier and analog I/O features and how they must be accessed during circuit design. When the RZ5\_AmpIn\_MC and RZ5\_AmpIn macros are not used, reference the table and be sure to use the appropriate component, channel offset, scale factor and so forth. Also, see the *RPvdsEx Manual* for more information on circuit design.

1-18 RZ Z-Series Processors

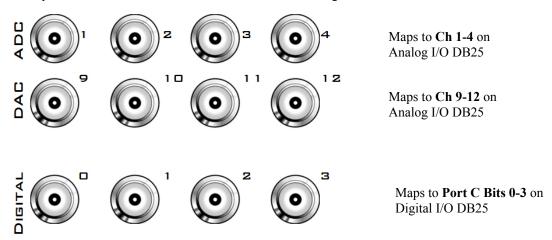

| Analog I/O       | Description            | Components | Channels | Notes                                                                           |

|------------------|------------------------|------------|----------|---------------------------------------------------------------------------------|

| ADC<br>Inputs    | Analog Input           | AdcIn      | 1 - 4    | Accessed through ADC Input<br>BNCs or Analog I/O labeled<br>DB25                |

| DAC<br>Outputs   | Analog Output          | DacOut     | 9 - 12   | Accessed through DAC Output<br>BNCs or Analog I/O labeled<br>DB25               |

| Optical<br>Amp-A | Medusa<br>PreAmp Input | AdcIn      | 17 - 32  | When the RZ5_AmpIn_MC or RZ5_AmpIn is NOT USED, apply a scale factor of .000833 |

| Optical<br>Amp-B | Medusa<br>PreAmp Input | AdcIn      | 33 - 48  | When the RZ5_AmpIn_MC or RZ5_AmpIn is NOT USED, apply a scale factor of .000833 |

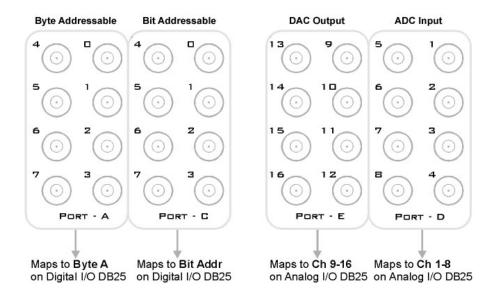

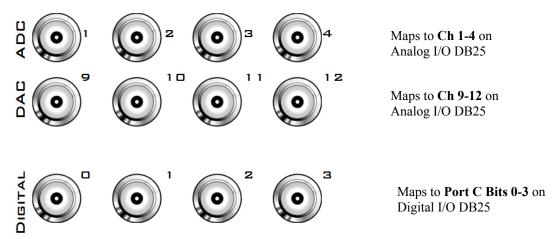

#### Onboard Analog I/O

The RZ5 is equipped with four channels of 16-bit PCM D/A and four channels of 16-bit PCM A/D. All 8 channels can be accessed via front panel BNCs marked ADC and DAC or via a 25-pin analog I/O connector. See RZ5 Technical Specifications, page 1-11 for the DB25 pinout.

#### **Fiber Optic Preamplifier Ports**

The RZ5 acquires digitized signals from a Medusa preamplifier over a fiber optic cable. This provides loss-less signal acquisition between the amplifier(s) and the base station. Two fiber optic ports are provided to support simultaneous acquisition from up to two preamplifiers. Each port can input up to 16 channels at a maximum sampling rate of ~25 kHz.

The fiber optic ports can be used with any of the Medusa preamplifiers including the RA16PA, RA4PA, or RA8GA. The channel numbers for each port begin at a fixed offset regardless of the number of channels available on the connected device.

#### Channels are numbered as follows:

Amp-A 17 - 32

Amp-B 33 - 48

**Note:** When using the RZ5\_AmpIn\_MC and RZ5\_AmpIn macros, the necessary scale factors and channel offsets for configuring the fiber optic ports are automatically applied.

#### Fiber Oversampling (acquisition only)

The fiber optic cable that carries the signals to the fiber optic input ports on the RZ5 has a transfer rate limitation of 6.25 Mbits/s. With 16 channels of data and 16 bits per sample, this limitation translates to a maximum sampling rate of  $\sim$ 25 kHz.

However, the need may arise to run a circuit at a higher sampling rate while still acquiring data via a fiber optic port. The two fiber optic ports on the RZ5 can oversample the digitized signals that have already been sampled up to 2X or  $\sim 50$  kHz. This will allow the RZ5 to run a DSP chain at  $\sim 50$  kHz and still sample data acquired through an optically connected preamplifier that digitized the incoming data stream at its maximum rate of  $\sim 25$  kHz.

Oversampling is performed on the base station. The signals being acquired will still be sampled at  $\sim$ 25 kHz on the preamplifier. This means that, even with oversampling, signals acquired by an

optically connected preamplifier are still governed by the bandwidth and frequency response of the preamplifier.

### Fiber Optic Output (Stimulator) Port

The output port, labeled Stimulator, can be used to transfer microstimulation waveforms to the Stimulus Isolator and/or to control its digital output.

**Important Note:** This fiber optic port is disabled if the sampling rate of the system is set to a value greater than  $\sim$ 25 kHz.

#### **Monitor Speaker**

The RZ5 is equipped with an onboard speaker. To use the speaker feed the desired signal to output channel 9 using a DacOut component. The speaker is provided primarily for audio monitoring of a single channel of electrophysiological potentials during recording.

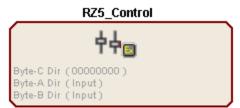

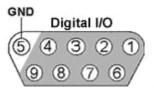

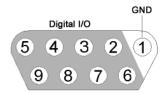

#### Digital I/O

24 bits of programmable digital I/O is divided into three bytes (A, B, and C) as described in the chart below. All digital I/O lines are accessed via the 25-pin connector on the front of the RZ5 and bits 0 - 3 of byte C are available through BNC connectors on the front panel labeled Digital. See RZ5 Technical Specifications, page 1-11, for the DB25 pinout and BNC channel mapping.

See the Digital I/O Circuit Design section of the RPvdsEx Manual for more information on programming the digital I/O.

| Digital I/O | Description | DB25 | BNCs | Notes            |

|-------------|-------------|------|------|------------------|

| Byte A      | bits 0 - 7  | Yes  | No   | byte addressable |

| Byte B      | bits 0 - 7  | Yes  | No   | byte addressable |

| Byte C      | bits 0 – 7  | Yes  | Yes* | bit addressable  |

\*Note: Byte C Bits 0 - 3 are available via front panel BNCs

## Configuration

**Note:** For more information on addressing and Digital I/O see the *RPvdsEx Manual*.

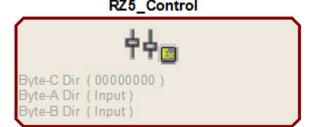

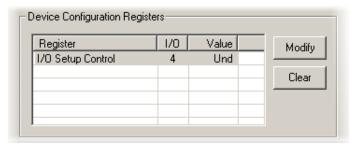

The data direction for the digital I/O is configured using the RZ5\_Control macro in RPvdsEx. Double-click the macro to access the settings on the Digital I/O tab. The RZ5\_Control macro also offers a Direction Control Mode parameter that enables the macro inputs and allows the user to control data direction dynamically. For more information on using the RZ5\_Control macro see the help provided in the macro's properties dialog box.

1-20 RZ Z-Series Processors

**Note:** By default, all digital I/O are configured as inputs.

The RZ digital I/O ports have different voltage outputs and logic thresholds depending on the type. Below is a table depicting the different voltage outputs and thresholds for both types.

| Digital I/O      | Voltage Output |           | Voltage Input |            |

|------------------|----------------|-----------|---------------|------------|

| Туре             | logic high     | logic low | logic high    | logic low  |

| byte addressable | 5 V            | 0 V       | ≥ 2.5 V       | 0 - 2.45 V |

| bit addressable  | 3.3 V          | 0 V       | ≥ 1.5 V       | 0 - 1.4 V  |

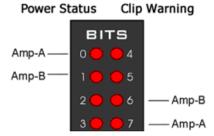

#### **LED Indicators**

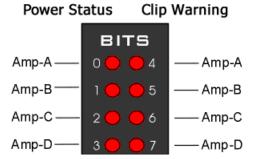

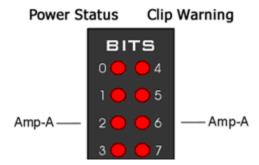

The RZ5 contains 16 LED indicators for the analog and digital I/O. These indicators are located directly below the VFD and DSP status LEDs and display information relative to the various analog and digital I/O contained on the RZ5. The following tables illustrate the possible display options and their associated descriptions.

#### Digital I/O - Byte C

8-bit, bit addressable byte C LED indicators are located to the bottom left of the RZ5 front panel.

| Light Pattern | Description                                                      |

|---------------|------------------------------------------------------------------|

| Dim Green     | Bit is configured for output and is currently a logical low (0)  |

| Solid Green   | Bit is configured for output and is currently a logical high (1) |

| Dim Red       | Bit is configured for input and is currently a logical low (0)   |

| Solid Red     | Bit is configured for input and is currently a logical high (1)  |

#### Analog I/O - ADC Inputs and DAC Outputs

ADC and DAC LED indicators are labeled and located to the right of the byte C LED indicators.

| Light Pattern | Description                                                   |

|---------------|---------------------------------------------------------------|

| Off           | Analog I/O channel signal voltage is less than +/-100 mV      |

| Dim Green     | Analog I/O channel signal voltage is less than +/-5 V         |

| Solid Green   | Analog I/O channel signal voltage is between +/-5 V to +/-9 V |

| Solid Red     | Analog I/O channel clip warning (voltage greater than +/-9 V) |

## **UDP Ethernet Interface (Optional)**

The RZ UDP Ethernet interface is designed to transfer data to or from a PC. RZ devices equipped with a UDP interface contain an additional port located on the back panel. See *UDP User Interface*, *page 1-49*, for more information.

#### Specialized DSP/Optical Interface Boards (Optional)

The RZ Standard DSP Boards can be replaced with specialized DSP Boards which include an optical interface for communication and control of RZ compatible devices, such as the IZ2 Stimulator and RV2 Video Processor. RZ devices equipped with one or more specialized DSP boards include an optical port for each card. The ports are located on the back panel and labeled for easy identification.

#### **RZDSP-I**

This board supports the IZ2 Stimulator, allowing the RZ device to function as a controller or base station. See the IZ2 Stimulator section, page 7-23, for more information on using and designing circuits for the stimulator.

#### **RZDSP-P**

This board supports PZ amplifier input, providing an alternate method for acquiring data from a PZ amplifier. It can be used to expand the number of channels that can be acquired on any RZ processor. Access to this input can be enabled in the PZ control macro.

#### **RZDSP-V**

This board supports the RV2 Video Tracking System, allowing the RZ device to function as a controller or base station. See the RV2 Video Processor section, page 8-1, for more information on using and designing circuits for the RV2.

1-22 RZ Z-Series Processors

## **Technical Specifications**

Specifications for the RZ5 BioAmp Processor.

**Note**: Technical Specifications for amplifier A/D converters are found under the preamplifier's technical specifications.

| DSP                   | 400 MHz DSPs, 2.4 GFLOPS peak per DSP<br>One or Two     |  |

|-----------------------|---------------------------------------------------------|--|

| Memory                | 64 MB SDRAM per DSP                                     |  |

| D/A                   | 4 channels, 16-bit PCM                                  |  |

| Sample Rate           | Up to 48828.125 Hz*                                     |  |

| Frequency Response    | DC-Nyquist (~1/2 sample rate)                           |  |

| Voltage Out           | +/- 10.0 Volts                                          |  |

| S/N (typical)         | 82 dB (20 Hz - 20 kHz at 9.9 V)                         |  |

| A/D                   | 4 channels, 16-bit PCM                                  |  |

| Sample Rate           | Up to 48828.125 Hz *                                    |  |

| Frequency Response    | DC - 7.5 kHz (3 dB corner, 2nd order, 12 dB per octave) |  |

| Voltage In            | +/- 10.0 Volts                                          |  |

| S/N (typical)         | 82 dB (20 Hz - 20 kHz at 9.9 V)                         |  |

| Fiber Optic Ports     |                                                         |  |

| Stimulator (MS16)     | One output for MS16 Stimulus Isolator*                  |  |

| Preamplifier (Medusa) | Two 16-channel inputs                                   |  |

| Digital I/O           | 24 bits programmable                                    |  |

• Note: When used with the Stimulus Isolator, the sampling rate is limited to 24.414 kHz.

## **BNC Channel Mapping**

Please note channel numbering begins at the top left block of BNCs for both analog and digital I/O and is printed on the face of the device to minimize miswiring.

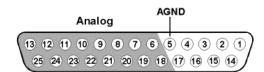

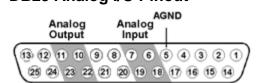

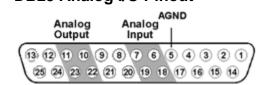

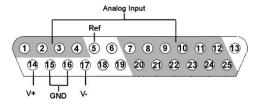

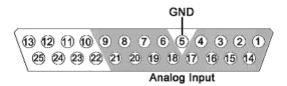

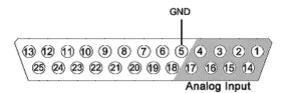

## **DB25 Analog I/O Pinout**

| Pin | Name | Description            |

|-----|------|------------------------|

| 1   | NA   | Not Used               |

| 2   |      |                        |

| 3   |      |                        |

| 4   |      |                        |

| 5   | AGND | Analog Ground          |

| 6   | A2   | ADC Analog Input       |

| 7   | A4   | Channels (ADC Inputs)  |

| 8   | NA   | Not Used               |

| 9   |      |                        |

| 10  | A10  | DAC Analog Output      |

| 11  | A12  | Channels (DAC Outputs) |

| 12  | NA   | Not Used               |

| 13  |      |                        |

| Pin | Name | Description            |

|-----|------|------------------------|

| 14  | NA   | Not Used               |

| 15  |      |                        |

| 16  |      |                        |

| 17  |      |                        |

| 18  | A1   | ADC Analog Input       |

| 19  | A3   | Channels (ADC Inputs)  |

| 20  | NA   | Not Used               |

| 21  |      |                        |

| 22  | A9   | DAC Analog Output      |

| 23  | A11  | Channels (DAC Outputs) |

| 24  | NA   | Not Used               |

| 25  |      |                        |

1-24 RZ Z-Series Processors

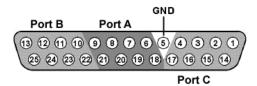

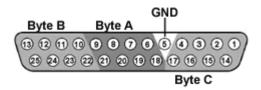

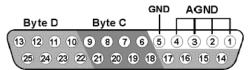

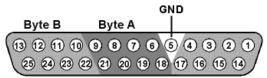

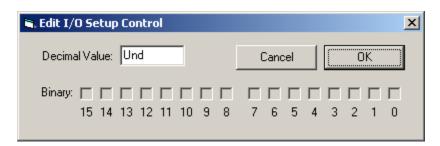

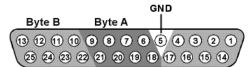

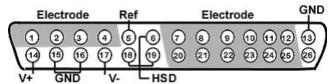

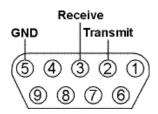

## **DB25 Digital I/O Pinout**

| Pin | Name | Description                     |

|-----|------|---------------------------------|

| 1   | C0   | Byte C                          |

| 2   | C2   | Bit Addressable<br>digital I/O  |

| 3   | C4   | Bits 0, 2, 4, and 6             |

| 4   | C6   |                                 |

| 5   | GND  | Digital I/O Ground              |

| 6   | A1   | Byte A                          |

| 7   | A3   | Word addressable<br>digital I/O |

| 8   | A5   | Bits 1, 3, 5, and 7             |

| 9   | A7   |                                 |

| 10  | В1   | Duto D                          |

| 11  | В3   | Byte B<br>Word addressable      |

| 12  | B5   | digital I/O                     |

| 13  | В7   | Bits 1, 3, 5, and 7             |

| Pin | Name | Description                     |

|-----|------|---------------------------------|

| 14  | C1   | Byte C                          |

| 15  | C3   | Bit Addressable<br>digital I/O  |

| 16  | C5   | Bits 1, 3, 5, and 7             |

| 17  | C7   |                                 |

| 18  | A0   | Byte A                          |

| 19  | A2   | Word addressable<br>digital I/O |

| 20  | A4   | Bits 0, 2, 4, and 6             |

| 21  | A6   |                                 |

| 22  | В0   | Byte B                          |

| 23  | B2   | Word addressable<br>digital I/O |

| 24  | B4   | Bits 0, 2, 4, and 6             |

| 25  | В6   |                                 |

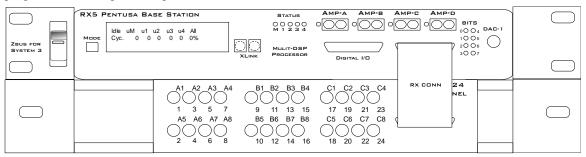

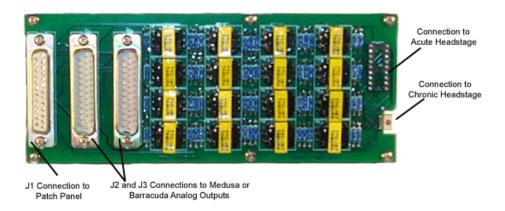

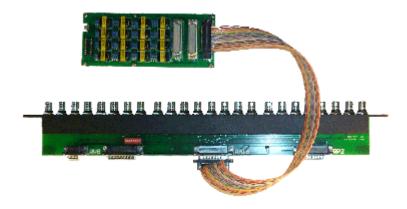

## **RZ5D BioAmp Processor**

## **Overview**

The RZ5D BioAmp Processor is available with either three or four 400 MHz Sharc digital signal processors networked on a multiprocessor architecture that features efficient onboard communication and memory access. The RZ5D is a versatile solution for real-time processing and simultaneous acquisition and stimulation.

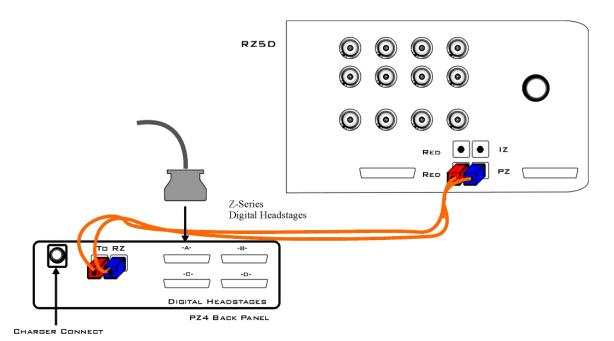

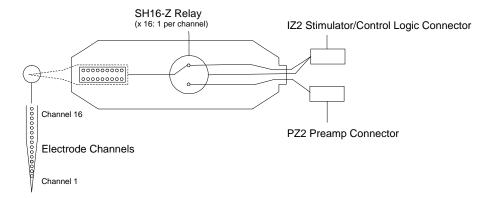

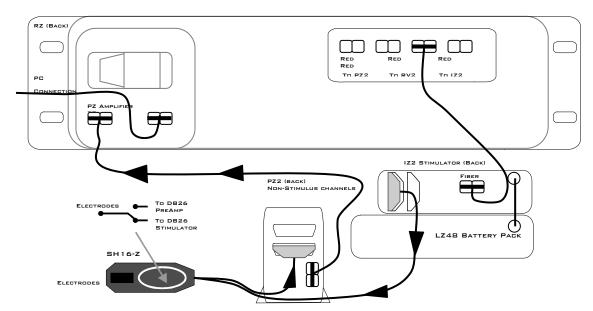

The RZ5D acquires and processes up to 32 channels of neurophysiological signals in real-time. Data can be input from a PZ amplifier or digital headstage manifold at a sampling rate of up to ~50 kHz. The RZ5D also supports microstimulation applications. The RZ5D can be used with TDT's IZ2 stimulus isolator for up to 128 channels of stimulation and switching headstages (SH16-Z) to comprise a complete microstimulation system. For more information see *IZ2 Stimulator*, page 7-23.

The RZ5D also features eight channels of analog I/O, 24 bits of digital I/O and an onboard monitor speaker with volume control.

#### **Power and Communication**

The RZ5D's integrated Optibit optical interface ensures fast and reliable data transfer from the RZ5D to the PC. Connectors are provided on the back panel and are color coded for correct wiring. The RZ5D's integrated power supply is shipped from the factory configured for the desired voltage setting (110 V or 220V). If you need to change the voltage setting, please contact TDT support at 386.462.9622 or email support@tdt.com.

#### Software Control

Software control is implemented with circuit files developed using TDT's RP Visual Design Studio (RPvdsEx). Circuits are loaded to the processor through TDT run-time applications or custom applications. This manual includes device specific information needed during circuit design. For circuit design techniques and a complete reference of the RPvdsEx circuit components, see the *RPvdsEx Manual*.

1-26 RZ Z-Series Processors

## RZ5D Architecture

The RZ5D processor utilizes a multi-bus architecture and offers three dedicated, data buses for fast, efficient data handling. While the operation of the system architecture is largely transparent to the user, a general understanding is important when developing circuits in RPvdsEx.

As shown in the diagram above, the RZ5D architecture consists of three functional blocks:

The DSPs

Each DSP in the DSP Block is connected to 64 MB SDRAM and a local interface to the three data buses: two buses that connect each DSP to the other functional blocks and one that handles data transfer between the DSPs (as described further in Distributing Data Across DSPs below). This architecture facilitates fast DSP-to-off-chip data handling.

Because each DSP has its own associated memory, access is very fast and efficient. However, large and complex circuits should be designed to balance memory needs (such as data buffers and filter coefficients) across processors.

When designing circuits also note that the maximum number of components for each RZ5D DSP is 768.

DSP-2 and DSP-3 are special optical DSPs. These DSPs have a direct fiber optic connection to the IZ and PZ interface port, respectively.

The zBus Interface

The zBus Interface provides a connection to the PC. Data and host PC control commands are transferred to and from the DSP Block through the **zBus Interface Bus**, allowing for large high-speed data reads and writes without interfering with other system processing.

The I/O Interface

The I/O Interface serves as a connection to outside signal sources or output devices. It is used to input data from the digital and analog

channels. The **I/O Interface Bus** provides a direct connection to each DSP.

#### **Distributing Data Across DSPs**

To reap the benefits of added power made possible by multi-DSP modules, processing tasks must be efficiently distributed across the available DSPs. That means transferring data across DSPs. The RZ5D architecture provides the zHop Bus for this type of data handling.

#### The zHop Bus

The zHop Bus allows the transfer of single or multi-channel signals between each DSP in the RZ5D.

In RPvdsEx data is transferred across the zHop Bus using paired zHop Components, including zHopIn, zHopOut, MCzHopIn, MCzHopOut, and MCzHopPick. Up to 126 pairs can be used in a single RPvdsEx circuit.

#### **Bus Related Delays**

The zHop Bus introduces a single sample delay. However, this delay is taken care of for the user in OpenEx when Timing and Data Saving macros are used.

## **RZ5D Features**

#### **DSP Status Displays**

The RZ5D include status lights and a VFD (Vacuum Fluorescent Display) screen to report the status of the individual processors.

##

Two LEDs report the status of the multiprocessor's individual DSPs and will be lit solid green when the corresponding DSP is installed and running. The corresponding LED will be lit dim green if the cycle usage on a DSP is 0%. If the demands on a DSP exceed 99% of its capacity on any given cycle, the corresponding LED will flash red (~1 time per second).

1-28 RZ Z-Series Processors

#### Front Panel VFD Screen

The front panel VFD screen reports detailed information about the status of the system. The display includes two lines. The top line reports the system mode (Run!, Idle, or Reset) and displays heading labels for each processor. The bottom line reports the current status indicator for each DSP followed by an aggregate value.

The user can cycle through the various status indicators using the Mode button to the bottom right of the display. Push and release the button to change the display or push and hold the button for one second then release to continuously cycle through each of the display options. The VFD screen may also report booting status (Reset).

**Note:** When burning new microcode or if the firmware on the RZ5D is blank, the VFD screen will report a cycle usage of 99% and the processor status lights will flash red.

#### **Status Indicators**

Cyc: cycle usage

**Bus%:** percentage of internal device's bus capacity used

I/O%: percentage of data transfer capacity used

**Important Note!:** The status lights flash when a DSP goes over the cycle usage limit, even if only for a particular cycle. This helps identify periodic overages caused by components in time slices.

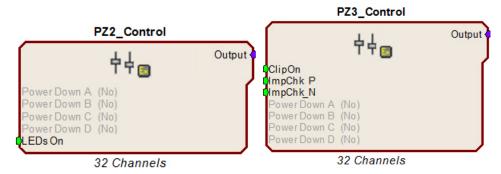

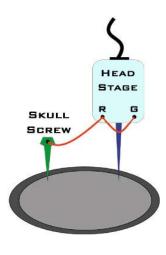

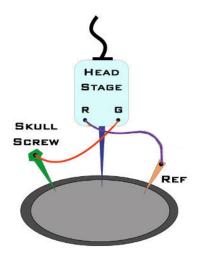

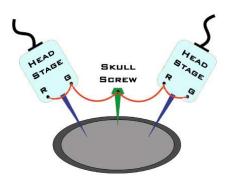

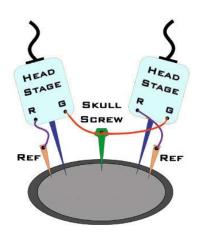

#### **PZ Preamplifier Port**

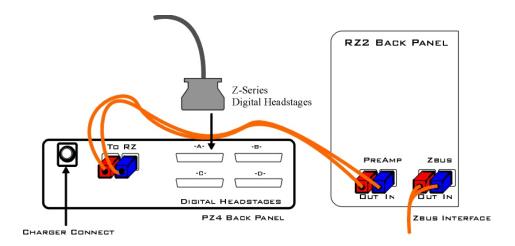

The RZ5D acquires digitized signals from a PZ preamplifier over a fiber optic cable through the port labeled 'PZ' on the front panel. This port can input up to 32 channels at a maximum sampling rate of ~50 kHz. The PZ port can be used with any of the PZ preamplifiers including the PZ2 and PZ3 or the PZ4 digital headstage manifold. The PZn\_Control macro is used to access neurophysiological data in the processing chain. **Important!:** The PZn\_Control macro must be placed on DSP-3 in the RPvdsEx circuit and must have the Direct Input option enabled. See the internal macro help for more details.

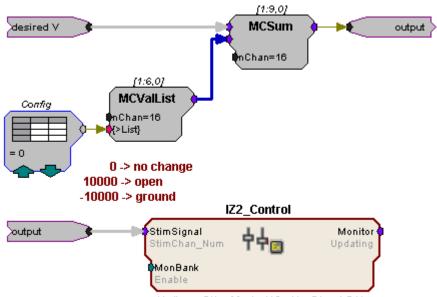

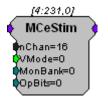

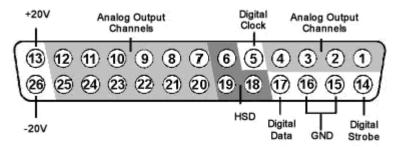

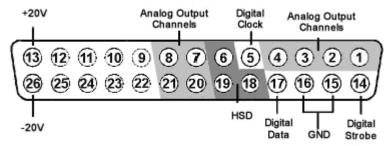

#### **IZ Stimulator Port**

The output port labeled IZ can be used to transfer microstimulation waveforms to the IZ2 Stimulator and/or to control an attached SH16-Z switching headstage. This port can output up to

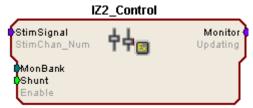

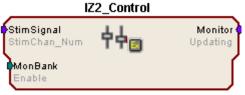

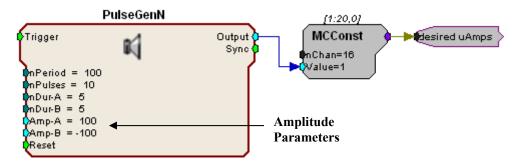

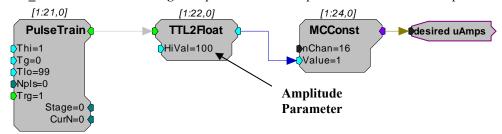

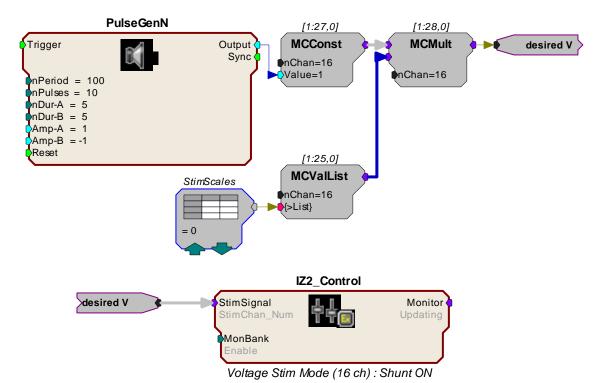

128 channels of stimulator at a maximum sampling rate of ~50 kHz. The IZ2\_Control macro is used to send stimulation waveforms, control an optional SH16-Z and receive monitor information from the IZ2.

**Important!:** The IZ2\_Control macro must be placed on DSP-2 in the RPvdsEx circuit. See the internal macro help for more details.

Voltage Stim Mode (32 ch)

#### Onboard Analog I/O

The RZ5D is equipped with four channels of 16-bit PCM D/A and four channels of 16-bit PCM A/D. All 8 channels can be accessed via front panel BNCs marked ADC and DAC or via a 25-pin analog I/O connector. See RZ5D Technical Specifications on page 1-33 for the DB25 pinout.

The following table provides a quick overview of the analog I/O features and how they must be accessed during circuit design. See the *RPvdsEx Manual* for more information on circuit design.

| Analog I/O     | Description   | Components | Channels | Notes                                                             |

|----------------|---------------|------------|----------|-------------------------------------------------------------------|

| ADC<br>Inputs  | Analog Input  | AdcIn      | 1 - 4    | Accessed through ADC Input<br>BNCs or Analog I/O labeled<br>DB25  |

| DAC<br>Outputs | Analog Output | DacOut     | 9 - 12   | Accessed through DAC Output<br>BNCs or Analog I/O labeled<br>DB25 |

#### **Monitor Speaker**

The RZ5D is equipped with an onboard speaker. To use the speaker, feed the desired signal to output channel 9 using a DacOut component. The speaker is provided primarily for audio monitoring of a single channel of electrophysiological potentials during recording.

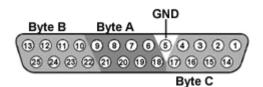

#### Digital I/O

The digital I/O includes 24 bits of programmable I/O. The digital I/O is divided into three bytes (A, B, and C) as described in the chart below. All digital I/O lines are accessed via the 25-pin connector on the front of the RZ5D and bits 0 - 3 of byte C are available through BNC connectors on the front panel labeled Digital. See *RZ5D Technical Specifications*, page 1-33, for the DB25 pinout and BNC channel mapping.

See the Digital I/O Circuit Design section of the RPvdsEx Manual for more information on programming the digital I/O.

1-30 RZ Z-Series Processors

| Digital I/O                                                 | Description | DB25 | BNCs | Notes            |  |  |

|-------------------------------------------------------------|-------------|------|------|------------------|--|--|

| Byte A                                                      | bits 0 - 7  | Yes  | No   | byte addressable |  |  |

| Byte B                                                      | bits 0 - 7  | Yes  | No   | byte addressable |  |  |

| Byte C                                                      | bits 0 – 7  | Yes  | Yes* | bit addressable  |  |  |

| *Note: Byte C Bits 0 - 3 are available via front panel BNCs |             |      |      |                  |  |  |

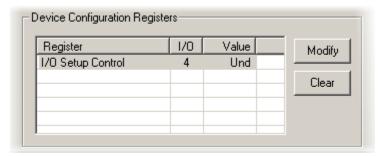

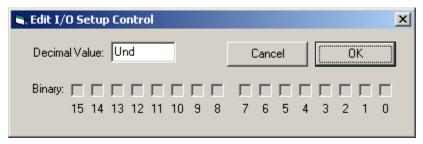

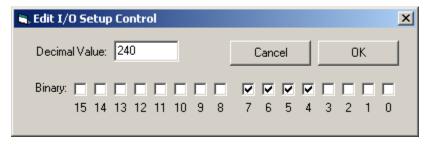

By default, all digital I/O are configured as inputs. The data direction for the digital I/O is configured using the RZ5\_Control macro in RPvdsEx. Double-click the macro to access the settings on the Digital I/O tab. The RZ5\_Control macro also offers a Direction Control Mode parameter that enables the macro inputs and allows the user to control data direction dynamically. For more information on using the RZ5\_Control macro see the help provided in the macro's properties dialog box.

The RZ5D digital I/O ports have different voltage outputs and logic thresholds depending on the type of I/O. The table below specifies the different voltage outputs and thresholds for both types.

| Digital I/O<br>Type | Voltage Output |           | Voltage Input |            |  |

|---------------------|----------------|-----------|---------------|------------|--|

|                     | logic high     | logic low | logic high    | logic low  |  |

| byte addressable    | 5 V            | 0 V       | ≥ 2.5 V       | 0 - 2.45 V |  |

| bit addressable     | 3.3 V          | 0 V       | ≥ 1.5 V       | 0 - 1.4 V  |  |

#### **LED Indicators**

The RZ5D has 16 LED indicators for the analog and digital I/O. These indicators are located directly below the VFD and DSP status LEDs. They display information about the state of the analog and digital I/O. The following tables illustrate the possible display options and their associated descriptions.

### Digital I/O

These LEDs indicate the state of the 8 bit-addressable I/O of byte C.

| Light Pattern | Description                                                      |

|---------------|------------------------------------------------------------------|

| Dim Green     | Bit is configured for output and is currently a logical low (0)  |

| Solid Green   | Bit is configured for output and is currently a logical high (1) |

| Dim Red       | Bit is configured for input and is currently a logical low (0)   |

| Solid Red     | Bit is configured for input and is currently a logical high (1)  |

### Analog I/O

These LEDs indicate the state of the four ADC and four DAC channels.

| Light Pattern | Description                                                   |

|---------------|---------------------------------------------------------------|

| Off           | Analog I/O channel signal voltage is less than +/-100 mV      |

| Dim Green     | Analog I/O channel signal voltage is less than +/-5 V         |

| Solid Green   | Analog I/O channel signal voltage is between +/-5 V to +/-9 V |

| Solid Red     | Analog I/O channel clip warning (voltage greater than +/-9 V) |

# **UDP Ethernet Interface (Optional)**

The RZ UDP Ethernet interface is designed to transfer data to or from a PC. RZ devices equipped with a UDP interface contain an additional port located on the back panel. See *UDP User Interface*, page 1-49, for more information.

1-32 RZ Z-Series Processors

# **Technical Specifications**

Specifications for the RZ5D BioAmp Processor.

**Note**: Technical Specifications for amplifier A/D converters are found under the preamplifier or digital headstage technical specifications.

| DSP                | 400 MHz DSPs, 2.4 GFLOPS peak per DSP<br>Three or Four  |  |

|--------------------|---------------------------------------------------------|--|

| Memory             | 64 MB SDRAM per DSP                                     |  |

| D/A                | 4 channels, 16-bit PCM                                  |  |

| Sample Rate        | Up to 48828.125 Hz*                                     |  |

| Frequency Response | DC-Nyquist (~1/2 sample rate)                           |  |

| Voltage Out        | +/- 10.0 Volts                                          |  |

| S/N (typical)      | 82 dB (20 Hz - 20 kHz at 9.9 V)                         |  |

| A/D                | 4 channels, 16-bit PCM                                  |  |

| Sample Rate        | Up to 48828.125 Hz *                                    |  |

| Frequency Response | DC - 7.5 kHz (3 dB corner, 2nd order, 12 dB per octave) |  |

| Voltage In         | +/- 10.0 Volts                                          |  |

| S/N (typical)      | 82 dB (20 Hz - 20 kHz at 9.9 V)                         |  |

| Fiber Optic Ports  |                                                         |  |

| 1Z                 | One output for IZ2, up to 128 channels                  |  |

| PZ                 | One input for PZ2, PZ3 or PZ4, up to 32 channels        |  |

| Digital I/O        | 24 bits programmable                                    |  |

## **BNC Channel Mapping**

Please note that channel numbering begins at the top left block of BNCs for both analog and digital I/O and is printed on the face of the device to avoid miswiring.

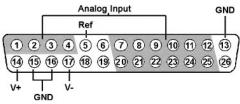

## **DB25 Analog I/O Pinout**

| Pin | Name | Description           |  |

|-----|------|-----------------------|--|

| 1   | NA   | Not Used              |  |

| 2   |      |                       |  |

| 3   |      |                       |  |

| 4   |      |                       |  |

| 5   | AGND | Analog Ground         |  |

| 6   | A2   | ADC Analog Input      |  |

| 7   | A4   | Channels (ADC Inputs) |  |

| 8   | NA   | Not Used              |  |

| 9   |      |                       |  |

| 10  | A10  | DAC Analog Output     |  |

| 11  | A12  | Channels (DAC Outputs |  |

| 12  | NA   | Not Used              |  |

| 13  |      |                       |  |

| Pin | Name | Description            |  |

|-----|------|------------------------|--|

| 14  | NA   | Not Used               |  |

| 15  |      |                        |  |

| 16  |      |                        |  |

| 17  |      |                        |  |

| 18  | A1   | ADC Analog Input       |  |

| 19  | A3   | Channels (ADC Inputs)  |  |

| 20  | NA   | Not Used               |  |

| 21  |      |                        |  |

| 22  | A9   | DAC Analog Output      |  |

| 23  | A11  | Channels (DAC Outputs) |  |

| 24  | NA   | Not Used               |  |

| 25  |      |                        |  |

1-34 RZ Z-Series Processors

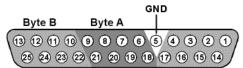

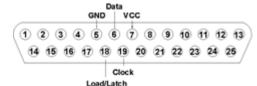

# **DB25 Digital I/O Pinout**

| Pin | Name | Description                     |

|-----|------|---------------------------------|

| 1   | C0   | Byte C                          |

| 2   | C2   | Bit Addressable<br>digital I/O  |

| 3   | C4   | Bits 0, 2, 4, and 6             |

| 4   | C6   |                                 |

| 5   | GND  | Digital I/O Ground              |

| 6   | A1   | Byte A                          |

| 7   | A3   | Word addressable<br>digital I/O |

| 8   | A5   | Bits 1, 3, 5, and 7             |

| 9   | A7   |                                 |

| 10  | B1   | Puta P                          |

| 11  | В3   | Byte B<br>Word addressable      |

| 12  | BO   | digital I/O                     |

| 13  | В7   | Bits 1, 3, 5, and 7             |

| Pin | Name | Description                     |

|-----|------|---------------------------------|

| 14  | C1   | Byte C                          |

| 15  | C3   | Bit Addressable<br>digital I/O  |

| 16  | C5   | Bits 1, 3, 5, and 7             |

| 17  | C7   |                                 |

| 18  | A0   | Byte A                          |

| 19  | A2   | Word addressable<br>digital I/O |

| 20  | A4   | Bits 0, 2, 4, and 6             |

| 21  | A6   |                                 |

| 22  | В0   | Byte B                          |

| 23  | B2   | Word addressable<br>digital I/O |

| 24  | B4   | Bits 0, 2, 4, and 6             |

| 25  | В6   |                                 |

# **RZ6 Multi I/O Processor**

# **Overview**

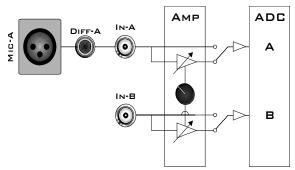

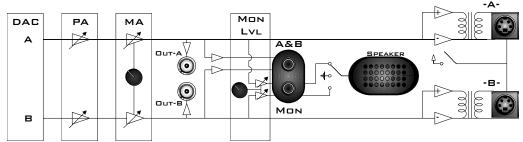

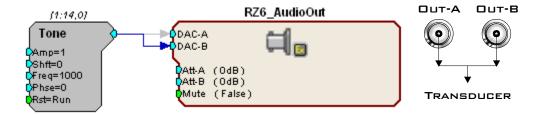

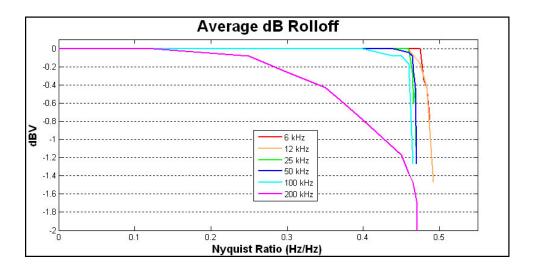

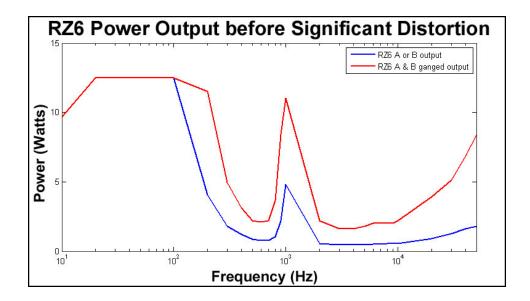

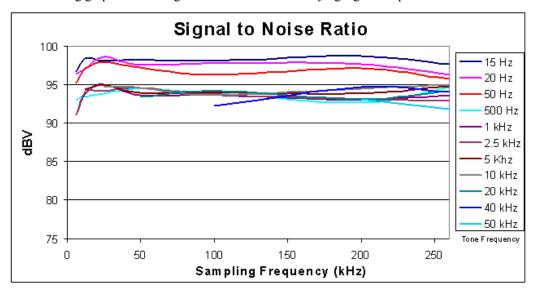

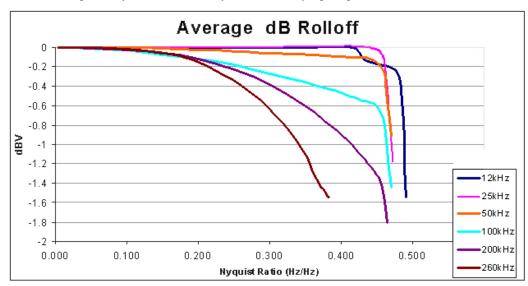

The RZ6 Multi I/O Processor is a high sample rate processor with flexible input/output capabilities. Up to four 400 MHz Sharc digital signal processors are networked in an optimized multiprocessor architecture that features efficient onboard communication and memory access. Two channels each of sigma-delta D/A and A/D converters provide a dynamic range of up to 115 dB and sampling rates up to  $\sim$ 200 kHz.

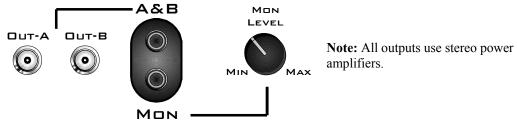

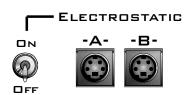

The single device form factor incorporates two channels of onboard programmable and manual attenuation and can drive headphones and standard, magnetic, or electrostatic speakers. It includes an onboard monitor speaker, two channels of amplification for analog inputs, and 24 channels of digital I/O. XLR, audio jack, and BNC connections are supported. Optionally, the RZ6 can be equipped with a fiber optic input, allowing it to support a four channel Medusa preamplifier.

The RZ6-A Base version starts with a single DSP and makes an excellent all-in-one psychoacoustics system or can be added to any system to add audio stimulus generation to experiments.

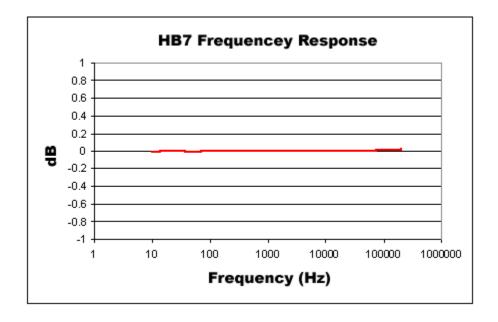

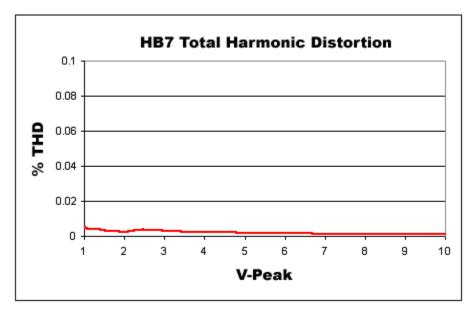

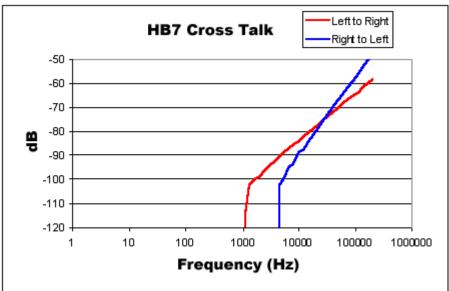

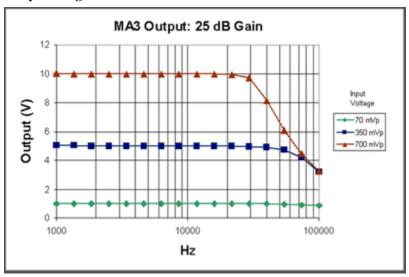

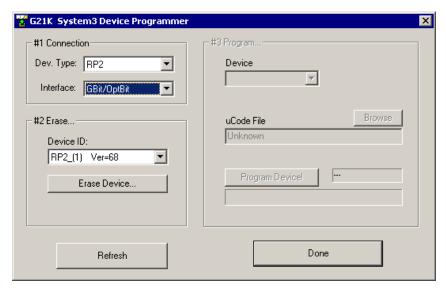

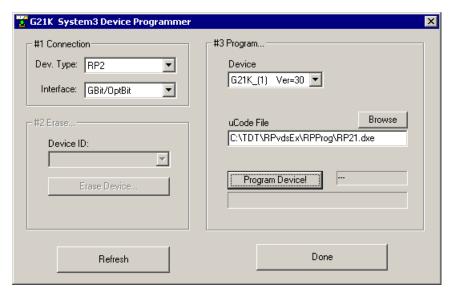

The RZ6-A-P1 comes equipped with three DSPs for more processing power and includes the optional fiber optic input port, allowing it to serve as a BioAmp base station for ABR and OAE studies.