# LatticeECP3 sysCONFIG Usage Guide

July 2013

Technical Note TN1169

## Introduction

Configuration is the process of loading or programming a design into volatile memory of an SRAM-based FPGA. This is accomplished via a bitstream file, representing the logical states, that is loaded into the FPGA internal configuration SRAM memory. The functional operation of the device after programming is determined by these internal configuration RAM settings. The SRAM cells must be loaded with configuration data each time the device powers up.

The configuration memory in LatticeECP3<sup>™</sup> FPGAs is built using volatile SRAM; therefore, an external non-volatile configuration memory is required to maintain the configuration data when the power is removed. This non-volatile memory supplies the configuration data to the LatticeECP3 when it powers up or anytime the device needs to be updated.

To support multiple configuration options the LatticeECP3 supports the Lattice sysCONFIG<sup>™</sup> interface as well as the dedicated JTAG port. The available configuration options, or modes, are listed in Table 15-1.

| Interface | Port                                       | Description                                                                         |

|-----------|--------------------------------------------|-------------------------------------------------------------------------------------|

|           | SPI                                        | Serial Peripheral Interface to single or multiple FPGA devices.                     |

|           | SPIm                                       | Serial Peripheral Interface to single Flash memory devices with partitioned memory. |

| sysCONFIG | SSPI                                       | Configure and readback by standard SPI Master driver or devices.                    |

|           | SCM                                        | Slave Serial Mode for daisy chain configuration.                                    |

|           | SPCM                                       | Slave 8-bit parallel CPU-like programming interface.                                |

| JTAG      | JTAG (IEEE 1149.1 and IEEE 1532 compliant) | Standard 4-pin JTAG interface.                                                      |

#### Table 15-1. Supported Configuration Modes

This technical note covers all of the configuration options available for LatticeECP3.

The LatticeECP3 configuration RAM can be loaded in a number of different modes. In these configuration modes, the FPGA can act as a master, a peripheral to a CPU, or a slave of other system devices. It also supports in-system configuration via the JTAG port.

The decision about which configuration mode to use is a system design concern. There are many methods for configuring the FPGA utilizing four basic schemes.

- **Master**: As a master, the FPGA is the source of the clock, and accesses an external PROM or EPROM storage device through a serial connection, with no additional timing or control signals used. This scheme includes Serial Programming Interface (SPI) that supports a seamless connection for programming using industry-standard external Flash-based memory devices.

- Slave: In slave mode the FPGA receives bit-serial or byte-wide data and a clock from an external data and timing source, either from a microprocessor, or from the lead device in an FPGA-daisy chain. As a slave device, the clock used to configure the FPGA is generated externally and provided to the CCLK input.

- **JTAG**: The device can be configured through the JTAG port. The JTAG port is always on and available regard-less of the configuration mode selected.

The system designer should determine the requirements for configuration very early in the design. Many factors must be considered when deciding which configuration mode is best suited for the design. The flexible features for configuration can provide a seamless design to the system.

<sup>© 2013</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## **General Configuration Flow**

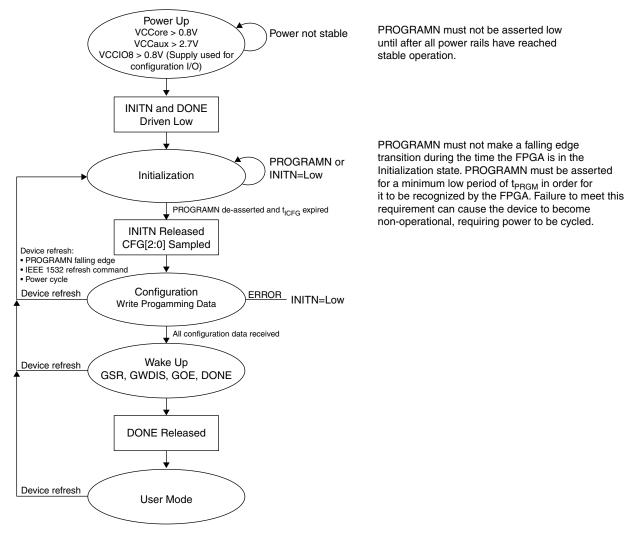

The LatticeECP3 enters Configuration mode when one of three things happens: power is applied to the device, the PROGRAMN pin is driven low, or a JTAG or SSPI Refresh instruction is issued. Upon entering Configuration mode the INITN pin and the DONE pin are driven low to indicate that the device is initializing (i.e. getting ready to receive configuration data).

Once initialization is complete, the INITN pin will be driven high. The low-to-high transition of the INITN pin causes the CFG pins to be sampled, telling the LatticeECP3 which port it will configure from. The LatticeECP3 then begins reading data from the selected port and starts looking for the preamble header (BDB3 hex for unencrypted bitstreams, and BFB3 for encrypted bitstreams). All data after the preamble is valid configuration data.

When the LatticeECP3 has finished reading all of the configuration data, and assuming there have been no errors, the DONE pin goes high and the LatticeECP3 enters user mode. In other words, the device begins to function according to your design.

Note that the LatticeECP3 may also be programmed via JTAG. When programming via JTAG, the INITN and DONE signals have no meaning, because JTAG, per the IEEE standard, takes complete control of all device I/Os. It is recommended that the PROGRAMN input be held high when using the JTAG port to configure the FPGA. This prevents the FPGA SRAM memory from being cleared when the JTAG programming cycle is complete.

The following sections define each configuration pin, each configuration mode, and all of the configuration options for the LatticeECP3.

# **Configuration Pins**

The LatticeECP3 supports two types of configuration pins, dedicated and dual-purpose. The dedicated pins are used exclusively for configuration; the dual-purpose pins, when configuration is complete, are available as extra I/O pins. If a dual-purpose pin is to be used both for configuration and as a general purpose I/O (GPIO) the following conditions must be met:

- The I/O type must remain the same. For example, if the pin is a 3.3V CMOS pin (LVCMOS33) during configuration, it must remain a 3.3V CMOS pin as a GPIO.

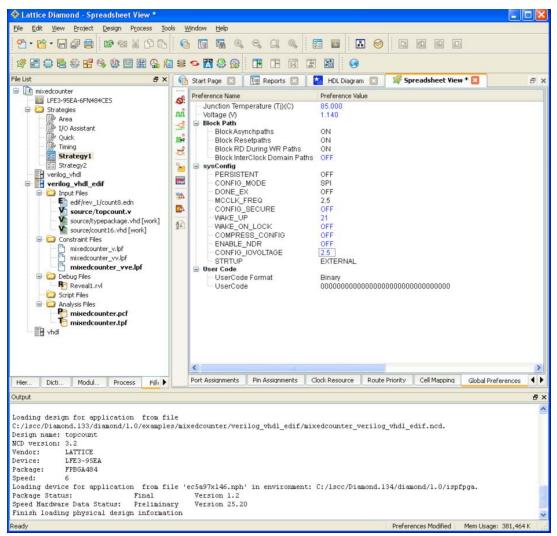

- You must select the correct CONFIG\_MODE setting and set the PERSISTENT attribute to OFF. Doing so permits the dual-purpose sysCONFIG pins to be used as GPIO when configuration completes. These settings can be found in the ispLEVER<sup>®</sup> Design Planner or Spreadsheet View in Lattice Diamond<sup>™</sup> design software. See Table 15-3 for more information.

- You are responsible for insuring that no internal or external logic will interfere with the control signals required by configuration mode you have selected.

The dual-purpose configuration pins are controlled using HDL source file attributes, or with the ispLEVER or Diamond Preference Editor. You can read about how to apply HDL preferences in TN1177, <u>LatticeECP3 sysIO Usage</u> <u>Guide</u>.

The LatticeECP3 also supports JTAG for configuration, transparent read back, and JTAG testing. The following sections describe the function of the various sysCONFIG and JTAG pins. Table 15-2 is provided for reference.

#### Table 15-2. LatticeECP3 Configuration Pins

|                          |                                        |              | Configuration Mode |              |                    |                  |                   |      |

|--------------------------|----------------------------------------|--------------|--------------------|--------------|--------------------|------------------|-------------------|------|

| Pin Name                 | I/О Туре                               | Pin Type     | SPI                | SPIm         | SSPI <sup>1</sup>  | SCM <sup>1</sup> | SPCM <sup>1</sup> | JTAG |

| CFG[2:0]                 | Input, weak pull-up                    | Dedicated    | =000               | =010         | =001               | =101             | =111              |      |

| PROGRAMN                 | Input, weak pull-up                    | Dedicated    |                    |              | ALL                |                  |                   |      |

| INITN                    | Bi-directional open drain <sup>5</sup> | Dedicated    |                    |              | ALL                |                  |                   |      |

| DONE                     | Bi-directional open drain <sup>5</sup> | Dedicated    |                    |              | ALL                |                  |                   |      |

| CCLK                     | Input                                  | Dedicated    | Slave mo           | ode, determi | ned by the         | CFG0 s           | etting =1         |      |

| MCLK                     | Bi-directional, weak pull-up           | Dual-Purpose | Master m           | ode, determ  | ined by the        | e CFG0 s         | setting =0        |      |

| D0/SPIFASTN <sup>2</sup> | Bi-directional <sup>2</sup>            | Dual-Purpose | SPIFASTN           | SPIFASTN     |                    |                  | D0                |      |

| D1 <sup>2, 3</sup>       | Bi-directional <sup>2</sup>            | Dual-Purpose |                    |              |                    |                  | D1                |      |

| D2 <sup>2, 3</sup>       | Bi-Directional <sup>2</sup>            | Dual-Purpose |                    |              |                    |                  | D2                |      |

| D3/SI <sup>2, 3</sup>    | Bi-directional <sup>2</sup>            | Dual-Purpose |                    |              | SI                 |                  | D3                |      |

| D4/SO <sup>2, 3</sup>    | Bi-directional <sup>2</sup>            | Dual-Purpose |                    |              | SO                 |                  | D4                |      |

| D5 <sup>2</sup>          | Bi-directional <sup>2</sup>            | Dual-Purpose |                    |              |                    |                  | D5                |      |

| D6 <sup>2, 3</sup>       | Bi-directional <sup>2</sup>            | Dual-Purpose |                    |              |                    |                  | D6                |      |

| D7/SPID0 <sup>2, 3</sup> | Bi-directional <sup>2</sup>            | Dual-Purpose | SPID0              | SPID0        | Note 4             |                  | D7                |      |

| CSN/SN                   | Bi-directional, weak pull-up           | Dual-Purpose |                    |              | SN                 |                  | CSN               |      |

| CS1N/HOLDN               | Bi-directional, weak pull-up           | Dual-Purpose |                    |              | HOLDN <sup>3</sup> |                  | CS1N              |      |

| WRITEN                   | Active low control input pin           | Dual-Purpose |                    |              |                    |                  | WRITEN            |      |

| BUSY/SISPI               | Bi-directional, weak pull-up           | Dual-Purpose | SISPI              | SSIPI        | Note 4             |                  | BUSY              |      |

| DI/CSSPI0N               | Bi-directional, weak pull-up6          | Dual-Purpose | CSSPION            | CSSPION      | Note 4             | DI               |                   |      |

| DOUT/CSON                | Bi-directional, weak pull-up           | Dual-Purpose | DOUT               |              | DOUT               | DOUT             | DOUT/<br>CSON     |      |

1. SSPI = Slave SPI, SCM = Serial Configuration Mode, SPCM = Slave Parallel Configuration Mode.

2. D[0:7] pins have no pull-up during power-up and configuration in all programming modes. This allows you to use large pull-up or pulldown resistors to pre-set those pins to a certain state while powering up your systems.

3. Weak pull-ups consist of a current source of 30µA to 150µA. The pull-ups for sysCONFIG dedicated and dual-purpose pins track VCCIO8. The pull-ups for TDI, TDO, and TMS track VCCJ.

4. This pin is used for programming the SPI Flash boot PROM.

5. Optional weak pull-up resistor available.

6. Requires external pull-up to VCCIO8.

# **Configuration Process and Flow**

Prior to becoming operational, the FPGA goes through a sequence of states, including initialization, configuration and wake-up.

#### Figure 15-1. Configuration Flow

## **Power-up Sequence**

In order for the LatticeECP3 to operate, power must be applied to the device. During a short period of time, as the voltages applied to the system rise, the FPGA will have an indeterminate state. Other devices in the system will also be in an indeterminate state.

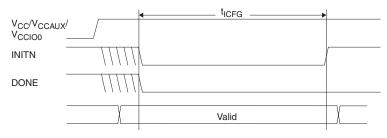

As power continues to ramp, a Power On Reset (POR) circuit inside the FPGA becomes active. The POR circuit, once active, makes sure the external I/O pins are in a high-impedance state. It also monitors the  $V_{CCcore}$ ,  $V_{CCaux}$ , and the  $V_{CCIO8}$  input rails. The POR circuit waits for the following conditions:

- V<sub>CCcore</sub> > 0.8V

- V<sub>CCaux</sub> > 2.7V

- V<sub>CCIO8</sub> > 0.8V (Supply used for configuration I/O)

When these conditions are met the POR circuit releases an internal reset strobe, allowing the device to begin its initialization process. The FPGA samples the CFG[2:0] input pins to determine if a master or a slave mode configuration is selected. The FPGA uses this information to determine the  $t_{ICFG}$  initialization period. The next step is to assert INITN active low, and to drive DONE low. When INITN and DONE are asserted low the device moves to the initialization state, as shown in Figure 15-1.

The PROGRAMN input must not be asserted low as power is applied to the FPGA. Nor should it be allowed to transition from high to low at any time that INITN is in the initialization state.

#### Figure 15-2. Configuration from Power-On-Reset Timing

### Initialization

The LatticeECP3 enters the memory initialization phase immediately after the Power On Reset circuit drives the INITN and DONE status pins low. The purpose of the initialization state is to clear all of the SRAM memory inside the FPGA.

The FPGA remains in the initialization state until all of the following conditions are met:

- The t<sub>ICFG</sub> time period has elapsed

- The PROGRAMN pin is deasserted

- The INITN pin is no longer asserted low by an external master

The dedicated INITN pin provides two functions during the initialization phase. The first is to indicate the FPGA is currently clearing its configuration SRAM. The second is to act as an input preventing the transition from the initialization state to the configuration state.

During the  $t_{ICFG}$  time period the FPGA is clearing the configuration SRAM. When the LatticeECP3 is part of a chain of devices each device will have different  $t_{ICFG}$  initialization times. The FPGA with the slowest  $t_{ICFG}$  parameter can prevent other devices in the chain from starting to configure. Premature release of the INITN in a multi-device chain may cause configuration of one or more chained devices to fail to configure intermittently.

The active-low, open-drain initialization signal INITN must be pulled high by an external resistor when initialization is complete. To synchronize the configuration of multiple FPGAs, one or more INITN pins should be wire-ANDed. If one or more FPGAs or an external device holds INITN low, the FPGA remains in the initialization state.

## Loading the Configuration Memory

The rising edge of the INITN pin causes the FPGA to enter the configuration state. The FPGA is able to accept the configuration bitstream created by the ispLEVER and Diamond development tools.

If the FPGA CFG[2:0] input pins have placed it in a master configuration mode it will begin fetching data from an external non-volatile memory.

If the FPGA CFG[2:0] input pins have placed it in a slave configuration mode, the FPGA waits for configuration data to be presented to it on each CCLK rising edge.

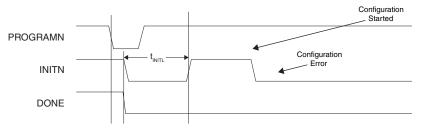

During the time the FPGA receives its configuration data the INITN control pin takes on its final function. INITN is used to indicate an error exists in the configuration data. When INITN is active high configuration is proceeding without issue. If INITN is asserted low, an error has occurred and the FPGA will not operate.

### Wake-up

Wake-up is the transition from configuration mode to functional mode. Wake-up starts when the device has correctly received all of its configuration data. When all configuration data is received, the FPGA asserts an internal DONE strobe. The assertion of the internal DONE causes a Wake Up state machine to run that sequences four controls. The four control strobes are:

- External DONE

- Global Write Disable (GWDISn)

- Global Output Enable (GOE)

- Global Set/Reset (GSR)

External DONE is a bi-directional, open-drain I/O. The FPGA releases the open-drain DONE pin at the programmed wake-up phase. If an external agent is holding the external DONE pin low, the wake-up process of the LatticeECP3 does not proceed. Only after the external DONE is active high do the final wake-up phases complete. Once the final wake-up phases are complete, the FPGA enters user mode.

The Global Output Enable, when it is asserted, permits the FPGA's I/O to exit a high-impedance state and take on their programmed output function. The FPGA inputs are always active. However, they are typically prevented from performing any action on the FPGA logic by the assertion of the Global Set/Reset (GSR).

The Global Set/Reset is an internal strobe that, when asserted, causes all I/O/LUT flip-flops, distributed RAM output flip-flops, and Embedded Block RAM output flip-flops that have the GSR enabled attribute to be set/cleared per their HDL definition.

The Global Write Disable is a control that overrides the write enable strobe for all RAM logic inside the FPGA. The inputs on the FPGA are always active, as mentioned in the Global Output Enable section. Keeping GWDIS asserted prevents accidental corruption of the instantiated RAM resources inside the FPGA.

## **Clearing the Configuration Memory and Re-initialization**

Several methods are available to clear the internal configuration memory of the LatticeECP3 device. The first is mentioned earlier when the device powers up (see the "Power-up Sequence" section of this document). A second method is to toggle the PROGRAMN pin. Also, JTAG can reinitialize the memory through an ISC Refresh command. SSPI can also initiate a reconfiguration with the Refresh command.

The other methods available are:

- Assertion of the PROGRAMn dedicated input

- Sending the ISC Refresh command using a configuration port (JTAG, or Slave SPI)

Invoking one of these methods causes the LatticeECP3 to drive INITN and DONE low. The FPGA enters the initialization state described above.

## **Reconfiguration Priority**

There are many sources that can initiate a reconfiguration while a configuration is already in process. There is a priority as to which of these sources can interrupt the configuration process depending on which of the sources initiated the original configuration. Note that if an interruption occurs, the reconfiguration will occur without informing the original configuration source that the configuration did not complete. JTAG always has the highest priority and any JTAG initiated configuration event will cause a reconfiguration to occur. Toggling the PROGRAMN pin has the next highest priority. It will interrupt any current configuration other than a JTAG configuration.

# **FPGA Configuration Control Pin Definitions**

The LatticeECP3 FPGA provides a set of I/O pins that can be used to load a configuration bitstream into the device. Some of these I/O are single purpose and are always available to perform configuration operations. Those configuration pins that are not dedicated can be configured for your use after the FPGA has entered user mode. This section describes what each I/O is, how it functions, and how to reclaim some for your own use.

### **Configuration Pin Management**

The dual-purpose sysCONFIG pins described in the Table 15-2 are dedicated configuration pins during the device configuration process. The PERSISTENT attribute is used to determine whether the dual-purpose sysCONFIG pins remain sysCONFIG pins during normal operation. The LatticeECP3 provides three settings for the PERSISTENT feature. The available options are shown in Table 15-3.

#### Table 15-3. PERSISTENT Setting and Affected Pins

| Persistent Setting | Pins                                                                                      |

|--------------------|-------------------------------------------------------------------------------------------|

| OFF                | All dual-purpose configuration pins are available as GPIO                                 |

| SLAVE_PARALLEL     | D [0:7], CSN, CS1N, WRITEN, BUSY, CSON, MCLK <sup>1</sup>                                 |

| SSPI               | SI, SO, SN, HOLDN, SISPI, SPID0, SPID1, CSSPIN and CSSPI1N                                |

|                    | w the Slove Parellel legis, but they are received by the Slove Parellel legis. They are r |

1. These pins are not used by the Slave Parallel logic, but they are reserved by the Slave Parallel logic. They are not available for use as GPIO.

You can use the SLAVE\_PARALLEL or the Slave SPI configuration port to access some of the resources connected to the FPGA. Accessing the FPGA resources requires special command sequences, which are described in other documents.

## **Dedicated Control Pins**

The LatticeECP3 makes a set of dedicated control pins available to allow you to select the way you want to configure the FPGA. The following sub-sections describe the LatticeECP3 dedicated sysCONFIG pins. These pins are powered by  $V_{CCIO8}$ .

While the device is under IEEE 1149.1 or 1532 JTAG control the dedicated programming pins have no meaning. This is because a boundary scan cell will control each pin, per JTAG 1149.1, rather than normal internal logic.

## JTAG Pins

The JTAG pins are standard IEEE 1149.1 TAP (Test Access Port) pins. The JTAG pins are dedicated pins and are always accessible when the LatticeECP3 device is powered up. While the device is under 1149.1 or 1532 JTAG control the dedicated programming pins INITN, DONE, and CCLK have no meaning. This is because a boundary scan cell will control each pin, per the IEEE standard, rather than normal internal logic. If the device is being accessed by JTAG then PROGRAMN will still be an active input even in JTAG mode.

These pins are powered by  $V_{CCJ}$ .

#### TDO

The Test Data Output pin is used to shift out serial test instructions and data. When TDO is not being driven by the internal circuitry, the pin will be in a high impedance state. This pin should be wired to TDO of the JTAG connector, or to TDI of a downstream device in a JTAG chain. An internal pull-up resistor on the TDO pin is provided. The internal resistor is pulled up to  $V_{CCJ}$ .

#### TDI

The Test Data Input pin is used to shift in serial test instructions and data. This pin should be wired to TDI of the JTAG connector, or to TDO of an upstream device in a JTAG chain. An internal pull-up resistor on the TDI pin is provided. The internal resistor is pulled up to  $V_{CCJ}$ .

#### TMS

The Test Mode Select pin controls test operations on the TAP controller. On the falling edge of TCK, depending on the state of TMS, a transition will be made in the TAP controller state machine. An internal pull-up resistor on the TMS pin is provided. The internal resistor is pulled up to  $V_{CCJ}$ .

#### тск

The test clock pin, TCK, provides the clock to run the TAP controller state machine, which loads and unloads the JTAG data and instruction registers. TCK can be stopped in either the high or low state and can be clocked at frequencies up to that indicated in the LatticeECP3 Family Data Sheet. The TCK pin supports hysterisis; the typical hysterisis is approximately 100mV when  $V_{CCJ} = 3.3V$ . The TCK pin does not have a pull-up. A pull-down resistor between TCK and ground on the PCB of 4.7 K is recommended to avoid inadvertent clocking of the TAP controller as  $V_{CC}$  ramps up.

#### **Optional TRST**

Test Reset, TRST, is not supported on the LatticeECP3.

#### V<sub>CCJ</sub>

Having a separate JTAG V<sub>CC</sub> (V<sub>CCJ</sub>) pin lets you apply a voltage level to the JTAG port that is independent from the rest of the device. Valid voltage levels are 3.3V, 2.5V, 1.8V, 1.5V, and 1.2V, but the voltage used must match the other voltages in the JTAG chain. V<sub>CCJ</sub> must be connected even if JTAG is not used.

Please see <u>In-System Programming Design Guidelines for ispJTAG Devices</u> for further JTAG chain information.

#### **Configuration and JTAG Pin Physical Description**

All of the sysCONFIG dedicated and dual-purpose pins are part of Bank 8. Bank 8  $V_{CCIO}$  determines the output voltage level of these pins, input thresholds are determined by the I/O Type selected in the ispLEVER Design Planner (default is 3.3V LVCMOS) and Diamond Spreadsheet View.

JTAG voltage levels and thresholds are determined by the V<sub>CCJ</sub> pin, allowing the LatticeECP3 to accommodate JTAG chain voltages from 1.2V to 3.3V.

#### CFG**[2:0]**

The Configuration Mode pins, CFG[2:0], are used to inform the FPGA how you want to configure the device. The actions performed by the remaining configuration pins depend on the state of the CFG[2:0] inputs. The CFG[2:0] input pins have weak internal pull-up resistors, that guarantee a valid configuration mode is selected should they be left unconnected. Lattice recommends the CFG pins be connected with independent pull-up/pull-down resistors. It is also recommended that these pins not be directly connected to the power or ground planes.

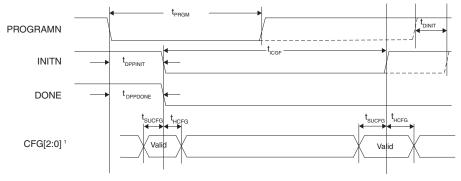

The CFG[2:0] pins are sampled at two different points in the configuration process. The first sample point is when the Power-On Reset state machine starts up. The POR sample point determines if the FPGA to be configured in master or slave mode. The  $t_{ICFG}$  time period changes based on this information.

The second time the CFG pins are sampled is at the rising edge of the INITN pin. This sample is used to make the final configuration selection. Table 15-4 describes the configuration mode that is active based on the CFG input pins. The state on the CFG pins at any other time is not important. The state pins can be changed freely, which may be useful for selecting a new configuration mode.

#### Table 15-4. LatticeECP3 Configuration Pins<sup>1</sup>

| Configuration Mode    | Clock | CFG [2] | CFG [1] | CFG <b>[0]</b> |

|-----------------------|-------|---------|---------|----------------|

| SPI Master (Single)   | MCLK  | 0       | 0       | 0              |

| SPI Master (Multiple) |       | 0       | 1       | 0              |

| Slave SPI             | CCLK  | 0       | 0       | 1              |

| Slave SFI             |       | Х       | Х       | Х              |

| SCM                   | CCLK  | 1       | 0       | 1              |

| SPCM                  | CCLK  | 1       | 1       | 1              |

1. JTAG is always available for IEEE 1149.1 and 1532 support.

#### PROGRAMN

The PROGRAMn is a dedicated input that is used to configure the FPGA. The PROGRAMn pin is a falling edge sensitive, and has an internal weak pull-up. When a falling edge occurs, the FPGA exits user mode and starts a device configuration sequence at the Initialization phase, as described earlier.

Proper operation of the LatticeECP3 FPGA depends on the PROGRAMn pin. The following conditions must be met:

- The PROGRAMn pin must not be asserted until after all of the supply rails are stable. This can be achieved by either placing an external pullup resistor and tying it to the VCCIO8 voltage, or permitting the FPGA's internal pull-up resistor to pull the input high.

- The PROGRAMn pin must make a high to low transition in order to cause the FPGA to enter configuration mode. This is not necessary when first powering the FPGA, as the FPGA will enter configuration mode after the internal Power On Reset circuit releases the internal reset.

- The PROGRAMn pin must not be allowed to transition from high to low at any time INITn is active (i.e. low) as a result of being in the Initialization state.

- PROGRAMn must meet the minimum active pulse width t<sub>PRGM</sub>.

- PROGRAMn remains an active input even when the JTAG bus is being used to program the FPGA. The PRO-GRAMn pin should not be asserted during JTAG programming sequences.

Failing to follow these guidelines may prevent the FPGA from operating.

PROGRAMn must be de-asseted in order for the FPGA to exit the Initialization state.

#### Figure 15-3. Configuration from PROGRAMN Timing

1. The CFG pins are normally static (hard wired).

#### INITN

The INITn pin is a bidirectional open-drain control pin. It has the following functions:

- After power is applied, or after a PROGRAMn assertion it goes low to indicate the FPGA configuration cells are being erased. The low time assertion is specified with the t<sub>ICFG</sub> parameter.

- After the t<sub>ICFG</sub> time period has elapsed the INITn pin is deasserted (i.e. is active high) to indicate the FPGA is

ready for its configuration bits. In master mode the FPGA starts loading bits from an attached non-volatile memory. In slave mode the FPGA waits for the bits to arrive over the interface selected by the CFG[2:0] input pins. The

rising edge of the INITn samples the CFG[2:0] inputs, allowing the FPGA to determine how it is to be configured.

- INITn can be asserted low by an external agent before the t<sub>ICFG</sub> time period has elapsed in order to prevent the

FPGA from reading configuration bits. This is useful when there are multiple FPGA's chained together. The

FPGA with the longest t<sub>ICFG</sub> time can hold all other FPGA's in the chain from starting to get data until it is ready

itself.

- The last function provided by INITn is to signal an error during the time configuration data is being read. Once t<sub>ICFG</sub> has elapsed, and the INITn pin has gone high, any INITn assertion signals the FPGA has detected an error during configuration.

The following conditions will cause INITN to become active, indicating the Initialization state is active:

- Power has just been applied

- PROGRAMN falling edge occurred

- The IEEE 1532 Refresh command has been sent using a slave configuration port (JTAG, SSPI, etc.).

If the INITN pin is asserted due to an error condition, the error can be cleared by correcting the configuration bitstream and forcing the FPGA into the Initialization state.

#### Figure 15-4. Configuration Error Notification

#### DONE

The DONE pin is a dedicated bi-directional open drain with a weak pull-up that signals the FPGA is in User mode. DONE is first able to indicate entry into User mode only after the internal DONE pin is asserted. The intenal DONE signal defines the beginning of the FPGA Wake-Up state.

The DONE output pin is controlled by the DONE\_EX configuration parameter. The default state of this pin is OFF. The default mode causes the LatticeECP3 to start immediately after the internal DONE bit is asserted. The FPGA does not stall waiting for the DONE pin to be asserted high.

The FPGA can be held from entering User mode indefinitely by having an external agent keep the DONE pin asserted low. In order to use DONE to stall entering user mode the DONE\_EX configuration preference must be set ON. A common reason for keeping DONE driven low is to allow multiple FPGAs to be completely configured. As each FPGA reaches the DONE state, it is ready to begin operation. The last FPGA to configure can cause all FPGAs to start in unison.

It is critical that DONE be asserted low when the LatticeECP3 is in a chain of FPGAs. The LatticeECP3 continues to pass configuration clock pulses to FPGAs attached downstream as long as DONE is de-asserted. Any FPGA

permitted to assert DONE and enter User mode will only pass a few hundred more configuration clock cycles. Downstream FPGAs will never complete their configuration process if this occurs.

The DONE pin drives low in tandem with the INITN pin when the FPGA enters Initialization mode. As described earlier, this condition happens when power is applied, PROGRAMN is asserted, or an IEEE 1532 Refresh command is received via a slave configuration port.

Sampling the DONE pin is a good way for an external device to tell if the FPGA has finished configuration. However, when using IEEE 1532 JTAG to configure SRAM the DONE pin is driven by a boundary scan cell, so the state of the DONE pin has no meaning during IEEE 1532 JTAG configuration (once configuration is complete, DONE takes on the behavior defined by the DONE\_EX configuration parameter).

#### Configuration Clock (CCLK)

The CCLK is a dedicated input-only whose purpose is to provide a reference clock for the FPGA when one of the slave configuration modes is selected by the CFG[2:0] inputs.

Please refer to the LatticeECP3 AC Timing information in the <u>LatticeECP3 Family Data Sheet</u> for information about maximum clock rates, and data setup and hold parameters.

When the LatticeECP3 is in a chain of FPGAs it is necessary to continue to drive CCLK until all of the FPGAs have received their configuration data. It is recommended the CCLK continue to be toggled until the DONE signal is active.

### **Dual-Purpose sysCONFIG Pins**

The Dual-Purpose sysCONFIG pins, depending on the configuration mode selected by the CFG[2:0] input pins, provide special configuration functions during the Configuration phase of the device wake-up process. The dualpurpose pins can be recovered for your use once the FPGA enters User mode. Successful recovery of the dualpurpose pins relies on following the guidelines described in the "Configuration Pins" section of this document.

The dual-purpose configuration pins are located in the same I/O bank as the dedicated configuration pins. The configuration pins in the LatticeECP3 are powered by the VCCIO8 voltage rail.

#### Master Clock (MCLK)

The MCLK provides a reference clock for synchronous non-volatile memories attached to the FPGA. MCLK is only active when the FPGA CFG[2:0] inputs select a master configuration mode. See Table 15-4 for a full description of the available configuration modes selectable by the CFG[2:0] input pins. MCLK acts as a general purpose I/O if the FPGA is in a slave configuration mode.

The LatticeECP3 generates MCLK from an internal oscillator. The initial output frequency of the MCLK is approximately 2.5MHz. The MCLK frequency can be altered using the MCCLK\_FREQ parameter. You can select the MCCLK\_FREQ using the Diamond Spreadsheet View. For a complete list of the supported MCLK frequencies, see Table 15-8.

During the initial stages of device configuration the frequency value specified using MCCLK\_FREQ is loaded into the FPGA. Once the FPGA accepts the new MCLK\_FREQ value the MCLK output begins driving the selected frequency. Make certain that when selecting the MCLK\_FREQ that you do not exceed the frequency specification of your configuration memory, or of your PCB. Lattice recommends reviewing the LatticeECP3 AC specifications in the LatticeECP3 Family Data Sheet when making MCLK\_FREQ decisions.

The LatticeECP3 provides the ability to be configured from a bitstream that is encrypted. There are additional requirements on the MCCLK\_FREQ selection that you must adhere to when configuring the LatticeECP3 with an encrypted bitstream. These conditions are discussed in the "Bitstream Encryption/Decryption Flow" section of this document.

#### DI/CSSPI0N

The DI/CSSPI0N configuration pin provides one of two functions depending on the FPGA's configuration mode. When the FPGA is in Serial Configuration Mode the pin is set to DI (Data Input) mode. When the FPGA is in SPI Master or SPI Master Multiboot mode, the pin is set to CSSPI0N (Chip Select SPI 0).

When the FPGA is in Serial Configuration Mode the DI pin receives incoming configuration data. See the Serial Configuration Mode section of this document for more information.

When the FPGA is in SPI Master or SPI Master Multiboot mode the CSSPI0N is the chip select strobe to the attached SPI memory that contains the FPGA's configuration bits. The FPGA asserts this pin active low during the Configuration phase of the wake-up process.

An external pull-up resistor is required on CSSPI0N in SPI and SPIm modes of operation. Some SPI memory devices require the CSn input to rise in tandem with their input voltage. The internal pull-up on CSSPI0N does not become active until the FPGA determines all input voltage rails are stable. This does not meet the requirements of some SPI memory vendors.

#### DOUT/CSON

The DOUT/CSON configuration pin is used only when placing the LatticeECP3 into a chain of FPGAs requiring configuration.

The DOUT/CSON pin is an output from the LatticeECP3 and is only active when the FPGA is connected to another FPGA in a daisy chain.

When in a daisy chain, the pin may act as either a data output (DOUT) or a chip select (CSON). The behavior is described in detail in the Configuring Multiple FPGA Devices section of this document.

For serial and parallel configuration modes, when Bypass mode is selected, this pin becomes DOUT (see Figure 15-10). When the device is fully configured a Bypass instruction in the bitstream is executed and the data on DI, or D[0:7] in the case of a parallel configuration mode, will then be routed to the DOUT pin. This allows data to be passed, serially, to the next device. In a parallel configuration mode D0 will be shifted out first followed by D1, D2, and so on.

Daisy chaining the Parallel devices can be implemented with the Flowthrough attribute. This attribute allows the CSON pin to be driven when the done bit is set and configuration of the first part is complete. The CSON of the first part will drive the CSN of the second part.

You will find this attribute in the ispLEVER Generate Bitstream Data property under Chain Mode or in the Diamond Bitstream options window. See Appendix B for more information on setting these options in Diamond.

The DOUT/CSON drives out a high on power-up and will continue to do so until the execution of the Bypass instruction within the bitstream, or until the I/O Type is changed by your code.

#### CSN/SN

The CSN/SN is a bidirectional pin that is active in Slave Parallel Configuration mode, or in Slave SPI mode. The pin is a chip select that gates the incoming configuration data.

Detailed information about using the chip select pin can be found in the "Slave Parallel Mode (SPCM)" and "Slave SPI (SSPI)" configuration sections of this document.

#### CS1N/HOLDN

The CS1N/HOLDN configuration pin is active only in Slave Parallel Configuration mode or in Slave SPI mode.

When the LatticeECP3 is in a Slave Parallel Configuration mode the pin acts as a chip select that works in conjunction with CSN. Information detailing the interaction of these two pins is described in the Parallel Configuration mode section of this document.

The configuration pin takes on the HOLDN function when the LatticeECP3 is in Slave SPI Configuration mode. Assertion of the HOLDN input causes the FPGA to ignore the SPI SCLK. Details for using HOLDN are provided in the Slave SPI Configuration section.

When CSN or CS1N is high, the D[0:7], and BUSY pins are tri-stated. CSN and CS1N are interchangeable when controlling the D[0:7], and BUSY pins.

#### WRITEN

The WRITEN configuration pin is an input pin that is active in Slave Parallel Configuration mode. It is a write enable strobe that controls the direction data flows on the D[0:7] data bus pins. When WRITEN is asserted active low the FPGA D[0:7] pins are tri-stated to allow an external bus master to write data into the FPGA.

#### **BUSY/SISPI**

The BUSY/SISPI configuration pin is active in Slave Parallel Configuration mode and in SPI Master modes.

When the LatticeECP3 is in a Slave Parallel Configuration mode, the pin is a tri-state output pin. When the FPGA parallel bus is active due to the assertion of CSN/CS1N the BUSY pin indicates the FPGA's ability to accept a byte of configuration data. The FPGA is able to accept another configuration byte when this output is driven low.

When the LatticeECP3 is in SPI Master mode the pin is connected to the data input of the SPI PROM that contains the configuration data. SISPI is an output used by the LatticeECP3 to transmit commands to the SPI PROM.

#### D[0]/SPIFASTN

The D[0]/SPIFASTN configuration pin is available in Slave Parallel Configuration and SPI Master configuration modes.

In Slave Parallel Configuration mode the D[0] pin is the most-significant data bit in the combined D[0:7] parallel data bus.

In SPI Master configuration modes it becomes the SPIFASTN input. The input is sampled at the rising edge of the INITN output.

The SPIFASTN selects the Read Opcode transmitted to the SPI PROM. When SPIFASTN is deasserted (i.e. driven to Vih) the FPGA requests a Read Operation using the 03 hex Read Opcode. When SPIFASTN is asserted (i.e. driven to Vil) the FPGA requests a Read Operation using the 0B hex Read Opcode. A SPI PROM that accepts the 0B Read Opcode is able to operate at higher serial clock rates. Consult the SPI memory vendor's data sheet for the exact capabilities of the SPI memory device.

Do not leave this input floating when a SPI Master mode is selected.

In parallel mode this pin is D[0] and operates in the same way as D[1:6] below. Taken together D[0:7] form the parallel data bus, D[0] is the most significant bit in the byte. The D[0:7] data bus are open-drain I/O without a pullup resistor during the time that power is applied to the FPGA. They also remain in this state until the FPGA is fully configured. When the FPGA is configured the D[0:7] I/O take on the attributes defined in your HDL source code, or using the Spreadsheet View preference editor.

As with D[1:6], if SRAM (configuration memory) needs to be accessed using the parallel pins while the part is in user mode (the DONE pin is high) then the PERSISTENT control cell must be set to preserve this pin as D[0]. Note that SRAM may only be read using JTAG or Slave Parallel mode.

#### D[1], D[2], D[5] and D[6]

These configuration pins are only available in Slave Parallel Configuration mode and are intermediary data bits for the parallel data bus made up of bits D[0:7].

Remember that D[0] is the most-significant data bit and D[7] is the least-significant.

### D[3]/SI

The D[3]/SI configuration pin is only available in Slave Parallel Configuration or in Slave SPI Configuration mode.

When the LatticeECP3 is in Slave Parallel Configuration mode the pin acts as D[3].

In Slave SPI Configuration mode the pin acts as the Serial Input pin for data supplied by a SPI Master Controller.

### D[4]/SO

The D[4]/SO configuration pin is only available in Slave Parallel Configuration or in Slave SPI Configuration mode.

When the LatticeECP3 is in Slave Parallel Configuration mode the pin acts as D[4].

In Slave SPI Configuration mode the pin acts as the Serial Output pin for data transmitted from the FPGA back to the SPI Master Controller.

#### D[7]/SPID0

The D[7]/SPID0 configuration pin is only available in Slave Parallel Configuration or in Master SPI Configuration mode.

When the LatticeECP3 is in Slave Parallel Configuration mode the pin acts as D[7]. This is the least-significant-bit of the D[0:7] data bus.

In Master SPI Configuration mode the pin acts as the SPI Data Input pin receiving data from an attached SPI PROM.

## **Configuration Modes**

LatticeECP3 devices support many different configuration modes, utilizing either serial or parallel data paths. The configuration method used by the LatticeECP3 is selected by driving the CFG[2:0] input pins. The CFG[2:0] input pins are sampled at the falling edge of INITN to determine if the part is in a master or a slave configuration mode. The pins are sampled a second time at the rising edge of INITN to determine the specific configuration mode.

The LatticeECP3 starts the configuration process in one of three ways:

- Initial application of power

- Assertion of the PROGRAMN input pin

- Reception of a REFRESH command form a configuration port (JTAG, Slave SPI, Slave Parallel)

### **SPI Interface**

The Serial Peripheral Interface (SPI) is a four-wire de facto bus standard used to transmit and receive serial data. The LatticeECP3 can use a SPI data bus to retrieve its configuration data from most SPI ROMs.

The amount of ROM storage required depends on the number of Look Up Tables (LUTs) in the LatticeECP3 device you have selected. Figure 15-5 shows how many bits of configuration data are required for each member of the LatticeECP3 family.

| Device   | Bitstream Size <sup>1</sup> | SPI Flash | Dual Boot SPI<br>Flash | Units |

|----------|-----------------------------|-----------|------------------------|-------|

| ECP3-17  | 4.5                         | 8         | 16                     | Mb    |

| ECP3-35  | 8.2                         | 16        | 32                     | Mb    |

| ECP3-70  | 22.5                        | 32        | 64                     | Mb    |

| ECP3-95  | 22.5                        | 32        | 64                     | Mb    |

| ECP3-150 | 35.7                        | 64        | 128                    | Mb    |

#### Table 15-5. Maximum Configuration Bits – SPI Flash Mode Bitstream File<sup>1</sup>

1. The Bitstream Size column is the maximum number of bits the FPGA may require. This number takes into account the pre-initialization of all Embedded Block RAMs.

The estimated configuration time can be calculated by dividing the bitstream size (in bits) from Table 15-5 by the configuration clock (MCLK or CCLK) frequency. The MCLK frequency is modified using the Global Preferences tab within the Diamond Spreadsheet View or in the ispLEVER Design Planner.

The LatticeECP3 provides the following three SPI configuration modes:

- SPI Master (SPI)

- SPI Master Multiboot (SPIm)

- Slave SPI (SSPI)

#### **SPI Master Mode**

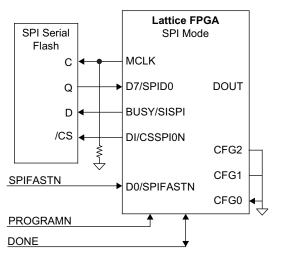

The simplest SPI configuration consists of one SPI Serial Flash connected to one LatticeECP3, as shown in Figure 15-5. In this configuration the LatticeECP3 is the master of the SPI bus. The FPGA controls the chip select and the MCLK, and receives the configuration data on the SPID0 input.

During FPGA configuration the SISPI output sends a command sequence to reset the SPI PROM's internal address pointer. The SPIFASTN informs the FPGA which SPI Read Command to send to the SPI PROM. When the SPIFASTN input is driven high, the FPGA sends a 03 Hex Read Opcode. When it is asserted active low, the FPGA sends a 0B Hex Read Opcode to the SPI PROM.

As mentioned in the section describing the MCLK behavior, the configuration clock frequency can be altered. The MCLK frequency must not exceed the clock input frequency of the SPI PROM.

#### Figure 15-5. One FPGA, One SPI Serial Flash

Note: The board-level pull-down on MCLK should have a 1-3 Kohms resistance. This counteracts the weak internal pull-up on MCLK and prevents an unintentional rising edge at power-up.

In order to configure properly, the LatticeECP3 must transmit at least 128 clock pulses before it receives the preamble code (BDB3 hex for unencrypted bitstreams, and BFB3 for encrypted bitstreams). It is required that the data in the SPI PROM be padded to account for these extra clocks. The bitstream generation tool automatically adds the necessary padding information.

There are some general rules that user has to follow in order to configure properly:

- The POR of the SPI flash device should be lower than the POR of LatticeECP3 or the SPI flash must be powered first.

- SPI flash maximum frequency must be higher than LatticeECP3 MCLK frequency.

- Board routing requirements need to ensure proper timing. Please refer to ECP3 data sheet for detailed timing requirement.

## SPI Master Multiboot (SPIm) Mode

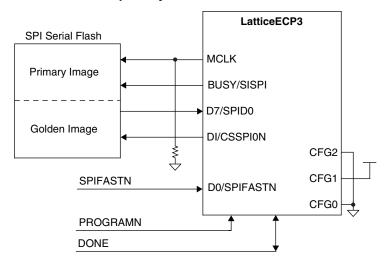

SPI Master Multiboot mode is an enhancement to the SPI Master boot mode. The SPI memory is attached to the FPGA in exactly the same way as SPI Master mode. SPIm enables you to partition the SPI PROM to store two configuration bitstreams. The FPGA will attempt to configure from the Primary image, and if the FPGA fails to configure from the primary image it tries to load a fail-safe Golden bitstream. Figure 15-6 shows the concept from a high level.

#### Figure 15-6. SPIm Mode for Dual-Boot Capability

Internally, SPIm mode adds logic to detect a configuration failure and the ability to reattempt configuration from a different address within the SPI Flash device. While SPI mode treats the SPI Flash device as a single block of storage starting at address zero, SPIm mode allows segmentation of the Flash device for the golden bitstream.

In SPIm mode, the primary bitstream is stored at address offset 0x010000. When configuring, the LatticeECP3 device automatically reads the data beginning at this address first. If after 2\*14 clocks the device still does not receive the pre-amble code or a bitstream error is encountered after receiving the pre-amble code, the configuration logic resets and loads the data located at address offset 0xFFFF00.

The LatticeECP3 uses a 24-bit addressing scheme to access the SPI memory array. The amount of storage remaining in the SPI starting at address 0xFFFF00 is only 256 bytes. This is not enough to store a complete LatticeECP3 configuration bitstream. The LatticeECP3 configuration bitstream is stored elsewhere in the SPI PROM. The data retrieved by the FPGA at address 0xFFFF00 is an instruction pointing to the start of the failsafe configuration data.

An example of the SPI Flash memory organization for SPIm mode is shown in Table 15-6.

#### Table 15-6. SPIm Mode Data Map<sup>1, 2, 3</sup>

| Block (512Kb)  | SPI Flash Address                          | Contents                     |

|----------------|--------------------------------------------|------------------------------|

| 0              | 0x000000                                   | Unused                       |

| 1<br>2<br>3    | 0x010000<br>0x020000<br>0x030000<br>-<br>- | Primary Bitstream            |

| 18             | 0x120000                                   |                              |

| 32<br>33<br>34 | 0x200000<br>0x210000<br>0x220000           |                              |

|                |                                            | Golden Bitstream             |

| 49             | 0x310000                                   |                              |

| Ν              | 0xFF0000                                   |                              |

| IN IN          | 0xFFFF00                                   | Jump instruction to 0x200000 |

1. The bitstream sizes shown are examples. Actual sizes and address boundaries vary with device density.

2. After the golden bitstream is written into the SPI Flash device, the top half of the SPI Flash can be write-protected to secure the golden bitstream from alterations.

3. When the SPI Flash device reaches the address 0xFFFFF, it rolls over to address 0x000000. If the last page is un-programmed, the device can read the jump instruction programmed on address 0x000000 effectively implementing a multiple patterns support for board development or debugging need.

## Slave SPI (SSPI)

The LatticeECP3 can be configured by a SPI Master controller. Using the CFG[2:0] inputs to select SSPI configuration mode the FPGA becomes a SPI Slave device, receiving data from a SPI Master controller. The FPGA can be accessed using Mode 0 and Mode 3 bus transactions.

The slave SPI interface allows for a the following functions to be performed:

- Configuration of the FPGA

- Readback of the FPGA configuration bitstream

- Forcing the device to REFRESH as if PROGRAMN were asserted

- Read/Write access to a SPI PROM attached to the SPI Master configuration pins

- Clearing the FPGA configuration

- Reading the FPGA ID code

- Reading the FPGA User ID code

#### Table 15-7. Slave SPI Pins

| Signal Name | Туре                             | Description            | Function                                                                                                                         |

|-------------|----------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| SN          | Active Low Input                 | Chip Select            | A falling edge on SN causes the FPGA to enter Command<br>State. A rising edge on SN causes the FPGA to enter Reset<br>State.     |

| SI          | Input                            | Serial Input Data      | Serial input for command and data.                                                                                               |

| SO          | Tri-state Output                 | Serial Output Data     | Serial output data to the SPI Master.                                                                                            |

| SCK         | Clock Input                      | Serial Data Clock      | Serial input clock for command and data.                                                                                         |

| HOLDN       | Asynchronous Active<br>Low Input | Put the Device on Hold | Tri-state SO and set the device into the suspension state by ignoring the CCLK. Do not assert when loading encrypted bitstreams. |

The chip select pin (SN) is a chip select input to the FPGA. The LatticeECP3 responds on the falling and rising edges of the SN input. SN is not a level sensitive input. When the SN falling edge occurs the FPGA is ready to accept commands from a SPI Master Controller. A rising edge on the SN input resets the internal state machine and tri-states the SO output pin. The only exception to this is when the FPGA has received a SPI\_PROGRAM command. This command can only be interrupted by the assertion of the PROGRAMN input.

The HOLDN pin is provided to allow a SPI Master Controller to pause transactions on the Slave SPI port. When HOLDN is asserted low the FPGA tri-states the SO output and ignores the SCLK input. This allows the SPI Master Controller to interact with another SPI device and then resume transactions to the LatticeECP3. Encrypted bitstreams must be sent without interruption. You are not permitted to assert HOLDN or deassert SN once an encrypted bitstream transmission has begun.

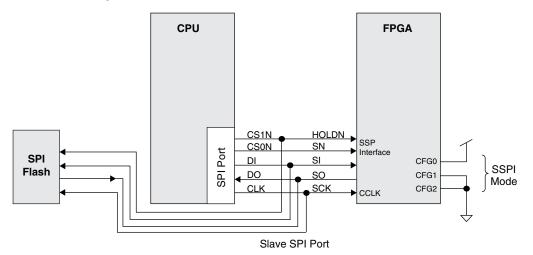

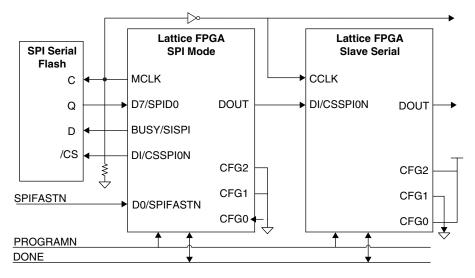

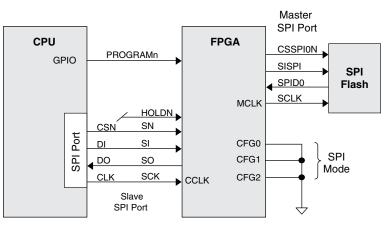

#### Figure 15-7. Slave SPI Example

Figure 15-7 illustrates how an on-board CPU can be connected to the LatticeECP3 using the Slave SPI programming interface. The CPU can fetch configuration data from the attached SPI PROM. The CPU is not required to deassert the SN input to the FPGA. When the CPU asserts the CS1N to access the SPI PROM the FPGA HOLDN is asserted causing it to ignore SCLK transitions. The HOLDN input can not be asserted when transferring an encrypted bitstream.

Full details on using Slave SPI mode on the LatticeECP3 are provided in TN1222, <u>LatticeECP3 Slave SPI Port</u> <u>User's Guide</u>.

## Slave Serial Configuration Mode (SCM)

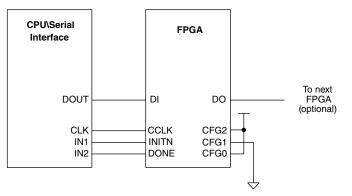

Slave Serial Configuration mode provides a simple, low pin count method for configuring one or more FPGAs. Data is presented to the FPGA on the Data Input pin DI at every CCLK rising edge.

#### Figure 15-8. Slave Serial Block Diagram

The bitstream data generated by Lattice Diamond is formatted so that it is ready to shift into the FPGA. Left shift the data out of the file in order for it to be correctly received by the FPGA.

The FPGA synchronizes itself on either a 0xBDB3 or 0xBFB3 code word. It is critical that any data presented on DIN not be recognized as one of these two synchronization words early. To guarantee proper recognition of the synchronization word it is recommended that the synchronization word always be preceded by a minimum of 128 '1' bits. Presenting any other bitstream data, Programmer generated header information for example, risks the being misinterpreted due to bit slippage.

Slave Serial Configuration Mode can be used to configure a chain of FPGAs. Details about configuring a chain of devices is discussed in "Combining Configuration Modes" on page 38 of this document.

## Slave Parallel Mode (SPCM)

The LatticeECP3 can be configured using Slave Parallel Configuration Mode. Slave Parallel permits an external master to configure the FPGA using an 8-bit synchronous SRAM bus interface. Slave Parallel Configuration Mode is a flexible method for configuring one or more FPGAs. It is also the fastest mode available for configuring the LatticeECP3.

The slave parallel interface allows for a multitude of different functions to be performed:

- Configuration of the FPGA

- Readback of the FPGA configuration bitstream

- Reading the device CRC

- Reading the programming status register

- Reading the FPGA ID code

- Reading the FPGA User ID code

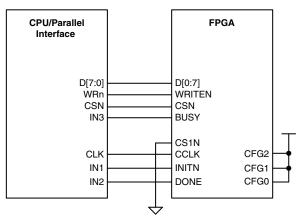

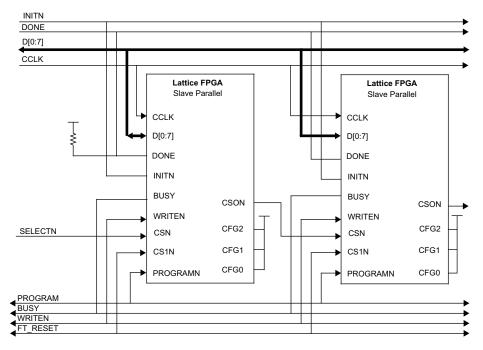

#### Figure 15-9. Slave Parallel Block Diagram

Figure 15-9 shows the typical Slave Parallel Configuration Mode usage. Configuration data can be written to the LatticeECP3 immediately following the INITN rising edge. The LatticeECP3 data bus bit ordering is denoted using a big-endian nomenclature. This means that D0 receives the MSBit, and D7 receives the LSBit. One byte of data can be sent to the FPGA on each rising CCLK edge as long as CSN, CS1N, and WRITEN are asserted. When the LatticeECP3 is the only device being configured the FPGA can receive configuration data at the full CCLK rate. The master device is not required to monitor the BUSY pin in this situation, because the configuration bitstreams are padded to avoid BUSY assertion.

Sending an encrypted bitstream must be done atomically, i.e. without interruption. The bus master is not permitted to pause the transfer of an encrypted bitstream by deasserting the CSN or CS1N inputs. The CCLK pin can be stretched or stopped if desired, but the CSN and CS1N pins must remain asserted.

Slave Parallel mode can also be to read status registers and the configuration bitstream. In order for the Slave Parallel port to be used to perform read operations the FPGA must have the PERSISTENT preference set to SLAVE\_PARALLEL mode. See the Configuration Pin Management section of this document for more information.

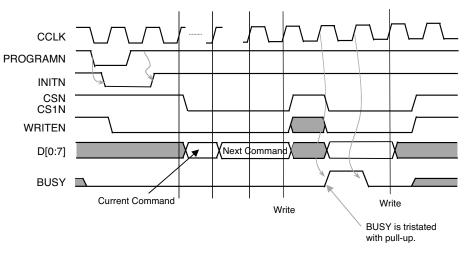

#### Figure 15-10. Parallel Port Write Timing Diagram

Note: The BUSY pin cannot go high while both CS1N and CSN are low. The second BUSY high shown is OK since CS1N or CSN was low previously.

## JTAG Mode (IEEE 1149.1 and IEEE 1532)

The LatticeECP3 provides an IEEE 1532 compliant interface. The IEEE 1532 specification, a superset of the IEEE 1149.1 JTAG specification, describes a standard methodology for configuring programmable logic devices. The LatticeECP3 only requires the four IEEE 1149.1 control signals (TCK, TMS, TDI, and TDO) in order to initiate and complete programming operations. The LatticeECP3 JTAG port is always available for use, regardless of the configuration mode selected.

Programming the LatticeECP3 using the JTAG port is typically accomplished in one of several ways:

- You can use Lattice Diamond Programmer software in combination with a Lattice download cable

- You can use Automatic Test Equipment that can read Serial Vector Format (SVF), In-System Configuration (ISC), STAPL/JAM, or ATE vector files

- You can use an embedded microprocessor to run Lattice's ispVM Embedded configuration software

#### Lattice Diamond Programmer's Fast Program

The Lattice Diamond development tools translate your design into a bitstream containing an optional header, mandatory preamble, and the device configuration data. The configuration data includes its own preamble, fuse data, and finally a trailing CRC. This basic structure is used for all of the configuration modes supported by the LatticeECP3. The IEEE 1532 mode adds some additional operations to the device configuration process.

Prior to sending the configuration data the FPGA's Boundary Scan I/O Cells are placed in a high-impedance state, and the FPGA's configuration memory is cleared. Because the I/O are tri-stated the DONE and INITn output signals do not provide status information while the configuration data is being written to the FPGA. The JTAG configuration mode uses an internal status register to confirm the FPGA DONE and INITn status signals indicate the device configured correctly. After the internal DONE and INITn controls are confirmed, the Boundary Scan I/O Cells are re-enabled, and all I/O take on the function assigned to them.

The JTAG interface, because it can control the Boundary Scan I/O Cells, can also be used to configure the LatticeECP3 without putting the I/O into a high-impedance state. During device configuration the I/O cells can be locked in their last known active state. This mode of operation is called TransFR Programming. A full description of how to use TransFR is provided in TN1087, <u>Minimizing System Interruption During Configuration Using TransFR Technology</u>.

#### JTAG Configuration Data Read and Save

The JTAG interface can be used to read the configuration data stored in the FPGA's SRAM array. There are two modes available to retrieve the data, foreground mode or background mode.

Foreground readback is accessed using IEEE 1532 mode. When using this method the JTAG Boundary Scan Cells are placed in a high-impedance state, and the configuration data read. Once the configuration data is retrieved the Boundary Scan Cells are restored, and the FPGA returns to normal operation.

The Background Read and Save operation allows you to read the content of the device while the device remains in operation. All I/O, as well at the non-JTAG configuration pins, continue normal operation during the Background Read and Save operation. You must not violate the following conditions when using the Background Read and Save function:

- The Soft Error Detection system must not be running. De-assert the SEDENABLE pin to prevent the SED circuit from interfering with the Background Read and Save operation. It is recommended that you wait at least one full SEDSTART to SEDDONE time period after the deassertion of the SEDENABLE to make sure the SED circuit has discontinued operation. Alternately monitor the SEDINPROG output, and wait for it to de-assert.

- Write operations to distributed RAM blocks must be suspended. Write operations that occur at the same time the SRAM cell is being read are non-deterministic. It is possible for the SRAM to receive, or retain, incorrect RAM data.

Regardless of which read and save mode is used the configuration data will not include the EBR or the distributed RAM contents. Distributed RAM contents will always be return zeroes.

#### Boundary Scan and Boundary Scan Description Language (BSDL) Files

The LatticeECP3, as mentioned previously, provides an IEEE 1149.1 compliant JTAG interface. The JTAG interface can be controlled by Automatic Test Equipment (ATE) that uses Boundary Scan Description Language (BSDL) files. Lattice makes BSDL files available for the LatticeECP3 on the Lattice Semiconductor website.

The boundary scan ring covers all of the I/O pins, as well as the dedicated and dual-purpose sysCONFIG pins. Note that PROGRAMN, CCLK, and the CFG pins are observe only (BC4, JTAG read-only) boundary scan cells.

When performing JTAG 1149.1 EXTEST instructions, the SERDES CML termination for both Tx and Rx is set to 50 ohm pull-ups. This allows the high-speed channels to operate properly if DC data is sent or received. During JTAG EXTEST, the termination will be set to 50 ohm. This overrides the termination resistance programmed into the SERDES logic.

## **Bitstream Generation Software Usage**

This section describes the settings for bitstream generation performed by the Diamond software program that generates a bitstream. These options are controlled through the Global Preferences of the Diamond Spreadsheet View and the property settings of the Bit Generation Software tool. To set the Global Preferences and properties in Diamond, see Appendix B. By setting the proper parameter in the Lattice design software the selected configuration options are set in the generated bitstream. As the bitstream is loaded into the device the selected configuration options take effect. These options are described in the following sections.

Bit Generation takes a fully routed Physical Design (.ncd file) as input and produces a configuration bitstream (bit images). The bitstream file contains all of the configuration information from the Physical Design defining the internal logic and interconnections of the FPGA, as well as device-specific information from other files associated with the target device. The data in the bitstream can then be downloaded directly into the FPGA memory cells or used to generate files for PROM programming (using a separate program, ispVM). Please refer to the ispVM documentation for details on creating PROM image files.

## **Configuration Options**

Several configuration options are available for each configuration mode. These options are controlled from the Spreadsheet View for each Strategy. They include the following items.

- When daisy chaining multiple FPGA devices an overflow option is provided for serial and parallel configuration modes

- When using SPI or SPIm mode, the master clock frequency can be set

- A security bit can be set to prevent SRAM readback

- The Persistent option can be set

- Configuration pins can be protected

- DONE pin options can be selected

By setting the proper parameter in the Lattice design software the selected configuration options are set in the generated bitstream. As the bitstream is loaded into the device the selected configuration options take effect. These options are described in the following sections.

#### Master Clock

If the CFG pins indicate an SPI or SPIm mode, the MCLK pin will become an output with a default frequency, or one selected when you added preferences to your design. The default Master Clock Frequency is 2.5 MHz. For a complete list of the supported Master Clock frequencies, please see the <u>LatticeECP3 Family Data Sheet</u>. When using the LatticeECP3 devices, the available frequencies are restricted, as shown in the data sheet.

You can change the Master Clock frequency by setting the MCCLK\_FREQ global preference in the Diamond Spreadsheet view tool. During configuration one of the first pieces of information loaded is the MCCLK\_FREQ parameter. When this parameter is loaded the master clock frequency changes to the selected value without glitching. Care should be exercised not to exceed the frequency specification of the slave devices or the signal integrity capabilities of the PCB layout.

Configuration time is computed by dividing the maximum number of configuration bits, as given in Table 15-5 above, by the Master Clock frequency.

| MCCLK (MHz)      | MCCLK (MHz)     |

|------------------|-----------------|

| 2.5 <sup>1</sup> | 10              |

|                  | 13              |

| 4.3              | 15 <sup>2</sup> |

| 5.4              | 20              |

| 6.9              | 26              |

| 8.1              |                 |

| 9.2              | 33 <sup>3</sup> |

Table 15-8. Selectable Master Clock (MCCLK) Frequencies During Configuration (Nominal)

1. Software default MCLK frequency. Hardware default is 3.1MHz.

2. Maximum MCCLK with encryption enabled.

3. Maximum MCCLK without encryption

#### Security Bit

Setting the CONFIG\_SECURE option to ON prevents readback of the SRAM from JTAG or the sysCONFIG pins. When CONFIG\_SECURE is set to ON the only operations available are erase and write. The security control bit is updated as the last operation of SRAM configuration. If a secured device is read it will output all ones.

For LatticeECP3 devices the CONFIG\_SECURE option is accessed via the Design Planner in ispLEVER. To set this option in Diamond, see Appendix B. The default is OFF.

#### Persistent Option

The PERSISTENT option is used to direct the place and route tools about how it can use the sysCONFIG pins. By default the PERSISTENT option is turned OFF, which allows the place and route tools to reclaim most of the configuration pins as general purpose input/output. Changing the PERSISTENT configuration option from its default state prevents the place and route tools from either the Slave SPI or the Slave Parallel configuration ports from becoming general purpose I/O.

Enabling the dedicated sysCONFIG ports is useful for performing additional capabilities while the FPGA is in user mode.

You use the SLAVE\_PARALLEL setting when:

- You want to read back the FPGAs SRAM contents. The LatticeECP3 provides a command set and access protocol that allows the configuration SRAM to be read from the FPGA. The Slave Parallel port can read all of the configuration data, except the EBR and the distributed RAM contents.

- You have a LatticeECP3, configured as a SPI Master, in series of FPGAs in a device chain. The SPI Master FPGA must keep the MCLK pin active in order to provide a configuration clock for all of the chained FPGAs. Table 15-3 describes the configuration pins that are preserved. The MCLK output is only preserved Slave Parallel configuration mode. If PERSISTENT is set to OFF, or SSPI the MCLK output tri-states after the lead FPGA is configured, which prevents chained FPGAs from configuring.

Use the SSPI PERSISTENT setting when:

• You want to access a SPI PROM attached to the SPI Master configuration pins. You can attach a SPI memory

controller and using a custom command you can perform erase, program, and verify sequences on the SPI PROM while the FPGA is in operation. Table 15-3 describes the configuration pins that are preserved. Information about the Slave SPI transactions are published in TN1222 <u>LatticeECP3 Slave SPI Port User's Guide</u>. You can also use the SSPI Embedded device programming software provided by Lattice.

#### **Configuration Mode**

The CONFIG\_MODE option tells the software which configuration port the hardware is using to program the FPGA. Setting this parameter permits the design software to check to make sure configuration port pins are not oversubscribed. The oversubscription is only flagged as a warning. In some cases it is acceptable to oversubscribe the configuration port. For example it is acceptable to have the FPGA in SPI Master configuration mode and use the SISPI, SPID0, and SPICS pins as general purpose I/O.

The CONFIG\_MODE is also used to make sure encrypted bitstreams are generated correctly. To guarantee correct operation of encrypted bitstreams you need to set the CONFIG\_MODE parameter.

#### DONE EX

During configuration the DONE output pin is low. Once configuration is complete, indicated by assertion of an internal DONE bit, the device wake-up sequence takes place. The external DONE pin is able to operate in one of two modes during the wake up sequence. The default behavior, set when DONE\_EX = OFF, is for it to actively drive to VIL. When DONE\_EX is set ON, the external DONE pin becomes an open-drain output. The LatticeECP3 wake up sequence will stall until the external DONE pin is pulled high. Set DONE\_EX to ON when you want to synchronize the when a chain of FPGAs wakes up. Make sure you place a pullup resistor that is able to drive all of the DONE pins.

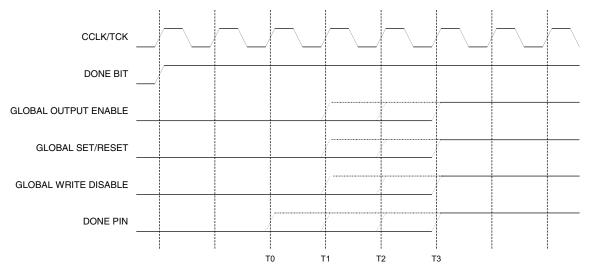

## **Device Wake-Up**

When configuration is complete the device will wake up in a predictable fashion. Wake-Up occurs after successful configuration, without errors, and provides the transition from Configuration Mode to User Mode. The Wake-Up process begins when the internal DONE bit is set.

Table 15-9 provides a list of the Wake-Up sequences supported by the LatticeECP3; Figure 15-11 shows the Wake-Up timing. The default Wake-Up sequence works fine for most single device applications.

| Sequence       | Phase T0 | Phase T1        | Phase T2        | Phase T3        |

|----------------|----------|-----------------|-----------------|-----------------|

| 1              | DONE     | GOE, GWDIS, GSR |                 |                 |

| 2              | DONE     |                 | GOE, GWDIS, GSR |                 |

| 3              | DONE     |                 |                 | GOE, GWDIS, GSF |

| 4 <sup>1</sup> | DONE     | GOE             | GWDIS, GSR      |                 |

| 5              | DONE     | GOE             |                 | GWDIS, GSR      |

| 6              | DONE     | GOE             | GWDIS           | GSR             |

| 7              | DONE     | GOE             | GSR             | GWDIS           |

| 8              |          | DONE            | GOE, GWDIS, GSR |                 |

| 9              |          | DONE            |                 | GOE, GWDIS, GSF |

| 10             |          | DONE            | GWDIS, GSR      | GOE             |

| 11             |          | DONE            | GOE             | GWDIS, GSR      |

| 12             |          |                 | DONE            | GOE, GWDIS, GSF |

| 13             |          | GOE, GWDIS, GSR | DONE            |                 |

| 14             |          | GOE             | DONE            | GWDIS, GSR      |

| 15             |          | GOE, GWDIS      | DONE            | GSR             |

| 16             |          | GWDIS           | DONE            | GOE, GSR        |

| 17             |          | GWDIS, GSR      | DONE            | GOE             |

#### Table 15-9. Wake-Up Options

#### Table 15-9. Wake-Up Options (Continued)

| Sequence        | Phase T0 | Phase T1        | Phase T2        | Phase T3 |

|-----------------|----------|-----------------|-----------------|----------|

| 18              |          | GOE, GSR        | DONE            | GWDIS    |

| 19              |          |                 | GOE, GWDIS, GSR | DONE     |

| 20              |          | GOE, GWDIS, GSR |                 | DONE     |

| 21 <sup>2</sup> |          | GOE             | GWDIS, GSR      | DONE     |

| 22              |          | GOE, GWDIS      | GSR             | DONE     |

| 23              |          | GWDIS           | GOE, GSR        | DONE     |

| 24              |          | GWDIS, GSR      | GOE             | DONE     |

| 25              |          | GOE, GSR        | GWDIS           | DONE     |

1. Default when DONE\_EX=ON.

2. Default when DONE\_EX=OFF.

### Figure 15-11. Wake-Up Timing Diagram

## Synchronizing Wake-Up

The LatticeECP3 is, in most cases, configured using one of the master configuration modes. The FPGA, when in master configuration mode, is driving the configuration clock. The configuration clock is used for stepping through the final four Wake-Up states described in the previous section.

The LatticeECP3 has the ability to use an external clock source to control the final state transitions in the Wake\_Up process. There are three possible sources for the clock. The JTAG TCK, the Slave Configuration CCLK, and a general-purpose input.

#### Start\_Up Clock Selection

Once the FPGA is configured, it enters the start-up state, which is the transition between the configuration and operational states. This sequence is synchronized to a clock source, which defaults to CCLK when a slave configuration mode is used, or TCK when JTAG is used.

If desired, a user-defined clock source can be used instead of CCLK/TCK. You need to specify this clock signal, and instantiate the STRTUP library element in your design. The example shown below shows the proper syntax of instantiating the STRTUP library element.

#### Verilog

```

STRTUP u1 (.UCLK(<clock_name>)) /* synthesis syn_noprune=1 */;

```

#### VHDL

```

component STRTUP

port(STRTUP: in STD_ULOGIC );

end component;

attribute syn_noprune: boolean ;

attribute syn_noprune of STRTUP: component is true;

begin

u1: STRTUP port map (UCLK =><clock name>);

```

#### Synchronous to Internal DONE Bit

If the LatticeECP3 is the only device in the configuration chain, or the last device in the chain, DONE\_EX should be set to the default value (OFF). The Wake-Up process will be initiated by setting of the internal DONE bit on successful completion of configuration.

#### Synchronous to External DONE Pin

The DONE pin can be used to synchronize Wake-Up to other devices in a configuration chain. If DONE\_EX (see the DONE EX section above) is ON then the DONE pin is an open-drain bi-directional pin. If an external device drives the DONE pin low then the Wake-Up sequence stalls until DONE is active high. Once the DONE pin goes high the device will follow the selected WAKE\_UP sequence.