Winfried Hofacker . Ekkehard Floegel

## the custom apple

& OTHER MYSTERIES

Winfried Hofacker . Ekkehard Floegel

# the custom apple & other wysteries

**Charles Trapp** — **Editor**

David Moore — Technical Editor

D. J. Smith — Additional Graphics

H. C. Pennington and D. J. Smith — Cover Design

First Edition

First Printing

June 1982

Printed in the United States of America

Copyright© 1982 by W. Hofacker and E. Floegel

ISBN 0 936200 05 7

All rights reserved. No Part of this book may be reproduced by any means without the express written permission of the publisher. Example programs are for personal use only. Every reasonable effort has been made to ensure accuracy throughout this book, but neither the author or publisher can assume responsibility for any errors or omissions. No liability is assumed for any direct, or indirect, damages resulting from the use of information contained herein.

Published by IJG Inc 1953 West 11th Street Upland,CA 91786 (714)

Apple and Apple II are registered trademarks of Apple Computer Inc. BYTE WIDE is a registered trademark of Mostek Inc. Radio Shack is a registered trademark of the Tandy Corporation.

## IMPORTANT

### Read This Notice

Any software or computer hardware modifications are done at your own risk. Neither the PUBLISHER nor the AUTHOR assumes any responsibility or liability for loss or damages caused or alleged to be caused directly or indirectly by applying any modification or alteration to software or hardware described in this book, including but not limited to any interruption of service, loss of business, anticipatory profits or consequential damages resulting from the use or operation of such modified or altered computer hardware or software. Also, no patent liability is assumed with respect to the use of the information contained herein.

While every precaution has been taken in the preparation of this book, the PUBLISHER and the AUTHOR assume no responsibility for errors or omissions.

The reader is the sole judge of his or her skill and ability to perform the modifications and/or alterations contained in this book.

### **Editor's Note**

### ABOUT THE AUTHORS

The authors have previously published several books in Germany, including: Programming in Basic and Machine Language with the ZX81, Pascal Handbook Programming in Machine Language with the 6502 (by E. Floegel), as well as Transistor Logic and Construction Handbook (2 volumes) and Basic for Laymen (by W. Hofacker). In addition, Winfried Hofacker operates a publishing firm (with offices in Holzkirchen, Bavaria and Los Angeles) specializing in computer books written in both English and German.

This book is the first to be written in English by the two authors, and it had a spectacularly unlucky beginning as a result. Several chapters were composed verbally on the spot by the two authors in German, then dictated in literal English-German translation to the technical editor, who in turn, dictated into a cassette. Some weeks later the cassettes were typed into disk files by a person unfamiliar with computers, and the resulting manuscript given to myself was really unbelievable.

I'd like to say an especial word of thanks to Ekkehard Floegel, who spent a week helping me with the "too long German sentences" and numerous technical points, as well as his interesting stories of Bavaria.

I'd also like to thank:

David Moore, for teaching me to speak English again when this project was completed;

Nancy DeDiemar of Helen's Place and Eric Jorgensen of Clymer Publications, for their useful suggestions and the 'TLC' they gave our typesetting;

Muriel Brock, for laying out the majority of the book;

and all the fine folks of IJG, Inc., for helping in so many ways.

Charles Trapp June, 1982

### **Table of Contents**

| General Information:                       |     |

|--------------------------------------------|-----|

| The Tools You Will Need                    | . 7 |

| Reading Schematics                         | . 9 |

| Be Tolerant                                | 14  |

| Those Colors:                              |     |

| What They Mean and How to Read Them        | 15  |

| Copacetic Comprehension                    | 17  |

| Number Systems                             | 17  |

| Converting Binary to Decimal               | 20  |

| Digital Logic Devices                      | 21  |

| Reading the Pins                           | 25  |

| Wire-Wrapping Technique                    |     |

| Soldering Technique                        | 28  |

| Tips on Handling Integrated Circuits       | 31  |

|                                            |     |

| Introduction:                              |     |

| Data Acquisition and Control Applications  | 33  |

| An A/D and D/A Convertor                   | 33  |

|                                            |     |

|                                            |     |

|                                            |     |

| Chapter One:                               |     |

| The 6522VIA I/O Board                      | 35  |

| Programming the Ports of the 6522VIA Board |     |

| Programming a Visual Display Indicator     |     |

| Using the LED Visual Display               |     |

| USING the LED VISUAL DISDIAY               | 40  |

| Chapter One:                                                |     |

|-------------------------------------------------------------|-----|

| Bar Graph 2 Demonstration                                   | 40  |

| Programming the 6522 Internal Timer                         | 41  |

| Timer Operating Modes                                       | 42  |

| Line Comments: Square-Wave Generator Using the 6522         |     |

| Another Project With the 6522 Timer                         |     |

| Using the Timer as a Counter                                |     |

| Programming the Internal Shift Register                     |     |

|                                                             |     |

| A Variable Duty-cycle Square-wave Generator                 |     |

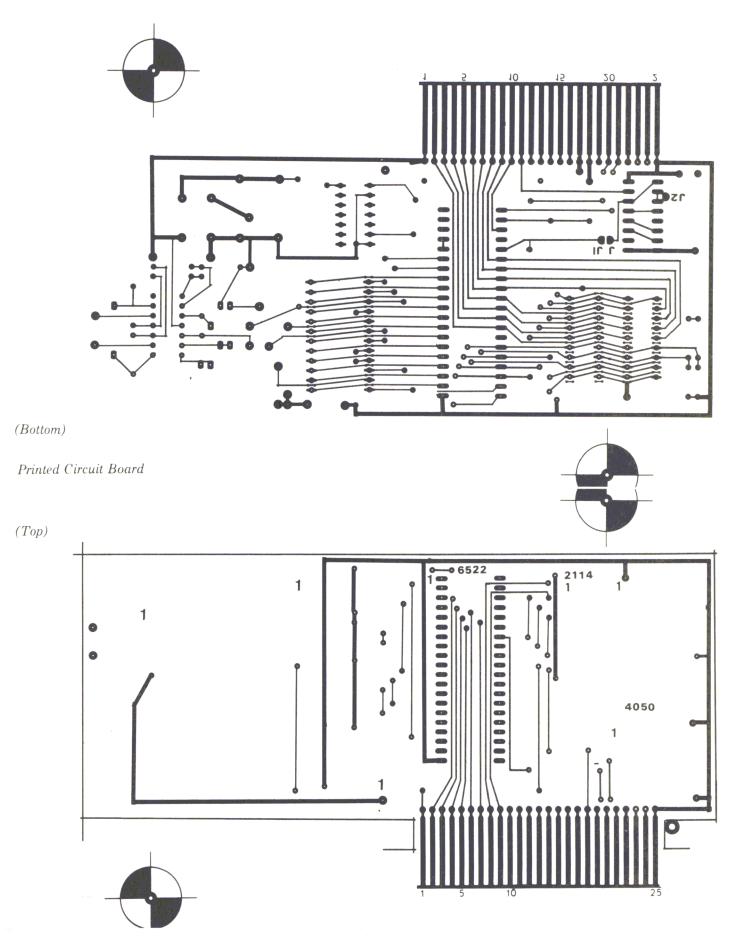

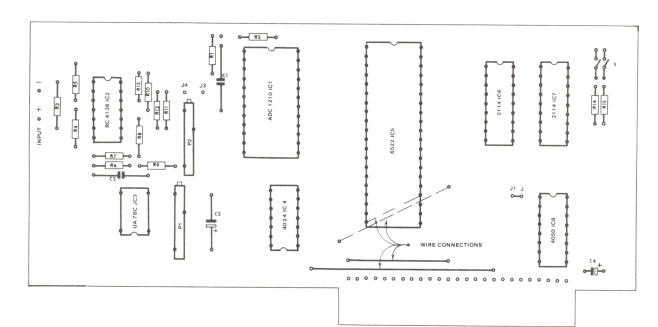

| Constructing the 6522 I/O Board                             | 51  |

|                                                             |     |

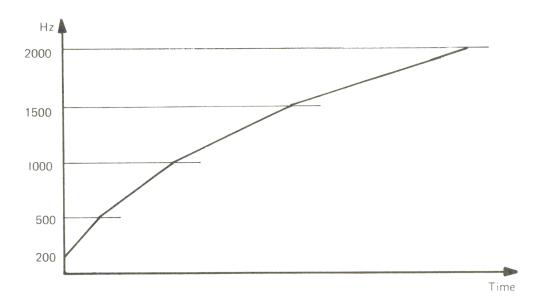

| Chapter Two: Sound and Noise Generation Using the AY-3-9812 | 50  |

|                                                             |     |

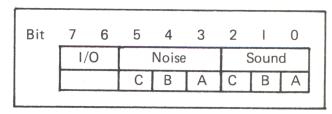

| How the Internal Registers Work                             |     |

| Programming the GI Soundchip                                |     |

| Programming an Example Gunshot                              |     |

| Program PIANO                                               |     |

| Sound Demo for the AY-3-8912                                |     |

| Program Description                                         |     |

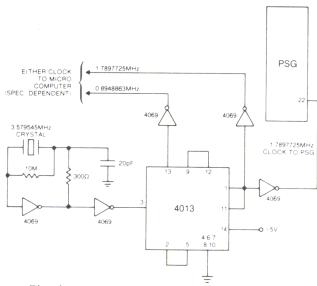

| Assembling a Sound Generator Board                          | 65  |

|                                                             |     |

| Chapter Three:                                              |     |

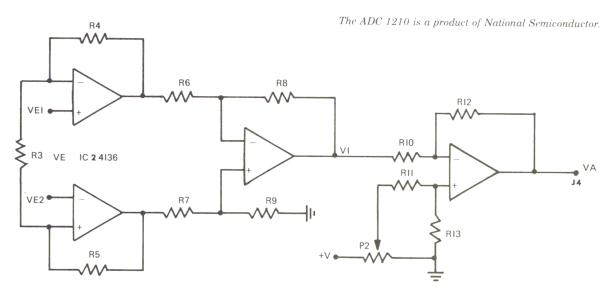

| An 8-Bit D/A and A/D Convertor                              | 67  |

| Resolution                                                  |     |

| Accuracy                                                    |     |

| Quantizing Error                                            |     |

| Conversion Rate / Clock Rate                                |     |

| Using Two D/A Convertors                                    |     |

| A/D Conversion with the ADC1210                             |     |

|                                                             |     |

|                                                             |     |

| Chantan Farm                                                |     |

| Chapter Four:                                               | O.F |

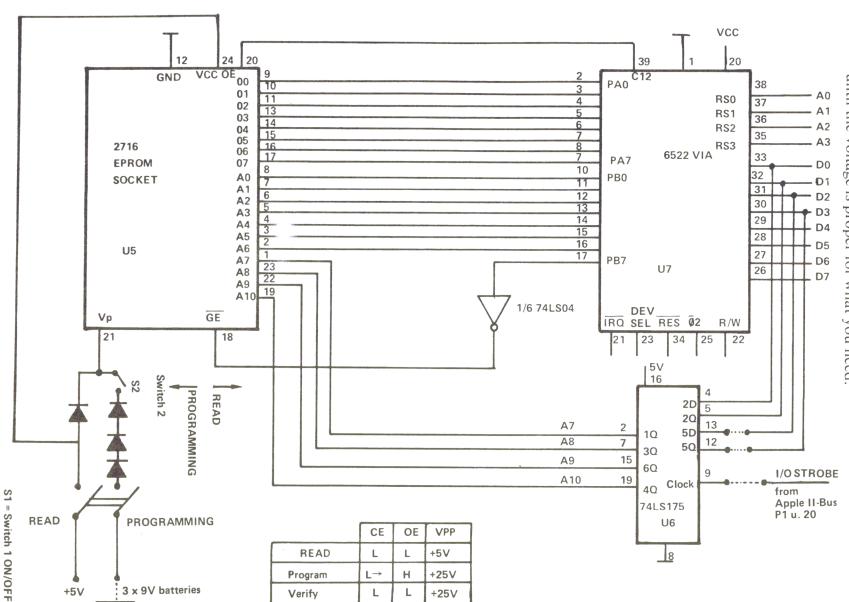

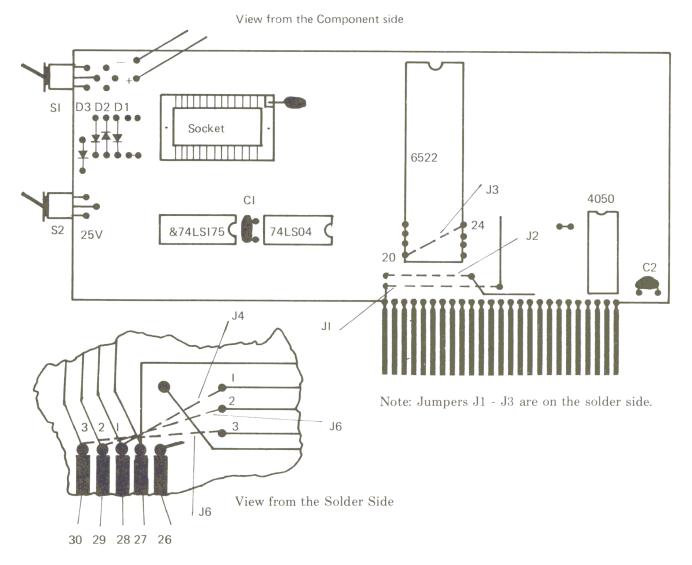

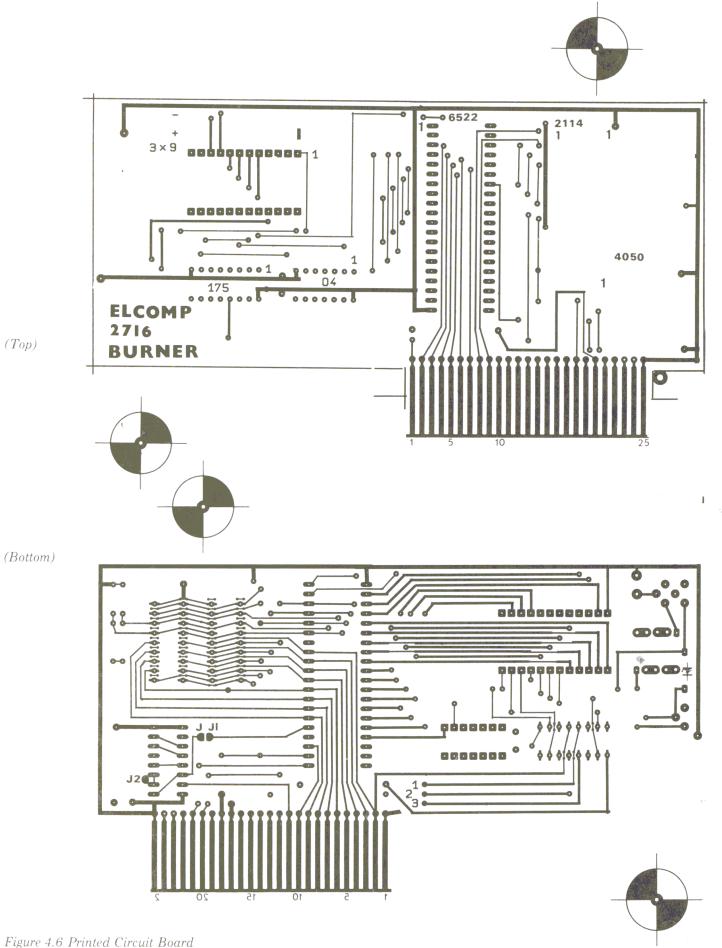

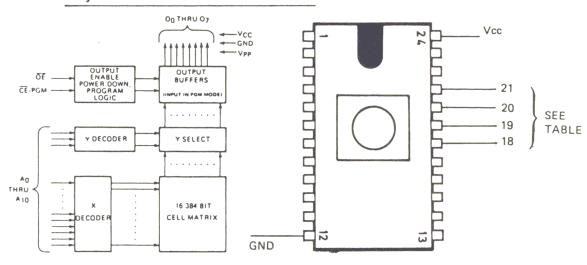

| An Eprom Burner for the Apple Computer                      |     |

| Using the Eprom Burner                                      |     |

| Using the Software                                          |     |

| Testing an Eprom                                            |     |

|                                                             | 100 |

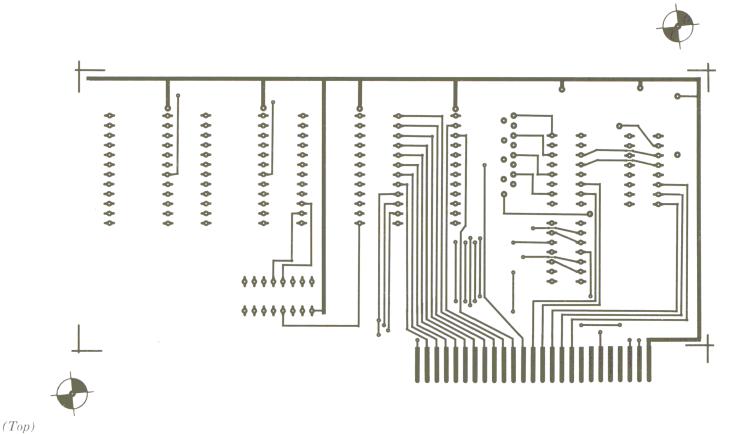

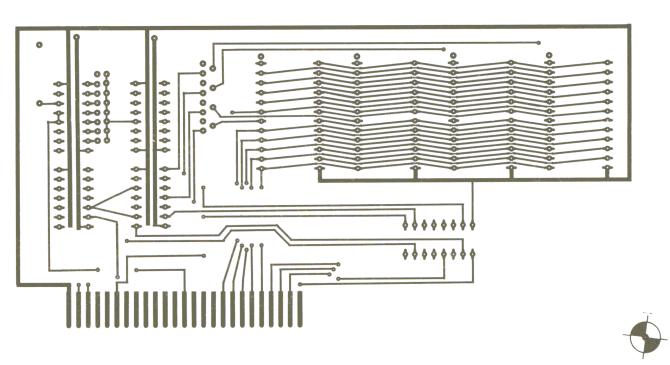

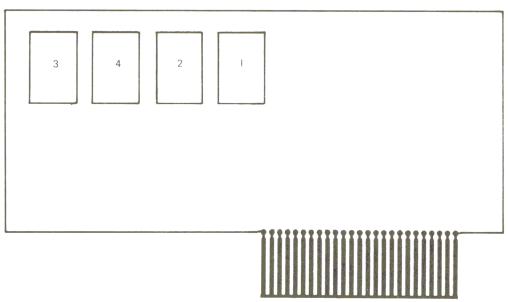

| Assambling the Enrom Rurner Roard                           | 101 |

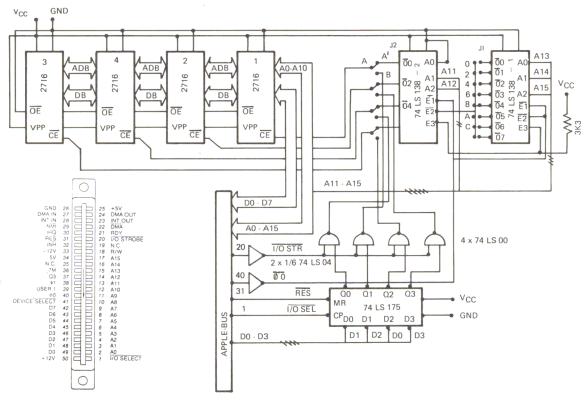

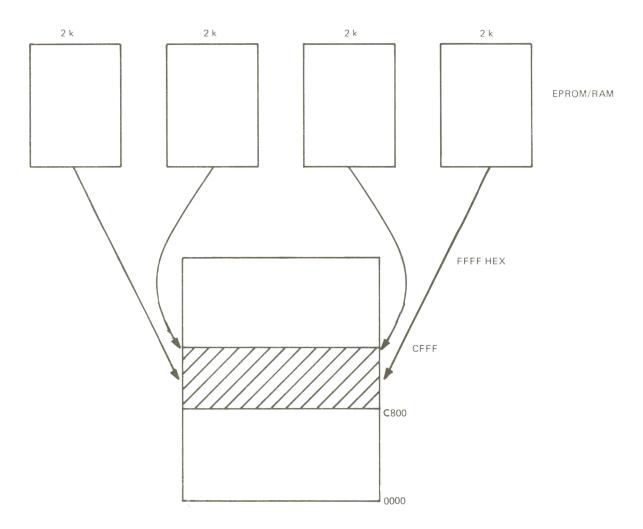

| Chapter Five:                         |     |

|---------------------------------------|-----|

| Assembling an Eprom/RAM Board         | 113 |

| Bank-Select Circuitry and Programming |     |

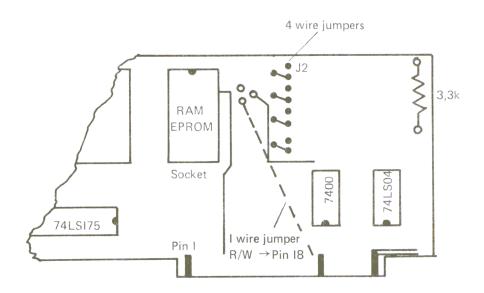

| How to Assemble the Board             | 120 |

|                                       |     |

|                                       |     |

|                                       |     |

|                                       |     |

| Chantan Chan                          |     |

| Chapter Six:                          |     |

| The Apple Slot Repeater               |     |

| How to Assemble the Board             | 124 |

|                                       |     |

|                                       |     |

|                                       |     |

| Chapter Seven:                        |     |

| The Coupling of Two 6502 Systems      | 131 |

| Program Description                   |     |

| 2 rogram 2 osoripuon                  | 101 |

|                                       |     |

|                                       |     |

| Chapter Eight:                        |     |

| Connecting Other Microprocessors      | 135 |

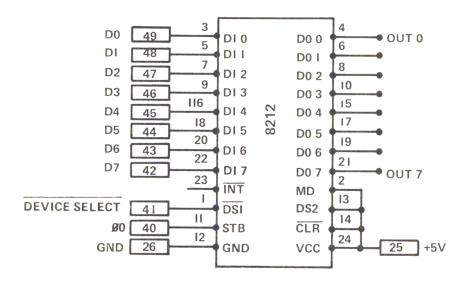

| The 8212 8-Bit I/O Port               | 135 |

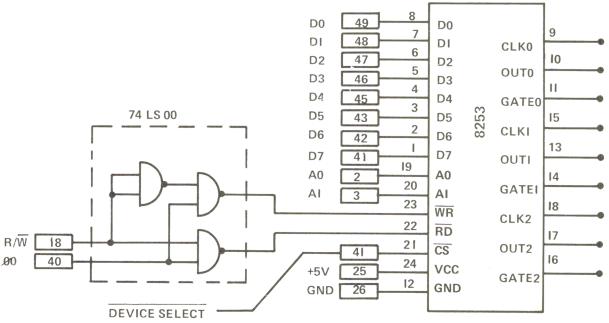

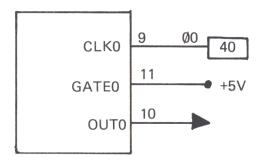

| The 8253 Programmable Interval Timer  | 136 |

| Mode 0: Interrupt on Terminal Count   |     |

| Mode 1: Programmable One-Shot         | 139 |

| Mode 2: Rate generator                | 139 |

| Mode 3: Square-wave Rate Generator    | 139 |

| Mode 4: Software Triggered Strobe     |     |

| Mode 5: Hardware Triggered Strobe     | 140 |

| Additional Information on the 8253    | 140 |

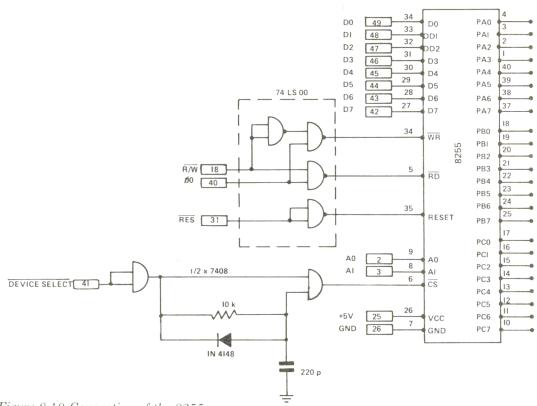

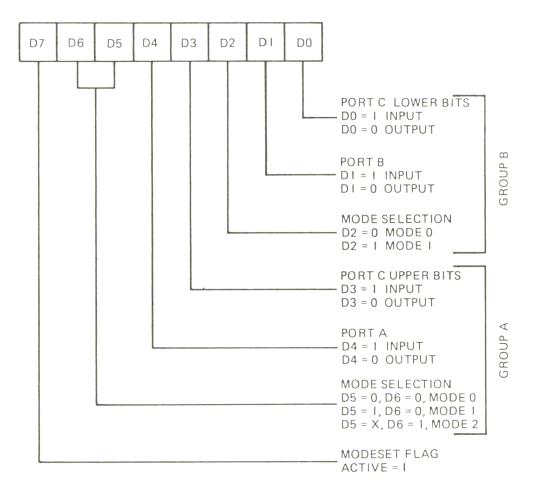

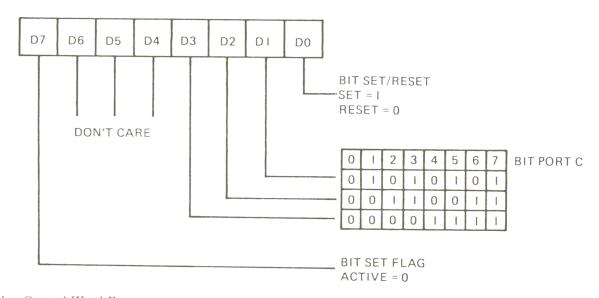

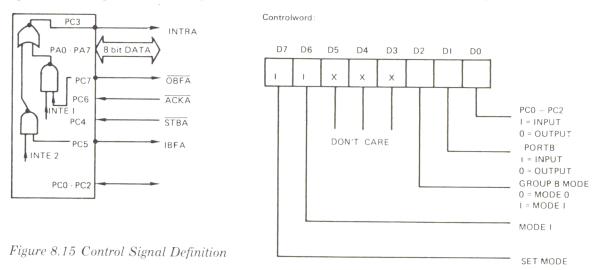

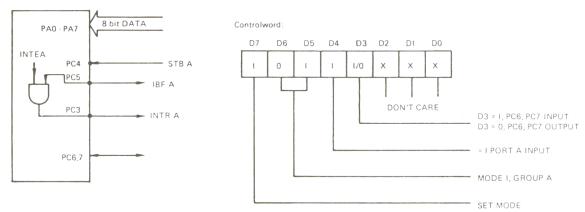

| The 8255 Programmable Interface       | 141 |

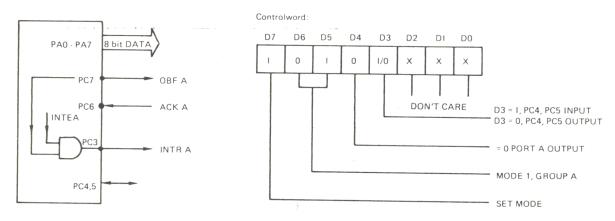

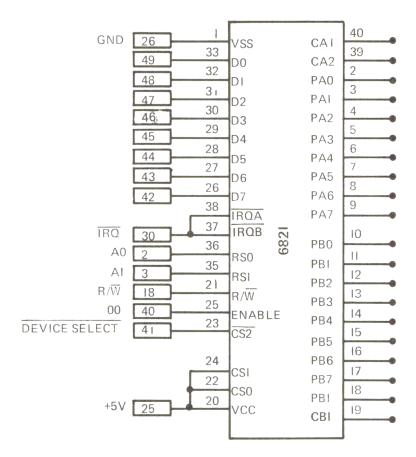

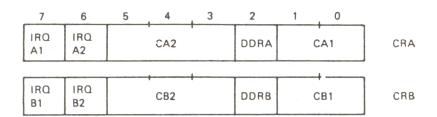

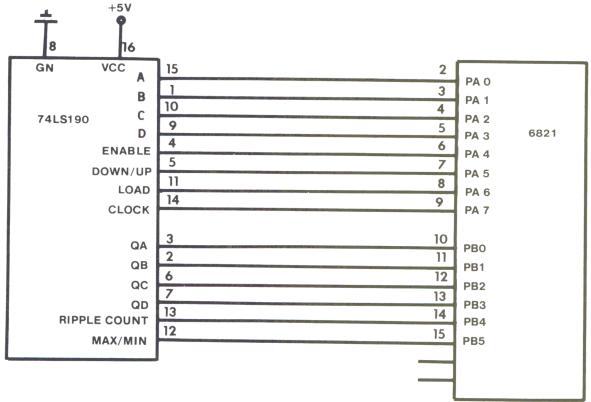

| The Interface Adapter PIA 6821        | 148 |

| The Apple as a Logic Tester           | 153 |

|                                       |     |

|                                       |     |

|                                       |     |

| Chapter Nine:                         |     |

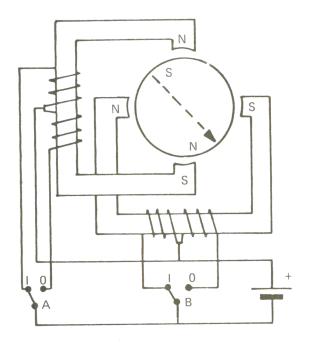

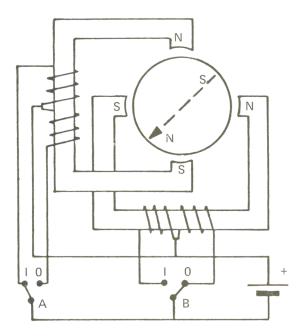

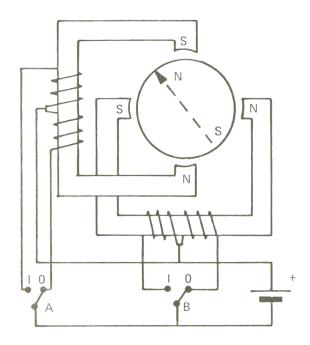

| The Control of Step Motors            | 161 |

|                                       |     |

|                                       |     |

| Appendix                              | 182 |

| Glossary                              | 184 |

### General Information

For those of you who have not previously done many hardware modifications or detailed analyses of schematic diagrams, this general information section gives easy to understand tips on the tools you will need, logic diagrams, binary and decimal numbering systems, and wire-wrapping and soldering techniques.

### The Tools You Will Need

Your basic APPLE II Computer, with some attachments and software, is a thousand-dollar item. So I'll not encourage you to use dime-store tools. Buy the best you can afford, keep them clean, and reserve them just for use on the APPLE. Don't double up tools with the family auto. You may not need them all, but here is my customizer's toolbox:

A medium-sized flat-blade screwdriver and Phillips blade screwdriver (a reversible combination is ideal). With these you open cases and remove cabinets.

A jeweler's set of flat and Phillips blade screwdrivers; hex nut drivers are optional. These drivers can be used to align tape heads, help make delicate wire bends, adjust trimmer controls and even repair watches.

One very thin screwdriver for lifting integrated circuits out of sockets. This will be its only purpose, but the first time you break the pins off a \$10 jumper cable, you'll wish you'd used it!

Small scissor-type cutters (manicuring types are excellent). These will be used for snipping leads in tight spots.

Small diagonal wire cutters and/or front-cutting 'nippers'. Your general purpose cutters. They are fast and easy to use, but not to be used for heavy wire around the house.

**Needlenose pliers** (two pairs, normal and 90-degree types). You'll need these for bending leads, also extracting bits and pieces you've dropped into a nest of wiring.

An X-acto type knife, with a strong blade and handle you feel comfortable with. Since this will be used to cut delicate solder traces, you should be able to handle it deftly. I use a single edged razor blade, but have leather fingers!

A scalpel, if you can get one. For very delicate trimming and scraping; a dental pick for pulling off solder balls or lifting parts off a board (get this item from an obliging dentist — they are often discarded when worn); tweezers and needle point hooks. The latter comes in handy for tracing incorrect wirewrapping connections.

Rat-tail, triangular, and flat files. These are only for sprucing up the cosmetics, so if you don't care how it looks, save a few bucks.

A wire-wrapping tool. The decision on this can be tough. If you can afford it, get one of the electrically operated slit-and-wrap types, stay away from 'just wrap' tools, since they depend on the sharpness and quality of the sockets; also they are useless for wrapping capacitors or resistors. I use a simple double-ended tool sold by Radio Shack for about \$5. It wears out after a thousand or so connections, but it fits my hand well, and is not clumsy like some electric units.

A soldering iron. The decision is not easy. Should you spend top dollar and get an expensive one or buy a cheap unit that can be discarded when it wears out? I use a \$5 soldering iron which can be junked when it gets beat, but my editor uses the best he can get (a \$30 temperature-controlled one). I file a set of \$1 tips to my satisfaction, and lubricate the threads with white heat sink grease. This way I have a few different tips at my disposal. You **never** file plated tips.

A Multimeter. The voltage regulators in your Apple are very good, so any problems will usually show up as gross errors. This offers you a way out of buying an expensive multimeter; for most of these projects, the \$10 pocket variety will suffice. However, for lots of repair work a better meter is in order; I use a \$40 type (not digital!) for my work.

An oscilloscope. For the projects, no. But for repairs, yes. Don't panic thinking of a thousand dollars for a digital scope, because an old color television scope will do perfectly well; they can be found in the bargain bins for \$50 to \$100. If it saves you a \$100 repair bill, you've paid for it. Mine is an old RCA type WO-90Q, built for early color TV, and just fine for the bulk of your Apple work.

You will also need supplies in the tool box. Among these are:

**Solder.** Get the best you can afford. There's nothing so unpleasant as a great glob of the stuff between two traces on a board. Order the multicore rosin flux type, and stay away from most of the off-the-shelf stuff. Remember, multicore rosin type only, and the finer the gauge the better. **Never use acid flux solder,** as used by plumbers and electricians.

Soldering wick. Marketed under the names Spirig, Solder Up and Solder Wick, it's a copper braid impregnated with soldering flux. When heated with the soldering iron it absorbs Solder off the board, thus freeing components. Don't do without this stuff unless you like fried circuit boards and burnt fingers.

Wirewrap wire. Also called by the tradename Kynar, this is 28-or 30-gauge single-strand wire used to interconnect the pins of wire wrap sockets. It comes in an assortment of colors; get them all, so you can keep data, address, power and ground lines separate.

Multiconductor cable. The more flexible wire is easier on the coordination, but also the most expensive. Best buy is Spectra Twist, and its kin, from surplus houses. If you need jumper cables, buy them; Making a two-ended, 40-pin jumper cable can be three hours of maddening work.

Bus wire. This is solid, uninsulated stuff. A small roll will do for a lifetime. I use it for wiring, securing bulky capacitors to circuit boards, holding bundles of things together and for making special tools.

Miscellaneous. Sockets, perforated board, mounting hardware, and such will always be needed.

Details about supplies needed for each project in this book will be presented with the project. Except for integrated circuits, most of the items are available right off the shelf at a local Radio Shack or other electronics supply house.

### **Schematics**

Schematic drawings of electronic circuits are identical to maps. They show routes, direction, junctions, relative importance and functions of locales, two-way and one-way streets, traffic flow and congestion and so forth. At first, the symbols may seem like the mysterious hieroglyphics of a secret society, but their symbolism can soon become as familiar as a roadmap. Even strange places can be assessed from afar.

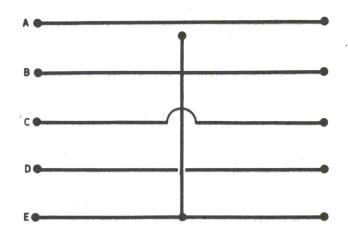

First, the symbols. A line is a wire running from some point in the circuit to another. Consider the sketches below:

The first drawing is a simple wire. The electrical path moves from one point to another, in either direction. By following the path of a wire point to another, in either direction. By following the path of a wire through a circuit, the pattern of connections can be discovered. When wires are forced to cross one another, but not to connect with each other, it must be made clear. On a roadmap, non-intersecting roads are shown either by a break in one of the intersecting lines, or in showing interstate highways, merely by crossing one 'below' the other in a different color.

Sketches b, c and d are the three ways of drawing wires which do not connect to each other. The first, simple crossing them, is the most common. The second method places a semicircular bump in the crossing path, and it used by Sams Publications in this country and commonly in Europe. Occasionally the broken path crossing shown in sketch d is used.

When wires connect, a dot is used to clarify that a connection is to be made. Occasionally, you may come across earlier schematics which use the 'bump' method of showing unconnected wires. On these schematics, the lack of a bump indicates wires are connected.

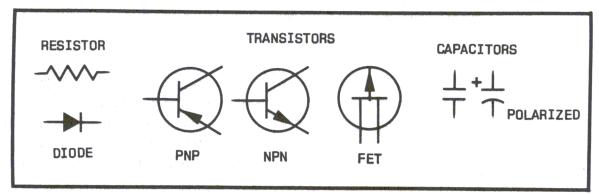

The wires (or patterns of copper etched on circuit boards) connect electronic components. Some of them are:

Since this is a lesson in reading schematics and not electronic theory, I recommend that you turn to an excellent book by Forrest Mims, 'Engineer's Notebook', sold by Radio Shack, for an introduction to what each of these parts does. Briefly, the symbol for a resistor has the flavor of a long wire being compressed, meaning the electrical flow is somehow being resisted. The innards of a capacitor generally consist of metal foil separated by a non-conducting paper or plastic, and the capacitor's schematic symbol is fairly representative, with two plates facing each other but not joining.

Some capacitors are designed to fit into a circuit in only one direction; these capacitors are identified on their bodies by a positive or negative sign. Another one direction (polarized) device is the diode. It consists of an arrowhead striking a barrier, implying that current may flow in the direction of the arrowhead, but not back across the plate. The body of a diode may have the diode symbol imprinted on it, or a band to indicate the 'barrier' end.

The transistor usually has three connections (such connections are called 'leads' on small parts such as these). These leads are identified as collector, base and emitter or source, gate and drain, depending on the transistor type. This will be shown on the diagram, and the transistor will be imprinted with the information, or it will be provided on the package in which the transistor is sold.

### A few other symbols are:

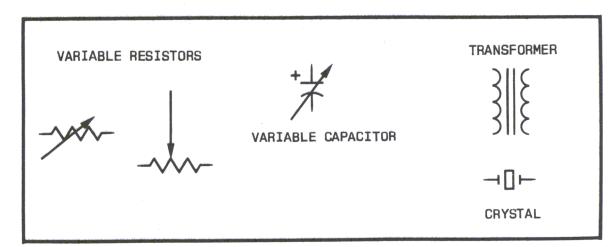

The first is a transformer, whose job it is to take current fed into one coil and induce that current, into a second coil. An iron or ferrite center (the parallel lines in the symbol) aids in efficent transfer of that current.

The next three symbols look like resistors and capacitors, which they are. The added arrows show that their values may be varied; hence, they are called variable resistors and variable capacitors. The variable resistor is best known as the volume control on a television, and the variable capacitor is found as the tuning control on a table radio.

The last symbol is a crystal, a piece of cut quartz capable of vibrating (resonating) under certain electrical conditions. Because a crystal is a very accurate, fixed, molecular device, it's capable of resonating (also called oscillating) at precise intervals. It is used for the master control of all pulses in the APPLE.

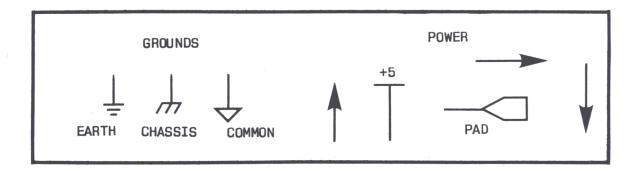

A few directional symbols are now in order:

The first are known as grounds, and they are used to indicate a potential of zero or neutral voltage. The first of the trio is an earth ground, commonly used in radio, television and hi-fi schematics, but purist use it only describe an actual connection to a ground spike or cold water pipe. The second is a chassis ground, indicating an electrical connection to the metal case which encloses the circuit. It is often (though incorrectly) interchanged with the earth ground.

The last of the three grounds is a 'common' or neutral ground, and the one which is used to indicate the zero voltage line in the computer. All other voltages within the computer system are described in terms of their relation to this ground.

The next quartet of symbols indicate power. The up arrow generally points to an actual voltage value (such as +5 or +12). The horizontal line indicates merely a 'high' is made to the normal positive power supply for the circuits in the system (+5 volts in the TRS-80).

Non-positive voltages have no standard symbols. Negative (or below ground) voltages can have either a horizontal arrow or a down arrow, pointing to the voltage desired at that point. The schematic tells you that a connection is made to the voltage level shown.

Another use of a horizontal arrow is to point to important connections to be made elsewhere on the schematic or on other sheets of the schematic. In the former case, the arrow is used because actually drawing the wire may clutter the schematic, making it illegible. When you see an arrow, be sure to find the other end of the connection described (indicating words such as 'clock', 'mem' or 'port FF' may be used as guides to where the connection is made).

Another useful symbol is the last of the group above, the pad. It indicates a significant connection, usually to another device or circuit board. Using this symbol makes it clear that the connection is to be made somewhere off the board on which you are working.

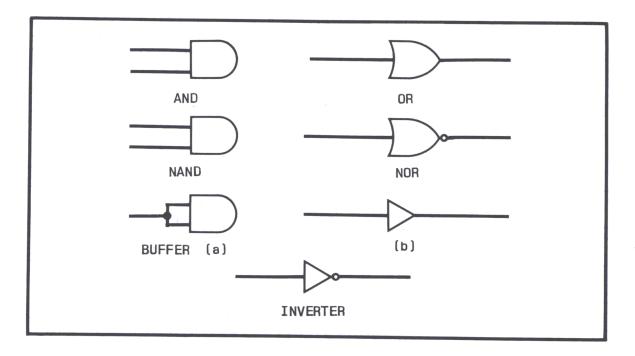

The most common families of parts found in computer circuits are shown below:

These symbols represent integrated circuits, those multiple lead, buglike packages that handle the bulk of the work in the computer. Briefly, these are logical building blocks. Sometimes there are several blocks in one integrated circuit, and these various blocks may be scattered throughout the circuit diagram. This can be confusing when actually building a circuit, but since pin (lead) numbers are given, you only have to remember where you put the part.

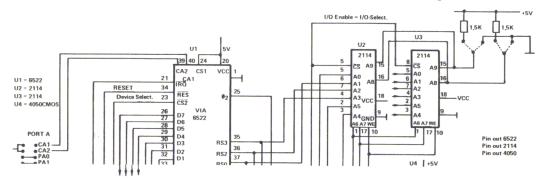

Basically, that covers reading a schematic roadmap. Below is a section of circuit. See how the logic elements are connected to each other. An arrowhead indicates a wire leading off the board, and power and ground connections are shown. The numbers on the logic elements are the pin numbers for the component connections:

### Be Tolerant

Every electronic component is manufactured to work within specific limits. whether they be accuracy, temperature, speed, power use or other limit. These are the components parameters or tolerance. The circuits in this book have been designed to use the most commonly available parts, so the matter of tolerances is rarely important. However, sometimes those tolerances are important, such as when talking about memory speed or power supply voltages.

Power supply should be within five percent of the voltage specified: a supply indicated at five volts may vary only from 4.5 volts to 5.5 volts. By using the power supply regulators shown in the schematics, these voltages should not be of concern. Unless you are familiar with power supply design, do not attempt to use other methods of regulation.

Very few of the resistors have tolerances noted on the schematics. The rule of thumb is one quarter watt at five percent, but if you can only obtain half watt units, or 10 or 20 percent resistors, don't be concerned. The quarter watt resistors are a bit less costly and are a bit more aesthetically appealing. Consider also that if a resistor is specified as 1,000 ohms, a 20 percent deviation gives a range of 800 ohms to 1,200 ohms. Thus, the standard values of 910 ohms or 1,200 ohms should do as well.

Capacitors are notoriously sloppy in their tolerances, especially electrolytic types (those whose polarity is marked on the schematics). These normally vary from 20 percent low to more than 100 percent high — thus, when a 500 microfarad capacitor is noted, it can range from 400 to 1,000 microfarads. Also, there is some revision in the standard numbering method used for parts values: 470 microfarads is now being called 500 microfarads, for example. So when you try to obtain a capacitor value marked in the parts list, remember that a nearby higher value is fine.

Voltage parameters for polarized (electrolytic) capacitors are important. Never get an electrolytic capacitor with a value less than that specified, but do not hesitate to take one with a higher voltage parameter. That is, a capacitor specified at 47 microfarads, 16 volts, can be replaced with one specified at 50 microfarads, 35 volts. It may be physically larger, but it will work equally well.

If you walk into a store and hand the sales clerk a parts list, don't be surprised if you are asked a few more questions. You might be faced with chosing between parts which are identical as far as the parts list in this book is concerned, but which include other parameters.

Resistors can be carbon composition, carbon film, glass or wire-wound. These days, carbon film is common and cheap, and that's your first choice. Carbon composition is the next choice at a lower quality, and glass is excellent but at a higher cost. Forget wire wound, because they can contribute unwanted side effects.

Ordinary capacitors are manufactured in many ways: ceramic, polstyrene, polyester, silver mica, polycarbonate and paper. For the bypass capacitors necessary for all the circuits in this book, ceramic types are your choice. Cheap. If you get silver mica, so much the better, but you'll pay a price. Watch out for polystyrenes or polyesters if you plan to solder, because they are delicate and you can damage them with too much heat. Otherwise they are excellent, but quality overkill. Polycarbonates are slick types, and you might consider using these if you build the 8-track mass storage system. Run the other way if you see paper capacitors.

Electrolytic capacitors come in two basic types — metal cans (covered with plastic), and those manufactured using tantalum (an expensive metal of great strength and purity). For most digtal projects, choose the ordinary cans. Tantalums of the same value, although smaller, high quality, and very pert looking, are costly and not required here.

Digital integrated circuit part numbers are generic, which means that a 74LS00 circuit might be sold as an SN74LS00 or an NEC-74LS00. The prefix characters refer to manufacturers. On the other hand, those parts whose numbers contain 'LS' may not be substituted by parts marked 'S' or 'C' or by those with no markings. 74LS00 may not be replaced by 7400, 74S00, or 74C00, nor may they be exchanged for each other. When integrated circuits are specified, try not to substitute with other circuit 'families'.

This section will not make you a master schematic reader; only practice will do that. Pick up copies of the Engineer's Notebook mentioned above, as well as various of the project books sold by Radio Shack and others.

### Those Colors: What They Mean and How to Read Them

The color codes used for resistors, capacitors and other parts are brought to you by the same folks that brought your phrases like 10W-40 and RS-232C: the standards-setting powers of the engineering industry. It becomes an international shorthand.

The colors are black, brown, red, orange, yellow, green, blue, purple, grey and white. If you can't immediately remember that, then pick up a piece of multiconductor "rainbow" cable. The colors are all there in the same order. The table below presents the color codes and how they can be read on the bodies of resistors, capacitors and diodes.

|        | AND SECOND<br>R BANDS | THIRD COLOR BAND   |

|--------|-----------------------|--------------------|

| BLACK  | 0                     | BLACK O            |

| BROWN  | 1                     | BROWN X 10         |

| RED    | 2                     | RED X 100          |

| ORANGE | 3                     | ORANGE X 1000      |

| YELLOW | 4                     | YELLOW X 10,000    |

| GREEN  | 5                     | GREEN X 100,000    |

| BLUE   | 6                     | BLUE X 1,000,000   |

| VIOLET | 7                     | SILVER 100         |

| GRAY   | 8                     | GOLD 10            |

| WHITE  | 9                     |                    |

| FOURTH | COLOR BAND            | IS THE TOLERANCE   |

| GOLD = |                       | R = 10% NONE = 20% |

What do these values mean? Resistance is a kind of objection to electron flow, measured in ohms (pronounced with a long O). The abbreviation is a Greek omega ( $\Omega$ ). Thousands of ohms are kilo-ohms, or just kilohms and abbreviated K (k in Europe). Millions of ohms are megohms, abbreviated simply M. The ability of a resistor to withstand electrical current is measured in Watts (W). Most computer work is done with 1/4 Watt resistors.

For resistors without color bands, the values are stamped on using R (instead of omega) for ohms, K and M.

Capacitance is the inclination of a non-conducting object to store an electrical charge, measured in Farads. The abbreviation is a capital F. Since this is a very large amount of capacitance, real work is generally done in millionths of Farads, or microfarads (mF), and millionths of millionths of Farads, called picofarads (pF). Since many of the more popular capacitance ranges for computer work fall between these two figures, the abbreviation for thousandths of millionths of Farads, or nanofarads (nF) is common in Europe. The ability of a capacitor to withstand voltage is measured in voltage tolerance (V).

Capacitance is usually printed on the capacitor in mF; color bands are rare. Picofarads are marked "p"; the absence of an abbreviation indicated microfarads. Note that these capacitor "base values" are equivalent: 18=20, 27=30, 39=40, 47=50.

### **Copacetic Comprehension**

There will doubtless be a day when books like this will be unnecessary. Personal computers will probably develop into the appliance area, with programmers, hobbyists, hardware designers and language specialists present only in the distant background of the market. But until then, we are all faced with being either frustated users or solderer-programmers, tailoring machines according to our personal demands.

To do this, certain skills are inevitably required. Among these are an understanding of non-decimal number systems, digital logic devices, machine-level languages, and a smattering of diagnostic sense. There are some fine books that cover all these topics, so this chapter will only deal with them as far as needed to put this book to work. Among them are:

- Binary, decimal and hexadecimal number systems, how they arose, how and why

they can be used, and where understanding them is essential.

- Common digital logic devices that appear in the Apple and these projects, and how and where to use them.

- Some of the basic elements of machine language, and a few personal considerations on where it is best applied, and when BASIC is a better choice.

### **Number Systems**

Numbering is the single most overrated problem in computer programming. The answer (posed before the question) is this: numbers are merely *counting names*. That is, it makes no difference whether we think in tenths of a mile or eighths of an inch. Nor does it bother us that a day is made up of 24 hours, while an hour is 60 minutes. That a year is 365 days frightens us not, nor that months are a motley collection sizes.

In parking lots, does it bother us that our vehicle may be parked in Row N as opposed to Row 14? There is no mystery when we mark off points with four scratches and a crosshatch. And does a dozen always conjure up 'twelve', or is a dozen something we have understood since youth?

Names are sizes are numbers; so it is with the number systems that we arbitrarily assign for the convenience of working with computers. When we are talking about electrical signals, it is clearest and easiest to think about ons and offs. Ons look pretty much like ones, and offs look like zeros. It's a nice, clean concept and one that illuminates the way we can refer to the machinery.

There's more convenience to naming a computer data condition 10110100 than to calling it an on off on on off on off off. Were data the only consideration, the binary one and zero method might have been satisfactory, without resorting to other means of stroking our memories.

Finding a location in a computer's memory is a much more difficult task. Although a memory location called . . .

### 111010001001101010

... might be easier to think about than ...

on on on of fon of fof fon of fon of fon of fon of fon of fon of fon on one of the following states of the following states

. . . it could use another step forward. In music, a long string of sixteenth notes like this —

Illustration of Illegible Musical Notation

— is broken up to make it legible, so it looks instead like this —

Illustration of Legible Musical Notation

Likewise, that long binary string can be broken up from 1101000100110101 into convenient groups . . .

### 1101 0001 0011 0101

... although the legibility is improved, the human spark, the ability to look and recognize (that *aha!*) is not there. So the next step is to set about naming the sections. Since these on-off conditions can be written down as binary numbers, why not write them down in their decimal equivalents?

The question is rhetorical, of course, because not only can it be done, it is done. The only question is how to do it. Were a computer capable of swallowing all sixteen of those binary digits (bits) in one gulp, that question might be easily answered by calculating the conversion of 1101 0001 0011 0101 using a binary-to-decimal conversion table. The result, we find, is 53557.

But the computer, alas, cannot swallow all those bits in one bite . . . it can only swallow one bite full of bits (pardon). In other words, though a computer may need numbers sixteen bits long, only eight data lines exist to carry that data. The component parts of the number 1101000100110101 are needed, eight bits at a time: 11010001 00110101.

There's the mathematical rub. 11010001 is 209 decimal, and 00110101is 54 decimal. This seems hardly related to 53,557. Another solution is necessary, and it is a naming system as much as a numbering system. It names each of the sixteen possible combinations of four binary digits:

| 0000 | is | named | 0 | and | is | equal | to | decimal | 0  |

|------|----|-------|---|-----|----|-------|----|---------|----|

| 0001 | is | named | 1 | and | is | equal | to | decimal | 1  |

| 0010 | is | named | 2 | and | is | equal | to | decimal | 2  |

| 0011 | is | named | 3 | and | is | equal | to | decimal | 3  |

| 0100 | is | named | 4 | and | is | equal | to | decimal | 4  |

| 0101 | is | named | 5 | and | is | equal | to | decimal | 5  |

| 0110 | is | named | 6 | and | is | equal | to | decimal | 6  |

| 0111 | is | named | 7 | and | is | equal | to | decimal | 7  |

| 1000 | is | named | 8 | and | is | equal | to | decimal | 8  |

| 1001 | is | named | 9 | and | is | equal | to | decimal | 9  |

| 1010 | is | named | Α | and | is | equal | to | decimal | 10 |

| 1011 | is | named | В | and | is | equal | to | decimal | 11 |

| 1100 | is | named | С | and | is | equal | to | decimal | 12 |

| 1101 | is | named | D | and | is | equal | to | decimal | 13 |

| 1110 | is | named | Ε | and | is | equal | to | decimal | 14 |

| 1111 | is | named | F | and | is | equal | to | decimal | 15 |

This may seem overdone; but A, B, C, D, E, and F are darn good names for binary values which exceed the number nine. If you don't have a name, make one up. For practical purposes, keep it within the symbols everyone has on the typewriter.

Back to the number 1101000100110101. Crack it into those four legible pieces (1101 0001 0011 0101), and it can be named D135. To convert it to decimal, remember the old rule: the 5 is in the ones place, the 3 is this time in the sixteens place, the 1 is in the two-hundred-fifty-sixes place, and the D is in the four-thousandninety-sixes place. Thus, **D135** is 5 plus 3 x 16 plus 1 x 256 plus (see the chart) 13 x 4,096, or . . . 53,557!

So, now that long binary number can actually be digested by the computer as a byte of **D1** and a byte of **35**. After a while, the number system comes easily. My personal recommendation: work in it. Convert to decimal only when you absolutely must. Think in hexadecimal and binary. They are the tools with which you can speak to the computer.

Throughout this book, numbers in hexadecimal are printed in BOLD.

### **Converting Binary to Decimal**

In the grade school years, students used to learn that a number like 5,163 contained a 3 in the ones place, a 6 in the tens place, a 1 in the hundreds place, and a 5 in the thousands place. It was to remind them that 5,163 was really 3 plus  $60 (6 \times 10)$  plus  $100 (1 \times 10 \times 10)$  plus  $5,000 (5 \times 10 \times 10)$ .

The way other number systems are written follows this same pattern for their own bases. In base eight the number 5,163 would have a 3 in the ones place, a 6 in the eights place, a 1 in the sixty-fours place, and a 5 in the five-hundred-twelves place. That means that 5,163 is really 3 plus 48 (6 x 8) plus 64 (1 x 8 x 8) plus 2,560 (5 x 8 x 8 x 8). But notice how that's decimal thinking! Really in base eight there could be no '8' . . . it would have to be called '10'! 1, 2, 3, 4, 5, 6, 7, 10, 11, 12, 13, 14, 15, 16, 17, 20, and so on. So 5,163 in base eight is still 3 plus 60 plus 100 plus 5,000!

The binary system sneaks in the same way. A number like 1101 0001 0001 0001 turns into a 1 in the ones place, a 1 in the twos place, a 0 in the fours place, a 0 in the eights place, all the way up to a 1 in the thirty-two-thousand-seven-hundred-sixty-sevens place. In binary, the one on the far left is still a 1 in the quadrillions place, don't forget. But the message is how to convert all this to decimal. And here it is:

```

32768 16384 8192 4096 2048 1024 512 256 128 64 32 16 8 4 2 1

1 0 1 0 0 0 1 0 1 0 0 1 0 0 1 1

```

Just add the numbers: 1x1 + 1x2 + 0x4 + 0x8 + 1x16... + 1 times 32,768 + 41,619. Voila. No matter how long the number is, and in whatever base:

- 1. Start at the left and produce a chart of the base number's powers, starting with 0 (X to the 0 power is always 1).

- 2. Lay the number to be converted underneath the base number chart.

- 3. Multiply each base number power by the digit in its place.

- 4. Sum the resulting numbers.

| Base 9 powers: 9 to that power: Number to convert: Multiplication: Subtotals: Converted result:                | 1<br>1 x59049<br>59049 | 6<br>6 x 65 6 1<br>+ 3 9 3 6 6  | 3                             | 3<br>3 x 8 1<br>+ 2 4 3 | 1<br>9<br>4<br>4x9<br>+36 | 0<br>1<br>1<br>1x1<br>+1 |

|----------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------|-------------------------------|-------------------------|---------------------------|--------------------------|

| Base 7 powers:<br>7 to that power:<br>Number to convert:<br>Multiplication:<br>Subtotals:<br>Converted result: | 1<br>1×16807           | 2401<br>6<br>6×2401<br>+14406   | 343<br>3<br>3×343<br>+1029    | 3<br>3 x 49             | 1<br>7<br>4<br>4×7<br>+28 | 0<br>1<br>1<br>1×1<br>+1 |

| Base 10 powers: 10 to that power: Number to convert: Multiplication: Subtotals: Converted result:              | 100000<br>1<br>1×10000 | 10000<br>6<br>0 6×100<br>+60000 | 1000<br>3<br>000 3×1<br>+3000 | 100<br>3<br>000 3×10    | 10<br>4                   | 0<br>1<br>1<br>1x1<br>+1 |

### **Digital Logic Devices**

The binary number system and digital logic devices were developed together as a way of solving a practical dilemma: how to mass produce computers which could work quickly and accurately, and yet be inexpensive. The problems of creating consistently accurate circuits, working with many different voltages levels, are formidable. Thus, simple yes-no, on-off logic was developed.

The intimidating term Boolean algebra is being used for the first, and last, time in this book — right in this sentence. You'll probably hear the phrase from time to time, but no matter — it's a professional's buzzword to keep the masses out. Forget it.

Back to digital logic devices. The essence of digital logic is to evaluate binary, onoff input; sometimes to determine a pattern of similarity or difference, sometimes to sense a change and sometimes to search for a signal. An appropriate result is produced as a result of the logical operation.

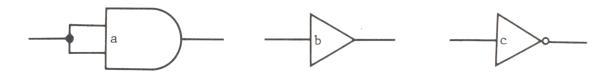

One of the logic building blocks is called a gate. A gate electronically evaluates its input to determine the pattern of similarity and difference of signals, and produces a specific output. A simple gate is shown below:

Its job is to determine if the first AND second inputs are both at the one (high) level. Only under that condition will its output produce a high (one) signal. The table below shows how this AND gate works.

AND Gate

| If input #1 is -                                                                                                   | If input #2 is -                        | The output result is -                                                                                          |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Contractive grave discordance dates discording a given discordance discordance discordance discordance discordance | dina dina dina dina dina dina dina dina | Min-differ down Since Water State State State State Controller or got to down down down down down down down dow |

| G                                                                                                                  | 0                                       | 0                                                                                                               |

| 1                                                                                                                  | 0                                       | 0                                                                                                               |

| 0                                                                                                                  | 1                                       | 0                                                                                                               |

| 1                                                                                                                  | 1                                       | 1                                                                                                               |

AND Gate Action

The table is called a *truth table*, and its purpose is to present every possible input and output condition for a given gate. Below is an OR gate. Stated in words, if either the first OR the second input is high, the output will be high. Examine the OR gate truth table; it really is quite logical.

Simple OR Gate

OR Gate

| Input 1 | Input 2 | Output |

|---------|---------|--------|

| G       | 0       | 0      |

| 1       | 0       | 1      |

| 0       | 1       | 1      |

| 1       | 1       | 1      |

OR Gate Action

Given a huge set of interconnected gates and their known inputs, the final output of the group can be determined by using truth tables like these. Gates may have more than two inputs (some have sixteen), and may produce the opposite results from the two described above (NOT-AND and NOT-OR gates, known as NAND and NOR gates). Truth tables reveal how the integrated circuit's design engineer specified the pattern of binary logic inside the circuit.

In this way, given a desired output and a known number of input signals, it is possible to determine what set of input values will trigger the desired output.

There are a number of other types of digital circuits. Most are created out of gates like those described above, but their features are unique enough to think about them separately. Among these other digital logic circuits are buffers, flip-flops, counters, latches, multiplexers and shift registers.

A buffer can be thought of as a two-input gate with both inputs tied together, like this:

Buffer as (a) Two-input Gate, (b) Buffer and (c) Inverting Buffer

Its truth table is much simpler than that for two-input gates, because there are now only two input conditions. Either both inputs are high, or both inputs are low. Gates with 'true' outputs (AND, OR) will merely follow the input condition. When the inputs are high, the output is high; if the inputs go low, the output becomes low. Separate logic devices are manufactured that perform this 'follow-the-leader' function, and they are called *buffers*. They serve to isolate sections of a circuit, or rejuvenate a signal so it can feed many dozens of inputs in a large machine.

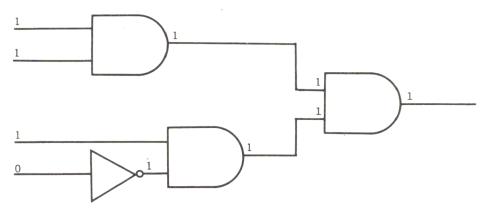

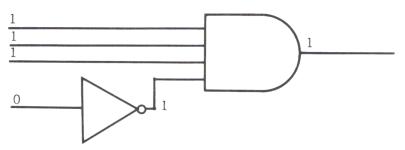

When a buffer reverses the condition of its input, (a high input is output low, and vice versa), the device is called an *inverter*. This kind of circuit can save the day in some cases, as when trying to locate a given binary number. Assume a circuit needs the binary number 1110 to turn on a pilot light. It is possible to choose four separate gates, each of which would provide an output matching the desired number. These would be connected through more gates, and eventually the number could be discovered when the final signal was triggered properly. One way of detecting 1110 is shown below:

Bad Decoding Scheme for 1110

But, although this circuit works, economy of cost and space and simple clarity dictate another solution. The last input could be inverted before it is evaluated, resulting in a pattern (1111) which could be quickly recognized by a multiple-input gate. The result is electronic simplicity and legibility; an improved decoding circuit is shown below. The ultimate result is the same.

Good Decoding Scheme for 1110

A flip-flop is a 'black box' which provides two outputs. When an input value is high (one), the first output will be high, and the second will be low. When the input value switches low (zero), the outputs will reverse. In other words, two opposite outputs for the price of one. But there is another significant use of the flip-flop.

Flip-flops also have an important input called a clock trigger, which is triggered only when its input returns to a given level. Only then will the outputs of the flip-flop reverse. That is, a given flip-flop clock may receive a 'zero' pulse. Its outputs will reverse. Then the zero pulse changes to a 'one' pulse. Nothing happens, but the trap is set to spring. When the one pulse changes back to a zero, the outputs reverse again. For every two changes at the clock, there will be but one change at the output. It takes four clock changes to produce two output changes.

Why is this useful? Because it is electronic, binary division. The truth table here shows how it works.

Binary Division with a Flip-Flop Output of First Flip-Flop Connected to Clock of Second Flip-Flops Change State Each Time Input Returns Low

| Clock<br>Input | Flip-Flop<br>Output | Second Clock<br>Input | Second Flip-Flop<br>Output |

|----------------|---------------------|-----------------------|----------------------------|

| G              | 0                   | 0                     | 0                          |

| 1              | 0                   | 0                     | 0                          |

| 0              | 1                   | 1                     | 0                          |

| 1              | 1                   | 1                     | 0                          |

| 0              | 0                   | 0                     | 1                          |

| 1              | 0                   | 0                     | 1                          |

| 0              | 1                   | 1                     | 1                          |

| 1              | 1                   | 1                     | 1                          |

| (Input)        | (Input/2)           |                       | (Input/4)                  |

Binary Division with a Flip-flop

Digital logic devices known as *counters* are combinations of gates and flip-flops that allow certain patterns be counted: Binary, Binary Coded Decimal (BCD, where the highest number is decimal 10), Gray code and others.

Latches are very much like flip-flops, except that the input is 'captured' at the output by a trigger signal called an enable, a select, or a gating pulse. The input may change continuously, but the output only reflects the input when the enable is activated. Latches are very useful when hundreds of thousands of signals are flying around on one set of lines, and the computer must select only certain groups of signals. The cassette output of data is a latch; only the 500-baud (bits per second) pulses of data reach the cassette output, even though many different signals reach its input.

Multiplexers are sometimes misunderstood, but mostly because of their formidable name. A traffic light is a multiplexer — it allows several streams of traffic to meet at one intersection, but only one stream to proceed. The multiplexer is the electronic equivalent, having several inputs. Gating signals select which of the inputs may reach the output. In a computer, this allows several devices to share a circuit (like the video, which must be sent to the screen, but also sends and receives characters from the rest of the computer).

Finally, *shift registers* treat bits of data like a bucket brigade sends up water: it goes in one end, and at each electronic 'go!', the bucket is sent along one position. The dots which make up the video display are produced by circuits which shift them out to the screen one bit at a time, in synchronization with the monitor's sweeping electron beam.

### Reading The Pins

Finding your way through digital circuits is much easier than finding your way through an ordinary table radio. Industry standards have made the process simple. Consumer integrated circuits are packaged in small, rectangular, plastic or ceramic cases with anywhere from 8 to 40 external connections known as 'pins'.

Earlier integrated circuits — and many of the audio types currently being produced — were packaged in small metal cans and looked like transistors, with many wires protruding from the bottom. The wires were arranged around a keying tab on the edge of the can, and numbered like so:

Can-type IC Pin Numbering

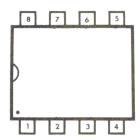

As such circuits developed into more sophisticated and powerful devices, more pins were needed for input and output. A rectangular package was developed, but it was still numbered in a circle, starting (when looking down from the top) from left of the notch, so:

Dip-type IC Pin Numbering (8 Pins)

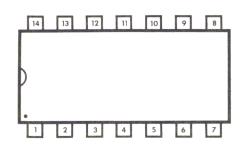

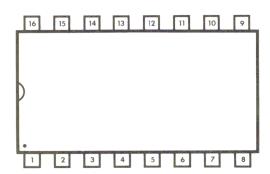

All modern integrated circuits can be read from the top in this same way. 14-and 16-pin types start from the top left and read around:

14- and 16-Pin Dip IC Pin Numbering

You can read the pinouts of 18-, 20-, 24-, 28-, and 40-pin circuits in the same manner. The highest numbered pin sits just opposite the lowest numbered pin. In the beginning this practice may seem confusing; it is. But after using the circuits — and counting their pins over and again — you will probably feel comfortable with the pin arrangement.

Just one thing: when you assemble Apple add-ons, most of your work will be done from the bottom . . . which means reading backwards!

### Wire-Wrapping Technique

It's not without a bit of hesitation that I attacked many of the hardware projects presented in this book. Some are simple, but many, particularly those using memory circuits, need many connections. The wiring is not complicated, just tedious.

If you work carefully, all is likely to be well; but even a touch of haste will encourage confused connections. It is in these cases especially that wire-wrapping is the technique to use.

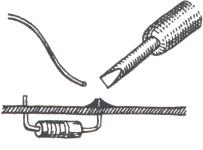

Wire-wrapping is not only easier than soldering, it is secure, simple, easier for correcting mistakes — and less costly. For wire-wrapping, you will need wire-wrap sockets, which are sold by most hobbyist supply houses including Radio Shack. Likewise, wire-wrap wire and a simple hand tool are used for the process. Here are the steps:

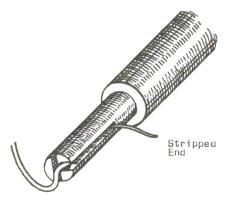

1. The wire, still connected to the spool, is inserted in the V-shaped stripping slot. Insert beteen one half and one inch of wire. Pull downward from the V, and the wire will slip out, leaving a piece of insulation in the stripper, where it can be shaken out.

1. Insert stripped wire.

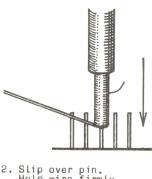

2. Look carefully at the end of the wire-wrap tool. There is a small hole, meant to fit over the pins of a wire-wrap socket. Next to it is a half-circle, into which you must slide the stripped wire. The stripped portion will slide up a groove in the side of the tool, stopping where the insulation begins.

Slip over pin. Hold wire firmly, and slide fully down.

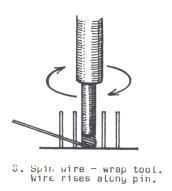

3. When the wire is in place, pull it sharply but gently upwards, and slide the tool on the wire-wrap socket. Holding the wire firmly, spin the tool in your hand. The wire will wind up on the socket pin, freeing itself from the tool. Remove the tool. The wire-wrapping is complete for that end of the connection.

4. Cut the wire to a length that will comfortably reach its destination, and then some. Strip the end of it, and repeat the process above. The connection is complete. Don't forget to use different colors (white, yellow, red and blue are generally available). This will help you distinguish your connection patterns if changes become necessary.

Finished connection has no bare wire protruding.

### **Soldering Technique**

For projects from scratch, soldering should be considered the final process, the actions of a self-assured, confident hobbyist. For modifications, it is a necessity. In either case, and whether you are a micro-acrobat or distinctively clumsy like me, you can solder well. The requirements are patience and good solder.

To start, make sure you are using an iron in the 25 to 40 watt range, never a soldering gun. The solder should be high quality, multicore solder. It is expensive, but will save many grief stricken hours tracing 'cold solder joints', or removing globs of dull solder from between and under integrated circuits.

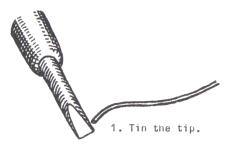

1. Clean the soldering iron tip, and heat the iron. Flow fresh solder on the tip to 'tin' the tip, which will help the solder flow from the tip of the iron to the part to be soldered. If the iron has been used, clean any encrusted material from the tip, and use coarse emery paper to shine the solder. If the point gets deformed, bent, or very corroded, file it sharp with a fine file, and re-tin the tip.

2. Keep an old sponge handy, slightly damp. Run the tip of the iron quickly over it as you solder to remove the excess flux. Always use a soldering iron holder (usually provided with an iron); if you don't, you'll wish you had the first time you burn a large hole in your imitation walnut, vinyl-topped desk.

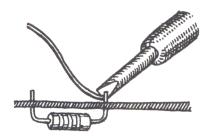

Bring solder, parts and iron into contact.

3. In the olden days, the rule was 'heat the parts, not the solder'. Forget it. Make sure the iron is no hotter than 40 watts (and remember never to use a soldering gun) and that the parts you are about to solder are very clean. Place the iron against the part, making as much contact with it as possible along the angled tip of the iron. Place the end of the solder at the junction of the iron and the part, and flow just enough solder to make a clean, shiny, flowing connection.

3. Lift iron and solder simultaneously.

4. Remove the iron immediately and let the part cool. If a wire is being soldered, hold it still until the solder becomes cloudy and cool, or else an incomplete connection may result.

4. Finished solder connection.

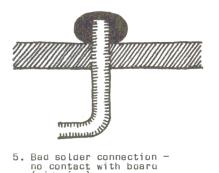

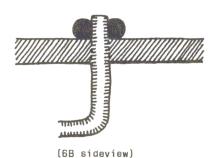

5. If solder bridges develop between connections that are very close together, don't try to suck up the solder with the iron; you can only overheat the parts that way, and end up with blobs of solder and flux. Instead, use solder wick or solderup to remove the excess solder, and start again. Let the parts cool before soldering again (a half minute should be enough).

5. Bad solder connection no contact with board (sideview).

<sup>6.</sup> Bad solder connection - no contact with pin

### Tips on Handling Integrated Circuits

In the early days of microcomputers, there was a lot of user hesitation about installing memory chips because of warnings about static electricity damaging the memory devices. At that time the fear was reasonable; but today (with just a little caution) there need be no problem.

- 1. Never place any integrated circuit on highly charged plastic material, especially styrofoam.

- 2. Handle memory chips, CPU's (such as the 6502), LSI devices (large-scale integrated circuits, usually those with 28 or 40 pins), or any marked MOS, CMOS or NMOS (metal-oxide semiconductors), with care. Hold them by their ends, never by the connection pins.

- 3. Purchase a static-free workbench, which is a conductive cloth sheet with a wrist strap and safe grounding cable. These can be obtained from Wescorp for about \$18.

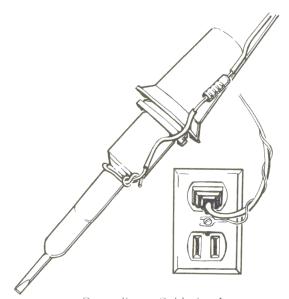

- 4. Ground your soldering iron to an earth ground *but only through a series-connected one-megohm resistor*—*never directly!* The grounding is not absolutely essential, but helps if you live in a very dry, static-producing environment.

Grounding a Soldering Iron

- 5. Work with any integrated circuits with the power off. Make sure the integrated circuit's ground and power pins are all connected (soldered or in sockets) before turning on the juice! A difference of a mere half a volt between certain pins can **kill** an IC.

- 6. Use high-quality sockets for integrated circuits wherever you can. This will not only keep excessive heat away from them, but will also save the day if one is damaged. Unsoldering a 40-pin integrated circuit is not pleasant.

- 7. Above all, work slowly and carefully. By far the greatest villian is haste. Oh yes do keep furry animals out of the area!

## NOTES

### Introduction

Why expand the Apple Computing System at all? What proud Apple owner has never wished that the computer would do just this one more thing, to somehow be able to perform the magic necessary to do that certain thing that would just exactly fit your particular application. While there are a lot of interfaces and expansion modules available on the market, none was really designed with the particular application you had in mind. The purpose of this book is to provide you with an expansion module that will be flexible enough that you will be able to adapt it to any specific application you have in mind. Most people, when faced with the arduous task of trying to make their Apple do one particular thing that would make it perfect for their system, are really dismayed by how much special knowledge they would need and how really complex it appears. A lot of people will simply decide, "Oh well, I can probably get by without it." The authors, in writing this book, are providing a much better alternative to simply doing without that special little goodie vou would like. They are going to lead you step by step through a series of projects and applications that will allow you to custom design exactly the piece of hardware you need for that special application you have been wanting to do ever since you got your computer.

### Data Acquisition and Control Applications.

The Apple was originally called 'The Appliance Machine'; however, it was designed, at least to some degree, to also be used for data acquisition and control applications. The way the Apple is usually configured, you will find that there are four empty slots inside, and it would really be nice to utilize them in order to expand the capabilities of your Apple II Computer.

### An A/D and D/A Convertor

The analog to digital and digital to analog convertor will be one of the most important projects you can put together and one of the most useful applications presented in this book. The reason for this is that the real world is analog, not digital, but the computer deals exclusively with digital information. Examples of

analog would be temperature control and sensing, light control and sensors, and the measurement of voltage levels. Virtually any type of sensor could be hooked to an analog/digital convertor, allowing the computer to 'see' what's going on.

There are things that would be really handy around the house; perhaps a hobby environment such as model railroad control, a burglar alarm system that could be monitored by your computer, and all of the peripheral devices that are already available for the computer user at home. This book will prove invaluable to people who have just bought a strange new device or a new printer, and wonder, "How can I hook that to my Apple?" This book will give you the opportunity to control even the most complex industrial or home applications at a very low price. Gastromatic is a relatively new application where the home computer can be used in lowering the energy costs of running your furnace. The ability to do this, before the advent of the small home computer, would have cost many thousands of dollars and been prohibitive for most people. With the interfaces and applications described in this book you will find you have the ability to control machines in a way that only a few years ago would have been absolutely impossible. Examples of this would be driving step motors, automatic monitoring and remote control of drive motors and fans, or the control of any machine that was previously controlled by mechanical means. The basic concept of this book is to vastly improve the Apple II Computer's ability to communicate with and control the real world.

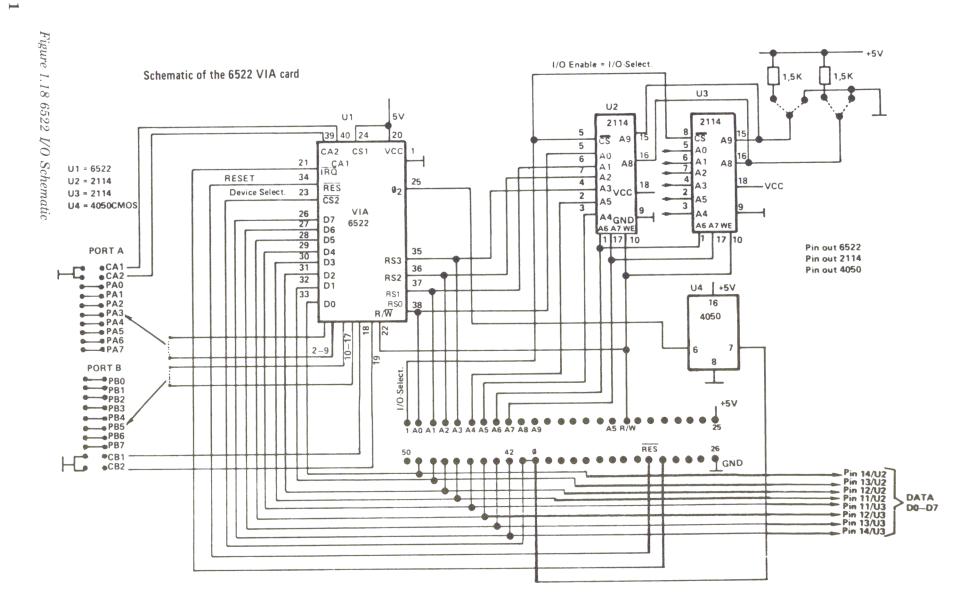

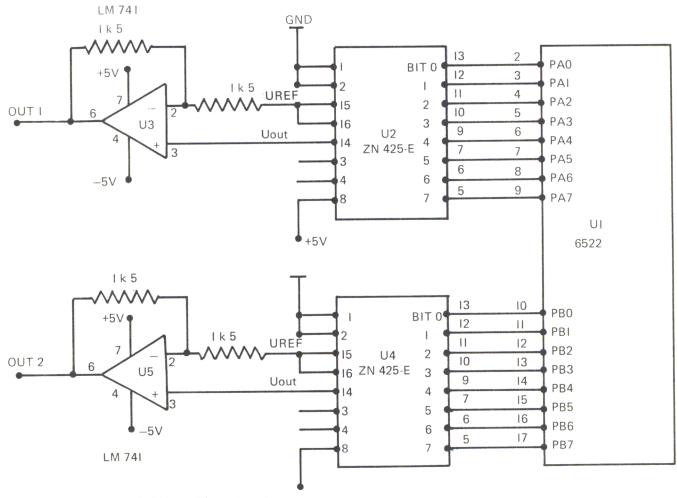

#### The 6522VIA I/O Board.

The Apple II Computer, as configured at the factory, has practically no way to interface with the real world, with the possible exception of playing a game with the joysticks. Games are very impressive and fun, but after awhile you will begin to wonder, "Now how do I get this nifty little machine to do something practical and prove I didn't just waste my money on a game-playing machine?" One of the biggest problems with trying to use the game playing input ports for transfer of data is that they are limited to four bits or one nybble, which really limits the amount of data that can be transferred in a given period of time. Because of the severe I/O limitations of the Apple computer, the authors intend to show you how to use the 6522 versatile application interface I/O board to move large amounts of data in relatively short periods of time. Consequently, you will have the ability to do a great many of the things people said couldn't be done.

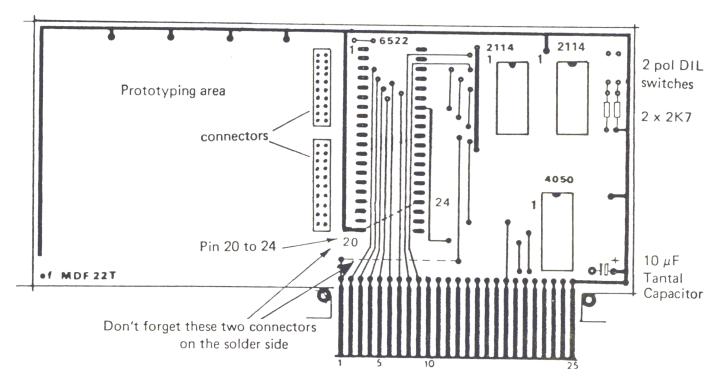

One of the first problems you will encounter, which is not known to many people, is that the 6522 I/O chip is not fast enough to pick up the clock pulse from the 6502 microprocessor chip. In order to make the 6522 compatible with the 6502 microprocesor, it is necessary to incorporate a time delay. We will use the small 4050 CMOS chip. This solution will work in 99% of the cases. For that 1% of the time when it doesn't, never fear, there will be further help outlined later in the book. The 6522 I/O board also has 1K of RAM built into it, of which 1/4 is usable at any time. These 256 bytes are suitable for applications such as a small machine-language monitor that you want to tuck safely out of BASIC's way.

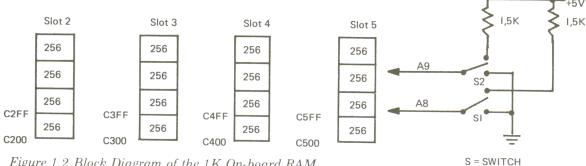

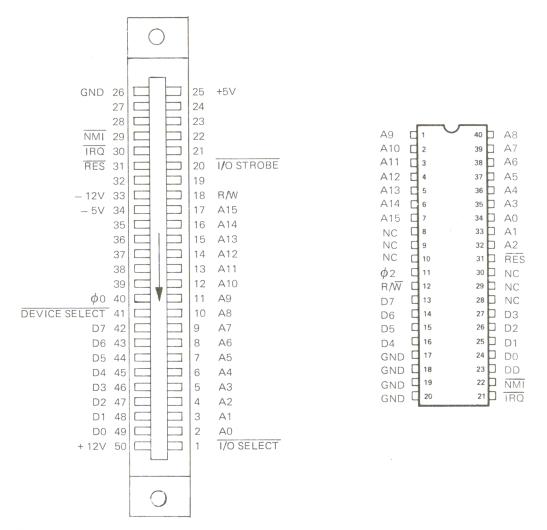

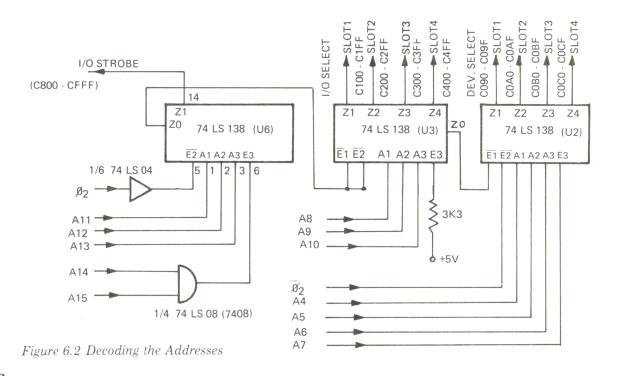

Figure 1.2 demonstrates how you can use the 1K byte RAM on your 6522 I/O board. On each board there are two 2114 1K by 4-bit static RAMs for your machine-language programs. But out of this 1K RAM you can really only use 256 bytes at a time. The addresses for that 1/4K bytes of RAM depend on the slot in which the board is plugged. For instance, if you want to put a small machine-language program in the RAM on the board while it's plugged into slot 4,

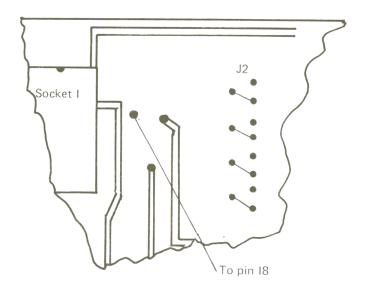

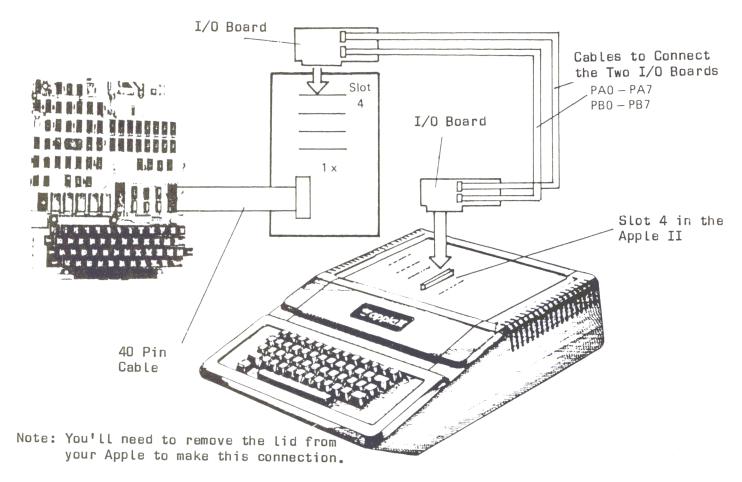

Figure 1.1 The Four Empty Slots in the Apple

you can write your program into the RAM area starting at C400. You need not be concerned about which 1/4 of the RAM your program is in, because you may select any 1/4 you wish by using the two switches on the I/O board. Note that every 1/4K block on each board is addressed using similar addresses (for example, **C500-C5FF** in slot 5).

Figure 1.2 Block Diagram of the 1K On-board RAM

|          | SI  | S2  |

|----------|-----|-----|

| I. 1/4 k | off | off |

| 2. 1/4 k | on  | off |

| 3. 1/4 k | off | on  |

| 4. 1/4 k | on  | on  |

Suppose you need four different machine-language programs for a particular application. You could write these four routines into address C500-C5FF (with the I/O card in slot 5) while setting the two switches to the four different positions. Then the four programs (each being 256 bytes or less) are in that 1K RAM block. By setting the switches, you can now address four different programs in the same area of memory.

Different 1/4's of the 1K RAM in 256 Byte chunks can easily be accessed by simply flipping the switches on the board itself.

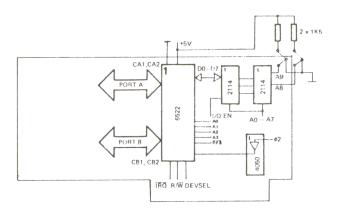

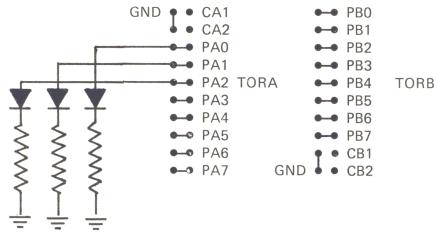

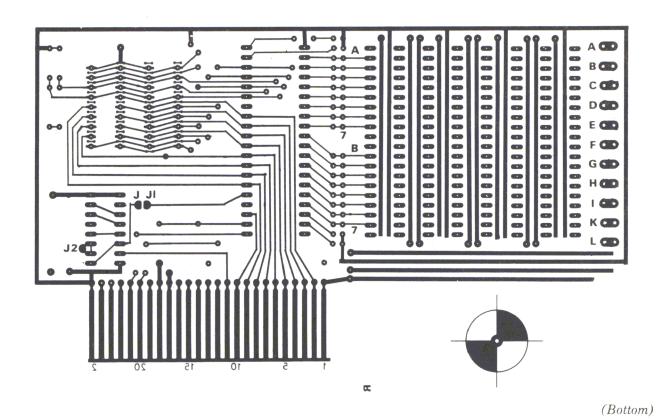

The clear area on the left side of the board is a prototype area free for you to use for your own experimentation and custom applications. The 6522 I/O board can be programmed and controlled from virtually any language, whether it's store instructions from machine-language or POKE and PEEK commands used with the higher level languages. A section of this book is devoted to showing you how this is done, whether it's from machine-language, or a higher level language such as PASCAL or BASIC. The 6522 has two ports, A and B, and 8 bi-directional data lines. It also contains 2 timers, 1 eight-bit shift register, and 4 hand-shaking lines. The hand-shaking lines are used to communicate with the other devices that are capable of sensing a READY or NOT READY condition.

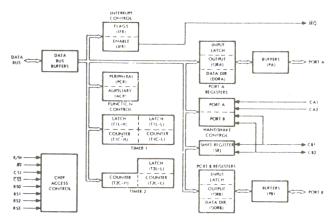

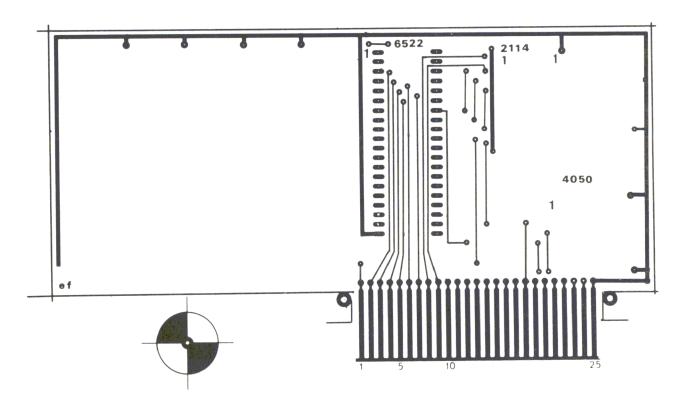

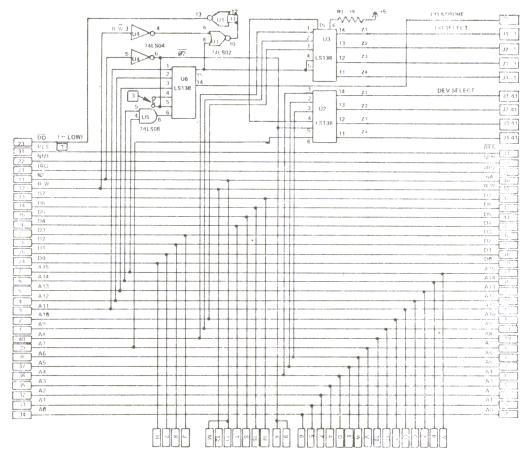

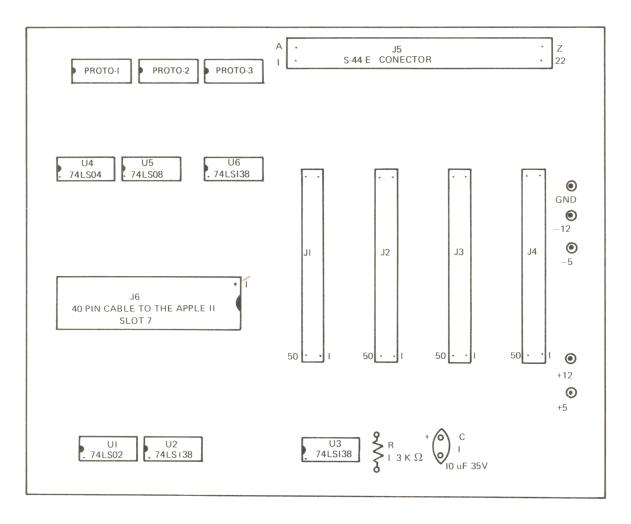

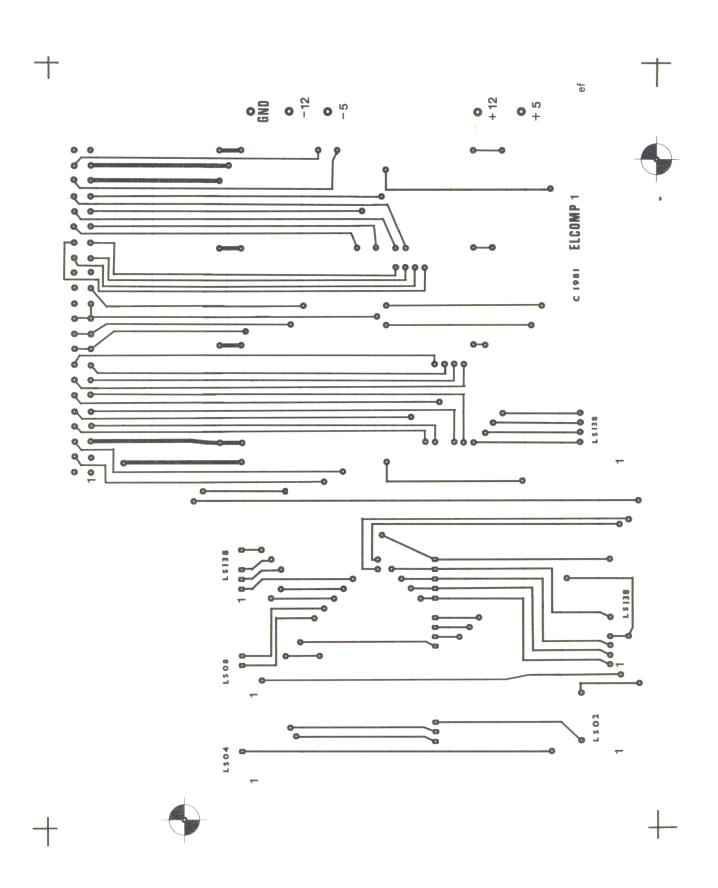

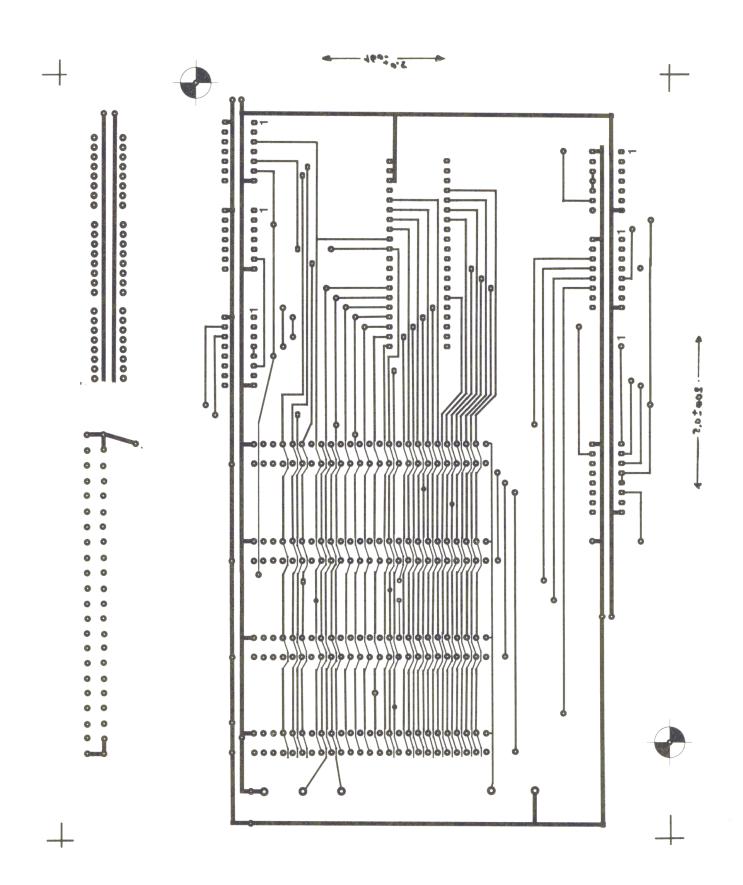

Figure 1.3 Block Diagram of the 6522 Board

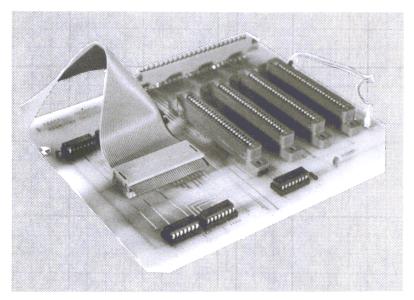

Figure 1.4 Photo of the 6522 Board

| board   |      | 6522 | 77 H 14 7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | To the state of th |

|---------|------|------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| in slot | Hex  |      | Decima                                      | al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | from | to   | from                                        | to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

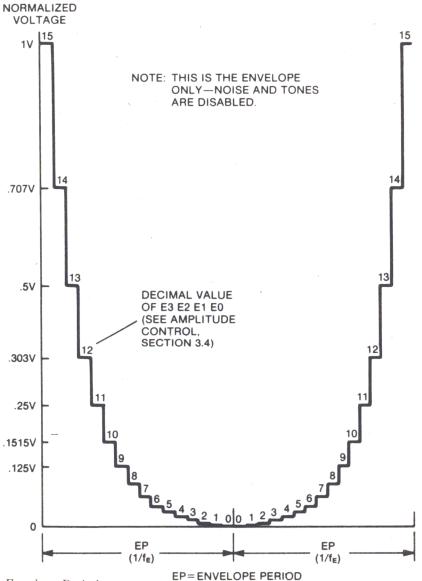

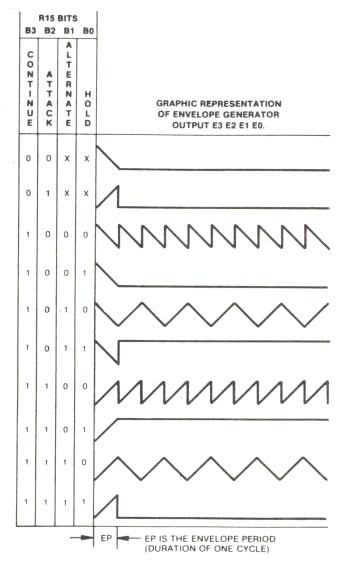

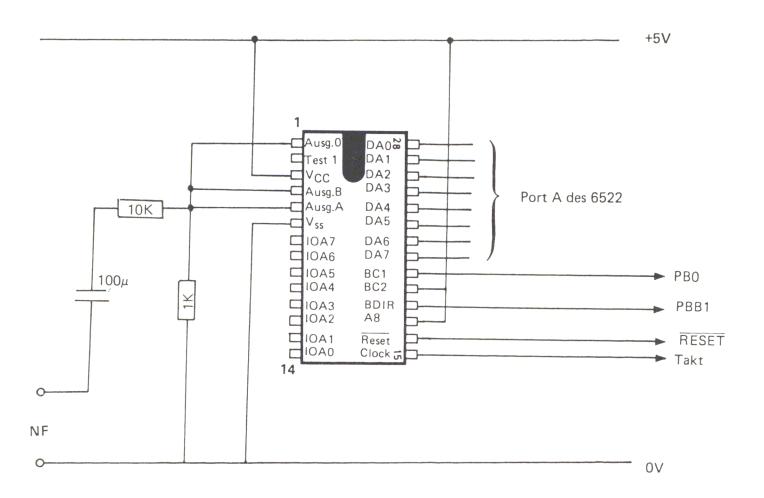

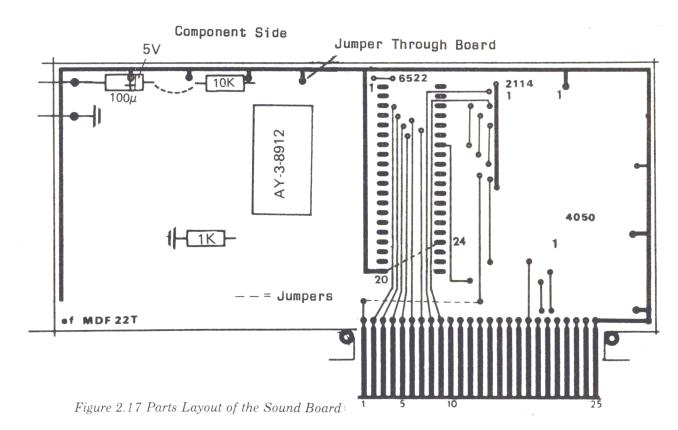

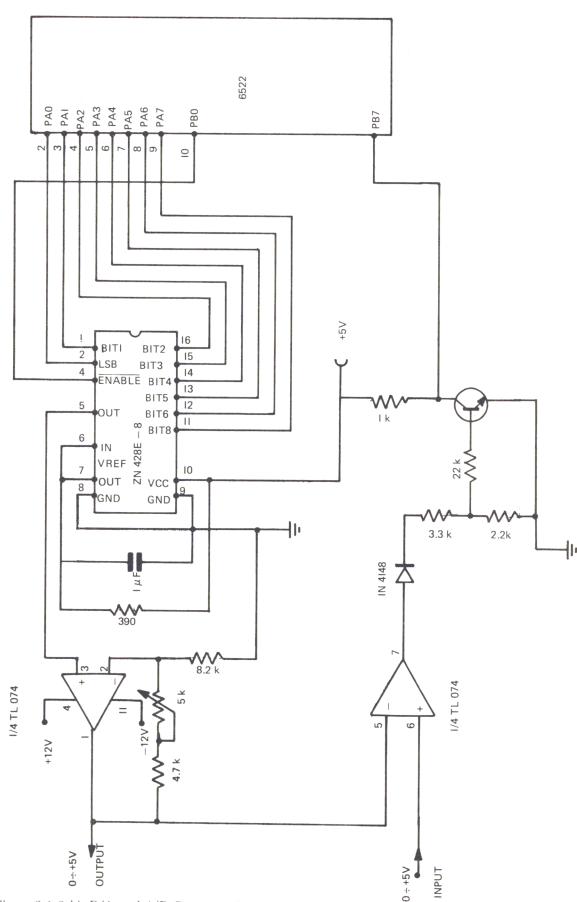

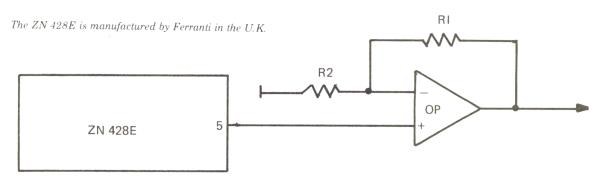

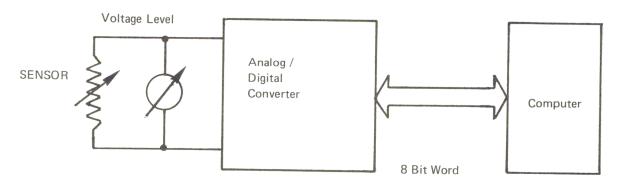

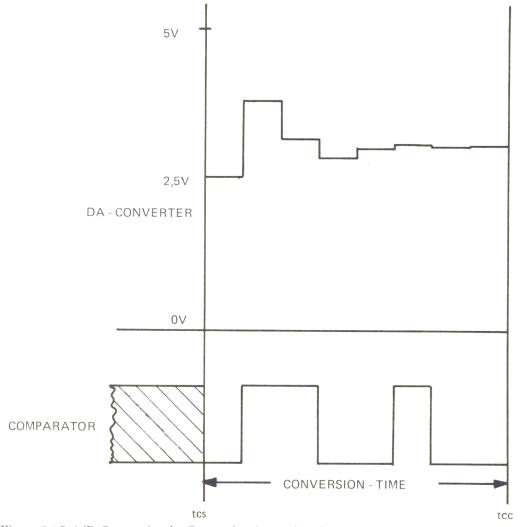

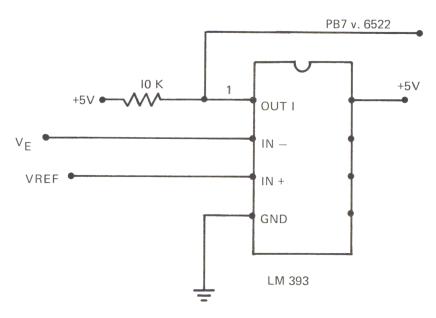

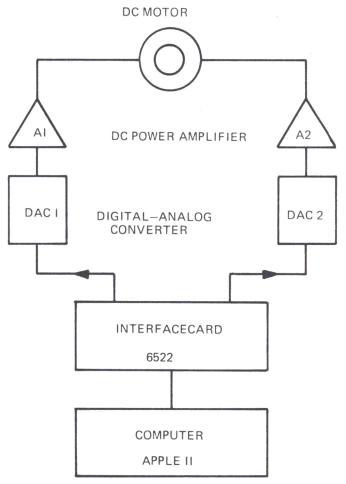

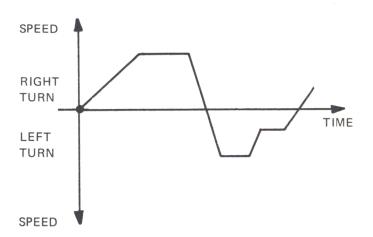

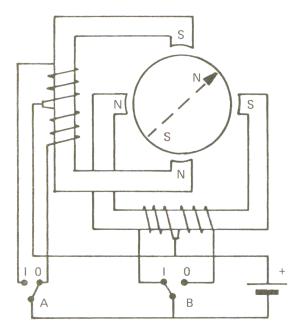

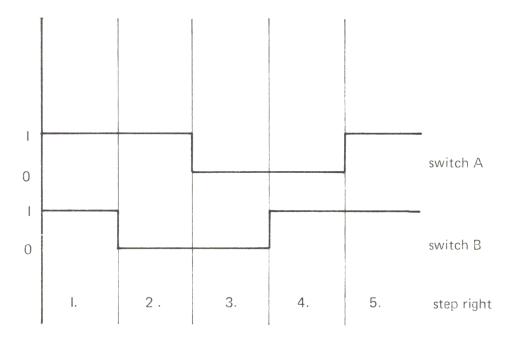

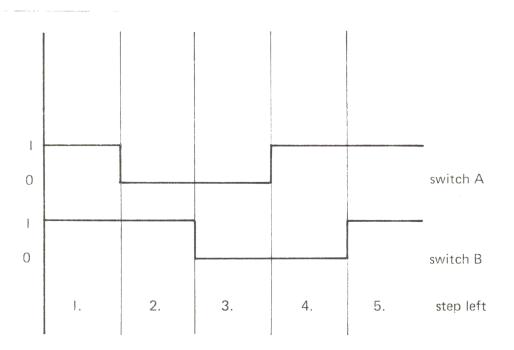

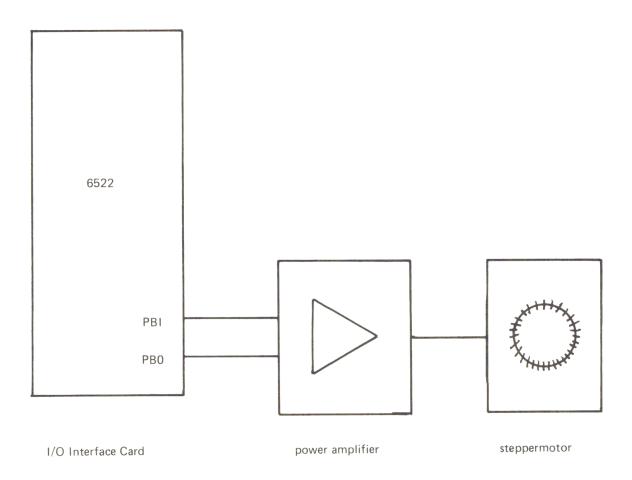

| 2       | C0A0 | C0AF | -16224                                      | -16209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |