# SPERRY UNIVAC 9400/9480 Systems

# **Processors**

**Programmer Reference**

This document contains the latest information available at the time of publication. However, Sperry Univac reserves the right to modify or revise its contents. To ensure that you have the most recent information, contact your local Sperry Univac representative.

Sperry Univac is a division of Sperry Rand Corporation.

FASTRAND, MATED-FILM, PAGEWRITER, SPERRY UNIVAC, UNISCOPE, UNISERVO, and UNIVAC are trademarks of the Sperry Rand Corporation.

PSS 1 PAGE

# **PAGE STATUS SUMMARY**

ISSUE:

**UP-8080**

| Part/Section          | Page<br>Number | Update<br>Level | Part/Section | Page<br>Number | Update<br>Level | Part/Section | Page<br>Number |

|-----------------------|----------------|-----------------|--------------|----------------|-----------------|--------------|----------------|

| Cover/Disclaimer      |                |                 |              |                |                 |              |                |

| PSS                   | 1              |                 |              |                |                 |              |                |

| Contents              | 1 thru 5       |                 |              |                |                 |              |                |

| 1                     | 1 thru 10      |                 |              |                |                 |              |                |

| 2                     | 1 thru 22      |                 |              |                |                 |              |                |

| 3                     | 1 thru 22      |                 |              |                |                 |              |                |

| 4                     | 1 thru 8       |                 |              |                |                 |              |                |

| 5                     | 1 thru 14      |                 |              |                |                 |              |                |

| Appendix A            | 1, 2           |                 |              |                |                 |              |                |

| Appendix B            | 1, 2           |                 |              |                |                 |              |                |

| Index                 | 1 thru 7       |                 |              |                |                 |              |                |

| User Comment<br>Sheet |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              | ,              |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                |                 |              |                |                 |              |                |

|                       |                | 1               | 1            | 1              | 1               | ·            |                |

| Part/Section | Page<br>Number | Update<br>Level |

|--------------|----------------|-----------------|

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

|              |                |                 |

# **Contents**

# **PAGE STATUS SUMMARY**

# **CONTENTS**

# 1. INTRODUCTION

|    | 1.1.     | GENERAL                           | 1-1  |

|----|----------|-----------------------------------|------|

|    | 1.2.     | FUNCTIONAL DESCRIPTION            | 1–2  |

|    | 1.2.1.   | Processor                         | 1–3  |

|    | 1.2.1.1. | Registers                         | 1–3  |

|    | 1.2.1.2. | Status                            | 1–3  |

|    | 1.2.1.3. | Interrupts                        | 1-3  |

|    | 1.2.1.4. | Timer                             | 1-4  |

|    | 1.2.1.5. | Instruction Types                 | 1-4  |

|    | 1.2.2.   | I/O Section                       | 1-4  |

|    | 1.2.2.1. | Multiplexer Channel               | 1-5  |

|    | 1.2.2.2. | Selector Channels                 | 1–5  |

|    | 1.2.3.   | Main Storage                      | 1–5  |

|    | 1.2.3.1. | Parity Checking                   | 1-5  |

|    | 1.2.4.   | System Console                    | 1–5  |

|    | 1.3.     | CONFIGURATIONS                    | 1–6  |

|    | 1.3.1.   | Minimum Configurations            | 16   |

|    | 1.3.2.   | Expanded Configurations           | 1–6  |

|    | 1.4.     | CHARACTERISTICS                   | 1—10 |

| 2. | PROCES   | SSOR                              |      |

|    | 2.1.     | INFORMATION FORMATS               | 2–1  |

|    | 2.1.1.   | Data Formats                      | 2-2  |

|    | 2.1.1.1. | Fixed-Point Numbers               | 2-2  |

|    | 2.1.1.2. | Decimal Numbers                   | 2-2  |

|    | 2.1.1.3. | Logical Information               | 2–3  |

|    | 2.1.2.   | Instruction Formats               | 2-4  |

|    | 2.1.3.   | Fixed-Point Arithmetic            | 2-5  |

|    | 2.1.3.1. | Fixed-Point Data Formats          | 2-6  |

|    | 2.1.3.2. | Fixed-Point Number Representation | 2-6  |

|    | 2.1.3.3  | Fixed-Point Condition Code        | 2-6  |

3-7

3-8

3-8

3-9 3-9

3-9

3-13

3.

3.3.3.1.

3.3.3.2.

3.3.4.

3.3.5.

3.3.5.1.

3.3.5.2. 3.3.5.3. Parity Generation and Checking

Special Character Recognition

Nonshared Subchannel Status

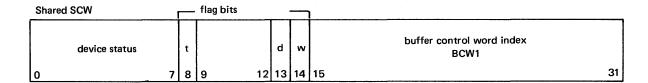

**Shared Subchannel Status**

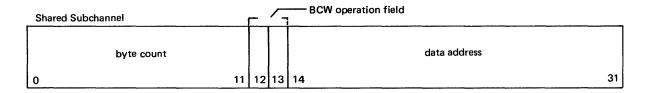

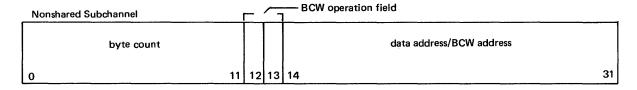

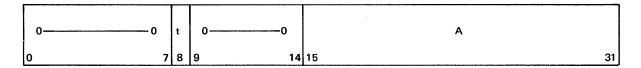

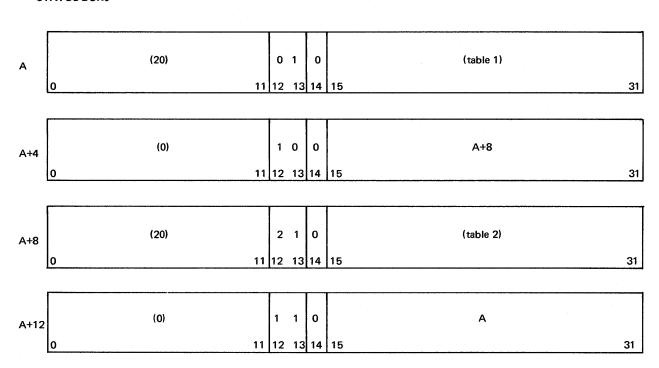

**Buffer Control Word**

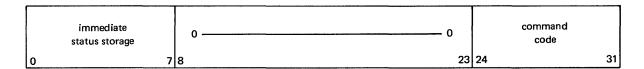

Start I/O Status

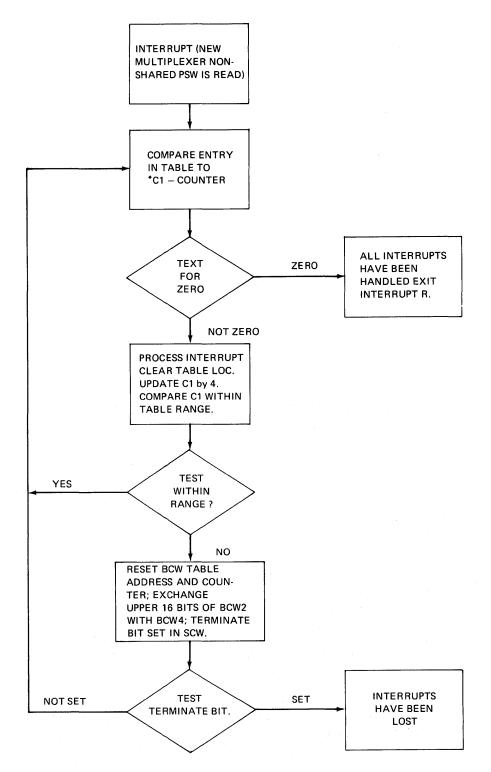

Status Handling

|    | 3.4.     | SELECTOR CHANNEL                        | 3–13 |

|----|----------|-----------------------------------------|------|

|    | 3.4.1.   | Channel Address Word (Selector Channel) | 3-14 |

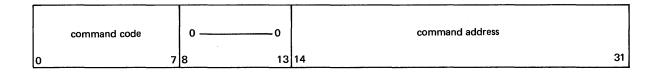

|    | 3.4.2.   | Channel Command Word (CCW)              | 3-14 |

|    | 3.4.2.1. | Channel Command Codes                   | 3-15 |

|    | 3.4.3.   | Channel Status Word                     | 3–16 |

|    | 3.4.4.   | Command Chaining                        | 3-17 |

|    | 3.4.5.   | Status Handling                         | 318  |

|    | 3.4.5.1. | Start-I/O Status                        | 3–18 |

|    | 3.4.5.2. | Other Channel Status                    | 3–18 |

|    | 3.5.     | COMMUNICATIONS ADAPTER                  | 3–18 |

|    | 3.6.     | START-I/O INSTRUCTION                   | 3–19 |

|    | 3.7.     | INITIAL LOADING                         | 3–20 |

|    | 3.7.1.   | Initial Loading at Multiplexer Channel  | 3–20 |

|    | 3.7.2.   | Initial Loading at Selector Channel     | 3–20 |

|    | 3.8.     | I/O PRIORITY                            | 3–21 |

|    | 3.8.1.   | Selector Channel                        | 3–21 |

|    | 3.8.2.   | Multiplexer Channel                     | 3–21 |

|    | 3.9.     | I/O LOADING AND TIMING                  | 3–21 |

|    | 3.9.1.   | Loading Considerations                  | 3–21 |

|    | 3.9.2.   | Timing Considerations                   | 3–22 |

| 4. | MAINS    | TORAGE                                  |      |

|    | 4.1.     | MAIN STORAGE CHARACTERISTICS            | 4—1  |

|    | 4.1.1.   | Addressing                              | 42   |

|    | 4.2.     | INFORMATION POSITIONING                 | 4–2  |

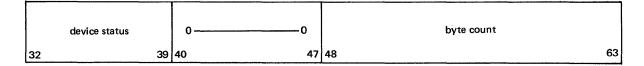

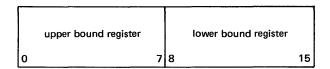

|    | 4.3.     | FIXED STORAGE ASSIGNMENTS               | 4-2  |

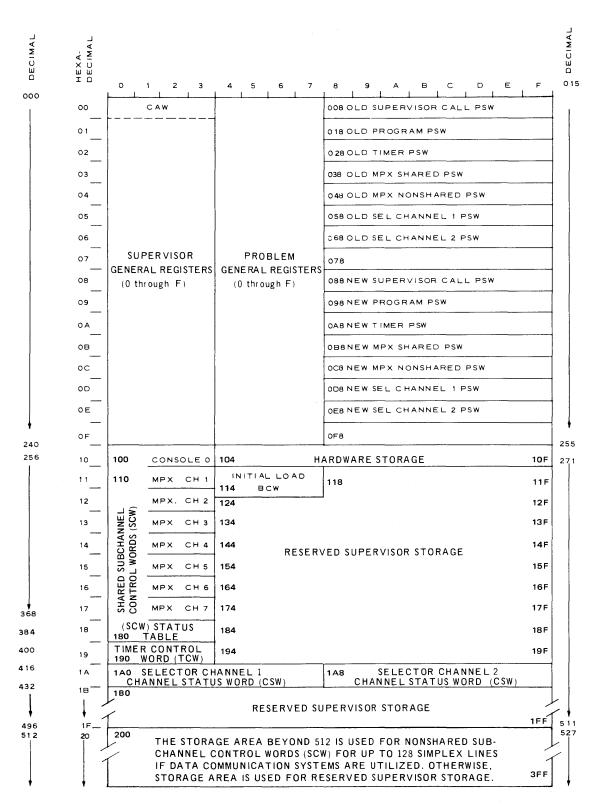

|    | 4.4.     | WRITE PROTECTION                        | 46   |

|    | 4.4.1.   | Parity Verification                     | 4–6  |

|    | 4.5.     | OPERAND ADDRESSING                      | 47   |

| 5. | SYSTE    | M CONSOLE                               |      |

|    | 5.1.     | GENERAL                                 | 5–1  |

|    | 5.2.     | COMPONENTS                              | 5-1  |

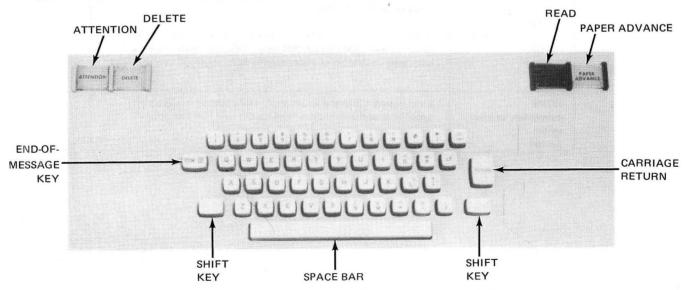

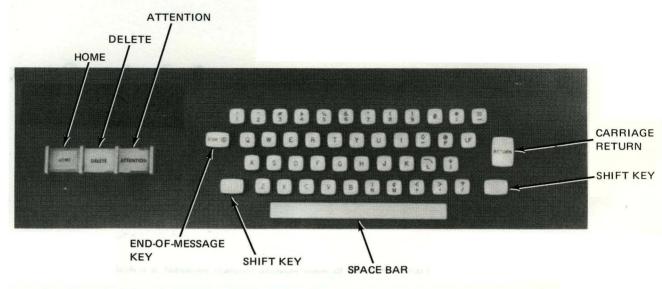

|    | 5.2.1.   | Keyboard                                | 5–3  |

|    | 5.2.2.   | Printer                                 | 5–5  |

|    | 5.2.3.   | Command Codes                           | 5–8  |

|    | 5.2.4.   | Status Codes                            | 5–9  |

|    | 525      | Sense Codes                             | 511  |

4-1

4-4

| 5.2.6.   | Operating Characteristics       | 5–12 |

|----------|---------------------------------|------|

| 5.2.6.1. | Interface                       | 5–12 |

| 5.2.6.2. | Initial Selection Sequence      | 5–12 |

| 5.2.6.3. | Control-Unit-Initiated Sequence | 5–13 |

| 5.2.6.4. | Control Unit Resets             | 5—14 |

| 5.2.6.5. | Chaining                        | 5—14 |

#### **APPENDIXES**

#### A. INSTRUCTIONS

# B. GLOSSARY

# **INDEX**

#### **USER COMMENT SHEET**

4-1. Main Storage Differences

4-2. Fixed Main Storage Functions

# **FIGURES**

| 1-1. | UNIVAC 9400/9480 Systems Processors                                                                       | 1–2        |

|------|-----------------------------------------------------------------------------------------------------------|------------|

| 1-2. | UNIVAC 9400 System Processor Configuration                                                                | 1—7        |

| 1–3. | UNIVAC 9480 System Processor Configuration                                                                | 1–8        |

| 2–1. | Information Formats                                                                                       | 2–1        |

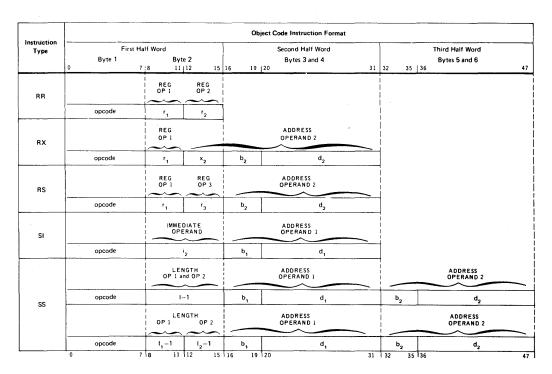

| 2–2. | Instruction Formats                                                                                       | 2-5        |

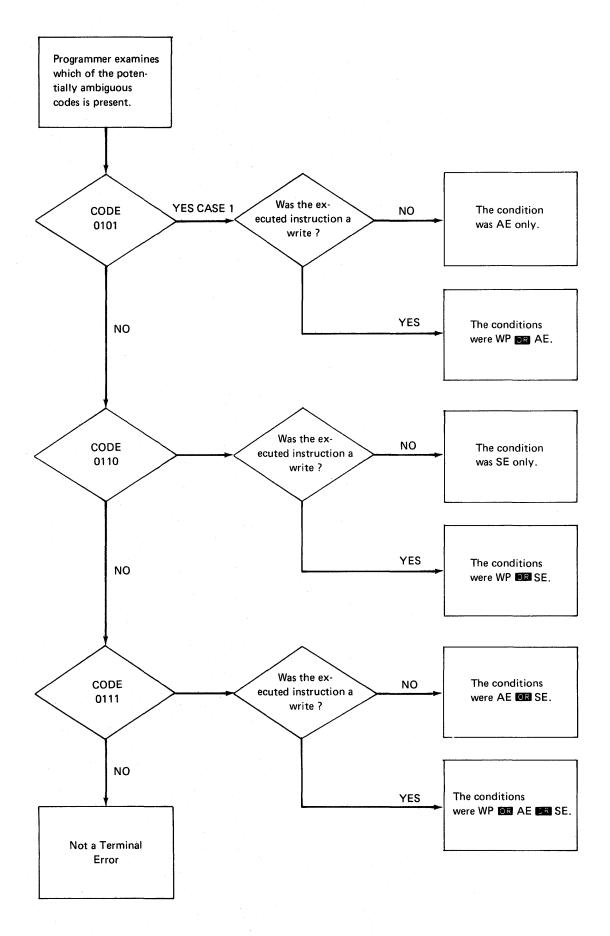

| 2–3. | Terminal Error Flowchart                                                                                  | 2–18       |

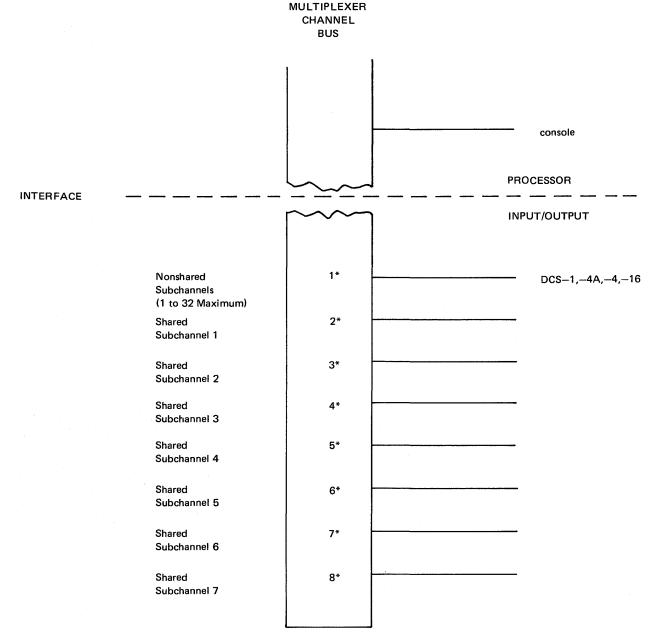

| 3–1. | Multiplexer Channel Simplified Physical and Functional Diagram                                            | 3–3        |

| 3–2. | Program Control of BCWs                                                                                   | 3–11       |

| 4–1. | Fixed Main Storage Assignments                                                                            | 4–3        |

| 5–1. | System Console Keyboard (Serial Numbers 100 to 204)                                                       | 5—1        |

|      | System Console Keyboard (Serial Numbers 205 and Above and UNIVAC 9480 System) Character Transfer Sequence | 5–2<br>5–7 |

| ТАВ  | LES                                                                                                       |            |

| 1-1. | Optional Hardware Expansion Features                                                                      | 1–8        |

| 1–2. | UNIVAC 9400 and 9480 Characteristics                                                                      | 1-10       |

| 3-1. | Operational Aspects of Each Multiplexer Subchannel Type                                                   | 3-4        |

|      | Multiplexer Channel Data Transferring Capability (Bytes per Second)                                       | 3-22       |

# **UNIVAC 9400/9480 SYSTEMS**

PAGE REVISION

Contents 5

| 5–1. | System Console Printer Controls, Indicators, and Keys    | 5–2 |

|------|----------------------------------------------------------|-----|

| 5-2. | Keyboard Character Coding (Serial Numbers 205 and Above) | 5–4 |

| 5–3. | Printer Character Coding (Serial Numbers 100 to 204)     | 5–5 |

| 5-4. | Serial Arrangement of Font on Printer                    | 5-7 |

| 5-5. | Command Codes                                            | 5–8 |

| 5-6. | Status Codes                                             | 5–9 |

| 5–7. | Sense Byte Codes                                         | 5—1 |

| A-1  | Alphabetical List of Instructions                        | A-1 |

# 1. Introduction

#### 1.1. GENERAL

The information contained in this manual is designed to familiarize system programmers with the overall operation of the UNIVAC 9400 and UNIVAC 9480 Systems Processors (Figure 1–1) and their relation to system programming.

The manual is organized in five sections, each containing a description of each system hardware component, plus appendixes, as follows:

#### Section 1

This section contains an overall description of the processor, input/output (I/O) channels, main storage, and system console, in addition to the possible system configurations, minimum and maximum, with expansion features.

#### Section 2

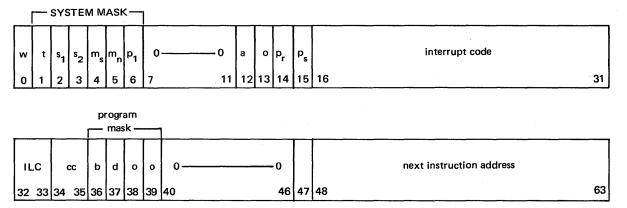

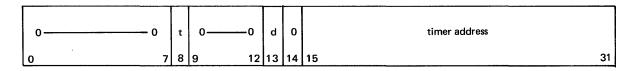

Data and instruction formats, fixed-point and variable-length decimal arithmetic instructions, the program status word (PSW), interrupts, and the purpose and use of the timer control word (TCW) are described in this section.

#### Section 3

The I/O sections of the processors, including the multiplexer channel, functional interfaces, optional selector channels, and the optional communications adapter are described in this section, as well as the start-I/O instruction, initial loading, I/O priorities, and timing.

#### Section 4

Main storage characteristics for each system are described in this section.

#### Section 5

This section contains descriptions of the system consoles, including operation of printers.

#### Appendix A

Appendix A contains table listings (alphabetical by name) of instructions, including hexadecimal opcodes, and execution times.

#### Appendix B

Appendix B is a glossary of acronyms.

a. Serial numbers between 100 and 204

b. Serial numbers 205 and above

Figure 1-1. UNIVAC 9400/9480 Systems Processors

#### 1.2. FUNCTIONAL DESCRIPTION

Inasmuch as the UNIVAC 9400 and 9480 Systems Processors are very nearly identical, information presented in this manual is for both processors, with only the differences between the two processors being specified separately.

#### 1.2.1. Processor

The processor consists mainly of a control section, arithmetic section, and I/O channels. The control section controls the sequence in which instructions are executed, and interprets and controls the execution of each instruction. The arithmetic section processes binary and decimal integers and logical information. Also, it performs data comparisons, shifting, and single or double indexing of operand addresses. It is shared with the multiplexer input/output channel. (Each selector channel contains its own arithmetic section.) All binary operations are performed in the twos complement form. This is accomplished by taking the ones complement of the number and adding one.

| 11000110 | original number |

|----------|-----------------|

| 00111001 | ones complement |

| 1        | add one         |

| 00111010 | twos complement |

The I/O channels consist of one multiplexer channel and up to two selector channels which permit peripheral subsystems to be connected to main storage and utilize instructions from the processor.

#### 1.2.1.1. Registers

The processor has access to two sets of general registers, 16 supervisor and 16 problem, located in low-order main storage. These registers are used to eliminate storing of register content when the supervisor intercepts the program to process interrupts. Register storage is required only when switching between problem programs.

#### 1.2.1.2. Status

Overall processor status is determined by the contents of a 64-bit program status word (PSW) register. All interrupts cause the contents of the PSW register to be transferred to storage allocated for that class of interrupt. The area of storage for each interrupt type is called the old PSW. The PSW register is then loaded with new corresponding PSW unique to the type of interrupt. This information is located in the storage area assigned to new PSWs. An old PSW area and a new PSW area are available for each class of interrupt.

#### 1.2.1.3. Interrupts

Seven classes of interrupts are available in the processor. In all cases, each interrupt causes the contents of the PSW register to be stored in the old PSW area and the new PSW to be loaded into the PSW register. The seven classes of interrupts are:

#### Supervisor call

This interrupt is used for communicating between the problem program and the supervisor program. The interrupt is caused by the execution of the supervisor-call instruction (SVC).

#### Program exception

This interrupt is caused by illegal operation codes, privileged instruction execution in problem mode, storage protection violation, addressing and specification exceptions, binary and decimal overflow, and divide check.

#### Timer

This interrupt is caused by the interrupt count field of the timer word being decremented from 1 to 0.

This interrupt is caused by an I/O interrupt on selector channel 1.

Selector channel 2

This interrupt is caused by an I/O interrupt on selector channel 2.

Multiplexer channel (shared subchannel)

This interrupt is caused by an I/O interrupt on the shared subchannels of the multiplexer channels.

■ Multiplexer channel (nonshared subchannel)

This interrupt is caused by an I/O interrupt on one of the nonshared multiplexer subchannels.

#### 1.2.1.4. Timer

The timer is standard equipment and provides variable-length, periodic interrupts and an interval timer. The timer is used to measure elapsed time over 2-minute (short) intervals and maintains the time of day by providing the necessary data for logging job functions. The timer is decremented in the interrupt count field and incremented in the running time counter (interval timer) field of the timer word each millisecond. The range of the interrupt count is 1 to  $(2^{12}-1)$  milliseconds (4096-1). The range of the interval timer is 0 to  $(2^{17}-1)$  milliseconds (131,072-1).

#### 1.2.1.5. Instruction Types

The instructions are:

- register-to-indexed-storage and indexed-storage-to-register (RX);

- storage-to-immediate-operand (SI);

- register-to-register (RR);

- storage-to-storage (SS); and

- register-to-storage and storage-to-register (RS).

The basic RX execution (add) time is 6.0 microseconds. For exact execution times for all instructions, see Appendix A.

#### 1.2.2. I/O Section

The I/O section consists of the I/O channels and the I/O interface connecting the channels with the subsystem controllers. This section initiates, directs, and monitors the transfer of data between main storage and the peripheral subsystems. One multiplexer channel is provided as part of both the 9400 and 9480 systems. Up to two selector channels may be added as optional features to the 9400 system, while the 9480 system is provided with one selector channel as part of its system, with the capability of a second selector channel being added as an optional feature.

# 1.2.2.1. Multiplexer Channel

Data transfer for the multiplexer channel is a maximum of 85k bytes per second for restricted applications, the transfer mode being a single byte.

The channel is capable of operating with eight shared subchannels and 128 nonshared subchannels, the 128 nonshared subchannels being part of the communications adapter optional feature. The adapter enables:

- special-character recognition;

- odd or even parity generation and checking;

- data chaining; and

- status tabling.

#### 1.2.2.2. Selector Channels

Data transfer for the selector channel is a maximum of 333k bytes per second. This data rate can be sustained on one selector channel so long as no interference is encountered from a second selector channel.

The channel is capable of operating with eight subchannels (not simultaneously) in burst mode with command chaining.

#### 1.2.3. Main Storage

Main storage access is a 600-nanosecond cycle time: using plated-wire type storage modules expandable from 32K bytes to 256K bytes (UNIVAC 9400 System); using semiconductor type storage modules expandable from 64K bytes to 256K bytes (UNIVAC 9480 System). Main storage contains a ninth bit associated with each byte for parity. Locations are consecutively numbered in main storage, with each address specifying one byte of information. Bytes may be accessed separately or in groups. The address of a group of bytes is the leftmost byte of the group. Main storage is specified in terms of K bytes of capacity, the K term being defined as 210 or 1024 bytes.

#### 1.2.3.1. Parity Checking

The parity bit is checked as data, is read out of storage, and regenerated when data is altered as a result of processing or when data is introduced into the processor from peripheral devices. Parity also is checked and generated at the I/O channel interface to a bus to verify the transmission between the channel and device controls. Odd parity is the correct parity; even parity (parity error) causes the processor to stop.

#### 1.2.4. System Console

The system console consists of a printer, keyboard, and associated I/O interface logic. The keyboard and printer, which are housed in a desk-like cabinet attached to the processor, derive power from the processor.

The system console control is housed in the processor cabinet.

The system console keyboard generates 8-bit EBCDIC characters, each being transferred to the control with an uppercase or lowercase strobe pulse.

When the control holds an active read command, the keyboard transmits characters to the printer and channel in an online mode, or to the printer only in an offline mode. Once the control receives a character, another character is not accepted until the first is printed.

Two types of printers are provided for the system console. For processors with serial numbers between 100 and 204, a 10-character-per-second print rate is provided. For processors with serial numbers 205 and above, a printer with a 25-character-per-second print rate is provided. The control required to translate data bytes coded in EBCDIC to the interface signals required by the printer is provided by printer control located in the processor.

#### 1.3. CONFIGURATIONS

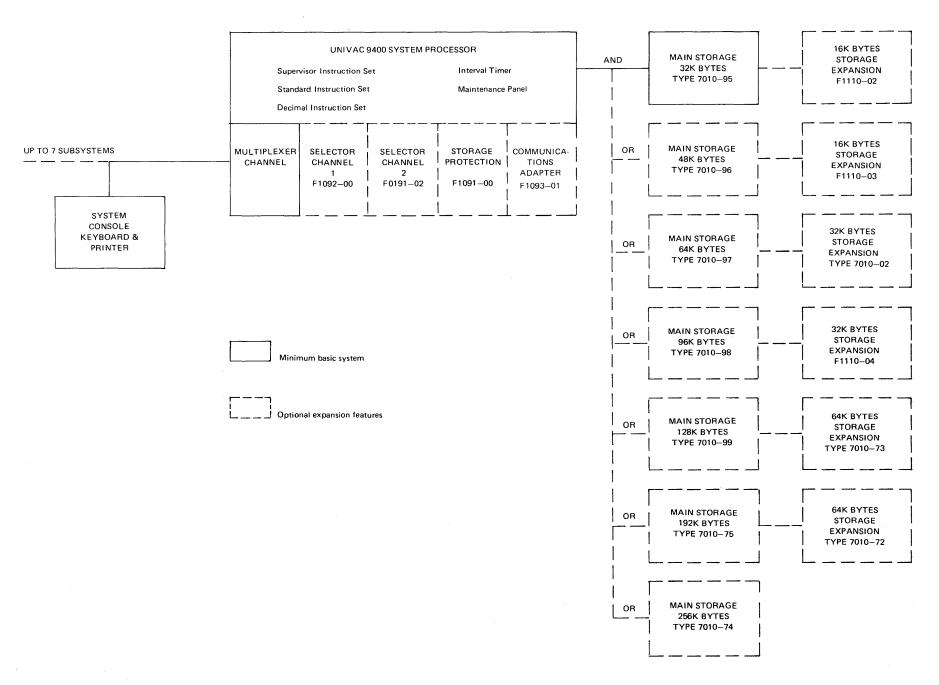

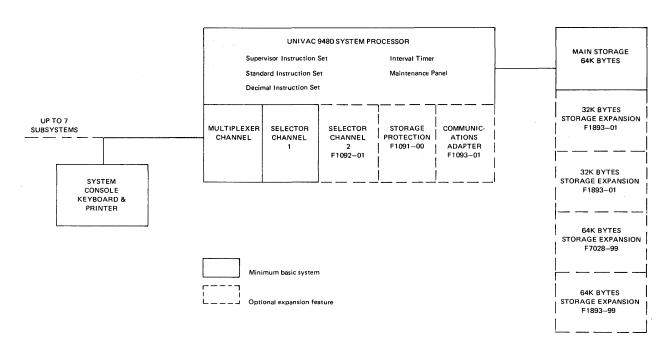

The minimum and expanded configurations of the systems processors are illustrated in Figures 1–2 and 1. The minimum configuration for each system processor is defined by the solid-line boxes. The dashed-line boxes define the possible expanded configuration for each system. All expansions for each system are optional features. The features available for each system are listed, and briefly described, in Table 1–1.

#### 1.3.1. Minimum Configurations

- Processor

- UNIVAC 9400 System Processor

- UNIVAC 9480 System Processor

- Internal main storage

- UNIVAC 9400 System Processor: minimum of 32K bytes of plated-wire main storage

- UNIVAC 9480 System Processor: minimum of 64K bytes of semiconductor main storage

- Multiplexer channel

- Selector channel 1

- System console, keyboard, and printer

#### 1.3.2. Expanded Configurations

The optional expansion features are:

- Selector channel 2

- Communications adapter

- Storage protection

- Main storage

- UNIVAC 9400 System Processor: maximum of two 16K-byte, two 32K-byte, and two 64K-byte storage expansion modules, resulting in a maximum of 256K bytes of main storage.

- UNIVAC 9480 System Processor: maximum of two 32K-byte and two 64K-byte storage expansion modules, resulting in a maximum of 256K bytes of main storage.

Figure 1-2. UNIVAC 9400 System Processor Configuration

Figure 1-3. UNIVAC 9480 System Processor Configuration

Table 1-1. Optional Hardware Expansion Features (Part 1 of 2)

| Feature/Type<br>Number | Name                      | Description                                                                                                                                                         |

|------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                           | Provides additional I/O capability for eight high-speed subsystems.<br>Maximum transfer rate is 333k bytes (includes command chaining).                             |

| F109201                | Selector channel 2        | Provides second selector channel with same characteristics as selector channel 1.                                                                                   |

| F1091-00               | Storage protection        | Provides program write protection over contiguous increments of 512 bytes for a system up to 131,072 bytes or 1024 bytes for systems with more than 131,072 bytes.  |

| F1093-00               | Communications<br>adapter | Provides interfaces and control required to coordinate the transfer of data between this feature and a maximum of 12 line adapters (communications line terminals). |

|                        |                           | Provides 128 nonshared multiplexer subchannels for the Data Communications Subsystem (DCS).                                                                         |

Table 1-1. Optional Hardware Expansion Features (Part 2 of 2)

| Feature/Type Name                                                                                                                                    |                                  | Description                                                                                                                         |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Storage Expansion, UNIVAC 9400 System Processor                                                                                                      |                                  |                                                                                                                                     |  |  |

| 7010–96 Main storage (48K pytes)  Main storage (48K pytes)  Provides 49,152 bytes of main storage expandable to 65,536 bytes                         |                                  | Provides 49,152 bytes of main storage expandable to 65,536 bytes.                                                                   |  |  |

| 7010–97                                                                                                                                              | Main storage<br>(64K bytes)      | Provides 65,536 bytes of main storage expandable to 98,304 bytes.                                                                   |  |  |

| 7010–98                                                                                                                                              | Main storage<br>(96K bytes)      | Provides 98,304 bytes of main storage expandable to 131,072 bytes.                                                                  |  |  |

| 7010–99                                                                                                                                              | Main storage<br>(128K bytes)     | Provides 131,072 bytes of main storage expandable to 196,608 bytes.                                                                 |  |  |

| 701075                                                                                                                                               | Main storage<br>(192K bytes)     | Provides 196,608 bytes of main storage expandable to 262,144 bytes.                                                                 |  |  |

| 7010—74                                                                                                                                              | Main storage<br>(256K bytes)     | Provides maximum of 262,144 bytes of main storage.                                                                                  |  |  |

| F1110-02                                                                                                                                             | Storage expansion<br>(16K bytes) | Provides 16,384 bytes of storage to be added to type 7010—95 main storage for a total of 49,152 bytes.                              |  |  |

| F1110-03                                                                                                                                             | Storage expansion<br>(16K bytes) | Provides 16,384 bytes of storage to be added to type 7010–96 main storage for a total of 65,536 bytes.                              |  |  |

| 701002                                                                                                                                               | Storage expansion<br>(32K bytes) | Provides 32,768 bytes of storage to be added to type 7010–97 main storage for a total of 98,304 bytes.                              |  |  |

| F1110-04                                                                                                                                             | Storage expansion<br>(32K bytes) | Provides 32,768 bytes of storage to be added to type 7010–98 main storage for a total of 131,072 bytes.                             |  |  |

| 7010-73                                                                                                                                              | Storage expansion<br>(64K bytes) | Provides 65,536 bytes of storage to be added to type 7010–99 main storage for a total of 196,608 bytes.                             |  |  |

| 7010–72                                                                                                                                              | Storage expansion<br>(64K bytes) | Provides 65,536 bytes of storage to be added to type 7010—75 main storage for a maximum total of 262,144 bytes.                     |  |  |

|                                                                                                                                                      | Storage Exp                      | pansion, UNIVAC 9480 System Processor                                                                                               |  |  |

| F1893-01                                                                                                                                             | Storage expansion                | Provides a 32,768-byte storage increment to be added to minimum main storage (65,532 bytes) for a total of 98,304 bytes of storage. |  |  |

| F1893-01                                                                                                                                             | Storage expansion                | Provides a 32,768-byte storage increment to be added to a 98,304-byte storage for a total of 131,072 bytes of storage.              |  |  |

| F7028-99                                                                                                                                             | Storage expansion                | Provides a 65,536-byte storage increment to be added to a 131,072-byte storage for a total of 196,608 bytes of storage.             |  |  |

| F1893—99 Storage expansion Provides a 65,536-byte storage increment to be added to a 196,608-byte storage for a maximum of 262,144 bytes of storage. |                                  |                                                                                                                                     |  |  |

#### 1.4. CHARACTERISTICS

The processors are small-to-medium scale in size and capabilities, handling random or sequential batch processing, and communication-oriented data processing with a maximum repertoire of 70 instructions.

The characteristics, capabilities, and optional features available for the processor, main storage, I/O channels, and some typical peripheral devices are listed in Table 1–2.

Table 1-2. UNIVAC 9400 and 9480 Characteristics

|                                                                                   | Processor                                                                              |                                                                                |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Data organization                                                                 | 8-bit byte                                                                             |                                                                                |

| Decimal multiply and divide instructions                                          | Included as part of standard instruction repertoire                                    |                                                                                |

| Edit instructions Included as part of standard instruction repertoire             |                                                                                        |                                                                                |

| Add (binary) instruction time (two 32-bit words)                                  | 6 microseconds                                                                         |                                                                                |

| Registers                                                                         | 16 for problem program fur<br>16 for supervisor functions                              | nctions                                                                        |

|                                                                                   | Main Storage                                                                           |                                                                                |

|                                                                                   | UNIVAC 9400                                                                            | UNIVAC 9480                                                                    |

| Туре                                                                              | Plated wire                                                                            | Semiconductor (chip)                                                           |

| Storage access time                                                               | 600 nanoseconds<br>per 2 bytes                                                         | 600 nanoseconds<br>per 2 bytes                                                 |

| Storage capacity                                                                  | Minimum 32K bytes;<br>maximum 256K bytes in<br>16K-, 32K-, and 64K-<br>byte increments | Minimum 64K bytes;<br>maximum 256K bytes in<br>32K- and 64K-byte<br>increments |

| Storage protection                                                                | Optional feature                                                                       | Optional feature                                                               |

|                                                                                   | I/O Channels                                                                           |                                                                                |

| Multiplexer channel                                                               | One — standard                                                                         | One – standard                                                                 |

| Multiplexer channel transfer rate                                                 | 85,000 bytes per second                                                                |                                                                                |

| Selector channels                                                                 | Two — maximum as optional features                                                     | One — standard, one as an optional feature                                     |

| Selector channel transfer rate                                                    | 333,000 bytes per second                                                               | -                                                                              |

| Communications adapter                                                            | Up to 64 duplex lines as an optional feature                                           |                                                                                |

|                                                                                   | Typical Peripheral Devices                                                             |                                                                                |

| Card reader                                                                       | 600 or 1000 cards per minu                                                             | ute                                                                            |

| Card punch                                                                        | 250 cards per minute                                                                   | -                                                                              |

| Read/punch                                                                        | Optional feature to card pu                                                            | nch                                                                            |

| Printer 840 to 1600 lines per minute, depending on print drum                     |                                                                                        |                                                                                |

| Magnetic tape Transfer rate of 34,160 to 192,000 bytes per second                 |                                                                                        |                                                                                |

| Disc storage Auxiliary storage for 29.18 or 58.35 million bytes per disc<br>drive |                                                                                        |                                                                                |

# 2. Processor

#### 2.1. INFORMATION FORMATS

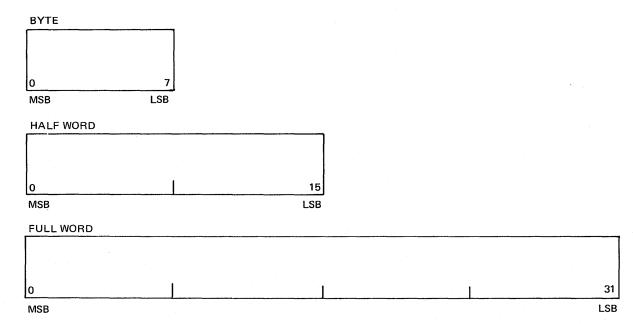

Data and instructions are transmitted in single or multiple 8-bit increments called bytes. Up to four bytes of information may be transmitted in parallel between various sections of the system. Instructions are made up of half-word lengths and can be 1, 2, or 3 half words long.

A half word is defined as a field containing two consecutive bytes and is basic for the instructions. A full word is a field containing four consecutive bytes. Figure 2–1 illustrates the various word formats and bit numbering.

Fixed-length fields such as half words and full words are located in main storage on a integral boundary for the unit of information. Instructions must be located on half-word boundaries. An integral boundary is defined as main storage address for a unit of information that is a multiple of the length of the unit in bytes, as follows:

Half word (two bytes) - multiple of 2

Full word (four bytes) - multiple of 4

Storage addresses are expressed in binary form within the processor. Integral boundaries for half words and full words are given as binary addresses in which 1 or 2 of the low-order bits are 0, respectively.

Variable-length fields are not limited to integral boundaries and can start at any byte address.

Figure 2-1. Information Formats

#### 2.1.1. Data Formats

Data is represented in several different formats, depending on the type of instruction that is to manipulate the data.

#### 2.1.1.1. Fixed-Point Numbers

Fixed-point numbers are represented in one of three fixed-length formats consisting of one sign bit (bit 0) followed by a binary integer field. When the sign bit is set to 1, the integer represents a negative value; when set to 0, the integer represents a positive value. Negative integers are represented in the twos complement notation.

The half-word and full-word formats are as follows:

| HA | LF WORD |

|----|---------|

| s  | INTEGER |

| 0  | 1 15    |

| FU | FULL WORD |         |                                       |    |  |

|----|-----------|---------|---------------------------------------|----|--|

|    |           |         |                                       |    |  |

| s  |           | INTEGER |                                       | 1  |  |

| į. |           |         |                                       |    |  |

| 0  | 1         |         | · · · · · · · · · · · · · · · · · · · | 31 |  |

When held in one of the 16 general registers, a fixed-point number is treated as a 32-bit operand.

#### 2.1.1.2. Decimal Numbers

Decimal numbers are represented in signed absolute form and in either packed or unpacked formats with variable lengths. These are used in decimal arithmetic and logical operations. For decimal operations, the numbers are again processed from data stored in the general purpose registers or in main storage, and the results are returned to the general purpose registers or sent to main storage, requiring a field area of from 1 to 16 eight-bit bytes.

The packed and unpacked decimal formats are:

#### UNPACKED DECIMAL FORMAT

| BYT<br>(HIGH C |       | ВҮТ  | E 2   |      | TE n<br>DRDER) |

|----------------|-------|------|-------|------|----------------|

| ZONE           | DIGIT | ZONE | DIGIT | SIGN | DIGIT          |

#### PACKED DECIMAL FORMAT

| BYT<br>(HIGH C | TE 1<br>ORDER) | ву    | ΓΕ 2  |       | TE n<br>DRDER) |

|----------------|----------------|-------|-------|-------|----------------|

| DIGIT          | DIGIT          | DIGIT | DIGIT | DIGIT | SIGN           |

#### 2.1.1.3. Logical Information

Logical information is processed as fixed-length or variable-length data. Operations using this type of information include moving, comparing, translating, editing, bit testing, bit manipulation, and shifting.

Fixed-length data, which consists of 1 or 4 bytes, is processed from data stored in the general purpose register or in main storage, and the results are returned to these registers or to main storage.

Data in the general registers normally occupies all 32 bits. In logical operations, all bits are treated uniformly, with no distinction made between sign and numeric bits. In some operations, only the low-order eight bits of a register are used; the remaining 24 bits are unchanged.

Logical data in fixed-length format is:

| BYTE |        |   |

|------|--------|---|

| ļ    | BYTE 1 |   |

|      |        |   |

| j    |        |   |

| 0    |        | 7 |

|   | ORD<br>BYTE 1<br>GH ORDER) | BYTE 2 | BYTE 3 | BYTE 4<br>(LOW ORDER) |

|---|----------------------------|--------|--------|-----------------------|

|   |                            |        |        |                       |

| 0 | 7                          | 8 15   | 16 23  | 24 31                 |

Variable-length data contains up to 256 bytes of alphabetic or numeric character codes (alphanumeric data). This information is again processed from data stored in the processor or in main storage, and the results are returned to the processor or to main storage; the information occupies fields that may start at any byte address. The processing order of variable-length data is from high-order (most significant) byte to the low-order (least significant) byte.

Logical data in variable-length format is:

| (H | BYTE 1<br>HIGH ORDER) | BYTE 2 | BYTE 256<br>(LOW ORDER) |

|----|-----------------------|--------|-------------------------|

|    |                       |        |                         |

| 0  | 7                     | 8 15   | <br>2040 2047           |

#### 2.1.2. Instruction Formats

Instructions are identified by an opcode, which is the most significant byte (eight bits) of the instruction. Two general categories of instructions related to a processor state are available to the programmer:

#### Supervisor (Privileged) Instructions

Privileged instructions can be executed only when the processor is in the supervisor state. The current PSW specifies the operating state of the processor. Processor states may switch as a result of an interrupt condition that causes a new PSW to be obtained from storage or from a load-program-status-word (LPSW) instruction. If the program in program mode attempts to execute a privileged instruction, a program exception interrupt occurs. It should be noted that the supervisory routines use the privileged instructions, and the problem programmer should avoid these instructions.

#### Problem (Nonprivileged) Instructions

The problem instructions can be executed either in the supervisor or in the program state.

The format used for programmed instructions for directing peripheral devices and processing data may vary in format and length. The format used is dictated by the operation to be performed and the operand location. The length of the instruction is dictated by the format and is either 1, 2, or 3 half words.

The five instruction formats are shown in Figure 2-2 and are identified as follows:

- register-to-register (RR);

- register-to-indexed storage (RX);

- register-to-storage (RS);

- storage-to-immediate operand (SI); and

- storage-to-storage (SS).

Figure 2-2. Instruction Formats (Part 1 of 2)

| Symbol         | Definition                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| opcode         | Instruction operation code                                                                                                                                                                                                                                                                                                                                                                     |

| r <sub>1</sub> | Number of a general register containing the first operand. If an arithmetic compilation, $r_1$ field specifies where result is to be stored. For RS instruction, $r_1$ field contains either the first operand or the number that represents a boundary for general register usage. For RR and RX instructions, the $r_1$ field is used as a mask in the branch-on-condition (BC) instruction. |

| r <sub>2</sub> | Number of a general register containing the second operand. Both $r_1$ and $r_2$ may be the same if the same operand is used.                                                                                                                                                                                                                                                                  |

| r <sub>3</sub> | Number of a general register containing the third operand, or the number representing a boundary for general register usage. This field is ignored when executing shift instructions.                                                                                                                                                                                                          |

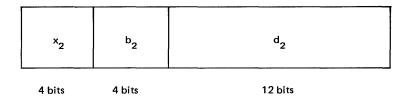

| × <sub>2</sub> | The number of a general register containing an index number. When field is 0, index number is 0.                                                                                                                                                                                                                                                                                               |

| i <sub>2</sub> | Immediate data used as operand 2 of an SI instruction.                                                                                                                                                                                                                                                                                                                                         |

| 11             | For instructions with opcodes Fx (where x is any hexadecimal digit 0 through F), contains a 4-bit number specifying the number of additional bytes in the first operand field that are to the right of the leftmost byte.                                                                                                                                                                      |

| <sup>1</sup> 2 | For instructions with opcodes Fx (where x is any hexadecimal digit 0 through F), contains a 4-bit number specifying the number of additional bytes in the second operand field that are to the right of the leftmost byte.                                                                                                                                                                     |

| 1              | For instructions with opcodes Dx (where x is any hexadecimal digit 0 through F), I <sub>1</sub> and I <sub>2</sub> are combined as I to form an 8-bit number specifying the number of additional bytes that are to the right of the operand address. Operands 1 and 2 may overlap except for the decimal-multiply and decimal-divide instructions.                                             |

| b <sub>1</sub> | The number of a general register containing an index number representing the base address of the first operand. When 0, base address is 0.                                                                                                                                                                                                                                                     |

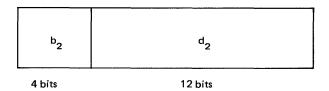

| b <sub>2</sub> | The number of a general register containing an index number representing the base address of the second operand; when 0, the base address is 0.                                                                                                                                                                                                                                                |

| d <sub>1</sub> | Contains a 12-bit number that, when added to the contents of $b_1$ , represents the address of the leftmost (high order) byte of the first operand.                                                                                                                                                                                                                                            |

| d <sub>2</sub> | Contains a 12-bit number that, when added to the contents of B <sub>2</sub> , represents the address of the second operand. For shift instructions, it represents the number of bits of shifting to be performed. For an SS instruction, it represents the address of the leftmost (high order) byte of the second operand.                                                                    |

| op 1           | Operand 1                                                                                                                                                                                                                                                                                                                                                                                      |

| op 2           | Operand 2                                                                                                                                                                                                                                                                                                                                                                                      |

| ор 3           | Operand 3                                                                                                                                                                                                                                                                                                                                                                                      |

Figure 2-2. Instruction Formats (Part 2 of 2)

#### 2.1.3. Fixed-Point Arithmetic

Fixed-point arithmetic operations include binary arithmetic on operands serving as addresses, indexed quantities, counts, and fixed-point data. In general, both operands are signed (negative or positive) and 32 bits long. Sixteen-bit operands may be specified to conserve storage locations. Negative quantities are held in the two's-complement form. One operand is always in one of the 16 general registers; the other can be in storage or in another general register. The fixed-point instructions (RR, RX, and RS) provide for loading, adding, subtracting, comparing, storing, and shifting of fixed-point operands. The condition code (2.1.3.3) is set as a result of all add, subtract, compare, and shift operations.

2-6

# 2.1.3.1. Fixed-Point Data Formats

Fixed-point numbers occupy a fixed-length format consisting of a sign bit followed by the integer field. When held in one of the general registers, a fixed-point quantity consists of a 31-bit integer field and occupies all 32 bits of the register. In register-to-register operations, the same register may be specified for both operand locations. Fixed-point data in storage occupies a 32-bit full word or a 16-bit half word with a binary integer field of 31 or 15 bits, respectively. A half word in storage is extended to a full word as the operand is retrieved from storage. Subsequently, the operand participates as a full-word operand.

#### 2.1.3.2. Fixed-Point Number Representation

All fixed-point operands are treated as signed integers. Positive numbers are true binary notation with the sign bit set to 0. Negative numbers are represented in the twos complement notation with a 1 in the sign bit position. The twos complement of a number is obtained by inverting each bit of the number and adding a 1 in the low-order bit position. This type of number representation can be considered the low-order portion of an infinitely long representation of the number. When the number is positive, all bits to the left of the most significant bit of the number, including the sign bit, are 0's. When the number is negative, all these bits, including the sign bit, are 1's. When an operand must be extended with high-order bits, the expansion is achieved by prefixing a field in which each bit is set equal to the high-order bit of the operand.

The twos-complement notation does not include a negative 0. It has a number range in which the set of negative numbers is one larger than the set of positive numbers. The maximum positive number consists of a 1's integer field with a sign bit of 0; the maximum negative number consists of 0's integer field with a 1 bit for the sign.

The processor cannot represent the complement of the maximum negative number. When an operation (such as a subtraction from 0) produces the complement of the maximum negative number, the number remains unchanged, and a binary overflow exception interruption is recognized. An overflow does not result when the number is complemented and the final result is within the representable range. An example of this is a subtraction from minus 1.

The sign bit is leftmost in a number. An overflow carries into the sign bit and does not change even if the significant high-order bits are shifted out. The twos-complement notation is particularly suited to address computation and multiple-precision arithmetic. The twos-complement representation of a negative number may be considered the sum of the integer part of the field, taken as a positive number, and the maximum negative number. Therefore, in multiple-precision arithmetic, the low-order fields should be treated as positive numbers. Also, when negative numbers are shifted to the right, the resulting rounding off, if any, is toward minus infinity and not toward 0.

#### 2.1.3.3. Fixed-Point Condition Code

The results of fixed-point add, subtract, compare, and shift operations are used to set the condition code (bits 34 and 35) in the program status word (2.2.1). Loading and storing operations leave this code undisturbed. The condition code can be used for decision-making by subsequent branch-on-condition instructions.

The condition code can be set to reflect three types of results for fixed-point arithmetic. For most operations,  $00_2$ ,  $01_2$ , or  $10_2$  condition codes indicate a zero, less-than-zero, or greater-than-zero content of the result register, respectively; an  $11_2$  condition code is used when the result overflows. For a comparison, the  $00_2$ ,  $01_2$ , or  $10_2$  condition codes indicate that the first operand is equal to, less than, or greater than, the second operand, respectively.

#### 2.1.4. Decimal Arithmetic

Decimal arithmetic operations on data occur in the packed format. In this format, two decimal digits are placed in one 8-bit byte. Inasmuch as data is often communicated to or from external devices in the zoned (unpacked) format, the necessary format conversion operations also are provided in the decimal instruction (SS) group.

Data is interpreted as integers, right-aligned in their fields, and is kept in true notation with a sign in the low-order 4-bit byte.

Processing occurs from right to left between storage locations. All decimal arithmetic instructions are a 2-address SS format. Each address specifies the leftmost byte of an operand. Associated with this address is a length field indicating the number of additional bytes that the operand extends beyond the first byte.

The decimal arithmetic instruction set provides for adding, subtracting, comparing, multiplying, and dividing, as well as the format conversion of variable-length operands.

The condition code is set as a result of all addition, subtraction, and comparison operations.

#### 2.1.4.1. Decimal Data Formats

Decimal operands reside in main storage only. They occupy fields that may start at any byte address and consist of 1 to 16 bytes.

Lengths of the two operands specified in an instruction need not be the same. They are considered to be extended with 0's to the left of the high-order digits. Results never exceed the limits set by addresses and length specification. Lost carries or lost digits from arithmetic operations are signaled as a decimal overflow exception interruption.

Operands are either in the packed or unpacked (zoned) format. In the packed format, two decimal digits are normally placed adjacent in a byte, except for the rightmost byte of the field. A sign is placed to the right of decimal digits in the rightmost byte. Both digits and a sign are encoded and occupy four bits each. In the unpacked (zoned) format, the low-order four bits of the byte, the numeric, are normally occupied by a decimal digit. The four high-order bits of a byte are called the zone, except for the rightmost byte of the field, where, normally, the sign occupies the zone position.

Arithmetic operations are performed with operands and results are in the packed format. In unpacked format, the digits are represented as part of an alphanumeric character set. A pack instruction is provided to transform unpacked data into packed data and an unpack instruction performs the reverse transformation. The edit instruction is used to change data from packed to unpacked format.

In move-type operations, the operand digits and sign are not checked, and the operand fields may overlap without restrictions. For example, in the move characters (MVC) instruction, the multiple-byte first operand is in storage at address  $d_1+(b_1)$  and the length specification is I (SS type instruction). The multiple-byte second operand is in storage at address d<sub>2</sub>+(b<sub>2</sub>) and the length specification is I. The second operand replaces the first operand. Storage occurs from left to right, one byte at a time.

#### 2.1.4.2. Decimal Number Representation

Numbers are represented as right-aligned true integers with a plus or minus sign. The digits 0 through 9 are binary-coded 0000 through 1001. The codes 1010<sub>2</sub> through 1111<sub>2</sub> are invalid as digits. This set of codes is interpreted as sign codes with  $1010_2$ ,  $1100_2$ ,  $1110_2$ , and  $1111_2$  recognized as plus, and with  $1011_2$  and  $1101_2$  recognized as minus. The codes  $0000_2$  through  $1001_2$  are invalid as sign codes. The zones are not tested for valid codes, inasmuch as they are eliminated in changing data from the unpacked to packed format.

PAGE REVISION

UP-NUMBER

The sign and zone codes generated for all decimal arithmetic results differ for EBCDIC and ASCII. The choice between the two codes is determined by the a field (bit 12) of the PSW (2.2.1). When the a field is 0, the preferred EBCDIC codes are generated. These are plus, 11002; minus, 11012; and zone, 11112. When the a field is 1, the preferred ASCII codes are generated. These are plus, 1010<sub>2</sub>; minus, 1011<sub>2</sub>; and zone, 0101<sub>2</sub>.

#### 2.1.4.3. Decimal Condition Code

The results of all addition, subtraction, and comparison operations are used to set the condition code. All other decimal arithmetic operations leave the code unchanged. The condition code can be used for decision making by subsequent branch-on-condition instructions.

The condition code can be set to reflect two types of results for decimal arithmetic operations. For most operations, 002, 012, and 102 condition codes indicate a zero, less-than-zero, and greater-than-zero for the content of the result field, respectively. The 11, condition code is used when the result of the operation overflows.

For the comparison operation,  $00_2$ ,  $01_2$ , or  $10_2$  condition codes indicate that the first operand is equal to, less than, or greater than the second operand field, respectively.

#### 2.1.5. Logical Operations

A set of instructions is provided for the logical manipulation of data, with the operands treated generally as 8-bit bytes. In a few cases, the left or right four bits are treated separately or operands are shifted a bit at a time. The operands are either in storage or in a general register. Some operands are introduced from the instruction stream (SI instructions).

Processing of data in main storage proceeds from left to right through fields that can start at any byte position. In the general registers, the processing generally involves the entire register contents.

Except for the edit instruction, data is not treated as numbers. Editing provides a transformation from packed decimal to alphanumeric characters. The set of logical operations includes moving, comparing, bit setting, bit testing, translating, editing, and shift operations.

The condition code is set as a result of all logical comparing, connecting, testing, and editing operations.

#### 2.1.5.1. Logical Data Formats

Data resides in general registers or in storage, or is introduced from the instruction stream. The data size can be a single word, a single character, or a variable length. When two operands are involved, they are of equal length, except in the edit instruction. Data in the general registers normally occupies all 32-bits. Bits are treated uniformly, and no distinction is made between sign and numeric bits. In a few operations, only the low-order eight bits of a register are involved, leaving the remaining 24 bits unchanged.

When the processor has access to less than 128K bytes of main storage, the load-address instruction introduces a 17-bit address into a general register, and the high-order 15 bits of the register are made 0. If the processor has access to a main storage greater than 128K bytes, the load-address instruction introduces a 16-bit address into a general register, and the high-order 14 bits of the register are made 0.

In RS operations, the storage data occupies either a full word of 32 bits or a byte of eight bits. The word must be located on full-word boundaries; that is, the two low-order bits of its address must be 0's.

In SS operations, data is of variable-length field format, starting at any byte address and continuing to a total of 256 bytes, processing again being from left to right.

Operations introducing data from the instruction stream into main storage as immediate data are restricted to an 8-bit byte. Only one byte is introduced from the instruction stream, and only one byte in storage is involved.

Editing requires a packed decimal field and generates zoned decimal digits. These digits, signs, and zones are recognized and generated the same as for decimal arithmetic. Therefore, no internal data structure is required and all bit configurations are considered valid.

The translating operations use a list of arbitrary values. A list provides a relationship between an argument (the quantity used to reference the list) and the function (the contents of the location related to the argument). The purpose of the translation may be to convert data from one code to another or to perform a control function.

A list is specified by an initial address that designates the leftmost byte location of the list. The byte from the operand to be translated is the argument. The actual address used to address the list is obtained by adding the argument to the low-order positions of the initial address. As a result, the list contains 256 eight-bit function bytes. In cases where it is known that not all 8-bit argument values occur, it may be possible to reduce the size of the list.

In SS operations, the operand fields can be defined in such a way that they overlap. The effect of this overlap depends upon the operation. When the operands remain unchanged, as in the compare instruction, overlapping does not affect the execution of the instruction. For the edit and translate instructions, one operand is replaced by new data, and the execution of the operation may be affected by the amount of overlap and the manner in which data is fetched and stored. For purposes of evaluating the effect of overlapped operands, consider that the data is handled one byte at a time. All overlapping fields are considered valid, but in editing, overlapping fields give unpredictable results.

#### 2.1.5.2. Logical Condition Code

The results of most logical operations are used to set the condition code in the PSW. The load-address, insert-character, store-character, and translate instructions, along with the moving and shift operations, leave the condition code unchanged. The condition code can be used for decision-making by subsequent branch-on-condition instructions.

The condition code can be set to specify the following results for logical operations:

#### Compare-logical instructions

The  $00_2$ ,  $01_2$ , or  $10_2$  values indicate that the first operand is equal to, less than, or greater than the second operand, respectively.

#### Test-under-mask instruction

The  $00_2$ ,  $01_2$ , or  $10_2$  values indicate that the selected bits are 0's, mixed 0's and 1's, or 1's, respectively.

#### Editing instructions

The  $00_2$ ,  $01_2$ , or  $10_2$  values indicate a zero, less-than-zero, or greater-than-zero content, respectively, of the last result field.

#### 2.1.6. Branching

Instructions are executed primarily in the sequential order of their locations. A departure from this normal sequential operation may occur when branching is performed. The branching instructions provide a means for making a 2-way choice:

- to reference a subroutine; or

- to repeat a segment of coding, such as a loop.

Branching is performed by introducing a branch address as a new instruction address. The branch address may be obtained from one of the general registers or it may be the address specified by the instruction. The branch address is independent of the updated instruction address.

Operational details of branching are determined by the condition code, or by the results in the general registers that are specified in the loop-closing operations.

During a branching operation, the rightmost half of the PSW, including the updated instruction address, may be stored before the instruction address is replaced by the branch address. The stored information may be used to link the new instruction sequence with the preceding instruction sequence.

#### 2.1.6.1. Normal Sequential Operation

Normal operation of the processor is controlled by the sequence of instructions. An instruction is retrieved from a location specified by the instruction address field of the PSW. The instruction address is incremented by the number of the bytes of the instruction in order to address the next instruction in sequence. This new instruction-address value, called the updated instruction address, replaces the previous contents of the instruction-address field in the PSW. The current instruction is executed, and the same steps are repeated, using the updated instruction address to fetch the next instruction.

Instruction length is a half word or multiple of a half word. An instruction can be composed of up to three half words. The number of half words in an instruction is specified by the instruction length code (ILC), bits 32 and 33 of the PSW. An 01<sub>2</sub> code specifies a half word instruction; a 10<sub>2</sub> code specifies a 2-half-word instruction, and an 11<sub>2</sub> code specifies a 3-half-word instruction. Code 00<sub>2</sub> specifies length is not available.

Main storage wraps around from the maximum addressable storage location, byte location 262,143 to byte location 0. An instruction with a last half word at the maximum storage location is followed by the instruction at address 0. Also, a multiple half-word instruction may straddle the upper storage boundary; no special indication is given in these cases.

Actually, an instruction is retrieved from main storage after the preceding operation is compiled and before execution of the current operation, even though physical storage-word size and overlap of instruction execution with storage access may cause the retrieved instruction to be different.

A change in the sequential operation may be caused by branching, interruption, or manual intervention. Sequential operation is initiated and terminated from the system console and maintenance panel. (It is possible to modify an instruction in main storage with an immediately preceding instruction.)

Exceptional instruction addresses or operation codes cause a program interruption. When the interruption occurs, the current PSW is stored as an old PSW, and a new PSW is obtained. The interrupt code in the old PSW identifies the cause of the interruption. The following program interruptions can occur in normal instruction sequencing, independently of the instruction performed.

#### Illegal operation exception

Caused by an operation code not having been assigned.

#### Addressing exception

Caused by a reference to main storage outside the problem program boundaries when the processor is in the problem state.

#### Specification exception

Caused when reference to main storage is not on the proper boundary.

In each case, the operation is suppressed; therefore, the condition code and the data in main storage and in the register remains unchanged. The instruction address stored as part of the old PSW is updated by the number of half words indicated by the ILC in the old PSW.

It should be noted that an addressing exception address can occur when normal instruction sequencing proceeds from a valid storage region into an unavailable region or following a branching operation.

When the last location in available main storage contains an instruction that again introduces a valid instruction address, no program interruption is caused, even though the updated address designates an unavailable location. The main storage or register address specification of an instruction with an unassigned operation code can cause an addressing or specification exception interruption when the requirements for the particular instruction class are not met.

#### 2.1.6.2. Decision-Making

Branching can be conditional or unconditional. Unconditional branches replace the updated instruction address with the branch address. Conditional branches can use the branch address or can leave the updated instruction address unchanged. When branching occurs, the instruction is called successful; otherwise, it is called unsuccessful. Whether a conditional branch is successful depends on the result of operations concurrent with the branch or preceding the branch. The successful branch is represented by the branch-on-count instruction. The unsuccessful branch is represented by a branch-on-condition instruction which inspects the condition code that reflects the result of a previous arithmetic, logical, or I/O operation.

#### 2.1.6.3. Branching Condition Code

A condition code provides a means of data-dependent decision-making. The code is inspected to qualify the execution of the condition-branch instructions. This code is set by some operations to reflect the result of the operation independently of the previous setting of the code and remains unchanged for all other operations. The condition code occupies bit positions 34 and 35 of the PSW and is stored as part of the rightmost half of the PSW in a branch and link operation. A new condition code is obtained by a load-PSW or set-program-mask instruction, or by a new PSW being loaded as a result of an interruption.

The condition code indicates the outcome of some of the arithmetic, logical, or I/O operations. It is not changed for any branching operation.

#### 2.2. CONTROL SECTION