# TBM Field Engineering Theory of Operation

(Manual of Instruction)

**Restricted Distribution**

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

Specifications contained herein are subject to change without notice. Revisions and/or supplements to this publication will be issued periodically.

System/360 Model 44

ţ

**Principles of Operation-Processing Unit**

.

**Restricted** Distribution

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

Specifications contained herein are subject to change without notice. Revisions and/or supplements to this publication will be issued periodically.

System/360 Model 44

**Principles of Operation-Processing Unit**

#### PREFACE

This volume contains the Principles of Operation for the IBM 2044 Processing Unit, the processor for the IBM System/360 Model 44. The manual describes the operation of the machine instructions (other than floating-point instructions) and program and machine interrupts, for both the basic machine and the basic machine with accelerator feature. Where the description for the basic machine differs from that for the accelerator feature, the relevant text is indented and appropriately headed 'BASIC only' or 'ACCELERATOR only'.

The manual assumes knowledge of the System/360 as described in <u>IBM System/360 Principles of</u> Operation, Form A22-6821.

This volume is one of the manuals that constitute the <u>IBM Field Engineering Theory of Operation</u> manual for the IBM System/360 Model 44. The other volumes and their form numbers are:

System/360 Model 44, Introduction and Functional Units, Form Y33-0001: Gives a general outline of digital computers and computing technique, defines the relationship of the IBM 2044 to the System/360 and describes the various parts which form the processing unit.

System/360 Model 44, Principles of Operation - Channels, Form Y33-0003: Describes the Common Channel area, the Multiplexor Channel 0 and the High Speed Multiplexor Channel. These volumes are referenced in other volumes by the main element of their titles.

Reference is also made in these volumes to the following associated manuals:

- Field Engineering Theory of Operation (FETO), IBM System/360 Model 44, Floating Point Feature, Form Y33-0005: Gives an introduction to floating-point arithmetic, describes the functional implementation of floating-point arithmetic in the 2044 and details the operation of floating-point instructions.

- Field Engineering Theory of Operation (FETO), IBM System/360 Model 44, Single Disk Storage Drive, Form Y33-0006: Gives an introduction to the operation of the control unit and describes in detail the functional parts and the operations that may be performed.

- Field Engineering Maintenance Manual (FEMM), IBM System/360 Model 44, Form Y33-0007: Contains information for servicing the 2044 Processing Unit.

- Field Engineering Maintenance Diagrams (FEMD), IBM System/ <u>360 Model 44</u>, Volume 2, Form Y33-0008: Contains maintenance information in the following categories: Data Flow Charts, Flow Charts, Timing Charts, MAP's.

Other related manuals that describe units used in the System/360 Model 44 are:

- Field Engineering Manual of Instruction (FEMI), 1052 Adapter, Form 223-2808.

- Field Engineering Maintenance Manual (FEMM) Single Disk Storage/Direct Access, Form Y26-3663.

#### First Edition

This manual makes obsolete Field Engineering Theory of Operation, System/360 Model 44, Forms Z33-0003-0, Z33-0004-0.

The manual is written basically to Engineering Change Level 390049 and in some cases anticipates Engineering Change Level 390063. Significant changes or additions to the information in the manual will be covered in subsequent revisions or FE supplements.

This publication was prepared by IBM European Laboratories, Product Publications. A form is provided at the back of this manual for reader's comments. If the form has been removed, comments may be addressed to: IBM Corporation, FE Manuals, Dept. P96, PO Box 390, Poughkeepsie, N.Y. 12602

© International Business Machines Corporation 1966

## CONTENTS

## CHAPTER 3A. PRINCIPLES OF OPERATION --

| PROCESSING UNIT                                   | 3A-1                                               |

|---------------------------------------------------|----------------------------------------------------|

|                                                   | <b></b>                                            |

| Introduction to Instruction Fetching              |                                                    |

| Instruction Format and Decoding                   | 3A-1                                               |

| I-Fetch                                           | 3A-3                                               |

| Instruction Read-Out                              |                                                    |

| No Index Cycles                                   | 3A-4                                               |

| One Index Cycle                                   | 3A-4                                               |

| Two Index Cycles                                  | 3A-5                                               |

| Last Instruction Cycle Conditions                 | 3A-6                                               |

| · · ·                                             |                                                    |

| FIXED-POINT INSTRUCTIONS                          | 3A-7                                               |

| Halfword Expansion                                | 3A-7                                               |

| Load Instructions                                 | 3A-8                                               |

| Load, Load Halfword, Load and Test                | 3A-8                                               |

| RX Format                                         | 3A-8                                               |

| RR Format                                         | 3A-8                                               |

| Load Complement, Load Positive, Load Negative     | 3A-8                                               |

| Load Complement                                   | 3A-9                                               |

| Load Positive                                     | 3A-9                                               |

| Load Negative                                     | 3A-9                                               |

| Result Storage Cycle                              | 3A-9                                               |

|                                                   |                                                    |

|                                                   |                                                    |

| Add, Subtract and Compare Instructions            | 3A-11                                              |

| Add, and Add Halfword Instructions                | 3A-11                                              |

| Subtract, and Subtract Halfword Instructions      | 3A-12                                              |

| Compare, and Compare Halfword Instructions        | 3A-12                                              |

| Shift Arithmetic Instructions                     | 3A-13                                              |

| Multiply and Multiply-Halfword Instructions       | 3A-15                                              |

| Principles of Multiply Operation                  | 3A-15                                              |

| Instruction Objectives Multiply Instruction       | 3A-17                                              |

| Execution Sequence Multiply Instruction           | 3A-17                                              |

| Operand Fetch and Initialize Cycles               | 3A-17                                              |

| Multiply Cycles Shift Counter 31 to 1 Inclusive . | 3A-18                                              |

| Multiply Cycle, Shift Counter = 0                 | 3A-20                                              |

| Product Store Cycles                              | 3A-20                                              |

| Instruction Objectives, Multiply Halfword         | 3A-20                                              |

| Execution Sequence, Multiply Halfword             | 3A-21                                              |

| · Operand Fetch and Initialize Cycles             | 3A-21                                              |

| Product Store Cycle                               |                                                    |

| Divide Instruction                                | 3A-22                                              |

| Principles of Division                            |                                                    |

| Instruction Execution                             |                                                    |

|                                                   |                                                    |

| Division Set-Up Cycles                            | 3A-24<br>3A-25                                     |

| Division Compute Cycles                           |                                                    |

| Remainder Correction Cycle                        | 3A-26                                              |

| Quotient Correction Cycle                         |                                                    |

| Quotient and Remainder Store Cycles               | 3A-27                                              |

|                                                   |                                                    |

| LOGICAL INSTRUCTIONS                              | 3A-31                                              |

| OR, Exclusive OR and AND Instructions             | 3A-31                                              |

| OR Instructions                                   | 3A-31                                              |

| RR and RX Format                                  | 3A-31                                              |

|                                                   | 0.1 01                                             |

| SI Format                                         | 3A-31                                              |

| SI Format                                         |                                                    |

|                                                   | 3A-31                                              |

| Exclusive OR Instruction                          | 3A-31<br>3A-32                                     |

| Exclusive OR Instruction                          | 3A-31<br>3A-32<br>3A-32                            |

| Exclusive OR Instruction                          | 3A-31<br>3A-32<br>3A-32<br>3A-32                   |

| Exclusive OR Instruction                          | 3A-31<br>3A-32<br>3A-32<br>3A-32<br>3A-33<br>3A-33 |

| Add Logical, Subtract Logical a | ınc        | I C | <b>.</b> m | חפרו | - T | ogi | c a l |   |   |   |                |

|---------------------------------|------------|-----|------------|------|-----|-----|-------|---|---|---|----------------|

| Instructions                    |            |     |            |      |     | -   |       | • |   |   | 3A-34          |

|                                 |            |     |            | •••  |     |     |       | • | • | • | 3A-34          |

| Subtract Logical Instructions   |            |     | •          | •••  |     |     | •     | : | : | • | 3A-34          |

| Compare Logical Instructions    |            |     |            |      |     |     |       |   |   | · | 3A-34          |

| RR and RX Formats               |            |     |            |      |     |     | •     | • | · | • | 3A-35          |

|                                 |            |     |            | •    |     |     | •     | • |   | • | 3A-35          |

|                                 |            |     |            |      |     |     | •     | • | · | • | 3A-35          |

| Character Handling Instructions |            |     | •          |      |     |     | •     | • | · | • | 3A-35          |

| Insert Character Instruction    |            |     | •          |      |     |     | •     | · | • | • | 3A-35          |

| Store Character Instruction     |            |     |            |      |     |     | •     | • | • | • | 3A-30          |

| Test Under Mask                 |            |     |            |      |     |     | •     | • | • | · | 3A-30<br>3A-37 |

| Test and Set                    |            |     |            |      |     |     | •     | · | • | • | 3A-37          |

| Miscellaneous Logical Operatio  |            |     |            |      |     |     | • .   | · | • | • | 3A-38          |

| Shift Logical Instructions .    |            |     | •          |      |     |     | •     | • | • | • |                |

| Load Address                    |            |     |            | •    |     |     | •     | • | • | • |                |

| Move Instruction                |            | •   | •          | •    | •   | •   | •     | • | • | • | 3A-40          |

| DRANCHING INCODICTIONS          |            |     |            |      |     |     |       |   |   |   | 3A-41          |

| BRANCHING INSTRUCTIONS          |            |     | •          | •    |     |     | •     | • | • | • | 3A-41          |

| Instruction Formats             |            |     | •          |      |     |     | •     |   | • | • | 3A-41          |

| Branch On Condition             |            | •   | •          |      | •   |     | •     | • |   | • |                |

|                                 |            |     | •          |      | •   |     | •     | • | • | • |                |

| Brnach On Count                 |            | •   | •          | •    | •   | •   | •     | • | · | • | 3A-42          |

| CTATUS SMITCHING INSTRU         | <b>~</b> T |     | 15         |      |     |     |       |   |   |   | 3A-43          |

| STATUS SWITCHING INSTRUC        |            |     |            |      |     | •   | •     | • |   | • | 3A-43          |

| Set System Mask                 |            |     |            | •    |     | •   | •     |   | · | • | 3A-43          |

| Set Program Mask                |            | •   |            |      |     | •   | •     | • |   | · | 3A-43          |

| <b>_</b>                        |            |     | •          |      | •   | •   | •     | • | • | · | 3A-43<br>3A-43 |

|                                 |            |     | •          | •    |     | •   | •     | · |   | • |                |

| Diagnose Instruction            |            |     | •          |      | •   | •   | •     | • |   | · | 3A-44          |

| Instruction Format              |            |     |            |      | •   | •   | •     | · |   | • | 3A-44          |

| Instruction Applications        |            |     |            |      | •   | •   | •     | · |   | ٠ | 3A-45          |

| Operation of Test Parity Lat    |            |     |            |      | •   | •   | •     |   |   |   |                |

| Instruction Execution .         |            | •   | •          | •    | •   | ·   | •     | · | · | · | 3A-45          |

| UPDATE INTERVAL TIMER .         |            |     |            |      |     |     |       |   |   |   | 3A-46          |

|                                 |            |     |            |      |     |     |       |   |   |   |                |

| INTERRUPTS                      |            |     | •          |      | •   | •   |       |   |   |   | 3A-48          |

| Accepting the Interrupt         |            | •   | •          |      | •   | •   | •     |   |   | • | 3A-50          |

| Machine-Check Interrupt .       |            |     |            | •    |     |     |       |   |   |   | 3A-50          |

| Program Interrupt               |            |     |            |      |     |     |       |   |   |   | 3A-50          |

| Program Interrupt Backup        |            |     |            | •    |     |     |       |   |   |   | 3A-51          |

| Supervisor-Call Interrupt .     |            |     |            |      |     |     |       |   |   |   | 3A-51          |

| External Interrupt              |            |     |            | •    |     |     |       |   | • |   | 3A-51          |

| External Machine Check          |            |     |            | •    |     |     |       |   |   |   | 3A-51          |

| I/O Interrupts                  |            | •   |            |      |     |     |       |   |   |   | 3A-52          |

| Interrupt Cycles                |            |     |            | •    |     |     |       |   |   |   | 3A-52          |

| Cycle 1, New PSW 1 Period       |            |     |            |      |     |     |       |   |   |   | 3A-53          |

| Cycle 2, Old PSW 1 Period       |            |     |            |      |     |     |       |   |   |   | 3A-53          |

| Cycle 3, New PSW 2 Period       |            |     |            | •    |     |     |       |   |   |   | 3A-53          |

| Cycle 4, Old PSW 2 Period       |            |     |            |      |     |     |       |   |   |   | 3A-53          |

| Summary of Interrupt Cycle      |            |     |            |      |     |     |       |   |   |   | 3A-53          |

| I/O Interrupts                  |            |     | •          |      |     |     |       |   |   |   | 3A-53          |

| Storing the CSW                 |            | •   | •          | •    |     |     |       |   |   |   | 3A-54          |

| Developing the Interrupt Co     |            |     |            |      |     |     |       |   |   |   | 3A-54          |

| Machine-Check Interrupt         |            |     | •          |      |     |     | -     |   |   |   | 3A-54          |

| Program Interrupt               |            | •   | •          | :    |     | :   |       | ÷ |   |   | 3A-54          |

| Supervisor-Call Interrupt       |            |     |            |      |     |     |       |   |   |   | 3A-54          |

| External Interrupt              |            | :   | :          | •    |     |     | •     | • | • |   | 3A-54          |

| Input/Output Interrupt          |            |     | :          | :    |     |     | •     | • | • | : | 3A-54          |

| Terminating the Interrupt Cycl  |            |     |            |      |     |     | •     |   | • |   | 3A-54          |

| Cancellation of an I/O Inter    |            |     |            |      |     |     | :     | • | • |   | 3A-55          |

| Cancentation of an 1/0 miles    |            | r   | •          | -    | •   | •   | •     | • | • | • |                |

# **ILLUSTRATIONS**

| Figure | Title                                          | Page  |

|--------|------------------------------------------------|-------|

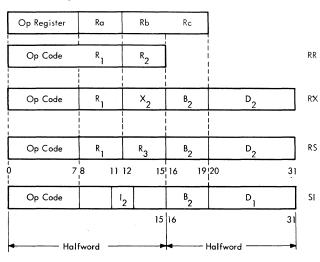

| 3A-1   | Formats and Operation Registers                | 3A-2  |

| 3A-2   | I-Fetch Timings, Double Index (Basic           |       |

|        | Machine Only)                                  | 3A-5  |

| 3A-3   | Halfword Expansion                             | 3A-7  |

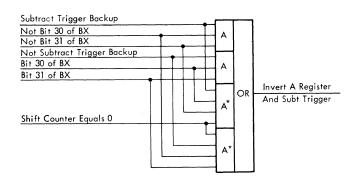

| 3A-4   | Shift Operations Arithmetic                    | 3A-14 |

| 3A-5   | Sign Correction                                | 3A-15 |

| 3A-6   | Invert A Register and Subtract Trigger Logic . | 3A-18 |

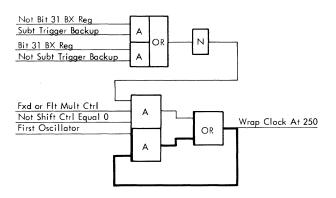

| 3A-7   | Compute Clock Control for Multiply             |       |

|        | Operation                                      | 3A-19 |

| 3A-8   | Multiply Conditions                            | 3A-19 |

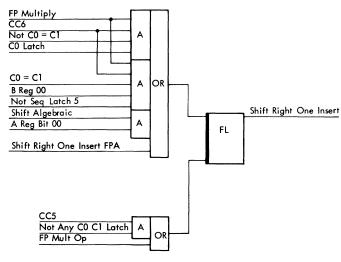

| 3A-9   | Shift Right One Insert for Multiply            |       |

|        | Operations                                     | 3A-19 |

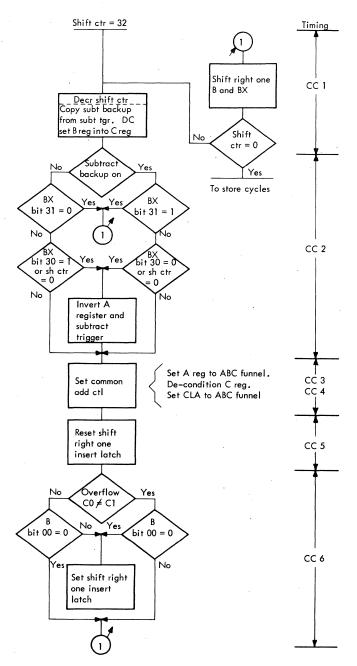

| 3A-10  | Instructional Multiply Flow Chart              | 3A-20 |

| 3A-11  | Multiply Examples with Eight-Bit Multiplier .  | 3A-21 |

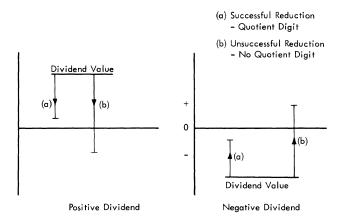

| 3A-12  | Illustration of Normal Reduction Cycle         | 3A-23 |

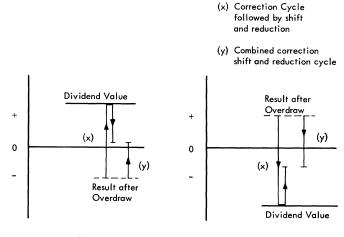

| 3A-13  | Illustration of Combined Correction and        |       |

|        | Reduction Cycles                               | 3A-23 |

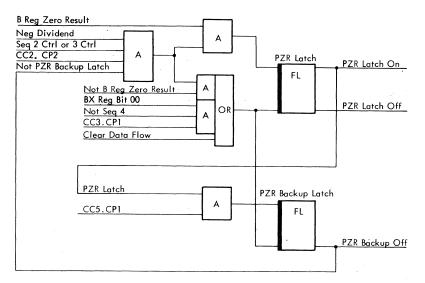

| 3A-14  | Possible Zero Remainder Latch                  | 3A-24 |

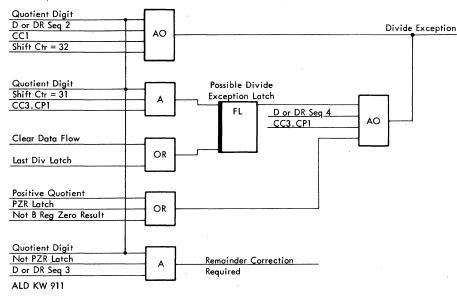

| 3A-15  | Divide Exception and Remainder Connection .    | 3A-25 |

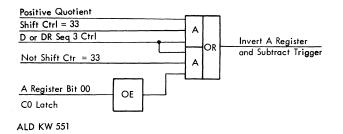

| 3A-16  | Invert A Register and Subtract Trigger for     |       |

|        | Divide Instruction                             | 3A-26 |

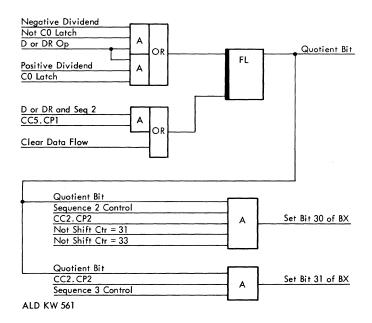

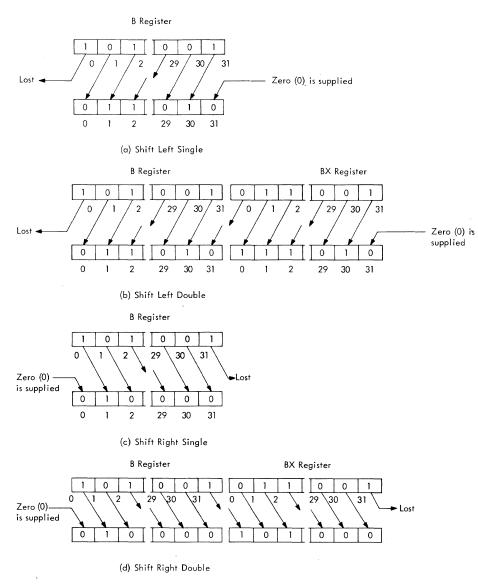

| 3A-17  | Quotient Bit Logic                             | 3A-26 |

| 3A-18  | Example of Divide with Two Negative            |       |

|        | Operands                                       | 3A-28 |

| 3A-19  | Example of Divide with Remainder Correction    |       |

|        | Required                                       | 3A-29 |

| 3A-20  | Example of Divide with Remainder Correction    |       |

|        | and PZR on                                     | 3A-30 |

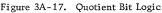

| 3A-21  | Shift Operations Logical                       | 3A-39 |

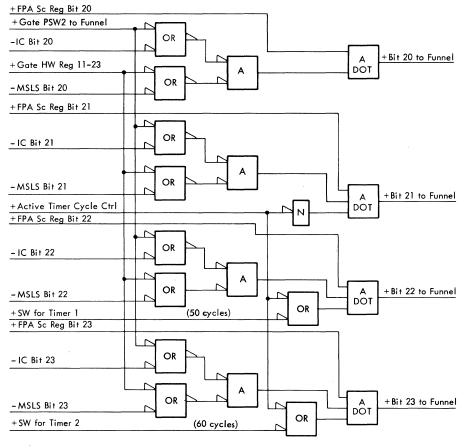

| 3A-22  | PSW 2 and HW Register to Funnel Logic          | 3A-46 |

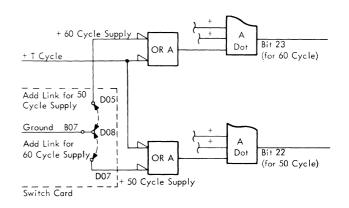

| 3A-23  | Mains Frequency Determination                  | 3A-47 |

| 3A-24  | Table of Interrupts                            | 3A-48 |

| 3A-25  | Summary of Interrupt Control Latches           | 3A-49 |

| 3A-26  | PSW and CSW Storage Locations                  | 3A-52 |

|        |                                                |       |

## ABBREVIATIONS

v

The following abbreviations are used in this manual:

| ac             | alternating current       |

|----------------|---------------------------|

| CLA            | Carry Look-ahead          |

| CLI            | Compare Logical Immediate |

| dc             | direct current            |

| E-phase        | Execute-phase             |

| EXOR           | Exclusive OR              |

| GPR            | General Purpose Register  |

| HW funnel      | Hardware funnel           |

| IC             | Instruction Counter       |

| I-cycle        | Instruction-cycle         |

| I-fetch        | Instruction-fetch         |

| ILC            | Instruction Length Code   |

| I/O            | Input/Output              |

| IPL            | Initial Program Loading   |

| Ор             | Operation                 |

| PSW            | Program Status Word       |

| $\mathbf{PZR}$ | Possible Zero Remainder   |

| SAR            | Storage Address Register  |

| SDR            | Storage Data Register     |

|                |                           |

•

## INTRODUCTION TO INSTRUCTION FETCHING

- Instructions are either one or two halfwords in length.

- Instructions must be located on integral halfword boundaries.

- Instruction-fetch reads out the instruction to instruction registers and develops the effective address for all but RR type instructions.

- SS format instructions are not used in the IBM System/360 Model 44 instruction set.

The length of a machine instruction can be one or two halfwords. The length is determined by the number of storage addresses required to perform the operation. An instruction of one halfword cannot cause any reference to main storage because it is the second halfword of an instruction, where present, that contains the storage address in the form of a base address followed by a displacement. Therefore, an instruction two halfwords long is required to provide one storage address. All instructions must be located in storage on integral halfword, that is, any 24-bit address whose low-order bit is zero.

The instruction field is read out from storage by Instruction-fetch (I-fetch). The information brought out is processed in preparation for the execution of the instruction. This execution is carried out in the Execute-phase (E-phase).

The System/360 Model 44 instruction set does not contain any SS format instructions. Therefore, no Model 44 instruction exceeds two halfwords in length.

For RR format (one halfword long), the I-fetch reads out the instruction from storage and sets it into the instruction registers (Op, Ra, Rb and Rc). For RX, RS and SI formats, the I-fetch reads out the full-word instruction, sets the Op, Ra, Rb and Rc registers with bits 00 to 19 of the instruction, sets the 12-bit displacement to the B register and develops the effective address in the B register.

For all instruction formats the Op register content is decoded to set the controls for the E-phase of the instruction.

For two instructions the E-phase is overlapped

with the I-fetch. These are the supervisor-call instruction and the branch-on-condition instruction where the branch is not taken. These instructions are described in the "Status Switching Instructions" and "Branching Instructions" sections respectively.

For all other instructions and for branch-oncondition where the branch is to be taken, the Ephase always follows I-fetch.

I-fetch cannot begin if, at the end of E-phase, an interrupt is pending or the interval timer requires updating. If both these conditions are present, the interrupt is taken and then the interval timer is updated prior to the next I-fetch. (Refer to the "Interrupts" section.)

Under normal operating conditions of running a program, the machine stops processing at the end of the E-phase (end-execute time) and after all pending interrupts and interval-timer updates are handled if any of the following conditions are present:

1. The wait bit, PSW 1 bit 14 is a one.

2. The console rate switch is in the INSN STEP position.

3. The stop button has been pressed.

Condition 1 causes the machine to enter the wait state and the interval timer is updated when required. The machine can proceed only if an I/O or external interrupt is requested.

Condition 2 is an operator intervention. The machine enters the manual-stop state and the I-fetch proceeds only when the start button is pressed. Any interrupt or timer update requested while the machine is in the manual-stop state remains pending until the next end-execute time.

Condition 3 causes the machine to enter the manual-stop state after all pending interrupts are taken. Any I/O activity proceeds to termination with the associated interrupt held pending.

A flow chart analyzing end-execute time is shown in FEMD, Figure 6077/78 (Basic) and 6291/92 (Accelerator).

#### INSTRUCTION FORMAT AND DECODING

- Four instruction registers are used: Op, Ra, Rb and Rc.

- Instruction format is defined by the op register bits 0, 1.

There are four instruction registers used in the IBM 2044 Processing Unit. These are:

| Register | Bits  | Format | Contents                      |

|----------|-------|--------|-------------------------------|

| Op       | 00-07 | RR     | Instruction op code           |

|          |       | RX     | Instruction op code           |

|          |       | RS     | Instruction op code           |

|          |       | SI     | Instruction op code           |

| Ra       | 08-11 | RR     | First operand GPR address     |

|          |       | RX     | First operand GPR address     |

|          |       | RS     | First operand GPR address     |

|          |       | SI     | Bits 0 to 3 of immediate data |

| Rb       | 12-15 | RR     | Second operand GPR address    |

|          |       | RX     | Index register GPR address    |

|          |       | RS     | Index register GPR address    |

|          |       | SI     | Bits 4 to 7 of immediate data |

| Rc       | 16-19 | RX     | Base GPR address              |

|          |       | RS     | Base GPR address              |

|          |       | SI     | Base GPR address              |

The alignment of the instruction with the instruction registers is shown in Figure 3A-1.

The first byte of an instruction is the operation (op) code. For convenience this is often expressed in hexadecimal form, and given a mnemonic for programming purposes, for example:

| Mnemonic | Hexadecimal | Binary   | Instruction        |

|----------|-------------|----------|--------------------|

| NR       | 14          | 00010100 | RR binary AND      |

| Ν        | 54          | 01010100 | RX binary AND      |

| CLI      | 95          | 10010101 | SI compare logical |

The second byte, bits 8 to 15 of the instruction halfword, is used as two four-bit registers in the RR, RS and RX formats, and is used as an immediate eight-bit operand in the SI format. These eight bits

Registers used during I-Fetch

Figure 3A-1. Formats and Operation Registers

of immediate data in SI format are held in the Ra (4 bits) and Rb (4 bits) registers. When these registers are read out, there is a special data path to convey the byte to the ABC funnel.

During I-fetch the eight bits of the op code are decoded to enable decisions to be made as to the format and the operation required.

The op decode is performed using the output from four decode groupings of three bits of the op register bits 0 to 7. The four combinations used are:

| Op | register | bits | 2, | 4, | 5 |  |

|----|----------|------|----|----|---|--|

| Op | register | bits | 1, | 3, | 5 |  |

| Op | register | bits | 0, | 6, | 7 |  |

| Op | register | bits | 3, | 6, | 7 |  |

These lines are used to derive the controls necessary to define fully the instruction and its type.

The op decode logic is contained in ALD Pages DN 001 to 191. An example of op decoding for the RX format compare instruction follows:

Bit positions

0

1

2

3

4

5

6

7

Op code of RX compare

0

1

0

1

1

0

0

1

In this example, bits 2, 4 and 5 are 0, 1 and 0. The following shows the output of op register encoder positions for the four combinations used.

|     | Bits 2, 4, 5 | Bits 1, 3, 5 | Bits 0, 6, 7 | Bits 3,6,7 |

|-----|--------------|--------------|--------------|------------|

| 000 |              |              |              |            |

| 001 |              |              | х            |            |

| 010 | х            |              |              |            |

| 011 |              |              |              |            |

| 100 |              |              |              |            |

| 101 |              |              |              | х          |

| 110 |              | х            |              |            |

| 111 |              |              |              |            |

Reference to ALD Pages DN 001 to 191 shows that the following control lines are generated from these encoded lines:

| ALD    | Op Decode Line Name                                                                                     |

|--------|---------------------------------------------------------------------------------------------------------|

| DN 021 | Compare Algebraic Op<br>Subt + Comp + Load C-N-P<br>Subt + Comp + Store + Test Set<br>Add + Subt + Comp |

| DN 031 | Load C-N-P + Arith + Log Ops<br>Add Alg + Subt Alg + Comp Alg                                           |

DN 101 Arith + Log + Load Ops These lines and the 'not' condition of other lines from these ALD pages provide the control for the instruction execution.

The op decode for all instructions is handled in a similar manner.

If the op code is not part of the Model 44 instruction set or is for a feature that is not installed, an 'operation exception' is signalled, causing a program interrupt (invalid operation).

If the op code represents a privileged instruction and the machine is in the problem state (PSW 1 bit 15 equals 1), a privileged-operation exception is signalled, again causing a program interrupt.

The Model 44 privileged instructions are:

| Instruction     | Op Code | Mnemonic |

|-----------------|---------|----------|

| Halt I/O        | 9E      | HIO      |

| Load PSW        | 82      | LPSW     |

| Diagnose        | 83      | DIAG     |

| Set System Mask | 80      | SSM      |

| Start I/O       | 9C      | SIO      |

| Test Channel    | 9F      | TCH      |

| Test I/O        | 9D      | TIO      |

#### I-FETCH

- The instruction is read out of the locations defined by the Instruction Counter (IC).

- The instruction is aligned in the data flow.

- The Op, Ra, Rb and Rc registers are set from bits 0 to 19 of the data flow.

- The op decode is performed.

- Indexing, when required, is performed.

- Controls for E-phase are set up.

- In accelerator, I-fetch cycles are overlapped.

#### Instruction Read-Out

The conditions under which I-fetch can proceed have been described previously (see "Introduction to Instruction Fetching").

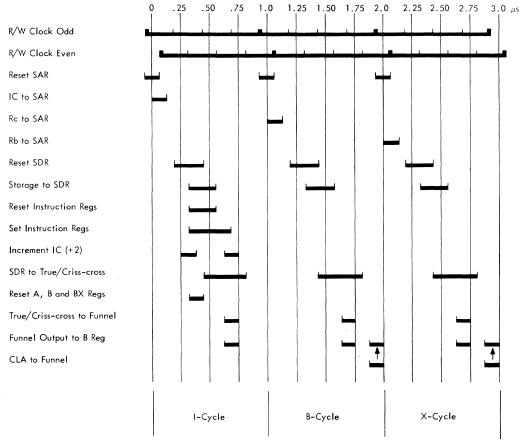

To start all I-fetch operations, an Instruction cycle (I-cycle) is taken. During this I-cycle the IC (PSW 2 bits 8 to 31) is used to address main storage, and the instruction field is read out to the Storage Data Register (SDR) as explained under "Main Storage Addressing" in <u>Introduction and Functional</u> <u>Units</u>, Form Y33-0001. The instruction is correctly aligned in the SDR if the instruction address specifies an address in the half of main storage addressed by Storage Address Register (SAR) 1. However, if the instruction address specifies an address in the half of main storage addressed by SAR 2, a criss-cross operation is performed to align the instruction correctly in the data flow.

The correctly aligned instruction is then available at the true/criss-cross output.

At the start of the I-cycle, a 'clear data flow' line is conditioned to reset all the internal registers and controls in the arithmetic and logic section of the machine. The Op, Ra, Rb and Rc registers are also reset at this time.

When the aligned instruction is available at the true/criss-cross output, bits 00 to 19 are used to set the Op, Ra, Rb and Rc registers.

Up to this stage, all instructions are treated alike and it is only after the Op, Ra, Rb and Rc registers have been set that instruction and op decoding can proceed.

The Op register is immediately decoded to determine the instruction format and type.

If the op is invalid, the operation-exception latch is turned on. If the op is a privileged operation and the machine is in the problem state (PSW 1 bit 15 equals 1), the privileged-operation-exception latch is turned on.

For both these exceptions an end-execute signal is generated at the end of the I-cycle, and the I-fetch is terminated. The machine then enters the end execute time analysis, shown in FEMD, Figures 6077/78 (Basic) and 6291/92 (Accelerator). A program interrupt would normally be taken under these exception conditions.

If the op code is valid, the instruction format together with the contents of the Rb and Rc registers are used to determine if indexing cycles are required.

The instruction format decode output is also used to determine if the displacement field should be gated to the B and C registers.

If the instruction format is not RR, the true/crisscross output, bits 20 to 31, is gated through the ABC funnel and is set into the B and C registers. Bits 20 to 31 represent the displacement, and they are set into the B and C registers in readiness for the addition of the base address or the index field if indexing is required.

The conditions which cause either no index cycles, one index cycle or two index cycles are: No Index

| no maca   |               |                            |

|-----------|---------------|----------------------------|

|           | RR format     | All instructions           |

|           | RX format     | Rc = 0, $Rb = 0$           |

|           | RS, SI format | $\mathbf{R}\mathbf{c} = 0$ |

| One Index |               |                            |

|           | RX format     | $Rb = 0, Rc \neq 0$        |

|           | RX format     | $Rb \neq 0$ , $Rc = 0$     |

|           | RS, SI format | $\mathbf{Rc} \neq 0$       |

| Two Index |               |                            |

|           | RX format     | $Rb \neq 0$ , $Rc \neq 0$  |

#### No Index Cycles

BASIC only: For the three conditions causing no-index cycles, I-fetch can end at the completion of the I-cycle.

For the RR format, the information required for the E-phase is located in the Op, Ra and Rb registers. For the RX format, the information required for the E-phase is located in the Op, Ra, Rb, Rc and B registers. The B register contains the displacement, which, as no indexing cycles were required, is also the effective address.

For the RS and SI formats, the information required for the E-phase is located in the Op, Ra, Rb and B registers. The B register contents again represent the effective address.

For these no-index conditions the lastinstruction-cycle signal is generated during the I-cycle and the op decode is used to set the appropriate controls for the E-phase of the instruction. (See "Last Instruction Cycle Conditions" section.)

ACCELERATOR only: For the RR format, indexing is never required. The op decode output signals that the instruction is in RR format, identifies the op code, and the instruction execution is allowed to proceed.

As all operands in RR format are in GPR's, no storage cycles are required and the instruction execution can be performed in parallel with the remainder of the I-cycle on which the instruction information in SDR is regenerated in storage.

For RR instructions, the common signals for I-fetch occur in the first part of the I-cycle only. In FEMD, Figure 6201/2, the timing charts for the RR I-fetch show these common signals. The timing charts for all RR-type instructions start at the beginning of I-fetch to illustrate the overlap of I-fetch and E-phase relevant to the instruction.

The common I-fetch signals for each instruction are not shown on the timing chart, but a cross reference is made to the RR I-fetch chart.

On the I-cycle, regardless of format, the compute clock is started at RC4 time. This first run of the compute clock uses the 'I-time' latch as a control, and a sequence latch is not activated unless a second run of the compute clock is required.

For the RX, SI or RS formats and the noindex conditions previously listed, I-fetch can be concluded, as the displacement in the B register represents the effective address. As the E-phase of instructions in these three formats can start after the I-cycle or after one or two index cycles, the E-phase is not normally overlapped with I-fetch.

For the no-index conditions, the E-phase starts, using the controls set during the I-cycle by the op decode networks.

A functional op decode flowchart is provided in FEMD, Figure 6201/2 to enable controls set at the end of I-fetch to be established.

## One Index Cycle

BASIC only: For the one-index condition, a B-cycle or an X-cycle is taken to read out the appropriate General-Purpose Register (GPR) contents to be added to the displacement. It is only after this cycle is complete that I-fetch can be ended.

The cycle taken for each of the one-index conditions is as follows:

| Format   | Conditions                                           | Cycle   |

|----------|------------------------------------------------------|---------|

| RX<br>RX | $Rb = 0, Rc \neq 0$<br>$Rb \neq 0, Rc = 0$           |         |

| RS, SI   | $\operatorname{Re} \neq 0$ , $\operatorname{Re} = 0$ | B-cvcle |

The contents of the GPR defined by the address in Rb for the X-cycle and Rc for the B-cycle are read out to the SDR on this indexing cycle.

The SDR is then gated to the A, B and C registers via the true/criss-cross and the ABC funnel. The Carry Look-Ahead (CLA) output is then gated to the B register, forming the sum of the displacement and base or index register contents in the B register.

Thus, at the end of this cycle, the effective address is contained in the B register and the I-fetch can be ended by signalling 'last instruction cycle'.

The controls set on this cycle in preparation for the E-phase of the instruction are described in the "Last Instruction Cycle Conditions" section.

ACCELERATOR only: The conditions that cause one index cycle have been listed previously.

If these conditions are present, the computeclock cycle started at WC1 of the I-cycle is used to add the index information to the displacement.

For the RX format, if the Rb register is zero, the base address is read from the GPR defined by the Rc register, and if the Rc register is zero, the indexing address is read from the GPR defined by the Rb register.

Figure 3A-2. I-Fetch Timings, Double Index (Basic Machine Only)

For RS or SI format, the base address is read out of the GPR defined by the Rc register.

At the completion of the compute-clock cycle, the first index latch is turned on and the E-phase can start, using the controls set by the op decode networks.

The flowchart and timing chart for these cycles are shown in FEMD Figure 6203/4. A flowchart for the controls set by the op decode is also provided.

#### Two Index Cycles

BASIC only: For the two-index condition, both the base address and the index field must be added to the displacement before the I-fetch can be ended. This requires a B-cycle and an X-cycle, with the two cycles taken in that order.

The operation for the B-cycle is similar to the one-index cycle in that the base register defined by the Rc register is read and its contents added to the displacement in the B register.

The X-cycle uses the Rb register to define the GPR to be read out to the SDR. The arithmetic and logic section of the machine is prepared for the second addition process by resetting the A register and copying the B register contents into the C register.

The indexing register content is then gated from the SDR, via the true/criss-cross and the ABC funnel, to the A, B and C registers. The CLA output is then gated to the B register to form the effective address in the B register. The timing of these controls is shown in Figure 3A-2.

The last instruction cycle can then be generated and the controls generated for the E-phase of the instruction. These controls are described in the following section.

ACCELERATOR only: As listed previously, two-index conditions occur if Rb and Rc are non-zero on an RX-format operation.

For these conditions, the compute-clock cycle started at WC1 of the I-cycle is used to add the base register contents to the displacement, and a second compute-clock cycle is called to add the index register contents to the displacement. To define the cycles, the first index latch is turned on near the completion of the first compute-clock cycle, and the second index latch is turned on near the completion of the second compute-clock cycle.

At the completion of this second cycle, the E-phase proceeds, using the controls set up by the op decode network.

A flowchart and timing chart of the I-fetch two-index conditions and a flowchart of the controls set by the op decode are provided in FEMD, Figures 6205/6 and 6207/8.

The last instruction cycle can then be generated and the controls generated for the E-phase of the instruction. These controls are described in the following section.

## Last Instruction Cycle Conditions

The last instruction cycle signal and the op decode combine to set the controls required for the E-phase of the instruction

The method of op decoding has been described previously and the signals generated from this area set the appropriate cycle and/or sequence controls for the following cycle.

Flow charts and timing charts relating to I-fetch are contained in FEMD, Figures 6001/2, 6003/4, 6005/6 and 6007/8 for basic machines and 6201/2, 6203/4, 6205/6 and 6207/8 for accelerator machines. A functional op decode flowchart shows the controls that are set on this last instruction cycle; it does not show the actual method the machine uses to determine the controls to be set, but enables them to be correctly established. The exact method can then be determined from the ALD's.

3A-6 8/66 Model 44 FETO

#### FIXED-POINT INSTRUCTIONS

## HALFWORD EXPANSION

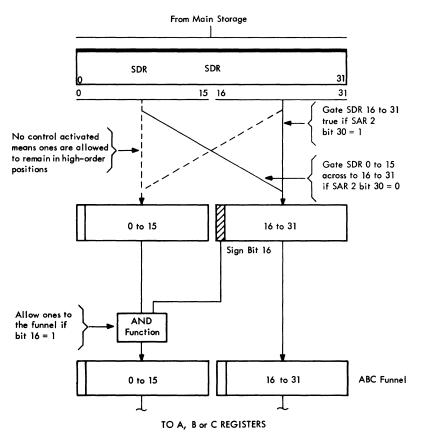

- Halfword is expanded to appear as a full word to enter the ABC funnel.

- Halfword operation allows ones out of bits 0 to 15 of true/criss-cross.

- Admission of forced ones to ABC funnel is dependent on bit 16 (sign bit).

Figure 3A-3 is a schematic representation of the halfword expansion.

When an operand has been read out from main storage to SDR, and analysis of the address and operation code shows it to be a halfword operation, the true/criss-cross is used to align the data in the low-order 16 bits at the ABC funnel entry. The true/criss-cross is constructed in negative logic so that if the high-order 16 bits are not controlled for use, as during halfword operations, ones are propagated from these unused positions. These ones may or may not be admitted to the ABC funnel, depending on the state of bit position 16 (the sign bit) of the halfword operand. If bit 16 is a zero (positive sign), the forced ones are not used. If bit 16 is a one (negative sign), the forced ones are allowed to enter positions 0 to 15 of the funnel with the halfword from main storage occupying the low-order bit positions 16 to 31.

To summarize, a halfword from main storage with a positive sign appears in the funnel in the form:

0000 0000 0000 0000 0101 1011 1101 0111

A halfword with a negative sign appears in the form:

1111 1111 1111 1111  $\underline{1}101$  1011 1101 0111

Figure 3A-3. Halfword Expansion

## LOAD INSTRUCTIONS

#### Load, Load Halfword, Load and Test

- The load instruction is either RR or RX format.

- The respective op codes and mnemonics are 18 (LR) and 58 (L).

- The load-halfword instruction is RX format.

- The op code and mnemonic is 48 (LH).

- The load and test instruction is RR format.

- The op code and mnemonic is 12 (LTR).

- The second operand is placed in the first operand location.

- The second operand remains unchanged.

- On load halfword, the halfword is expanded to a full word by propagating the sign bit in the 16 high-order positions.

- The condition code is set only for 'load and test' instructions as follows:

- 00 : Result is zero

- 01 : Result is less than zero

- 10 : Result is greater than zero

- 11 : Not set

- In accelerator, GPR's go to B register via HW funnel.

BASIC only: The load, load halfword and load and test operations cause the second operand to be read out of storage and set in the SDR. From there it is gated through the true/crisscross to the B and C registers. The true/ criss-cross controls are set to gate SDR true for the load, and load and test instructions. For the load halfword instruction the true/ criss-cross controls are used to align the halfword to the right-hand half of the B and C registers, and to propagate the sign bit to the left-hand half of these registers.

The first operand is then read out of storage but is not gated to the SDR during the read section of the storage cycle. Instead, the second operand is gated from the B register to the SDR, and is stored from there into the first operand location during the write section of the storage cycle.

The load and test instruction causes the B register to be analyzed and the condition code to be set.

The sequence and timing of these instructions are shown in FEMD, Figure 6009/10.

## RX Format

ACCELERATOR only: The instructions of this group in the RX format are load (op code 58) and load halfword (op code 45).

For these instructions an EA-cycle is taken and the second operand is read out to the SDR. It is then gated to the B register (aligning and expanding the operand for the halfword operand condition).

From the B register, the second operand is gated to the GPR defined by the Ra register and 'end execute' is signalled.

#### RR Format

ACCELERATOR only: The instructions of this group in the RR format are load (op code 18) and load and test (op code 12).

For these instructions, the second operand is gated from the GPR defined by Rb and set into the B register using the compute clock started during I-time.

The compute clock is stopped at CC4 and 'end execute' is signalled.

Sequence 2 is then called and the compute clock restarted. The B register is gated to the GPR defined by Ra and the condition code is set for the load and test instruction early in this compute cycle.

Note that 'end execute' is signalled prior to starting the second compute cycle. This gives an overlap of the next I-fetch or interrupt cycle with the E-phase of this instruction

#### Load Complement, Load Positive, Load Negative

- The load complement, load positive, and load negative instructions are in RR format.

- The respective op codes and mnemonics are 13 (LCR), 10 (LPR), 11 (LNR).

- The second operand is loaded into the first operand GPR in the form specified by the instruction.

- The condition code is set from the result stored.

The load complement, load positive, or load negative instructions cause the second operand to be read out of storage and set into the SDR. The B and C registers are set to all ones, and the second operand is gated to the A, B and C registers. Thus, the A register contains the second operand in true form and the B and C registers contain the second operand Exclusive OR'ed with ones (that is, the one's complement of the second operand).

The instruction is then analyzed to determine the operation to be performed.

#### Load Complement

• The two's complement of the second operand is stored.

For this operation the A register is reset and the subtract trigger is set. A subtract operation is then performed by adding the A register contents to the B register contents with the carry-in forced by the subtract trigger. This forms the two's complement of the second operand in the B register.

#### Load Positive

• The absolute value of the second operand is stored.

BASIC only: The SDR sign is tested. If it is negative, the A register is reset and a subtract operation is performed similar to that described for load complement. Thus, if the second operand is negative, it is complemented, the result being formed in the B register.

If the SDR is positive, the B and C registers are reset and the A register is gated via the ABC funnel to the B and C registers.

Thus, the B register contains, in both cases, the absolute value of the second operand.

ACCELERATOR only: The A register is tested. If it is negative, the A register is reset and a subtract operation is performed similar to that described for load complement. Thus, if the second operand is negative, it is complemented, the result being formed in the B register.

If the A-register sign is positive, the B and C registers are reset and the A register is gated via the ABC funnel to the B and C registers.

Thus the B register contains, in both cases, the absolute value of the second operand.

Load Negative

• The two's complement of the absolute value is stored.

BASIC only: The conditions that apply for load positive are reversed for load negative. If the

sign of the second operand in the SDR is negative, the B and C registers are reset and the A register is gated via the ABC funnel to the B and C registers.

If the second operand in the SDR is positive, the A register is reset and a subtract operation is performed, forming the two's complement of the second operand in the B register.

Thus, the B register will in both cases contain the two's complement of the absolute value of the second operand.

ACCELERATOR only: The conditions that apply for load positive are reversed. If the sign of the second operand in the A register is negative, the B and C registers are reset and the A register is gated via the ABC funnel to the B and C registers.

If the second operand in the A register is positive, the A register is reset and a subtract operation is performed, forming the two's complement of the second operand in the B register.

Thus the B register contains, in both cases, the two's complement of the absolute value of the second operand.

#### **Result Storage Cycle**

BASIC only: For all these instructions the first operand is then read out, but not set to the SDR. The content of the B register is set to the SDR. The SDR is then stored in the first operand location during the write section of the storage cycle.

ACCELERATOR only: When 'end execute' is signalled, the B register is gated to the GPR defined by Ra.

The B register is also analyzed to determine the setting of the condition code as follows:

Load Complement

- 00 : Result is zero

- 01 : Result is less than zero

- 10 : Result is greater than zero

- 11 : Fixed-point overflow

Load Positive

- 00 : Result is zero

- 01 : Not set

- 10 : Result is greater than zero

- 11 : Fixed-point overflow ( $C0 \neq C1$ )

Load Negative

- 00 : Result is zero

- 01 : Result is less than zero

- 10 : Not set

- 11 : Not set

For the fixed-point overflow condition, the fixedpoint overflow exception latch is turned on if the mask bit (PSW 2 bit 4) is a one. This latch generates a program interrupt request (refer to "Interrupts" section).

The sequence and timing of these instructions are shown in FEMD, Figures 6011/12 (basic) and 6213/14 (accelerator).

## STORE AND STORE-HALFWORD INSTRUCTIONS

- The store and store-halfword instructions are both in RX format.

- The respective op codes and mnemonics are 50 (ST) and 40 (STH).

- The first operand is stored in the second operand location.

- The store-halfword instruction stores the 16 loworder bits of the first operand GPR (bits 16 to 31).

- The condition code is not altered.

- In accelerator, GPR's enter the B register via HW funnel.

BASIC only: The store and store-halfword instructions are both in RX format. This means that the developed effective address is in the B register at the start of the E-phase of these instructions.

The objective of these instructions is first to read out the first-operand GPR, and then to store the full 32 bits (store) or bits 16 to 31 (store halfword) into the storage location defined by this effective address. This means that the first cycle must be an R1 cycle, and that the effective address must be stored out of the main data flow during this cycle. The second, or store cycle, is an EA cycle and for this cycle the effective address is temporarily returned to the data flow so that this information can be set into the SAR's for addressing purposes.

The sequence and timing of the store and store-halfword instructions are shown in FEMD, Figure 6013/14.

For the store instruction, the machine takes an R1 cycle and reads out the GPR defined by the Ra register from extension storage to the SDR. The B and BX registers are interchanged, placing the effective address in the BX register and zeros in the B register.

The SDR is gated to the B register and the B and BX registers are re-interchanged to

place the effective address back in the B register in preparation for the EA cycle.

The machine takes an EA cycle using the B register to provide the information for the SAR's. The full word defined by the effective address is read out of main storage, and the SDR reset, but the storage to SDR gate is inhibited. The B register is gated to the SDR and stored on the write section of the EA cycle.

For the store halfword instruction, the machine takes an R1 cycle, reads out the GPR defined by the Ra register to the SDR, and interchanges the B and BX registers in the same way as described for the store instruction.

The halfword to be stored is contained in bits 16 to 31 of the SDR. This is aligned to the appropriate half of the B register by gating SDR bits 16 to 31 true if BX bit 30 is a one, and SDR bits 16 to 31 criss-cross if BX bit 31 is a zero. The B and BX registers are interchanged, placing the effective address back into the B register in preparation for the EA cycle.

The machine takes an EA cycle, as with the store instruction, but only 16 bits of the SDR are inhibited and the corresponding 16 bits of the B register are gated to those positions of the SDR.

If the SAR 2 bit 30 is a zero, the 16 bits are bits 00 to 15; if it is a one, the 16 bits are bits 16 to 31.

The SDR is then stored on the write section of the EA cycle.

ACCELERATOR only: The store instructions are started by the machine taking an EA cycle.

The SDR is not set with the effective-address information. That is, for the store instruction it is not set at all, while for the store-halfword instruction, the halfword to be regenerated to storage is set into the SDR.

The second operand information is gated to the B register. For the store-halfword instruction the halfword is aligned to the appropriate half of the B register by entering the Hardware (HW) funnel, bits 00 to 15, into the ABC funnel, bits 00 to 15 or 16 to 31 if the effective address bit 30 is a zero or a one respectively.

At this time the EA cycle is split, the compute clock is started and the required bits are gated from the B register to the SDR.

The write clock is started at CC3 time and the information in the SDR is written into the storage locations defined by the effective address.

As the E-phase is controlled by a storage cycle, 'end execute' is signalled at WC4 time.

The flowchart and timing chart for these instructions are provided in FEMD, Figure 6215/16.

ADD, SUBTRACT AND COMPARE INSTRUCTIONS

The Model 44 follows all the principles of fixed-point binary operations, summarized as follows:

1. Halfword operands are expanded to full word by propagating the sign bit (see also "Halfword Expansion").

2. Positive binary numbers are represented in their true form with a zero in their high-order sign position.

3. Negative binary numbers are represented in their two's complement form with a one in their highorder sign position.

4. On add instructions, no complementing is done because negative operands are already in complement form. The two operands are true added.

5. On subtract instructions the second operand is always complemented (or recomplemented if negative) and the two operands are added.

6. A fixed-point overflow occurs if the carry into the sign position is not equal to the carry out of the sign position.

NOTE: In accelerator machines, GPR's enter the B register via the HW funnel.

Flow charts and timing charts of the add, subtract and compare instructions are shown in FEMD, Figures 6015/16 and 6017/18 (basic) and 6217/18 to 6223/24 inclusive (accelerator).

ACCELERATOR only: For RR-format instructions, the E-phase is started during the I-cycle. The compute clock is started at RC4 of the Icycle and controls the read-out of the second operand from the GPR defined by Rb, to the A, B and C register.

A sequence-2 compute cycle starts and the first operand is gated from the GPR defined by Ra, via the HW and ABC funnels to the A, B and C registers.

When 'end execute' is signalled, the B register content goes to the GPR defined by Ra. For RX-format instructions an EA-cycle is taken to read out the second operand to the SDR.

#### Add, and Add Halfword Instructions

- The add instruction is in either RR or RX format.

- The respective op codes and mnemonics are 1A (AR) and 5A (A).

- The add halfword instruction is in RX format.

- The op code and mnemonic are 4A (AH)

- The second operand is added to the first operand, and the result placed in the first-operand location.

- The result determines the setting of the condition code as follows:

- 00: Result is zero

- 01: Result is less than zero

- 10: Result is greater than zero

- 11: Fixed-point overflow

- A fixed-point overflow occurs if the carry from the high-order position (bit 1) fails to match a carry from the sign position (bit 0).

The add operation is fully described under "Arithmetic and Logic Section, and Registers" in Chapter 2 of <u>Introduction and Functional Units</u>, Form Y33-0001. Briefly, the operation is: clear A, B and C registers, set the second operand in B and C registers and then set the first operand into the A, B and C registers. The A, B and C registers consist of binary input triggers, so that the B and C registers now contain the EXOR sum of the operand without the carries. Carries are derived from the CLA unit by EXOR'ing the A and C registers. The CLA unit output is then EXOR'ed to the partial sum in the B register to produce the final sum in the B register. The state of the registers at the end of the operation is therefore:

- A register, operand 1

- B register, complete total

- C register, addition total less the carries (partial sum).

BASIC only: Note that, as shown in FEMD Figure 6015/16, the R1 cycle is a split cycle to allow for the result to be formed before the write section of this cycle. When a fixed-point overflow occurs, it is tested by AND'ing with PSW 2 bit 4. If PSW 2 bit 4 is a one, the 'fixed-point overflow exception' latch is set to give a 'program interrupt request'.

Subtract, and Subtract Halfword Instructions

- The subtract instruction is in either RR or RX format.

- The respective op codes and mnemonics are 1B (SR) and 3B (S).

- The subtract halfword instruction is in RX format.

- The op code and mnemonic are 4B (SH).

- The two's complement of the second operand is added to the first operand and the result is placed in the first-operand location.

- Halfword operands are expanded to full words.

- The result determines the setting of the condition code as follows:

- 00: Result is zero

- 01: Result is less than zero

- 10: Result is greater than zero

- 11: Fixed-point overflow

- A fixed-point overflow occurs if the carry out from the high-order position (bit 1) fails to match a carry out from the sign position (bit 0).

A full description of the subtract operation is given under "Arithmetic and Logic Section and Registers" in Chapter 2 of Introduction and Functional Units, Form Y33-0001. Subtraction is achieved by adding the two's complement of the second operand to operand 1. The A register is set to zero and the B and C registers are set to all ones. The second operand is EXOR'ed into the B and C registers. The first operand is gated into the A, B and C registers. The state of the registers at the end of the operation is, therefore:

A register, operand 1

B register, sum total

C register, inverse of partial sum.

The output of the B register is gated to the addressed internal unit.

## Compare, and Compare Halfword Instructions

- The compare instruction is in either RR or RX format.

- The respective op codes and mnemonics are 19 (CR) and 59 (C).

- The compare halfword instruction is in RX format.

- The op code and mnemonic is 49 (CH).

- The second operand is compared with the first operand and the result determines the setting of the condition code.

- Operands remain unaltered in storage.

- Halfword operands are expanded to full words.

- The result determines the setting of the condition code as follows:

- 00: Operands are equal

- 01: First operand is low

- 10: First operand is high

- 11: Not set

- The comparison is done by subtracting operand 2 from operand 1 and analyzing the result.

The compare operation starts in the same way as a subtract operation, but differs in that the result is not stored and the condition code has an altered meaning.

> BASIC only: In the compare operation, R1 is not split because the result does not have to be formed (the object of compare operation is satisfied when the condition code is set). Both operands are returned to storage unchanged.

> ACCELERATOR only: The operands are gated back to their original locations unchanged.

#### SHIFT ARITHMETIC INSTRUCTIONS

- Instructions are in RS format.

- The R3 field is not used for these instructions.

- The low-order six bits of the developed effective address define the number of positions to be shifted (bits 26 to 31).

- The operands, which are signed integers, may be either single or double words, and are contained in the GPR or GPR pair defined by the R1 field of the instruction.

- The op codes and their mnemonics for the shift arithmetic instructions are:

```

Shift left single : 8B (SLA)

Shift left double : 8F (SLDA)

Shift right single : 8A (SRA)

Shift right double: 8E (SRDA)

```

- Shift single is a single-word operation and shifting is done in the B register.

- Shift double is a double-word operation and shifting is done in the B and BX registers.

- Multiple shift is a series of single-shift operations.

- The shift counter is reduced by one for each shift and shifting ends when the shift counter equals zero.

- For shift-right operations, the original sign bit is supplied to the high-order bit positions.

- For shift-left operations, zeros are supplied to the low-order bit positions.

- The result is stored in the original operand registers.

- Shift overflow is checked on shift-left operations.

- The condition code is set as follows: 00: Result is zero

- 01: Result is less than zero

- 10: Result is greater than zero

- 11: Shift Left : Overflow Shift Right: Not set

- In accelerator machines GPR's enter B register via HW funnel.

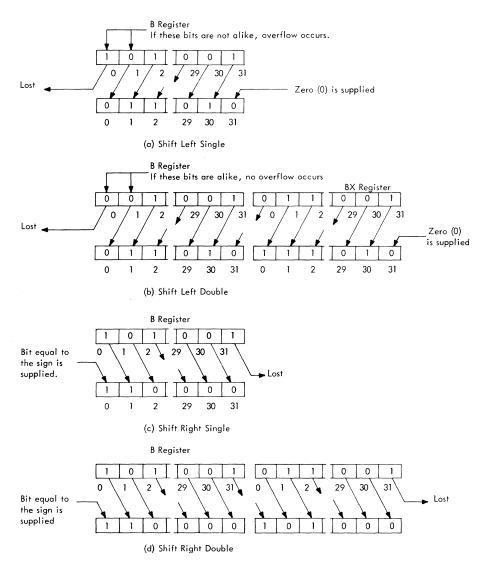

- The four shift operations are shown in Figure 3A-4. Shifting is the operation of moving all the bits in

a word or double word to the right-hand or left-hand adjacent bit position respectively without disturbing their order.

Shift single is a full-word operation, and the operand is fed into the B register. There is no limitation for the addressing of the register.

Shift double is a double-word operation and the operand is the pair of even and odd addressed registers. Addressing of the operand should always be made on the even-numbered register, otherwise the specification exception occurs and causes a program interrupt. The machine automatically addresses the next odd-numbered register. The even register address contains zeros in bit positions 29, 30 and 31. The odd address number is developed by forcing a 1 bit in SAR bit position 29 on the first-operand fetch cycle.

The odd-numbered register content, which is the low-order word, is fed into the BX register via the B register. The even-numbered register content, which is the high-order word, is then fed to the B register.

The low-order six bits (bits 26 to 31) of the instruction format indicate the number of shift places, and are fed into the shift counter before the operand is fetched.

Multiple shift is a series of single-shift operations in which the shift counter value is reduced by one at each shift. Shifting ends when the shift counter is zero.

On shift double, when the B register is shifted right, bit 31 of the B register is shifted into the bit 00 position of the BX register. Bit 31 of the BX register is defined as the low-order bit.

In shift-right operations the low-order bit is shifted out without inspection and is lost. Bit 00 of the B register (sign bit) goes to bit position 01 of the B register in the same way as any other bit. A bit equal to the original sign bit is supplied to the vacated bit position 00 of the B register as follows. The A register contains the original operand in a shift-single operation or the high-order word in a shift-double operation. Therefore, the original sign bit is stored in bit position 00 of the A register and this bit is fed into bit position 00 of the B register by each shift.

In a shift-left operation, bit 00 of the BX register is shifted into bit position 31 of the B register. Bit 01 of the B register goes to bit position 00 of the B register in the same way as any other bit. Therefor, if these two bit positions have different bit status, the operand is changed from positive to negative or the reverse. Note that the sign bit is corrected in the operand store cycle as explained later.

Bit positions 00 and 01 of the B register are examined for the overflow condition on every shift. If the status of these bits is different on a shift-left, an

Figure 3A-4. Shift Operations -- Arithmetic

overflow occurs and sets the fixed-point overflow exception latch if the corresponding mask bit is a one. When the fixed-point overflow line becomes active it is tested against PSW 2 bit 4. If PSW 2 bit 4 is a one the overflow exception latch is set to allow a program interrupt request. (Refer to the "Checking" section in Chapter 2 of <u>Introduction and Functional Units</u> Form Y33-0001 and the "Interrupts" section in this manual.)

> BASIC only: When the shift counter is greater than two, the compute clock wraps at CC2. In both shift-left and shift-right operations, the B and BX registers are shifted one position. In either case the shift counter is reduced by one for each wrapped cycle.

When the shift counter reaches two, the compute clock runs to CC6 instead of wrapping,

but still performs the shift twice, once at CC3, CP1 time and once at CC5, CP1 time.

If the shift counter is set to two at the beginning of this operation, the compute clock runs to CC6, performing the shift operation twice, once at CC1, CP1 time and once at CC3, CP1 time. If the shift counter is set to one at the beginning of the operation, the compute clock runs to CC6, performing the shift operation once at CC1, CP1 time. If the shift counter is set to zero, the compute clock runs to CC6, but no shift takes place.

Zeros are supplied to the low-order position (bit 31) for the shift-left operation. This is the B register bit 31 for a shift-left-single and the BX register for a shift-left-double operation. The original sign bit is supplied into the bit 00 position of the B register in a shift-right opera-

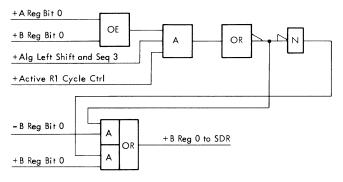

Figure 3A-5. Sign Correction

tion. The simplified diagram is shown in Figure 3A-5.

The result is stored during the write section of a second R1 cycle for single shifts, and during the write section of a second set of double R1 cycles for double shifts. The addressing method is the same as in the operand-fetch cycle previously described.

The condition code is set as follows:

- 00: Result is zero

- 01: Result is less than zero

- 10: Result is greater than zero

During shift-left-double operation the condition code is set at sequence latch 4 time. At this time only the B register has been analyzed. However, the BX register may contain a small positive number so that if the condition code setting is 00 (result is zero), a chance is given to test again during sequence latch 5 time. The result may remain zero or it may be amended to 10 (result is greater than zero).

The flow charts and timing charts for each of the shift operations are contained in FEMD Figures 6019/20, 6021/22, 6023/24 and 6025/26.

ACCELERATOR only: When the shift counter is greater than zero, the compute clock wraps at CC2. In both shift-left and shift-right operations, the B and BX registers are shifted one position. In either case the shift counter is reduced by one for each wrapped cycle. When the shift counter reaches zero, the compute clock runs to CC6.

If the shift counter is set to one at the beginning of this operation, the compute clock runs to CC6, performing the shift operation at CC1, CP1 time. If the shift counter is set to zero, the compute clock runs to CC6, but no shift takes place.

Zeros are supplied to the low-order position (bit 31) for the shift-left operation. This is the B register bit 31 for a shift-left-single and the BX register bit 31 for a shift-left-double operation. The original sign bit is supplied into the 00 position of the B register in a shift-right operation. A simplified diagram of the signcorrection circuit is shown in Figure 3A-5.

The result is stored during the CC3 section of the compute cycle for single shifts, and during the CC3 section of both sequence-3 and sequence-4 cycles for double shifts.

The condition code is set as follows:

- 00: Result is zero

- 01: Result is less than zero

- 10: Result is greater than zero

For fixed-point overflow conditions on the shift-left instructions when the mask bit PSW 2 bit 4 is one, the 'fixed-point overflow exception' latch is set and a program interrupt is requested. (Refer to the "Interrupts" section of this manual.)

The flow charts and timing charts for each of the shift instructions are contained in FEMD, Figures 6225/26 to 6231/32 inclusive.

MULTIPLY AND MULTIPLY-HALFWORD INSTRUC-TIONS

- The multiply instruction is either RR or RX format.

- The respective op codes and mnemonics are 1C (MR) and 5C (M).

- The multiply-halfword instruction is in RX format.

- The op code and mnemonic is 4C (MH).

## Principles of Multiply Operation

The multiply operation is performed by successively shifting the multiplicand relative to the product, and executing an arithmetic operation with the multiplicand on the product field as determined by the multiplier digit. The multiplier is scanned from right to left, or low-order bit to high-order bit.

A simple binary multiply would cause an arithmetic add of the multiplicand to the product field each time the multiplier digit is a one, and, if the multiplier digit is a zero, it would cause a shift to the next position (no arithmetic operation). This is illustrated in the following example:

| 1115 15 1110 | istrated in the tono |

|--------------|----------------------|

| 21 x         | 10101 x              |

| 5            | 101                  |

| 105          | 10101                |

|              | 10101                |

|              | 1101001              |

Note that, for this simple binary multiplication, the number of combined shift and arithmetic cycles equals the number of ones in the multiplier, and the number of shift-only cycles equals the number of zeros in the multiplier.

The number of cycles using this simple type of multiply for some sample multipliers is shown as follows:

| Mu      | ltiplier  | Cycles               |            |

|---------|-----------|----------------------|------------|

| Decimal | Binary    | Shift and Arithmetic | Shift Only |

| 1       | 0000 0001 | 1                    | 7          |

| 4       | 0000 0100 | 1                    | 7          |

| 7       | 0000 0111 | 3                    | 5          |

| 8       | 0000 1000 | 1 .                  | 7          |

| 15      | 0000 1111 | 4                    | 4          |

| 27      | 0001 1011 | 4                    | 4          |

| 32      | 0010 0000 | 1                    | 7          |

In the Model 44 the shift-only cycles can be performed in 250 nanoseconds whereas the combined shift and arithmetic cycle takes 750 nanoseconds. This means that if the number of arithmetic cycles is reduced, a significant saving in time is achieved.

The number of arithmetic cycles is reduced by the use of the carry-look-ahead group-of-ones principle.

Basically this principle means that if there is a multiplier of, for example, +15 (001111), a multiplier of 16 (010000) is used and <u>added</u> to the product field and a multiplier of 1 (000001) is used and <u>subtracted</u> from the product field.

This means that if a group of ones occurs in the multiplier field, an arithmetic subtract operation occurs when the multiplier digit is the first one of the group (the subsequent ones of the group cause shift-only cycles), and an arithmetic add operation is performed for the first zero after the group of ones.

Reviewing this for the preceding example of the multiplier of 001111 (+15), the cycles are:

| Multiplier Digit | Cycle Type         | Effective Multiplier |

|------------------|--------------------|----------------------|

| -1               | Shift and Subtract | - 1                  |

| . 1              | Shift only         | 0                    |

| 1                | Shift only         | 0                    |

| 1                | Shift only         | 0                    |

| 0                | Shift and add      | + 16                 |

| 0                | Shift only         | 0                    |

This gives an effective multiplier of +15. Note that only two arithmetic cycles are used as opposed to the four that are required for the simple binary multiply.

An extension of the above rule occurs when a single zero appears within a group of ones. If an

example of +27 is taken (0011011), then using the principles described above, the cycles are:

| Multiplier Digit | Cycle Type         | Effective Multiplier |

|------------------|--------------------|----------------------|

| 1                | Subtract           | - 1                  |

| 1                | Shift only         | 0                    |

| 0                | Shift and add      | + 4                  |

| 1                | Shift and subtract | - 8                  |