# VAX 8600 CONSOLE SPECIFICATIONS

Prepared by Educational Services of Digital Equipment Corporation

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

Digital Equipment Corporation assumes no responsibility for the use or reliability of its software on equipment that is not supplied by DIGITAL.

The manuscript for this book was produced on a DIGITAL Word Processing System. Book production was done by Educational Services Development and Publishing in Bedford, MA.

Copyright 0 1986 Digital Equipment Corporation. All rights reserved.

The following are trademarks of Digital Equipment Corporation:

**EDGRIN**

ALL-IN-1 BAL-8 CDP COMPUTER LAB COMSYST COMTEX CTBUS DATATRIEVE DDT DEC DECCOM DECmail **DECmate** DECnet DECsystem-10 DECSYSTEM-20 DECtape **DECUS** DECWORD DECwriter DIBOL DIGITAL

DNC

EduSystem FLIP CHIP FOCAL GLC-8 IAS IDAC IDACS INDAC KA10 KI10 LAB-K MASSBUS OMNIBUS os 8 PDP PDT PHA PS 8 P/OS Professional PRO/BASIC

PRO/FMS

PRO/RMS PROSE OUICKPOINT RAD-8 Rainbow RSTS RSX RT-11 RTM SABR Tool Kit TYPESET-8 TYPESET-10 TYPESET-11 UNIBUS VAX **VMS** Work Processor 1 . 10 . 1 . . . .

# CONTENTS

| CHAPTER | 1                                                                | INTRODUCTION AND OVERVIEW.          |

|---------|------------------------------------------------------------------|-------------------------------------|

|         | 1.2<br>1.2.1<br>1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.3.5 | Console PROM                        |

| CHAPTER | 2                                                                | STANDARDS                           |

|         | 2.1<br>2.1.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                  | Noncompliance                       |

| CHAPTER | 3                                                                | CONSOLE PROM OPERATION              |

|         | 3.2<br>3.3<br>3.4<br>3.4.1                                       | POWER-UP OPERATION                  |

| CHAPTER | 4                                                                | CONSOLE DIAGNOSTIC OPERATION        |

|         | 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3                            |                                     |

| CHAPTER | 5                                                                | CONSOLE SOFTWARE EXTERNAL OPERATION |

|         | 5.1<br>5.1.1                                                     | FRONT PANEL SWITCHES                |

| VAX 8600/8650 | CONSOLE | SOFTWARE SPECIFICATION        | Page iv        |

|---------------|---------|-------------------------------|----------------|

| COPYRIGHT (c) | 1985 by | DIGITAL EQUIPMENT CORPORATION | 6 January 1986 |

|           | 5.1.1.1 | OFF Position 5-                              | 3      |

|-----------|---------|----------------------------------------------|--------|

|           | 5.1.1.2 | OFF Position                                 | 3      |

|           | 5.1.1.3 | LOCAL Position 5-                            | 3      |

|           | 5.1.1.4 | LOCAL Position                               | 4      |

|           | 5.1.1.5 | REMOTE Position 5-                           | 4      |

|           | 5.1.2   | Restart Control Switch 5-                    | 5      |

|           | 5.1.2.1 | BOOT Position 5-                             | 5      |

|           | 5.1.2.2 |                                              | 5      |

|           | 5.1.2.3 | RESTART HALT                                 | ž      |

|           | 5.1.2.4 | HALT                                         | ٥<br>د |

|           | 5.1.2.5 | SWITCH TABLE                                 |        |

| ,         | 5.1.2.5 | FRONT PANEL LED INDICATORS                   | 7      |

|           | 5.2.1   | ALERT Indicator                              |        |

|           |         | REMOTE ACTIVE Indicator                      |        |

|           | 5.2.2   |                                              |        |

|           | 5.2.3   | REMOTE ENABLE Indicator                      |        |

|           | 5.2.4   | VAX STATE Indicator                          |        |

|           | 5.3     | TERMINAL SUPPORT                             |        |

|           | 5.3.1   | In Program IO Mode 5-9                       |        |

|           | 5.3.2   | In Console IO Mode 5-10                      |        |

|           | 5.4     | SYSTEM (AC) POWER FAILURE HANDLING 5-10      |        |

|           | 5.4.1   | Detection 5-10                               |        |

|           | 5.4.2   | Recovery                                     |        |

|           | 5.5     | POWER REGULATOR FAILURES 5-1                 | 1      |

|           | 5.6     | CPU PARITY ERROR HANDLING 5-1;               | 1      |

|           | 5.7     | CI780 MAINTENANCE RESTART PACKETS (CI REBOOT |        |

|           |         | HANDLING)                                    | 3      |

|           | 5.8     | CPU REBOOT REQUESTS 5-1:                     | 3      |

|           | 5.9     | CPU KEEP ALIVE FAILURE HANDLING 5-14         |        |

|           | 5.9.1   |                                              |        |

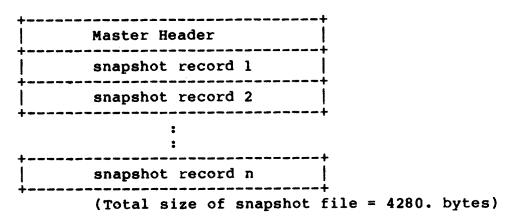

| *         | 5.9.1.1 | Master Header Record Format 5-10             | 6      |

|           | 5.9.1.2 |                                              | Ř      |

|           | 5.9.1.3 |                                              |        |

|           | 5.10    | CONSOLE SUBSYSTEM REBOOT                     |        |

|           | 5.11    | CONSOLE PACK HANDLING CONSIDERATIONS 5-24    |        |

|           | 5.11.1  |                                              |        |

|           | 3.11.1  | Standarone Backup Procedure                  | 3      |

|           |         |                                              |        |

| CHADTED   | 6       | CONSOLE SOFTWARE (MACHINE) INITIALIZATION    |        |

| CHAFIER   | U       | CONSOLL BOTTWARD (MACHINE) INTITALIZATION    |        |

|           | 6 1     | PROM CODE INITIALIZATION 6-                  | 1      |

|           |         | CONSOLE PROGRAM INITIALIZATION               |        |

|           | 6.2.1   | Power System (MPS) Initialization 6-2        |        |

|           | 6.2.1   | MACRO CONTEXT INITIALIZATION                 |        |

|           |         |                                              |        |

|           | 6.3.1   | CPU Initialization 6-6                       |        |

|           | 6.3.2   | PIO Mode Initialization 6-7                  |        |

|           |         | DIAGNOSTIC CONTEXT INITIALIZATION 6-1        |        |

|           | 6.5     | MHC CONTEXT INITIALIZATION 6-8               | 3      |

|           |         |                                              |        |

| СНУБДЕР   | 7       | REMOTE TERMINAL (RTY) SUPPORT                |        |

| C.TIL LUI | •       | NEW TENNITHME (NII) COLLON                   |        |

|           | 7.1     | ESTABLISHING AN RTY CONNECTION               | 1      |

|           |         | RTY DISCONNECTION                            |        |

|           | 7.3     | OPERATION                                    | 3      |

|           | . • •   |                                              | _      |

# VAX 8600/8650 CONSOLE SOFTWARE SPECIFICATION Page v COPYRIGHT (c) 1985 by DIGITAL EQUIPMENT CORPORATION 6 January 1986

|         | 7.3.1<br>7.3.2<br>7.3.3<br>7.3.4 | Transparent Mode                 | -5<br>-5 |

|---------|----------------------------------|----------------------------------|----------|

| CHAPTER | 8                                | EMM HANDLING                     |          |

|         | 8.1                              | EMM/CONSOLE COMMUNICATIONS       | -1       |

|         | 8.2                              | POLLING FOR EMM STATUS           | -2       |

|         | 8.3                              | PRIORITY MESSAGE HANDLING        | -2       |

| CHAPTER | 9                                | CONSOLE I/O MODE                 |          |

|         | 9.1                              | CONSOLE COMMAND SYNTAX 9         | -2       |

|         | 9.1.1                            | General Command Set 9            | -4       |

|         | 9.1.2                            | DEBUG                            | -4       |

|         | 9.1.3                            | DIAGNOSE                         | - 4      |

|         | 9.1.4                            | HELP                             | -5       |

|         | 9.1.5                            | IF                               | -5       |

|         | 9.1.6                            | INITIALIZE (CLOCK, POWER, SDB) 9 | -6       |

|         | 9.1.7                            | LOAD (control Store) 9           | -7       |

|         | 9.1.8                            | LUPC                             | -8       |

|         | 9.1.9                            | MACRO                            | -9       |

|         | 9.1.10                           | MHC                              | -9       |

|         | 9.1.11                           | ODT                              | -9       |

|         | 9.1.12                           | PROM                             | -9       |

|         | 9.1.13                           | REBOOT 9-                        |          |

|         | 9.1.14                           | REPEAT 9-                        |          |

|         | 9.1.15                           | RESET                            |          |

|         | 9.1.16                           | RESTART                          |          |

|         | 9.1.17                           | SET BASE                         |          |

|         | 9.1.17                           | SET Flag ON/OFF 9-               | 12       |

|         |                                  | SET CLOCK                        |          |

|         | 9.1.19                           |                                  | 17       |

|         | 9.1.20                           |                                  |          |

|         | 9.1.21                           |                                  |          |

|         | 9.1.22                           |                                  |          |

|         | 9.1.23                           |                                  |          |

|         | 9.1.24                           |                                  |          |

|         | 9.1.25                           | SHOW PANEL 9-                    |          |

|         | 9.1.26                           | SHOW POWER 9-                    |          |

|         | 9.1.27                           | SHOW TERMINAL 9-                 |          |

|         | 9.1.28                           | SHOW UCODE 9-                    |          |

|         | 9.1.29                           | SHOW VERSION 9-                  |          |

|         | 9.1.30                           | START/STOP CPU 9-                |          |

|         | 9.1.31                           | START/STOP SYSTEM 9-             |          |

|         | 9.1.32                           | UNHANG                           |          |

|         | 9.1.33                           | VTERM                            |          |

| •       | 9.1.34                           | WAIT                             |          |

|         | 9.1.35                           | x                                |          |

|         | 9.1.36                           | <b>0</b>                         | 26       |

|         | 9.2                              | MACRO CONTEXT 9-                 | 27       |

| 9.2.1    | Context Initialization                  | 9-27 |

|----------|-----------------------------------------|------|

| 9.2.2    | Console Support Microcode (CSM)         | 9-27 |

| 9.2.3    | MACRO Context Command Set               | 9-27 |

| 9.2.4    | BOOT                                    | 9-27 |

| 9.2.5    | CONTINUE                                | 9-28 |

| 9.2.6    | CLEAR MEMORY                            | 9-29 |

| 9.2.7    | DEPOSIT (CPU Or Tll Address Spaces)     | 9-29 |

| 9.2.8    | EXAMINE (CPU And Tll Address Spaces)    | 9-30 |

| 9.2.8.1  | Supported GPR Names                     | 9-32 |

|          |                                         | 9-33 |

| 9.2.8.2  | Supported IPR Names                     |      |

| 9.2.8.3  | Supported IR Names                      | 9-34 |

| 9.2.8.4  | Supported Miscellaneous Register Names  | 9-35 |

| 9.2.9    | FIND                                    | 9-35 |

| 9.2.10   | HALT                                    | 9-36 |

| 9.2.11   | INITIALIZE (CPU, ESCRATCH, MICRO, PAMM) | 9-36 |

| 9.2.12   | LOAD (main Memory)                      |      |

| 9.2.13   | START                                   |      |

| 9.2.14   | START/STEP                              |      |

| 9.2.15   | NEXT                                    |      |

| 9.2.16   |                                         |      |

|          | UNJAM                                   |      |

| 9.2.17   | VERIFY                                  | 9-39 |

|          |                                         |      |

| 9.3 DI   | AGNOSTIC CONTEXT                        | 9-41 |

| 9.3.1    | Context Initialization                  | 9-41 |

| 9.3.2    | Diagnostic Support Microcode (DSM)      | 9-41 |

| 9.3.3    | Console/DSM Communication               |      |

| 9.3.4    | Microdiagnostic Operation               | 9-43 |

| 9.3.5    | Pausing/Continuing                      | 9-44 |

| 9.3.6    | Control Character Handling              | 9-44 |

| 9.3.7    | Error Report Format                     | 9-45 |

|          | Diagnostic Fault Isolation              | 9-45 |

| 9.3.8    |                                         |      |

| 9.3.8.1  | Solid Faults                            | 9-46 |

| 9.3.8.2  | Non-Solid Faults                        | 9-46 |

| 9.3.9    | DIAGNOSTIC Context Command Set          | 9-46 |

| 9.3.9.1  | CLEAR DATA                              | 9-46 |

| 9.3.9.2  | CONTINUE (a Microdiagnostic)            | 9-47 |

| 9.3.9.3  | DEPOSIT (Cache, Escratch, Wbus)         | 9-47 |

|          | EXAMINE (Cache, Escratch, Wbus)         | 9-47 |

|          | FAULT FREE                              |      |

| 9.3.9.6  | GENERATE                                | 9-48 |

| 9.3.9.7  | RUN                                     | 9-49 |

| 9.3.9.8  |                                         | 9-50 |

| 9.3.9.9  | SET DATA                                | 9-50 |

|          |                                         |      |

|          | SET NAME                                | 9-51 |

|          | SET SWITCH                              | 9-52 |

| 9.3.9.12 | SHOW DATA                               | 9-53 |

|          | SHOW SWITCHES                           | 9-54 |

|          | START                                   | 9-54 |

| 9.3.9.15 | STEP                                    | 9-56 |

|          | •                                       |      |

| 9.4 M    | CROHARDCORE CONTEXT                     | 9-57 |

| 9.4.1    | MICROHARDCORE Context Command Set       |      |

| 9.4.2    | START                                   | 9-57 |

|          | LOOP                                    | 9-59 |

|          |                                         |      |

| VAX 860  | 0/8650 C | CONSOLE SOFTWARE SPECIFICATION Page              |             |

|----------|----------|--------------------------------------------------|-------------|

| COPYRIGI | HT (c) 1 | 985 by DIGITAL EQUIPMENT CORPORATION 6 January 1 | 986         |

|          |          |                                                  |             |

|          | 9.4.4    | CONTINUE                                         | -61         |

|          | 9.4.5    | REPORT                                           | -62         |

|          | 9.5      | THE HEX DEBUGGER                                 | -63         |

|          | 9.5.1    | The HEX Command Set 9                            | -63         |

|          | 9.5.2    | CLEAR BREAK                                      | -63         |

|          | 9.5.3    | CLEAR COUNT                                      | -63         |

|          | 9.5.4    | DEPOSIT (control Store Address Spaces) 9         | -64         |

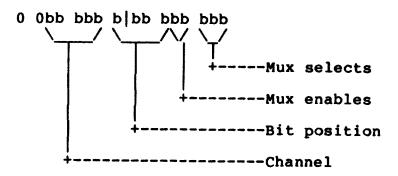

|          | 9.5.5    | DEPOSIT/CHANNEL                                  | -65         |

|          | 9.5.6    | DEPOSIT/CSPE                                     | -68         |

|          | 9.5.7    | DEPOSIT/MARK                                     | -68         |

|          | 9.5.8    | EXAMINE (control Store Address Spaces) 9         | -69         |

|          | 9.5.9    | EXAMINE/CHANNEL                                  | -70         |

|          | 9.5.10   | EXAMINE/SDB                                      | -71         |

|          | 9.5.11   | EXIT                                             | -72         |

|          | 9.5.12   | MICROSTEP                                        | -72         |

|          | 9.5.13   | REPORT                                           | -73         |

|          | 9.5.14   | SET BREAK                                        | -73         |

|          | 9.5.15   | SET HISTORY                                      | -74         |

|          | 9.5.16   | SET MARGINS                                      | -76         |

|          | 9.5.17   | SHOW BREAK                                       | -76         |

|          | 9.5.18   | SHOW DEFINE                                      | -77         |

|          | 9.5.19   | SHOW HISTORY 9                                   |             |

|          | 9.5.20   | SHOW NAME                                        | -78         |

|          | 9.5.21   | SHOW REGISTER                                    | -79         |

|          | 9.5.22   | SHOW TRACE                                       | -80         |

|          | 9.5.23   | STATESTEP                                        | -80         |

|          | 9.5.24   | TMICRO, TSTATE 9                                 |             |

|          | 9.5.25   | TRACE ADD                                        |             |

|          | 9.5.26   | TRACE DEFINE 9                                   | -82         |

|          | 9.5.27   | TRACE DELETE                                     |             |

|          | 9.5.28   |                                                  | -84         |

|          | 9.5.29   | TRACE RESTORE 9-                                 | -84         |

| CHAPTER  | 10       | PROGRAM I/O MODE                                 |             |

|          | 10.1     | IPR'S HANDLED BY CONSOLE DURING PIO MODE 10      | )-2         |

|          | 10.1.1   | SID                                              |             |

|          | 10.1.2   | · · · · · ·                                      | 0-2         |

|          | 10.1.3   | TODR                                             | <b>3</b> –3 |

|          | 10.1.4   | TXCS And TXDB                                    |             |

|          |          | _                                                | <b>3</b>    |

|          | 10.1.6   | STXCS And STXDB                                  |             |

|          |          |                                                  | -           |

APPENDIX A SAMPLE OF DEFBOO.COM FILE

APPENDIX B SAMPLE CLOCK.COM, LOAD.COM AND ULOAD.COM FILES

# VAX 8600/8650 CONSOLE SOFTWARE SPECIFICATION COPYRIGHT (c) 1985 by DIGITAL EQUIPMENT CORPORATION 6 January 1986

E.41

WBUS . .

APPENDIX C CONSOLE MODULE INTERRUPT SYSTEM APPENDIX D SDB ID FORMAT APPENDIX E DEFAULT VISIBILITY REGISTERS E.l ABUS . . . . . . . . . . . . . . . . . . . . E-3 E.2 ARADR . . . . . . ..... E-3 ARBUS DBUS . EBFLSH E.3 DBUS · · E.4 . . . . . . . . . . . . . . E-5 EBFLSH . . . . . E.5 E.6 EFORK . . . . . . . . . . . . . . . . . . E-6 E.7 . . . . . . . . . . . . . . . . . . E-7 E.8 EMCF . . ESTALL . . . . . E.9 . . . . . E-8 E.10 E.11 E.12 ..... E-10 E.13 FAUPC .... E-11 E.14 FMUPC IBDBUF . . . . . . . . . . . . . . . . . . E-11 E.15 ..... E-12 IBUF . . E.16 .... E-13 IBXERR . . E.17 IDIAG . . . . . . . . . . . . . . . . . E-13 E.18 INCR . . . . . . . . . . . . . . . . E-13 E.19 IOPSEL . . . . . . . . . . . . . . . . . E-13 E.20 ... E-14 E.21 E.22 MDBUSI . . . . . . . . . . . . . . . . . . E-15 E.23 MDBUSM . . . . . . . . . . . . . . . . E-16 E.24 . . . . . . . . E-16 E.25 MEMREO . . . . . . . . . . . . . E-17 E.26 NATRAM . . . . . . . . . . . . . . . . . . E-17 E.27 E.28 OPAR . . . . . . . . . . . . . . . . . . E-18 OPBUS . . . . . . . . . . . . . . . . . . E-19 E.29 .... E-20 OPCODE . . . . . . E.30 OPMCF . . . . . . . . . . . . . . . . . E-20 E.31 OPPORT . . . . . . . . . . . . . . . . E-20 E.32 . . . . . . . E-22 PAACK . . . . . . E.33 . . . . . . . . . E-22 E.34 E.35 PARITY . . . . . . . . . . . . . . . . . . E-23 E.36 PSL . . . . . . . . . . . . . . . . . E-25 E.37 . . . E-25 E.38 E.39 E.40

.... E-27

#### CHAPTER 1

#### INTRODUCTION AND OVERVIEW

This document describes the design and operation of the 8600 console software and is intended to be used, in part, as training material for internal and customer use. The chapter describing console I/O mode operation can also be used as a command set reference.

The console software consists of three parts: the console PROM code, a set of console subsystem diagnostics, and a console program (EDOAA.SAV). They are designed to work together to provide support for running and troubleshooting the VAX 8600 CPU and console.

Note that console software V9.0 and above support the VAX 8650 CPU as well as the 8600. Throughout the remainder of this document, 8600 implies 8600 and/or 8650.

The term 'console' is used often in this document and refers to the console program which is booted from the console disk (EDOAA.SAV). The console program is the main portion of the console software package and provides a variety of services to the operator and VAX operating system.

Other documents referenced to by this one include DEC STD 032 (chapter 11), the EMM INTERFACE SPECIFICATION, the CSM FUNCTIONAL SPECIFICATION, the DSM FUNCTIONAL SPECIFICATION, the RCP DESIGN SPECIFICATION, the XXNET PROTOCOL SPECIFICATION and the 8600 REGISTER SPECIFICATION. Note that some of these documents may be for internal use only.

# 1.1 GLOSSARY OF TERMS

Terms used throughout this document are define here.

o CBUS -- The CPU Bus is a 32x8-bit dual access RAM used for CPU/console communication. The CBUS RAM is the means by which the RX, TX, STX, and TODR register functions are provided to the CPU.

- o CCS -- Console Command Strings are diagnostic commands issued from the VAX processor, under program control, to the console program. The console interprets the string as a series of console commands to be executed.

- O CIO mode -- Console I/O mode. One of two modes that the console program can be running in (see also PIO mode). In CIO mode the console program accepts command input from the CTY and RTY ports.

- O CPU -- In this document, CPU refers to the VAX Central processor running Macro-instructions.

- o CSM -- Console Support Microcode runs in the Ebox while the console program is in CIO mode (MACRO context) and provides the console program with access to various address spaces in the CPU.

- O CTY PORT -- This is a PCI port used for console communications with the local terminal device.

- o DSM -- Diagnostic Support Microcode runs in the Ebox while the console program is in CIO mode (Diagnostic context) and provides the console with access to various address spaces in the CPU.

- O EMM -- Environmental Monitoring Module. This microprocessor-controlled unit is part of the power system and communicates to the console program to provide control and status of the power system.

- O EMM PORT -- This is a PCI port used for EMM/console communication.

- O KAF -- Refers to a CPU KEEP ALIVE FAILURE. This is a condition detected in PIO mode where the CPU stops executing instructions. In most cases the only recourse for the console program is to reinitialize and reboot the CPU. A restart of the CPU is attempted if the KAF was one of those defined in DEC STD 032 as CPU ERROR HALTS.

- O KEYWORD -- An argument on a console command line (that is not a switch).

- O LOGICAL REGISTER -- A set of visibility bits grouped together to form a register. The EXAM/SDB command is one way of displaying the state of a logical register.

- o MPS -- Modular Power System.

- O PAMM -- The Physical Address Memory Map is a RAM in the Mbox that is initialized by the INIT/PAMM command. The PAMM assigns memory arrays and I/O adapters to specific ranges of physical memory addresses.

- o PCI -- Programmable Communications Interface (generic term for USART).

- o PIO mode -- Program I/O mode. One of two modes that the console program can be running in (see also CIO mode). In PIO mode the console is a dedicated I/O device to the CPU.

- o QBA -- The Qbus Adapter interfaces the 16-bit Qbus with the 8-bit console memory bus, and also performs the necessary handshaking with the Qbus device (RLV12 controller) for DMA and register transfers.

- o RCP -- Remote Console Protocol. This is the name of the remote protocol used by the console to communicate with remote host systems.

- o REGISTER ID -- A unique 16-bit number (with the most-significant bit set) assigned to a LOGICAL REGISTER. May be used as an argument to the EXAMINE/SDB command, but mainly intended as an "tag" used internally by the console program.

- o RTY PORT -- This is the PCI port used for console communications with the remote (RD) terminal device.

- o SCP -- The System Control Panel contains the 4 state LEDs and 2 rotary switches.

- o SDB -- The Serial Diagnostic Bus provides the console with visibility into the CPU and also is used for loading control stores and state information into the CPU.

- o SDB ID -- A unique 16-bit number (with the most-significant bit clear) assigned by the CHASER utility to single visibility signal.

- o SNAPSHOT -- The process of the console collecting data from the CPU after a KAF and saving it on the console's disk.

- o TODR -- The Time Of Day Register is a 32-bit integer in the CBUS that the console increments once each 10 milliseconds to provide the CPU with Time-of- Year information.

- o TOY -- Time of Year, in terms of 10 millisecond increments from the beginning of the year.

- o TRANSPARENT MODE -- Term used to describe normal, non-protocol, remote terminal activity.

- o UPC -- Short for micro PC.

- O VISIBILITY REGISTER -- See LOGICAL REGISTER.

O VTERM -- Visibility Terminator. Special logic device used to terminate up to 8 ECL signals and provide visibility to each individual bit.

# 1.2 HARDWARE OVERVIEW

The hardware environment is discussed in detail in the specification for the console hardware subsystem. The following points highlight the hardware characteristics of main interest.

- O DEC's own T-ll chip is used as the microprocessor for the console subsystem, supporting the LSI-ll instruction set less MUL, DIV, SXT, and MARK instructions.

- o The console subsystem has 256kb of on-board, parity assisted, dynamic RAM. There is a custom section of mapping logic to facilitate virtual memory operation of the console program.

- o The console subsystem has 3 on-board PCI's for handling Cty, Rty, and EMM communications.

- o All I/O device CSR base addresses and vector addresses are non-standard, in terms of other PDP-11 products.

- o An 8-bit by 32 location dual-ported RAM (CBUS) is used for console/CPU communication.

- O A Serial Diagnostic Bus (SDB) provides control and visibility to the CPU and is used to access machine control stores.

- o A single-chip timer (Am9513) provides lms timing for the console program, which in turn is used to handle the 10ms TODR register.

The console software has been designed to run only on the 8600 console subsystem and is not intended to be transportable to other PDP-11 based systems.

# 1.2.1 Console Subsystem Illustration

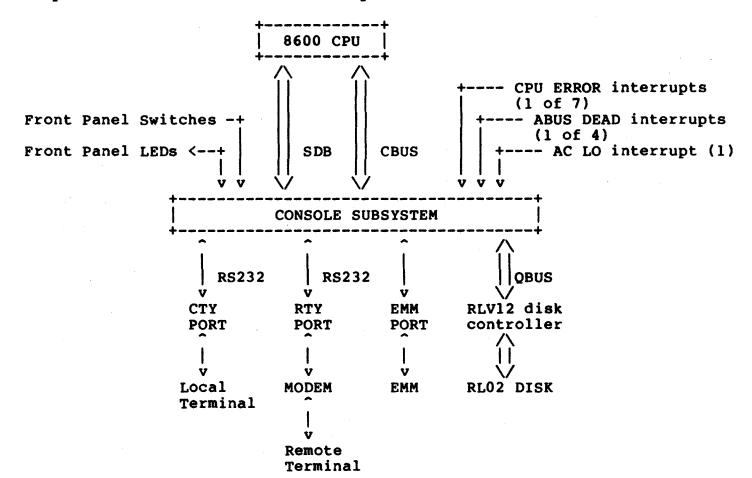

The following diagram shows the relationship between the console subsystem and the rest of the 8600 system.

#### 1.3 CONSOLE SOFTWARE OVERVIEW

#### 1.3.1 Console PROM

The console hardware includes an 8KB PROM which provides power up self-tests of the console hardcore, handling of console reboots and unexpected interrupts, and a simple command interpreter. A full description of the console PROM code is given in its own chapter of this document.

#### 1.3.2 Console Program

The console program is loaded from the console pack by the PROM code during normal system power-up initialization. Once running, the console program is in control of the console subsystem and VAX CPU.

From the user perspective there are three distinct modes that the application software can be running in:

- Console IO (CIO) mode. In this mode the VAX processor is halted and the console accepts and processes commands from the operator.

- 2. Program IO (PIO) mode. In this mode the console is slave to the running VAX processor and does not accept any console commands from the operator.

- 3. CIO mode with CPU running. In this mode the operator has entered CIO mode by typing ^P, but the CPU is still running. In this mode the operator may issue a limited set of console commands (those that don't affect the CPU operation), and the CPU cannot perform I/O to the Cty, Rty, console load device, or EMM).

While in CIO mode (with the CPU not running) there are three separate command contexts that can be run, each having a specific purpose and command set. A general command set is available under all of these CIO mode contexts, and a microcode/hardware debugger command set can be enabled under two of the three contexts.

#### 1.3.3 RT-11 Operating System

A conditionalized version of RT-ll is used to provide the console program with the general system-software requirements. This includes a disk file structure, CTY port services, timer functions, disk I/O handling and bootstrapping.

The presence of RT-11 is invisible to the operator; its commands and utilities are not available. Any console pack file maintenance (e.g., updates) must be done from the timesharing system via the console/CPU interface (CBUS). The RT-11 software is considered a part of the console program kernel.

/A special command, PROM/RT, is provided for INTERNAL use only, and will transfer control from the console program to the RT-11 operating system./

# 1.3.4 Console Subsystem Diagnostics

The console diagnostic (EDOBA) is loaded from the RLO2 by the console PROM's 'T' command. Other diagnostics may be loaded using the T command with a filename argument. Instructions on how to enter the PROM command mode and run console diagnostics is given in the section describing the PROM code.

#### 1.3.5 On-line Utilities

There are two preparation utilities responsible for console program data file generation. UCBLD creates machine loadable microcode files, and CHASER creates SDB visibility data "lookup" tables.

# 1.3.5.1 UCBLD Utility

UCBLD is maintained by the Large Vax Diagnostics group. It runs under VMS and is written in FORTRAN. Its purpose is to convert assembled microcode (.ULD output from the MICRO2 assembler) into a binary formatted output file (.BPN for Binary Physical Normalized). The .BPN file conserves space on the console pack and also allows more time-efficient loading of control stores.

The .BPN file consists of fixed-length records, each file having its own record size depending on the size needed for the largest record in that file. Records are padded with null-byte characters where necessary to make them all the same size.

All .BPN files begin with a header record that contains control and revision information and uses a minimum of 6 bytes. The header contains the number of data records following it. The last data record can be followed by another header record if another type of microcode data is present in the file, or by a null record which indicates the end of the file has been reached.

The format of the header record is:

| byte | contents                |

|------|-------------------------|

|      |                         |

| 1    | letter code             |

| 2    | version, minor          |

| 3    | version, major          |

| 4    | record size             |

| 5    | record count, low byte  |

| 6    | record count, high byte |

| x    | padding if necessary    |

The "letter code" is the unique letter assigned to the control store and is used in determining the size and destination of the control store data. The letter code assignments are:

| ~ |     | When Hall sembus? shows | / 40 | L 2 L L |   | <b>610</b> |            |

|---|-----|-------------------------|------|---------|---|------------|------------|

|   |     | Fbox "A" control store  | (48  | Dits    | X | 512        | locations) |

|   |     | Ibox decode Ram         |      |         |   |            | locations) |

| E | -   | Ebox scratch Pad Ram    |      |         |   |            | locations) |

|   |     | Fbox decode Ram         |      |         |   |            | locations) |

| F | _   | Fbox "M" control store  |      |         |   |            | locations) |

| H | -   | Access control Ram      |      |         |   |            | locations) |

| I | -   | Ibox control store      | (52  | bits    | X | 256        | locations) |

| M | *** | Mbox control store      | (80  | bits    | X | 256        | locations) |

|   |     | Cycle parameter Ram     |      |         |   |            | locations) |

|   |     | Ebox control store      |      |         |   |            | locations) |

|   |     | Ebox context Ram        |      |         |   |            | locations) |

| Y | -   | Ebox MCF Ram            | (16  | bits    | X | 256        | locations) |

|   |     |                         |      |         |   |            |            |

The second and third bytes in the header contain microcode version information divided into a major level and minor level. The major rev number is an 8-bit integer independent of the minor rev, which is also an 8-bit integer. This allows version numbers up to 255.255. This version number is extracted from the second line of the .ULD file and is forced to zero if no version number is found. The .ULD version number must be on the second line of the file and be in one of the following formats:

```

;Vmajor

;V.minor

;Vmajor.minor

```

Note that the following version numbers are equivalent:

```

;V1.01 = ;V1.1

;V02 = ;V2

```

The next header byte contains the record size and is the size in bytes of all records in the file, including the header record. Records are padded with null-byte characters where necessary.

The last two header bytes contain the record count, which is the number of data records following the header. The record count does not included the header itself.

The header record is followed by the first data record, which begins at byte offset "filestart+recordsize". The format of a data record is:

| byte | contents                     |

|------|------------------------------|

|      |                              |

| 1    | load address, low byte       |

| 2    | load address, high byte      |

| 3    | ecc code                     |

| 4    | null byte                    |

| 5    | data, least-significant byte |

| 6    | data                         |

| •    | data                         |

| •    | data                         |

| •    | data                         |

| n    | data, most-significant byte  |

| x    | padding if necessary         |

The first two bytes of a data record contains the load address at which to load the data. This is followed by the ECC code calculated for the data field of this record and is used for single-bit parity error correction. Following the ECC byte is a null byte used to word-align the data field.

The fifth byte in the data record is the least-significant byte of the data to be deposited into the control store ram.

# 1.3.5.2 CHASER Utility

This utility, maintained by the CAD group, analyzes the CAD data base and produces a set of ASCII files which the console program uses to identify SDB visibility-bit addresses. At console initialization time the file CDF860(or 865).DAT is opened (on the console pack) and a list of .CDF filenames extracted from it. The .CDF files are then opened and processed, yielding a Tll-memory resident set of SDB translation tables tailored to the particular system configuration at hand.

#### CHAPTER 2

#### **STANDARDS**

This chapter lists the DEC standards which apply to the console software. Unless stated otherwise, compliance with all aspects of these standards have been met.

# 2.1 DEC STD 032 - "VAX ARCHITECTURE"

There are two chapters in DEC STD 032 which affect console software directly. All areas of non-compliance must be sited since this standard deals heavily with operator and VAX processor interfaces to the console.

The first area of concern is Chapter 11, Console and Bootstrap. This defines most of the commands implemented in the CIO mode MACRO context. It defines the means by which console devices, such as the disk and terminals, should be communicated with by native mode programs.

Another area of concern is Chapter 9, privileged registers, which is relevant to the console as the names and addresses of these registers as well as whether they are read only or read/write is detailed. Also the format and nature of the RXCS, TXCS, STXCS, STXDB, TODR, and SID is affected by the design and structure of the console program.

#### 2.1.1 Noncompliance

The major areas of non-compliance with this standard are listed below. Only MACRO context commands are included here.

- The EXAMINE command displays a full 32-bit number even if the /BYTE or /WORD switch is used. The unspecified portion of the data is forced to 0.

- o The /C switch on the LOAD, EXAMINE, and DEPOSIT commands is not supported.

- o An additional switch is provided on the BOOT command (/NOSTART) to allow easy modification of boot parameters.

- o The character typed to exit from space-bar-step-mode is thrown away.

- o There is no way to set a default data type or address space for the EXAMINE and DEPOSIT commands. The defaults are always longword, physical.

- o BOOT, START, and CONTINUE do not cause a command file to suspend execution.

- o The %O, %X, and %D prefixes can be used to override the default radix.

- o There is no TEST command.

- o The START and CONTINUE commands are used to re-enter PIO mode after a ^P break to CIO mode, regardless of whether or not the CPU is already running.

# 2.2 DEC STD 051 - "ASCII DATA STANDARD"

The area of major concern with this standard is in the use of control characters. Since only certain DEC products will be supported as terminals the impact of a variant is slight.

# 2.3 DEC STD 052 - "MODEM SUPPORT"

This standard defines MODEM support necessary to meet requirements of all known modem devices. All requirements of this specification have been met.

# 2.4 DEC STD 172 - "LEGAL NOTICES"

This standard defines copyright and liability information to be included in all source files for the console program.

# 2.5 DEC STD 112 - "FORMATTING DATE AND TIME"

This standard defines how the time and date is to be expressed in messages and commands visible to the users. In all aspects of customer visible functions it has been complied with fully.

# 2.6 DEC STD 145 - "FORMATTING DATA"

This standard defines internal data formats as well as ways of expressing floating point and integer values. Compliance with this standard makes borrowing and interfacing with existing software easier.

#### CHAPTER 3

#### CONSOLE PROM OPERATION

PROM code initialization is performed whenever the machine power is turned on, or whenever a power failure recovery is being attempted. It is not performed entirely when a console reboot is requested by the CPU interrupt (TSTRT) or by the REBOOT command. Initialization begins with the execution of several self-tests and ends with the booting of the console program from the RL.

Optionally, the user may wish to use the limited PROM command set to test the console further or perform some I/O register manipulation.

Invisible to the user is the fact that the console PROM is segmented into two 4kb sections, only one of which is enabled at a time. When a segment is enabled it occupies the Tll addresses between 164000 and 173776. This reduces the amount of console memory space needed to run the 8kb PROM to only 4kb. Switching between segments is handled mainly by the PROM code itself, with the exception of a power on condition.

#### 3.1 POWER-UP OPERATION

On power-up the Tll issues a console INIT pulse to clear most of the console hardware registers (which disables all Tll interrupts and enables the lower segment of the PROM) and vectors to the PROM address 172000. Immediately the PROM begins a series of self tests designed to verify logic critical to operation. It is assumed, however, that the Tll chip and its instruction set is fully operational. The following subsection describes the self-tests in detail.

When a self-test fails the console loops indefinately. In some cases the front panel LEDs are used to indicate the failing test number, but mostly there will be an error message displayed on the CTY.

If none of the self-tests fail the PROM code turns off the 4 front panel LEDs and sets up all T11 interrupt vectors to point to the "unexpected interrupt handler" entry to the PROM (172010). It then transfers control to the upper 4kb segment. The upper segment begins by sending a <CR><LF><BELL> sequence to the CTY to let the operator

know that the self-tests have completed and that the console program is about to be booted. A pause of 3-4 seconds occurs between the ringing of the CTY bell and the beginning of the RL boot sequence, during which any input typed on the CTY causes the PROM to enter its command input loop.

The RL boot sequence consists of a series of RL-access tests prior to the actual boot attempt. These tests are explained in the section describing the B command.

#### 3.1.1 Self-test Execution

The execution of the PROM self-tests occurs immediately after power is supplied to the Tll processor and surrounding circuitry. It is assumed that the Tll internal logic is operational.

Test loop controls similar to those found in diagnostic programs are used. A test will loop on error, respond to ^S, ^Q, and ^O (if the test outputs anything), and will exit the loop in response to ^E (only for some tests). Furthermore, a special trigger signal is SET immediately after detection of the error and cleared at the end of each test loop. This serves as a trigger input for oscillascopes and analyzers and is located as the signal CLO9 DIAG TRIGGER H.

The tests are arranged in a building block fashion so that logic is not used before it is tested. Because the CTY interface is not known to be good the initial tests rely on the front panel LEDs to contain test numbers. When one of the primitive tests fails the front panel LEDs will contain the test's number. As soon as the CTY interface is tested the PROM Vn.n banner is printed. The CTY is used to report errors beyond that point while the LEDs remain in there last set state, which happens to be 1001 (test 9).

Errors reported to the CTY are of the following form:

CONSOLE SELF-TEST DETECTED ERROR: TEST #n SUBTEST #n "descriptive message"

"data header"

"data ..."

The first couple of self-tests verify the integrity of the PROM code, the front panel LEDs, and much of the Tll addressing and data paths.

Upon receiveing power the front panel LEDs are forced to the ON state. At this time the PROM code begins its first test, which is to calculate the additive checksum of the entire 8kb PROM. If unsuccessful the code falls into a "BR." instruction and the LEDs remain in the llll state. Note that the llll state will also remain if some other critical Tll logic is broken.

Below is a list of the PROM tests executed up to the displaying of the PROM Vn.n banner.

Test #0 PROM CHECKSUM TEST

LED state = 1111

Description: An additive checksum of both the lower and upper segments

of the PROM is calculated. The result should be 377(8).

On error a "BR ." is executed.

Test #1 SCP SDB CHANNEL TEST

LED state = 0001 -> 0010 -> 0100 -> 1000

Description: A floating 1 pattern is shifted through the LED's at a fairly

slow speed so the operator can tell if there is a LED

failure. The test checks most of the SDB control logic and the SCP LED logic which is used by following tests to report

test numbers. The test is open ended and cannot fail.

Test #2 CTY INTERFACE MODE REGISTER 1 BIT TEST

LED state = 0010

Description: Alternating 01010101 and 10101010 patterns are written and

read from the CTY's PCI MODE REGISTER 1.

Test #3 CTY INTERFACE MODE REGISTER 2 BIT TEST

LED state = 0011

Description: Alternating 01010101 and 10101010 patterns are written and

read from the CTY's PCI\_MODE\_REGISTER\_2.

Test #4 CTY INTERFACE COMMAND REGISTER BIT TEST

LED state = 0100

Description: Both a 01010101 and a 10101010 pattern is written and

read from the CTY's PCI\_COMMAND\_REGISTER.

Test #5 CTY INTERFACE RESET TEST

LED state = 0101

Description: A pattern is loaded into the PCI COMMAND REGISTER and a

PCI RESET is performed. If the command register clears then

the PCI's RESET input is connected and working.

Test #6 CTY INTERFACE TXRDY BIT TEST

LED state = 0110

Description: The local PCI is configured to run in its normal operating

mode (9600baud, 8-bit, noparity, 1 stop). The TxRDY bit in the PCI status register is then expected to set within 100ms. If ok, the PCI transmit register is loaded and the TxRDY

bit is expected to clear immediately.

Test #7 CTY INTERFACE RXRDY BIT TEST

LED state = 0111

Description: The local PCI is reinitialized but this time in local loop-

back mode. A character is transmitted and the RxRDY bit in

the PCI status register is expected to set. When the RECEIVED\_CHARACTER\_REGISTER is read the RXRDY bit is

expected to clear.

Test #10 CTY INTERFACE LOOP BACK TEST

LED state = 1000

Description: This is essentially the same as the previous test except that several loopback transmissions are perform-

ed to make certain the PCI and crystal can handle it.

Test #11 CTY BANNER TEST

LED state = 1001

Description: This is an open ended test that relies on the operator

to observe the PROM Vn.n banner.

At this point the CTY interface, cable, and printer are assumed to be operational. Test failures from here on are reported on the CTY and CTY input may also be recognized where indicated. The remaining tests in the PROM initialization are listed below. Tests that allow the ^E input character can be exited if they fail, otherwise the test will loop indefinately. The other input control characters can be used stop (^S) or resume (^Q) test execution, or suppress (^O) error report output.

Test #12 PARITY ERROR LATCH TEST

Allowable Control Characters are 'S 'Q 'O E.

Description: Tests that the latch responsible for indicating parity

errors can be set and cleared directly.

Test #13 PARITY CIRCUIT TEST, PART 1

Allowable Control Characters are 'S 'Q 'O E.

Description: Simultaneously tests that RAM location 0 will hold a

01010101 pattern. If ok, location 0 of the parity RAM

is expected to contain 1.

Test #14 PARITY CIRCUIT TEST, PART 2

Allowable Control Characters are 'S 'Q 'O 'E.

Description: Simultaneously tests that RAM location 0 will hold a

10101010 pattern. If ok, location 0 of the parity RAM is expected to contain 0 (since the "force parity error"

bit in MCSRO was set prior to depositing the pattern).

Test #15 58KB RAM DATA/ADDRESS TEST, BOTTOM-UP

Allowable Control Characters are 'S 'O 'O E.

Description: A modified moving-inversions test is performed on the

first 58KB of physical RAM. The test verifies all data stuck-at faults likely to occur in the console RAM con-

figuration as well as all addressing faults in the

positive (incrementing) direction. On error the address,

expected data, and received data are displayed.

Test #16 58KB RAM DATA/ADDRESS TEST, TOP-DOWN

Allowable Control Characters are 'S 'Q 'O E.

Description: A modified moving-inversions test is performed on the

first 58KB of physical RAM. The test verifies all data stuck-at faults likely to occur in the console RAM con-

figuration as well as all addressing faults in the

negative (decrementing) direction. On error the address,

expected data, and received data are displayed.

Test #17 MAP RAM LOCATION 0 QV TEST

Allowable Control Characters are 'S 'Q 'O E.

Description: A loop is first performed that uses the first mapping RAM

location (MAPR00) to initialize all of physical memory with zero's and good parity, and placing each 4kb-page number in the first location of its own 4kb page boundary. The process is repeated to check that the first byte of each

page does contain the correct value.

Test #20 MAPPING RAM DATA TEST, BOTTOM-UP

Allowable Control Characters are 'S Q O E.

Description: This test uses the memory pattern verified by the previous

test to check that all mapping RAM locations can access

pages uniquely, in the positive direction.

Test #21 MAPPING RAM DATA TEST, TOP-DOWN

Allowable Control Characters are 'S Q O E.

Description: This test uses the memory pattern verified by the previous

test to check that all mapping RAM locations can access

pages uniquely, in the negative direction.

Test #22 MAPPING RAM ADDRESSING TEST

Allowable Control Characters are 'S Q O E.

Description: This test uses the memory pattern verified by the previous

tests to check that all mapping RAM locations are themselves

uniquely addressable. The memory mapper is then turned off.

Test #23 TOY CHIP ACCESS TEST

Allowable Control Characters are 'S 'Q 'O 'E.

Description: This test checks that registers in the console's TOY chip

can be accessed. This verifies that the TOY chip is receiving power from the +5 B signal input from the BBU.

Test #24 RTY INTERFACE MODE REGISTER 1 BIT TEST

Allowable Control Characters are 'S 'Q 'O 'E.

Description: Normal operation patterns are loaded into the RTY's PCI\_

MODE REGISTER 1 and checked.

Test #25 RTY INTERFACE MODE REGISTER 2 BIT TEST

Allowable Control Characters are 'S Q O E.

Description: Normal operation patterns are loaded into the RTY's PCI\_

MODE REGISTER 2 and checked.

Test #26 RTY INTERFACE COMMAND REGISTER BIT TEST

Allowable Control Characters are 'S Q O E.

Description: Both a 01000101 and a 10101010 pattern is written and

read from the RTY's PCI COMMAND REGISTER.

Test #27 RTY INTERFACE RESET TEST

Allowable Control Characters are 'S Q O E.

Description: A pattern is loaded into the PCI\_COMMAND\_REGISTER and a

PCI RESET is performed. If the command register clears then the PCI's RESET input is connected and working.

Test #30 RTY INTERFACE TXRDY BIT TEST

Allowable Control Characters are 'S 'O 'O 'E.

The remote PCI is configured to run in its normal oper-Description: ating mode (1200baud, 8-bit, noparity, 1 stop). The

TXRDY bit in the PCI status register is then expected to set within 100ms. If ok, the PCI transmit register is loaded and the TxRDY bit is expected to clear

immediately.

Test #31 RTY INTERFACE RXRDY BIT TEST

Allowable Control Characters are 'S 'Q 'O 'E.

Description: The remote PCI is reinitialized but this time in local

loop-back mode. A character is transmitted and the RXRDY bit in the PCI status register is expected to set. When the RECEIVED CHARACTER REGISTER is read the RXRDY

bit is expected to clear.

Test #32 RTY INTERFACE LOOP BACK TEST

Allowable Control Characters are 'S 'Q 'O 'E.

Description: This test duplicates the function of the previous test

to verify that the remote PCI can handle consecutive

character transmissions.

Test #33 SCP SDB LOGIC TEST

Allowable Control Characters are ^S ^Q ^O ^E.

Description:

This test checks the continuity of the SDB control chan-nel on the SCP. This test will affect the state of the front panel LEDs but is done so fast it is unnoticable.

Test #34 "CL15 TSTRT" INTERRUPT TEST

Allowable Control Characters are 'S 'Q 'O.

This test checks that the TSTRT interrupt input to the Description:

console is not asserted. This interrupt is not maskable

through PSW so it must be cleared before the console

program will run.

Test #35 UNEXPECTED INTERRUPT TEST

Allowable Control Characters are 'S 'Q 'O.

Description: This test checks that after a full console reset there

are no pending (or stuck) interrupts to the Tll. This is to ensure the proper startup of RT and the console

kernel.

# 3.2 PROM COMMAND LOOP

When the PROM code signals the completion of the selt-tests sending the bell character to the CTY the operator can type any input and cause the PROM to enter its command null loop. While in the null loop the PROM code may service the RTY device as well as the CTY for possible input (provided the front panel switch is in the REMOTE position and a remote connection has been made). The PROM code indicates its readyness for input with the "ROM>" prompt.

The command parser in the PROM is extremly simple. It accepts single character commands and alphanumeric arguments. The commands available to the user are listed below.

Command: Description:

Boot the console software from the RL. This command begins by testing the interface between the console and the RL controller. The sequence of tests are:

Check for AC LOW and DC LOW conditions in the BAll.

Check that console generated BUS INIT reaches the RL controller and clears all RL controller registers.

Check that RLCS, RLBA, and RLDA will retain a full compliment of patterns.

Perform an RL MAINTENANCE TRANSFER to verify DMA logic between the console and RL, and other logic on the RLV12.

Check that the first word read in from the RL boot block contains "240" (NOP).

If any of the above checks fail a message is reported to both the CTY and RTY and the B command aborts. There is no test looping capability. If a drive or controller status error is detected during the actual booting of the device a number of retries is done.

D addr data

Deposit the data word to the specified address. The address must be an even number.

E addr

Examine the data word at the specified address. Odd addresses are made even by dropping the low order bit.

S addr

Start the Tll execution at the specified address. The address must be an even number. The command-argument delimiter is optional.

T [ filename ]

Without any argument this command re-runs the PROM self-tests and then loads and runs the console diagnostic program (EDOBA) for 2 passes. If a filename is specified the self-tests are not run and the file is loaded and started at location 200. The default filename extension is .SAV.

Q addr data

This command allows direct deposits to Qbus registers. The addresses 174400, 174402, 174404, and 174406 are the RLCS, RLBA, RLDA, and RLMPR registers, respectively. All other addresses are rejected.

R addr

This command allows direct examines of Qbus registers. The addresses 174400, 174402, 174404, and 174406 are the RLCS, RLBA, RLDA, and RLMPR registers,

respectively. All other addresses are rejected.

V

This command causes the PROM code to enter a loop designed to allow characters to pass directly between the CTY and RTY. This is commonly used in manufacturing to allow the operator to communicate with VMS in order to initiate the down-line loading of test code into the console (using the X command). The escape sequence ^P^X^P can be entered from either input device to force the PROM code to exit this mode.

X

This command complies (less any switches) with the description of same in chapter 11 of DEC STD 032. It is intended to be used for binary data transfers between T11 memory and a computer using the remote port input. It is not intended for use by humans and will work properly only when issued from the RTY device.

#### 3.3 PROM RTY SUPPORT

The PROM code services the RTY port with a much simpler procedure than the one used by the console program. This is necessary since the PROM code has no timer or interrupt capability. No remote protocol support is offered by the PROM, only character mode operation exists.

After the PROM code completes its power-up self-tests, which includes loop back tests on the RTY PCI, it configures the PCI to operate with default characteristics (same defaults used by the SET TERMINAL command). Once the PCI is set up, and if the front panel terminal control switch is in the REMOTE position, the PROM asserts the DTR signal to the MODEM, thus allowing the MODEM to turn on-line. If the DSR and CD signals from the MODEM are sensed as TRUE then all character output to the CTY will also be sent to the RTY port, and input will be accepted from either. Note that because the DTR signal to the MODEM is not asserted until the end of the self-tests it will be virtually impossible to establish a MODEM connect to the RTY port during system power-on intialization while he PROM is still running. However, a terminal connected locally with a NULL MODEM cable should not have any problem getting control of the PROM code, and it is for this reason that this scheme becomes useful.

Once the PROM asserts DTR to the MODEM the dial-in capability is activated. When the console program starts running it begins to service the RTY port immediately, thus giving the remote user control throughout PROM-to- console program transitions, and visa-versa. This means that if Tll control transfers to the PROM because of some unexpected condition, such as for a T-ll HALT or unexpected interrupt, the PROM can continue to service the remote connection.

During the handling of connections and disconnections of the remote terminal by the PROM code the state of the front panel indicators is updated in accordance with the definitions of those

indicators within this document.

Because the RTY interface is tested by the prom self tests and by the console diagnostic (EDOBA) the T command cannot be used by the RTY user. It is therefore an assumption that the console subsystem is fully operable before a remote session can be properly handled.

#### 3.4 SPECIAL SERVICES

The console PROM code provides two special services to the console program. The first is to handle unexpected interrupts, and the second to handle console reboot requests. These services are described below.

# 3.4.1 Unexpected Interrupt Handling

Whenever the PROM code receives control of the T11, whether by first-time power up, a console reboot, or an unexpected interrupt, it disables T11 interrupts by raising the interrupt priority level (IPL) in the PSW to 7 (highest) and loads all T11 interrupt vectors with a pointer to the PROM's unexpected interrupt service routine (172010). The "new PSW", contained in the location following each vector location, contains a 4-bit id in the condition code field such that a single service routine entry can be used for all interrupt vectors.

There are 16 possible vectored interrupts on the console module, 2 of which are unused and can never occur. Each vector is dedicated for one specific device. The following table lists the vectors, priority levels, and id codes for all possible console interrupts.

| Vector | IPL | ID | I/O Device                        |

|--------|-----|----|-----------------------------------|

|        |     |    |                                   |

| 24     | *   | 00 | PROM RESTART (*UNMASKABLE by PSW) |

| 60     | 4   | 01 | REMOTE PCI TRANSMIT/RECEIVE/MODEM |

| 64     | 4   | 02 | LOCAL PCI TRANSMIT/RECEIVE        |

| 70     | 4   | 03 | QBUS REPLY TIMEOUT                |

| 100    | 6   | 04 | UNUSED                            |

| 104    | 6   | 05 | TOY 1MS INTERRUPT                 |

| 110    | 6   | 06 | CPU CONTROL STORE PARITY ERROR    |

| 114    | 6   | 07 | STOR RDY                          |

| 120    | 5   | 10 | TXCS RDY                          |

| 124    | 5   | 11 | RXCS DNE                          |

| 130    | 5   | 12 | QBUS ADAPTER                      |

| 134    | 5   | 13 | EMM PCI TRANSMIT/RECEIVE          |

| 140    | 7   | 14 | CONSOLE RAM PARITY ERROR          |

| 144    | 7   | 15 | UNUSED                            |

| 150    | 7   | 16 | SYSTEM AC LOW                     |

| 154    | 7   | 17 | ABUS DEAD                         |

The devices handled by vectors 24, 70, and 140 are always handled by the PROM code as unexpected interrupts.

When the PROM receives control at its unexpected interrupt service routine it decodes the four-bit ID number in the condition code field of the PSW and reports the vector through which the transfer was made. This is followed by the contents of the Tll registers (R0 through R7 and PSW) at the time of the interrupt. In the case of vector 140, console ram parity error, the PROM code constructs the address of the parity error (from the PECAS and PERAS registers) and displays this, along with the contents of the location and whether or not the parity error is hard or soft.

Because most of the interrupts on the console are level-sensitive rather than edge-sensitive there is no easy way for the PROM to dismiss the interrupt and return to the previous Tll instruction stream. Thus, the PROM code enters its command loop and waits for operator intervention, or a CPU reboot request, to restart the console program.

# 3.4.2 Console Reboot Handling

In addition to the 16 vectored interrupts described in the previous section there is another which forces the console to begin execution at the PROM entry responsible for handling console reboots (172004). When the Tll interrupt facility is enabled (MCSRO bit 0 = 1) it treats this interrupt as an unmaskable edge-sensitive input which saves the PC and PSW, forces the IPL to priority 7, and vectors the Tll directly to the reboot address. This same operation occurs when the Tll executes a HALT instruction.

If the cause of the entry into the reboot/halt routine was a TSTRT interrupt, which can be generated by the CPU's MTPR CRBT instruction or the console's REBOOT command, the message "?Console Reboot Initiated" is printed and the PROM reboots the RL. Note: VMS issues a TSTRT interrupt if the console fails to update the Time-Of-Day register (TODR) for a considerable period of time  $(1-2\,\text{minutes})$ .

If the cause of the entry was due to a Tll HALT instruction the ?Tll HLT message is printed followed by the Tll registers saved prior. The PROM code then enters its command loop and waits for input. While the PROM code waits in its command loop it is still sensitive to TSTRT interrupt requests from the CPU.

The PROM code has no responsibility for saving or restoring console state information during a reboot. This is done entirely by the console program.

#### CHAPTER 4

#### CONSOLE DIAGNOSTIC OPERATION

The VAX 8600 Console diagnostic is named EDOBA and is a stand-alone program that can be loaded directly by the PROM "T" command. Its tests begin where the PROM self-tests leave off, but has loop controls superior to those in the PROM.

The purpose of this diagnostic is to detect problems in consoles installed in either a VAX 8600 system or in one of the special console test stations used in manufacturing. The 8600 CPU must be brought down before the diagnostic can be run; it cannot be run on-line.

Note that the diagnostic cannot be run by the RTY user since it tests the RTY interface.

#### 4.1 HOW TO RUN THE DIAGNOSTIC

The console diagnostic can be loaded directly from the PROM command prompt, using the T command, or down-line loaded from a remote host using the X command and then started with the S command. The normal start address is 200, which is also the restart address. The entry at location 204 is used by the T command as an auto-run entry where EDOBA automatically runs 2 complete passes and then returns control to the PROM code.

When the PROM "T" command is used without argument the console diagnostic is automatically loaded and started at location 204 after the PROM self-tests complete. If EDOBA detects an error or is interrupted by the operator (via G) then the return to the PROM is inhibited and EDOBA runs indefinately.

While EDOBA is running the operator can enter any of the following control characters at any time:

<sup>^</sup>S - SUSPEND PROGRAM OUTPUT, PROGRAM WAITS FOR Q

<sup>^</sup>O - RESUME PROGRAM OUTPUT

<sup>^</sup>G - ENTER SWREG-CHANGE MODE

While in SWREG-CHANGE mode the following control characters may be used:

^U - IGNORE INPUT LINE AND PREPARE TO ACCEPT ANOTHER

^C - RESTART THE PROGRAM

^P - EXIT TO THE PROM COMMAND PROMPT

# 4.2 PROGRAM REQUIREMENTS

The diagnostic program requires that the local terminal (CTY) interface be set to the following characteristics:

Transmit/Receive Baud rate = 9600/9600 8 data bits, no parity, 1 stop bit

The RTY interface is tested and cannot be used as a remote terminal during execution of EDOBA.

Also required is an RLO2 disk pack loaded and ready in the RL drive. No disk-write operations are done by the diagnostic, only register and DMA reads are done.

# 4.2.1 Diagnostic SWREG Settings

The ^G character causes the diagnostic to enter SWREG-CHANGE mode. This begins by displaying the current setting of the SWREG, in octal, and then prompts the operator for a new value or a <CR> to leave it unchanged. The list below shows the different SWREG bit positions.

| SWITCH | BIT    | DESCRIPTION                             |

|--------|--------|-----------------------------------------|

|        |        | *************************************** |

| 15     | 100000 | EXIT SUBTEST LOOP AND PROCEED           |

| 14     | 040000 | LOOP ON (NEXT) FAILING SUBTEST          |

| 13     | 020000 | INHIBIT ERROR TYPEOUTS                  |

| 12     | 010000 | ENABLE TEST-TRACE MODE                  |

| 11     | 004000 | INHIBIT INTERNAL TEST ITERATIONS        |

| 9      | 001000 | LOOP ON TEST IN SWR<7:0>                |

| 7-0    | 000XXX | TEST NUMBER TO LOOP ON                  |

#### 4.2.2 Test Looping Characteristics

When it is desired to force a specific test into a loop the SWREG is used. The number of the test to loop on is loaded into SWREG bit 0 thru 7 and bit 9 is set. For example, a SWREG value of 1120 will cause EDOBA to loop on test number 120 the next time that test is encountered. In the test loop all test intialization and subtests are performed on each interation. To exit the test loop bit 9 of the SWREG must be cleared, or another test number can be placed in bits 7

thru 0.

When SWREG bit 14 is set the diagnostic will loop on the next failing subtest encountered. Only the failing subtest is executed in the loop, regardless of whether or not the subtest continues to fail. To exit this loop SWREG bit 14 can be cleared, or bit 15 can be set. Note that setting both bits 14 and 15 causes the looping test to exit but looping resumes on the next failing test encountered. Note that a subtest loop due to a detected failure has precedence over a test loop controlled by SWREG bit 9.

When a diagnostic test fails and begins looping the console signal "CL09 DIAG TRIGGER H" is fired once on each iteration of the loop. This helps to synchronize a 'scope to the test and thus isolate the failure. This is not identical to the way this signal is used by the PROM self-tests.

# 4.2.3 Interpreting Failure Reports

The general format of an error report generated by the diagnostic is shown below. The "expected and received data" field is included only where pertinent data is available.

ERROR DETECTED BY TEST #xxx, SUBTEST #yyy "descriptive error message" "expected and received data"

The "descriptive error message" will, in most cases, consist of a console module signal name and the schematic page number (in parenthesis) where the error was actually perceived by the diagnostic (point of visibility). The diagnostic listing must be referred to for details of the actual failure, and from there the cause of the failure. In most cases a subtest failure involves only a few logic components and thus provides the isolation necessary for quick manufacturing repairs.

The contents of the "expected and received data" field is a function of the test being performed. Each data item displayed has its own header which indicates what the data is.

Some examples of typical error reports are:

ERROR DETECTED BY TEST #4, SUBTEST #1

"CL18 STOP CLOCK" FAILURE (CL18)

ERROR DETECTED BY TEST #40, SUBTEST #2

MCSRO REGISTER BIT FAILURE (CL08)

EXPD RCVD

000242 000252

In the first error report, the signal "CL18 STOP CLOCK" failed to respond correctly to the test stimulus applied. The point of visibility is given to the right of the descriptive message.

In the second error report the console register MCSRO failed one of its data pattern tests. The expected data (test pattern) is shown under EXPD and the received data (test result) is shown under RCVD.

#### CHAPTER 5

# CONSOLE SOFTWARE EXTERNAL OPERATION

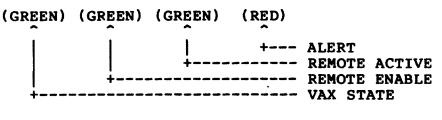

This chapter discusses general console operations that are, in most cases, visible to the user. Such items include the handling of external interrupts from the VAX processor, front panel switch input and LED output, remote and local terminal handling, and system initialization.

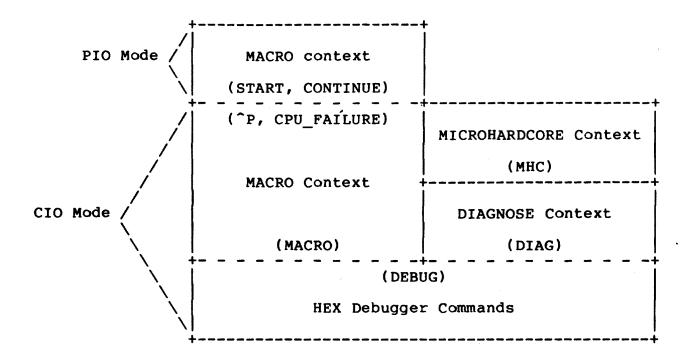

Briefly, there are two modes of operation in the console program: Console I/O (CIO) mode, where operator command input is accepted, and Program I/O (PIO) mode, where the console acts as a slave to the VAX processor servicing its requests. These two modes are discussed in more detail in other chapters. For now, it suffices to know that there are three separate CIO mode contexts that can be run: MACRO context, DIAGNOSTIC context, and MICROHARDCORE context. Each context has its own command set and specific purpose, and are discussed in their own sections within this document. Unless otherwise indicated, the term CIO mode will be used to refer to the generic CIO mode, where any of the three contexts could be running.

The following diagram illustrates how transitions can be made between the major states of the console program using operator commands and special character input. The event (or command) required to cause a transition to a specific state is shown in parenthesis.

# 5.1 FRONT PANEL SWITCHES

The setting of the two front panel switches, combined with the current console mode, control the action of the console program to a variety of external events. The console polls the state of the front panel switches using a dedicated SDB (Serial Diagnostic Bus) control channel.

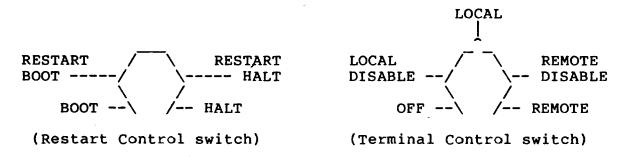

The orientation of the switches on the VAX 8600 front panel is:

### 5.1.1 Terminal Control Switch

The terminal control switch (located as the right-most switch) controls remote (RD) and local (CTY) terminal port access to Console I/O (CIO) mode, and access by the RTY port to software running on the VAX processor. When in the LOCAL DISABLE position (console locked) the console program ignores the setting of the restart control switch

(left-most switch).

There are 5 positions to the terminal control switch, each described in a separate section below.

## 5.1.1.1 OFF Position

In this position the power system is inoperable and the battery backup unit is disabled to the CPU memory arrays (but continues to power the console's Time Of Year logic. When moved from this position the MPS provides +/-12 volt power to the EMM and the module keying circuit. If the keying circuit is satisfied (all modules in their correct slot) then regulator A is enabled, which powers the console and EMM TTL logic.

At this point, the console PROM code begins execution and performs the steps of the PROM CODE INITIALIZATION procedure.

#### 5.1.1.2 LOCAL DISABLE Position

Interpret this position as saying "REMOTE terminal inactivated, ^P DISABLED".

with the terminal control switch in this position during console program initialization the setting of the restart control switch is ignored and the console performs an automatic RESTART BOOT attempt. An automatic restart/boot attempt will also be done in the event of a system power failure or CPU KEEP ALIVE failure.

In CIO mode the console accepts command input from the CTY device only. Remote port access is not allowed and any remote connection established will be disconnected if the terminal control switch is moved to this position.

In PIO mode the console program passes ^P characters entered at the CTY through the the CPU. Remote port access is not allowed and any remote connection established is disconnected if the terminal control switch is moved to this position.

#### 5.1.1.3 LOCAL Position

Interpret this position as saying "REMOTE terminal inactivated, ^P ENABLED".

With the terminal control switch in this position during console program initialization the setting of the restart control switch is used to determine console action to power-up initialization and to CPU KEEP ALIVE failures.

In CIO mode the console accepts command input from the CTY device only. Remote port access is not allowed and any remote connection established will be disconnected if the terminal control switch is moved to this position.

In PIO mode the console program intercepts ^P characters entered at the CTY and exits PIO mode. Remote port access is not allowed and any remote connection established is disconnected if the terminal control switch is moved to this position.

## 5.1.1.4 REMOTE DISABLE Position

Interpret this position as saying "REMOTE terminal activated, but 'P DISABLED".

With the terminal control switch in this position during console program initialization the setting of the restart control switch is used to determine console action to power-up initialization and to CPU KEEP ALIVE failures.

In CIO mode the console accepts command input from the CTY device only. Remote port access is not allowed and any remote connection established will be disconnected if the terminal control switch is moved to this position, or if the console mode changes from PIO to CIO for any reason.

In PIO mode the console program passes ^P characters entered at either the CTY or RTY through to the CPU. Remote port access is allowed as a user terminal to the CPU, independent of the local terminal.

The "Local-Copy" feature, which allows all Rty dialogue to be copied to the Cty, is not enabled automatically by this switch position. See the SET LOCAL-COPY command for a description of how to enable local copy.

## 5.1.1.5 REMOTE Position

Interpret this position as saying "REMOTE terminal activated, ^P ENABLED".

With the terminal control switch in this position during console program initialization the setting of the restart control switch is used to determine console action to power-up initialization and to CPU KEEP ALIVE failures.

In CIO mode RTY access is allowed and the console accepts simultaneous command input from both the CTY and RTY (on a line by line basis). Refer to the REMOTE TERMINAL SUPPORT section for remote port access and operation information.

In PIO mode remote port access is allowed as a user terminal to the CPU, independent of the local terminal. The console intercepts ^P characters and exits PIO mode when encountered from either the CTY or RTY.

The "Local-Copy" feature, which allows all Rty dialogue to be copied to the Cty, is not enabled automatically by this switch position. See the SET LOCAL-COPY command for a description of how to enable local copy.

#### 5.1.2 Restart Control Switch