MindShare Technology Series

# x86 Instruction Set Architecture

Comprehensive 32- and 64-bit Coverage

Tom Shanley | MindShare, Inc.

## x86 Instruction Set Architecture

Comprehensive 32/64-bit Coverage

First Edition

Also by Tom Shanley

7 HSO by Tom Shamey

HEAVEN'S FAVORITE

—A Novel of Genghis Khan—

Book 1, ASCENT: THE RISE OF CHINGGIS KHAN

Book 2, DOMINION: DAWN OF THE MONGOL EMPIRE

#### MINDSHARE TECHNICAL TRAINING

Please visit www.mindshare.com for a complete description of Mind-Share's technical offerings:

- Books

- eBooks

- · eLearning modules

- Public courses

- On-site course

- On-line courses

Intel Core 2 Processor (Penryn) Intel Nehalem Processor Intel Atom Processor AMD Opteron Processor (Barcelona) Intel 32/64-bit x86 Software Architecture AMD 32/64-bit x86 Software Architecture x86 Assembly Language Programming **Protected Mode Programming** PC Virtualization IO Virtualization (IOV) Computer Architectures with Intel Chipsets Intel QuickPath Interconnect (QPI) PCI Express 2.0 **USB 2.0 USB 3.0** Embedded USB 2.0 Workshop PCI PCI-X Modern DRAM Architecture SAS Serial ATA High Speed Design FMI / FMC Bluetooth Wireless Product Development SMT Manufacturing

**SMT Testing**

### x86 Instruction Set Architecture

## Comprehensive 32/64-bit Coverage First Edition

MINDSHARE, INC.

TOM SHANLEY

**MindShare Press**

Colorado Springs, USA

Refer to "Trademarks" on page 5 for trademark information.

The author and publisher have taken care in preparation of this book but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

ISBN: 0-9770878-5-3

Copyright © 2009 by MindShare, Inc.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America.

Cover Design: Michelle Petrie Set in 10 point Palatino by MindShare, Inc.

First Printing, December 2009

MindShare Press books are available for bulk purchases by corporations, institutions, and other organizations. For more information please contact the Special Sales Department at (575)-373-0336.

Find MindShare Press on the World Wide Web at: http://www.mindshare.com/

#### To Nancy, the strongest person I know.

With Love,

Tom

P. S. It's done. I'm back.

# At-a-Glance Table of Contents

**Part 1: Introduction**, intended as a back-drop to the detailed discussions that follow, consists of the following chapters:

- Chapter 1, "Basic Terms and Concepts," on page 11.

- Chapter 2, "Mode/SubMode Introduction," on page 21.

- Chapter 3, "A (very) Brief History," on page 41.

- Chapter 4, "State After Reset," on page 63.

**Part 2: IA-32 Mode** provides a detailed description of two IA-32 Mode submodes—Real Mode and Protected Mode—and consists of the following chapters:

- Chapter 5, "Intro to the IA-32 Ecosystem," on page 79.

- Chapter 6, "Instruction Set Expansion," on page 109.

- Chapter 7, "32-bit Machine Language Instruction Format," on page 155.

- Chapter 8, "Real Mode (8086 Emulation)," on page 227.

- Chapter 9, "Legacy x87 FP Support," on page 339.

- Chapter 10, "Introduction to Multitasking," on page 361.

- Chapter 11, "Multitasking-Related Issues," on page 367.

- Chapter 12, "Summary of the Protection Mechanisms," on page 377.

- Chapter 13, "Protected Mode Memory Addressing," on page 383.

- Chapter 14, "Code, Calls and Privilege Checks," on page 415.

- Chapter 15, "Data and Stack Segments," on page 479.

- Chapter 16, "IA-32 Address Translation Mechanisms," on page 493.

- Chapter 17, "Memory Type Configuration," on page 599.

- Chapter 18, "Task Switching," on page 629.

- Chapter 19, "Protected Mode Interrupts and Exceptions," on page 681.

- Chapter 20, "Virtual 8086 Mode," on page 783.

- $\bullet \quad$  Chapter 21, "The MMX Facilities," on page 835.

- $\bullet \quad$  Chapter 22, "The SSE Facilities," on page 851.

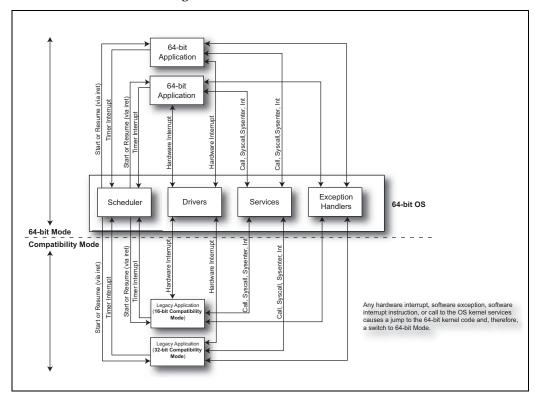

**Part 3: IA-32e OS Kernel Environment** provides a detailed description of the IA-32e OS kernel environment and consists of the following chapters:

- Chapter 23, "IA-32e OS Environment," on page 913.

- Chapter 24, "IA-32e Address Translation," on page 983.

**Part 4: Compatibility Mode** provides a detailed description of the Compatibility submode of IA-32e Mode and consist of the following chapter:

• Chapter 25, "Compatibility Mode," on page 1009.

**Part 5: 64-bit Mode** provides a detailed description of the 64-bit submode of IA-32e Mode and consists of the following chapters:

- Chapter 26, "64-bit Register Overview," on page 1023.

- Chapter 27, "64-bit Operands and Addressing," on page 1041.

- Chapter 28, "64-bit Odds and Ends," on page 1075.

#### **Part 6: Mode Switching Detail** provides a detailed description of:

- Switching from Real Mode to Protected Mode. This topic is covered in Chapter 29, "Transitioning to Protected Mode," on page 1113.

- Switching from Protected Mode to IA-32e Mode. This topic is covered in Chapter 30, "Transitioning to IA-32e Mode," on page 1139.

#### **Part 7: Other Topics** provides detailed descriptions of the following topics:

- Chapter 31, "Introduction to Virtualization Technology," on page 1147.

- Chapter 32, "System Management Mode (SMM)," on page 1167.

- Chapter 33, "Machine Check Architecture (MCA)," on page 1207.

- Chapter 34, "The Local and IO APICs," on page 1239.

| About This Book                                                     |          |

|---------------------------------------------------------------------|----------|

| Is This the Book for You?                                           | 1        |

| A Moving Target                                                     |          |

| x86 Instruction Set Architecture (ISA)                              |          |

| Glossary of Terms                                                   |          |

| 32-/64-bit x86 Instruction Set Architecture Specification           | 2        |

| The Specification Is the Final Word                                 |          |

| Book Organization                                                   | 3        |

| Topics Outside the Scope of This Book                               | 4        |

| The CPUID Instruction                                               | 4        |

| Detailed Description of Hyper-Threading                             | 4        |

| Detailed Description of Performance Monitoring                      | 5        |

| Documentation Conventions                                           | 5        |

| Trademarks                                                          | 5        |

| Visit Our Web Site                                                  | 6        |

| We Want Your Feedback                                               | 7        |

| Part 1: Introduction  Chapter 1: Basic Terms and Concepts           |          |

| ISA Definition                                                      |          |

| This Book Focuses on the Common Intel/AMD ISA                       |          |

| For Simplicity, Intel Terminology Is Used Throughout                | 11<br>10 |

| Some Terms in This Chapter May Be New To the Reader                 |          |

| Two x86 ISA Architectures  Processors, Cores and Logical Processors |          |

| Fundamental Processing Engine: Logical Processor                    |          |

| IA Instructions vs. Micro-ops                                       |          |

| RISC Instructions Sets Are Simple                                   |          |

| x86 Instruction Set Is Complex                                      |          |

| But You Can't Leave It Behind                                       |          |

| Complexity vs. Speed Dictated a Break With the Past                 |          |

| Why Not Publish a Micro-Op ISA?                                     |          |

| Some Important Definitions                                          |          |

| Virtual vs. Physical Memory                                         |          |

| Other Important Terms                                               |          |

| r                                                                   |          |

| Chapter 2: Mode/SubMode Introduction                                |          |

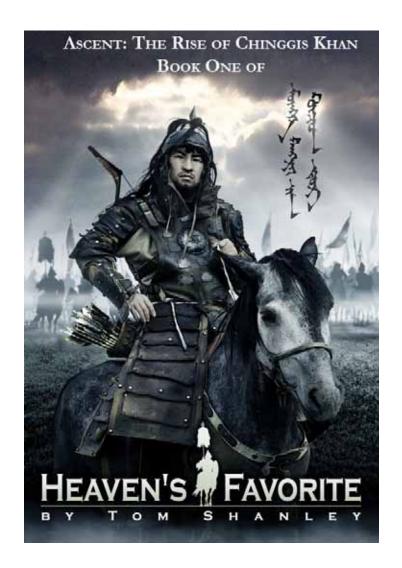

| Basic Execution Modes                                               | 21       |

| IA-32 SubModes                                   | 25 |

|--------------------------------------------------|----|

| IA-32e SubModes                                  | 28 |

| Mode Switching Basics                            | 30 |

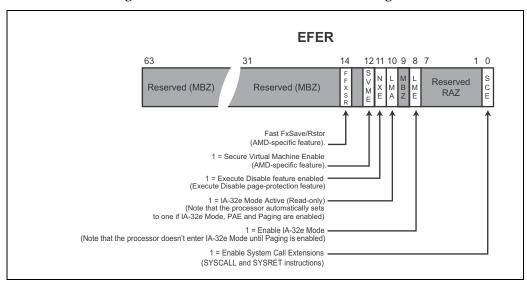

| Initial Switch from IA-32 to IA-32e Mode         | 30 |

| IA-32e SubMode Selection                         | 33 |

| Protected/Compatibility 16-/32-bit SubModes      | 38 |

| Chapter 3: A (very) Brief History                |    |

| Major Evolutionary Developments                  | 42 |

| 16-bit Mode Background                           | 46 |

| 8086 and Real Mode                               |    |

| 286 Introduced 16-bit Protected Mode             | 48 |

| 386 Supported Both 16- and 32-bit Protected Mode |    |

| The Intel Microarchitecture Families             |    |

| A Brief Timeline                                 |    |

|                                                  |    |

| <b>Chapter 4: State After Reset</b>              |    |

| State After Reset                                | 64 |

| Soft Reset                                       |    |

| Boot Strap Processor (BSP) Selection             |    |

| AP Discovery and Configuration                   |    |

| Initial Memory Reads                             |    |

|                                                  |    |

| Part 2: IA-32 Mode                               |    |

| Chapter 5: Intro to the IA-32 Ecosystem          |    |

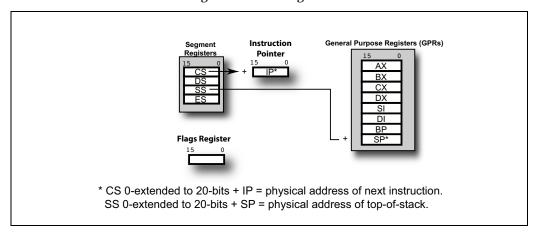

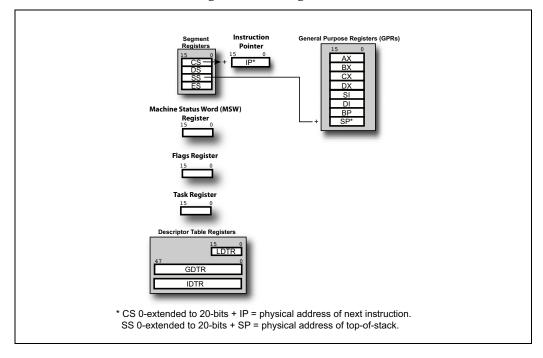

| The Pre-386 Register Sets                        | 80 |

| 8086 Register Set                                |    |

| 286 Register Set                                 |    |

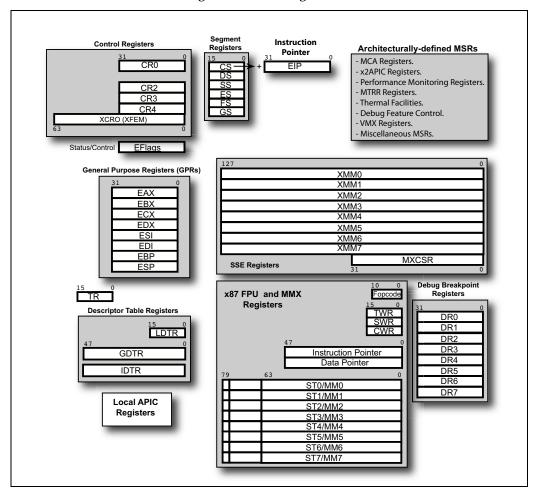

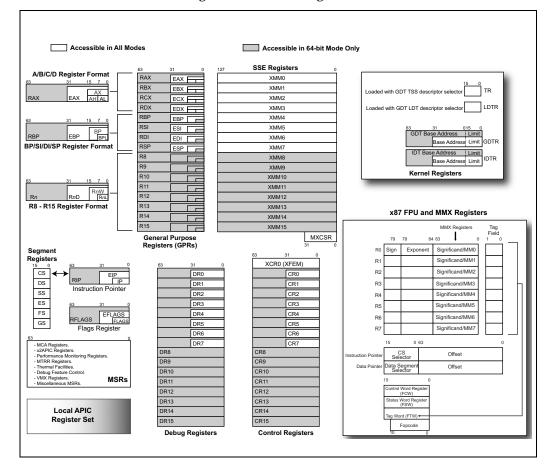

| IA-32 Register Set Overview                      |    |

| Control Registers                                |    |

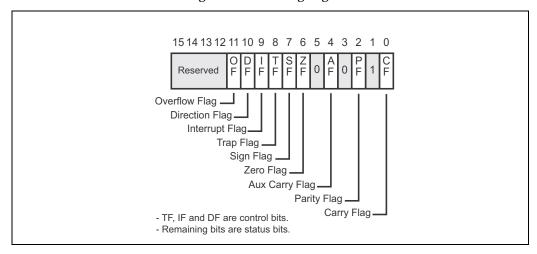

| Status/Control Register (Eflags)                 |    |

| Instruction Fetch Facilities                     |    |

| General                                          |    |

| Branch Prediction Logic                          |    |

| General Purpose Data Registers                   |    |

| Defining Memory Regions/Characteristics          | 92 |

| MTRRs                                            |    |

| Segment Registers                                |    |

| Address Translation Facilities                   |    |

|                                                  |    |

| Interrupt/Exception Facilities                             | 93  |

|------------------------------------------------------------|-----|

| Kernel Facilities                                          |     |

| Real Mode Has No Memory Protection                         | 95  |

| Memory Protection in Protected Mode                        | 95  |

| Introduction                                               | 95  |

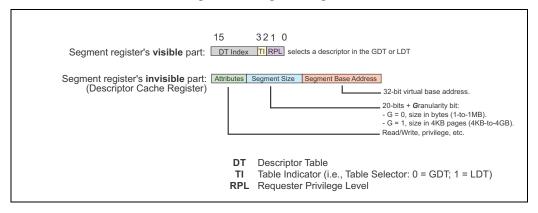

| Segment Selection in Protected Mode                        | 95  |

| Access Rights Check                                        | 96  |

| The Descriptor Tables                                      | 96  |

| Descriptor Table Registers                                 | 96  |

| Task Data Structure                                        |     |

| Address Translation Facilities                             | 97  |

| Effective/Virtual/Linear/Physical Addresses                | 97  |

| Introduction to Address Translation (Paging)               | 98  |

| RAM Is Finite and Can't Hold Everything                    | 98  |

| RAM and Mass Storage Are Managed on a Page Basis           | 99  |

| This Requires a Series of Directories                      | 99  |

| Malloc Request                                             | 99  |

| Problem: Non-Contiguous Memory Allocation                  | 100 |

| Malloc Returns a Virtual Address to the Application        | 100 |

| IA-32 Applications Have a 4GB Virtual Address Space        | 101 |

| Legacy FP Facilities                                       |     |

| In the Beginning, FPU Was External and Optional            | 101 |

| It Was Slow                                                | 102 |

| 486DX Integrated It                                        | 102 |

| x87 Register Set                                           | 102 |

| x87 FP Instruction Set                                     |     |

| General Purpose Instruction Set                            | 102 |

| MMX Facilities                                             | 102 |

| Introduction                                               |     |

| SIMD Programming Model                                     | 103 |

| SSE Facilities                                             | 104 |

| Introduction                                               | 104 |

| Motivation                                                 | 104 |

| Instruction Set                                            | 105 |

| Model-Specific Registers                                   | 105 |

| General                                                    |     |

| Accessing the MSRs                                         | 106 |

| Debug Facilities                                           |     |

| Automatic Task Switching Mechanism                         |     |

|                                                            |     |

| Chapter 6: Instruction Set Expansion                       |     |

| <u> </u>                                                   | 110 |

| Why a Comprehensive Instruction Set Listing Isn't Included | 110 |

| 386 Instruction Set                                    | 111<br>117 |

|--------------------------------------------------------|------------|

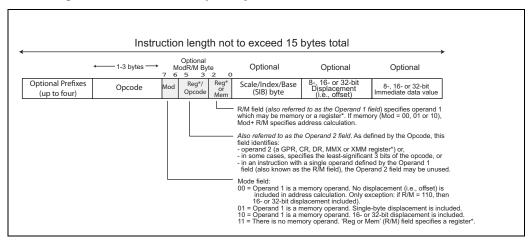

| Chapter 7: 32-bit Machine Language Instruction Form    | nat        |

| 64-bit Machine Language Instruction Format             |            |

| A Complex Instruction Set with Roots in the Past       | 130<br>150 |

| Effective Operand Size                                 |            |

| Introduction                                           |            |

| Operand Size in 16- and 32-bit Code Segments           |            |

| Operand Size in 64-bit Code Segments                   |            |

| Instruction Composition                                |            |

| Instruction Format Basics                              |            |

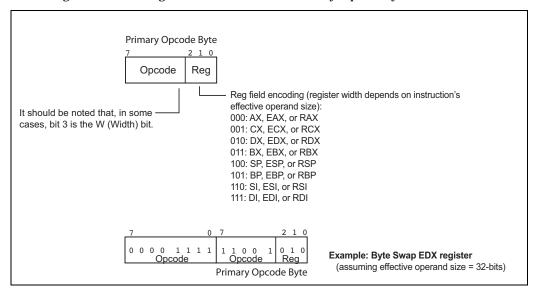

| Opcode (Instruction Identification)                    |            |

| In the Beginning                                       |            |

| 1-byte Opcodes                                         |            |

| 2-byte Opcodes Use 2-Level Lookup                      |            |

| 2nd-Level Opcode Map Introduced in 286                 |            |

| Instructions with 2-byte Opcodes: Five Possible Forms  |            |

| 3-byte Opcodes Use 3-Level Lookup                      |            |

| 3-Level Opcode Maps Introduced in Pentium 4 Prescott   |            |

| Currently There Are Two 3rd-Level Maps Defined         |            |

| Instructions with 3-byte Opcodes: Three Possible Forms |            |

| Special Use of Prefix Bytes                            |            |

| Opcode Micro-Maps (Groups)                             |            |

| Micro-Maps Associated with 1-byte Opcodes              |            |

| Some Opcodes Employ 2 x 8 Micro-Maps                   | 180        |

| Micro-Maps Associated with 2-byte Opcodes              |            |

| 3-byte Opcodes Don't Use Micro-Maps                    | 187        |

| x87 FP Opcodes Inhabit Opcode Mini-Maps                |            |

| Special Opcode Fields                                  |            |

| Operand Identification                                 |            |

| General                                                |            |

| Specifying Registers as Operands                       |            |

| Implicit Register Specification                        |            |

| Explicit Register Specification in Opcode              |            |

| Explicit Register Specification in ModRM Byte          |            |

| Addressing a Memory-Based Operand                      |            |

| Instruction Can Specify Only One Memory-Based Operand  |            |

| Addressing Memory Using the ModRM Byte                 |            |

| When Effective Address Size = 16-Bits                  |            |

| When Effective Address Size = 32-Bits                  |            |

| Using the SIB Byte to Access a Data Structure          | 203        |

| Near and Far Branch Target Addressing                    |     |

|----------------------------------------------------------|-----|

| Specifying an Immediate Value As an Operand              |     |

| Instruction Prefixes                                     |     |

| Operand Size Override Prefix (66h)                       |     |

| In 32-bit Mode                                           |     |

| In 16-bit Mode                                           |     |

| Special Usage of 66h Prefix                              |     |

| Address Size Override Prefix (67h)                       |     |

| In 32-Bit Mode                                           |     |

| In 16-Bit Mode                                           |     |

| Lock Prefix                                              |     |

| Shared Resource Concept                                  |     |

| Race Condition Can Present Problem                       |     |

| Guaranteeing Atomicity of Read/Modify/Write              |     |

| Use Locked RMW to Obtain and Give Up Semaphore Ownership |     |

| Instructions That Accept Lock Prefix                     | 218 |

| Repeat Prefixes                                          |     |

| Normal Usage                                             | 218 |

| Special Usage                                            | 220 |

| Segment Override Prefix                                  | 220 |

| General                                                  | 220 |

| Usage In String Operations                               |     |

| Segment Override Use With MMX and SSE1 - 4 Instructions  | 221 |

| Branch Hint Prefix                                       |     |

| Summary of Instruction Set Formats                       | 222 |

|                                                          |     |

| Chapter 8: Real Mode (8086 Emulation)                    |     |

| 8086 Emulation                                           | 229 |

| Unused Facilities                                        | 231 |

| Real Mode OS Environment                                 | 232 |

| Single-Task OS Environment Overview                      | 232 |

| Command Line Interface (CLI)                             | 232 |

| Program Loader                                           | 233 |

| OS Services                                              | 233 |

| Direct IO Access                                         | 234 |

| Application Memory Usage                                 | 234 |

| Task Initiation, Execution and Termination               | 234 |

| Running Real Mode Applications Under a Protected Mode OS |     |

| Real Mode Applications Aren't Supported in IA-32e Mode   |     |

| Real Mode Register Set                                   | 235 |

| Introduction                                             | 235 |

|                                                          |     |

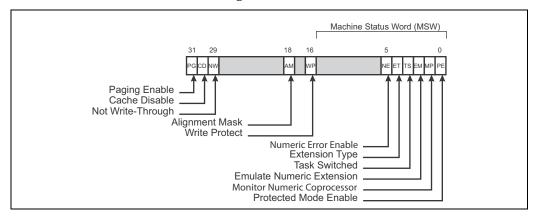

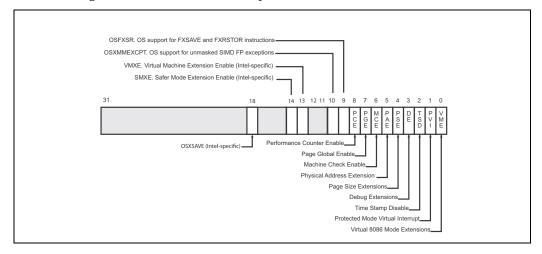

| Control Registers                                   | 237 |

|-----------------------------------------------------|-----|

| CR0                                                 | 238 |

| Address Translation (Paging) Control Registers      | 243 |

| CR2                                                 |     |

| CR3                                                 | 243 |

| CR4 (Feature Control Register)                      | 244 |

| XCR0 (XFEM)                                         | 249 |

| Flags Register                                      | 251 |

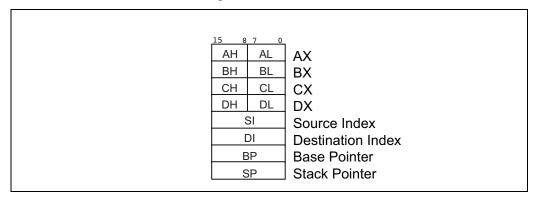

| General Purpose Registers (GPRs)                    | 255 |

| A, B, C and D Registers                             | 255 |

| General Usage                                       | 255 |

| Special Usage Examples                              |     |

| EBP Register: Stack Frame Address Register          | 256 |

| Index Registers                                     | 258 |

| Stack Pointer (SP) Register                         | 259 |

| Instruction Pointer Register                        | 259 |

| Kernel Registers                                    | 260 |

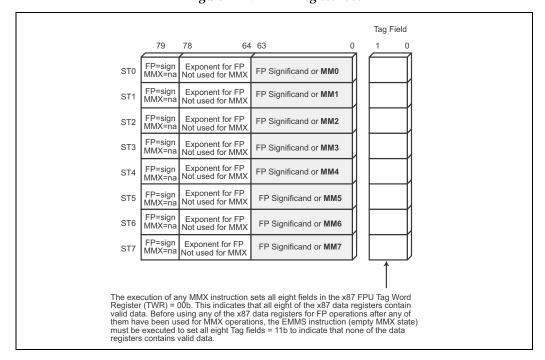

| x87/MMX FPU Register Set                            | 260 |

| SSE Register Set                                    | 262 |

| Debug Address Breakpoint Register Set               | 262 |

| General                                             |     |

| Defining Trigger Address Range                      | 263 |

| Defining Access Type                                |     |

| Defining Scope (Current Task or All Tasks)          | 264 |

| Special Notes                                       | 264 |

| Local APIC Register Set                             | 269 |

| Architecturally-Defined MSRs                        | 272 |

| General                                             | 272 |

| Determining MSR Support                             |     |

| Accessing the MSRs                                  | 272 |

| IO Space versus Memory Space                        |     |

| IO Operations                                       | 281 |

| IO Operations in IO Address Space                   |     |

| IN and OUT Instructions                             |     |

| Block (String) IO Operations                        |     |

| Block Transfer from IO Port to Memory               |     |

| Block Transfer from Memory to an IO Port            |     |

| IO Space is Limited and Crowded                     |     |

| Memory-Mapped IO (MMIO) Operations                  |     |

| Introduction                                        |     |

| Know the Characteristics of Your Target             |     |

| Why the Logical Processor Must Know the Memory Type | 284 |

| Uncacheable (UC) Memory                          | 285 |

|--------------------------------------------------|-----|

| No IO Protection                                 |     |

| Operand Size Selection                           | 286 |

| Address Size Selection                           |     |

| Real Mode Memory Addressing                      | 288 |

| No Address Translation                           |     |

| Introduction to Real Mode Segmentation           | 288 |

| All Segments are 64KB in Size                    | 292 |

| Memory Address Representation                    | 293 |

| Accessing the Code Segment                       |     |

| Jumping Between Code Segments                    | 294 |

| Far Jumps and Calls                              | 294 |

| Near Jumps and Calls                             | 295 |

| IP-Relative Branches                             |     |

| Operations That Default to the Code Segment      | 296 |

| Accessing the Stack Segment                      | 297 |

| Introduction                                     | 297 |

| Stack Characteristics                            | 298 |

| Pushing Data Onto the Stack                      | 298 |

| Popping Data From the Stack                      | 300 |

| Stack Underflow/Overflow                         | 300 |

| Processor Stack Usage                            | 301 |

| Accessing Parameters Passed on the Stack         | 301 |

| Operations That Default To the Stack Segment     | 302 |

| Accessing the DS Data Segment                    | 303 |

| General                                          | 303 |

| Operations That Default to the DS Data Segment   | 303 |

| Accessing the ES/FS/GS Data Segments             | 304 |

| General                                          | 304 |

| Operations That Default to the ES Data Segment   | 305 |

| Segment Override Prefixes                        |     |

| Example Segment Register Initialization          |     |

| Accessing Extended Memory in Real Mode           |     |

| Big Real Mode                                    | 310 |

| 286 DOS Extender Programs                        |     |

| Hot Reset and 286 DOS Extender Programs          |     |

| Alternate (Fast) Hot Reset                       |     |

| 286 DOS Extenders on Post-286 Processors         |     |

| String Operations                                |     |

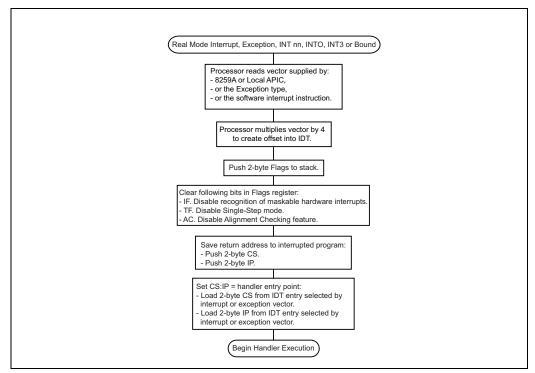

| Real Mode Interrupt/Exception Handling           |     |

| Events and Event Handlers                        |     |

| Events Are Recognized on an Instruction Boundary | 317 |

| The IDT                                           |     |

|---------------------------------------------------|-----|

| Definition of the IDT                             | 317 |

| IDT and IDTR Initialization                       | 324 |

| Stack Initialization                              | 325 |

| Event (Interrupt and Exception) Handling          |     |

| Software Event Types                              | 327 |

| Introduction                                      |     |

| Software Exceptions                               |     |

| Definition of an Exception                        | 328 |

| Exception Handling                                |     |

| Three Categories of Software Exceptions           |     |

| Software Interrupt Instructions                   | 330 |

| INT nn Instruction                                | 330 |

| BOUND Instruction                                 |     |

| INTO Instruction                                  | 331 |

| INT3 (Breakpoint) Instruction                     |     |

| Hardware Event Types                              | 332 |

| NMI                                               |     |

| Definition of NMI and Delivery Mechanisms         |     |

| External NMI Masking Mechanism                    |     |

| NMI Handling                                      | 333 |

| SMI                                               | 334 |

| Maskable Interrupts                               |     |

| Maskable Interrupts Are Originated by Devices     |     |

| Enabling/Disabling Maskable Interrupt Recognition |     |

| Selective Masking of Maskable Interrupts          | 335 |

| Maskable Interrupt Delivery Mechanisms            | 335 |

| IDT Entries Associated with Maskable Interrupts   | 335 |

| Handling Maskable Interrupts                      | 335 |

| Machine Check Exception                           | 336 |

| Summary of Real Mode Limitations                  | 337 |

| Transitioning to Protected Mode                   | 337 |

| Chapter 9: Legacy x87 FP Support                  |     |

| A Little History                                  | 340 |

| x87 FP Instruction Format                         | 341 |

| FPU-Related CR0 Bit Fields                        |     |

| x87 FPU Register Set                              |     |

| The FP Data Registers                             |     |

| x87 FPU's Native Data Operand Format              |     |

| 32-bit SP FP Numeric Format                       |     |

| Background                                        |     |

| Ducksi vana                                       | ,   |

| A Brief IEEE FP Primer                        |     |

|-----------------------------------------------|-----|

| The 32-bit SP FP Format                       | 347 |

| Representing Special Values                   | 348 |

| An Example                                    | 348 |

| Another Example                               | 349 |

| DP FP Number Representation                   | 350 |

| FCW Register                                  | 350 |

| FSW Register                                  | 352 |

| FTW Register                                  | 355 |

| Instruction Pointer Register                  |     |

| Data Pointer Register                         | 355 |

| Fopcode Register                              | 356 |

| General                                       |     |

| Fopcode Compatibility Mode                    | 356 |

| FP Error Reporting                            |     |

| Precise Error Reporting                       | 357 |

| Imprecise (Deferred) Error Reporting          |     |

| Why Deferred Error Reporting Is Used          | 358 |

| The WAIT/FWAIT Instruction                    | 358 |

| CR0[NE]                                       |     |

| DOS-Compatible FP Error Reporting             |     |

| FP Error Reporting Via Exception 16           | 359 |

| Ignoring FP Errors                            | 360 |

| Chapter 10: Introduction to Multitasking      |     |

| Concept                                       | 363 |

| An Example—Timeslicing                        |     |

| Another Example—Awaiting an Event             | 364 |

| 1. Task Issues Call to OS for Disk Read       |     |

| 2. Device Driver Initiates Disk Read          |     |

| 3. OS Suspends Task                           |     |

| 4. OS Makes Entry in Event Queue              |     |

| 5. OS Starts or Resumes Another Task          |     |

| 6. Disk-Generated Interrupt Causes Jump to OS |     |

| 7. Interrupted Task Suspended                 |     |

| 8. Task Queue Checked                         |     |

| 9. OS Resumes Task                            |     |

| Chapter 11: Multitasking-Related Issues       |     |

| Hardware-based Task Switching Is Slow!        | ያልያ |

| Private (Local) and Global Memory             |     |

| i iivate (Locai) aliu Giobai wiellioi y       |     |

| Preventing Unauthorized Use of OS Code                         | 369 |

|----------------------------------------------------------------|-----|

| With Privilege Comes Access                                    |     |

| Program Privilege Level                                        | 370 |

| The CPL                                                        | 370 |

| Calling One of Your Equals                                     | 371 |

| Calling a Procedure to Act as Your Surrogate                   | 371 |

| Data Segment Protection                                        |     |

| Data Segment Privilege Level                                   |     |

| Read-Only Data Areas                                           |     |

| Some Code Segments Contain Data, Others Don't                  | 372 |

| IO Port Anarchy                                                |     |

| No Interrupts, Please!                                         |     |

| BIOS Calls                                                     | 376 |

| Chapter 12: Summary of the Protection Mechanisms               |     |

| Protection-Related Mechanisms                                  | 378 |

| Chapter 13: Protected Mode Memory Addressing                   |     |

| Real Mode Segment Limitations                                  | 384 |

| An Important Reminder: Segment Base + Offset = Virtual Address |     |

| Descriptor Contains Detailed Segment Description               |     |

| Segment Register—Selects Descriptor Table and Entry            |     |

| Introduction to the Descriptor Tables                          |     |

| Segment Descriptors Reside in Memory                           |     |

| Global Descriptor Table (GDT)                                  |     |

| GDT Description                                                |     |

| Setting the GDT Base Address and Size                          |     |

| GDT Entry 0                                                    |     |

| Local Descriptor Tables (LDTs)                                 |     |

| General                                                        | 395 |

| Creating and Selecting an LDT                                  | 396 |

| General Segment Descriptor Format                              |     |

| Granularity Bit and the Segment Size                           |     |

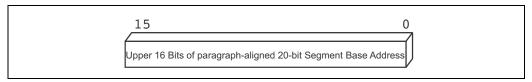

| Segment Base Address Field                                     |     |

| Default/Big Bit                                                |     |

| In a Code Segment Descriptor, D/B = "Default" Bit              | 400 |

| Override Prefixes                                              |     |

| In a Stack Segment Descriptor, D/B = "Big" Bit                 | 402 |

| Segment Type Field                                             | 403 |

| Introduction to the Type Field                                 | 403 |

| Non-System Segment Types                                       |     |

| Segment Present Bit                                 |     |

|-----------------------------------------------------|-----|

| Descriptor Privilege Level (DPL) Field              | 406 |

| System Bit                                          | 407 |

| Available Bit                                       | 408 |

| Goodbye to Segmentation                             |     |

| Introduction                                        |     |

| IA-32 Flat Memory Model                             |     |

| No Protection? Paging Takes Care of It              |     |

| A Reminder of Where We Are                          | 412 |

| <b>Chapter 14: Code, Calls and Privilege Checks</b> |     |

| Abbreviation Alert                                  | 416 |

| Selecting the Active Code Segment                   |     |

| CS Descriptor                                       |     |

| CS Descriptor Selector                              |     |

| Calculating the Descriptor's Memory Address         | 419 |

| Descriptor Read and Privilege Checked               |     |

| CS Descriptor Format                                |     |

| Accessing the Code Segment                          | 423 |

| In-Line Code Fetching                               | 423 |

| Short and Near Branches (Jumps and Calls)           | 423 |

| General                                             | 423 |

| Example Near Jump                                   |     |

| Far Branches (Far Jumps and Calls)                  | 424 |

| General                                             | 424 |

| Example Far Jump                                    | 425 |

| Short/Near Jumps                                    | 427 |

| General                                             | 427 |

| No Privilege Check                                  | 427 |

| Unconditional Short/Near Branches                   |     |

| Conditional Branches                                |     |

| General                                             | 428 |

| Loop Instructions                                   |     |

| Unconditional Far Jumps                             |     |

| The Privilege Check                                 |     |

| Far Jump Targets                                    |     |

| Far Jump Forms                                      |     |

| Privilege Checking                                  |     |

| No Check on Near Calls or Near Jumps                |     |

| General                                             |     |

| Definitions                                         |     |

| Definition of a Task                                | 437 |

| Definition of a Procedure                          | 437 |

|----------------------------------------------------|-----|

| CPL Definition                                     | 437 |

| CS DPL Definition                                  |     |

| Conforming and Non-Conforming Code Segments        | 438 |

| Definition                                         |     |

| Examples                                           | 438 |

| RPL Definition                                     | 439 |

| General                                            | 439 |

| RPL Usage in Privilege Check                       | 439 |

| RPL Use on RET or IRET                             | 440 |

| Privilege Check on Far Call or Far Jmp             | 440 |

| General                                            | 440 |

| Example                                            | 440 |

| Jumping from a Higher-to-Lesser Privileged Program |     |

| Direct Procedure Calls                             | 442 |

| Introduction                                       | 442 |

| General                                            | 442 |

| Near Calls/Returns                                 | 443 |

| Description                                        | 443 |

| Call/Ret Operand Size Matching                     | 445 |

| Near Call/Return Forms                             | 445 |

| Far Calls                                          | 447 |

| General                                            | 447 |

| Far Call Forms                                     | 447 |

| Far Call, Same Privilege Level                     | 451 |

| Far Call to a More-Privileged Procedure            |     |

| Far Call to a Procedure in a Different Task        | 452 |

| Indirect Procedure Far Call Through a Call Gate    | 452 |

| Example Scenario Defines the Problem               | 452 |

| The Scenario                                       | 452 |

| The Problem                                        | 453 |

| The Solution—Different Gateways                    | 454 |

| The Call Gate Descriptor                           |     |

| Call Gate Example                                  | 456 |

| Execution Begins                                   | 456 |

| Call Gate Descriptor Read                          | 457 |

| Call Gate Contains Target Code Segment Selector    |     |

| Target Code Segment Descriptor Read                |     |

| The Big Picture                                    |     |

| The Call Gate Privilege Check                      |     |

| Automatic Stack Switch                             |     |

| Background                                         | 462 |

| A Potential Problem  The Solution: Pre-Allocated Stacks  Far Call From 32-bit CS to 16-bit CS  General |     |

|--------------------------------------------------------------------------------------------------------|-----|

|                                                                                                        | 462 |

|                                                                                                        | 466 |

|                                                                                                        |     |

|                                                                                                        | 466 |

|                                                                                                        |     |

|                                                                                                        | 470 |

| Far Call From 16-bit CS to 32-bit CS                                                                   |     |

| Method 1: Far Call With an Operand Size Prefix                                                         | 472 |

| Method 2: Far Call Via a 32-bit Call Gate                                                              |     |

| Far Returns                                                                                            | 475 |

| General                                                                                                |     |

| Far Return Forms                                                                                       | 476 |

| Chapter 15: Data and Stack Segments                                                                    |     |

| A Note Regarding Stack Segments                                                                        | 480 |

| Data Segments                                                                                          |     |

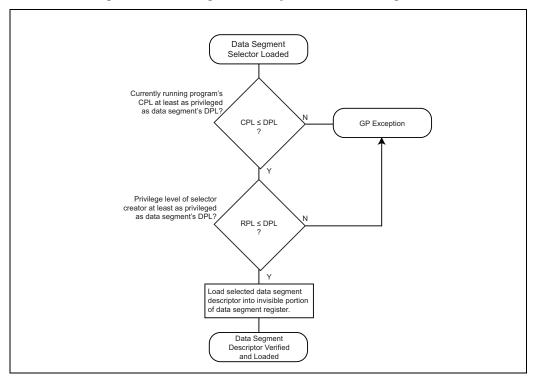

| General Two-Step Permission Check An Example Selecting and Accessing a Stack Segment Introduction      |     |

|                                                                                                        |     |

|                                                                                                        | 482 |

|                                                                                                        |     |

|                                                                                                        |     |

| Expand-Up Stack                                                                                        |     |

| Expand-Down Stack                                                                                      |     |

| The Problem                                                                                            |     |

| Expand-Down Stack Description                                                                          |     |

| An Example                                                                                             |     |

| Another Example                                                                                        | 491 |

| <b>Chapter 16: IA-32 Address Translation Mechanism</b>                                                 | ıs  |

| Three Generations                                                                                      |     |

| Demand Mode Paging Evolution                                                                           | 495 |

| Background                                                                                             | 496 |

| Memory and Disk: Block-Oriented Devices                                                                |     |

| Definition of a Page                                                                                   |     |

| Example Scenario: Block Transfer from Disk to Memory                                                   |     |

| A Poor Memory Allocation Strategy                                                                      |     |

| Applications Are Presented With a Simplified World-View                                                |     |

| Introduction                                                                                           |     |

| Life Without Paging Would Be Chaotic                                                                   |     |

| The Virtual World Is a Simple One                                                                      | 500 |

| Virtual Address Space Partitioning                       | 506 |

|----------------------------------------------------------|-----|

| Example Virtual Buffer Allocation                        | 508 |

| Address Translation Advantages                           | 509 |

| Introduction                                             | 509 |

| Simplifies Memory Management                             | 509 |

| Efficient Memory Usage                                   | 510 |

| A Wasteful Approach                                      | 510 |

| A Better Approach: Load On Demand                        |     |

| Attribute Assignment                                     | 511 |

| Track Access History                                     |     |

| Allows DOS Applications to Co-Exist                      |     |

| Problem: Running Multiple DOS Programs                   | 512 |

| Solution: Address Redirection                            | 512 |

| First-Generation Paging                                  |     |

| Definition of First Generation Paging                    |     |

| Paging Logic's Interpretation of a Virtual Address       |     |

| First-Generation Paging Overview                         |     |

| The Set-Up                                               |     |

| Virtual-to-Physical Address Translation                  |     |

| The Goal                                                 |     |

| The Translation                                          | 516 |

| Two Overhead Memory Reads Take a Toll                    |     |

| The TLBs                                                 |     |

| TLB Miss                                                 |     |

| TLB Hit                                                  |     |

| TLB Maintenance                                          |     |

| TLBs Are Cleared on Task Switch or Page Directory Change | 525 |

| Updating a Single Page Table Entry                       |     |

| Global Pages                                             |     |

| Problem                                                  |     |

| Global Page Feature                                      |     |

| Enabling Paging                                          |     |

| Detailed Description of PDE and PTE                      | 529 |

| PDE Layout                                               |     |

| PTE Layout                                               |     |

| Checking Page Access Permission                          |     |

| The Privilege Check                                      |     |

| Segment Privilege Check Takes Precedence Over Page Check |     |

| U/S Bit in PDE and PTE Are Checked                       |     |

| Accesses with Special Privilege                          |     |

| The Read/Write Check                                     |     |

| Missing Page or Page Table                               | 538        |

|----------------------------------------------------------|------------|

| Introduction                                             |            |

| Page Table Not Present                                   | 538        |

| Page Not Present                                         | 542        |

| Page Faults                                              | 545        |

| Page Fault Causes                                        |            |

| Page Fault During a Task Switch                          |            |

| Page Fault while Changing to a Different Stack           |            |

| Page Fault Error Code                                    |            |

| Additional Page Fault Information                        |            |

| Access History                                           | <b>548</b> |

| 4MB Pages                                                |            |

| Basic Concept                                            |            |

| Enabling the PSE Feature                                 | 550        |

| Simplifies Housekeeping                                  |            |

| How To Set Up a 4MB Page                                 |            |

| The Address Translation                                  | 552        |

| Second-Generation Paging                                 |            |

| First-Gen Problem: 4GB Physical Memory                   | 553        |

| The Solution: PAE-36 Mode                                |            |

| Enabling PAE-36 Mode                                     |            |

| CR4[PSE] Is "Don't Care"                                 |            |

| Application Still Limited to a 4GB Virtual Address Space |            |

| Virtual Address Space Partitioning                       |            |

| First Generation Partitioning                            |            |

| Second Generation Partitioning                           |            |

| Second Generation Uses 3-Level Lookup Mechanism          |            |

| CR3 Points to PDPT in Lower 4GB                          |            |

| Enlarged Physical Address Space                          |            |

| The Translation                                          |            |

| Step 1: PDPT Lookup                                      |            |

| Step 2: Page Directory Lookup                            |            |

| Step 2a: PDE Points to a Page Table                      |            |

| Step 2b: PDE Points to a 2MB Physical Page               |            |

| Step 3: Page Table Lookup                                |            |

| Page Protection Mechanisms                               |            |

| General                                                  |            |

| Write-Protection                                         |            |

| Example Usage: Unix Copy-on-Write Strategy               |            |

| 3-Level Lookup—Increased TLB Size                        |            |

| Microsoft PAE Support                                    |            |

| Linux PAE Support                                        | 574        |

| PSE-36 Mode (PAE-36 Mode's Poor Cousin)                   | 574         |

|-----------------------------------------------------------|-------------|

| PSE-36 Mode Background                                    |             |

| Detecting PSE-36 Mode Capability                          |             |

| Enabling PSE-36 Mode                                      |             |

| Per Application Virtual Memory Space = 4GB                |             |

| First-Generation Lookup Mechanism                         |             |

| Selected PDE Can Point to 4KB Page Table or a 4MB Page    | 576         |

| Virtual Address Maps to a 4MB Page in 64GB Space          | 577         |

| Windows and PSE-36                                        |             |

| AMD Enhanced PSE-36 to PSE-40                             | 579         |

| Execute Disable Feature                                   | 579         |

| Problem: Malicious Code                                   | 579         |

| The Overflow                                              | 579         |

| The Exploit                                               | 581         |

| The Fix: Intercept Code Fetches from Data Pages           |             |

| Enabling the Execute-Disable Feature                      |             |

| Available in both IA-32 and IA-32e Mode                   |             |

| How It Works                                              |             |

| Defining a Page's Caching Rules                           | <b>58</b> 5 |

| Introduction                                              |             |

| Translation Table Caching Rules                           | 585         |

| General                                                   |             |

| First-Generation Paging Tables                            | 586         |

| Second-Generation Paging Tables                           |             |

| Page Caching Rules                                        |             |

| PAT Feature (Page Attribute Table)                        |             |

| What's the Problem?                                       |             |

| Detecting PAT Support                                     |             |

| PAT Allows More Memory Types                              |             |

| Default Contents of IA32_CR_PAT MSR                       |             |

| Memory Type When Page Definition and MTRR Disagree        |             |

| General                                                   |             |

| The UC- Memory Type                                       |             |

| Altering IA32_CR_PAT MSR                                  |             |

| Ensuring IA32_CR_PAT and MTRR Consistency                 |             |

| Assigning Multiple Memory Types to a Single Physical Page |             |

| Compatibility with Earlier IA-32 Processors               |             |

| Third Generation Paging                                   |             |

|                                                           |             |

| <b>Chapter 17: Memory Type Configuration</b>              |             |

| Characteristics of Memory Targets                         | enn         |

| v o                                                       |             |

| Introduction                                              | 600         |

| Example Problem: Caching from MMIO               |     |

|--------------------------------------------------|-----|

| Early Processors Implemented Primitive Mechanism | 601 |

| Solution/Problem: Chipset Memory Type Registers  | 602 |

| Solution: Memory Type Register Set               | 602 |

| MTRR Feature Determination                       | 603 |

| MTRRs Are Divided Into Four Categories           | 604 |

| MTRRDefType Register                             | 604 |

| State of the MTRRs after Reset                   | 605 |

| Fixed-Range MTRRs                                | 605 |

| The Problem: Legacy Issues                       | 605 |

| Enabling the Fixed-Range MTRRs                   |     |

| Defining Memory Types in Lower 1MB               | 606 |

| Variable-Range MTRRs                             | 607 |

| How Many Variable-Range Register Pairs?          | 607 |

| Variable-Range Register Pair Format              | 607 |

| MTRRPhysBasen Register                           | 608 |

| MTRRPhysMaskn Register                           |     |

| Programming Variable-Range Register Pairs        | 609 |

| Enabling Variable-Range Register Pairs           | 609 |

| Memory Types                                     |     |

| Memory Type Defines Processor Aggressiveness     | 609 |

| Five Memory Types                                |     |

| Uncacheable (UC) Memory                          |     |

| Uncacheable Write-Combining (WC) Memory          | 611 |

| Description                                      |     |

| Weakly-Ordered Writes                            | 612 |

| Cacheable Write-Protect (WP) Memory              |     |

| Cacheable Write-Through (WT) Memory              |     |

| Cacheable Write-Back (WB) Memory                 |     |

| The Definition of a Speculatively Executed Load  |     |

| Rules as Defined by MTRRs                        | 616 |

| Memory Type Provided in Memory Transaction       |     |

| Paging Also Defines Memory Type                  | 617 |

| In an MP System, MTRRs Must Be Synchronized      |     |

| Posted-Write Related Issues                      |     |

| General                                          |     |

| Synchronizing Events                             |     |

| PMWB and WCBs Aren't Snooped                     |     |

| WCB Usage                                        |     |

| An Example                                       |     |

| All WCBs in Use                                  | 627 |

| Draining the WCBs                                | 628 |

| Chapter 18: Task Switching                             |     |

|--------------------------------------------------------|-----|

| Hardware- vs. Software-Based Task Switching            | 630 |

| A Condensed Conceptual Overview                        |     |

| A More Comprehensive Overview                          |     |

| The Scheduler and the Task Queue                       |     |

| Setting Up a Task                                      |     |

| The Task Data Structure                                |     |

| The LDT                                                |     |

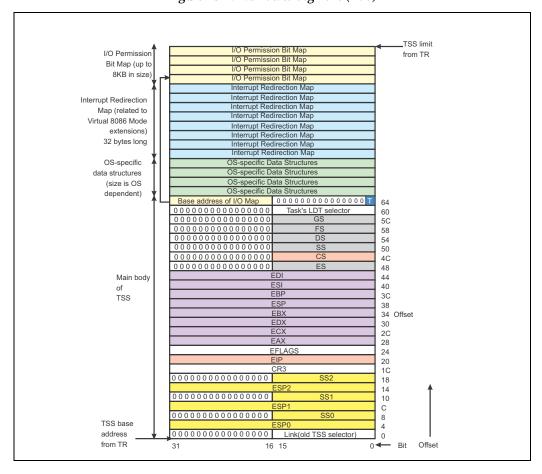

| The TSS                                                |     |

| The Address Translation Tables                         |     |

| The GDT and GDTR Register                              |     |

| The LDTR Register                                      |     |

| The Task Register (TR)                                 |     |

| Starting a Task                                        |     |

| Suspend Task and Resume Scheduler Execution            |     |

| Hardware-Based Task Switching                          |     |

| It's Slow                                              |     |

| Why Didn't OSs Use It?                                 |     |

| Why Wasn't It Improved?                                |     |

| Why Does It Still Exist?                               |     |

| Introduction to the Key Elements                       |     |

| The Trigger Events                                     |     |

| The Descriptors                                        |     |

| TSS Descriptor                                         |     |

| Task Gate Descriptor                                   |     |

| Task Gate Selected by a Far Call/Jump                  |     |

| Gate Selected by Hardware Interrupt/Software Exception | 650 |

| Task Gate Selected by a Software Interrupt Instruction |     |

| The Task Register                                      |     |

| General                                                | 652 |

| TR Instruction Pair                                    | 652 |

| STR Instruction                                        | 652 |

| LTR Instruction                                        | 653 |

| TSS Data Structure Format                              | 654 |

| General                                                | 654 |

| Required Fields                                        | 655 |

| Optional Fields                                        | 655 |

| Register Snapshot Area                                 | 656 |

| LDT Selector Field                                     |     |

| Segment Register Fields                                |     |

| General Purpose Register Fields                        | 657 |

| SS:ESP Register Pair Fields                              | 657 |

|----------------------------------------------------------|-----|

| Extended Flags (Eflags) Register Field                   |     |

| CS:EIP Register Pair Fields                              |     |

| Control Register 3 (CR3) Field                           |     |

| Debug Trap Bit (T)                                       |     |

| IO Port Access Protection                                |     |

| IO Protection in Real Mode                               |     |

| Definition of IO Privilege Level (IOPL)                  |     |

| IO Permission Check in Protected Mode                    |     |

| IO Permission Check in VM86 Mode                         |     |

| IO Permission Bit Map                                    | 661 |

| Required or Optional?                                    |     |

| The Bitmap Offset Field                                  |     |

| The Permission Check                                     |     |

| Interrupt Redirection Bit Map                            | 664 |

| OS-Specific Data Structures                              | 664 |

| Privilege Level 0 - 2 Stack Definition Fields            | 664 |

| Link Field (to Old TSS Selector)                         | 665 |

| Comprehensive Task Switch Description                    | 665 |

| Calling Another Task                                     | 670 |

| An Overview                                              | 670 |

| A Comprehensive Example                                  |     |

| LTR Instruction and the Busy Bit                         |     |

| When Is Busy Cleared?                                    |     |

| Critical Error: Switching to a Busy Task                 |     |

| Busy Toggle Is a Locked Operation                        | 678 |

| Linkage Modification                                     |     |

| Task Switching and Address Translation                   |     |

| One GDT to Serve Them All                                |     |

| Each Task Can Have Different Virtual-to-Physical Mapping |     |

| TSS Mapping Must Remain the Same for All Tasks           |     |

| Placement of a TSS Within a Page(s)                      |     |

| Switch from More-Privileged Code to Lower                |     |

| Software-Based Task Switching                            | 680 |

| Chapter 19: Protected Mode Interrupts and Exceptio       | ns  |

| Handler vs. ISR                                          |     |

| Real Mode Interrupt/Exception Handling                   |     |

| The IDT                                                  |     |

| General                                                  | 684 |

| Protected Mode IDT and the IDTR                          | 685 |

| The Gates                                             | 688 |

|-------------------------------------------------------|-----|

| Introduction                                          | 688 |

| Interrupt Gate                                        | 691 |

| Trap Gate                                             | 693 |

| Actions Taken When Interrupt or Trap Gate Selected    | 694 |

| Actions Taken When Task Gate Selected                 | 696 |

| Interrupt/Exception Event Categories                  | 697 |

| General Event Handling                                |     |

| State Saved on Stack (but which stack?)               |     |

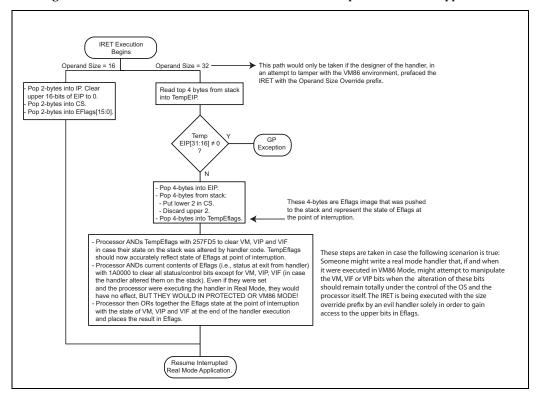

| Return to the Interrupted Program                     | 708 |

| General                                               | 708 |

| The IRET Instruction                                  | 709 |

| Maskable Hardware Interrupts                          | 713 |

| General                                               | 713 |

| Maskable Interrupt Vector Delivery                    | 713 |

| PC-Compatible Vector Assignment                       | 714 |

| Actions Performed by the Handler                      | 719 |

| Effect of CLI/STI Execution                           | 720 |

| General                                               | 720 |

| Other Events That Affect Interrupt Flag Bit           | 722 |

| Protected Mode Virtual Interrupt Feature              |     |

| Non-Maskable Interrupt (NMI) Requests                 | 723 |

| PC-Compatible NMI Logic                               | 723 |

| NMI Description                                       |     |

| More Detailed Coverage of Hardware Interrupt Handling |     |

| Machine Check Exception                               | 724 |

| SMI (System Management Interrupt)                     | 725 |

| Software Interrupts                                   | 725 |

| INT nn Instruction                                    | 726 |

| INTO Instruction                                      |     |

| BOUND Instruction                                     | 727 |

| INT3 (Breakpoint) Instruction                         | 727 |

| Software Exceptions                                   | 728 |

| General                                               | 728 |

| Faults, Traps, and Aborts                             |     |

| Instruction Restart After a Fault                     | 735 |

| Exception Error Codes                                 | 735 |

| Interrupt/Exception Priority                          |     |

| Detailed Description of Software Exceptions           |     |

| Divide-by-Zero Exception (0)                          | 743 |

| Processor Introduced In                               | 743 |

| Exception Class                                       | 743 |

| Description                                        |     |

|----------------------------------------------------|-----|

| Error Code                                         | 743 |

| Saved Instruction Pointer                          | 743 |

| Processor State                                    | 743 |

| Debug Exception (1)                                | 744 |

| Processor Introduced In                            | 744 |

| Exception Class                                    | 744 |

| Description                                        | 744 |

| Error Ĉode                                         | 745 |

| Saved Instruction Pointer                          | 745 |

| Processor State                                    | 745 |

| The Resume Flag Prevents Multiple Debug Exceptions | 745 |

| NMI (2)                                            | 746 |

| Processor Introduced In                            | 746 |

| Exception Class                                    | 746 |

| Error Code                                         | 746 |

| Saved Instruction Pointer                          | 746 |

| Processor State                                    | 746 |

| Breakpoint Exception (3)                           | 746 |

| Processor Introduced In                            | 746 |

| Exception Class                                    | 747 |

| Description                                        | 747 |

| Error Ĉode                                         | 747 |

| Saved Instruction Pointer                          | 747 |

| Processor State                                    | 747 |

| Overflow Exception (4)                             | 748 |

| Processor Introduced In                            | 748 |

| Exception Class                                    | 748 |

| Description                                        | 748 |

| Error Code                                         | 748 |

| Saved Instruction Pointer                          | 748 |

| Processor State                                    | 748 |

| Array Bounds Check Exception (5)                   |     |

| Processor Introduced In                            | 748 |

| Exception Class                                    | 749 |

| Description                                        | 749 |

| Error Code                                         |     |

| Saved Instruction Pointer                          | 749 |

| Processor State                                    | 749 |

| Invalid OpCode Exception (6)                       |     |

| Processor Introduced In                            | 749 |

| Exception Class                                    | 749 |

| Description                                          | . 749 |

|------------------------------------------------------|-------|

| Error Code                                           | . 750 |

| Saved Instruction Pointer                            | . 750 |

| Processor State                                      |       |

| Device Not Available (DNA) Exception (7)             | . 751 |

| Processor Introduced In                              | . 751 |

| Exception Class                                      | . 751 |

| Description                                          | . 751 |

| General                                              | . 751 |

| X87 FPU Emulation                                    |       |

| CR0[TS]: Task Switch, But FP/SSE Registers Not Saved | . 751 |

| CR0[MP]                                              |       |

| Error Code                                           |       |

| Saved Instruction Pointer                            | . 752 |

| Processor State                                      | . 752 |

| Double Fault Exception (8)                           | . 752 |

| Processor Introduced In                              |       |

| Exception Class                                      | . 752 |

| Description                                          |       |

| Shutdown Mode                                        | . 755 |

| Error Code                                           | . 756 |

| Saved Instruction Pointer                            | . 756 |

| Processor State                                      |       |

| Coprocessor Segment Overrun Exception (9)            |       |

| Processor Introduced In                              | . 756 |

| Exception Class                                      |       |

| Description                                          | . 756 |

| Error Ĉode                                           | . 756 |

| Saved Instruction Pointer                            | . 756 |

| Processor State                                      |       |

| Invalid TSS Exception (10)                           | . 757 |

| Processor Introduced In                              | . 757 |

| Exception Class                                      | . 757 |

| Description                                          | . 757 |

| Error Code                                           | . 758 |

| Saved Instruction Pointer                            | . 759 |

| Processor State                                      | . 759 |

| Segment Not Present Exception (11)                   |       |

| Processor Introduced In                              |       |

| Exception Class                                      |       |

| Description                                          | . 760 |

| Error Code                                           |       |

| Saved Instruction Pointer                           | 760 |

|-----------------------------------------------------|-----|

| Processor State                                     | 761 |

| Stack Exception (12)                                | 761 |

| Processor Introduced In                             | 761 |

| Exception Class                                     | 761 |

| Description                                         | 761 |

| Error Code                                          |     |

| Saved Instruction Pointer                           | 762 |

| Processor State                                     | 763 |

| General Protection (GP) Exception (13)              | 763 |

| Processor Introduced In                             | 763 |

| Exception Class                                     | 763 |

| Description                                         | 763 |

| Error Code                                          | 765 |

| Saved Instruction Pointer                           | 765 |

| Processor State                                     | 766 |

| Page Fault Exception (14)                           | 766 |

| Processor Introduced In                             | 766 |

| Exception Class                                     | 766 |

| Description                                         | 766 |

| Error Code                                          | 767 |

| CR2                                                 | 768 |

| Saved Instruction Pointer                           | 768 |

| Processor State                                     | 768 |

| The More Common Case                                | 768 |

| Page Fault During a Task Switch                     | 769 |

| Page Fault During a Stack Switch                    | 769 |

| Vector (Exception) 15                               | 770 |

| FPU Exception (16)                                  | 770 |

| Processor Introduced In                             | 770 |

| Exception Class                                     | 770 |

| Description                                         |     |

| Handling of Masked Errors                           | 771 |

| Handling of Unmasked Errors                         | 772 |

| Error Code                                          |     |

| Saved Instruction Pointer                           | 773 |

| Processor State                                     |     |

| Alignment Check Exception (17)                      | 774 |

| Processor Introduced In                             |     |

| Background: Misaligned Transfers Affect Performance |     |

| Alignment Is Important!                             | 774 |

| Exception Class                                     | 775 |

| Description                                                 | 775 |

|-------------------------------------------------------------|-----|

| Implicit Privilege Level 0 Accesses                         |     |

| Storing GDTR, LDTR, IDTR or TR                              | 776 |

| FP/MMX/SSE Save and Restore Accesses                        | 777 |

| MOVUPS and MOVUPD Accesses                                  | 777 |

| FSAVE and FRSTOR Accesses                                   | 777 |

| Error Code                                                  | 777 |

| Saved Instruction Pointer                                   | 777 |

| Processor State                                             | 778 |

| Machine Check Exception (18)                                | 778 |

| Processor Introduced In                                     | 778 |

| Exception Class                                             | 778 |

| Description                                                 | 778 |

| Error Code                                                  |     |

| Saved Instruction Pointer                                   | 779 |

| Processor State                                             | 779 |

| SIMD Floating-Point Exception (19)                          | 779 |

| Processor Introduced In                                     | 779 |

| Exception Class                                             | 779 |

| Description                                                 | 779 |

| Exception Error Code                                        |     |

| Saved Instruction Pointer                                   | 782 |

| Processor State                                             |     |

| Legacy Problem: 2-Step SS:ESP Update                        | 782 |

| Problem Description                                         |     |

| The Solution                                                | 782 |

| Chapter 20: Virtual 8086 Mode                               |     |

| A Special Note                                              |     |

| Real Mode Applications Are Dangerous                        |     |

| Solution: a Watchdog                                        | 785 |

| Real Mode Applications Run at Privilege Level 3             | 787 |

| Switching Between Protected Mode and VM86 Mode              |     |

| Eflags[VM] = 1 Switches Processor into VM86 Mode            | 787 |

| But Software Cannot Directly Access Eflags[VM]              | 788 |

| Scheduler Activates VM86 Mode                               |     |

| Exiting VM86 Mode                                           |     |

| Determining Interrupted Task Is a Real Mode Task            |     |

| Returning to VM86 Mode from VMM                             |     |