ShangHai Ehong Technology Co.,Ltd.

# **QCA4020 Module (WL501)**

## **Product Specification**

WL501

October 31, 2018

Ehong is a trademark of Ehong Solutions, registered in the United States and other countries. Other product and brand names may be trademarks or registered trademarks of their respective owners.

This technical data may be subject to U.S. and international export, re-export, or transfer ( export ) laws. Diversion contrary to U.S. and international law is strictly prohibited.

ShangHai Ehong Technology Co.,Ltd.

2018 ShangHai Ehong Technology Co.,Ltd. All rights reserved.

ShangHai Ehong Technology Co.,Ltd. (Ehong) and its affiliates reserve the right to make any updates, corrections and any other modifications to its documentation. The information provided in this document represents Ehong's knowledge and belief as of the date this document is provided. Ehong makes no representation or warranty as to the accuracy of such information, and Ehong assumes no liability for any use of the information in this documentation. You should obtain the latest information before placing orders for any hardware, and you should verify that such information is current and complete. Information published by Ehong regarding any third-party products does not constitute a license to use such products or a warranty or endorsement thereof. Use of such information may require a license from a third party under the intellectual property rights of such third party, or a license from Ehong or its affiliates under the intellectual property rights of Ehong or its affiliates.

All hardware, equipment, components or products are sold subject to Ehong's (or such other Ehong affiliated company that is designated by Ehong) standard terms and conditions of sale, as applicable. Notwithstanding anything to the contrary in this documentation or otherwise: (i) you do not receive any rights, licenses, or immunities from suit under any patents of Ehong Solutions, Ehong or their respective affiliates as a result of receiving this documentation (whether expressly, impliedly, by virtue of estoppel or exhaustion, or otherwise), (ii) without limitation, you shall not use or sell any wireless wide area network baseband integrated circuit that you

purchase or acquire from Ehong or any product that incorporates any such baseband integrated circuit (whether alone or in combination with any other software or components) without a separate license or non-assertion covenant from Ehong Solutions in respect of or under all applicable patents, (iii) nothing in this document modifies or abrogates your obligations under any license or other agreement between you and Ehong Solutions, including without limitation any obligation to pay any royalties, and (iv) you will not contend that you have obtained any right, license, or immunity from suit with respect to any patents of Ehong Solutions, Ehong or their respective affiliates under or as a result of receiving this documentation (whether expressly, impliedly, by virtue of estoppel or exhaustion, or otherwise).

# **Revision history**

| Revision | Date         | Description     |

|----------|--------------|-----------------|

| Α        | October 2018 | Initial release |

# Contents

| 1 Introduction                                                                                | 5  |

|-----------------------------------------------------------------------------------------------|----|

| 2 Hardware specification                                                                      | 7  |

| 2.1WL501 module pinout                                                                        | 7  |

| 2.2WL501 interface summary                                                                    |    |

| 2.3Bootstrap signals                                                                          |    |

| 2.4 Electrical characteristics                                                                |    |

| 2.4.1 General DC electrical characteristics                                                   |    |

| 2.4.3 WL501 5 GHz power measurements                                                          |    |

| 2.4.4 BLE power measurements                                                                  |    |

| 2.4.5 802.15.4 power measurements                                                             |    |

| 3 Mechanical interface specification                                                          | 16 |

| 3.1 WL501 module dimensions                                                                   | 16 |

| Figures                                                                                       |    |

| Figure 1-1 WL501 block diagram                                                                | 5  |

| Figure 2-1 WL501 front view                                                                   | 7  |

| Figure 2-2 WL501 back view                                                                    | 8  |

| Figure 2-3 WL501 pinout definition                                                            |    |

| Figure 3-1 WL501 module dimensions                                                            |    |

| Figure 3-2 WL501 module pinout dimensions (in mm)                                             |    |

| Figure 3-3 WL501 module pinout dimensions-Detail B (in mm)                                    | 18 |

| Tables                                                                                        |    |

| Table 2-1 WL501 module non-GPIO pinout definition                                             |    |

| Table 2-2 WL501 module pinout definition and QCA4024 GPIO assignment                          |    |

| Table 2-3 Bootstrap mode                                                                      |    |

| Table 2-4 JTAG mode                                                                           |    |

| Table 2-5 XTAL mode                                                                           |    |

| Table 2-6 32.768KHz Sleep Clock Mode                                                          |    |

| Table 2-7 DC electrical characteristics for digital I/Os                                      |    |

| Table 2-8 2.4 GHz power measurements at antenna port at 25 C, 3.3V nominal                    | 14 |

| Table 2-9 5 GHz power measurements at antenna port at 25 C, 3.3V nominal                      | 14 |

| Table 2-10 BLE power measurements at antenna port at 25 C, 3.3V nominal with external PA      | 15 |

| Table 2-11 802.15.4 power measurements at antenna port at 25 C, 3.3V nominal with external PA | 15 |

# 1 Introduction

The WL501 module provides a highly-integrated and flexible platform for developing and evaluating products and applications based on the QCA4020 SoC. The WL501 module can be either used with CDB20 development kit for software development or incorporated into OEM products to enable rapid deployment of Wi-Fi connected systems.

The WL501 module includes the following components:

- QCA4020 chip (WLAN/BLE/15.4)

- A printed antenna

- 32 Mb NOR flash memory

The QCA4020 is a dual band 1x1 802.11 a/b/g/n device optimized for low-power embedded applications with single-stream capability for both Tx and Rx. It has an integrated network processor with a large set of TCP/IP with IPv4/IPv6-based services.

#### WL501 module features

- Dual-Band IEEE 802.11 a/b/g/n, single stream 1x1

- BLE 5.0

- ZigBee 802.15.4

- Green Tx power saving mode

- Low -power listen mode

- Four-layer PCB design

- Rich set of GPIO(s) and interfaces: I2C, HSUART, UART, SPI, QSPI, SDIO 2.0, I2S, JTAG, Sensor ADC (up to 8 channels, 12bit, 1Msps). Up to 8 PWM optimized for LED lighting applications.

- Secure boot and support for application-level AES encryption and image authentication hash function (SHA256)

- Advancement power management scheme to minimize power dissipation for each use case

#### WL501 manufacturing interface

■ USB 2.0 interface with integrated controller and PHY for manufacturing test and configuration

#### WL501 host interfaces

■ UART host interface to a remote microcontroller with an AT style command set

# 2 Hardware specification

## 2.1 WL501 module pinout

Figure 2-1 WL501 front view

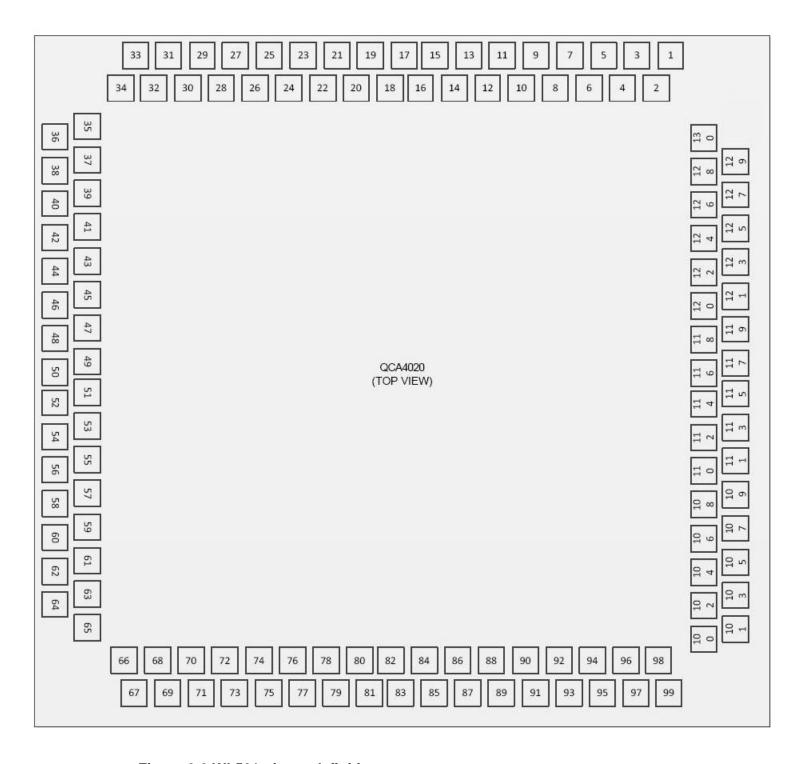

Figure 2-3 WL501 pinout definition

9

Table 2-1 WL501 module non-GPIO pinout definition

| Pin #         | Pin Name    | Description               |

|---------------|-------------|---------------------------|

| Power         |             |                           |

| 2-4           | VBATT_BE    | 3.3V Input Power          |

| Input Signals |             |                           |

| 22            | USB20_DM_BE | USB Differential Negative |

| 23            | USB20_DP_BE | USB Differential Positive |

| Pin #                                                                                       | Pin Name           | Description                                             |

|---------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------|

| 27                                                                                          | SENSEADC_0_BE      | 12bit ADC, ADC 0 input                                  |

| 24                                                                                          | SENSEADC_1_BE      | 12bit ADC, ADC 1 input                                  |

| 37                                                                                          | CHIP_PWD_L_BE      | BLE/802.15.4 Reset Pin                                  |

| Ground                                                                                      |                    |                                                         |

| 1, 5, 33, 38, 42, 45, 67-69, 71, 76, 85, 98-<br>101, 104, 109, 111, 115, 119, 124, 127, 130 | GND                | Ground                                                  |

| No Connect                                                                                  |                    |                                                         |

| 43,44                                                                                       | VDDIO18_BE         | Not used, NC                                            |

| 39-41                                                                                       | VDD11_SWREG_OUT    | Not used, NC                                            |

| 128, 129                                                                                    | VDDIO18_WL         | Not used, NC                                            |

| 117                                                                                         | PWRDWN_OUT_N       | Not used, NC                                            |

| 17                                                                                          | BYPASS_INT_PMU_MSK | Not used, NC                                            |

| 126                                                                                         | IOT_MODE_EN_WL     | Not used, NC                                            |

| 7                                                                                           | WAKEUP_N           | Not used, NC                                            |

| 13                                                                                          | USB_DPOS           | USB Differential Positive, WLAN interface, Not used, NC |

| 14                                                                                          | USB_DNEG           | USB Differential Negative, WLAN interface, Not used, NC |

### Table 2-2 WL501 module pinout definition and QCA4024 GPIO assignment

| Pin<br># | Pin<br>Name   | Primary<br>Functio<br>n | SPI or<br>I2C or<br>QSPI | SDIO | SD<br>Memory<br>Card | UART               | JTAG                 | PWMADC<br>or<br>SenseADC | РТА             | Codec |

|----------|---------------|-------------------------|--------------------------|------|----------------------|--------------------|----------------------|--------------------------|-----------------|-------|

| 84       | GPIO4<br>_BE  | WL_WK<br>UP_BE          |                          |      |                      |                    |                      |                          |                 |       |

| 83       | GPIO5<br>_BE  | GPIO_5                  |                          |      |                      |                    |                      |                          | BT_ACTIVE       |       |

| 81       | GPIO6<br>_BE  | GPIO_6                  |                          |      |                      |                    |                      |                          | WLAN_ACT<br>IVE |       |

| 79       | GPIO7<br>_BE  | GPIO_7                  |                          |      |                      |                    |                      |                          | BT_PRIORI<br>TY |       |

| 61       | GPIO8<br>_BE  | GPIO_8                  |                          |      |                      | M0&M4_U<br>ART0_RX | JTAG1_<br>BE_TC<br>K |                          |                 |       |

| 58       | GPIO9<br>_BE  | GPIO_9                  |                          |      |                      | M0&M4_U<br>ART0_TX | JTAG1_<br>BE_TD<br>O |                          |                 |       |

| 59       | GPIO1<br>0_BE | GPIO_10                 | I2C0_M<br>aster_S<br>CL  |      |                      |                    | JTAG1_<br>BE_TM<br>S |                          |                 |       |

| 56       | GPIO1<br>1_BE | GPIO_11                 | I2C0_M<br>aster_S<br>DA  |      |                      |                    | JTAG1_<br>BE_TDI     |                          |                 |       |

| 32       | GPIO1<br>2_BE | GPIO_12                 |                          |      |                      |                    |                      | pwm_out_0                |                 |       |

| Pin<br># | Pin<br>Name   | Primary<br>Functio<br>n | SPI or<br>I2C or<br>QSPI | SDIO                      | SD<br>Memory<br>Card        | UART                | JTAG                 | PWMADC<br>or<br>SenseADC | PTA             | Codec         |

|----------|---------------|-------------------------|--------------------------|---------------------------|-----------------------------|---------------------|----------------------|--------------------------|-----------------|---------------|

| 54       | GPIO1<br>3_BE | GPIO_13                 |                          |                           |                             |                     |                      | pwm_out_7                |                 |               |

| 52       | GPIO1<br>4_BE | GPIO_14                 |                          |                           |                             | HS_UART0<br>_DM_CTS |                      |                          |                 |               |

| 55       | GPIO1<br>5_BE | GPIO_15                 |                          |                           |                             | HS_UART0<br>_DM_TXD |                      |                          |                 |               |

| 53       | GPIO1<br>6_BE | SPI0_CS<br>2_N          | I2C1_M<br>aster_S<br>CL  |                           |                             | HS_UART0<br>_DM_RFR |                      |                          | BT_ACTIVE       |               |

| 51       | GPIO1<br>7_BE | SPI0_CS<br>1_N          | I2C1_M<br>aster_S<br>DA  |                           |                             | HS_UART0<br>_DM_RXD |                      |                          | WLAN_ACT<br>IVE |               |

| 16       | GPIO1<br>8_BE | GPIO_18                 | SPI_Sla<br>ve_CLK        | SDIO_S<br>lave_CL<br>K    | SD_Master<br>_CLK (O)       | HS_UART1<br>_DM_CTS |                      | pwm_out_6                |                 |               |

| 11       | GPIO1<br>9_BE | GPIO_19                 | SPI_Sla<br>ve_CS_<br>N   | SDIO_S<br>lave_C<br>MD    | SD_Master<br>_CMD (B)       | HS_UART1<br>_DM_TXD |                      | pwm_out_1                |                 |               |

| 15       | GPIO2<br>0_BE | GPIO_20                 | SPI_SL<br>AVE_MI<br>SO   | SDIO_S<br>lave_D<br>ATA_0 | SD_Master<br>_DATA_0<br>(B) | HS_UART1<br>_DM_RXD |                      | pwm_out_2                |                 |               |

| 19       | GPIO2<br>1_BE | GPIO_21                 |                          | SDIO_S<br>lave_D<br>ATA_1 | SD_Master<br>_DATA_1<br>(B) |                     |                      | pwm_out_4                |                 |               |

| 26       | GPIO2<br>2_BE | GPIO_22                 |                          | SDIO_S<br>lave_D<br>ATA_2 | SD_Master<br>_DATA_2<br>(B) |                     |                      | pwm_out_3                |                 |               |

| 21       | GPIO2<br>3_BE | GPIO_23                 | SPI_SL<br>AVE_M<br>OSI   | SDIO_S<br>lave_D<br>ATA_3 | SD_Master<br>_DATA_3<br>(B) | HS_UART1<br>_DM_RFR |                      | pwm_out_5                |                 |               |

| 29       | GPIO2<br>4_BE | GPIO_24                 | SPI0_M<br>aster_C<br>S_N |                           |                             | M0&M4_U<br>ART2_RX  | JTAG2_<br>BE_TC<br>K |                          |                 |               |

| 31       | GPIO2<br>5_BE | GPIO_25                 | SPI0_M<br>aster_C<br>LK  |                           |                             | M0&M4_U<br>ART2_TX  | JTAG2_<br>BE_TD<br>O |                          |                 |               |

| 28       | GPIO2<br>6_BE | GPIO_26                 | SPI0_M<br>aster_M<br>OSI |                           |                             |                     | JTAG2_<br>BE_TM<br>S |                          |                 |               |

| 30       | GPIO2<br>7_BE | GPIO_27                 | SPI0_M<br>aster_M<br>ISO |                           |                             |                     | JTAG2_<br>BE_TDI     |                          |                 |               |

| 46       | GPIO2<br>8_BE | GPIO_28                 |                          |                           |                             |                     |                      |                          |                 | I2S_BC<br>LK  |

| 47       | GPIO2<br>9_BE | GPIO_29                 |                          |                           |                             |                     |                      |                          |                 | I2S_RX<br>D   |

| 48       | GPIO3<br>0_BE | GPIO_30                 |                          |                           |                             |                     |                      |                          |                 | I2S_TX<br>D   |

| 50       | GPIO3<br>1_BE | GPIO_31                 |                          |                           |                             |                     |                      |                          |                 | I2S_FS<br>YNC |

| Pin<br># | Pin<br>Name   | Primary<br>Functio<br>n | SPI or<br>I2C or<br>QSPI | SDIO | SD<br>Memory<br>Card | UART                       | JTAG                 | PWMADC<br>or<br>SenseADC | PTA             | Codec        |

|----------|---------------|-------------------------|--------------------------|------|----------------------|----------------------------|----------------------|--------------------------|-----------------|--------------|

| 49       | GPIO3<br>2_BE | GPIO_32                 |                          |      |                      |                            |                      |                          |                 | I2S_MC<br>LK |

| 10       | GPIO3<br>3_BE | CHIP_P<br>WD_L_<br>WL   |                          |      |                      |                            |                      |                          |                 |              |

| 80       | GPIO4<br>1_BE | PWR_ST<br>ATUS          |                          |      |                      |                            |                      |                          |                 |              |

| 57       | GPIO4<br>8_BE | Ext_32K<br>_IN          |                          |      |                      |                            |                      |                          |                 |              |

| 64       | GPIO4<br>9_BE | GPIO_49                 |                          |      |                      |                            |                      |                          |                 |              |

| 78       | GPIO5<br>0_BE | GPIO_50                 |                          |      |                      |                            | JTAG3_<br>BE_TC<br>K |                          |                 |              |

| 63       | GPIO5<br>1_BE | GPIO_51                 |                          |      |                      |                            | JTAG3_<br>BE_TD<br>O |                          |                 |              |

| 62       | GPIO5<br>2_BE | GPIO_52                 |                          |      |                      |                            | JTAG3_<br>BE_TM<br>S |                          |                 |              |

| 60       | GPIO5<br>3_BE | GPIO_53                 |                          |      |                      |                            | JTAG3_<br>BE_TDI     |                          |                 |              |

| 25       | GPIO5<br>4_BE | GPIO_54                 |                          |      |                      |                            | _                    | SENSEADC<br>2            |                 |              |

| 20       | GPIO5<br>5_BE | GPIO_55                 |                          |      |                      |                            |                      | SENSEADC<br>3            |                 |              |

| 18       | GPIO5<br>6_BE | GPIO_56                 |                          |      |                      |                            |                      | SENSEADC<br>4            |                 |              |

| 12       | GPIO5<br>7_BE | GPIO_57                 |                          |      |                      |                            |                      | SENSEADC<br>5            |                 |              |

| 9        | GPIO5<br>8_BE | GPIO_58                 |                          |      |                      |                            |                      | SENSEADC<br>6            |                 |              |

| 8        | GPIO5<br>9_BE | GPIO_59                 |                          |      |                      | HS_UART2<br>_DM_CTS<br>(I) |                      | SENSEADC<br>7            |                 |              |

| 82       | GPIO6<br>0_BE | GPIO_60                 |                          |      |                      | HS_UART2<br>_DM_TXD<br>(O) |                      |                          | BT_PRIORI<br>TY |              |

## 2.2 WL501 interface summary

- 2x I2C Master Interface

- 1x High speed UART

- Up to 3Mbps data rate

- 1x UART

- Up to 115200 kbps data rate

- 1x I2S

- 1x JTAG

- 1x ADC Sense

- 1x USB2.0 interface

- 1x SPI Interface

### 2.3 Bootstrap signals

#### Table 2-3 Bootstrap mode

| GPIO9_BE GPIO22_BE |   | Description                                        |

|--------------------|---|----------------------------------------------------|

| 0                  | 0 | Force M4 to load image from flash memory (Default) |

| 0                  | 1 | Force M4 to boot in EDL (Emergency Download Mode). |

#### **Table 2-4 JTAG mode**

| GPIO9_BE | GPIO25_BE | GPIO18_BE | Description                 |

|----------|-----------|-----------|-----------------------------|

| 0        | 0         | 0         | No JTAG enabled             |

| 0        | 0         | 1         | JTAG Pins on GPIO[53:50]_BE |

| 0        | 1         | 0         | JTAG Pins on GPIO[11:8]_BE  |

| 0        | 1         | 1         | JTAG Pins on GPIO[27:24]_BE |

| 1        | X         | Х         | Not Allowed                 |

#### Table 2-5 XTAL mode

| GPIO23_BE | Description |

|-----------|-------------|

| 0         | 40MHz Xtal  |

| 1         | Not Allowed |

#### Table 2-6 32.768KHz Sleep Clock Mode

| GPIO21_BE | GPIO20_BE | Description                                           |

|-----------|-----------|-------------------------------------------------------|

| 0         | 0         | Chip Internal LPO                                     |

| 0         | 1         | External Crystal 32.768KHz                            |

| 1         | 0         | External 32.768KHz TCXO Clock connected to GPIO_48_BE |

| 1         | 1         | Not Allowed                                           |

### 2.4 Electrical characteristics

#### 2.4.1 General DC electrical characteristics

These conditions apply to all DC characteristics unless otherwise specified: T<sub>amb</sub> = 25 C,

VBATT BE = 3.3 V

Table 2-7 DC electrical characteristics for digital I/Os

| Symbol | Parameter            | Conditions | Min  | Тур | Max | Unit     |

|--------|----------------------|------------|------|-----|-----|----------|

| VIH    | High level I voltage | _          | 2.4  | -   | 3.6 | <b>V</b> |

| VIL    | Low level I voltage  | _          | -0.3 | 1   | 0.3 | <b>V</b> |

| Vон    | High level O voltage | _          | 3.0  | _   | 3.3 | ٧        |

| Vol    | Low level O voltage  | _          | -0.3 | _   | 0.4 | V        |

### 2.4.2 WL501 2.4 GHz power measurements

Table 2-8 2.4 GHz power measurements at antenna port at 25 C, 3.3V nominal

| Standard     | Typical Tx<br>Compliant Power <sup>1</sup> | Rx Sensitivity | Unit |

|--------------|--------------------------------------------|----------------|------|

|              |                                            |                | dBm  |

| 802.11b      | 22.06                                      | -87            | dBm  |

|              | 22.86                                      |                | dBm  |

|              |                                            |                | dBm  |

| 000 11 =     | 23.53                                      | -91.5          | dBm  |

| 802.11g      | 25.55                                      | -01.0          | dBm  |

| 000 44 11700 | 20.05                                      | 00             | dBm  |

| 802.11n HT20 | 23.35                                      | -92            | dBm  |

| 000 44 11740 | 21.62                                      |                | dBm  |

| 802.11n HT40 | 21.02                                      | -89.5          | dBm  |

### 2.4.3 WL501 5 GHz power measurements

Table 2-9 5 GHz power measurements at antenna port at 25 C, 3.3V nominal

| Standard     | Typical Tx<br>Compliant Power <sup>2</sup> | Rx Sensitivity | Unit |

|--------------|--------------------------------------------|----------------|------|

| 802.11a      | B1:21.16                                   | -89.5          | dBm  |

|              | B4:18.57                                   | -00.0          | dBm  |

| 802.11n HT20 | B1:21.98                                   | -89.5          | dBm  |

|              | B4:18.46                                   | -03.5          | dBm  |

| 802.11n HT40 | B1:21.44<br>B4:18.73                       | -86.5          | dBm  |

|              |                                            |                | dBm  |

<sup>&</sup>lt;sup>1</sup> Numbers shown based on OLPC per board calibration

<sup>&</sup>lt;sup>2</sup> Numbers shown based on OLPC per board calibration

### 2.4.4 BLE power measurements

Table 2-10 BLE power measurements at antenna port at 25 C, 3.3V nominal with external PA

| Parameter      | Description | Typical | Unit |

|----------------|-------------|---------|------|

| Tx Power       | BT LE 1M    | 2.10    | dBm  |

|                | BT LE 2M    | 1.11    | dBm  |

| Rx Sensitivity | BT LE 1M    | -93     | dBm  |

|                | BT LE 2M    | -93     | dBm  |

### **2.4.5 802.15.4 power measurements**

Table 2-11 802.15.4 power measurements at antenna port at 25 C, 3.3V nominal with external PA

| Parameter      | Description | Typical | Unit |

|----------------|-------------|---------|------|

| Tx power       | O-QPSK DSSS | 1.98    | dBm  |

| Rx Sensitivity | O-QPSK DSSS | -101    | dBm  |

# 3 Mechanical interface specification

### 3.1 WL501 module dimensions

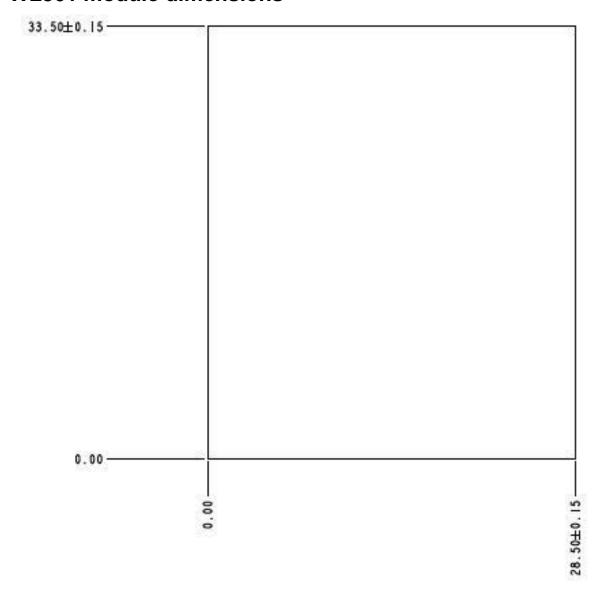

Figure 3-1 WL501 module dimensions

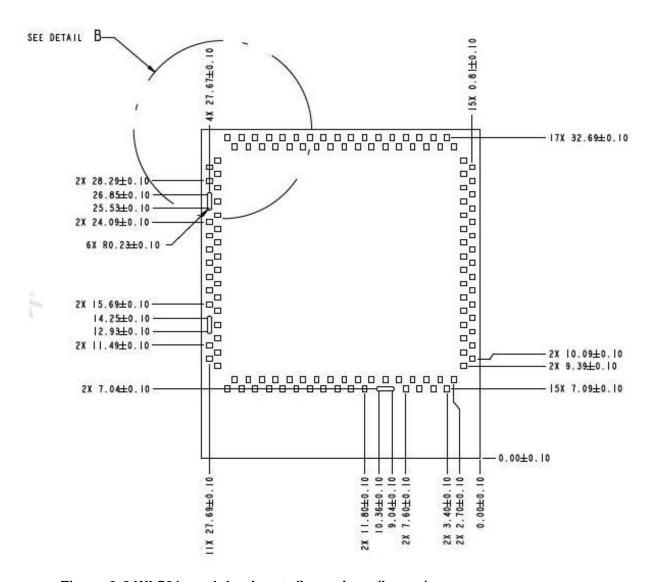

Figure 3-2 WL501 module pinout dimensions (in mm)

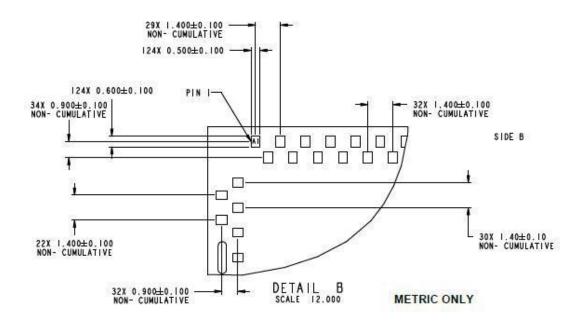

Figure 3-3 WL501 module pinout dimensions-Detail B (in mm)

#### **FCC Statement:**

Any Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Note: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- —Reorient or relocate the receiving antenna.

- —Increase the separation between the equipment and receiver.

- —Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- —Consult the dealer or an experienced radio/TV technician for help.

#### **OEM Guidance**

#### 1. Applicable FCC rules

This device complies with part 15.247/15.407 of the FCC Rules.

#### 2. The specific operational use conditions

This module can be used in IoT devices. The input voltage to the module is nominally 3.3 V DC. The operational ambient temperature of the module is 0  $^{\circ}$ C  $^{\circ}$ C. the embedded PCB antenna is allowed. Any other external antenna is prohibited.

3. Limited module procedures

N/A

4. Trace antenna design

N/A

#### 5. RF exposure considerations

The equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. This equipment should be installed and operated with minimum distance 20cm between the radiator and your body. If the equipment built into a host as a portable usage, the additional RF exposure evaluation may be required as specified by 2.1093.

6. Antenna

Antenna type: PCB antenna Peak gain: 1.0dBi

7. Label and compliance information

An exterior label on OEM's end product can use wording such as the following: "Contains Transmitter Module FCC ID: 2ACCRWL501" or "Contains FCC ID: 2ACCRWL501"

8. Information on test modes and additional testing requirements

a)The modular transmitter has been fully tested by the module grantee on the required number of channels,modulation types, and modes, it should not be necessary for the host installer to re-test all the available transmitter modes or settings. It is recommended that the host product manufacturer, installing the modular transmitter,perform some investigative measurements to confirm that the resulting composite system does not exceed the spurious emissions limits or band edge limits (e.g., where a different antenna may be causing additional emissions).

b)The testing should check for emissions that may occur due to the intermixing of emissions with the other transmitters, digital circuitry, or due to physical properties of the host product (enclosure). This investigation is especially important when integrating multiple modular transmitters where the certification is based on testing each of them in a stand-alone configuration. It is important to note that host product manufacturers should not assume that because the modular transmitter is certified that they do not have any responsibility for final product compliance.

c)If the investigation indicates a compliance concern the host product manufacturer is obligated to mitigate the issue. Host products using a modular transmitter are subject to all the applicable individual technical rules as well as to the general conditions of operation in Sections 15.5, 15.15, and 15.29 to not cause interference. The operator of the host product will be obligated to stop operating the device until the interference have been corrected.

9. Additional testing, Part 15 Sub part B disclaimer The final host / module combination need to be evaluated against the FCC Part 15B criteria for unintentional radiators in order to be properly authorized for operation as a Part 15 digital device.

The host integrator installing this module into their product must ensure that the final composite product complies with the FCC requirements by a technical assessment or evaluation to the FCC rules, including the transmitter operation and should refer to guidance in KDB 996369. For host products with certified modular transmitter, the frequency range of investigation of the composite system is specified by rule in Sections 15.33(a)(1) through (a)(3), or the range applicable to the digital device, as shown in Section 15.33(b)(1), whichever is the higher frequency range of investigation

When testing the host product, all the transmitters must be operating. The transmitters can be enabled by using publicly-available drivers and turned on, so the transmitters are active. In certain conditions it might be appropriate to use a technology-specific call box (test set) where accessory 50 devices or drivers are not available. When testing for emissions from the unintentional radiator, the transmitter shall be placed in the receive mode or idle mode, if possible. If receive mode only is not possible then, the radio shall be passive (preferred) and/or active scanning. In these cases, this would need to enable activity on the communication BUS (i.e., PCIe, SDIO, USB) to ensure the unintentional radiator circuitry is enabled. Testing laboratories may need to add attenuation or filters depending on the signal strength of any active beacons (if applicable) from the enabled radio(s). See ANSI C63.4, ANSI C63.10 and ANSI C63.26 for further general testing details.

The product under test is set into a link/association with a partnering device, as per the normal intended use of the product. To ease testing, the product under test is set to transmit at a high duty cycle, such as by sending a file or streaming some media content.