802.11 b/g/n Wi-Fi module QFM-2202

#### **User manual**

Rev0

# Revision history

| 0 | 12/20/2014 | Initial version |

|---|------------|-----------------|

|   |            |                 |

|   |            |                 |

- 1. Overview

- 2. Features

- 3. Hardware specification

- 3.1 System block diagram

3.2 Module signal description

3.3 Module GPIO pin functions

3.4 Electrical characteristics

- 3.5 Power up sequence

- 3.6 Power consumption

- 3.7 RF characteristics

- 4. Layout guide

- 5. Mechanical interface specification

- Ordering Information

1. Overview In translation

#### 2. Features

Operating voltage: 3.3V

Operating temperature : 0 - 85 °C CPU Cortex-M4 @ 120MHz

o Flash 512KB

FlashMemory128KB

# Wi-Fi system

- o IEEE 802.11b/g/n

- o Single stream 1x1

- o Single-band 2.4GHz

- o Green Tx power saving mode

- o Low power listen mode

- o Data rates up to 150Mbps

- o Data rates up to 1-52Mbps for 802.11 b/g, data rates up to 150Mbps for 802.11n (MCS0-7).

- o Networking protocol support: IPv4/IPv6, TCP/UDP, ARP/NDP, DHCPv4, ICMPv6

- o Full security support: WPS, WPA, WPA2, WAPI, WEP, TKIP

- o Each Tx power calibrated

# Software and stack

- o Real Time OS: MQX

- o Architecture of internet software : Alljoyn

- o iOS homekit frame and MFi supported

- o Bootloader encrypted with RSA2048/SHA-256

- o Update firmware via WiFi or UART

- o Drivers of interfaces of MCU

#### Suitable integrated development environment

- o IAR EWARM V7.10 or above

- o GCC ARM V4.8.4 or above

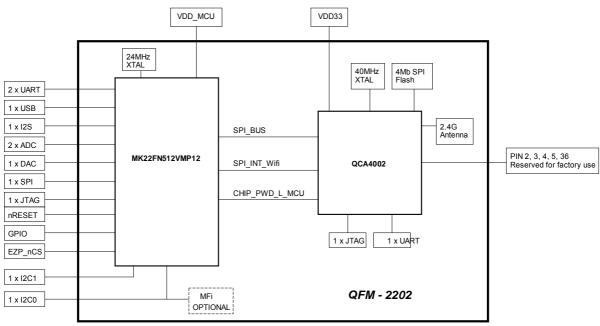

# 3. Hardware Specification3.1 System block diagram

Figure-1 QFM-2202 system block diagram

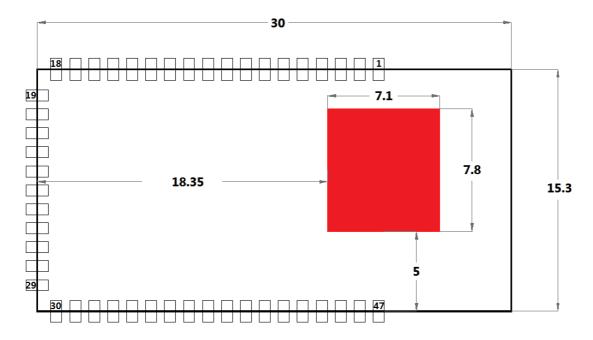

Figure-2 QFM-2202 top view

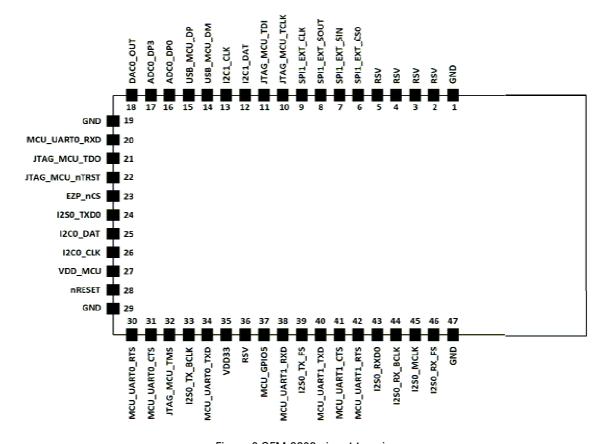

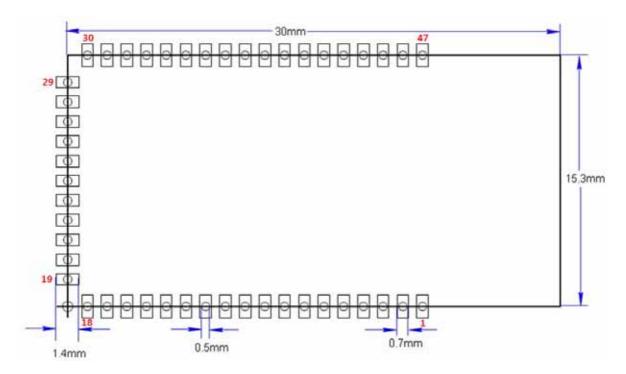

Figure-3 QFM-2202 pinout top view

Table-1 QFM-2202 pin assignment and description

| 0: 1                 |                |                  | ignment and description                            |

|----------------------|----------------|------------------|----------------------------------------------------|

| Signal name          | Pin            | Туре             | Description                                        |

| GND                  | 1, 19, 29, 47  | Power            | Ground                                             |

| VDD_MCU              | 27             | Power            | 3.3V power supply for K22                          |

| VDD33                | 35             | Power            | 3.3V power supply for QCA4002                      |

| RSV                  | 2, 3, 4, 5, 36 | N/A              | Reserved for factory use, NC                       |

| USB_MCU_DM           | 14             |                  | USB FS/LS OTG controller with onchip               |

| USB_MCU_DP           | 15             |                  | transceiver.                                       |

| ADC0_DP0             | 16             | Al               | 16-bit SAR ADCs converting at 1.2 MS/s in 12bit    |

| ADC0_DP3             | 17             | Al               | mode.                                              |

| DAC0_OUT             | 18             | AO               | 12-bit DAC.                                        |

| nRESET               | 28             | DI               | K22 POR reset, active LOW.                         |

| EZP_nCS <sup>1</sup> | 23             | DI <sup>2</sup>  | EzPort Chip Select                                 |

| SPI1_EXT_CS0         | 6              | DIO <sup>2</sup> | Peripheral Chip Select                             |

| SPI1_EXT_SIN         | 7              | DI <sup>2</sup>  | Serial Data In                                     |

| SPI1_EXT_SOUT        | 8              | DO <sup>2</sup>  | Serial Data Out                                    |

| SPI1_EXT_CLK         | 9              | DIO <sup>2</sup> | Serial Clock                                       |

| JTAG_MCU_TCLK        | 10             | DI <sup>2</sup>  | JTAG Test Clock / Serial Wire Clock                |

| JTAG_MCU_TDI         | 11             | DI <sup>2</sup>  | JTAG Test Data Input                               |

| JTAG_MCU_TDO         | 21             | DO <sup>2</sup>  | JTAG Test Data Output                              |

| JTAG_MCU_nTRST       | 22             | DI <sup>2</sup>  | JTAG Reset                                         |

| JTAG_MCU_TMS         | 32             | DIO <sup>2</sup> | JTAG Test Mode Selection / Serial Wire Data        |

| I2C1_DAT             | 12             | DIO <sup>2</sup> | Bidirectional serial data line of the I2C system   |

| I2C1 CLK             | 13             | DIO <sup>2</sup> | Bidirectional serial clock line of the I2C system  |

| I2C0 DAT             | 25             | DIO <sup>2</sup> | Bidirectional serial data line of the I2C system   |

| I2C0 CLK             | 26             | DIO <sup>2</sup> | Bidirectional serial clock line of the I2C system  |

| MCU UARTO RXD        | 20             | DI <sup>2</sup>  | Receive data                                       |

| MCU UARTO RTS        | 30             | DO <sup>2</sup>  | Request to send                                    |

| MCU UARTO CTS        | 31             | DI <sup>2</sup>  | Clear to send                                      |

| MCU UARTO TXD        | 34             | DO <sup>2</sup>  | Transmit data                                      |

| MCU_UART1_RXD        | 38             | DI <sup>2</sup>  | Receive data                                       |

| MCU UART1 TXD        | 40             | DO <sup>2</sup>  | Transmit data                                      |

| MCU UART1 CTS        | 41             | DI <sup>2</sup>  | Clear to send                                      |

| MCU UART1 RTS        | 42             | DO <sup>2</sup>  | Request to send                                    |

| I2S0_TXD0            | 24             | DO <sup>2</sup>  | Transmit Data. The transmit data is generated      |

| _                    |                |                  | synchronously by the bit clock and is tristated    |

|                      |                |                  | whenever not transmitting a word.                  |

| I2SO_TX_BCLK         | 33             | DIO <sup>2</sup> | Transmit Bit Clock. The bit clock is an input when |

|                      |                |                  | externally generated and an output when            |

|                      |                |                  | internally generated.                              |

| I2S0_TX_FS           | 39             | DIO <sup>2</sup> | Transmit Frame Sync. The frame sync is an input    |

|                      |                |                  | sampled synchronously by the bit clock when        |

|                      |                |                  | externally generated and an output generated       |

|                      |                |                  | synchronously by the bit clock when internally     |

|                      |                |                  | generated.                                         |

| I2S0_RXD0            | 43             | DI <sup>2</sup>  | Receive Data. The receive data is sampled          |

|                      |                |                  | synchronously by the bit clock.                    |

| I2SO_RX_BCLK         | 44             | DIO <sup>2</sup> | Receive Bit Clock. The bit clock is an input when  |

|                      |                |                  | externally generated and an output when            |

| 1222 12211           |                |                  | internally generated.                              |

| I2S0_MCLK            | 45             | DIO <sup>2</sup> | Audio Master Clock. The master clock is an input   |

|                      |                |                  | when externally generated and an output when       |

|            |    |                  | internally generated.                                                                                                                                                                             |

|------------|----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12S0_RX_FS | 46 | DIO <sup>2</sup> | Receive Frame Sync. The frame sync is an input sampled synchronously by the bit clock when externally generated and an output generated synchronously by the bit clock when internally generated. |

| MCU_GPIO5  | 37 | DIO <sup>2</sup> |                                                                                                                                                                                                   |

<sup>&</sup>lt;sup>1</sup> Minimum 2 bus clock cycles of EZP\_nCS=0 after reset will force K22 enter into EZP mode.

<sup>&</sup>lt;sup>2</sup> All IOs are with multiplexed functions. See table-2 for details.

# 3.3 Module GPIO pin functions

| Table-2 | OEN/   | 2202  | CDIO | nin | func | tione |

|---------|--------|-------|------|-----|------|-------|

| Table-Z | QFIVI: | -2202 | GPIU | חומ | Tunc | zuons |

| Signal          | Pin      | Default                | ALT0                   | ALT1               | ALT2                 | ALT3        | I ALT4        | ALT5       | ALT6         | ALT7          | EzPort                                           |

|-----------------|----------|------------------------|------------------------|--------------------|----------------------|-------------|---------------|------------|--------------|---------------|--------------------------------------------------|

| EZP nCS         | 23       | NMI_b/                 | ,                      | PTA4/              | , I &                | FTM0_CH1    |               | 71210      | 7.210        | NMI b         | EZP CS b                                         |

|                 |          | EZP CS b               |                        | LLWU P3            |                      |             |               |            |              |               |                                                  |

| SPI1_EXT_CS0    | 6        | DISABLED               |                        | PTD4/<br>LLWU P14  | SPIO_PCS1            | UARTO_RTS_b | FTM0_CH4      | FB_AD2     | EWM_IN       | SPI1_PCS0     |                                                  |

| SPI1_EXT_SIN    | 7        | DISABLED               |                        | PTD7               |                      | UARTO_TX    | FTM0_CH7      |            | FTM0_FLT1    | SPI1_SIN      |                                                  |

| SPI1 EXT SOUT   | 8        | ADC0 SE7b              | ADC0 SE7b              | PTD6/              | SPIO PCS3            | UARTO RX    | FTM0 CH6      | FB AD0     | FTM0 FLT0    | SPI1 SOUT     |                                                  |

|                 |          | _                      |                        | LLWU_P15           |                      | _           |               |            |              |               |                                                  |

| SPI1_EXT_CLK    | 9        | ADC0_SE6b              | ADC0_SE6b              | PTD5               | SPI0_PCS2            | UARTO_CTS_b | FTM0_CH5      | FB_AD1     | EWM_OUT_b    | SPI1_SCK      |                                                  |

| JTAG_MCU_TCLK   | 10       | JTAG_TCLK/             |                        | PTA0               | UARTO_CTS_b          | FTM0_CH5    |               |            |              | JTAG_TCLK/    | EZP_CLK                                          |

|                 |          | SWD_CLK/               |                        |                    |                      |             |               |            |              | SWD_CLK       |                                                  |

|                 |          | EZP_CLK                |                        |                    |                      |             |               |            |              |               |                                                  |

| JTAG_MCU_TDI    | 11       | JTAG_TDI/<br>EZP_DI    |                        | PTA1               | UARTO_RX             | FTM0_CH6    |               |            |              | JTAG_TDI      | EZP_DI                                           |

| JTAG_MCU_TDO    | 21       | JTAG_ TDO/             |                        | PTA2               | UARTO_TX             | FTM0_CH7    |               |            |              | JTAG_TDO/     | EZP_DO                                           |

|                 |          | TRACE_SWO/             |                        |                    |                      |             |               |            |              | TRACE_SWO     |                                                  |

|                 |          | EZP_DO                 |                        |                    |                      |             |               |            |              |               |                                                  |

| JTAG_MCU_nTRST  | 22       | DISABLED               | 1                      | PTA5               | USB_ CLKIN           | FTM0_CH2    | 1             |            | I2SO_TX_BCLK | JTAG_TRST_b   |                                                  |

| JTAG_MCU_TMS    | 32       | JTAG_TMS/              | -                      | PTA3               | UARTO_RTS_b          | FTM0_CH0    | -             |            | <b> </b>     | JTAG_TMS/     | +                                                |

| 1004 DAT        | 40       | SWD_DIO                | 1001 051               | DTF0 /             | 0014 0004            | LIADTA TV   |               |            | 1004 004     | SWD_DIO       |                                                  |

| I2C1_DAT        | 12       | ADC1_SE4a              | ADC1_SE4a              | PTE0/<br>CLKOUT32K | SPI1_PCS1            | UART1_TX    |               |            | I2C1_SDA     | RTC_CLKOUT    |                                                  |

| I2C1_CLK        | 13       | ADC1_SE5a              | ADC1_SE5a              | PTE1/<br>LLWU P0   | SPI1_SOUT            | UART1_RX    |               |            | I2C1_SCL     | SPI1_SIN      |                                                  |

| I2CO_DAT        | 25       | ADC0_SE9/<br>ADC1_SE9  | ADC0_SE9/<br>ADC1_SE9  | PTB1               | I2CO_SDA             | FTM1_CH1    |               |            | FTM1_QD_PHB  |               |                                                  |

| 12C0_CLK        | 26       | ADC0_SE8/              | ADC0_SE8/              | PTB0/              | I2CO_SCL             | FTM1_CH0    |               |            | FTM1_QD_PHA  |               |                                                  |

| MCU UARTO RXD   | 20       | ADC1_SE8  DISABLED     | ADC1_SE8               | PTB16              | SPI1_ SOUT           | UARTO RX    | FTM CLKINO    | FB AD17    | EWM IN       |               | +                                                |

| MCU_UARTO_RXD   | 30       | ADCO SE12              | ADC0 SE12              | PTB2               | 12C0_SCL             | UARTO_RTS_b | F IIVI_CLKINU | FB_AD17    | FTM0_FLT3    |               |                                                  |

| MCU UARTO CTS   | 31       | ADC0_SE12              | ADC0_SE12              | PTB3               | 12C0_SCL<br>12C0_SDA | UARTO CTS b |               |            | FTM0_FLT0    |               | -                                                |

| MCU_UARTO_TXD   | 34       | DISABLED               | ADCU_SETS              | PTB17              | SPI1 SIN             | UARTO TX    | FTM CLKIN1    | FB AD16    | EWM OUT b    |               | -                                                |

| MCU UART1 RXD   | 38       | CMP1_IN1               | CMP1_IN1               | PTC3/              | SPIO PCS1            | UART1 RX    | FTM_CERINT    | CLKOUT     | I2SO TX BCLK | LPUARTO RX    | +                                                |

| WICO_OAKTI_KXD  | 30       | CIVILLINI              | CIVII 1_IIVI           | LLWU P7            | 3110_1 031           | OAKII_KX    | T TIVIO_CITZ  | CEROOT     | 1230_TX_DOLK | LI OAKTO_KX   |                                                  |

| MCU_UART1_TXD   | 40       | DISABLED               |                        | PTC4/              | SPI0_PCS0            | UART1_TX    | FTM0_CH3      | FB_AD11    | CMP1_OUT     | LPUARTO_ TX   |                                                  |

| W100_0/W11_1/XD | 40       | DIONBLEB               |                        | LLWU P8            | 0110_1000            | O/IIII_IX   | 111110_0110   | 10_7.011   | 01011 1_001  | LI GARTIO_ IX |                                                  |

| MCU_UART1_CTS   | 41       | ADC0_SE4b/<br>CMP1_IN0 | ADC0_SE4b/<br>CMP1_IN0 | PTC2               | SPI0_PCS2            | UART1_CTS_b | FTM0_CH1      | FB_AD12    | 1280_TX_FS   | LPUARTO_CTS_b |                                                  |

| MCU_UART1_RTS   | 42       | ADC0_SE15              | ADC0_SE15              | PTC1/              | SPI0_PCS3            | UART1_RTS_b | FTM0_CH0      | FB_AD13    | 1280_TXD0    | LPUARTO_RTS_b |                                                  |

| 12S0_TXD0       | 24       | DISABLED               |                        | PTA12              |                      | FTM1_CH0    | +             | +          | I2S0_TXD0    | FTM1_QD_PHA   | +                                                |

| I2SO_IADO       | 33       | DISABLED               | 1                      | PTB18              | 1                    | FTM1_CH0    | I2SO TX BCLK  | FB AD15    | FTM2 QD PHA  | THE COLUMN    | +                                                |

| I2SO_BCLK       | 39       | DISABLED               | <b>+</b>               | PTB19              |                      | FTM2_CH0    | I2SO TX FS    | FB_ADTS    | FTM2_QD_PHB  |               | <del>                                     </del> |

| 12S0_TX_TS      | 43       | DISABLED               |                        | PTC5/              | SPIO SCK             | LPTMR0_ALT2 | 1250_TX_T3    | FB_AD10    | CMP0_OUT     | FTM0 CH2      |                                                  |

| 1200_1000       | 170      | DIO/IOLLO              |                        | LLWU P9            | 5. 10_00K            |             | 00_1//00      | 7.0_7.0.10 |              |               |                                                  |

| I2SO_RX_BCLK    | 44       | CMP0_IN0               | CMP0_IN0               | PTC6/              | SPI0_SOUT            | PDB0_EXTRG  | I2SO_RX_BCLK  | FB_AD9     | I2S0_MCLK    |               |                                                  |

| I2SO_MCLK       | 45       | ADC1_SE4b/             | ADC1_SE4b/             | PTC8               |                      | FTM3_CH4    | I2S0_MCLK     | FB_AD7     |              |               |                                                  |

|                 | <b>L</b> | CMP0_IN2               | CMP0_IN2               |                    |                      |             |               |            |              |               | -                                                |

| I2SO_RX_FS      | 46       | CMP0_IN1               | CMP0_IN1               | PTC7               | SPIO_SIN             | USB_SOF_OUT | 1280_RX_FS    | FB_AD8     |              |               | 1                                                |

| MCU_GPIO5       | 37       | ADC0_SE14              | ADC0_SE14              | PTC0               | SPI0_PCS4            | PDB0_EXTRG  | USB_SOF_OUT   | FB_AD14    |              |               | +                                                |

|                 |          |                        |                        |                    |                      |             |               |            |              |               |                                                  |

|                 |          |                        |                        |                    |                      |             |               |            |              |               |                                                  |

# 3.4 Electrical characteristics

# 3.4.1 Absolute maximum ratings

Table-3 QFM-2202 absolute maximum ratings

| Symbol              | Description                                      | Min. | Max.                      | Unit |

|---------------------|--------------------------------------------------|------|---------------------------|------|

| V <sub>DD_MCU</sub> | MCU Supply Voltage                               | -0.3 | 3.8                       | V    |

| V <sub>DD33</sub>   | QCA4002 Supply Voltage                           | -0.3 | 4.0                       | V    |

| V <sub>DIO</sub>    | Digital Input Voltage                            | -0.3 | V <sub>DD_MCU</sub> + 0.3 | V    |

| Vaio                | Analog <sup>1</sup>                              | -0.3 | V <sub>DD_MCU</sub> + 0.3 | V    |

| <b>I</b> D          | Maximum current single pin limit (applies to all | -25  | 25                        | mA   |

|                     | digital pins)                                    |      |                           |      |

| V <sub>USB_DP</sub> | USB_DP Input Voltage                             | -0.3 | 3.63                      | V    |

| Vusb_dm             | USB_DM Input Voltage                             | -0.3 | 3.63                      | V    |

<sup>&</sup>lt;sup>1</sup> Analog pins are defined as pins that do not have an associated general purpose I/O port function.

# 3.4.2 Recommended operating conditions

Table-4 QFM-2202 recommended operating conditions

| Symbol              | Description        | Min. | Max. | Unit |

|---------------------|--------------------|------|------|------|

| V <sub>DD_MCU</sub> | MCU Supply Voltage | 2.7  | 3.6  | V    |

| $V_{\text{DD33}}$ | QCA4002 Supply Voltage | 3.14 | 3.46 | V  |

|-------------------|------------------------|------|------|----|

| Tstg              | Storage temperature    | - 40 | 135  | °C |

| TA                | Operating Temperature  | 0    | 85   | °C |

#### 3.4.3 DC electrical characteristics

Table-5 QFM-2202 DC electrical characteristics

| Symbol                | Description                                                               | Min.                       | Max.                       | Unit |

|-----------------------|---------------------------------------------------------------------------|----------------------------|----------------------------|------|

| VIH                   | Input High Voltage                                                        | 0.7 x V <sub>DD_MCU</sub>  | _                          | V    |

| VIL                   | Input Low Voltage                                                         | _                          | 0.35 x V <sub>DD_MCU</sub> | V    |

| Voh                   | Output high voltage                                                       |                            |                            |      |

|                       | Normal drive pad (IoH = -5mA)                                             | V <sub>DD_MCU</sub> - 0.5  | _                          | V    |

|                       | High drive pad (IoH = -20mA)                                              | V <sub>DD_MCU</sub> - 0.5  | _                          | ,    |

| Vol                   | Output low voltage                                                        | _                          |                            |      |

|                       | Normal drive pad (IoH = 5mA)                                              | _                          | 0.5                        | V    |

|                       | High drive pad (Іон = 20mA)                                               | _                          | 0.5                        |      |

| Іонт                  | Output high current total for all ports                                   | _                          | 100                        | mA   |

| lout                  | Output low current total for all ports                                    | _                          | 100                        | mA   |

| lin                   | Input leakage current (per pin) for full temperature                      |                            |                            |      |

|                       | range                                                                     |                            |                            |      |

|                       | All pins other than high drive port pins                                  | _                          | 0.5                        | uA   |

|                       | High drive port pins                                                      | _                          | 0.5                        |      |

| lin                   | Input leakage current (total all pins) for full                           | _                          | 1.0                        | uA   |

|                       | temperature range                                                         |                            |                            |      |

| Rpu                   | Internal pullup resistors                                                 | 20                         | 50                         | kΩ   |

| Rpd                   | Internal pulldown resistors                                               | 20                         | 50                         | kΩ   |

| V <sub>HYS</sub>      | Input Hysteresis                                                          | 0.06 x V <sub>DD_MCU</sub> | _                          | V    |

| licio                 | Analog and I/O pin DC injection current - single pin                      |                            |                            |      |

|                       | V <sub>IN</sub> < V <sub>SS</sub> - 0.3V (Negative current injection)     | -3                         | _                          | mA   |

|                       | V <sub>IN</sub> > V <sub>DD_MCU</sub> + 0.3V (Positive current injection) | _                          | +3                         |      |

| I <sub>ICcont</sub> 1 | Contiguous pin DC injection current —regional limit,                      |                            |                            |      |

|                       | includes sum of negative injection currents or sum                        |                            |                            |      |

|                       | of positive injection currents of 16 contiguous pins                      |                            |                            | mA   |

|                       | Negative current injection                                                | -25                        | _                          |      |

|                       | Positive current injection                                                | _                          | +25                        |      |

| Vodpu                 | Open drain pullup voltage level                                           | V <sub>DD_MCU</sub>        | V <sub>DD_MCU</sub>        | V    |

| VRAM                  | VDD_mau voltage required to retain RAM                                    | 1.2                        | _                          | V    |

| V <sub>POR</sub> 2    | Falling VDD_mou POR detect voltage                                        | 0.8                        | 1.5                        | V    |

¹ All analog and I/O pins are internally clamped to Vss and VDD\_mcu through ESD protection diodes. If VIN is less than VIO\_MIN or greater than VIO\_MAX, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(VIO\_MIN-VIN)/|IICO|. The positive injection current limiting resistor is calculated as R=(VINVIO\_MAX)/|IICO|. Select the larger of these two calculated resistances if the pin is exposed to positive and negative injection currents.

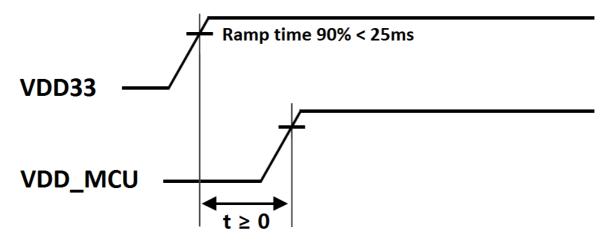

# 3.5 Power up sequence

<sup>&</sup>lt;sup>2</sup> Typical value is 1.1V.

Figure-4 QFM-2202 power up sequence

- 3.6 Power consumption

- 3.6.1 Operating power consumption

Table-6 QFM-2202 operating power consumption

| Mode | Standard | Rate    | Тур   | Unit |

|------|----------|---------|-------|------|

| Тх   | 11b      | 1       | 247.6 |      |

|      |          | 11      | 241.2 |      |

|      | 11g      | 6       | 246.1 |      |

|      |          | 54      | 210.6 |      |

|      | 11n HT20 | MCS0    | 263.0 | mA   |

|      |          | MCS7    | 217.3 |      |

|      | 11n HT40 | MCS0    | 221.5 |      |

|      |          | MCS7    | 195.5 |      |

| Rx   | Al       | l rates | 66.7  | mA   |

# 3.6.2 Standby power consumption

Table-7 QFM-2202 standby power consumption

| Typical current consumption for SPI/UART at 3.3V |                                                            |                                                                                                                                          |  |  |  |

|--------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Standby CHIP_PWD 5uA                             |                                                            |                                                                                                                                          |  |  |  |

| 50uA                                             |                                                            |                                                                                                                                          |  |  |  |

| 130uA                                            |                                                            |                                                                                                                                          |  |  |  |

| s) T2 (ms)                                       | Tbeacon (ms)                                               | T3 (ms)                                                                                                                                  |  |  |  |

| 0.36                                             | 0.99                                                       | 0.39                                                                                                                                     |  |  |  |

| 0.32                                             | 1.06                                                       | 0.41                                                                                                                                     |  |  |  |

| 0.30                                             | 1.01                                                       | 0.41                                                                                                                                     |  |  |  |

| 0.43                                             | 0.97                                                       | 0.47                                                                                                                                     |  |  |  |

|                                                  | 5uA<br>50uA<br>130uA<br>s) T2 (ms)<br>0.36<br>0.32<br>0.30 | 5uA       50uA       130uA       s)     T2 (ms)     Tbeacon (ms)       0.36     0.99       0     0.32     1.06       0     0.30     1.01 |  |  |  |

<sup>&</sup>lt;sup>1</sup> Numbers are for switch mode.

# 3.7 RF characteristics RF

# 3.7.1 Wireless LAN radio configuration and general specifications

Table-8 Wireless LAN radio configuration and general specifications

| Item                  |             | Specification                   |      |  |  |

|-----------------------|-------------|---------------------------------|------|--|--|

| Country/Domain Code 1 | Reserved    | Reserved                        |      |  |  |

| Center Frequency      | 11b         | 2.412-2.472                     | GHz  |  |  |

|                       | 11g         | 2.412-2.472                     | GHz  |  |  |

|                       | 11n HT20    | 2.412-2.472                     | GHz  |  |  |

|                       | 11n HT40    | 2.422-2.452                     | GHz  |  |  |

| Rate                  | 11b         | 1, 2, 5.5, 11                   | Mbps |  |  |

|                       | 11g         | 6, 9, 12, 18, 24, 36, 48, 54    | Mbps |  |  |

|                       | 11n 1stream | MCS0, 1, 2, 3, 4, 5, 6, 7       | Mbps |  |  |

| Modulation type       | 11b         | DSSS (CCK, DQPSK, DBPSK)        | _    |  |  |

|                       | 11g/n       | OFDM (64QAM, 16QAM, QPSK, BPSK) |      |  |  |

<sup>&</sup>lt;sup>1</sup> This code will be written during calibration.

# 3.7.2 radio Tx characteristics

Table-9 radio Tx characteristics

| Symbol | Parameter                 | Conditions | Min   | Тур | Max   | Unit |

|--------|---------------------------|------------|-------|-----|-------|------|

| Ftx    | Tx output frequency range | _          | 2.412 | _   | 2.484 | GHz  |

| Pout   | Output power 1            |            | •     |     |       |      |

|        | 11b                       | 1 Mbps     | _     | 19  | _     | dBm  |

|        |                           | 11 Mbps    | _     | 19  | _     | dBm  |

|        | 11g                       | 6 Mbps     | _     | 19  | _     | dBm  |

|        |                           | 54 Mbps    | _     | 18  | _     | dBm  |

|        | 11n HT20                  | MCS0       | _     | 20  | _     | dBm  |

|        |                           | MCS7       | _     | 17  | _     | dBm  |

|        | 11n HT40                  | MCS0       | _     | 17  | _     | dBm  |

|        |                           | MCS7       | _     | 14  | _     | dBm  |

|        |                           |            |       |     |       |      |

<sup>&</sup>lt;sup>1</sup> Performance calculated at the balun. Loss from balun to antenna connector in the test board is 1.2 dB (2.4GHz).

# 3.7.3 radio Rx characteristics

Table-10 radio Rx characteristics

| Symbol | Parameter                | Conditions | Min   | Тур | Max   | Unit |

|--------|--------------------------|------------|-------|-----|-------|------|

| Frx    | Rx input frequency range | _          | 2.412 |     | 2.484 | GHz  |

| Srf    | Sensitivity 1            |            |       |     |       | •    |

|        | CCK                      | 1 Mbps     |       |     |       |      |

|        |                          | 2 Mbps     |       |     |       |      |

|        |                          | 5.5 Mbps   |       |     |       |      |

|        |                          | 11 Mbps    |       |     |       |      |

|        | OFDM                     | 6 Mbps     |       |     |       |      |

|        |                          | 9 Mbps     |       |     |       |      |

|        |                          | 12 Mbps    |       |     |       |      |

|        |                          | 18 Mbps    |       |     |       |      |

|        |                          | 24 Mbps    |       |     |       |      |

|        |                          | 36 Mbps    |       |     |       |      |

|        |                          | 48 Mbps    |       |     |       |      |

|        |                          | 54 Mbps    |       |     |       |      |

|        | HT20                     | MCS0       |       |     |       |      |

|        |                          | MCS1       |       |     |       |      |

|      | MCS2 |  |  |

|------|------|--|--|

|      | MCS3 |  |  |

|      | MCS4 |  |  |

|      | MCS5 |  |  |

|      | MCS6 |  |  |

|      | MCS7 |  |  |

| HT40 | MCS0 |  |  |

|      | MCS1 |  |  |

|      | MCS2 |  |  |

|      | MCS3 |  |  |

|      | MCS4 |  |  |

|      | MCS5 |  |  |

|      | MCS6 |  |  |

|      | MCS7 |  |  |

<sup>&</sup>lt;sup>1</sup> Performance measured at the balun. Loss from balun to antenna connector in the test board is 1.2 dB (2.4GHz).

- 4. Layout guide

- 1 ) The antenna area should be towards outside of base board. The distance from pin1 or pin47 to edge of board should be smaller than 2mm.

- 2 ) Red rectangle is the clearance area: on the base board, top and internal layers of the red rectangle should have no shapes or clines; the bottom layer of the red rectangle should have a whole ground shape.

Figure-5 QFM-2202 clearance area for base board

# 5. Mechanical interface specification

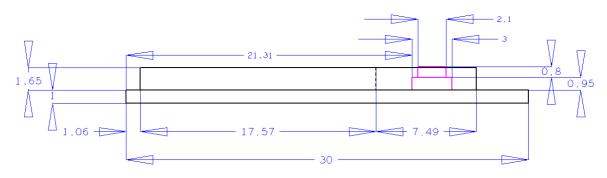

# 5.1 QFM-2202 module dimensions

Figure-6 QFM-2202 module dimensions top view

Figure-7 QFM-2202 module dimensions bottom view

Figure-8 QFM-2202 module dimensions side view (unit: mm)

# 6. Ordering Information

| Part number | Temperature | Package | MFi & HomeKit |

|-------------|-------------|---------|---------------|

| QFM-2202    | 0 to 85 °C  |         | Not Available |

| QFM-2202-A  | 0 to 85 °C  |         | Available     |

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference and (2) this device must accept any interference received, including interference that may cause undesired operation.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC rules. These limits are designed to provide r easonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures: -Reorient or relocate the receiving antenna. -

Increase the separation between the equipment and receiver. -

Connect the equipment into an outlet on a circuit different from that to which the receiver is connected. -Consult the dealer or an experienced radio/TV technician for help.

You are cautioned that changes or modifications not expressly approved by the party r esponsible for compliance could void your authority to operate the equipment.

FCC RF Radiation Exposure Statement: 1. This Transmitter must not be colocated or operating in conjunction with any other antenna or transmitter. 2. This equipment complies with FCC RF radiation exposure limits set forth for an uncontrolled environment. This equipment should be installed and operated with a minimum distance of 20 centimeters between the radiator and your body.

# Information to OEM integrator

The OEM integrator has to be aware not to provide information to the end user regard ing how to install or remove this RF module in the user manual of the end product. The user manual which is provided by OEM integrators for end users must include the following information in a prominent location.

1. To comply with FCC RF exposure compliance requirements, the antenna used for this transmitter must be installed to provide a separation distance of at least 20 cm from all persons and must not be co-located or operating in conjunction with any other antenna or transmitter, except in accordance with FCC multi-transmitter product

transmitter product procedures.

- 2. Only those antennas with same type and lesser gain filed under this FCC ID number c an be used with this device.

- 3. The regulatory label on the final system must include the statement: "Contains FCC I D: RUN-QFM2202".

- 4. The final system integrator must ensure there is no instruction provided in the user manual or customer documentation indicating how to install or remove the transmitter module except such device has implemented two-

ways authentication between module and the host system.