# microNode Integration Specification

**On-Ramp Wireless Confidential and Proprietary.** This document is not to be used, disclosed, or distributed to anyone without express written consent from On-Ramp Wireless. The recipient of this document shall respect the security of this document and maintain the confidentiality of the information it contains. The master copy of this document is stored in electronic format, therefore any hard or soft copy used for distribution purposes must be considered as uncontrolled. Reference should be made to On-Ramp Wireless to obtain the latest revision.

On-Ramp Wireless Incorporated 10920 Via Frontera, Suite 200 San Diego, CA 92127 U.S.A.

Copyright © 2012 On-Ramp Wireless Incorporated. All Rights Reserved.

The information disclosed in this document is proprietary to On-Ramp Wireless Inc., and is not to be used or disclosed to unauthorized persons without the written consent of On-Ramp Wireless. The recipient of this document shall respect the security of this document and maintain the confidentiality of the information it contains. The master copy of this document is stored in electronic format, therefore any hard or soft copy used for distribution purposes must be considered as uncontrolled. Reference should be made to On-Ramp Wireless to obtain the latest version. By accepting this material the recipient agrees that this material and the information contained therein is to be held in confidence and in trust and will not be used, copied, reproduced in whole or in part, nor its contents revealed in any manner to others without the express written permission of On-Ramp Wireless Incorporated.

On-Ramp Wireless Incorporated reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed for any damages arising directly or indirectly by their use or application. The information provided in this document is provided on an "as is" basis.

This document contains On-Ramp Wireless proprietary information and must be shredded when discarded.

This documentation and the software described in it are copyrighted with all rights reserved. This documentation and the software may not be copied, except as otherwise provided in your software license or as expressly permitted in writing by On-Ramp Wireless, Incorporated.

Any sample code herein is provided for your convenience and has not been tested or designed to work on any particular system configuration. It is provided "AS IS" and your use of this sample code, whether as provided or with any modification, is at your own risk. On-Ramp Wireless undertakes no liability or responsibility with respect to the sample code, and disclaims all warranties, express and implied, including without limitation warranties on merchantability, fitness for a specified purpose, and infringement. On-Ramp Wireless reserves all rights in the sample code, and permits use of this sample code only for educational and reference purposes.

This technology and technical data may be subject to U.S. and international export, re-export or transfer ("export") laws. Diversion contrary to U.S. and international law is strictly prohibited.

Ultra-Link Processing<sup>™</sup> is a trademark of On-Ramp Wireless.

Other product and brand names may be trademarks or registered trademarks of their respective owners.

microNode Integration Specification 014-0033-00 Rev. B March 13, 2012

# Contents

| 1 Overview                                               | 1 |

|----------------------------------------------------------|---|

| 2 DC and AC Characteristics                              | 2 |

| 2.1 Absolute Maximum Ratings                             | 2 |

| 2.2 Recommended Operating Conditions                     |   |

| 2.3 Effects of Temperature and Voltage                   |   |

| 3 Electrical Interface                                   | 7 |

| 3.1 Signal Descriptions                                  | 9 |

| 3.1.1 VBATT                                              | 9 |

| 3.1.2 POWER_ON                                           | 9 |

| 3.1.3 RESET_N                                            | 9 |

| 3.1.4 MRQ                                                | 9 |

| 3.1.5 SRDY                                               | 9 |

| 3.1.6 SRQ                                                | 9 |

| 3.1.7 USTATUS                                            | 0 |

| 3.1.8 SPI System 1                                       | 0 |

| 3.1.9 ANT_SEL1                                           | 0 |

| 3.1.10 UART_SIN                                          | 0 |

| 3.1.11 UART_SOUT1                                        | 0 |

| 3.1.12 TOUT                                              | 0 |

| 3.1.13 RF_PAEN_EXT 1                                     | 0 |

| 3.1.14 RF_TXENA1                                         | 0 |

| 3.1.15 RF_SHDN1                                          | 1 |

| 3.1.16 RF                                                | 1 |

| 3.2 Environmental1                                       | 1 |

| 3.2.1 ESD1                                               | 1 |

| 3.2.2 Harsh Environments1                                | 1 |

| 4 SPI Interface and Sequences1                           | 2 |

| 4.1 SPI System Interface Overview1                       | 2 |

| 4.2 SPI Mode and Timing1                                 | 3 |

| 4.3 Host Initialization                                  | 3 |

| 4.4 Startup (Power On) Sequence1                         | 3 |

| 4.5 Wake Sequence1                                       | 5 |

| 4.5.1 Wake Sequence (Synchronous)1                       | 5 |

| 4.5.2 Wake Sequence (Asynchronous)1                      | 6 |

| 4.6 Host-Driven Reset Sequence1                          |   |

| 4.7 Host MRQ Release/microNode Allowed to Sleep Sequence |   |

| 5 Power States                           | 19 |

|------------------------------------------|----|

| 5.1 Operating States                     |    |

| 5.1.1 Power Off State                    |    |

| 5.1.2 Deep Sleep State                   |    |

| 5.1.3 Oscillator Calibration State       |    |

| 5.1.4 Idle State                         |    |

| 5.1.5 RX State                           |    |

| 5.1.6 TX State                           |    |

| 5.2 System                               | 21 |

| 6 Messaging Protocol                     |    |

| 6.1 Arbitration                          | 23 |

| 6.2 Message Protocol                     |    |

| 6.3 Host Interface SPI Bus State Machine |    |

| 6.4 SPI Bus Timing Example               |    |

| 6.5 Host Message SPI Example             |    |

| 6.6 Host Message "Connect" SPI Example   |    |

| 7 microNode Configuration                |    |

| 8 Antenna Diversity                      |    |

| 8.1 Antenna Design Considerations        |    |

| 8.2 Diversity Considerations             |    |

| 9 Regulatory Considerations              |    |

| 9.1 Block Diagram                        |    |

| 9.2 Certifications                       |    |

| 9.3 FCC Warnings                         |    |

| 9.4 IC Warnings                          |    |

| 9.5 ETSI Warnings                        |    |

| 9.6 Usage                                |    |

| 9.6.1 Note to Integrators                |    |

| 9.6.2 RF Exposure Statement              |    |

| 9.7 Antennas                             |    |

| 10 Manufacturing Considerations          | 41 |

| 10.1 Mechanical Outline                  |    |

| 10.2 Host PCB Constraints                |    |

| 10.3 Solder Profile                      |    |

| 10.3.1 Handling Procedures for microNode |    |

| 10.3.2 Solder Procedures for microNode   |    |

| 11 Errata                               |  |

|-----------------------------------------|--|

| Appendix A Abbreviations and Terms      |  |

| Appendix B Coplanarity Requirements     |  |

| B.1 microNode Dimensions                |  |

| B.2 Bow Measurement                     |  |

| B.3 Twist Measurement                   |  |

| Appendix C PCB Land Pattern             |  |

| Appendix D microNode Solder Profile     |  |

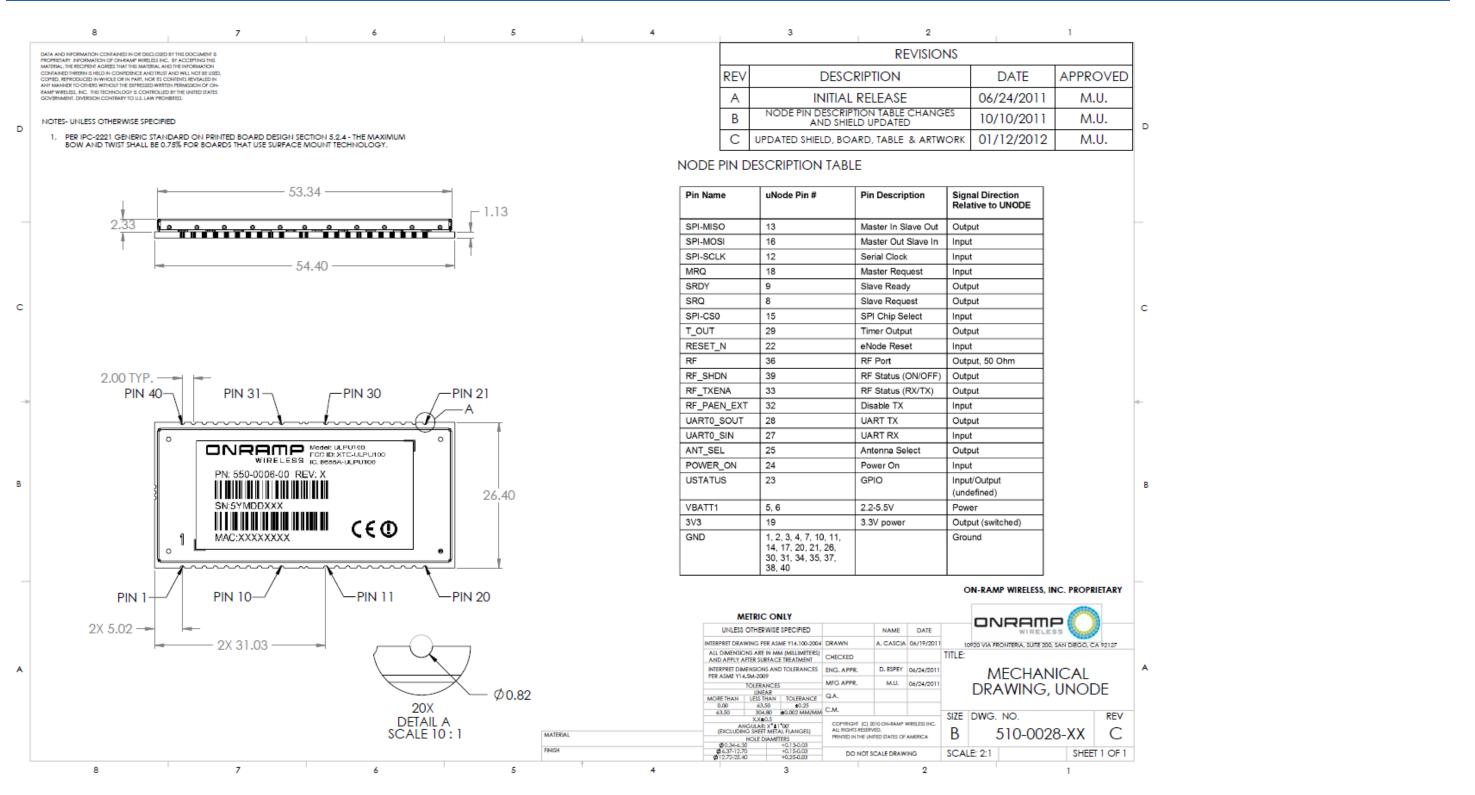

| Appendix E microNode Mechanical Drawing |  |

# Figures

| Figure 1. microNode Deep Sleep Power Consumption (mW Power vs VBATT Input)                                              | 5  |

|-------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2. RX State Power Consumption (mW Power vs VBATT Input)                                                          | 5  |

| Figure 3. TX Power Consumption at 21.5 dBm (mW Power vs VBATT Input)                                                    | 6  |

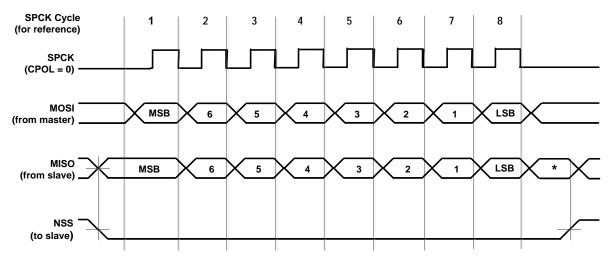

| Figure 4. SPI Timing, CPOL = 0, CPHA = 0                                                                                | 13 |

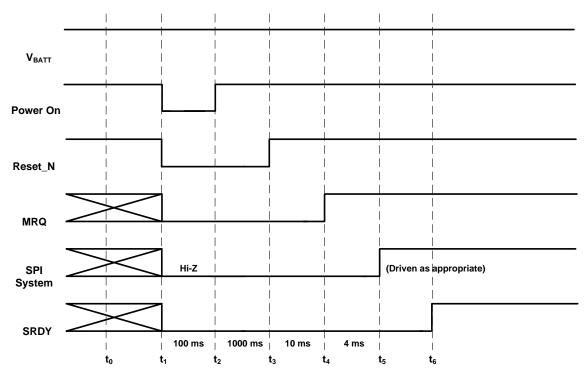

| Figure 5. microNode Powerup Timing Sequence                                                                             | 14 |

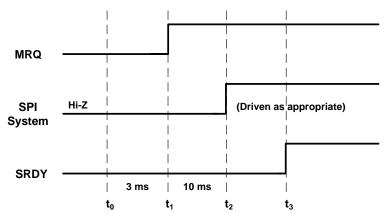

| Figure 6. Host-Initiated microNode Wake Sequence - SRDY Low (Synchronous)                                               | 15 |

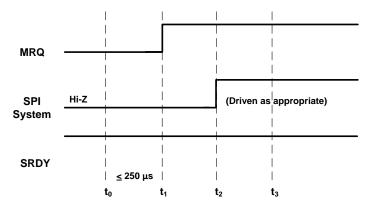

| Figure 7. Host-Initiated microNode Wake Sequence – SRDY High (Asynchronous)                                             |    |

| Figure 8. Host-Driven Reset Sequence                                                                                    |    |

| Figure 9. Host MRQ Release/microNode Allowed to Sleep Sequence                                                          |    |

| Figure 10. microNode Oscillator Calibration: Current (Amps) vs Time (Seconds)                                           |    |

| Figure 11. Representative Current Consumption During Sleep, Idle, RX, and TX; x16<br>Spreading Factor (Amps vs Seconds) |    |

| Figure 12. SPI Master and Slave Message Sequences                                                                       |    |

| Figure 13. Host Interface SPI Bus State Machine                                                                         |    |

| Figure 14. SPI Timing Example                                                                                           |    |

| Figure 15. Host Message on SPI – MMsg Pair                                                                              |    |

| Figure 16. Host Message on SPI – MHdr Pair                                                                              |    |

| Figure 17. Antenna Diversity Circuit                                                                                    |    |

| Figure 18. microNode Block Diagram                                                                                      |    |

| Figure 19. microNode Dimensions                                                                                         | 46 |

| Figure 20. Bow Measurement of Length and Width Bow                                                                      | 47 |

| Figure 21. Twist Measurement                                                                                            | 47 |

| Figure 22. microNode PCB Land Pattern                                                                                   | 48 |

| Figure 23. Solder Profile                                                                                               |    |

| Figure 24. microNode Mechanical Dimensions                                                                              | 50 |

# Tables

| Table 1. Absolute Maximum Ratings   | 2  |

|-------------------------------------|----|

| Table 2. Operating Conditions       | 2  |

| Table 3. Operating Characteristics  | 2  |

| Table 4. microNode Pin Descriptions | 7  |

| Table 5. ESD Information            | 11 |

| Table 6. microNode Certifications   | 38 |

| Table 7. Solder Profile Information | 42 |

# **Revision History**

| Revision | Release Date     | Change Description                                                                         |  |

|----------|------------------|--------------------------------------------------------------------------------------------|--|

| А        | January 18, 2012 | Initial release.                                                                           |  |

| В        | March 13, 2012   | <ul> <li>Expanded information for regulatory considerations and certifications.</li> </ul> |  |

|          |                  | <ul> <li>Removed errata section that is no longer relevant.</li> </ul>                     |  |

# 1 Overview

The purpose of this document is to provide guidelines allowing an integrator to design a Host product that utilizes the microNode and ensures that the system meets all of its technical objectives and requirements.

The following documents are referenced and provide more detail.

- ULP Node Interface Library (UNIL) (010-0066-00)

Provides information about the library of portable C code provided by On-Ramp Wireless which can be integrated into a customer's existing software architecture.

- **n** UNIL API (010-0072-00) Provides details relating to the UNIL Application Programming Interface.

- **n** ULP Node Host Message Specification (014-0020-00) Provides details relating to Node Host messages.

- Node FCC/IC/ETSI EMC Compliance Test Procedures (009-0021-00)

Describes/explains the FCC/IC/ETSI EMC compliance tests and how to use On-Ramp Wireless's configuration software for these tests.

- NPT User Guide (010-0060-00)

Describes the setup, configuration, and use of a collection of utilities called Node Provisioning Tools (NPT) used for Node provisioning.

# 2 DC and AC Characteristics

# 2.1 Absolute Maximum Ratings

Operating outside of these ranges may damage the unit.

The microNode is MSL 3-rated and should be handled as an MSL 3 device per IPC/JEDEC J-STD-033 (latest revision). See section 10.3.1 for further information.

### Table 1. Absolute Maximum Ratings

| Parameter                               | Min | Max | Unit |

|-----------------------------------------|-----|-----|------|

| Storage Temperature                     | -40 | 85  | °C   |

| Operating Temperature                   | -40 | 85  | °C   |

| Input Voltage                           | 2.2 | 5.5 | V    |

| Digital Interface Signals, 3.3V nominal | 3.0 | 3.6 | V    |

# 2.2 Recommended Operating Conditions

### **Table 2. Operating Conditions**

| Parameter               | Min | Max | Unit |

|-------------------------|-----|-----|------|

| Input voltage, VBATT    | 2.2 | 5.5 | V    |

| Ambient Temperature, Ta | -40 | 85  | °C   |

The following characteristics apply across the -40°C to +85°C temperature range unless otherwise noted.

### **Table 3. Operating Characteristics**

| Description                            | Min     | Тур | Мах     | Units |  |  |

|----------------------------------------|---------|-----|---------|-------|--|--|

| DC Characteristics                     |         |     |         |       |  |  |

| Voltage – VBATT                        | 2.2     | 3.6 | 5.5     | Volt  |  |  |

| Off Current – Note 1                   | 0.05    | 0.1 | 2.0     | μA    |  |  |

| Deep Sleep Current - Note 1            | 10      | 20  | 40      | μA    |  |  |

| Idle Current – Note 1                  | 10      | 15  | 25      | mA    |  |  |

| Receive Current – Note 1               | 75      | 85  | 90      | mA    |  |  |

| Transmit Current – Note 2              | 200     | 245 | 280     | mA    |  |  |

| Digital                                |         |     |         |       |  |  |

| VOL – Voltage Output, Low (4mA sink)   | 0       |     | 0.1     | V     |  |  |

| VOH – Voltage Output High (4mA source) | Vdd-0.9 |     | Vdd-0.1 | V     |  |  |

| Environmental                          |         |     |         |       |  |  |

| Operating Temperature                  | -40     |     | +85     | °C    |  |  |

| Description                                                                                  | Min  | Тур            | Max            | Units      |

|----------------------------------------------------------------------------------------------|------|----------------|----------------|------------|

| Storage Temp                                                                                 | -40  |                | +85            | °C         |

| Humidity – non-condensing                                                                    | 5    |                | 95             | %          |

| Ramp Temperature (maximum rate at which operating temperature should change)                 |      |                | 30             | °C/Hr.     |

| Receiver                                                                                     |      |                |                |            |

| Receiver Sensitivity – Note 3                                                                | -140 | -142           | -144           | dBm        |

| Receiver Image Reject                                                                        | 38   | 45             | 50             | dB         |

| Noise Figure                                                                                 | 3.5  | 5.0            | 6.7            | dB         |

| Input IP3 (high LNA gain mode)                                                               |      | -11            |                | dBm        |

| Maximum RF input level for specification compliance                                          |      |                | -20            | dBm        |

| General RF Characteristics                                                                   |      |                | •              |            |

| Frequency Range – Note 4                                                                     | 2402 |                | ~2482          | MHz        |

| Channel Spacing                                                                              | N/A  | 1.99           | N/A            | MHz        |

| Transmitter                                                                                  |      |                | •              |            |

| Maximum RF Conducted Power –Note 5                                                           |      |                |                |            |

| FCC/IC markets:                                                                              | 20.0 | 21.3           | 21.5           | dBm        |

| ETSI markets:                                                                                | 8.5  | 9.5            | 10.0           | dBm        |

| Carrier Rejection                                                                            | -35  | -40            | -50            | dBc        |

| Signal Modulation                                                                            |      | DSSS-<br>DBPSK |                |            |

| Signal Bandwidth                                                                             |      | 1.0            |                | MHz        |

| BT Factor                                                                                    |      | 0.3            |                |            |

| Peak to Average Ratio                                                                        |      | 2.3            |                | dB         |

| Spectral bandwidth at maximum RF power:<br>-6dB BW<br>-20dB BW                               |      | 0.96<br>1.75   |                | MHz<br>MHz |

| ACPR – Note 6                                                                                |      |                | -30            | dBc        |

| Harmonics – Note 7                                                                           |      |                | -43            | dBm        |

| Transmit Power Level Accuracy – Note 8                                                       |      |                | ±1.5           | dB         |

| Transmitter Spurious Outputs – Note 9<br>30MHz to 2400MHz:<br>2482MHz to 8000MHz:            |      |                | < -43<br>< -43 | dBm<br>dBm |

| VSWR Tolerance<br>Maximum VSWR for spec compliance – Note 10:<br>Maximum VSWR for stability. |      |                | 1.5:1<br>9:1   |            |

### NOTES:

- 1. Tested at 3.6V input.

- 2. Measured at 21.5 dBm TX output (Typ=50W), 3.6V, range includes VSWR  $\leq$  1.5:1 (Po not compensated).

- 3. Sensitivity at maximum spreading factor of 13 (8192) with 10% FER.

- 4. The upper frequency range is market dependent:

- a. FCC/IC: CH38; 2475.63 MHz.

- b. ETSI: CH40; 2479.61 MHz.

- c. Japan: CH41; 2481.60 MHz.

- 5. Maximum TX RF power is limited by FCC/IC grant to 21.5 dBm in these markets.

- 6. Spec and test method comes from FCC 15.247(d); Band Edge Emissions, 2 MHz offset.

- 7. At any TX power level, VSWR  $\leq$  3:1. Harmonics fall into FCC restricted bands.

- 8. Estimated sum of all contributors with VSWR  $\leq$  1.5:1. Normal link mode.

- 9. At any TX power level, VSWR  $\leq$  3:1. Applies to spurious, not ACPR or harmonics. Generally the largest spurious output outside the 2.40-2.48GHz band is at 2/3LO and 4/3LO.

- 10. Maximum VSWR for spec compliance applies at 25C only. Slightly degraded ACPR/mask and power variation can be expected at temperature extremes.

### 2.3 Effects of Temperature and Voltage

The microNode is based largely on Complementary Metal–Oxide–Semiconductor (CMOS) technology. The current drain of CMOS circuitry can vary substantially over Temperature. The RF circuitry and its performance also vary substantially over Temperature.

The microNode utilizes two main power domains when it is functioning:

### 1. LDO Regulators that work from 2.2V up to 5.5V.

These are enabled when the POWER\_ON signal for the microNode is active. These can act as a linear load as voltage increases from minimum to maximum – although these circuits do not normally consume much power.

### 2. Switching power domains.

When the microNode wakes up to communicate with the Host or for networking events, its switching regulators are enabled. These buck-boost switching regulators supply the 3.3V and other logic supplies over the input range of 2.2-5.5V. The power efficiency of these regulators change dramatically over input voltage, load levels, and temperature. Nominally, the power efficiency is best at 3-4.0V. The efficiency becomes poor below 3.0V and is moderately efficient at the higher input levels.

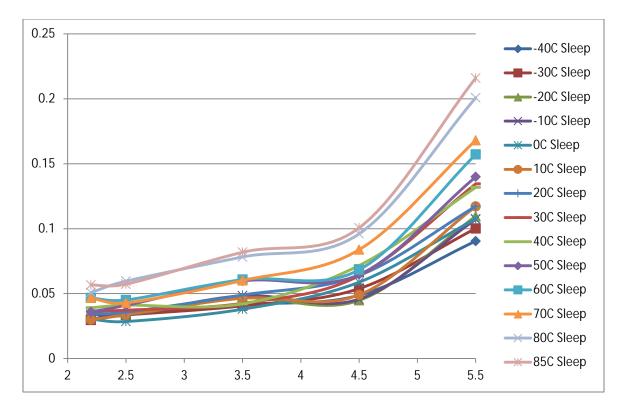

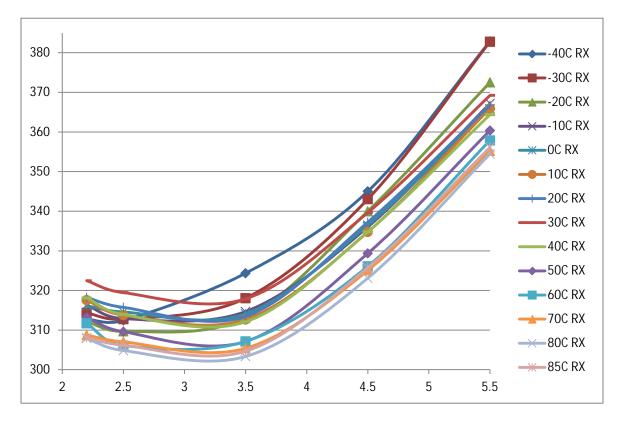

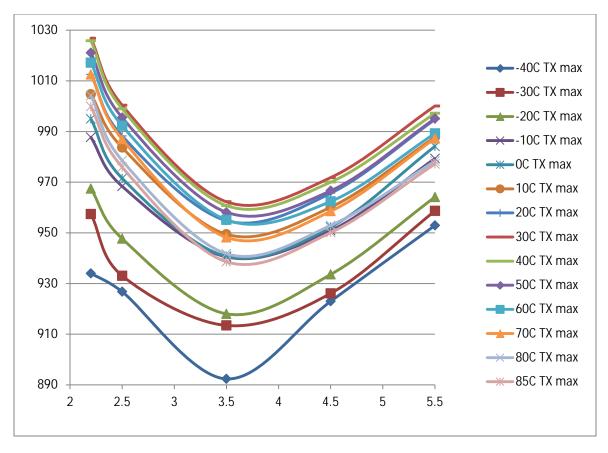

The following graphs show the relative differences across the operating voltages and their effect on current consumption.

Figure 1. microNode Deep Sleep Power Consumption (mW Power vs VBATT Input)

Figure 2. RX State Power Consumption (mW Power vs VBATT Input)

Figure 3. TX Power Consumption at 21.5 dBm (mW Power vs VBATT Input)

# **3** Electrical Interface

This chapter describes the electrical interface of the microNode and how the Host processor controls the microNode.

| Pin #                                                   | Pin Name | Signal<br>Direction<br>Relative to<br>microNode | Signal<br>Type    | Comment                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------|----------|-------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 4, 7, 10                                       | Ground   | Power                                           | Power             | Ground return. Should be low RF impedance to a solid ground plane of the Host                                                                                                                                                                                                 |

| 11,14, 17, 20, 21,<br>26, 30, 31, 34, 35,<br>37, 38, 40 | Ground   | Power                                           | Power             |                                                                                                                                                                                                                                                                               |

| 5, 6                                                    | VBATT    | Power                                           | Power             | Input power to the microNode. It is<br>recommended that the Host<br>integrator allow for decoupling of<br>the microNode by placing space<br>for up to a 100 µF ceramic cap.<br>This may or may not be required,<br>depending on the Host's power<br>supply and its impedance. |

| 8                                                       | SRQ      | Output                                          | CMOS_O            | Slave Request                                                                                                                                                                                                                                                                 |

| 9                                                       | SRDY     | Output                                          | CMOS_O            | Slave Ready                                                                                                                                                                                                                                                                   |

| 12                                                      | SCLK     | Input                                           | CMOS_I            | SPI Clock                                                                                                                                                                                                                                                                     |

| 13                                                      | MISO     | Output                                          | CMOS_O            | SPI Master In Slave Output                                                                                                                                                                                                                                                    |

| 15                                                      | CS       | Input                                           | CMOS_I            | SPI Chip Select                                                                                                                                                                                                                                                               |

| 16                                                      | MOSI     | Input                                           | CMOS_I            | SPI Master Output Slave In                                                                                                                                                                                                                                                    |

| 18                                                      | MRQ      | Input                                           | CMOS_I            | Master Request                                                                                                                                                                                                                                                                |

| 19                                                      | 3V3      | Output                                          | CMOS_O            | 3.3V Switcher output                                                                                                                                                                                                                                                          |

| 22                                                      | RESET_N  | Input                                           | OC_1              | RESET input                                                                                                                                                                                                                                                                   |

| 23                                                      | USTATUS  | I/O                                             | CMOS_O,<br>CMOS_I | USTATUS. To be used by the microNode as a GPIO. Undefined at this time. Float for now.                                                                                                                                                                                        |

| 24                                                      | POWER_ON | Input                                           | CMOS_A            | This is used to turn ON/OFF the<br>Internal Power supplies of the<br>microNode.                                                                                                                                                                                               |

| 25                                                      | ANT_SEL  | Output                                          | CMOS_O            | This is used by the microNode to control its antennas for diversity.                                                                                                                                                                                                          |

| 27                                                      | UART_SIN | Input                                           | CMOS_I            | UART Serial input. Not supported at this time.                                                                                                                                                                                                                                |

### Table 4. microNode Pin Descriptions

| Pin # | Pin Name    | Signal<br>Direction<br>Relative to<br>microNode | Signal<br>Type | Comment                                                                                                              |

|-------|-------------|-------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------|

| 28    | UART_SOUT   | Output                                          | CMOS_O         | UART Serial output. Not supported at this time.                                                                      |

| 29    | TOUT        | Output                                          | CMOS_O         | TOUT is a normally low signal that<br>pulses high in response to specific<br>Network Timing Events                   |

| 32    | RF_PAEN_EXT | Input                                           | CMOS_I         | This is used to force the PA off. It<br>is internally pulled low. Do not<br>connect at this time.                    |

| 33    | RF_TXENA    | Output                                          | CMOS_O         | This signal is used to indicate<br>status of the Power Amplifier for<br>the microNode: Low - OFF, High -<br>Enabled. |

| 36    | RF          | RF RX/TX                                        | 50 Ohm         | This is the RF input/output for the microNode. It is a 50 Ohm castellated "pin."                                     |

| 39    | RF_SHDN     | RF Shutdown                                     | CMOS_O         | This pin indicated the status of the<br>microNode's RF Transceiver:<br>Low= Shutdown, High = Active                  |

### NOTES:

- 1. The VDD of the internal logic of the microNode is 3.3Volt.

- 2. The Host is the SPI Master and the microNode is the SPI Slave.

- 3. OC\_1

The pin-type is unique for the RESET line. Internal to the microNode, this is a simple RC circuit that Resets to GND (0 Volts) and rises to 1.8Volts (maximum). Externally, it is required to drive this pin via an Open Collector (States: Ground=microNode Reset, or float=microNode Active). Most Host CPUs have programmable I/Os that allow setting as an output (low) and as input (tri-state or float). A pull-up is not permitted. Voltages above 1.8V can damage the Reset line of the microNode or place the microNode in a latchup state.

- 4. CMOS\_A

- a. The CMOS\_A pin is used to control two Analog Regulators and their Enable pins.

- b. The pin has hysteresis.

- **n** Going High (Active): V input High is 1.2V

- **n** Going Low (OFF): V input Low is 0.4V

- c. When the microNode is ON, this pin consumes a nominal 0.2  $\mu$ A but as maximum of 2  $\mu$ A over the entire temperature range.

- 5. VBATT

- a. The microNode operating voltage is 2.2-5.5V, which drives a buck/boost regulator (3.3Volts) internal to the microNode.

- b. The 3.3V regulator drives the RF and PA circuitry of the microNode which also drives its operating CMOS I/O voltages.

# 3.1 Signal Descriptions

### 3.1.1 VBATT

This is the main power to the microNode. This needs a low impedance source to the Host's power source. It is recommended that the Host have provision for up to a 100  $\mu$ F low ESR capacitor. It is likely this capacitor is not required if low impedance design rules are followed.

### 3.1.2 POWER\_ON

This signal controls the power-on of the LDO circuitry for the microNode. It must be shut off prior to starting the microNode power-up sequence as defined in section 4.4: Startup (Power On) Sequence. After the microNode is powered up, this signal is to remain logic high.

### 3.1.3 RESET\_N

The microNode has a basic RC Reset circuit that should be cleared during the startup sequence for the microNode. This signal is an Open Collector style of signal that can be cleared (grounded) for Reset and allowed to float when the microNode is operational. This pin should never be exposed to a voltage greater than 1.8V.

### 3.1.4 MRQ

The MRQ (Master Request) is the Host's normal way of waking the microNode to initiate SPI communications. Logic "High" forces the microNode awake.

### 3.1.5 SRDY

SRDY (Slave Ready) is an indication from the microNode that it has fully booted its internal Firmware image, initialized its Hardware and Interfaces, and is ready for communication (arbitration) with the Host. Logic "High" indicates the microNode is ready for communications.

### 3.1.6 SRQ

The SRQ (Slave Request) signal is an indication from the microNode that it wants the Host's attention. When SRQ is asserted "High," the Host must read the Status registers of microNode. If SRQ is "High," SRDY will also be "High."

### **3.1.7 USTATUS**

USTATUS is currently undefined. In software it can be either an Input or Output. Currently it is configured as an input. The Host should not use this signal.

### 3.1.8 SPI System

The SPI system is the generic term used for all SPI signals (MOSI, MISO, CS, SCLK) to be set up for SPI communications to occur between Host and microNode.

The microNode SPI is the Slave in the Master/Slave communications and is defined in section 4.2: SPI Mode and Timing.

### 3.1.9 ANT\_SEL

The Antenna Select (microNode output) signal is used to control a RF T/R signal to allow Antenna Diversity. This is more fully defined in Chapter 8: Antenna Diversity.

### 3.1.10 UART\_SIN

This UART\_SIN is a microNode UART input signal. It is reserved for future use and should not be used by the Host. Leave unconnected.

### 3.1.11 UART\_SOUT

The UART\_SOUT is a UART output signal that is currently reserved. The Host should not use this pin.

### 3.1.12 TOUT

This signal is a Time Synchronizing signal that pulses high upon specific network timing events.

### 3.1.13 RF\_PAEN\_EXT

The RF\_PAEN\_EXT signal is a direct hardware signal that can be used to disable the Power Amplifier (PA) for the microNode. This signal is pulled low (100k to ground) to allow the PA to work as normal. A microNode external device can temporarily assert this signal high to de-key the PA for the microNode. The purpose of this direct control is to allow simple coexistence algorithms with other RF devices. If the external device is transmitting, its transmitter signal can disable the PA for the microNode thus avoiding a TX collision.

### 3.1.14 RF\_TXENA

This signal is a status output of the microNode that allows other RF devices to monitor when the microNode is transmitting. In a simple RF coexistence scheme, the RF\_TXENA can disable a coexisting radio's transmitter, while the microNode is transmitting. The RF\_TXENA signal goes active high when transmitting.

### 3.1.15 RF\_SHDN

This microNode output indicates status of the microNode's RF Transceiver. If low, the transceiver sleeps (no RX and no TX). Using RF\_SHDN and RF\_TXENA in combination, co-existing RF devices can determine the absolute state of the RF Transceiver of the microNode.

### 3.1.16 RF

This is the RF port (TX and RX) for the microNode. It is a nominal 50 Ohm port. For best results ensure the load termination (antenna) has a VSWR of 1.5:1 or better (return loss < -14 dB).

# 3.2 Environmental

### 3.2.1 ESD

The microNode is designed to be a truly embedded module and can almost be considered an IC. The microNode is to be placed as a direct-connect to the Host CPU. Therefore, the microNode has inherent minimal electrostatic discharge (ESD) protection on its I/O.

### Table 5. ESD Information

| ESD Model | Class and Minimum Voltage |

|-----------|---------------------------|

| НВМ       | Class 1C ( >1000V)        |

| MM        | Class A (>100V)           |

The RF port does have some protection in the form of an inductor to ground, thus allowing some robustness to direct ESD strikes.

If the application is intended for harsh ESD or lightning strike scenarios it is recommended that the Integrator take extra precautions to guard against accidental resets or ESD damage.

### 3.2.2 Harsh Environments

The microNode employs miniature surface-mounted components in its assembly. If the target design is intended for high humidity or salt environments and intended to have a long service life, it is recommended that the designer take necessary precautions to guard against prolonged exposure to moisture and other contaminants. A sealed enclosure (IP68) or potting may be required in extreme environments.

# **4** SPI Interface and Sequences

### 4.1 SPI System Interface Overview

The SPI slave interface is currently the only supported interface for Host-to-Node communication.

**NOTE:** The microNode must be the only SPI slave on the bus.

The SPI slave interface provides communication with an external Host through a 7-wire interface. The Host is the SPI master and the microNode is the SPI slave. In addition to the four standard SPI signals, three additional signals are used to complement the SPI bus: MRQ, SRQ, and SRDY. The additional signals are included to support microNode state transitions and bi-directional message traffic.

The SPI signals include four that are controlled by the master and three that are controlled by the slave.

### Master-controlled Signals

- n MOSI

- n SCLK

- n CS

- n MRQ

**Slave-controlled Signals**

- n MISO

- n SRQ

- n SRDY

When MRQ and SRQ are low, the remaining master controlled signals (MOSI, SCLK, and CS) must be held low or tri-stated. This is to prevent these signals from back-driving the microNode slave that may be in deep sleep. When either MRQ or SRQ assert high, the master should set each of the three signals appropriately according to their standard usage. No pull-up resistors should ever be applied to any signals on the microNode.

### 4.2 SPI Mode and Timing

Figure 4. SPI Timing, CPOL = 0, CPHA = 0

### 4.3 Host Initialization

What is described here is the initialization of the Host, its operating software, and the control sequences used to drive the microNode.

Due to specific clock and memory requirements, the microNode must go through specific Initialization and Wake sequences.

**NOTE:** Some CPUs have internal pull-up resistors that are active after Power On Reset. Through CMOS leakage, the Host CPU can supply voltages to the microNode I/O bus prior to the Host CPU fully initializing and disabling the pull-up resistors. It must be noted that during the brief initialization period, the POWER\_ON signal must be "low." Activating the POWER\_ON signal with other microNode signals being pulled "high" can cause CMOS latchup within the microNode.

# 4.4 Startup (Power On) Sequence

During, and immediately after Power On Reset (POR), the Host has no control of its I/O power states. For instance, some CPUs have GPIO that tri-state or act as inputs during power up. Other CPU brands have programmable pull-ups on its I/O and need the Host CPU to disable those pull-ups for the Host's GPIO to work correctly with the microNode. This setup and configuration of GPIO takes a finite time during the Host boot process. This is detailed in the following figure.

Whereas the power-up sequence is described here, it is recommended the Integrator not attempt this entire startup sequence without assistance. On-Ramp Wireless offers a formal and controlled library to help with this startup and communication interface called UNIL. This is fully documented and released by On-Ramp Wireless. The UNIL tracks all details of the lower (physical) and higher

VBATT Host Init (not a signal) Power On Reset\_N MRQ Hi-Z SPI System SRDY 100 ms 1000 ms 10 ms 4 ms t<sub>0</sub>  $\mathbf{t}_1$ t<sub>2</sub> t<sub>3</sub> t4 t<sub>5</sub> t<sub>6</sub> - t<sub>4</sub> < 300 ms or error

(messages) layers of the Host-Node communications. For more information on UNIL see the documents referenced in chapter 1 at the beginning of this document.

#### Figure 5. microNode Powerup Timing Sequence

The timing sequence shown in Figure 5 above is described below.

- n t0 à t1 This phase is where the Host's System power has been applied and the Host Software must power up and initialize the GPIO interfaces for the microNode to the required states defined at time t1. The t1 state becomes "TRUE" indicating the Host sets all the GPIO to a known and controlled state (Low).

- At t2 state, all the output signals to the microNode are set low and the Power On Signal is set high. This turns on the internal LDO regulators of the microNode to initiate a power up sequence. The time between t1-t2 is approximately 100 ms, or longer.

- **t t 3** is when the Host releases the microNode from its Reset state. This time allows the microNode's 32 kHz to turn on and stabilize. The time between t2-t3 is 1 second, or longer.

- **t4** t4 signals the start of the Host wanting to initiate communications (arbitration) with the microNode. The Host raises MRQ to turn on various circuitry. The time between t3-t4 is 10 ms, or longer.

- After the assertion of t4, the microNode begins its "Wake sequence." The microNode must boot, initialize its operating system and hardware and when it is ready for communications it raises its SRDY signal back to the Host. At this point, communications (Arbitration) can begin.

- **n t6** At this point the microNode signals its readiness by asserting the SRDY pin. The Host can now begin communications with the microNode.

### 4.5 Wake Sequence

The microNode can be awakened in two manners:

- n MRQ assertion from the Host. The Host desires communications with the microNode and awakens the microNode by asserting the MRQ line. This is a Synchronous Wake Sequence.

- n The microNode can "self-awaken" due to network events. In this case, a timer internal to the microNode "pops" and triggers the microNode to "Wake." When the microNode is awake it asserts its SRDY as a matter of course to indicate to the Host (if it needs to) that it can start communicating with the microNode while it is awake. This is an Asynchronous Wake Sequence.

### 4.5.1 Wake Sequence (Synchronous)

The following sequence demonstrates the timing required of the Host to awaken the microNode from a sleep state.

### Assumptions:

- n The microNode has been previously Powered On and Arbitrated.

- **n** The power (VBATT) has remained stable and the microNode has not been Reset (Reset is set to tri-state/float).

#### Figure 6. Host-Initiated microNode Wake Sequence – SRDY Low (Synchronous)

The timing sequence shown in Figure 6 above is described below.

- **n t0** The Host desires to Wake the microNode and asserts MRQ high.

- n t0 à t1

After MRQ has gone High, the Host's SPI system and other I/O can be enabled.

Asserting the MRQ has enabled the internal I/O power supply of the microNode and the Host's SPI can be enabled 4 ms after the rise of MRQ.

- n t1 à t2

After the initial assertion of MRQ, the microNode has to internally power up and initialize its systems. When it is ready to communicate it will assert its SRDY line to signal it is now ready for SPI interaction. From MRQ assertion until the microNode is ready, takes about 80 ms.

- **n** t3 The microNode is now ready to communicate with the Host.

### 4.5.2 Wake Sequence (Asynchronous)

In this scenario, the microNode is already awake due to a networking event (SRDY is already High) and the Host wants to communicate with the microNode while it is awake. The Host asserts MRQ to ensure that the microNode stays awake during its communication cycle.

Figure 7. Host-Initiated microNode Wake Sequence – SRDY High (Asynchronous)

### 4.6 Host-Driven Reset Sequence

If the microNode fails to communicate (or similar), it may be necessary to Reset the microNode. The following figure shows the proper sequence to reset the device.

**NOTE:** Resetting the device causes it to go through a Cold Acquisition process to reacquire the network.

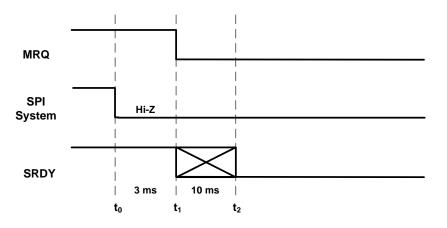

### 4.7 Host MRQ Release/microNode Allowed to Sleep Sequence

If the Host determines there are no more messages or SPI transactions required, it nominally deasserts the MRQ to allow the microNode to fall back to Deep Sleep (lowest power mode). The figure below shows how this is sequenced by the Host/microNode. A small delay in de-asserting SRDY is enforced to prevent quick toggling (Waking) of the microNode.

# 5 Power States

The microNode has a number of states it runs through during its various operating modes.

General comments:

- 1. The microNode accepts a wide input voltage range (2.2-5.5V).

- 2. The microNode has low drop out (LDO) regulators that will operate 100% of the time the microNode is powered (POWER\_ON signal set high).

- 3. There are 3.3V/1.2V Buck/Boost Switching regulators that use the wide input range to drive key RF and Digital circuits. The 3.3V regulator is only turned on in certain active operating states of the microNode.

The microNode tries to minimize its power consumption but is largely driven by network operating states and ULP modes of operation. This document does not describe all of the modes in detail but, in general, there are two main operating modes for the microNode:

n Continuous Mode

In this mode, the microNode is ON (awake) at least 50% of the time (100% of its RX cycle). The microNode starts up, searches for the network, locks on, and Joins. In this mode, the microNode nominally is either in RX or TX modes (radio is ON and in a high power consumption state), or in an Idle state where the clocks and CPU are ON but the radio is OFF (moderately low power mode). The continuous mode is usually for applications where the Host and microNode are AC-powered and system current consumption is not an issue.

### n Slotted Mode

This mode has the microNode falling into a Deep Sleep state – the lowest power state of the microNode. In this mode, the microNode is mostly powered down – except for a couple of low power LDO Regulators. The microNode can sleep for hours at a time if the network is configured to allow this.

The power states are described in the following sections.

# 5.1 Operating States

This section describes the various operating states within the operational modes.

### 5.1.1 Power Off State

When the microNode is totally non-functional, the Host can set the POWER\_ON signal Low to deactivate the circuitry of the microNode. This should NOT be confused with Deep Sleep states where the microNode mostly sleeps yet maintains key network timers to wake up synchronously with network activity. If awakened from the Power Off state, the microNode must go through a very power-hungry search/acquisition algorithm to re-acquire the ULP network.

### 5.1.2 Deep Sleep State

The microNode shuts off all its power regulators except a couple low quiescent LDO regulators. These regulators keep a minimal amount of circuitry alive for tracking network timers, enable a 32 kHz clock, and some minor interface circuitry.

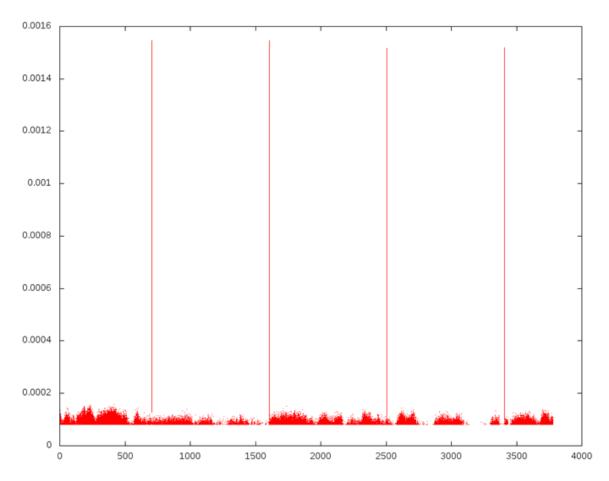

### 5.1.3 Oscillator Calibration State

When the microNode is in Deep Sleep state, it attempts to maintain accuracy of its low power 32 kHz clock to enable faster network synchronizing when it wakes up. The CPU of the microNode is not activated during this calibration state. The microNode will periodically, and briefly, Wake in a very low power mode to calibrate its 32 kHz clock to its very accurate 26 MHz clock. This is especially important when the temperature varies substantially causing the 32 kHz oscillator to drift. This is illustrated in the following figure.

This plot is an example of the microNode performing a self-calibration of its 32 kHz oscillator. The pulses represent the TCXO being turned on periodically to perform the calibration. The microNode Wakes itself from Deep Sleep, Calibrates, and then falls back to sleep. Minimal power is consumed during this self-calibration process. As can be seen, the microNode does this approximately every 900 seconds.

Figure 10. microNode Oscillator Calibration: Current (Amps) vs Time (Seconds)

### 5.1.4 Idle State

Idle state has various sub-states but generally refers to a state where the microNode is "awake" and its system clock is on, the CPU is awake, but the RF is OFF.

### 5.1.5 RX State

The microNode turns on all its clocks, the main CPU and the RF in an RX-only state. The RF transceiver, in RX state, consumes a moderate amount of power.

### 5.1.6 TX State

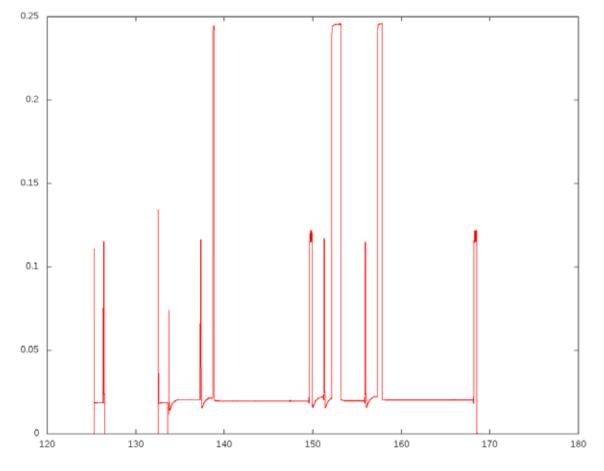

When the microNode transmits, it uses a variable transmit power that is correlated to its received RSSI. In this state, the microNode is likely at its highest power states, but this is somewhat dependent on RSSI. The worst case state (maximum power) is shown in Figure 11. This is at approximately 21.5 dBm output power. This is the microNode's highest power state.

# 5.2 System

As noted, the microNode can go through various states of Deep Sleep, Idle, RX, and TX. The plot shown in the following figure provides a representative microNode waking up and going through these states and transitions.

All ULPs are different and current consumption is affected by many factors.

- n Network coverage. How much TX power does a microNode need to transmit its data?

- n Temperature range

- n Operating Voltage

- n Continuous mode vs Slotted mode: What is the Uplink Interval?

- **n** Amount of data in the data model

- n Quality of Service (QoS) for data delivery

All of the factors indicated above must be examined carefully and plotted to understand the end result in current profiles and expected battery life projections.

Figure 11. Representative Current Consumption During Sleep, Idle, RX, and TX; x16 Spreading Factor (Amps vs Seconds)

The plot shown in the figure above represents the nominal transitions for the microNode from Deep Sleep, Idle, and Transmit states. In this case, a TX spreading factor of 16 is used. It is important that the Host designer understand the System operating profile, operating voltages, different operating modes of the microNode and the ultimate effect on System power consumption. Of course, this is especially true if a battery powered device is being considered.

The details of Host/Node messaging are typically not necessary for integrators to implement, given the functional interface provided by the *ULP Node Interface Library (UNIL) (010-0066-00)* and *UNIL API (010-0072-00)*. However, low-level understanding of the SPI protocol used may be critical in resolving Host interface issues.

For mid-level details of the messages that may be sent over this interface, refer to ULP Node Host Message Specification (014-0020-00).

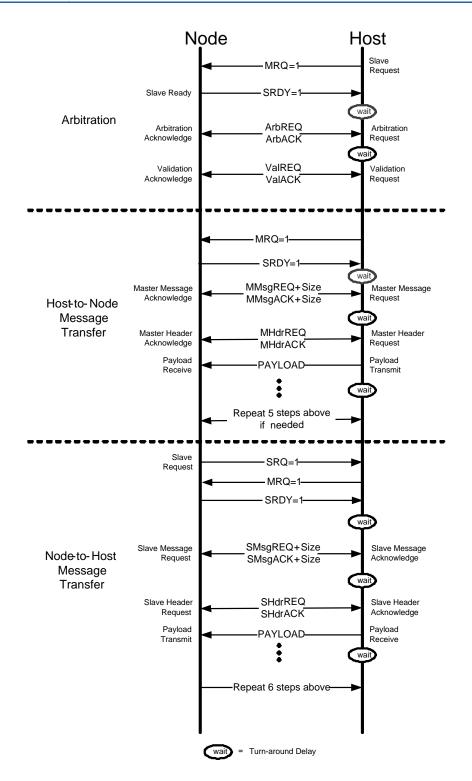

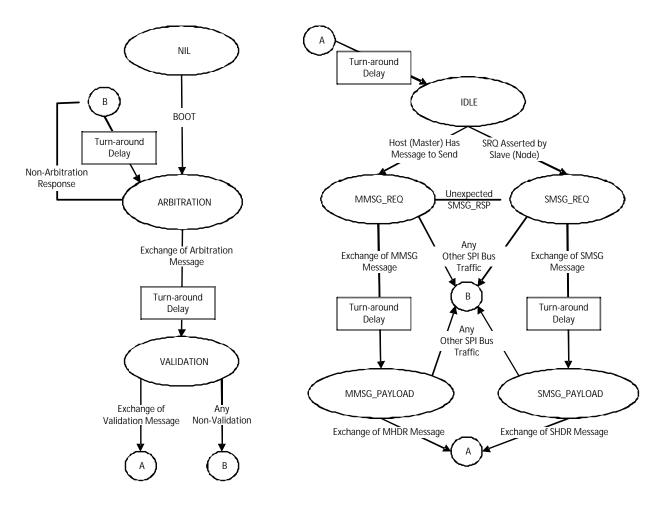

# 6.1 Arbitration

Arbitration is the process a Host uses to signal to the Node that it supports the On-Ramp Wireless bi-directional messaging protocol. The arbitration sequence is designed to reduce the probability that an arbitrary non-Host transfer sequence can mirror a valid arbitration sequence.

Arbitration consists of both Host and Node transmitting an arbitration request/reply pair. After a defined turn-around delay, both transmit a validation request/reply. The turn-around delay avoids race conditions between Host and Node and provides enough time to allow ISR execution to complete before the next SPI transfer.

If the Node does not reply to the Host request, the Host needs to wait for a turn-around delay and retry the arbitration request.

The Host must perform the arbitration sequence before any other SPI Bus communication can take place between the Host and the Node.

The Host must initiate this arbitration sequence on boot up. Additionally, the Host must perform the arbitration sequence when the Node sends to the Host an arbitration message. This can occur due to the Node going into Deep Sleep and then waking up. Since the Node requires the arbitration sequence after waking from Deep Sleep and since the Host is not aware of when the Node goes to Deep Sleep, the Host must be able to detect that the Node is requesting arbitration and the Host must then reset its Host interface state machine and perform arbitration. For more information on the Host interface SPI bus state machine, refer to section 6.3: Host Interface SPI Bus State Machine.

# 6.2 Message Protocol

Host-to-Node transfers use master message command pairs and Node-to-Host transfers use slave message command pairs. Both transfers use identical command sequences with only the encoding of the commands differing. The command sequence for a message transfer consists of a request/acknowledgement pair followed by a defined turn-around delay and then a message composed of a header pair and a payload.

Variable length payloads are supported by encoding the payload size in the second half of the message request. The second half of the message reply contains the available receive buffer

size. If the message payload size exceeds the receive buffer size, then a new request must be made after a turn-around delay with a payload size that does not exceed the receive buffer size.

After a successful message request transfer, the Host waits a turn-around delay and then initiates the transfer with a message header command. The payload immediately follows the header and, if necessary, is zero padded to match the payload size indicated in the message request.

After the payload, the Host waits a turn-around delay before proceeding with any other further messages.

The Host interface SPI bus is a standard SPI bus (with MISO, MOSI, CS, and SCLK) with the addition of three lines (MRQ, SRQ, and SRDY). These three additional lines are used to provide the Host with the ability to wake up the Node over the SPI Bus as well as providing the Node with the ability to prompt the Host to begin a SPI Bus transaction. The Node is also exceptional in that it must be the only slave present on the SPI Bus, since MOSI, CS, and SCLK must be undriven (tri-stated) any time that MRQ is low.

Before any message is communicated over the SPI Bus, the MRQ and SRDY lines must be high. The Host guarantees this by pulling the MRQ line high and waiting for the Node to pull the SRDY line high. The Host cannot proceed with SPI Bus communication until both of these lines are high. Once MRQ and SRDY are high, the Host, being SPI Bus master, can continue with a normal SPI Bus transaction.

When the Node wishes to communicate with the Host, it pulls the SRQ line high. The Host must have the ability to detect this and start a SPI Bus transaction (by first pulling the MRQ high and waiting for SRDY to go high). A standard SPI Bus transaction is described and illustrated in Figure 14.

Message exchanges between Host and Node are shown below in Figure 12.

#### Figure 12. SPI Master and Slave Message Sequences

In each of the request/acknowledge command pairs shown, the top command is transmitted by the Host (master) and the bottom command is transmitted by the Node (slave). The wait

bubbles indicate a predefined turn-around delay which provides ISR processing time and avoids race conditions between Host and Node.

### 6.3 Host Interface SPI Bus State Machine

This section illustrates the sequence of messages that can take place on the Host interface SPI bus. The design and implementation of the actual state machine on the Host software is up to the Host software designer. This diagram is provided to demonstrate the message sequence over the SPI Bus. Note the usage of the turn-around delay, which is required in between each step of message exchange. This delay is required by the Node and is currently defined as having a time of 200  $\mu$ s.

Figure 13. Host Interface SPI Bus State Machine

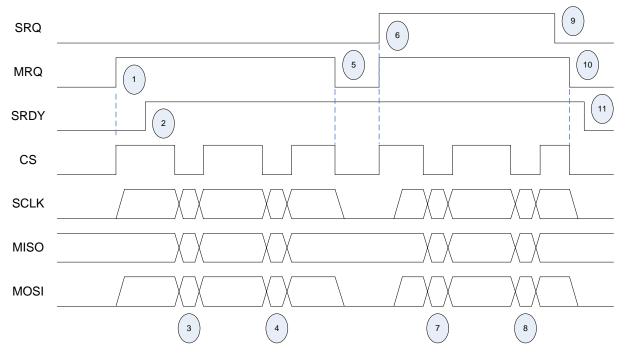

# 6.4 SPI Bus Timing Example

This section provides an example illustration of an exchange of messages first from master (Host) to slave (Node) and then from slave (Node) to master (Host). Each step in the timing sequence is described below:

#### Figure 14. SPI Timing Example

Note that MRQ state transitions must respect the timing requirements shown in Figure 6, Figure 7, and Figure 9.

The following items pertain to the numbered bubbles above:

- 1. Host has a message that it desires to send to Node. The first thing that it does is drive MRQ and CS high.

- 2. The Host then waits for the Node to drive SRDY high. No SPI bus transaction with the Node can occur before this.

- 3. After SRDY is high, the Host can start with the SPI data transaction. This is accomplished by driving the Node CS line low and then having the Host toggle the SCLK, and MOSI lines and having the Node toggle the MISO line according to the data to be transferred. The SPI Host interface specifies that first a MMsg pair is exchanged.

- 4. A MHdr pair is exchanged. Note that the payload of the message is appended to the MHdr.

- 5. The Host detects that the transaction is complete and that it does not wish to send more messages to the Node at this time. It drives the MRQ line low. Since MRQ is low, CS, SCLK and MOSI are tri-stated.

- 6. At some time in the future, the Node desires to send a message to the Host. It indicates this to the Host by driving SRQ high. Since SRQ is high, the Host drives MRQ and then CS high. It then waits for SRDY to go high, which it already is.

- 7. The Host starts the SPI data transaction. This is accomplished by driving the Node CS line low and then having the Host toggle the SCLK, and MOSI lines and having the Node toggle the MISO line according to the data to be transferred. The SPI Host interface specifies that first a SMsg pair is exchanged.

- 8. A SHdr pair is exchanged. Note that the payload of the message is appended to the SHdr.

- 9. The Node detects that the transaction is complete and that it does not wish to send more messages to the Host at this time. It drives the SRQ line low.

- 10. The Host detects that SRQ has gone low and that it does not have any messages to send to the Node. It drives the MRQ line low. Since MRQ is low, CS, SCLK and MOSI are tri-stated.

- 11. The Node drives the SRDY line low after MRQ goes low.

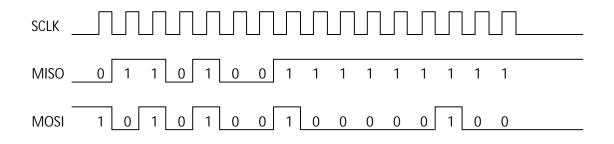

### 6.5 Host Message SPI Example

This section provides an example Host message exchange from master (Host) to slave (Node). In this example, the Host is sending a version request message.

This example is a zoomed-in view of the example provided previously in Figure 14. This section covers what happens in step 3, which includes the two SPI exchanges initiated by the Host.

With any SPI Host interface message, first an MMsg or SMsg pair must be exchanged. This pair contains information on how big the message is (from the message originator) and how much message queue space is available (on the message destination).

The following diagram shows such an example:

#### Figure 15. Host Message on SPI – MMsg Pair

The SPI clock edging is configurable with a polarity and phase. In order to communicate with the Node, the SPI clock polarity must be set to "the inactive state value of SPI clock is logic level zero" and the SPI clock phase must be set to "data is captured on the leading edge of SPI clock and changed on the following edge of SPI clock." This means that the data lines (both MISO and

MOSI) are read on the SCLK rising edge and are set or cleared on the SCLK falling edge, and is commonly referred to as CPOL=0, CPHA=0.

This illustration shows that the bit streams for MISO and MOSI are:

- **n** MISO: 011010011111111

- n MOSI: 101010010000100

These bits indicate:

MISO: from slave to master (01)

length of message=2 (10)

opcode=MMsgACK (1001)

buffer size=255 (11111111)

MOSI: from master to slave (10)

length of message=2 (10)

opcode =MMsgREQ (1001)

payload size=4 (00000100)

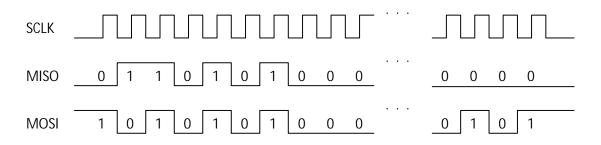

An MMsg pair or SMsg pair is immediately followed by the corresponding MHdr pair or SHdr pair. This is illustrated below:

#### Figure 16. Host Message on SPI – MHdr Pair

For purpose of brevity, this timing diagram shows only a portion of the data exchange. The complete bit streams for MISO and MOSI are as follows:

These bits indicate:

MISO: from slave to master (01)

length of message=2 (10)

opcode=MHdrACK (1010)

Hard coded byte=1 (0000001)

Unused Extra Data (0000.....0)

MOSI: from master to slave (10)

length of message=2 (10)

opcode =MhdrREQ (1010)

Hard coded byte=1 (0000001)

Payload:

length=8 (000010000000000)

message type=VERSION (0001010101000000)

trailing sequence (11110000111100001010010110100101)

- n The payload is Little Endian. The least significant byte is transmitted over SPI first.

- n All MHdr and SHdr payloads are terminated by the fixed trailing sequence 11110000111100001010010110100101.

- The example above shows a message going from master to slave, thereby having a

payload in the master to slave direction appended at the end of the MhdrREQ and no

payload appended at the end of the MhdrACK.

### 6.6 Host Message "Connect" SPI Example

This section provides an example Host message exchange of the CONNECT message from master/Host to slave/Node and subsequent response from the slave to the master.

The timing is similar to the timing illustrated in the previous section, but the data and length of data is different.

The steps involved in this exchange are as follows:

The Host desires to send the CONNECT message to the Node. As described in the previous section, this starts with an MmsgREQ/MmsgACK exchange over the SPI bus.

- n MISO: 0110100111111111

- n MOSI: 1010100100000110

These bits indicate:

MISO: from slave to master (01)

length of message=2 (10)

opcode=MMsgACK (1001)

buffer size=255 (11111111)

- MOSI: from master to slave (10)

- length of message=2 (10)

opcode =MmsgREQ (1001)

payload size=6 (00000110)

The MMsg exchange is followed by the MHdr exchange, which includes the payload of the CONNECT message.

These bits indicate:

MISO: from slave to master (01)

length of message=2 (10)

opcode=MHdrACK (1010)

Hard coded byte=1 (0000001)

Unused Extra Data (0000.....0)

MOSI: from master to slave (10)

length of message=2 (10)

opcode =MhdrREQ (1010)

Hard coded byte=1 (0000001)

Payload:

length=12 (000011000000000)

message type=CONNECT (001100100100000)

trailing sequence (11110000111100001010010110100101)

The payload of the message includes first the length, which is the number of bytes in the payload including the length and the trailing sequence.

It is followed by the message type, which in this case is 0x4032, and corresponds with CONNECT.

The CONNECT message has a 4-byte field that is a Boolean flag specifying whether or not the Node should send asynchronous SPI messages to the Host. To specify that the Node should send messages to the Host, the value of 0x00000001 is used.

It is then followed by the standard fixed trailing sequence.

This message exchange is followed by a Node-initiated message exchange for the purpose of sending an ACK of the CONNECT message to the Host. This starts with a SmsgREQ/SMsgACK exchange over the SPI bus.

- n MISO: 0110101100000100

- **n** MOSI: 101010111111111

These bits indicate:

MISO: from slave to master (01)

length of message=2 (10)

opcode=SMsgACK (1011)

buffer size=255 (11111111)

payload size=4 (00000100)

MOSI: from master to slave (10)

length of message=2 (10)

opcode =SmsgREQ (1011)

buffer size=255 (1111111)

The SMsg exchange is followed by the SHdr exchange, which includes the payload of the ACK message.

These bits indicate:

MISO: from slave to master (01)

length of message=2 (10)

opcode=SHdrACK (1100)

Hard coded byte=1 (0000001)

Payload:

length=8 (00001000000000)

message type=ACK (00110000000000)

trailing sequence (11110000111100001010010110100101)

MOSI: from master to slave (10)

length of message=2 (10)

opcode =ShdrREQ (1100)

Hard coded byte=1 (0000001)

Unused Extra Data (0000.....0)

# 7 microNode Configuration

Node Provisioning Tools (NPT) are used for Node provisioning. Complete provisioning of Nodes involves three distinct utilities:

- 1. Node Software Upgrade Utility (sw\_upgrade.py) This utility is used for upgrading the Node firmware.

- 2. Node Flash Configuration Utility (config\_node.py) This utility is used for programming Node flash configuration parameters.

- 3. Node Key Provisioning Utility (provision\_node\_keys.py) This utility is used for programming Node Over-the-Air (OTA) security keys.

For details about Node Provisioning Tools, refer to the NPT User Guide (010-0060-00).

## 8 Antenna Diversity

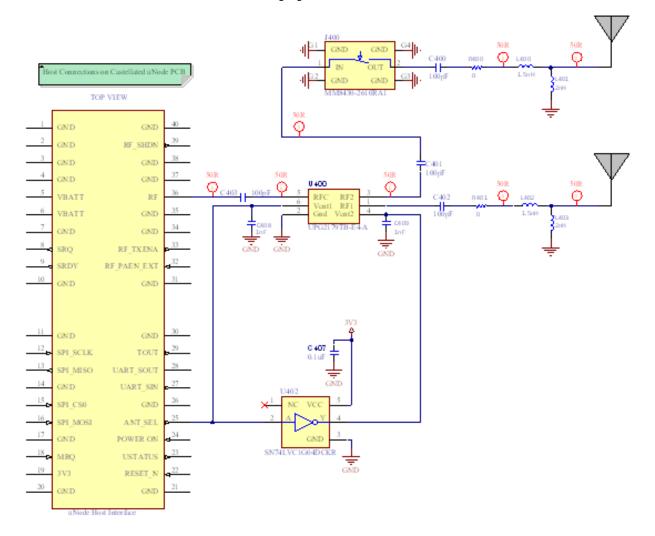

The microNode supports Antenna Diversity for optimal System performance. In many cases, the microNode and Host system are mounted in fixed locations that often experience nulls in the RF spectrum. Antenna Diversity can help with optimization of the RX and TX paths. In marginal coverage areas, an RF null could easily disadvantage the microNode to enforce it to transmit at a higher TX Power (more current) or causes network loss and frequent rescanning to reacquire the network (again, more current). These scenarios produce customer dissatisfaction as well as increased battery drain. On-Ramp Wireless has designed numerous diversity solutions and has found the circuit in shown in the following figure to work well.

Figure 17. Antenna Diversity Circuit

### 8.1 Antenna Design Considerations

Good antenna design is also crucial to success. It is important to consider some pertinent issues.

- n Ceramic antennas can work well but may sometimes have issues. Careful testing must be done to ensure desired gains and radiation patterns.

- n The product must be researched in conjunction to the AP, its deployment, and its antenna radiation pattern. Nominally the AP will be tower or mountain mounted with a downward tilt. The microNode and System may be mounted vertically or horizontally—forcing requirements on the microNode's optimal radiation pattern.

- n The antenna must be well matched and with low loss between microNode and antenna. It is important to follow the manufacturer's recommendations. The use of low tolerance ceramic capacitors and low tolerance thin film inductors are recommended. Examples include the Murata GJM series of capacitors and LQP series of inductors. If using stripline RF port feeds, care must be employed to ensure low loss and proper impedance. The antenna match may change when fully integrated into a product. Is advised to recheck the match after full integration. During tuning this may require the use of so called "RF pigtails" in an ad hoc fashion. If the Bill of Materials (BOM) cost will allow, a special connector can be implemented to support this verification/optimization.

- n Metallic objects nearby to the antenna can affect radiation gains, patterns, and power match. Typically anything within about 4-5 inches can affect the match significantly particularly if the nearby metal is resonant at 2.4 GHz. A little pattern distortion usually is not of too much concern unless deep wide angular nulls in the antenna pattern results. Other types of pattern distortion can be caused by absorptive losses due to lossy dielectrics nearby the antenna, which represents real power loss dissipated as heat in the loss object. This represents power that is completely lost and not radiated in a useful direction.

- Noisy System clocks with harmonics can fall into the operating band of the microNode and can be picked up by the antennas—degrading sensitivity, or causing Electromagnetic Compatibility (EMC) regulatory failures.

#### 8.2 Diversity Considerations

The operating frequency of the microNode is the ISM 2.4GHz band. This has a wavelength of 12.3 cm in air. For optimal null/peak diversity detection, the antennas must be separated by at least 2.5" (5cm). It is a good idea on the diversity antenna to orient it 90 degrees from the main antenna in order to improve on polarization diversity between antennas in addition to spatial de-correlation.

Practical ground plane-independent antennas are preferable to those that require the printed circuit board (PCB) copper for the antenna counterpoise. Examples of these are dipole antennas and some chip patch antennas. However these can be cost adders in certain cases. It should be noted however that some chip antennas that use the PCB for ground return have been shown to produce reasonable performance. Two examples of this are the surface mount offerings from Molex and Antenova.

- **n** The Antenova Rufa was found to have slightly better performance but about 2x higher cost. It is low profile but consumes more "XY" space. Cost is approximately \$0.70 for 10k pieces.

- **n** The Molex 47948-0001 works well. It stands about 4 mm tall but consumes much less "XY" space. Cost is approximately \$0.35.

# 9 Regulatory Considerations

The microNode uses a castellation for its RF port. This lowers the unit cost but also requires the System Integrator to certify the complete Host System for FCC, IC, ETSI, Japan, or other regions intended for sale into their respective markets. Whereas On-Ramp Wireless does not provide a modular certification for the module, it has gone through its own certification of the product to ensure it can be certified. The microNode was certified on an On-Ramp Wireless application platform—the "eHost." These documents and results are available to System Integrators to ensure that the product can be certified.

Additionally, On-Ramp Wireless has prepared certification guidelines on how to use the software and system tools required for certification. Some markets (such as FCC/IC) are fairly straight forward for certification and are largely TX Spectrum-based. Other markets (such as ETSI) require a much more sophisticated FER process involving an Access Point and Quick Start System. These procedures are defined in the document entitled *Node FCC/IC/ETSI EMC Compliance Test Procedures (009-0021-00)*. This document also includes hints and recommendations to help make the process as easy as possible. For more information about this document, see the list of documents referenced in Chapter 1: Overview.

### 9.1 Block Diagram

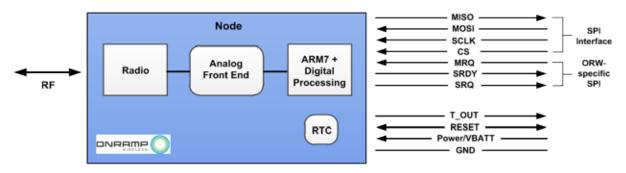

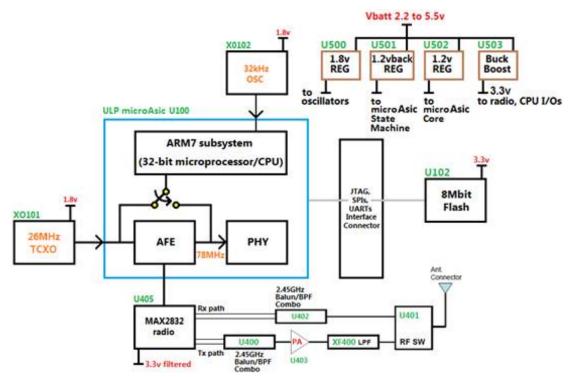

Some regulatory domains require a block diagram of the module for their documentation similar to that shown in the following figure.

Figure 18. microNode Block Diagram

### 9.2 Certifications

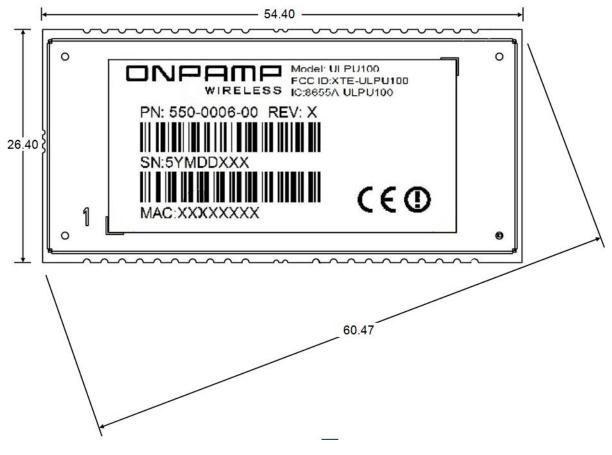

The microNode is designed to meet regulations for world-wide use. It is certified in the United States, Canada, and Europe as a Limited Single Module. The certifications currently achieved are listed in the following table.

#### Table 6. microNode Certifications

| Country       | Certifying Agency                                               | Certification(s)                                                                                                                                |  |

|---------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| United States | Federal<br>Communications<br>Commission (FCC)                   | <ul> <li>n 15.207 for powerline conducted emissions.</li> <li>n 15.215 for RF TX bandwidth, power, conducted and radiated emissions.</li> </ul> |  |

| Canada        | Industry Canada (IC)                                            | n RSS210e, includes FCC tests and IC-specific tests (RX radiated emissions).                                                                    |  |

| Europe        | European<br>Telecommunications<br>Standards Institute<br>(ETSI) | <ul> <li>a 300 440-1 and 440-2, ETSI Emissions.</li> <li>a 301 489-1, ETSI Immunity.</li> </ul>                                                 |  |

Additional details can be found in the document entitled *Node FCC/IC/ETSI EMC Compliance Test Procedures (009-0021-00)* referenced in Chapter 1: Overview.

The integrator of the final product is often required to do additional compliance tests. The integration application and market will determine specifics. The integrator is advised to consult with local experts in compliance certifications for complete information.

n FCC/IC

The final product may only need Class B unintentional radiator and powerline conducted emissions tests. This should be done with the actual production antenna.

n ETSI

Europe's system is a self-declaration system. There are no documents to submit or certification grants to obtain. One must have the passing test results available for all applicable requirements at any time if challenged.

**n** Other countries will vary.

#### 9.3 FCC Warnings

This device complies with part 15 of the Federal Communications Commission (FCC) Rules. Operation is subject to the following two conditions:

- 1. This device may not cause harmful interference.

- 2. This device must accept any interference received, including interference that may cause undesired operation.

Changes or modifications not expressly approved by the manufacturer could void the user's authority to operate the equipment.

- **NOTE:** This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation.

- **WARNING:** This equipment generates, uses, and can radiate radio frequency energy. If not installed and used in accordance with the instructions, this equipment may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- n Re-orient or relocate the receiving antenna.

- n Increase the separation between the equipment and receiver.

- **n** Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- **n** Consult the dealer or an experienced radio/TV technician for help.

#### 9.4 IC Warnings

The installer of this radio equipment must ensure that the antenna is located or pointed so that it does not emit RF field in excess of Health Canada limits for the general population. Consult Safety Code 6 which is obtainable from Health Canada's website <u>http://www.hc-sc.gc.ca/index-eng.php</u>.

Operation is subject to the following two conditions:

- 1. This device may not cause harmful interference.

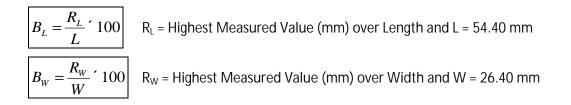

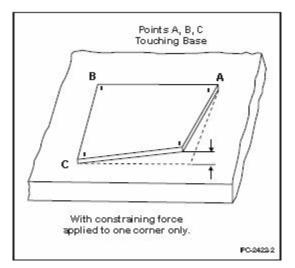

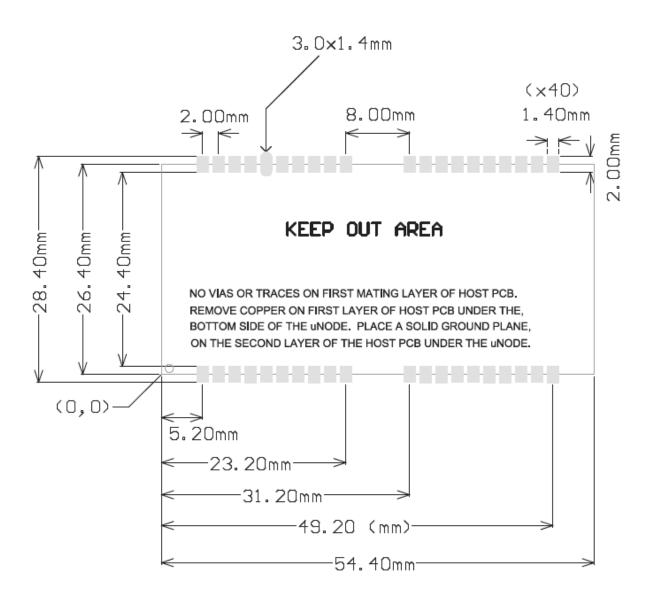

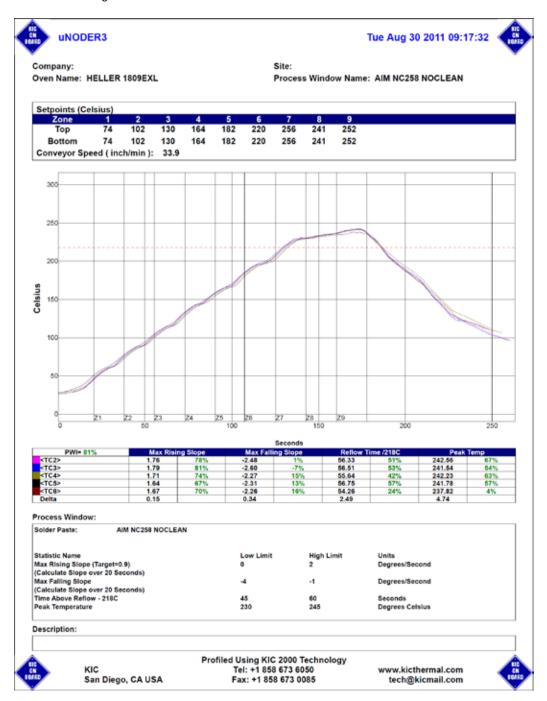

- 2. This device must accept any interference received, including interference that may cause undesired operation.