| Program: | Idea Labs Itron Riva Dev Mini           |

|----------|-----------------------------------------|

| Name:    | Itron Riva Dev Mini Hardware User Guide |

<u>Compliance Information (Certification Exhibit) – For further</u> <u>information see Appendix A.:</u>

| FCC ID:        | 2ANHYMINI1                 |

|----------------|----------------------------|

| FCC Rule Part: | 15.247                     |

| Model:         | Itron Riva Dev Mini        |

| Part Number:   | 575188r3                   |

| Manufacturer:  | Itron Inc                  |

|                | 2111 N Molter Rd           |

|                | LIBERTY LAKE WA 99019-9469 |

|                | P: +1509.9249900           |

|                |                            |

**ITRON PROPRIETARY & CONFIDENTIAL INFORMATION** For Reference Only, Printed: 3/6/2018 Page 1 of 49

## Contents

| Contents                                                     | 2  |

|--------------------------------------------------------------|----|

| List of Tables                                               | 4  |

| Change List                                                  | 5  |

| Introduction                                                 |    |

| Purpose of Document                                          |    |

| Definitions and Acronyms                                     |    |

| Reference Documents<br>Itron Riva Dev Mini Introduction      |    |

| Itron Riva Dev Mini Board Description                        |    |

| Mechanical                                                   | 12 |

| Major Components                                             | 12 |

| CPU Brief                                                    | 12 |

| Clocking                                                     | 12 |

| FLASH And RAM Brief                                          | 12 |

| RTC Brief                                                    |    |

| PIC Brief                                                    |    |

| PMIC Brief                                                   |    |

| Itron Riva Dev Mini Power Handling                           | 14 |

| Power Input                                                  | 14 |

| +5 VDC supply                                                | 14 |

| +5 VDC from USB                                              |    |

| +5 VDC from Expansion Header                                 |    |

| Power Output                                                 |    |

| +5 VDC to USB                                                | 14 |

| +3.3 VDC supply To Expansion Connector (3V3_EXP)             |    |

| User Power Supply Warning                                    |    |

| SYS_BOOT Configuration Jumpers                               | 15 |

| Startup – Riva Itron Riva Dev Mini Linux First Time Power On | 16 |

| direct Wiring, No Solderless Breadboard Expansion Board      |    |

| Power Supplies                                               | 16 |

| Create a console port                                        | 16 |

| Solderless Breadboard Expansion Board                        | 17 |

| Itron Riva Dev Mini/NIC Test Fixture                         | 18 |

| Pogo-pin and socket Information (spring test pins)           | 19 |

| Socket                                                       | 19 |

| Pins                                                         | 19 |

| <b>ITRON PROPRIETARY &amp; CONFIDENTIAL INFORMATION</b>      |    |

| Spear Pin                                                             |    |

|-----------------------------------------------------------------------|----|

| Chisel Triad Pin<br>Cup Pin                                           |    |

| Establishing a Linux Session                                          |    |

| Get into a terminal                                                   |    |

| Getting a Prompt, and what to do with it                              | 20 |

| Linux prompt                                                          |    |

| u-boot prompt                                                         |    |

| "C" stream (Continuous "C"s about 1 second apart)<br>No prompt at all |    |

| Pin Configuration and usage                                           | 21 |

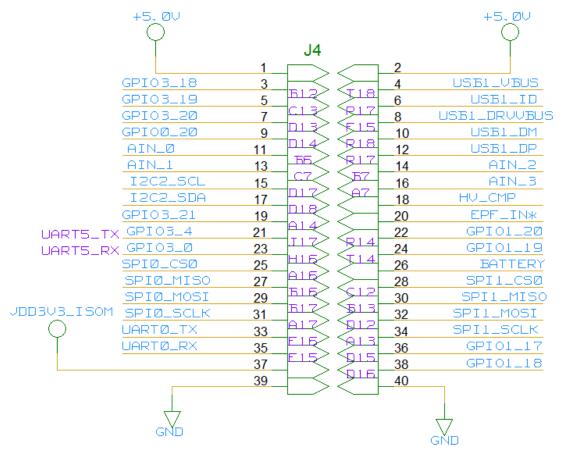

| Itron Riva Dev Mini Pinout                                            | 22 |

| Expansion Connector Pinout Description                                | 22 |

| Expansion Connector J4 Pinout                                         | 22 |

| P4 Pin Descriptions                                                   |    |

| P4-1 and 2 +5.0 VDC                                                   |    |

| P4-18 hv_cmp<br>P4-20 epf_IN* (This section requires work)            |    |

| P4-26 Battery                                                         |    |

| P4-37 3V3_EXP                                                         |    |

| Expansion Peripheral Port Usage                                       |    |

| SPI0                                                                  |    |

| SPI1                                                                  |    |

| AIN0AIN3                                                              |    |

|                                                                       |    |

| DSP TO A8 Interconnects<br>RF Connector and Cable                     |    |

| Downloading, If necessary (Linux)                                     |    |

| Erasing FLASH Image                                                   |    |

| Erasing FLASH Image From u-boot                                       |    |

| Erasing FLASH Image From Linux                                        |    |

| Itron Riva Dev Mini Test Procedure                                    |    |

| Equipment Required:                                                   |    |

| Minimal Operational Connections                                       |    |

| Mini DK Test Fixture                                                  |    |

| Mini DK Solderless Breadboard Adapter<br>Mini DK Direct Wiring        |    |

| Smoke/Boot Test                                                       |    |

|                                                                       |    |

**ITRON PROPRIETARY & CONFIDENTIAL INFORMATION** For Reference Only, Printed: 3/6/2018 Page 3 of 49

| LE     | D Testing                         | б |

|--------|-----------------------------------|---|

| GF     | PIO Testing                       | 6 |

| Ar     | D Testing                         | 6 |

| I2     | C2 Testing                        | 7 |

| SP     | I Testing                         | 9 |

| UA     | ART0 Testing40                    | 0 |

| US     | B1 Testing40                      | 0 |

| EF     | F* Testing4                       | 0 |

| H١     | /_CMP Testing40                   | 0 |

| Ba     | ttery Pin Testing40               | 0 |

| DSP Pr | ogramming (Requires Fixture)42    | 2 |

| USB-To | 9-Serial Adapters                 | 5 |

| USB Ca | bles47                            | 7 |

| Append | ogramming (Requires Fixture)      | 3 |

| OEM    | Labeling Requirements             | 8 |

| FCC    | Notices                           | 8 |

|        | xposure4                          |   |

| FCC-   | Approved Antennas (902-928 MHz)49 | 9 |

|        |                                   |   |

# LIST OF TABLES

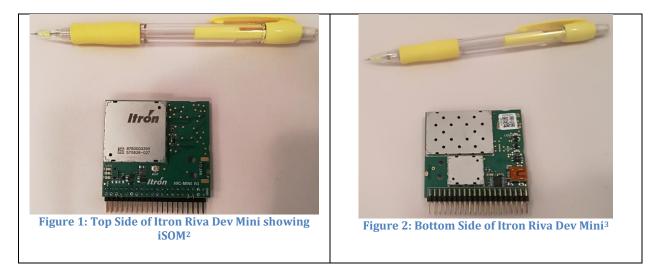

| Figure 1: Top Side of Itron Riva Dev Mini showing iSOM      | . Error! Bookmark not defined. |

|-------------------------------------------------------------|--------------------------------|

| Figure 2: Bottom Side of Itron Riva Dev Mini                | . Error! Bookmark not defined. |

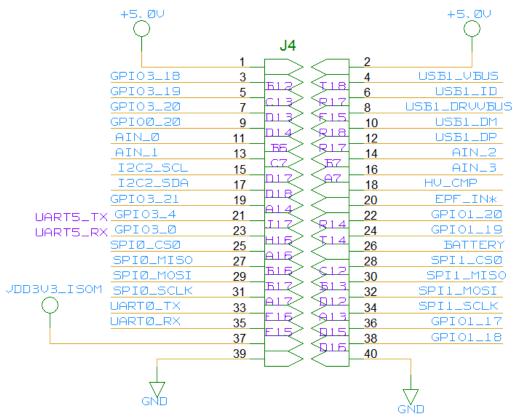

| Figure 3: Expansion Connector Pinout                        |                                |

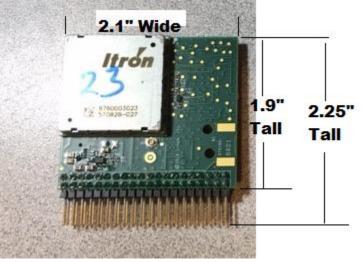

| Figure 4 - Revision 2 Itron Riva Dev Mini Board jumpers     |                                |

| Figure 5 - ACT NIC on Solderless Breadboard Expansion Board |                                |

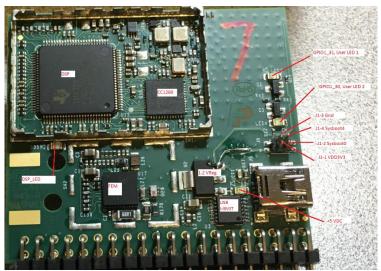

| Figure 6 - Itron Riva Dev Mini/NIC Test Fixture             |                                |

| Figure 7 - FTDI TTL-232R-RPI                                | 45                             |

| Figure 8 - FTDI TTL232R-3V3-WE                              |                                |

# **CHANGE LIST**

Rev 0.07 -

- 1. Added RF cable information

- 2. Added Solderless Breadboard section

- 3. Added Test Fixture section

- 4. Updated revision number and table of contents

Rev 0.09 -

1. Added text to pin table

Rev 0.10 -

- 1. Added information about USB cables

- 2. Updated revision number and table of contents

Rev 0.11 –

- 1. Changed document name from ACT Dongle to Riva Edge Mini Dev Kit

- 2. Added testing section

- 3. Cleaned up other sections

Rev 0.12 -

1. Added DSP Programming section

Rev 0x13

1. Altered text in HV\_CMP section

Rev 0x14

- 1. Updated pin out diagram for easier readability

- 2. Updated some text in Pinout description area

Rev 0.17

- 1. Corrected GPIO1\_17 Table information

- 2. Added info on testing UART5

- Rev 0.19

- 1. Switched Antenna and cables to reflect RP-SMA types

Rev 0.20

1. Enhanced Introduction section text.

Rev 0.21

1. Mentioned required pull-up resistors on I2C2\_SCL\_3.3 and I2C2\_SDA\_3.3

Rev 0.22

1. Added section on Expansion Connector J4 peripheral usage

Rev 1.0

- 1. APPENDIX A: FCC RELATED STATEMENTS added

- 2. 1<sup>st</sup> page edited with FCC related info (FCC ID, itd.)

- 3. Antenna info modified

Rev 1.01

1. RF Exposure statement added

## INTRODUCTION

The Itron Riva Dev Mini Kit is a complete Linux system on a module that includes an Itron ACT Radio suitable for addition to an Itron ACT RF network. It contains all hardware and comes loaded with firmware which allows the user to easily bring up a product within an ACT Network.

It is intended to be used in a laboratory environment for product development or used as a professionally installed OEM module1.

The end user will be a hardware developer who will ensure a proper power supply, ESD protection, physical enclosure, and antenna are provided to suit their product needs. The end user will also provide customized firmware to suit their application.

Only specified antennas may be used for integration of the OEM module to comply with FCC emission limits! Please refer to the antenna tables in this document. Antenna and RF Cable type and purchasing information are provided later in the document.

If the product is used as an OEM device within a user's product they will be responsible for all testing, qualifications and specifications to insure the Mini DK operates within all agency certifications that apply to the product. The end user is also responsible for all design related to safety designs and testing of safety features.

Only specified antennas listed in this document may be used for integration of the OEM module to comply with FCC emission limits! Please refer to the antenna tables in this document. Antenna and RF Cable type and purchasing information are provided later in the document.

The Itron Riva Dev Mini is designed by Itron and based on an Itron iSOM module which is based on a TI AM335X ARM Cortex Microprocessor. The iSOM module contains the processor, FLASH, RAM, power supply control, clock and other features. This iSOM module is mounted to a small board which includes all ACT RF circuitry to act as a USB NIC. There is also an expansion connector to allow the board to serve as the control and communications part of assorted devices.

<sup>&</sup>lt;sup>1</sup> Only specified antennas may be used for integration of the OEM module to comply with emission limits! Please refer to the antenna tables in this document.

For Reference Only, Printed: 3/6/2018

$<sup>^{\</sup>rm 2}$  Note that 40 Pin connector is not place in this picture.

<sup>&</sup>lt;sup>3</sup> Note that 40 Pin connector is not place in this picture and that the shields are left off of the RF and DSP sections.

**ITRON PROPRIETARY & CONFIDENTIAL INFORMATION**

## **PURPOSE OF DOCUMENT**

The goal of this document is to provide a hardware designer with enough information to use the Itron Riva Dev Mini board as a processing engine for assorted types of projects. It will cover the hardware necessary, at a high level, to guide a designer to the point where they can bring Linux up on the platform.

This document is intended to show the user how to interface the Itron Riva Dev Mini to a product based on the Muse platform. However, there will not be a comprehensive definition of how to use each type of GPIO to interface to assorted devices. This will have to be obtained through the A8 datasheet. Some examples will be given but most of the time only the parameters of the pin will be defined and its usage left up to the end product designer to reconfigure them as necessary. You may contact Itron for specific interface assistance.

Building Linux will also be covered in a separate document.

This document is not intended to inform the user how to use Linux or any subset of Linux commands. The coverage of Linux will only cover booting to a kernel prompt. This document is not intended to be a detailed usage guide to Linux or to the intricacies of the additions that Itron has made to Linux through its extensive IP library. These details are covered in separate documents.

This document is also will not cover Muse additions to the Linux Operating System or the Itron Over the Air protocols or how to use them. Contact Itron for specific assistance in these areas.

## **ESD Warning**

## **ESD Warning**

This product is intended to be treated as any other solid state component that you may use in an ESD save engineering or manufacturing environment. Many exposed pins do not have any additional ESD protection beyond what is provided by the integrated circuit that is directly connected to that pin. Treat it as you would treat any other high density low voltage electronic component.

This product, like all microcontroller products, uses semiconductors that can be damaged by electrostatic discharge (ESD). When handling, care must be taken so that the devices are not damaged. Damage due to inappropriate handling is not covered by the warranty.

The following precautions must be taken:

•Do not open the protective conductive packaging until you have read the following, and are at an approved anti-static work station.

•Use a conductive wrist strap attached to a good earth ground.

- •If working on a prototyping board, use a soldering iron or station that is marked as ESD-safe.

- •Always disconnect the microcontroller from the prototyping board when it is being worked on.

•Always discharge yourself by touching a grounded bare metal surface or approved anti-static mat before picking up an ESD - sensitive electronic component.

•Use an approved anti-static mat to cover your work surface.

| Term                   |                                                    | Definition                                                                                                                                                                                                                                       |

|------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPF                    | Early Power Fail                                   | An indication to the Linux system that the system requires a graceful shutdown.                                                                                                                                                                  |

| HV_CMP                 | High Voltage Compare                               | This is the circuit name for the power fail<br>sense input to the PMIC. It is used to create<br>PDN_POWERFAIL to insure the rails are<br>shutdown with proper sequencing.                                                                        |

| IP                     | Intellectual Property                              | For example, the extensions Itron has<br>created to extend the capabilities of the<br>platform in our products.                                                                                                                                  |

| MMPS                   | Main Motherboard Power Supply                      | This is the main power supply for the motherboard that the module is soldered to. At times in this document it is also referred to as +24VDC. This supply is the one that all power rails and power control signals are ultimately derived from. |

| PIC                    |                                                    | A Microchip microprocessor used to control<br>our power rails and provide other services to<br>the A8                                                                                                                                            |

| PLC                    | Power Line Carrier or<br>Power Line Communications | A method of transmitting and receiving data through the power lines.                                                                                                                                                                             |

| PMIC                   | Power Management IC                                | This chip contains multiple switching and LDO regulators and other power rail management circuitry.                                                                                                                                              |

| FTDI                   | Future Technology Devices<br>International LTD     | Manufacturer of USB to Serial converter cables                                                                                                                                                                                                   |

| Itron Riva Dev<br>Mini | This board                                         | Either of these two terms may be used to describe this board depending on how it is                                                                                                                                                              |

| ACT NIC                | This board                                         | used.                                                                                                                                                                                                                                            |

## **DEFINITIONS AND ACRONYMS**

## **REFERENCE DOCUMENTS**

- A8 Product Preview Document. (SPRS717B.PDF)

- A8 Technical Reference Document (SPRUH73C)

- PIC16(L)F1824/8 Datasheet (DS40001419E)

- NXP PCF85363A RTC Datasheet

- CDP 3.02 PICInCircuitProgramming.docx

- Riva ACT-RF Design and User Guide

- DS\_TTL-232R\_CABLES.pdf

- SMSC 9514 USB 2.0 Hub and 10/100 Ethernet Controller Chip

## **ITRON RIVA DEV MINI INTRODUCTION**

This section describes, at a very high level, the nature of the Itron Riva Dev Mini which is based on the Itron iSOM and includes ACT RF functionality to support the 870 MHz and the 920 MHz bands used for the proprietary Openway network. The RF section connects to an antenna via a UF.L connector<sup>4</sup>.

The Itron Riva Dev Mini has one mini-USB connector. Power can be derived from the external host when the board is operating as a USB device. Power can be provided to a device when the board is operating as a host. This is basic OTG operation but not certified as OTG by the USB group.

The Mini DK does NOT directly support Ethernet. An Ethernet port can be created by using a USB-to-Ethernet adapter.

The Itron Riva Dev Mini does NOT support EMMC or other external memory. It is possible to breakout J4 to provide a second USB port that can use USB based external memory such as a hard drive or a thumb drive.

A 40 pin expansion connector is provided to bring control and communications off the board. The pinout is shown below. This connector allows use of a standard ribbon cable to extend the signals to another board.

<sup>&</sup>lt;sup>4</sup> Only specified antennas may be used for integration of the OEM module to comply with emission limits! Please refer to the antenna tables in this document. RF Cable type and purchasing information is provided later in the document.

#### **Figure 3: Expansion Connector Pinout**

## **ITRON RIVA DEV MINI BOARD DESCRIPTION**

The Itron Riva Dev Mini takes the Itron iSOM module, combines it with an ACT RF module and expands it into a Complete Embedded Linux Communications system through an assortment of communications and control lines on an expansion header. The board is designed to be used as a development platform for embedded product prototyping or as the core processor NIC for an embedded product.

| Item                | Description                                  | Notes                                       |  |  |

|---------------------|----------------------------------------------|---------------------------------------------|--|--|

| Single 5VDC supply  | •                                            | All other rails are generated on the module |  |  |

| A8 Microprocessor   | ARM <sub>®</sub> Cortex <sup>™</sup> -A8 32- | 32KB L1 Cache                               |  |  |

| -                   | Bit RISC                                     | 256KB L2 Cache                              |  |  |

|                     | Microprocessor                               |                                             |  |  |

| Internal RAM        | Dedicated to boot and                        | 64KB Dedicated on-chip RAM                  |  |  |

|                     | security                                     |                                             |  |  |

| Internal RAM        | General Purpose                              | 64KB on chip RAM                            |  |  |

| Internal ROM        |                                              | 176K On-Chip boot ROM                       |  |  |

| Crypto Hardware     |                                              | AES, SHA, PKA and RNB                       |  |  |

| Accelerator         |                                              |                                             |  |  |

| External FLASH      | 2Gb as x16                                   | Code, file system and data storage          |  |  |

| External RAM        | 1Gb as x16                                   | Data storage                                |  |  |

| EEPROM              | 256 Bytes                                    | On PIC, accessible through I2C              |  |  |

| RTC                 | NXP PCF85363A                                | Very Low Power                              |  |  |

| External Interrupts |                                              |                                             |  |  |

| Early Power Fail    |                                              | For graceful Linux shutdown, Accessed       |  |  |

| Detection           |                                              | through the Expansion Connector             |  |  |

| Expansion Signals   | SPIO, SPI1                                   | Accessed through the Expansion Connector    |  |  |

|                     | 12C2                                         | Accessed through the Expansion Connector    |  |  |

| UART1, UART4        |                                              | Accessed through the Expansion Connector    |  |  |

| Assorted GPIOs      |                                              | Accessed through the Expansion Connector    |  |  |

| AIN_0AIN_3          |                                              | 4 ADC inputs, 12 Bits,                      |  |  |

|                     |                                              | Accessed through the Expansion Connector    |  |  |

|                     | UART0                                        | Linux Console                               |  |  |

|                     |                                              | Accessed through the Expansion Connector    |  |  |

|                     | USB0                                         | Mini-USB connector                          |  |  |

|                     | USB1                                         | Accessed through the Expansion Connector    |  |  |

|                     | JTAG                                         | Bottom of board Test Points marked JTAG     |  |  |

| PIC interface       | PIC Programming                              | Bottom of board Test Points Marked JPIC     |  |  |

Following is a list of the available hardware:

### MECHANICAL

The Mini is a compact board designed for small environments. It is available with a vertical connector, a right-angle connector or no connector. The connector can also be located on either side of the board to best suit a customer's needs.

Figure 4: Mini Board Dimensions

## **MAJOR COMPONENTS**

The following sections will list the major components on the Itron Riva Dev Mini and briefly describe them. Datasheets are available for more detailed information.

Caution!! Only specified antennas listed in this document may be used for integration of the OEM module to comply with FCC emission limits! Please refer to the antenna tables in this document. Antenna and RF Cable type and purchasing information are provided later in the document.

## **CPU BRIEF**

The Muse Platform contains a TI AM335X ARM Cortex Microprocessor. The processor contains a number of internal peripherals such as UARTs, SPI, I2C, USB, MMC, RTC and others. It also contains an internal boot ROM and internal RAM. The ROM and RAM are mostly used during the boot-up process and during security operations.

### CLOCKING

A 26MHz clock crystal is used to clock the AM335X. This is internally changed to 450 MHz using an internal PLL through Firmware. Other speeds can be selected depending on user requirements.

### FLASH AND RAM BRIEF

The system contains a Micron technologies MT29C2G24MAABAHAMD-5IT chip in a 130 ball package combining both FLASH and RAM on single chip. The Itron PN is 570725-003. This is a 2Gb NAND (x16bit) + 1Gb (x16bit) LPDDR.

## **RTC BRIEF**

The module contains a NXP PCF85363A RTC CHIP. It is a tiny Real-Time Clock/calendar with 64-byte RAM, alarm function, battery switch over and I2C-bus.

## **PIC BRIEF**

The module contains a Microchip PIC16LF1823, or PIC16LF1823 microprocessor to serve as the power rail control and to provide some system support features.

The PIC provides

- 1. Power Rail control

- 2. PON timing

- 3. Reset capability for the A8

- 4. EEPROM and some configuration storage.

## **PMIC BRIEF**

The TI TPS650250 PMIC provides 3.3VDC, 1.8VDC and 1.1VDC regulators to supply the requirements for the A8, RAM, FLASH and other components.

The PMIC also provides two LDO regulators. One provides 3.3VDC to the PIC and the other provides 3.3VDC to the Real Time Clock chip<sup>5</sup>. The two LDO enables are hard wired to a MIC826 voltage monitor chip and come on as soon as 5 VDC is applied to the module. The PIC will then sequence the power rails to the A8 and other circuitry.

**ITRON PROPRIETARY & CONFIDENTIAL INFORMATION** For Reference Only, Printed: 3/6/2018

<sup>&</sup>lt;sup>5</sup> As of the writing of this document the RTC chip was being changed. The original chip was an AM1805. I do not know what the new chip is at this time.

## **ITRON RIVA DEV MINI POWER HANDLING**

## **POWER INPUT**

The Mini requires a single +5 VDC supply. The input voltage should be within 4.75 VDC and 5.25 VDC.

## +5 VDC SUPPLY

The Itron Riva Dev Mini requires an input power supply of +5 VDC. This can be supplied through the mini-USB connector or through the expansion connector. The +5.0 VDC supply derives from one of two sources: U57, the mini-USB connector or from the expansion header pins 1 and 2. In either case this board can consume a peak of about 6 watts during full power transmissions.

#### +5 VDC from USB

When the Itron Riva Dev Mini is powered through the mini-usb connector it will provide +5 VDC power to the expansion connector pins 1 and 2. There is a circuit to limit the inrush current to prevent the host from triggering an over-current error. Once the initial period of current limiting ends the TPS2151 will allow up to 1.6 amps to flow from the USB Host. Note it is up the system firmware to provide the configuration and protocol operations to request the maximum required current from the host port. Careful attention to this detail must be followed for adding external circuitry.

### +5 VDC from Expansion Header

If the mini-USB port is not used as a power source +5 VDC may be supplied through the expansion connector pins 1 and 2. Currently, for the first prototype run, this will not provide power to the mini-USB port. It should be possible to put a diode where R21 is to allow powering the mini-usb from the expansion +5 VDC input.

### Power Output +5 VDC to USB

When powered from the USB connector the current limited +5 VDC is routed to the Expansion header to provide power for additional circuitry.

### +3.3 VDC SUPPLY TO EXPANSION CONNECTOR (3V3\_EXP)

There is a 3.3 VDC regulator connected to the +5 VDC signal to create an expansion power supply for use by the user. This rail is gated by a signal from the iSOM which tells the system that the iSOM is powered on and ready. This supply rail is limited to 250ma.

### **USER POWER SUPPLY WARNING**

When adding hardware to the interface connector it may be required to create additional power supply rails or higher current supplies. It is important to not connect any of these voltages to the Itron Riva Dev Mini before the A8 has its power rails in place and steady. Having a voltage on an I/O Pin on the A8 before it has its Vdd supply can cause permanent damage to the A8.

If you need to create your own power supplies make sure you gate them with 3V3\_EXP because 3V3\_EXP will not rise until the A8 supply rails are ready. This will prevent you from damaging the A8 processor or other circuitry.

**ITRON PROPRIETARY & CONFIDENTIAL INFORMATION** For Reference Only, Printed: 3/6/2018 Page 14 of 49

## **SYS\_BOOT CONFIGURATION JUMPERS**

The board comes configured to run its preloaded Linux on delivery. It is rarely necessary to change the configuration jumper or switches.

The A8 can boot from a number of peripherals or memory units. For instance, it can boot from a UART, USB, I2C, NAND or other sources. Often first stage of booting is used to load a small bootloader which will then download the full system code. The iSOM module brings two of the system boot configuration pins out on its connector. The two signals are SYSBOOT0, on J1 pins 1 and 2, and SYSBOOT4, on J1 pins 3 and 4.

Normally both jumpers will be in the off condition. But occasionally other modes may be required. For instance, if a download was interrupted leaving bad contents in FLASH the system may appear dead or not be presenting CCCC. You can configure Sysboot0 jumpered and Sysboot4 unjumpered to not allow booting from NAND thereby forcing a boot from UART0. This will present CCCC allowing you to xmodem the SPL file and then ymodem the u-boot program to get a u-boot prompt. Once at the prompt a "nand erase.chip" will restore the flash to a blank state and a complete reload can be started.

These two pins are connected to individual mini-jumpers and can be used together to determine the boot sequence the A8 will use. Typically, the both jumpers are left in the open position.

| Rev. 1   |          | Boot Order |       |       |         |                              |

|----------|----------|------------|-------|-------|---------|------------------------------|

| SYSBOOT4 | SYSBOOT0 |            |       |       |         |                              |

| J1 (3-4) | J1 (1-2) |            |       |       |         |                              |

| On = 0   | Off = 0  | UART0      | SPI0  | NAND  | NANDI2C | A8 Sends Cs                  |

| On = 0   | On = 1   | EMAC1      | MMC0  | XIP   | NAND    |                              |

| Off = 1  | Off = 0  | NAND       | NANDI | USB0  | UART0   | DEFAULT                      |

| Off = 1  | On = 1   | MMC0       | SPI0  | UART0 | USB0    | Force CCC to allow xmodem of |

|          |          |            |       |       |         | spl + mlo to get to uboot to |

|          |          |            |       |       |         | erase nand.chip              |

#### Figure 5 - Revision 2 Itron Riva Dev Mini Board jumpers

## STARTUP - RIVA ITRON RIVA DEV MINI LINUX FIRST TIME POWER ON

This section covers powering the board on and getting a prompt at the command line. The information below assumes you are starting with a fresh power-up having had your supply at 0VDC previously. This is the absolute minimal step to get an operational Linux console.

When shipped from the Itron factory the board is programmed with MLO, u-boot and a valid kernel. The PIC is also programmed. The two configuration jumpers are also placed in the basic operation configuration. So on receipt the board should boot into Linux without any changes.

The board can be powered up by using several different methods;

- 1. Connecting to a solderless breadboard expansion board

- 2. By direct wiring

- 3. On a Test Fixture

- 4. By connecting to another host board.

The following sections explain these methods in detail. Item 4 is not covered because it implies the user has developed their own host board.

#### DIRECT WIRING, NO SOLDERLESS BREADBOARD EXPANSION BOARD

Establishing a terminal session is a very simple process. Essentially only +5 VDC is required along with a console serial port. This is the minimal requirements to boot into a Linux system.

#### **POWER SUPPLIES**

Connect +5 VDC through the expansion connector. Leave this turned off for now.

#### **CREATE A CONSOLE PORT**

Connect a USB-To-Serial adapter to J4. Some adapters do not require 3.3 VDC so Pin 37 may be omitted based on the wiring guide provided by the USB adapter manufacturer. More information about USB-To-Serial adapters is provided later in this document.

| J4 Pin 33 | UART0_TX |

|-----------|----------|

| J4 Pin 35 | UART0_RX |

| J4 Pin 37 | 3.3 VDC  |

| J4 Pin 39 | Ground   |

## **SOLDERLESS BREADBOARD EXPANSION BOARD**

The easiest way to connect and power the board is to use the solderless breadboard expansion board. This board breaks the pins out spaced properly to allow the device to be plugged into a solderless breadboard. Even if not being used with an actual breadboard it provides the typical +5 barrel connector and 4-pin UART0 connection used on our development kits.

Figure 6 - ACT NIC on Solderless Breadboard Expansion Board

When inserting the Itron Riva Dev Mini/NIC into the expansion board be very careful of orientation. Note that the mating connector on the expansion board has a label in each side noting which shield should be visible and power orientation. The "iSOM side" is the side with a single square shield with the large Itron logo printed on it and the 57088-027 part number. The last 3 digits of the part number may vary depending on the iSOM configuration.

Simply plug the board into the expansion board, connect a +5 VDC power supply to the barrel connector (center +) and a serial port to the 4-pin connector. The system is now ready to boot.

## ITRON RIVA DEV MINI/NIC TEST FIXTURE

A test fixture has been designed to support programming and testing of the Itron Riva Dev Mini/NIC. Typically this will be an Itron factory item or an Itron development base. At this time, I do not know if it will be made available to customers.

This fixture provides the following capabilities:

- 1. A8 UART0 breakout and Other UARTs

- a. JM4 Breakout (40 Pin Expansion Connector) to LEDs and headers

- 2. A8 JTAG

- 3. DSP JTAG

- 4. USB1 Breakout and connector

- 5. +5 VDC Supply Connector

- 6. Miscellaneous test point breakout

There is a separate manual that describes this fixture in detail.

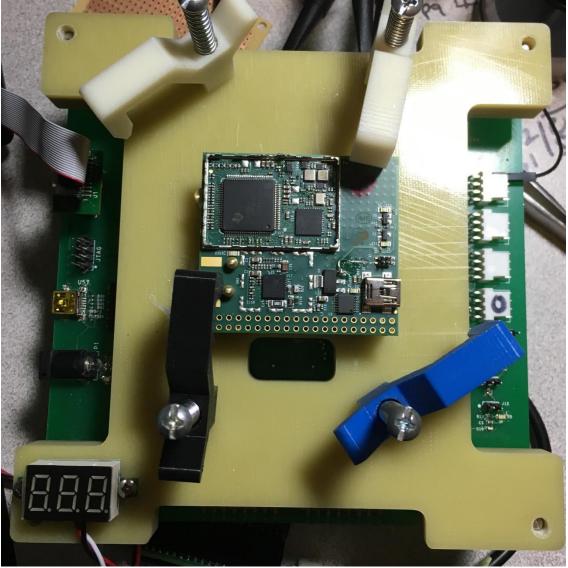

Figure 7 - Itron Riva Dev Mini/NIC Test Fixture

## **POGO-PIN AND SOCKET INFORMATION (SPRING TEST PINS)**

Pogo-pins are used for reliable temporary connection between the fixture and the Itron Riva Dev Mini Under test.

Do not turn the fixture upside down without something to hold the pins in. By their nature the pins slide in and out of the sockets easily. If you do turn a fixture upside down many, if not all, of the pogo pins may fall out.

Note that it is nearly impossible to clamp a board onto the fixture with all pins inserted. We recommend that you only insert the pins that are required for the particular function you are performing. For instance, it is not necessary to insert all pins for DSP or A8 programming. Pin usage is shown in the

following section including a map of pins by usage group for each function.

#### SOCKET

Sockets are used to hold the pogo-pins into the test fixture. They are soldered in but can be replaced. Different types of pins may be inserted into the sockets as needed.

The pogo-pin socket is QA Technology Company art number 100-SDN2502 a "100 Socket, Sgl PR, WireWrap". This socket is press fit into the alignment block and then goes into a PCB hole. The pin is soldered into the PCB. Because of the way these are mounted it is very difficult to remove or replace a socket.

The best method is remove a socket is to heat the respective pin at the PCB until the solder melts. Then pull the socket from the top of the alignment board through the alignment board.

#### PINS

Three types of pogo-pins are used for this fixture and one type of socket. Pins just slide into and out of the sockets with no force needed.

#### **SPEAR PIN**

This spear pin type used to mate to test points on the Itron Riva Dev Mini PCB. Many useful signals are brought out on test pins for diagnostics and programming. For instance, all usable GPIO are brought out to LEDs so they can be flashed for testing. The QA Technology part number for the spear pin compatible with this fixture is "100-PRN2541L".

#### **CHISEL TRIAD PIN**

The Chisel Triad pin type used to mate to holes in the Itron Riva Dev Mini PCB. Often the fixture will be used with a Itron Riva Dev Mini that does not have the 40 pin expansion connector populated. The QA Technology part number for the chisel Triad pin compatible with this fixture is "100-PRN2518L".

#### CUP PIN

This Cup pin type used to mate to through hole connectors on the Itron Riva Dev Mini PCB such as an expansion connector has been soldered onto a board. Cup pins mate to the bottom of the connector that protrudes through the bottom of the board. The QA Technology part number for the spear pin compatible with this fixture is "100-PRN2522L".

#### **ESTABLISHING A LINUX SESSION**

## **ITRON PROPRIETARY & CONFIDENTIAL INFORMATION**

For Reference Only, Printed: 3/6/2018 Page 19 of 49

### **GET INTO A TERMINAL**

Establish a terminal using a terminal emulator application. This can be done from Windows with something like Hyperterm or from Linux using minicom. In either case make sure you are connected to the proper serial port (the USB-To-Serial converter) and have set your configuration to 115200bps and N81.

### Getting a Prompt, and what to do with it

It is now time to power-on your board. Once power is applied you should get a prompt after the board finishes booting. Typically, as shipped from the factory, the system will load u-boot then Linux and after about a minute will stop at a Linux Prompt. Depending on the state of the firmware in the module you will get one of the following:

| Seen Onscreen        | Description     | Meaning                                                                                                                       |

|----------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|

| Linux Prompt         |                 | System is up and ready to use                                                                                                 |

| u-boot prompt        |                 | Linux must be loaded                                                                                                          |

| "C" character stream | Continuous "C"s | The PIC is loaded but MLO, u-boot and the kernel are                                                                          |

|                      | about 1 second  | not                                                                                                                           |

|                      | apart           |                                                                                                                               |

| Nothing              |                 | This is an undefined state. It is possible that power is<br>not being applied, the PIC is not loaded or the system<br>is bad. |

|                      |                 |                                                                                                                               |

#### LINUX PROMPT

This verifies that the PIC, MLO, u-boot and a valid kernel are all loaded and have operated successfully. At this point you can operate the system as any other Linux system.

#### **U-BOOT PROMPT**

This means that the PIC, MLO, u-boot are loaded but the kernel is not loaded. This could mean a kernel is not present in the file system or the kernel image is bad. Reload a kernel image using u-boot and restart the system.

### "C" STREAM (CONTINUOUS "C"S ABOUT 1 SECOND APART)

This means that PIC is loaded but MLO, u-boot and the kernel are not or have bad images. Reload the firmware starting with MLO and u-boot and verify you can boot with u-boot. Then reload the kernel.

#### NO PROMPT AT ALL

This is an undefined state. It is possible that power is not being applied, a signal is not tied, the PIC is not loaded, the kernel or u-boot are not loaded or corrupted. It can also mean that J1 is not placed correctly.

#### **PIN CONFIGURATION AND USAGE**

The A8 is extremely configurable including peripheral to pin assignments. Table 2-7 from TI document SPRS717B provides the list showing which peripherals can be assigned to which ball (pin) on the processor package. This table also lists other information about the signal such as its reset state, drive current, power domain and if there is an internal pull down or pull up resistor.

Most A8 GPIO pins can take the form of up to one of 7 different peripheral functions. Typically,<sup>6</sup>, at least in Linux configuration code, the pin is referred to using the name from the PIN name column of Table 2-7 from TI document SPRS717B. The signal you wish to put onto that pin is chosen by setting the mode of the port. So to use this pin as a general purpose IO you would set the GPMC\_A8 port to mode 7.

This versatility can make layout easier but it can also produce mutually exclusive situations. For instance, peripheral A may not be available if you are using peripheral B or if you require peripheral B to use a particular pin. TI provides a software application that allows you to define your pin usage and shows any conflicts. It will also export C code that can be used in u-boot or Linux to configure the pins according to what you have defined.

Typically, IO pin selection is done through u-boot or on kernel setup. At times the kernel definition may prevent certain pins from being changed from user space commands. But typically, it is possible to set the port type and direction through the console. Once set the console can be used to control the pins in some modes. For instance, you can raise and lower GPIO1\_24 if GPMC\_A8 is set to mode 7 as shown in the table below.

The following table is a copied section from the A8 Product Preview Document (SPRS717B.PDF). For detailed pin information and muxing information see that document.

| Pin Name | Signal Name  | Mode | Туре |

|----------|--------------|------|------|

| GPMC_A8  | GPMC_A8      | 0    | 0    |

|          | GMII2_RXD3   | 1    | Ι    |

|          | RGMII2_RD3   | 2    | Ι    |

|          | MMC2_DATA6   | 3    | I0   |

|          | GPMC_A24     | 4    | 0    |

|          | PR1_MII_RXD0 | 5    | Ι    |

|          | MCASP0_ACLKX | 6    | I0   |

|          | GPIO1_24     | 7    | 10   |

In some cases, Linux requires a pin for its usage or the pin may be used for a dedicated function based on the platform hardware design. This may make a particular pin unavailable for usage by the product motherboard designer

**ITRON PROPRIETARY & CONFIDENTIAL INFORMATION**

For Reference Only, Printed: 3/6/2018 Page 21 of 49

<sup>&</sup>lt;sup>6</sup> I say typically here because a programmer can define a new name and use that in their code. Also some names are slightly different than the default @defines for some pins.

## **ITRON RIVA DEV MINI PINOUT**

## **EXPANSION CONNECTOR PINOUT DESCRIPTION**

The following tables show the connections to the two expansion headers.

The modes column shows the possible modes the A8 can support for that pin. The red item indicates the mode that is selected by the default bootloader and kernel.

After each table is a detailed description of each pin that is not directly connected to a processor pin on the A8. Pins that connect directly to the A8 are described in detail in the A8 Product Preview Document (SPRS717B.PDF) or A8 Technical Reference Document (SPRUH73C). These documents provide much more detail than would be possible here.

### **EXPANSION CONNECTOR J4 PINOUT**

|     | Expansion Connector Pinout |     |      |      |               |                  |

|-----|----------------------------|-----|------|------|---------------|------------------|

| J4  |                            | LGA | Ball | Rail | LGA Name      | MODES            |

| PIN |                            | Pin | ZCZ  |      |               |                  |

| 1   |                            |     |      |      | +5.0V         |                  |

| 2   |                            |     |      |      | +5.0V         |                  |

| 3   |                            | 9   | B12  | 3.3  | GPIO3_18      | (0) MCASP0_ACLKR |

|     |                            |     |      |      | Test with:    | (1) EQEPOA_IN    |

|     |                            |     |      |      | ./gpio3_18.sh | (2) MCASP0_AXR2  |

|     |                            |     |      |      |               | (3) MCASP1_ACLKX |

ITRON PROPRIETARY & CONFIDENTIAL INFORMATION For Reference Only, Printed: 3/6/2018 Page 22 of 49

| j4<br>PIN         LGA         Ball         Rail         LGA Name         MODES           PIN         Pin         ZCZ         Image: Construction of the second secon                                                                                                       |        | <br> |             |      | Expansion Connector Pinout |                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-------------|------|----------------------------|-------------------|

| 4         -         T18         -         (1) MAC0_SDWP           5         11         C13         3.3         Test with:<br>-/gpio3_19.sh         (0) MCASP0_FSR           5         11         C13         3.3         Test with:<br>-/gpio3_19.sh         (0) MCASP0_FSR           6         -         P17         (0) MCASP1_FSX         (1) EQF0B_1N           7         10         D13         V6         GP103_20         (7) GP103_19           6         -         P17         USB1_ID         (0) MCASP0_AXR3         (3) MCASP1_FSX           6         P17         USB1_ID         (0) MCASP0_AXR1         (1) EQF0_JNDEX         (2) GP10_3_19           6         P17         USB1_DRVVBUS         (0) MCASP1_AXR0         (3) MCASP1_AXR0         (4) EMU3           7         10         D13         V6         GP10_2.20         (3) MCASP1_AXR0         (4) EMU3           7         130         D14         V6         GP10_2.20         (3) MCASP1_AXR0         (4) EMU3           9         130         D14         V6         GP10_2.20         (0) XDM_A EVENT_INTR1         (1) EQEP0_JND_2.20           10         R18         USB1_DP         (2) TCLKIN         (3) LICAUT2         (5) FR1_PRU0_PRU_PR0_PU_PRU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |      |             | Rail |                            |                   |

| $ \begin{vmatrix}                                     $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN    | Pin  | ZCZ         |      |                            |                   |

| 4         7         11         C13         3.3         GPI03.19<br>GPI03.19         (0) MCASP0_FSR           5         11         C13         3.3         GPI03.19<br>GPI03.19         (0) MCASP0_FSR           5         11         C13         3.3         GPI03.19<br>GPI03.19.sh         (1) MCASP0_FSR           6         11         C13         3.3         GPI03.19<br>GPI03.20.sh         (2) MCASP0_FSX           6         P17         USB1_ID         (7) GPI03.19         (0) MCASP0_AXR1           7         10         D13         V6         GPI03.20<br>GPI03.20.sh         (3) MCASP1_AXR0           7         10         D13         V6         GPI03.20<br>GPI03.20.sh         (2) MCASP0_AXR1           7         130         D14         V6         GPI03.20<br>GPI03.20.sh         (3) MCASP1_AXR0           9         130         D14         V6         GPI03.20<br>GPI03.20.sh         (3) MCASP1_AXR0           10         R17         USB1_DRVVBUS         (3) MCASP1_AXR0         (4) EMU3           9         130         D14         V6         GPI00.20         (0) XDMA_EVENT_INTR1           11         R18         AIN_0         TEst with:<br>-/// AIDSh and voltage input<br>(Vin <1.8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |      |             |      |                            |                   |

| 4         T18         USB1_VEUS         (7) CP103_18           5         11         C13         3.3         GP103_19         (0) MCASP0_FSR         (1) FQEP0B_1N           7         10         C13         3.3         GP103_19.sh         (2) MCASP0_AXR3         (3) MCASP1_FSX         (4) FMU2           6         -         P17         USB1_ID         (7) GP103_19         (9) MCASP0_AXR3         (3) MCASP0_AXR3         (3) MCASP0_AXR3         (3) MCASP0_AXR3         (7) GP103_19         (7) GP103_20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |      |             |      |                            |                   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |      |             |      |                            |                   |

| 5         11         C13         3.3         GPI03.19<br>Test with:<br>./gpi03_19.sh         (0) MCASP0_FSR<br>(1) EQEP0B_IN<br>(2) MCASP0_AXR3<br>(3) MCASP1_FSX<br>(4) EMU2<br>(5) PR1_PRU0_PRU_R31_5<br>(7) GPI03_19           6         P17         USB1_ID<br>Test with:<br>./gpi03_20.sh         (0) MCASP0_AXR3<br>(3) MCASP1_AXR3<br>(4) EMU2<br>(5) PR1_PRU0_PRU_R31_5<br>(7) GPI03_19           6         P17         USB1_ID<br>Test with:<br>./gpi03_20.sh         (0) MCASP0_AXR1<br>(1) EQEP0_INDEX<br>(2)<br>(3) MCASP1_AXR0<br>(4) EMU3<br>(5) PR1_PRU0_PRU_R32_6<br>(7) GPI03_20           8         F15         USB1_DRVVBUS<br>GPI00_20         (0) NDMA_EVENT_INTR1<br>(1)<br>(2) TCLKIN<br>(3) CLK0UT2<br>(4) TIMER7<br>(5) PR1_PRU0_PRU_R31_16<br>(6) EMU3<br>(7) GPI00_20           10         R18         USB1_DM         (0) NDMA_EVENT_INTR1<br>(1)<br>(2) TCLKIN<br>(3) CLK0UT2<br>(4) TIMER7<br>(5) PR1_PRU0_PRU_R31_16<br>(6) EMU3<br>(7) GPI00_20           10         R18         USB1_DM         Note: 1.8 VDC MAX           11         R17         USB1_DP         Note: 1.8 VDC MAX           12         R17         USB1_DP         Note: 1.8 VDC MAX           14         I.8         AIN_1<br>Test with:<br>./ad_2sh and voltage input<br>(Vin <1.8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4      |      | <b>T</b> 10 |      |                            | (7) GPI03_18      |

| Image: Section of the sectio        | 4<br>F | 11   |             | 2.2  |                            | (0) MCASDO ESD    |

| $ \begin{vmatrix}                                     $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5      | 11   | C15         | 5.5  | _                          |                   |

| Image: Second         |        |      |             |      |                            |                   |

| i         EMU2         (i)         EMU2         (i)         EMU2         (i)         FMU2         FMU2 <thf< td=""><td></td><td></td><td></td><td></td><td>./gpi03_19.511</td><td></td></thf<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |      |             |      | ./gpi03_19.511             |                   |

| 6         P17         USB1_ID         (5) PR1_PRU0_PRU_R30_5<br>(6) PR1_PRU0_PRU_R31_5<br>(7) GP103_19           6         P17         USB1_ID         (0) MCASP0_AXR1<br>(1) EQEP0_INDEX<br>(2)<br>(3) MCASP1_AXR0<br>(4) EMU3           7         10         D13         V6         GP103_20<br>Test with:<br>/gpi03_20.sh         (0) MCASP0_AXR1<br>(1) EQEP0_INDEX<br>(2)<br>(3) MCASP1_AXR0<br>(4) EMU3           8         P15         USB1_DRVVBUS         (0) MCASP0_AXR0<br>(4) EMU3           9         130         D14         V6         GP100_20<br>Test with:<br>/gpi03_20.sh         (0) XDMA_EVENT_INTR1<br>(1)<br>(2) TCLKIN<br>(3) CLKOUT2<br>(4) TIMER7<br>(5) PR1_PRU0_PRU_R31_16<br>(6) EMU3           10         R18         USB1_DM         (1)<br>(2) TCLKIN<br>(3) CLKOUT2<br>(4) TIMER7<br>(5) PR1_PRU0_PRU_R31_16<br>(6) EMU3           11         R18         AIN_0<br>Test with:<br>/d0 sh and voltage input<br>(Vin <1.8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |      |             |      |                            |                   |

| 6         P17         USB1_ID         (6) PR1_PRU_PRU_R31_5<br>(7) GPI03_19           7         10         D13         V6         GPI03_20         (0) MCASP0_AXR1           8         -         F15         USB1_DRVVBUS         (2)           9         130         D14         V6         GPI00_20           Test with:<br>./ggi03_20.sh         (2) TCLKIN         (3) CLKOUT2           (1) TEST         USB1_DM         (2) TCLKIN           11         R18         USB1_DM           11         R18         USB1_DM           11         R17         USB1_DP           12         R17         USB1_DP           13         R17         USB1_DP           14         R18         AIN_1<br>Test with:<br>./ad2.sh and voltage input<br>(Vin <1.8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |      |             |      |                            |                   |

| 6         P17         USB1_ID         (7) GPI03_19           6         P17         USB1_ID         (0) MCASP0_AXR1         (1) EQEP0_INDEX           7         10         D13         V6         GPI03_20         (0) MCASP0_AXR1           7         USB1_DRVEWS         (2) MCASP1_AXR0         (4) EMU3         (3) MCASP1_AXR0           8         F15         USB1_DRVVBUS         (7) GPI03_20         (7) GPI03_26           9         130         D14         V6         GPI00_20         (0) XDMA_EVENT_INTR1           (1)         CHO0_20         (1) XDMA_EVENT_INTR1         (1) XDMA_EVENT_INTR1         (1) XDMA_EVENT_INTR1           (2) TCLKIN         SCLKOUT2         (4) TTRN1         (2) TCLKIN         (3) CLKOUT2           (4)         F15         USB1_DM         (2) TCLKIN         (3) CLKOUT2           10         R18         USB1_DM         (2) TCLKIN         (3) CLKOUT2           11         VI         1.8< AIN_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |      |             |      |                            |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |      |             |      |                            |                   |

| 7         10         D13         V6         GPI03_20<br>Test with:<br>./gpi03_20.sh         (0) MCASP0_AXR1<br>(1) EQEP0_INDEX<br>(2)<br>(3) MCASP1_AXR0<br>(4) EMU3<br>(5) PR1_PRU0_PRU_R32_6<br>(7) GPI03_20           8         F15         USB1_DRVVBUS         (0) XDMA_EVENT_INTR1<br>(1)<br>(2) TCLKIN<br>(3) CLKUT2<br>(4) TIMER7<br>(5) PR1_PRU0_PRU_R31_16<br>(6) EMU3<br>(7) GPI00_20           9         130         D14         V6         GPI0_20<br>Test with:<br>./gpi03_20.sh         (0) XDMA_EVENT_INTR1<br>(1)<br>(2) TCLKIN<br>(3) CLKUT2<br>(4) TIMER7<br>(5) PR1_PRU0_PRU_R31_16<br>(6) EMU3<br>(7) GPI00_20           10         R18         USB1_DM         (7) GPI00_20           11         I.8         AIN_0<br>Test with:<br>./ad1.sh and voltage input<br>(Vin <1.8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6      |      | P17         |      | USB1_ID                    |                   |

| Image: Section of the sectio        | 7      | 10   |             | V6   |                            | (0) MCASP0_AXR1   |

| Image: Section of the sectin of the section of the section        |        |      |             |      |                            |                   |

| Image: Constraint of the second sec        |        |      |             |      | ./gpio3_20.sh              |                   |

| Image: Section of the sectin of the section of the section        |        |      |             |      |                            |                   |