# SECTION 19

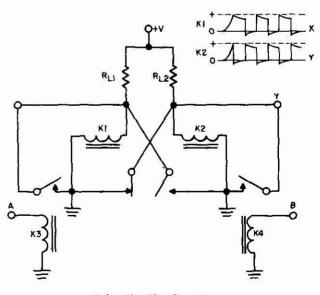

# LOGIC CIRCUITS

# PART A. ELECTRON-TUBE CIRCUITS

Part A of this section is reserved for electron tube logic circuits, which may be included in a later revision of the Handbook. No electron tube circuits are discussed in this issue."

;

# PART B. SEMICONDUCTOR CIRCUITS

### LOGIC POLARITY.

Computer logic is expressed by a form of two-value logic which is easily adaptable to the binary number system. Thus computer elements (circuits) have only two states, such as: the conduction or nonconduction of a circuit, the presence or absence of a hole on a card or paper, or the presence or absence of a magnetic field. The use of two-value logic also means that, basically, these states may assume a value of either 0 or 1. (While true or false could also be used, the numeric values lend themselves readily to computations and algebraic manipulations.)

In any electrical circuit, any two distinct voltages. or currents can be used to represent the two logic states of 0 and 1. For example, a negative voltage could indicate 0 and a positive voltage could indicate 1, or vice versa. Likewise, current flow into the circuit could indicate 0, and current flow out of the circuit could indicate 1. Similar results could be obtained with amplitude control, using small and large voltages or currents. Pulses could also be used in a like fashion, with a negative pulse indicating 0 and a positive pulse indicating 1; or 0 could be indicated by the absence of a pulse, in which case the presence of a pulse could signify 1. Many combinations of logic expressions are possible; they can also be used interchangeably, since each logic element (circuit) or operating entity can actually function independently as long as the desired result is achieved. Mixed logic systems are not used in large computers, however, since this practice would cause expensive circuit complications. Most present-day logic systems utilize polarity to define the circuit state, since positive and negative voltages are easily obtained and manipulated, regardless of whether the actual logic element (circuit) employs relays, switches, diodes, or transistors. Logic circuits can be divided into two general classes, according to polarity, namely positive and negative logic. As employed on logic diagrams, a signal may assume either the "active (or true)" state (logic 1), or the "inactive (or false)" state (logic 0). The electrical signal levels used and a statement concerning whether positive or negative logic applies are usually specified explicitly on the individual logic diagrams by the manufacturer or the logic designer.

In practice, many variations of logic pointity are encloyed: for example, from a high-positive to a lowpositive voltage, or from positive to ground; from a high-negative to a low-negative voltage, or from negative to ground; and mixed polarity, from a high posirive to a negative (below ground) potential, and vice verse. A brief discussion of the two general classes ot polarity is presented in the following paragraphs. Each of the logic circuit disc isions also given in this section will be based upor the form of logic polarity best suited for simpla explanation of the circuit action. Diode logic circuits will be discussed separately from transistor logic circuits in Part P of this potton, and putchy medianical curvaits

#### 19-B-1

involving only switches and relays will be covered under "Mechanical Circuits", Part C of this section.

### POSITIVE LOGIC.

### APPLICATION.

900,000,102

Positive logic polarity is usually more adaptable to the use of NPN type transistors.

### CHARACTERISTICS.

The input activates the logic element only when it is of positive polarity.

The output of the logic element is also of positive polarity (except when it is purposely inverted).

Operation may be from a high positive to a low positive voltage or current, or positive against ground (the high positive voltage or current usually activates the circuit).

### CIRCUIT OPERATION.

Positive logic polarity is defined as follows: When the logic 1 state has relatively more positive electrical level than the logic 0 state, and the circuit is activated (operated) by the logic 1 signal, the logic polarity is considered to be positive. The following typical examples illustrate the manner in which positive logic may be employed.

| Example 1: | Logic 1 = +10 volts |

|------------|---------------------|

|            | Logic D = 0 volts   |

| Example 2: | Logic 1 = 0 volts   |

|            | Logic 3 = -10 volts |

In both examples the logic 1 state is always more positive than the logic 0 state, even though in example 2 the logic 0 state is negative. The previous statements and definitions are particularly appropriate for d-c switching circuits, but also apply to a-c circuits as well. For example, a positive pulse can be used to simulate a positive voltage, and a negative pulse can be used to simulate a negative voltage. However, such complexity is unnecessary, since the absence of a pulse can signify the logic () state and the original definition of positive polarity will still apply. That is, the logic 1 state is more positive than the no signal (or logic 0) state.

As normally used, positive logic is more adaptable to NPN type transistors because of the SPt polarity. requirements. Since a positive collector voltage is required to reverse-bias the NPN transistor, operation of the transistor produces either a low or a high positive autput voltage. Thus by using direct counling, a fully transistorized positively polarized d-a system can be developed, thereby eliminating interstage coupling capacitors and any possible waveform distortion effects. The functioning of direct-coupled tran. sistor louid (DCTL) dircuits is discussed later in this section. The use of positive logic, however, is not restricted to NPN transistors, since PNP transistors can be used in a-d dystems using the commonemitter (CE) contiguration, which invertes the input polarity in the output circuit. The use of NPN iconsistors merely makes the design of d-c positive logic

100 90 8 O to 1 55

ORIGINAL

NAVSHIPS

900,000,102

LOGIC CIRCUITS

circuits easier and simpler, so that normally positive logic is associated with NPN transistors, while negative logic is associated with PNP transistors. At present, however, it is unimportant which type of logic polarity (positive or negative) is used, since logic components and circuits are available for all types. In fact, by using a form of mnemonic (symbolic) notation, such as H for the high or active state (1), and L for the low or inactive state (0), logic design may be completed and circuitry devised without concern for the polarity or levels used. Once the logic design is completed, standard circuits of the proper type and polarity for the components and level to be used are selected, and the unit is constructed.

#### FAILURE ANALYSIS.

Since positive logic polarity involves the operation of circuits by means of a more positive voltage or signal, it is evident that under normal operation such circuits would be activated by a positive signal and would produce a positive output. However, while the previous statement is generally true, it may not apply to a particular circuit because of special design considerations. Reference should be made to the proper logic circuit (schematic) and flow diagrams to determine the polarity and levels that activate the suspected circuit.

### NEGATIVE LOGIC.

#### APPLICATION.

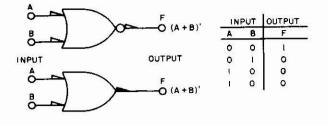

Negative logic polarity is usually more adaptable to the use of PNP type transistors.

### CHARACTERISTICS.

The input activates the logic element only when it is of negative polarity.

The output of the logic element is also of negative polarity (except when it is purposely inverted).

Operation may be from a high negative to a low negative voltage or current, or negative against ground (the high negative voltage or current usually activates the circuit).

### CIRCUIT OPERATION.

Negative logic polarity is defined as follows: when the logic 1 state has relatively more **negative** electrical level than the logic 0 state, and the circuit is **activated** (operated) by the logic 1 signal, the logic polarity is considered to be negative. The following typical examples illustrate the manner in which negative logic can be employed.

| Example 1: | Logic l = 0 volts                |

|------------|----------------------------------|

|            | Logic $0 = +10$ volts            |

| Example 2: | Logic $1 = -10$ volts            |

| 2          | Logic 0 = 0 volts                |

| 22 222 222 | 그 문서 바람이 있는 것을 들었는 것이 바람이 많이 했다. |

In both examples the logic 1 state is always more negative than the logic 0 state, even though in example I both states are in the positive region. While the above definitions of logic polarity are particularly applicable for d-c switching circuits, they also apply to a-c circuits as well. For example, a negative pulse can be used to simulate a negative voltage, and a positive pulse can be used to simulate a positive voltage. Such complexity is unnecessary, however, since the absence of a pulse can be assumed to indicate the logic 0 state. Thus only a negative pulse is necessary, and the above definitions will still apply.

As normally used, negative logic is more adaptable to PNP type transistors because of the PNP polarity requirements. Since a negative collector voltage is required to reverse-bias the PNP transistor, operation of the transistor produces either a low or a high negative output voltage. By using direct coupling, a completely negatively polarized d-c system can be developed, and interstage coupling capacitors can be eliminated. Thus, besides the saving of the cost of a component, waveform distortion due to phase shift through the coupling capacitor can be minimized. Operation may also be speeded up, since it is no longer necessary to wait for the charge and discharge of the capacitor. Direct-coupled transistor logic (DCTL) circuits are discussed later in this section. Negative logic is not limited to PNP transistors, since the common emitter configuration (in an a-c coupled circuit) can invert the polarity of the input signal and provide a negative output from an NPN transistor. The use of PNP transistors merely makes the design of d-c negative logic circuits easier and simpler, so that negative logic is normally associated with PNP transistors, while positive logic is associated with NPN transistors. Since logic circuits and components are available for all types of polarity, there is no particular reason why negative logic should be used in preference to positive logic. In fact, for design reasons some special computers use both (mixed) positive and negative polarity. The usual practice is to design the logic without regard to polarity or levels. Once designed, the proper type of polarity and levels for the standard logic circuit and components to be used is selected, and the unit is constructed.

### FAILURE ANALYSIS.

Since negative logic polarity involves the operation of circuits by means of a more negative voltage or signal, it can be reasoned that under normal operation the logic circuit must be activated by a negative signal and that the output must also be negative. However, since special design considerations sometimes negate this reasoning, it is necessary to refer to the schematic and flow diagrams to determine the actual polarity and levels which activate the suspected circuit. NAVSHIPS

0967-000-0120

### DIODE LOGIC.

Diode logic (DL) concerns basic logic circuits utilizing the diode as the operating element. Functionally, logic circurts are broken down into simple basic circuits such as the OR gate, and the AND gate, which have their counterparts for each type of logic. Thus transistor logic also has its OR gate and AND gate, plus additional circuits such as the NOR gate and NAND gate. Combinations of these basic circuit building blocks, in turn, form additional but more complex configurations. For example, a combination of AND and OR circuits forms a half-adder, and two half-adders form a full-adder of adder. Thus the logic blocks are arranged to perform the desired circuit functions of the final computer design. In addition to diode and transistor logic, other forms of logic utilizing diodes or transistors are encountered. For example, where only d-c is involved, directcoupled transistor logic (DCTL) is usually employed to avoid losses in coupling circuits. Where a-c pulses are employed resistor-transistor logic circuits (RTL) or resistance-capacitance transistor logic (RCTL) are usually used (this is similar to the resistance coupling used in audio amplifiers). Therefore, each basic logic group has its simple basic OR and AND circuits, plus any other circuits peculiar to that type of logic. In most cases, the more involved circuits are made up of combinations of CR, AND, and NOT circuits. While the operation of these basic circuits may be slightly different, they are similar: For example, transistor logic can easily be visualized by considering the emitter-base junction as an input diode and base-collector junction as the output diode.

Diode logic is the simplest type of logic, corresponding, in general, to switch operation. Either the switch is ON (diode conducting) or it is OFF (diode non-conducting). It is usually used where signals of only two levels are involved (the off level and the on level) although three-level circuits may be arranged, if desired. Either negative or positive logic may be use with the same circuit arrangements, except that the diode connections must be reversed. While it is important that the forward resistance of the diode be low, it is more important that the reverse resistance be very high. Thus when diodes are parallel-connected their paralled reverse-resistance is still high, and leakage and operating power requirements are low, also, false triggering will not occur. Another advantage to the use of diode logic is that no inversion of the output signal occurs. Thus it is unnecessary to add an inverter circuit to return the stanal to its original polarity; this helps simplify computer design.

The diede also lends itself to multiple arrangements where a combination of inputs is used to produce a single output, usually called a decoding matrice or matrix. Theversely, an arrangement with single inputs producing a multiple output is known as an encoder matrice or matrix. In general, when arranged in a rectangular arrangement the matrice becomes a rectangular matrice, regardless of function, that is, it may be either an encoder or decoder. Each of these basic circuits and arrangements are fully discussed in the following paragraphs.

# OR GATE.

# APPLICATION.

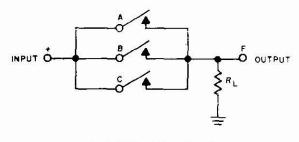

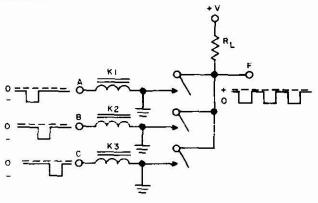

The diode OR gate is a basic logic circuit which produces an output when either input is activated, and when both inputs are simultaneously activated (inclusive OR). It replaces the relays and electron tubes used in earlier computers.

#### CHARACTERISTICS.

May use either positive or negative logic.

May be operated by short duration pulses, or by static d-c voltage levels representing inputs and outputs.

Represents logic addition (1+0-1).

Corresponds to an oppositely polarized AND gate.

Output never exceeds the input (no amplification is obtained.)

#### CIRCUIT ANALYSIS.

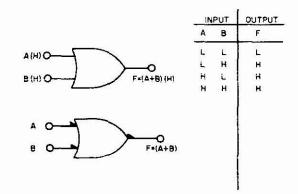

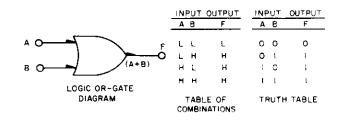

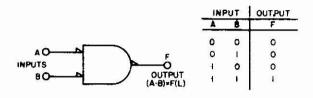

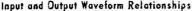

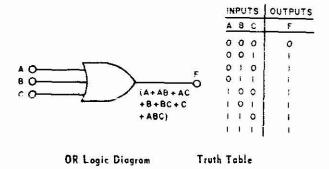

General. Logic circuits differ from basic electronic circuits in their general treatment. Through the use of standard logic symbols (see MIL STD 00806C (NAVY) for a complete list), a block-diagram type of presentation may be used, instead of the conventional schematic representation with which the ET is more familiar. Thus the signal path and operation can be followed, or considered, without regard to the actual electronic circuit operation. Typical standard symbols used to represent a **positive** logic OR circuit are shown below, accompanied by a truth table of possible combinations.

Positive OR Gate Symbols Table of Combinations

The (H) notation means high level or positive logic and in the lower symbol this is indicated by the tilled-in (or solid) right triangles. The inputs are A or B. The output, F shows in Boolean algebra notation the result (A + B), where the + sign indicates CR (addition). The table of combinations shows every possible combination of input and output and is therefore, called a truth table. When either input A or input B (or both) are at a relatively high level, the output, F, is also at a relatively high level. When both A and B are at a low level, so is output  $\Gamma$ .

### 0710-000-7960

SAIHSVAN

### LOGIC CIRCUITS

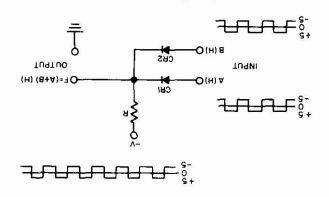

to any si aid the true is not inverted (this is true of pected, since the diode itself has no inherent gain. Note, than the input, when using diode logic. This is to be exthe actual OR gate output is always slightly less in value considered to have zero resistance. Thus, at all times, cussed above are for the idealized case where the diade is -zib salqmore and the caratance, and the examples disevident that no gain results. Actually, the conducting considered to be a logic I in this example. It is clearly either A or B, the output at F will be +5 volts, which is input voltage applied the anode. If +5 volts is applied R. Hence the only voltage existing as an output will be the either A or B the entire bias source will be dissipated across of R to ground. Thus, it sufficient voltage is applied to be dropped across R. The output is taken from the dicde end volts. A larger current will flow and a greater voltage will will be as if the anode of the associated diode were at +35 Similarly, it 5 volts positive is applied to A or B, the effect be effectively 10 volts positive with respect to the cathode. Volts applied and assuming V to be -30 volts the anode will by an equivalent positive voltage will flow. That is with -20 It negative, but less than -V a current equal to that produced diade will be at equal potentials and no current will flow.

tor actuating the next logic circuit. of sufficient amplitude and of the proper phase (or polarity) it is only necessary for the logic circuit to provide a signal tolerable in the communications circuit is acceptable. Thus is that in the logic circuit, distortion which would be inbetween logic circuits and conventional electronic circuits amplitude signals, both diodes will conduct. The difference determines which diode shall conduct. For exactly equal inputs A and B, simultaneously, the larger amplitude signal non-conducting diode. Therefore, when signals are applied the output pulse, a reverse bias of this value is applied the imately the same shape. Because the input pulse appears as tinue for the duration of the trigger pulse and be of approxan output, positive logic is used. The output pulse will conin every case a positive input signal is required to produce put will be the highest voltage applied to CRI or CR2. Since When both diodes are activated simultaneously, the out-

all diode logic circuits and helps simplify design).

The positive OR circuit is sometimes referred to as a negative AND circuit, because if the polarity of the input trigget is reversed so that a negative signal represents a 1 and a positive signal a zero, a combined input will produce a negative signal a zero, a combined input will produce a polarity it is necessary to adopt certain conventions to avoid signals produce a 1, and relatively negative signals produce a 0, we may call the OR circuit previously discussed above sume this convention throughout the remainder of the circuit discussions in this Chapter of the Handbook.

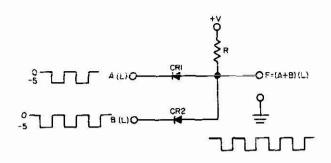

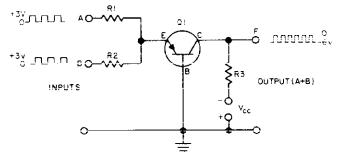

A two input negative OR gate is shown in the accompanying illustration. The gate consists of two diodes, CRI and CR2, with current limiting resistor, R, connected as shown in the schematic.

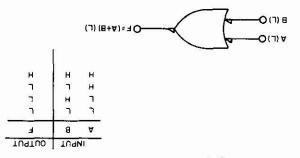

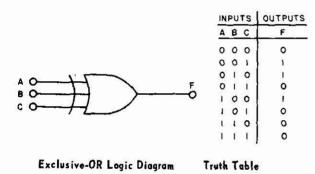

> When negative logic is used, the symbol shown below and turk table apply.

> > ELECTRONIC CIRCUITS

Regative OR Gate Symbol Table of Combinations

The (L) notation means low level or negative logic, and the small open right triangle at the inputs and outputs on the symbol indicates they are low (If filled-in they are high). When the triangles are used the parenthetical (L) notation may be omitted. The table of combinations shows that for all inputs but one, the output is low. When both inputs are inputs but one, the output is low. When both inputs are inputs by high, then the output is olso high.

Circuit Operation. A two-input positive OR gate is shown in the accompanying illustration. The gate consists of two diodes, CR1 and CR2, and current limiting resistor, R, connected as shown in the schematic.

Two Input Positive OR Gate

When the OR gate is inactive (no inputs) it is forward bigged by the large negative voltage applied the cathode, and usually a small negative voltage, representing O, is applied to the anode and a small curtent flows through either CRI or CR2. Actually, a reverse curtent flows through either CRI or upon the reverse leakage of the diode, this current, however, is so small in most cases that it may be neglected. Thus upon the reverse leakage of the diode, this current, however, is applied to either A or B, more current flows through R depending upon the amount of voltage applied, and its polardepending upon the amount of voltage applied, and its polarity. If a voltage of exactly -V is applied, both sides of the ity.

#### **Two Input Negative OR Gate**

The negative OR gate operates inversely to the positive OR gate. Thus, when inactive, it is held so by inputs approximately equal to +V and no conduction occurs. This represents the 0 state. When a negative 1 is applied either A or B, the respective diode is forward biased and current flows through R. Electron flow is in such a direction that the output end of resistor R is negative, and the input signal appears as the output. While one diode is conducting, the other diode is reverse biased by the amount of the output signal; thus it cannot conduct unless a greater negative voltage is applied its input. When both inputs are simultanecusiv activated with a negative signal, it equal in amplitude both diodes conduct. This is the case of the inclusive OR. If the polarities of the 0 and 1 are reversed, the negative OR gate will function as a positive AND gate. Thus the proper conventions must be used to produce the desired function. When the 1 input is relatively more negative than the 0 input, the above discussion, the symbol, the schematic, and the truth table for the negative OR gate apply.

#### FAILURE ANALYSIS.

General. In the basic OR circuit only three parts are involved and it is a simple matter to make a resistance and continuity check with an ohmmeter to quickly determine if the parts are defective. Military computers are usually made self indicating—that is, for a given module, normal operation is shown by a lamp operating in synchronism with the input or by a test signal incerted at specific intervals. Thus the operator can quickly determine if the module is working properly and substitute a new one when needed. In some instances it may be considered economical to throw away the module, in other instances, local or factory repair is made and the following trouble analysis will be applicable.

No Output. If no output is obtained from either the positive or negative OR gate when an input voltage or pulse is applied to either A or B terminal, the associated diode is defective. Use an ohmmeter to check the forward and reverse resistance of either CR1 or CR2. A high reverse resistance and a low forward resistance are normal. If the resistance is the same in both directions replace the diode with a known good diode. **Continuous Output.** When a diode is short-circuited, the 0 level will appear continuously at the output. That is a constant d-c level will appear at the output, because a d-c current path exists from the supply through resistor R, through the diode, and through the input impedance or voltage supply impedance to ground. Thus the output will be a constant and oppositely polarized voltage to that normally produced. The output amplitude will be either higher or lower than normal depending upon voltage divider action of R and the input resistance. When the input portion presents a high resistance the output will be near the supply voltage. If equal to the value of resistor R, the output voltage will also be low.

Erratic Operation or Reduced Output. If resistor R is open, no forward bias will be applied to the diodes and they will be in a floating condition, subject to operation by random noise pulses, or any signal that makes the anode more positive than the cathode (or the cathode more negative than the anode). Make a resistance check of resistor, R, with an ohmmeter when erratic operation occurs, and replace it if it reads outside the tolerance range.

#### AND GATE.

### APPLICATION.

The diode AND gate is a basic logic circuit which produces an output only if all of its inputs are simultaneously activated. It represents the basic logic circuit for binary multiplication, and the dot symbol is used to indicate this  $(A \cdot B = C)$ . It replaces the relays and electron tubes used in earlier computers.

### CHARACTERISTICS.

May use either positive or negative logic.

May be operated by short duration pulses, or by static d-c voltage levels representing inputs and outputs.

Corresponds to an oppositely polarized OR gate. Output never exceeds the input (no amplification is op-

#### CIRCUIT ANALYSIS.

tained).

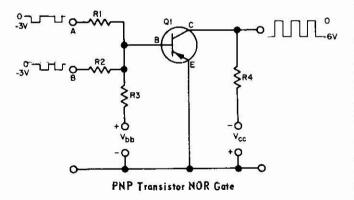

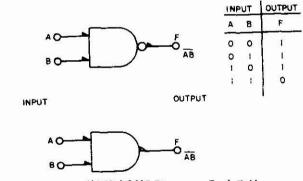

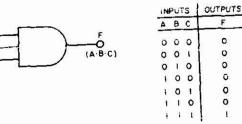

**General.** Logic circuits differ from basic electronic circuits in their general treatment. Through the use of standard logic symbols (see ML STD 00806C (NAVY) for a complete list), a block diagram type of presentation may by used, instead of the conventional schematic circuit representation with which the ET is more familiar. Thus the signal path or operation, may be followed, or considered without regard to the actual electronic circuit operation. A typical standard symbol used to represent a positive logic AND circuit is shown below, accompanied by a truth table of possible combinations.

28

NAVSHIPS

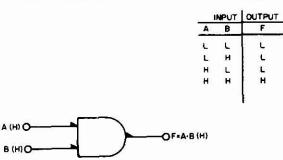

Positive AND Gate Symbol Table of Compinations

The (H) notation means high level or positive logic and is indicated in the symbol by the filled-in right triangle (when the triangles are used the parenthetical notation may be omitted). The inputs are A and B. The output, F, shows in Boolean algebra notation the result (A\*B), where the dot sign indicates AND (multiplication). The table of combinations shows every possible combination of input and output, and is, therefore, called a truth table. When inputs A and B are both at a relatively high level, the output, F, is also at a relatively high level. When both A and B are at a low level, so is F. For a single input the gate remains inactive.

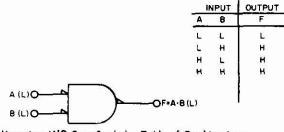

When negative logic is used, the symbol shown below and accompanying truth table apply.

The (L) notation means low level or negative logic, and the small open right triangle at the inputs and outputs of the symbol indicates they are low (if filled in they are high). When the triangles are used, the parenthetical (L) notation may be omitted. The table of combinations shows that for all inputs but one, the output is high. When both inputs are low, the output also is low. For a single input the gate remains inactive and rests in the high state.

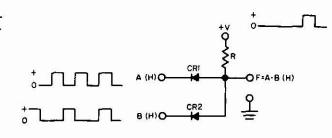

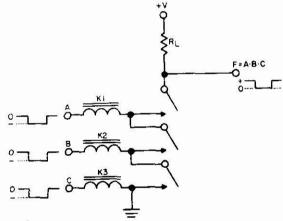

**Circuit Operation.** A two-input positive AND gate is shown in the accompanying illustration. The gate consists of two diodes, CR1 and CR2, and current limiting resistor, R, connected as shown in the schematic.

**Two-Input Positive AND Gate**

When the gate is inactive (no output is applied) the cathodes of CR1 and CR2 are at a relatively low level with respect to their anode. Thus the cathodes are effectively negative with respect to the anode and the diodes conduct. The diode current flowing through resistor R produces a voltage drop equal to that of the supply and of opposite polarity. Therefore, at the output end of R the potential is zero, and no output signal exists between F and ground.

Should a positive input be applied to either A or B alone, either CR1 or CR2 will cease conducting. However, the other diode will then conduct more heavily and keep output F at zero. Thus if only one input is activated there will be no output. On the other hand, if both A and B inputs are activated simultaneously by a high level or positive signal, the cathodes become more positive than the anodes and both diodes cease conducting. When conduction ceases, the voltage drop across resistor R no longer exists, and output F rises to the full value of the supply voltage (becomes highly positive). Thus a positive output is produced when both inputs are simultaneously activated by a relatively high level input representing a 1.

A positive AND gate is sometimes referred to as a negative OR gate, because if the polarity of the input trigger is reversed so that a negative signal represents a 1, and a positive signal represents a zero, a single input will produce a negative output, but combined inputs will not. Refer to the OR gate schematic in the previous discussion earlier in this Chapter and observe they are identical. Because of the interchangeability of the AND and OR functions with polarity it is necessary to adopt certain conventions to avoid confusion. Therefore, if we assume that relatively positve signals produce a 1, and relatively negative signals a O, we may call the AND circuit discussed previously above a **positive AND gate**. Unless otherwise noted, we shall assume this convention throughout the remainder of the circuit discussions in this Chapter of the Handbook.

In some systems, O's and 1's are represented by the absence or presence of a pulse. If the pulse is absent it represents a O, if present, a 1. The AND gate must produce a pulse at its output only when all inputs are activated. Thus in a three input AND gate, inputs A, B, and C must all be activated before an output can be produced. Likewise, where both d-c and pulse levels are used, all must be activated. Where two levels are d-c and the third is a pulse, both d-c levels must be positive and a positive pulse must appear at the third level before the circuit will operate. Absence of the pulse would be a O exactly as though a negative signal were applied instead, and the circuit would not operate.

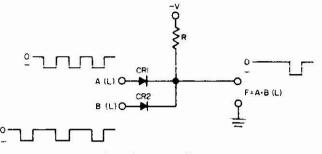

A two input negative AND gate is shown in the accompanying illustration. The gate consists of two diodes, CR1 and CR2, with current limiting resistor, R, connected as shown in the schematic.

Two Input Negative AND Gate

The negative AND gate operates inversely to the positive AND gate. Thus, when inactive, the anodes are at a relatively high level (positive) with respect to the cathodes, which are connected to the negative supply through R, and they conduct. The voltage drop across R is opposite the supply and equal so that no voltage exists at the output end of register R, thus no output is obtained from  $\Gamma$ . When either input A or B is activated (with a negative 1 signal) the associated diode stops conduction, but the other diode maintains the output at zero. However, when both inputs are simultaneously activated by a low level or relatively negative input the anodes become more negative than the cathode and the diodes cease conduction. "Since no current now flows through R, the voltage at the output terminal rises to the value of the supply voltage, and a negative output representing a 1 is produced. When the inputs cease, the output again terminates and the gate is considered inactive, even though this is the period during which the diodes are active and conducting.

If the polarities of the O and 1 are reversed, the negative AND gate will function as a positive OR gate (see schematic in previous OR gate discussion in this section of the Handbook). Thus the proper conventions must be used to produce the desired function. When the 1 input is relatively more negative than the O input, the above discussion, the symbol, the schematic and the truth table for the negative AND gate apply.

### FAILURE ANALYSIS.

**Control**. Since only three parts are used in the basic AND gate, it is a simple matter to make resistance and continuity checks with an ohmmeter to determine if these parts are defective. Military computers are usually self indicating—that is, for a given module, normal operation is shown by a lamp operating in synchronism, with the input, or by a test signal inserted at specific intervals. Thus the operator can determine if the module is working properly and substitute a new one when needed. In some instances it may be considered economical to throw away the defective module, in other instances, local or factory repair is made and the following trouble analysis will be applicable.

**No Output.** If no output is obtained from either the positive or negative AND gate when an input voltage or pulse of the proper polarity and amplitude is applied simultaneously to both inputs A and B, both diodes are defective or resistor R is open. Use an ohmmeter to check the forward and reverse resistances of CR1 and CR2. A high reverse resistance and a low forward resistance are normal. If the resistance is the same in both directions replace the diode with a known good one. If resistor R is outside its toler-once range, replace it.

**Continuous Output.** If either the positive or negative AND gate produces an output with no input applied, boin diodes are defective, or resistor R is shorted. Check the diodes with an ohmmeter for forward and reverse resistance, and the value of R. Replace the defective parts.

Erratic Operation. If an output is obtained when only one input is activated, the diode associated with the other input is open. Check the diodes for forward and reverse resistance with an ohmmeter, and replace the defective diode. If an output is obtained when either A or B are activated individually or simultaneously, resistor R is probably open and the diodes are free floating, subject to operation by any trigger or noise signal which makes the anodes more positive than the cathode, (or the cathodes more negative than the anodes). A resistance check of R will reveal the trouble.

## RECTANGULAR MATRICES.

# APPLICATION.

A rectangular diode matrice (matrix) is used in computers to perform a specific function, such as supplying a single output when supplied with multi-inputs or vice versa. It may also be known by its functional name instead. Thus, although arranged as a rectangular array it may be known as an encoding or decoding matrice. Actually it is a generic name for a class of circuits which are also named for the function they represent.

# CHARACTERISTICS.

May use positive of negative logic.

Consists of an orderly rectangular array of divide When many inputs are supplied only one or a very few

outputs are produced, and vice versa,

Gain is less than 1 (no amplification is providen).

### CIRCUIT AMALYSIS.

**General.** Rectangular diode matrices have no special characteristics or functions of their own other than an ordered array of diodes. The matrix arrangement does not wake it a logic circuit. It is the manner in which the matrix

5

0967-000-0120

#### LOGIC CIRCUITS

elements are connected that determines the logic function produced. Thus to describe a computer as containing a rectangular matrice is of no significance unless the associated function is also described.

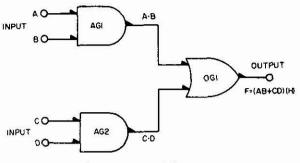

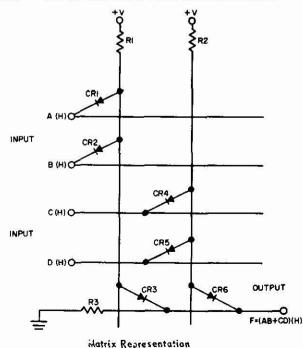

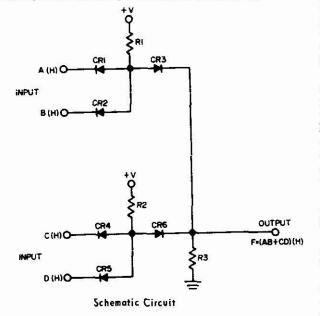

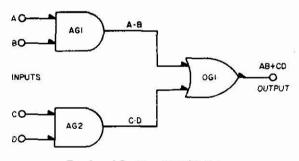

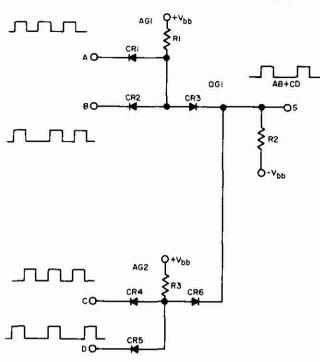

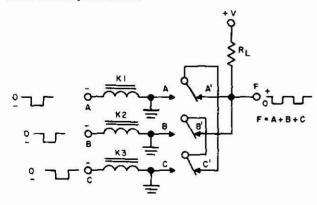

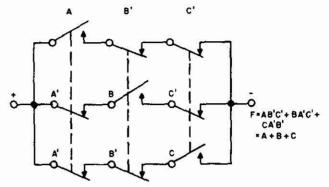

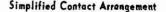

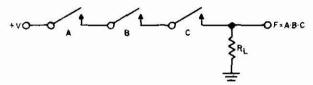

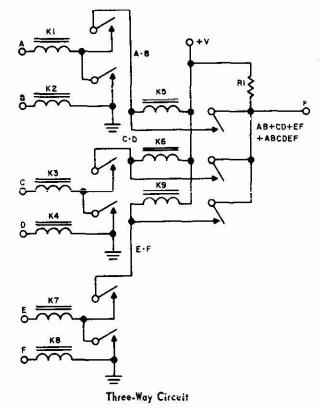

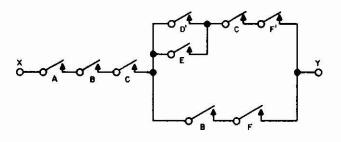

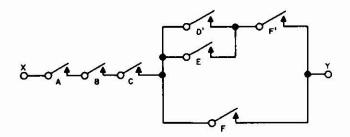

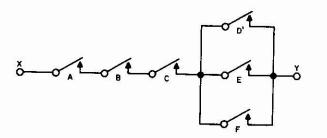

**Circuit Operation.** A simple rectangular matrice composed of two AND gates and one OR gate, which perform the logic function (AB + CD) are first shown symbolically, then as a matrix diagram, and finally, in schematic diagram form.

Logic Diagram of Matrice

As shown in the logic diagram, the diode AND gates are AG1 and AG2, and the diode OR gate is OG1. Inputs A and B are provided for AG1, and C and D for AG2; the output of both circuits is combined by the OR gate at F. Thus output F is active whenver AG1 output (A  $^{\circ}$ B) is active, or when AG2 output (C  $^{\circ}$ D) is active, or when both AG1 and AG2 are active. The output function is written symbolic-ally as AB+CD, which is read as A and B, or C and D, or both A AND B and C AND D. The last mentioned condition is the inclusive OR function.

The diode matrix representation of the function, F = AB + CD is shown in the following illustration. AND gate AGI consists of diodes CR1 and CR2, with current limiting

resister R1. AND gate AG2 consists of diodes CR4 and CR5, with current limiting resistor R2. OR gate OG1 consists of diodes CR3 and CR6, with current limiting resistor R3. In the drawing, zero volts represents a logic 0 and +V volts represents a logic 1, thus positive logic is used, and output F is active (logic 1) when it is at +V volts relative to ground. It is inactive (logic 0) when it is at zero volts relative to ground.

Assume that all inputs (A,B,C, and D) are at zero volts (logic O). With the anodes of CR1, CR2, and CR4, CR5 connected to the positive bias supply through R1 and R2, respectively, the diodes are forward biased and conduct. The supply voltage is dropped across resistors R1 and R2 so that the anodes of OR gate diodes CR3 and CR6 are also at approximately zero volts. Because the cathodes of the OR gate diodes connect to ground via R3, there is no difference in potential across these diodes and no conduction occurs. Thus, the output of the OR gate remains at zero volts (a logic O). The conditions stated above are shown on line 1 of the table of combinations shown below, that is, all inputs and the output are at a low level (L).

|        |    |    | INPUT | s          | QUTPUT         |

|--------|----|----|-------|------------|----------------|

| LINE - | A  | 9  | C     | D          | F* (AB+CD) (H) |

| 1      | L  | L  | L     | 8 <b>L</b> | L              |

| 2      | L  | L  | L     | н          | L              |

| 3      | Ļ  | L  | н     | L          | L              |

| 4      | L  | È. | н     | н          | н              |

| 5      | L  | н  | L     | L          | L              |

| 6      | L  | н  | L     | н          | L              |

| 7      | L. | н  | н     | L          | L              |

| 8      | L  | н  | н     | н          | н              |

| 9      | н  | L. | i L   | <u>a</u>   | ,L             |

| ю      | н  | L  | L     | н          | L              |

| 11     | н  | L. | н     | L 1        | L              |

| 12     | н  | L  | н     | H          | н              |

| ¥ 13   | н  | н  | L     | L          | н              |

| 14     | н  | H  | L     | H          | н              |

| 15     | н  | н  | н     | L          | н              |

| 16     | H  | н  | н     | н          | н              |

#### **Table of Combinations**

Assume now that the condition on line 13 is true. That is, inputs A and B are active at +V volts (relatively high), and inputs C and D are inactive at zero volts (relatively low). With inputs A and B both at +V volts, diodes CR1 and CR2 are held in the non-conducting state (reverse biased), while CR3 anode is positive with respect to ground and conducts, current flow is from ground through R3, diode CR3, and R1 to the supply. Thus, output F is equal to the supply voltage minus the drop across R1, and the small drop through the diode, or approximately +V volts, a logic 1. Meanwhile, inputs C and D are inactive at zero volts, and diodes CR4 and CR5 conduct because of the high positive anode potential. The current flow through R2 drops the supply voltage to zero, with respect to ground, at the

19-B-8

anode of diode CR6 (the OR gate). With the cathode of CR6 connected to ground through R3, no potential exists across the diode, it is reverse biased by the positive output voltage across R3, therefore CR6 does not conduct.

Assume now, that conditions are reversed, that is, inputs C and D are activated by a positive voltage, and inputs A and B are inactive at zero volts, this is combination number 4 in the table above. OR gate diode CR6 now conducts, while CR3 remains nonconducting, and the output at F is again at +V volts, and produces a logic 1 while in this active state. It is evident from the table of combinations, above, that if each of the input combinations is performed, only combinations number 4, 8, 12, 13, 14, 15, and 16 will cause an active (high) output to be produced at F.

The schematic representation of the circuit described above is shown in the accompanying illustration. While this drawing and the matrix representation are identical, the

arrangement is slightly different. Thus the schematic representation shows the more familiar AND and OR gate arrangements at a glance. However, the matrix drawing is usually used for matrices because it essentially conforms to the physical and wiring arrangement of the matrice, and it is clearer and easier to follow signal path flow when a large number of cascaded circuits are used. Both circuits are identical, however, so you may use whichever seems easier to follow or understand. The circuit explanation is applicable to both drawings. To fully understand operation of this circuit, you should apply each input condition shown in the table of combinations and verify that an identical result is obtained. Once established, the truth table makes it necessary to know how the circuit operates in determining a particular result. If the inputs are known, then the output can be determined at a glance.

### 0967-000-0120

#### LOGIC CIRCUITS

#### FAILURE ANALYSIS.

General. The simple rectangular matrice discussed above only contains three times as many parts as the basic AND or OR circuits, so that a resistance and continuity check with an ohmmeter will quickly determine if the parts are defective. Usually in Military computers, the module is made self indicating so the operator can determine quickly if the entire module is working and replace it when necessary. The defective module is then repaired either at a local activity or at the factory, or is discarded if it is considered economically feasible. In large computer repair centers test jigs are usually available, and the module is inserted in the jig and simulated test signals are applied to the mouts, and the outputs of luck of outputs are noted. Thus the defective part and circuit is quickly located. For small computers, when authorized, a similar procedure may be followed. The computer can be used to supply the necessary inputs, and the outputs can be observed on either a voltmeter, a VTVM, or an oscilloscope. Lack of output when the proper trigger is applied, or a continuous output with no trigger applied will usually isolate the trouble to the circuit and part at fault.

**No Output.** With a trigget applied to either diode CR3, or CR6, if no output is obtained, the associated diode is probably open. Check the forward and reverse resistance with an ohmmeter, if it indicates the same resistance in both directions and is a high value the diode is open. If no output is obtained with an input to both A and B, or C and D, diodes CR1 and CR2, or CR4 and CR5, respectively, are open, or either R1 or R2 is open. A resistance check will determine which is at fault.

If both AND gate diodes are shorted, the associated AND gate will not operate, but the matrice can be operated by the other AND gate. However, if both AND gates are inoperative no output will be obtained from the matrice, and all diodes must be defective. If R3 is shorted, no output will be obtained; check R3 with an ohmmeter.

**Continuous Output.** If a continuous output is obtained and remains unaffected by any input trigger combination, either diode CR3, or CR6 is shorted. Checking the reverse resistance of either diode will indicate which one is defective (if low, the diode under test is defective; if high the other diode is defective).

If both AND gate dicdes are open, their associated OR gate will be triggered and a continuous output will occur. A reverse resistance check will reveal this condition. Simtlarly, if R1 or R2 are shorted, their associated OR cate diodes CR3 or CR6 will conduct continuously, and produce a larger than normal output across R3. A resistance the k of the resistors with an obimineter will determine the defactive part.

# ENCODING MATRICES.

#### APPLICATION.

Encoding matrices (matrix) are used to change data from one form into another. For example, the conversion of conventional decimal or english notation into a form usable in a digital computer. The decimal numbers, letters, and punctuation marks are converted to binary form for use in the digital computer.

# CHARACTERISTICS.

Consists of many input lines, but only a few output lines.

Only one input line is activated at a time to produce a unique output.

May use positive or negative logic, or combined logic. Gain is less than 1 (no amplification is provided).

The matrix may be arranged in any suitable geometric form (rectangular, square, pyramid etc.).

### CIRCUIT ANALYSIS,

**General.** A decimal-to-binary encoder matrice changes a voltage level which represents a specific decimal number into a unique set of voltage levels representing the binary form of the decimal number. The following table shows decimal numbers from 0 through 9 with their binary equivalents.

| DECIMAL NUMBER | BIN | ARY | NUN | IBER |

|----------------|-----|-----|-----|------|

| o              | 0   | 0   | 0   | 0    |

| 1              | 0   | 0   | 0   | 1    |

| 2              | 0   | 0   | 4   | 0    |

| 3              | 0   | 0   | 1   | 1    |

| 4              | 0   | 1   | 0   | 0    |

| 5              | 0   | F   | ο   | 1    |

| 6              | 0   | t.  | 1   | 0    |

| 7              | 0   | 1   | 1   | 1    |

| 8              | 1   | 0   | 0   | 0    |

| 9              | 1   | 0   | 0   | Ŧ    |

Note that the decimal digit requires four binary digits (or bits) to represent it. Therefore, the circuit which performs the decimal to binary encoding must have 10 input lines, one for each decimal digit input, and 4 output lines, one for each binary output.

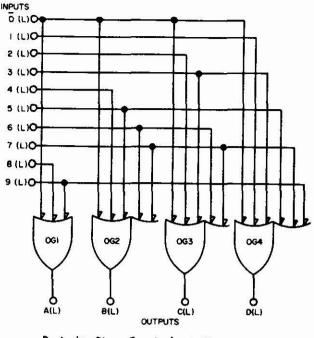

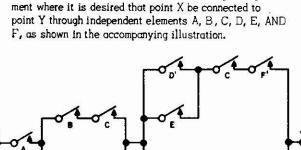

**Circuit Operation.** The logic diagram for a typical decimal-to-binary encoder is shown in the accompanying illustration.

Decimal to Binary Encoder Logic Diagram

Examination of the logic diagram reveals that four OR gates are employed. OR gate number 1 has three inputs rand one output. OR gates numbers 2 and 3 have five inputs and one output, and OR gate number 4 has six inputs with one output. The open triangles indicate that negative logic is used. Therefore, a logic 0 (inactive state) is represented by a relatively high voltage level (H), while logic 1 (the active state) is represented by a relatively low voltage level (L).

The following table of combinations shows the specific decimal number input and level, and the unique output level for each of the inputs.

| INPUT |     | OUTI | PUT |   |

|-------|-----|------|-----|---|

| F     | A   | Ð    | C   | Ď |

| δ     | L   | L    | L   | L |

| 1     | н   | н    | н   | L |

| 2     | H   | н    | L   | H |

| 3     | Н   | н    | L   | L |

| 4     | н   | L    | н   | н |

| 5     | н   | L    | н   | Ľ |

| 6     | . н | L    | E.  | н |

| 7     | н   | L    | L   | L |

| 8     | L L | н    | н   | H |

| 9     | L   | H    | н   | L |

Table of Combinations (Truth Table)

#### NAVSHIPS

Examination of the table of combinations reveals that the listed gate output is activated when the input is the decimal number(s) shown in the following matrix truth table; note that the number of inputs correspond to those shown on the logic diagram.

> A = 0,8,9 B = 0,4,5,6,7 C = 0,2,3,6,7 D = 0,1,3,5,7,9

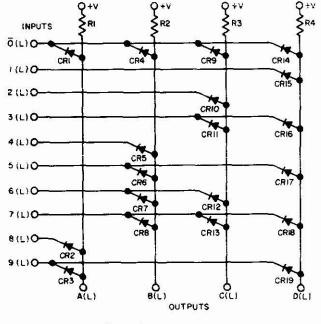

The following illustration shows the complete matrix schematic representation of the encoder.

Matrix Representation

Examination of the matrix schematic reveals that OH gate number 1 (output A) consists of diodes CR1 through CR3, with current limiting resistor R1. OH gate number 2 (output B) consists of diodes CR4 through CR8, with current limiting resistor R2. OH gate number 3 (output C) consists of diodes CH9 through CR13, with current limiting resistor R3. And OP gate number 4 (output D) consists of diodes CR14 through CR19, with current limiting resistor R4. As shown in the schematic, the anodes of all diodes are connected to a positive bias supply through the current limiting resistors. When their cathodes are connected to a less positive voltage, or placed at zero (ground) potential they will conduct. When left unterminated (no input) the circuit from the supply through the diode to ground is open, and no conduction occurs. When

#### LOGIC CIRCUITS

no conduction occurs, no current flows through the associated current limiting resistor and the gate output is +V, the supply voltage. Since negative logic is employed, a positive (relatively high) output represents a 0 and the circuit is then considered inactive. When a zero voltage (negative or relatively low) input is applied, all diodes on this line will conduct. The normally high (positive) output will be dropped to zero by the current flowing through the associated current limiting resistor, thus zero voltage or no output represents a 1, that is, an active negative output.

For example, assume the decimal number 7 is applied by grounding that input line (a relatively low (L) input is applied). The cathodes of diodes CR8, CR13, and CR18 are, therefore, more negative than their anodes, and these diodes will conduct. Thus at gate outputs B, C, and D, no voltage will appear, and these OR gates will all be at a relatively low (L) output. At the same time, since gate A output is not connected to line 7 it will remain highly positive at +V volts creating a relatively high (H) output. Thus by activating the number 7 line (through grounding it) the output will be HLLL, representing 0111 or the binary number 7. By following the table of combinations, number for number, in a similar fashion and applying each input in tum, the outputs shown in the table of combinations will be obtained. Only one decimal number input at a time is permitted, with all the remaining lines resting in the inactive state. If two or more input lines were simultaneously activated, one of the numbers might be produced correctly and the others masked out, or else the wrong number would be produced. Thus in an encoder of this type a series input must be used, since a parallel input would produce a false indication. Conversely, the decoder which works just the opposite, requires a parallel input. This the coding time for a series of decimal digits in a simple computer represents a finite time, since only one can be produced at a time. However, the operating time for each digit is only a tew microseconds, so that the coding is usually accomplished as fast as the information can be inserted, and appears to be instantaneous.

While the above explanation assumes the use of d-c voltage levels, the same action can be obtained with pulses using appropriate coupling circuits, when needed. Because of the inherent loss in the diode, although assumed zero for ease of discussion in these paragraphs, when large numbers of diodes are used considerable power is required. Thus diode logic is usually used together with transistors, and diode-transistor logic (DTL) circuits are used in large computers.

#### FAILURE ANALYSIS.

General. In large matrices one has a choice of making a resistance check of the numerous components of the modale, or applying an operational check using the truth table and a matrix schematic to analyze the outputs. In large computer repair shops this is accomplished autickly by prepared test jigs into which the module may be plugged. The trouble is thereby pin-pointed to a few associated com-

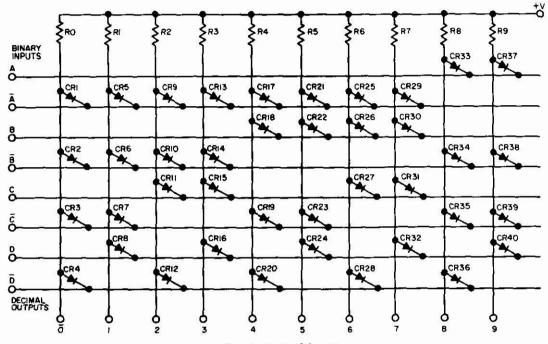

#### CIRCUIT ANALYSIS.

0967-000-0120

**General.** A binary-to-decimal decoder matrice changes a unique set of input voltage levels representing a binary number into an output which represents a single decimal number. The following table shows binary numbers from 0 through 9, with their decimal equivalents.

| BINA | RY | NUM | BER | DECIMAL NUMBER |

|------|----|-----|-----|----------------|

| 0    | ο  | 0   | 0   | 0              |

| 0    | 0  | 0   | 0   | 1              |

| 0    | 0  | 1   | 0   | 2              |

| 0    | 0  | E   | 1   | 3              |

| 0    | L. | 0   | 0   | 4              |

| 0    | ĩ  | 0   | )   | 5              |

| 0    | H. | 1   | 0   | 6              |

| 0    | Ĩ  | ñ.  | 1   | 7              |

| 1    | 0  | 0   | 0   | 8              |

| 1    | 0  | 0   | 1   | 9              |

Note that each decimal digit requires four binary digits (bits) to represent it. Thus this type of decoder is sometimes called a "many-to-one" decoder, since many inputs are converted to a single output. To perform the binary decoding 8 inputs are required (four inputs for binary 1's and four inputs for their complement, binary 0), with 10 outputs representing the decimals from 0 through 9.

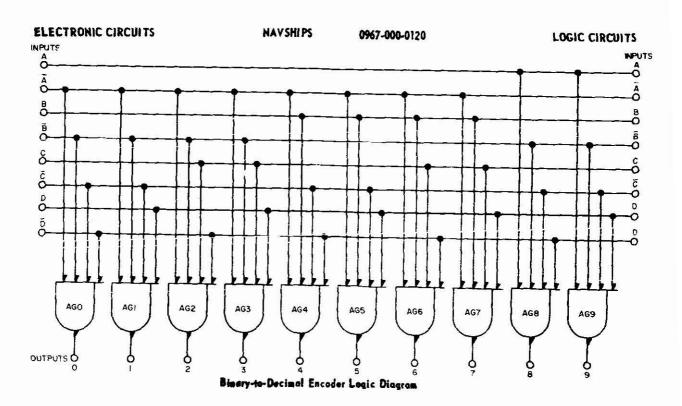

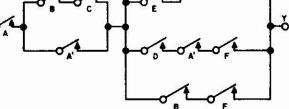

**Circuit Operation.** A logic diagram for a typical binaryto-decimal decoder is shown in the accompanying illustration.

ponents which are then checked individually. The following paragraphs indicates a systematic method of analyzing failures for trouble localization.

Gate Output Always High. If a particular gate output always remains in the high state regardless of the inputs to the matrix, it can be assumed that all the diodes associated with that gate are probably open circuited, or the associated current limiting resistor is shorted. Make a forward resistance check of the diodes with an ohmmeter, if the resistance is the same in both directions and high, the diodes are open. Check the resistance of the resistor. With a shorted current limiting resistor, the heavy current through the diode will usually be sufficient to cause the diode to heat, smoke, and eventually burn out, or to blow the supply fuse.

Gates Outputs Always Low. If a particular gate output always remains in the low state, regardless of the inputs to the matrix, all of the diodes associated with that gate are probably short circuited, or the associated current limiting resistor is open. Make a reverse resistance check of the diodes with an ohmmeter, if they read the same in both directions and it is very low, the diodes are shorted. Check the resistor value.

**Incorrect Output.** By using the truth table and the proper input, each input line can be checked individually for proper operation. For example, if input line  $\overline{U}$  (decimal zero) is active and low (L) and the outputs are: A high (H), B low (L), C low (L), and D low (L) it indicates that diode CR1 is open circuited. This is indicated by outputs B, C, and D being normal, and output A abnormal when compared with the proper outputs listed in the table of combinations. Note that while diodes CR2 and CR3 are also connected to output line A, they can only be activated when lines 8 or 9, respectively, are activated. Thus, since only one line may be active at a time only the diodes associated with that line need be considered. It is evident that if three diodes are concerned, and two outputs are wrong, two of the diodes must be at fault.

# DECODING MATRICES.

## APPLICATION.

Decoding matrices (matrix) are used to change data from machine (computer) language to ordinary decimal or english notation. The binary representation of a decimal or an english character (machine language) is automatically converted by the matrix into a straight-forward reading character or digit easily recognized by the reader.

#### CHARACTERISTICS.

Consists of many input lines, and many more output lines.

Several inputs are activated simultaneously to produce a unique output.

May use positive or negative logic, or combined logic. Gain is less than 1 (no amplification is provided).

The matrix may be arranged in dny suitable geometric form (rectangular, square etc.).

Examination of the logic diagram shows that 10-AND gates having 4-inputs and four diodes in each gate (AGO through AG9) are used. The closed triangles indicate that positive logic is employed. Therefore, the inactive state (a logic 0) is represented by a relatively low voltage level (L), while the active state (a logic 1) is represented by a relatively high level (H).

The following table of combinations shows the various **binary** input levels and the unique output level for each of **the possible** input combinations.

|   | A  | В  | C  | D  | F          |     |

|---|----|----|----|----|------------|-----|

|   | L  | L. | L  | L  | н          | (0) |

|   | L  | L  | L  | н  | н          | (4) |

|   | L  | L  | н  | L  | ) н        | (2) |

|   | L  | Ĺ  | н  | н  | н          | (3) |

|   | L  | х  | L  | i. | н          | (4) |

|   | L  | н  | 1  | н  | ) н        | (5) |

|   | L  | н  | н  | L  | <b>।</b> म | (6) |

|   | L. |    | H  | н  | Н          | (7) |

| × | н  | L  | ۱. | Ł  | н          | (8) |

|   | Н  | ٤. | ۲. | н  | н          | (9) |

# Table of Combinations

Examining the table of combinations, we find that if the binary inputs A, B, C, D are activated (H. L. L, L), gate AG8 is activated to produce a high (H) output, which indicate that the matrix has decoded a binary 8. While the gate that is activated for each binary input is shown by the table of combinations, if it is converted into a Truth Table by substituting the 0 and 1's corresponding to the decimal number as shown below, operation becomes easier to

| BIN | ARY | NUMBER |   | DECIMAL NUMBER |

|-----|-----|--------|---|----------------|

| σ   | 0   | 0      | 0 | 0              |

| 0   | 0   | 0      | 1 | 1              |

| 0   | 0   | \$     | 0 | 2              |

| 0   | O   | 1      | 3 | 3              |

| 0   | T   | 0      | 0 | 4              |

| 0   | E.  | 0      | 1 | 5              |

| 0   | ł   | 3      | 0 | 6              |

| 0   | ÷.  | 3      | 1 | 7              |

| Ĩ.  | 0   | 0      | 0 | 8              |

| ĩ   | Ū   | Û      | 1 | 9              |

follow. It is also evident that this is the same as the binary-decimal equivalent numbers previously listed. When the gates are activated it is by means of a logic 1 signal. In the logic zero state the gate remains inactivated. When the gate input is activated, the input signal stops the

0967-000-0120

associated gate diodes from conducting, and an output is produced as the output level rises to the +V supply voltage. When the gate input is inactivated, the cathode of the associated diode is at a lower potential than the anode and the diode conducts. The current flow through the associated current limiting resistor drops the supply voltage to zero so that no output is obtained. Thus when input A is activated a positive voltage is applied to block off or reverse bias any diodes connected to that line. When  $\overline{A}$  (A-bar) is activated it is a "NOT A"; thus, it is not a logic 1 but a logic 0, and all the diodes associated with that line conduct because of the forward bias applied by the relatively-low (L) input signal.

This operation may be followed more easily if the accompanying matrix schematic is examined in conjunction with the truth table inputs as the discussion continues.

# **Decoder Matrix Schematic**

For example, assume that inputs A, B, C, and D are active high (H), and are at +V volts. The truth table shows that the corresponding combination 0101 must activate gate number 5 and produce a high positive output. Examination of the matrix schematic shows that gate 5 consists of CR21 through CR24 with current limiting resistor R5. When input line A is activated, made high (H), diode CR21 ceases conduction; likewise, as B, C and D, respectively, are also made high the diodes CR22, CR23, and CR24 are also reverse biased. Thus all the diodes of AND gate 5 stop conduction simultaneously, and output F which is assigned the decimal number 5 rises to the supply voltage level creating a positive output pulse, as required by the table. Note that if any one of these inputs were not activated (H), but were low (L) instead, then that one diode would conduct and the high output could not occur. Thus one, and only one particular combination will activate each of the AND gates. To prove this, examine each of the input lines which are not activated and are at a relatively low value. We find, then, that line A forward biases diodes CR33 and CR37 and decimal outputs 8 and 9 are, therefore, at zero. Likewise, for input line B diodes CR2, CR6, CR10, and

CR14 conduct and outputs T, 1, 2, and 3 are low or zero. For line C diodes CR11, CR15, CR27, and CR31 conduct so that outputs 2, 3, 6, and 7 are zero. Finally, input D inactive causes conduction of diodes CR4, CR12, CR20, CR28, and CR36, with outputs T, 2, 4, 6, and 8 at zero. Thus, while gate 5 is high, all the other outputs are low or zero since at least one of the associated diodes is conducting. Sometimes two or more diodes will be conducting, but only one is necessary to prevent the gate from operating, and producing an output.

If you follow the truth table combinations, applying high and low inputs as indicated and noting the output, or lack of output, you will see that the truth table shows the proper combination for the desired output, and no other combinanation will produce the same results.

#### FAILURE ANALYSIS.

**General**. In large matrices one has a choice of making a resistance check of the numerous components of the module, or applying an operational check using the truth table and a matrix schematic to analyze the outputs. In lagre computer repair shops this is accomplished quickly by

prepared test jigs into which the module may be plugged. The tests are than run sequentially (using the proper input) until the wrong response is obtained. The trouble is thereby pin-pointed to a few associated components, which are then checked individually. The following paragraphs indicate a systematic method of analyzing failures for trouble localization.

Gate Output Always High. If a particular gate output always remains in the high state regardless of the inputs to the matrix, it can usually be assumed that all the diodes associated with that gate are probably open circuited, or the associated current limiting resistor is shorted. Make a forward and reverse resistance check of the diodes in that gate with an ohmmeter. If the resistance is the same in both directions and high, the diodes are open. Check the resistance of the current limiting resistor with an ohmmeter. Usually with a shorted current limiting resistor, the heavy current through the diodes will be sufficient to cause the diodes to heat, smoke, and eventually burn out, or to blow the supply fuse.

Gate Output Always Low. If a particular gate output always remains in the low state, regardless of the inputs to the matrix, one of the diodes associated with that gate is proably short circuited, or the associated current limiting resistor is open. Make a reverse resistance check of the diodes with an ohmmeter. If the resistance is the same in both directions, and it is very low, the diode is shorted. Check the resistor value with an ohmmeter.

incorrect Output. By using the truth table and the proper input, each input line can be checked individually for proper operation. For example, if diode CRI of gate AGO were open-circuited, AGO would become active whenever inputs B, C, and D were high. The table of combinations shows that inputs B, C, and D must be active to produce an output from gates AGO and AG8 under these conditions (A input is not connected to AG8, and A input is not connected to AGO). Therefore, both AGO and AG8 would become active when the AG8 inputs are correct, and AGO would also become active when its inputs are correct. Thus the open circuited CRI diode would not be detected unless it was noted that BOTH AGO and AG8 outputs were active when only the AG8 output should be active. It is evident, then, that the logical procedure is to apply the proper inputs separately, as listed in the table of combinations, while checking the output lines to be certain that only one gate (the correct gate) is activated for a particular input combination.

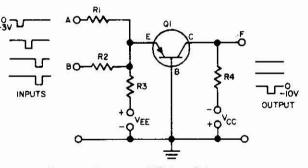

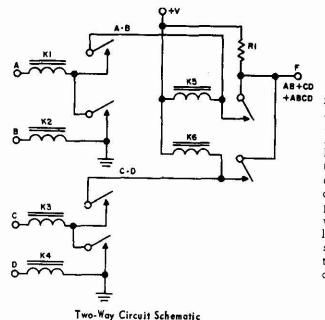

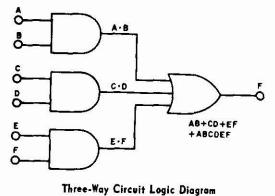

#### TWO-LEVEL AND-OR GATE

#### APPLICATION

Combinations of ANL+OK gates which form a two-level logic circuit can be used to apply the outputs of two or more logic circuits to the input of another logic

circuit to produce logic addition, subtraction and other functional operations.

### 0967-000-0120

### CHARACTERISTICS.

May use positive or negative logic, or combined logic.

Has not less than four inputs for one output, and may have six or eight inputs with only one output, if desired.

The actual input levels may be different, however, the outputs are always at the same level.

Output never exceed the input (no amplification is obtained).

# CIRCUIT ANALYSIS

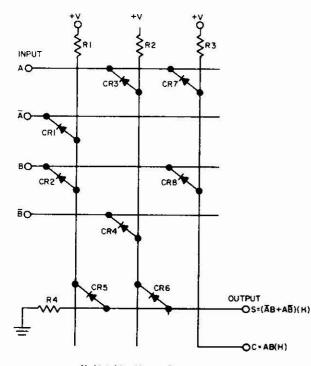

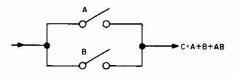

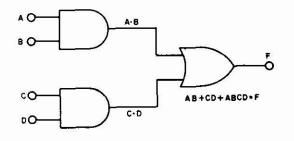

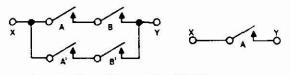

General. Two-level logic circuits have two basic input circuits and a single cutput circuit. The input circuits may have a number of input lines, each controlled by a diode, but there is only one output line. Thus it is common practice to make the input circuits AND gates, and the output circuit an OR gate. Although this logic may be changed to exactly the opposite by applying negative logic inputs. Thus, the AND gates become OR gates, and the OR gate becomes an AND gate without changing any circuitry. This allows complete flexibility in combining logic operations, and, therefore, two-level logic circuits are universally used throughout computers. The logic diagram for a combination of two positive AND gates, and a positive OR gate is shown in the following illustration.

#### **Two-Level Positive AND-OR Gate**

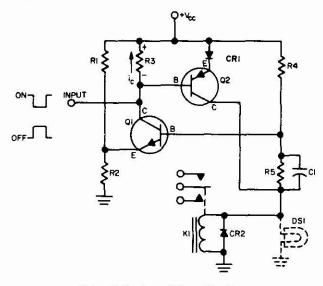

**Circuit Operation.** The schematic for a typical two-level AND-OR gate is shown in the accompanying illustration. Although only two inputs are shown for each branch circuit for ease of dicussion, a larger number of inputs may be accommodated. NAVSHIPS

0967-000-0120

4

**Two-Level AND-OR Gate Schematic**

It is evident from the schematic that AND gate number 1(AG1) is identical to AG2. Two different inputs are applied to each AND gate. The output of the AND gates are applied through CR3 and CR6, and are summed across R2. A table of combinations shows that the following truth table is applicable, where O is ground or zero level, and 1 is a +5.

|   | INPL | JTS | 1   | OUTPUT |  |

|---|------|-----|-----|--------|--|

| Δ | В    | С   | D   | S      |  |

| С | 0    | 0   | 0   | 0      |  |

| 0 | I.   | 0   | 0   | 0      |  |

| L | 0    | - E | 0   | 0      |  |

| 1 | T    | Ê   | 1.1 | Ê      |  |

#### Truth Table

Thus with no input applied, diodes CR1, CR2 and CR4, CR5 conduct since they are forward biased, and the voltage across R1 and R3 is dropped to zero. OR diodes CR3 and CR6 are also conducting (anode is more positive than cathode) so that this output is also zero. When either A or B, or C or D is made a 1 (by applying plus 5 volts) the associated diode is reverse-biased and stops conducting. However, circuit operation remains unaffected since the other diode of the pair still conducts and holds the gate in the zero state. However, whenever both inputs are applied simultaneously to either AND gate, both diodes are reverse biased, conduction ceases, and the voltage at the bottom end of B1 or B3 is the same as the supply, if the reverse bias is equal to or greater than the supply. If the reverse bias is only a portion of the supply voltage, (as is the case) conduction above that level holds the output at the value of the reverse bias. Thus with a 10 volt supply and a 5- volt reverse bias, the output is +5 volts. This output of the AND gate when applied to the OR gate passes through either CR3 or CR6 and appears as the output sum (AB + CD). When +5 volts appears at the output the inactive OR diode is reverse-biased by that same amount, so that the other AND output has no effect. That is the exclusive OR function is represented, where either one or the other (AG1 or AG2) appears but not both. In this respect, the truth table appears erroneous. However, it is just the manner in which it is arranged. Thus this circuit is sometimes called a one-quarter adder, since it only represents the sum of two digits. When another AND gate is added to indicate the carry where both OR gate inputs are present simultaneously, the circuit then is known as a half-adder (discussed separately later in this section of the Handbook).

#### FAILURE ANALYSIS.

General. Since the two-level gate is composed of AND and OR circuits, the failure analysis for each of these circuits can be applied individually (see separate discussion of AND and OR circuits in this section of the Handbook) after it has been determined which is at fault. To determine which is at fault, proceed generally as follows.

No Output. Use a vacuum tube voltmeter or an oscilloscope as an indicator and apply a simulated "1" signal to input A, B, C, and D separately; no output should be observed at the OR input. However, if both A and B, or C and D inputs are activated and no output appears at the OR gate, the AND gate portion of the circuit is defective. Check the diodes for a short circuit or resistor R1 or R3 with a ohmmeter. If no outputs occurs from the OR gate portion, with an input appearing on the anode of CR3 or CR6, either the diode or R2 is open. Make a check of forward diode resistance and check the resistor with an ohmmeter.

Wrong Output. Usually with a wrong output, it will be found that the diode associated with that circuit is either inoperative or shorted. A forward and reverse resistance check of the diodes with an ahmmeter will usually locate this form of failure.

**Continuous output.** Usually in the case of a continuous output you will find that the diode associated with that output is shorted. The key to determining which is at fault is to study the circuit

operation. If the circuit requires that the diode conduct to produce the desired output, then the diode is shorted. If the diode must cease conduction, then the diode is open. Because of the few parts involved in a simple basic circuit a resistance analysis is usually easy to make, requiring only an anomater.

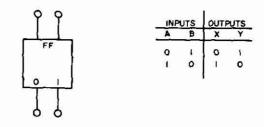

# HALF-ADDER CIRCUITS.

### APPLICATION.

Half-adders are used to form the sum of two incident binary digits. They are used as the basic circuit for a full-adder (two half-adders make a full-adder). Thus full binary adding networks used in computers consist of a number of half-adders, and associated circuitary.

# CHARACTERISTICS.

May use either positive or negative logic, or combined logic.

Usually has four input lines with two output lines. Consists of three AND gates and one OR gate. Gain is less than 1 (no amplification is provided.)

# CIRCUIT ANALYSIS.

**General.** Since the half-adder performs binary (arithmetic) addition it is necessary that its output be identical to the results of the binary addition table as follows:

| Ą     | 0 | ο | Į. | ŧ |

|-------|---|---|----|---|

| B     | 0 | 1 | 0  | £ |

| SUM   | 0 | ł | ŧ  | 0 |

| CARRY | 0 | 0 | 0  | 1 |

We see from the table that two outputs are needed, since there is a carry of 1 when two 1's are added. It is evident that to add three binary numbers another carry output is needed. Hence to add more than two binary bits it is necessary to employ more than one half adder so that full-adders (consisting of two or more half-adders) are usually used in adder networks.

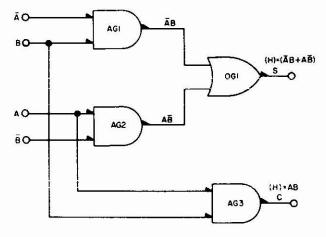

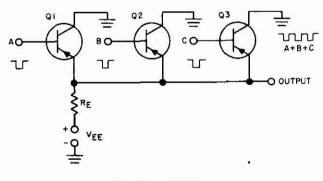

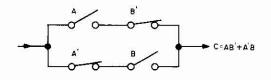

**Circuit Operation.** A typical half-addet is shown in the accompanying logic diagram.

### Half-Adder Lagic Diagrom

Examining the diagram we see that three two-diode AND gates AG1, AG2, and AG3 are used, together with a single two-diode OR gate OG 1. The logic equation at the output shows that the sum output (S) is high (H), and active whenever the two inputs A and B are unlike, and is inactive low (L) whenever the two inputs are alike. The output equation  $S = \overline{AB} + \overline{AB}$  is read as "A or B, but not both'; this is the **exclusive OR** function. The carry output is active and high (H) whenever the two inputs A and B are equal to binary 1's, and is inactive low (L) for all other conditions. The table of combinations below shows the proper output for any particular input combination.

| INP | UTŞ | OUT | PUTS |

|-----|-----|-----|------|

| A   | 8   | S   | с    |

| L   | L   | L   | Ē,   |

| L   | н   | н   | L    |

| н   | L   | н   | Ł    |

| н   | н   | L   | н    |

TABLE OF COMBINATIONS FOR HALF-ADDER

When the table of combinations is converted into a truth table by substituting the 0's and 1's, as shown below, it is evident that it corresponds to the binary addition table previously shown above, and that the circuit is performing the desired function.

| INP      | JTS | OUTI | PUTS  |

|----------|-----|------|-------|

| A        | 8   | SUM  | CARRY |

| 0        | 0   | 0    | 0     |

| D        | 1   | 1 1  | 0     |

| i        | 0   | 1 1  | Ō     |

| <u> </u> | I   | 0    | 1     |

|          |     |      |       |

HALF-ADDER TRUTH TABLE

Circuit details are as shown in the accompanying matrix schematic (the half-adder may also be considered as a rectangular or square matrice).

Half Adder Matrix Diagram

Examination of the matrix diagram reveals that AND gate number 1 consists of diodes CR1 and CR2 with current limiting resistor R1; AND gate number 2 consists of diodes CR3 and CR4, with current limiting resistor R2, and the carry gate is AND gate number 3 with diodes CR7 and CR8, and current limiting resistor R3. The OR gate consists of aiodes CR5 and CR6, with current limiting resistor R4. Zero volts represents logic 0 (L), and +V volts represents logic 1 (H).

Assume that inputs A and B are logic 1's, thus their input line is at a high level (H). Therefore, associated diodes, CR3, CR7 on line A, and CR2, CR8 on line B are reverse-biased and will stop conduction. Thus output C of AND gate number 3 (the carry gate) will rise to +V volts and also be at a high level, which is the output expressed by the formula C=AB. With inputs A and B high, their complement inputs A and B (NOT A and NOT B) are low, causing diodes CR1 and CR4 to conduct. Therefore, OR gate diodes CR5 and CR6 will not conduct, since the potential at the anode end of R1 and R2 will be zero, and with the diode cathodes connected to ground through R4 no potential exists across these diodes. Thus there is no output from the S output line, and it is a logic 0.

In a similar manner, it is evident that for the sum output (S) to be high (H), inputs  $\overline{AB}$  or  $\overline{AB}$  but **not both** must be a logic 1 (H). For these conditions, either diode CR7 or

0967-000-0120

#### LOGIC CIRCUITS

diode CR8 is held inoperative by reverse bias from the logic 1 input, while the other diode conducts because of the lack of an input (both diodes must be reverse biased to produce an output). Therefore, carry output, C, remains inactive and low or a logic 0. By following the table of combinations (or truth table) for each input condition, and by using the matric diagram to determine which diodes are activated and which are not, you can verify operation of the circuit against each unique output listed in the table. Normally, when inputs A and B are alike, the sum output is always 0 (L), and when unlike it is always 1 (H). The carry output, C, is always 0 (low) except when both A and B inputs are high (1), in which case it is also high (H), and a logic 1.

#### FAILURE ANALYSIS.

**General.** Large computers are usually designed with built-in test circuits, signals, and alarms which indicate when a section or module is operating incorrectly. The offending board or chassis may then be replaced quickly to keep the computer operating. In large computer repair shops, test jigs are provided into which the module may be plugged and the necessary inputs applied to locate the defective circuit. Once the circuit is located the individual parts are easily checked by resistance or voltage measurements to find the defective part. Once the module is located, a systematic procedure such as indicated in the following paragraphs will help isolate the failure.

**No Output.** Loss of output can be caused by loss of input signals, loss of bias supply, or open diodes. When no output is obtained from any of the gates with the proper input supplied, it is most probable that the bias supply is defective. No output from a single gate usually involves the diodes and current limiting resistor for that gate only. Refer to the discussion of failure analysis for the AND gate (or the OR gate, as applicable) and which were previously explained in this section of the Handbook.

**Continuous Output.** A continuous output regardless of the type of input signal applied may be caused by a shorted OR gate diode, or by AND gate outputs occurring at the wrong time. Follow the procedure discussed in the following paragraph for an incorrect output to locate the defective circuit and part.

Incorrect Output. The sum output, S, and carry output C, must be active only as indicated in the table of combinations (or the truth table). Any other output for a specified set of inputs indicates a change in circuit logic caused by a defective part. Therefore, it is usually easier to set up specific inputs (preferably inputs which yield incorrect outputs) and check the output of each gate with a voltmeter or an oscilloscope. For example, assume that both A and B inputs are made high (H), and the sum and carry outputs both show high (H). Checking against the truth table reveals that for such an input the sum output is a logic 0, and the carry output is a logic 1. In this case the C output is correct, but the S output is not (it should be a logic 0). This indicates that OR gate number 1 is being activated when it should not be (both inputs should be low). Con-

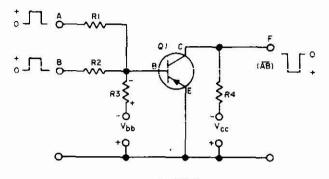

#### NAVSHIPS