#### Operational or User's Manual

The manual should include instruction, installation, operator, or technical manuals with required 'information to the users'. This manual should include a statement that cautions the user that changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment. The manual shall include RF Hazard warning statements, if applicable.

The instruction and service manual for this base radio are not published at this time. However, draft copy of some of the manual information has been assembled and has been included as part of this filing package.

Upon request, published and/or printed manuals will be sent to the commission and/or telecommunication certification body (TCB) as soon as they become available. All of the descriptions, block diagrams, and schematics that are included in this filing package are current as of the package submittal date.

#### EXHIBIT DESCRIPTION

- D1-1 Manual Front Matter (Draft)

- D1-2 Specifications (Draft)

- D1-3 Field Replaceable Units and Orderable Parts (Draft)

- D1-4 Tune-Up Procedure

- D1-5 Functional Description / Operation of Modules (Draft)

Manual Front Matter (Draft)

#### COMPUTER SOFTWARE COPYRIGHTS

The Motorola products described in this instruction manual may include copyrighted Motorola computer programs stored in semiconductor memories or other media. Laws in the United States and other countries preserve for Motorola certain exclusive rights for copyrighted computer programs, including the exclusive right to copy or reproduce in any form the copyrighted computer program. Accordingly, any copyrighted Motorola computer programs contained in the Motorola products described in this instruction manual may not be copied or reproduced in any manner without the express written permission of Motorola. Furthermore, the purchase of Motorola products shall not be deemed to grant either directly orby implication, estoppel, or otherwise, anylicenseunder the copyrights, patents or patent applications of Motorola, except or thenormal non – exclusive, royalty free ficense to use that arises by operation of law in the sale of a product.

EPS-34440-B

#### COMMERCIAL WARRANTY (STANDARD)

Motorola radio communications products are warranted to be free from defects in material and workmanship for a period of ONE (1) YEAR, (except for crystals and channel elements which are warranted for a period of ten (10) years) from the date of shipment. Parts, including crystals and channel elements, will be replaced and labor will be provided free of charge for the full warranty period. Thereafter purchaser must pay for the labor involved in repairing the product or replacing the parts at the prevailing rates together with any transportation charges to or from the place where warranty service is provided. This express warranty is extended by Motorola Communications and Electronics, Inc., 1301 E. Algonquin Road, Schaumburg, Illinois 60196, to the original purchaser only, and only to those purchasing for purpose of leasing or solely for commercial, industrial, or governmental use.

#### THIS WARRANTY IS GIVEN IN LIEU OF ALL OTHER WARRANTIES EXPRESSED OR IMPLIED WHICH ARE SPECIFICALLY EXCLUDED, INCLUDING WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PAR-TICULAR PURPOSE. IN NO EVENT SHALL MOTOROLA BE LIABLE FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES TO THE FULL EXTENT SUCH MAY BE DISCLAIMED BY LAW.

In the event of a defect, malfunction or failure to conform to specifications established be seller, or if appropriate, to specifications accepted by Seller in writing, during the period shown, Motorola, at its option, will either repair or replace the product or refund the purchase price thereof, and such action on the part of Motorola shall be the full extent of Motorola's liability hereunder.

This warranty is void if:

- a. the product is used in other than its normal and customary manner;

- b. the product has been subject to misuse, accident, neglect or damage;

- c. unauthorized alterations or repairs have been made, or unapproved parts used in the equipment.

This warranty extends only to individual products, batteries are excluded. Because each radio system is unique, Motorola disclaims liability for range, coverage, or operation of the system as a whole under this warranty except by a separate written agreement signed by an officer of Motorola.

LICENSED PROGRAMS — Motorola software provided in connection with this order is warranted to be free from reproducible defects for a period of one (1) year. All material and labor to repair any such defects will be provided free of charge for the full warranty period, and SUBJECT TO THE DISCLAIMER IN BOLD FACE TYPE.

Non-Motorola manufactured products are excluded from this warranty, but subject to the warranty provided by their manufacturers, a copy of which will be supplied to you on specific written request.

In order to obtain performance of this warranty, purchaser must contact its Motorola salesperson or Motorola at the address first above shown, attention Quality Assurance Department.

This warranty applies only within the United States.

EPS-48759-0

#### FCC INTERFERENCE WARNING

The FCC Requires that manuals pertaining to Class A and Class B computing devices must contain warnings about possible interference with local residential radio and TV reception. This warning reads as follows:

NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Pules. These limits are designed to provide reas chable protection against harmful interference when the equipment is operated in a commercial or residential environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications.

#### Manual Front Matter (Draft, Continued)

# About This Volume

Volume 2 of the Enhanced Base Transceiver System (EBTS) manual, Base Radios, provides the experienced service technician with an overview of the EBTS operation and functions, and contains information regarding the 800 MHz, 900 MHz, 800/900 MHz QUAD Channel, and 800/900 MHz QUAD+2 Channel base radios.

The EBTS has three major components:

- Generation 3 Site Controller (Gen 3 SC) or integrated Site Controller (iSC)

- Base Radios (BRs)

- RF Distribution System (RFDS)

Installation and testing is described in Volume 1, System Installation and Testing, and RFDS are described in Volume 3, RF Distribution Systems (RFDS). Detailed information about the Gen 3 SC is contained in the Gen 3 SC Supplement Manual, 68P80801E30. Detailed information about the iSC is contained in the iSC Supplement Manual, 68P81098E05

The information in this manual is current as of the printing date. If changes to this manual occur after the printing date, they will be documented and issued as Schaumburg Manual Revisions (SMRs).

# Audience Profile

The target audience of this document includes field service technicians responsible for installing, maintaining, and troubleshooting the EBTS.

In keeping with Motorola's field replaceable unit (FRU) philosophy, this manual provides sufficient functional information to the FRU level. Please refer to the appropriate section of this manual for removal and replacement instructions.

# Manuals On-line

This manual is available on the World Wide Web at *mynetworksup port*, the iDEN customer site. This site was created to provide secure access to critical iDEN Infrastructure information. This web site features a library of iDEN Infrastructure technical documentation such as bulletins, system release documents and product manuals.

The documents are located on the secured extranet website at the URL:

https://mynetworksupport.motorola.com

For information on obtaining an account on this site, go to:

https://membership.motorola.com/motorola.

Manual Front Matter (Draft, Continued)

# General Safety

Important Remember Safety depends on you!!

General safety precautions must be observed during all phases of operation, service, and repair of the equipment described in this manual. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment.

You must heed the safety precautions and warnings listed in the product manuals for your equipment. Any individual using or maintaining the product(s), should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment. Motorola, Inc. assumes no liability for failure to comply with these requirements.

#### Keep Away From Live Circuits

HAZARDOUS VOLTAGE, CURRENT, AND ENERGY LEVELS ARE PRESENT IN THIS PRODUCT. POWER SWITCH TERMINALS CAN HAVE HAZARDOUS VOLTAGES PRESENT EVEN WHEN THE POWER SWITCH IS OFF. DO NOT OPERATE THE SYSTEM WITH THE COVER REMOVED. ALWAYS REPLACE THE COVER BEFORE TURNING ON THE SYSTEM.

Operating personnel must:

- Not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly, or component replacement, or any internal adjustment.

- Not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed.

- Always disconnect power and discharge circuits before touching them.

Manual Front Matter (Draft, Continued)

| General Salely                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ground the<br>Equipment                                            | To minimize shock hazard, the equipment classis and enclosure must be<br>connected to an electrical earth ground. The power cable must be either<br>plugged into an approved three-contact electrical outlet or used with a three-<br>contact to two-contact adapter. The three-contact to two-contact adapter must<br>have the grounding wire (green) firmly connected to an electrical ground<br>(safety ground) at the power outlet. The power jack and mating plug of the<br>power cable must meet International Electrotechnical Commission (IEC)<br>safety standards.                                                                                                                                                     |

| Electro-Static<br>Discharge                                        | Motorola strongly recommends that you use an anti-static wrist strap and a conductive foam pad when installing or upgrading the system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to Electro-Static Discharge (ESD). After removing the component from the system or its protective wrapper, place the component flat on a grounded, static-free surface, and in the case of a board, component-side up. Do not slide the component over any surface.<br>If an ESD station is not available, always wear an anti-static wrist strap that is attached to an unpainted metal part of the system chassis. This will greatly reduce the potential for ESD damage. |

| Do Not Operate In<br>An Explosive<br>Atmosphere                    | Do not operate the equipment in the presence of flammable gases or fumes.<br>Operation of any electrical equipment in such an environment constitutes a<br>definite safety hazard.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Do Not Service Or<br>Adjust Alone                                  | Do not attempt internal service or adjustment, unless another person, capable<br>of rendering first aid and resuscitation, is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Use Caution When<br>Exposing Or<br>Handling a Cathode-<br>Ray Tube | Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. The CRT should be handled only by qualified maintenance personnel, using approved safety mask and gloves.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Do Not Substitute<br>Parts Or Modify<br>Equipment                  | Because of the danger of introducing additional hazards, do not install<br>substitute parts or perform any unauthorized modification of equipment.<br>Contact Motorola Warranty and Repair for service and repair to ensure that<br>safety features are maintained.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Manual Front Matter (Draft, Continued)

# GENERAL SAFETY INFORMATION

The following general safety precautions must be observed during all phases of operation, service, and repair of the equipment described in this manual. The safety precautions listed below represent warnings of certain dangers of which we are aware. You should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### General Safety Precautions

- Read and follow all warning notices and instructions marked on the product or included in this manual before installing, servicing or operating the equipment. Retain these safety instructions for future reference. Also, all applicable safety procedures, such as Occupational, Safety, and Health Administration (OSHA) requirements, National Electrical Code (NEC) requirements, local code requirements, safe working practices, and good judgement must be used by personnel.

- Refer to appropriate section of the product service manual for additional pertinent safety information.

- Because of danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modifications of equipment.

- Identify maintenance actions that require two people to perform the repair. Two people are required when:

- A repair has the risk of injury that would require one person to perform first aid or call for emergency support. An example would be work around high voltage sources. A second person may be required to remove power and call for emergency aid if an accident occurs to the first person.

Note Use the National Institute of Occupational Safety and Health (NIOSH) lifting equation to determine whether a one or two person lift is required when a system component must be removed and replaced in its rack.

- If troubleshooting the equipment while power is applied, be aware of the live circuits.

- DO NOT operate the transmitter of any radio unless all RF connectors are secure and all connectors are properly terminated.

- All equipment must be properly grounded in accordance with Motorola Standards and Guideline for Communications Sites "R56" 68P81089E50 and specified installation instructions for safe operation.

- Slots and openings in the cabinet are provided for ventilation. To ensure reliable operation of the product and to protect if from overheating, these slots and openings must not be blocked or covered.

- Only a qualified technician familiar with similar electronic equipment should service equipment.

- Some equipment components can become extremely hot during operation. Turn off all power to the equipment and wait until sufficiently cool before touching.

#### Human Exposure Compliance

This equipment is designed to generate and radiate radio frequency (RF) energy by means of an external antenna. When terminated into a non-radiating RF load, the base station equipment is certified to comply with Federal Communications Commission (FCC) regulations pertaining to human exposure to RF radiation in accordance with the FCC Rules Part 1 section 1.1310 as published in title 47 code of federal regulations and procedures established in TIA/EIA TSB92, Report On EME Evaluation for RF Cabinet Emissions Under FCC MPE Guidelines. Compliance to FCC regulations of the final installation should be assessed and take into account site specific characteristics.

Manual Front Matter (Draft, Continued)

such as type and location of antennas, as well as site accessibility of occupational personnel (controlled environment) and the general public (uncontrolled environment). This equipment should only be installed and maintained by trained technicians. Licensees of the FCC using this equipment are responsible for insuring that its installation and operation comply with FCC regulations Part 1 section 1.1310 as published in title 47 code of federal regulations.

Whether a given installation meets FCC limits for human exposure to radio frequency radiation may depend not only on this equipment but also on whether the "environments" being assessed are being affected by radio frequency fields from other equipment, the effects of which may add to the level of exposure. Accordingly, the overall exposure may be affected by radio frequency generating facilities that exist at the time the licensee's equipment is being installed or even by equipment installed later. Therefore, the effects of any such facilities must be considered in site selection and in determining whether a particular installation meets the FCC requirements.

FCC OET Bulletin 65 provides materials to assist in making determinations if a given facility is compliant with the human exposure to RF radiation limits. Determining the compliance of transmitter sites of various complexities may be accomplished by means of computational methods. For more complex sites direct measurement of the power density may be more expedient. Additional information on the topic of electromagnetic exposure is contained in the Motorola Standards and Guideline for Communications Sites publication. Persons responsible for installation of this equipment are urged to consult the listed reference material to assist in determining whether a given installation complies with the applicable limits.

In general the following guidelines should be observed when working in or around radio transmitter sites:

- All personnel should have electromagnetic energy awareness training

- All personnel entering the site must be authorized

- Obey all posted signs

- Assume all antennas are active

- Before working on antennas, notify owners and disable appropriate transmitters

- Maintain minimum 3 feet clearance from all antennas

- Do not stop in front of antennas

- Use personal RF monitors while working near antennas

- Never operate transmitters without shields during normal operation

- Do not operate base station antennas in equipment rooms

For installations outside of the U.S., consult with the applicable governing body and standards for RF energy human exposure requirements and take the necessary steps for compliance with local regulations.

#### References

TIA/EIA TSB92 "Report On EME Evaluation for RF Cabinet Emissions Under FCC MPE Guidelines," Global Engineering Documents: http://global.ihs.com/

FCC OET Bulletin 65 "Evaluating Compliance with FCC Guidelines for Human Exposure to Radiofrequency Electromagnetic Fields": http://www.fcc.gov/oet/rfsafety/.

Motorola Standards and Guideline for Communications Sites, Motorola manual 68P81089E50.

IEEE Recommended Practice for the Measure of Potentially Hazardous Electromagnetic Fields – RF and Microwave, IEEE Std C95.3–1991, Publication Sales, 445 Hoes Lane, PO. Box 1331, Piscattaway, NJ 08855–1331

IEEE Standard for Safety Levels with Respect to Human Exposure to Radio Frequency Electromagnetic Fields, 3 kHz to 300 GHz, IEEE C95.1–1991, Publication Sales, 445 Hoes Lane, P.O. Box 1331, Piscattaway, NJ 08855–1331.

#### Specifications (Draft)

#### QUAD+2 Base Radio General Specifications

Table 1-12 lists general specifications for the BR.

#### Table 1-12 QUAD+2 Channel BR General Specifications

| Specification                                     | Value or Range                                                   |

|---------------------------------------------------|------------------------------------------------------------------|

| Dimensions:<br>Height<br>Width<br>Depth<br>Weight | 5.25" (133mm)<br>19" (482.6mm)<br>18" (483mm)<br>45 lbs. (20 kg) |

| Operating Temperature                             | 32° to 122° F (0° to 50° C)                                      |

| Storage Temperature                               | -22° to 140° F (-30° to 60° C)                                   |

| Rx Frequency Range:                               | 806 - 902 MHz                                                    |

| Tx Frequency Range:                               | 851 - 941 MHz                                                    |

| Tx – Rx Spacing:<br>800 MHz iDEN<br>900 MHz iDEN  | 45 MHz<br>39 MHz                                                 |

| Carrier Spacing                                   | 25 kHz                                                           |

| Carrier Capacity*                                 | 1, 2, 3, 4, 5 or 6                                               |

| Frequency Generation                              | Synthesized                                                      |

| Digital Modulation                                | QPSK, M-16QAM, and M-64QAM                                       |

| Power Supply Inputs:<br>VDC<br>VAC                | -48 VDC (-41 to -60 VDC)                                         |

| Diversity Branches                                | Up to 3                                                          |

Note \* Multi-carrier operation must utilize adjacent, contiguous RF carriers.

| Table 1-14 GOADTZ Glatillet necelve opechications | Table 1-14 | QUAD+2 Channel Receive | Specifications |

|---------------------------------------------------|------------|------------------------|----------------|

|---------------------------------------------------|------------|------------------------|----------------|

| Specification                                                               | Value or Range                                      |

|-----------------------------------------------------------------------------|-----------------------------------------------------|

| Static Sensitivity †:<br>800/900 MHz BR                                     | -108 dBm (BER = 8%)                                 |

| BER Floor (BER = 0.01%)                                                     | ≥ -80 dBm                                           |

| IF Frequencies (depends on # of carriers)<br>1st IF (All bands):<br>2nd IF: | Range from 73.300 to 73.425 MHz<br>450 kHz (2nd IF) |

| Frequency Stability *                                                       | 1.5 ppm                                             |

#### Specifications (Draft) (Continued)

#### Table 1-14 QUAD+2 Channel Receive Specifications (continued)

| Specification                       | Value or Range |

|-------------------------------------|----------------|

| RF Input Impedance                  | 50 Ω (nom.)    |

| FCC Designation (FCC Rule Part 15): | ABZ89FR5814    |

Note † Measurement referenced from single receiver input port of BR.

Note \* Stability without site reference connected to station. Receive frequency stability locks to an external site reference, which controls ultimate frequency stability to a level of 50 ppb.

#### QUAD+2 Base Radio Transmit Specifications

Table 1-13 lists the BR transmit specifications.

#### Table 1-13 QUAD+2 Channel BR Transmit Specifications

| Specification                       | Value or Range                  |                                  |

|-------------------------------------|---------------------------------|----------------------------------|

|                                     | Low average<br>output power per | High average<br>output power per |

| Average Power Output:               | carrier                         | carrier                          |

| (800/900 MHZ) Single Carrier        | 5.0W                            | 70W/52.0W                        |

| (800/900 MHZ) Dual Carrier          | 2.5W                            | 26.0W                            |

| (800/900 MHZ) Triple Carrier        | 1.7W                            | 16.1W                            |

| (800/900 MHZ) QUAD Carrier          | 1.3W                            | 10.5W                            |

| (800/900 MHZ) Five Carrier          | 1W                              | 8.7W                             |

| (800/900 MHZ) Six Carrier           | 0.8A                            | 7.3W                             |

| Transmit Bit Error Rate (BER)       | 0.01%                           |                                  |

| Occupied Bandwidth                  | 17.7 kHz per carrie             | er (17.7 to 143 kHz)             |

| Frequency Stability *               | 1.5 ppm                         |                                  |

| RF Input Impedance                  | 50 Ω (nom.)                     |                                  |

| FCC Designation (FCC Rule Part 90): | ABZ89FC5813                     |                                  |

Note \* Transmit frequency stability locks to an external site reference, which controls ultimate frequency stability to a level of 50 ppb.

#### Field Replaceable Units and Orderable Parts (Draft)

Field replaceable units, or FRUs, include special packaging to allow shipment to customers. Parts and FRUs available for customer order are listed in this section. All parts and FRUs are sourced through the Radio Products and Service Division (RPSD).

| Structure of Part / FRU # | Description                                                              |

|---------------------------|--------------------------------------------------------------------------|

| T7132A iDEN QUAD+2        | 2 800 / 900 MHz Base Radio                                               |

| CLF1835B                  | Power Amplifier Tanapa                                                   |

| CLF6528A                  | Combiner board (New kit number for 800/900)                              |

| CLF6506C                  | PA Driver module                                                         |

| CLF6530A                  | PA Final                                                                 |

| CLF6531A                  | PA Low Pass Filter                                                       |

| CLN8053C                  | PA Low Pass Filter<br>PA DC Board<br>NULL Modulator Board                |

| CLN8117A                  | NULL Modulator Board                                                     |

| CLN8215A                  |                                                                          |

| 01740                     | 00A10 PA Mechanics specific                                              |

|                           | 00A19 PA Heatsink and Cover                                              |

| PCUF1001B                 | Transceiver, 6 Channel 800 / 900 MHz                                     |

| PCCN4025A                 | Transceiver board                                                        |

|                           | 00A76 Transceiver Core assembly                                          |

| CLN8221B                  | Hardware, Transceiver, 6-Channel                                         |

| MCPN1082B                 | BR Power Supply Tanapa                                                   |

| 0180706H34                | Chassis and Backplane, Quad2                                             |

| 0180706G92                | •                                                                        |

| 0173000A68                | BR Chassis Core                                                          |

| 43858                     | 26Y01 Plastic shim                                                       |

| CLN8251A                  | BR Card Cage Kit                                                         |

| 0173000A67                |                                                                          |

| 0180706G82                | Fan Assembly                                                             |

| 0173000A34                | Fan Module Parts                                                         |

| CLN8332A                  | QUAD+2 rack filler                                                       |

| CLN8333A                  | FCC Label                                                                |

| T7132A iDEN QUAD+2        | 2 800 / 900 MHz Base Radio                                               |

| X899AF                    | BR FRU packing option (must be added to order for BR to ship standalone) |

| CBN6230A                  | BR Packing kit                                                           |

| DLN6654A Transceiver FI   |                                                                          |

| CUF1001B                  | Transceiver, 6 Channel 800 / 900 MHz                                     |

| CBN6239A                  | PA / Transceiver Packing kit                                             |

|                           | -                                                                        |

| · · · · · ·               | er FRU number                                                            |

| CLF1835B                  | Power Amplifier Tanapa                                                   |

| CBN6239A                  | PA / Transceiver Packing kit                                             |

| DLN6656A BR Power Sur     | pply FRU number                                                          |

| MCPN1082A                 | Power Supply Tanapa                                                      |

| CBN6240A                  | Power Supply Packing kit                                                 |

| DLN6657A Fan Assembly     | FRII number                                                              |

| 0180706G82                | Fan Assembly Tanapa                                                      |

| CBN6244A                  | Fan Packing kit                                                          |

|                           |                                                                          |

#### Tune-Up Procedure

There is no field tune-up procedure. All adjustments are software controlled and are pre-set at the factory. Certain station operating parameters can be changed via man-machine interface (MMI) commands, within predetermined limits. Examples include transmit / receiver operating frequencies and transmitter power level.

Functional Description / Operation of Modules (Draft)

The following pages are excerpts from the manual and are intended to give an overview of the base radio and the modules that comprise the base radio. The content of the finalized manual will be similar to what is shown here.

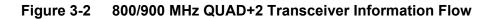

|            | QUAD+2 Base Radio<br>Theory of Operation | The QUAD+2 Channel BR operates together with other site controllers and equipment that are properly terminated. The following description assumes such a configuration. Figure 1-11 shows an overall block diagram of the QUAD+2 Channel BR.                                                                                                                         |

|------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                          | Power is applied to the DC Power inputs located on the QUAD+2 Channel BR backplane. The DC Power input is connected if -48 VDC or batteries are used in the site.                                                                                                                                                                                                    |

| 9          |                                          | Power is applied to the BR by setting the Power Supply power switch to the ON position. Upon power-up, the QUAD+2 Channel BR performs self-diagnostic tests to ensure the integrity of the unit. These tests, which include memory and Ethernet verification routines, primarily examine the EX / CNTL.                                                              |

| <b>y-0</b> |                                          | After completing self-diagnostic tests, the QUAD+2 Channel BR reports<br>alarm conditions on any of its modules to the site controller via Ethernet.<br>Alarm conditions may also be verified locally. Local verification involves<br>using the service computer and the STATUS port located on the front of the<br>QUAD+2 Channel BR.                               |

| 5-May-06   |                                          | The software resident in FLASH on the XCVR registers the BR with the site controller via Ethernet. After BR registration on initial power-up, the BR software downloads via Ethernet and executes from RAM. The download includes operating parameters for the QUAD+2 Channel BR. These parameters allow the QUAD+2 Channel BR to perform call processing functions. |

#### QUAD+2 Base Radio Overview

After software downloads to the BR via Ethernet, FLASH memory stores the software object. Upon future power-ups, the software object in FLASH loads into RAM for execution.

The BR operates in a TDMA (Time Division Multiple Access) mode. This mode, combined with voice compression techniques, increases channel capacity by a ratio of as much as six to one. TDMA divides both the receive and transmit signals of the BR into six individual time slots. Each receive slot has a corresponding transmit slot. This pair of slots comprises a logical RF channel.

The BR uses diversity reception for increased coverage area and improved quality. The Receiver modules within the QUAD+2 Channel BR contain three receiver paths. Two-branch diversity sites use two Receiver paths, and three-branch diversity sites use three Receiver paths.

All Receiver paths within the Transceiver module are programmed to the same receiver frequency. Signals from each receiver are diversity combined and undergo error-correction. Then, via Ethernet, the site controller acquires the signal, along with control information about signal destination.

Two separate FRUs comprise the transmit section of the QUAD+2 Channel BR. These are the Exciter and Control (XCVR) portion of the Transceiver and the Power Amplifier (PA). The Exciter processes commands from the CNTL, assuring transmission in the proper modulation format. Then the low-level signal enters the PA. The PA amplifies this signal to the desired output power level. The PA is a continuously keyed linear amplifier. A power control routine monitors the output power of the BR. The routine adjusts the power as necessary to maintain the proper output level.

## Overview **Overview**

**Number Cross**

Reference

This chapter provides information on the QUAD+2 Base Radio Transceiver (XCVR).

**FRU Number to Kit** Base Radio Transceiver (XCVR) Field Replaceable Units (FRUs) are available for the iDEN EBTS. The FRU contains the XCVR kit and required packaging. Table 3-1 provides a cross reference between XCVR FRU numbers and kit numbers.

#### Table 3-1 FRU Number to Kit Number Cross Reference

| Description                           | FRU<br>Number | Kit<br>Number |  |

|---------------------------------------|---------------|---------------|--|

| QUAD+2 Channel Base Radio Transceiver | DLN6654       | PCUF1001      |  |

# **QUAD+2** Channel Base Radio Transceiver

| QUAD+2 Base Radio<br>Overview | The transceiver (XCVR) module provides the control, exciter and receiver functions for the Base Radio.                                                                                                                                                        |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | The XCVR generates the station reference which typically needs to be locked<br>on to one of many possible external sources. The external source can be either<br>the site controller 20 MHz TDM clocks or the external reference operating at<br>5 or 10 MHz. |

|                               | The XCVR SPI bus allows communication with its receiver and exciter circuitry, as well as the power supply and power amplifier modules.                                                                                                                       |

|                               | The XCVR circuit board contains two major sections:                                                                                                                                                                                                           |

|                               | <ul> <li>XCVR Control : Performs the control management, digital signal<br/>processing, and transmit and receive data formatting for the Base Radio.</li> </ul>                                                                                               |

|                               | <ul> <li>XCVR RF : Contains DC power conversion/regulation and performs<br/>receiver and exciter functions.</li> </ul>                                                                                                                                        |

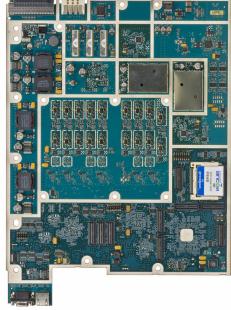

|                               | Figure 3-1shows a top view of the Transceiver.                                                                                                                                                                                                                |

#### Figure 3-1 800/900 MHz QUAD+2 Channel Transceiver (Front View)

| _                              |                                                                                                                                                                                                                                                                                  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transceiver Control<br>Section | The main operating software for the base radio is loaded in the XCVR's control section. As the main manager for the base radio, the XCVR control provides operational control over the other station modules. It handles three types of information flow, in the following ways: |

|                                | <ul> <li>Serves as a gateway between the network and RF functionality, by<br/>distributing the RF payload to and from the network</li> </ul>                                                                                                                                     |

|                                | <ul> <li>Supports operational and diagnostic functions with digital control data (for<br/>example: site information, channel assignments, and identification numbers<br/>for call processing)</li> </ul>                                                                         |

|                                | <sup>n</sup> Ensures the flow of other network management configuration information                                                                                                                                                                                              |

|                                | Figure 3-2 shows the information flow through the transceiver Control and RF sections for HPD systems.                                                                                                                                                                           |

Transceiver RF Section

In addition to DC power conversion/regulation, the XCVR RF section provides circuitry for the following receiver and exciter functions.

#### Exciter

The exciter on the XCVR RF section provides the transmitter functions for the base radio. The exciter circuitry generates a low-level, modulated RF signal that passes to the power amplifier. It supports various modulation types as well as bandwidths up to 25 kHz, through software programming.

The exciter also provides a controlled output power level to the power amplifier.

Enhanced Base Transceiver System (EBTS)

5-May-06

#### Receiver

The QUAD+2 receiver provides multiple receiver inputs for one to three diversity branches with multiple channels of up to six channels within each branch. The receiver is tuned to pass frequenies anywhere between 806 MHz and 901 MHz. The receiver is best suited for:

- n Low density RF environments

- n Stations with external multicouplers

- n Stations with requirements for multi-frequency operation beyond 14 MHz

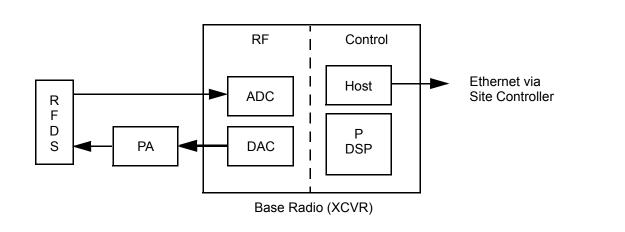

# Controls and Indicators

The transceiver external interfaces include 2 external ports, a switch and LEDs. The ports and switch are described here. The LED states are listed in the reference section of the documentation. Figure 3-3 shows the port, switch and LED locations when the access door is opened. Figure 3-4 shows the Rear View connectors.

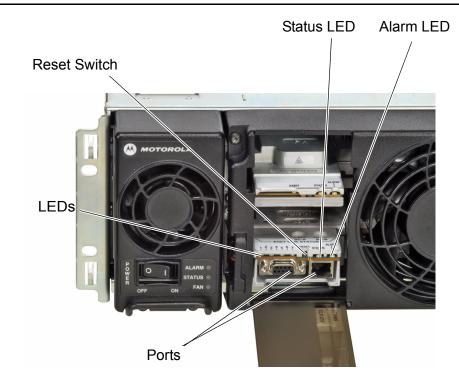

#### Figure 3-3 800/900 MHz QUAD+2 QUAD+2 Transceiver (with access door opened)

#### Figure 3-4 800/900 MHz QUAD+2 Transceiver Backplane (Rear View)

#### Transceiver Ports - Front

Two ports are accessible via a dropdown door to the left of the fans. An asynchronous port and a synchronous port.

Table 3-2Transceiver Connections

| XCVR Port /<br>Type   | Connects to this<br>Device/Port | Description                            |

|-----------------------|---------------------------------|----------------------------------------|

| RJ-45                 | 10/100BaseT port                | Ethernet port for future use.          |

| Service port,<br>DB-9 | Service PC, RS-232<br>port      | Serial service port for configuration. |

#### Transceiver Ports - Rear

The transceiver interconnects to the backplane using a 120–pin HVDML digital connector and 8–pack RF connector, as shown in Figure 3-4. These connections handle multiple signals including power, power supply communications, power amplifier communications, 10Base2 Ethernet, fan interface and peripheral interface. The digital connection receives alarm data and the site controllers' TDM signals, which are used to pass reference and control data to the station.

#### **Transceiver Switch**

There is one multifunction switch on the front of the transceiver module, accessible via the dropdown door to the left of the fans.

Table 3-3 lists the Transceiver Front Switch Functions.

#### Table 3-3 XCVR Front Switch Functions

| User Action                             | Result                           |

|-----------------------------------------|----------------------------------|

| Press switch for less than 1 second     | Access Disable                   |

| Press switch for greater than 3 seconds | Transceiver Control Module Reset |

#### Transceiver LEDs

Table 3-4 and Table 3-5 lists the Transceiver LEDs.  $\$

# Table 3-4QUAD+2 Channel Base Radio Status and Alarm LED<br/>Indications

| Condition  | Status LED       | Alarm LED      |

|------------|------------------|----------------|

| No Power   | Off              | Off            |

| Lamp Test  | Green            | Red            |

| Failure    | Off              | Red            |

| Impaired   | Green            | Red (blinking) |

| Booting Up | Green (blinking) | Off            |

| Online     | Green            | Off            |

#### Table 3-5 QUAD+2 Channel Base Radio Transceiver LED Indications

| Label | LED State        | Description                                                                           |

|-------|------------------|---------------------------------------------------------------------------------------|

|       | Green            | Proper Base Radio operation with no alarm conditions and channel 1 is keyed           |

| 1     | Green (Blinking) | Channel 1 is not keyed                                                                |

|       | Off              | Channel 1 is not in operation or the Base Radio is out of service or power is removed |

|       | Green            | Proper Base Radio operation with no alarm conditions and channel 2 is keyed           |

| 2     | Green (Blinking) | Channel 2 is not keyed                                                                |

|       | Off              | Channel 2 is not in operation or the Base Radio is out of service or power is removed |

#### Table 3-5 QUAD+2 Channel Base Radio Transceiver LED Indications (continued)

| Label           | LED State        | Description                                                                           |

|-----------------|------------------|---------------------------------------------------------------------------------------|

| 3               | Green            | Proper Base Radio operation with no alarm conditions and channel 3 is keyed           |

|                 | Green (Blinking) | Channel 3 is not keyed                                                                |

|                 | Off              | Channel 3 is not in operation or the Base Radio is out of service or power is removed |

|                 | Green            | Proper Base Radio operation with no alarm conditions and channel 4 is keyed           |

| 4               | Green (Blinking) | Channel 4 is not keyed                                                                |

|                 | Off              | Channel 4 is not in operation or the Base Radio is out of service or power is removed |

| 5<br>(See Note) | Green            | Proper Base Radio operation with no alarm conditions and channel 5 is keyed           |

|                 | Green (Blinking) | Channel 5 is not keyed                                                                |

|                 | Off              | Channel 5 is not in operation or the Base Radio is out of service or power is removed |

| 6<br>(See Note) | Green            | Proper Base Radio operation with no alarm conditions and channel 6 is keyed           |

|                 | Green (Blinking) | Channel 6 is not keyed                                                                |

|                 | Off              | Channel 6 is not in operation or the Base Radio is out of service or power is removed |

**Note** Five and six carrier operation is only supported in Test Application mode and requires licensing agreement with Motorola for activation in Call Processing mode.

#### **Transceiver Band States**

Table 3-6 lists the Transceiver Band States

#### Table 3-6

#### QUAD+2 Channel Base Radio Band State

| Label | LED State   | BR Band              |

|-------|-------------|----------------------|

|       | Solid Red   | Install Band Failure |

| 7     | Solid Green | 800 MHz              |

|       | Solid Amber | 900 MHz              |

#### Theory of Operation - Controller Section

Table 3-7 briefly describes the BRC circuitry. Figure 3-5 shows the Controller with the cover removed. Figure 3-8 shows the Controller's functional block diagram.

Table 3-7

Control Section Circuitry

| Circuit                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Microprocessor                  | Contains integrated circuits that comprise the central controller of the BRC and station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Non-Volatile Memory                  | <ul> <li>Consists of:</li> <li>FLASH containing the station operating software</li> <li>Codeplug data</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Volatile Memory                      | Contains SDRAM to store station software used to execute commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Ethernet Interface                   | Provides the BRC with a 10Base2 Ethernet<br>communication port to network both control and<br>compressed voice data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RS-232 Interface                     | Provides the BRC with an RS-232 serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Digital Signal Processor             | Performs high-speed modulation/demodulation of compressed audio and signaling data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2QIC                                 | <ul> <li>Contains integrated circuits that provide:</li> <li>Highly stable, reclocked transmit signals and peripheral transmit control logic</li> <li>Receive SPI capability for receive control, metering ADC and signal path attenuators</li> <li>Receive DSP functions including baseband mixing and digital filtering for multiple branches with multiple channels with interleaved serialization of output</li> <li>Synthesizer for station reference and related control</li> <li>Site Reference timing decode and related Base Radio timing signals generation</li> <li>SPI interface to ADC devices for metering</li> </ul> |

| Station Reference<br>Circuitry       | Generates the 16.8 MHz and 48 MHz reference signals used throughout the station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Remote Station Shutdown              | Provides software control to cycle power on the BR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Serial Peripheral Interface<br>(SPI) | Provides serial control and metering capability<br>with the exciter, receiver, power amplifier, and<br>power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# Figure 3-5 Controller Section (with housing removed)

#### Host Microprocessor

The host microprocessor is the main controller for the BR. The processor operates at a 266-MHz core clock speed. The processor controls Base Radio operation according to station software in memory. Station software resides in FLASH memory. For normal operation, the system transfers this software to volatile S-DRAM memory.

**Note** At BR power-up and normal conditions, the Status and Alarm LEDs transition through the Conditions stated in Table 3-4 as follows: Power Off, Failure, Lamp Test, Booting Up and Online states as indicated in Table 3-4. Any other sequence of Conditions indicates an impairment or failure.

#### Serial Communication Buses

The microprocessor provides a general-purpose SMC serial management controller bus.

#### **Base Radio Transceiver**

### QUAD+2 Channel Base Radio Transceiver

The SMC serial communications bus is an asynchronous RS-232 interface with no hardware handshake capability. The BRC front panel includes a ninepin, D-type connector. This connector provides a port where service personnel may connect a service computer. Service personnel can perform programming and maintenance tasks via Man-Machine Interface (MMI) commands. The interface between the SMC port and the front- panel STATUS connector is via EIA-232 Bus Receivers and Drivers.

# MPC8250 Host Processor

The MPC8250 microprocessor incorporates 16k bytes of instruction cache and 16k bytes of data cache that significantly enhance processor performance.

The microprocessor has a 32-line data bus. The processor uses this bus to access non-volatile memory and SDRAM memory. Via memory mapping, the processor also uses this bus to control other BRC circuitry.

The microprocessor uses its Chip Select capability to decode addresses and assert an output signal. The chip-select signals select non-volatile memory, SDRAM memory, and DSP.

The microprocessor has a Local Bus that is used to interface to the DSP.

The Host processor...

- Provides serial communications between the Host Microprocessor and other Base Radio devices and modules for control and metering of radio functions.

- n Provides RS-232 serial user interface

- Provides condition signals necessary to access SDRAM, FLASH, and Compact Flash

- n Accepts interrupt signals from BRC circuits (such as DSP and 2QIC).

- n Organizes the interrupts, based on hardware-defined priority ranking.

- The Host supports several internal interrupts from its Communications Processor Module. These interrupts allow efficient use of peripheral interfaces.

- n The Host supports 10/100 Mbps BaseT and 10Base2 Ethernet/IEEE 802.3

- <sup>n</sup> Provides a 32-line data bus transfers data to and from BRC SDRAM and other BRC circuitry.

- n Provides a Local Bus for communciations with the DSP

#### Non-Volatile Memory

Base Radio software resides in a minimum of 32M x 16 bits of Compact FLASH memory and 16M x 16 bits of additional board FLASH. The Host Microprocessor addresses the Compact FLASH memory with 4 of the host address bus' 32 lines in conjunction with the data lines. The host accesses FLASH data over the 16-line host data bus. A host-operated chip-select line provides control signals for these transactions.

FLASH memory contains the operating system and application code. The system stores application code in Compact FLASH for fast recovery from reset conditions. Application code transfers from network or site controllers may occur in a background mode. Background mode transfers allow the station to remain operational during new code upgrades.

The data that determines the station personality (codeplug) resides in the 16M x 16 bit FLASH. The microprocessor addresses the FASH with 24 of the host address bus' 32 lines. The host accesses FLASH data with 16 of the data bus' 32 lines. A host-operated chip-select line provides control signals for these transactions.

During the manufacturing process, the factory programs the codeplug's default data. The BRC must download field programming data from network and site controllers. This data includes operating frequencies and output power level. The station permits adjustment of many station parameters, but the station does not store these adjustments. Refer to the Software Commands chapter for additional information.

#### Volatile Memory

Each BRC contains 16MB x 32 bits of SDRAM. The BRC downloads station software code into SDRAM for station use. SDRAM also provides short-term storage for data generated and required during normal operation. SDRAM is volatile memory. A loss of power or system reset destroys SDRAM data.

The system performs read and write operations over the Host Address and Data buses. These operations involve column and row select lines under control of the Host processor's DRAM controller. The Host address bus and column row signals sequentially refresh SDRAM memory locations.

## Ethernet Interface

The Host processor's Communications Processor Module (CPM) provides the Local Area Network (LAN) Controller for the Ethernet Interface. The LAN function implements the CSMA/CD access method, which supports the IEEE 802.3 10Base2 standard.

The LAN coprocessor supports all IEEE 802.3 Medium Access Control, including the following:

Enhanced Base Transceiver System (EBTS)

5-May-06

- n framing

- n preamble generation

- n stripping

- n source address generation

- n destination address checking

The PCM LAN receives commands from the CPU.

The Ethernet Serial Interface works directly with the CPM LAN to perform the following major functions:

- n 10 MHz transmit clock generation (obtained by dividing the 20 MHz signal provided by on-board crystal)

- n Manchester encoding/decoding of frames

- n electrical interface to the Ethernet transceiver

An isolation transformer provides high-voltage protection. The transformer also isolates the Ethernet Serial Interface (ESI) and the transceiver. The pulse transformer has the following characteristics:

- n Minimum inductance of 75 μH

- n 2000 V isolation between primary and secondary windings

- n 1:1 Pulse Transformer

The Coaxial Transceiver Interface (CTI) is a coaxial cable line driver and receiver for the Ethernet. CTI provides a 10Base2 connection via a coaxial connector on the board. This device minimizes the number of external components necessary for Ethernet operations.

A DC/DC converter provides a constant voltage of -9 Vdc for the CTI from a 3.3 Vdc source.

The CTI performs the following functions:

- n Receives and transmits data to the Ethernet coaxial connection

- n Reports any collision that it detects on the coaxial connection

- Disables the transmitter when packets are longer than the legal length (Jabber Timer)

#### Digital Signal Processors

The BRC includes one Digital Signal Processor for receive and transmit processing. This DSP and related circuitry process compressed station transmit and receive audio and data. The related circuitry includes the QUAD+2 Integrated Circuit (2QIC). The DSP only accepts input and output signals in digitized form.

The DSP inputs are digitized receiver signals. The DSP outputs are digitized voice audio and data (modulation signals). These signals pass from the DSP to the Exciter section of the QUAD+2. DSP communicates with the Microprocessor via a 32-bit, host data bus on the host processor side. Interrupts drive communication between the DSP and the host.

The DSP operate from an external 49 MHz clock, provided by the CPLD and phase locked to the 16.8 MHz local station reference clock. The DSP internal core operating clock signal is 394MHz, produced by an internal Phase-Locked Loop (PLL).

The DSP accepts receive digitized signals from the 2QIC through the Time-Division Multiplexing (TDM) interface ports. The QUAD+2 uses 3 of these ports. All 3 ports use the same clock and framesync signals to input data. Each port handles digital data for 1 of the 3 branches. Each port handles digitized data for 6 channels, 2 status words, and 2 power detect words.

The QUAD+2 accesses its DSP program and signal-processing algorithms in 1440 kB of internal memory. The DSP communicates with the host bus over an 32-bit interface.

The DSP communicates with the 2QIC to provide serial communications to the receiver paths for receiver control over a Serial Peripheral Interface (SPI) link. The 2QIC provides a parallel-to-serial conversion circuit that accepts parallel data from the DSP and serial data to the receive circuitry.

The DSP sends up to six carriers of digitized signal to the 2QIC along with embedded control signals. Two framed and synchronized data streams are output. One data stream is I-data, and the other is the Q-data stream. The control bits are appendended at the end of the data streams. The 2QIC extracts and applies the control signals. The 2QIC synchronizes the 2QIC I and Q output frames with system timing signals that exist in the 2QIC. The synchronized outputs are sent to a Digital to Analog Converter (DAC) in the exciter section that converts the digital signals to analog.

#### 2QICplus

The 2QIC controls internal DSP operations. This circuit provides the following functions:

The 2QICplus is a DSP programmable FPGA that provides the circuit integration needed to condition, route and control receive and transmit data between the RF circuitry and the DSP, and provide consolidated monitoring and control for QUAD+2 transceiver. Following are the major functions of the 2QICplus

- <sup>n</sup> For nitialization and control, the 2QICplus interfaces with the DSP through address and data buses.

- Provides six Independent Abacus III receiver data and control interfaces with fault detection and handling

RF Signal Gain Control for 18 receiver paths

n

- Programmable General-Purpose Input/Output pins for monitor and control of the transceiver

- n Provides clocks required for the transceiver

- Phase detector for the 16.8MHz Synthesizer and PLL with PLL steering line gate control

- <sup>n</sup> Inputs a site reference signal, demodulates a 1PPS timing marker from this signal and outputs the 1PPS signal for network timing alignment.

- n 15 ms and 7.5 ms timing signals generation. (These signals are synchronize to the 1 PPS time mark. The system decodes the time mark from the site reference. Then the system routes the reference to the DSP.)

- <sup>n</sup> Programmable Interrupt Controller for metering and status.

- Provides serial transmit data translation and tranmit control and synchronization to the network timing

- Complex Mixer capability to translate each of the six receive channels to DC

- Polyphase 256 FIR filter with decimation by 10 for enhancing channel selectivity

- n Signal Energy detector for signal strength indication used for system signal path attenuator control

- Provides output serializers to Time Division Multiplex information for six channels two status values and two Energy Detection values for each branch

## Station Reference Circuitry

The Station Reference Circuitry is a phase-locked loop (PLL). This PLL consists of a high-stability, Voltage-Controlled, Crystal Oscillator (VCXO) and a PLL IC. GPS output from the iSC connects to the 5 MHz/1 PPS BNC connector on the BR backplane. Wiring at this connector routes signals to EXBRC station reference circuitry.

The PLL compares the 5 MHz reference frequency to the 16.8 MHz VCXO output. Then the PLL generates a DC correction voltage. The PLL applies this correction voltage to the VCO through an analog gate. The analog gate closes when three conditions coexist: (1) The 5 MHz tests stable. (2) The PLL IC is programmed. (3) Two PLL oscillator and reference signal output alignments occur.

A loss of the 5 MHz/1PPS signal causes the control voltage enable switch to open. This permits the PLL to free run, which allows the BR to retain a clock for control purposes.

When the gate enables, the control voltage from the PLL can adjust the highstability VCXO frequency. The adjustment can achieve a stability nearly equivalent to that of the external, 5 MHz frequency reference.

The correction voltage from the PLL continuously adjusts the VXCO frequency. The VXCO outputs a 16.8 MHz clock signal. The circuit applies this clock signal to the receiver, 48 MHz reference and TISIC.

The receivers use the 16.8MHz as the clock input and synthesizer reference.

The 48 MHz EXBRC synthesizer uses the 16.8 MHz as its synthesizer reference. The 48 MHz synthesizer output is the clock input for the TXDSP I and Q data reclock circuitry.

The TISIC divides the 16.8 MHz signal by seven, and outputs a 2.4 MHz signal. This output signal then becomes the 2.4 MHz reference for the Exciter.

#### **Input Ports**

One general-purpose input register provides for BRC and station circuit input signals. The register has 16 input ports. The Host Data Bus conveys input register data to the Host Microprocessor. Typical inputs include 16.8 and 48 MHz Station Reference Circuitry status outputs and reset status outputs.

#### **Output Ports**

Two general-purpose output registers distribute control signals from the Host Microprocessor to the BRC and station circuitry. One register has 32 output ports and the other register has 8 output ports. Control signal distribution occurs over the backplane. The Host Data Bus drives the output ports' latched outputs. Typical control signals include front-panel LED signals and SPI peripheral enable and address lines.

#### Remote Station Shutdown

The BRC contains power supply shutdown circuitry. This circuitry can send a shutdown pulse to the Base Radio Power Supply. BRC software generates the shutdown control pulse.

After receiving a shutdown pulse, the power supply turns off BR power. Shut down power sources include 3.3, 28.6 and 14.2 Vdc sources throughout the BR. Due to charges retained by BR storage elements, power supply voltages may not reach zero. The shutdown only assures that the host processor enters a power-on-reset state.

A remote site uses the shutdown function to perform a hard reset of all BR modules.

| Theory of Operation<br>- Exciter and Power<br>Amplifier Section | The Exciter and the Power Amplifier (PA) provide the transmitter functions of<br>the QUAD+2 Channel 800/900 MHz Base Radio. The Exciter module<br>consists of a printed circuit board, a slide in housing, and associated hardware.<br>The BRC shares the printed circuit board and housing. |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                 | The Exciter connects to the Base Radio backplane through a 168-pin<br>connector and two blindmate RF connectors. Controller and exciter circuitry<br>also interconnect on the Exciter/Controller module. Two Torx screws on the<br>front of the Exciter secure it to the chassis.            |

|                                                                 | An LED identifies the Exciter's operational condition, as described in the manual's Controller section. The Base Radio section of the manual provides specifications for transmitter circuitry. This information includes data on the Exciter and PAs.                                       |

| RF- Exciter Board                                               | Table 3-8 describes the basic circuitry of the Exciter. Figure 3-6 shows the                                                                                                                                                                                                                 |

Exciter with the housing removed. Figure 3-9 show the Exciter's functional block diagram.

| Table 3-8         Exciter Board Circuitry |                                                                                                                                                                                    |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Circuit                                   | Description                                                                                                                                                                        |  |

| LNODCT IC                                 | <ul> <li>Up-converts baseband data to the transmit frequency</li> <li>Down-converts the PA feedback signal to baseband</li> <li>Uses a baseband Cartesian feedback loop</li> </ul> |  |

|                                           | system, necessary to obtain linearity from the transmitter and avoid splattering power into adjacent channels                                                                      |  |

|                                           | <ul> <li>Performs training functions for proper<br/>linearization of the transmitter</li> </ul>                                                                                    |  |

| Memory & A/D Converter                    | Serves as the main interface between the synthesizer, Tranlin IC, A/D, and EEPROM on the Exciter, and the BRC via the SPI bus                                                      |  |

| Frequency Synthesizer<br>Circuitry        | Consists of a phase-locked loop and VCO                                                                                                                                            |  |

|                                           | <ul> <li>Provides a LO signal to the LNODCT IC for<br/>the second up-conversion and first down-<br/>conversion of the feedback signal from the<br/>PA</li> </ul>                   |  |

| 1025 MHz VCO (900 MHz<br>BR)              | Provides a LO signal to the LNODCT IC, for up-<br>conversion to the transmit frequency                                                                                             |  |

#### Tabla 2 0 .:4 ......

Table 3-8

Exciter Board Circuitry

| Circuit                      | Description                                                                                                                                                                                                   |