# CPX8000 Series CPX8216/CPX8216T CompactPCI® System

## **Reference Manual**

CPX8216A/RM4

August 2002 Edition

#### © Copyright 2002 Motorola Inc.

#### All rights reserved.

#### Printed in the United States of America.

Motorola® and the Motorola symbol are registered trademarks of Motorola, Inc.

PowerPC® and the PowerPC logo are registered trademarks of International Business Machines Corporation (IBM) and are used by Motorola, Inc. under license from IBM.

CompactPCI® is a registered trademark of the PCI Industrial Computer Manufacturer's Group (PICMG).

All other product or service names mentioned in this document are trademarks or registered trademarks of their respective holders.

### **Safety Summary**

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the equipment is supplied with a three-conductor AC power cable, the power cable must be plugged into an approved three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

#### Keep Away From Live Circuits Inside the Equipment.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified service personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Service personnel should not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, such personnel should always disconnect power and discharge circuits before touching components.

#### Use Caution When Exposing or Handling a CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, do not handle the CRT and avoid rough handling or jarring of the equipment. Handling of a CRT should be done only by qualified service personnel using approved safety mask and gloves.

### Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that all safety features are maintained.

### Observe Warnings in Manual.

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

To prevent serious injury or death from dangerous voltages, use extreme caution when handling, testing, and adjusting this equipment and its components.

## **Flammability**

All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers.

## **CE Notice (European Community)**

This is a Class A product. In a domestic environment, this product may cause radio interference, in which case the user may be required to take adequate measures.

Motorola Computer Group products with the CE marking comply with the EMC Directive (89/336/EEC). Compliance with this directive implies conformity to the following European Norms:

EN55022 "Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment"; this product tested to Equipment Class A

EN55024 "Information technology equipment—Immunity characteristics—Limits and methods of measurement"

This product also fulfills EN60950 (product safety) which is essentially the requirement for the Low Voltage Directive (73/23/EEC).

AC configurations of this system also meet the requirements of the following European standards:

EN61000-3-2 "Limits of Harmonic Current Emissions (equipment input current ≤ 16 A per phase)"

EN61000-3-3 "Limits of Voltage Fluctuations and Flicker in Low-Voltage Supply Systems for Equipment with Rated Current ≤ 16 A"

In accordance with European Community directives, a "Declaration of Conformity" has been made and is available on request. Please contact your sales representative.

This product is not a workstation per the European Ergonomic Standard.

Kein Bildschirmarbeitsplatz nach dem Europäischen Ergonomie Standard.

#### **FCC Class A**

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

Changes or modifications not expressly approved by Motorola Computer Group could void the user's authority to operate the equipment.

Use only shielded cables when connecting peripherals to assure that appropriate radio frequency emissions compliance is maintained.

### **EMI Caution**

This equipment generates, uses and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection.

### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to the Motorola Computer Group Web site. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Motorola, Inc.

It is possible that this publication may contain reference to or information about Motorola products (machines and programs), programming, or services that are not available in your

country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

## **Limited and Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

## **Contents**

### **About this Manual** Summary of Changes ......xix Systems Supported xxi Overview .....xxii Comments and Suggestions xxii Conventions Used in This Manual xxiii **CHAPTER 1** System Architecture PICMG Compliance 1-1 System Domains 1-1 System Layout 1-2 CPX8216T (H.110) ......1-4 System Processor Configurations 1-7 I/O Configurations .......1-10 Drive Modules ......1-11 The CPU Module 1-12

| Hot Swap Control Status Register (CSR)     | 1-16 |

|--------------------------------------------|------|

| The Hot Swap Process                       | 1-16 |

| Physical Connection Process                | 1-17 |

| Hardware Connection Process                | 1-17 |

| Software Connection Process                | 1-18 |

| Software Disconnection Process             | 1-18 |

| Typical Insertion and Extraction Processes | 1-19 |

| Device Drivers                             | 1-19 |

| CHAPTER 2 CPU Modules                      |      |

| Overview                                   | 2-1  |

| CPX750HA                                   | 2-1  |

| Connectors and Jumper Settings             |      |

| Backplane Connectors (P5, P4, P3, P2, P1)  |      |

| Front USB Connectors (J17 and J18)         |      |

| 10BaseT/100BaseTx Connector (J8)           |      |

| COM1 Connector (J15)                       |      |

| Debug Connector (J19)                      |      |

| DRAM Mezzanine Connector (J10)             | 2-10 |

| EIDE Compact FLASH Connector (J9)          | 2-14 |

| Flash Bank Selection (J6)                  | 2-15 |

| CPV5350                                    | 2-16 |

| Connectors                                 | 2-18 |

| Transition Module                          | 2-19 |

| DRAM Memory Configuration                  | 2-20 |

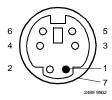

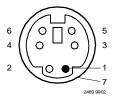

| Keyboard/Mouse PS2 Connector               | 2-20 |

| Ethernet Connectors                        | 2-21 |

| Universal Serial Bus (USB) Connector       | 2-21 |

| Serial Port Connectors                     | 2-22 |

| Video Connector                            | 2-22 |

| CHAPTER 3 CPX8540 Carrier Card             |      |

| Overview                                   |      |

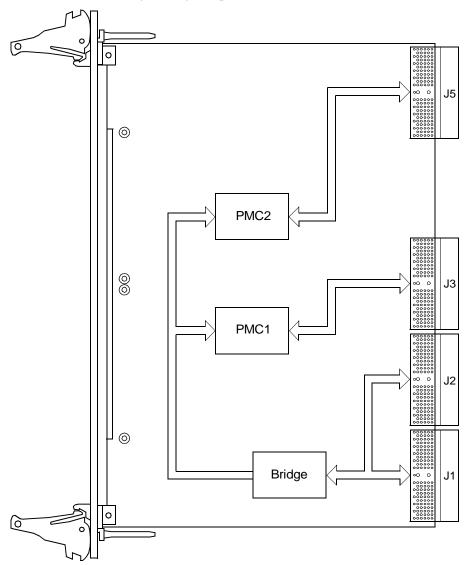

| CPX8540 Carrier Card                       | 3-1  |

| Connector Pinouts                          | 3-4  |

### **CHAPTER 4 PMC Modules**

| Overview                                                       | 4-1  |

|----------------------------------------------------------------|------|

| SCSI-2 Controller PMC                                          | 4-1  |

| Switch Settings                                                | 4-3  |

| Connector Pin Assignments                                      | 4-4  |

|                                                                |      |

| CHAPTER 5 Transition/Bridge Modules                            |      |

| Overview                                                       | 5-1  |

| CPX750HATM Transition Module                                   | 5-1  |

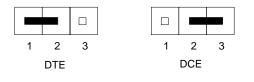

| Serial Ports 3 and 4 Default Configuration                     | 5-2  |

| Serial Port Interface Jumper (J8 and J9)                       |      |

| Connectors                                                     | 5-4  |

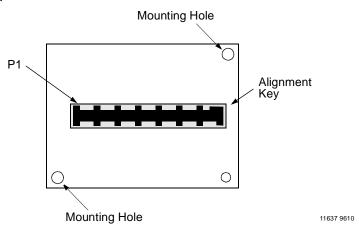

| Backplane Connectors (J3/J4/J5)                                | 5-4  |

| Asynchronous Serial Port Connectors (J10 and J11)              | 5-6  |

| Asynchronous/Synchronous Serial Port Connectors (J6 and J24) . | 5-7  |

| Parallel I/O Port Connector (J7)                               | 5-9  |

| Keyboard/Mouse Connector (J16)                                 | 5-10 |

| USB Connectors (J19 and J18)                                   | 5-10 |

| EIDE Connector (J15)                                           |      |

| Floppy Port Connector (J17)                                    |      |

| +5Vdc Power Connector (J14)                                    |      |

| Speaker Output Connector (J13)                                 |      |

| PMC I/O Connectors                                             |      |

| Installing the Serial Interface Modules                        |      |

| Port Configuration Diagrams                                    |      |

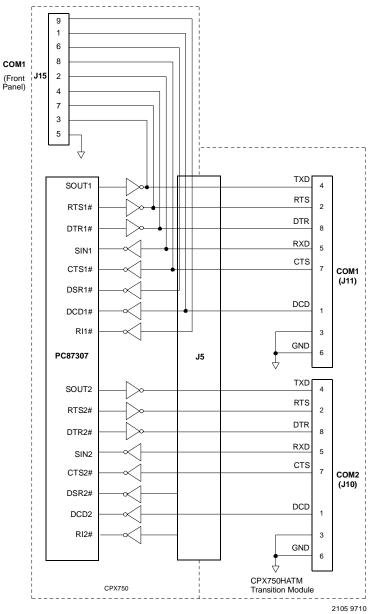

| COM1 and COM2 Asynchronous Serial Ports                        |      |

| Asynchronous/Synchronous Serial Ports                          |      |

| CPV5350TM80 Transition Module                                  |      |

| Connectors                                                     |      |

| Keyboard/Mouse PS2 Connector                                   |      |

| Ethernet Connectors                                            |      |

| Serial Port Connectors                                         |      |

| Video Connector                                                |      |

| Parallel Port Connector (J20)                                  |      |

| EIDE Headers (J5)                                              |      |

| Floppy Header (J9)                                             |      |

| Keyboard/Mouse/Power LED Header (J6)                           |      |

| USB Headers (J12 and J19)                                      |      |

| SM Bus and LM78 Header (J1)                                    |      |

| Fan Tachometer Headers (J3 and J4)                             | 5-43 |

| Indicator LED/Miscellaneous Header (J2)                           | 5-43 |

|-------------------------------------------------------------------|------|

| CHAPTER 6 Subassembly Reference                                   |      |

| •                                                                 | 6.1  |

| Chapter Overview                                                  |      |

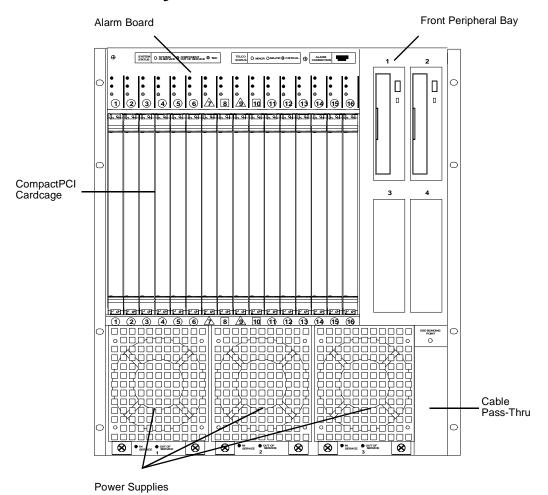

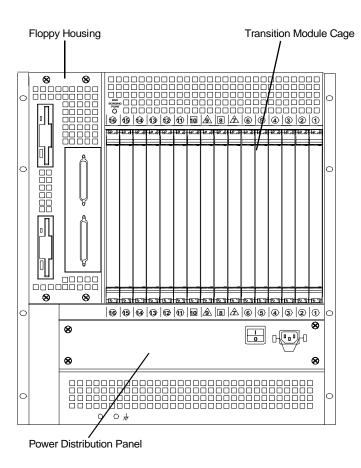

| Parts of the System                                               |      |

| CompactPCI Card Cage Reference                                    |      |

| Backplane Reference                                               |      |

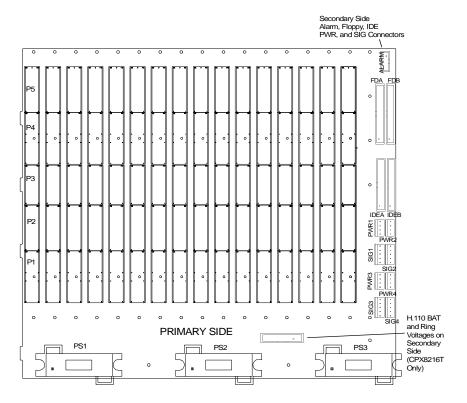

| Power Supply Connectors (PS1, PS2, PS3)                           |      |

| H.110 Power Connector (CPX8216T Only)                             |      |

| Alarm Interface Connector (ALARM)                                 |      |

| Floppy Drive Connectors (FDA, FDB)                                |      |

| IDE Drive Connectors (IDEA and IDEB)                              |      |

| Peripheral Power Connectors (PWR1, PWR2, PWR3, PWR4)              |      |

| Peripheral Signal Connectors (SIG1, SIG2, SIG3, SIG4)             |      |

| CompactPCI Connectors (P1, P2, P3, P4, P5)—CPX8216 Standard Backp |      |

| Primary (Front) Side I/O Connectors (Slots 1-6 and 11-16)         |      |

| Primary (Front) Side CPU Slot Connectors (7 and 9)                |      |

| Secondary (Rear) Side I/O Connectors                              | 6-26 |

| CPU Transition Module Connectors                                  |      |

| (Transition Slots 7 and 9)                                        |      |

| Hot Swap Controller/Bridge Connectors (Transition Slots 8 and 10) |      |

| H.110 Bus Connectors—CPX8216T System Only                         |      |

| Primary (Front) Side I/O Connectors                               |      |

| Primary (Front) Side (Slots 1-6 and 11-16)                        |      |

| Primary (Front) Side CPU Connectors                               |      |

| Primary (Front) Side HSC Connectors                               |      |

| Secondary (Rear) Side I/O Connectors                              |      |

| Secondary (Rear) Side CPU Transition Module Connectors            |      |

| Alarm Display Panel                                               |      |

| Alarm Display Panel Interface Connector (J4)                      |      |

| Remote Alarm Connector (J1)                                       |      |

| Power Distribution Panel                                          |      |

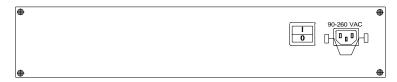

| AC Power Distribution Panel (CPX8216)                             |      |

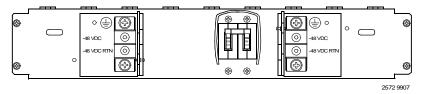

| Dual Input DC Power Distribution Panel (CPX8216)                  |      |

| Dual Breaker DC Power Distribution Panel (CPX8216)                |      |

| H.110 DC Power Distribution Panel (CPX8216T)                      |      |

| Power Supplies                                                    | 6-58 |

| APPENDIX A Specifications              |     |

|----------------------------------------|-----|

| Environmental Characteristics          |     |

| Power Supply Electrical Specifications | A-2 |

| Motorola Computer Group Documents      | B-1 |

| Related Specifications                 | B-2 |

| URLs                                   | B-4 |

## **List of Figures**

| Figure 1-1. CPX8216 Domains                                      | 1-2  |

|------------------------------------------------------------------|------|

| Figure 1-2. CPX8216 Standard System Layout                       | 1-3  |

| Figure 1-3. CPX8216T H.110 System Layout                         | 1-4  |

| Figure 1-4. CPX8216 I/O Bus Connectivity                         | 1-5  |

| Figure 1-5. The CPX8216T H.110 Bus                               | 1-14 |

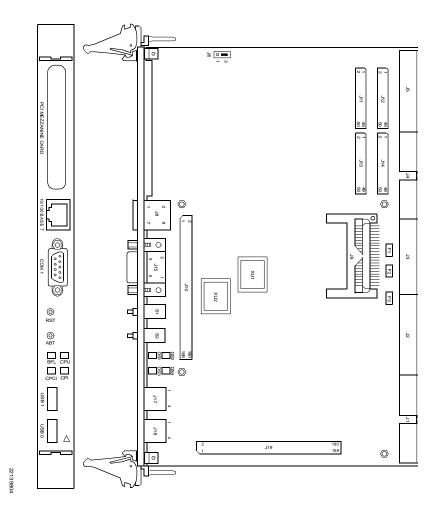

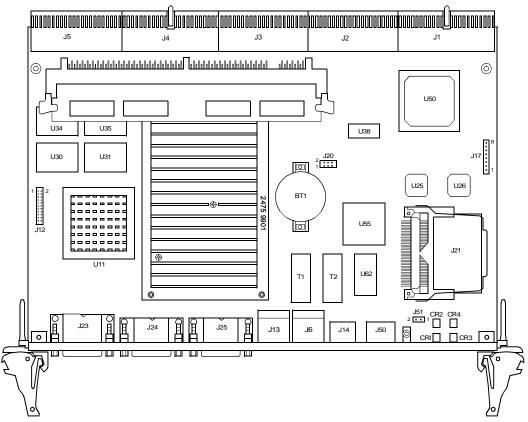

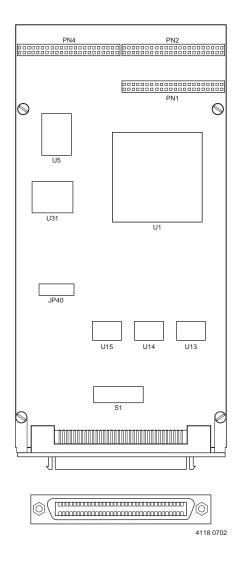

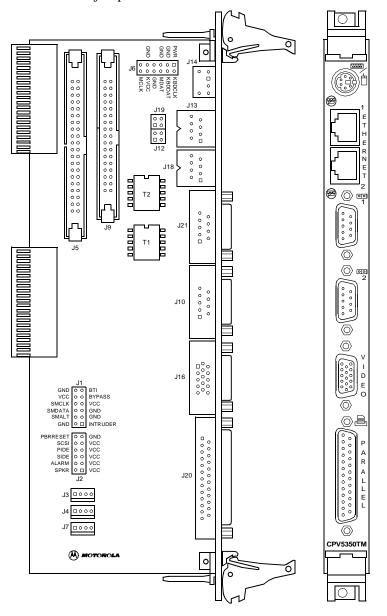

| Figure 2-1. CPV5350 Component Side View                          | 2-19 |

| Figure 2-2. Keyboard/Mouse Connector Diagram                     | 2-20 |

| Figure 3-1. PMC Modules to CPX8540 Carrier Card                  | 3-2  |

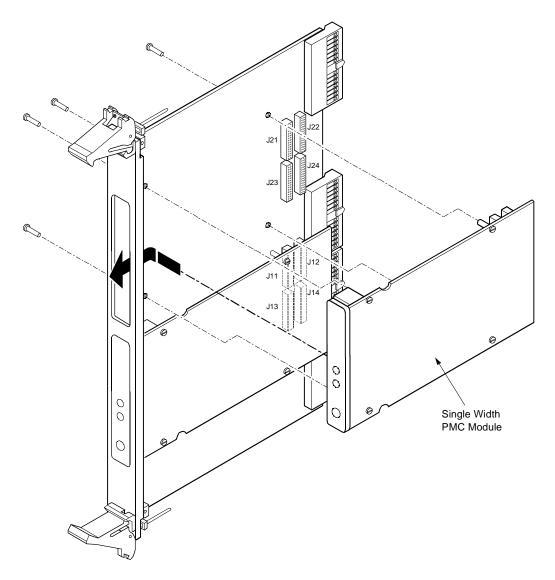

| Figure 3-2. Installing a PMC Module                              | 3-3  |

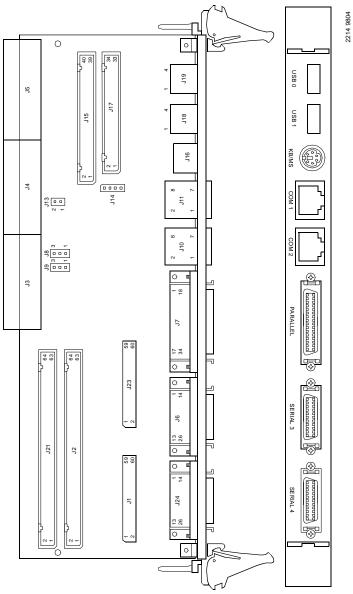

| Figure 5-1. CPX750HATM Transition Module                         |      |

| Figure 5-2. Serial Port Interface Jumper (J9) Settings           | 5-4  |

| Figure 5-3. DTE Port Configuration (COM1 and COM2)               | 5-19 |

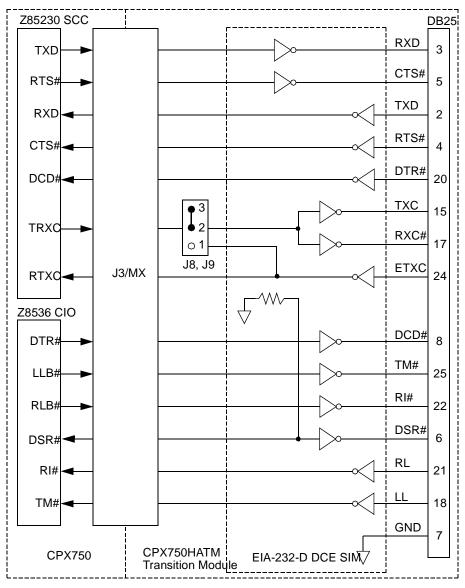

| Figure 5-4. EIA-232-D DCE Port Configuration (Ports 3 and 4)     | 5-21 |

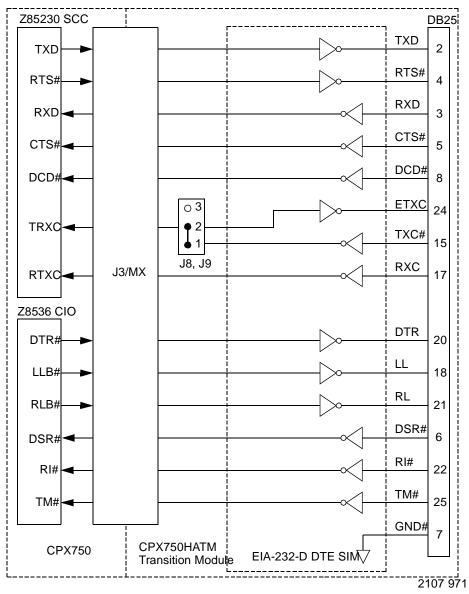

| Figure 5-5. EIA-232-D DTE Port Configuration (Ports 3 and 4)     | 5-22 |

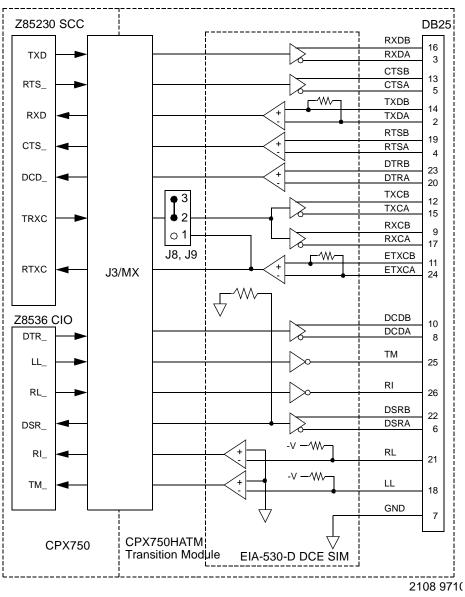

| Figure 5-6. EIA-530 DCE Port Configuration (Ports 3 and 4)       | 5-23 |

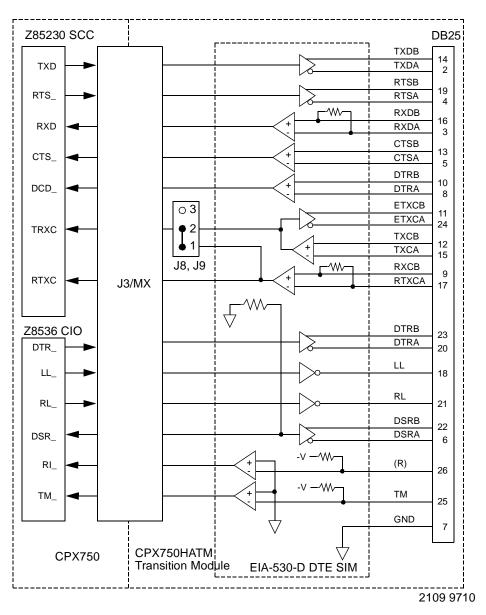

| Figure 5-7. EIA-530 DTE Port Configuration (Ports 3 and 4)       | 5-24 |

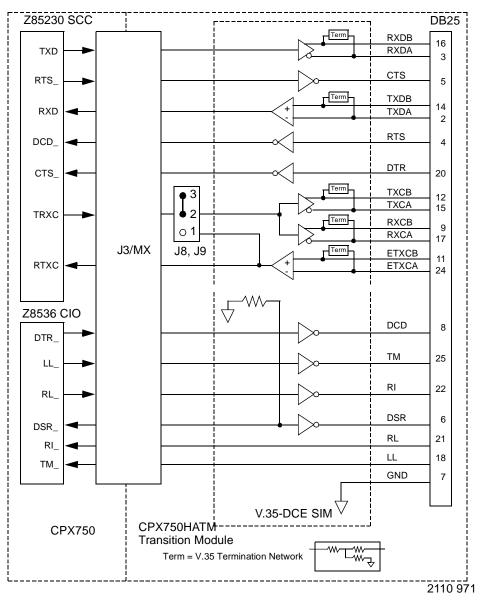

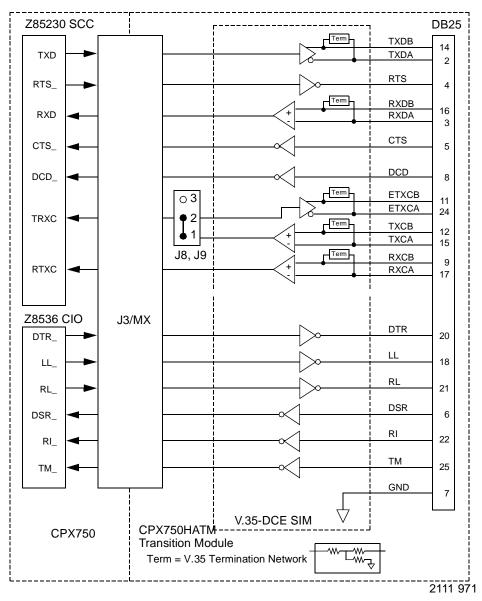

| Figure 5-8. V.35-DCE Port Configuration (Ports 3 and 4)          | 5-25 |

| Figure 5-9. V.35-DTE Port Configuration (Ports 3 and 4)          | 5-26 |

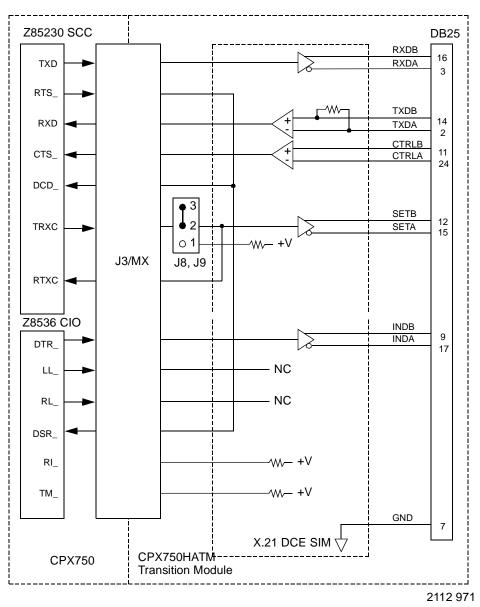

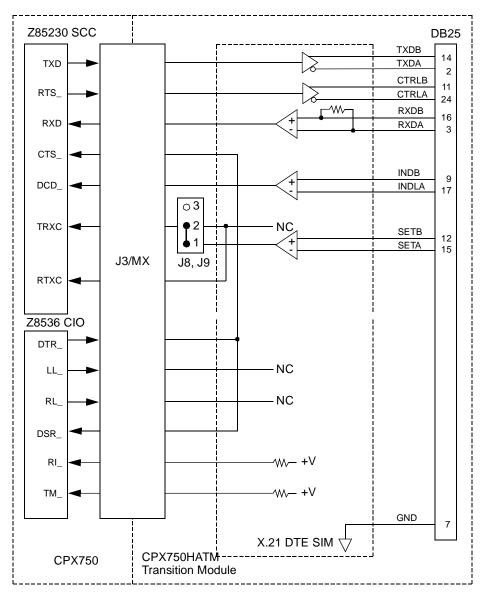

| Figure 5-10. X.21-DCE Port Configuration (Ports 3 and 4)         | 5-27 |

| Figure 5-11. X.21-DTE Port Configuration (Ports 3 and 4)         | 5-28 |

| Figure 5-12. Keyboard/Mouse Connector Diagram                    | 5-32 |

| Figure 6-1. CPX8216 Front View                                   |      |

| Figure 6-2. CPX8216 Rear View                                    | 6-3  |

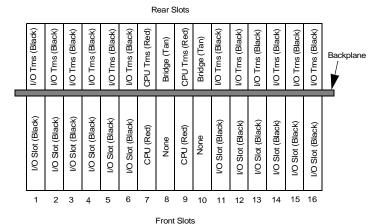

| Figure 6-3. Card Cage Rail Color Scheme—CPX8216 Standard System  | 6-4  |

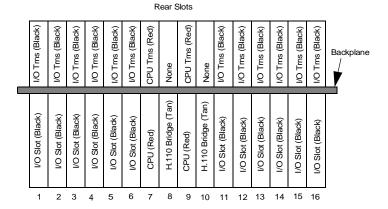

| Figure 6-4. Card Cage Rail Color Scheme—CPX8216T H.110 System    | 6-4  |

| Figure 6-5. CPX8216 and CPX8216T Backplane—Primary Side          | 6-5  |

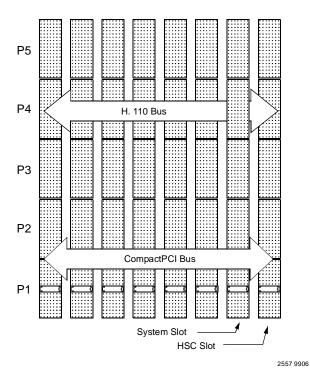

| Figure 6-6. The CPX8216T H.110 Bus                               | 6-37 |

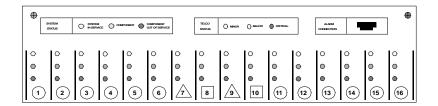

| Figure 6-7. Alarm Display Panel Block Diagram                    | 6-51 |

| Figure 6-8. Alarm Display Panel—Front View                       | 6-52 |

| Figure 6-9. AC Power Distribution Panel—Front View               | 6-54 |

| Figure 6-10. Dual Input DC Power Distribution Panel—Front View   | 6-55 |

| Figure 6-11. Dual Breaker DC Power Distribution Panel—Front View | 6-56 |

| Figure 6-12. H.110 DC Power Distribution Panel                   | 6-57 |

## **List of Tables**

| Table 2-1. CompactPCI Boards                                                     | 1 |

|----------------------------------------------------------------------------------|---|

| Table 2-2. USB 0 Connector J18                                                   | 4 |

| Table 2-3. USB 1 Connector J17                                                   | 4 |

| Table 2-4. 10BaseT/100BaseTx Connector J8                                        | 5 |

| Table 2-5. COM1 Connector J15                                                    | 5 |

| Table 2-6. Debug Connector (J19)2-                                               | 6 |

| Table 2-7. DRAM Mezzanine Connector (J10)                                        | 0 |

| Table 2-8. EIDE Compact FLASH Connector J9                                       | 4 |

| Table 2-9. CPV5350 Front Panel Connectors, Board Headers and Components $$ . 2-1 | 8 |

| Table 2-10. Keyboard/Mouse P/S2 Connector Pin Assignments (J50)2-2               |   |

| Table 2-11. Ethernet Connector Pin Assignments (J13 and J6)2-2                   | 1 |

| Table 2-12. USB Connector Pin Assignments (J14)                                  |   |

| Table 2-13. Serial Port Connector Pin Assignments (J24 and J25)2-2               | 2 |

| Table 2-14. Video Connector Pin Assignments (J23)                                | 2 |

| Table 3-1. CPCI J3 I/O Connector Pinout                                          | 4 |

| Table 3-2. CPCI J5 I/O Connector Pinout                                          | 4 |

| Table 3-3. PCI 32-bit Interface Connector P11/J11, P21/J21                       |   |

| Table 3-4. PCI 32-bit Interface Connector P12/J12, P22/J22                       | 7 |

| Table 3-5. PCI 64 bit PCI extension on PMC Connector J13, J23                    | 8 |

| Table 3-6. User-Defined I/O PCI Interface Connector P14/J14, P24/J24 3-          | 9 |

| Table 4-1. PMC Switch Settings                                                   |   |

| Table 4-2. PMC Pin Assignments                                                   | 4 |

| Table 5-1. System Components                                                     | 1 |

| Table 5-2. J3 User I/O Connector                                                 | 5 |

| Table 5-3. J5 User I/O Connector                                                 | 6 |

| Table 5-4. COM1 (J11) and COM2 (J10)                                             |   |

| Table 5-5. Serial Port 3 (J6)                                                    |   |

| Table 5-6. Serial Port 4 (J24)                                                   |   |

| Table 5-7. Parallel I/O Connector (J7)                                           |   |

| Table 5-8. Keyboard/Mouse Connector (J16)                                        |   |

| Table 5-9. EIDE Connector (J15)5-1                                               |   |

| Table 5-10. Floppy Connector (J17)                                               |   |

| Table 5-11. +5Vdc Power Connector (J14)                                          | 3 |

| Table 5-12. Speaker Output Connector (J13)                                       | 3 |

| Table 5-13. PMC I/O Connector (J2)                                  | 5-14 |

|---------------------------------------------------------------------|------|

| Table 5-14. PMC I/O Connector (J21)                                 | 5-15 |

| Table 5-15. Keyboard/Mouse P/S2 Connector Pin Assignments (J14)     | 5-32 |

| Table 5-16. Ethernet Connector Pin Assignments (J13 and J18)        | 5-33 |

| Table 5-17. Serial Port Connector Pin Assignments                   |      |

| (J21 and J10)                                                       | 5-33 |

| Table 5-18. Video Connector Pin Assignments (J16)                   | 5-34 |

| Table 5-19. Parallel Connector Pin Assignments (J20)                | 5-35 |

| Table 5-20. EIDE Header (J5) Pin Assignments                        | 5-36 |

| Table 5-21. Floppy Header (J9) Pin Assignments                      | 5-38 |

| Table 5-22. Keyboard/Mouse/Power LED Header (J6) Pin Assignments    | 5-40 |

| Table 5-23. USB Headers (J12 and J19) Pin Assignments               | 5-41 |

| Table 5-24. SM Bus and LM78 Header (J1)Pin Assignments              | 5-42 |

| Table 5-25. Fan Tachometer Header (J3 and J4) Pin Assignments       | 5-43 |

| Table 5-26. Indicator LED/Miscellaneous Header (J2) Pin Assignments | 5-43 |

| Table 6-1. System Components                                        | 6-1  |

| Table 6-2. PS1, PS2, and PS3 Pin Assignments                        | 6-6  |

| Table 6-3. Fan Module Pin Assignments                               | 6-7  |

| Table 6-4. H.110 Power Connector                                    | 6-7  |

| Table 6-5. ALARM Connector Pin Assignments                          | 6-8  |

| Table 6-6. FDA and FDB Pin Assignments                              | 6-8  |

| Table 6-7. IDEA and IDEB Pin Assignments                            | 6-9  |

| Table 6-8. PWR1, PWR2, PWR3, PWR4 Pin Assignments                   | 6-10 |

| Table 6-9. SIG1, SIG2, SIG3, SIG4 Pin Assignments                   | 6-11 |

| Table 6-10. P5 Connector, I/O Slots 1-6 and 11-16                   |      |

| (User I/O)                                                          |      |

| Table 6-11. P4 Connector, I/O Slots 1-6 and 11-16 (User I/O)        |      |

| Table 6-12. P3 Connector, I/O Slots 1-6 and 11-16 (User I/O)        | 6-12 |

| Table 6-13. P2 Connector, I/O Slots 1-6 and 11-16 (CPCI Bus)        |      |

| Table 6-14. P1 Connector, I/O Slots 1-6 and 11-16 (CPCI Bus)        |      |

| Table 6-15. P5 Connector, CPU Slots 7 and 9                         | 6-17 |

| Table 6-16. P4 Connector, CPU Slots 7 and 9                         |      |

| Table 6-17. P3 Connector, CPU Slots 7 and 9                         |      |

| Table 6-18. P2 Connector, CPU Slot 7 (Domain A)                     |      |

| Table 6-19. P2 Connector, CPU Slot 9 (Domain B)                     | 6-22 |

| Table 6-20. P1 Connector, CPU Slots 7 and 9                         |      |

| Table 6-21. P5 Connector, I/O Slots 1-6 and 11-16 (User I/O)        |      |

| Table 6-22. P4 Connector, I/O Slots 1-6 and 11-16 (User I/O)        |      |

| Table 6-23. P3 Connector, I/O Slots 1-6 and 11-16 (User I/O)        | 6-26 |

| Table 6-24.  | P5 Connector, CPU Transition Module Slots        | 6-27 |

|--------------|--------------------------------------------------|------|

| Table 6-25.  | P3 Connector, CPU Transition Slots 7 and 9       | 6-28 |

| Table 6-26.  | P5 Connector, HSC/Bridge (Slots 8 and 10)        | 6-29 |

| Table 6-27.  | P4 Connector, HSC/Bridge (Slots 8 and 10)        | 6-29 |

| Table 6-28.  | P3 Connector, HSC Slots 8 and 10                 | 6-31 |

| Table 6-29.  | P2 Connector, HSC Slot 10                        | 6-32 |

| Table 6-30.  | P2 Connector, HSC Slot 8                         | 6-34 |

| Table 6-31.  | P1 Connector, HSC Slots 8 and 10                 | 6-35 |

| Table 6-32.  | P4 Connector, I/O Slots 1-6, 11-16               | 6-38 |

| Table 6-33.  | P5 Connector, HSC/Bridge (Slots 8 and 10)        | 6-40 |

| Table 6-34.  | P4 Connector, HSC Slots 8 and 10                 | 6-42 |

| Table 6-35.  | P3 Connector, HSC Slots 8 and 10                 | 6-44 |

| Table 6-36.  | P2 Connector, HSC Slot 10                        | 6-45 |

| Table 6-37.  | P2 Connector, HSC Slot 8                         | 6-47 |

| Table 6-38.  | P1 Connector, HSC Slots 8 and 10                 | 6-48 |

| Table 6-39.  | P5 Connector, I/O Slots 1-6 and 11-16 (User I/O) | 6-50 |

| Table 6-40.  | P3 Connector, I/O Slots 1-6 and 11-16 (User I/O) | 6-50 |

| Table 6-41.  | Alarm LED Color and Description                  | 6-52 |

| Table 6-42.  | Alarm Display Panel Interface Connector (J4)     | 6-53 |

| Table 6-43.  | Remote Alarm Connector (J1)                      | 6-53 |

| Table 6-44.  | DC Analog Voltages for H.110 Bus                 | 6-57 |

| Table A-1.   | Total Regulation (per Output)                    | .A-3 |

| Table B-1. I | Related Specifications                           | .B-2 |

## **About this Manual**

This manual is directed at the person who needs detailed configuration and specification information for CompactPCI modules and system subassemblies of the CPX8000 series computer system. Included is an overview of the system architecture for the CPX8216 and CPX81216T systems. It also presents the correct strapping and pin-out information for the modules and subassemblies covered.

This manual does not provide installation, removal, or use procedures. People requiring this type of information should refer to the *CompactPCI CPX8216 and CPX8216T System Installation and Use* manual as listed in Appendix B, *Related Documentation*.

## **Summary of Changes**

This manual has been revised and replaced any previous editions. Below is a history of the changes affecting this manual.

| Date       | Change                                                                                                                                                     |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| July 2002  | Updated PMC Module chapter, see Chapter 4, PMC Modules.                                                                                                    |  |

|            | Load sharing information added, see <i>The Active/Active or Load-Sharing Configuration</i> on page 1-9                                                     |  |

|            | Domain ownership further defined, see Chapter 1, System Architecture                                                                                       |  |

|            | Dual breaker DC power distribution panel information added (with Smart cable), see <i>Dual Breaker DC Power Distribution Panel (CPX8216)</i> on page 6-55. |  |

| April 2002 | Section describing system domains and domain ownership information added, see <i>System Domains</i> on page 1-1.                                           |  |

|            | Section describing hot swap controllers added, see <i>Hot Swap Controller</i> on page 1-6.                                                                 |  |

| Date          | Change                                                                                                             |

|---------------|--------------------------------------------------------------------------------------------------------------------|

|               | Power distribution information added, see <i>Power Distribution Panel</i> on page 6-54.                            |

| August 2001   | Details about assigning chassis IDs on the CPX8216T system added. See <i>Chassis ID for CPX8216T</i> on page 1-13. |

|               | Updated model numbers, see <i>Systems Supported</i> in this section.                                               |

| April 2001    | Added cautions regarding hot swap software and hot swappable drives.                                               |

| July 2000     | Updated pin assignment tables for connector P2 (HSC and CPU slots.)                                                |

| March 2000    | DC Input voltage changed to -36Vdc to -72Vdc. Changed URLs to reflect new Web sites.                               |

| November 1999 | Added System Architecture chapter. Added TNV branch circuit safety standards information. Added the Index.         |

| August 1999   | Added information for the CPV5350 Intel CPU                                                                        |

|               | Added information for the H.110 Backplane and Power Distribution Panel for the CPX8216T system                     |

| May 1999      | Replaced Figure 2-1 with corrected board illustration                                                              |

| January 1999  | Original Document                                                                                                  |

## **Systems Supported**

This information in this manual applies to the modules and subassemblies supported by the following systems:

| Model Number | Description                                              |

|--------------|----------------------------------------------------------|

| CPX8216SK24  | CPX8216 Dual SCSI 466 MHz PowerPC Starter Kit, 256MB     |

| CPX8216TSK24 | CPX8216T Dual EIDE 700 MHz Pentium Starter Kit, 512MB    |

| CPX8216SK25  | CPX8216 Dual EIDE 700 MHz Pentium Starter Kit, 512MB     |

| CPX8216TSK25 | CPX8216T Dual EIDE 466 MHz PowerPC Starter<br>Kit, 256MB |

### **Overview**

This manual is divided into the following topics:

- □ Chapter 1, System Architecture

- ☐ Chapter 2, CPU Modules

- ☐ Chapter 3, *CPX8540 Carrier Card*

- ☐ Chapter 4, PMC Modules

- ☐ Chapter 5, *Transition/Bridge Modules*

- ☐ Chapter 6, Subassembly Reference

- ☐ Appendix A, *Specifications*

- ☐ Appendix B, *Related Documentation*

## **Comments and Suggestions**

Motorola welcomes and appreciates your comments on its documentation. We want to know what you think about our manuals and how we can make them better. Mail comments to:

Motorola Computer Group Reader Comments DW164 2900 S. Diablo Way Tempe, Arizona 85282

You can also submit comments to the following e-mail address: reader-comments@mcg.mot.com

In all your correspondence, please list your name, position, and company. Be sure to include the title and part number of the manual and tell how you used it. Then tell us your feelings about its strengths and weaknesses and any recommendations for improvements.

## **Conventions Used in This Manual**

The following typographical conventions are used in this document:

#### bold

is used for user input that you type just as it appears; it is also used for commands, options and arguments to commands, and names of programs, directories and files.

#### italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples, and to introduce new terms.

#### courier

is used for system output (for example, screen displays, reports), examples, and system prompts.

#### <Enter>, <Return> or <CR>

represents the carriage return or Enter key.

#### Ctrl

represents the Control key. Execute control characters by pressing the **Ctrl** key and the letter simultaneously, for example, **Ctrl-d**.

## **PICMG Compliance**

The CPX8216 system is designed to be fully compliant with the CompactPCI Hot Swap Specification developed by the PCI Industrial Computers Manufacturing Group (PICMG). With the proper software support and testing, it should be possible to integrate all proprietary and third-party I/O modules which are compatible with this specification. Further, the system allows the use of I/O modules which are not hot swappable, but the system must be powered off when such modules are inserted and extracted.

The CPX8216 also features the ability to hot swap system and nonsystem processor boards, a feature which is beyond the scope of the PICMG specification. As part of its commitment to open standards, Motorola will propose that the processor hot swap capabilities of the CPX8216 be added to the Hot Swap Specification. At this point, however, there are no third-party CPU modules which are compatible with the CPX8216 system.

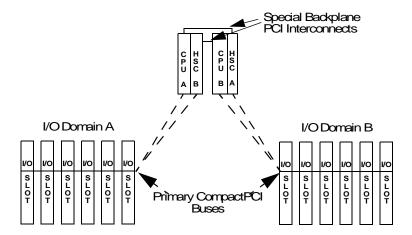

## **System Domains**

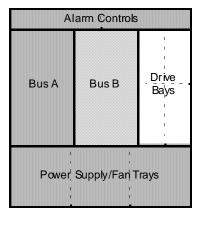

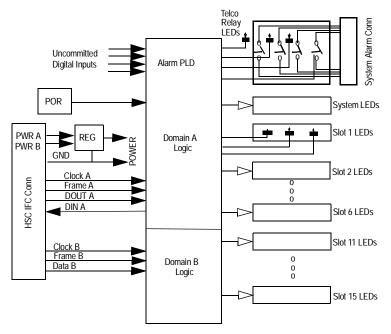

The high availability and high slot count of the CPX8216 systems is made possible by implementing two host CPU slots and multiple CompactPCI bus segments in a single chassis. These bus segments, along with other system resources are grouped into two logical domains, A and B, which can be controlled by either host-HSC pair regardless of the bus segment the host sits on. Domain A includes CompactPCI bus segment A (slots 1 to 8), the power supply/fan tray modules and alarm controls. In the CPX8216, domain B consists of the CompactPCI bus segment B (slots 9 to 16). For further information on domain control or ownership, see the section, *Hot Swap Controller* on page 1-6.

1-1

Figure 1-1. CPX8216 Domains

## System Layout

The CPX8216 is a 16-slot, high-availability CompactPCI system with two separate 6-slot CompactPCI I/O domains and the capability to contain redundant CPU modules and redundant Hot-Swap Controller (HSC) modules. It is also possible to configure the system as a simplex, high I/O system containing a single CPU-HSC pair. Even as a simplex system, the CPX8216 still provides improved availability through redundant power supplies and the control/monitoring capabilities of the HSC, as described in *The Hot Swap Controller/Bridge (HSC) Module* on page 1-5.

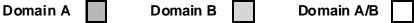

### **CPX8216**

The CPX8216 standard system consists of two 8-slot subsystems, or domains, each with two slots for the host processor and six slots for nonhost CompactPCI boards. The HSC board mounts in the rear of the chassis, behind the secondary CPU slot. Figure 1-2 on page 1-3 provides a diagram of this configuration.

2450 9812

### Figure 1-2. CPX8216 Standard System Layout

Each of the two independent I/O domains has its own system processor slot. Each system processor has direct access to its local bus through an onboard PCI-to-PCI (P2P) bridge. Each domain is also capable of supporting a Hot Swap Controller (HSC) module that contains its own P2P bridge. Thus, in a fully redundant configuration, there are two bridges that have access to each of the I/O buses—one associated with the CPU and one with the HSC. Only one of the bridges may be active at a time, however.

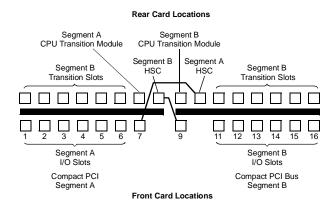

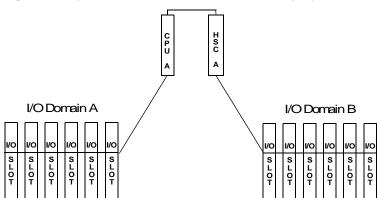

## CPX8216T (H.110)

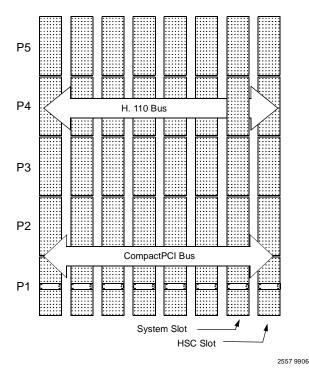

The CPX8216T H.110 system consists of two 8-slot subsystems, or domains, each with one slot for the host processor, one slot for the front-loaded HSC, and six slots for nonhost CompactPCI boards. Figure 1-3 on page 1-4 provides a diagram of this configuration.

Figure 1-3. CPX8216T H.110 System Layout

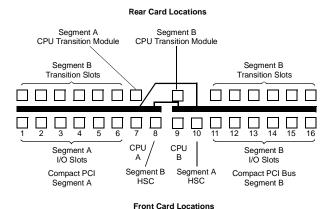

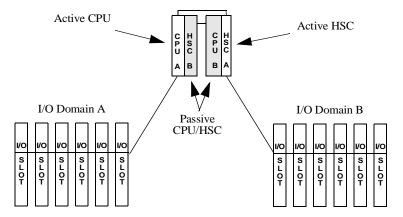

## **Bus Access and Control**

In the fully redundant configuration, the CPU in the left system slot, CPU A, is associated with the HSC in the right HSC slot, HSC A (note that HSC A actually sits on the Domain B bus). There is a local connection between each CPU-HSC pair that allows the CPU in one domain to control the other domain through its HSC. This architecture is illustrated in the following figure.

Figure 1-4. CPX8216 I/O Bus Connectivity

In addition to providing bridges to the remote I/O buses, the HSC provides the services necessary to hot swap CPU boards and nonhost processor boards and also controls the system alarm panel, fans, and power supplies.

## The Hot Swap Controller/Bridge (HSC) Module

The HSC module connects to the CPU module through a local PCI bus, as illustrated in Figure 1-2 and Figure 1-3. The HSC module contains a PCI-to-PCI bridge and also contains a Hot Swap Controller.

The functionality provided by the HSC is at the heart of the High Availability CPX8216 System. Its primary functions include:

- ☐ Providing a bridge between the two eight-slot CompactPCI buses so that they can be managed by a single CPU module

- ☐ Maintaining a Control Status Register which contains information on the status of each system module

- ☐ Controlling power and resets to each system module through radial connections

- Monitoring and controlling CPU boards, nonhost boards, and peripherals, including power and fan sleds, board and system LEDs, and alarms

## **Hot Swap Controller**

Each of the nonhost slots in the system can be controlled from either HSC. When an HSC has control over a domain it has control over the nonhost boards in that domain. Each host processor/bridge pair is controlled as a single item by the other processor/bridge pair. The bridge and the host processor are linked together so that both must be present for power to be applied. A host processor cannot be operated without its HSC.

With the CPX8216 architecture it is important that the system initializes to a state that allows the host processors and HSCs to be in control of the system. The default conditions are:

- ☐ System processors and bridges are powered up (if present)

- ☐ System processors and bridges are disconnected from their busses

- ☐ HSCs are not in control of either domain

- ☐ Nonhost boards are powered off

- ☐ Peripheral bays are powered up (if present)

- ☐ Fans and power supplies are powered on

#### Note

System components such as fans and power supplies may be controlled by either HSC but not both. Default control belongs to Domain A and whichever HSC has control of Domain A has control of the system functions.

If Domain A is not controlled, nonhost boards are powered-off and all LED updates to the display panel and power supplies are suspended. Also, monitoring of alarm inputs from the display panel and power supplies are inhibited. Subsequent to the default, the system software must determine the configuration of the system and then proceed to change it.

## **System Processor Configurations**

The CPX8216 is a flexible system that allows for multiple configurations of processor control, I/O redundancy, and peripheral configurations. The following sections briefly touch on possible configurations.

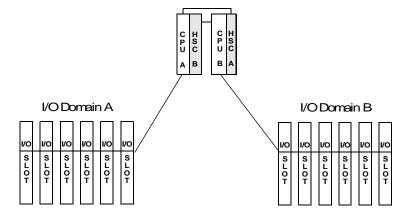

As noted above, there are three possible processor/control configurations:

- A simplex system containing a single CPU-HSC pair controlling both I/O domains

An active/passive configuration similar to the simplex configuration, but providing a warm backup for both the CPU and the HSC

An active/active or load-sharing configuration in which each CPU runs a single domain while also serving as a backup to the other CPU.

- **Note** H.110 traffic and HA Linux do not support a load-sharing configuration.

The following sections give a general description of these configurations.

## The Simplex Configuration

Because of the flexible nature of the CPX8216, it is possible to configure it with different levels of redundancy and availability. For applications which do not require the benefits of full high availability, it is possible to configure the CPX8216 as a simplex, 16-slot system. This configuration provides the benefits of redundant power supplies and the system monitoring capabilities of the fully redundant configuration.

The simplex configuration is illustrated in the following figure.

## The Active/Passive Configuration

In the active/passive configuration, one CPU manages all twelve I/O slots, much like in the simplex configuration. In addition, the second CPU serves as a warm standby, ready to run the system in the event of a failure on the active system.

The active/passive configuration is illustrated in the following figure.

## The Active/Active or Load-Sharing Configuration

In the load sharing configuration, each CPU manages six of the twelve I/O slots, much like a dual 8-slot system with the added benefit of one CPU being able to control all twelve I/O slots if the other CPU fails. It is important in a load-sharing configuration to note that the total critical activity does not exceed the capabilities of a single CPU, because either one of the CPUs must be ready to take over the load carried by the other.

The active/active configuration is illustrated in the following figure.

**Note** H.110 traffic and HA Linux do not support a load-sharing configuration.

## I/O Configurations

The CPX8216 contains two independent 8-slot CompactPCI buses. One slot in each bus is dedicated to a system processor, and another is needed for the HSC. This leaves six slots on each bus to support I/O devices or nonsystem processors.

One possible configuration is to use the CPX8216 as a high I/O CompactPCI system with redundant CPUs. With this configuration, it is possible to run twelve independent I/O modules within a CPX8216 system. Applications requiring dense processing power could use all twelve I/O slots to support nonsystem processors.

Such a system would be protected against a CPU or HSC fault, but it would be vulnerable to data losses if any of the I/O modules or nonsystem processor modules were to fail. In systems handling critical data, it is possible to implement a 2N or an N+1 I/O redundancy strategy that allows the level of service to be continued in the event that a module fails.

In the case of a 2N-redundant system, each I/O module or nonsystem processor module is matched with an identical module on the other bus. The paired modules can be configured in an active/passive arrangement or a load-sharing arrangement in which each carries half of the load of a single module. In an N+1 arrangement, multiple modules are backed up by a single spare. For example, a single passive nonsystem processor module can be used to back up five others.

## **Peripherals**

### **Power/Fan Modules**

The CPX8216 system requires a minimum of two power/fan sled modules and a fan-only sled module to provide adequate power and cooling for a fully loaded, nonredundant system. The system can contain a third power supply/fan sled as part of an N+1 strategy, meaning that the system can continue providing service if one of the modules fails. These modules are hot swappable and available for DC and AC environments.

The fans run at either high speed (default) or temperature controlled, which can be changed using the operating system software via the API.

#### **Drive Modules**

The CPX8216 contains four hot-swappable peripheral bays, all of which support both SCSI and EIDE protocols.

The hot swapping of hard drives is supported when your system is configured with the appropriate software support for hot swap and when the drives are in a hot-swap drive carrier.

SCSI devices can be configured to be fully hot-swappable, and data can be hot switched between two independent SCSI controllers. EIDE devices are assigned to a single EIDE controller. They can be warm swapped, meaning that a failed device can be replaced once the controller has been powered off.

The rear of the CPX8216 chassis may be configured with either single or double, fixed, floppy drives. Floppy drives are not hot-swappable.

For more information on installing both hot-swappable and non-hot-swappable drives, refer to the *Drive Removal and Installation* chapter of the *CPX8216 and CPX8216T CompactPCI System Installation and Use* manual.

## **CPU Complex Architecture**

The CPU complex in the CPX8216 contains two CPU modules and their corresponding Hot Swap Controller (HSC) modules. The figure below illustrates the architecture, including elements on the boards as well as local connections between the CPU modules and the PCI-to-PCI (P2P) connections to the local CompactPCI buses.

#### RAM RAM Proc Proc **HSC** HSC **Enet Enet** ISA P2P P2P P2P P2P ISA Serial Serial Link Link IDE **IDE** CompactPCI Bus CompactPCI Bus

Local Connections between CPU Modules

### The CPU Module

In addition to the processor, RAM, etc., each CPU module contains one:

- ☐ Up to two Ethernet controllers

- ☐ Up to two serial communications links

- ☐ P2P bridge to the local CompactPCI bus

- Local PCI Bus connection to the HSC

## **Switching Service to the Passive CPU**

The switchover from one CPU to another is initiated by the passive CPU when there is an indication that there is something wrong with the active CPU--such as a failed heartbeat protocol. The passive side notifies the active side that it is about to begin a switchover process. If the active side agrees to the switchover, then the two sides coordinate the hand-off and no bus signals, clocks, or devices should be corrupted. If the active system fails to cooperate with the takeover attempt, then we must assume that bus signals, clocks, and devices attached to the bus may be corrupted.

In a more extreme takeover, it is possible for the passive CPU to power-on reset the active CPU and to take control that way.

## Chassis ID for CPX8216T

A unique 5-bit chassis ID can be assigned for each CPX8216T system. Hex values are on the rotary switches located on the HSC boards. A jumper can be added to J14 to double the number of unique identifiers. This feature should be used if more than 15 chassis are deployed in one location. The HSC boards are shipped with no jumper as the default. For guidelines on setting the chassis ID on your CPX8216T system, refer to the CPX8000 Series CPX8216 and CPX8216T CompactPCI System Installation and Use manual.

## **Alarms and LEDs**

In order to provide a uniform appearance, without depending on individual board manufacturers, the CPX8216 contains a separate alarm display panel, which runs across the top of the chassis. In addition to In Service/Out of Service LED indicators for all sixteen slots, the alarm display panel contains LEDs for system status (System in Service/Component out of Service/System out of Service) and for the three standard Telco levels (Critical/Major/Minor). The three Telco alarms are also signalled through a dry contact relay.

## **H.110 Telephony Bus**

The CPX8216T supports an H.110 Computer Telephony Bus. The H.110 bus uses P4/J4 as defined in the PICMG specification for CompactPCI.

**Figure 1-5. The CPX8216T H.110 Bus**

## **Board Insertion and Extraction Features**

The PICMG specification details software and hardware features, in order to support hot swapping of I/O boards. Hardware features include:

- ☐ Staged pins that control voltages when inserting or extracting boards

- □ BD\_SEL#, HEALTHY#, and ENUM# signals

- ☐ Hot swap control status register

## **Staged Pins**

The PICMG CompactPCI hot swap specification provides for three separate pin lengths in order to control the insertion and extraction voltages and to notify the system when boards are inserted or extracted.

The longest pins, which include VCC pins and GND pins, are the first to mate during the insertion process and the last to break contact during extraction. These pins are used to supply power to pre-charge the PCI interface signals to a neutral state before they contact the bus. This pre-charging serves to minimize the capacitive effects of the board as it makes or breaks contact with the bus.

The medium-length pins carry PCI and other signal traffic.

The shortest pins are used to assert signals, including BD\_SEL#. During insertion, the BD\_SEL# signal enables the board to attach to the local PCI bus. On extraction, it causes the board to logically and electrically disconnect from the PCI bus before the bus pins physically break contact with the bus.

### BD\_SEL#

BD\_SEL# is asserted by one of the pins that mate last on insertion and break first on extraction. On insertion, the signal tells the board to connect to the PCI bus. On extraction this pin breaks first, causing the board to logically and electrically disconnect from the PCI bus before the PCI bus pins physically break contact with the bus.

### ENUM#

An ENUM interrupt is generated when a board is hot inserted into the CPX8216 chassis, or when an operator trips the board microswitch by raising its ejector handles. The signal informs the active CPU that the status of a board has changed. The CPU then identifies the board by polling the INSert and EXTract bits in all of the boards' Control Status Registers.

## **Hot Swap Control Status Register (CSR)**

The CPX8216 supports hot swap CompactPCI cards with the standard control status register defined by the PICMG Hot Swap Specification. The register is visible in PCI configuration space and provides hot swap control and status bits: INS and EXT. The INS signal is set when ENUM# is asserted by a board being inserted into the system. The EXT signal is asserted when ENUM# is asserted by an operator triggering the microswitch in the board handles. The host also uses these bits to acknowledge and de-assert ENUM#.

## The Hot Swap Process

PICMG divided the complete hot swap process into physical, hardware and software connection processes. These processes are formally broken down further into a group of transitional states, which are illustrated in the following figure.

| PHYSICAL<br>CONNECTION<br>STATES |          |   | WARE<br>ON STATES |          | SOFTWAR<br>CONNECTION STATES |    |                 |

|----------------------------------|----------|---|-------------------|----------|------------------------------|----|-----------------|

| O<br>P0 —                        | — Р<br>Н |   | )<br>)<br>        | <b>)</b> | 0                            | 0  | 0               |

|                                  |          | H | H1F 5             | 30 ———   | S1 ———                       | S2 | · \$3<br>- \$30 |

When inserting a board, it goes through all states from P0 to S3. Conversely, a board transitions from S3 to P0 before being extracted. During normal operation, no states are skipped. Extracting a board in a software connection state other than S0 is likely to disrupt software enough to crash the system, but the CompactPCI bus, from a purely electrical point of view, will not be disrupted enough to cause logic levels to be violated.

Certain states are overlapping. For example, when the board is fully seated (completed P1), but has not yet started the hardware connection process

(H0), it said to be in the P1/H0 state. Similarly, one can speak of a board being in the H2/S0 state.

### **Physical Connection Process**

The physical connection process is the basic process of putting a board into a live system, or physically removing the board. The process includes two states:

| P0 - The | board is | physically | separate fi | rom the system |

|----------|----------|------------|-------------|----------------|

|          |          | P J J      | ~ -         |                |

☐ P1 - The board is fully seated, but not powered, and not active on the PCI bus. All pins are connected.

#### **Hardware Connection Process**

The hardware connection process involves the electrical connection or disconnection of the board. This process includes three states:

- ☐ H0 The board is not active on the PCI bus. This state is equivalent to P1 above.

- ☐ H1 The board has powered up and is sufficiently initialized to connect to the PCI bus.

- ☐ H2 The board is powered, and enabled for access by a PCI bus transaction (normally by the host) in PCI configuration space only. The board configuration space is not yet initialized.

When a newly inserted board has completed H2, the board is operable from a hardware perspective. It has run its power up diagnostics, initialized itself, loaded EEPROM data, etc. The blue LED is off in the H2 state, indicating that the board should not be pulled out.

#### **Software Connection Process**

The software connection process includes the tasks needed to configure and load software. This process contains four states:

- □ S0 The Software Connection Process has not been initiated. The board's configuration space registers are accessible but not yet initialized.

- □ S1 The board is configured by the system. The system has initialized the board's PCI configuration space registers with I/O space, memory space, interrupts and PCI bus numbers. The board is ready to be accessed by a device driver, but no drivers are loaded at this time.

- ☐ S2 The necessary supporting software (drivers, etc.) have been loaded. The board is ready for use by the OS and/or the application, but no operations involving the board are active or pending.

- □ S3 The board is active. Software operations are either active or pending.

#### **Software Disconnection Process**

The software disconnection process defines two additional states which are used when quiescing activity on a board in preparation for extraction:

- □ S3Q The software is completing current operations, but is not allowed to start new ones. When current operations are completed, the board transitions to S2.

- □ S2Q The board is quiesced. This is the same state as S2, except that no new operations are allowed to be initiated.

The Software Disconnection Process proceeds as S3, S3Q, S2Q, S1, and finally S0.

### **Typical Insertion and Extraction Processes**

Many of the steps in the insertion and extraction processes are automated by software. After the operator installs a board, it automatically advances to P1. The hardware connection process proceeds automatically and asserts the ENUM# signal to initiate the software connection process. The host responds to the bussed ENUM# signal by reading the Hot Swap Control Status Register of each board to find out which one is signaling an insertion or extraction (INS or EXT bit asserted). Upon detecting an insertion, the Host responds by adding software drivers to support the newly inserted board.

Extraction is initiated when the operator opens the board ejector handle, which activates a mechanical switch to assert ENUM#. The hot plug system driver senses ENUM# and notifies software that board activity must be quiesced and that software device drivers should be unloaded. The application that is using the board is informed that the resource is no longer available. When the board is ready for extraction, software informs the operator by illuminating the blue LED. After extraction, all system resources previously assigned to that board are made available for other uses.

## **Device Drivers**

In order to take full advantage of the high availability functions of the CPX8216, and to support hot swap, board device drivers need to be enhanced. Drivers need to cease all activity when the device is about to be hot swapped, and they need to support initialization of the device without support from the device firmware or BIOS.

Further, high availability device drivers need to be able to enter a standby mode while bus control is being passed from one CPU to another. They also provide diagnostic interfaces for run time fault detection and for preinitialization testing of newly inserted boards.

### **Overview**

This chapter provides reference information for the CompactPCI system controller/host CPU modules supported in the CPX8216 system.

The correct jumper setting and pin-out information is provided for each module.

**Note**

The CPX750HA is sometimes identified as an MCP750HA in some chassis and firmware documentation, for packaging and ordering purposes, but both numbers apply to the same board.

Your system may not contain all boards listed in this chapter, or it may contain third-party boards that are not listed in this chapter. For information about third-party boards, refer to the board manufacturer's documentation.

This chapter contains information for the following CompactPCI boards:

| Part No. | Description               | Slots<br>Occupied | Page |

|----------|---------------------------|-------------------|------|

| СРХ750НА | PowerPC Hot Swappable CPU | 1                 | 2-1  |

| CPV5350  | Intel Hot Swappable CPU   | 1                 | 2-16 |

Table 2-1. CompactPCI Boards

### CPX750HA

The CPX750HA is a single-slot, single-board computer equipped with a PowerPC<sup>TM</sup> 750 Series microprocessor. The processor implements a backside cache controller and the board comes with 1MB of cache memory.

The CPX750HA offers many standard features desirable in a CompactPCI computer system, such as:

|         | PCI Bridge and Interrupt Controller                           |

|---------|---------------------------------------------------------------|

|         | ECC Memory Controller chipset                                 |

|         | 5MB to 9MB of linear FLASH memory                             |

|         | IDE CompactFlash memory                                       |

|         | 16MB to 256MB of ECC-protected DRAM                           |

|         | Interface to a CompactPCI bus                                 |

|         | Several I/O peripherals                                       |

| The I/C | peripheral interfaces present on the onboard PCI bus include: |

|         | One 10/100-BASE-T Ethernet interface                          |

|         | One USB host controller                                       |

|         | One SA master/slave interface                                 |

|         | One Fast EIDE interface                                       |

|         | One PMC Slot                                                  |

Functions provided from the ISA bus are two asynchronous and two synchronous/asynchronous serial ports, keyboard, mouse, a floppy disk controller, printer port, a real time clock, and NVRAM.

The CPX750HA interfaces to a CompactPCI bus using a DEC 21154 PCI-to-PCI bridge device. This device provides a 64-bit primary and a 64-bit secondary interface allowing full 64-bit data access between CompactPCI bus devices and the host/PCI bridge. This bus is capable of driving seven CompactPCI slots.

Another key feature of the CPX750HA is the PCI (Peripheral Component Interconnect) bus. In addition to the onboard local bus peripherals, the PCI bus supports an industry-standard mezzanine interface, IEEE P1386.1 PMC (PCI Mezzanine Card). PMC modules offer a variety of possibilities for I/O expansion.

The base board supports PMC I/O for the front panel or through backplane connector J3 to a CPX750HATM transition module.

### **Connectors and Jumper Settings**

The next sections provide pinout information and jumper settings for the CPX750HA board. Additional pinout assignments can be found in Chapters 3 through 6.

#### Backplane Connectors (P5, P4, P3, P2, P1)

Refer to the backplane reference section for the backplane connector pin assignments.

#### Front USB Connectors (J17 and J18)

Two USB Series A receptacles are located at the front panel of the CPX750HA board. The pin assignments for these connectors are as follows:

Table 2-2. USB 0 Connector J18

| 1 | UVCC0   |

|---|---------|

| 2 | UDATA0N |

| 3 | UDATA0P |

| 4 | GND     |

Table 2-3. USB 1 Connector J17

| 1 | UVCC1   |

|---|---------|

| 2 | UDATA1N |

| 3 | UDATA1P |

| 4 | GND     |

#### 10BaseT/100BaseTx Connector (J8)

The 10BaseT/100BaseTx Connector is an RJ45 connector located on the front panel of the CPX750HA board. The pin assignments for this connector are as follows:

Table 2-4. 10BaseT/100BaseTx Connector J8

| 1 | TD+           |

|---|---------------|

| 2 | TD-           |

| 3 | RD+           |

| 4 | AC Terminated |

| 5 | AC Terminated |

| 6 | RD-           |

| 7 | AC Terminated |

| 8 | AC Terminated |

### **COM1 Connector (J15)**

A standard DB9 receptacle is located on the front panel of the CPX750HA to provide the interface to the COM1 serial port. These COM1 signals are also routed to J11 on the transition module. A terminal may be connected to J15 or J11 on the transition module but not both at the same time. The pin assignments for this connector is as follows:

Table 2-5. COM1 Connector J15

| 1 | DCD |

|---|-----|

| 2 | RXD |

| 3 | TXD |

| 4 | DTR |

| 5 | GND |

| 6 | DSR |

| 7 | RTS |

| 8 | CTS |

| 9 | RI  |

#### **Debug Connector (J19)**

A 190-pin connector (J19 on the CPX750HA base board) provides access to the processor bus (MPU bus) and some bridge/memory controller signals. It can be used for debugging purposes. The pin assignments are listed in the following table.

**Table 2-6. Debug Connector (J19)**

| 1  | PA0     |     | PA1     | 2  |

|----|---------|-----|---------|----|

| 3  | PA2     |     | PA3     | 4  |

| 5  | PA4     |     | PA5     | 6  |

| 7  | PA6     |     | PA7     | 8  |

| 9  | PA8     |     | PA9     | 10 |

| 11 | PA10    |     | PA11    | 12 |

| 13 | PA12    |     | PA13    | 14 |

| 15 | PA14    |     | PA15    | 16 |

| 17 | PA16    |     | PA17    | 18 |

| 19 | PA18    | GND | PA19    | 20 |

| 21 | PA20    |     | PA21    | 22 |

| 23 | PA22    |     | PA23    | 24 |

| 25 | PA24    |     | PA25    | 26 |

| 27 | PA26    |     | PA27    | 28 |

| 29 | PA28    |     | PA29    | 30 |

| 31 | PA30    |     | PA31    | 32 |

| 33 | PA_PAR0 |     | PA_PAR1 | 34 |

| 35 | PA_PAR2 |     | PA_PAR3 | 36 |

| 37 | APE*    |     | RSRV*   | 38 |

| 39 | PD0     |     | PD1     | 40 |

| 41 | PD2     |     | PD3     | 42 |

Table 2-6. Debug Connector (J19) (continued)

| 43 | PD4  |     | PD5  | 44 |

|----|------|-----|------|----|

| 45 | PD6  |     | PD7  | 46 |

| 47 | PD8  |     | PD9  | 48 |

| 49 | PD10 |     | PD11 | 50 |

| 51 | PD12 |     | PD13 | 52 |

| 53 | PD14 |     | PD15 | 54 |

| 55 | PD16 |     | PD17 | 56 |

| 57 | PD18 | +5V | PD19 | 58 |

| 59 | PA20 |     | PD21 | 60 |

| 61 | PD22 |     | PD23 | 62 |

| 63 | PD24 |     | PD25 | 64 |

| 65 | PD26 |     | PD27 | 66 |

| 67 | PD28 |     | PD29 | 68 |

| 69 | PD30 |     | PD31 | 70 |

| 71 | PD32 |     | PD33 | 72 |

| 73 | PD34 |     | PD35 | 74 |

| 75 | PD36 |     | PD37 | 76 |

| 77 | PD38 |     | PD39 | 78 |

| 79 | PD40 |     | PD41 | 80 |

| 81 | PD42 |     | PD43 | 82 |

| 83 | PD44 |     | PD45 | 84 |

| 85 | PD46 |     | PD47 | 86 |

| 87 | PD48 |     | PD49 | 88 |

| 89 | PA50 |     | PD51 | 90 |

| 91 | PD52 |     | PD53 | 92 |

| 93 | PD54 |     | PD55 | 94 |

Table 2-6. Debug Connector (J19) (continued)

| 95  | PD56          | GND   | PD57          | 96  |

|-----|---------------|-------|---------------|-----|

| 97  | PD58          |       | PD59          | 98  |

| 99  | PD60          |       | PD61          | 100 |

| 101 | PD62          |       | PD63          | 102 |

| 103 | PDPAR0        |       | PDPAR1        | 104 |

| 105 | PDPAR2        |       | PDPAR3        | 106 |

| 107 | PDPAR4        |       | PDPAR5        | 108 |

| 109 | PDPAR6        |       | PDPAR7        | 110 |

| 111 | No Connection |       | No Connection | 112 |

| 113 | DPE*          |       | DBDIS*        | 114 |

| 115 | TT0           |       | TSIZ0         | 116 |

| 117 | TT1           |       | TSIZ1         | 118 |

| 119 | TT2           |       | TSIZ2         | 120 |

| 121 | TT3           |       | No Connection | 122 |

| 123 | TT4           |       | No Connection | 124 |

| 125 | CI*           |       | No Connection | 126 |

| 127 | WT*           |       | No Connection | 128 |

| 129 | GLOBAL*       |       | No Connection | 130 |

| 131 | SHARED*       |       | DBWO*         | 132 |

| 133 | AACK*         | +3.3V | TS*           | 134 |

| 135 | ARTY*         |       | XATS*         | 136 |

| 137 | DRTY*         |       | TBST*         | 138 |

| 139 | TA*           |       | No Connection | 140 |

| 141 | TEA*          |       | No Connection | 142 |

| 143 | No Connection |       | DBG*          | 144 |

| 145 | No Connection |       | DBB*          | 146 |

Table 2-6. Debug Connector (J19) (continued)

| 147 | No Connection  |     | ABB*          | 148 |

|-----|----------------|-----|---------------|-----|

| -   |                |     |               | _   |

| 149 | TCLK_OUT       |     | MPUBG-0*      | 150 |

| 151 | No Connection  |     | MPUBR0*       | 152 |

| 153 | MPUBR1*        |     | IRQ0*         | 154 |

| 155 | MPUBG1*        |     | MCHK*         | 156 |

| 157 | WDT1TO*        |     | SMI*          | 158 |

| 159 | WDT2TO*        |     | CKSTPI*       | 160 |

| 161 | L2BR*          |     | CKSTPO*       | 162 |

| 163 | L2BG*          |     | HALTED (N/C)  | 164 |

| 165 | CLAIM*         |     | TLBISYNC*     | 166 |

| 167 | No Connection  |     | TBEN          | 168 |

| 169 | No Connection* |     | No Connection | 170 |

| 171 | No Connection* | GND | No Connection | 172 |

| 173 | No Connection* |     | No Connection | 174 |

| 175 | No Connection  |     | NAPRUN        | 176 |

| 177 | SRST1*         |     | QREQ*         | 178 |

| 179 | SRESET*        |     | QACK*         | 180 |

| 181 | HRESET*        |     | CPUTDO        | 182 |

| 183 | GND            |     | CPUTDI        | 184 |

| 185 | CPUCLK1        |     | CPUTCK        | 186 |

| 187 | No Connection  |     | CPUTMS        | 188 |

| 189 | No Connection  |     | CPUTRST*      | 190 |

### **DRAM Mezzanine Connector (J10)**

A 190-pin connector (J10 on the CPX750HA base board) supplies the interface between the memory bus and the RAM300 DRAM mezzanine. The pin assignments are listed in the following table.

**Table 2-7. DRAM Mezzanine Connector (J10)**

| 1  | A_RAS*  |     | A_CAS*  | 2  |

|----|---------|-----|---------|----|

| 3  | B_RAS*  |     | B_CAS*  | 4  |

| 5  | C_RAS*  |     | C_CAS*  | 6  |

| 7  | D_RAS*  |     | D_CAS*  | 8  |

| 9  | OEL*    |     | OEU*    | 10 |

| 11 | WEL*    |     | WEU*    | 12 |

| 13 | ROMACS* |     | ROMBCS* | 14 |

| 15 | RAMAEN  |     | RAMBEN  | 16 |

| 17 | RAMCEN  |     | EN5VPWR | 18 |

| 19 | RAL0    | GND | RAL1    | 20 |

| 21 | RAL2    |     | RAL3    | 22 |

| 23 | RAL4    |     | RAL5    | 24 |

| 25 | RAL6    |     | RAL7    | 26 |

| 27 | RAL8    |     | RAL9    | 28 |

| 29 | RAL10   |     | RAL11   | 30 |

| 31 | RAL12   |     | RAU0    | 32 |

| 33 | RAU1    |     | RAU2    | 34 |

| 35 | RAU3    |     | RAU4    | 36 |

| 37 | RAU5    |     | RAU6    | 38 |

| 39 | RAU7    |     | RAU8    | 40 |

| 41 | RAU9    |     | RAU10   | 42 |

| 43 | RAU11   |     | RAU12   | 44 |

Table 2-7. DRAM Mezzanine Connector (J10) (continued)

| 45 | RDL0  |     | RDL1  | 46 |

|----|-------|-----|-------|----|

| 47 |       |     |       | 48 |

|    | RDL2  |     | RDL3  |    |

| 49 | RDL4  |     | RDL5  | 50 |

| 51 | RDL6  |     | RDL7  | 52 |

| 53 | RDL8  |     | RDL9  | 54 |

| 55 | RDL10 |     | RDL11 | 56 |

| 57 | RDL12 | +5V | RDL13 | 58 |

| 59 | RDL14 |     | RDL15 | 60 |

| 61 | RDL16 |     | RDL17 | 62 |

| 63 | RDL18 |     | RDL19 | 64 |

| 65 | RDL20 |     | RDL21 | 66 |

| 67 | RDL22 |     | RDL23 | 68 |

| 69 | RDL24 |     | RDL25 | 70 |

| 71 | RDL26 |     | RDL27 | 72 |

| 73 | RDL28 |     | RDL29 | 74 |

| 75 | RDL30 |     | RDL31 | 76 |

| 77 | RDL32 |     | RDL33 | 78 |

| 79 | RDL34 |     | RDL35 | 80 |

| 81 | RDL36 |     | RDL37 | 82 |

| 83 | RDL38 |     | RDL39 | 84 |

| 85 | RDL40 |     | RDL41 | 86 |

| 87 | RDL42 |     | RDL43 | 88 |

| 89 | RDL44 |     | RDL45 | 90 |

| 91 | RDL46 |     | RDL47 | 92 |

| 93 | RDL48 |     | RDL49 | 94 |

| 95 | RDL50 | GND | RDL51 | 96 |

**Table 2-7. DRAM Mezzanine Connector (J10) (continued)**

| 97  | RDL52         |       | RDL53         | 98  |

|-----|---------------|-------|---------------|-----|

| 99  | RDL54         |       | RDL55         | 100 |

| 101 | RDL56         |       | RDL57         | 102 |

| 103 | RDL58         |       | RDL59         | 104 |

| 105 | RDL60         |       | RDL61         | 106 |

| 107 | RDL62         |       | RDL63         | 108 |

| 109 | CDL0          |       | CDL1          | 110 |

| 111 | CDL2          |       | CDL3          | 112 |

| 113 | CDL4          |       | CDL5          | 114 |

| 115 | CDL6          |       | CDL7          | 116 |

| 117 | No Connection |       | No Connection | 118 |

| 119 | RDU0          |       | RDU1          | 120 |

| 121 | RDU2          |       | RDU3          | 122 |

| 123 | RDU4          |       | RDU5          | 124 |

| 125 | RDU6          |       | RDU7          | 126 |

| 127 | RDU8          |       | RDU9          | 128 |

| 129 | RDU10         |       | RDU11         | 130 |

| 131 | RDU12         |       | RDU13         | 132 |

| 133 | RDU14         | +3.3V | RDU15         | 134 |

| 135 | RDU16         |       | RDU17         | 136 |

| 137 | RDU18         |       | RDU19         | 138 |

| 139 | RDU20         |       | RDU21         | 140 |

| 141 | RDU22         |       | RDU23         | 142 |

| 143 | RDU24         |       | RDU25         | 144 |

| 145 | RDU26         |       | RDU27         | 146 |

| 147 | RDU28         |       | RDU29         | 148 |

Table 2-7. DRAM Mezzanine Connector (J10) (continued)

| 140 | DDI130 |     | DDII21 | 150 |

|-----|--------|-----|--------|-----|

| 149 | RDU30  |     | RDU31  | 150 |

| 151 | RDU32  |     | RDU33  | 152 |

| 153 | RDU34  |     | RDU35  | 154 |

| 155 | RDU36  |     | RDU37  | 156 |

| 157 | RDU38  |     | RDU39  | 158 |

| 159 | RDU40  |     | RDU41  | 160 |

| 161 | RDU42  |     | RDU43  | 162 |

| 163 | RDU44  |     | RDU45  | 164 |

| 165 | RDU46  |     | RDU47  | 166 |

| 167 | RDU48  |     | RDU49  | 168 |

| 169 | RDU50  |     | RDU51  | 170 |

| 171 | RDU52  | GND | RDU53  | 172 |

| 173 | RDU54  |     | RDU55  | 174 |

| 175 | RDU56  |     | RDU57  | 176 |

| 177 | RDU58  |     | RDU59  | 178 |

| 179 | RDU60  |     | RDU61  | 180 |

| 181 | RDU62  |     | RDU63  | 182 |

| 183 | CDU0   |     | CDU1   | 184 |

| 185 | CDU2   |     | CDU3   | 186 |

| 187 | CDU4   |     | CDU5   | 188 |

| 189 | CDU6   |     | CDU7   | 190 |

### **EIDE Compact FLASH Connector (J9)**

A 50-pin Compact FLASH card header connector provides the EIDE interface to the Compact FLASH Memory Card. The pin assignments for this connector are as follows:

Table 2-8. EIDE Compact FLASH Connector J9

| 1  | GND          | DATA3      | 2  |

|----|--------------|------------|----|

| 3  | DATA4        | DATA5      | 4  |

| 5  | DATA6        | DATA7      | 6  |

| 7  | DCS1A_L      | GND        | 8  |

| 9  | GND          | GND        | 10 |

| 11 | GND          | GND        | 12 |

| 13 | +5V          | GND        | 14 |

| 15 | GND          | GND        | 16 |

| 17 | GND          | DA2        | 18 |

| 19 | DA1          | DA0        | 20 |

| 21 | DATA0        | DATA1      | 22 |

| 23 | DATA2        | NO CONNECT | 24 |

| 25 | CD2_L        | CD1_L      | 26 |

| 27 | DATA11       | DATA12     | 28 |

| 29 | DATA13       | DATA14     | 30 |

| 31 | DATA15       | DCS3A_L    | 32 |

| 33 | NO CONNECT   | DIORA_L    | 34 |

| 35 | DIOWA_L      | NO CONNECT | 36 |

| 37 | INTRQA       | +5V        | 38 |

| 39 | MASTER/SLAVE | NO CONNECT | 40 |

| 41 | RST_L        | DIORDYA    | 42 |

| 43 | NO CONNECT   | NO CONNECT | 44 |

Table 2-8. EIDE Compact FLASH Connector J9

| 45 | NO CONNECT | NO CONNECT | 46 |

|----|------------|------------|----|

| 47 | DATA8      | DATA9      | 48 |

| 49 | DATA10     | GND        | 50 |

#### Flash Bank Selection (J6)

The CPX750HA base board has provision for 1MB of 16-bit flash memory. The RAM300 memory mezzanine accommodates 4MB or 8MB of additional 64-bit flash memory.

The flash memory is organized in either one or two banks, each bank either 16- or 64-bits wide. Bank B contains the onboard debugger, PPCBug.

To enable flash bank A (4MB or 8MB of firmware resident on soldered-in devices on the RAM300 mezzanine), place a jumper across header J6 pins 1 and 2. To enable flash bank B (1MB of firmware located in sockets on the base board), place a jumper across header J6 pins 2 and 3.

Flash Bank A Enabled (4MB/8MB, Soldered)

Flash Bank B Enabled (1MB, Sockets) (Factory Configuration)

## **CPV5350**

The CPV5350 Single Board Computer (SBC) is a hot swap, CompactPCI (Compact Peripheral Communication Interface) compliant computer with high availability platform support. It is powered by a PICMG (PCI Industrial Computer Manufacturers Group) compatible Pentium® II Deschutes Mobile Module. The CPV5350's 6U CompactPCI standard form factor (160mm x 233mm x 61mm), 4HP (.8 inch) is designed for installation into PICMG CompactPCI-compliant backplanes.

| The CP | V5350 provides:                                                                               |

|--------|-----------------------------------------------------------------------------------------------|

|        | Standard PC I/O                                                                               |

|        | USB                                                                                           |

|        | PCI EIDE                                                                                      |

|        | 3D AGP graphics                                                                               |

|        | Dual fast Ethernet controllers                                                                |

|        | Optional onboard CompactFlash <sup>TM</sup> connector                                         |

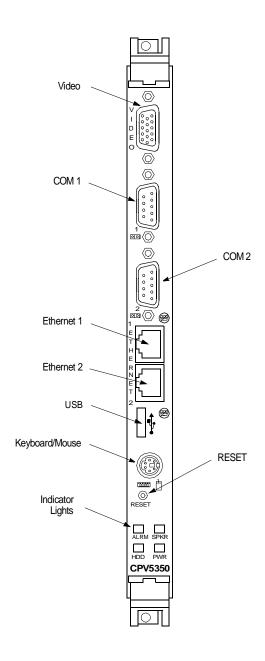

| The CP | VV5350's front panel has connectors for:                                                      |