| EEL 3744                  |     |        | SP      | 6/7-bit        | <i>y</i> |

|---------------------------|-----|--------|---------|----------------|----------|

| TI <b>DSC</b>             | AR  | 0H[16] | AR0[    | offset†<br>16] | XAR0[32] |

| 11 DSC                    | AR  | 1H[16] | AR1[    | 16]            | XAR1[32] |

| Programming               | AR  | 2H[16] | AR2[    | 16]            | XAR2[32] |

|                           | AR  | 3H[16] | AR3[    | 16]            | XAR3[32] |

| Model                     | AR  | 4H[16] | AR4[    | 16]            | XAR4[32] |

| ST0[16]                   | AR  | 5H[16] | AR5[    | 16]            | XAR5[32] |

| ST1[16]                   | AR  | 6H[16] | AR6[    | 16]            | XAR6[32] |

| G 420                     | AR  | 7H[16] | AR7[    | 16]            | XAR7[32] |

| See spru430,<br>Fia 2 3   |     |        | PC[22]  |                |          |

| Fig 2-3                   |     |        | RPC[22] |                |          |

| See also                  |     |        |         |                |          |

| lecture 3                 | T[1 | 6]     | TL[16   | ]              | XT[32]   |

| Plus <b>MANY</b> built-in | PH  | 16]    | PL[16   | ]              | P[32]    |

| peripheral devices        | AH  | [16]   | AL[1    | 6]             | ACC[32]  |

| © Drs. Schwartz & Arroyo  |     |        |         |                | 3        |

|                                                                                    | _ |

|------------------------------------------------------------------------------------|---|

| EEL 3744 <b>6811 &amp; 6812</b> General-                                           | _ |

| Purpose Registers                                                                  |   |

| • Within the 68HC11/12, there are two general-purpose                              |   |

| registers.                                                                         |   |

| > They are referred to as 8-bit registers A and B or alternatively as              |   |

| a 16-bit register <b>D</b> .                                                       |   |

| • Registers A and B, often called <i>accumulators</i>                              |   |

| [Examples]                                                                         |   |

| LDAA VALUE1 ; Move the byte at location VALUE1 to Register A.                      |   |

| ABA ; Add the byte in B to A; put the result in A.                                 |   |

| LDD WORD1 ; The 16-bit word at location WORD1 and WORD1+1 are                      |   |

| * ; moved to Register $D = A   B$ .                                                |   |

| ADDD WORD2 ; The 16-bit data at Word1 and Word1+1 are added to $D \Rightarrow D$ . |   |

| <ul> <li>This instruction set is <i>nearly symmetric</i>.</li> </ul>               |   |

| [Examples] LDA (LDAA and LDAB), STA (STAA and STAB),                               |   |

| University of Florida, EEL 3744-File 05 ROL (ROLA and ROLB), etc.                  | 5 |

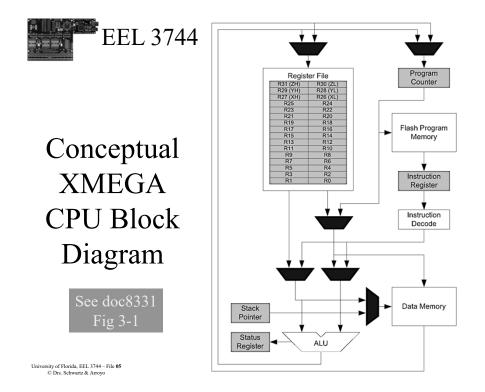

| EEL 3744                                                              |                  | 7             |     | 0    | Addr. |

|-----------------------------------------------------------------------|------------------|---------------|-----|------|-------|

|                                                                       |                  |               | R0  |      | 0x00  |

|                                                                       |                  |               | R1  |      | 0x01  |

|                                                                       |                  |               | R2  |      | 0x02  |

|                                                                       |                  |               |     |      |       |

| XMEGA CPU                                                             |                  |               | R13 |      | 0x0D  |

| General Purpos                                                        | e                |               | R14 |      | 0x0E  |

| L                                                                     | General i uipose |               | R15 |      |       |

| Working Register                                                      |                  | R16           |     | 0x10 |       |

| 0 0                                                                   |                  |               | R17 | ,    | 0x11  |

| Summary _                                                             |                  |               |     |      |       |

| X                                                                     | -regis           | ster Low Byte | R26 |      | 0x1A  |

|                                                                       | -regis           | ter High Byte | R27 | ,    | 0x1B  |

|                                                                       | -regis           | ster Low Byte | R28 |      | 0x1C  |

| Fig 3-4 Y-                                                            | -regis           | ter High Byte | R29 |      | 0x1D  |

| Z·                                                                    | -regis           | ster Low Byte | R30 |      | 0x1E  |

| University of Florida, EEL 3744 – File 05<br>© Drs. Schwartz & Arroyo | -regis           | ter High Byte | R31 |      | 0x1F  |

3

6

8

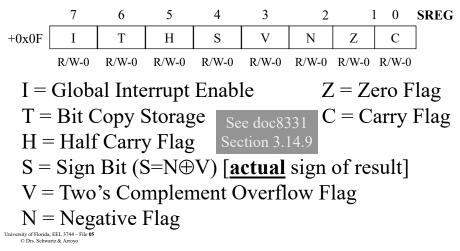

# EEL 3744 XMEGA Status Register (SREG)

• Contains information about the result of the most recently executed arithmetic or logic instruction

EEL 3744 XMEGA Flags See doc8331 Section 3.14.9 in SREG Global Int Enable (I): Set for interrupts to be enabled. If cleared, none of the interrupts are enabled. Can be set and cleared with the SEI and CLI instructions. Bit Copy Storage (T): The instructions BLD and BST use the T bit as source or destination for the operated bit Half-Carry Flag (H): Set if a carry occurs between bits 3 and 4 during some arithmetic instructions; otherwise, it is reset (to 0). Is useful in BCD arithmetic Sign Flag (S):  $S=N\oplus V$ . The sign bit is the Exclusive-OR between the negative flag (N) and the two's complement overflow flag (V). The actual sign of the result, even if there was an overflow. **Overflow (V):** Set if the last operation caused an arithmetic overflow; otherwise, it is reset. Ex: Set if the addition of two positive #'s (negative #'s) result in an apparently negative # (positive #). University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arrovo

See doc8331 Section 3.14.9

9

<u>Negative Flag (N)</u>: Set if the result of the last arithmetic, logic, or data manipulation operation was negative; otherwise, it is reset

<u>Zero (Z)</u>: Set if the result of the last arithmetic, logic, or data manipulation operation was zero; otherwise, it is reset

Carry (C): If an instruction operation results in a carry (from addition) or a borrow (from subtraction or comparison) out of bit 7 of the resulting value, then the Carry flag is set; otherwise, it is reset

#### Key for Flags affected by Instructions

- $\Leftrightarrow$ : Flag affected by instruction

- 0: Flag cleared by instruction

- 1: Flag set by instruction

- -: Flag not affected by instruction

University of Florida, EEL 3744 – File 05

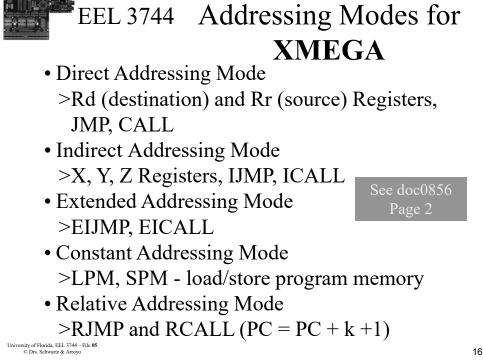

University of Florida, EEL 3744 – File **05** © Drs. Schwartz & Arroyo See doc0856 Page 2

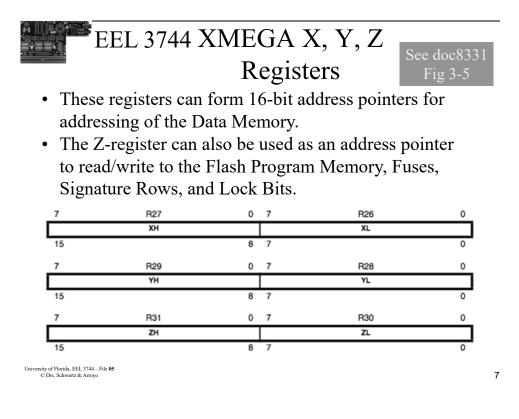

#### RAMPX, RAMPY, RAMPZ

- > Registers concatenated with the X-, Y-, and Z-registers enabling indirect addressing of the whole data space on MCUs with more than 64K bytes data space, and constant data fetch on MCUs with more than 64K bytes program space.

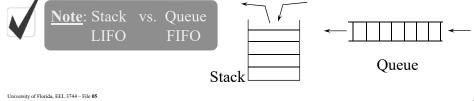

- Stack

- > STACK: Stack for return address and pushed/popped registers

- > **SP**: Stack Pointer to STACK

University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arroyo

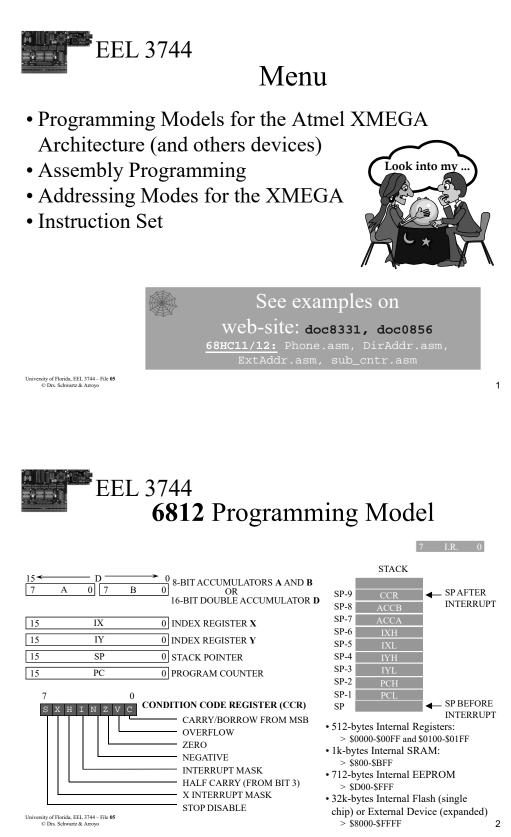

EEL 3744 6812 Special-Purpose Registers: CCR & IX/IY

- \* Index Registers (IX and IY): The 16-bit registers used to store the index value for operands retrieved using the indexed addressing mode.

- \* Condition Code Register (CCR): An 8-bit flag register in which condition codes (binary flags) are stored and tested.

#### CONDITION CODE REGISTER

- S Stop Disable N - Negative

- X X Interrupt Mask Z - Zero

- H Half Carry

- V Arithmetic Overflow

- I I Interrupt Mask

- C Carry/Borrow

University of Florida, EEL 3744 - File 05

University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arroyo

6

#### EEL 3744 **6812** Flags in CCR

There are five condition flags associated with the execution of the arithmetic instructions of the M68HC11/12. Half-Carry Flag (H): Set (to 1) if a carry occurs between bits 3 and 4 during ADD, ABA, or ADC instructions; otherwise, it is reset (to 0). Negative Flag (N): Set if the result of the last arithmetic, logic, or data manipulation operation was negative; otherwise, it is reset. Zero (Z): Set if the result of the last arithmetic, logic, or data manipulation operation was zero; otherwise, it is reset. **Overflow (V):** Set if the last operation caused an arithmetic overflow; otherwise, it is reset. Ex: Set if the addition of two positive #'s (negative #'s) result in an apparently negative # (positive #). <u>Carry (C)</u>: If an instruction operation results in a carry (from addition) or a borrow (from subtraction or comparison) out of bit 7 of the resulting value, then the Carry flag is set; otherwise, it is reset. University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arrovo 13

#### EEL 3744 **68HC11/12** Special-Purpose Registers: PC & SP

- Program Counter (PC): A 16-bit register whose content addresses the memory location that contains the next instruction to be executed.

- Stack Pointer (SP): A 16-bit register which contains the address of the memory location in which the top of the stack is stored.

University of Florida, EEL 3744 – File **05** © Drs. Schwartz & Arroyo

## EEL 3744 Addressing Modes for 68HC11/12

- Immediate Addressing Mode

- Direct Addressing Mode

- Extended Addressing Mode

- Indexed Addressing Mode

- Inherent Addressing Mode

- Relative Addressing Mode

University of Florida, EEL 3744 – File **05** © Drs. Schwartz & Arroyo 0

8

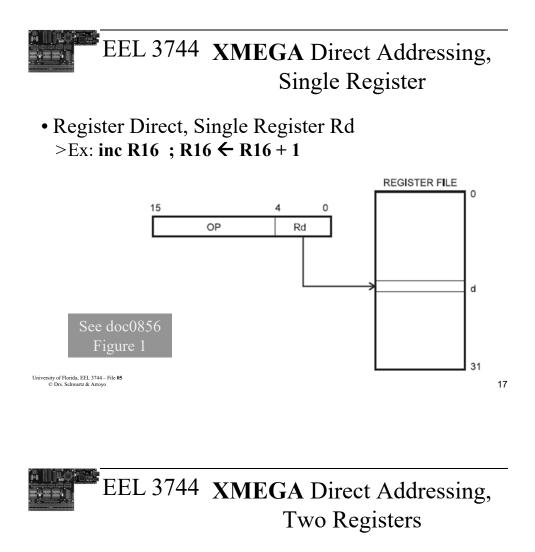

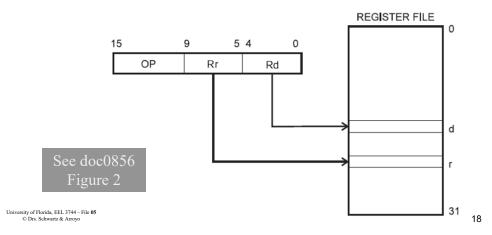

• Register Direct, Two Registers Rd and Rr >Ex: and R16, R17 ; R16 ← R16 AND R17

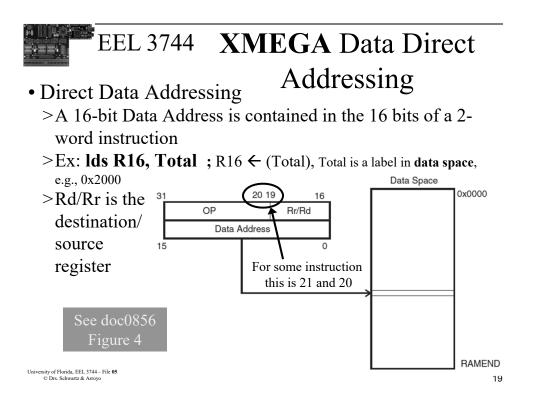

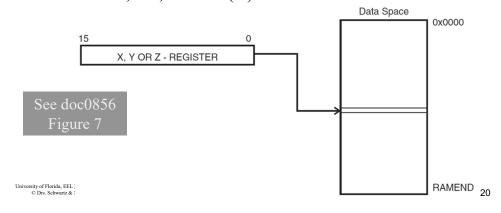

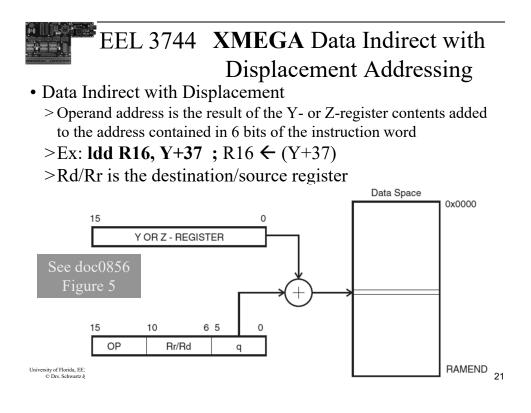

#### EEL 3744 XMEGA Data Indirect Addressing

- Data Indirect Addressing

- > Operand address is the contents of the X-, Y-, or the Z-register

- > Register Indirect Addressing is a subset of Data Indirect Addressing since the data space form 0 to 31 is the Register File

- >Ex: ld R16, X ; R16  $\leftarrow$  (X)

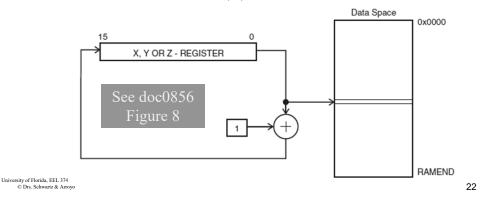

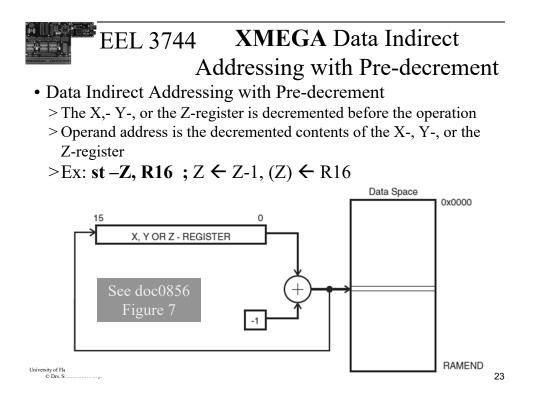

#### EEL 3744 XMEGA Data Indirect Addressing with Post-increment

- Data Indirect Addressing with Post-increment

- > The X,- Y-, or the Z-register is incremented after the operation

- > Operand address is the content of the X-, Y-, or the Z-register prior to incrementing

- >Ex: ld R16, Z+ ; R16 ← (Z), Z ← Z+1

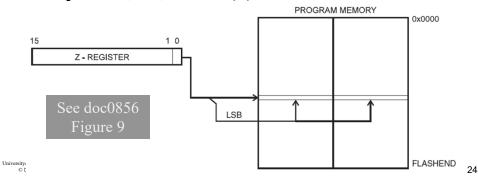

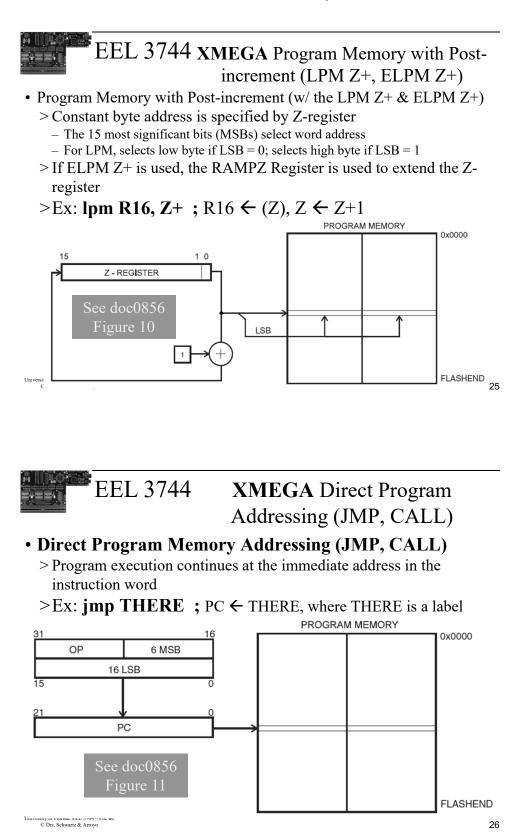

#### EEL 3744 XMEGA Program Memory Constant Addressing (LPM, SPM, ELPM)

• Program Memory Constant Addressing (LPM, SPM, ELPM)

> Constant byte address is specified by Z-register

- The 15 most significant bits (MSBs) select word address

- For LPM, selects low byte if LSB = 0; selects high byte if LSB = 1

- For SPM, the LSB should be cleared

- If ELPM is used, the RAMPZ Register is used to extend the Z-register

- >Ex: lpm R16, Z ; R16 < (Z)

EEL 3744 See doc0856

#### **XMEGA** Conditional **Branch Summary**

| Test         | Boolean                      | Mnemonic            | Complementary | Boolean                      | Mnemonic  | Comment  |

|--------------|------------------------------|---------------------|---------------|------------------------------|-----------|----------|

| Rd > Rr      | $Z \bullet (N \oplus V) = 0$ | BRLT <sup>(1)</sup> | $Rd \leq Rr$  | Z+(N ⊕ V) = 1                | BRGE*     | Signed   |

| Rd ≥Rr       | (N ⊕ V) = 0                  | BRGE                | Rd < Rr       | (N ⊕ V) = 1                  | BRLT      | Signed   |

| Rd = Rr      | Z = 1                        | BREQ                | Rd ≠ Rr       | Z = 0                        | BRNE      | Signed   |

| $Rd \leq Rr$ | Z+(N ⊕ V) = 1                | BRGE <sup>(1)</sup> | Rd > Rr       | $Z \bullet (N \oplus V) = 0$ | BRLT*     | Signed   |

| Rd < Rr      | (N ⊕ V) = 1                  | BRLT                | $Rd \geq Rr$  | (N ⊕ V) = 0                  | BRGE      | Signed   |

| Rd > Rr      | C + Z = 0                    | BRLO <sup>(1)</sup> | Rd ≤ Rr       | C + Z = 1                    | BRSH*     | Unsigned |

| Rd≥Rr        | C = 0                        | BRSH/BRCC           | Rd < Rr       | C = 1                        | BRLO/BRCS | Unsigned |

| Rd = Rr      | Z = 1                        | BREQ                | Rd ≠ Rr       | Z = 0                        | BRNE      | Unsigned |

| $Rd \leq Rr$ | C + Z = 1                    | BRSH <sup>(1)</sup> | Rd > Rr       | C + Z = 0                    | BRLO*     | Unsigned |

| Rd < Rr      | C = 1                        | BRLO/BRCS           | Rd ≥ Rr       | C = 0                        | BRSH/BRCC | Unsigned |

| Carry        | C = 1                        | BRCS                | No carry      | C = 0                        | BRCC      | Simple   |

| Negative     | N = 1                        | BRMI                | Positive      | N = 0                        | BRPL      | Simple   |

| Overflow     | V = 1                        | BRVS                | No overflow   | V = 0                        | BRVC      | Simple   |

| Zero         | Z = 1                        | BREQ                | Not zero      | Z = 0                        | BRNE      | Simple   |

Note: 1. Interchange Rd and Rr in the operation before the test, i.e., CP Rd,  $Rr \rightarrow CP Rr$ , Rd University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arroyo

University of Florida, EEL 3744 - File 05 © Drs. Schwartz & Arroyo

## EEL 3744 **XMEGA** Instructions: Arithmetic and Logic

- ADD, ADC, ADIW, SUB, SUBI, SBC, SBCI, SBIW

- AND, ANDI, OR, ORI, EOR, COM, NEG

- SBR (Set Bits in Register), CBR (Clear Bits in Register)

- INC, DEC

- TEST, CLR (Clear Register), SER (Set Register)

- MUL, MULS, MULSU, FMUL, FMULS, FMULSU

- DES (Data Encryption)

Complete Instruction Summary in doc0856 Pages 11-15

University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arroyo

31

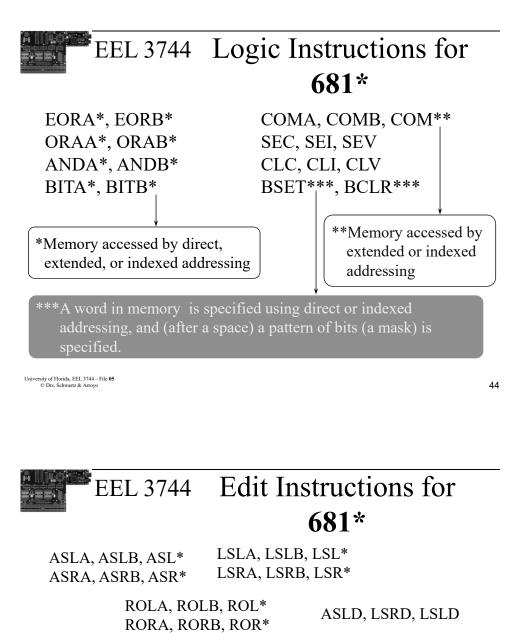

### EEL 3744 **XMEGA** Instructions: Branch Instructions

- See doc0856 page 10 (branch instructions, back 2 pages)

> BREQ, BRNE, BRCS, BRCC, BRSH, BRLO, BRMI, BRPL

> BRGE, BRLT, BRHS, BRHC, BRTS, BRTC, BRVS, BRVC

> BRIE, BRID (Branch if Interrupt Enabled/Disabled)

> BRBS, BRBS (Branch if Status Flag Set/Clear)

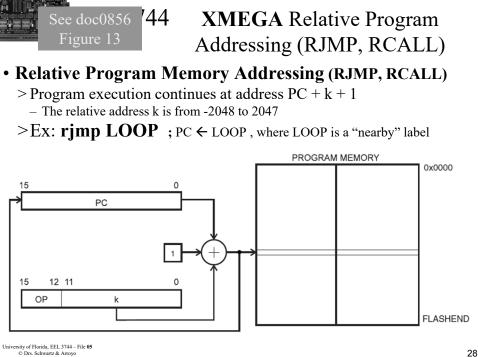

- **RJMP**, IJMP, EIJMP, **JMP**

- RCALL, ICALL, EICALL, CALL

- **RET**, RETI

- CPSE (ComPare, Skip if Equal), CP, CPI

- SBRC, SBRS, SBIC, SBIS (Skip if bit ---)

Complete Instruction Summary in doc0856 Pages 11-15

University of Florida, EEL 3744 – File **05**

University of Florida, EEL 3744 - File 05

© Drs. Schwartz & Arroyo

## EEL 3744 **XMEGA** Instructions: Data Transfer

- MOV, MOVW, LDI, LDS, LDD, LD (many)

- STS, ST (many)

- LPM, ELPM, SPM, IN, OUT

- PUSH, POP (uses the stack)

- XCH

University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arroyo

• LAS, LAC, LAT (Load and Set/Clear/Toggle)

33

### EEL 3744 XMEGA Instructions: Bit and Bit-Test

- LSL, LSR, ROL, ROR, ASR, SWAP (swap nibbles)

- BSET, BCLR

- SBI, CBI (Set/Clear Bit in I/O Register)

- BST, BLD

- SEC, CLC, SEN, CLN, SEZ, CLZ, SEV, CLV, SEH, CLH (Set/Clear C, N, Z, V, H)

- SEI, CLI (Set/Clear Interrupt Enable)

- SES, CLS (Set/Clear Signed Test)

- SET, CLT (Set/Clear T in SREG

University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arroyo Complete Instruction Summary in doc0856 Pages 11-15

University of Florida, EEL 3744 – File **05** © Drs. Schwartz & Arroyo

## EEL 3744 XMEGA Instructions: MCU Control BREAK, NOP, SLEEP, WDR (Watchdog Reset)

University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arroyo

#### Program Memory

- The 15 MSBits of the 16-bit address selects word addresses (the address of the 16-bit instruction)

- The least significant bit determines the least significant byte (when 0) and the most significant byte (when 1) of the 16-bit instruction

| Program Mem Address                                                          |      |      |      | MSB Address   | LSB Address | 8 |

|------------------------------------------------------------------------------|------|------|------|---------------|-------------|---|

| 0x0000→0b0000                                                                | 0000 | 0000 | 000_ | 0x0001        | 0x0000      |   |

| 0x0001→0b0000                                                                | 0000 | 0000 | 001_ | 0x0003        | 0x0002      |   |

| 0x0002→0b0000                                                                | 0000 | 0000 | 010_ | 0x0005        | 0x0004      |   |

|                                                                              | •••  |      |      | •••           |             |   |

| 0x7FFF→0b1111                                                                | 1111 | 1111 | 111_ | <b>0xfffe</b> | 0xFFFF      |   |

| University of Florida, EEL 3744 – File <b>05</b><br>© Drs. Schwartz & Arroyo |      |      |      |               |             | 3 |

University of Florida, EEL 3744 – File **05** © Drs. Schwartz & Arroyo 17

| EEL 3                                                                                                                                | 744 Subroutine C<br>Instructions for                                                                                           |                                                                                                      |    |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----|

| • call (Call to Subro<br>> General format:<br>> Description:                                                                         | outine)<br>call LABEL (or address)<br>STACK ← PC+2<br>SP ← SP-2<br>PC ← k (constant address operand)                           | )                                                                                                    |    |

| • rcall (Relative Ca<br>> General format:<br>> Description:                                                                          | <pre>11 to Subroutine)     rcall LABEL (or address)     STACK ← PC+1     SP ← SP-2     PC ← PC+k+1 (constant address op)</pre> | For Subroutine<br>Control Examples,<br>see <i>Lecture 7:</i><br><i>Program Structures</i><br>perand) |    |

| • ret (Return from S<br>> General format:<br>> Description:<br>University of Florida, EEL 3744 - File 05<br>@ Drs. Schwartz & Arroyo | Subroutine)<br>ret<br>$PC \leftarrow STACK$<br>$SP \leftarrow SP+2$                                                            |                                                                                                      | 40 |

```

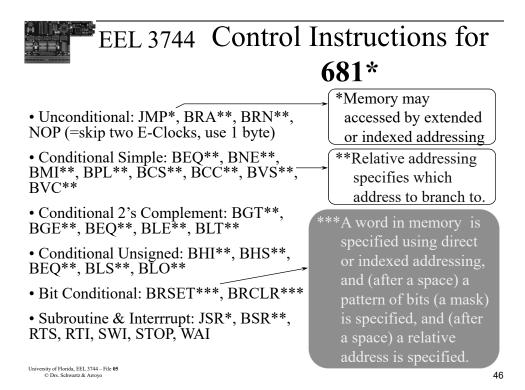

681* Instruction Set

```

• The instructions on the subsequent pages are a subset of the available 68HC12 instructions. The instructions can be divided up into the following 5 categories:

>Move Instructions

- >Arithmetic Instructions

- >Logic Instructions

- >Edit Instructions

- >Control Instructions

Instruction Bible S&H: Chap 4

S&H: Tab 4.1

41

University of Florida, EEL 3744 – File **05** © Drs. Schwartz & Arroyo

University of Florida, EEL 3744 - File 05

| E                                                                                                                                                                                                                            | EEL 3744                                             | Move Instructions for <b>681</b> *                   |                                                              |                        | ns for       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------|------------------------|--------------|

|                                                                                                                                                                                                                              | STAA**<br>STAB**<br>STD**<br>STX**<br>STY**<br>STS** | TAB<br>TBA<br>TAP<br>TPA<br>TSX<br>TXS<br>TSY<br>TYS | PSHA<br>PULA<br>PSHB<br>PULB<br>PSHX<br>PULX<br>PSHY<br>PULY | CLRA<br>CLRB<br>CLR*** | XGDX<br>XGDY |

| direct, extended,<br>indexed, or immediate<br>addressing  ***Memory accessed by<br>extended or indexed<br>addressing  **Memory accessed by direct, extended, or indexed addressing University of Florida, EEL 3744 - Flor 64 |                                                      |                                                      |                                                              |                        |              |

# EEL 3744 Arithmetic Instructions for **681**\*

| ADDA*, ADDB*                                                                 |                   |                                      |

|------------------------------------------------------------------------------|-------------------|--------------------------------------|

| ADCA*, ADCB*                                                                 | INCA, INCB, INC** | ADDD*                                |

| ABA                                                                          | DECA, DECB, DEC** | SUBD*                                |

| SUBA*, SUBB*                                                                 | NEGA, NEGB, NEG** | CPD*, CPX*, CPY*                     |

| SBCA*, SBCB*                                                                 | ASLA, ASLB, ASL** | INX, INY, INS                        |

| SBA                                                                          | ASRA, ASRB, ASR** | DEX, DEY, DES                        |

| CMPA*, CMPB*                                                                 | LSLA, LSLB, LSL** | FDIV, IDIV                           |

| CBA                                                                          | LSRA, LSRB, LSR** | ASLD, LSRD, LSLD                     |

| TSTA, TSTB                                                                   | Special: DAA,     | 443 1                                |

| TST**                                                                        | MUL, ABX, ABY     | **Memory accessed                    |

| *Memory accessed<br>direct, extended, in<br>or immediate addr                | ndexed,           | by extended or<br>indexed addressing |

| University of Florida, EEL 3744 – File <b>05</b><br>© Drs. Schwartz & Arroyo |                   | 43                                   |

|                                                                              |                   |                                      |

University of Florida, EEL 3744 – File **05** © Drs. Schwartz & Arroyo

\*Memory may accessed by extended or indexed addressing

University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arroyo

University of Florida, EEL 3744 – File **05** © Drs. Schwartz & Arroyo

#### EEL 3744 Other Useful **6812** Instructions

- MOVB, MOVW, TFR, EXG

- PSHD, PSHC, PULD, PULC

- Long branches (same but start with L, e.g., LBEQ)

EEL 3744 Subroutine Control Instructions for 68HC11 2: for Direct or Indexed X • BSR (Branch to Subroutine) 3: for Extended or Indexed Y > General format: BSR offset > Addressing Mode: PC Relative  $(-128 \le \text{offset} \le 127)$ > Description:  $(PC) \leftarrow (PC) + 2; \quad ((SP)) \leftarrow (PC_L);$  $(SP) \leftarrow (SP) - 1;$  $((SP)) \leftarrow (PC_H);$  $(SP) \leftarrow (SP) - 1; PC \leftarrow PC + offset$ • JSR (Jump to Subroutine) JSR address (or label) > General format: > Addressing Mode: Direct, Extended, Indexed X, Indexed Y  $(PC) \leftarrow (PC) + 2/3; \checkmark ((SP)) \leftarrow (PC_{I});$ > Description:  $(SP) \leftarrow (SP) - 1;$  $(SP) \leftarrow (SP) - 1; PC \leftarrow addr$  $((SP)) \leftarrow (PC_H);$ • RTS (Return from Subroutine) RTS > General format: > Addressing Mode: Inherent > Description: (SP)←(SP)+1;  $(PC_{H}) \leftarrow ((SP));$  $(SP) \leftarrow (SP) + 1;$  $(PC_1) \leftarrow ((SP))$

University of Florida, EEL 3744 – File 05 © Drs. Schwartz & Arroyo

EEL 3744

The End!

University of Florida, EEL 3744 - File 05

University of Florida, EEL 3744 – File **05** © Drs. Schwartz & Arroyo 49