# SoC-FPGA Design Guide DE0-Nano-SoC Edition

LAP - IC - EPFL

Version 1.32

Sahand Kashani-Akhavan

René Beuchat

# **1** TABLE OF CONTENTS

| 2 |    | List  | of Fig  | ures                                           | 5    |

|---|----|-------|---------|------------------------------------------------|------|

| 3 |    | Tabl  | e of T  | ables                                          | 8    |

| 4 |    | Prer  | equis   | ites                                           | 9    |

|   | 4. | 1     | Hard    | lware                                          | 9    |

|   | 4. | 2     | Soft    | ware                                           | 9    |

|   |    | 4.2.  | 1       | Software Versions Used in this Guide           | 9    |

|   |    | 4.2.  | 2       | Licenses                                       | 9    |

| 5 |    | Intro | oduct   | ion                                            | . 11 |

| 6 |    | Tera  | isic DI | E0-Nano-SoC Board                              | . 12 |

|   | 6. | 1     | Spec    | ifications                                     | . 12 |

|   |    | 6.1.  | 1       | FPGA Device                                    | . 12 |

|   |    | 6.1.  | 2       | Configuration and Debug                        | . 12 |

|   |    | 6.1.  | 3       | Memory Device                                  | . 12 |

|   |    | 6.1.  | 4       | Communication                                  | . 12 |

|   |    | 6.1.  | 5       | Connectors                                     | . 12 |

|   |    | 6.1.  | 6       | Switches, Buttons and Indicators               | . 12 |

|   |    | 6.1.  | 7       | Sensors                                        | . 13 |

|   |    | 6.1.  | 8       | Power                                          | . 13 |

|   |    | 6.1.  | 9       | Block Diagram                                  | . 13 |

|   | 6. | 2     | Layo    | ut                                             | . 14 |

| 7 |    | Cycl  | one \   | / Overview                                     | . 15 |

|   | 7. | 1     | Intro   | duction to the Cyclone V Hard Processor System | . 15 |

|   | 7. | 2     | Feat    | ures of the HPS                                | . 17 |

|   | 7. | 3     | Syste   | em Integration Overview                        | . 18 |

|   |    | 7.3.  | 1       | MPU Subsystem                                  | . 18 |

|   |    | 7.3.  | 2       | SDRAM Controller Subsystem                     | . 18 |

|   |    | 7.3.  | 3       | Support Peripherals                            | . 18 |

|   |    | 7     | .3.3.1  | System Manager                                 | . 18 |

|   |    | 7     | .3.3.2  |                                                |      |

|   |    | 7.3.  | 4       | Interface Peripherals                          | . 19 |

|   |    | 7     | .3.4.1  | GPIO Interfaces                                | . 19 |

|   |    | 7.3.  | 5       | On-Chip Memory                                 | . 19 |

|   |     | 7.3.5.1  | L On-Chip RAM                                | 19 |

|---|-----|----------|----------------------------------------------|----|

|   |     | 7.3.5.2  | 2 Boot ROM                                   | 19 |

|   | 7.4 | HPS      | -FPGA Interfaces                             | 19 |

|   | 7.5 | HPS      | Address Map                                  | 19 |

|   | 7.  | 5.1      | HPS Address Spaces                           | 19 |

|   | 7.  | 5.2      | HPS Peripheral Region Address Map            | 21 |

|   | 7.6 | HPS      | Booting and FPGA Configuration               | 23 |

|   | 7.  | 6.1      | HPS Boot and FPGA Configuration Ordering     | 23 |

|   | 7.  | 6.2      | Zooming In On the HPS Boot Process           | 25 |

|   |     | 7.6.2.1  | L Preloader                                  | 26 |

| 8 | U   | sing the | e Cyclone V – General Information            | 27 |

|   | 8.1 | Intro    | oduction                                     | 27 |

|   | 8.2 | FPG      | A-only                                       | 27 |

|   | 8.3 | HPS      | & FPGA                                       | 27 |

|   | 8.  | 3.1      | Bare-metal Application                       | 27 |

|   | 8.  | 3.2      | Application Over an Operating System (Linux) | 28 |

|   | 8.4 | Goa      | ls                                           | 28 |

|   | 8.5 | Proj     | ect Structure                                | 28 |

| 9 | U:  | sing the | e Cyclone V – Hardware                       | 30 |

|   | 9.1 | Gen      | eral Quartus Prime Setup                     | 30 |

|   | 9.2 | Syst     | em Design with Qsys – Nios II                | 30 |

|   | 9.3 | Syst     | em Design with Qsys – HPS                    | 31 |

|   | 9.  | 3.1      | Instantiating the HPS Component              | 32 |

|   |     | 9.3.1.1  |                                              |    |

|   |     | 9.3.1.2  | Peripheral Pins Tab                          | 32 |

|   |     | 9.3.     | 1.2.1 Theory                                 | 32 |

|   |     | 9.3.     | 1.2.2 Configuration                          | 33 |

|   |     | 9.3.1.3  | B HPS Clocks Tab                             | 35 |

|   |     | 9.3.1.4  |                                              |    |

|   |     | 3.2      | Interfacing with FPGA Peripherals            |    |

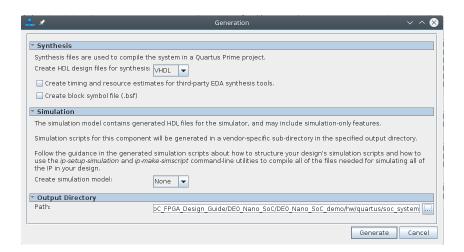

|   | 9.4 |          | erating the Qsys System                      |    |

|   | 9.5 | Inst     | antiating the Qsys System                    | 39 |

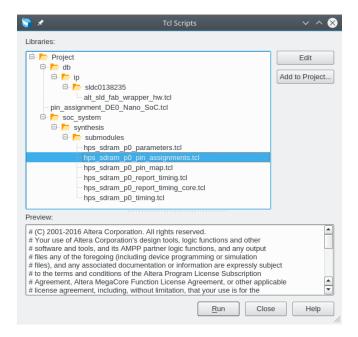

|   | 9.6 |          | DDR3 Pin Assignments                         |    |

|   | 9.7 | Wir      | ing the DEO-Nano-SoC                         | 42 |

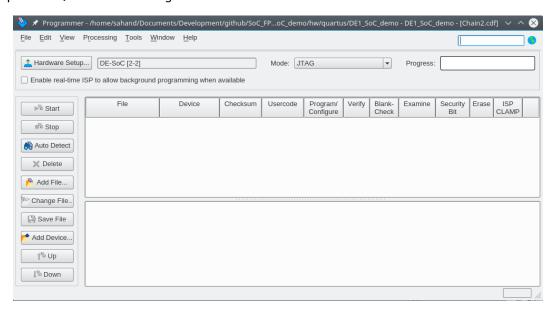

| 9.8 Pr       | ogramming the FPGA                                       | 43 |

|--------------|----------------------------------------------------------|----|

| 9.9 Cr       | eating Target sdcard Artifacts                           | 44 |

| 10 Usin      | g the Cyclone V – FPGA – Nios II – Bare-metal            | 45 |

| 10.1 Pr      | oject Setup                                              | 45 |

| 10.2 Ni      | os II Programming Theory – Accessing Peripherals         | 45 |

| 10.3 Ni      | os II Programming Practice                               | 46 |

| 11 Usin      | g the Cylone V – HPS – ARM – General                     | 48 |

| 11.1 Pa      | artitioning the sdcard                                   | 48 |

| 11.2 Ge      | enerating a Header File for HPS Peripherals              | 48 |

| 11.3 HF      | PS Programming Theory                                    | 49 |

|              | g the Cyclone V – HPS – ARM – Bare-metal                 |    |

|              | eloader                                                  |    |

| 12.1.1       | Preloader Generation                                     |    |

| 12.1.2       | Creating Target sdcard Artifacts                         |    |

|              | RM DS-5                                                  |    |

| 12.2.1       | Setting Up a New C Project                               |    |

| 12.2.2       | Writing a DS-5 Debug Script                              |    |

| 12.2.3       | Setting Up the Debug Configuration                       |    |

|              |                                                          |    |

| 12.2.4       | Bare-metal Programming                                   |    |

| 12.2<br>12.2 |                                                          |    |

|              | 2.2.4.2.1 Using Altera's HWLIB - Prerequisites           |    |

|              | 2.2.4.2.2 Global Timer & Clock Manager                   |    |

| 12           | 2.2.4.2.3 GPIO                                           |    |

| 12.2         | .4.3 Launching the Bare-metal Code in the Debugger       | 60 |

| 12.2         | .4.4 DS-5 Bare-metal Debugger Tour                       | 61 |

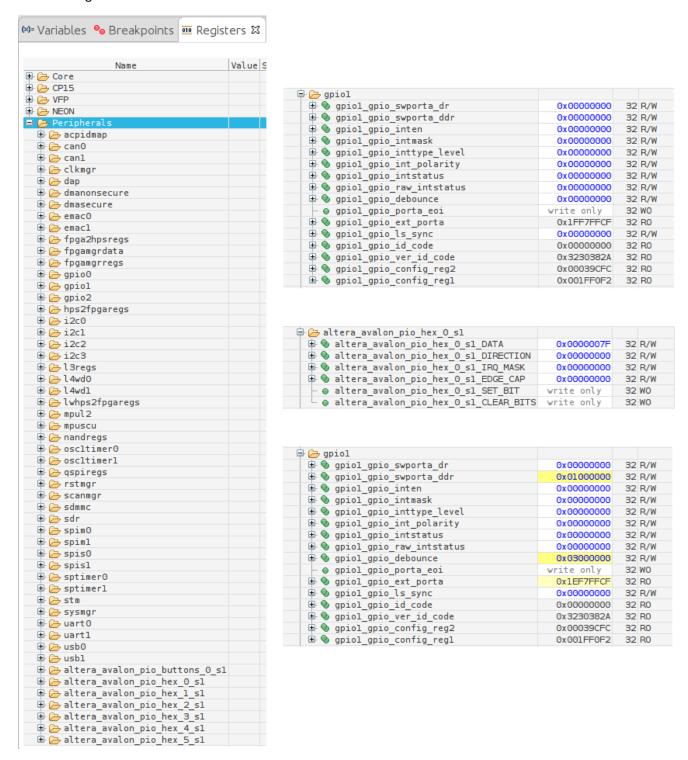

| 12           | 2.2.4.4.1 "Registers" View [UNAVAILABLE IN SoC EDS 16.0] | 61 |

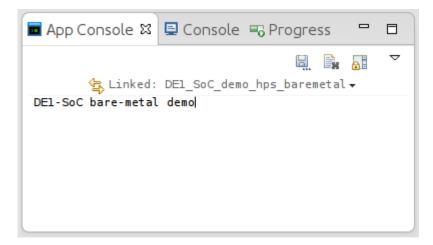

|              | 2.2.4.4.2 App Console                                    |    |

|              | g the Cyclone V – HPS – ARM – Linux                      |    |

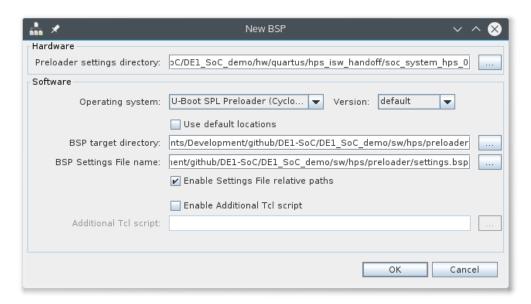

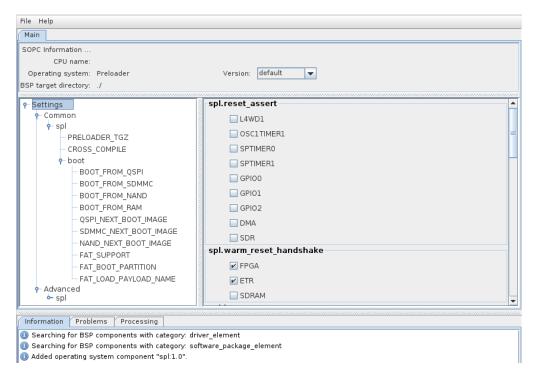

| 13.1 Pr      | eloader                                                  | 63 |

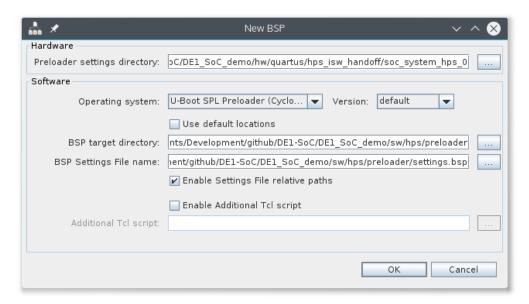

| 13.1.1       | Preloader Generation                                     | 63 |

| 13.1.2       | Creating Target sdcard Artifacts                         | 64 |

| 13.2 Bo      | potloader                                                | 64 |

| 13.2.1       | Getting & Compiling U-Boot                               | 64 |

|    | 13.2.2 Scripting U-Boot                                             | 66 |

|----|---------------------------------------------------------------------|----|

|    | 13.2.3 Creating Target sdcard Artifacts                             | 67 |

| 13 | .3.3 Linux Kernel                                                   | 67 |

|    | 13.3.1 Getting & Compiling Linux                                    | 67 |

|    | 13.3.2 Creating Target sdcard Artifacts                             | 68 |

| 13 | .3.4 Ubuntu Core Root Filesystem                                    |    |

|    | 13.4.1 Obtaining Ubuntu Core                                        |    |

|    | ·                                                                   |    |

|    | 13.4.2 Customizing Ubuntu Core                                      |    |

|    | 13.4.2.1 System configuration on first boot                         |    |

|    | 13.4.2.2 Post-install configuration script                          |    |

|    | 13.4.3 Creating Target sdcard Artifacts                             |    |

| 13 | .3.5 Writing Everything to the sdcard                               | 72 |

| 13 | 3.6 Scripting the Complete Procedure                                | 73 |

| 13 | .3.7 Testing the Setup                                              | 74 |

| 13 | 3.8 ARM DS-5                                                        | 84 |

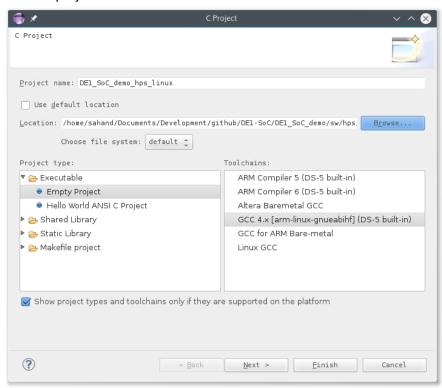

|    | 13.8.1 Setting Up a New C Project                                   | 84 |

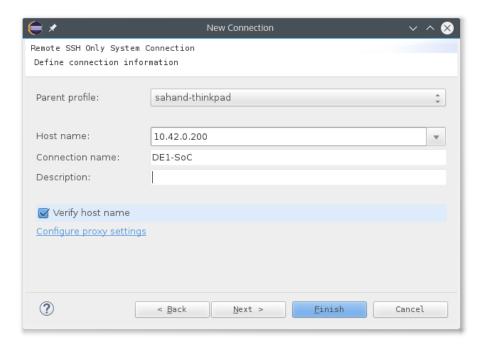

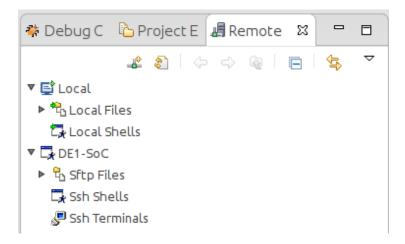

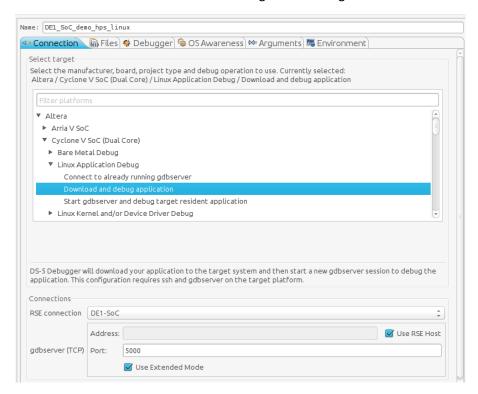

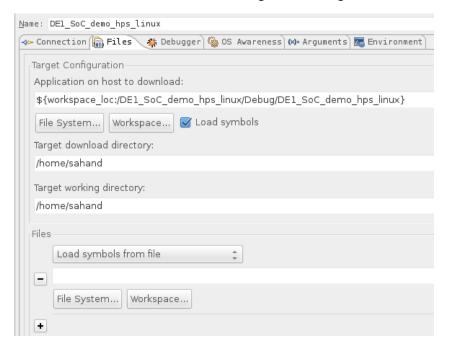

|    | 13.8.2 Creating a Remote Debug Connection to the Linux Distribution | 85 |

|    | 13.8.2.1 Find the Linux Distribution's IP Address                   | 85 |

|    | 13.8.2.2 Create an SSH Remote Connection                            | 87 |

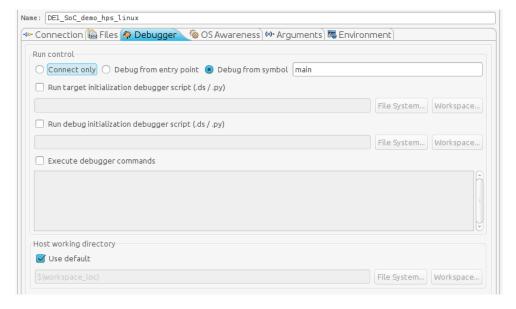

|    | 13.8.2.3 Setting Up the Debug Configuration                         | 88 |

|    | 13.8.3 Linux Programming                                            | 89 |

|    | 13.8.3.1 Using Altera's HWLIB - Prerequisites                       | 91 |

|    | 13.8.3.2 Accessing Hardware Peripherals from User Space             | 91 |

|    | 13.8.3.2.1 Opening the Physical Memory File Descriptor              | 91 |

|    | 13.8.3.2.2 Accessing HPS Peripherals                                | 92 |

|    | 13.8.3.2.3 Accessing FPGA Peripherals                               | 93 |

|    | 13.8.3.2.4 Cleaning Up Before Application Exit                      | 94 |

|    | 13.8.3.3 Launching the Linux code in the Debugger                   | 94 |

|    | 13.8.3.4 App Console                                                | 95 |

|    | 13.8.3.5 DS-5 Linux Debugger Restrictions                           | 96 |

| 14 | TODO                                                                | 97 |

| 15 | References                                                          | 98 |

# 2 LIST OF FIGURES

| Figure 6-1. Terasic DE0-Nano-SoC Board [1]                                                                                                                                                                                                        | 12    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

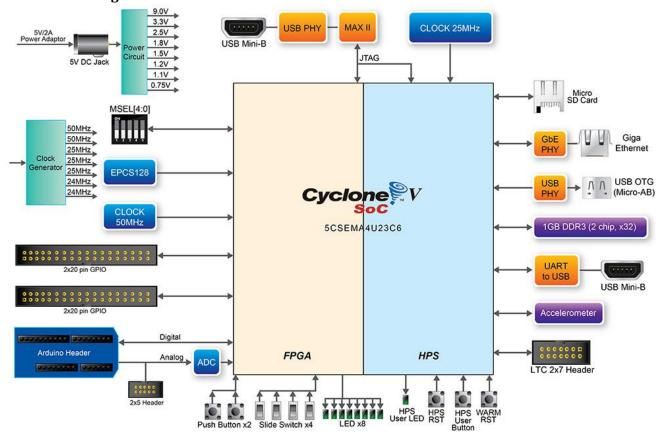

| Figure 6-2. Block Diagram of the DEO-Nano-SoC Board [1]                                                                                                                                                                                           | 13    |

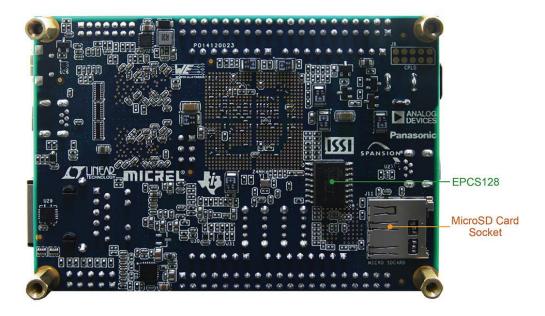

| Figure 6-3. Back [1]                                                                                                                                                                                                                              | 14    |

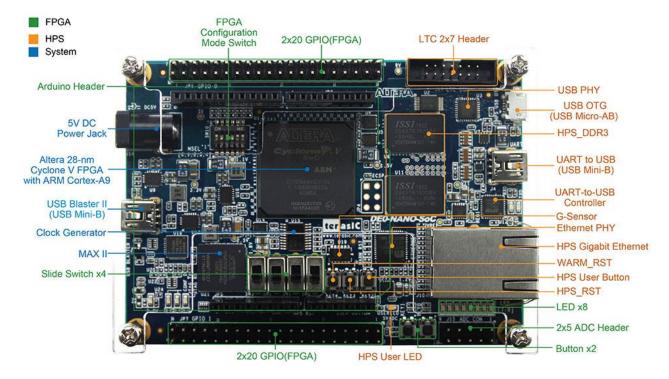

| Figure 6-4. Front [1]                                                                                                                                                                                                                             | 14    |

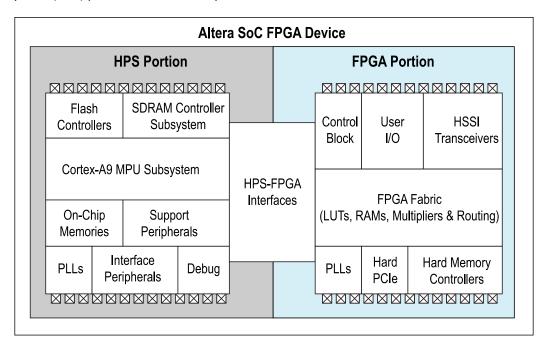

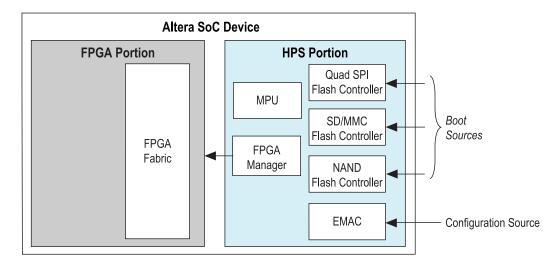

| Figure 7-1. Altera SoC FPGA Device Block Diagram [2, pp. 1-1]                                                                                                                                                                                     | 15    |

| Figure 7-2. HPS Block Diagram [2, pp. 1-3]                                                                                                                                                                                                        | 17    |

| Figure 7-3. HPS Address Space Relations [2, pp. 1-14]                                                                                                                                                                                             | 20    |

| Figure 7-4. Simplified HPS Boot Flow [2, pp. A-3]                                                                                                                                                                                                 | 23    |

| Figure 7-5. Independent FPGA Configuration and HPS Booting [2, pp. A-2]                                                                                                                                                                           | 24    |

| Figure 7-6. FPGA Configuration before HPS Booting (HPS boots from FPGA) [2, pp. A-2]                                                                                                                                                              | 24    |

| Figure 7-7. HPS Boots and Performs FPGA Configuration [2, pp. A-3]                                                                                                                                                                                | 25    |

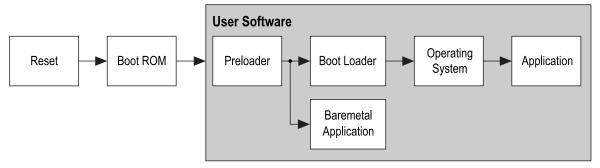

| Figure 7-8. HPS Boot Flows [2, pp. A-3]                                                                                                                                                                                                           | 25    |

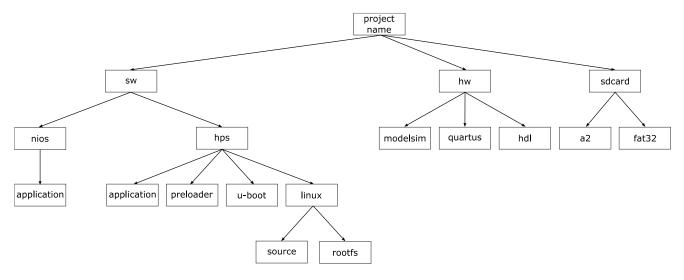

| Figure 8-1. Project Folder Structure                                                                                                                                                                                                              | 29    |

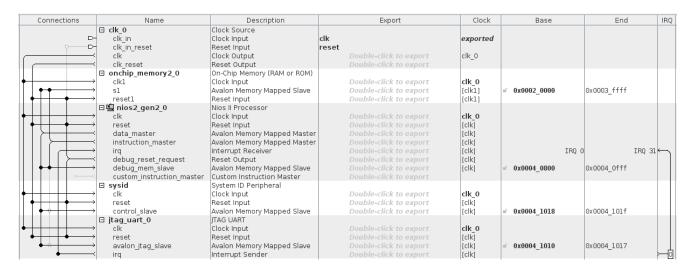

| Figure 9-1. Basic Nios II System with on-chip memory and JTAG UART                                                                                                                                                                                | 31    |

| Figure 9-2. Adding LEDs to the System                                                                                                                                                                                                             | 31    |

| Figure 9-3. HPS Component Parameters                                                                                                                                                                                                              | 32    |

| Figure 9-4. HPS_KEY_N & HPS_LED on DEO-Nano-SoC Schematic. Note that the schematic uses "HPS_KEY" instead of "HPS_KEY_N" as the name of the signal. This is a mistake, as the button is active-low, so the "_I the name is warranted for clarity. | N" in |

| Figure 9-5. HPS_KEY_N & HPS_LED on Qsys Peripheral Pins Tab                                                                                                                                                                                       | 33    |

| Figure 9-6. Using Pin G21 for SPI                                                                                                                                                                                                                 |       |

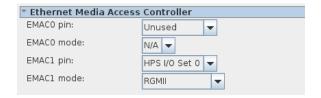

| Figure 9-7. Ethernet MAC configuration                                                                                                                                                                                                            |       |

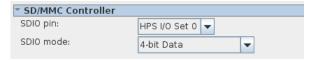

| Figure 9-8. SD/MMC configuration                                                                                                                                                                                                                  | 34    |

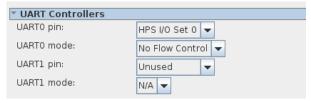

| Figure 9-9. UART configuration                                                                                                                                                                                                                    | 34    |

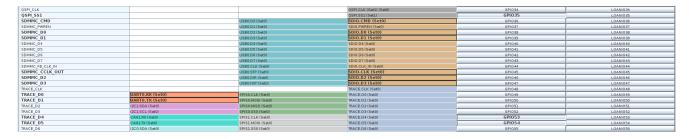

| Figure 9-10. Exported peripheral pins                                                                                                                                                                                                             | 34    |

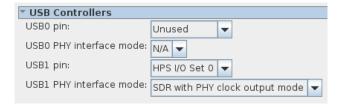

| Figure 9-11. USB, SPI, and I <sup>2</sup> C peripheral pin configurations                                                                                                                                                                         | 35    |

| Figure 9-12. Adding the "Standalone" HPS to the System                                                                                                                                                                                            | 37    |

| Figure 9-13. Adding Buttons and 7-segment Displays to the Lightweight HPS-to-FPGA Bridge                                                                                                                                                          | 38    |

| Figure 9-14. Generate Qsys System                                                                                                                                                                                                                 | 38    |

| Figure 9-15. Qsys Component Instantiation                                                                                                                                                                                                         | 40    |

| Figure 9-16. Final Top-level Entity                                                                                                                                                                                                               | 41    |

| Figure 9-17. Correct HPS DDR3 Pin Assignment TCL Script Selection                                                                                                                                                                                 | 42    |

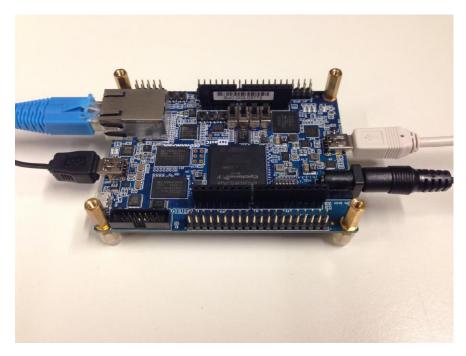

| Figure 9-18. DE0-Nano-SoC Wiring                                                              | 42 |

|-----------------------------------------------------------------------------------------------|----|

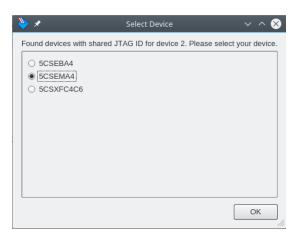

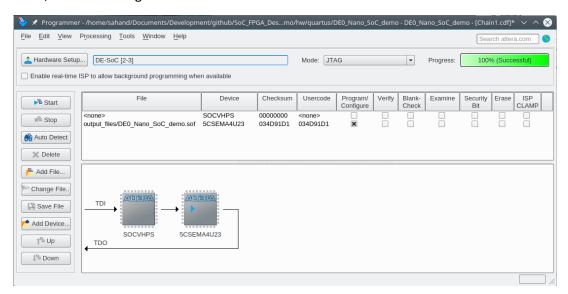

| Figure 9-19. Quartus Prime Programmer                                                         | 43 |

| Figure 9-20. FPGA Selection                                                                   | 43 |

| Figure 9-21. JTAG Scan Chain                                                                  | 43 |

| Figure 9-22. Programming the FPGA                                                             | 44 |

| Figure 10-1. Incorrect Nios II Peripheral Access in C                                         | 45 |

| Figure 10-2. Correct Nios II Peripheral Access in C                                           | 46 |

| Figure 10-3. nios.c                                                                           | 47 |

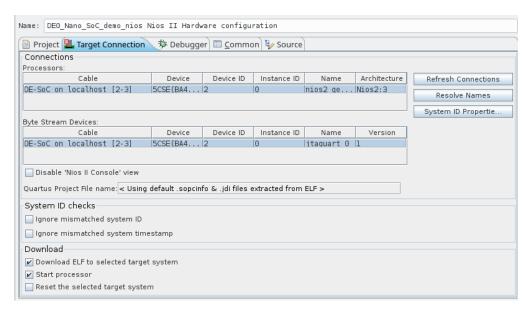

| Figure 10-4. Nios II Target Connection Dialog                                                 | 47 |

| Figure 11-1. Partitioning the sdcard                                                          | 48 |

| Figure 11-2. hps_soc_system.h                                                                 | 49 |

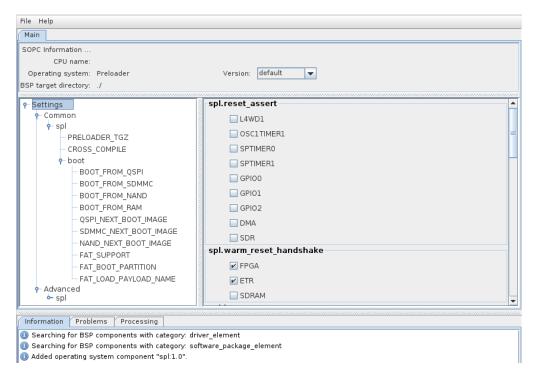

| Figure 12-1. New BSP Dialog                                                                   | 51 |

| Figure 12-2. Preloader Settings Dialog                                                        | 52 |

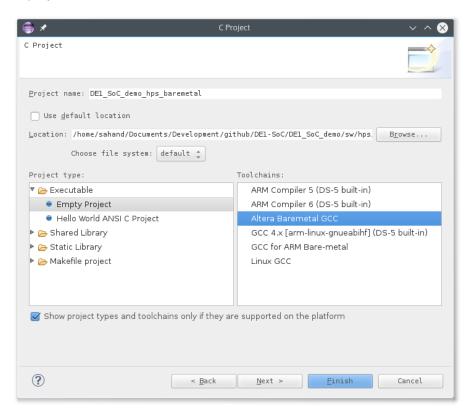

| Figure 12-3. New C Project Dialog                                                             | 53 |

| Figure 12-4. debug_setup.ds                                                                   | 55 |

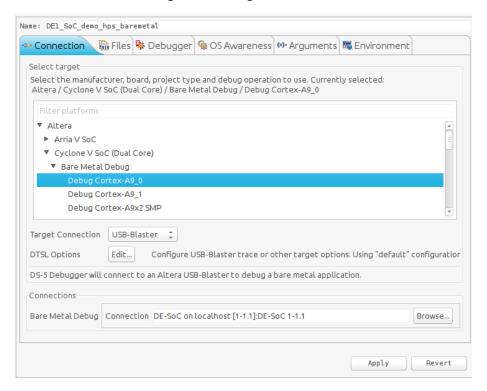

| Figure 12-5. Debug Configuraton "Connection" Tab                                              | 55 |

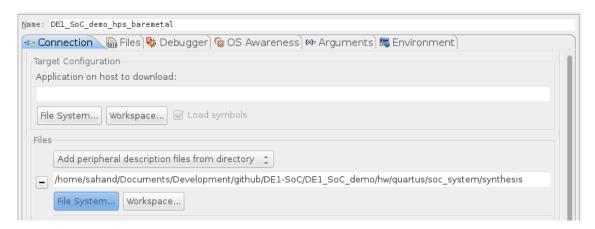

| Figure 12-6. Debug Configuration "Files" Tab                                                  | 56 |

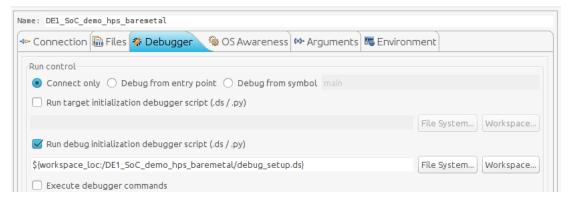

| Figure 12-7. Debug Configuration "Debugger" Tab                                               | 56 |

| Figure 12-8. hps_baremetal.c main() function                                                  | 57 |

| Figure 12-9. Accessing FPGA Buttons from the HPS                                              | 57 |

| Figure 12-10. Programming the HPS Global Timer                                                | 58 |

| Figure 12-11. Programming the HPS GPIO Peripheral                                             | 59 |

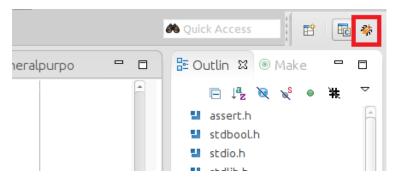

| Figure 12-12. Switching to the DS-5 Debug Perspective                                         | 60 |

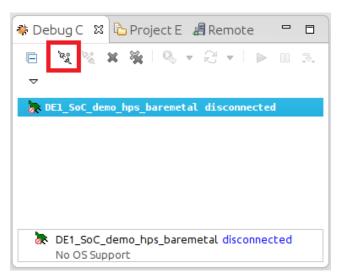

| Figure 12-13. Debug Control View                                                              | 60 |

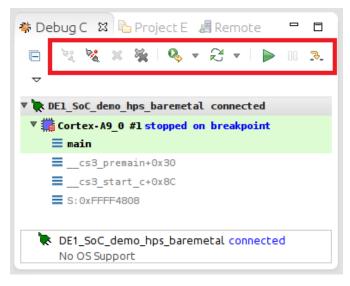

| Figure 12-14. DS-5 Debugger Controls                                                          | 60 |

| Figure 12-15. DS-5 Debugger Registers View                                                    | 61 |

| Figure 12-16. DS-5 App Console View                                                           | 62 |

| Figure 13-1. New BSP Dialog                                                                   | 63 |

| Figure 13-2. Preloader Settings Dialog                                                        | 64 |

| Figure 13-3. U-Boot Script                                                                    | 67 |

| Figure 13-4. Rootfs system configuration script to be used on first boot ("config_system.sh") | 71 |

| Figure 13-5. Rootfs /etc/rc.local file                                                        | 71 |

| Figure 13-6. Rootfs post-install configuration script to be used <b>AFTER</b> the first boot ("config_post_ir | =  |

|---------------------------------------------------------------------------------------------------------------|----|

| Figure 13-7. Target sdcard directory                                                                          |    |

| Figure 13-8. Incorrect DEO-Nano-SoC Boot Messages (from U-Boot)                                               | 74 |

| Figure 13-9. DE0-Nano-SoC Boot Messages (first boot)                                                          | 79 |

| Figure 13-10. DE0-Nano-SoC Boot Messages (second boot)                                                        | 84 |

| Figure 13-11. New C Project Dialog                                                                            | 84 |

| Figure 13-12. hps_linux.c with an empty main() function.                                                      | 85 |

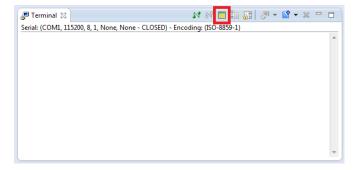

| Figure 13-13. ARM DS-5 Serial Terminal                                                                        | 85 |

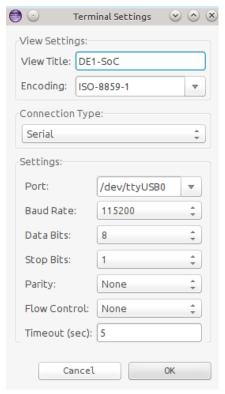

| Figure 13-14. ARM DS-5 Serial Terminal Settings                                                               | 86 |

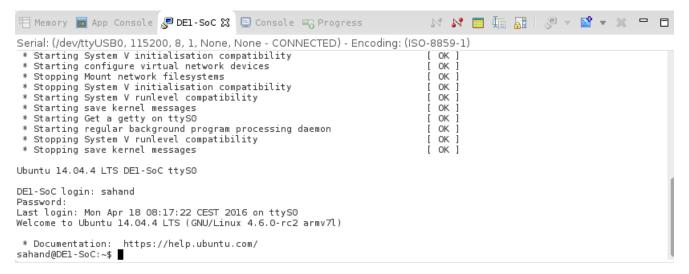

| Figure 13-15. ARM DS-5 Serial Terminal Linux Prompt                                                           | 86 |

| Figure 13-16. Obtaining the DEO-Nano-SoC's IP Address through ARM DS-5's Serial Terminal                      | 87 |

| Figure 13-17. New SSH Only Connection                                                                         | 87 |

| Figure 13-18. New SSH Connection In "Remote Systems" View                                                     | 88 |

| Figure 13-19. Debug Configuration "Connection" Tab                                                            | 88 |

| Figure 13-20. Debug Configuration "Files" Tab                                                                 | 89 |

| Figure 13-21. Debug Configuration "Debugger" Tab                                                              | 89 |

| Figure 13-22. hps_linux.c main() function.                                                                    | 90 |

| Figure 13-23. Prototype of the mmap() function.                                                               | 91 |

| Figure 13-24. open_physical_memory_device() function.                                                         | 91 |

| Figure 13-25. mmap_hps_peripherals() function.                                                                | 92 |

| Figure 13-26. setup_hps_gpio() function                                                                       | 92 |

| Figure 13-27. handle_hps_led() function                                                                       | 93 |

| Figure 13-28. mmap_fpga_peripherals() function                                                                | 93 |

| Figure 13-29. setup_fpga_leds() function                                                                      | 94 |

| Figure 13-30. handle_fpga_leds() function.                                                                    | 94 |

| Figure 13-31. munmap_peripherals() family of functions.                                                       | 94 |

| Figure 13-32. close_physical_memory_device() function.                                                        | 94 |

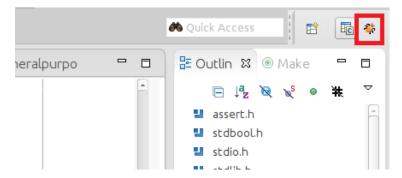

| Figure 13-33. Switching to the DS-5 Debug Perspective                                                         | 95 |

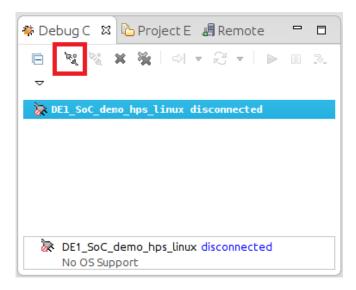

| Figure 13-34. Debug Control View                                                                              | 95 |

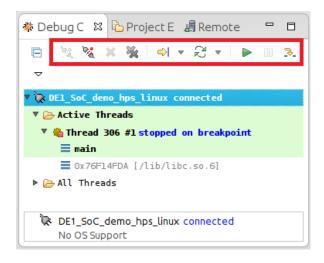

| Figure 13-35. DS-5 Debugger Controls                                                                          | 95 |

| Figure 13-36. DS-5 App Console View                                                                           | 96 |

# 3 TABLE OF TABLES

| Table 7-1. Possible HPS and FPGA Power Configurations      | . 16 |

|------------------------------------------------------------|------|

| Table 7-2. HPS Address Spaces [2, pp. 1-13]                | . 20 |

| Table 7-3. Common Address Space Regions [2, pp. 1-15]      | . 20 |

| Table 7-4. HPS Peripheral Region Address Map [2, pp. 1-16] | . 22 |

| Table 11-1 Predefined Data Sizes in socal h                | 10   |

## 4 Prerequisites

#### 4.1 HARDWARE

We use the Terasic DEO-Nano-SoC board in this guide, but the guide can easily be adapted to be used with any other Cyclone V SoC device.

#### 4.2 SOFTWARE

This guide assumes users are running a version of the **UBUNTU** operating system on their host machines. Furthermore, it is assumed you have **ROOT PERMISSIONS** on the machine and have installed the following programs:

- Quartus Prime

- Nios II Software Build Tools (Nios II SBT)

- ModelSim-Altera

- SoC Embedded Design Suite (SoC EDS)

Additionally, we require that you install the following packages from the Ubuntu package manager:

- git

- minicom

Finally, we insist that **ALL** command-line instructions provided in this guide **MUST** be executed in an **ALTERA EMBEDDED COMMAND SHELL**. The executable for the **Altera Embedded Command Shell** can be found at "<altra\_install\_directory>/<version>/embedded/embedded\_command\_shell.sh"

#### 4.2.1 Software Versions Used in this Guide

- All HARDWARE examples in this guide were made with Quartus Prime, SoC EDS and Nios II SBT version

16.0

- All **SOFTWARE** examples in this guide were made with *Quartus Prime*, *SoC EDS* and *Nios II SBT* version **16.0**

- Some FIGURES in this guide were made with Quartus Prime, SoC EDS and Nios II SBT version 14.0.

- The **HOST OPERATING SYSTEM** used is **UBUNTU 16.04**, but all instructions in the guide have also been successfully tested on all versions of Ubuntu from 14.04 to 16.04.

#### 4.2.2 Licenses

• Chapter 12: "Using the Cyclone V – HPS – ARM – Bare-metal" shows how to perform bare-metal debugging for demonstration purposes in order to see what the systems described in this tutorial can do. However, I highly recommend using linux on the HPS instead or bare-metal debugging.

Indeed, *BARE-METAL* debugging in *ARM DS-5 REQUIRES* a *PAID LICENSE* (not the free community license). If you do not have a paid license, then you should use linux on the HPS instead of bare-metal debugging as debugging a *LINUX* application in *ARM DS-5* does *NOT REQUIRE* a *PAID LICENSE*, and is *FULLY SUPPORTED* with the *FREE COMMUNITY LICENSE*.

Additionally, using linux on such a system is much easier and supperior to bare-metal programming.

Using a Nios II processor as described in this tutorial REQUIRES a PAID LICENSE in order to convert the

FPGA programming file that Quartus Prime generates (\*.sof) into a RAW Binary File (\*.rbf) to be

used to program the FPGA automatically at boot time.

If you do not have a paid license for the Nios II processor, then you should avoid using it and just use the HPS instead. No license is required for using the HPS.

## **5** Introduction

The development of embedded systems based on chips containing one or more microprocessors and hardcore peripherals, as well as an FPGA part is becoming more and more important. This technology gives the designer a lot of freedom and powerful abilities. Classical design flows with microcontrollers are emphasized with the full power of FPGAs.

Mixed designs are becoming a reality. One can now design specific accelerators to greatly improve algorithms, or create specific programmable interfaces with the external world.

Two main HDL (Hardware Design Language) languages are available for the design of the FPGA part: VHDL and Verilog. There also exist other tools that perform automatic translations from C to HDL. New emerging technologies like OpenCL allow compatibility between high-level software design, and low-level hardware implementations such as:

- Compilation for single or multicore processors

- Compilation for GPUs (Graphical Processing Unit)

- Translation and compilation for FPGAs. The latest models use a PCIe interface or some other way of parameters passing between the main processor and the FPGA

We will introduce and use the Terasic DEO-Nano-SoC board, as well as the ARM DS-5 IDE.

## 6 TERASIC DEO-NANO-SOC BOARD

Figure 6-1. Terasic DEO-Nano-SoC Board [1]

The DEO-Nano-SoC board has many features that allow users to implement a wide range of designed circuits. We will discuss some noteworthy features in this guide.

#### **6.1 Specifications**

#### 6.1.1 FPGA Device

- Cyclone V SoC **5CSEMA4U23C6N** Device

- Dual-core ARM CORTEX-A9 (HPS)

- 40K Programmable Logic Elements

- 2'460 Kbits embedded memory

#### 6.1.2 Configuration and Debug

- Serial Configuration device EPCS128 on FPGA

- On-Board USB BLASTER II

#### 6.1.3 Memory Device

- 1 GB (2x256Mx16) DDR3 SDRAM on HPS

- MICRO SD Card Socket on HPS

#### 6.1.4 Communication

- USB OTG Port (USB Micro-AB connector)

- UART to USB (USB Mini-B connector)

- 10/100/1000 Ethernet

#### 6.1.5 Connectors

- Two 40-pin Expansion Headers

- One 10-pin ADC Input Header

- One LTC connector

#### 6.1.6 Switches, Buttons and Indicators

- 3 User Keys (FPGA x2; Hps x1)

- 4 User switches (FPGA x4)

- 11 User LEDs (FPGA x10; HPS x1)

• 2 HPS Reset Buttons (HPS\_RST\_n and HPS\_WARM\_RST\_n)

#### 6.1.7 Sensors

G-Sensor on HPS

#### **6.1.8** Power

• 12V DC input

## 6.1.9 Block Diagram

Figure 6-2. Block Diagram of the DEO-Nano-SoC Board [1]

## 6.2 LAYOUT

Figure 6-3. Back [1]

Figure 6-4. Front [1]

- Green for peripherals directly connected to the FPGA

- Orange for peripherals directly connected to the HPS

- Blue for board control

## 7 CYCLONE V OVERVIEW

This section describes some features of the Cyclone V family of devices. We do not list all features, but only the ones most important to us. All information below, along with the most complete documentation regarding this family can be found in the Cyclone V Device Handbook [2].

#### 7.1 Introduction to the Cyclone V Hard Processor System

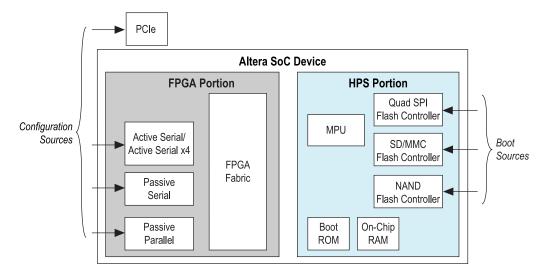

The Cyclone V device is a single-die system on a chip (SoC) that consists of two distinct parts – a hard processor system (HPS) portion and an FPGA portion.

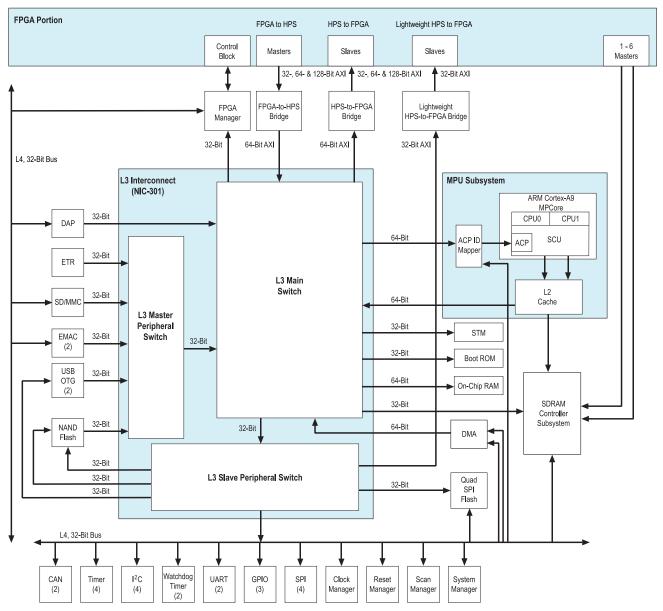

Figure 7-1. Altera SoC FPGA Device Block Diagram [2, pp. 1-1]

The HPS contains a microprocessor unit (MPU) subsystem with single or dual ARM Cortex-A9 MPCore processors, flash memory controllers, SDRAM L3 Interconnect, on-chip memories, support peripherals, interface peripherals, debug capabilities, and phase-locked loops (PLLs). The dual-processor HPS supports symmetric (SMP) and asymmetric (AMP) multiprocessing.

The DEO-Nano-SoC has a **DUAL**-processor HPS.

The FPGA portion of the device contains the FPGA fabric, a control block (CB), phase-locked loops (PLLs), and depending on the device variant, high-speed serial interface (HSSI) transceivers, hard PCI Express (PCIe) controllers, and hard memory controllers.

The DEO-Nano-SoC does not contain any HSSI transceivers, or hard PCIe controllers.

The HPS and FPGA portions of the device are distinctly different. The HPS can boot from

- the FPGA fabric,

- external flash, or

- JTAG

In contrast, the FPGA must be configured either through

- the HPS, or

- an externally supported device such as the Quartus Prime programmer.

The MPU subsystem can boot from

- flash devices connected to the HPS pins, or

- from memory available on the FPGA portion of the device (when the FPGA portion is previously configured by an external source).

The HPS and FPGA portions of the device each have their own pins. Pins are not freely shared between the HPS and the FPGA fabric. The **FPGA I/O PINS** are configured by an **FPGA CONFIGURATION IMAGE** through the HPS or any external source supported by the device. The **HPS I/O PINS** are configured by **SOFTWARE** executing in the HPS. Software executing on the HPS accesses control registers in the Cyclone V system manager to assign HPS I/O pins to the available HPS modules.

#### The **SOFTWARE** that configures the **HPS I/O PINS** is called the **PRELOADER**.

The HPS and FPGA portions of the device have separate external power supplies and independently power on. You can power on the HPS without powering on the FPGA portion of the device. However, to power on the FPGA portion, the HPS must already be on or powered on at the same time as the FPGA portion. Table 7-1 summarizes the possible configurations.

| <b>HPS Power</b> | <b>FPGA Power</b> |

|------------------|-------------------|

| On               | On                |

| On               | Off               |

| Off              | Off               |

Table 7-1. Possible HPS and FPGA Power Configurations

#### 7.2 FEATURES OF THE HPS

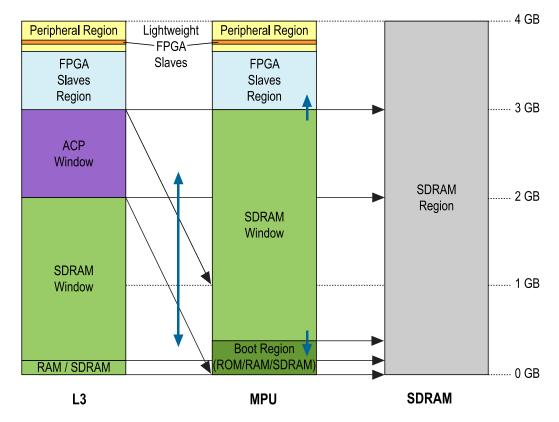

Figure 7-2. HPS Block Diagram [2, pp. 1-3]

The following list contains the main modules of the HPS:

#### Masters

- o MPU subsystem featuring dual ARM Cortex-A9 MPCore processors

- o General-purpose Direct Memory Access (DMA) controller

- o Two Ethernet media access controllers (EMACs)

- o Two USB 2.0 On-The-Go (OTG) controllers

- o NAND flash controller

- o Secure Digital (SD) / MultiMediaCard (MMC) controller

- o Two serial peripheral interface (SPI) master controllers

- o ARM CoreSight debug components

#### Slaves

- Quad SPI flash controller

- Two SPI slave controllers

- o Four inter-integrated circuit (I<sup>2</sup>C) controllers

- o 64 KB on-chip RAM

- o 64 KB on-chip boot ROM

- o Two UARTs

- Four timers

- Two watchdog timers

- Three general-purpose I/O (GPIO) interfaces

- o Two controller area network (CAN) controllers

- o System manager

- Clock manager

- Reset manager

- Scan manager

- o FPGA manager

#### 7.3 System Integration Overview

In this part, we briefly go through some features provided by the most important HPS components.

#### 7.3.1 MPU Subsystem

Here are a few important features of the MPU subsystem:

- Interrupt controller

- One general-purpose timer and one watchdog timer per processor

- One Memory management unit (MMU) per processor

The HPS masters the L3 interconnect and the SDRAM controller subsystem.

#### 7.3.2 SDRAM Controller Subsystem

The SDRAM controller subsystem is **MASTERED** by **HPS MASTERS** and **FPGA FABRIC MASTERS**. It supports DDR2, DDR3, and LPDDR2 devices. It is composed of 2 parts:

- SDRAM controller

- DDR PHY (interfaces the single port memory controller to the HPS I/O)

The DEO-Nano-SoC contains DDR3 SDRAM

#### 7.3.3 Support Peripherals

#### 7.3.3.1 System Manager

This is one of the most essential HPS components. It offers a few important features:

- PIN MULTIPLEXING (term used for the SOFTWARE configuration of the HPS I/O PINS by the PRELOADER)

- Freeze controller that places I/O elements into a safe state for configuration

- Low-level control of peripheral features not accessible through the control and status registers (CSRs)

The low-level control of some peripheral features that are not accessible through the CSRs is **NOT** externally documented. You will see this type of code when you generate your custom preloader, but must **NOT** use the constructs in your own code.

#### 7.3.3.2 FPGA Manager

The FPGA manager offers the following features:

- Manages the configuration of the FPGA portion of the device

- Monitors configuration-related signals in the FPGA

- Provides 32 general-purpose inputs and 32 general-purpose outputs to the FPGA fabric

#### 7.3.4 Interface Peripherals

#### 7.3.4.1 GPIO Interfaces

The HPS provides three GPIO interfaces and offer the following features:

- Supports digital de-bounce

- Configurable interrupt mode

- Supports up to 71 I/O pins and 14 input-only pins, based on device variant

- Supports up to 67 I/O pins and 14 input-only pins

The DEO-Nano-SoC has 67 I/O pins and 14 input-only pins

#### 7.3.5 On-Chip Memory

The following on-chip memories are **DIFFERENT** from any on-chip memories located in the FPGA fabric.

## 7.3.5.1 On-Chip RAM

The on-chip RAM offers the following features:

- 64 KB size

- High performance for all burst lengths

#### 7.3.5.2 **Boot ROM**

The boot ROM offers the following features:

- 64 KB size

- Contains the code required to support HPS boot from cold or warm reset

- Used **EXCLUSIVELY** for booting the HPS

The code in the boot ROM **CANNOT** be changed.

#### 7.4 HPS-FPGA INTERFACES

The HPS-FPGA interfaces provide a variety of communication channels between the HPS and the FPGA fabric. The HPS-FPGA interfaces include:

- **FPGA-to-HPS bridge** a high performance bus with a configurable data width of 32, 64, or 128 bits. It allows the FPGA fabric to master transactions to slaves in the HPS. This interface allows the FPGA fabric to have full visibility into the HPS address space.

- **HPS-to-FPGA bridge** a high performance bus with a configurable data width of 32, 64, or 128 bits. It allows the HPS to master transactions to slaves in the FPGA fabric. I will sometimes call this the "heavyweight" HPS-to-FPGA bridge to distinguish its "lightweight" counterpart (see below).

- **Lightweight HPS-to-FPGA bridge** a bus with a 32-bit fixed data width. It allows the HPS to master transactions to slaves in the FPGA fabric.

- FPGA manager interface signals that communicate with the FPGA fabric for boot and configuration.

- Interrupts allows soft IPs to supply interrupts directly to the MPU interrupt controller.

- HPS debug interface an interface that allows the HPS debug control domain to extend into the FPGA.

#### 7.5 HPS ADDRESS MAP

#### 7.5.1 HPS Address Spaces

The HPS address map specifies the address of slaves, such as memory and peripherals, as viewed by the HPS masters. The HPS has 3 address spaces:

| Name  | Description                | Size |

|-------|----------------------------|------|

| MPU   | MPU subsystem              | 4 GB |

| L3    | L3 interconnect            | 4 GB |

| SDRAM | SDRAM controller subsystem | 4 GB |

Table 7-2. HPS Address Spaces [2, pp. 1-13]

The following figure shows the relationships between the different HPS address spaces. The figure is **NOT** to scale.

Figure 7-3. HPS Address Space Relations [2, pp. 1-14]

The window regions provide access to other address spaces. The thin black arrows indicate which address space is accessed by a window region (arrows point to accessed address space).

The SDRAM window in the MPU can grow and shrink at the top and bottom (short blue vertical arrows) at the expense of the FPGA slaves and boot regions. The ACP window can be mapped to any 1 GB region in the MPU address space (blue vertical bidirectional arrow), on gigabyte-aligned boundaries.

The following table shows the base address and size of each region that is common to the L3 and MPU address spaces.

| <b>Region Name</b>      | Description                                       | <b>Base Address</b> | Size   |

|-------------------------|---------------------------------------------------|---------------------|--------|

| FPGA slaves             | FPGA slaves connected to the heavyweight HPS-to-  | 0xC0000000          | 960 MB |

|                         | FPGA bridge                                       |                     |        |

| HPS peripherals         | Slaves directly connected to the HPS (corresponds | 0xFC000000          | 64 MB  |

|                         | to all orange colored elements on Figure 6-4 and  |                     |        |

|                         | Figure 6-3)                                       |                     |        |

| Lightweight FPGA slaves | FPGA slaves connected to the lightweight HPS-to-  | 0xFF200000          | 2 MB   |

|                         | FPGA bridge                                       |                     |        |

Table 7-3. Common Address Space Regions [2, pp. 1-15]

## 7.5.2 HPS Peripheral Region Address Map

The following table lists the slave identifier, slave title, base address, and size of each slave in the HPS peripheral region. The *Slave Identifier* column lists the names used in the HPS register map file provided by Altera (more on this later).

| Slave Identifier | Slave Title                                       | Base Address | Size   |

|------------------|---------------------------------------------------|--------------|--------|

| STM              | STM                                               | 0xFC000000   | 48 MB  |

| DAP              | DAP                                               | 0xFF000000   | 2 MB   |

| LWFPGASLAVES     | FPGA slaves accessed with lightweight HPS-to-FPGA | 0xFF200000   | 2 MB   |

|                  | bridge                                            |              |        |

| LWHPS2FPGAREGS   | Lightweight HPS-to-FPGA bridge GPV                | 0xFF400000   | 1 MB   |

| HPS2FPGAREGS     | HPS-to-FPGA bridge GPV                            | 0xFF500000   | 1 MB   |

| FPGA2HPSREGS     | FPGA-to-HPS bridge GPV                            | 0xFF600000   | 1 MB   |

| EMAC0            | EMAC0                                             | 0xFF700000   | 8 KB   |

| EMAC1            | EMAC1                                             | 0xFF702000   | 8 KB   |

| SDMMC            | SD/MMC                                            | 0xFF704000   | 4 KB   |

| QSPIREGS         | Quad SPI flash controller registers               | 0xFF705000   | 4 KB   |

| FPGAMGRREGS      | FPGA manager registers                            | 0xFF706000   | 4 KB   |

| ACPIDMAP         | ACP ID mapper registers                           | 0xFF707000   | 4 KB   |

| GPIO0            | GPIO0                                             | 0xFF708000   | 4 KB   |

| GPIO1            | GPIO1                                             | 0xFF709000   | 4 KB   |

| GPIO2            | GPIO2                                             | 0xFF70A000   | 4 KB   |

| L3REGS           | L3 interconnect GPV                               | 0xFF800000   | 1 MB   |

| NANDDATA         | NAND controller data                              | 0xFF900000   | 1 MB   |

| QSPIDATA         | Quad SPI flash data                               | 0xFFA00000   | 1 MB   |

| USB0             | USB0 OTG controller registers                     | 0xFFB00000   | 256 KB |

| USB1             | USB1 OTG controller registers                     | 0xFFB40000   | 256 KB |

| NANDREGS         | NAND controller registers                         | 0xFFB80000   | 64 KB  |

| FPGAMGRDATA      | FPGA manager configuration data                   | 0xFFB90000   | 4 KB   |

| CAN0             | CANO controller registers                         | 0xFFC00000   | 4 KB   |

| CAN1             | CAN1 controller registers                         | 0xFFC01000   | 4 KB   |

| UARTO            | UARTO                                             | 0xFFC02000   | 4 KB   |

| UART1            | UART1                                             | 0xFFC03000   | 4 KB   |

| 12C0             | 12C0                                              | 0xFFC04000   | 4 KB   |

| I2C1             | 12C1                                              | 0xFFC05000   | 4 KB   |

| 12C2             | 12C2                                              | 0xFFC06000   | 4 KB   |

| 12C3             | 12C3                                              | 0xFFC07000   | 4 KB   |

| SPTIMER0         | SP Timer0                                         | 0xFFC08000   | 4 KB   |

| SPTIMER1         | SP Timer1                                         | 0xFFC09000   | 4 KB   |

| SDRREGS          | SDRAM controller subsystem registers              | 0xFFC20000   | 128 KB |

| OSC1TIMER0       | OSC1 Timer0                                       | 0xFFD00000   | 4 KB   |

| OSC1TIMER1       | OSC1 Timer1                                       | 0xFFD01000   | 4 KB   |

| L4WD0            | Watchdog0                                         | 0xFFD02000   | 4 KB   |

| L4WD1            | Watchdog1                                         | 0xFFD03000   | 4 KB   |

| CLKMGR           | Clock manager                                     | 0xFFD04000   | 4 KB   |

| RSTMGR           | Reset manager                                     | 0xFFD05000   | 4 KB   |

| SYSMGR           | System manager                                    | 0xFFD08000   | 16 KB  |

| DMANONSECURE     | DMA nonsecure registers                           | 0xFFE00000   | 4 KB   |

| DMASECURE        | DMA secure registers                              | 0xFFE01000   | 4 KB   |

| SPIS0            | SPI slave0                                        | 0xFFE02000   | 4 KB   |

| SPIS1            | SPI slave1                                        | 0xFFE03000   | 4 KB   |

| SPIM0            | SPI master0                                       | 0xFFF00000   | 4 KB   |

| SPIM1            | SPI master1                                       | 0xFFF01000   | 4 KB   |

| SCANMGR | Scan manager registers            | 0xFFF02000 | 4 KB  |

|---------|-----------------------------------|------------|-------|

| ROM     | Boot ROM                          | 0xFFFD0000 | 64 KB |

| MPUSCU  | MPU SCU registers                 | 0xFFFEC000 | 8 KB  |

| MPUL2   | MPU L2 cache controller registers | 0xFFFEF000 | 4 KB  |

| OCRAM   | On-chip RAM                       | 0xFFFF0000 | 64 KB |

Table 7-4. HPS Peripheral Region Address Map [2, pp. 1-16]

The programming model for accessing the HPS peripherals in Table 7-4 is the same as for peripherals created on the FPGA fabric. That is, every peripheral has a base address at which a certain number of registers can be found. You can then read and write to a certain set of these registers in order to modify the peripheral's behavior.

When using a HPS peripheral in Table 7-4, you do not need to hard-code any base address or peripheral register map in your programs, as Altera provides a header file for each one.

Three directories contain all HPS-related HEADER FILES:

- "<altera\_install\_directory>/<version>/embedded/ip/altera/hps/altera\_hps/hwlib/inclu de"

Contains HIGH-LEVEL header files that typically contain a few FUNCTIONS which facilitate control over the HPS components. These functions are all part of Altera's HWLIB, which was created to make programming the HPS easier. This directory contains code that is common to the Cyclone V, Arria V, and Arria 10 devices.

- "<altera\_install\_directory>/<version>/embedded/ip/altera/hps/altera\_hps/hwlib/inclu de/soc\_cv\_av"

Same as above, but more specifically for the Cyclone V and Arria V FPGA families.

- 3. "<altera\_install\_directory>/<version>/embedded/ip/altera/hps/altera\_hps/hwlib/inclu de/soc\_cv\_av/socal" Contains LOW-LEVEL header files that provide a peripheral's BIT-LEVEL REGISTER DETAILS. For example, any bits in a peripheral's register that correspond to undefined behavior will be specified in these header files.

To illustrate the differences among the high and low-level header files, we can compare the ones related to the FPGA manager peripheral:

2. ".../hwlib/include/soc\_cv\_av/socal/alt\_fpgamgr.h"

```

/* The width in bits of the ALT_FPGAMGR_CTL_EN register field. */

#define ALT_FPGAMGR_CTL_EN_WIDTH 1

/* The mask used to set the ALT_FPGAMGR_CTL_EN register field value. */

#define ALT_FPGAMGR_CTL_EN_SET_MSK 0x00000001

/* The mask used to clear the ALT_FPGAMGR_CTL_EN register field value. */

#define ALT_FPGAMGR_CTL_EN_CLR_MSK 0xfffffffe

```

An *important* header file is ".../hwlib/include/soc\_cv\_av/socal/hps.h". It contains the HPS component's full **REGISTER MAP**, as provided in Table 7-4.

Note however, that there exists **NO HEADER FILE** for the "heavyweight" HPS-to-FPGA bridge, as it is not located in the "HPS peripherals" region in Figure 7-3. Indeed, the "heavyweight" HPS-to-FPGA bridge is not considered a HPS peripheral, whereas the "lightweight" HPS-to-FPGA bridge is. Therefore, in order to use the "heavyweight" HPS-to-FPGA bridge, you will have to define a macro in your code, as follows:

#define ALT\_HWFPGASLVS\_OFST 0xc0000000

Note that HWLIB can only be directly used in a **BARE-METAL APPLICATION**, as it directly references physical addresses. The library can unfortunately **NOT** be used directly in a **LINUX DEVICE DRIVER**, because it uses standard header files that are not available in the kernel. Needless to say that a userspace linux program cannot use the library either, as the linux kernel would terminate a user process that tries to access any of these physical addresses directly.

#### 7.6 HPS BOOTING AND FPGA CONFIGURATION

Before being able to use the Cyclone V SoC, one needs to understand how the HPS boots and how the FPGA is configured. We'll first take a look at the ordering between the HPS and FPGA.

#### 7.6.1 HPS Boot and FPGA Configuration Ordering

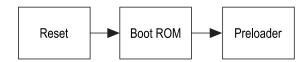

The *HPS BOOT* starts when the processor is released from reset (for example, on power up) and executes code in the internal *boot ROM* at the reset exception address. The boot process ends when the code in the boot ROM jumps to the next stage of the boot software. This next stage of the boot software is referred to as the *preloader*. Figure 7-4 illustrates this *initial* incomplete HPS boot flow.

Figure 7-4. Simplified HPS Boot Flow [2, pp. A-3]

The processor can boot from the following sources:

- NAND flash memory through the NAND flash controller

- SD/MMC flash memory through the SD/MMC flash controller

- SPI and QSPI flash memory through the QSPI flash controller using Slave Select 0

- FPGA fabric on-chip memory

The choice of the boot source is done by modifying the *BOOTSEL* and *CLKSEL* values *BEFORE THE DEVICE IS* **POWERED UP.** Therefore, the Cyclone V device normally uses a **PHYSICAL DIP SWITCH** to configure the *BOOTSEL* and *CLKSEL*.

The DEO-Nano-SoC can **ONLY BOOT** from **SD/MMC** flash memory, as its BOOTSEL and CLKSEL values are hard-wired on the board. Although its HPS contains all necessary controllers, the board doesn't have a physical DIP switch to modify the BOOTSEL and CLKSEL values.

**CONFIGURATION OF THE FPGA** portion of the device starts when the FPGA portion is released from reset state (for example, on power up). The control block (CB) in the FPGA portion of the device is responsible for obtaining an FPGA configuration image and configuring the FPGA. The FPGA configuration ends when the configuration image has been fully loaded and the FPGA enters user mode. The FPGA configuration image is provided by users and is typically stored in non-volatile flash-based memory. The FPGA CB can obtain a configuration image from the HPS through the FPGA manager, or from another external source, such as the *Quartus Prime Programmer*.

The following three figures illustrate the possible HPS boot and FPGA configuration schemes. Note that Cyclone V devices can also be fully configured through a JTAG connection.

Figure 7-5. Independent FPGA Configuration and HPS Booting [2, pp. A-2]

Figure 7-5 shows the scheme where the FPGA configuration and the HPS boot occur independently. The FPGA configuration obtains its image from a non-HPS source (*Quartus Prime Programmer*), while the HPS boot obtains its configuration image from a non-FPGA fabric source.

Figure 7-6. FPGA Configuration before HPS Booting (HPS boots from FPGA) [2, pp. A-2]

Figure 7-6 shows the scheme where the FPGA is first configured through the *Quartus Prime Programmer*, then the HPS boots from the FPGA fabric. The HPS boot waits for the FPGA fabric to be powered on and in user mode before executing. The HPS boot ROM code executes the preloader from the FPGA fabric over the HPS-to-FPGA bridge. The preloader can be obtained from the FPGA on-chip memory, or by accessing an external interface (such as a larger external SDRAM).

Figure 7-7. HPS Boots and Performs FPGA Configuration [2, pp. A-3]

Figure 7-7 shows the scheme under which the HPS first boots from one of its non-FPGA fabric boot sources, then software running on the HPS configures the FPGA fabric through the FPGA manager. The software on the HPS obtains the FPGA configuration image from any of its flash memory devices or communication interfaces, such as the SD/MMC memory, or the Ethernet port. The software is provided by users and the boot ROM is not involved in configuring the FPGA fabric.

#### 7.6.2 Zooming In On the HPS Boot Process

Figure 7-8. HPS Boot Flows [2, pp. A-3]

Booting software on the HPS is a multi-stage process. Each stage is responsible for loading the next stage. The first software stage is the *boot ROM*. The boot ROM code locates and executes the second software stage, called the *preloader*. The preloader locates, and *IF PRESENT*, executes the next software stage. The preloader and subsequent software stages are collectively referred to as *user software*.

The *reset*, *boot ROM*, and *preloader* stages are always present in the HPS boot flow. What comes after the preloader then depends on the type of application you want to run. The HPS can execute 2 types of applications:

- Bare-metal applications (no operating system)

- Applications on top of an operating system (linux)

Figure 7-8 shows the HPS' available boot flows. The *Reset* and *Boot ROM* stages are the only *fixed* parts of the boot process. Everything in the *user software* stages can be *customized*.

Although the DEO-Nano-SoC has a **DUAL**-processor HPS (CPU0 and CPU1), the boot flow only executes on CPU0 and CPU1 is under reset. If you want to use both processors of the DEO-Nano-SoC, then **USER SOFTWARE** executing on CPU0 is responsible for releasing CPU1 from reset.

#### 7.6.2.1 Preloader

The preloader is one of the most important boot stages. It is actually what one would call the boot "source", as all stages before it are unmodifiable. The preloader can be stored on external flash-based memory, or in the FPGA fabric.

The preloader typically performs the following actions:

- Initialize the SDRAM interface

- Configure the HPS I/O through the scan manager

- Configure pin multiplexing through the system manager

- Configure HPS clocks through the clock manager

- Initialize the flash controller (NAND, SD/MMC, QSPI) that contains the next stage boot software

- Load the next boot software into the SDRAM and pass control to it

The preloader does **NOT** release CPU1 from reset. The subsequent stages of the boot process are responsible for it if they want to use the extra processor.

## 8 Using the Cyclone V – General Information

#### 8.1 Introduction

The HPS component is a **SOFT** component, but it does **NOT** mean that the HPS is a softcore processor. In fact, the HPS exclusively contains **HARD LOGIC**. The reason it is considered a softcore component originates from the fact that it enables other soft components to interface with the HPS hard logic. As such, the HPS component has a *small footprint* in the FPGA fabric, as its only purpose is to connect the soft and hard logic together.

Therefore, it is possible to use the Cyclone V SoC in 3 different configurations:

- FPGA-only

- HPS-only

- HPS & FPGA

We will look at the *FPGA-only* and *HPS & FPGA* configurations below. We will not cover the *HPS-only* configuration as it is identical to the *HPS & FPGA* one where you simply don't load any design on the FPGA fabric. The configurations using the HPS are more difficult to set up than the *FPGA-only* one.

#### 8.2 FPGA-ONLY

Exclusively using the FPGA part of the Cyclone V is easy, as the design process is identical to any other Altera FPGA. You can build a complete design in *Quartus Prime* & *Qsys*, simulate it in *ModelSim-Altera*, then program the FPGA through the *Quartus Prime Programmer*. If you instantiated a Nios II processor in *Qsys*, you can use the *Nios II SBT* IDE to develop software for the processor.

The DEO-Nano-SoC has a lot of pins, which makes it tedious to start an FPGA design. It is recommended to use the **ENTITY** in [3] for your **TOP-LEVEL VHDL FILE**, as it contains all the board's FPGA and HPS pins.

After having defined a top-level module, it is necessary to map your design's pins to the ones available on the DEO-Nano-SoC. The *TCL SCRIPT* in [4] can be executed in *Quartus Prime* to specify the board's device ID and all its *PIN ASSIGNMENTS*. In order to execute the TCL script, place it in your quartus working directory, then run it through the "Tools > Tcl Scripts..." menu item in *Quartus Prime*.

#### 8.3 HPS & FPGA

#### 8.3.1 Bare-metal Application

On one hand, bare-metal software enjoys the advantage of having no OS overhead. This has many consequences, the most visible of which are that code executes at native speed as no context switching is ever performed, and additionally, that code can directly address the HPS peripherals using their *PHYSICAL* memory-mapped addresses, as no virtual memory system is being used. This is very useful when trying to use the HPS as a high-speed microcontroller. Such a programming environment is very similar to the one used by other microcontrollers, like the TI MSP430.

On the other hand, bare-metal code has one great disadvantage, as the programmer must continue to configure the Cyclone V to use all its resources. For example, we saw in 7.6.2.1 that the preloader does not release CPU1 from reset, and that it is up to the *user software* to perform this, which is the bare-metal application itself in this case. Furthermore, supposing CPU1 is available for use, it is still difficult to run multi-threaded code, as an OS generally handles program scheduling and CPU affinity for the programmer. The programmer must now manually assign code fragments to each CPU.

#### 8.3.2 Application Over an Operating System (Linux)

Running code over a linux operating system has several advantages. First of all, the kernel releases CPU1 from reset upon boot, so all processors are available. Furthermore, the kernel initializes and makes most, if not all HPS peripherals available for use by the programmer. This is possible since the linux kernel has access to a huge amount of device drivers. Multi-threaded code is also much easier to write, as the programmer has access to the familiar OS facilities for threading. Finally, the linux kernel is not restricted to running compiled C programs. Indeed, you can always run code written in another programming language providing you first install the runtime environment required (which must be available for ARM processors).

However, running an "EMBEDDED" application on top of an operating system also has disadvantages. Due to the virtual memory system put in place by the OS, a program cannot directly access the HPS peripherals through their physical memory-mapped addresses. Instead, one first needs to map the physical addresses of interest into the running program's virtual address space. Only then will it be possible to access a peripheral's registers. Ideally, the programmer should write a device driver for each specific component that is designed in order to have a clean interface between user code and device accesses.

At the end of the day, bare-metal applications and applications running code on top of linux can do the same things. Generally speaking, programming on top of linux is superior and much easier compared to bare-metal code, as its advantages greatly outweigh its drawbacks.

#### 8.4 GOALS

Let's start by defining what we want to achieve in this tutorial. We want to create a system in which both the HPS and FPGA can do some computation simultaneously. More specifically, we want the following capabilities:

- 1. A **NIOS II** processor on the **FPGA** must be able to access the LEDs connected to the **FPGA PORTION** of the device and will be responsible for creating a strobing light effect on the *lower* 4 LEDs.

- 2. The Nios II processor will use the DEO-Nano-SoC's on-chip FPGA memory.

- 3. The *HPS* must be able to use the LED and button that are directly connected to the *HPS PORTION* of the device. Pressing the button should toggle the LED.

- 4. The *HPS* must be able to access the LEDs connected to the *FPGA PORTION* of the device and will be responsible for creating a strobing light effect on the *upper* 4 LEDs.

- 5. The *HPS* must be able to use the ethernet port on the board.

- 6. The **HPS** must be able to use the microSD card port on the board to which we will write anything we want.

#### 8.5 Project Structure

The development process creates a lot more files compared to an FPGA-only design. We will use the folder structure shown in Figure 8-1 to organize our project. In this demo, we will use "DEØ\_Nano\_SoC\_demo" as the project name.

- The "hw" directory contains all hardware-related files.

- The "sw" directory contains all software-related files.

- The "sdcard" directory contains all final targets needed to create a valid sdcard from which the DEO-Nano-SoC can boot.

Figure 8-1. Project Folder Structure

Many steps have to be performed in order to configure the Cyclone V before you can use the HPS.

- The *HARDWARE* design is *IDENTICAL* whether you want to write bare-metal applications, or linux HPS applications.

- The **SOFTWARE** design is **DIFFERENT** for bare-metal and linux HPS applications.

The complete design for this tutorial can be found in DEO\_Nano\_SoC\_demo.zip [5].

## 9 Using the Cyclone V – Hardware

The details below give step-by-step instructions to create a full system from scratch.

Note that this version of the SoC-FPGA Design Guide is an adaptation from that of another board, the DE1-SoC. All the text in this DE0-Nano-SoC version has been adapted, but some of the figures in this document are copies from the DE1-SoC version of the guide. As such, you may find "DE1-SoC" or "DE1\_SoC" in some figures, and you can simply replace this text with "DE0-Nano-SoC" or "DE0\_Nano\_SoC", respectively.

## 9.1 GENERAL QUARTUS PRIME SETUP

- 1. Create a new *Quartus Prime* project. You only need to specify the project name and destination, as all other settings will be set at a later stage by a TCL script. For this demo, we will call our project "DEO\_Nano\_SoC\_demo" and will store it in "DEO\_Nano\_SoC\_demo/hw/quartus".

- 2. Download DE0\_Nano\_SoC\_top\_level.vhd [3] and save it in "DE0\_Nano\_SoC\_demo/hw/hd1". We will use this file as the project's top-level VHDL file, as it contains a complete list of pin names available on the DE0-Nano-SoC for use in your designs. Add the file to the *Quartus Prime* project by using "Project > Add/Remove Files in Project..." and set it as your design's top-level entity.

- 3. Download pin\_assignment\_DE0\_Nano\_SoC.tcl [4] and save it in "DE0\_Nano\_SoC\_demo/hw/quartus". This script assigns pin locations and I/O standards to all pins names in "DE0\_Nano\_SoC\_top\_level.vhd". Execute the TCL script by using "Tools > Tcl Scripts..." in Quartus Prime.

At this stage, all general *Quartus Prime* settings have been performed, and we can start creating our design. We want to use the HPS, as well as a Nios II processor in our design, so we will use the *Qsys* tool to create the system.

4. Launch the Qsys tool and create a new system. Save it under the name "soc\_system.qsys".

## 9.2 System Design with Qsys – Nios II

In this section, we assemble all system components needed to allow the Nios II processor to create a strobing light effect on the lower 4 LEDs.

- 5. Add an on-chip memory to the system. Use the following settings:

- Memory type

- Type: RAM (Writeable)

- Size

- Slave S1 Data Width: 32

- Total memory size: 128 KB (if you write "128k" and press <TAB>, the value will automatically be converted to "131072")

- 6. Add a Nios II processor to the system. You can choose any variant. In this demo, we use the "non-classic" Nios II processor, with configuration "Nios II/f".

- 7. Add a System ID Peripheral to the system. In *Qsys'* "System Contents" tab:

- Rename the component to "sysid"

- 8. Add a JTAG UART to the system. This serial console will be used to be able to see the output generated by the printf() function when programming the Nios II processor.

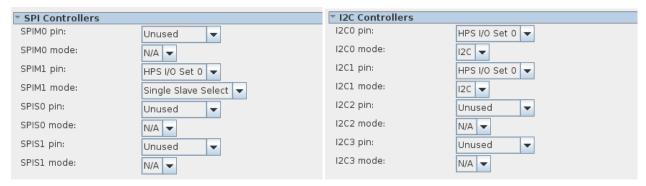

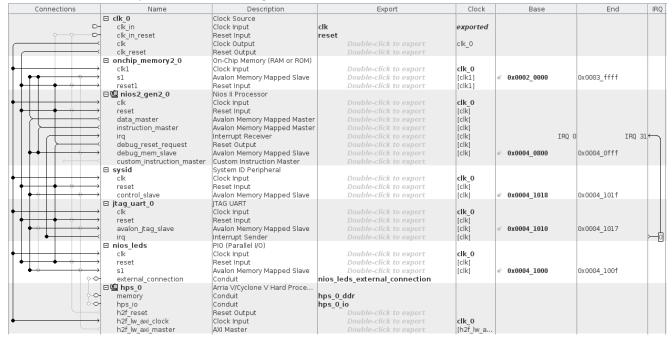

- 9. Connect the system as shown in Figure 9-1 below:

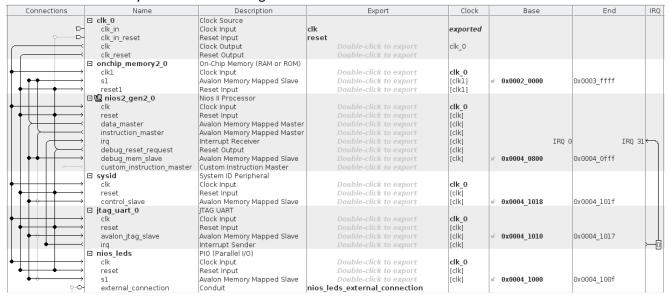

Figure 9-1. Basic Nios II System with on-chip memory and JTAG UART

- 10. Edit the Nios II processor and set "onchip memory2 0.s1" as its Reset and Exception vectors.

- 11. Add a PIO component to the system for the LEDs. The DEO-Nano-SoC has 8 LEDs, but we will only use the 4 lower ones with the Nios II processor, so we will use a 4-bit PIO component.

- Width: 4 bitsDirection: Output

- Output Port Reset Value: 0x00

In Qsys' "System Contents" tab:

- Rename the component to "nios leds"

- Export "nios\_leds.external\_connection"

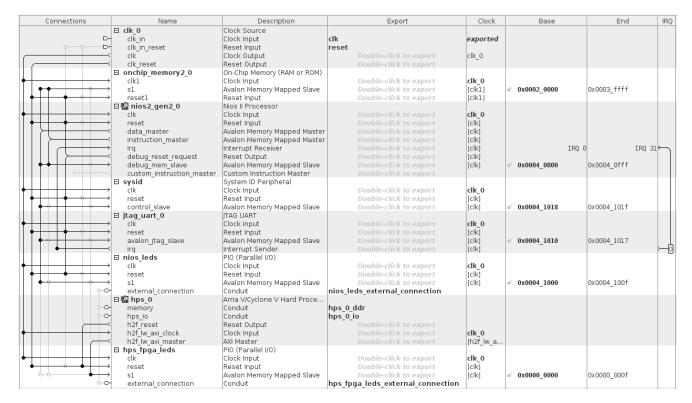

- 12. Connect the system as shown in Figure 9-2 below:

Figure 9-2. Adding LEDs to the System

## 9.3 System Design with Qsys – HPS

In this section, we assemble all system components needed to allow the HPS to access a button and LED connected directly to itself, as well as the 4 upper LEDs connected to the FPGA portion of the device.

Note: When using *Qsys* to manipulate any signal or menu item related to the HPS, the GUI will seem as though it is not responding, but this is not the case. The GUI is just checking all parameters in the background, which makes the interface hang momentarily. It is working correctly behind the scenes.

#### 9.3.1 Instantiating the HPS Component

- 13. To use the HPS, add an "Arria V/Cyclone V Hard Processor System" to the system.

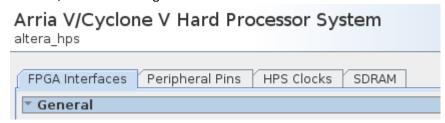

- 14. Open the HPS' parameters and have a look around. There are 4 tabs that control various aspects of the HPS' behaviour, as shown on Figure 9-3.

Figure 9-3. HPS Component Parameters

#### 9.3.1.1 FPGA Interfaces Tab

This tab configures everything related to the interfaces between the HPS and the FPGA. You can configure which bridges to use, interrupts, ...

- 15. We want to use the HPS to access FPGA peripherals, so we need to enable one of the following buses:

- HPS-to-FPGA AXI bridge

- Lightweight HPS-to-FPGA AXI bridge

Since we are not going to be using any high performance FPGA peripherals in this demo, we'll choose to enable the Lightweight HPS-to-FPGA AXI bridge.

- Set the FPGA-to-HPS interface width to "Unused".

- Set the HPS-to-FPGA interface width to "Unused".

By default, *Qsys* checks "Enable MPU standby and event signals", but we are not going to use this feature, so

• Uncheck "Enable MPU standby and event signals".

Qsys also adds an FPGA-to-HPS SDRAM port by default, which we are not going to use either, so

• Remove the port listed under "FPGA-to-HPS SDRAM Interface".

#### 9.3.1.2 Peripheral Pins Tab

This tab configures the physical pins that are available on the device. Most device pins have various sources, and are *multiplexed*. The pins can be configured to be sourced by the FPGA, or by various HPS peripherals.

#### 9.3.1.2.1 Theory

We want to use the HPS to access the button and LED that are directly connected to it. These HPS peripherals correspond to pins "HPS\_KEY\_N" and "HPS\_LED" on the device's top-level entity. We need to know how these 2 pins are connected to the HPS to access them. To find out this information, we have to look at the board's schematics. You can find the schematics in [6].

The right side of Figure 9-4 shows the area of interest on the DEO-Nano-SoC's schematics. We see that "HPS\_KEY\_N" and "HPS\_LED" are respectively connected to pins J18 and A20.

Figure 9-4. HPS\_KEY\_N & HPS\_LED on DEO-Nano-SoC Schematic. Note that the schematic uses "HPS\_KEY" instead of "HPS\_KEY\_N" as the name of the signal. This is a mistake, as the button is active-low, so the "\_N" in the name is warranted for clarity.

Figure 9-4 allows us to explain what *Qsys' Peripheral Pins* tab does. The *Qsys* GUI doesn't make any reference to pins J18 and A20, as they depend on the device being used, and cannot be generalized to other Cyclone V devices. However, the GUI does have references to what is displayed on the left side of Figure 9-4. We will

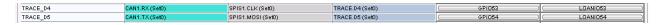

examine the details of pin J18, to which "HPS\_KEY\_N" is connected. The schematic shows that pin G21 is connected to 4 sources:

- TRACE D5

- SPIS1 MOSI

- CAN1\_TX

- HPS GPIO54

This can be seen in Qsys, as shown in Figure 9-5.

Figure 9-5. HPS KEY N & HPS LED on Qsys Peripheral Pins Tab

Depending on how you configure the Peripheral Pins tab, you can configure pin J18 to use any of the sources above. For example, if you want to use this pin as an SPI slave control signal, you would use the configuration shown in Figure 9-6.

Figure 9-6. Using Pin G21 for SPI

However, if you don't want to use any of the peripherals available at the top of the *Peripheral Pins* tab, then you can always use one of the 2 buttons on the right side of Figure 9-5:

- **GPIO**XY: Configures the pin to be connected to the **HPS' GPIO** peripheral.

- **LOANIO**XY: Configures the pin to be connected to the **FPGA** fabric. This pin can be exported from *Qsys* to be used by the FPGA.

#### 9.3.1.2.2 Configuration

- 16. We want the HPS to directly control the "HPS\_KEY\_N" and "HPS\_LED" pins. To do this, we will connect pins J18 and A20 to the HPS' GPIO peripheral.

- Click on the "GPI053" button. This corresponds to pin A20, which is connected to "HPS\_LED".

- Click on the "GPI054" button. This corresponds to pin J18, which is connected to "HPS\_KEY\_N".

- 17. We want to connect to our DEO-Nano-SoC with an SSH connection later in the tutorial, so we need to enable the Ethernet MAC interface.

- Configure "EMAC1 pin" to "HPS I/O Set 0" and the "EMAC 1 mode" to "RGMII", as shown in Figure 9-7.

- Click on the "GPI035" button. This corresponds to pin B14, which is connected to "HPS ENET INT N".

Figure 9-7. Ethernet MAC configuration

- 18. Our system will boot from the microSD card slot, so we need to enable the SD/MMC controller.

- Configure "SDIO pin" to "HPS I/O Set 0" and "SDIO mode" to "4-bit Data", as shown in Figure 9-8.

Figure 9-8. SD/MMC configuration

- 19. When initially configuring our system, we will need to connect a keyboard to our system. We will do this through a serial UART connection, so we need to enable the UART controller.

- Configure "UARTO pin" to "HPS I/O Set 0" and "UARTO mode" to "No Flow Control", as shown in Figure 9-9.

Figure 9-9. UART configuration

At this stage, you should have the same configuration shown in Figure 9-10.

Figure 9-10. Exported peripheral pins

- 20. Although not needed to satisfy the design goals defined in 8.4, we enable all the remaining HPS peripherals so future designs can use any of them if needed. Adding these peripherals does not increase FPGA resource usage as they are all hard peripherals connected directly to the HPS.

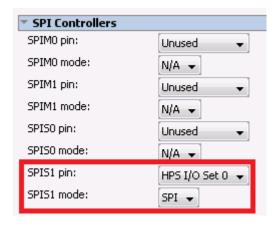

- Configure the USB controllers, SPI controllers, and the I<sup>2</sup>C controllers as shown in Figure 9-11.

- Click on the "GPI009" button. This corresponds to pin C6, which is connected to "HPS\_CONV\_USB\_N".

- Click on the "GPI040" button. This corresponds to pin H13, which is connected to "HPS\_LTC\_GPIO".

- Click on the "GPI061" button. This corresponds to pin A17, which is connected to "HPS\_GSENSOR\_INT".

Figure 9-11. USB, SPI, and I<sup>2</sup>C peripheral pin configurations

- 21. In Qsys' "System Contents" tab:

- Export "hps\_0.hps\_io" under the name "hps\_0\_io". This is a conduit that contains all the pins configured in the *Peripheral Pins* tab. We will connect these to our top-level entity later.

#### 9.3.1.3 HPS Clocks Tab

This tab configures the clocking system of the HPS. We will generally use the default settings here, so no need to change anything.

#### 9.3.1.4 SDRAM Tab

This tab configures the memory subsystem of the HPS.

- 22. We need to configure all clocks and timings related to the memory used on our system. The DE0-Nano-SoC uses DDR3 memory, so we need to consult its datasheet to find all the settings. The datasheet is available at [7]. Based on the memory's datasheet, we can fill in the following memory settings (you will soon see that it is quite tedious to enter these values):

- SDRAM Protocol: DDR3

- PHY Settings:

- Clocks:

- Memory clock frequency: 400.0 MHz

- PLL reference clock frequency: 25.0 MHz

- Advanced PHY Settings:

- Supply Voltage: 1.5V DDR3

- Memory Parameters:

- Memory vendor: Other

- Memory device speed grade: 800.0 MHz

- Total interface width: 32

- Number of chip select/depth expansion: 1

- Number of clocks: 1

- Row address width: 15

- Column address width: 10

- Bank-address width: 3

- Enable DM pins

- DQS# Enable

- Memory Initialization Options:

- Mirror Addressing: 1 per chip select: 0

- Mode Register 0:

- Burst Length: Burst chop 4 or 8 (on the fly)

- Read Burst Type: Sequential

- DLL precharge power down: DLL off

- Memory CAS latency setting: 7

- Mode Register 1:

- Output drive strength setting: RZQ/6

- ODT Rtt nominal value: RZQ/6

- Mode Register 2:

- o Auto selfrefresh method: Manual

- Selfrefresh temperature: Normal

- Memory write CAS latency setting: 7

- o Dynamic ODT (Rtt\_WR) value: Dynamic ODT off

- Memory Timing:

- tIS (base): 175 ps

- tIH (base): 250 ps

- tDS (base): 50 ps

- tDH (base): 125 ps

- tDQSQ: 120 ps

- tQH: 0.38 cycles

- tDQSCK: 400 ps

- tDQSS: 0.25 cycles

- tQSH: 0.38 cycles

- tDSH: 0.2 cycles

- tDSS: 0.2 cycles

- tINIT: 500 us

- tMRD: 4 cycles

- tRAS: 35.0 ns

- tRCD: 13.75 ns

- tRP: 13.75 ns

- tREFI: 7.8 us

- tRFC: 300.0 ns

- tWR: 15.0 ns

- tWTR: 4 cycles

- tFAW: 37.5 ns

- tRRD: 7.5 ns

- tRTP: 7.5 ns

- Board Settings:

- Setup and Hold Derating:

- Use Altera's default settings

- Channel Signal Integrity: